A 24Gb/s PAM-4 Clock and Data Recovery Circuit With High Jitter Tolerance

J.I.Bas

# A 24Gb/s PAM-4 Clock and Data Recovery Circuit With High Jitter Tolerance

by

# J.I.Bas

To obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on March 11 2024.

Student number:4386388Project Duration:September, 2022 - February 2024Thesis Committee:Dr. Masoud Babaie, TU Delft, Chair<br/>Dr. Fabio Sebastiano , TU Delft, Academic Supervisor

# Abstract

The escalating demand for higher data rates in modern communication networks are pushing more transmitters and receivers to use a modulation technique with more spectral efficiency, like pulse amplitude modulation 4-level (PAM-4).

On the receiver side, phase detection for PAM-4 has proven to be difficult with most receivers using phase detection for non return to zero (NRZ) data. This neglects most transitions and thus some phase information is lost. This results in low bandwidth and jitter tolerance, which is a problem in noisy communication systems where it will lead to a high bit error rate (BER).

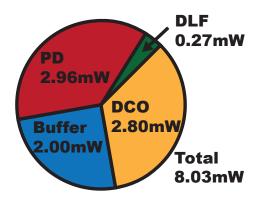

This thesis explores an integrated PAM-4 clock and data recovery (CDR) circuit utilizing a novel PAM-4 bang bang phase detector (BBPD) considering all data transitions. A digital oscillator with variable gain is used in order to achieve high jitter tolerance as-well as low jitter generation. at 24Gb/s the CDR consumes 8mW and generates 487fs of jitter. and has a 1 UI at 30MHz.

# Acknowledgements

First, I would like to thank my supervisor Dr. Masoud Babaie for his guidance during my thesis. His support kept me motivated and helped me reach new heights. The plentiful technical discussions we had were both enjoyable and insightful.

I also want to extend my gratitude to Dr. Fabio Sebastiano for reading my thesis and serving as committee.

My sincere appreciation goes to my daily supervisor, Rishabh Gurbaxani, for his help during the project. His work ethic inspired me during my thesis, and will continue to do so after.

I extend my special thanks to the Coolgroup and its members for the technical discussions and assistance, as well as for the lunch meetings and social events.

Finally, I want to thank my parents and friends for their continued support throughout the year, both in my academic life and my personal life.

J.I.Bas Delft, March 2024

# Contents

| Su      | Summary i                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                            |  |  |

|---------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|

| Ac      | knov                                            | vledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ii                                                         |  |  |

| Ac<br>1 |                                                 | oduction       7         Clock and Data Recovery       7         1.1.1       Pulse Amplitude Modulation       7         Phase Detection       7         1.2.1       Alexander Phase Detector       7         1.2.2       Baud-Rate Phase Detector       8         State of the Art       6                                                                                                                                                                                                                                                                                                                                           | <b>1</b><br>1<br>3<br>3<br>4<br>5<br>6<br>6<br>8<br>8<br>0 |  |  |

| 2       | <b>Sys</b> t<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | tem-Level Design12Phase Detection Method12Block Diagram14PAM-4 Phase Detector14DLF and Oscillator16Reference Calibration Loop17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2<br>4<br>4<br>6                                           |  |  |

| 3       | 3.1                                             | tem-Level Analysis19Discrete Time Domain Model193.1.1 BBPD Linearization193.1.2 Noise Sources21Phase Domain Model223.2.1 Limit Cycling22MATLAB Time Domain Model23Parameter Design243.4.1 Number of Bits243.4.2 Optimal Parameter Choice for Jitter25Jitter Tolerance273.5.1 Cycle Slipping21                                                                                                                                                                                                                                                                                                                                        | 9912334457                                                 |  |  |

| 4       | 4.1                                             | Suit Design         30           Phase Detector         30           4.1.1         Sample and Hold         30           4.1.2         Comparator         31           4.1.3         Transition Logic         32           4.1.4         Dynamic Flip-Flop         36           4.1.5         Multiplexer         38           4.1.6         Binary Current Steering DAC         40           4.1.7         Data extraction         42           4.1.8         Interpreter         42           4.1.9         Layout         44           4.2.1         Proportional Path         46           4.2.2         Integral Path         47 | 003568023466                                               |  |  |

|    | 4.3         DCO                                                                                                                                                                                                                                        |                                         |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 5  | Register Calibration Loop         5.1       Clock Domain Crossing         5.2       Calibration Loop Algorithm         5.3       Noise                                                                                                                 | <b>54</b><br>54<br>54<br>56             |

| 6  | Simulation Results         6.1       Locking Behavior         6.1.1       Phase Locking         6.1.2       Frequency Locking         6.2       Jitter Generation and Tolerance         6.3       Power Consumption         6.4       Comparison Table | <b>57</b><br>57<br>59<br>61<br>62<br>62 |

| 7  | Conclusion         7.1       Thesis Conclusion         7.2       Future Work         7.2.1       Current Design         7.3       Design Improvements         7.3.1       Data Rate         7.3.2       Variable DCO Gain                              | <b>64</b><br>64<br>64<br>65<br>65<br>65 |

| Re | eferences                                                                                                                                                                                                                                              | 67                                      |

| A  | MATLAB Code                                                                                                                                                                                                                                            | 70                                      |

| в  | Verilog Code                                                                                                                                                                                                                                           | 77                                      |

# Introduction

This chapter provides an introduction to the background information required to understand the thesis project. It outlines an overview of the basic clock and data recovery (CDR) concepts as well as pulse amplitude modulation (PAM) and recent developments in academia. Following this, it outlines the motivation and specifications of the thesis project. Finally, a thesis outline is presented along with the contributions of each chapter.

## 1.1. Clock and Data Recovery

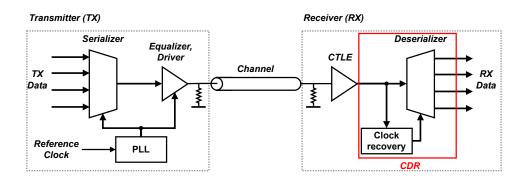

In wireline communications, a data stream is transmitted over a channel from a transmitter (TX) to a receiver (RX). A general block diagram is presented in Fig. 1.1. Data is serialized prior to being equalized and transmitted across a channel. At the receiver side, the incoming data is first amplified with a continuous time linear equalizer (CTLE) to compensate for channel loss. In most applications, the transmitter clock is not transmitted; this would require extra power and an extra channel. Therefore, the receiver has no information about the frequency and phase of the incoming data. A clock recovery circuit is used to align the receiver clock with the incoming data. With the recovered clock, a retimer or deserializer is used to create synchronized output data. Together, they make a CDR.

Figure 1.1: General TX-RX architecture.

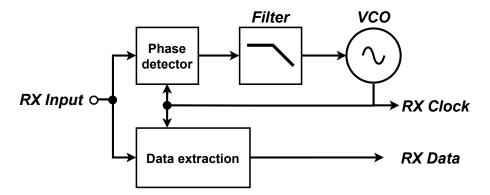

Most CDRs are based on a phase-locked loop (PLL) design, using the data as a reference instead of a crystal oscillator. A CDR always consists of a few necessary components, as depicted in Fig. 1.2. The incoming data is compared to the CDR clock by the phase detector (PD), a defining element in the CDR that will be discussed later. Subsequently, the phase information is transmitted through a filter to adjust the frequency of a voltage-controlled oscillator (VCO) to align its phase and frequency with the data. The updated clock is then used for a renewed phase comparison and data extraction.

Figure 1.2: Standard CDR block diagram

Since CDR topologies vary widely, comparing the state-of-the-art designs is complicated. The absence of a universally accepted figure of merit (F.O.M), due to the various, sometimes conflicting design metrics, adds to the challenge of comparison. The optimal CDR choice depends on the specific implementation requirements.

The main design metrics for evaluating a CDR are as follows:

- Data rate: The maximum rate at which data can be processed by the CDR.

- Jitter tolerance: The maximum amount of jitter the CDR can tolerate before bits are misinterpreted and bit errors occur.

- Jitter generation: The jitter that is generated by the CDR on the output clock.

- · Jitter transfer: The amount of jitter the CDR transfers from input to output.

- Power consumption: The power consumed by the CDR, typically measured in pJ/bit for a fair comparison.

Jitter tolerance and jitter transfer directly oppose each other. For jitter tolerance the input jitter needs to be tracked accurately to the output in order to keep a valid data sample, thus increasing jitter transfer. The bandwidth of the CDR needs to be increased in order to have better tracking. To minimise jitter transfer the input jitter needs to be filtered out and a small bandwidth is required, thus decreasing jitter tolerance.

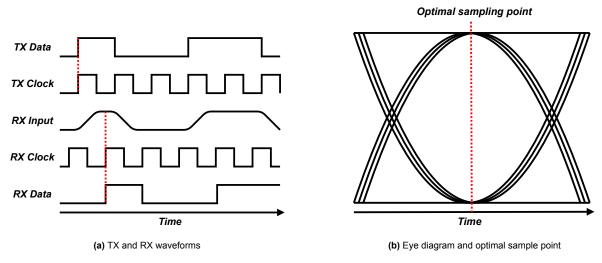

An important part of data recovery is data re-timing. This is done by sampling the data with the recovered clock. An optimal point exists where the bit error rate (BER) is minimal. This point is in the middle of a bit where amplitude noise, timing noise (jitter) and intersymbol interference (ISI) are least noticeable. This process is illustrated in Fig. 1.3. Half a symbol shift is therefore required between the received data rising edge and internal clock rising edge.

Figure 1.3: CDR data recovery.

#### 1.1.1. Pulse Amplitude Modulation

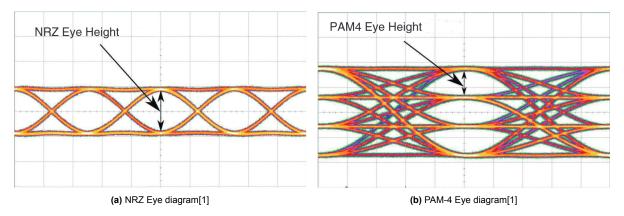

The previously discussed phase detectors were illustrated using non-return-to-zero (NRZ) data. A form of pulse amplitude modulation (PAM) with two levels, where the data is encoded in the amplitude of the signal. PAM-4 utilizes four different amplitudes, an eye diagram for NRZ data is illustrated in Fig.1.4a and for PAM-4 in 1.4b. Due to the higher possible states, the data rate is twice the baud rate. This is beneficial when high data rates are required. Loss in the medium is frequency-dependent, therefore it is better to transmit data at a lower frequency. However, since the states are only separated by  $\frac{1}{3}$  of the signal amplitude, the signal to noise ratio is -9.5dB lower than NRZ data without channel loss. This creates an optimum modulation type depending on the channel loss and data rate [1].

Figure 1.4: Eye diagrams for different PAM modulation techniques

# 1.2. Phase Detection

One of the most defining blocks of a CDR is the PD. In order to understand the challenges in PAM-4 phase detection, the topic of this thesis, it is beneficial to first analyze the phase detection methods of NRZ data. Not all common methods will be covered. Many topologies rely on the binary nature of NRZ data to extract the phase information and are difficult to adjust to PAM-4 data, with the Hogge PD being a prime example [2].

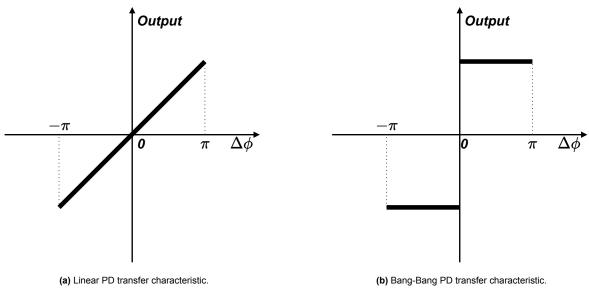

Phase detectors can be divided into two classes based on the type of information they provide to the rest of the CDR loop. A linear phase detector has a linear relation between input and output, as plotted in Fig. 1.5a. This generally allows for faster phase and frequency locking, but phase detection can be more difficult since the phase detector needs to provide a linear relation between the input phase error and its output. Linear PDs are mostly used in analog CDR loops where complex calculations can be

done easily in the current domain at no extra cost.

The Bang-Bang phase detection (BBPD) provides only binary information (early or late) to the loop filter, as illustrated in Fig. 1.5b. This simplicity allows for easy implementation in digital PLL-based CDRs. Since the phase information is already 1-bit quantized, no additional step is required to move from the analog to the digital domain. However, the simplicity comes at a cost. Since both large and small phase errors result in the same update to the VCO, the CDR must either over- or under-compensate the VCO phase error. Under compensation will result in slow locking while over compensation will result in additional jitter generation due to the increased phase step (dithering jitter) creating a trade-off between the two. A more in-depth analysis of BBPD is done in Chapter 3 3.

Figure 1.5: Phase detector classes

#### 1.2.1. Alexander Phase Detector

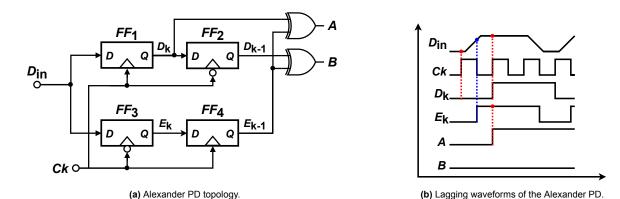

The Alexander PD [3] uses positively and negatively clocked flip-flops to detect the phase error. The topology is presented in Fig.1.6a. To illustrate the functionality, the waveforms for a lagging clock are presented in Fig.1.6b. The input data is sampled at the positive clock flank with  $FF_1$  to create  $D_k$  and at the negative clock flank with  $FF_2$  to create  $E_k$ .  $D_k$  represents the data samples and  $E_k$  represents the edge or transition samples. On the subsequent clock flanks, the states are propagated to the next flip-flops in order to store the samples. The Alexander PD compares the transition sample  $E_{k-1}$  to both its preceding bit  $D_{k-1}$  and its proceeding bit  $D_k$  to determine the phase information. The samples of  $E_k$  are not taken at rail-to-rail voltage since the sample is taken during a transition; the flip-flop acts as a 1-bit quantizer. If  $E_{k-1}$  and  $D_k$  are opposite, it means that the edge sample was taken closer to  $D_{k-1}$  and the clock phase is leading the input data. Signal B becomes high in this case. If  $E_{k-1}$  is equal to  $D_k$ , as illustrated in the figure, the phase is lagging and signal A becomes high.

Figure 1.6: Alexander PD.

Comparing whether the transition  $E_{k-1}$  was closer to  $D_k$  or  $D_{k-1}$  can be extended to PAM-4 data. This does pose extra challenges since a 1-bit quantizer is not sufficient for the multi-level data.

#### 1.2.2. Baud-Rate Phase Detector

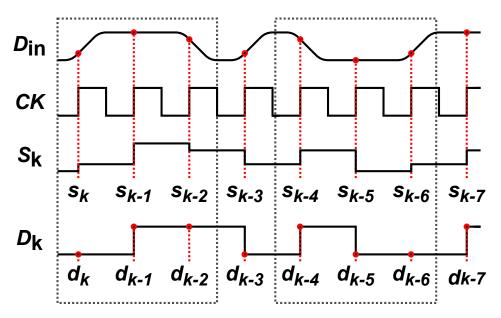

While the Alexander PD takes samples with twice the bit rate, a Mueller Muller PD [4] detects phase error with only data samples. Therefore, it is also known as a "Baud-Rate PD". Several types of algorithms exist, each with its own applicable data patterns. Let us examine an algorithm for baud rate detection to understand the basic principles.

In the waveforms and samples of Fig.1.7, the clock signal CK is lagging the data stream  $D_{in}$  significantly. The phase detector takes samples at each positive clock flank to create  $S_k$ . The samples are also resolved to the nearest data point to create  $D_k$ . For data patterns with one transition and two consecutive bits, the following formula can determine phase information:

Phase error =  $(s_k \cdot d_{k-1}) - (s_{k-1} \cdot d_k)$ If  $d_k \neq d_{k-1}$ And  $d_{k-1} = d_{k-2}$

The first three samples are  $s_k = -0.25$ ,  $s_{k-1} = 0.5$ , and  $s_{k-2} = 0.25$  relative to the mid voltage. The resolved data  $d_k$ ,  $d_{k-1}$  and  $d_{k-2}$  is -1, 1, 1 respectively, and a quantized data stream will correspond to this. Applying the aforementioned algorithm:  $-0.25 \cdot 1 - 0.5 \cdot -1 = 0.25$  yields a positive value corresponding to a lagging clock. For samples  $s_{k-4} = 0.25$ ,  $d_{k-5} = -0.5$  and  $d_{k-2} = 0.25$ , the same can be computed:  $0.25 \cdot -1 - -0.5 \cdot 1 = 0.25$  again indicates a lagging clock. Not all data patterns provide phase information. Alternating bits  $s_{k-2}$ ,  $s_{k-3}$ ,  $s_{k-4}$  will result in 0 for lagging and leading cases.

Figure 1.7: Baud-Rate PD waveforms.

Baud-rate PD relies on ISI and the channel attenuation to compute the phase information. The preceding bit attenuates the amplitude of the proceeding bit. The point at which the data sample is taken determines how much ISI is measured. Although the reduced sample rate is beneficial for high-speed data links, there are several drawbacks. As mentioned earlier, not all data patterns provide phase information, requiring some signal processing. Other baud rate detectors may use different algorithms requiring different data streams. Furthermore, the accuracy of the phase information depends on the level of ISI; if ISI is too low to be measured (also dependent on the sample resolution), no phase information can be detected. In the previous example, phase information can only be extracted when the clock shifts enough for ISI to occur. As the data stream has limited ISI, the clock can wander freely in a large range, resulting in high jitter.

Due to these intrinsic qualities of the Mueller-Muller PD, it is widely adopted in long-range high-speed communication systems where the benefits of the lower sample rate become crucial, and significant ISI occurs due to frequency-dependent attenuation of the channel. Since the Mueller Muller PD relies on ISI, less equalization is needed in these systems. However, a high-speed ADC is required, usually leading to high power consumption. The principle of baud-rate PD can be extended to PAM-4 with more complex algorithms.

## 1.3. State of the Art

As the industry transitions towards PAM-4 wireline communication, more research is focused on enhancing receivers. The phase detector is a relatively new subject and there is no dominant method yet. This section discusses several state-of-the-art PAM-4 phase detectors, their primary advantages, and their limitations.

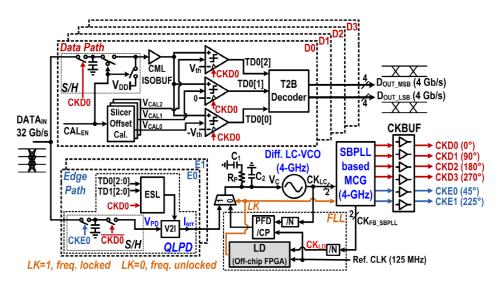

#### 1.3.1. PAM-4 Linear PD Based CDR

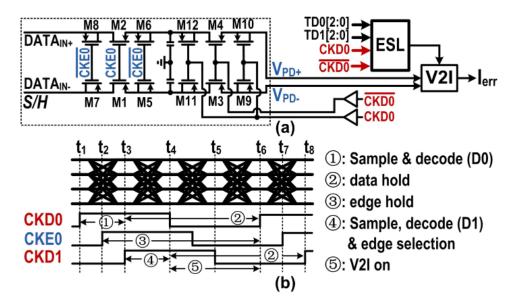

In [5], a quarter-rate linear phase detector (QLPD) is implemented using a sample and hold technique. The detailed schematic of the proposed CDR can be seen in Fig.1.8. Since the CDR runs at a quarter rate of the baud rate, four data recovery paths are required, each using a different clock phase. Only two phase detection paths are used to reduce power consumption. The CDR creates a voltage proportional to the phase error and converts it to current using a V/I amplifier. A simple RC low pass filter is used to update the LC-VCO. The VCO is used in a second PLL to generate the multi-phase clock required for quarter rate operation. The data path employs a sample and hold technique with 3 comparators to slice the data and a decoder to create an MSB and LSB output.

Figure 1.8: Block diagram of [5].

The phase detector schematic is presented in Fig.1.9. At CKE0, the differential data is sampled. Since only major transitions are considered, the ideal middle voltage is 0V, a phase offset will result in a voltage offset from this ideal point. A minor transition from -1 to +1 also results in a middle voltage of 0V, but due to the different slope, this transition would result in a different gain. Edge selection logic (ELS) uses the data paths to connect or disconnect the V/I stage. When a non-major transition occurs, no current should be provided to the loop filter since it will not provide correct information. Rising and falling transitions result in different polarities for the same phase offset. In order to compensate for this problem, the ESL switches the positive and negative input to the V/I stage between rising and falling transitions.

Figure 1.9: QRLPD schematic and waveforms [5].

The phase detection method shows a few issues. Although linear PD is good for avoiding the dithering jitter of bang-bang phase detection, due to the different slopes and middle voltages, it becomes impossible to consider all data transitions. Since only major transitions are considered and there are only two phase detectors, the update density is low at 0.0625. This results in a low jitter tolerance of 1UI at 2MHz. Due to the linear phase detection, accompanied by the LC oscillator and second PLL loop for phase generation, the CDR has very low jitter generation of 352fs while only consuming 0.46pJ/bit. The CDR is fabricated in 40nm technology.

#### 1.3.2. PAM-4 Alexander PD Based CDR

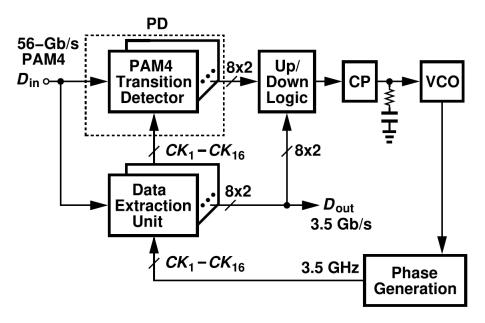

In [6], a PAM-4 CDR is proposed, based on the bang-bang Alexander PD. The block diagram can be seen in Fig.1.10. Due to the high data rate, parallel PDs and data extraction units are used. Current mode logic is used to update a VCO operating at the baud rate. A latch-based clock divider is used to create the necessary clock phases for phase detection and data recovery.

Figure 1.10: Block diagram for [6].

Each phase detector takes three consecutive samples: The leading bit,  $V_A$ , the lagging bit  $V_B$ , and the transition  $V_E$ . The sum  $V_{sum} = V_A + V_B - 2V_E$  shows if the transition was closer to  $V_A$  or  $V_B$  and is calculated in the current domain with four V/I stages, one extra is needed for offset calibration. Again, a problem arises with the ambiguity of the polarity of  $V_{sum}$ . If a falling transition occurred, a leading clock results in a high  $V_{sum}$  but a rising transition results in a negative  $V_{sum}$ . To counter this problem, the direction,  $V_B - V_A$ , is calculated in a similar fashion. The output of the phase detectors cannot immediately control the charge pumps due to non-transitions where the VCO should not be updated. Three charge pumps are controlled by each phase detector and activated by the data extraction unit when a transition occurred. The phase detector considers all data transitions leading to a high jitter tolerance of 1UI at 10MHz.

The CDR is fabricated in 28nm technology and has an incredibly low power consumption of 0.14pJ/bit, while maintaining 574fs jitter generation. There are still a few downsides to this design, first the use of an LC oscillator lowers the jitter generation but increases the area, this is especially important since this design is meant for die-to-die communication. Since the phase detection method requires a lot of calculation, a high loop delay is introduced, lowering the phase margin. Finally, since each level transition activates a charge pump, a different amount of charge pumps are used for different transitions. Major transitions activate all three while minor transitions only activate one. This leads to a variable phase detector gain and makes the loop difficult to optimize.

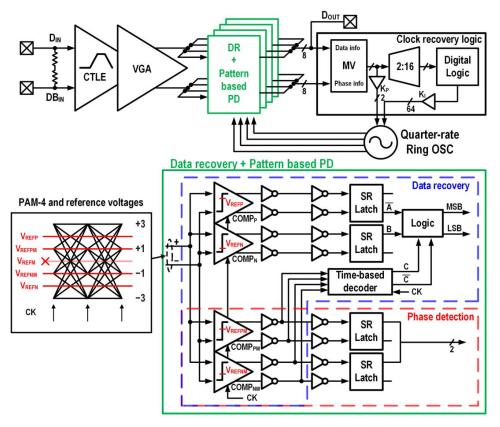

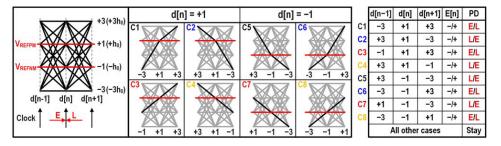

#### 1.3.3. Baud-Rate PAM-4 PD Based CDR

In [7], a pattern-based baud rate phase detector is used. A diagram of the complete CDR and PD can be seen in Fig.1.11. Four phase detectors are placed in parallel to allow for a quarter rate operation. The majority voter (MV) assesses the major status among the phase detectors. Using MV instead of individual PD outputs relaxes the speed at which the digital low pass filter (DLF) has to operate. The DCO receives updates with a proportional path directly from the MV. Digitally synthesized logic is employed for the integral path. Data recovery is facilitated using two comparators and reusing the phase detector comparators in combination with a time-based decoder, omitting the use of an extra

comparator.

Figure 1.11: Block diagram for [7].

The phase detector uses three consecutive data points as a pattern. A transition diagram is shown in 1.12. Each phase detector has two comparators with reference points -1 and 1. When two consecutive data transitions occur with either -1 or 1 as the middle data point, it can be determined if the data falls early or late depending on the output of the comparators. Only an update density of 0.125% is achieved with this method and with the majority voter algorithm this further falls to 0.103%. When no equalization is present the locking points of transitions  $C_{3,4,7,8}$  differ from  $C_{1,2,5,6}$ . Therefore the phase detector has two options, one where all eight transitions are considered and one for under-equalized signals where only  $C_{1,2,5,6}$  are considered.

Figure 1.12: Transition diagram for [7].

The CDR is fabricated in 28nm technology. The drawbacks and advantages of baud rate phase detectors become clear in this design. With a power consumption of 0.83pJ/bit including the continuous time linear equalization (CTLE), it is a very efficient design. However, the jitter performance is lacking with an integrated jitter from 1kHz to 100MHz of 430fs, a smaller bandwidth than previously discussed papers. The jitter tolerance exceeds the mask for CEI-56G-VSR, which corresponds to a 1UI jitter

tolerance at 0.8MHz, a relatively low standard.

#### 1.4. Thesis Motivation

As discussed before, wireline PAM-4 transceivers are becoming more popular due to the higher spectral efficiency the modulation technique provides. Many ADC-based PAM-4 CDR's exist [8] [9] [10]. High-speed ADCs have a large power consumption, making these designs inefficient. Transceivers with phase detection in the analog domain [11], [12] [13] have provided an adequate solution for this. However, these designs do not consider all data transitions, which can improve both jitter generation and tolerance.

To better understand this a phase domain model of an analog CDR is presented in Fig.1.13. The output clock phase tracks the input data phase:

Figure 1.13: General phase domain model for CDR.

$$\Phi_{out} = H_{cl} \Phi_{in} \tag{1.1}$$

UUU() = UOO()

$$H_{cl} = \frac{Kpd(s) \cdot KVI(s) \cdot LPF(s) \cdot VCO(s)}{1 + Kpd(s) \cdot KVI(s) \cdot LPF(s) \cdot VCO(s)}$$

(1.2)

A better tracking of the input phase means more jitter tolerance is achieved. This can be done by increasing the bandwidth or tuning the gain of each individual stage, as done in [14] [15]. However, increasing the phase detector gain is most beneficial. Each stage provides an additional noise source. Due to the closed-loop operation of the CDR, each noise source will be suppressed by the gain of the preceding block. The output-referred noise of each source can be expressed as:

$$\phi_{out,data,n}^2 = \phi_{data,n}^2 |H_{cl}(s)|^2$$

(1.3)

$$\phi_{out,pd,n}^2 = \phi_{pd,n}^2 |H_{cl}(s)|^2 \left| \frac{1}{Kpd(s)} \right|^2$$

(1.4)

$$\phi_{out,vi,n}^2 = \phi_{vi,n}^2 |H_{cl}(s)|^2 \left| \frac{1}{Kpd(s) \cdot KVI(s)} \right|^2$$

(1.5)

$$\phi_{out,lpf,n}^{2} = \phi_{lpf,n}^{2} |H_{cl}(s)|^{2} \left| \frac{1}{Kpd(s) \cdot KVI(s) \cdot LPF(s)} \right|^{2}$$

(1.6)

$$\phi_{out,vco,n}^{2} = \phi_{vco,n}^{2} |H_{cl}(s)|^{2} \left| \frac{1}{Kpd(s) \cdot KVI(s) \cdot LPF(s) \cdot VCO(s)} \right|^{2}$$

(1.7)

Looking at these equations, each noise source, except for the input noise, can be suppressed with a higher phase detector gain. The phase detector gain is linearly proportional to the transitions considered and transition density.

$$Kpd(s) \propto \alpha_T$$

(1.8)

Since the transition density of PAM-4 is 0.75 instead of 0.5 for NRZ, this provides an opportunity for improvement in jitter generation and jitter tolerance of the CDR.

The objective of this thesis is to design a PAM-4 CDR for wireline communication with low jitter generation and high jitter tolerance by considering all data transitions for phase detection. To have a practical design, a high data rate, low power consumption, and low area should also be achieved. The aimed design specifications are presented in table 1.1.

| Design Metric     | Specification   |

|-------------------|-----------------|

| Modulation        | PAM-4           |

| Data rate         | 24Gb/s          |

| Jitter generation | <500fs          |

| Jitter tolerance  | 1 UI at 30MHz   |

| Power consumption | 0.5pJ/bit       |

| Oscillator Type   | Ring oscillator |

Table 1.1: Design requirements.

# 1.5. Thesis Structure

The thesis is structured into several chapters to describe the design and analysis of the PAM-4 CDR:

- Chapter 1: Introduction This chapter introduces the thesis and discusses background information for PAM-4 CDR.

- Chapter 2: System-Level Design A novel phase detection method is proposed and based on this a system-level design is presented.

- Chapter 3: System-Level Analysis A linear method is proposed to analyze the system and choose optional design parameters.

- Chapter 4: Circuit Design This chapter elaborates on the design of the RF and mixed-signal blocks in the CDR.

- Chapter 5: Register Calibration Loop The calibration loop is discussed and analyzed.

- Chapter 6: Simulation Results The simulation results are discussed and compared to the expected performance.

- Chapter 7: Conclusion This chapter concludes the thesis and provides suggestions for improvement and future work.

$\sum$

# System-Level Design

This chapter delves into the system-level design and expands on the architecture of the PAM-4 CDR. First, the difficulties of PAM-4 phase detection will be discussed, and a novel phase detection method will be proposed. Subsequently, from the functionality requirements, a system-level design will be constructed for the whole CDR.

# 2.1. Phase Detection Method

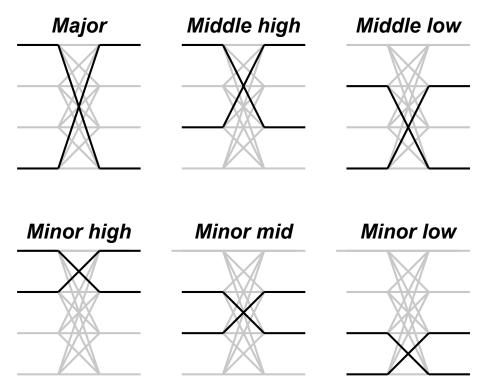

The theoretical benefits of a PAM-4 considering all data transitions have been explained in 1.4. However, this poses a few problems in practice. The adoption of PAM-4 complicates the phase detector due to the quaternary nature of the input. Unlike NRZ data, where only transitions between maximum and minimum voltage are considered, PAM-4 modulation involves the use of voltages between these levels for data symbols. This leads to many more transitions, as illustrated in Fig. 2.1. The transitions differ in three fundamental aspects: different slopes, different directions and different middle voltages, making a universal approach to each transition impossible.

Figure 2.1: Different transition types in PAM-4 modulation.

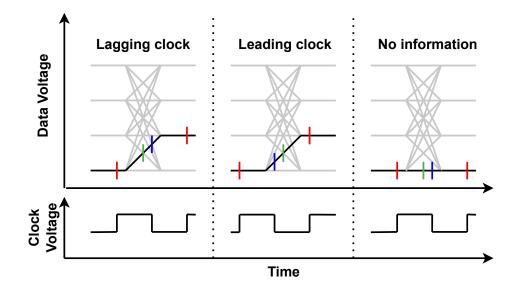

Fig. 2.2 presents a graphical illustration of the proposed phase detection method. To utilize all data transitions for clock recovery, the PD will take three samples. First, a data sample (shown in red), next, a transition sample (shown in blue) and finally, a second data sample (again in red). With the two data samples, the expected middle voltage (shown in green) can be determined. This reference voltage is compared to the transition sample to determine if the phase is leading or lagging with respect to the data. This method ensures all twelve transitions can be considered for determining the phase error.

Figure 2.2: Graphical illustration of the phase detection method.

The comparison of the reference voltage and transition sample alone is insufficient for determining phase information. Due to the consideration of both rising and falling transitions, a leading clock can result in either a higher or a lower sample voltage. This can be seen in the leading and lagging clock examples in Fig. 2.2. In order to circumvent this problem, the sign of the comparison needs to be evaluated along with the direction of the transition. An additional consideration arises when two consecutive bits occur. this will result in no information on the phase of the data, and therefore the clock should not be updated.

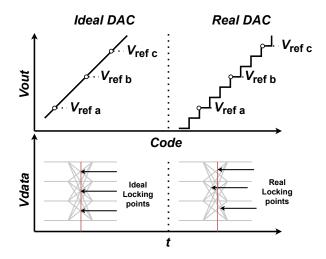

The use of reference voltages introduces potential challenges. The attenuation of the channel is unknown, and variations in transition times can further complicate the determination of the middle voltage (in relation to time). This renders the exact middle voltage unknown. If predetermined reference voltages are used, the locking points of the transitions can differ. To address this, a calibration loop that can adjust the reference voltages to an optimal point is essential.

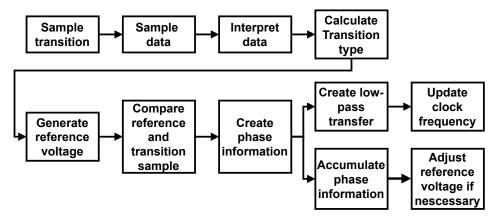

The phase detection method and challenges described above can be summarized into several circuit functions for the CDR, a flowchart is presented in Fig. 2.3.

Figure 2.3: Flowchart of circuit functions

# 2.2. Block Diagram

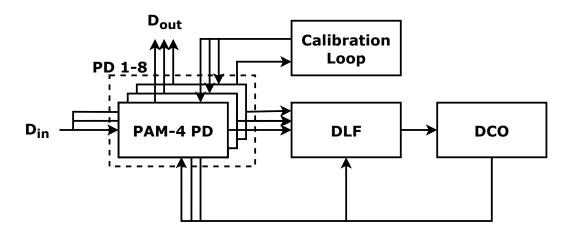

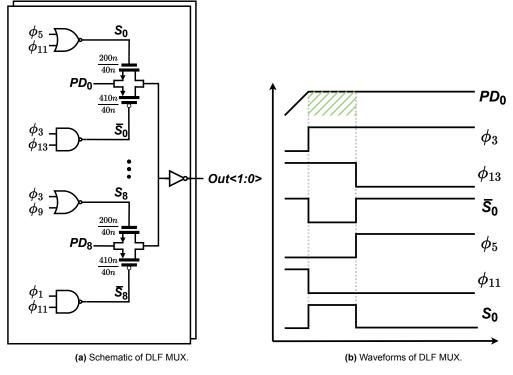

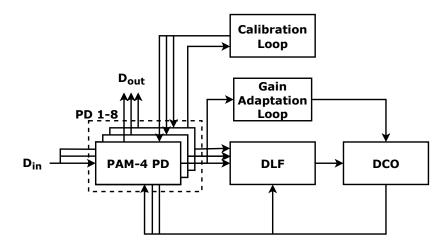

The proposed top-level block diagram of the system can be seen in Fig. 2.4. In order to facilitate enough computation time, eight phase detectors operating at  $\frac{1}{8}$  of the baud rate, operate in parallel. Given that data extraction is required for phase detection, the PD's also generate synchronized output data. The PD's provide tertiary information to the digital loop filter (DLF). To limit complexity, a bangbang PD is employed by the system.

The DLF consists of a proportional path for phase error correction and an integral path for frequency errors [16]. The digitally controlled oscillator (DCO) generates 16 clock phases for the operation of the PDs. Finally, the calibration loop provides the reference voltages to each phase detector and receives phase information from one PD. Due to the low frequency of the calibration loop, phase information of only one PD is sufficient for calibration. Considering all eight PD outputs for calibration will result in unnecessary power consumption while not significantly improving performance. This block diagram ensures the effective operation of the PAM-4 CDR.

Figure 2.4: Block diagram of the PAM-4 CDR

## 2.3. PAM-4 Phase Detector

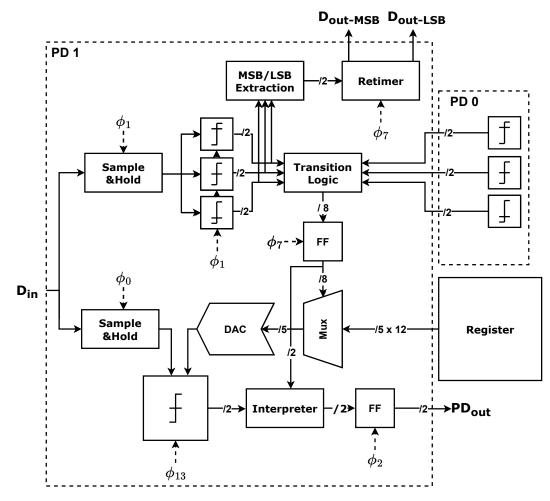

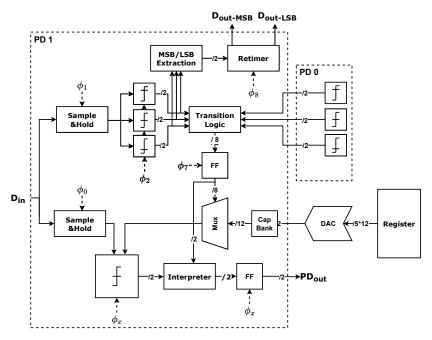

The PD is the most complex block. A block diagram can be seen in Fig. 2.5. The accommodating timeline of the calculation steps and data can be seen in Fig. 2.6

Figure 2.5: Block diagram of the PAM-4 Phase Detector

Figure 2.6: Timeline of calculation steps for 12GHz input data

The sample-and-hold circuits are designed to capture voltage samples of the incoming data at  $\phi_0$  and  $\phi_1$ , corresponding to the transition and data, respectively. The timeline positions the transition sample at 0ps since this is the moment the phase information is measured.

The data sample is sliced by three comparators at  $\phi_1$  to determine the corresponding symbol. Each phase detector only takes one data sample, the leading data sample is sliced by the previous PD. The transition logic calculates which transition occurred with the two symbols. To maintain the validity of

the transition logic outputs after the slicers reset, flip-flops are used as buffers. This step takes 208ps and is ready at  $\phi_7$ .

The flip-flops generate control signals for the multiplexer (MUX). This can be done directly with the flop-flop output due to the MUX design. A binary digital-to-analog converter (DAC) is used to create a reference voltage. The MUX selects the bits of the register corresponding to the correct transition and provides them to the DAC. The register is incorporated in the calibration loop outside of the phase detector. All PDs require the same information. This step takes 250ps and is ready at 500ps after the transition sample.

The generated reference voltage is compared to the transition sample using a comparator. However, as discussed previously, this comparison alone does not provide phase information. An interpreter is needed to combine the comparator information with the direction of the transition and to create tertiary phase information in the case of non-transitions. Finally, the phase information needs to be buffered to maintain its validity for a complete clock cycle. The last step takes  $208p_s$  and is done at  $\phi_2$ , 9 symbols after the initial measurement. The information is passed to the DCO at  $\phi_3$  due to the delay of the flip-flop.

# 2.4. DLF and Oscillator

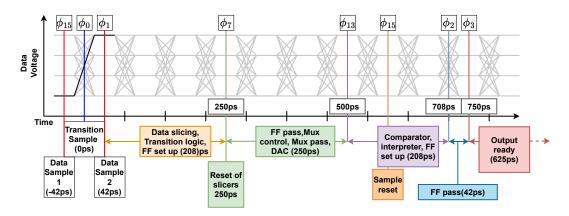

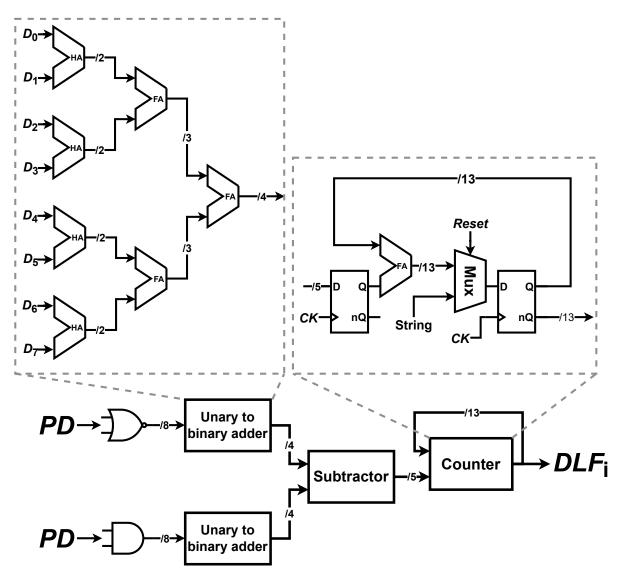

The digital low-pass filter needs to create a low-pass characteristic for the phase information provided by the phase detectors. The DLF consists of a proportional path and an integral path. The block diagram is presented in Fig. 2.7.

Figure 2.7: Block diagram of the DLF and oscillator

The proportional path of the filter must cycle through the outputs of the eight phase detectors. This needs to happen at the data frequency to maintain the instantaneous characteristic of the proportional path. Given that the oscillator operates at  $\frac{1}{8}$  of the data frequency, the clock phases need to be combined to create a smaller duty cycle before they can serve as select signals for the MUX.

The integral path does not require a higher frequency as it has a slower response. During each clock cycle, the outputs of the eight phase detectors are summed and added to a counter that controls the integral path of the DCO. The number of bits in the integral path determines the locking range according to Eq. 2.1, with  $K_{DCO}$  representing the DCO gain,  $\rho$  the integral path gain and N the number of bits in the integral path. The 12 bits in the final design corresponds to a locking range of 50MHz in the

positive and negative direction.

Locking Range =

$$K_{DCO} \cdot \rho \cdot (2^N - 1)$$

(2.1)

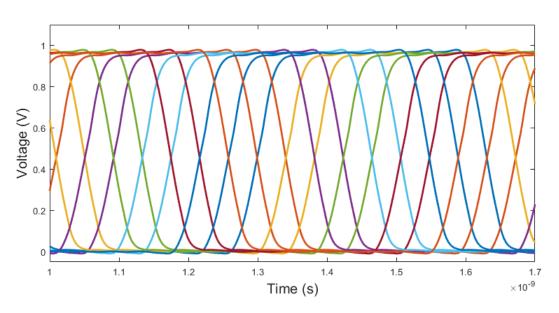

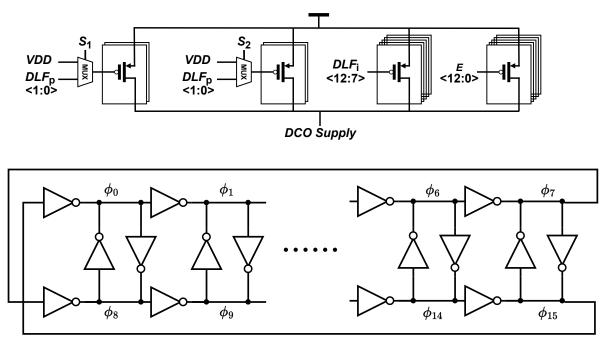

The DCO generates 8 complementary clock phases, resulting in a total of 16 clock phases. All the clock cycles are necessary to provide the stages of the phase detector with the correct control signals. Additionally, a clock buffer is essential since not every clock phase will be loaded equally, this imbalance would affect the phase spacing which could lead to timing errors.

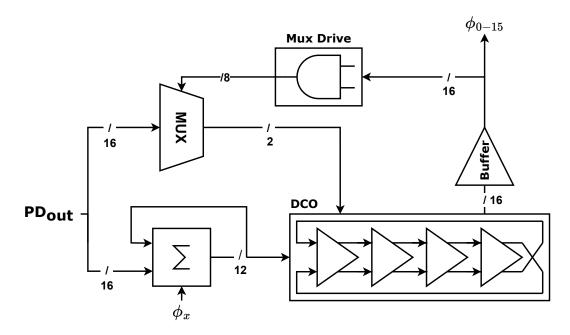

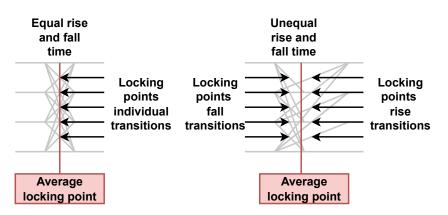

## 2.5. Reference Calibration Loop

The final block is the reference calibration loop, which is necessary for adjusting the reference voltages. This loop is needed to compensate for two phenomena. The first is unequal rise and fall times, as illustrated in Fig. 2.8. If the data experiences unequal rise and fall and the same predetermined references are used for rising and falling transitions, the locking points of rising and falling transitions will not be aligned. The locking point of the CDR will be the average of all locking points, assuming all transitions have an equal occurrence. However, since the locking point of each transition does not align with the locking point of the cODR, unnecessary jitter will be generated. Therefore, the reference voltages need calibration to address this issue and align all locking points.

Figure 2.8: Effect of unequal rise and fall transition times on locking point.

The second phenomenon involves deterministic non-idealities in the sampling. Due to the unequal middle voltage of each transition, the overdrive voltage of the sampling switch will differ between transitions. This results in unique time constants, and thus, different delays. This leads to a positive offset for falling transitions and a negative offset for rising transitions. Non-deterministic non-idealities, like the comparator offsets or DAC Differential nonlinearity (DNL), cannot be compensated with this loop since these phenomena are different for each phase detector.

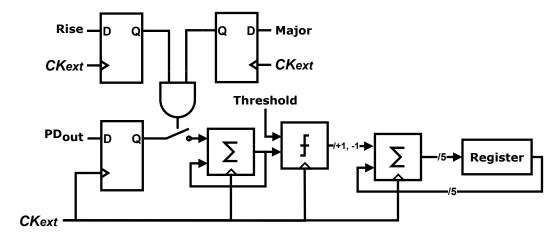

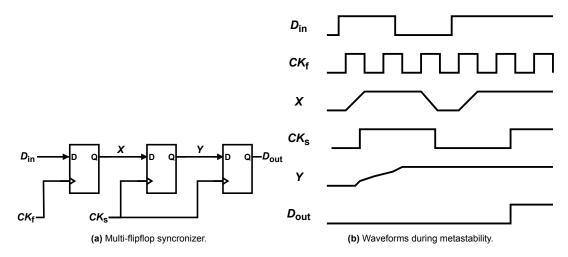

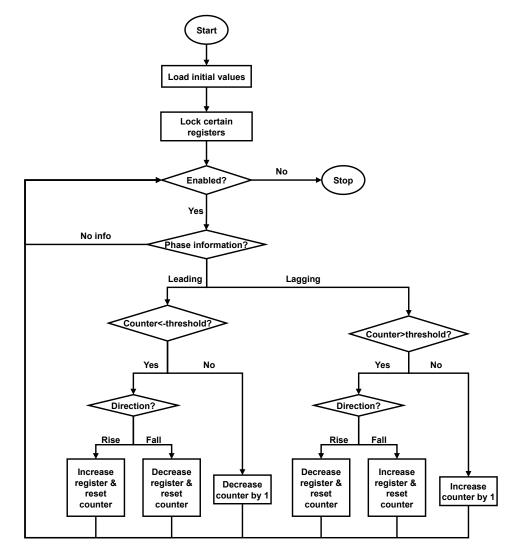

A block diagram of a single calibration loop is illustrated in Fig. 2.9. In total, twelve loops are required, one for each transition. This diagram depicts the functional aspects. The actual implementation of the loop will be designed using register-transfer level (RTL) code. The loop can operate at a very low frequency compared to the data frequency, an external clock  $CK_{ext}$  will provide this low-frequency signal. The output of one phase detector needs to be buffered to the lower clock frequency in order to maintain validity during the low-frequency clock.

Figure 2.9: Calibration loop block diagram.

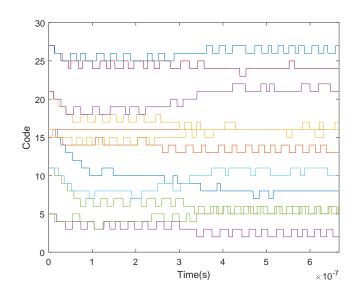

The buffered transition signals,  $PD_{out}$ , Rise and Major for the major rising transition, will activate the correct calibration loop. The phase information will be summed and accumulated each time the loop is activated. If the accumulated phase information reaches a threshold the register voltage needs to be adjusted. The accumulated phase information needs to be compared to both a positive and a negative threshold since the locking point of a transition can both be early or late with respect to the global locking point. The adjustment of the register can both be +1 or -1 depending on the direction of the transition and the phase information. The register value is adjusted with an accumulator. After the register is updated the accumulated phase information needs to be reset. The calibration loop is further explained in Chapter 5.

# 3

# System-Level Analysis

In order to analyze the noise sources in the system and to determine the required oscillator gain, a phase domain model is required. First, a discrete-time domain model is presented. Subsequently, the noise contributions are introduced and the complete model is translated to the phase domain. The CDR is simulated in Matlab to derive the required system parameters, the expected performance and to verify the phase domain model.

## 3.1. Discrete Time Domain Model

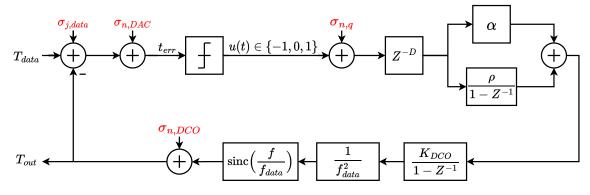

The time discrete or Z-domain model of the proposed PAM-4 CDR is presented in Fig. 3.1.

Figure 3.1: Discrete time domain model of the CDR.

The parameter of interest  $T_{data}$  denotes the midpoint of the data transition. The CDR attempts to align the sampling time  $T_{out}$  with  $T_{data}$  by minimizing  $t_{err}$ . The phase detector converts the incoming timing error into tertiary information: either "early", "late", or "neutral" in the absence of a transition. A delay is also added to the system by the phase detector due to the calculation time required for the phase information. The information is then passed through a digital low-pass filter with proportional gain  $\alpha$  and integral gain  $\rho$ , and the oscillator frequency is updated with gain  $K_{DCO} \frac{Hz}{LSB}$ . The DCO gain is multiplied by a factor  $\frac{1}{f_{data}^2}$  in order to move to a time step update. A sinc function is needed to model the zero-order hold (ZOH) characteristic of the oscillator [17].

#### 3.1.1. BBPD Linearization

The main obstacle in creating a linear model arises from the non-linear gain of the BBPD. The transfer function of the phase detector can be characterized by the sign function 3.1.

$$K_{pd}(t_{err}) = \begin{cases} -1 & \text{if } t_{err} < 0\\ 0 & \text{if } t_{err} = 0\\ 1 & \text{if } t_{err} > 0 \end{cases}$$

(3.1)

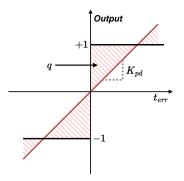

A linear approximation can be created by introducing a quantization error as discussed in [18]. Here,  $K_{pd}$  remains constant while a variable quantization error creates the properties of the sign function. This is illustrated in Fig. 3.2.

Figure 3.2: Linearization of the BBPD gain.

$$u(t) = K_{pd}t_{err} + q(t) \tag{3.2}$$

In the given expression u(t) represents the output,  $K_{pd}$  denotes the linearized gain and q(t) represents the quantization error. The BBPD gain can be linearized due to the effect of jitter. In the presence of a minor timing error between the CDR oscillator and the input data, jitter can result in a sample with incorrect information. A smaller timing error and higher jitter increase the likelihood of missampling and will thus result in a lower average output. This creates a linear gain behavior for small phase errors [19].  $K_{pd}$  can be estimated by minimizing the quantization error. Following the analysis of [18],  $K_{pd}$  can be expressed by equation 3.3.

$$K_{pd} = \sqrt{\frac{2}{\pi}} \frac{\alpha_T}{\sigma_{t_{err}}}$$

(3.3)

Where  $\alpha_T$  denotes the transition density and  $\sigma_{terr}$  represents the timing error between DCO rising clock edge and the middle of the input data transition. It is important to note that this analysis only remains valid when the timing error of the system stays within the linear gain region, about  $2\sigma_{terr}$ . The CDR will still work with larger input errors, but its behaviour can not be linearized anymore. In order to determine  $\sigma_{terr}$ , all the noise sources in the complete system and their transfer functions must be known.

Moving on to the next block, the DCO, the oscillator's gain is specified in frequency but can be transformed into a time adjustment for  $T_{out}$ .

$$f_{DCO} = f_{DCO,0} + K_{DCO} \cdot W \tag{3.4}$$

$$\frac{1}{T_{DCO}} = \frac{1}{T_{DCO,0}} + K_{DCO} \cdot W$$

(3.5)

$$\Delta T = T_{DCO} - T_{DCO,0} \tag{3.6}$$

$$\frac{-\Delta I}{T_{DCO}T_{DCO,0}} = K_{DCO} \cdot W \tag{3.7}$$

(3.8)

Assuming  $T_{DCO} \approx T_{DCO,0}$ , which is the case for  $K_{DCO} \cdot W \ll f_{DCO,0}$  with W representing the dimensionless control word.

$$\Delta T = \frac{K_{DCO}}{f_{dco}^2} \tag{3.9}$$

#### 3.1.2. Noise Sources

In the system, four distinct noise sources exist: input noise, DAC quantization noise, phase detector quantization noise, and oscillator phase noise. Only the computation of quantization noise sources is needed. The input noise arises from the implementation and the oscillator noise results from the circuit design.

#### **BBPD** Quantization Noise

Recognizing that the power of the PD output u(t) is equal to the transition density and using equation 3.3, it follows that the PD quantization noise power is only dependent on the transition density [18]. The output referred noise due to the quantization error, is of course dependent on more parameters.

$$\mathbb{E}[u^2] = \mathbb{E}[(K_{pd}t_{err}) + q)^2]$$

(3.10)

$$\sigma_u^2 = \frac{1}{N-1} \sum_{k=0}^{N-1} (u[k] - \mu)^2 = \alpha_T$$

(3.11)

$$\alpha_T = K_{pd}^2 \sigma_{t_{err}}^2 + \sigma_q^2 \tag{3.12}$$

$$\sigma_q^2 = \alpha_T - \frac{2}{\pi} \alpha_T^2 \tag{3.13}$$

#### **DAC** Quantization Noise

The calculation of DAC quantization noise is not straightforward. Fig. 3.3 depicts the consequences of quantized reference voltages. Instead of the ideal voltage points the nearest quantized voltage has to be used. This quantization error alters the locking point of an individual transitions. As the shift is unequal for the transitions, the locking points of individual transitions become misaligned. The time shift of locking point  $\Delta t$  can be described by equation 3.14.

$$\Delta t = t_{trans} \cdot \frac{V_q - V_{ideal}}{V_{trans}}$$

(3.14)

Figure 3.3: Illustration of the shift in locking point due to quantization noise

$t_{trans}$  represents the transition time,  $V_q$  denotes the quantized reference voltage,  $V_{ideal}$  the ideal reference voltage and  $V_{trans}$  the voltage difference between data levels for a certain transition. This formula assumes linear transitions, if this is not the case the slope has to be used around the locking point.

A shift of the locking point in successive transitions is analogous to an instantaneous shift in the input data. The power of the quantization error is equal to the power of a discrete time signal containing the shift of each locking point.

$$\sigma_{q,DAC}^2 = \frac{1}{N-1} \sum_{k=0}^{N-1} (\Delta t[k] - \mu)^2$$

(3.15)

Here,  $\sigma_{q,DAC}^2$  denotes the power or variance of the quantization error,  $\Delta t[k]$  is a vector containing the shift of each locking point. *N* is the number of transitions, and  $\mu$  is the average locking point. The total number of transitions is 16 in PAM-4 since non-transitions also have to be considered. The shift of a non-transition is zero since no locking point exists.

Alternatively, one can assume that the ideal reference codes are randomly positioned. The quantization noise can now be approximated similar to calculating the DAC quantization noise in [20]. This approximation gives more insight into the effects of design parameters. Since only twelve reference codes exist, the quantized references can fall on unfavorable positions and have a higher quantization error. Eq. 3.18 can either over or under estimate the actual quantization noise due to this uncertainty.  $V_{DAC}$  represents the full DAC swing, N the number of DAC bits,  $t_{trans}$  the transition time and  $V_{swing}$ the amplitude of the input signal.

$$\sigma_{q,DAC}^2 = \frac{1}{A_{LSB}} \int_{\epsilon = \frac{A_{lsb}}{2}}^{\epsilon = \frac{-A_{lsb}}{2}} A_{error}^2(\epsilon) \, d\epsilon \tag{3.16}$$

$$\sigma_{q,DAC}^{2} = \frac{2}{16} \frac{1}{A_{LSB}} \int_{\epsilon = \frac{A_{lsb}}{2}}^{\epsilon = \frac{-A_{lsb}}{2}} \epsilon^{2} \cdot \left(\frac{t_{trans}}{V_{swing}}\right)^{2} d\epsilon + \frac{4}{16} \frac{1}{A_{LSB}} \int_{\epsilon = \frac{A_{lsb}}{2}}^{\epsilon = \frac{-A_{lsb}}{2}} \epsilon^{2} \cdot \left(\frac{t_{trans}}{\frac{2}{3}V_{swing}}\right)^{2} d\epsilon + \frac{6}{16} \frac{1}{A_{LSB}} \int_{\epsilon = \frac{A_{lsb}}{2}}^{\epsilon = \frac{-A_{lsb}}{2}} \epsilon^{2} \cdot \left(\frac{t_{trans}}{\frac{1}{3}V_{swing}}\right)^{2} d\epsilon$$

(3.17)

$$\sigma_{q,DAC}^{2} = \frac{65}{16} \left( \frac{V_{DAC}}{(2^{N} - 1)\sqrt{12}} \right)^{2} \left( \frac{t_{trans}}{V_{swing}} \right)^{2}$$

(3.18)

#### 3.2. Phase Domain Model

The translation from the Z-domain to the S-domain can be accomplished using the following formula:

$$Z = e^{j\omega T_{data}} \tag{3.19}$$

For

$$f \ll f_{data}$$

(3.20)

$$Z = 1 + \frac{s}{f_{data}} \tag{3.21}$$

$$Z^{-1} = 1 - \frac{s}{f_{data}}$$

(3.22)

The open loop transfer function of the system is now given by:

$$H_{ol} = K_{pd} \cdot e^{-sT_{data} \cdot D} \cdot \left(\alpha + \frac{\rho f_{data}}{s}\right) \cdot \left(\frac{K_{DCO}}{sT_{data}} \cdot \frac{1}{f_{data}^2}\right) \cdot \operatorname{sinc}\left(\frac{f}{f_{data}}\right)$$

(3.23)

and in the closed-loop configuration:

$$H_{cl} = \frac{H_{ol}}{1 + H_{ol}}$$

(3.24)

The sinc function is neglected since the approximation does not hold for larger frequencies where the sinc function becomes noticeable.

$\sigma_{t_{err}}$  can now be calculated using the phase noise profiles and the loop dynamics. It is important to note that the incoming data jitter, DAC quantization noise and quantization noise have white spectra.

$$\mathcal{L}_{tot}(s) = \mathcal{L}_{data}(s) + \mathcal{L}_{q,DAC}(s) + \mathcal{L}_{q}(s) + \mathcal{L}_{DCO}(s)$$

(3.25)

$$\mathcal{L}_{tot}(s) = H_{cl}(s) \cdot (\sigma_{data}^2 + \sigma_{q,DAC}^2) \cdot \frac{(2\pi \cdot f_{data})^2}{\frac{1}{2} f_{data}} + \frac{H_{cl}(s)}{K_{pd}} \cdot \sigma_q^2 \cdot \frac{(2\pi \cdot f_{data})^2}{\frac{1}{2} f_{data}} + \frac{1}{1 + H_{ol}(s)} \cdot S_{\phi,DCO}(s)$$

(3.26)

$$\sigma_{t_{err}}^{2} = \int_{0.5}^{-0.5} H_{cl}(\omega) \cdot (\sigma_{data}^{2} + \sigma_{q,DAC}^{2}) \cdot \frac{(2\pi \cdot f_{data})^{2}}{\frac{1}{2} f_{data}} d\omega + \int_{0.5}^{-0.5} \frac{H_{cl}(\omega)}{K_{pd}} \cdot \left(\alpha_{T} - \frac{2}{\pi} \alpha_{T}^{2}\right) \cdot \frac{(2\pi \cdot f_{data})^{2}}{\frac{1}{2} f_{data}} d\omega + \int_{0.5}^{-0.5} \frac{1}{1 + H_{ol}(\omega)} \cdot S_{\phi,DCO}(\omega) d\omega$$

(3.27)

With the equations 3.3 and 3.27 an analytical solution can be derived given the phase noise profile of the DCO and the input noise are known. Alternative analytical approaches for the BBPD gain are presented in [21], [22] and [23]

#### 3.2.1. Limit Cycling

The linear system not only fails in the presence of large disturbances but also in scenarios with minimal noise. The absence of noise prevents the loop from converging to a stable point. Due to the delay and fixed frequency gain, the system toggles between phase states, resulting in spurs at specific frequencies in the phase spectrum. This phenomenon is known as limit cycling [24], [25]. While ring oscillators are less prone to this issue due to the random input data, it remains important to be mindful of this aspect. The minimum noise requirement can be expressed as:

$$\sigma_{t_{err}} \ge \frac{\alpha K_{DCO}(D+1)}{\alpha_T f_{dco}^2 \sqrt{3}}$$

(3.28)

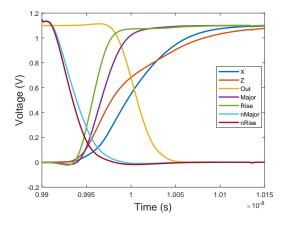

## 3.3. MATLAB Time Domain Model

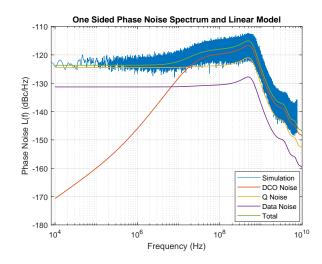

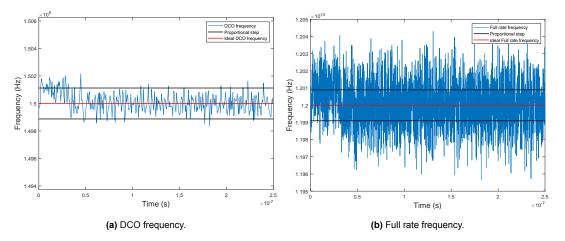

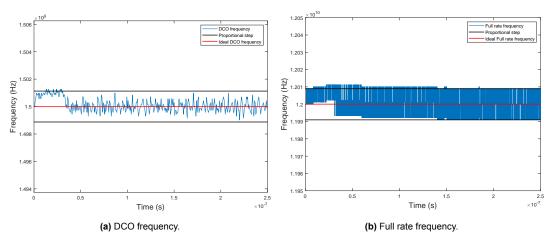

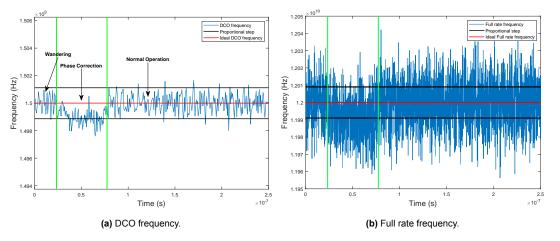

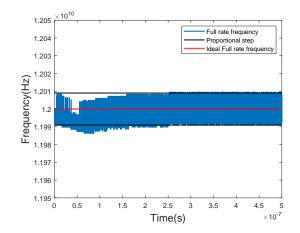

A time domain simulation of the system was created in Matlab, similar to the approach in [26], and compared to the linearized phase domain model. Matlab code can be found in appendix A. The results are presented in Fig. 3.4. It can be seen that the quantization noise is slightly underestimated. This can be attributed to the timing error occasionally falling outside the linear region.

Figure 3.4: Comparison of linear model and time domain simulation

The circuit implementation of the phase detector introduces a few critical non-idealities to the system. These can have a significant impact on the system and should therefore be added to the Matlab model. The modelled non-idealities are:

- Feed-through: When the sample switch is closed, some feed-through still occurs, attenuating the sample.

- **Comparator settling**: If the difference between the sample and the reference voltage is small, the comparator cannot settle in the given time, leading to no phase information.

- Low bandwidth integral path: The integral path is not updated at the data rate but at the DCO frequency.

- Deviations from the ideal oscillator gain: The final DCO will have non-ideal gain due to mismatch and compression.

These effects cause the timing error to deviate from the Gaussian distribution assumed in [18]. The PD gain can be calculated with the simulated decisions and timing error.

$$K_{pd} = \frac{\mathbb{E}[u(t) \cdot t_{err}]}{\mathbb{E}[t_{err}^2]}$$

(3.29)

And for the quantization error:

$$q[k] = u[k] - K_{pd} \cdot t_{err}[k]$$

(3.30)

$$\sigma_q^2 = \frac{1}{N-1} \sum_{k=0}^{N-1} (q[k] - \mu)^2$$

(3.31)

This way, the noise contributions of the quantization and oscillator can be compared, and an optimal  $K_{dco}$ ,  $\rho$ , and N can be chosen.

## 3.4. Parameter Design

The system has three tunable parameters: the number of DAC bits N, the oscillator gain  $K_{dco}$ , and the integral path gain  $\rho$  with respect to  $\alpha$ . Here,  $\alpha$  is set to one.

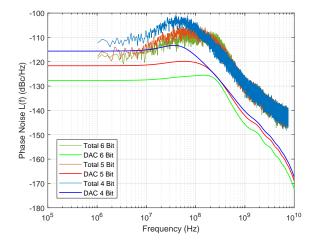

#### 3.4.1. Number of Bits

The DAC should be designed with a minimal number of bits to reduce power consumption. However, choosing too few bits will result in additional phase noise. The power of the quantization noise can be calculated using equations 3.14 and 3.15, as discussed previously. The noise is shaped by the closed-loop transfer function. Furthermore, the DAC noise reduces the PD gain, increasing the contribution

of other noise sources. The additional phase noise due to the DAC thus consists of both its direct and indirect contributions, making it difficult to calculate its overall impact analytically. In Fig. 3.5, the total phase noise and the direct DAC quantization phase noise are plotted for N = 4, 5, 6 for a worst-case scenario of a maximum transition time of the incoming data. N = 5 is chosen since it adds only 40 fs of jitter while significantly reducing power consumption. In practice, the added jitter will most likely be less due to the sinusoidal transition waveform having a steeper slope around the locking point.

Figure 3.5: DAC quantization noise contribution

#### 3.4.2. Optimal Parameter Choice for Jitter

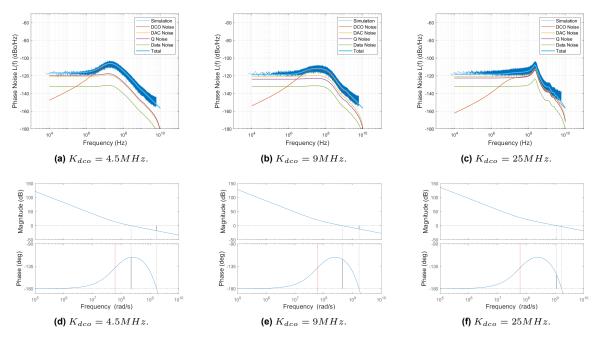

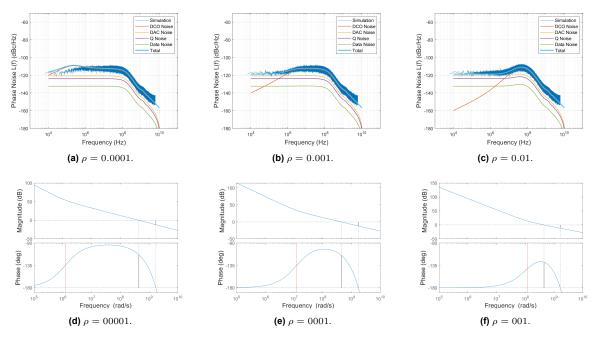

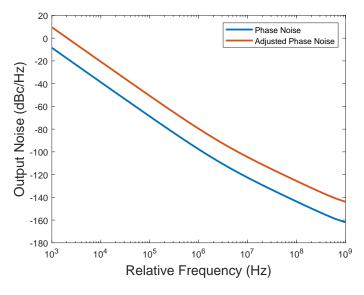

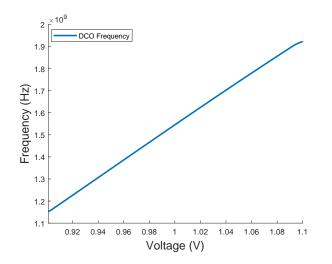

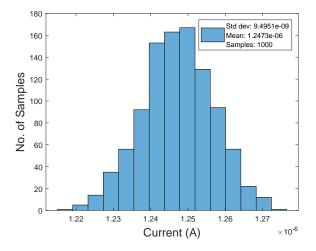

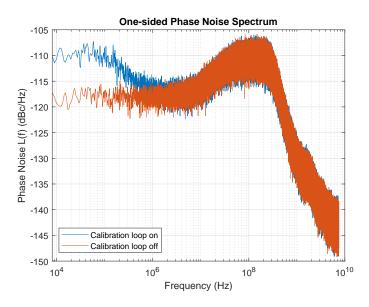

The only parameters that can be tuned without changing the circuit architecture are  $K_{dco}$  and  $\rho$ . In Fig. 3.6, the phase noise and open loop transfer functions are plotted for three different oscillator gains: 4.5MHz, 9MHz, and 25MHz. If the gain is too low, i.e., 4.5MHz, the oscillator thermal noise is not sufficiently suppressed, and therefore, jitter will be too high. If the gain is too large, the phase margin degrades, and limit cycling occurs. This also leads to an increase in jitter generation. The optimal  $K_{dco}$  is 9MHz.

**Figure 3.6:** One sided PN spectrum and Bode Plot for different  $K_{dco}$ .

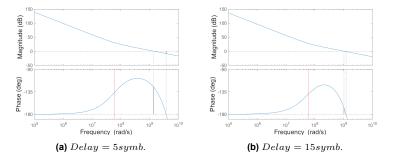

The phase margin experiences degradation due to delay. This effect is illustrated in the two cases

examined in Fig. 3.7. In Fig. 3.7a, a delay of 5 symbols is used, enabling a large open-loop gain and thus a large  $K_{dco}$ . In Fig. 3.7b, the delay is increased to 15 symbols while maintaining  $K_{dco}$ . It is clear that the phase margin has degraded significantly, resulting in a peak in the phase noise spectrum. Since a high  $K_{dco}$  is needed to sufficiently suppress the DCO noise, it is important that the delay is minimized in the system. If it cannot be minimized, it can be beneficial to increase the power consumption in the DCO, lowering the phase noise and thus the required  $K_{dco}$  for optimal suppression. In the final system, a delay of 10.5 bits is achieved.

Figure 3.7: Phase margins of the CDR for different delays.

The second adjustable parameter is the integral gain,  $\rho$ . Fig. 3.8 presents the Bode plot and phase noise for three distinct values of  $\rho$ . As  $\rho$  increases, the zero in the DLF shifts to a higher frequency as illustrated in Fig. 3.8d - 3.8f by the red line, giving more prominence to the proportional path. If  $\rho$  is chosen too low, as shown in Fig. 3.8a, the DCO noise is not suppressed enough, and flicker noise will start to have an influence. Note that flicker noise is absent in the time-domain simulation but only present in the linear model. A lower  $\rho$  also reduces the locking range for a given number of bits in the integral path according to Eq. 2.1. If  $\rho$  is chosen too high, as shown in Fig. 3.8c, it will reduce the phase margin, which is clearly visible in the Bode plot in Fig. 3.8f. A final value of  $\rho = 0.001$  is used. This leads to a minimal reduction in phase margin while suppressing the flicker noise and maintaining enough locking range.

Figure 3.8: One sided PN spectrum and bode Plot for different  $\rho$ .

## 3.5. Jitter Tolerance

Jitter tolerance is the maximum allowed jitter amplitude at a specific frequency in order to maintain an acceptable bit error rate (BER). The linearized model is unusable for calculating jitter tolerance since cycle slipping needs to occur. The phase error is too large for the linear model to stay valid.

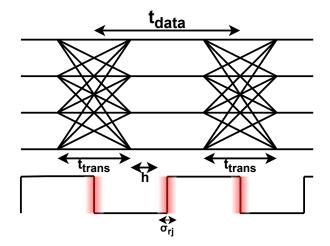

To ensure a reasonable BER, we aim to keep the phase error below h, measured in degree or unit intervals UI, h depends on the CDR's performance and incoming signal quality. A graphical illustration of h can be seen in Fig. 3.9, with  $t_{data}$  representing the bit period,  $t_{trans}$  the transition time and  $\sigma_{rj}$  the random jitter between the clock and the data. The clock can drift a certain amount h before a bit error occurs.

In an ideal case, h equals to  $\pi$  radians or 0.5UI (half the bit) since ideally, the clock is situated in the middle of a bit. For PAM-4 modulation, it's crucial to avoid sampling in transition regions to prevent errors, especially for major transitions quickly crossing to the next symbol level. Random jitter also needs to be considered. To achieve a BER of  $10^{-12}$ ,  $7\sigma_{rj}$  needs to be taken into account. h can be calculated in UI with equation 3.32.

Figure 3.9: Graphical description of h.

$$h = \frac{t_{data} - \frac{1}{2}t_{rise} - \frac{1}{2}t_{fall}}{2t_{data}} - \frac{7\sigma_{rj}}{t_{data}}$$

(3.32)

#### 3.5.1. Cycle Slipping

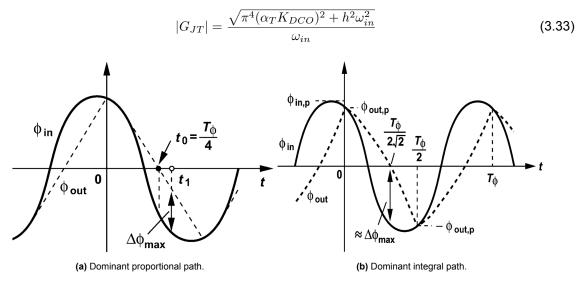

Since the linear model is invalid, another method is needed to find the point where  $t_{error} > h$ . There are three regions in the jitter transfer function. At high frequencies, the transfer is flat since the CDR cannot keep up with the input jitter. At medium frequencies, the proportional path is dominant and the transfer has a slope of -20dB/dec. At low frequencies, the proportional path is dominant and the transfer has a slope of -40dB/dec.

In the flat region, the jitter tolerance is equal to h since no jitter is transferred from input to output due to the high frequency.

In the -20dB region, the proportional path of the CDR can compensate for phase errors. To approximate the maximum tolerable jitter, let us examine the case presented in Fig. 3.10a. In this figure, the excess input and output phase are plotted when a sinusoidal jitter is applied to the input data. Since in this region the frequency is too high for the proportional path to have an effect, only the linear phase compensation of the proportional path is considered. The phase change of the input is too large for

the CDR to keep up. With each time step, a larger phase error between input and output is created. The maximum phase error  $\Delta \phi_{max}$  occurs when the slopes of the input and output are equal. After this point, the output starts to catch up. Since this point is difficult to approximate, the zero crossing of the excess output phase is considered, here the phase error  $\approx \phi_{max}$ . The following derivation finds an approximate formula for the jitter transfer.

$$\begin{split} \phi_{in}(t) &= \phi_{in,a} \cos \left(\omega t + \delta\right) \\ \phi_{out}(t) &= \phi_{out,a} - K_{DCO} \alpha_T \\ \Delta \phi_{max} &= \phi_{in,a} \cos \left(\omega \frac{T}{4} + \delta\right) \\ \delta &= \arccos \left(\frac{\pi^2 K_{DCO} \alpha_T}{\phi_{in,a} \omega_{in}}\right) \end{split}$$

Equating  $\Delta \phi_{max}$  to h and solving for  $\phi_{in,a}$  gives:

Figure 3.10: In and output phase error [19].

The low-frequency region is the The -40dB/dec region, where the integral path of the system is dominant. This region can be approximated with a similar method for a quadratic output phase instead of a linear one. A graphical illustration is given in Fig. 3.10b. Now the approximate maximal phase error occurs at  $t = \frac{T}{2\sqrt{2}}$ .

$$\begin{split} \phi_{out}(t) &= \phi_{out,a} - \int \alpha_T K_{DCO} \rho f_{data} t dt \\ \phi_{out} \left(\frac{T}{2}\right) &= -\phi_{out,a} = \phi_{out,a} - \frac{1}{2} \alpha_T K_{DCO} \rho f_{data} \frac{T^2}{4} \\ \Delta \phi_{max} &= \phi_{in,a} \cos \left(\omega_{in} \frac{T}{2\sqrt{2}} + \delta\right) \\ \delta &= \arccos \left(\frac{\pi^2 \alpha_T K_{DCO} \rho f_{data}}{4\phi_{in,a} \omega_{in}^2}\right) \end{split}$$

Equating  $\Delta \phi_{max}$  to h and solving for  $\phi_{in,a}$  gives:

$$|G_{JT}| \approx \frac{\sqrt{0.06c^2 - 0.31ch\omega_{in}^2 + h^2\omega_{in}^4}}{\omega_{in}^2}$$

(3.34)

$$c = \alpha_T K_{DCO} \rho f_{data} \pi^2 \tag{3.35}$$

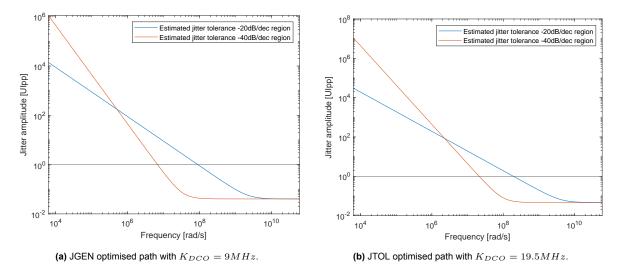

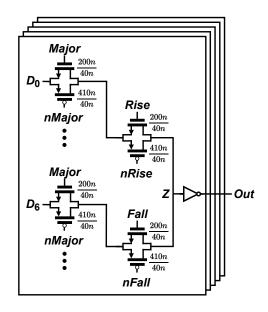

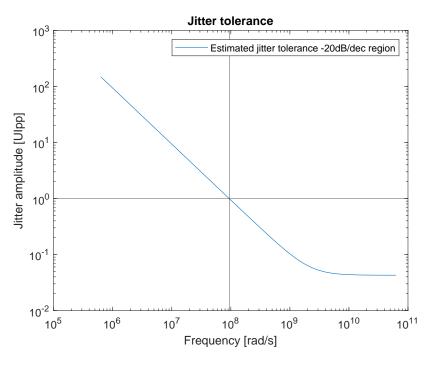

The result can be seen in Fig. 3.11a for  $K_{dco} = 9MHz$ . With a jitter tolerance of 1UI at 14MHz, the jitter tolerance is lower than the desired specification of 30MHz. However, the jitter tolerance can be easily increased with a higher  $K_{dco}$  due to the high transition density. In high-jitter environments, where the jitter tolerance is more important, this does not lead to an increase in jitter generation due to the reduced  $K_{pd}$ . If  $K_{dco} = 19.5MHz$ , the jitter tolerance increases to 1UI at 31MHz as can be seen in Fig. 3.11b. It is therefore proposed that the oscillator can switch between two frequency gains.

Figure 3.11: Estimated jitter tolerance.

## Circuit Design

This chapter covers the circuit design at the transistor level of the phase detector, digital low-pass filter, and oscillator. It also discusses the layout of the phase detector and verifies the functionality of each block.

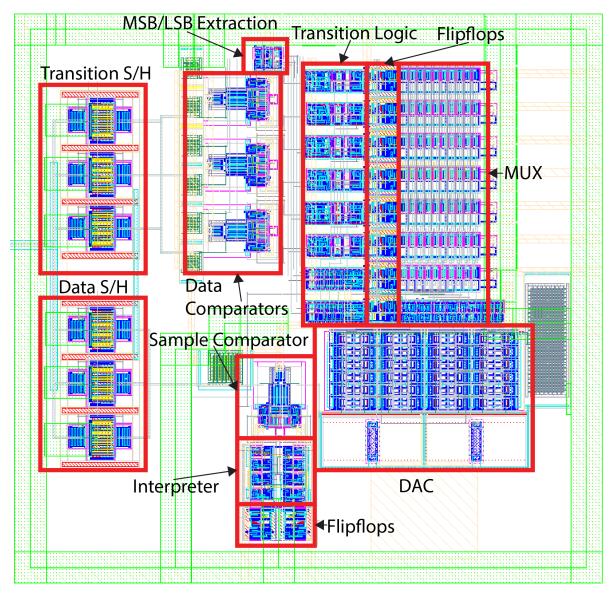

#### 4.1. Phase Detector

The phase detector consists of several analog and digital blocks, each requiring different design considerations. The primary design bottleneck of the phase detector is the delay. As seen in section 3.4.2, a lower delay in the phase detector allows for a larger oscillator gain, increasing the suppression of the dominant noise source, the DCO. Power consumption is also an important factor since, in the complete CDR, 8 parallel phase detectors exist. An accurate delay can only be found with a layout; therefore, the layout of the phase detector is needed to accurately illustrate the functionality of the CDR.

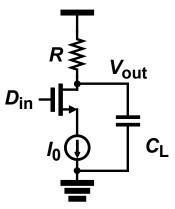

#### 4.1.1. Sample and Hold

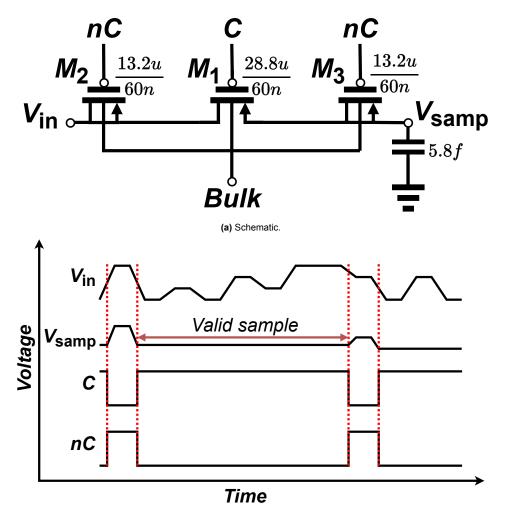

The sample and hold circuit is responsible for taking a sample of the incoming data and holding it before it is used by the comparator. The comparators require a input signal larger than the PMOS threshold voltage. Raising the signal after the sample and hold circuit would introduce an additional step and thus, additional delay. In order to circumvent this the incoming data ranges from 0.6V to 1.1V. In future work, an level shifter is needed to raise the signal to this level. Although sampling a higher voltage signal is more difficult due to the increased resistance of PMOS transistors, the timing budget in the phase detector is more important. In order to be able to compensate for the increased resistance of the PMOS transistors, a bulk connection is used to increase the overdrive voltage. The sample and hold circuit consists of a large switch with dummy switches and a sampling capacitor. The schematic and its waveforms can be seen in Fig. 4.1. The sampling circuit is the same for both the data sample and the transition sample to ensure equal time constants. The sampling capacitor cannot be made too large due to the increased charging time, the bottom limit is set by the discharging of the capacitance due to leakage current and, most importantly, the kickback of the comparators.

(b) Waveforms.

Figure 4.1: Sample and Hold Circuit.

The waveforms are presented in Fig.4.1b. The control signals C and nC are combined clock signals with a higher duty cycle for C (87.5%) and a lower duty cycle for nC (12.5%). This is done for two reasons: if direct clock signals with 50% duty cycle would be used, four sampling capacitors would be connected at all times, increasing the load on the level shifter. Now only one sampling capacitor is connected at all times, reducing the load. Additionally this also ensures the transition sample stays valid for a longer time increasing the calculation time budget. The transition sample needs to be compared to the generated reference voltage before the switch opens and a new sample is taken. With the lower duty cycle the calculation budget increases from 4 symbols, to 7 symbols.

M1 is the main sampling switch, its width is large to reduce on-resistance. Increasing it indefinitely will result in the parasitic capacitances becoming dominant over the sampling capacitance and thus will have no benefit.

Since M1 is relatively large, problems arise in the circuit. Charge injection occurs when switch M1 turns on. This can easily be mitigated by the dummy switches M2 and M3 having half the size of M1. The dummy switches turn on when switch M1 turns off, absorbing the injected charge.

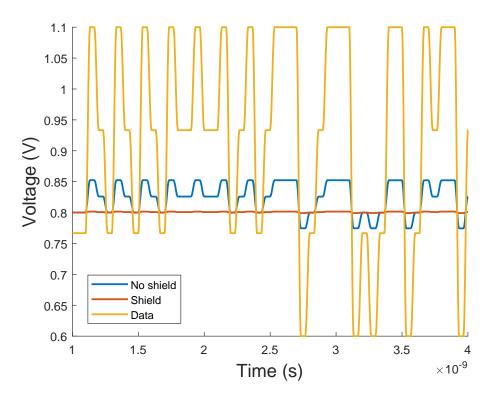

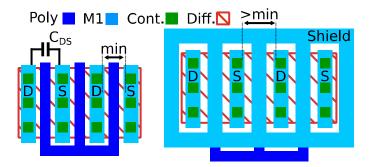

Another problem is the drain-source capacitance  $C_{ds}$ . This will result in a capacitive division with the sample capacitor when the switch is off, and feed-through of the data will occur, as can be seen in Fig.4.2. Without shielding, the feed-through on the sample would reach 15.7% of the input, leading to large errors in the transition sample. Since most of  $C_{ds}$  comes from the metal connecting the doped

regions, metal shields can be placed over the gate with a strong connection to ground to insulate the drain and source metal connections [27]. The schematic layout can be seen in Fig.4.3. This lowered the feed-through to about 0.5% in simulations.

Figure 4.2: Sample voltage with and without shielding.

Figure 4.3: Schematic shield layout [27].

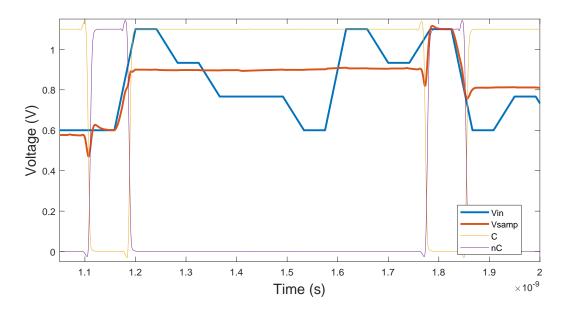

A transient simulation is depicted in Fig.4.4 for the two different major transitions. The control signals C and nC were created by NOR and NAND gates from the clock signals. It can be observed that  $V_{samp}$  tracks  $V_{in}$ , although slightly lagging, when C is low. Since  $V_{samp}$  lags  $V_{in}$  the falling transition results in a higher sample and a lower sample in the rising transitions. This shows that it is difficult to use predetermined voltages, however since the sample and hold circuits are the same for each phase detector, and thus the time constant, the calibration loop can adjust the reference voltages to its closest value. This is further explained in Chapter 5. It is also visible that charge gets injected and absorbed during the switching of C and nC. Finally, it can be seen that the feed-through is minimal when C is high. The component parameters can be seen in Fig. 4.1a

Figure 4.4: Transient S/H simulation

#### 4.1.2. Comparator

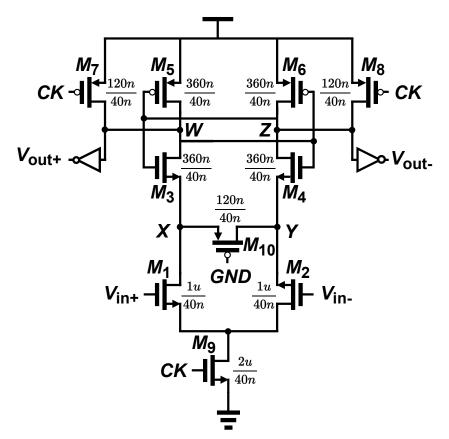

In the phase detector, four comparators are needed: Three to slice the PAM-4 data and one to compare the transition sample. A StrongARM latch is used for all comparators, and the schematic is depicted in Fig.4.5. The working of a StrongARM latch is well-established and extensively discussed in [28].

The StrongARM latch comprises two complementary inverters,  $M_3$  to  $M_6$ . The input transistors,  $M_1$  and  $M_2$ , pull down nodes X and Y. Whichever node is pulled down faster creates the stronger inverter. The strongest inverter turns the weaker inverter off, and the circuit is latched in a stable state.

A few modifications have been introduced to enhance performance. Buffers are added to the output to address unequal loading and ensure sufficient drive to the next stage. Additionally, instead of resetting nodes X and Y to  $V_{DD}$ , they are reset to  $V_{DD} - V_{th}$  and equalized with  $M_{10}$ . This adjustment reduces kickback to the input, which needs to be minimized to allow for a smaller sampling capacitor. This adjustment increases the reset time, which is not an issue in this design.

The size of transistors creates a trade-off between mismatch and speed. The comparator has two equal branches where the parasitic capacitances of all transistors need to be discharged. Increasing the size of  $M_{3-8}$  will result in more capacitance in each branch resulting in a slower settling of the comparator. However if the size is decreased the mismatch between the capacitances on each branch will be more resulting in more offset, if one branch has more parasitic capacitance the input voltage needs to be higher to achieve the same discharge time. The exception is the input pair  $M_{1,2}$ , where larger transistors result in both less mismatch and faster comparison since they supply the current required to drain the capacitance in each branch. However these transistors have an upper limit since they increase the kickback experiences on the input. Since the optimization focus of this design is primarily on speed, all transistors, except for the input pair, are chosen close ti minimal size.

An overview of transistor dimensions is provided in Fig. 4.5. Switches  $M_7$  and  $M_8$  are set to the minimum size, as there is enough time to ensure a full reset to  $V_{DD}$  for nodes W and Z. Transistors  $M_3$  to  $M_6$  are chosen close to the minimum size, as they increase capacitance at nodes W - Z and consequently slow down settling. In contrast, transistors  $M_1$  and  $M_2$  are relatively large compared to  $M_3$  and  $M_4$ , supplying the necessary current for discharging nodes X and Y. Increasing the size further would lead to higher kickback. Finally, transistor  $M_9$  is chosen with twice the width of  $M_1$  and  $M_2$  to ensure enough current is available.

The comparator schematic is simulated with cadence virtuoso and the results are presented in Fig. 4.6 Settling of the comparator nodes in a transient simulation is presented in Fig.4.6a. The settling takes around 60ps for an input difference of 5mV, less than 0.5LSB. A mismatch Monte Carlo simulation can be seen in Fig.4.6b. The standard deviation of the offset is 19mV. As  $3\sigma$  should be taken into account, this would lead to misinterpreted data and phase information. The calibration loop of the reference voltages provides no solution since the mismatch in each comparator is different while the reference voltages are the same for each PD. A second foreground calibration loop is required in future work. This could be done by equalizing the capacitances on node W and Z, as proposed in [29]. Both inputs are connected to a equal common mode voltage and varactors are connected to node W and Z. Comparisons are of the equal input are accumulated and the capacitance on the faster branch increased. This is done until the comparator has an equal decision change with equal inputs.

Figure 4.5: StrongARM comparator.

Figure 4.6: Comparator circuit simulations.

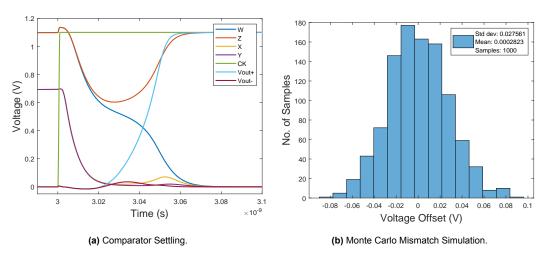

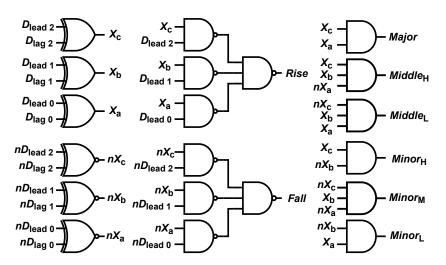

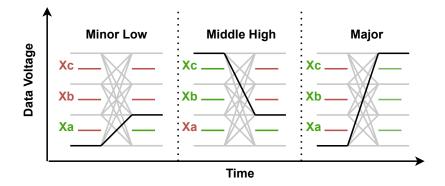

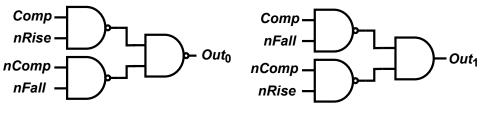

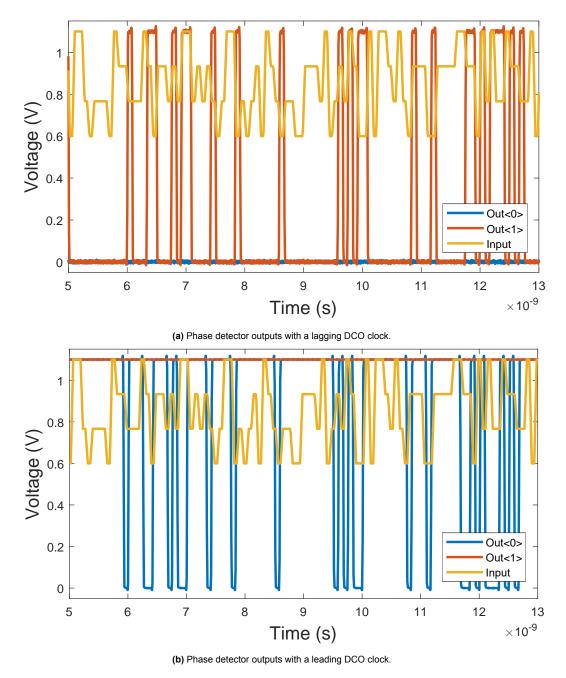

#### 4.1.3. Transition Logic

The transition logic calculates which PAM-4 transition occurred for the sampled transition. This happens with standard TSMC LVT logic gates. Fig.4.7 provides an overview of the circuit at the logic gate level. In order to compute the correct transition, the circuit compares the outputs of each comparator to see at which level a crossing occurred.  $D_{lead2-0}$  is XOR'd with  $D_{lag2-0}$  to create cross signals  $X_{a,b,c}$  and  $nD_{lead2-0}$  is XNOR'd with  $nD_{lag2-0}$  to create non-cross signals  $nX_{a,b,c}$ . All transitions can be found using this information. It is beneficial to use both comparator outputs to minimize loading of the comparators.

The process for three distinct transitions is illustrated in Fig.4.8. For a  $Minor_L$  transition, a transition occurs only at the lowest voltage level. If  $X_a$  is high and  $X_b, X_c$  are low, this transition must have occurred. For  $Middle_H$ ,  $X_a$  must be low and  $X_b, X_c$  are high. For Major, all XOR signals must be high. It is important to note that not all levels need to be considered for each transition. Looking back at the  $Minor_L$  transition, if  $X_a$  is high and  $X_b$  is low,  $X_c$  can only be low and therefore should not be considered.

It is still ambiguous if the transition is rising or falling. This can be computed by comparing the XOR signals with the leading data. If a transition occurred at the lowest level,  $X_a$  is high, comparing this signal to the leading data at the lowest level,  $D_{lead0}$ , the direction can be determined. If  $D_{lead0}$  is positive, the transition must be falling and if it is negative, rising. Since a transition can occur at all three levels, all have to be considered and combined for a valid rise or fall signal. A NAND gate implementation is used to minimize the delay and area. The lagging data can also be used, but since the leading data is available sooner, it is preferred to use these signals.

The power consumption is very low at  $100\mu W$  for a data frequency of 12GHz. The delay of the transition logic is predicted to be around 166ps in TT corner post-layout.

Figure 4.7: Transition logic circuit at gate level.

Figure 4.8: Transition determination.

#### 4.1.4. Dynamic Flip-Flop

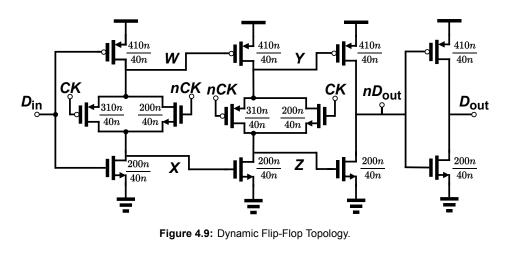

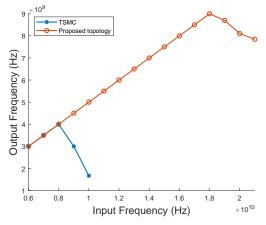

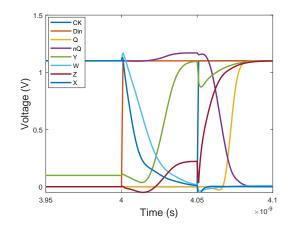

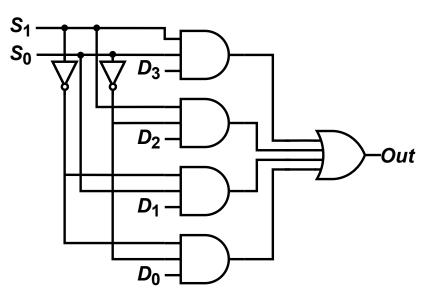

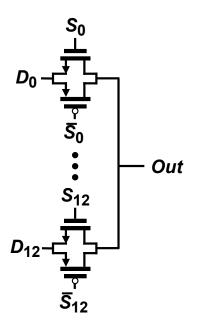

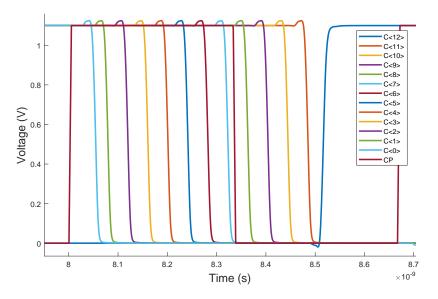

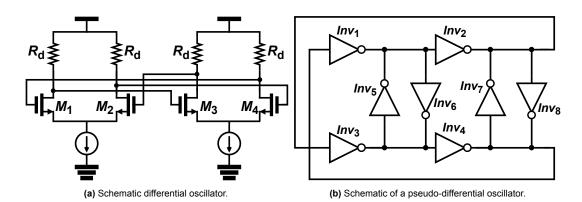

The conventional TSMC Dynamic Flip-Flop (DFF) has long setup and hold times, introducing undesired delay to the phase detector and thus limiting the maximum data rate. A faster alternative is based on the true single-phase clocking (TSPC) topology with split outputs [30]. This topology is not yet sufficient for high-frequency operation due to the degraded internal low voltage. Replacing the clocked transistors with complementary MOS switches, as used in [31], full swing is achieved at the internal nodes. The schematic is presented in Fig.4.9. The complementary switches can charge or discharge nodes W - Z to full swing. A comparison of the proposed circuit and the standard TSMC-DFF in a frequency division test can be seen in Fig.4.10. The TSMC-DFF fails at an input of 8GHz while the TSPC-DFF maintains its functionality until 18GHz.

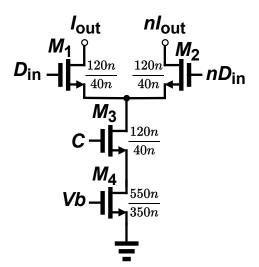

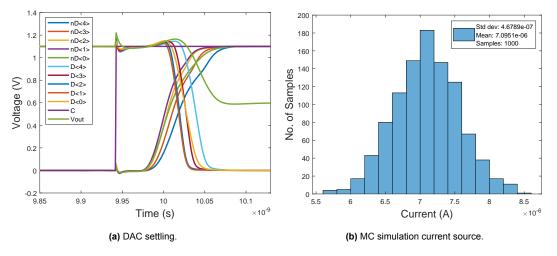

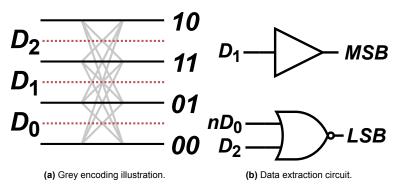

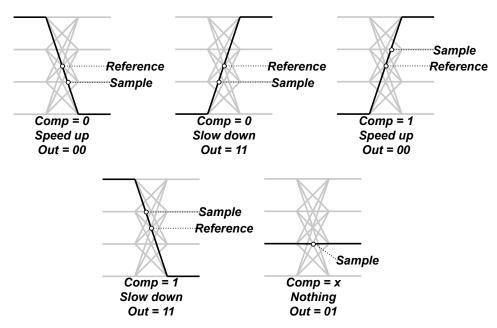

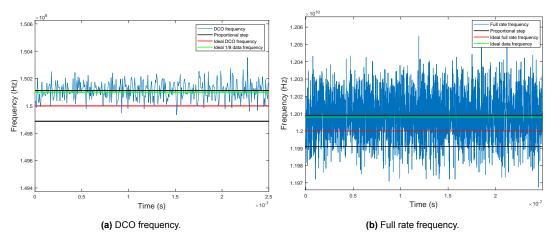

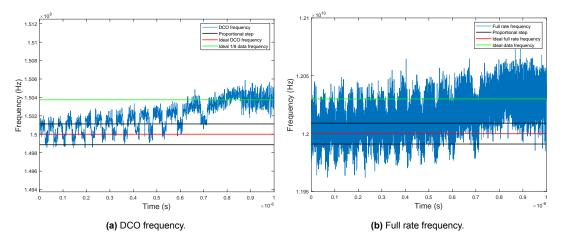

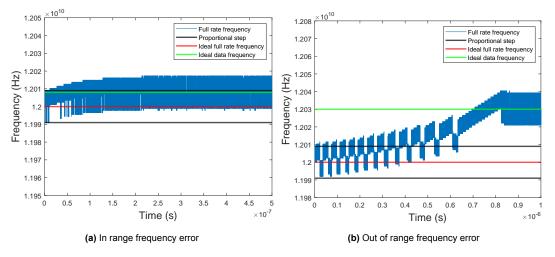

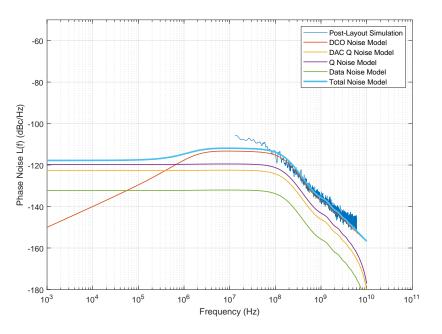

Figure 4.10: Performance of DFF in divide-by-two circuit.