# EFFICIENT RUNTIME MANAGEMENT OF RECONFIGURABLE HARDWARE RESOURCES

THOMAS MARCONI

Thomas Marconi

## Efficient Runtime Management of Reconfigurable Hardware Resources

### Efficient Runtime Management of Reconfigurable Hardware Resources

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.ir. K.C.A.M Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op

woensdag 29 Juni 2011 om 12:30 uur

door

Thomas MARCONI

Magister Teknik in Electrical Engineering Bandung Institute of Technology, Indonesië geboren te Belinyu, Indonesië Dit proefschrift is goedgekeurd door de promotor: Prof. dr. ir. H.J. Sips

Copromotor: Dr. ir. G.N. Gaydadjiev

Samenstelling promotiecommissie:

| Rector Magnificus,           | voorzitter                                 |

|------------------------------|--------------------------------------------|

| Prof. dr. ir. H.J. Sips,     | Technische Universiteit Delft, promotor    |

| Dr. ir. G.N. Gaydadjiev,     | Technische Universiteit Delft, copromotor  |

| Prof. dr. C.I.M. Beenakker,  | Technische Universiteit Delft              |

| Prof. dr. W. Najjar,         | University of California, USA              |

| Prof. dr. J.H. Takala,       | Tampere University of Technology, Finland  |

| Prof. dr. D.N.Pnevmatikatos, | Technical University of Crete, Griekenland |

| Dr. K.L.M. Bertels,          | Technische Universiteit Delft              |

| Prof. dr. P.M. Sarro,        | Technische Universiteit Delft, reservelid  |

#### CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Thomas Marconi

Efficient Runtime Management of Reconfigurable Hardware Resources Delft: TU Delft, Faculty of Elektrotechniek, Wiskunde en Informatica - III Thesis Technische Universiteit Delft. – With ref. –

Met samenvatting in het Nederlands.

#### ISBN 978-90-72298-20-1

Subject headings: runtime reconfigurable systems, partially reconfigurable devices, scheduling, placement, low power, reconfiguration, reconfigurable computing.

#### Copyright © 2011 Thomas Marconi

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed in The Netherlands

To Jesus Christ: my Lord, my Creator, my Motivator, my Savior, my Friend, my Healer, my Mentor, my Teacher, and my Redeemer.

### Efficient Runtime Management of Reconfigurable Hardware Resources

Thomas Marconi

### Abstract

untime reconfigurable systems built upon devices with partial reconfiguration can provide reduction in overall hardware area, power efficiency, and economic cost in addition to the performance improvements due to better customization. However, the users of such systems have to be able to afford some additional costs compared to hardwired application specific circuits. More precisely reconfigurable devices have higher power consumption, occupy larger silicon area and operate at lower speeds. Higher power consumption requires additional packaging cost, shortens chip lifetimes, requires expensive cooling systems, decreases system reliability and prohibits battery operation. The less efficient usage of silicon real estate is usually compensated by the runtime hardware reconfiguration and functional units relocation. The available configuration data paths, however, have limited bandwidth that introduces overheads that may eclipse the dynamic reconfiguration benefits. In this dissertation, we address three major problems related to hardware resources runtime management: efficient online hardware task scheduling and placement, power consumption reduction and reconfiguration overhead minimization. Since hardware tasks are allocated and deallocated dynamically at runtime, the reconfigurable fabric can suffer of fragmentation. This can lead to the undesirable situation that tasks cannot be allocated even if there would be sufficient free area available. As a result, the overall system performance is degraded. Therefore, efficient hardware management of resources is very important. To manage hardware resources efficiently, we propose novel online hardware task scheduling and placement algorithms on partially reconfigurable devices with higher quality and faster execution compared to related proposals. To cope with the high power consumption in field programmable devices, we propose a novel logic element with lower power consumption compared to current approaches. To reduce runtime overhead, we augment the FPGA configuration circuit architecture and allow faster reconfiguration and relocation compared to current reconfigurable devices.

### Acknowledgements

It will not be enough space to name all people who have used their various talents to help me finishing this work. Without all these wonderful men and women created by Almighty God, I could not finish this work. Thank God for His endless provision.

Although Stamatis Vassiliadis is not in this world anymore, his influence is never ended. I'm thankful to Stamatis for giving me the opportunity to work on the hArtes project and also for his short guidance before he left his last mark to many young scientists, especially in CE Lab of TU Delft.

I owe my deepest gratitude to George Gaydadjiev for supervising me. Although it was painful, his high quality expectation trained me to learn more and work harder for moving forward beyond my limitations. He showed me a real example of being a scientist. Although he was extremely busy, he invested a lot of his precious time for me. He helped me to fix this work even during the ICCD conference. He helped me to deal with all challenges I faced.

I would like to express the deepest appreciation to my other supervisor, Koen Bertels. He not only supervised me, but also he motivated me. This combination made me strong to keep doing my research despite many challenges. He demonstrated me a good example of being a teacher. He spent a lot of his time with me during my research even in his busiest moment. Moreover, without his phone calls, I would not be in Delft.

I'm thankful to my promotor, Prof. Henk Sips, for giving me the opportunity to officially finish this thesis. He significantly helped me to improve the quality of this thesis and the propositions. Without him, I would not be a doctor.

I would like to thank all of my doctoral committee: Prof. K.C.A.M. Luyben, Prof. H.J. Sips, Dr. G.N. Gaydadjiev, Dr. K.L.M. Bertels, Prof. C.I.M. Beenakker, Prof. W. Najjar, Prof. J.H. Takala, Prof. D.N. Pnevmatikatos, and Prof. P.M. Sarro. They gave their precious time for improving the quality of this thesis.

I am grateful to work with many of my colleagues. I'm thankful to Yi Lu for

working together in the area of online task scheduling and placement. I am indebted to Dimitris for working together in dealing with low power designs for reconfigurable devices. It is a pleasure to work together with Jae in investigating fast configuration circuit architecture. I am also happy to work together with Zubair for Recursive Variable Expansion. I am also indebted to Roel for the Dutch translation of the abstract and also for proofreading this work. I'm thankful to Carlo for providing the Latex template and printing this thesis.

I thank all members of hArtes project for financing this work. It's a great opportunity for me to work together with many professionals in this large project. I would like to thank all of my room mates: Yi Lu, Dimitris, and Fakhar. Thanks for being with me, chatting with me, and helping me during my research. They made our office enjoyable. Doing research at TU Delft also needs administrative and technical assistance. I would like to thank Lidwina, Marjo, Bert, Monique, Erik, and Eef for helping me with administrative and technical stuff during my work at TU Delft.

I will never forget a person that helped me and my family when the first time we arrived in the Netherlands. Thank you very much Oom Hong Tjoen. He helped us to get our accommodation before we came to Delft. He guided us to arrive safely in Delft and picked us up to our first place to live in Delft.

I also would like to thank to all my teachers who taught me about all subjects I need and especially about how to live a better life for being a blessing to many people around me. Thank you very much to all men/women of God who always pray for me to make me strong for my journey in this wonderful life.

Without my parents, I would not be here. I'm grateful to my parents who raised me, who loved me, who taught me, who trained me, and who supported me. They have invested whole of their life to me. Thank my dearest Papa and Mama. Your names are always in my heart.

Life is not just doing a research, life is more than that. My life is more beautiful when I'm with my family. Grace Elizabeth, my dearest wife, thank you for loving me, for supporting me, for helping me, and for being with me. Your love inspired me to be a better husband. Joseph Abraham Thomas, my dearest son, thank you for playing together. Your humorous character refreshed me after working whole day. Eliana Marvella Thomas, my dearest daughter, thank you for supporting me with your special way. By carrying you, I felt peaceful.

Thomas Marconi

Delft, The Netherlands, June 2011

### Table of contents

| Ab  | stract                     |                  |                                                | i                  |

|-----|----------------------------|------------------|------------------------------------------------|--------------------|

| Ac  | knowl                      | edgmen           | nts                                            | iii                |

| Lis | t of Ta                    | ables            |                                                | ix                 |

| Lis | t of Fi                    | gures            |                                                | xi                 |

| Lis | t of A                     | cronym           | s and Symbols                                  | XV                 |

| 1   | Intro<br>1.1<br>1.2<br>1.3 | Proble<br>Resear | m Overview                                     | 1<br>2<br>10<br>11 |

| 2   | Relat                      |                  | <b>k</b>                                       | 13                 |

|     | 2.1                        | Online           | e Hardware Task Placement Algorithms           | 13                 |

|     | 2.2                        | Online           | Task Scheduling and Placement                  | 21                 |

|     | 2.3                        | Low P            | ower Techniques for Reconfigurable Devices     | 22                 |

|     | 2.4                        | Recon            | figuration Overhead Reduction Techniques       | 29                 |

|     | 2.5                        | Summ             | ary                                            | 33                 |

| 3   | Onlir                      | ne Hardv         | ware Task Placement Algorithms                 | 35                 |

|     | 3.1                        | Intellig         | gent Merging Algorithm                         | 36                 |

|     |                            | 3.1.1            | Basic Idea of the Intelligent Merging Strategy | 36                 |

|     |                            | 3.1.2            | The Merging Only if Needed Technique           | 36                 |

|     |                            | 3.1.3            | The Partial Merging Technique                  | 37                 |

|     |                            | 3.1.4            | Direct Combine and Combine Before Placing      | 38                 |

|     |                            | 3.1.5            | Intelligent Merging Algorithm                  | 39                 |

|     |                            | 3.1.6            | Evaluation                                     | 40                 |

|     | 3.2                        | Propos           | sed Quad-Corner Algorithm                      | 45                 |

|   |      | 3.2.1    | Basic Idea of Quad-Corner Strategy             | 45  |

|---|------|----------|------------------------------------------------|-----|

|   |      | 3.2.2    | Two-dimensional Reconfigurable Device          | 46  |

|   |      | 3.2.3    | Task Types                                     | 46  |

|   |      | 3.2.4    | Initial Placement Positions                    | 47  |

|   |      | 3.2.5    | Data Structures                                | 48  |

|   |      | 3.2.6    | Searching Sequences for Placement              | 48  |

|   |      | 3.2.7    | The Algorithm                                  | 48  |

|   |      | 3.2.8    | Evaluation                                     | 49  |

|   | 3.3  | Summ     | ary                                            | 54  |

| 4 | Onli | ne Hard  | ware Task Scheduling and Placement Algorithms  | 55  |

|   | 4.1  | Intellig | gent Stuffing Algorithm for 1D Area Model      | 56  |

|   |      | 4.1.1    | 1D Area Scheduling and Placement Problems      | 56  |

|   |      | 4.1.2    | Intelligent Stuffing Algorithm Main Properties | 57  |

|   |      | 4.1.3    | The Proposed Algorithm                         | 57  |

|   |      | 4.1.4    | Evaluation                                     | 60  |

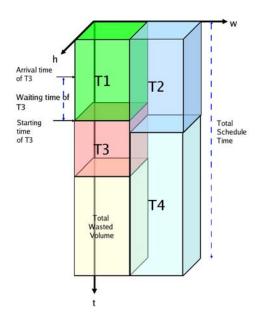

|   | 4.2  | Propos   | sed 3D Compaction Algorithm for 2D Area Model  | 61  |

|   |      | 4.2.1    | Problem of Scheduling and Placement on 2D Area |     |

|   |      |          | Model                                          | 61  |

|   |      | 4.2.2    | Blocking-Aware Algorithm Main Idea             | 62  |

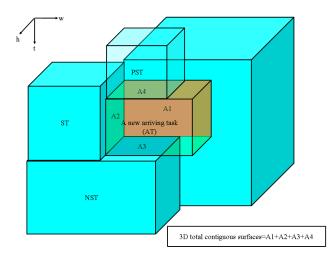

|   |      | 4.2.3    | 3D Total Contiguous Surface (3DTCS) Heuristic  | 63  |

|   |      | 4.2.4    | The 3D Compaction (3DC) Algorithm              | 65  |

|   |      | 4.2.5    | Evaluation                                     | 69  |

|   | 4.3  | Summ     | ary                                            | 74  |

| 5 | Low  | Power L  | ogic Element for FPDs                          | 75  |

|   | 5.1  | Introd   | uction                                         | 75  |

|   | 5.2  | The Pr   | roposed Logic Element                          | 77  |

|   | 5.3  | Transi   | stor-level Circuit Evaluation                  | 83  |

|   |      | 5.3.1    | Experimental Setup                             | 83  |

|   |      | 5.3.2    | Experimental Results                           | 86  |

|   | 5.4  | Evalua   | ation using a Real CAD Tool on a Real FPGA     | 89  |

|   |      | 5.4.1    | Experimental Setup                             | 89  |

|   |      | 5.4.2    | Experimental Results                           | 92  |

|   | 5.5  | Summ     | ary                                            | 96  |

| 6 | Impr | oved Co  | onfiguration Circuit Architecture for FPGAs    | 99  |

|   | 6.1  | Introd   | uction                                         | 99  |

|   | 6.2  | Config   | guration Circuit Architecture                  | 100 |

|     | 6.3     | Evaluation              |  |

|-----|---------|-------------------------|--|

|     | 6.4     | Summary 109             |  |

| 7   | Conc    | lusions and Future Work |  |

|     | 7.1     | Main Contributions      |  |

|     | 7.2     | Open Issues             |  |

| Bib | oliogra | phy                     |  |

| Lis | t of Pı | blications              |  |

| Sa  | menva   | tting                   |  |

| Cu  | rriculu | m Vitae                 |  |

### List of Tables

| 1.1 | Virtex FPGAs                                                                                                                                              | 5  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Simulated task sets (W:task width, H:task height, Lt:task life-<br>time)                                                                                  | 41 |

| 3.2 | Some examples of implemented hardware tasks ( $et_i$ for 100 operations, $rt_i$ at 100 MHz)                                                               | 50 |

| 4.1 | Obtained results using 100,000 task sets (TWA:total wasted area, TST:total schedule time, TRT:total response time and TAT:total algorithm execution time) | 60 |

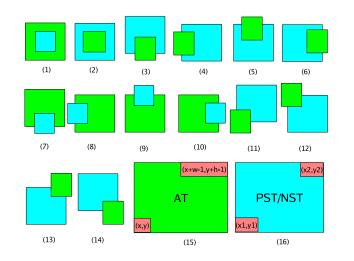

| 4.2 | Computations of horizontal contiguous surfaces for positions in Figure 4.6(1)-(14)                                                                        | 65 |

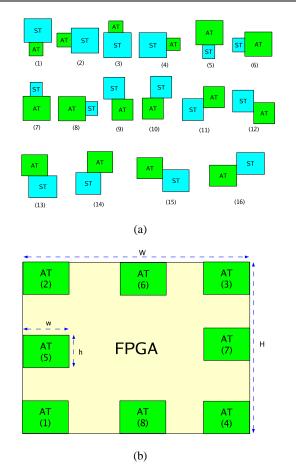

| 4.3 | Computations of vertical contiguous surfaces with scheduled tasks for positions in Figure $4.7(a)(1)-(16)$                                                | 65 |

| 4.4 | Computations of vertical contiguous surfaces with the FPGA boundary for positions in Figure $4.7(b)(1)$ - $(8)$                                           | 67 |

| 4.5 | Time complexity analysis of 3D Compaction algorithm                                                                                                       | 69 |

| 5.1 | The true table of $CLCG_1(conv)$                                                                                                                          | 82 |

| 5.2 | The true table of $CLCG_1(our)$                                                                                                                           | 82 |

| 5.3 | The MCNC benchmark circuits                                                                                                                               | 83 |

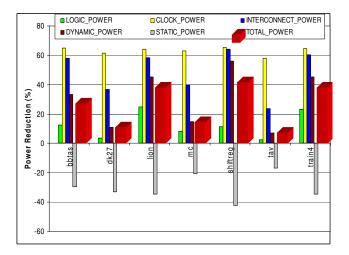

| 5.4 | Experimental results of Logic, Clock, and Interconnect Power $(\mu W)$                                                                                    | 87 |

| 5.5 | Experimental results of Dynamic, Static, and Total Power ( $\mu$ W)                                                                                       | 87 |

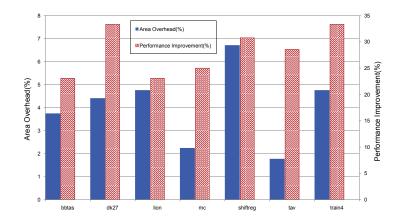

| 5.6 | Experimental results of power consumption at 50 MHz                                                                                                       | 93 |

| 5.7 | Experimental results of area and maximum clock frequency                                                                                  | 94  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.8 | Power reduction at 100, 150, and 200 MHz                                                                                                  | 94  |

| 5.9 | Comparison to clock gating solutions                                                                                                      | 96  |

| 6.1 | Speedup (S) (times) and bitstream size (BSS) reduction (R) (%) compared to the conventional FPGA (h and w are in number of occupied CLBs) | 108 |

| 6.2 | Area overhead                                                                                                                             | 109 |

# List of Figures

| 1.1  | Running multiple applications concurrently on a partially re-<br>configurable device | 2  |

|------|--------------------------------------------------------------------------------------|----|

| 1.2  | System Model (OS: operating system, P: placer, S: scheduler)                         | 7  |

| 1.3  | System at Design Time                                                                | 8  |

| 1.4  | System at Runtime                                                                    | 9  |

| 2.1  | KAMER vs KNER                                                                        | 14 |

| 2.2  | A rejection of an arriving task due to its previous wrong split-<br>ting decision    | 15 |

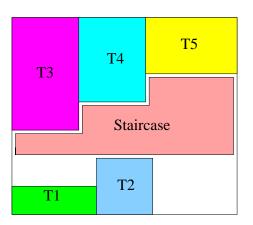

| 2.3  | Area matrix of the staircase algorithm                                               | 16 |

| 2.4  | A staircase                                                                          | 17 |

| 2.5  | Area matrix of SLA                                                                   | 17 |

| 2.6  | Fragmentation matrix of CF                                                           | 18 |

| 2.7  | FAP                                                                                  | 20 |

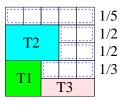

| 2.8  | Stuffing vs Classified Stuffing                                                      | 21 |

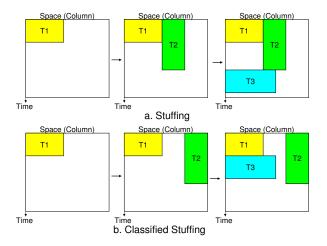

| 2.9  | Clock gating                                                                         | 24 |

| 2.10 | A partially reconfigurable FPGA                                                      | 30 |

| 3.1  | MON technique                                                                        | 36 |

| 3.2  | PM technique                                                                         | 37 |

| 3.3  | DC technique                                                                         | 38 |

| 3.4  | Pseudocode of Intelligent Merging algorithm                                          | 40 |

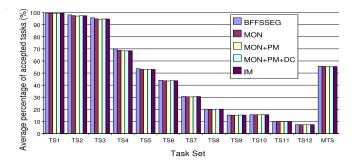

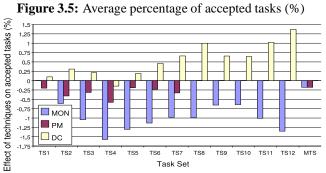

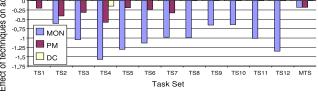

| 3.5  | Average percentage of accepted tasks (%)                                             | 43 |

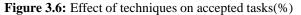

| 3.6  | Effect of techniques on accepted tasks(%)                                            | 43 |

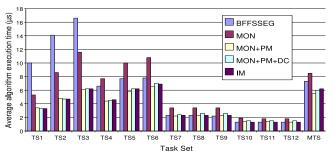

| 3.7  | Average algorithm execution time( $\mu$ s)                                      | 43 |

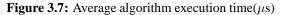

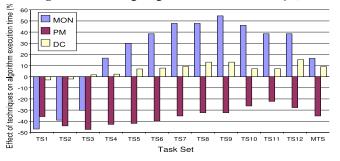

|------|---------------------------------------------------------------------------------|----|

| 3.8  | Effect of techniques on the algorithm execution time(%) $\ldots$                | 43 |

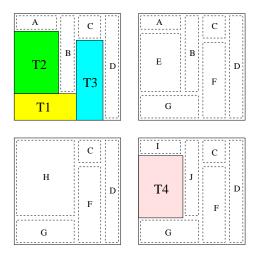

| 3.9  | Basic idea of quad-corner strategy                                              | 46 |

| 3.10 | Examples of four task types and their alternative placement positions           | 47 |

| 3.11 | The pseudocode of QC strategy                                                   | 49 |

| 3.12 | Evaluation with real hardware tasks                                             | 52 |

| 3.13 | FPGA technology impact on penalty (%) and wasted area (%)                       | 53 |

| 4.1  | Performance parameters and previous algorithms                                  | 56 |

| 4.2  | Our Intelligent Stuffing algorithm                                              | 58 |

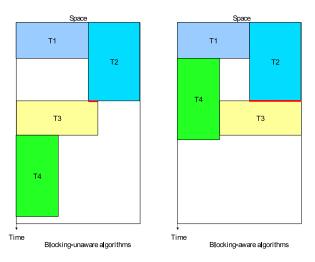

| 4.3  | Problem of scheduling and placement on 2D area model                            | 61 |

| 4.4  | Basic idea of blocking-aware algorithm                                          | 62 |

| 4.5  | 3D total contiguous surface (3DTCS) heuristic                                   | 63 |

| 4.6  | Horizontal contiguous surfaces                                                  | 64 |

| 4.7  | Vertical contiguous surfaces with scheduled tasks (a) and the FPGA boundary (b) | 66 |

| 4.8  | Pseudocode of 3D Compaction algorithm                                           | 68 |

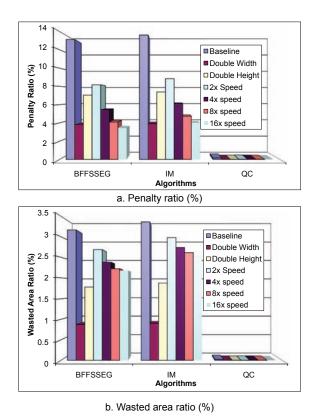

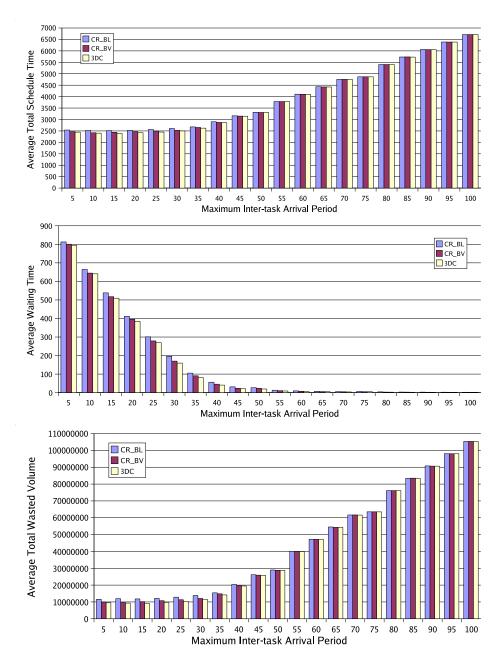

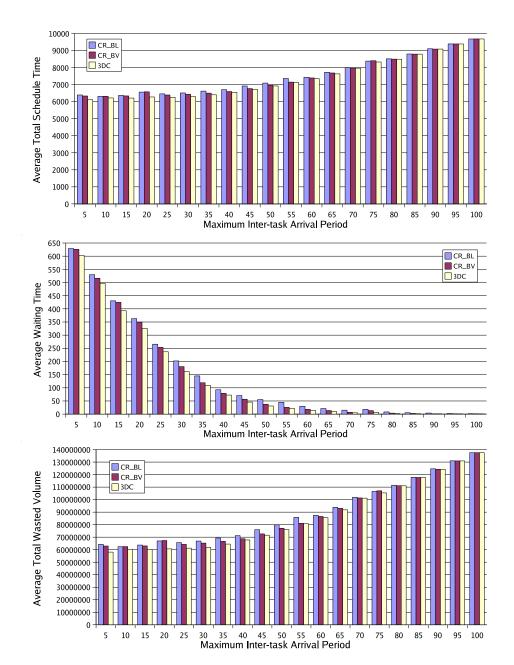

| 4.9  | Evaluation with synthetic workloads                                             | 71 |

|      | Evaluation with real workloads                                                  | 72 |

| 4.11 | Evaluation of algorithm execution time                                          | 73 |

|      |                                                                                 |    |

| 5.1  | Logic elements                                                                  | 77 |

| 5.2  | Basic operations of logic elements                                              | 78 |

| 5.3  | Shortest clock timing of conventional (a) and our (b) logic elements            | 80 |

| 5.4  | Simple circuit examples                                                         | 82 |

| 5.5  | Logic elements used in our experiments                                          | 84 |

| 5.6  | A flip-flop circuit used in conventional LE experiments                         | 85 |

| 5.7  | A flip-flop circuit used in the proposed LE experiments                         | 85 |

| 5.8  | Power Reduction (%)                                                             | 87 |

| 5.9  | Area Overhead and Performance Improvement (%)                                   | 88 |

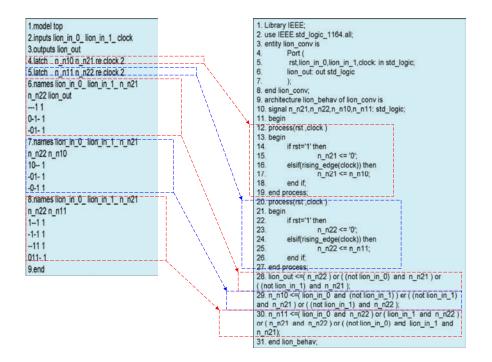

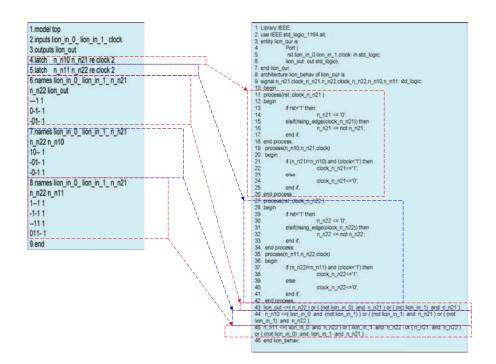

| 5.10 | blif to conventional VHDL conversion (lion.blif to                      |     |

|------|-------------------------------------------------------------------------|-----|

|      | lion_conv.vhd)                                                          | 90  |

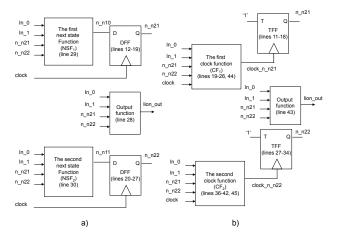

| 5.11 | lion benchmark example implemented using both coding styles             | 90  |

| 5.12 | blif to our VHDL file conversion (lion.blif to lion_our.vhd) $\ . \ .$  | 91  |

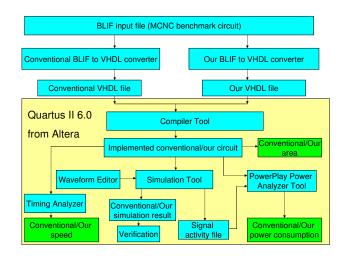

| 5.13 | Experimental setup                                                      | 92  |

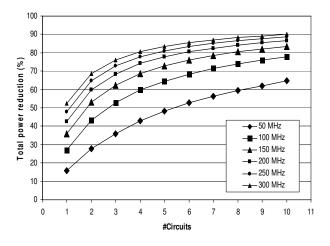

| 5.14 | Overall power (%) reduction versus number of circuits (#Circuits)       | 95  |

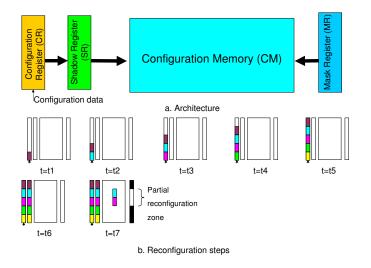

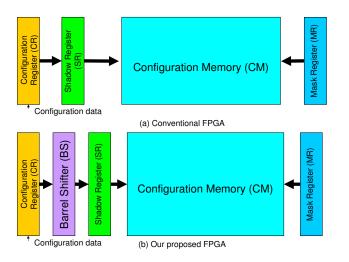

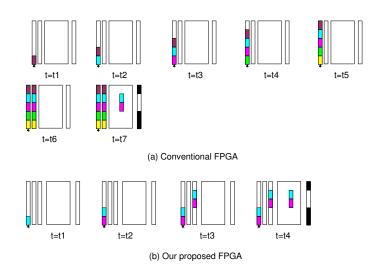

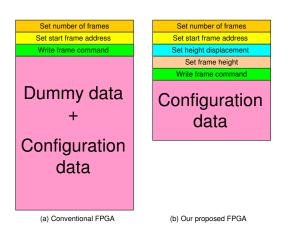

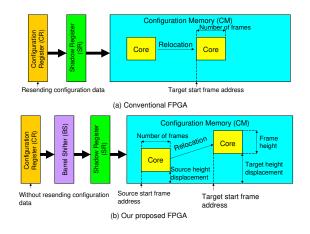

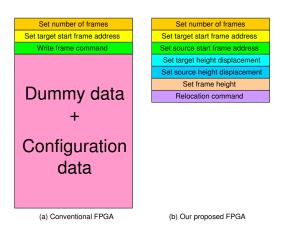

| 6.1  | Architecture of the conventional FPGA versus our proposed FPGA          | 101 |

| 6.2  | Reconfiguration steps of the conventional FPGA versus our proposed FPGA | 102 |

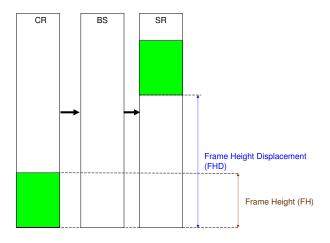

| 6.3  | Mechanism of our proposed architecture                                  | 103 |

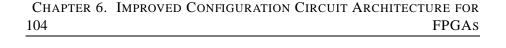

| 6.4  | Hardware overhead for supporting fast reconfiguration                   | 104 |

| 6.5  | Bitstream for reconfiguration                                           | 105 |

| 6.6  | Core relocation                                                         | 106 |

| 6.7  | Bitstream for core relocation                                           | 107 |

# List of Acronyms and Symbols

| 3DC   | 3D Compaction                             |

|-------|-------------------------------------------|

| 3DTCS | 3D Total Contiguous Surface               |

| ASICs | Application-Specific Integrated Circuits  |

| AT    | Arriving Task                             |

| BER   | Balanced Empty Rectangles                 |

| BF    | Best Fit                                  |

| BL    | Bottom-Left                               |

| BLIF  | Berkeley Logic Interchange Format         |

| BV    | Boundary Value                            |

| CABAC | Context-Adaptive Binary Arithmetic Coding |

| CB    | Clustering Based                          |

| CBP   | Combine Before Placing                    |

| CLBs  | Configurable Logic Blocks                 |

| CLCG  | Combinational Logic Circuit Generator     |

| СМ    | Configuration Memory                      |

| CPLDs | Complex PLDs                              |

| DC    | Direct Combine                            |

| DFF   | D Flip-Flop                               |

| DVS   | Dynamic Voltage Scaling                   |

| EA    | Earliest Available time                   |

| FAP   | Fragmentation-Aware Placement             |

| FH    | Frame Height                              |

| FHC   | Frame Height Counter                      |

| FHD   | Frame Height Displacement                 |

| FHDR  | Frame Height Displacement Register        |

| FHR   | Frame Height Register                     |

| FIR   | Finite Impulse Response                   |

| FM    | Fragmentation Matrix                      |

| FPD   | Field-Programmable Device                 |

| FPGA  | Field-Programmable Gate Array             |

| FSM   | Finite State Machine                      |

| GPP   | General-Purpose Processor                 |

| HAP   | Horizontal Alternative Position           |

| HDL   | Hardware Description Language             |

| HL    | Horizontal Line                           |

| HLS          | High-Level Synthesis                     |

|--------------|------------------------------------------|

| ICAP         | Internal Configuration Access Port       |

| IM           | Intelligent Merging                      |

| IPR          | Impossible Placement Region              |

| IS           | Intelligent Stuffing                     |

| KAMER        | Keeping All Maximal Empty Rectangles     |

| KNER         | Keeping Non-overlapping Empty Rectangles |

| LE           | Logic Element                            |

| LER          | Large Empty Rectangles                   |

| LIF          | Least Interference Fit                   |

| LLT          | Lower Left Task                          |

| LLTI         | Lower Left Task Initial                  |

| LRT          | Lower Right Task                         |

| LRTI         | Lower Right Task Initial                 |

| LSEG         | Longer Segment                           |

| LSLG<br>LSQR | Large Square Empty Rectangles            |

| LUT          | LookUp Table                             |

| MCNC         | Microelectronic Center of North Carolina |

| MER.         | Maximal Empty Rectangle                  |

| MER<br>MKEs  | Maximum Key Elements                     |

| MON          | Merging Only if Needed                   |

| MDN<br>MR    | Mask Register                            |

| MR<br>NER    | Non-overlapping Empty Rectangle          |

| NER<br>NPP   | Nearest Possible Position                |

|              | Next State Function                      |

| NSF          |                                          |

| NST          | Next Scheduled Task                      |

| OTF          | On The-Fly                               |

| PLDs         | Programmable Logic Devices               |

| PM           | Partial Merging                          |

| PPR          | Possible Placement Region                |

| PST          | Previous Scheduled Task                  |

| QC           | Quad-Corner                              |

| RCP          | Routing-Conscious Placement              |

| RPR          | Reuse and Partial Reuse                  |

| SAF          | Signal Activity File                     |

| SFTD         | Sum of Finishing Time Difference         |

| SHDR         | Source Height Displacement Register      |

| SL           | Space List                               |

| SLA          | Scan Line Algorithm                      |

| SPLDs | Simple PLDs                                                             |

|-------|-------------------------------------------------------------------------|

| SQR   | Square Empty Rectangles                                                 |

| SR    | Shadow Register                                                         |

| SRAM  | Static Random Access Memory                                             |

| SSEG  | Shorter Segment                                                         |

| SSFAR | Source Start Frame Address Register                                     |

| ST    | Scheduled Task                                                          |

| STM   | Starting Time Matrix                                                    |

| SUR   | Space Utilization Rate                                                  |

| TAAF  | Time-Averaged Area Fragmentation                                        |

| TAT   | Total Algorithm Execution Time                                          |

| TCM   | Task Configuration Microcode                                            |

| TFF   | T Flip-Flop                                                             |

| THDR  | Target Height Displacement Register                                     |

| TL    | Task List                                                               |

| TPA   | Task Parameter Address                                                  |

| TPHRA | Task Placement Algorithm for Heterogeneous Reconfigurable Architectures |

| TRT   | Total Response Time                                                     |

| TST   | Total Schedule Time                                                     |

| TWA   | Total Wasted Area                                                       |

| ULT   | Upper Left Task                                                         |

| ULTI  | Upper Left Task Initial                                                 |

| URT   | Upper Right Task                                                        |

| URTI  | Upper Right Task Initial                                                |

| VAP   | Vertical Alternative Position                                           |

| VHDL  | VHSIC Hardware Description Language                                     |

| VHSIC | Very-High-Speed Integrated Circuit                                      |

| VLS   | Vertex List Set                                                         |

# Introduction

owadays, digital electronic systems are used in a growing number of real life applications. The most flexible and straight forward way to implement such a system is to use a processor that is programmable and can execute wide variety of applications. The hardware, a general-purpose processor (GPP) in this case, is usually fixed/hardwired, whereas the software ensures the computing system flexibility. Since such processors perform all workloads using the same fixed hardware, it is too complex to make the hardware design efficient for a wide range of applications. As a result, this approach cannot guarantee the best computational performance for all intended workloads. Designing hardware devices for a particular single application, referred as Application-Specific Integrated Circuits (ASICs), provides a system with the most efficient implementation for the given task, e.g., in terms of performance but often area and/or power. Since this requires time consuming and very costly design process along with expensive manufacturing processes, it is typically not feasible in both: economic costs and time-to-market. This solution, however, can become interesting when very high production volumes are targeted. Another option that allows highly flexible as well as relatively high performance computing systems is using reconfigurable devices, such as FPGAs. This approach aims at the design space between the full custom ASIC solution and the General-Purpose Processors. Often platforms of this type integrate reconfigurable fabric with general-purpose processors and sometimes dedicated hardwired blocks. Since such platforms can be used to build arbitrary hardware by changing the hardware configuration, they provide a flexible and at the same time relatively high performance solution by exploiting the inherent parallelism in hardware. Such systems where hardware can be changed at runtime are referred as runtime reconfigurable systems. A system involving partially reconfigurable (FPGA) device can change some parts during runtime without interrupting the overall system operation [1, 83, 154]. For example,

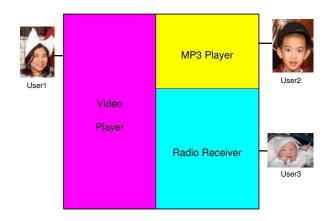

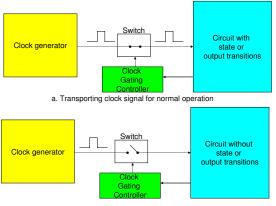

**Figure 1.1:** Running multiple applications concurrently on a partially reconfigurable device

while user1 is watching her exciting film, user2 can use part of the unoccupied hardware resources to enjoy listening to his favorite song without interrupting other user tasks running (e.g., the task used by user3 to listen to her favorite radio station) as illustrated in Figure 1.1. In this thesis, we target runtime reconfigurable systems that integrate tightly coupled general-purpose processor and a reconfigurable device, e.g., FPGA. This chapter provides the overview of the research presented in this dissertation. The main problems in runtime reconfigurable systems, addressed in this dissertation, are introduced in Section 1.1. In Section 1.2, we discuss briefly the main contributions of our work. The overall organization of this dissertation is presented in Section 1.3.

### **1.1 Problem Overview**

Current devices used in runtime reconfigurable systems have the ability to reconfigure parts of their hardware resources without interrupting the normal operation of processing elements instantiated on the remaining fabric. Run time configuration has been used in several application areas and implementations, e.g., network crossbar switches [2], image interpolation [3], video coding [4], cryptography [5], neural network implementation [6], image processing [7], image compression [8], filters [9], matrix multiplications [9], motion estimation [10], mechatronics [11], Viterbi decoding [12] [14], multimedia player [13], Department of Defense (DOD) systems [15], Reed-Solomon

#### Coder/Decoder [16], among many others.

Exploiting partially reconfigurable devices for runtime reconfigurable systems can offer reduction in hardware area [6] [3] [4] [5] [8] [9] [11] [13], power consumption [5] [10] [12] [14] [61] [83] [84], economic cost [5], bitstream size [15], and reconfiguration time [15] [16] [83] [154] in addition to performance improvements [5] due to better resource customization. To make better use of these benefits, one important problem that needs to be addressed is hardware task scheduling and placement. Since hardware tasks are allocated and deallocated dynamically at runtime, the reconfigurable fabric can suffer of fragmentation. This can lead to undesirable situations where tasks cannot be allocated even if there would be sufficient free area available. As a result, the overall system performance will be penalized. Therefore, efficient hardware management of resources is very important.

Hardware task scheduling and placement algorithms can be divided into two main classes: offline and online. Offline assumes that all task properties (e.g., arrival times, task sizes, execution times, and reconfiguration times) are known in advance. The offline version can then perform various optimizations before the system is started. In general, the offline version has much longer time to optimize system performance compared to the online version. However, the offline approach is not applicable for systems where arriving tasks properties are unknown beforehand. In such general-purpose systems, the online version is the only possible alternative. In contrast to the offline approach, the online version needs to take decisions at runtime; as a result, the algorithm execution time contributes to the overall application latency. Therefore, the goal of the online scheduling and placement algorithms is not only to produce better scheduling and placement quality, they also have to minimize the runtime overhead. In this thesis, we focus on online scheduling and placement since we strongly believe it represents a more genetic situation. The online algorithms have to quickly find suitable hardware resources on the partially reconfigurable device for the arriving hardware tasks. In cases when there are no available resources for allocating the hardware task at its arrival time, the algorithms have to schedule the task for future execution.

Field-Programmable Devices (FPDs) are integrated circuits that can be (re)configured by their end users to implement various digital functions [17]. There are three FPD main categories: Simple Programmable Logic Devices (SPLDs), Complex PLDs (CPLDs) and Field-Programmable Gate Arrays (FP-GAs) [17]. The main difference between PLDs and FPGAs is in the available number of logic inputs and the available logic capacities. While FPGAs

have much higher logic capacity (and flip-flop to logic ratio), CPLDs offer more logic inputs. Advantages of using field-programmable devices (FPDs) in runtime reconfigurable systems are instant manufacturing turnaround, reduced start-up costs, low financial risk, short time-to-market and easy design changes [17]. However to get these benefits, the users need to pay additional costs: higher power consumption (approximately 12x larger dynamic power), larger silicon areas (40x more area required) and lower operating speeds (3.2x slower), as compared to the ASICs [18]. Higher power consumption requires expensive packaging [19] [20] [21], shortens chip life-times [19], asks for costly cooling systems [19] [20] [21], decreases system reliability [21] and prohibits battery operations [19] [20] [21]. Therefore, reducing the power consumption of FPDs (CPLDs and FPGAs) is a critical issue.

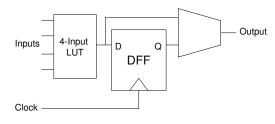

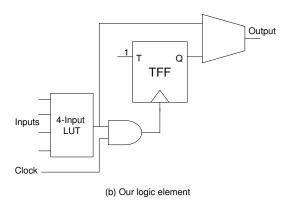

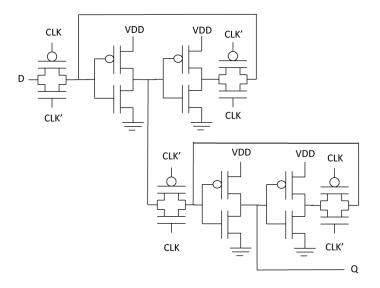

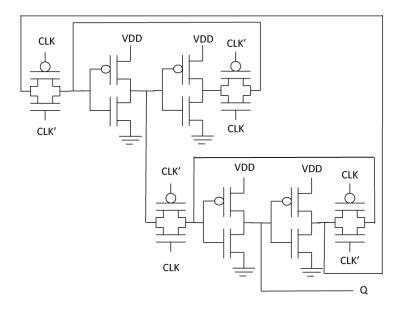

An FPGA device can be used to build arbitrary hardware circuits (same as any ASIC could implement) by reconfiguring and interconnecting its configurable logic elements (LEs) in different ways. Each LE contains a lookup table (LUT) as a configurable combinational circuit and a flip-flop (FF) as a storage element. A group of LEs forms configurable logic block (CLB). The CLB is the basic logic element used by Xilinx FPGAs. A somehow similar approach is used by Altera to organize LEs in clusters called logic array blocs (LABs). The complexity of the FPGAs in terms of available CLBs or LABs is growing very fast with the CMOS technology improvements and now allows the implementation of complete systems. Modern FPGAs can be used to implement circuits with complexity up to 474240 LUTs and 948480 FFs as shown in Table 1.1. The FPGA device can be reconfigured by changing the content of its configuration memory. The configuration memory content, called bitstream (BS) can be up to 185 Mbits and has to be transported to the FPGA internal memory using a dedicated configuration data path. Configuration data paths have usually limited bandwidth, hence, the time needed to send the configuration bits (called *reconfiguration time*) can be up to 58 ms for current technology with 32-bit wide configuration data path operating at 100 MHz. High reconfiguration time overhead can eclipse the benefits of dynamically reconfigurable systems. Therefore, it is very important to address this overhead. In addition, to use the FPGA resources more effectively and to cope with FPGA area fragmentation during runtime, one needs to easily reorganize the positions of running tasks, hence fast relocation is also necessary.

In this thesis, we assume pre-designed hardware tasks where for each task at least two options for execution exist: as software task on general-purpose processor or as hardware unit on the reconfigurable fabric. In the assumed system, each task can arrive at any time and its properties are unknown to the sys-

| FPGAs    | LUTs   | FFs    | Bitstream size(Mbits) | Reconfiguration time(ms) |

|----------|--------|--------|-----------------------|--------------------------|

| Virtex-4 | 178176 | 178176 | 51                    | 16                       |

| Virtex-5 | 207360 | 207360 | 83                    | 26                       |

| Virtex-6 | 474240 | 948480 | 185                   | 58                       |

Table 1.1: Virtex FPGAs

tem beforehand. This models real situations in which the time when the user requests system resources for his/her usage is unknown. As a result, the envisioned system has to provide support for runtime hardware tasks placement and scheduling since this cannot be done statically at system design time. Similar to other work (e.g., [22]- [53]), we assume that each hardware task requires reconfigurable area with rectangular shape and can be placed at any location on the reconfigurable device. Our task model includes all required reconfigurable units and interconnect resources. Each hardware task is defined by three parameters: its *area* (width and height in terms of atomic reconfigurable units), *reconfiguration time*, and its *execution time* (the latter two expressed in system clock cycles).

The software tasks that are identified for hardware acceleration are first designed using a hardware description language and after that are placed and routed by commercial FPGA synthesis CAD tools to obtain functionally equivalent modules that can replace their respective software versions. At this step of the design process we can use the synthesis results to extract the task sizes for the used FPGA fabric. The output of the synthesis is the configuration bitstream that should be loaded to the device using its integrated configuration infrastructure. Therefore, starting from the task bitstream file, we can obtain precisely its reconfiguration time on the targeted technology. The two key ingredients are the configuration data size (the bitstream length in number of bits) and the throughput of the internal FPGA configuration circuit. As an example, the Internal Configuration Access Port (ICAP) of Virtex 4 FPGAs from Xilinx can transport 3200 million bits/second and will load a bitstream of size 51 Mbits in 15.9ms. The last parameter, the task execution time is specified by the time needed to process a unit of data (referred as: Execution Time Per Unit of Data, ETPUD) and the overall data size to be processed (i.e. how much data need to be processed). Please note that for some applications, the task execution time is also dependent on the exact data content (e.g., as in the case of Viterbi and Context-Adaptive Binary Arithmetic Coding (CABAC)). In such applications, even when processing the same amount of data, the elapsed time will be different when the input data content changes. To address data dependent task execution times, we envision two solutions: worst case execution

#### time scenario and notification on task completion HW support.

In this thesis, we assume the worst case execution time scenario in which we use the task execution time when processing the worst case input data content. In such scenario, it is possible that the actual task completion can happen earlier than the scheduled completion time resulting in idle times that can not be used by the scheduler. In addition, such tasks will cause additional wasted area that cannot be utilized immediately by other HW tasks. In such non-optimal scenario, however, the overall computing system will operate correctly. Please note that the chosen scenario is the worst case in respect to the proposed placement and scheduling algorithms due to the introduced overheads in task execution time and wasted area. The second solution requires dedicated hardware support for feedback signaling when the running tasks complete, however, as mentioned earlier this can additionally improve the overall system performance. Some existing systems already have the necessary ingredients required to implement such support. For example, in the Molen architecture [203], the sequencer is aware of the hardware (HW) task start and completion timing. The only necessary extension in this case is to provide a way to pass this information to the HW scheduler and make it aware of running tasks completion. With this knowledge, the HW scheduler can make data content dependent tasks scheduling more efficient. This approach is outside of the scope of this thesis without loosing generality of our proposal. Even more the selected worst case execution scenario is less beneficial for the scheduling and placement algorithms presented in this thesis. We are strongly convinced that both types of systems will be able to benefit from the proposed algorithms.

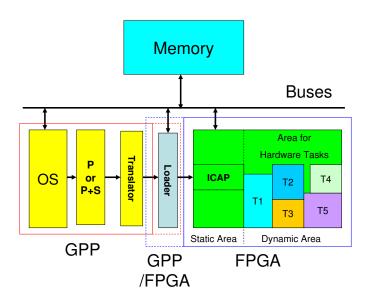

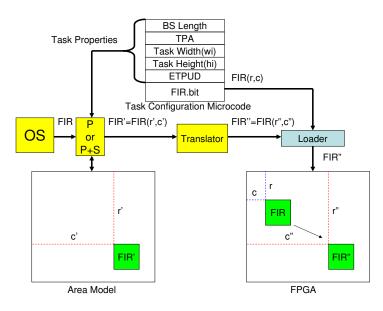

The assumed overall system model used in our study is depicted in Figure 1.2 consisting of two main devices: the general-purpose processor (GPP) and the reconfigurable device (FPGA). All hardware task bitstream images are available in a repository resuming in the main memory (not explicitly shown on the figure) and can be requested by any running application on the GPP by using a dedicated operating system (OS) call. In response to such request, the OS will invoke the Placer (P) to find the best location on the FPGA fabric for the requested hardware task. Once appropriate location is found, the Translator will resolve the coordinates by transforming the internal, technology independent model representation to the corresponding low level commands specific for the used FPGA device. The Loader reads the task configuration bitstream from the repository and sends it to the internal configuration circuit, e.g., ICAP in case of Xilinx, to partially reconfigure the FPGA at the specific physical location provided by the Translator. After reconfiguring the FPGA fabric the requested hardware task execution is started immediately to avoid idle hardware units on

Figure 1.2: System Model (OS: operating system, P: placer, S: scheduler)

the reconfigurable fabric. For systems with combined Placer and Scheduler (P+S), when the hardware area is fully occupied, the Scheduler (S) schedules the task for future execution at predicted free area places at specific locations and specific starting times. For systems with only Placer (P), in cases when no hardware resources are available the corresponding task can be executed using its software version with significant and often unpredictable execution time penalty. The Loader can be implemented at either the general-purpose processor (GPP) as OS extension or in the Static Area of the FPGA. If the Loader is implemented in the GPP, the communication between the Loader to the ICAP is performed using the available off-chip connection. For implementations in the FPGA, the Loader connects to the ICAP internally. Similar to [202], dedicated buses are used for the interconnect on chip. Those buses are located at every row of the reconfigurable regions to allow data connections between tasks (or tasks and I/Os) regardless of the particular task sizes.

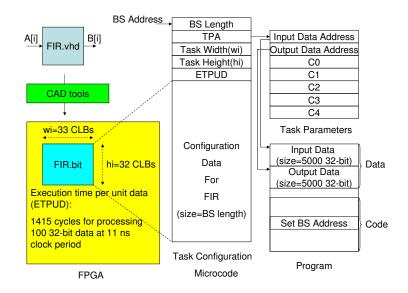

To illustrate the above processes at different stages of the system design and normal operation, we will use a simple example of hardware task creation as depicted in Figure 1.3. The hardware task in our example is a simple finite impulse response (FIR) filter. The task consumes input data from array A[i] and produces output data stored in B[i], where B[i] = C0 \* A[i] + C1 \* A[i+1] + C2 \* A[i+2] + C3 \* A[i+3] + C4 \* A[i+4] and all data elements are 32 bits

Figure 1.3: System at Design Time

wide. The task implementation described using a hardware description language (HDL) (FIR.vhd) is synthesized by commercial CAD tools that produce the partial bitstream file (FIR.bit) along with the additional synthesis results for that task. The bitstream contains the configuration data that should be loaded into the configuration memory to instantiate the task at a certain location on the FPGA fabric. The synthesis results are used to determine the rectangle area consumed by the task in terms of configurable logic blocks (CLBs) specified by the width and the height of the task. In our example, the FIR task width is 33 and the task height 32 CLBs for Xilinx Virtex-4 technology. Based on the synthesis output we determine the tasks reconfiguration times. Please note, that in a realistic scenario one additional design space exploration step can be added to steer task shapes toward an optimal point. At such stage, both, task sizes and reconfiguration times are predicted by using high-level models as the ones described in [54] in order to perform quick simulation of the different cases without the need of synthesizing all of the explored task variants. For example in Virtex-4 FPGA technology from Xilinx, there are 22 frames per column and each frame contains 1312 bits. Therefore one column uses 22x1312 = 28864 bits. Since our FIR HW task requires 33 CLBs in 2 rows of 16 CLBs totaling in 32 CLBs, we obtain a bitstream with 33x2x28864 = 1905024 bits. Virtex-4 ICAP can send 32-bit data every 100 MHz clock cycle, hence, we can estimate the reconfiguration time as  $1905024 \times 10/32 = 595320$  ns. Next,

Figure 1.4: System at Runtime

the FIR task is tested by the designer to determine how fast the input data can be processed. For our example from Figure 1.3, the task needs 1415 cycles to process 100, 32-bit input data elements at 11 ns clock period making its ETPUD 1415x11 = 15565 ns per 100, 32-bit unit data. Based on the above ETPUD number, we can estimate the task execution time for various input data sizes. In our example, there are 5000, 32-bit input data elements that have to be processed by the FIR HW task. Therefore, the expected execution time of our FIR task is  $(5000/100) \times 15565 = 778250$  ns (778ms). The configuration data and task specific information are merged together in what we call a Task Configuration Microcode (TCM) block as shown in the upper part of Figure 1.3. TCM is pre-stored in memory at the Bitstream (BS) Address. The first field, the BS length represents the size of the configuration data field. This value is used by the Loader when the task is fetched from memory. The task parameter address (TPA) is needed to define where the task input/output parameters are located. In Figure 1.3, the task parameters are the input and output data locations, the number of data elements to be processed and the FIR filter coefficients (C0-C4). The input data address gives the location where the data to be processed remains. The location where the output data should be stored is defined by the output data address.

During runtime, when the system needs to execute the FIR hardware task on

the FPGA, the OS invokes the Placer (P) to find a location for it (shown as example, in Figure 1.4). From the TCM the Placer gets the task properties information: task width, task height, reconfiguration time, and its execution time. Based on the current state of the used area model, the Placer searches for the best location for the task. When the location is found (in this example: r'and c'), the task is placed in the area model and its state is updated as shown on the left side of the figure. The Translator converts this location into real physical location on the targeted FPGA. In the bitstream file (FIR.bit), there is information about the FPGA location where the HW task was pre-designed (in this figure: r and c). By modifying this information at runtime, the Loader partially reconfigures the FPGA through the ICAP (by using the technology specific commands) at the location obtained from the Translator (r'' and c''in this example). By decoupling our area model from the fine-grain details of the physical FPGA fabric, we propose an FPGA technology independent environment where different FPGA vendors, e.g., Xilinx, Altera, etc, can provide their consumers with full access to partial reconfigurable resources without exposing all of the proprietary details of the underlying bitstream formats. On the other side, reconfigurable system designers can now focus on partial reconfiguration algorithms without having to bother with all low-level details of a particular FPGA technology.

### **1.2 Research Questions and Main Contributions**

As discussed in Section 1.1, efficient runtime reconfigurable systems management has to cope with the three main challenges: minimal hardware use, minimal power consumption, and minimal reconfiguration overhead. In respect to the above challenges the thesis at hand will provide an answer to the following research questions:

- 1. How to improve area utilization, application execution time and algorithm overhead of hardware task placement and scheduling approaches?

- 2. How to reduce the power consumption of reconfigurable devices by improving their basic logic elements?

- 3. Can hardware task reconfiguration overhead be reduced by revisiting the configuration infrastructure?

This dissertation elaborates on the above three questions critical for all modern runtime partially reconfigurable systems. The work contained in this dissertation provides evidence that the aforementioned questions can be successfully answered. More specifically, the main contributions of this thesis are:

- 1. Novel online hardware task scheduling and placement algorithms on partially reconfigurable devices with higher quality and shorter algorithm execution time compared to the state of the art;

- A novel logic element for FPDs with reduced power consumption compared to the industrial FPDs;

- Low overhead FPGA configuration circuit architectural extensions to shorten the reconfiguration and relocation times compared to current high-end FPGA devices.

### **1.3 Dissertation Organization**

This dissertation consists of the following chapters:

- Chapter 2 gives an overview of the state of the art in solving problems in runtime reconfigurable systems. It presents a survey on existing online hardware task scheduling and placement algorithms, techniques to reduce power consumption in reconfigurable devices, and techniques to reduce reconfiguration overhead in runtime reconfigurable systems.

- Chapter 3 introduces two novel algorithms to deal with online hardware task placement problem in runtime reconfigurable systems on partially reconfigurable devices. The first algorithm (Intelligent Merging) deals with reducing algorithm execution time by avoiding unnecessary operations. The algorithm run up to 3x faster than related art with 0.89 % less placement quality. The second one (Quad-Corner) is more challenging, the aim is to discover a faster algorithm yet with a higher quality. The algorithm not only has higher placement quality (78 % less penalty and 93 % less wasted area) than related art but also has lower runtime overhead.

- Chapter 4 presents two novel online hardware task scheduling and placement algorithms on partially reconfigurable devices. The first algorithm (Intelligent Stuffing) is designed for 1D area model. The algorithm outperforms related art in terms of reduced total wasted area up to 89.7 %, has 1.5 % shorter schedule time and 31.3 % shorter waiting time. The

second one (3D Compaction) is proposed for 2D area model. The algorithm has up to 4.8 % shorter schedule time, 75.1 % shorter waiting time, and 22.9 % less wasted volume compared to related art.

- Chapter 5 describes a novel low power logic element (LE) for FPDs. FPDs using our proposal consume 6-90 % less total power and run 2-33 % faster than FPDs using conventional LEs.

- Chapter 6 shows a novel configuration circuit architecture for fast reconfiguration and relocation. The architecture can speedup reconfiguration and relocation by 4x and 19.8x on average, respectively.

- Chapter 7 summarizes our findings and gives some suggestions for future research directions.

# Related Work

**s** presented in Chapter 1, this dissertation targets three major problems in current runtime partially reconfigurable systems: online hardware task scheduling and placement, power consumption, and runtime reconfiguration overhead. Before presenting our proposal of how to address these problems in more detail, in this chapter, we present related work published by other researchers in their attempts to address the same problems.

This chapter is organized as follows. In Section 2.1, we discuss existing online task placement algorithms for partially reconfigurable devices. Related art regarding online task scheduling and placement is presented in Section 2.2. This section is short because work in this area is quite recent. In Section 2.3, we survey existing techniques for reducing power consumption in FPDs. Related work for reducing reconfiguration overhead is addressed in Section 2.4. Finally, we conclude this chapter in Section 2.5.

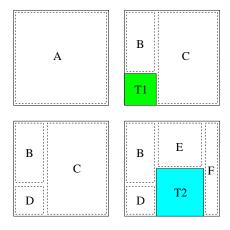

# 2.1 Online Hardware Task Placement Algorithms

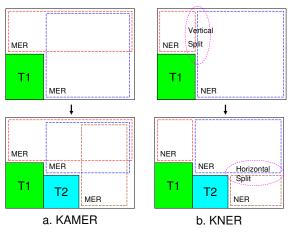

In [22], Bazargan et al. proposed two algorithms: Keeping All Maximal Empty Rectangles (KAMER) and Keeping Non-overlapping Empty Rectangles (KNER). An empty rectangle is a rectangle area that can be used to place a task without overlapping to any running tasks on the FPGA. Such rectangle is used to place each arriving task at runtime. The two algorithms (KAMER and KNER) differ mainly in the way the empty rectangle is partitioned during task placements as shown in Figure 2.1. If the rectangle cannot be expanded anymore, the authors refer to it as a Maximal Empty Rectangle (MER); otherwise they call it a Non-overlapping Empty Rectangle (NER). KAMER organizes all MERs, whereas KNER manages all NERs. If there is an arriving task, both algorithms search all empty rectangles (i.e. MERs for KAMER or NERs

for KNER) to find a suitable one which can fit the arriving task based on one of two-dimensional bin-packing heuristics: First Fit (FF), Best Fit (BF), and Bottom-left (BL). In KNER, only the selected empty rectangle is split into two smaller ones due to non-overlapping empty rectangles to decrease algorithm execution time of KAMER. The splitting can be done in one of two different ways: vertical split or horizontal split. For example, in Figure 2.1, the KNER decides to do vertical split after placing task T1 and horizontal split after placing task T2. Every time the algorithm places the task, it performs splitting operation. If it just splits the empty rectangles and does not merge them, FPGA will be partitioned into smaller and smaller of many empty rectangles. This situation will make placement quality worse, so the algorithm needs to do both merging and splitting operations. The split decision in KNER is made by utilizing one of these heuristics: Shorter Segment (SSEG), Longer Segment (LSEG), Square Empty Rectangles (SQR), Large Square Empty Rectangles (LSQR), Large Empty Rectangles (LER), and Balanced Empty Rectangles (BER). Although the authors have proposed these heuristics to avoid wrong splitting decisions, wrong decisions still cannot be totally avoided, lowering the placement quality of KNER. For example, in Figure 2.2, although the FPGA has enough free area for a new incoming task, KNER rejects it due to its incorrect splitting decision in the past.

Figure 2.1: KAMER vs KNER

In [23] and [24], Tabero et al. proposed a Vertex-list algorithm. Vertex List Set (VLS) data structure is used that each of the lists describes the contour of each unoccupied area fragment in the FPGA. The authors use bottom-left or top-right heuristic for placing arriving tasks on vertexes. The VLS structure is a

Figure 2.2: A rejection of an arriving task due to its previous wrong splitting decision

geometrical description of the whole FPGA free area perimeter. Instead of partitioning free areas as KAMER and KNER, the Vertex-list algorithm focuses on the free area perimeter for placing an arriving task. The algorithm places a task on one of the corners of this free area perimeter based on one of two heuristics: 2D-adjacency-based and fragmentation-based. The 2D-adjacencybased heuristic inserts the task on the vertex position that has the highest contact level in space of the task to the running tasks and the FPGA boundary, while the fragmentation-based heuristic inserts the task on the vertex position that has the lowest fragmentation level. To enhance placement quality of their Vertex-list algorithm, in [25], they proposed two new heuristics: 3D-adjacency and Look-ahead 3D. In addition to the contact level in space, the 3D-adjacency heuristic also computes the contact level in time to pack tasks in space and time. In Look-ahead 3D heuristic, the 3D-adjacency value is computed not only at current time but also at the future time when the next running task is finished. After computing all the 3D-adjacency values, the task is placed at the position with the highest 3D-adjacency value.

In [26] and [27], Steiger et al. and Walder et al. proposed an On The-Fly (OTF) algorithm. As mentioned earlier, the wrong split decision can lower the placement quality of KNER. To avoid such wrong decisions, they modified KNER by delaying the split decision until a next arrived task placed on the FPGA. However, for this modification, they need to resize several rectangles on a task insertion.

In [28], Morandi et al. proposed a Routing Aware Linear Placer (RALP) algo-

rithm. The algorithm is a modified version of KNER algorithm with an additional routing cost consideration between dependent tasks. Tasks are placed on empty rectangles that have the least Manhattan distances between dependent tasks to minimize routing cost. The algorithm can reduce routing cost compared to KNER as reported in [28]. However, it has a lower placement quality that KNER due to the negative impact of its routing consideration.

In [29], Ahmadinia et al. proposed a Horizontal Line (HL) algorithm to manage free space and the Clustering Based (CB) strategy to improve the placement quality of their HL approach. Instead of managing a list of empty rectangles like in KAMER, KNER [22], and OTF [26] [27], HL uses exactly two horizontal lines for placing the task; one above (top horizontal line) and one below (bottom horizontal line) the placed tasks. In order to store information on these horizontal lines, HL uses two separate linked-lists. HL is implemented in such a way that hardware tasks are placed above the currently running tasks as long as there is free space. Once there is no empty space found above the running tasks, the new ones start to be placed below them and so on. The basic idea of CB is to place all tasks with similar end times in the same strip such that a large empty space will be created at a certain location at the end time. This new empty space hopefully will be able to accommodate future larger tasks.

| 1 | -5 | -4 | -3 | -2       | -1 | 1  | 1 |

|---|----|----|----|----------|----|----|---|

| 2 | -5 | -4 | -3 | -2<br>-2 | -1 | 2  | 2 |

| 3 | 1  | 1  | 1  | 1        | 1  | 3  | 3 |

| 4 | 2  | 2  | 2  | 2        | 2  | 4  | 4 |

| 5 | 3  | 3  | 3  | -3       | -2 | -1 | 5 |

| 6 | 4  | 4  | 4  | -3       | -2 | -1 | 6 |

Figure 2.3: Area matrix of the staircase algorithm

In [30] and [31], Handa et al. proposed the Staircase algorithm for finding MERs. A 2D array, referred as area matrix, for modeling the FPGA surface with each cell in the array representing a CLB is used. For example, an FPGA (8x6 CLBs) with two running tasks (5x2 CLBs and 3x2 CLBs) is modeled with an area matrix in Figure 2.3. Every CLB array cell in the free area contains a positive number that gives the number of continuous empty cells in the column above including the cell itself. Every cell in the occupied area holds a negative number that represents the remaining width of the task measured on

Figure 2.4: A staircase

the right side from that cell. The area matrix is used for constructing staircases and finally these staircases are utilized for finding MERs. All the empty rectangles having same bottom right coordinate make a staircase as illustrated in Figure 2.4. They only check maximal staircases for extracting MERs. After a maximal staircase is detected, all the rectangles in the staircase can be checked to see if they are MERs.

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 2 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 1 | 2 | 0 | 0 | 0 |

| 1 | 2 | 3 | 4 | 5 | 6 | 0 | 0 | 0 |

| 1 | 2 | 3 | 4 | 5 | 6 | 0 | 0 | 0 |

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

Figure 2.5: Area matrix of SLA

In [32], Cui et al. proposed the Scan Line Algorithm (SLA) algorithm for finding MERs. The authors use the same area matrix as the staircase algorithm with a different encoding to represent the FPGA area. For example, an FPGA (9x6 CLBs) with two running tasks (4x2 CLBs and 3x4 CLBs) is modeled with an area matrix in Figure 2.5. Every free area CLB is represented by a positive number that gives the number of continuous empty cells on left including that cell as shown in Figure 2.5. Every occupied CLB is represented by a zero. In SLA, the area matrix is used for finding Maximum Key Elements (MKEs)

and finally these MKEs are scanned for finding all MERs. A key element is an empty cell with an occupied cell as its right hand neighbor. A column that contains one or more key elements is called as a scan line. A scan line is partitioned into segments by valley points. A valley point is the element within a scan line where values in the line starting to increase. Each segment has one MKE which is the largest key element in the corresponding segment.

In [33], Xiao et al. discovered that the SLA algorithm can find empty rectangles that are not MERs. To solve this problem, they proposed ESLA algorithm in [33]. Before the algorithm scans each MKE for finding MERs, the algorithm is instrumented with an ability to know a set of valid widths for that corresponding MKE. By doing so, the algorithm only needs to scan an MKE for those valid widths. To avoid duplicated scanning, the algorithm records a set of scanned positions during each MKE scanning.

| 7,4,0 | 7,4,0 | 7,4,0 | 7,2,0 | 7,2,0 | 7,2,0 | 7,6,0 |

|-------|-------|-------|-------|-------|-------|-------|

| 7,4,0 | 7,4,0 | 7,4,0 | 7,2,0 | 7,2,0 | 7,2,0 | 7,6,0 |

| 3,4,0 | 3,4,0 | 3,4,0 | 3,4,9 | 3,4,9 | 3,4,9 | 1,6,0 |

| 3,4,0 | 3,4,0 | 3,4,0 | 3,4,9 | 3,4,9 | 3,4,9 | 1,6,0 |

| 3,2,8 | 3,2,8 | 3,2,8 | 3,4,9 | 3,4,9 | 3,4,9 | 1,6,0 |

|       |       |       |       | 3,4,9 |       |       |

Figure 2.6: Fragmentation matrix of CF

In [34], Cui et al. proposed the Cell Fragmentation (CF) algorithm for their online placement algorithm. CF uses the SLA to find MERs and a Fragmentation Matrix (FM) to represent the area of the FPGA. For example, an FPGA (7x6 CLBs) with two running tasks (3x2 CLBs and 3x4 CLBs) is modeled with a fragmentation matrix in Figure 2.6. For empty cells, each cell is labeled by the number of contiguous empty cells in horizontal, in vertical direction, and a zero. For occupied cells, each cell is labeled by the number of contiguous occupied cells in horizontal, in vertical direction, and the finish time of the task. In order to place a task on the FPGA, CF calculates the Time-Averaged Area Fragmentation (TAAF) for all MERs that are large enough to accommodate the task and then places the task into one of the MERs which has the largest TAAF. The TAAF of a MER is the degree of impact of this MER on the overall degree of fragmentation. A MER with large TAAF means it has more impact on the overall degree of fragmentation, that's why CF places the arriving task to a MER that has the largest TAAF.

In [35] and [36], Tomono et al. proposed an online FPGA algorithm that does not only take into consideration the degree of fragmentation, but also the speed of I/O communication computed based on the Manhattan distances. The aim of their algorithm is to balance the degree of fragmentation and the speed of I/O communication. They use the same area matrix data structure as used by the Staircase algorithm with additional I/O communication constraints, so they increase the degree of fragmentation in order to gain the speed of I/O communication. Because of this additional consideration, they need to check the status of each communication channel during staircase creation.

In [37] and [38], Ahmadinia et al. proposed the Nearest Possible Position (NPP) algorithm. They manage the occupied space rather than the free space, because the set of empty rectangles grows much faster than the set of placed rectangles. The impossible placement region (IPR) of an arriving task relative to a placed task is the region near the placed task where it is impossible to place this arriving task without overlapping the placed task. The possible placement region (PPR) is the area where it is possible to place the arriving task without overlapping any placed tasks. In order to find the best position on the PPR for placing an arriving task, they compute the routing cost based on Euclidean distances and place an arriving task at the optimal point, where routing cost is minimum. If they cannot find the optimal point on the PPR, they will find the Nearest Possible Position (NPP) for placing the task.

In [39], Lu et al. proposed the Multi-Objective Hardware Placement (MOHP) algorithm. The algorithm uses the VLS data structure adopted from [23] and [24]. Incoming tasks are classified into three groups with different treatments. The first group is for independent tasks that need to be executed urgently due to short remaining time to the deadline. To handle tasks in this group, the algorithm uses the FF heuristic for fast allocation. The second group is for independent tasks that do not need urgent treatment. For this group, the algorithm adopts a vertex-list approach from [23] and [24]. The third group is for dependent tasks. In this group, the routing between dependent tasks needs to be shortened. For that reason, the algorithm utilizes the NPP approach adopted from [37] and [38] for tasks in this group.

In [40], Elbidweihy and Trahan proposed an online placement algorithm that manages both Maximal Horizontal Strips (MHS) and Maximal Vertical Strips, called the Maximal Horizontal and Vertical Strips (MHVS) algorithm. MHSs are rectangles generated by partitioning free area using top and bottom boundaries of running tasks; whereas MVSs are rectangles that result from free area partitioning using left and right boundaries of running tasks. In this algorithm, the first fit rectangle is used for placing an arriving task. The algorithm can run faster compared to KAMER as reported in [40]. However, it has a lower placement quality than KAMER.

In [41] and [42], Ahmadinia et al. proposed the Routing-Conscious Placement(RCP). In order to reduce free-space management to a single point, they expand inserted modules and concurrently shrink the FPGA area and an arriving task by half both in width and height. To choose the position for placing an arriving task, they choose a position, such that the weighted communication cost computed based on the Manhattan distances is minimized.

In [43], Köster et al. proposed a task placement algorithm for heterogeneous reconfigurable architectures, TPHRA. The basic idea of this algorithm is to avoid placing an arriving task with many feasible positions in areas that can be used by tasks with few feasible positions whenever possible.

In [44], Ahmadinia and Teich proposed the Least Interference Fit (LIF) algorithm. In order to reduce the reconfigurable overhead due to the limitation of currently available FPGA technology in that time (column-wise reconfigurable capability), LIF places tasks at the position where the tasks interfere with the currently running tasks as little as possible.

Figure 2.7: FAP

In [45], ElFarag et al. proposed the Fragmentation-Aware Placement (FAP) algorithm. In this paper, they introduced a fragmentation metric that gives an indication to the continuity of occupied (or free) space on the reconfigurable device and not the amount of occupied (or free) space. The algorithm places each arriving task on the location where the fragmentation metric is smallest. All empty spaces have to be tested before it can select one that causes the lowest fragmentation. Figure 2.7 shows how they compute the fragmentation metric. There are three tasks (T1, T2, and T3) placed on a reconfigurable device with size of 5x5 reconfigurable units. In the first row of reconfigurable

device, there is one contiguous empty space that consists of five reconfigurable units, therefore the fragmentation in this row is 1/5. Using similar way, the total row fragmentation is ((1/5) + (1/2) + (1/2) + (1/3)), while the total column fragmentation is ((1/1) + (1/1) + (1/1) + (1/4) + (1/4)).

## 2.2 Online Task Scheduling and Placement

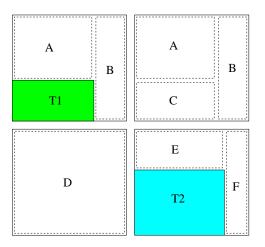

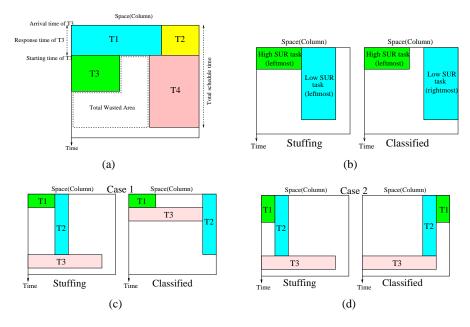

In [46] and [47], Steiger et al. proposed the Horizon and Stuffing algorithms both for 1D and 2D area models. The Horizon guarantees that arriving tasks are only scheduled when they do not overlap in time or space with other scheduled tasks. The Stuffing schedules arriving tasks to arbitrary free areas that will exist in the future by imitating future task terminations and starts. In these papers, the authors reported that the Stuffing algorithm outperforms the Horizon algorithm in scheduling and placement quality.

Figure 2.8: Stuffing vs Classified Stuffing

Discovered that the problem of the Stuffing that always places a task on the leftmost of its free space as shown in Figure 2.8a, Chen and Hsiung in [48] proposed their 1D Classified Stuffing. By classifying incoming tasks before scheduling and placement, the 1D Classified Stuffing performs better than the original 1D Stuffing. For example, because the Stuffing algorithm always places tasks on the leftmost edge of the available area, it places tasks T1 and T2 as shown in Figure 2.8a. These placements block task T3 to be scheduled earlier. In this case, the Stuffing fails to place task T3 earlier. The main difference between the Classified Stuffing and the Stuffing is the classification of

tasks. The Classified Stuffing can place a task on the leftmost or rightmost of its free space based on the task Space Utilization Rate (SUR). SUR is the ratio between the number of columns required by the task and its execution time. High SUR tasks (SUR > 1) are placed starting from the leftmost available columns of the FPGA space, while low SUR tasks (SUR  $\leq$  1) are placed from the rightmost available columns. For this simple example, the Classified Stuffing can recognize the difference between tasks T1 (high SUR task) and T2 (low SUR task), so it places successfully tasks on different sides as shown in Figure 2.8b. Therefore the task T3 can be scheduled earlier by the Classified Stuffing, outperforming the Stuffing as reported in [48].

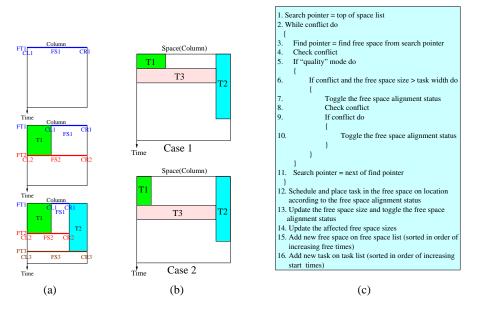

In [49], Marconi et al. proposed their 1D Intelligent Stuffing to solve the problems of both the 1D Stuffing and Classified Stuffing. The main difference between their algorithm and the previous 1D algorithms is the additional alignment flag of each free segment. The flag determines the placement location of the task within the corresponding free segment. By utilizing this flag, the 1D Intelligent Stuffing outperforms the previously mentioned 1D algorithms.

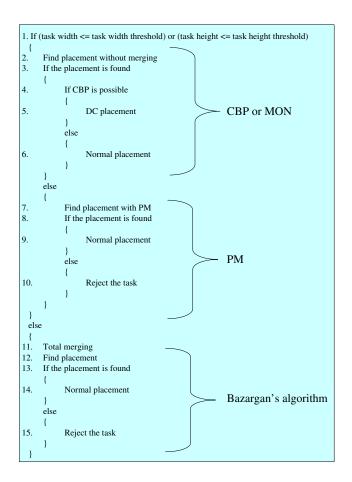

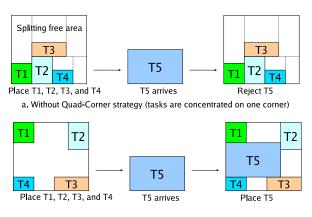

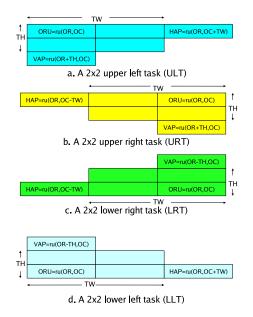

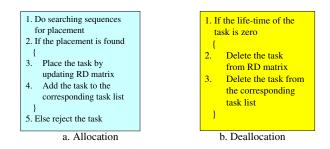

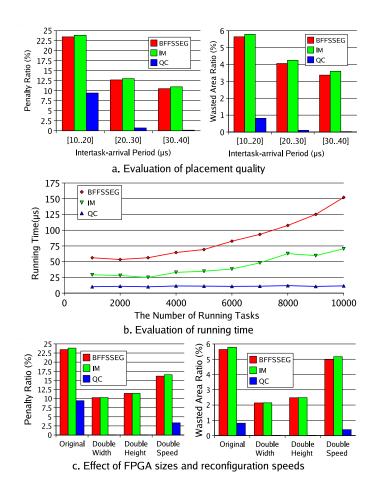

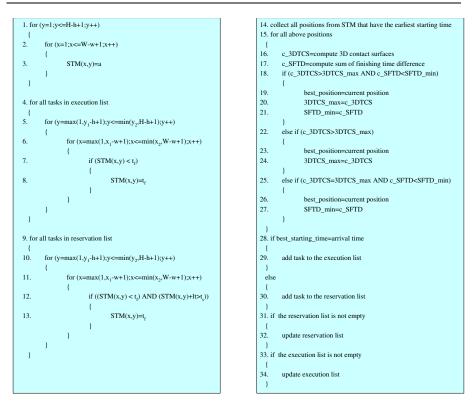

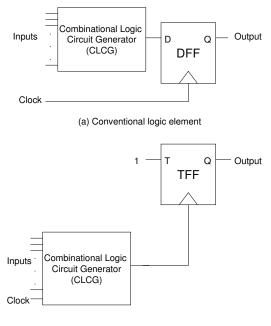

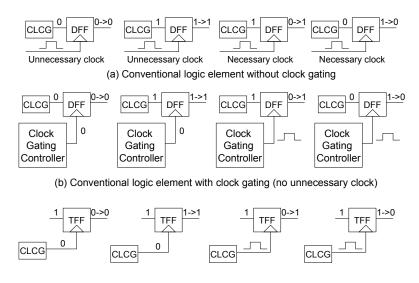

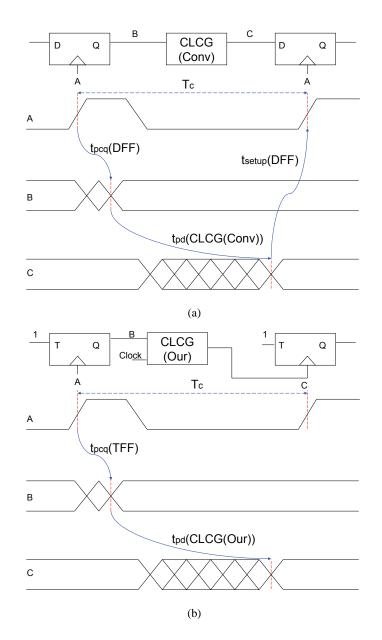

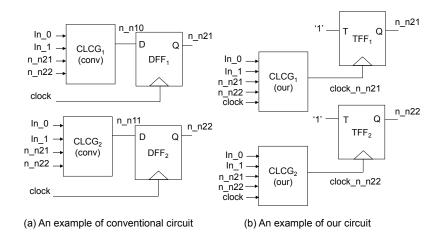

In [50], Lu et al. introduced their 1D reuse and partial reuse (RPR). The algorithm reuses already placed tasks to reduce reconfiguration time. As a result, the RPR outperforms the 1D Stuffing.