# High Performance Data Traversal

# Cache Aware Computing with Space Filling Curve

by

# Sagar Dolas

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Tuesday August 22, 2017 at 10:00 am.

Student number: 4593065

Project duration: November 1, 2016 – August 22, 2017 Thesis committee: Prof. dr. ir. K. Vuik, Supervisor, TU Delft

Prof. dr. ir. H. X. Lin Professor, Mathematical Physics, TU Delft

Dr. Matthias Möller, Supervisor, TU Delft Dr. Vahid Galavi, Supervisor, Deltares

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## **Preface**

Firstly, I would like to thank my thesis supervisor Dr Matthias Möller for his guidance, support, patience and advice. I would like to express my gratitude towards him for providing me the freedom to work on my concepts and help me channelise my ideas into appropriate direction. I also want to thank Dr Vahid Galavi for his guidance and the numerous fruitful discussions. Without the support of above two people, this thesis would not have been possible. I would like to thank Prof. dr. Kees Vuik for providing me the COSSE room, organising couple of COSSE workshops and all the necessary discussions. I would like to thank TU Delft and Deltares for providing me the resources to complete by master's thesis. Lastly, I would also like to extend my regards to everyone I met over the past two years in Europe.

Special acknowledgement go to the European Commission and the COSSE Consortium for providing me opportunities to travel and partially fund my master's studies in Germany and The Netherlands. Without their kind support, I did not stand a chance to leave my country and pursue higher education in Europe. Above all, I would like to express my sincere gratitude to my family in India and friends Ayesha and Sweta for their kind love and persistent belief. The moral support and love that I received from them made this journey comfortable, motivating and worthwhile.

Sagar Dolas Delft, August 2017

# Contents

| 1 | Intro              | oductio |                                                                               | 1  |

|---|--------------------|---------|-------------------------------------------------------------------------------|----|

|   | 1.1                |         | ition                                                                         |    |

|   |                    |         | rch Focus                                                                     |    |

|   | 1.3                |         | rch Objectives                                                                |    |

|   | 1.4                | _       | ht Process                                                                    |    |

|   | 1.5                | Thesis  | Outline                                                                       | 4  |

| 2 | Mod                |         | PU Architectures                                                              | 7  |

|   | 2.1                |         | uction                                                                        |    |

|   | 2.2                |         | Processor Architecture                                                        |    |

|   |                    | 2.2.1   |                                                                               |    |

|   |                    |         | Memory Management                                                             |    |

|   | 2.3                |         | core Socket Architecture                                                      |    |

|   |                    |         | Challenges for Performance on Multi-core Machines                             |    |

|   |                    |         | NUMA Architecture                                                             |    |

|   |                    | 2.3.3   | Performance Issues on NUMA Architecture                                       | 15 |

| 3 | Ana                |         | Performance Impact of Data Access on NUMA machine                             | 17 |

|   | 3.1                |         | uction                                                                        |    |

|   | 3.2                |         | ystem Specifications                                                          |    |

|   | 3.3                |         | mance Analysis                                                                |    |

|   |                    | 3.3.1   |                                                                               |    |

|   |                    | 3.3.2   | Modified Stream Benchmark                                                     |    |

|   |                    | 3.3.3   | Analyzing Memory Bound Kernel on ccNUMA machine                               |    |

|   |                    | 3.3.4   | Analyzing Compute Bound Kernel on ccNUMA machine.                             | 22 |

|   |                    | 3.3.5   | Analyzing Effect of Indirect Random Access on Memory Bandwidth Limited Kernel | 23 |

|   |                    | 3.3.6   | Analyzing Effect of Indirect Random Access on Compute Bound Kernel            |    |

|   | 3.4                |         | usion                                                                         |    |

|   |                    |         |                                                                               |    |

| 4 | <b>An</b> I<br>4.1 |         | ction to Space Filling Curves uction                                          | 31 |

|   | 4.1                | 4.1.1   |                                                                               |    |

|   |                    |         | Space Filling Curves in Use                                                   |    |

|   |                    |         | Space Filling Curve Construction for Arbitrary Mesh                           |    |

|   | 4.2                |         | opment of Parallel C++ Code for Space Filling Curves                          |    |

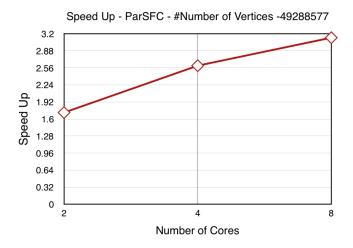

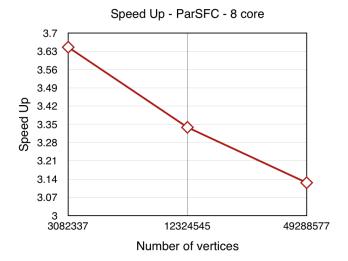

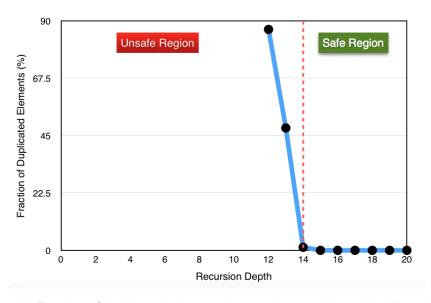

|   |                    |         | Parallel Performance Analysis of ParSFC application                           |    |

|   |                    | 4.2.2   | Relative Error                                                                |    |

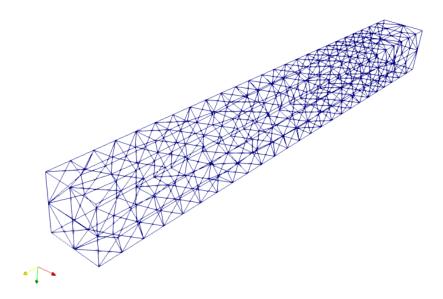

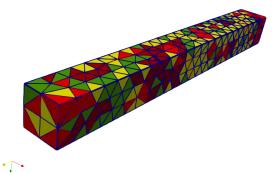

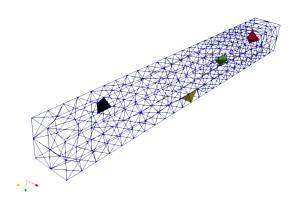

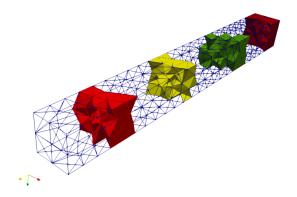

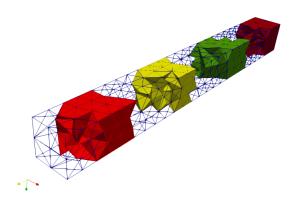

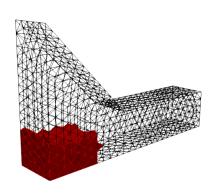

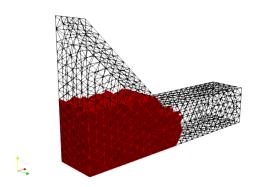

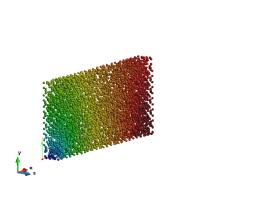

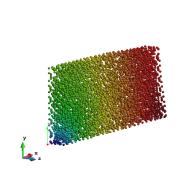

|   | 4.3                | Visuali | izing Data traversal with Space Filling Curves                                | 41 |

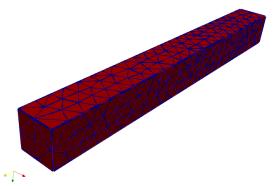

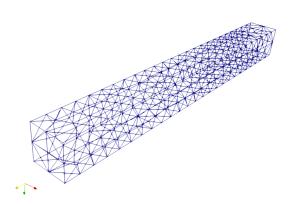

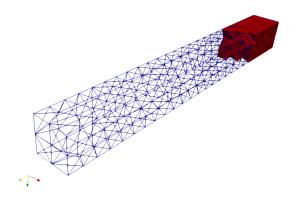

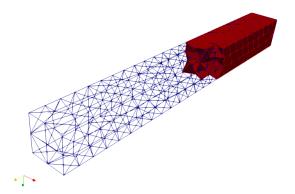

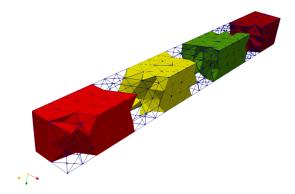

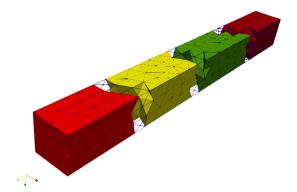

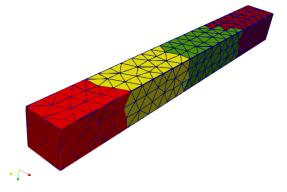

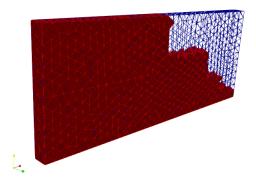

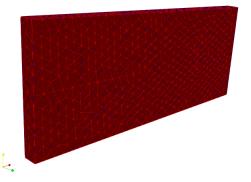

|   |                    |         | Test Case and Details                                                         |    |

|   |                    | 4.3.2   | Analysis of Serial Data Traversal                                             | 42 |

|   |                    | 4.3.3   | Analysis of Parallel Data Traversal                                           | 45 |

| 5 | Δna                | lysis w | rith Space Filling Curve on Finite Element Solver                             | 49 |

| • | 5.1                | -       | uction                                                                        |    |

|   |                    |         | The Governing Equation                                                        |    |

|   |                    |         | Review on various solvers with Space Filling Curve                            | 52 |

vi

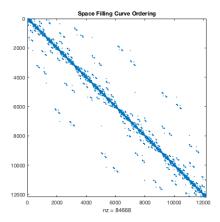

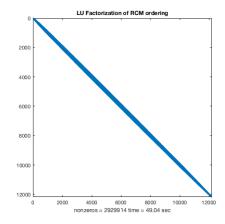

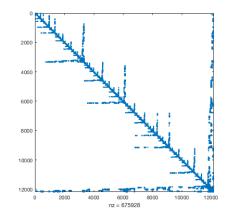

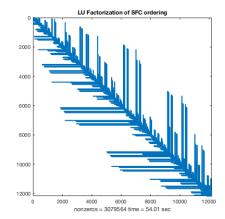

|     | 5.2<br>5.3<br>5.4<br>5.5 | Introduction to Finite Element Solver Performance Analysis and Methodology Interpreting Analysis 5.4.1 Interpreting Analysis on Matrix Assembly 5.4.2 Interpreting Impact on Inverse Power Iteration Matrix Structure Analysis 6.5.1 Impact on Matrix Bandwidth 6.5.2 Performance Impact on LU Factorization Conclusion 6.6                                                                                                               |

|-----|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

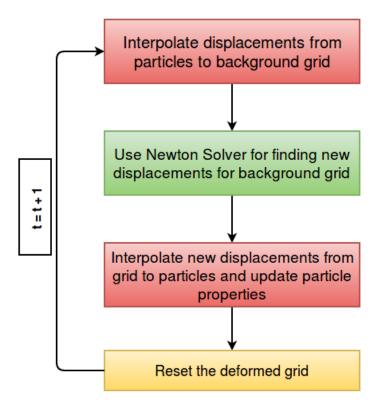

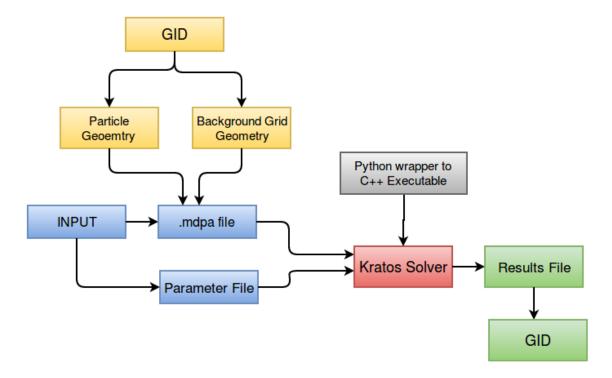

|     | 6.1                      | Introduction to the Material Point Method         6           Introduction         6           Governing Equations         6           6.2.1 Reynold's Transport Theorm         6           6.2.2 Conservation of Mass         6           6.2.3 Conservation of Linear Momentum         6           6.2.4 Boundary Conditions         6           6.2.5 Weak Formulation         7           Material Point Method Formulation         7 |

|     |                          | 6.3.1 Material Point Method Discretization                                                                                                                                                                                                                                                                                                                                                                                                |

| 7   | Chal                     | 6.3.2 Lagrangian Phase and Eulerian Phase                                                                                                                                                                                                                                                                                                                                                                                                 |

| •   | 7.1                      |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 7.2                      | Focus of Study                                                                                                                                                                                                                                                                                                                                                                                                                            |

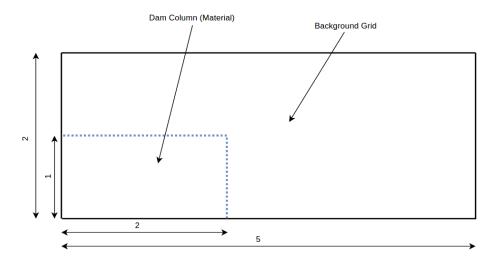

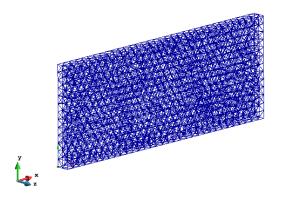

| 8   | Perf                     | formance Analysis of Explicit MPM 3D Simulation 79                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 8.1                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                              |

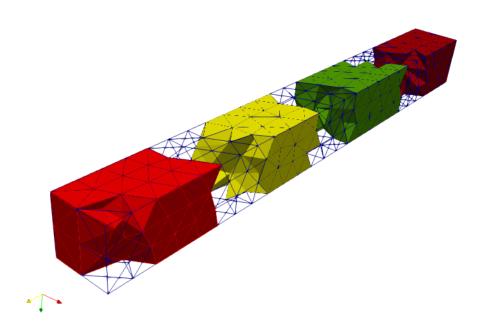

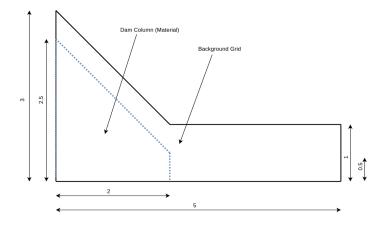

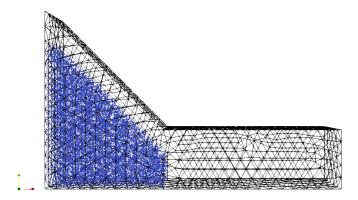

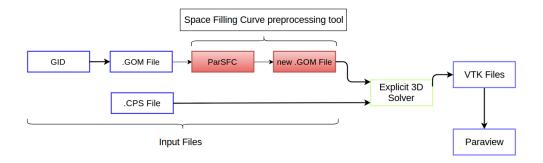

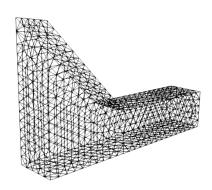

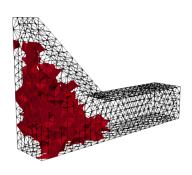

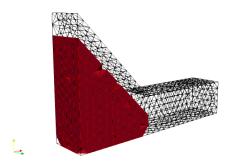

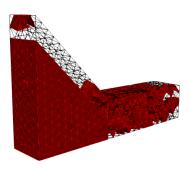

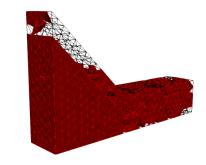

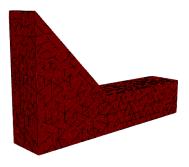

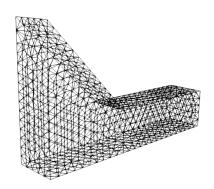

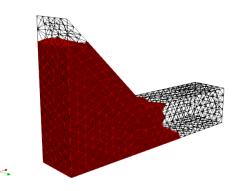

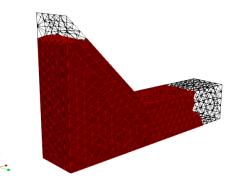

|     | 8.3                      | 8.2.1 Test Case Geometry, Boundary Condition and Simulation Parameters                                                                                                                                                                                                                                                                                                                                                                    |

| 9   | Anal                     | lysis of Implicit MPM 3D Simulation 9°                                                                                                                                                                                                                                                                                                                                                                                                    |

| -   | 9.1                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 9.3                      | 9.2.1 Test Case Geometry, Boundary Condition and Simulation Parameters                                                                                                                                                                                                                                                                                                                                                                    |

| 10  | 10.1<br>10.2             | nmary, Conclusions and Future Work Summary                                                                                                                                                                                                                                                                                                                                                                                                |

| Rik | aliog                    | raphy 10                                                                                                                                                                                                                                                                                                                                                                                                                                  |

1

## Introduction

"What Mathematics is to Physics, Data traversal is to High-performance computing"

#### 1.1. Motivation

The world of Computational science has witnessed an exponential expansion of complex numerical algorithms in the last few decades mainly to understand minute details and solve complex physical problems. It has established itself as the third pillar of science after theory and experimentation and has been successful in gaining immense popularity as a mainstream research work among academicians and scientists working in entirely different fields. The Computational Sciences has brought together Mathematicians and Computer Scientists to work in close collaboration on the variety of interdisciplinary research problems.

The need for developing large scale numerical and scientific codes for the simulation real world problems has taken the steep curve and so the current hardware industry. The Top500 <sup>1</sup> list ranks world's most powerful supercomputer capable of delivering 125 PFlop/s. To effectively understand this mammoth computational power, imagine 7 billion people on this planet continuously performing an add operation for ≈450000 years to match computational intensity which Sunway TaihuLight <sup>2</sup> shown in Figure 1.1 delivers in one second. Still, it is impossible to fully simulate the functional behaviour of the human brain or accurately predict decades of climate change. The pivotal point here is, expensive hardware or massive computational infrastructure does not naturally invoke high-performance computing but implementation of hardware auxiliary mathematical ideas, cache efficient data traversal strategies, sensible use of parallel programming paradigms and energy aware management of computational resources on machines ranging from very grass-root level basic NUMA system to entire million core server stack does.

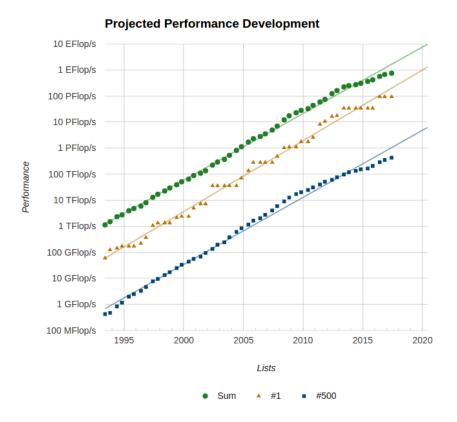

As the world's fastest supercomputer today stands at the horizon of PetaScale computing and looks ahead for Exascale floating point performance as clearly projected in Figure <sup>1</sup> 1.2, there has been a tremendous rush in the last decade to develop high performance and scalable scientific software mainly to exploit the enormous computational intensity of supercomputers judiciously. The foremost challenge to achieve high performance for computational researchers in near about every front is to optimise developed serial codes and achieve parallel scalability on thousands and millions of processing cores. The central theme to the above-mentioned problem is data traversal, data placement and memory access pattern which largely influences floating point performance and energy efficiency.

As highlighted earlier, an expensive machine is not an assurance for good performance. Careful investigation of underlying hardware and understanding ways to extract maximal

<sup>1</sup>https://www.top500.org

<sup>2</sup>http://www.nsccwx.cn

2 1. Introduction

performance are indispensable keys to achieving better computational throughput. Advance development of the numerical method and its analysis definitely ensures a numerically accurate solution to underlying mathematical physics, but competent software implementation and development is absolutely essential to solve real world problems. Deep understanding of elemental micro-architecture, effort to grasp behaviour of multi-core multi socket high-end server machines, reducing communication overhead and reducing energy consumption will play an important role in designing and implementing scalable numerical algorithms.

In this master's thesis we will first focus on investigating the impact of data traversal patterns on the performance of several micro-benchmarks on NUMA machine. In the second part we will implement an advanced data traversal scheme designed to improve cache utilisation for two numerical methods and analyse performance impact.

Figure 1.1: World's fastest supercomputer

#### 1.2. Research Focus

The Data traversal is the soul of high-performance computing. Indeed it is the backbone, the way data travels to the CPU from main memory largely influences the performance of particular kernel on specific machine architecture. The majority of modern machines are designed to deliver high performance if data traversal can utilize maximum bandwidth to main memory (DRAM) and make efficient use of hierarchical memory structure. Thus, a hardware optimal data access pattern should be designed to take advantage of the underlying hardware to scale and achieve performance and that forms the central theme of this work.

In this master's thesis, the focus will be on implementing strategy for efficient data arrangement and data reuse. This thesis work will try to explore challenges of achieving high performance in advance numerical methods by delving deep into their required memory access pattern.

CPUs processing power and memory access speed to DRAM have taken different curves over past few decades and it appears to widen in near future. In today's HPC scenario, most of the scientific kernels are poorly addressing their memory requirements and therefore there is dire need to include mechanisms which help to mollify it and reduce the load on memory controllers. In this thesis, there is an attempt to implement a recipe for improved data access pattern and explore it on matrix assembly and linear system solver for Finite Element code,

Figure 1.2: Projected performance development of world's 500 fastest supercomputers

and overall performance analysis of two different Material Point Method codes.

### 1.3. Research Objectives

This section highlights the research direction of the Master's thesis and precisely layouts the research objectives discretely.

#### **Objectives**

- 1. To understand the theoretical background of high-performance computing on modern CPU architectures and it's evolution in time.

- 2. To understand general performance bottlenecks of computational kernels in terms of limited hardware resources and programming paradigms.

- 3. To investigate and compare performance impact of data traversal schemes on simple modified stream benchmarks with respect to floating point performance and memory bandwidth.

- 4. To understand the mathematics behind numerical techniques such as finite element method, material point method and explore challenges in these methods to achieve high floating point performance.

- 5. To understand and choose advanced data traversal algorithms which may act as a unifying approach towards superior domain decomposition, generating cache oblivious data layout for NUMA machines, and comes packed with minimal computational overhead.

- 6. To investigate and compare performance improvements in scientific codes working with above mentioned numerical methods with the inclusion of new data traversal scheme.

4 1. Introduction

#### 1.4. Thought Process

This master's thesis starts with the theoretical understanding of high-performance computing by closely examining the changes in modern micro-architecture and multi-core multi-socket server machines. The first set of the investigation aims at understanding the available memory bandwidth and computational power of a typical dual socket server machine. Data traversal and memory access pattern are very basic yet important aspects of any scientific kernel and play an important role in achieving good performance specifically on modern machines where fetching data from DRAM can be up to  $\approx 2-3x$  more expensive compared to on-chip cache and up to  $\approx 5x$  from other NUMA nodes. A modified stream benchmark for NUMA machine was implemented as is used to study importance of data traversal and data placement on bandwidth utilization and computational power.

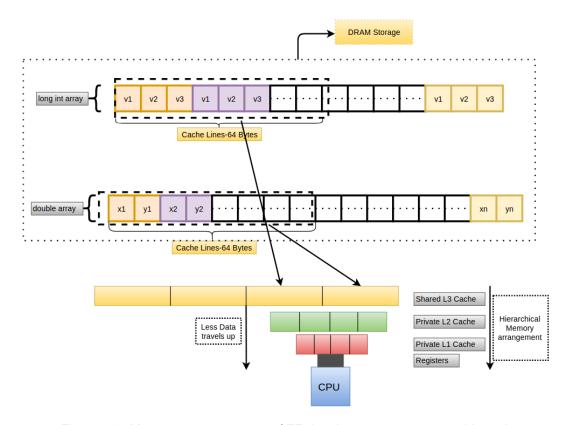

The FEM is widely used approach for approximate solution of PDE problems. As the name suggests, Finite element codes mainly involve global matrix assembly and solution of system of equations both for linear and nonlinear problems either with direct or iterative solvers. The elemental wise traversal of the underlying grid for sparse matrix assembly typically involves indirect random access to vertices and elements which invoke lots of cache misses, redundant bus cycles and therefore constrains it to utilize maximum available bandwidth offered by the machine. The HPC machines are converging towards more cores/socket, larger memory bandwidth to DRAM and increased bandwidth between CPUs and therefore the main aim of this work is to understand the evolution of modern machines and evolve scientific kernels towards it to achieve high performance. The technique which brings together temporal and spatial locality, generating cache oblivious data layout and makes use of larger bandwidth offered by the machine should be inculcated.

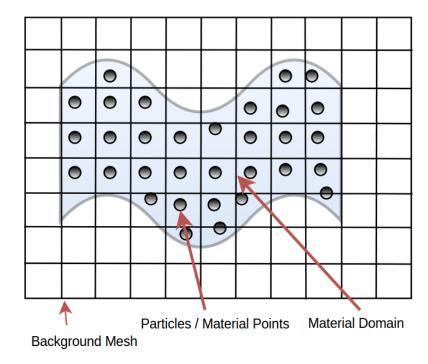

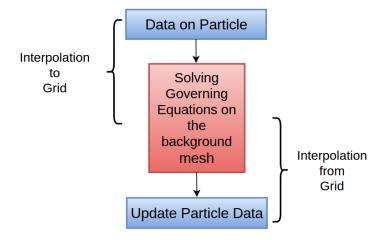

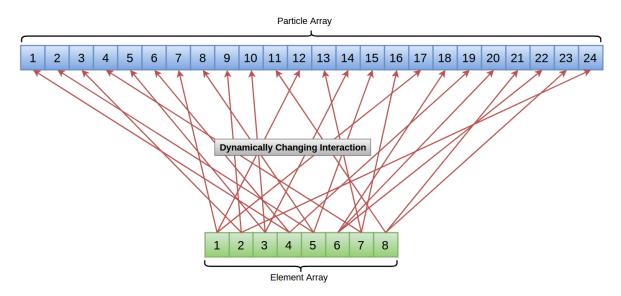

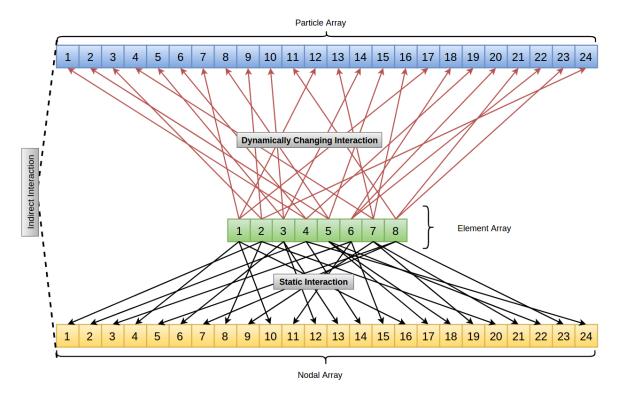

Going a step further, this thesis also explores the Material Point Method which combines the FEM with discrete particles. The particles move freely within the underlying grid in each computational cycle. Each computational step involves matrix assembly similar to finite elements and this unique interaction of particles with grid naturally invokes a lot of unstructured random access which inhibits this type of particular numerical scheme to achieve high performance even on bandwidth oriented machine. There exists, a special class of data traversal, mathematical curves called Space-filling curves which are originally fractal curves. One of the most important properties of Space Filling Curves is their ability to generate data layouts which can be distributed across multiple processors in distributed memory environments with minimal communication and also across multiple cores in shared memory environment with very low synchronization points.

#### 1.5. Thesis Outline

This section provides a brief introduction to the content of each chapter and guides the reader through the rest of this document.

Chapter 2 **Modern CPU architecture** highlights relevant bottlenecks in performance of single-core and multi-core CPUs and NUMA machine. It discusses critical components of modern processors and highlights the important functionality of memory module. It also describes performance related issues in NUMA architectures and reviews some key solution-strategies to improve computational throughput.

Chapter 3 **Analysing Performance Impact of Data Access on NUMA Machine** takes a deep dive into performance aspects of data access patterns on compute-bound and memory-bound kernels with respect to operational memory bandwidth utilisation. It also studies the impact of data traversal patterns on energy consumption and summarizes key strategies to be adopted while programming on NUMA machines for high bandwidth utilisation.

Chapter 4 An Introduction to Space Filling Curves introduces Space Filling Curves

1.5. Thesis Outline 5

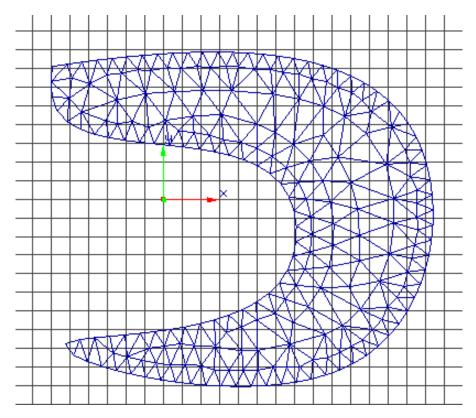

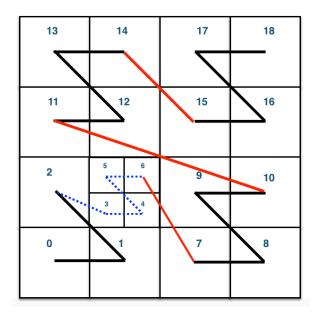

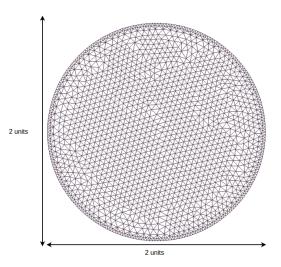

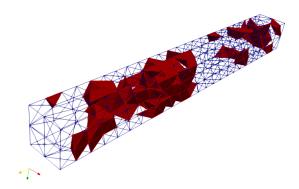

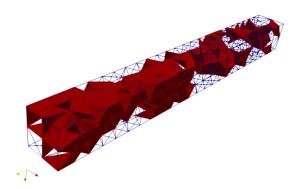

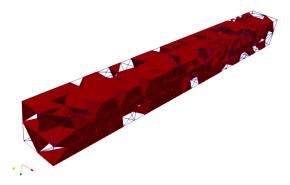

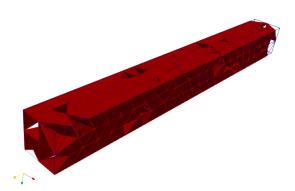

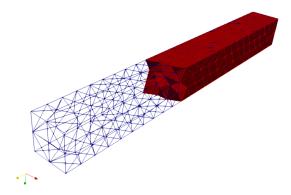

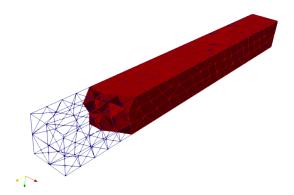

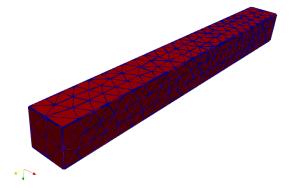

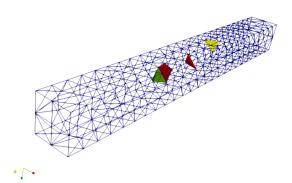

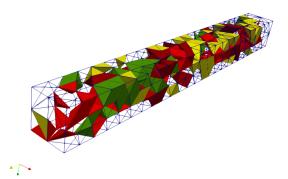

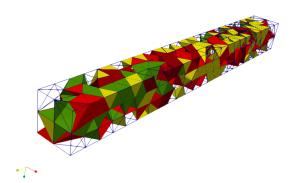

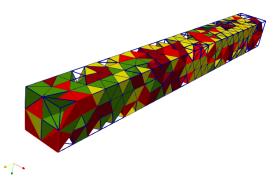

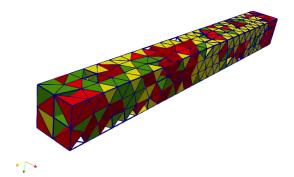

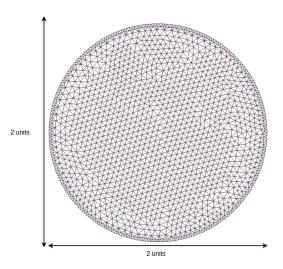

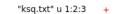

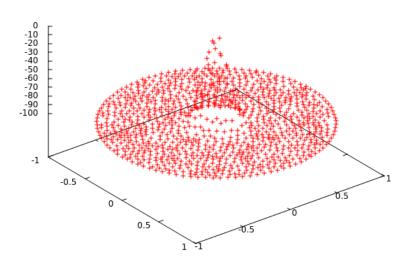

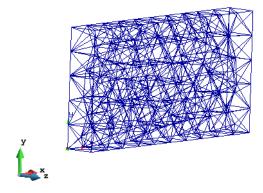

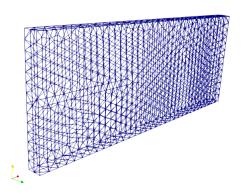

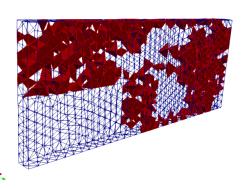

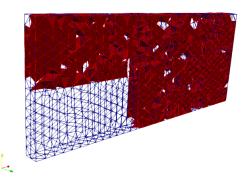

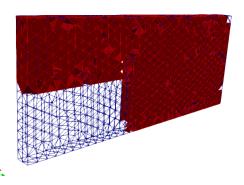

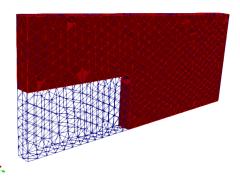

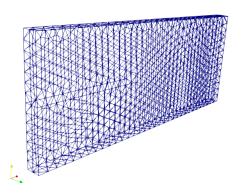

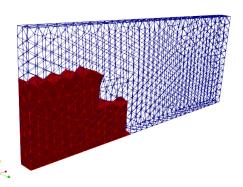

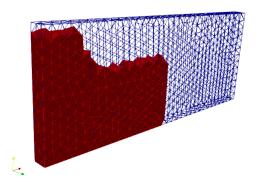

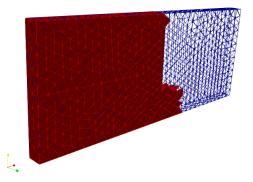

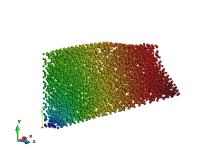

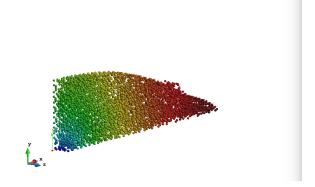

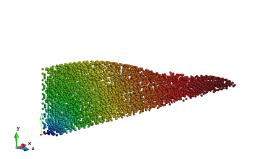

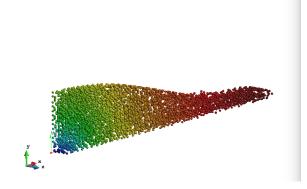

(SFC) and presents them as a versatile and efficient mesh reordering scheme. It provides mathematical basis to the idea of locality and explains SFC generation for arbitrary two or three-dimensional grid in detail. It provides a brief overview of the **ParSFC** application used for generating SFC and presents the three-dimensional visualizations of data traversal on arbitrary Finite Element grid to properly grasp and understand the potential impact of data access patterns on computational performance.

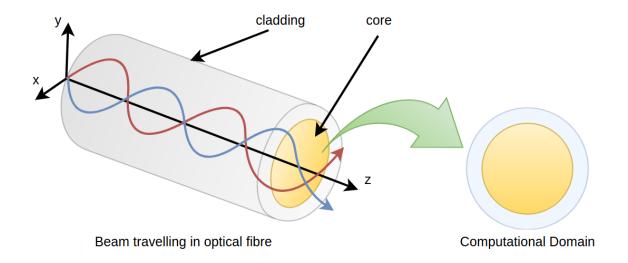

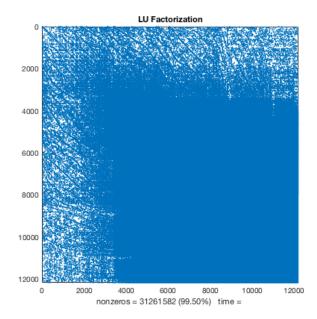

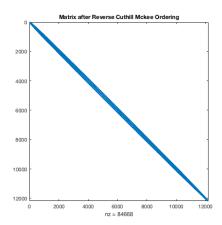

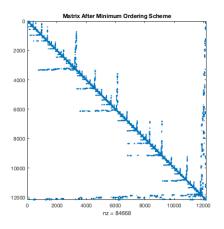

Chapter 5 **Analysis of Space Filling Curve on Finite Element Solver** introduces an eigenvalue problem of beam propagation in optical waveguide governed by Helmholtz equation. It establishes Finite Element discretization and simultaneous system of linear equation to solve for lowest eigenvalue and associated eigenvector. This chapter contains deep performance analysis of matrix assembly, sparse matrix-vector multiplication on the grounds of CPU time, energy efficiency, cache utilization and effective use of memory module. This analysis helps to redraw performance expectation of Space Filling Curve as a data traversal algorithm. This chapter also analyses matrix structure with respect to different industrial strength reordering schemes and compares their performance impact on LU factorization.

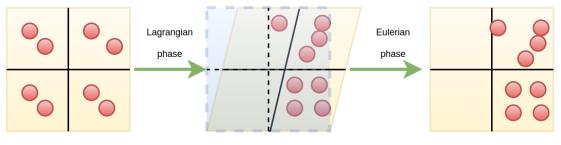

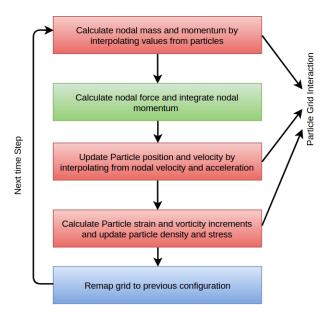

Chapter 6 **The Material Point Method** introduces the numerical method, the Material Point Method (MPM). It explains the mathematical physics behind MPM and outlines both the Lagrangian step and the Eulerian step.

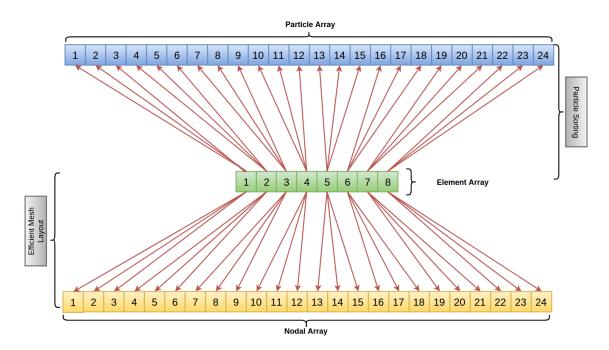

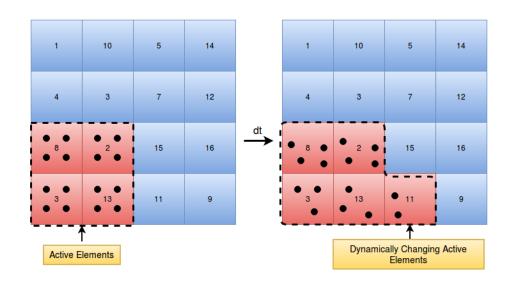

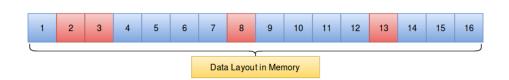

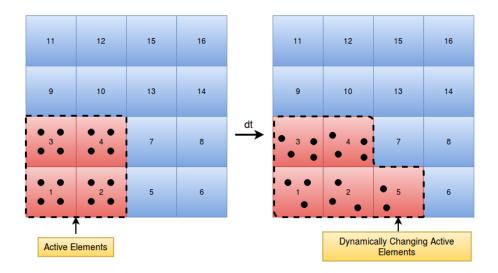

Chapter 7 **Challenges for Achieving High Performance for the Material Point Method** explores the source of bad memory access pattern in the particle-grid interaction. It explains the importance of coalesced memory access pattern for improving cache utilisation and how grid reordering can help to achieve it. It establishes the focus of study for following chapters and unleashes hidden computational challenge especially in the case of the Material Point Method, where the set of active elements changes frequently dynamically changing initial particle-grid interaction.

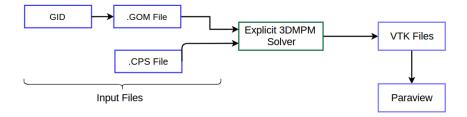

Chapter 8 **Analysis on Explicit MPM 3D Solver** first explains explicit MPM algorithm in detail and then describes a test case for experimentation. It also highlights the important features of Anura3D code developed by Deltares which is used here for analysis. The main focus of this chapter is to understand the effect of reordering of the elements and vertices of the background grid on the overall computational performance of the MPM code.

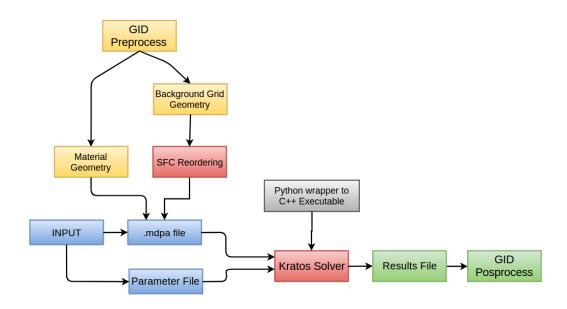

Chapter 9 **Analysis on Implicit MPM 3D Solver** first explains implicit MPM algorithm in detail and then describes a test case for experimentation. It explores the open source MPM code Kratos-Particle-Mechanics and describes its important components. The main focus of this chapter is to grasp performance impact of mesh reordering of the background grid on implicit MPM solver.

## Modern CPU Architectures

#### 2.1. Introduction

This chapter contains explanations of modern single and multi-core CPU architectures, discusses trends and optimisation strategies to be employed for achieving high performance on these kinds of machines. The most important point for high performance computing is applying techniques to reduce wastage of memory bandwidth and this chapter will pay plenty of attention to it. Some of the essential ideas and facts in this chapter have been taken from the book "Introduction to High-Performance Computing" by Victor Eijkhout [6]. The reader should refer to chapter 1-5 for more detailed explanations and ideas.

#### 2.2. Single Processor Architecture

This section focuses on minute details of single-core architecture and in particular on the movement of data between main memory and the processor and within different levels of memory in the processor. Understanding memory access and its productive usage is essential for efficient scientific computing since data movement from main memory to the processing core is an order of magnitude slower than processor's computing power in today's modern CPUs.

Highly efficient codes require an understanding of microprocessor architectures and therefore it is important and sometimes crucial to know the architecture before implementing the raw algorithm. For many problems of academic and industrial interest, the use of the parallel computer is a necessity, but before that, a proper understanding of single core and its capabilities is a must. In modern scientific computing, one of the biggest challenges is to provide data hungry processor with data efficiently, and this chapter will pay attention to that.

#### 2.2.1. Modern Processor

Modern processors are quite complicated and this section will give very concise introduction to important and pertinent parts of modern processor. The *Von Neumann* <sup>1</sup> architecture models sequential instruction handling. Modern processor supports *out of order* instruction handling that is, instructions can be handled differently than specified by the program only when reordering the instruction leaves the results of the execution unchanged. More detailed understanding of instruction handling can be found in Intel Architectures Optimization Reference Manual <sup>2</sup>. Some of the important features and trends in instruction handling are summarised as follows:=

<sup>1</sup>https://en.wikipedia.org/wiki/Von Neumann architecture

<sup>2</sup> https://www.intel.com/content/dam/www/public/us/en/documents/manuals/64-ia-32-architectures-optimization-manuals/pdf

- 1. **Multiple issue**: In Modern CPUs, instructions that are independent of each other can be executed in parallel.

- 2. Branch prediction and speculative execution: Today's compilers can guess whether a conditional instruction will evaluate to true and act accordingly. The purpose of branch predictor is to improve instruction pipeline, and they play a very critical role in achieving high performance for today's x86 based microprocessors. The branch predictor attempts to avoid waste of time by guessing whether conditional jump will be taken or not. The branch that is guessed will be speculatively executed. Otherwise, instructions are disregarded and pipeline starts over again with the correct branch. For example, to improve branch prediction, Intel's Sandy Bridge microprocessor was redesigned to have Branch Target Buffer (BTB) double memory than its predecessor Nehalem micro-architecture to store more data to guess next steps, therefore, allowing CPU to load more instructions beforehand leading to improved CPU performance.

- 3. Out of order execution: Instructions can be reordered if they are not dependent on each other. The processor executes instructions in an order governed by availability of input data. In this way the processor can avoid being idle while waiting for the preceding instruction to complete to retrieve data for the next instruction in a program, instead processes the next instructions that are able to run immediately and independently. Consider the in-ordered instruction for following assembly code:

- (a) ld r1, r2 (load from r1 from memory into r2)

- (b) add r2, r1, r3 (r1 = r2 + r3)

- (c) add r4, r5, r3 (r4 = r5 + r3)

Suppose, r3 and r5 are available but r2 has to be brought in from Level 2 cache which takes around 20 clock cycles. Until then pipeline is stalled, however second instruction is ready and can be executed. The out-of-instruction handling executes second instruction before first in order to avoid idle time.

4. Prefetching: Data prefetching fetches request data before it is needed to take advantage of fast caches. Instruction prefetching attempts to load instructions before they are executed to improve performance. Microprocessors based on Intel's Nehalem, Westmere, Sandy Bridge, Ivy Bridge, Haswell, and Broadwell support four types of hardware prefetchers for prefetching data. There are two prefetchers associated each with Level 1 and Level 2 cache which can prefetch up to 128 bytes of cache lines.

#### **Fused Multiply Add**

In scientific computing, floating point computation holds top most priority, and for this reason, cores have dedicated execution units for treating arithmetic operations. For example, Intel's Sandy Bridge micro-architecture features 15 execution units as compared to 12 execution units in its predecessor Nehalem micro-architecture. The arithmetic operations differ in a number of clock cycles required to execute them which determines computational performance.

For example, in modern CPU, a division operation can take up to 10 or 20 clock cycles limiting the performance of a numerical algorithm while multiple addition or multiplication execution units can asymptotically calculate the same result per cycle. The phenomenon of executing instruction  $x \leftarrow ax + b$  in the same amount of time as separate addition or multiplication is called *Fused Multiply Add* also called as FMA. FMA can achieve an asymptotic speed of several floating point operations per clock cycles so therefore effort should be made to convert expensive operation like the division into equivalent multiplication or addition operation.

#### **Instruction Pipelining**

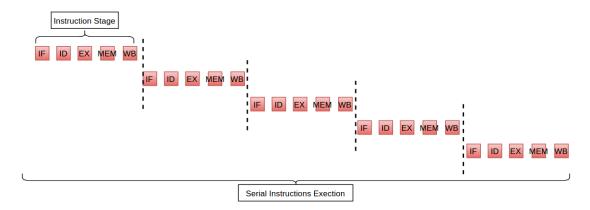

Figure 2.1 shows a typical sequence of serial pipelined arithmetic operations consisting of IF,ID,EX, MEM and WB stages. The computational throughput is 1 complete independent operation per 5 clocks cycles.

Figure 2.1: Schematic illustrations of serial pipelined operations, IF- Instruction Fetch, ID - Instruction Decode, EX- Execution, MEM- Memory Access, WB - Write back

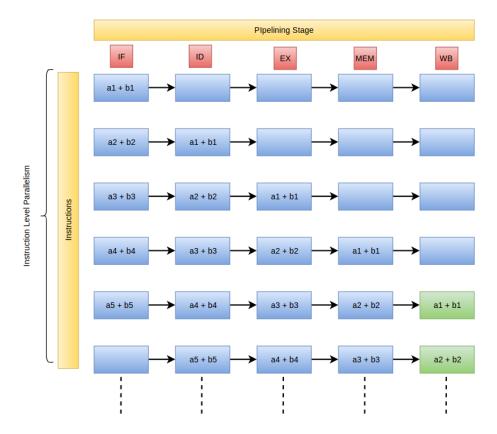

The modern processor features instruction level parallelism schematically shown in Figure 2.2. The asymptotic computational throughput is one independent operation per clock cycle which is a speed up of 4-6 compared to non-pipelined CPU. The first Intel's Pentium processor had five pipeline stages which were increased to 31 in Pentium-4 processor and again decreased to 14 in Core i3, i5, i7 whereas, the new Intel's Nehalem and Sandy Bridge microprocessor configuration features 19-25 pipelining stages. The crucial point here is, higher pipeline staged does not guarantee higher performance because entire pipeline may have to be flushed repeatedly imposing adverse effects.

#### 2.2.2. Memory Management

This section will mainly discuss essential ideas about memory management especially from hardware perspective and about how data travels from main memory to CPU core. This section will also point out challenges in achieving high performance specially on bandwidth limited kernels and techniques to overcome them.

#### **Bus Structure**

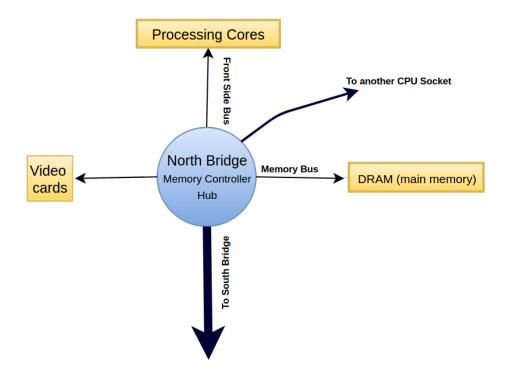

The bus structure is mainly responsible for moving data around the computer especially from main memory (DRAM) and CPU. The most important part is *Front Side Bus (FSB)* which connects processor to the main memory through memory controller hub as shown in Figure 2.3. The northbridge or fast connect typically handles communication among CPU sockets, from cores to main memory (DRAM), cores to video cards. However, Intel's Sandy Bridge processor configuration introduces full integration of northbridge functionality onto CPU chip decreasing overall size as shown in Figure 2.7.

Bus speed is typically much lower than the CPU frequency and therefore the rate at which the CPU can process data is much faster than the rate which data can be delivered to it. The introduction of fast and fat caches has alternatively solved this problem to some extent but has invoked other challenges which will be discussed later. Bus speed can not be increased indefinitely, but the number of bus channels can be increased ultimately increasing the volume of data to CPU.

For example, Intel's 5600 Nehalem series processor configuration featured support for maximum 3 memory channels, but on the other hand its successor Intel's 2600 Sandy Bridge series processor configuration features support for 4 memory channels increasing maximum

Figure 2.2: Schematic illustrations of parallel pipelined operations, IF- Instruction Fetch, ID - Instruction Decode, EX- Execution, MEM- Memory Access, WB - Write back

operational memory bandwidth by 33 %. This example suggests that trend in processor configuration is moving towards more operational bandwidth and therefore trying to solve the problem of low memory speed by supplying more data. However, increasing the number of memory channels will not help to achieve high performance if data access patterns does not adhere to the underlying hardware layout. In the next sections we will investigate this problem from hardware and programmer's perspective.

#### Caches

Caches are low-latency high-bandwidth memory where data can reside for a moderate amount of time. Data from the main memory travels through the caches up to the registers and CPU core. The principal advantage of cache memory is data reusability. If data is reused shortly after it was first needed, it will still be in the cache, and therefore can be accessed much faster than if it would have to be brought in again from the main memory.

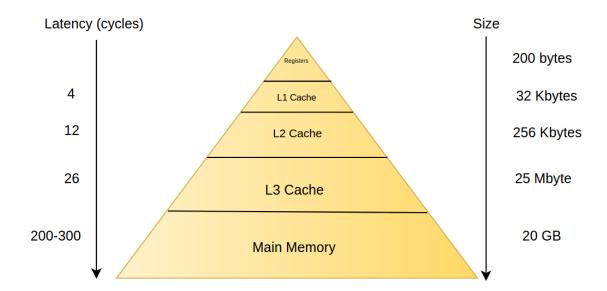

Figure 2.4 shows schematic layout of the cache hierarchy for Intel's Sandy Bridge processor configuration. Loading data from register is so fast that, it virtually involves no latency at all and therefore does not contribute to any limitations whatsoever. The different level of caches are called *Level 1* (L1) and *Level 2* (L2) and nowadays modern processors also have *Level 3* (L3) cache. The L1 and L2 cache are private and on chip memory whereas in most recent processor configurations L3 is off-chip. The L1 cache is small, typically around 16Kbytes to 32Kbytes but it is much faster and sustains a bandwidth of 32 bytes per cycle. The L2 cache is bigger around hundreds of Kbytes and roughly 8 times bigger than L1 cache and has 3 times more latency as compared to L1 cache. L3 is typically around Mbytes approximately 10 times bigger than L2 cache and sustains 2x latency shared among multiple cores.

Data needed in some operations gets copied into various levels of caches up to the main

Figure 2.3: Schematic diagram of memory-bus structure

processor, if some instructions later, a data item is needed again, it is first searched in L1 cache, if it is not found there it is searched in L2 cache and if it also not found there it is searched in L3 cache or the main memory. Main memory access has a latency of more than 200 cycles and bandwidth of 4.5 Bytes per cycle, which is about 1/7th of the L1 bandwidth. However this is again shared by multiple cores of a processor chip effectively reducing the operational bandwidth. There are three types of cache misses as summarized below.

- 1. **Compulsory miss**: This occurs during first time reference to data, and is unavoidable.

- 2. **Capacity miss**: This type of cache misses is due to the size of the working set and is caused by data having been overwritten because the cache simply cannot contain all data. This type of cache miss can be avoided by partitioning data into chunks that are small enough to easily stay in cache for sufficient amount of time providing spatial and temporal locality upon repetitive memory access.

- 3. **Conflict miss**: This type of cache miss occurs when one data gets mapped to the same cache address as another data, while both are still needed for computation.

The typical time required to retrieve data if not found in cache is as follows:

1. L1 Cache: 1-2 Clock cycles

2. L2 Cache: 5-20 Clock Cycles

3. L3 Cache: 50 - 100 Clock cycles

4. Main memory: 300 - 500 Clock Cycles

In this master's thesis, the focus is on avoiding capacity cache misses by travelling or accessing data in an efficient way.

Figure 2.4: Schematic diagram of cache hierarchy

#### **Data Movement between Main Memory and Processor**

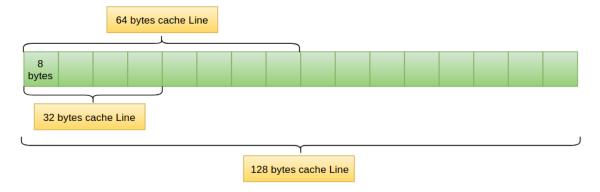

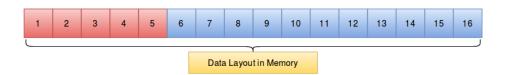

Data movement between memory and cache, or between caches is not done in single bytes, or even words. Instead, the smallest unit of data moves is called a cache line, sometimes referred as cache block. A typical cache line size can be 32 or 64 or 128 bytes which in context of scientific computing implies 4 or 8 or 16 double-precision floating-point numbers. It is important to understand the importance of cache line, since any memory access costs the transfer of several words. An efficient program then tries to use the other items in the cache line, since access to them is effectively free. This phenomenon is visible in codes that access arrays by unit stride. This is also one of the key-points of the next chapter. Typical description of cache line is illustrated in Figure 2.5.

Figure 2.5: Schematic illustration of cache line

#### 2.3. Multi-core Socket Architecture

Over the decade, multicore architectures have surfaced and now dominate most of the commodity hardware industry. The main reasons for this development are as follows :=

- 1. Clock frequency can not be increased further due to two main reasons, firstly: Energy consumption have increased drastically leading to dissipation of more heat generation and secondly: To increase computational power, more transistors have to be assembled in small amount of chip area, but transistors gate have reached their fundamental limits of few atomic layers restricting to further narrow down size thus ultimately restraining the number of transistors on chip.

- 2. It is not possible to extract more Instruction Level Parallelism (ILP) from codes due to compiler limitations.

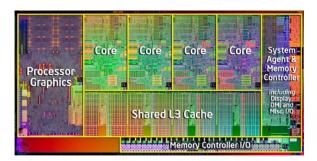

One of the ways to further increase the computational power is to move from traditional single-core architecture to multi-core chips because two cores of lower frequency can have the same asymptotic computational throughput as a single core at a higher frequency: hence reduction in energy consumption. A typical multicore chip is shown in Figure 2.6 <sup>3</sup>

Figure 2.6: A typical multi-core chip

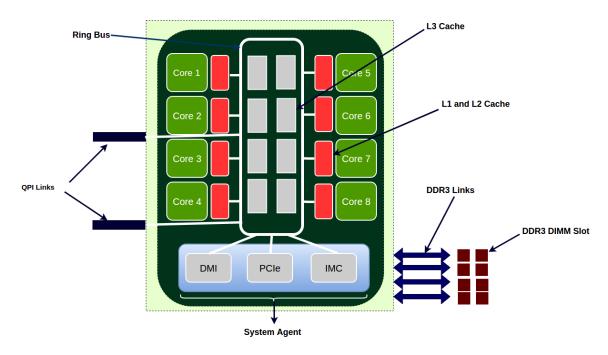

In this section, a brief introduction to Intel's Xeon E5-2600 multi-core processor series is presented along with relevant minute details to understand a classic multi-core multi-socket processor configuration. Figure 2.7 shows a typical Intel Xeon E5 2600 series processor configuration having 8 processing cores. Each processing core has private L1 and L2 cache and shared L3 cache with each core its share of L3 bucket represented in grey colour in Figure 2.7. Cores are connected to each other via bidirectional ring bus architecture which provides high scalability and low latency bandwidth to L3 cache.

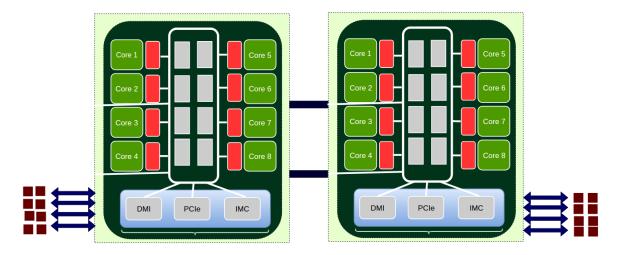

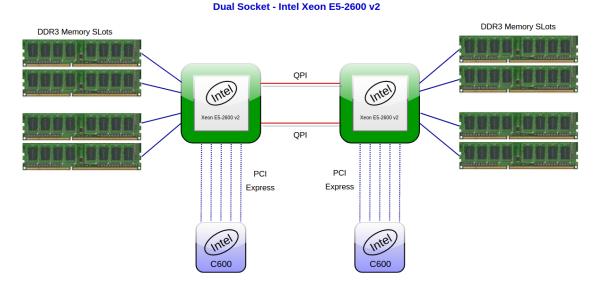

These processors support up to 4 memory channels per CPU socket and up to 3 DIMM slots per channel with a maximum of 32 GB memory per DIMM slot cumulating to 768 GB of RAM at most. All memory channel supports up to maximum memory speed of 1600 MHz which amounts to the maximum bandwidth of ≈102.4 GB/s. The Quick Path Interconnect (QPI) offers 8 GHz/link high bandwidth connection between CPUs as shown in Figure 2.8. In today's scenario, the focus of hardware development has shifted towards enlarged bandwidth-oriented architectures especially to mitigate the gap between memory speed and processor's computing power. On one hand, multi-core machines are moving towards increased memory bandwidth and more cores/ CPU-sockets so, on the other hand, complicated programming challenges have emerged making it difficult to efficiently utilise these machines. In the next section, there will be a brief discussion about some of the important challenges to consider while programming for high performance.

<sup>3</sup> https://www.cnet.com/news/what-became-of-multi-core-programming-problems/

Figure 2.7: Intel Xeon E5-2600 series processor configuration

Figure 2.8: Intel Xeon E5-2600 series dual-processor server

#### 2.3.1. Challenges for Performance on Multi-core Machines

This section will concisely explain very basic yet one of the most important performance issues in multi-core machines.

#### **Cache Coherency and False Sharing**

In multi-core machines, there is a huge potential for conflict if several processing cores have the same copy of data in their cache. *Cache coherence* is the problem of ensuring that all cached data are an exact copy of main memory. For example two cores have a copy of the same data in their private L1 cache, and one modifies its copy. Now the other core has cached data which is no longer valid or has inaccurate copy of the counterpart: the processor will invalidate the copy of the item, and in fact the whole cacheline and therefore this process of updating or invalidating cachelines is known as maintaining *cache coherency*. This phenomenon will waste bandwidth, which otherwise could have been used for load or store instructions.

The cache coherence problem can even occur if the core accesses different items, but they fall on the same cacheline and this problem is specifically known as *False Sharing*. The most common case of false sharing occurs when processing cores update consecutive locations of an array. The continuous update of cacheline by multiple cores has a huge impact on performance and therefore should be avoided.

#### 2.3.2. NUMA Architecture

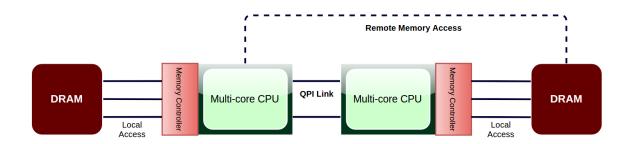

This section briefly explains Non Uniform Memory Access (NUMA) architecture and highlights challenges associated with it to achieve high performance. Figure 2.8 shows an actual Intel Xeon E5-2600 dual-CPU server NUMA machine and Figure 2.9 schematically shows typical working of NUMA machine. The name NUMA suggests that memory access time for a certain set of CPUs is different from another set of CPUs. NUMA machines have been derived from their counterpart UMA machines where memory access time is the same for all CPUs. The main limitation of UMA architecture is low bandwidth scalability due to congestion of memory controllers upon increasing number of CPUs on one chip.

Figure 2.9: NUMA architecture

NUMA moves away from a centralized pool of memory and introduces topological properties. The NUMA architecture allows bandwidth scalability by first separating cores on different chips and then adding multiple independent memory controllers allowing each CPU to have their own memory address space thus reducing the load on a single memory controller and scaling bandwidth. The Concept of local and remote memory is depicted in Figure 2.9. Remote memory access has additional latency overhead as compared to local memory, as it has to traverse an interconnect and connect to the remote memory controller.

#### 2.3.3. Performance Issues on NUMA Architecture

Optimizing codes on NUMA machines is not easy and involves delicate and careful treatment of cores and memory subsystems. This section will highlight some of the key issues for

sub-optimal performance and plausible solutions for improving code performance on NUMA systems. Memory allocation in NUMA typically demands more attention and knowledge of operating system's memory placement policies. Special attention has to be given to applications that span over multiple NUMA nodes for optimal code performance.

#### **Remote Memory Access**

Remote memory access is one of the main reason for sub-optimal performance. Table 2.1 shows the penalty caused by remote memory access on Intel's Xeon E5-2600 processor according to NUMA distance. It is clear from table 2.1 that remote memory access is twice is expensive as local memory access.

Table 2.1: Remote memory access penalty factor

| Numa Node | 0  | 1  |

|-----------|----|----|

| 0         | 1x | 2x |

| 1         | 2x | 1x |

Remote memory access also occurs, if memory allocated by the master thread on one node is accessed from worker threads on another node.

#### **Thread Migration**

Modern operating systems assign application threads to processor cores using schedulers. A given thread will execute on an associated core for some period before being swapped out by OS scheduler as other threads are given a chance to execute. Thread migration from one core to another poses a problem for NUMA architectures because it can disassociate a thread from its local memory pool causing remote memory access and the significant increase in total computational time. The complexity of thread increases upon increasing number of CPU sockets.

#### **Solution - Data Placement and Thread Pinning**

Thread pinning and data placement are key components in achieving good performance on NUMA architecture. Thread pinning or processor's affinity is the endurance of particular thread with a set of resource instance despite the availability of other instances. Exercising processor affinity or thread pinning avoids thread migration to another CPU socket and back memory allocations local to processing cores. Data placement is another important aspect of high-performance scientific computing. The more often that data can effectively be placed in memory local to the processing core, the more overall access time will be benefited. Thread pinning and data locality are somewhat related to each other. By forcing thread pinning or processor affinity, local data allocation can be ensured.

Thread pinning and local data placement are just enzymes to the path towards high-performance computing. The real challenge is to design data traversal patterns which match the design of underlying hardware. Data traversal patterns decide usage of memory subsystems, therefore, controlling code performance in these architectures. The next chapter will focus on analysing performance impact of data traversal on simple experimental modified stream benchmarks.

# Analyzing Performance Impact of Data Access on NUMA machine

#### 3.1. Introduction

Application performance is largely governed by the arithmetic intensity and the memory access pattern of the computational kernel. The gap between CPU's processing power and memory speed is a major roadblock to achieving high performance for bandwidth limited kernels. The primary resource limitation is the memory controller and the L3 cache which rapidly gets saturated and inhibits high performance. The multicore architecture features complex cache coherent mechanism which may have the severe performance impact and therefore it is important to develop strategies to exploit all levels of memory subsystem up to the highest level of cache efficiently for good performance. This chapter focuses on performance bottlenecks and strategies to reduce the overall computational time and the energy consumption of simple kernels on high-end cache coherent NUMA machines, unveil valuable insights into serial and parallel behaviour and summarise strategies that can be adopted for high bandwidth utilisation and high floating point performance.

STREAM <sup>1</sup> is a popular and well established memory bandwidth benchmark, but it lacks NUMA aware support which makes it useless for analysis on cache coherent NUMA machine. Therefore a modified stream benchmark has been developed for an in depth analysis and experimentation on wide range of performance parameters.

### 3.2. Test System Specifications

This section gives a very concise introduction to the state of art x86 server HP Z280. The HP machine supports Intel Xeon E5 2687w v2 processor architecture shown in Figure 3.1. The HPC system based on Intel's Xeon E5 2600 product family provides 80 % improvement in performance and 50 % improvement in power efficiency compared to its previous generation Intel Xeon 5600 series.

#### **Processor Micro-architecture**

The Intel Xeon E5 2600 family supports Sandy Bridge EP microarchitecture which is an evolution of Nehalem EP microarchitecture. Each processing core has dedicated 32KB of L1 data cache, 256KB of L2 cache and shared L3 cache. The Sandy Bridge microarchitecture also introduces Intel Advanced Vector Instructions(AVX), a 256-bit instruction set to Intel SSE which can support up to 16 single-precision or 8 double-precision floating-point operations per cycle. Sandy Bridge microarchitecture also supports Running Average Power Limit (RAPL) interface to power measurements and analysis. The RAPL exposes performance

<sup>1</sup> http://www.cs.virginia.edu/stream/ref.html

| Processor Family                      | Intel Xeon E5 2600 v2 |

|---------------------------------------|-----------------------|

| Micro-processor Architecture          | Sandy Bridge EP       |

| Cores                                 | 8                     |

| Processor Frequency                   | 3.1 GHz               |

| L3 Cache                              | 20 MB                 |

| DRAM                                  | 16 GB                 |

| DDR3(1600 Mhz) Memory Channel(Active) | 2                     |

| Max Memory Bandwidth                  | 25.1 GB/s             |

| NUMA Penalty                          | 2x                    |

Table 3.1: Test-system specifications

counters to measure the energy consumed by CPU cores and the memory module.

The Intel Xeon E5 product family also improves high bandwidth and scalable interconnect ring bus liking cores, last level cache, PCIe and Integrated Memory Controllers. The shared L3 cache of 20 MB per CPU socket is divided into slices of 2.5 MB per core although each core can address the entire L3 cache which increases its overall bandwidth to L3 cache. The latency to the L3 cache is significantly reduced from 36 cycles in the previous generation to 26-31 cycles. Ring architecture for L3 cache brings high bandwidth and scalability which is very crucial for bandwidth limited kernels. The current processor has a maximum support of 4 memory channels out of which only two are active in the test system provided by Deltares, each comprising of 8 GB 1600 MHz DDR3 DIMM slot providing a total bandwidth of 25.1 GB/s per CPU socket to 16 GB of DRAM per CPU and the 2 Quick Path Interconnect (QPI) links between two processors provide overall bandwidth of 32 GB/s. Table 3.1 shows the technical specification of one CPU socket.

Figure 3.1: Dual-socket Intel Xeon E5 2600 v2 series architecture

There has been a lot of improvements and evolution over time on this machine in terms of bigger and faster cache, more cores/socket, and increased memory bandwidth. Since we are converging towards increasing parallelism within a processor and more bandwidth to DRAM, the majority of scientific kernels should be adapted to take that advantage. This chapter and coming sections will try to peek into the machine and understand performance optimizations on simple modified stream benchmarks.

#### 3.3. Performance Analysis

#### **Categories of Computational Kernels** Memory Compute **Bound** Bound Kernel Kernel Random Random Access Access Memory Compute **Bound** Bound Kernel Kernel

Figure 3.2: Categories of computational kernels

This section will explore performance bottlenecks in terms of limited hardware resources and CPU's processing power by studying four different computational kernels as summarized in Figure 3.2. The whole analysis provides the complete picture of strategies to be adopted for achieving maximum bandwidth utilization and maximum floating-point operation. This section will also provide a brief introduction to software tools used for profiling, debugging and performance measurements.

#### 3.3.1. Softwares and External Libraries Used

#### **Perf**

Perf <sup>2</sup> tool is used for measuring performance counters under linux OS. Performanc counters in CPU are hardware registers that keep track of instructions executed, cache-misses suffered and branches miss-predicts. In this chapter, the Perf tool is used to measure energy consumption depending on different data access pattern. The Intel processor of the test system features Running Average Power Limit (RAPL) Model Specific Registers [5] which collects energy consumed by CPU-core and memory module in multiple of 15.3 µJ.

#### Numactl

The numactl <sup>3</sup> tool is used to bind specific threads to a set of processing cores and memory region to optimize data locality, avoid thread migration and avoid unnecessary OS scheduling. Memory locality or affinity is very important for high performance in NUMA machines, where remote memory access can be quite expensive compared to local memory access. The commands used for pinning threads to cores and allocating memory locally or remotely are summarised at web page of *IBM Knowledge Center* <sup>4</sup>

#### 3.3.2. Modified Stream Benchmark

The modified stream benchmark <sup>5</sup> is developed in C++ and parallelized with OpenMP for the purpose of testing and experimenting the above explained dual socket server machine. The NUMA-aware memory allocation by the first touch principle ensures that data is allocated local to processing cores, pinning of threads is enforced to fully avoid thread migration and hyper-threading is turned off to achieve performance. This stream benchmark is used to understand the behaviour of computational kernels under different data traversal schemes.

<sup>2</sup>https://perf.wiki.kernel.org/index.php/Main\_Page

<sup>3</sup>https://linux.die.net/man/8/numactl

https://www.ibm.com/support/knowledgecenter/en/linuxonibm/liaai.hpctune/cpuandmemorybinding. htm

<sup>&</sup>lt;sup>5</sup>https://github.com/computingdolas/Stream Benchnmark

#### **Compilation and Execution**

The following code kernels are compiled with gcc version 5.4.0 and with std=c++11 -O3 - fopenmp flags.

#### 3.3.3. Analyzing Memory Bound Kernel on ccNUMA machine

The parallel ADD operation shown in Kernel-1 involves very little computation and is bandwidth limited.

```

for (int i = 0 ; i < K_times ; ++i){

// Parallel Region

#pragma omp parallel shared(a,b,c,N) num_threads(<numthreads>)

{

double wtime = omp_get_wtime() ;

#pragma omp for schedule(static)

for (uint64_t k = 0 ; k < N ; ++k){

// ADD Operation

a[k] = b[k] + c[k] ;

}

wtime = omp_get_wtime() - wtime ;

#pragma omp master

global_time += wtime ;

}</pre>

```

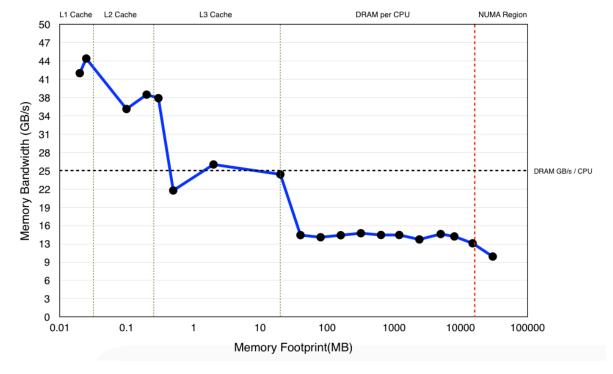

Figure 3.3: Analysis of memory-bound Kernel-1 on Single Core

The aim of this particular analysis is to clearly capture serial and parallel performance of bandwidth-limited Kernel-1 on the dual socket server machine as shown in Figure 3.3 and 3.4. Figure 3.3 shows single-core performance of Kernel-1 for entire memory footprint. It is clear that on-chip memory offers  $\approx 3x-4x$  increase in bandwidth which steadily decreases

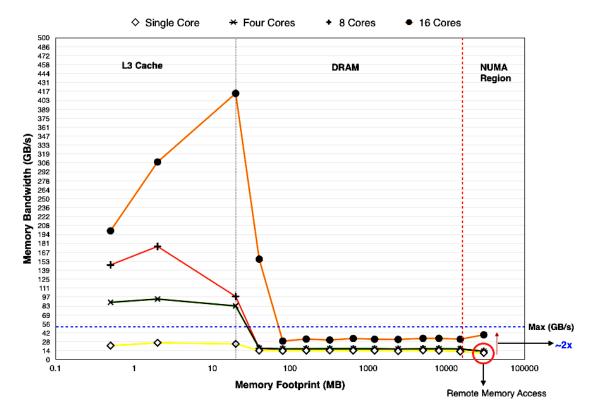

Figure 3.4: Parallel performance analysis of memory-bound Kernel-1 on 16 cores

until data is accessed from main memory (DRAM). The analysis also shows that maximum bandwidth achieved by Kernel-1 is  $\approx 16$  GB/s which is 65% of theoretical maximum. The crucial point here is that on-chip memory offers low latency and higher bandwidth compared to main memory (DRAM) and therefore programming effort should be invested to align data as close as possible to processing cores

On the other hand, the bandwidth limited kernels do not gain speed-up or scale by increasing the number of active cores especially when accessing data from main memory (DRAM) as shown in Figure 3.4, since it depends on memory access pattern, memory types (DDR3 1600), and number of active DIMM slots/ channels all of which combined determine theoretical maximum. In Figure 3.4 the perfect linear scaling in bandwidth is observed upon increasing core count from 1 to 16 until data is accessed from L3 cache because each core has private 32 KB of L1 data cache and 256 KB of L2 cache and 20MB L3 cache logically shared and physically separated for one CPU which enhances the core's ability to access the data independently thus scaling the bandwidth. As the processing cores start to access data from DRAM, there is a sudden drop in bandwidth, which is limited by the maximum theoretical bandwidth of 25.1 GB/s per CPU socket. In Figure 3.4 the maximum bandwidth achieved by Kernel-1 is 19 GB/s which is ≈75 % of theoretical peak.

The Figure 3.3 shows a sudden drop in bandwidth upon accessing memory in NUMA region because of the fact that, on the current machine remote memory access is twice as expensive as local memory access and on the other hand orange line in Figure 3.4 represents 16 cores operating on Kernel-1. There is ≈2x increase in bandwidth to 40 GB/s due to two more operational memory channels from another CPU. This is one of the major advantages of NUMA machines, the memory bandwidth to DRAM scales linearly if the number of CPU socket is increased. This analysis concludes that even though remote memory access can be quite expensive, NUMA nodes if operated independently can scale bandwidth linearly.

#### 3.3.4. Analyzing Compute Bound Kernel on ccNUMA machine

The ADD operation shown in Kernel-2 involves expensive sin() and cos() operation and therefore is compute bound.

```

for (int i = 0 ; i < K_times ; ++i){

// Parallel Region

#pragma omp parallel shared(a,b,c,N) num_threads(1)

{

double wtime = omp_get_wtime() ;

#pragma omp for schedule(static)

for (uint64_t k = 0 ; k < N ; ++k){

// ADD Operation

a[k] = sin([k]) + sin(c[k]) ;

}

wtime = omp_get_wtime() - wtime ;

#pragma omp master

global_time += wtime ;

}</pre>

```

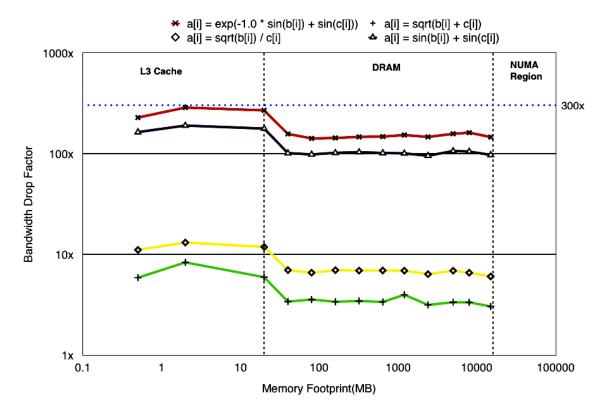

Figure 3.5 shows bandwidth drop factor due to various combinations of compute bound kernels. It is clear from the analysis shown in Figure 3.5 that data is stalled for the maximum of  $\approx 300x$  compared to add operation in Kernel-1, drastically reducing its potential to utilize maximum operational bandwidth and thus leading to an increase in overall computational time. This type of analysis gives the complete opposite picture of bandwidth limited kernel. The more the complexity, the more is the drop in bandwidth. The speed of memory now does not make a difference at least for unit stride access.

Figure 3.5: Single-core performance analysis of compute-bound Kernel-2

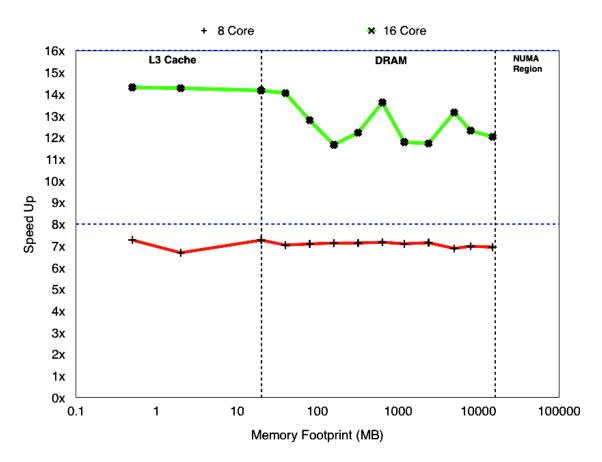

Figure 3.6 shows the parallel behavior and scalability of the compute-bound kernel with unit stride access on 8 and 16 cores respectively. The compute-bound kernel achieves the maximum speed of 7.3x with 8 active cores and  $\approx 14x$  on utilizing 16 cores of the test system. Comparing to the bandwidth-limited analysis shown in Figure 3.4, it is clear that although the compute bound kernel is extremely expensive due to memory stalls, it can become scalable on multiple cores easily. Data distribution and data placement are very important steps and by the virtue of NUMA aware data allocation, it is possible to maintain data locality which is the main thrust to achieve high performance

Figure 3.6: Speed-up of compute-bound Kernel-2 on 8 and 16 cores

## 3.3.5. Analyzing Effect of Indirect Random Access on Memory Bandwidth Limited Kernel

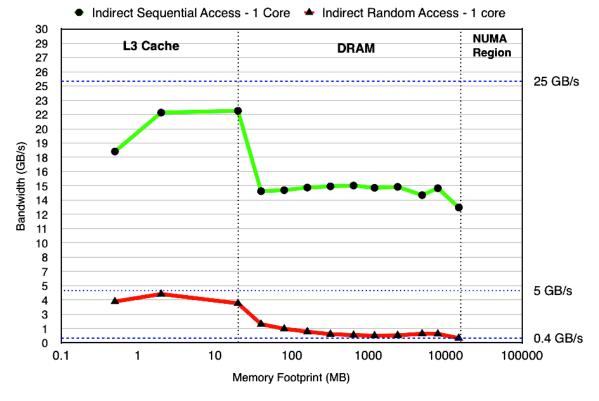

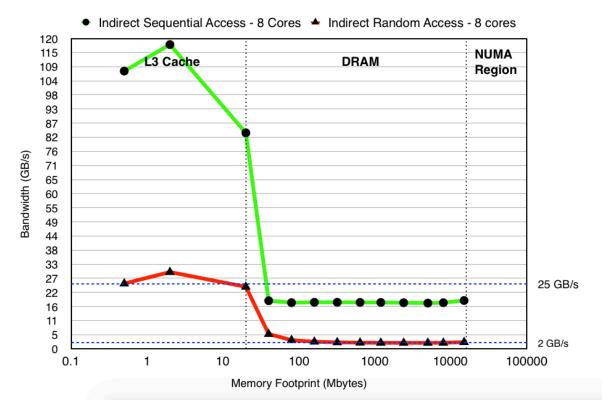

This analysis forms the central theme of the master thesis. Analyzing impact of random access on simple ADD kernel gives insight into drop in computational performance for both serial and parallel code. In Kernel-3 a **random[]** array is initialized and shuffled so as to have completely unpredictable behavior. Figures 3.7 and 3.8 depict the serial and parallel analysis respectively. From the serial analysis shown in Figure 3.7 one can see that, random access causes a drop in bandwidth to 0.4 GB/s from maximum of  $\approx$ 15 GB/s. Another compelling point to understand is that unit stride access maintains certain bandwidth drop across each memory levels, but random access drops non-linearly across memory access to DRAM.

Figure 3.8 shows parallel analysis of random access on 8 cores. There is a huge drop in bandwidth for in-core memory and a significant drop for memory accesses to DRAM. It is clearly visible that random access completely inhibits particular kernel to achieve operational maximum bandwidth and degrades performance. Bandwidth in Figure 3.8 is larger than in Figure 3.7, which is due to the fact that data is processed in parallel by processing cores.

Figure 3.7: Single-core performance analysis of random access on Kernel-3

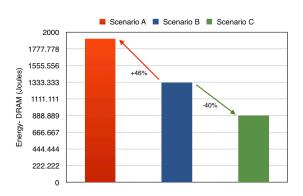

#### **Energy Studies on Bandwidth Limited Kernel**

Energy consumption is one of the major performance parameters which should also be studied because reduction in energy usage is as important as reduction in computational time.

Figure 3.8: Parallel performance analysis of random access on Kernel-3

This study will analyse the impact of random access on energy/cpu-core and energy/memory module and will peek into energy consumption on bandwidth limited Kernel-3 shown above by measuring hardware performance counters using perf tool.

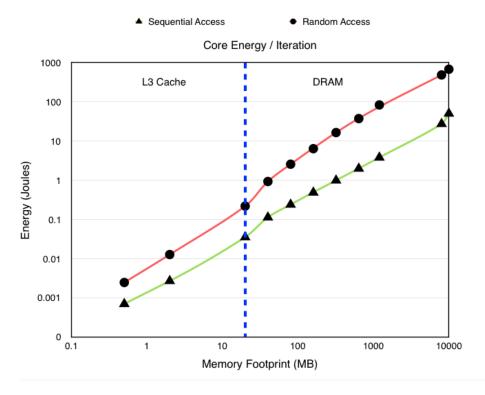

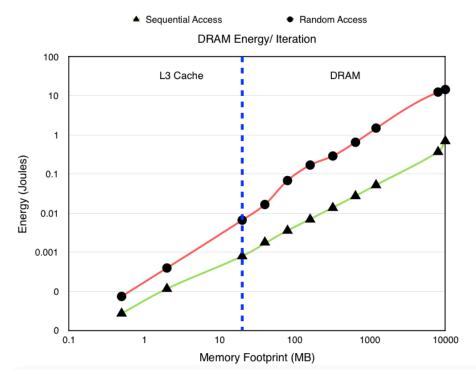

Figure 3.9 shows the impact of random access on energy consumed by a processing core per iteration. It is clearly visible that energy consumed by a core per iteration for random access is one order of magnitude higher than the sequential access. The energy consumption increases with increase in array size which is dictated by the memory footprint. The crucial point here is to understand that high-performance computing is not only about efficient usage of processing cores for reduction in computational time but also ensuring judicial consumption of energy. Random access has devastating effect on energy consumption and should be avoided for sustainability.

Figure 3.10 shows the impact of random access on energy consumption of memory module. It is very clear that the energy consumed by DRAM is not as large as consumed by a CPU core but it makes significant difference to overall energy consumption. It is certain that energy consumed by memory module is very low until data is accessed from L3 cache, but it increases exponential as soon as memory footprint crosses L3 cache. Also energy consumed by memory module upon random access is significantly higher due to non-linear increase in memory traffic. It is also one order of magnitude higher than the sequential access.

#### 3.3.6. Analyzing Effect of Indirect Random Access on Compute Bound Kernel

This section investigates the impact of random access on computational performance of compute bound kernel shown in Kernel-4.

Figure 3.9: Analysis of energy consumed per iteration by a CPU core on bandwidth limited Kernel-3

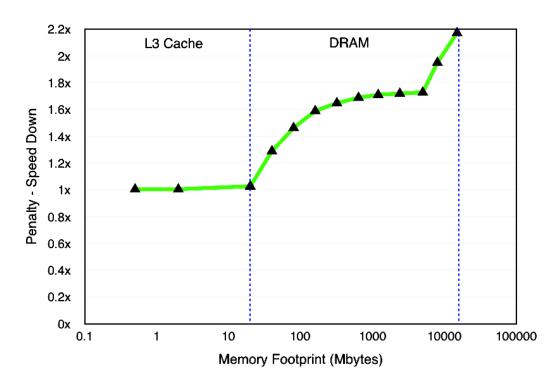

Figure 3.11 indicates that, there is a maximum drop of  $\approx 2.2x$  when the array length reaches maximum DRAM limit of 16 GB per CPU socket. There is no loss until data is accessed from L3 cache because of the simple fact that, the compute bound kernel takes much more time to process data and since L3 cache provides high bandwidth and low latency so data reaches as fast as possible to processing cores. As soon as array length starts crossing L3 cache limit there is visible speed drop increasing nonlinearly due to the fact that processing cores cannot find next set of data sets immediately and has to request data from DRAM which degrades its computational performance.

Figure 3.12 shows the parallel performance of random access in the compute bound ker-

Figure 3.10: Analysis of energy consumed per iteration by memory module on a bandwidth limited Kernel-3

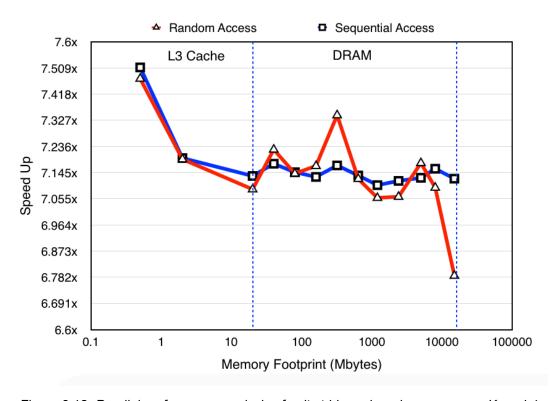

nel. It is surprising to see that, both random access and unit stride access appear to be scalable and achieve nearly same speed for every level of memory hierarchy. Well, there is no background literature as to why random access compute-bound kernels should achieve parallelism same as unit stride access, but there is a hidden reason of inefficient dedication of processing cores. Processors are twice as busy doing inefficient computation as clearly projected in Figure 3.11 while maintaining scalability due to the fact that Kernel-4 is so expensive that processing cores do not seem to worry about data arrival and departure but just processing it. This type performance analysis can be sometimes misleading in a sense that achieving parallelism is not certificate for high performance but there are numerous perspectives which should be looked in carefully for optimization.

Figure 3.11: Drop in speed due to random access in compute-bound Kernel-4

Figure 3.12: Parallel performance analysis of unit stride and random access on Kernel-4

3.4. Conclusion 29

#### 3.4. Conclusion

This chapter started with understanding technical specifications of the test hardware and assessing performance potential of simple kernels with regards to memory bandwidth utilisation, computational time and energy consumption. The main goal of this chapter was to observe theoretical basis of high-performance computing experimentally on particular machine architecture and establish the importance of data traversal by analysing the performance of simple stream benchmarks. This section will highlight key points of analysis of memory and compute bound kernels.

The performance of memory-bound kernel is limited by the rate at which data can be delivered to the processing cores or technically speaking it is bounded by the maximum bandwidth offered by the underlying hardware. So increasing the core count on one particular processor will certainly scale up the bandwidth linearly if data fits into the L3 cache but will not improve the DRAM access performance since shared resources of the memory subsystem get saturated very quickly. Therefore, increasing the number of CPUs or NUMA nodes will only be able to scale up the overall bandwidth used by the kernel, allowing memory controllers of different NUMA nodes to access data independently. The attempt should be made to utilize cache data as efficiently as possible because it offers low energy, low latency and high bandwidth access to the data.

This chapter also discussed performance impact of random access on bandwidth utilization and energy consumption. The conclusion is random access causes increase in DRAM traffic, therefore, leading to a huge drop in operational bandwidth utilization and a significant increase in energy consumption both for processing cores and memory modules. Programming effort should be invested in aligning or accessing data as per underlying hardware to maximize operational efficiency of cache hierarchy and memory subsystems.

This chapter also analyses compute bound kernels. Compute bound kernels are limited by the ability of the computing core to process data and is no longer controlled by the speed of the memory module. Compute bound kernels are scalable to a large extent since data processing takes much longer compared to its arrival and therefore individual cores can then process data seamlessly without waiting for it. Random access of data in compute bound kernel do not have a devastating effect on performance since a penalty due to cache miss or redundant memory reference to DRAM is comparatively much less time consuming than data processing itself. Therefore the conclusion is that performance impact of random access to data in compute bound kernel is not acutely visible but still plays an important factor in achieving high performance.

# An Introduction to Space Filling Curves

## 4.1. Introduction

This chapter introduces the concept of Space Filling Curves as versatile tool for efficient mesh data reordering algorithms for dynamic load balancing, mesh partitioning, domain decomposition and cache aware computing. The Space Filling Curves (SFC) have proven to be absolutely remarkable alternatives to travel spatial data structures and encourages energy efficient high-performance computing with the minimal amount of overhead involved.

There exists a vast number of algorithms for improving cache performance, performing domain decomposition, solving Molecular dynamics and N-body problems on distributed and shared memory computing architectures. Reordering algorithms like Reverse Cuthill-Mckee, Recursive Spectral Bisection or Multilevel Nested dissection are very robust and efficient in performing fast search for spatial data structures. However above-mentioned techniques require a large amount of investment in terms of programming and maintenance but none of them offer unifying approach towards domain decomposition and improvement in cache performance along with easy implementation and minimal computational cost [1].

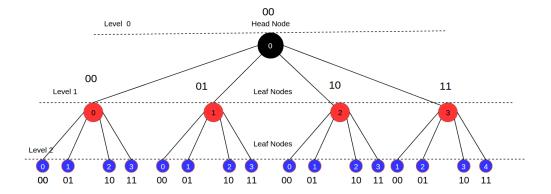

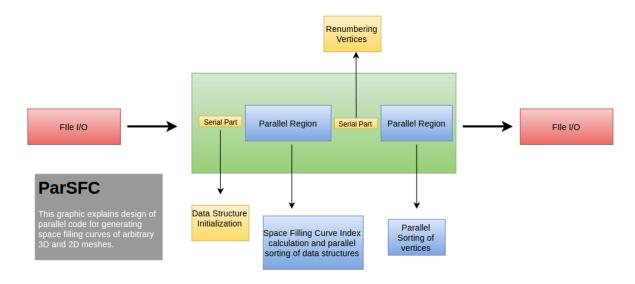

Space Filling Curves on the other hand, offer easy implementation and embarrassingly parallel construction of three-dimensional index in space. The construction of Space Filling Curve involves finding a unique index and sorting of data structures relative to that index. The asymptotic complexity of constructing the curve is therefore bounded by the sort algorithm which orders the mesh along the curve. This can be accomplished by using standard serial quick sort with O(NlogN) complexity.

Computational scientists have understood the importance of Space Filling Curves and these curves are already part of scalable scientific codes specifically for plasma simulations, fluid structure interaction, N-body problems and multi-physic Finite Element codes. Space Filling Curves apart from high-performance computing are also utilised for analysis in big data, graph analysis, geospatial analysis and communications. SFC have not been able to establish themselves as a cache friendly algorithms in the majority of high-performance scalable softwares. This section and later text will provide the comprehensive understanding of Morton-order Space Filling Curve and highlight its importance for cache aware high-performance computing on modern machines.

# 4.1.1. Mathematical Description

Mathematically speaking Space Filling Curves belong to family of fractal curves which recursively duplicate coarser design patterns on an infinite scale in any number of dimensions. They are mappings from a d dimensional space to 1-dimensional space [13].

$$c: (1 \cdots n)^d \to (1 \cdots n^d) \tag{4.1}$$

Space Filling Curves do not intersect themselves and therefore, a unique ordering of the points in d dimensional space is obtained. These curves strongly enjoy locality property which makes them good enough for high-performance computing in the wide range of topics in computational science and engineering. A mathematical description of 2D and 3D locality of Hilbert-order SFC is given in detail in [10]. For 2D Hilbert curve authors in [10] propose

$$|c(i) - c(j)| < \sqrt[2]{6(|i - j|)} \quad \forall \quad i, j \in \mathbb{N}$$

$$(4.2)$$

and for 3D order Hilbert curve as

$$|c(i) - c(j)| < \sqrt[3]{33.2(|i - j|)} \quad \forall \quad i, j \in \mathbb{N}$$

(4.3)

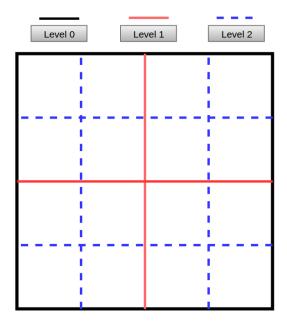

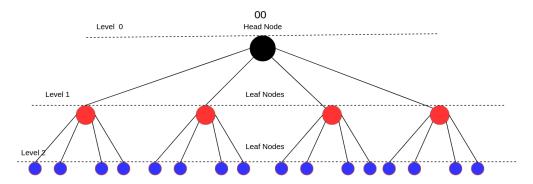

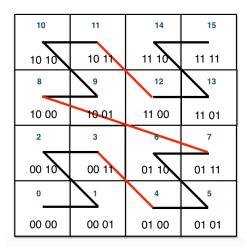

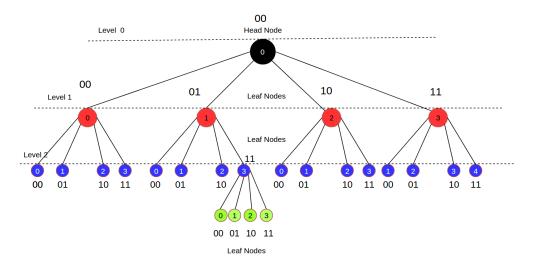

The origin of SFCs can be attributed to the development of Cantor sets  $^1$ . The Hilbert-order SFC or Morton order SFC for the square or cube can be generated by recursion. Space Filling Curves are not always generated explicitly, instead their mathematical description is used to calculate a spatial index associated with each entity. In d dimensions and p as the depth of recursion, the SFC provides an ordered enumeration of an imaginary bounding Cartesian grid having  $2^{dp}$  cubic cells in which the computational domain is fully embedded. Each cubic domain has unique SFC index and is duplicated on the entity which lies inside it. The algorithm used to generate SFC index for unstructured meshes is described in detail in Section 4.1.3.

# 4.1.2. Space Filling Curves in Use

#### **Dynamic Load Balancing and Efficient Domain Partitioning**

Load imbalance is one of the important roadblocks for scientific codes to become scalable on very large HPC systems. An efficient mesh partitioning becomes an essential component for scalable design of numerical applications. Space Filling Curves have been used for dynamic load balancing and efficient partitioning as documented in Campbell et al. [3] and Vo et al. [15].

On the other hand, there are many popular software such as ParMetis <sup>2</sup> which have been used to solve problem of dynamic load balancing, but SFCs as a better alternative is presented and argued in [9]. Authors observe that, SFCs provide memory efficient alternative and easy local implementation as opposed to techniques available in ParMetis which requires global knowledge of connectivity matrix. Authors have applied Space Filling Curves to balance dynamically changing workloads on static but unstructured mesh for an adaptable flow solver. Authors in [9] concluded that, ParMetis was not able to scale beyond 65,536 processors, in contrast to Space filling curves which scales well upto 294,912 processors with only 1- 2 % drop in quality of partitions as compared to ParMetis.

#### **Energy Aware Computing**

Energy aware computing is one of the most important research topics in today's high-performance computing systems and it is important thrust for economically operating HPC systems adding another yet challenge to run and maintain scalable codes on big HPC systems.