Delft University of Technology

## High-Power Digital Transmitters for Wireless Networks

Bootsman, R.J.

**DOI**

[10.4233/uuid:8baf679b-49d2-4799-8f2a-c2955943aade](https://doi.org/10.4233/uuid:8baf679b-49d2-4799-8f2a-c2955943aade)

**Publication date**

2025

**Document Version**

Final published version

**Citation (APA)**

Bootsman, R. J. (2025). *High-Power Digital Transmitters for Wireless Networks* (1 ed.). [Dissertation (TU Delft), Delft University of Technology]. <https://doi.org/10.4233/uuid:8baf679b-49d2-4799-8f2a-c2955943aade>

**Important note**

To cite this publication, please use the final published version (if applicable).

Please check the document version above.

**Copyright**

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**

Please contact us and provide details if you believe this document breaches copyrights.

We will remove access to the work immediately and investigate your claim.

# High-Power Digital Transmitters for Wireless Networks

Robert Jan Bootsma

# **High-Power Digital Transmitters for Wireless Networks**

## **Proefschrift**

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus prof. dr. ir. T.H.J.J. van der Hagen,

voorzitter van het College voor Promoties,

in het openbaar te verdedigen

op donderdag 18 december 2025 om 17.30 uur

door

**Robert Jan BOOTSMAN**

Elektrotechnisch ingenieur,

Technische Universiteit Delft, Nederland,

geboren te Nieuw-Vennep, Nederland.

Dit proefschrift is goedgekeurd door de promotoren.

Samenstelling promotiecommissie:

Rector Magnificus,

voorzitter

Prof. dr. ing. L.C.N. de Vreede,

Technische Universiteit Delft, promotor

Dr. S.M. Alavi,

Technische Universiteit Delft, promotor

*Onafhankelijke leden:*

Prof. dr. ir. W.D. van Driel,

Technische Universiteit Delft

Prof. dr. ir. A.B. Smolders,

Technische Universiteit Eindhoven

Prof. dr. ir. B. Nauta,

Technische Universiteit Twente

Prof. dr. P. Wambacq,

imec Leuven en Vrije Universiteit Brussel, België

Prof. dr. N. Llombart,

Technische Universiteit Delft, reservelid

*Overig lid:*

Dr. ir. F. van Rijs,

Ampleon Netherlands B.V.

The work in the dissertation was supported by the Nederlandse Organisatie voor Wetenschappelijk Onderzoek (NWO), Ampleon Netherlands B.V., and Nokia Bell Labs through the Open Technology Programme (OTP) under Project 16336 “DIPLoMAT” (Highly Integrated Digital-Intensive Massive MIMO Transceivers) and in part by the TKI HTSM research project “DRASTIC” (Digital transmitter ICs) with MediaTek in addition to the aforementioned project partners.

*Keywords:* Digital RF Transmitters, Power Amplifiers, Harmonic Matching, High-Speed Digital, CMOS, LDMOS, Heterogeneous Integration, Flip-Chip

*Cover:* Worlds first high-power fully digital transmitter, by R.J. Bootsman

The author set this dissertation in  $\text{\LaTeX}$ .

Copyright ©2025 by R.J. Bootsman. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, by photocopying, recording, training a machine learning language model, or otherwise, without the prior permission in writing from the copyright owners.

ISBN 978-94-6518-192-9 (e-book)

An electronic version of this dissertation is available at

<http://repository.tudelft.nl/>.

# Contents

|                                                                                       |              |

|---------------------------------------------------------------------------------------|--------------|

| <b>Glossary</b>                                                                       | <b>xix</b>   |

| <b>Symbols</b>                                                                        | <b>xxiii</b> |

| <b>Summary</b>                                                                        | <b>xxvii</b> |

| <b>Samenvatting</b>                                                                   | <b>xxix</b>  |

| <b>1 Introduction</b>                                                                 | <b>1</b>     |

| 1.1 Exponential Growth of Data Capacity . . . . .                                     | 1            |

| 1.1.1 Technological Advancement . . . . .                                             | 2            |

| 1.1.2 Network Energy Requirements. . . . .                                            | 3            |

| 1.2 Trends in Next-Generation Base Stations. . . . .                                  | 4            |

| 1.2.1 Higher Carrier Frequencies. . . . .                                             | 4            |

| 1.2.2 Small Cells, Massive MIMO, and Their Energy Consumption . . . . .               | 5            |

| 1.3 Technology Scaling and Digital-Intensive RF Transmitters . . . . .                | 5            |

| 1.4 Research Objective . . . . .                                                      | 7            |

| 1.5 Dissertation Outline . . . . .                                                    | 7            |

| <b>2 Background on Digital Transmitters (DTXs) and Power Amplifiers</b>               | <b>9</b>     |

| 2.1 Transmitter Architectures . . . . .                                               | 9            |

| 2.1.1 Cartesian Transmitters . . . . .                                                | 10           |

| 2.1.2 Polar Transmitters . . . . .                                                    | 12           |

| 2.1.3 Multi-Phase Transmitters . . . . .                                              | 13           |

| 2.2 Amplifier Classes. . . . .                                                        | 14           |

| 2.2.1 Analog Transconductance Classes . . . . .                                       | 16           |

| 2.2.2 Digital Current Scaling Classes. . . . .                                        | 17           |

| 2.2.3 Comparing Analog Transconductance and Digital Current Scaling Classes . . . . . | 19           |

| 2.2.4 Harmonic Tuning and Switching Classes. . . . .                                  | 23           |

| 2.3 Amplifier Efficiency Enhancement Techniques . . . . .                             | 27           |

| 2.3.1 Supply Modulation/Switching . . . . .                                           | 27           |

| 2.3.2 Load Modulation. . . . .                                                        | 28           |

| 2.4 DTX Topologies . . . . .                                                          | 31           |

| 2.4.1 Common Gate . . . . .                                                           | 32           |

| 2.4.2 Switched Capacitor. . . . .                                                     | 32           |

| 2.4.3 Common Source . . . . .                                                         | 34           |

| <b>3 High-Power DTX Implementation Considerations</b>                                 | <b>37</b>    |

| 3.1 Electrical Considerations. . . . .                                                | 37           |

| 3.1.1 Threshold Voltage Requirements . . . . .                                        | 38           |

| 3.1.2 Gate Segmentation . . . . .                                                     | 39           |

|          |                                                                |           |

|----------|----------------------------------------------------------------|-----------|

| 3.1.3    | ESD Protection . . . . .                                       | 40        |

| 3.2      | Physical Considerations . . . . .                              | 41        |

| 3.2.1    | Minimum Interconnect Pitch . . . . .                           | 41        |

| 3.2.2    | Thermal Requirements . . . . .                                 | 43        |

| 3.3      | Conclusion . . . . .                                           | 44        |

| <b>4</b> | <b>DTX Drivers</b>                                             | <b>45</b> |

| 4.1      | Digital Driver Requirements . . . . .                          | 46        |

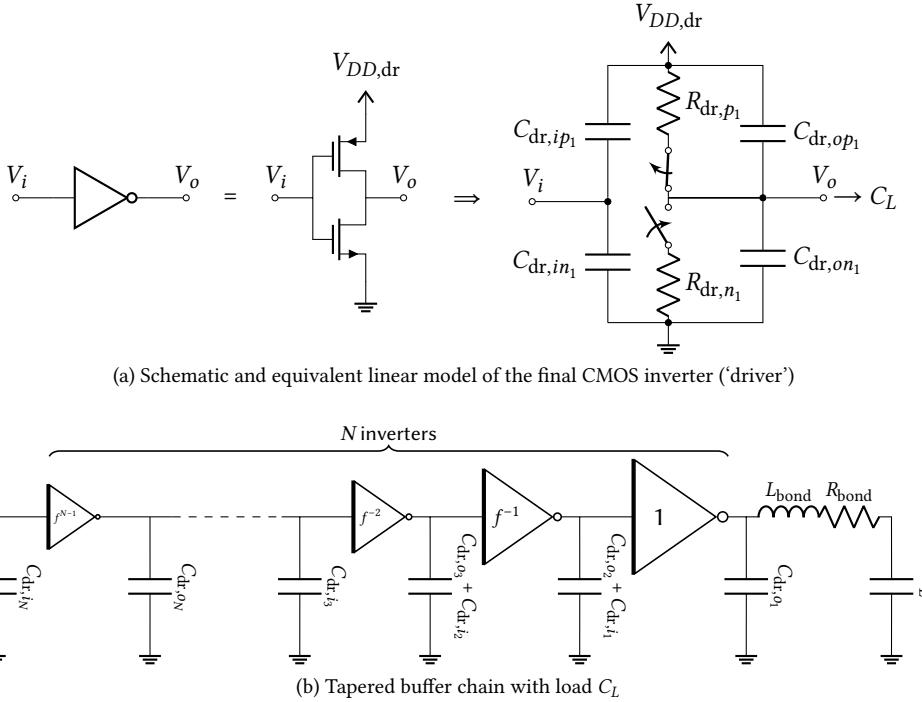

| 4.1.1    | The Linearized CMOS Model . . . . .                            | 46        |

| 4.1.2    | CMOS Driver Model . . . . .                                    | 47        |

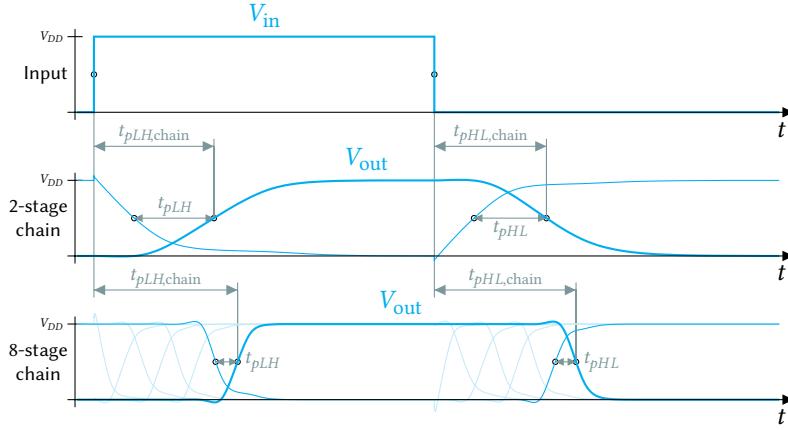

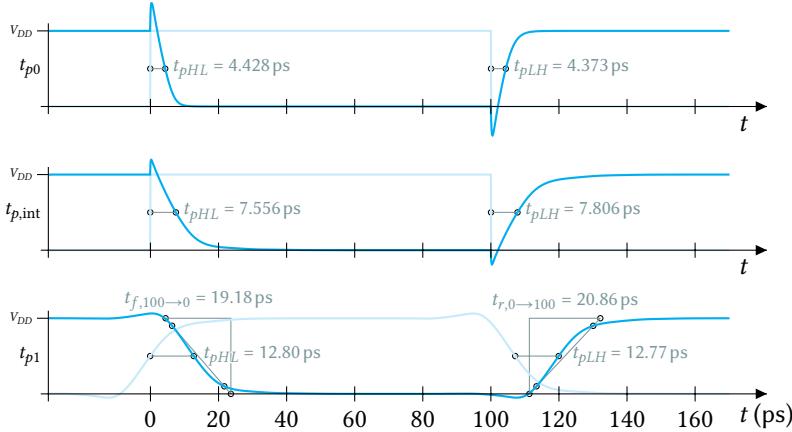

| 4.1.3    | Trade-Off Between Power Consumption and Driver Speed . . . . . | 49        |

| 4.2      | Technology Considerations for Digital Drivers . . . . .        | 51        |

| 4.2.1    | Inverter-Based Drivers . . . . .                               | 51        |

| 4.2.2    | Stacked Device Drivers . . . . .                               | 55        |

| 4.3      | Conclusion . . . . .                                           | 57        |

| <b>5</b> | <b>DTX Modeling</b>                                            | <b>59</b> |

| 5.1      | DTX Black-Box Operation . . . . .                              | 59        |

| 5.1.1    | Bits-in RF-out . . . . .                                       | 60        |

| 5.1.2    | Introducing <i>D</i> -Parameters for DTX . . . . .             | 62        |

| 5.1.3    | Normalized Digital Forward Transfer . . . . .                  | 64        |

| 5.2      | Simulating a Gate-Segmented DTX . . . . .                      | 68        |

| 5.2.1    | Discrete Simulation Model . . . . .                            | 69        |

| 5.2.2    | Current Scaling Simulation Model . . . . .                     | 69        |

| 5.2.3    | Example of System Level Simulations: DTX Two-Tone Operation .  | 71        |

| 5.3      | Conclusions . . . . .                                          | 76        |

| <b>6</b> | <b>Estimating the DTX Output Power and Efficiency</b>          | <b>77</b> |

| 6.1      | DTX Power and Efficiency Definitions . . . . .                 | 78        |

| 6.2      | DTX Power Model in a Single Line-Up . . . . .                  | 79        |

| 6.3      | DTX Power Model Using Efficiency Enhancement . . . . .         | 84        |

| 6.4      | Example Calculations with the DTX Power Model . . . . .        | 86        |

| 6.4.1    | Calculation Example for a Single-Ended DTX . . . . .           | 86        |

| 6.4.2    | Two-Way Doherty DTX . . . . .                                  | 89        |

| 6.4.3    | Comparison to an Analog TX Line-Up . . . . .                   | 92        |

| 6.5      | Conclusion . . . . .                                           | 92        |

| <b>7</b> | <b>The Proof-of-Concept for High-Power DTXs</b>                | <b>95</b> |

| 7.1      | Aimed Functionality and Requirements . . . . .                 | 96        |

| 7.2      | LDMOS Implementation . . . . .                                 | 97        |

| 7.2.1    | Unary and Binary Weighted Segments . . . . .                   | 98        |

| 7.2.2    | Assembly of the Demonstrator . . . . .                         | 101       |

| 7.3      | GaN Implementation . . . . .                                   | 103       |

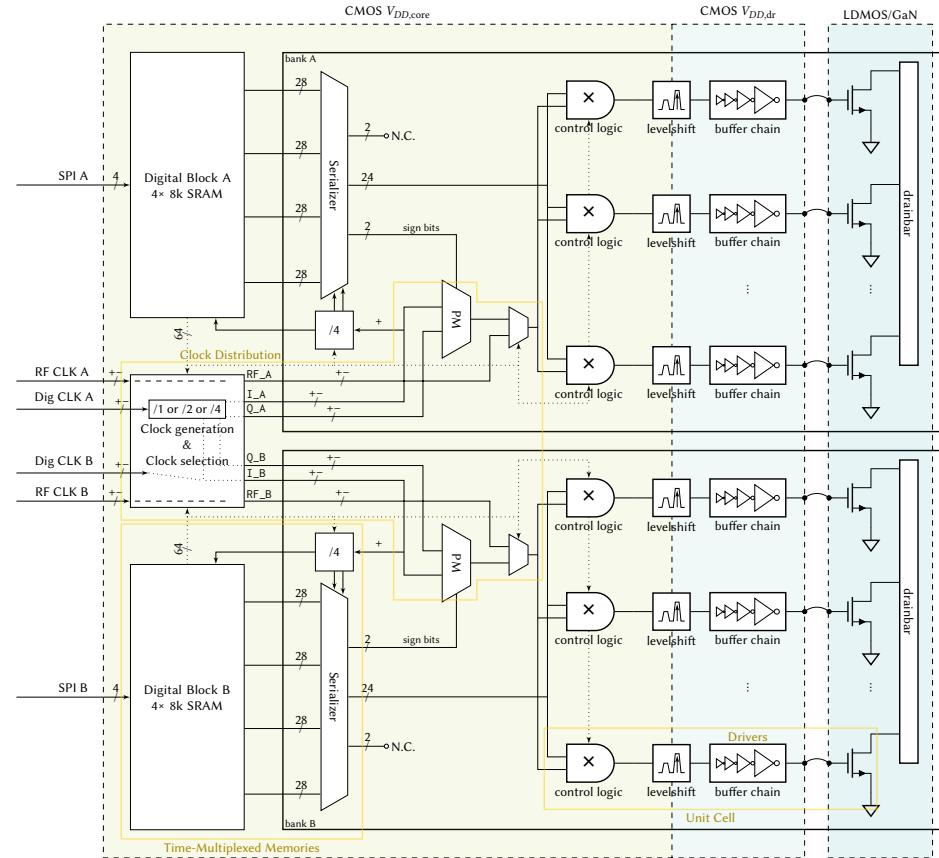

| 7.4      | CMOS Controller Architecture . . . . .                         | 104       |

| 7.4.1    | Overview . . . . .                                             | 105       |

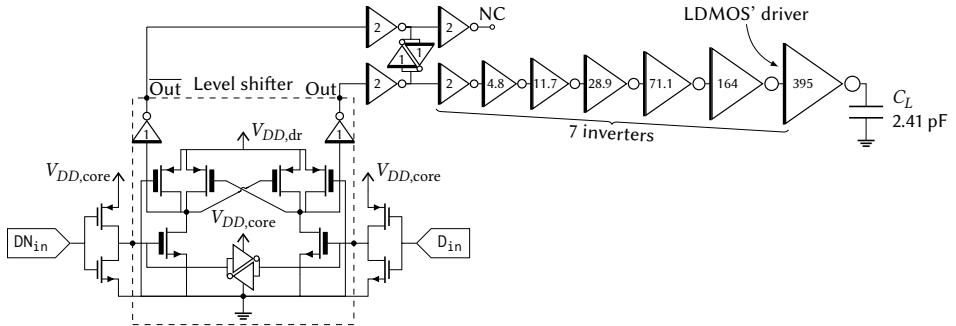

| 7.4.2    | Drivers . . . . .                                              | 110       |

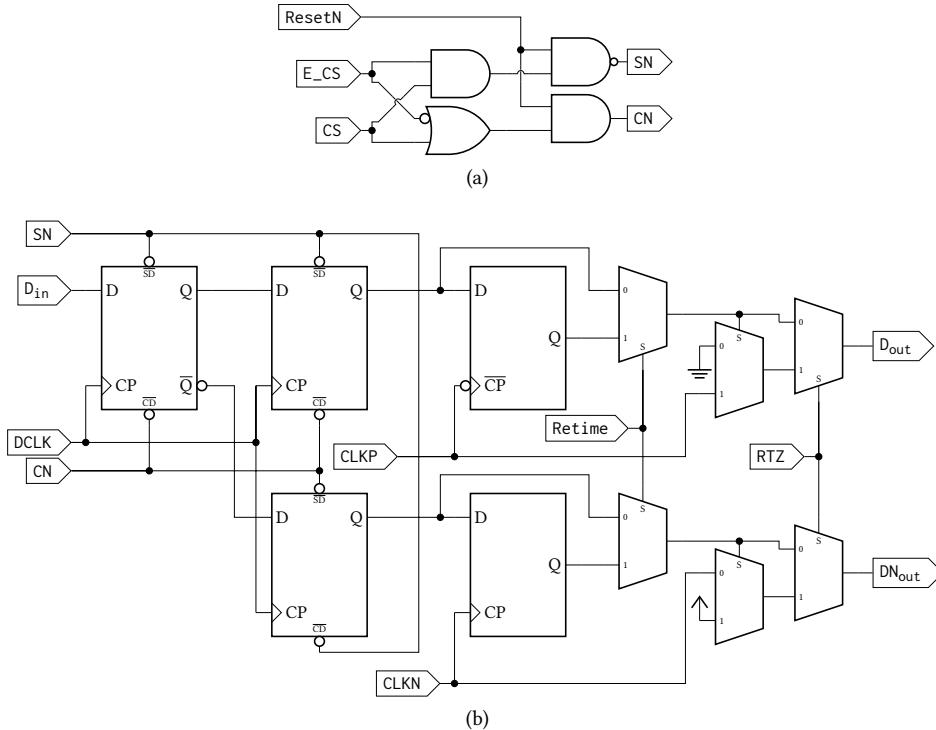

| 7.4.3    | Unit Cell . . . . .                                            | 110       |

| 7.4.4    | Time-Multiplexed Memories . . . . .                            | 111       |

|          |                                                                                         |            |

|----------|-----------------------------------------------------------------------------------------|------------|

| 7.4.5    | Clock Generation, Division and Distribution . . . . .                                   | 112        |

| 7.4.6    | Supply Decoupling . . . . .                                                             | 117        |

| 7.5      | High-Power DTX Demonstrator I: On-Resistance Modulation – Class-BE . . . . .            | 118        |

| 7.5.1    | Class-BE output match . . . . .                                                         | 118        |

| 7.5.2    | Demonstrator Realization and Measurement Results . . . . .                              | 121        |

| 7.5.3    | Key Take-Aways . . . . .                                                                | 131        |

| 7.6      | High-Power DTX Demonstrator II: Introducing Current Scaling – Digital class-C . . . . . | 133        |

| 7.6.1    | Designing for Class-B Multi-Phase Operation . . . . .                                   | 134        |

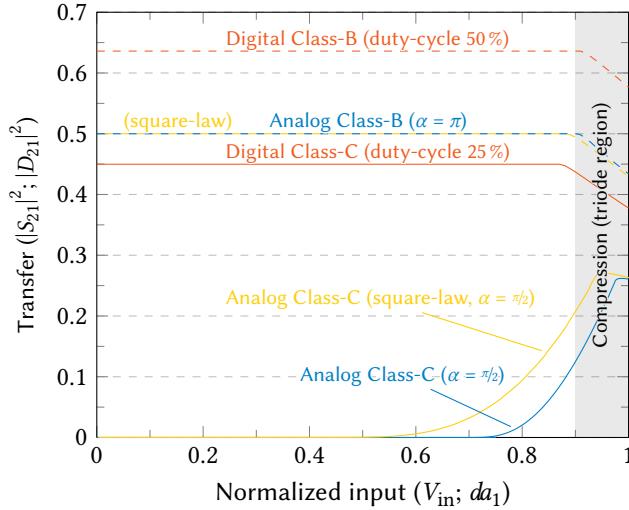

| 7.6.2    | Duty-Cycle Reduction and Linearity . . . . .                                            | 136        |

| 7.6.3    | Measurement Results . . . . .                                                           | 137        |

| 7.7      | High-Power DTX Demonstrator III: Wideband Digital Class-C Doherty . . . . .             | 142        |

| 7.7.1    | Design of the Harmonic Output Match . . . . .                                           | 142        |

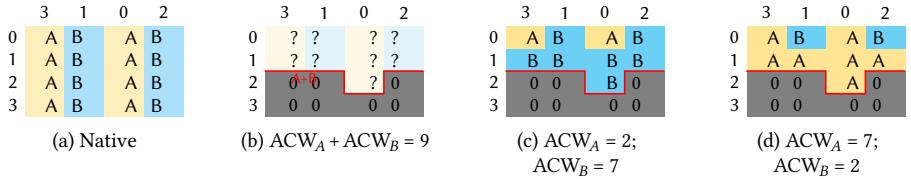

| 7.7.2    | Activation Pattern . . . . .                                                            | 144        |

| 7.7.3    | Improved Supply Decoupling . . . . .                                                    | 147        |

| 7.7.4    | Measurement Results . . . . .                                                           | 148        |

| 7.7.5    | ETSI Power Model . . . . .                                                              | 153        |

| <b>8</b> | <b>Design of a High-Resolution High-Power DTX</b>                                       | <b>157</b> |

| 8.1      | Goals and Design Requirements for the Next-Generation of Base Stations . . . . .        | 158        |

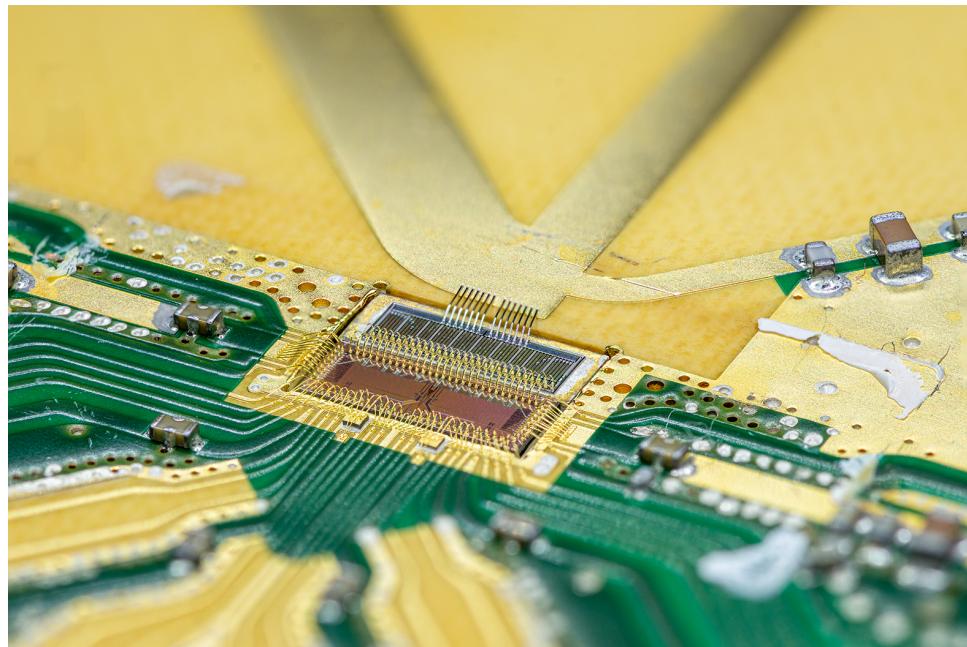

| 8.2      | LDMOS Layout and Flip-Chip Assembly . . . . .                                           | 160        |

| 8.2.1    | Switch-Bank Layout using Flip-Chip . . . . .                                            | 161        |

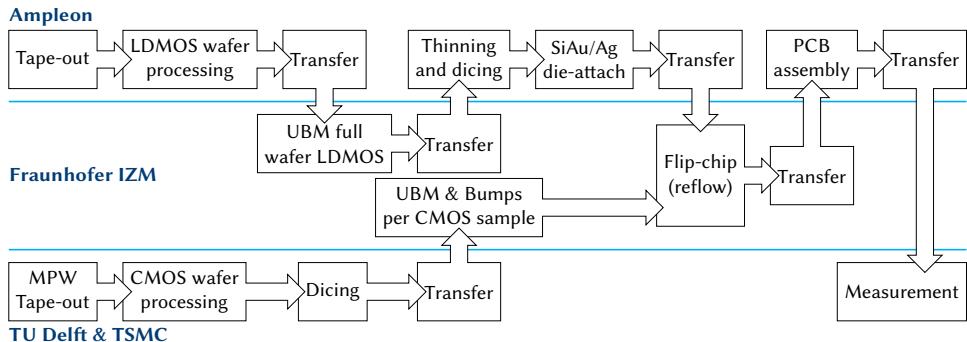

| 8.2.2    | Flip-Chip Assembly Flow for Minimized Risk . . . . .                                    | 163        |

| 8.3      | Activation Pattern . . . . .                                                            | 166        |

| 8.3.1    | Unit Cell Logic . . . . .                                                               | 167        |

| 8.3.2    | Bank Clock Line Design . . . . .                                                        | 168        |

| 8.4      | Advanced DTX Technology, Modeling and Design . . . . .                                  | 171        |

| 8.4.1    | A Modified LDMOS Technology . . . . .                                                   | 171        |

| 8.4.2    | LDMOS Interconnect and Power Stage Modeling . . . . .                                   | 172        |

| 8.4.3    | CMOS: Driver and ESD . . . . .                                                          | 177        |

| 8.5      | DC Supply Requirements for Wideband Operation . . . . .                                 | 182        |

| 8.5.1    | Definition of the Relevant Frequency Regions . . . . .                                  | 182        |

| 8.5.2    | Sensitivity Analysis . . . . .                                                          | 186        |

| 8.5.3    | Implementation . . . . .                                                                | 188        |

| 8.5.4    | PCB Design Considerations . . . . .                                                     | 193        |

| 8.6      | Demonstrator Overview . . . . .                                                         | 194        |

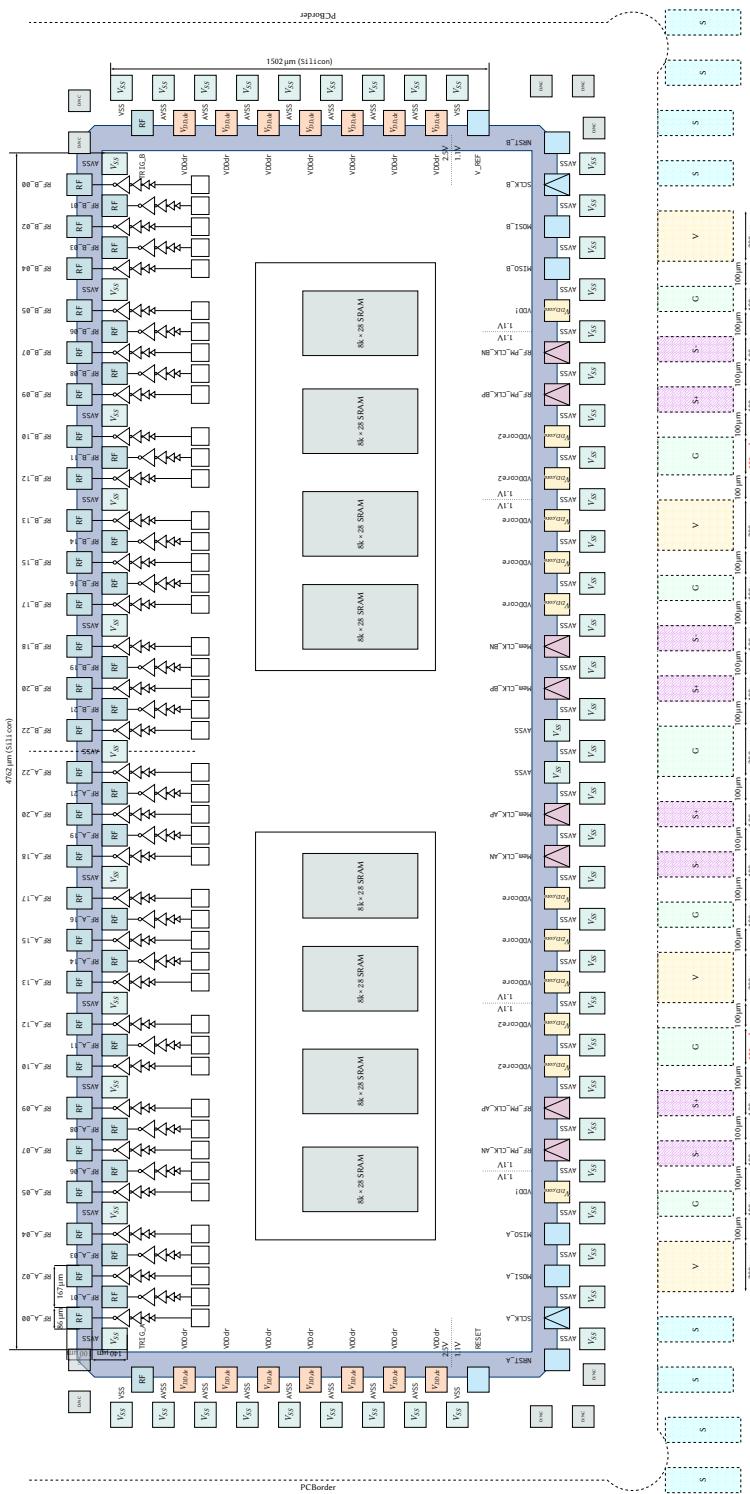

| 8.6.1    | CMOS Overview . . . . .                                                                 | 194        |

| 8.6.2    | Flip-Chip Assembly Verification . . . . .                                               | 197        |

| 8.6.3    | LDMOS Variants and Demonstrators . . . . .                                              | 198        |

| 8.7      | Measurements . . . . .                                                                  | 198        |

| 8.7.1    | Demonstrator I: Single-Ended 3.5 GHz Operation . . . . .                                | 199        |

| 8.7.2    | Demonstrator XI: Push-Pull 1.8 GHz Operation . . . . .                                  | 205        |

| <b>9</b> | <b>Conclusion and Outlook</b>                                                           | <b>211</b> |

| 9.1      | Dissertation Conclusions . . . . .                                                      | 211        |

| 9.2      | Outlook on the Future of High-Power DTX . . . . .                                       | 213        |

| 9.2.1    | Technology Trends . . . . .                                                             | 213        |

---

|                                                                            |            |

|----------------------------------------------------------------------------|------------|

| 9.2.2 Segmenting III-V Semiconductors . . . . .                            | 214        |

| 9.2.3 Future Work . . . . .                                                | 215        |

| <b>A Definitions and Derivations</b>                                       | <b>217</b> |

| A.1 Mathematics . . . . .                                                  | 217        |

| A.2 Power Amplifiers. . . . .                                              | 218        |

| A.2.1 Power, Gain, and Efficiencies . . . . .                              | 218        |

| A.2.2 Equations for the Analog Transconductance Classes . . . . .          | 219        |

| A.2.3 Linearity . . . . .                                                  | 220        |

| A.3 Further Derivations on <i>D</i> -Parameters for DTX . . . . .          | 220        |

| A.3.1 Higher-Order Multi-Port <i>D</i> -Parameters. . . . .                | 220        |

| A.3.2 Multi-Rate <i>D</i> -Parameters . . . . .                            | 221        |

| A.4 Circuits . . . . .                                                     | 222        |

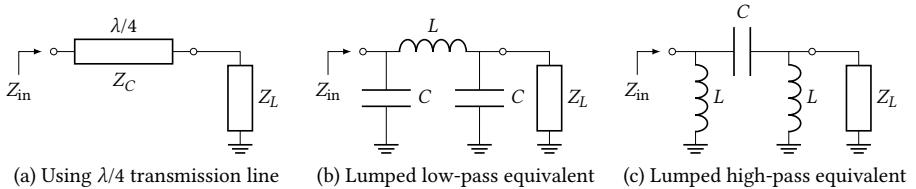

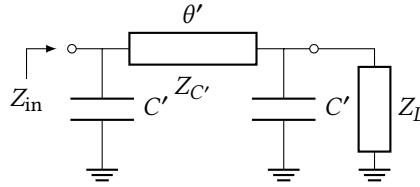

| A.4.1 Impedance Inverters . . . . .                                        | 222        |

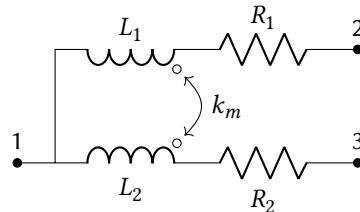

| A.4.2 Coupled Inductors with a Common Node . . . . .                       | 223        |

| A.5 Optimization of Driver Chains . . . . .                                | 224        |

| A.5.1 For Inverter Based Drivers . . . . .                                 | 224        |

| A.5.2 For Stacked Drivers . . . . .                                        | 225        |

| A.6 Conversion from <i>S</i> -Parameters to Distributed Elements . . . . . | 226        |

| A.7 Baseband considerations of a DTX . . . . .                             | 227        |

| A.7.1 Baseband Current Magnitude Calculation . . . . .                     | 227        |

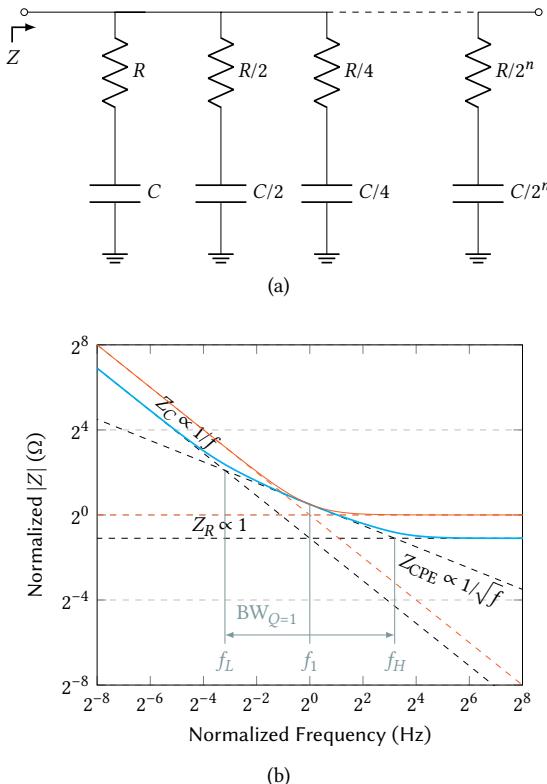

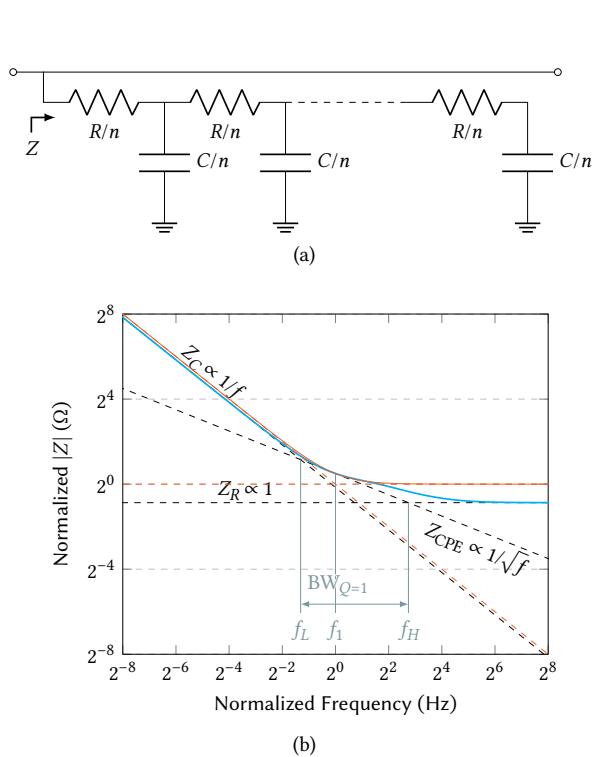

| A.7.2 Distributed Decoupling Capacitors . . . . .                          | 229        |

| <b>B Simulation Models</b>                                                 | <b>233</b> |

| B.1 General DTX Simulation Remarks . . . . .                               | 233        |

| B.1.1 Harmonic Balance (HB) Simulations . . . . .                          | 233        |

| B.1.2 Envelope Simulations . . . . .                                       | 234        |

| B.2 ADS Components . . . . .                                               | 234        |

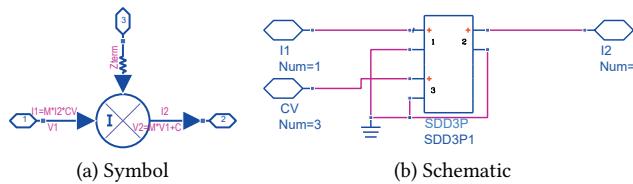

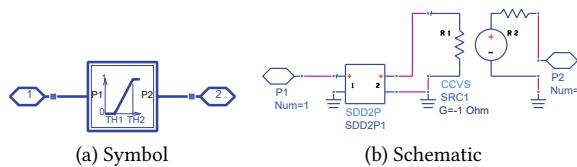

| B.2.1 Imult . . . . .                                                      | 234        |

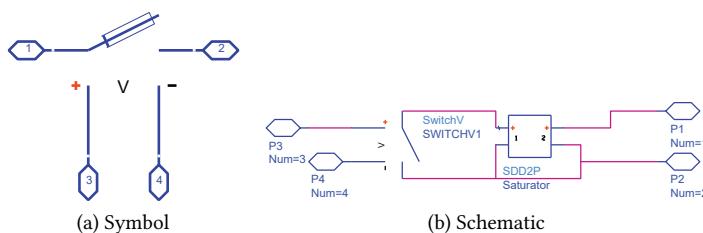

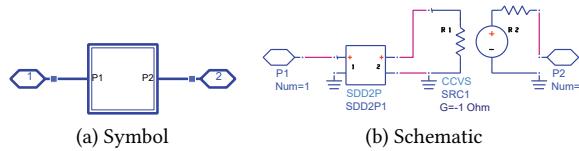

| B.2.2 Switch_ISAT_Ron . . . . .                                            | 235        |

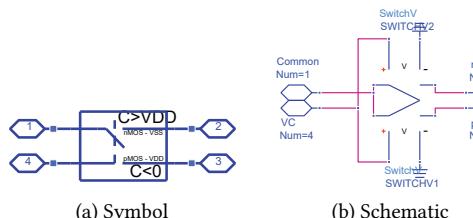

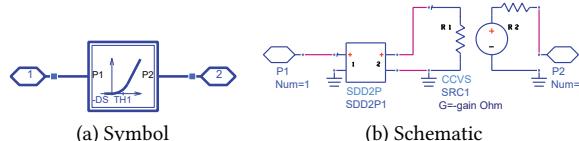

| B.2.3 SPDT_Dynamic_ADJcmosVDD . . . . .                                    | 236        |

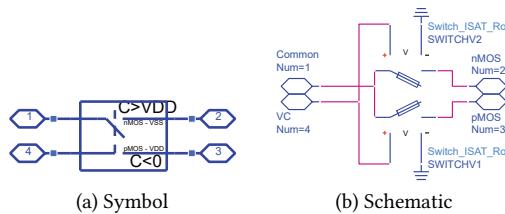

| B.2.4 SPDT_Dynamic_ADJcmosVDD_noInv_Sat. . . . .                           | 237        |

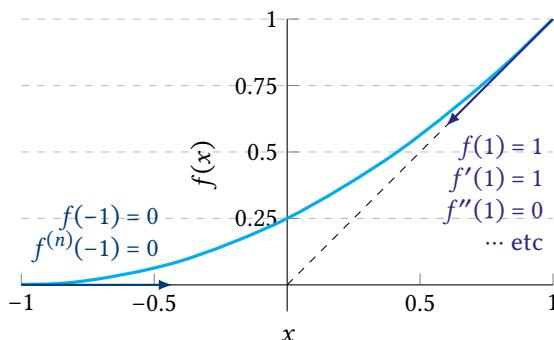

| B.2.5 LinearActivation . . . . .                                           | 238        |

| B.2.6 LinearActivation_Smooth . . . . .                                    | 238        |

| B.2.7 LinearActivation_SmoothExp . . . . .                                 | 239        |

| B.3 ADS AEL. . . . .                                                       | 240        |

| B.3.1 stogammaz . . . . .                                                  | 240        |

| B.3.2 storlgc . . . . .                                                    | 240        |

| B.4 Cadence . . . . .                                                      | 241        |

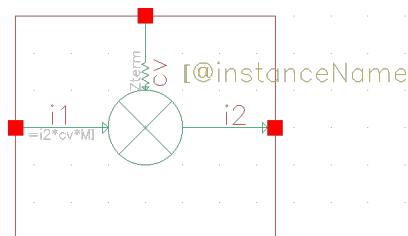

| B.4.1 Imult . . . . .                                                      | 241        |

| <b>C Chip Gallery</b>                                                      | <b>243</b> |

| <b>Bibliography</b>                                                        | <b>247</b> |

| <b>Acknowledgments</b>                                                     | <b>257</b> |

| <b>Curriculum Vitæ</b>                                                     | <b>261</b> |

| <b>List of Publications</b>                                                | <b>263</b> |

# List of Figures

|      |                                                                                                                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

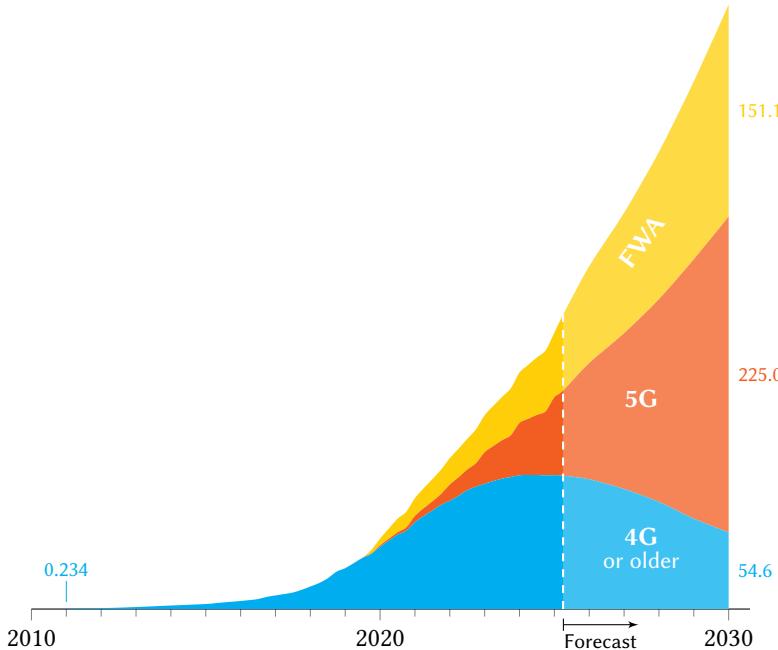

| 1.1  | Monthly mobile network traffic in EB/month, historic data and forecast. . . . .                                                                       | 2  |

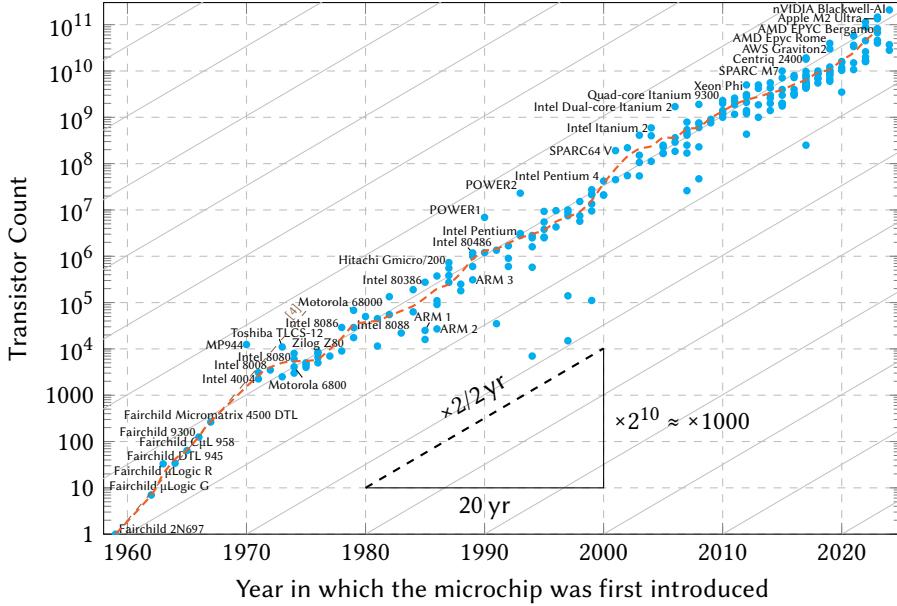

| 1.2  | The number of integrated transistors per microchip, illustrating Moore's Law over time. . . . .                                                       | 3  |

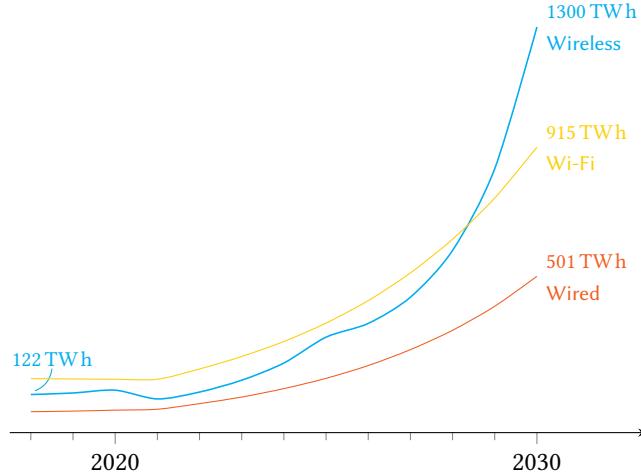

| 1.3  | Predicted electric power consumption of networks. . . . .                                                                                             | 4  |

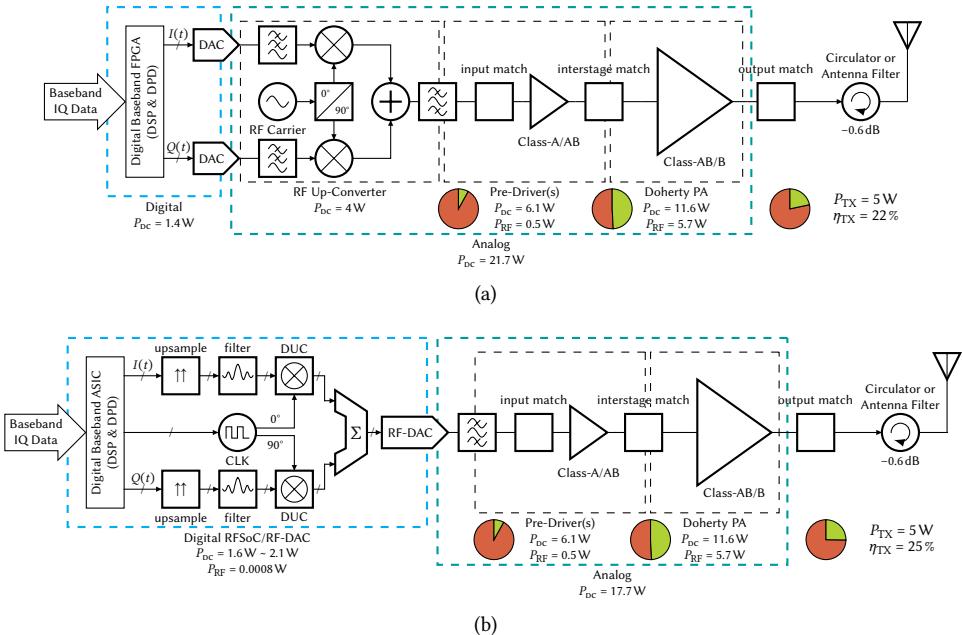

| 1.4  | Average power generation and power consumption breakdown of the different analog TX stages. . . . .                                                   | 6  |

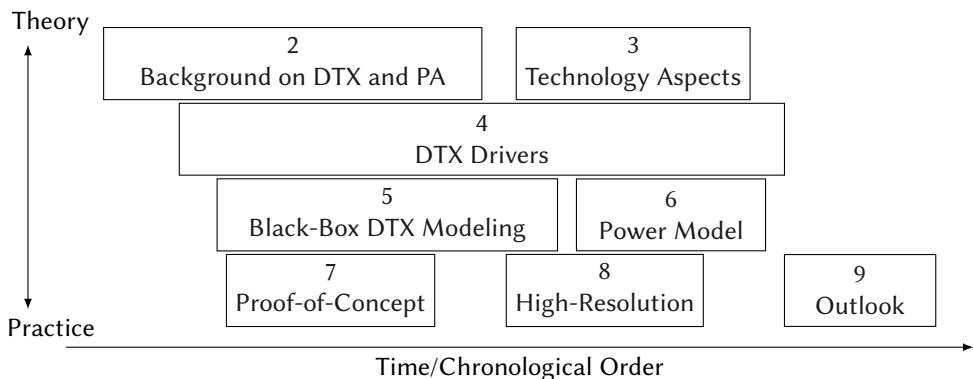

| 1.5  | Chapter guide for this dissertation. . . . .                                                                                                          | 8  |

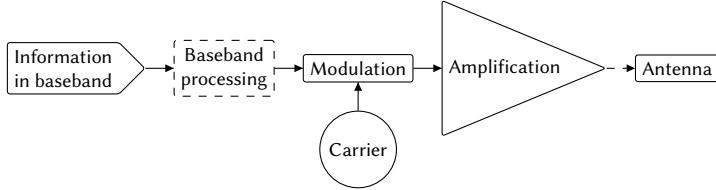

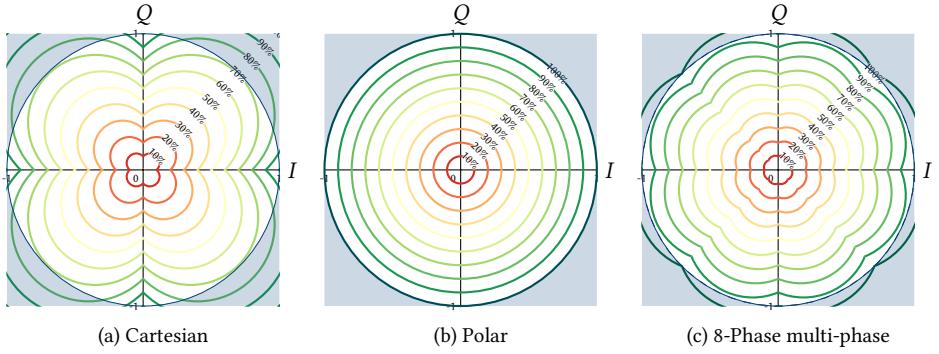

| 2.1  | Transmitter block diagram. . . . .                                                                                                                    | 10 |

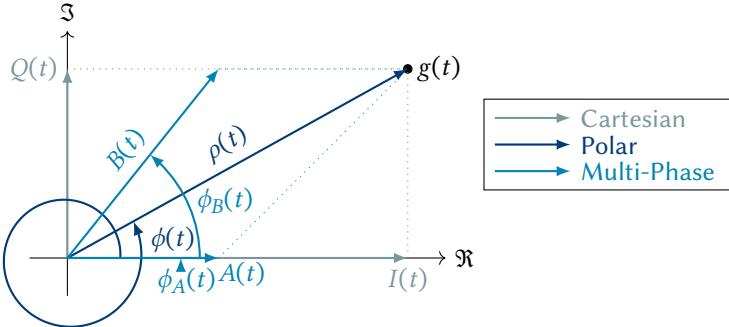

| 2.2  | Different vector representations of a complex baseband envelope point. . . . .                                                                        | 10 |

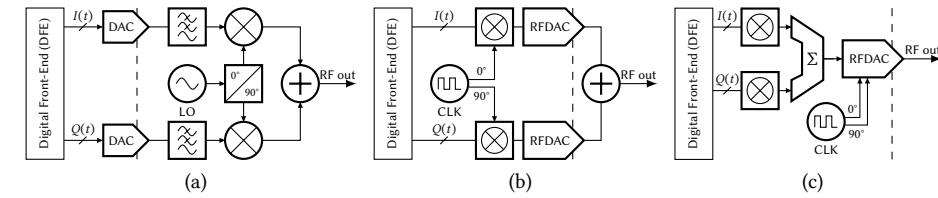

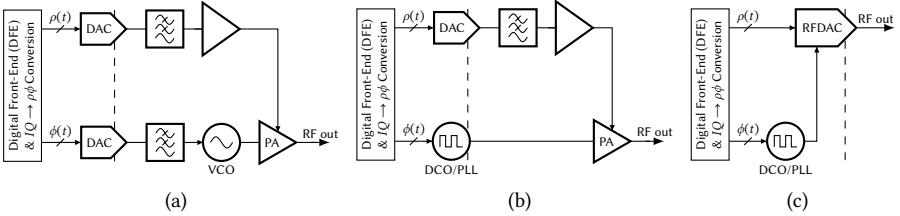

| 2.3  | Cartesian transmitter architectures, where the functional blocks are increasingly digitized. . . . .                                                  | 11 |

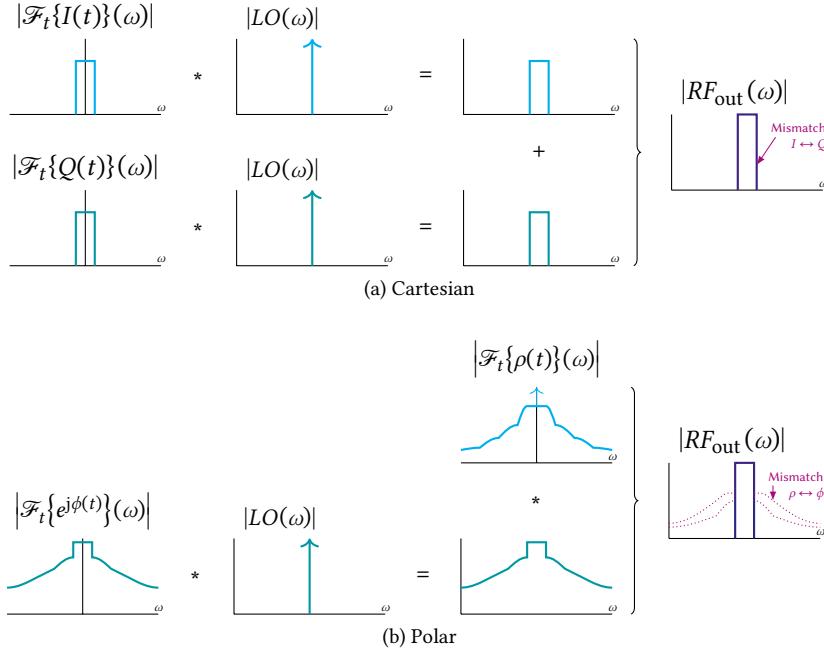

| 2.4  | Spectra of the intermediate signals for different transmitter architectures. . . . .                                                                  | 11 |

| 2.5  | Normalized efficiency contours vs. complex modulation points for different transmitter architectures. . . . .                                         | 12 |

| 2.6  | Polar transmitter architectures, where the functional blocks are increasingly digitized. . . . .                                                      | 12 |

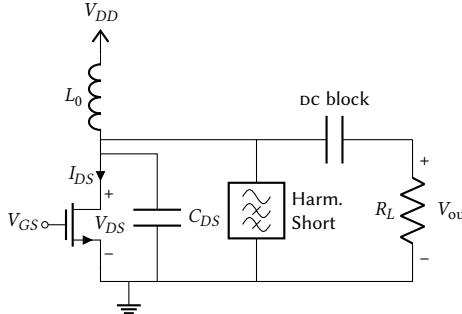

| 2.7  | Example of a digital-intensive multi-phase transmitter architecture. . . . .                                                                          | 13 |

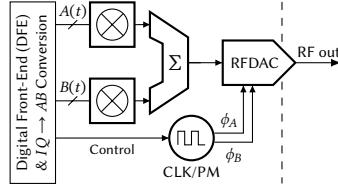

| 2.8  | Illustrating the difference between "analog" and "digital" waveforms. . . . .                                                                         | 15 |

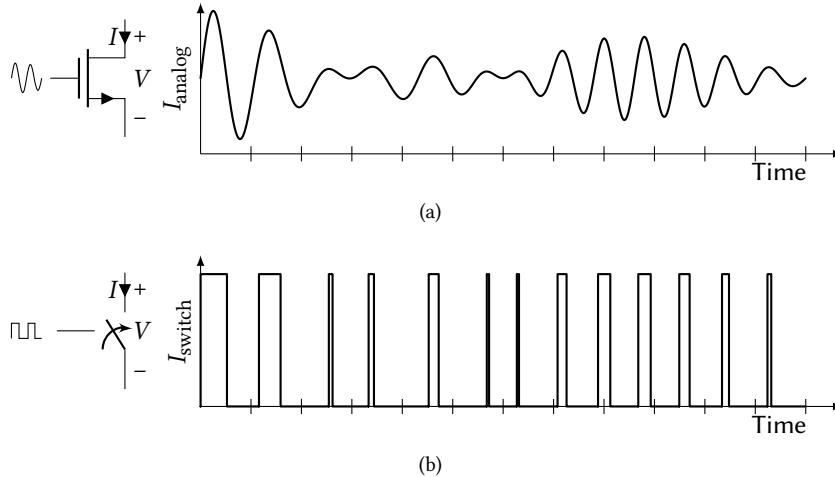

| 2.9  | Basic circuit topology of transconductance amplifiers. . . . .                                                                                        | 16 |

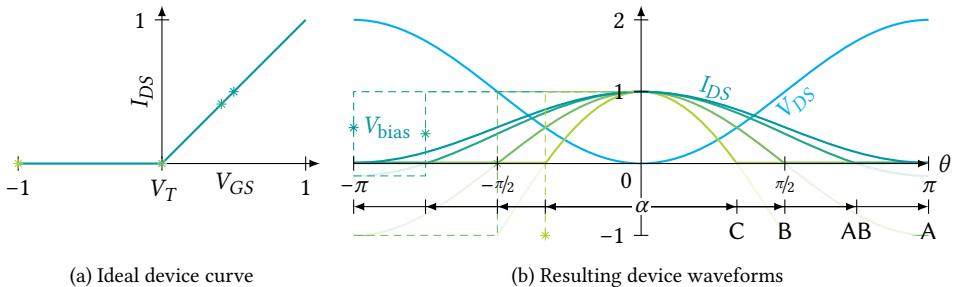

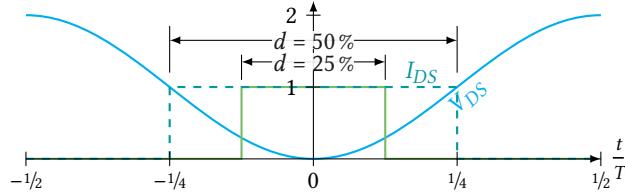

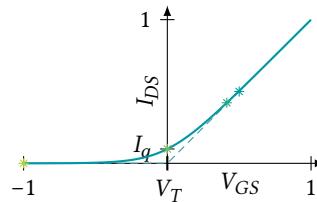

| 2.10 | Idealized transconductance class operation. . . . .                                                                                                   | 16 |

| 2.11 | Harmonic currents of analog transconductance classes. . . . .                                                                                         | 17 |

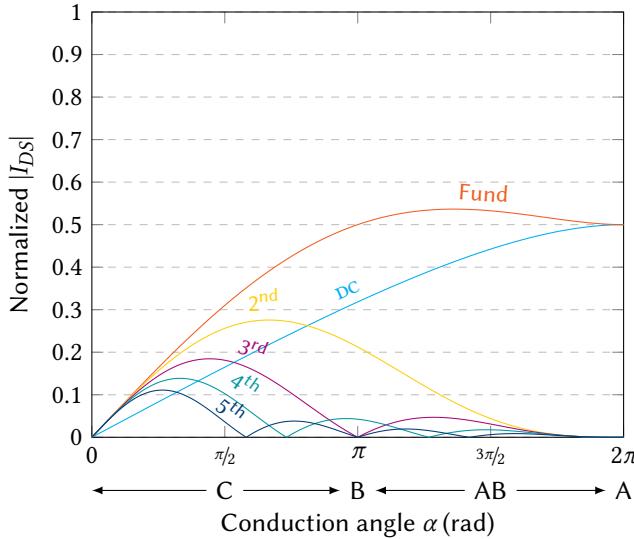

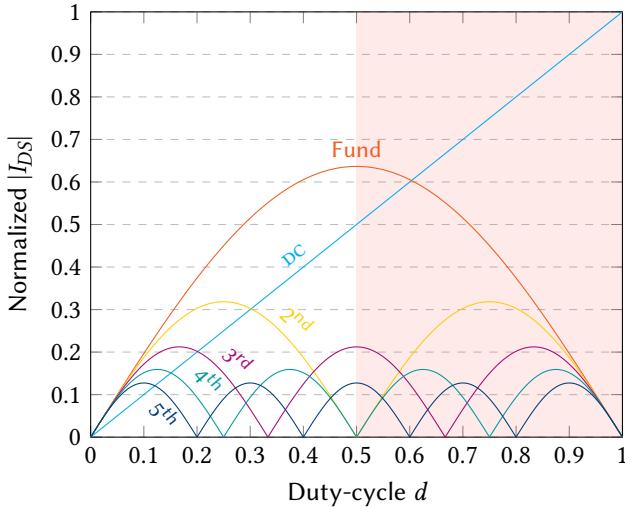

| 2.12 | Ideal digital current scaling waveforms for different duty-cycles $d$ . . . . .                                                                       | 18 |

| 2.13 | Harmonic currents of the family of digital current scaling classes. . . . .                                                                           | 18 |

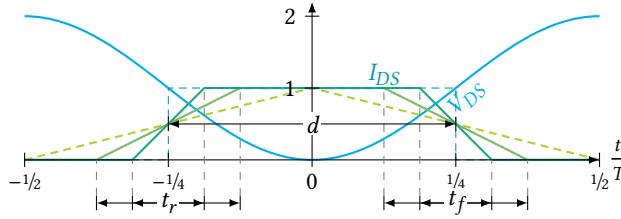

| 2.14 | Digital current scaling waveforms with nonzero rise and fall times. . . . .                                                                           | 19 |

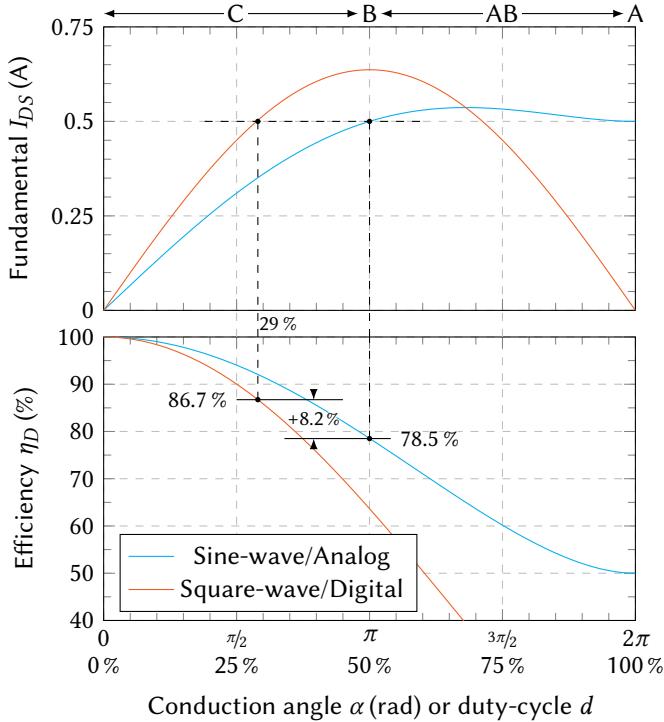

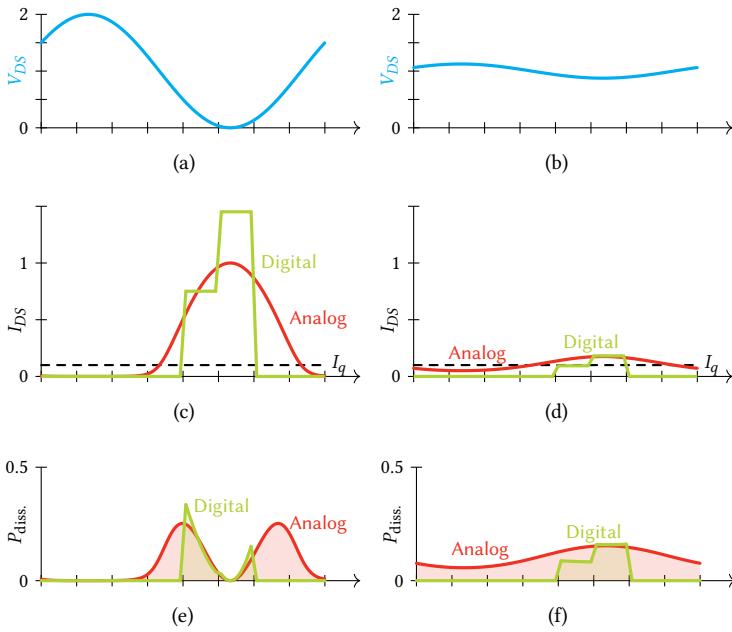

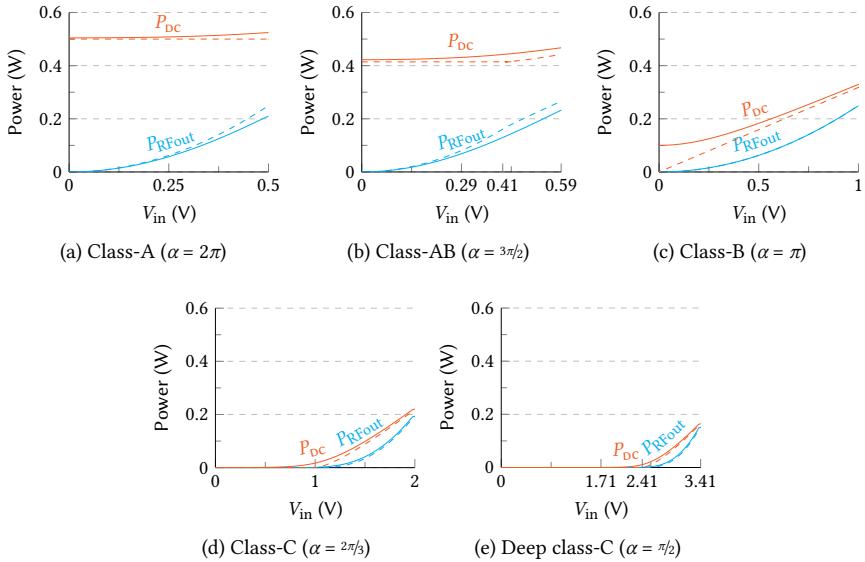

| 2.15 | Analog and digital class-AB/C theoretical performance compared: Normalized output power and drain efficiency vs. conduction angle/duty-cycle. . . . . | 20 |

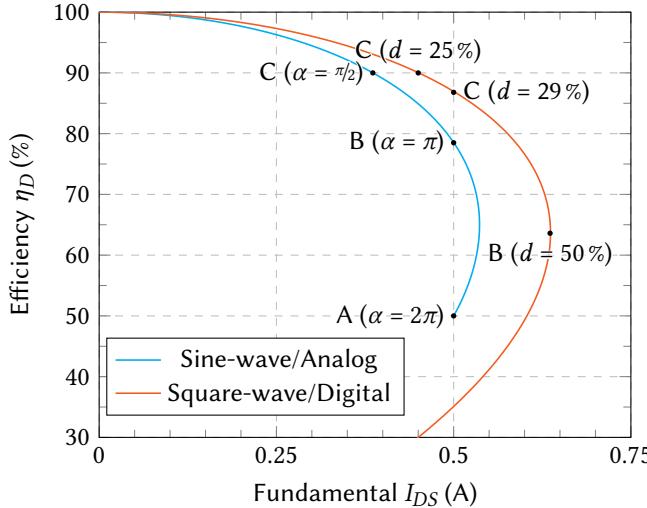

| 2.16 | Theoretical drain efficiency for the analog and digital class-AB/C vs. fundamental output current. . . . .                                            | 21 |

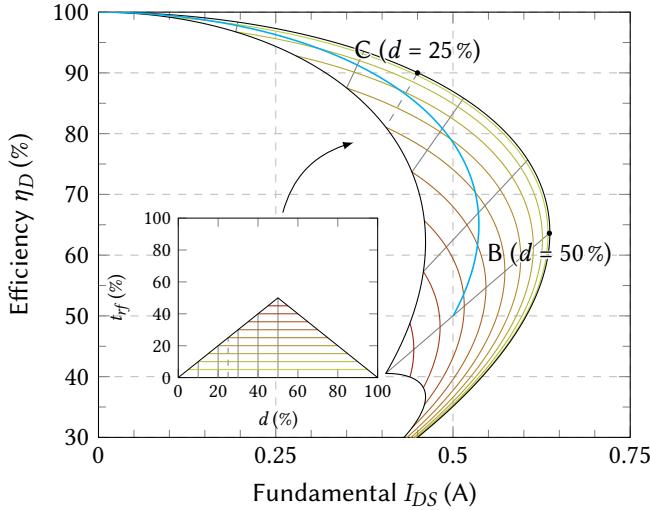

| 2.17 | Drain efficiency for digital class-AB/C with varying rise/fall times vs. fundamental output current. . . . .                                          | 22 |

| 2.18 | A more realistic device curve with a quiescent current $I_q$ at $V_T = 0\text{V}$ . . . . .                                                           | 22 |

| 2.19 | Comparing an example analog and digital current waveform, and their power dissipation for peak power condition and in power back-off. . . . .         | 23 |

| 2.20 | The impact in terms of power of an analog quiescent current for different operating classes vs. input magnitude. . . . .                              | 24 |

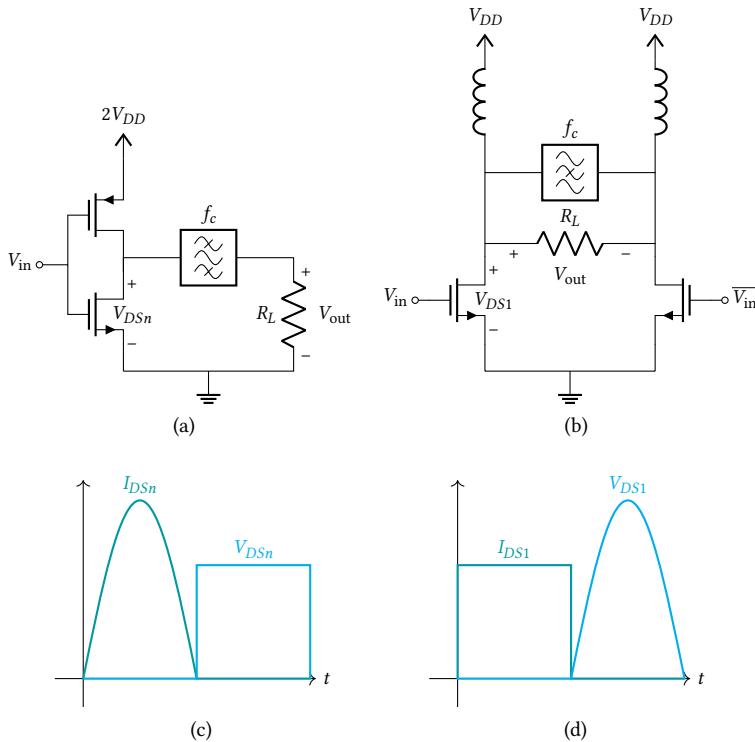

| 2.21 | The circuit topology and resulting device waveforms for class-D and $\text{D}^{-1}$ operation. . . . .                                                | 25 |

| 2.22 | The circuit topology and resulting device waveforms for class-E. . . . .                                                                              | 26 |

|      |                                                                                                                                                                                                |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

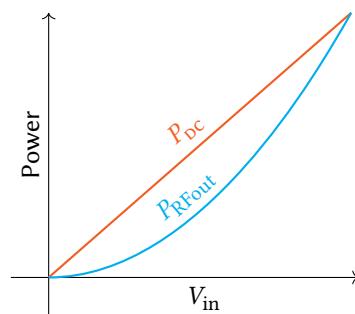

| 2.23 | The power relations with input voltage of an ideal amplifier without efficiency enhancement. . . . .                                                                                           | 27 |

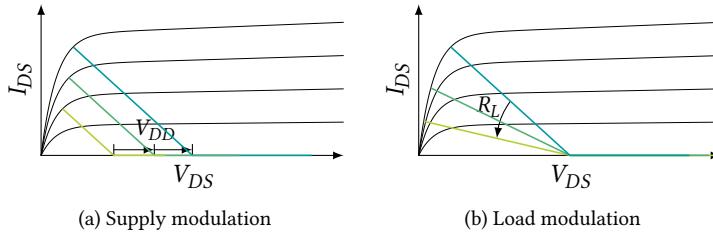

| 2.24 | The change in device load lines caused by efficiency enhancement. . . . .                                                                                                                      | 28 |

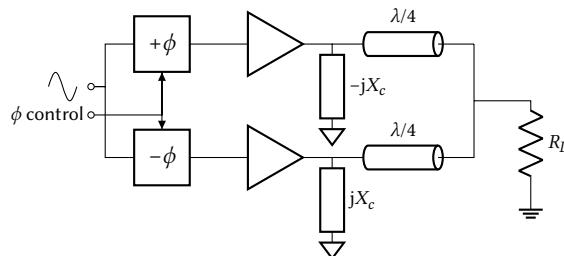

| 2.25 | A typical outphasing circuit topology. . . . .                                                                                                                                                 | 28 |

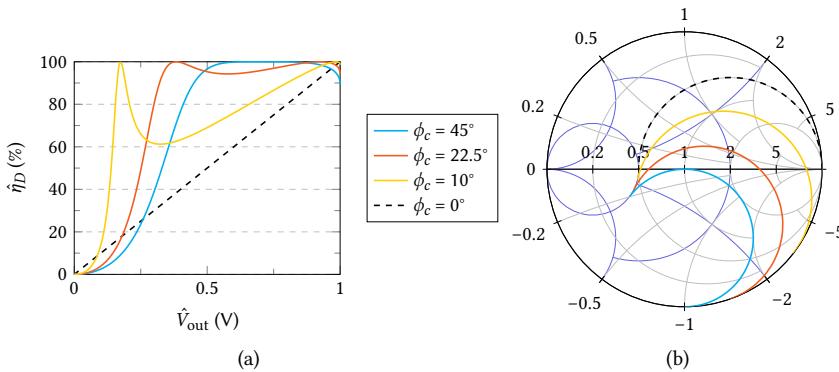

| 2.26 | The efficiency and load conditions for a selection of outphasing compensation angles $\phi_c$ . . . . .                                                                                        | 29 |

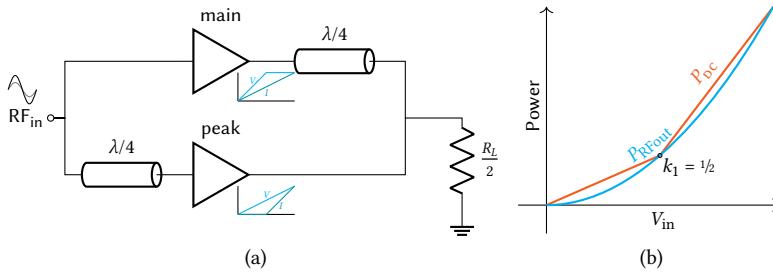

| 2.27 | A typical symmetrical 2-way Doherty circuit topology, with its ideal power relations. . . . .                                                                                                  | 29 |

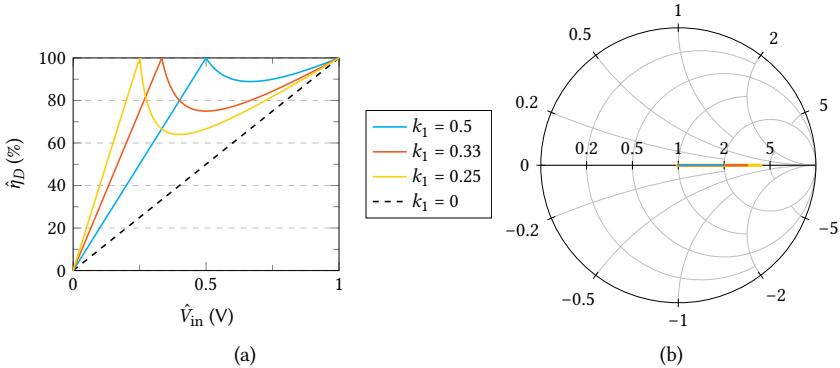

| 2.28 | The efficiency of a Doherty amplifier and the load conditions for the main amplifier for a varying power back-off point $k$ . . . . .                                                          | 30 |

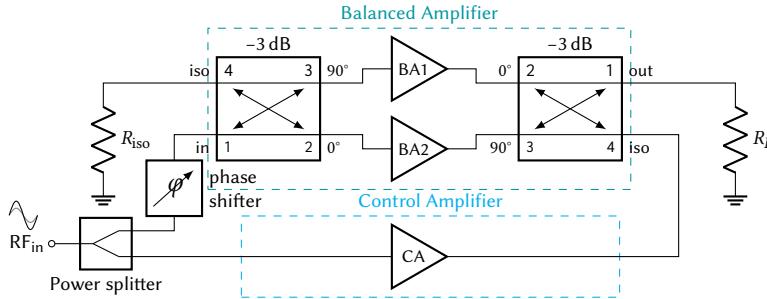

| 2.29 | Circuit topology for a pseudo-Doherty load-modulating balanced amplifier. . . . .                                                                                                              | 31 |

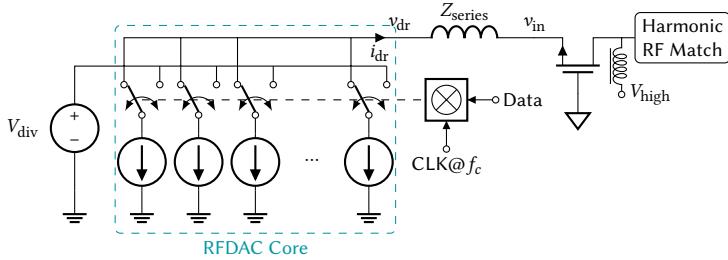

| 2.30 | A current steering RFDAC controlling a common gate stage. . . . .                                                                                                                              | 32 |

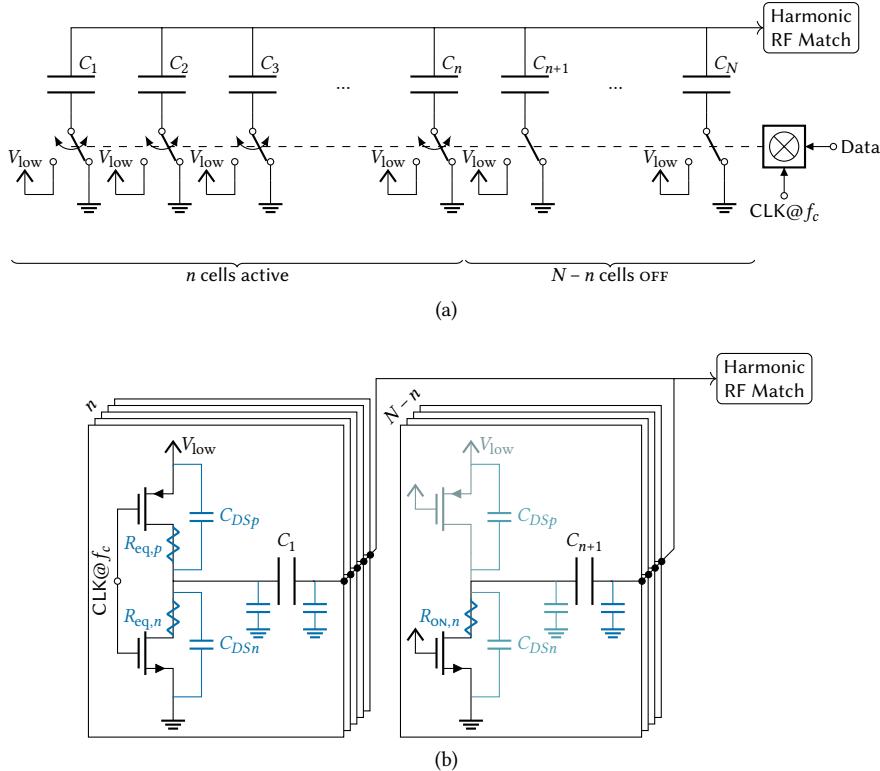

| 2.31 | A switched capacitor topology and its parasitics. . . . .                                                                                                                                      | 33 |

| 2.32 | Examples of common source topologies. . . . .                                                                                                                                                  | 34 |

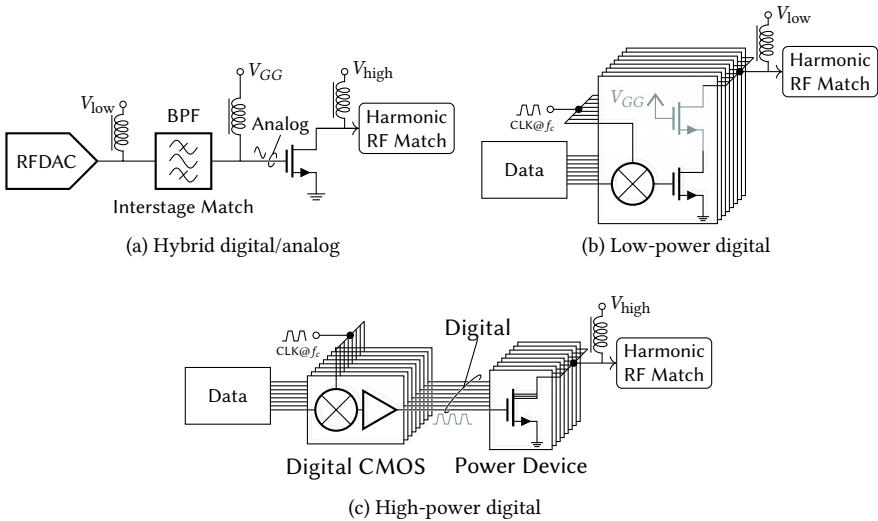

| 3.1  | High-power DTX schematic using a common source configuration. . . . .                                                                                                                          | 38 |

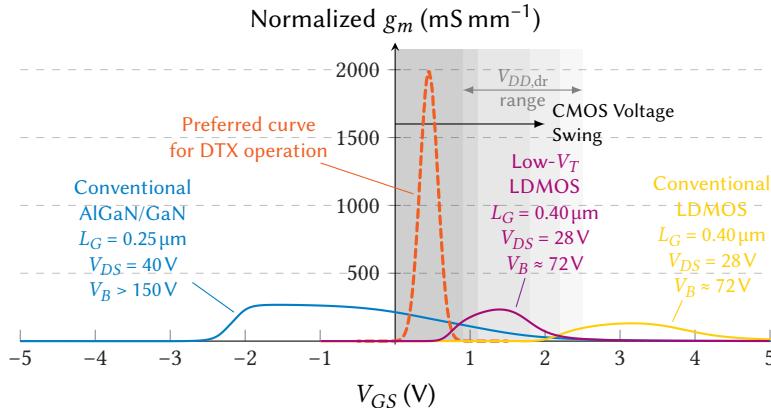

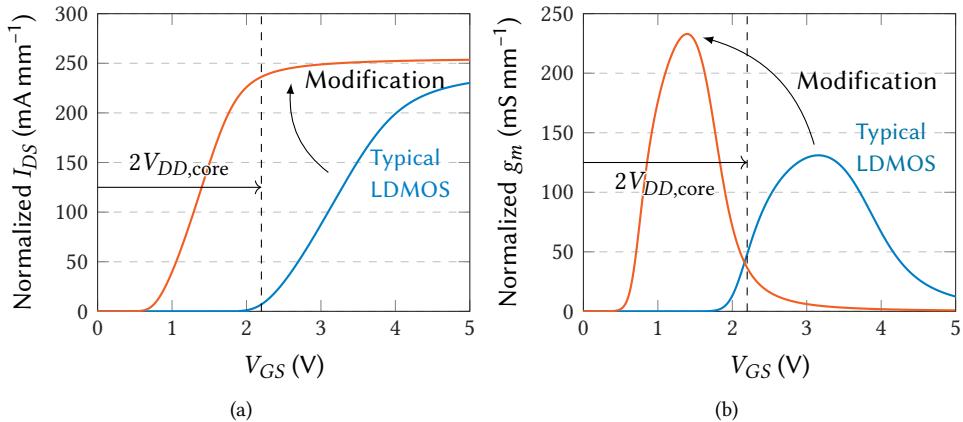

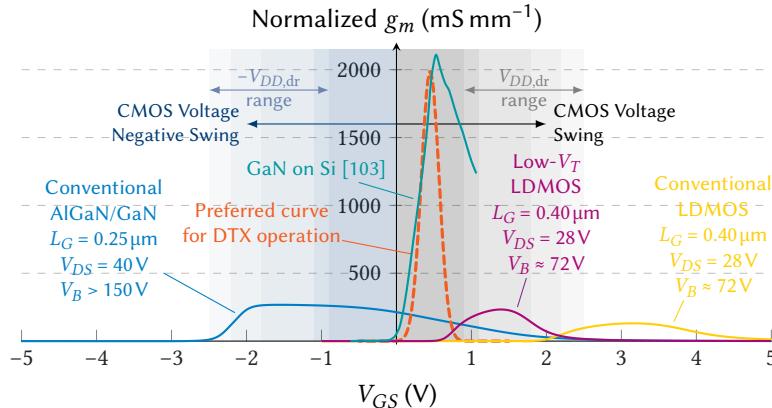

| 3.2  | Example $V_{GS}$ – $g_m$ curves for some RF power technologies, with the shaded area for possible $V_{DD,dr}$ ranges. . . . .                                                                  | 39 |

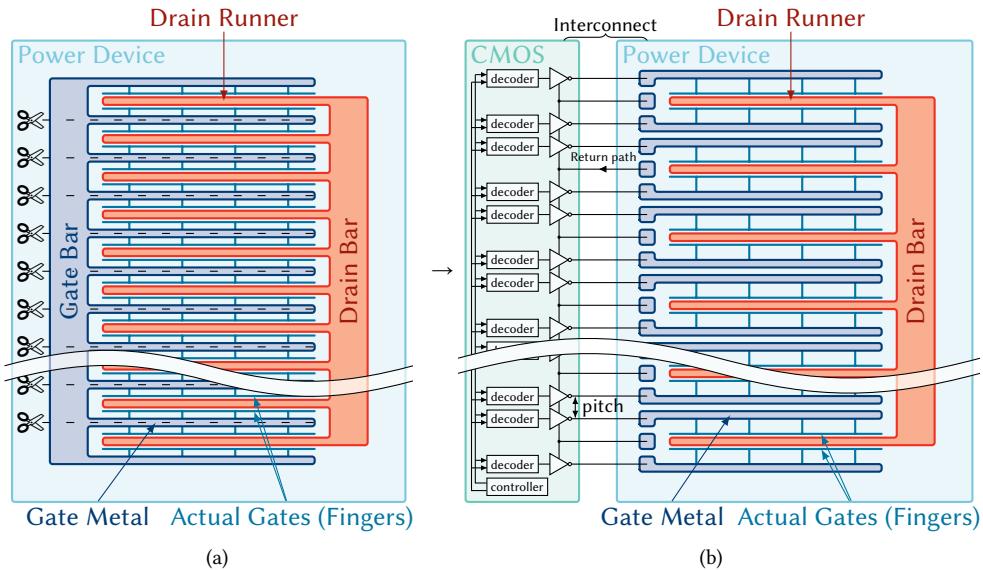

| 3.3  | Segmenting a device layout commonly used for analog applications into a layout suitable for DTX operation. . . . .                                                                             | 42 |

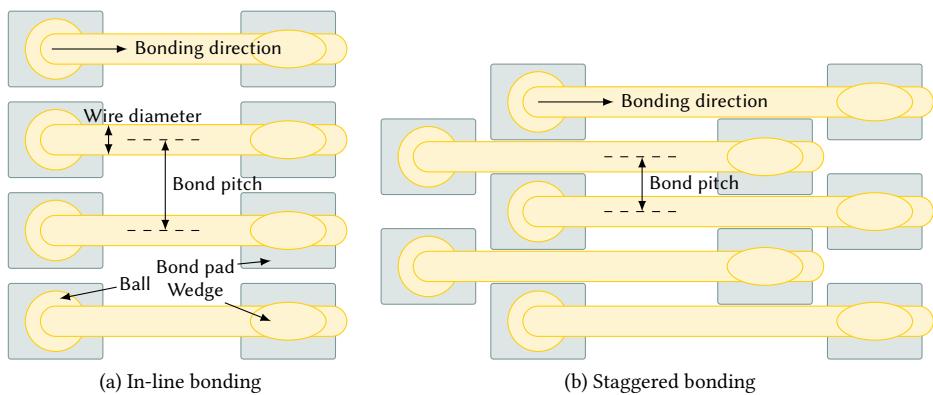

| 3.4  | Examples of ball–wedge bonded structures. . . . .                                                                                                                                              | 42 |

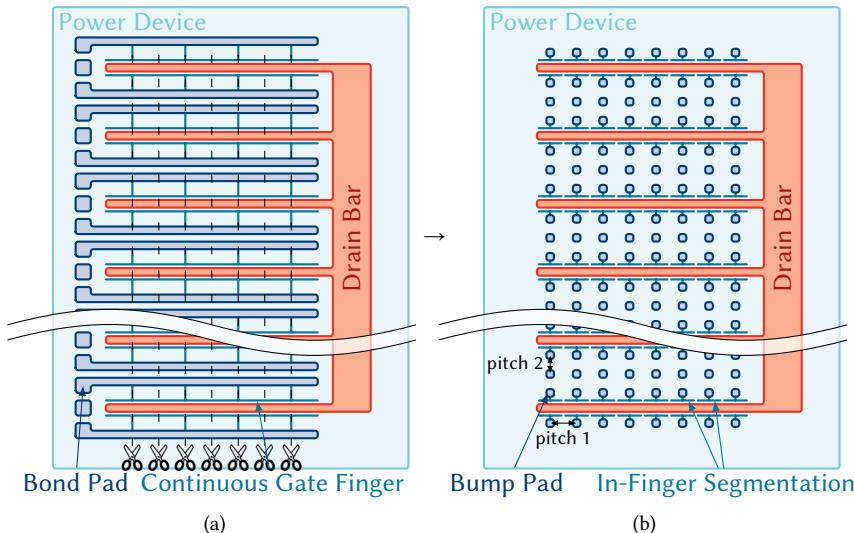

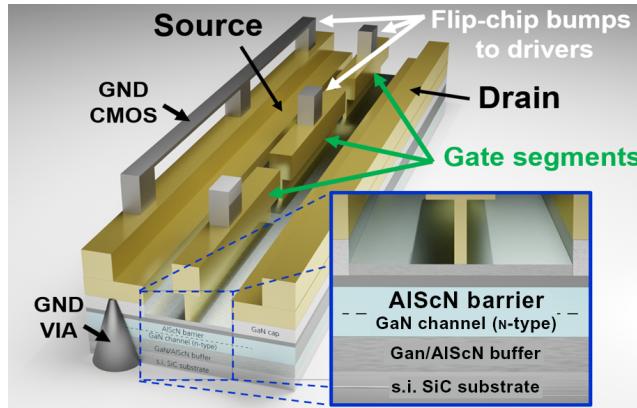

| 3.5  | In-finger segmentation of a power device layout suitable for flip-chip bonded DTXs. . . . .                                                                                                    | 43 |

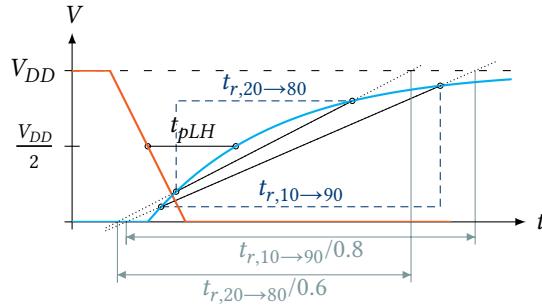

| 4.1  | Propagation delay and rise time definitions illustrated using a linear (inverting) $RC$ element. . . . .                                                                                       | 46 |

| 4.2  | The driver chain for a single output stage segment. . . . .                                                                                                                                    | 48 |

| 4.3  | Illustration of different possible definitions of ‘driver speed’. . . . .                                                                                                                      | 49 |

| 4.4  | Example simulation results of an inverter using TSMC 40 nm devices with RF models in core oxide. . . . .                                                                                       | 52 |

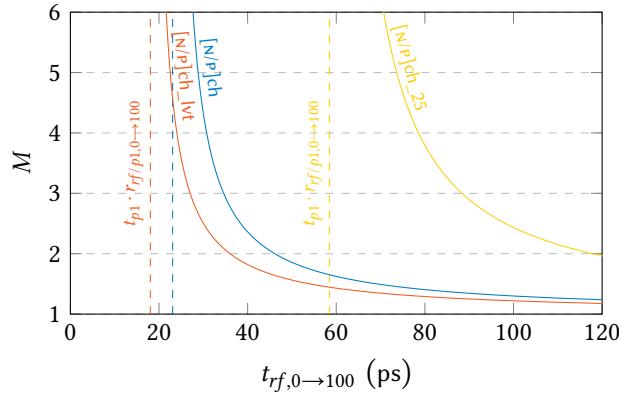

| 4.5  | Resulting $M$ -factor vs. rise/fall time (linearized to 0 % to 100 % based on 10 % to 90 %) using the model parameters from Table 4.1. . . . .                                                 | 53 |

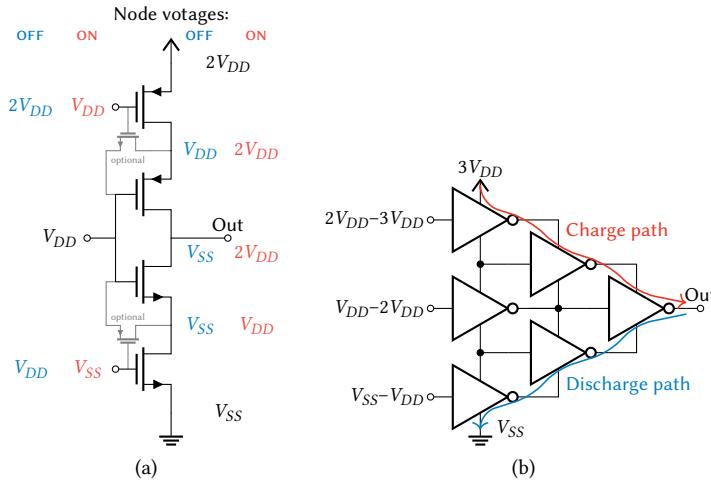

| 4.6  | The circuit of a stacked driver, which is then used as building block in a house-of-cards driver structure. . . . .                                                                            | 55 |

| 4.7  | Model of the stacked driver for analytically determining the power–speed-trade-off. . . . .                                                                                                    | 56 |

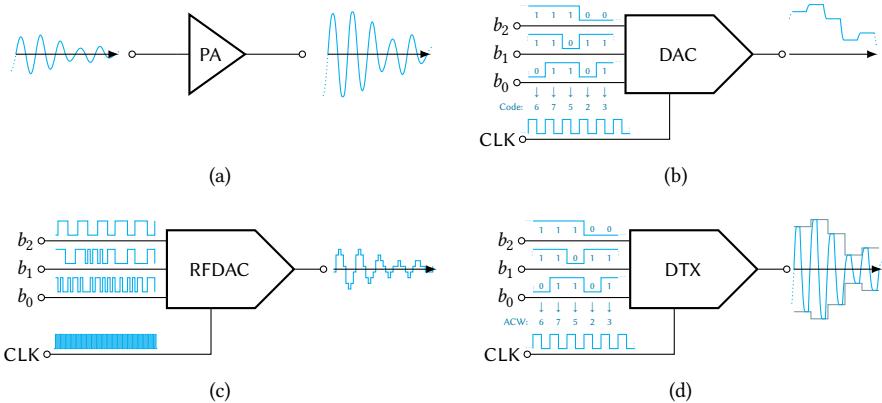

| 5.1  | Conceptual comparison of different systems’ inputs and outputs, highlighting both the digital-to-analog conversion as well as the modulating operation of DTXs. . . . .                        | 60 |

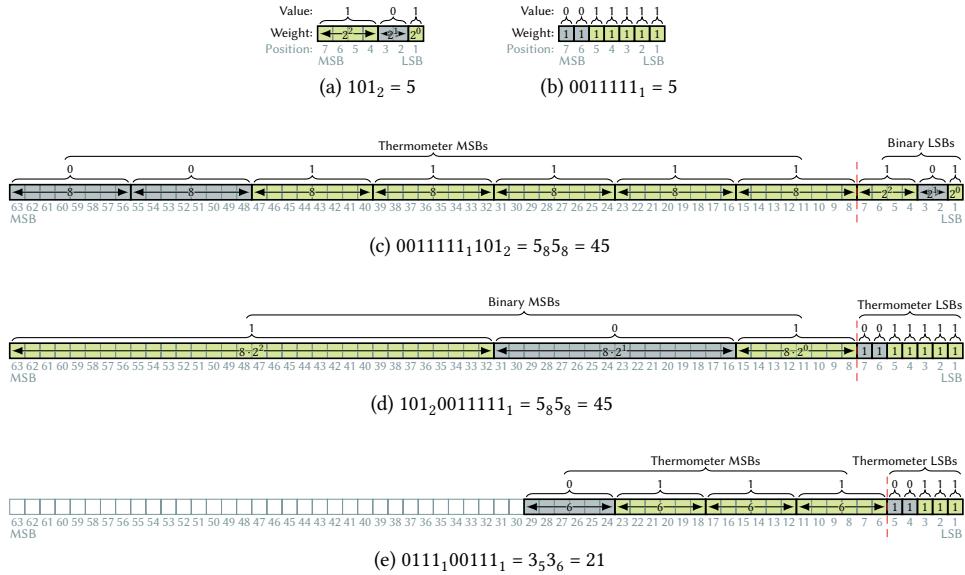

| 5.2  | Digital number representations. . . . .                                                                                                                                                        | 61 |

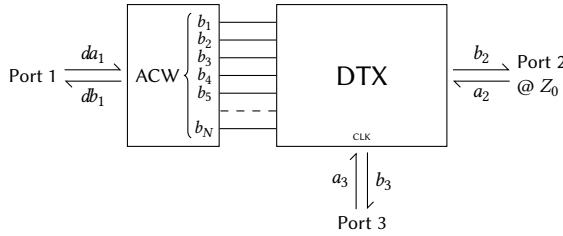

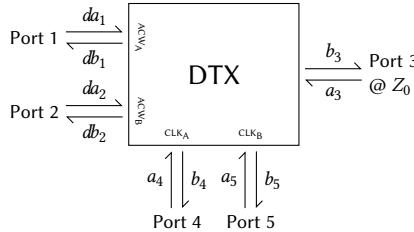

| 5.3  | The (3-port) black-box representation of a DTX. . . . .                                                                                                                                        | 62 |

| 5.4  | Simplified 2-port representation of a DTX at the fundamental frequency ( $f_c$ ). The phase reference(s) at $f_c$ are now included by making the baseband input $da_1$ complex-valued. . . . . | 64 |

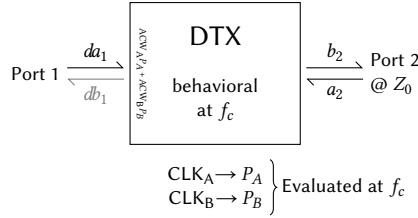

| 5.5  | Illustrating the sign/phase inequality when considering all harmonics of a square wave drain current. . . . .                                                                                  | 65 |

---

|      |                                                                                                                                                                                                                                                                                                                      |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

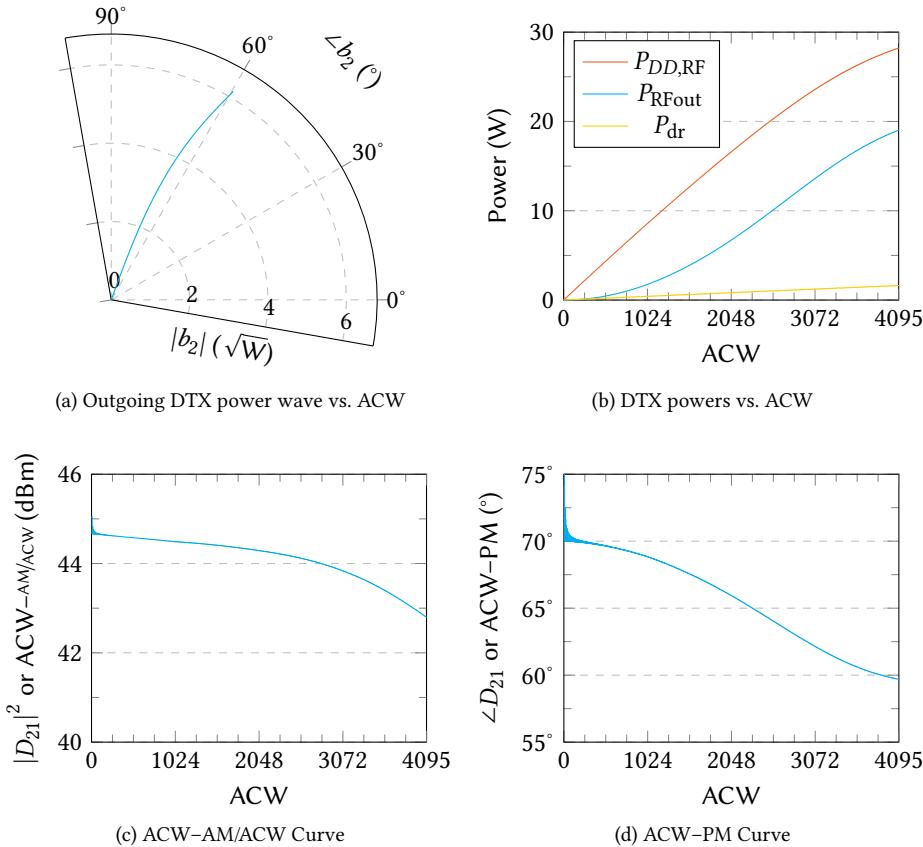

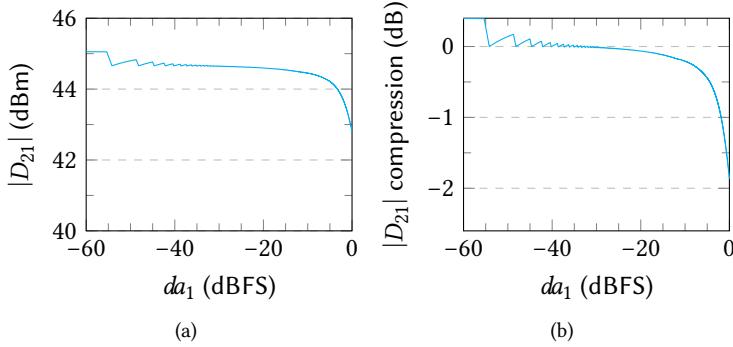

| 5.6  | Visualizations of the normalized digital forward transfer and its inputs. . . . .                                                                                                                                                                                                                                    | 67 |

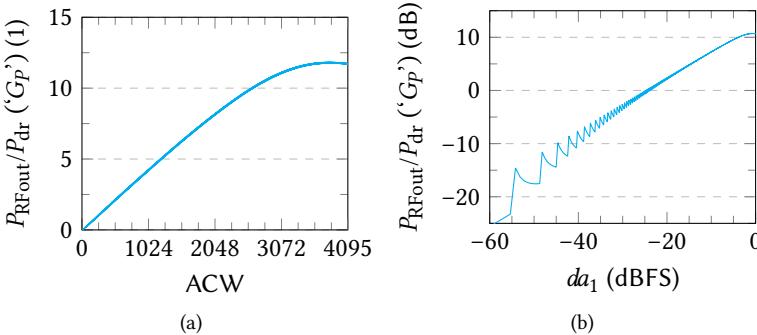

| 5.7  | Potentially useful alternative magnitude visualizations of the normalized digital forward transfer of Fig. 5.6c. . . . .                                                                                                                                                                                             | 68 |

| 5.8  | Example of RF output power over input switching loss in a DTX, which is the closest equivalent to analog power gain. It is not the transfer of a DTX, nor does it provide any linearity information. . . . .                                                                                                         | 68 |

| 5.9  | Schematic of a DTX simulation model using discrete segmented devices. . . . .                                                                                                                                                                                                                                        | 69 |

| 5.10 | Schematic of a simplified DTX simulation model using explicit current scaling and the simplified driver model using its equivalent switch resistance $R_{dr}$ . . . . .                                                                                                                                              | 70 |

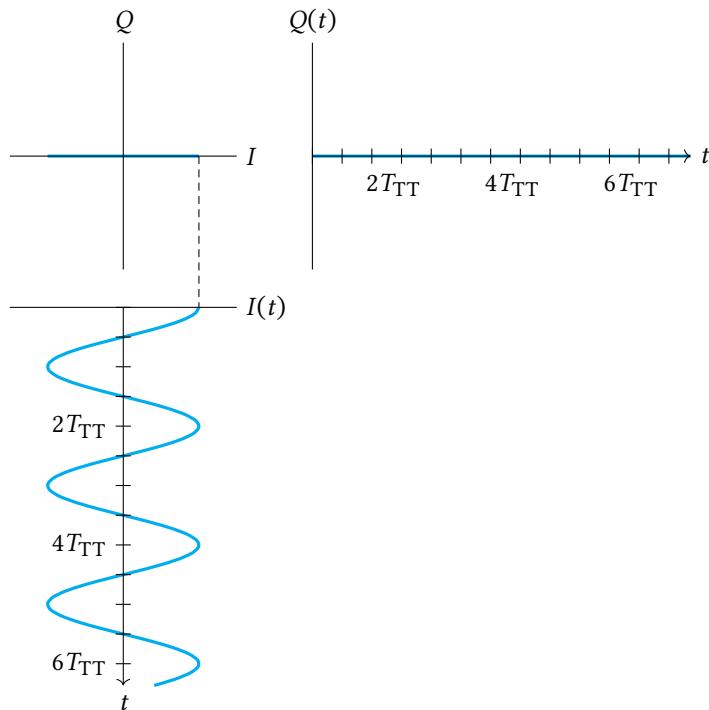

| 5.11 | Baseband $I$ and $Q$ representation of the digital input signal $da_1$ for a two-tone simulation. . . . .                                                                                                                                                                                                            | 72 |

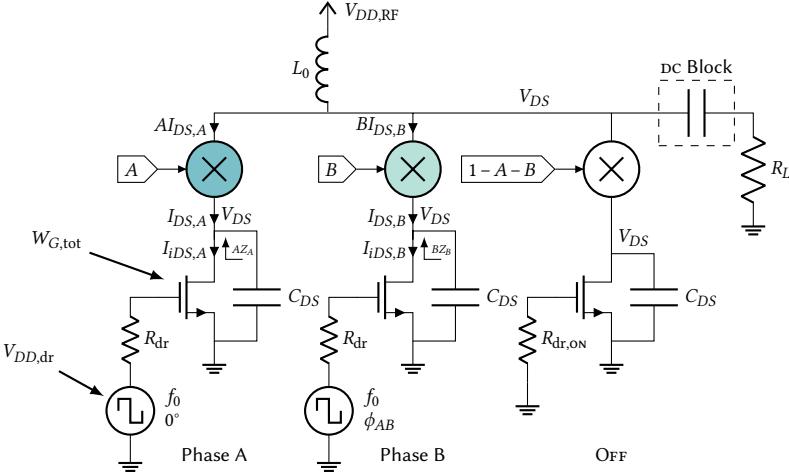

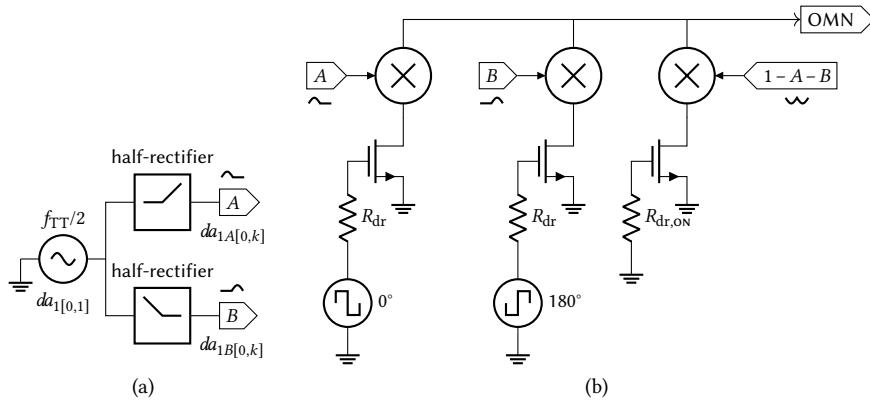

| 5.12 | Schematics for simulating a DTX with a two-tone input, suitable for harmonic balance simulation. The output matching network is provided in Fig. 5.14. . . . .                                                                                                                                                       | 73 |

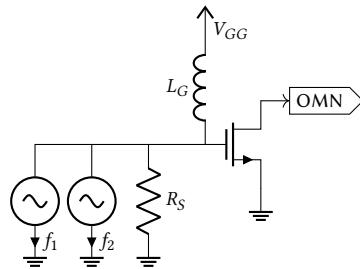

| 5.13 | Schematics for simulating an analog PA with a two-tone input, suitable for harmonic balance simulation. The output matching network is provided in Fig. 5.14. . . . .                                                                                                                                                | 73 |

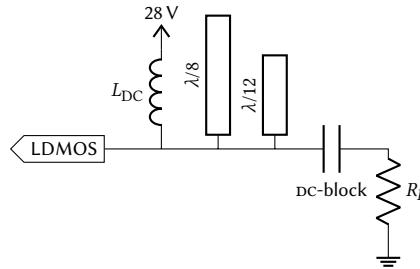

| 5.14 | The output matching network (OMN) used in the two-tone simulations, both for the analog PA and the DTX. . . . .                                                                                                                                                                                                      | 74 |

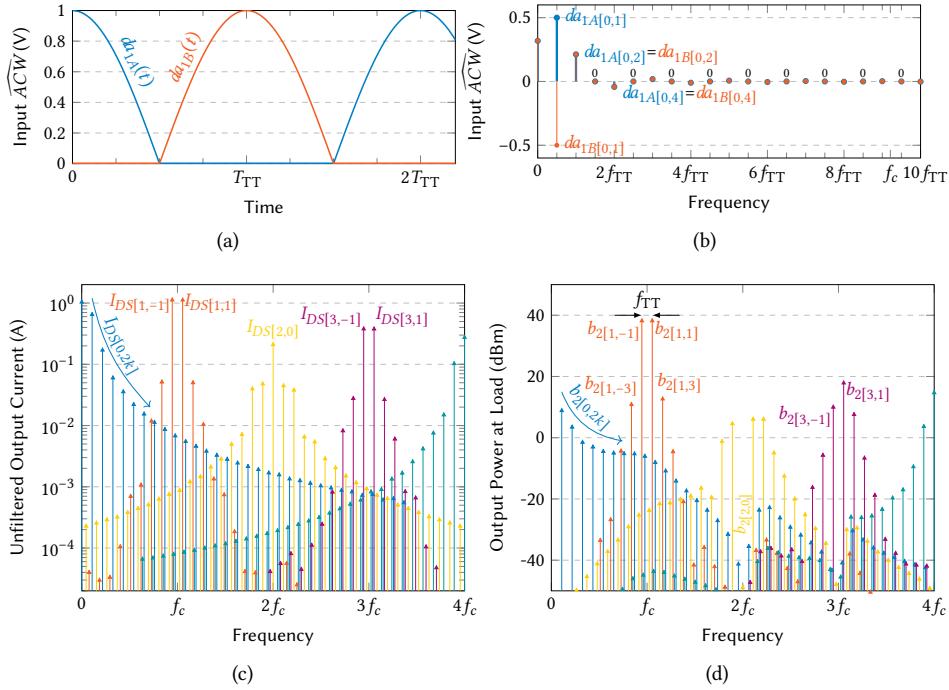

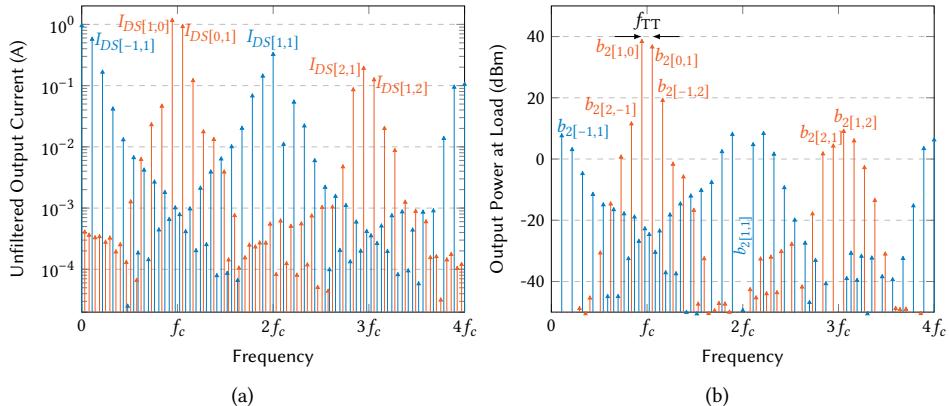

| 5.15 | Digital inputs and output spectra of a digital system using a large-signal two-tone excitation for realistic device models (without DPD), showing the frequency relations in a DTX. . . . .                                                                                                                          | 75 |

| 5.16 | Output spectra of an analog system using a large-signal two-tone excitation for a realistic device model (without DPD). . . . .                                                                                                                                                                                      | 75 |

| 6.1  | The power flows in a DTX. . . . .                                                                                                                                                                                                                                                                                    | 77 |

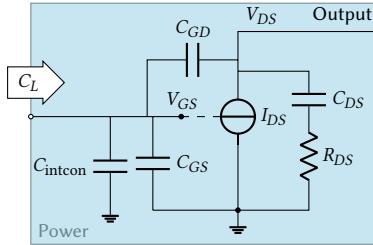

| 6.2  | Relevant capacitances for the power output stage. . . . .                                                                                                                                                                                                                                                            | 81 |

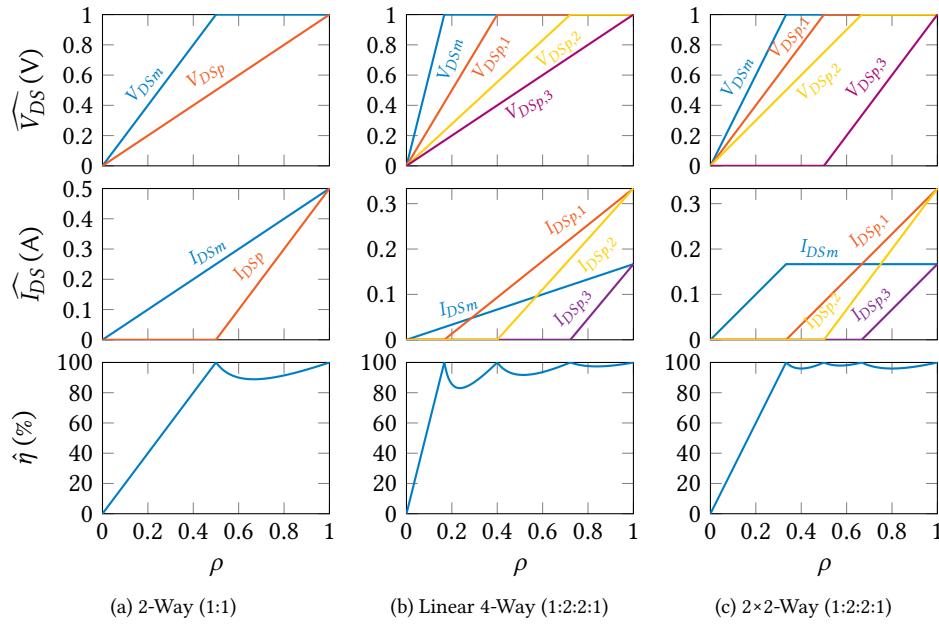

| 6.3  | Three examples of Doherty driving profiles. . . . .                                                                                                                                                                                                                                                                  | 85 |

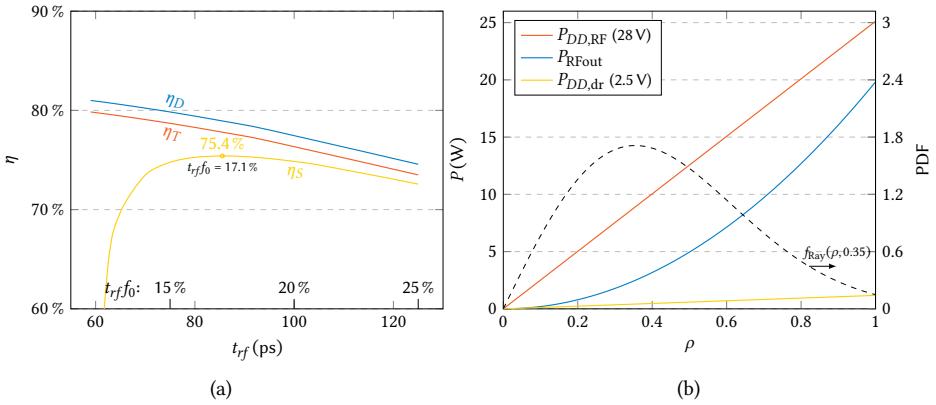

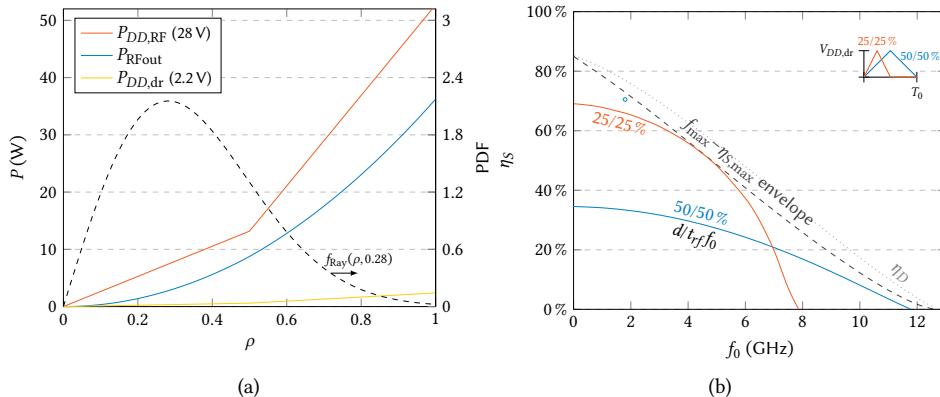

| 6.4  | Maximizing the DTX system efficiency by adjusting the driver's strength, and the resulting powers vs. amplitude $\rho$ . . . . .                                                                                                                                                                                     | 88 |

| 6.5  | Maximum system efficiency vs. DTX operating frequency for the provided technology parameters (thick oxide 40 nm CMOS + 400 nm LDMOS in a polar operation, from Table 6.2) when varying duty cycle and rise and fall times. . . . .                                                                                   | 89 |

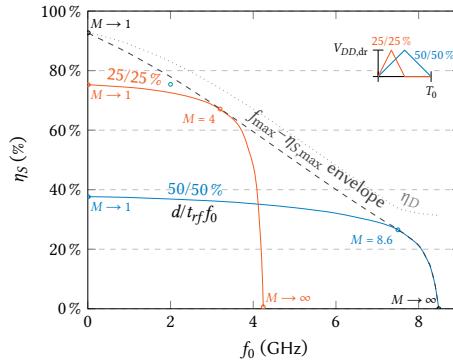

| 6.6  | The resulting powers vs. amplitude $\rho$ (using the model calculations from Table 6.5) and the maximum DTX system efficiency vs. operating frequency, for provided technology parameters (stacked core oxide lvt 40 nm CMOS + thin oxide 400 nm LDMOS in an 8-phase multi-phase operation, from Table 6.4). . . . . | 91 |

| 6.7  | Transfer of the 2-way Doherty DTX using the power model with drain losses. . . . .                                                                                                                                                                                                                                   | 91 |

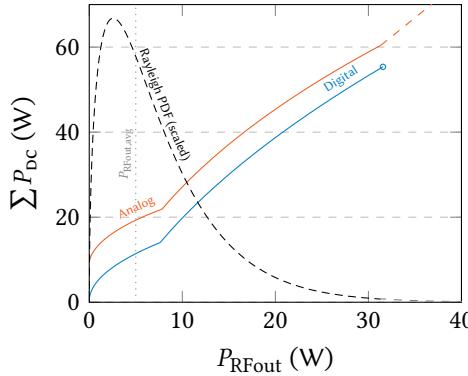

| 6.8  | Comparing the full dc power consumptions of an analog transmitter (case from Fig. 1.4b) to the 2-way Doherty DTX example with assumed matching and circulator loss. . . . .                                                                                                                                          | 92 |

|      |                                                                                                                                                                                                                                                                                |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

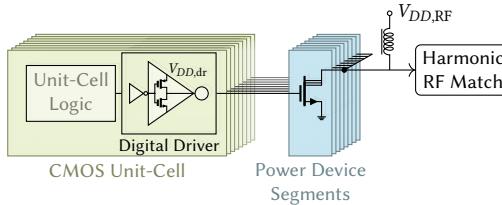

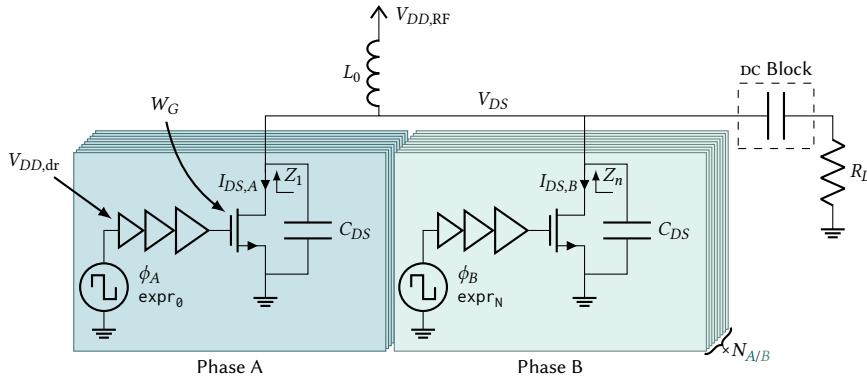

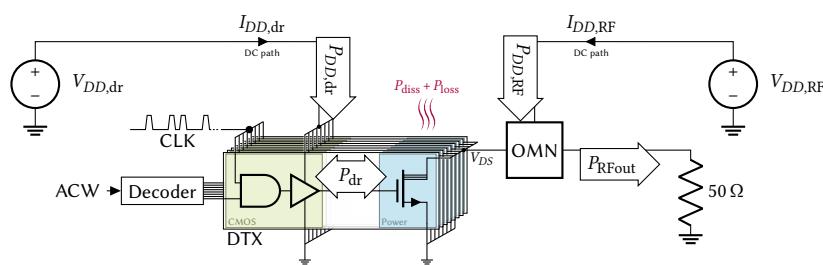

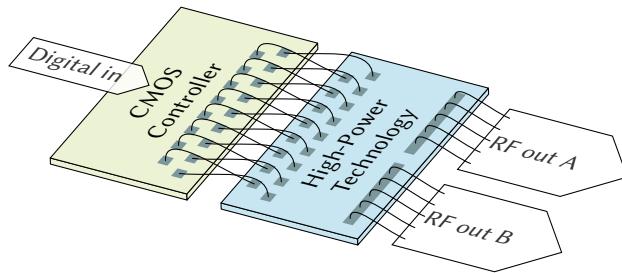

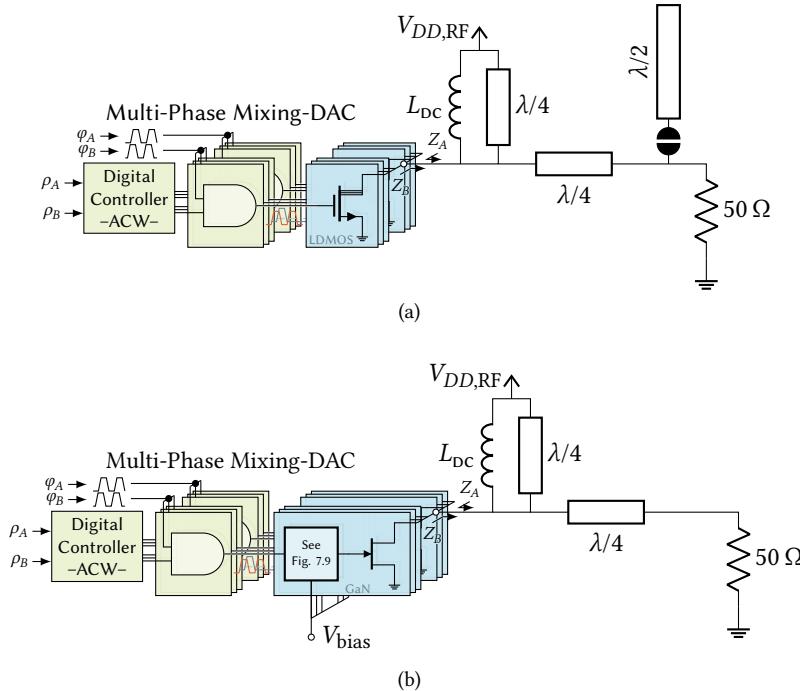

| 7.1  | Conceptual diagram of the proposed RF high-power mixing-DAC configuration with a dual TX line-up topology using a CMOS controller and a gate-segmented high-power output stage. . . . .                                                                                        | 96  |

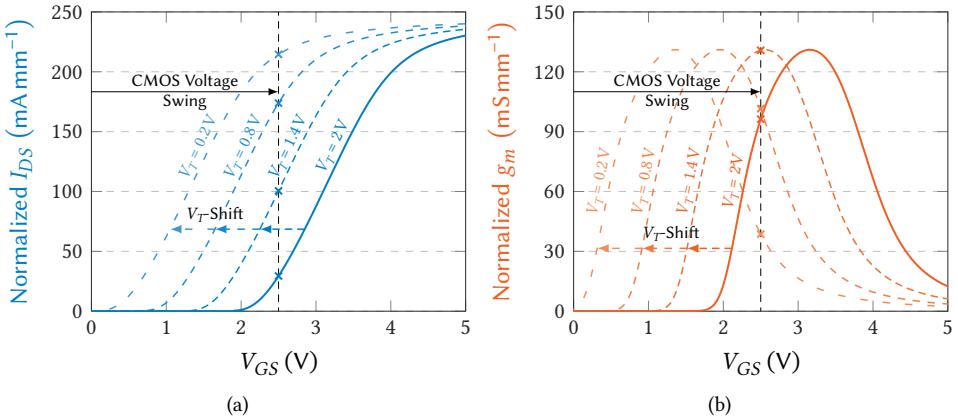

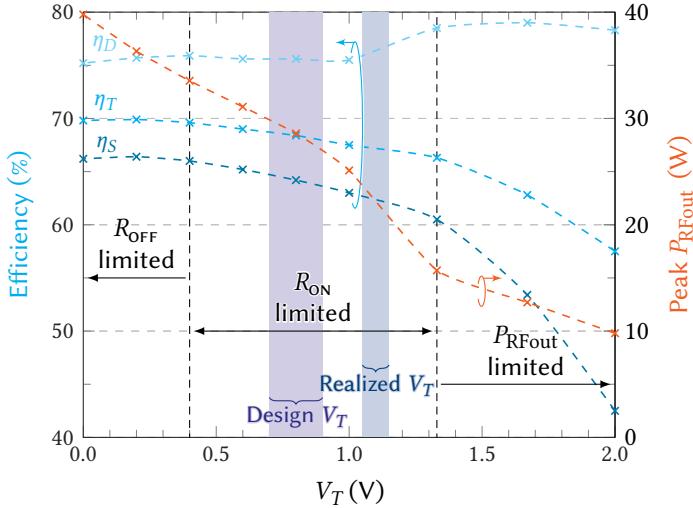

| 7.2  | $V_{GS}$ - $I_{DS}$ and $-g_m$ curves for the LDMOS process when $V_{DS} = 28$ V, while varying the $V_T$ . . . . .                                                                                                                                                            | 98  |

| 7.3  | Modeled drain ON/OFF resistance shown versus $V_{GS}$ for different values of $V_{DS}$ . . . . .                                                                                                                                                                               | 98  |

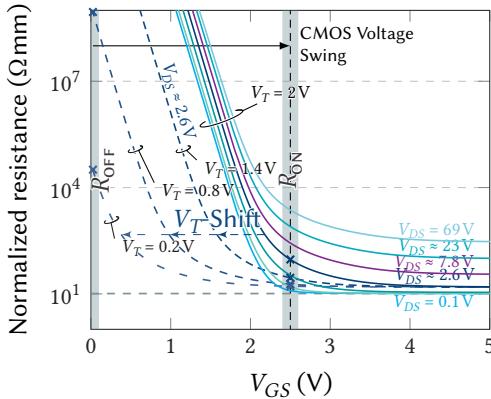

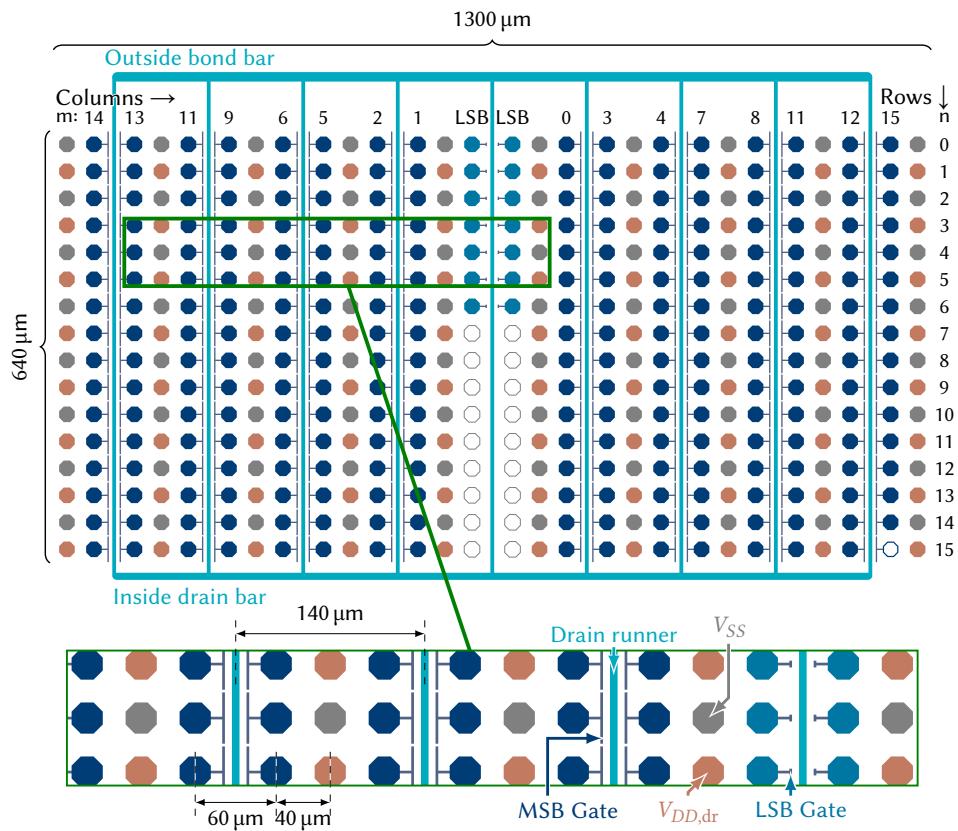

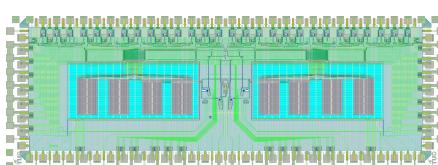

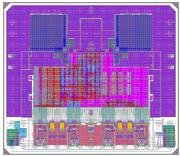

| 7.4  | Layouts of the segmented LDMOS power die. . . . .                                                                                                                                                                                                                              | 99  |

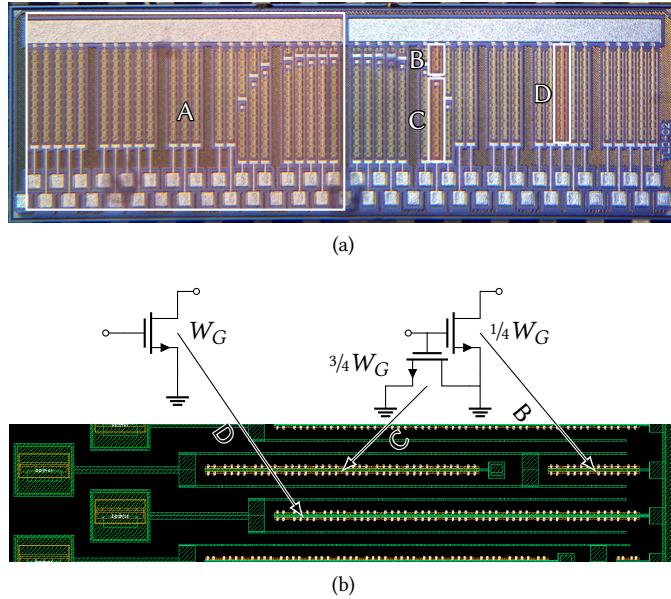

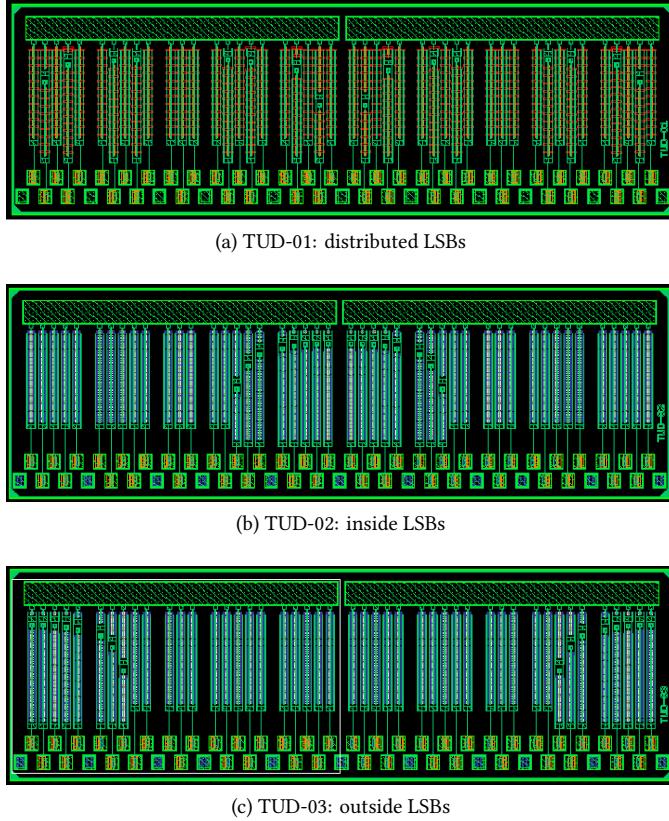

| 7.5  | Variations on the LDMOS layout, where the position of the LSBs is varied with respect to the MSBs. . . . .                                                                                                                                                                     | 100 |

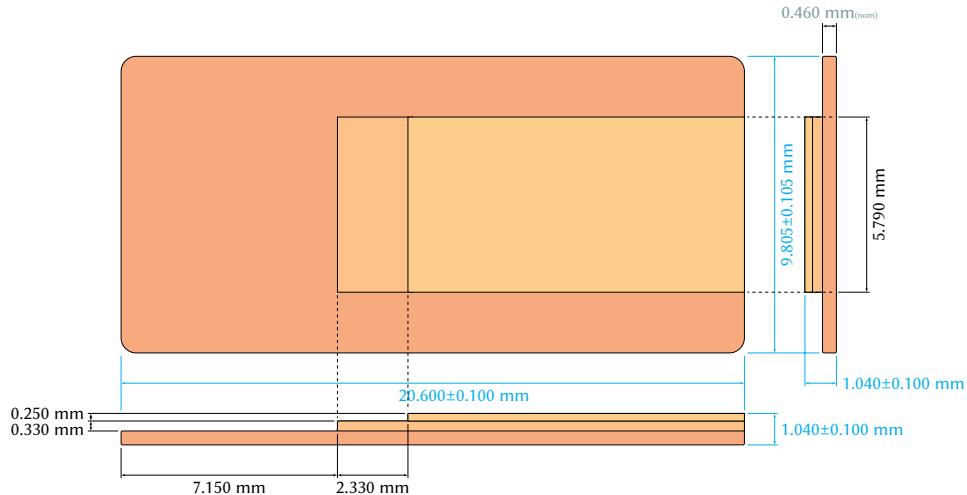

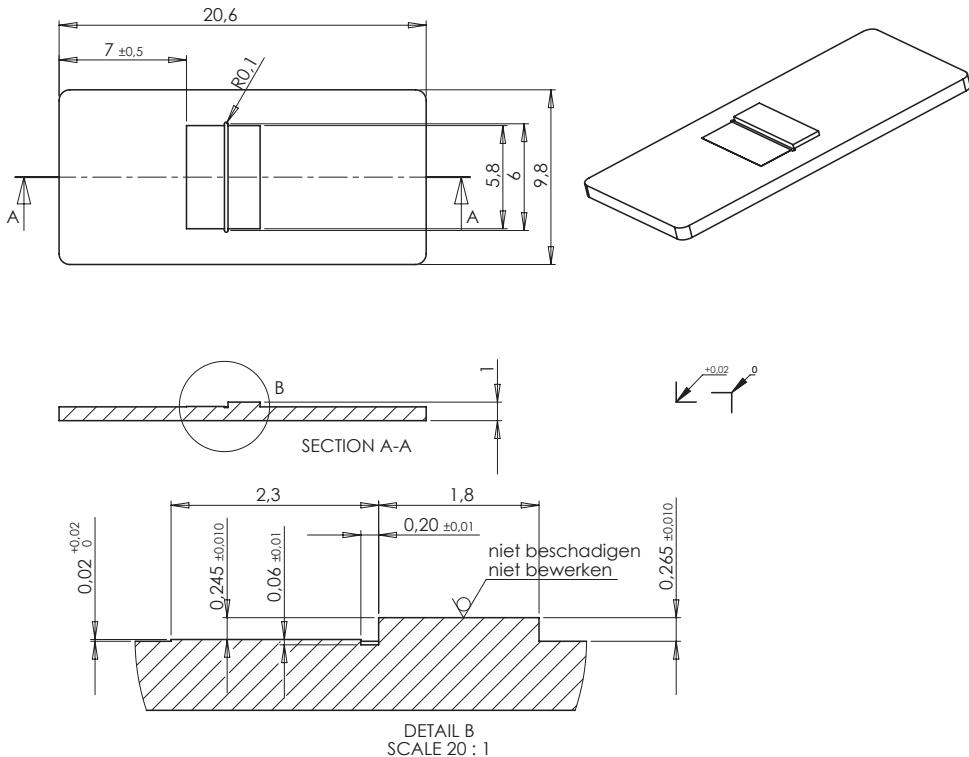

| 7.6  | The flange as used in a SOT1275-1 package, modified to accommodate different die thicknesses. . . . .                                                                                                                                                                          | 101 |

| 7.7  | Artist's impression of the assembly. . . . .                                                                                                                                                                                                                                   | 102 |

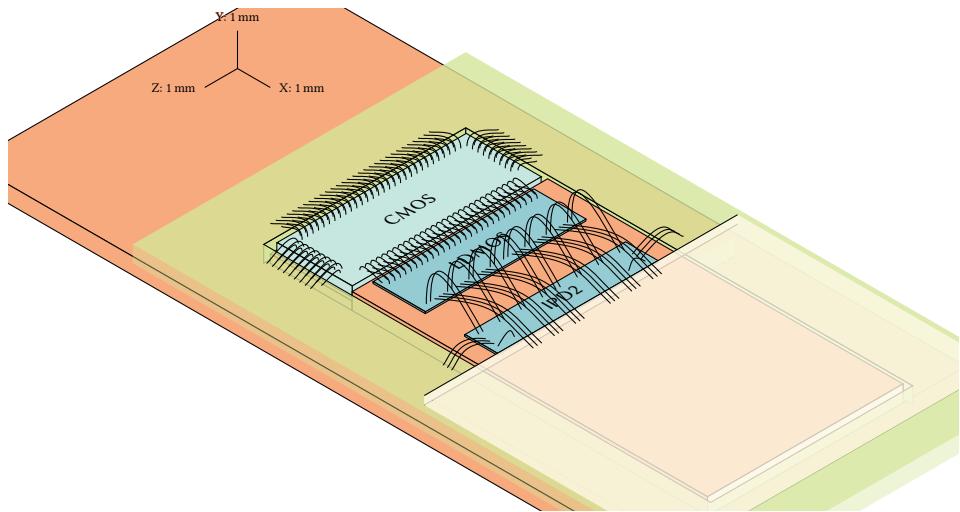

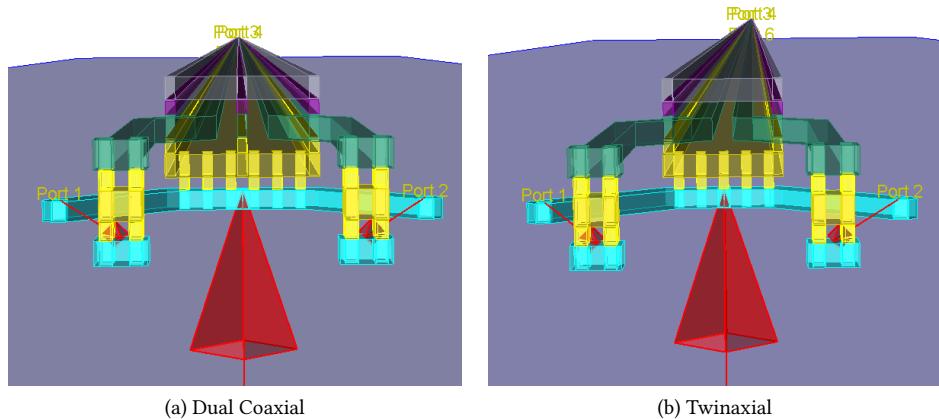

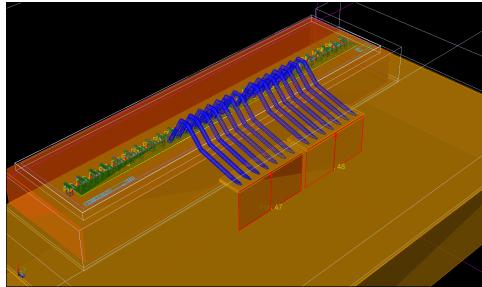

| 7.8  | 3D view of the FEM simulation setup of the bond wires between the CMOS controller and LDMOS power die, and the found self inductance and coupling values. . . . .                                                                                                              | 103 |

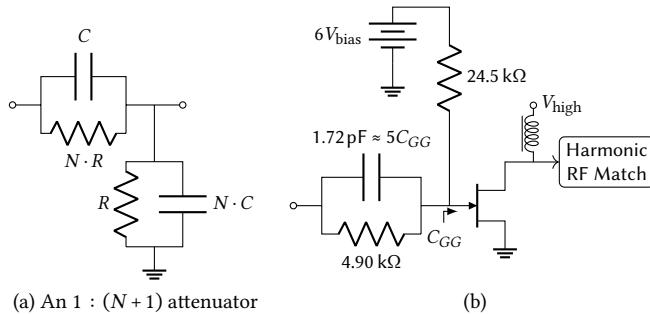

| 7.9  | GaN input match using an $RC$ all-pass. . . . .                                                                                                                                                                                                                                | 104 |

| 7.10 | Transient GaN input simulation setup, scaling the $RC$ input match such that no input DC drift occurs. . . . .                                                                                                                                                                 | 104 |

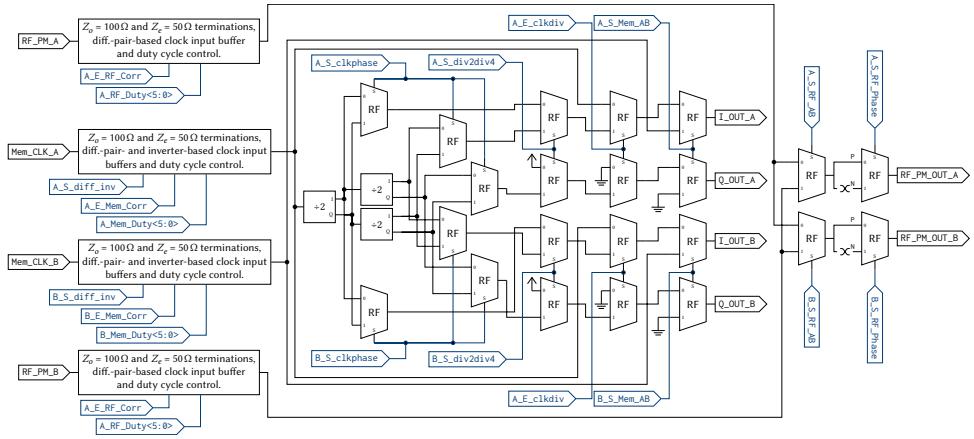

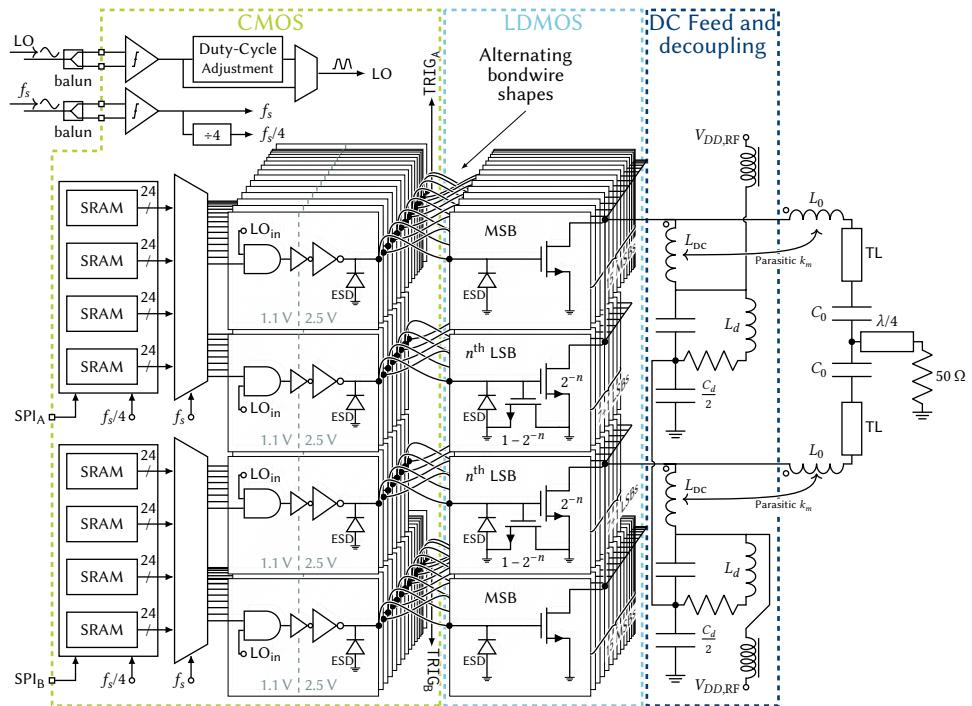

| 7.11 | Block diagram of the CMOS controller, showing the dual line-up. . . . .                                                                                                                                                                                                        | 105 |

| 7.12 | Physical input/output (IO) positioning of the CMOS controller layout. The controller's dimensions are fixed from the IO requirements. . . . .                                                                                                                                  | 109 |

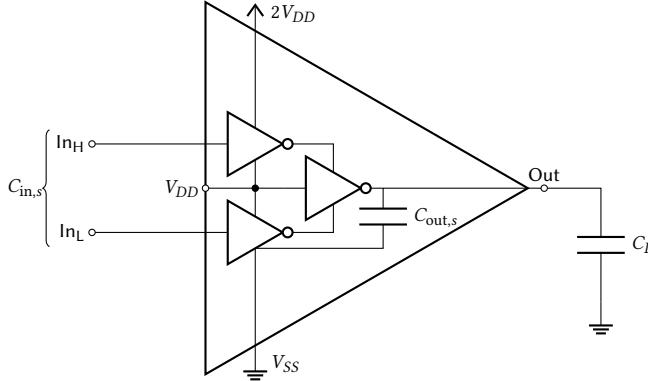

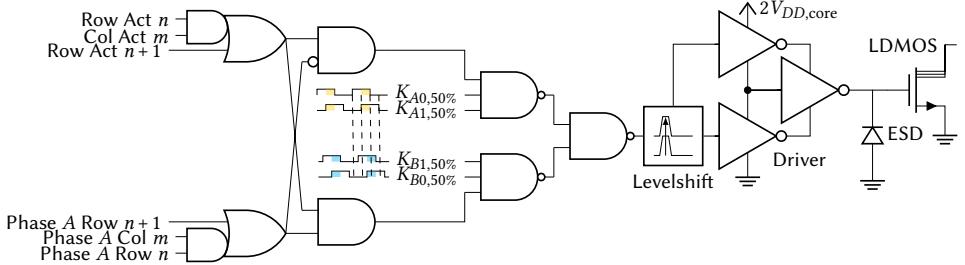

| 7.13 | Level shifter and tapered buffer chain. . . . .                                                                                                                                                                                                                                | 110 |

| 7.14 | Simplified unit cell logic (buffering and delay equalization removed), connected to the differential input of the levelshifter (Fig. 7.13). . . . .                                                                                                                            | 111 |

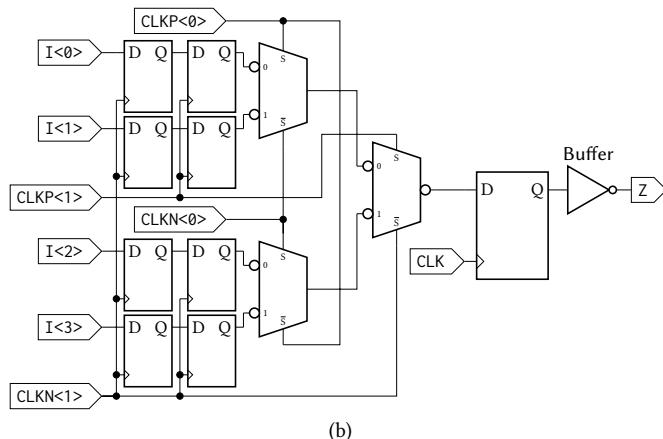

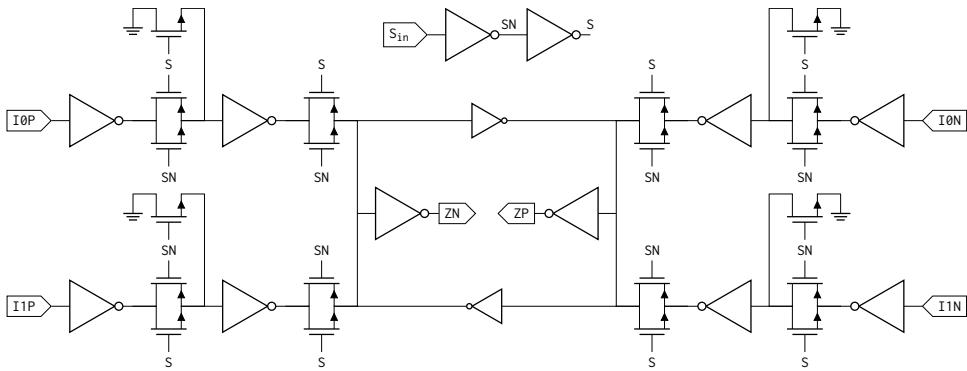

| 7.15 | Schematics used to achieve 4:1 serializing or time-multiplexing operation of the memory data: (a) the 2-bit Gray counter with additional retiming to prevent skewing of the 4 resulting clock phases; (b) the serializer schematic, implemented using pass-gate muxes. . . . . | 113 |

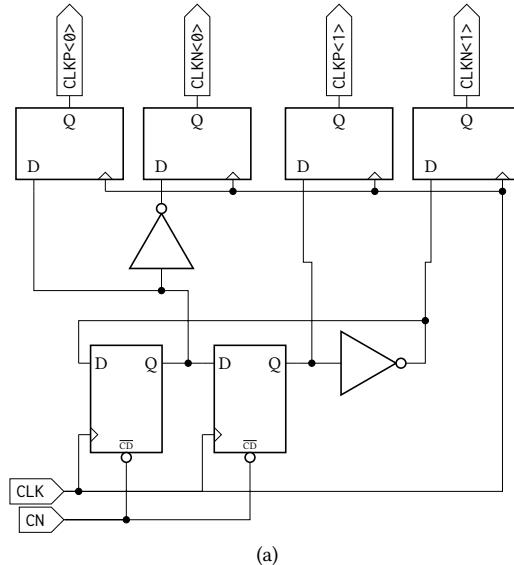

| 7.16 | The clock input routing and division schematic. . . . .                                                                                                                                                                                                                        | 114 |

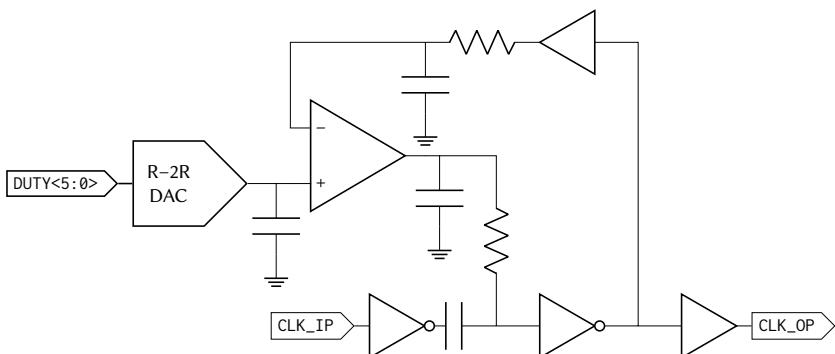

| 7.17 | Duty cycle loop. . . . .                                                                                                                                                                                                                                                       | 114 |

| 7.18 | Schematic of the multiplexer used for the RF clocks. Additional pull-down transistors have been added to improve isolation between the two clocks. .                                                                                                                           | 115 |

| 7.19 | 3D EM views of two possible shielded RF clock line implementations using the lower metal layers of the TSMC 40 nm CMOS technology. . . . .                                                                                                                                     | 116 |

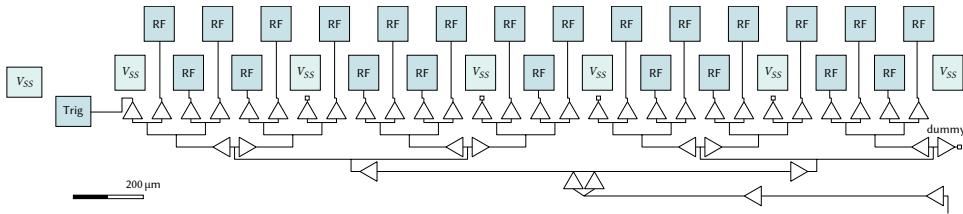

| 7.20 | The binary clock tree of bank A, where the $x$ -dimension is to scale. . . . .                                                                                                                                                                                                 | 117 |

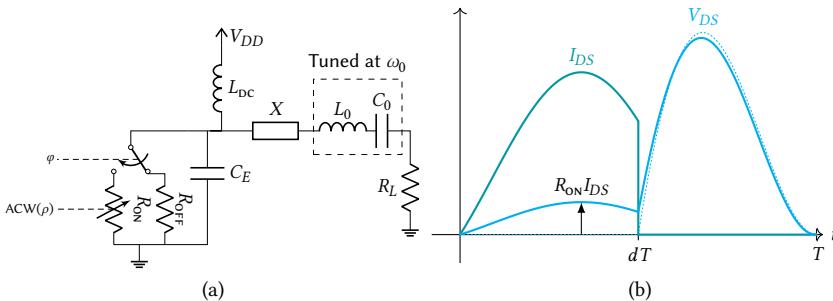

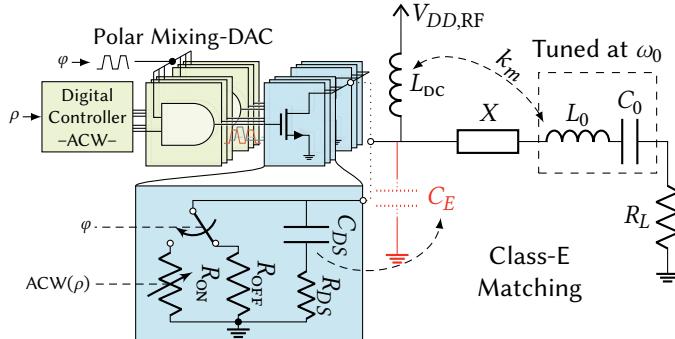

| 7.21 | Digital polar class-E DTX configuration using output stage segmentation. The digitally controlled segments can be modeled as a single switch with an ACW-controlled $R_{ON}$ . . . . .                                                                                         | 119 |

| 7.22 | Theoretical full power DTX performances for the optimized class-BE design sets for varying values of the $V_T$ of the applied LDMOS technology. . . . .                                                                                                                        | 120 |

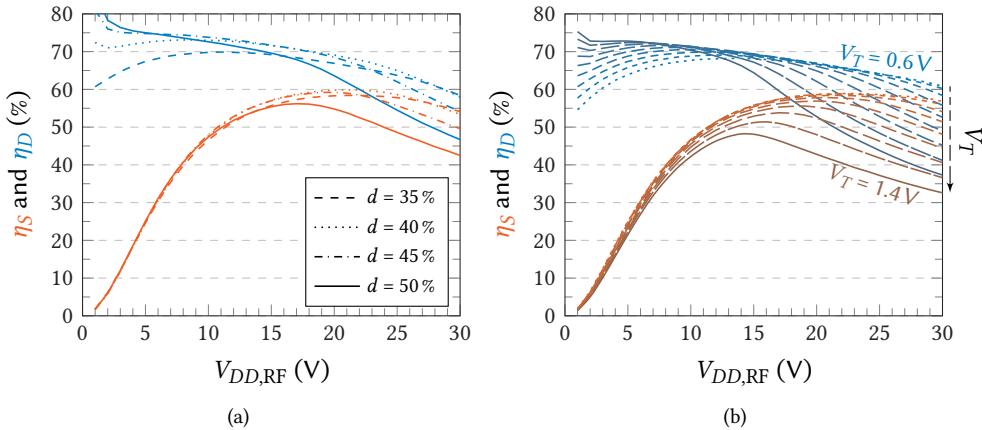

| 7.23 | System and drain efficiencies versus $V_{DD,RF}$ for: (a) post-production duty cycle adjustment assuming a realized $V_T$ of 0.8 V; (b) potential realized $V_T$ -shifts assuming a duty cycle of 50 %. . . . .                                                                | 121 |

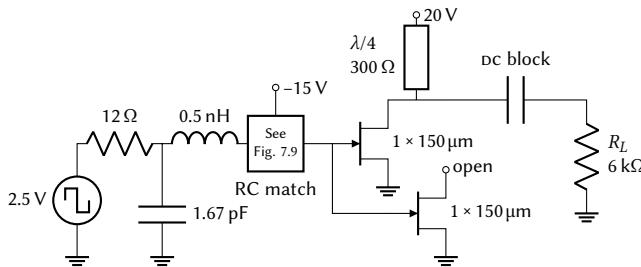

| 7.24 | Functional schematic of the power-DTX configured for polar operation with the single-ended 2.1 GHz class-BE output matching. . . . .                                                                                                                                           | 122 |

|      |                                                                                                                                                                                                                                                                                                                                          |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

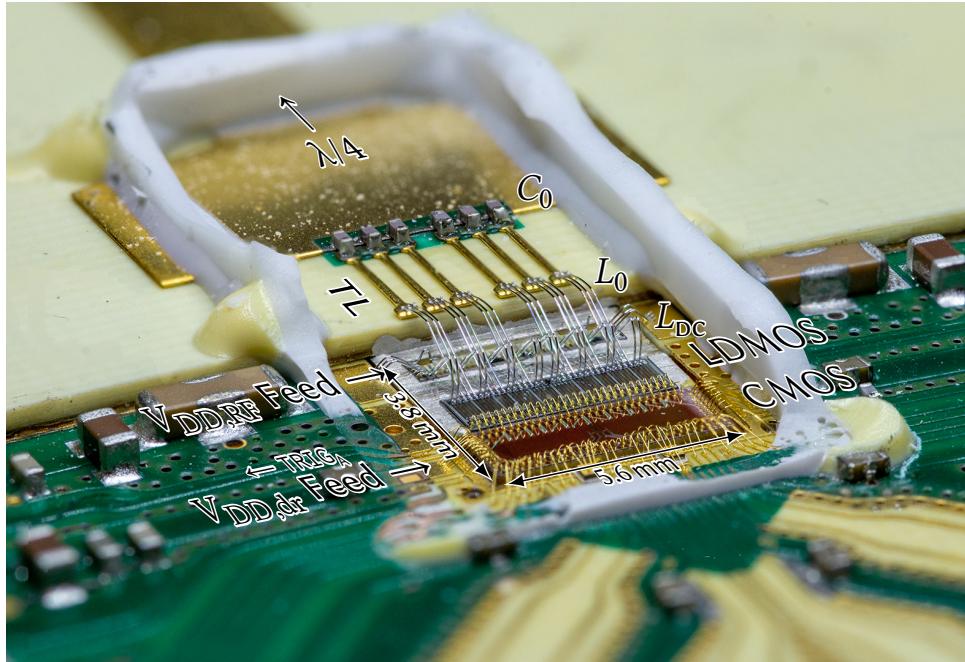

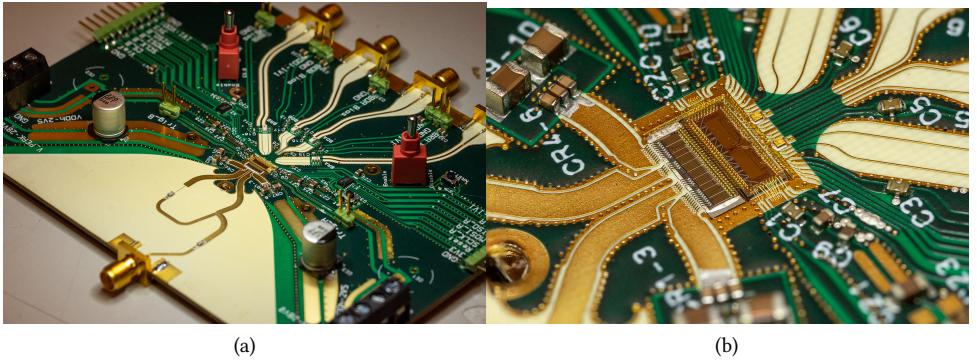

| 7.25 | Photograph of the power-DTX with the ceramic cap removed. . . . .                                                                                                                                                                                                                                                                        | 123 |

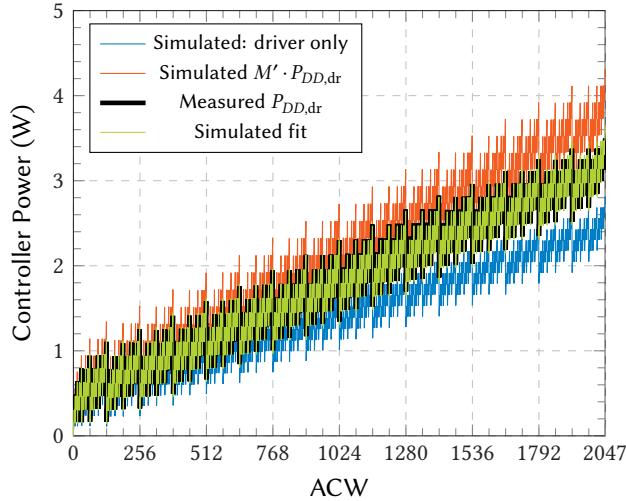

| 7.26 | Simulated drive power including $C_{dr,01}$ , multiplied by $M' = 1.532$ to provide the total power consumption of the driving drive chain, which is compared to its actual measured values. . . . .                                                                                                                                     | 124 |

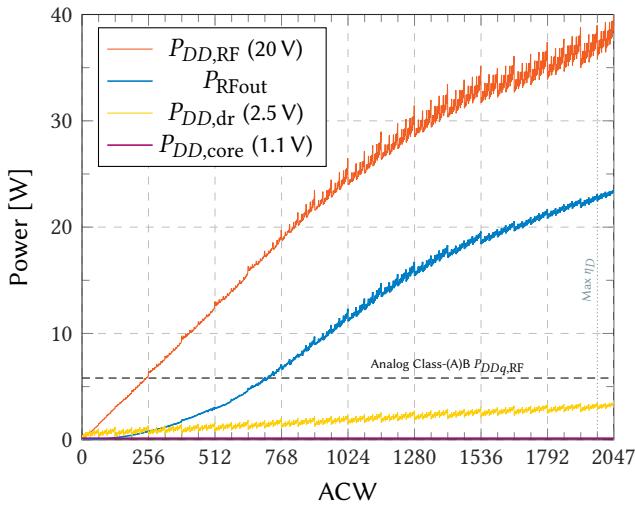

| 7.27 | Measurement of the fully digital-TX line-up ( $W_{G,tot} = 41.472$ mm, 11-bit) in pulsed CW operation at 2.1 GHz, using 15 % duty-cycling to lower thermal effects, and $V_{DD,RF} = 20$ V. . . . .                                                                                                                                      | 124 |

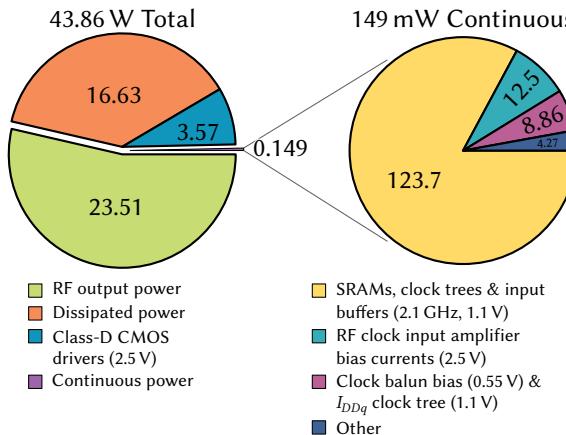

| 7.28 | The dynamic and continuous DC power consumption breakdown in the implemented DTX at peak RF output power conditions (ACW = 2047). . . . .                                                                                                                                                                                                | 125 |

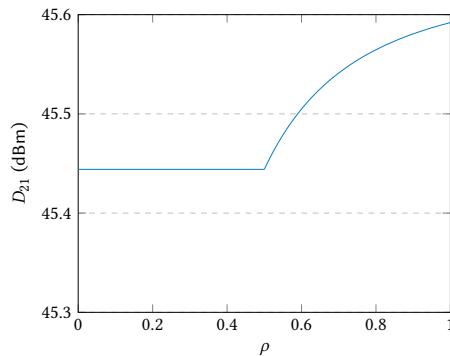

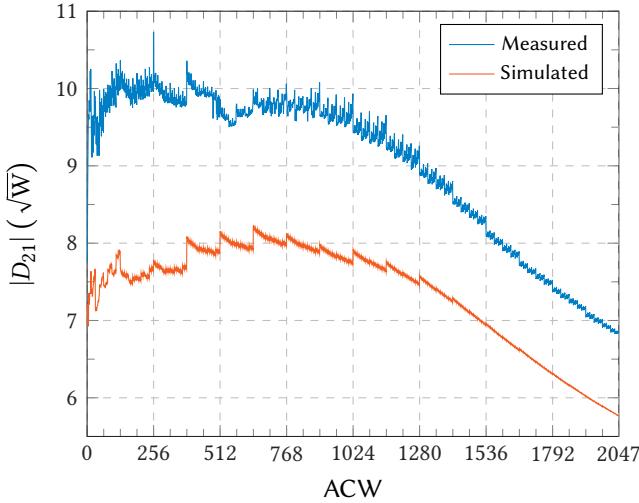

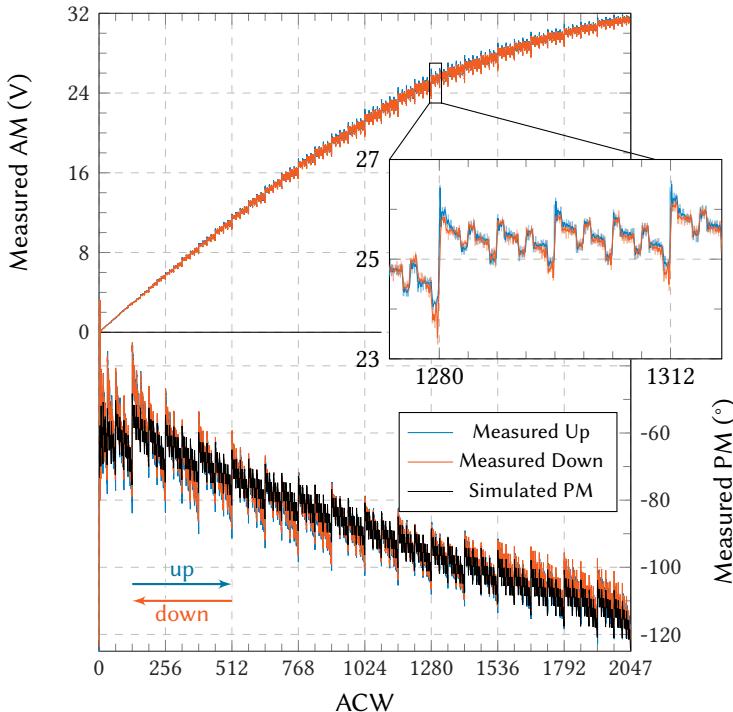

| 7.29 | Simulated and measured static normalized digital transfers ( $D_{21}$ ) compared. Both clearly show the effect of the hybrid unary and binary-weighted implementation of the segments, especially when switching to a unary weighted segment (every 128 ACWs). . . . .                                                                   | 126 |

| 7.30 | Measured dynamic response for a linear ACW triangle-shaped envelope signal, centered around 2.1 GHz with the $f_s$ and VSA analysis bandwidth set both to 525 MHz, leading to a cycle time of 62.4 $\mu$ s. . . . .                                                                                                                      | 127 |

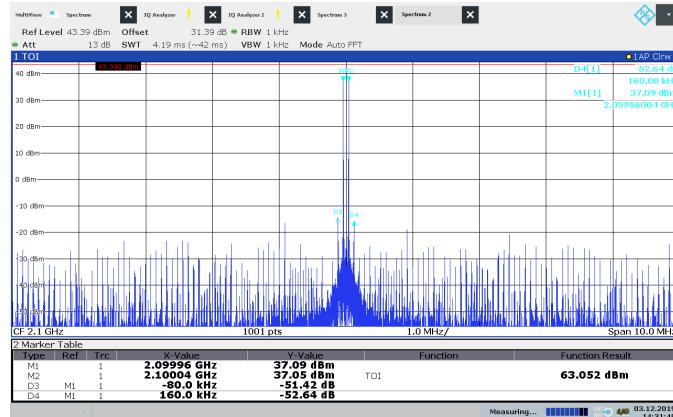

| 7.31 | The measured spectrum of the 80 kHz two-tone signal, showing an $IM_3 \leq -51.4$ dBc after static LUT calibration, only using the unary segments with pulse density modulation. . . . .                                                                                                                                                 | 128 |

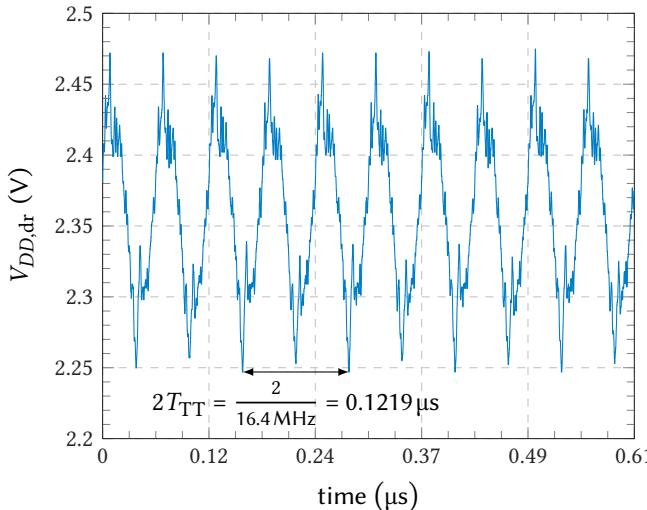

| 7.32 | Measured $V_{DD,dr}$ through the TRIG pins using a 2.1 GHz two-tone test with 16.4 MHz tone spacing. . . . .                                                                                                                                                                                                                             | 129 |

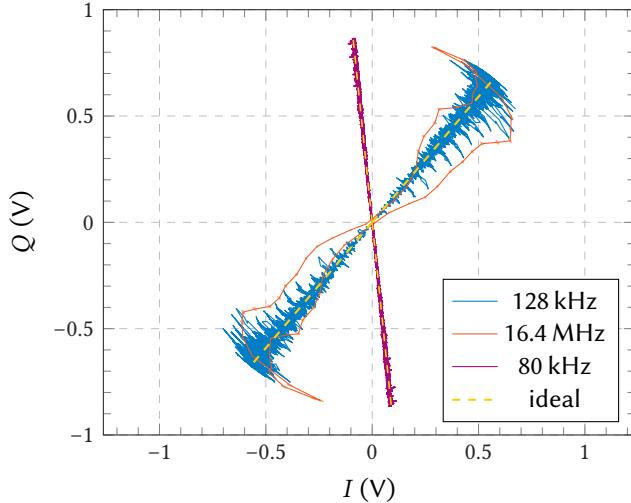

| 7.33 | Measurements using a 2.1 GHz two-tone test with varying tone spacing: down-converted IQ-constellations, after static DPD, showing hysteresis/memory-effects for 16.4 MHz tone spacing. . . . .                                                                                                                                           | 130 |

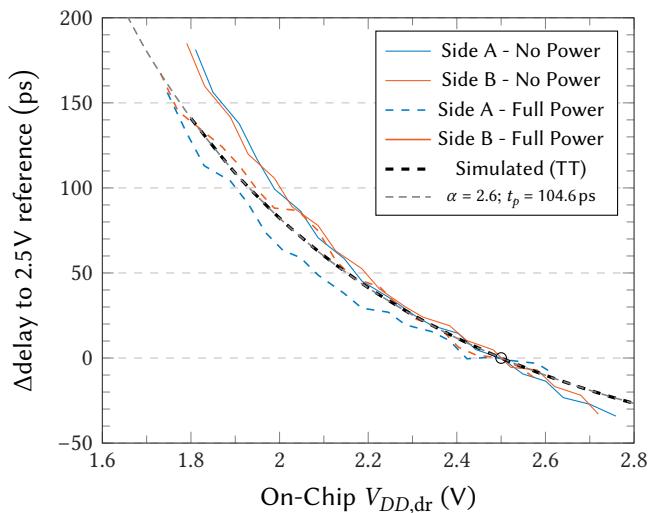

| 7.34 | Change in propagation delay of the CMOS tapered buffer chain compared to the $V_{DD,dr} = 2.5$ V reference case versus the measured $V_{DD,dr}$ which includes the IR-drop. . . . .                                                                                                                                                      | 130 |

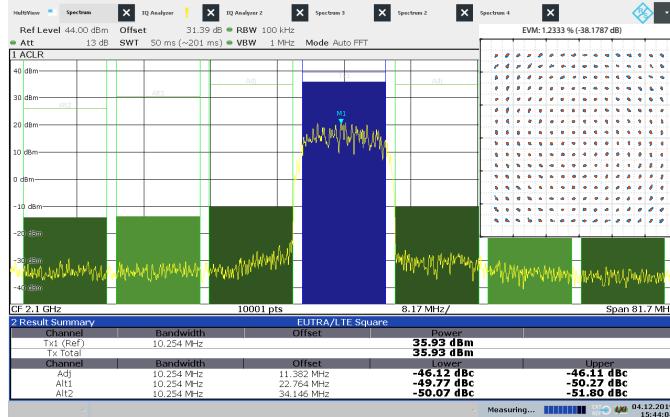

| 7.35 | The measured spectrum and constellation of the 10 MHz 256-QAM signal, showing an $ACLR = -46.1$ dBc and $EVM = 1.2\%$ after static DPD. . . . .                                                                                                                                                                                          | 131 |

| 7.36 | Class-B matching networks targeting digital current-mode operation at 1 GHz, implemented as a resonator for the fundamental with a parallel $\lambda/4$ short circuited stub as even order harmonic short and a series $\lambda/4$ transformer for matching the resistive load. . . . .                                                  | 135 |

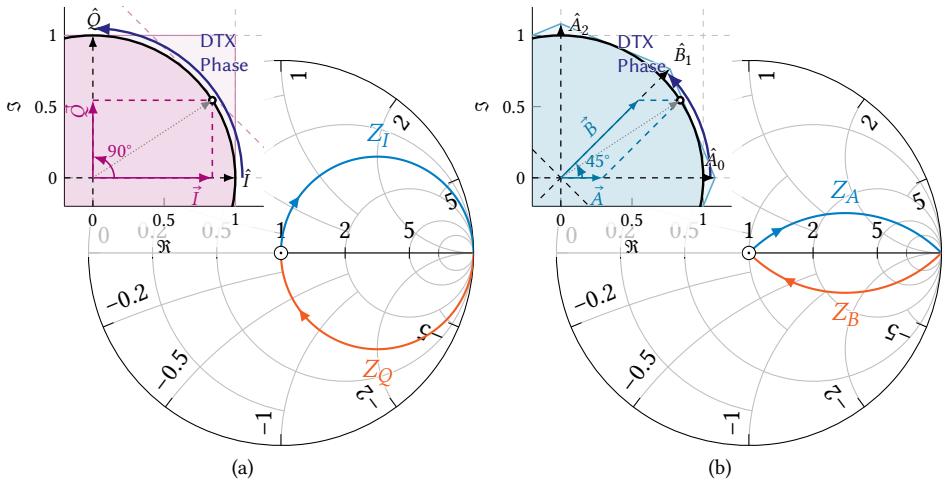

| 7.37 | Impedances seen by the intrinsic devices in (a) signed-Cartesian system and (b) 8-phase multi-phase systems. The device interaction leads to reactive loading, thus lowering drain efficiency over modulation phase. . . . .                                                                                                             | 136 |

| 7.38 | A 3D view of the bond wires from the GaN die to the PCB, for use in FEM simulation. . . . .                                                                                                                                                                                                                                              | 136 |

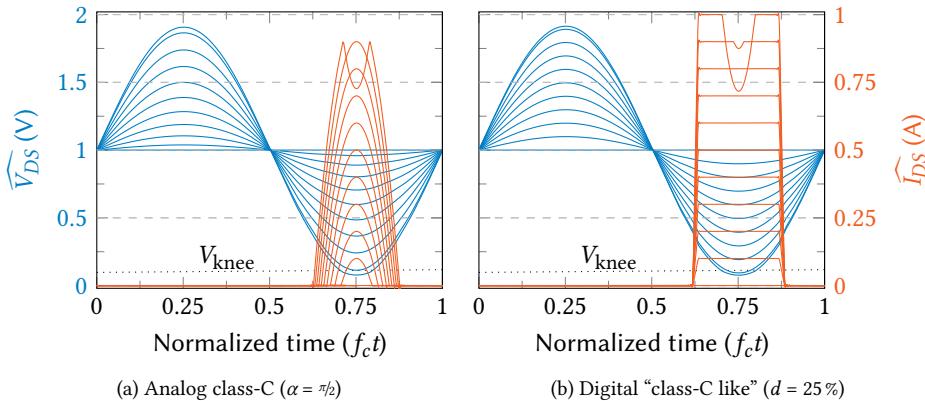

| 7.39 | Time domain waveforms for varying input quantity, all normalized. The analog case shows an expanding conduction angle with increasing activation, while in digital operation the duty cycle remains constant. . . . .                                                                                                                    | 137 |

| 7.40 | Transfers of analog and digital transconductance/current-scaling classes, using normalized input and output quantities ( $I_{DS,max} = 1$ A, $R_L = R_{L,opt}$ , and $P_{norm} = 0.5$ W). Solid lines show class-C operation ( $\pi/2$ conduction angle/25 % duty cycle), clearly indicating gain expansion in the analog cases. . . . . | 138 |

|      |                                                                                                                                                                                                                                                                                                                                    |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.41 | Photograph of the bits-in–RF-out, high-power DTX featuring the segmented LDMOS output stage with the class-B output match (Fig. 7.36a). To the left is the $\lambda/4$ stub for even order harmonic termination, in the middle the $\lambda/4$ transformer, and to the right the short-circuited inductive stub. . . . .           | 139 |

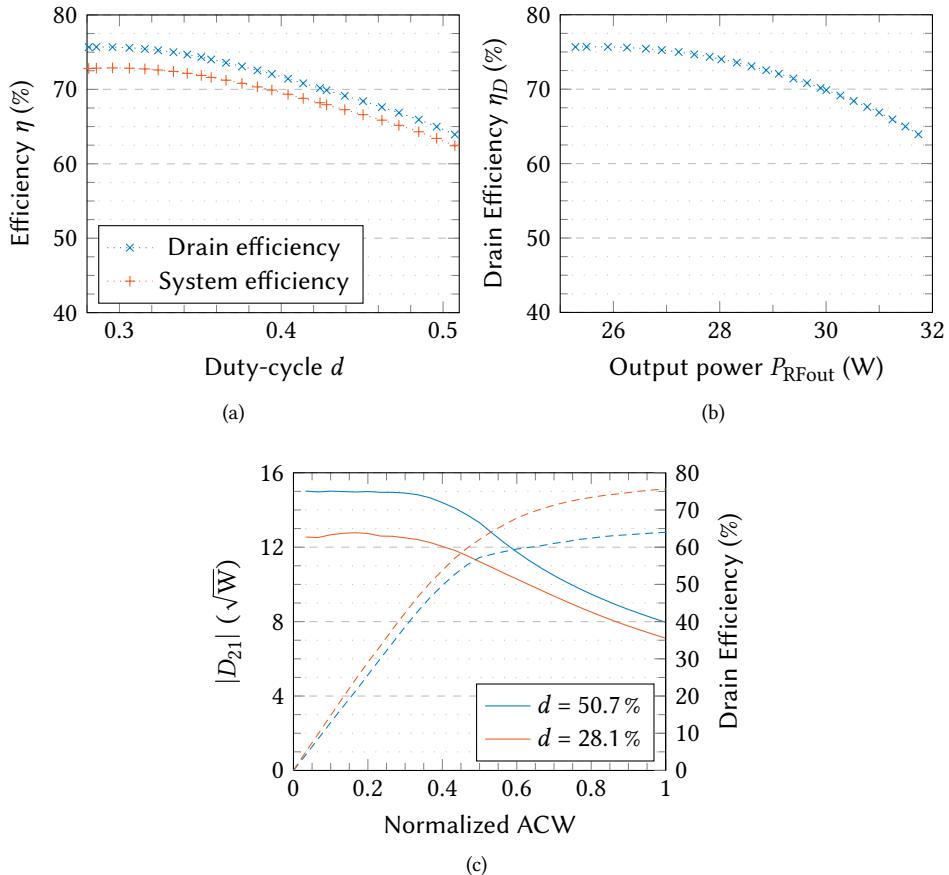

| 7.42 | Pulsed envelope RF measurements (10 % envelope duty cycle) using digital “class-C like” operation at 930 MHz with segmented LDMOS power devices: efficiencies and transfer. . . . .                                                                                                                                                | 140 |

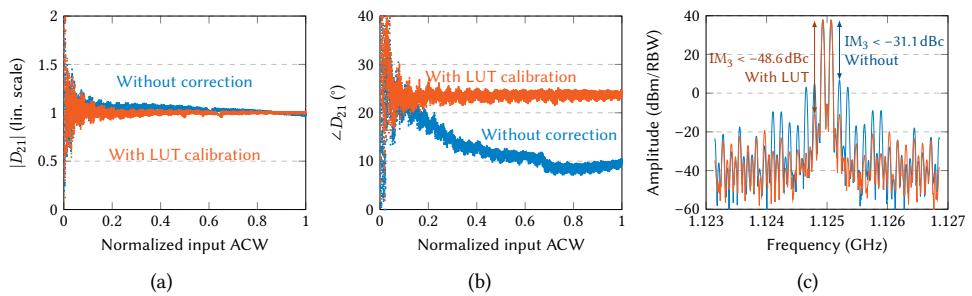

| 7.43 | Dynamic ACW–AM/ACW and ACW–PM transfers, and the output spectrum of the digital class-C setup using narrowband two-tone signals, with and without LUT calibration. . . . .                                                                                                                                                         | 140 |

| 7.44 | Output spectrum of the digital class-C setup using 8.8 MHz QAM signals, with annotated the measured channel power and ACLR levels. . . . .                                                                                                                                                                                         | 141 |

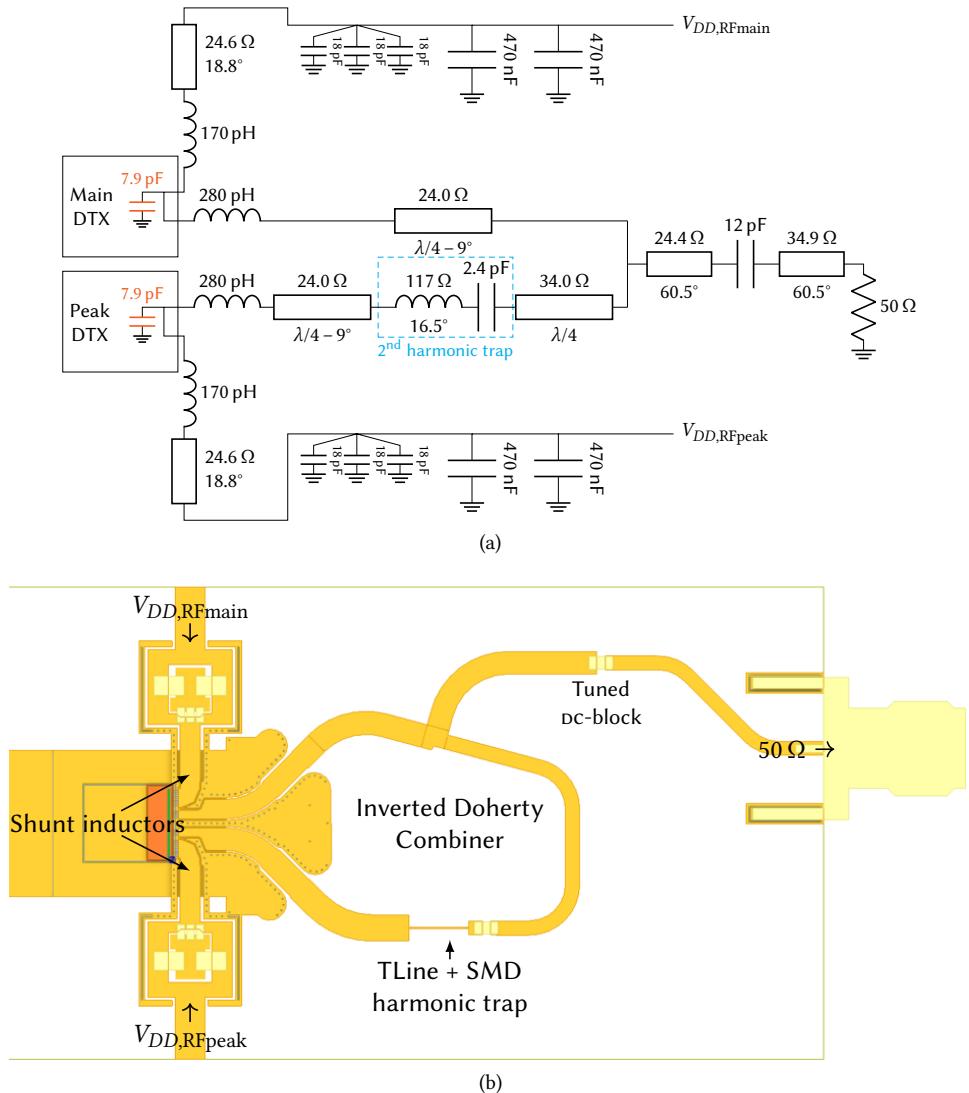

| 7.45 | Schematic (a) and layout (b) of the proposed inverted Doherty power combiner featuring a low-Q 2 <sup>nd</sup> harmonic trap in the peak path to guarantee smooth output power and efficiency vs. frequency. . . . .                                                                                                               | 143 |

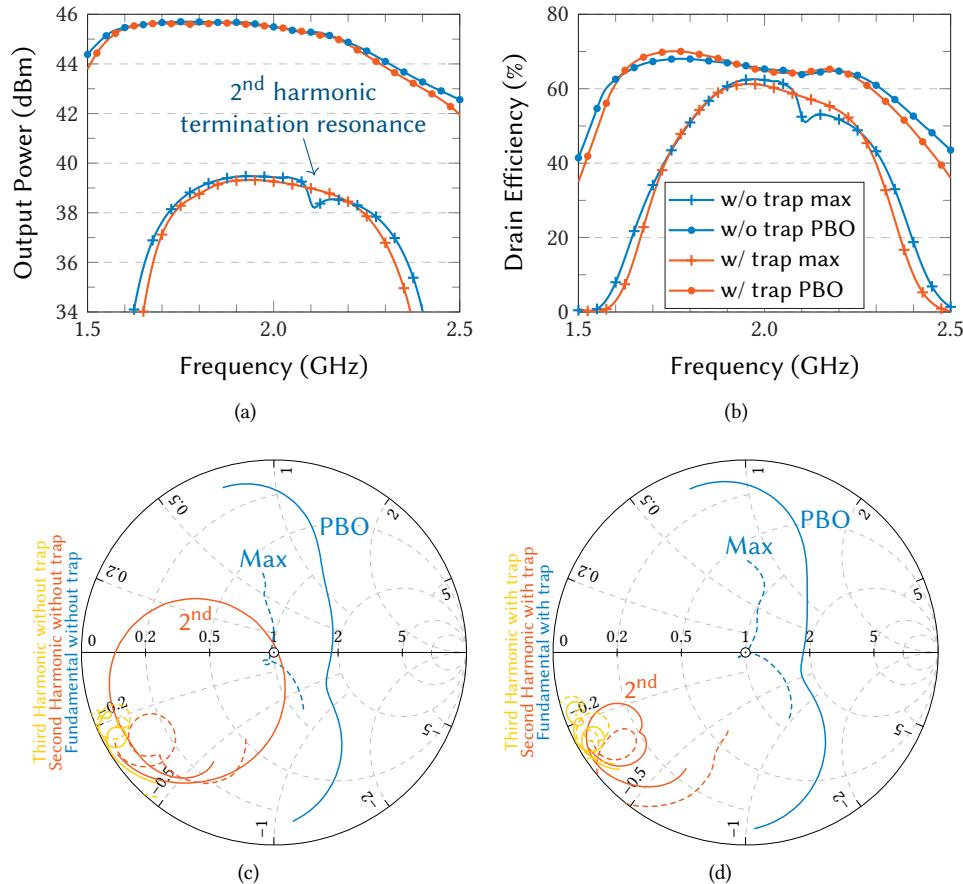

| 7.46 | Simulated performance of the DDTX on a schematic level, showing the impact of the harmonic trap. . . . .                                                                                                                                                                                                                           | 145 |

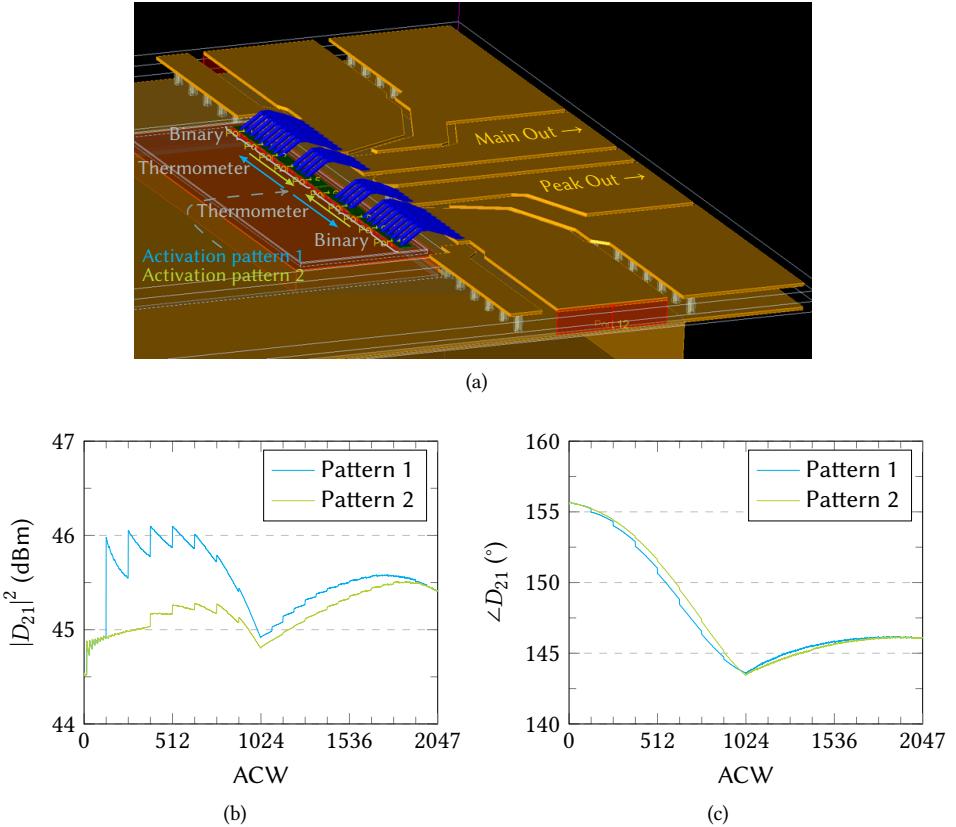

| 7.47 | A detail of the output bond wires with the two possible activation patterns illustrated: either the inside or the outside unary-weighted cells first. Depending on physical location the LDMOS segments will see a different matching condition, and thus leading to different (simulated) transfers. . . . .                      | 146 |

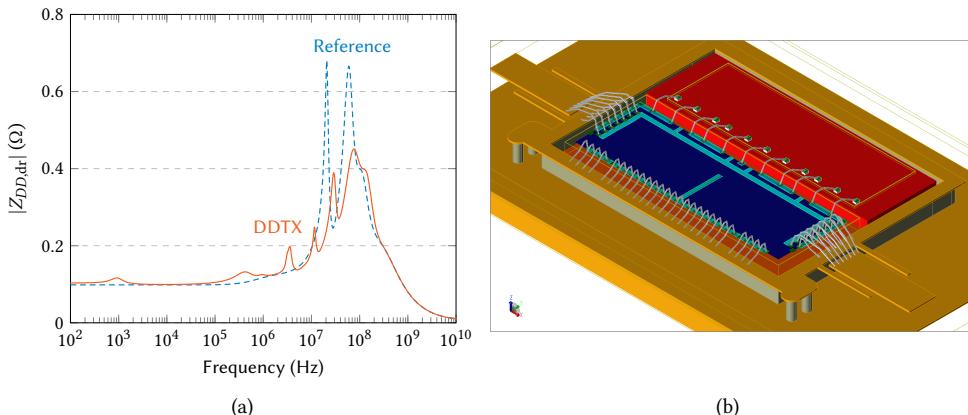

| 7.48 | In (a) the simulated impedance $Z_{DD,\text{dr}}$ seen into the $V_{DD,\text{dr}}$ supply, using lumped equivalents for capacitors on the PCB and transmission line equivalents of the traces, and (b) a 3D view for the EM simulated $V_{DD,\text{dr}}$ supply paths and its ground return paths used for the simulation. . . . . | 147 |

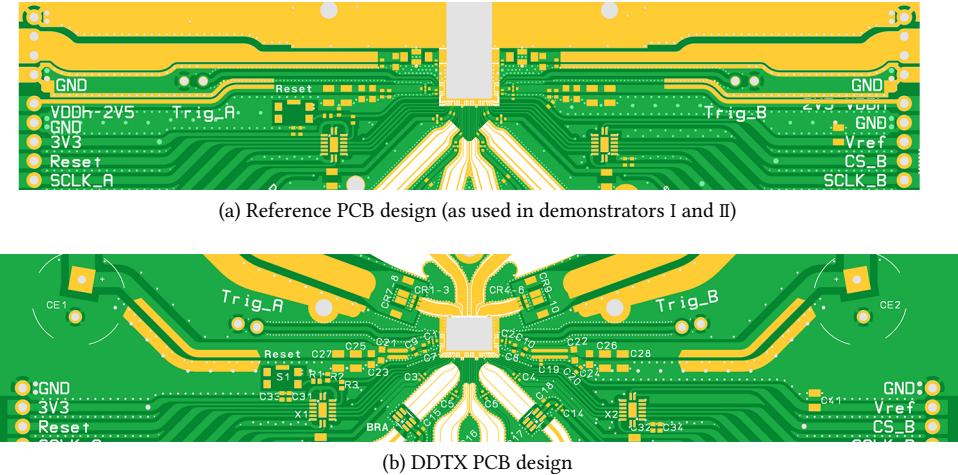

| 7.49 | Improvements on PCB level for the dc decoupling of the DDTX’s $V_{DD,\text{dr}}$ domain. Most notably, capacitors have been moved closer to the bond pads and traces have a lower impedance. . . . .                                                                                                                               | 148 |

| 7.50 | Improvement of the flange, featuring a small undercut/cavity on the edge between the CMOS and LDMOS dies. . . . .                                                                                                                                                                                                                  | 149 |

| 7.51 | Photograph of the realized Doherty combiner on PCB and a detail photo of the die assembly. . . . .                                                                                                                                                                                                                                 | 150 |

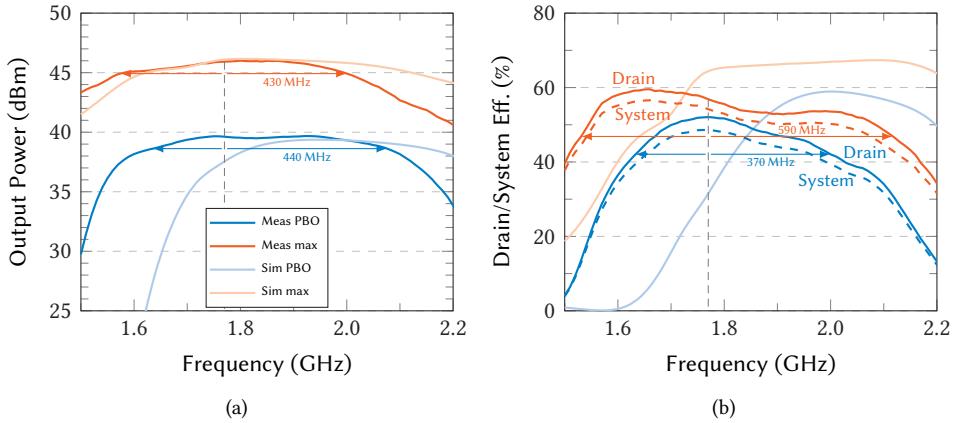

| 7.52 | Measurement results of the DDTX compared with the 3D EM simulated design. . . . .                                                                                                                                                                                                                                                  | 150 |

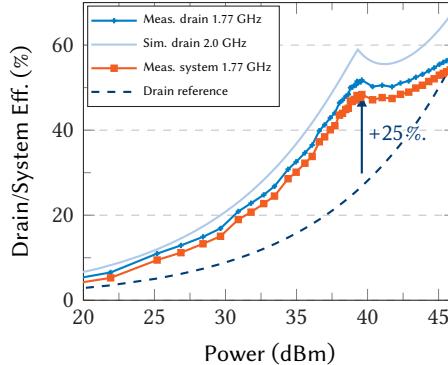

| 7.53 | The measured and simulated efficiencies vs. output power at $f_c = 1.77$ GHz, showing efficiency improvement in power back-off by 25 percentage points with respect to a situation with the same peak efficiency but without efficiency enhancement. . . . .                                                                       | 151 |

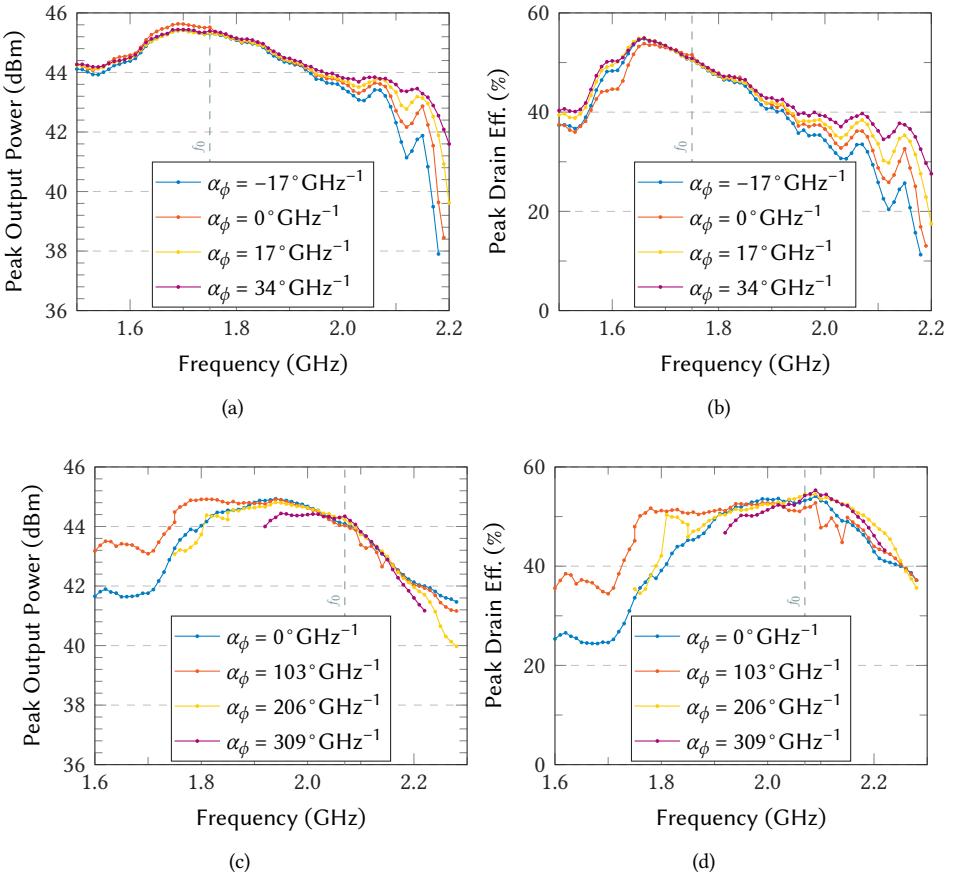

| 7.54 | Measurements with varying the phase relation of the peaking amplifier over frequency for two different samples. . . . .                                                                                                                                                                                                            | 152 |

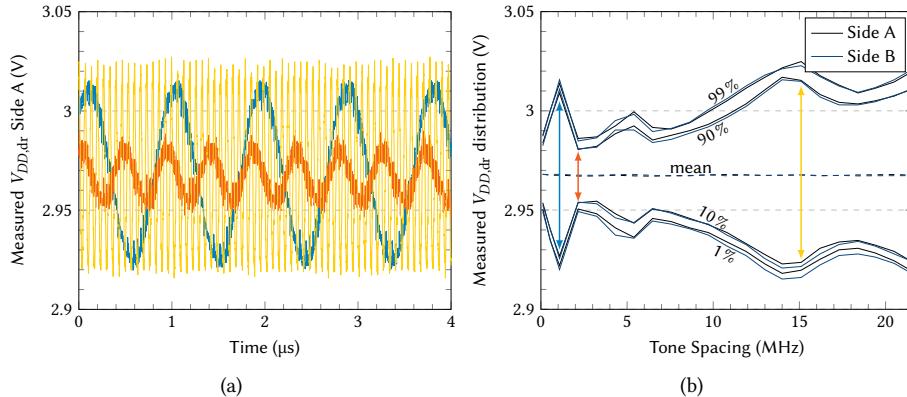

| 7.55 | Measured $V_{DD,\text{dr}}$ through the TRIG outputs in a two tone scenario with varying two tone spacing. . . . .                                                                                                                                                                                                                 | 153 |

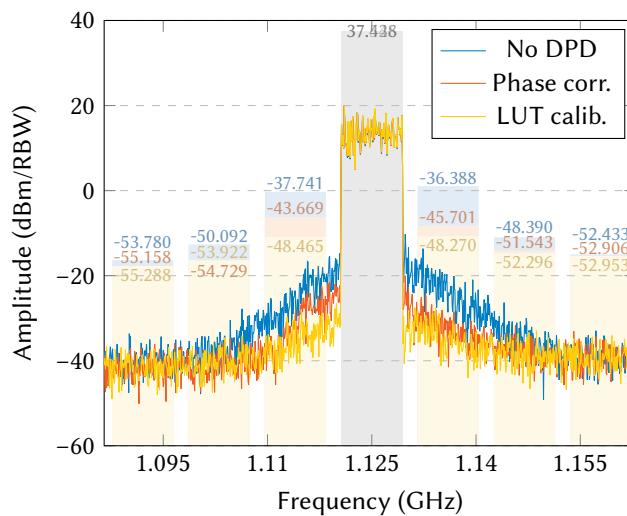

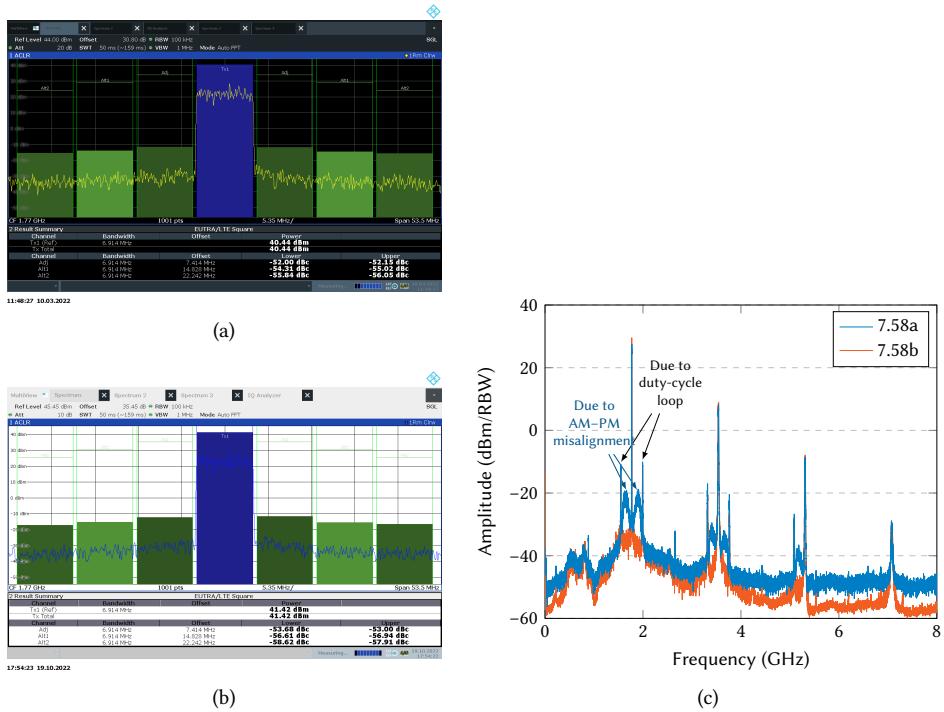

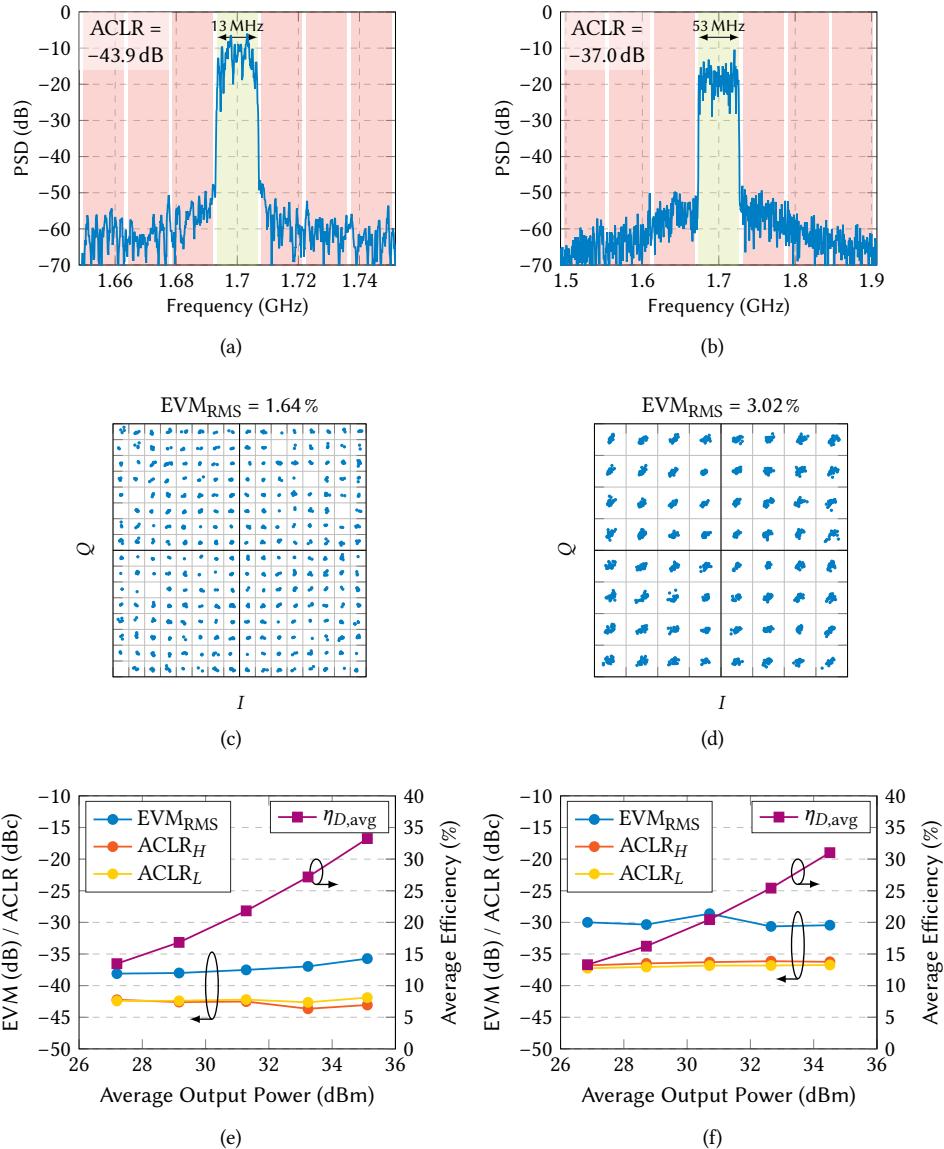

| 7.56 | Measured 6.9 MHz 256-QAM signal spectra with $f_c = 1.77$ GHz: ACLR measurements in (a) and (b), full spectrum in (c). . . . .                                                                                                                                                                                                     | 154 |

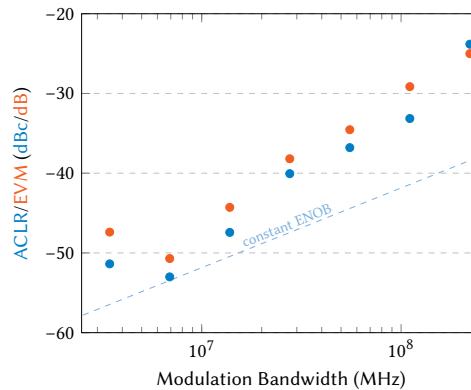

| 7.57 | The measured ACLR and EVM vs. modulation frequency. . . . .                                                                                                                                                                                                                                                                        | 154 |

---

|      |                                                                                                                                                                                                                                                                                                                          |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

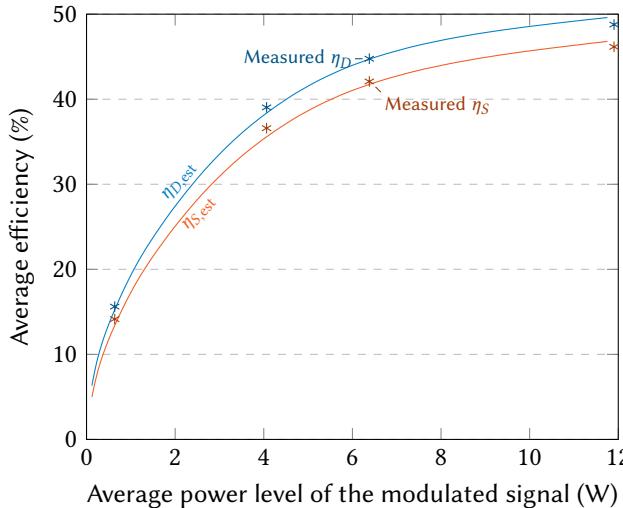

| 7.58 | The estimated and measured drain/system efficiencies vs. modulated RF power back-off to estimate 24 h energy consumption of the DDTX. . . . .                                                                                                                                                                            | 155 |

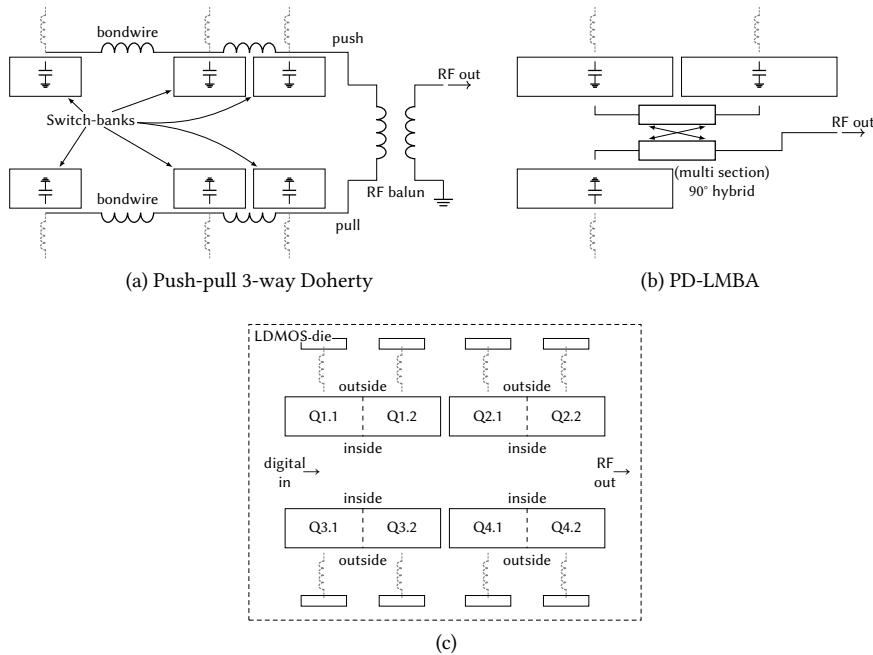

| 8.1  | Two example switch-bank configurations in (a) and (b), leading to the generic switch bank configuration as shown in (c). This allows for the most flexible configuration for possible demonstrators, including inshin with on-chip return path. . . . .                                                                  | 159 |

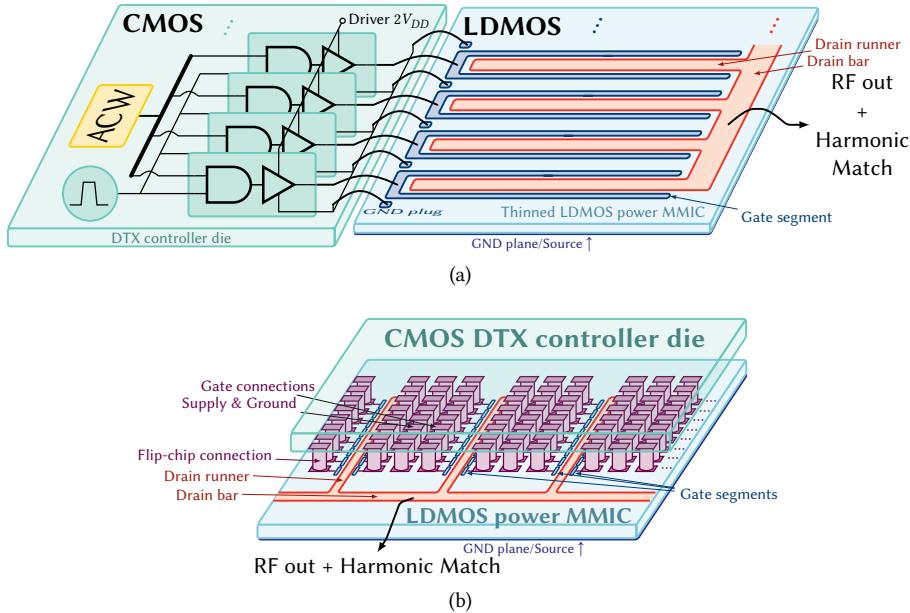

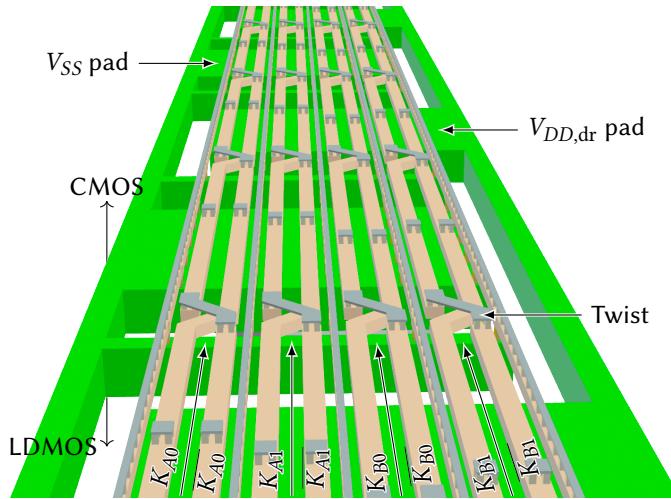

| 8.2  | Conceptual illustrations of (a) bond-wire-based DTX and (b) using high-density flip-chip. Reaching the required resolution with as much thermometer-coding as possible necessitates many interconnections between the CMOS controller and the power die, for which flip-chip assembly is a much better solution. . . . . | 161 |

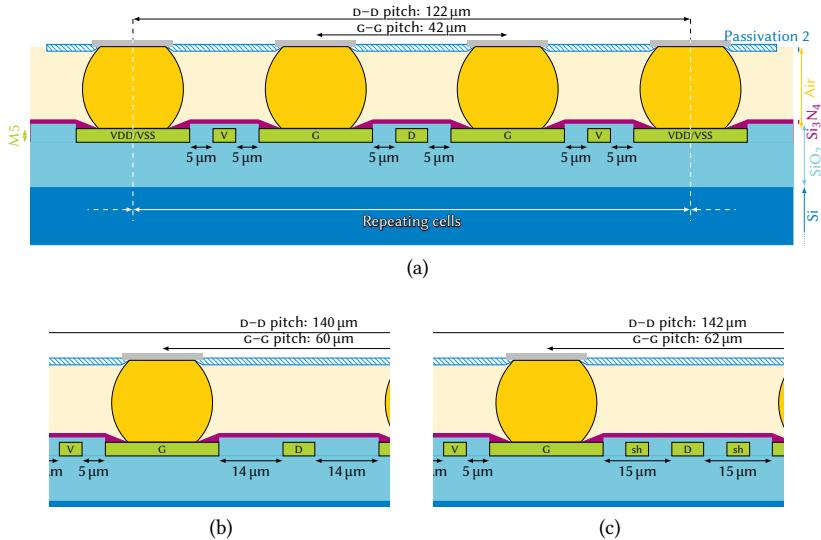

| 8.3  | Choosing the unit-cell pitch is dominated by feedback capacitance $C_{GD}$ layout parasitics in the LDMOS die: (a) shows the minimum possible pitch, (b) with increased G-D spacing, and (c) inserts a G-D ground shield. . . . .                                                                                        | 162 |

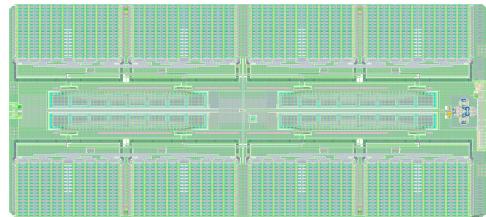

| 8.4  | Layout for a single switch bank, also featuring driver supply connections and ground return paths. . . . .                                                                                                                                                                                                               | 164 |

| 8.5  | The flip-chip assembly flow used that is compatible with all the manufacturing capabilities and requirements. . . . .                                                                                                                                                                                                    | 166 |

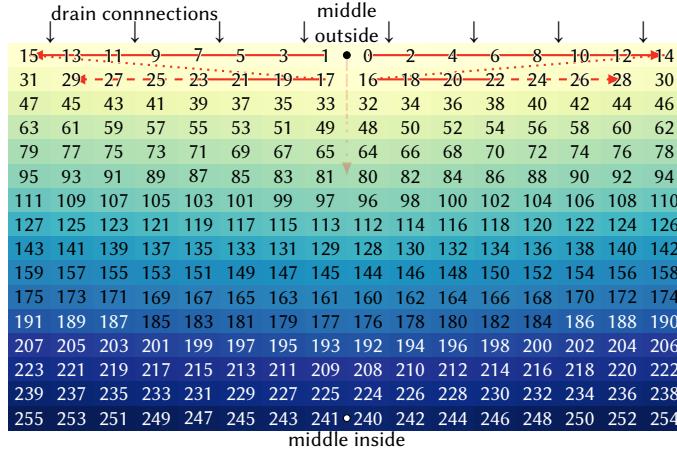

| 8.6  | Activation pattern as used for the MSBs, activating from 0 (light) to 255 (dark). . . . .                                                                                                                                                                                                                                | 167 |

| 8.7  | The dynamic phase allocation of the unit cells using $4 \times 4$ unit cells as simplified example. . . . .                                                                                                                                                                                                              | 168 |

| 8.8  | Simplified logic as applied in an unit cell (data retiming, glitch prevention, and buffering removed) for clock combining and selecting. . . . .                                                                                                                                                                         | 168 |

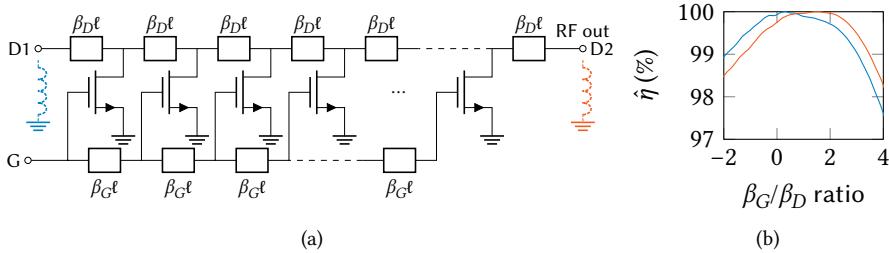

| 8.9  | Investigating the effects of different propagation constants ( $\beta$ ) of the driver's clock line at the gate and line at the drain side. The propagation constants should roughly match in the direction of the RF wave propagation. . . . .                                                                          | 169 |

| 8.10 | The implemented RF clock lines in CMOS. The lines are capacitively shielded by the supply pads and magnetically by twisting the clock lines. . . . .                                                                                                                                                                     | 170 |

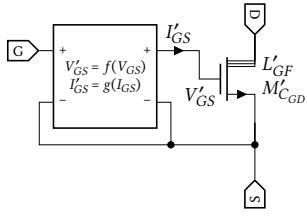

| 8.11 | LDMOS model modification using parameter conversion. . . . .                                                                                                                                                                                                                                                             | 172 |

| 8.12 | Modeled $V_{GS}$ - $I_{DS}$ and $-g_m$ curves based on measurement of the modified LDMOS process with thinned gate oxide, using $V_{DS} = 28\text{ V}$ . . . . .                                                                                                                                                         | 174 |

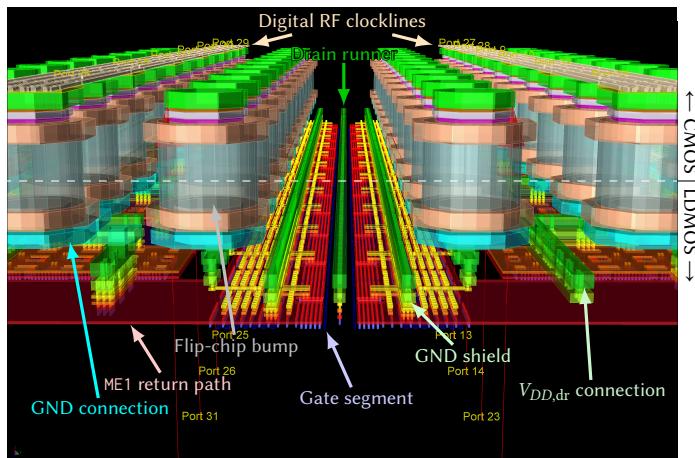

| 8.13 | Detailed 3D view of the structure to be modeled. . . . .                                                                                                                                                                                                                                                                 | 174 |

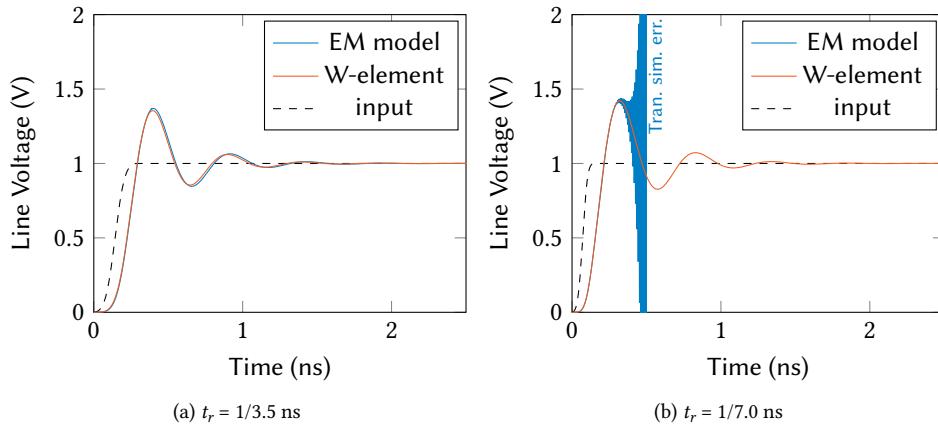

| 8.14 | Voltage step response of two drain runner models, showing good agreement between the EM model and the fitted W-element. However, for a fast step rise time, the EM model shows numerical instability, while the W-element remains numerically stable. . . . .                                                            | 175 |

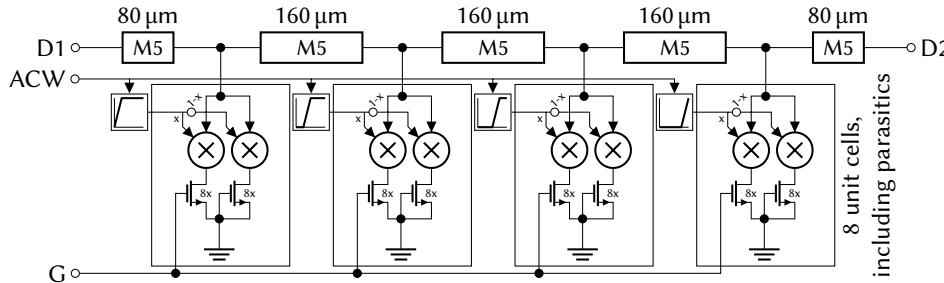

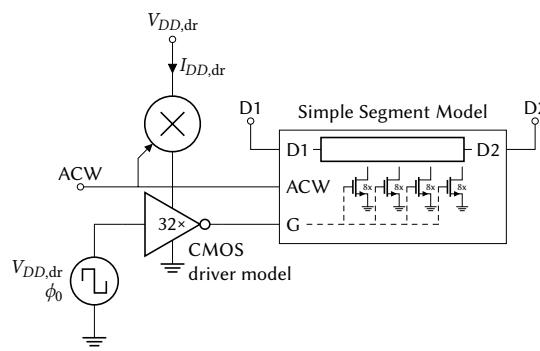

| 8.15 | Simplified LDMOS segment model, where the 32 individual unit cells are replaced by a single continuously scalable ACW, while maintaining the layout dependent effects and activation pattern. . . . .                                                                                                                    | 177 |

| 8.16 | The stacked driver topology with its tapered buffer chains and ESD diodes. . . . .                                                                                                                                                                                                                                       | 179 |

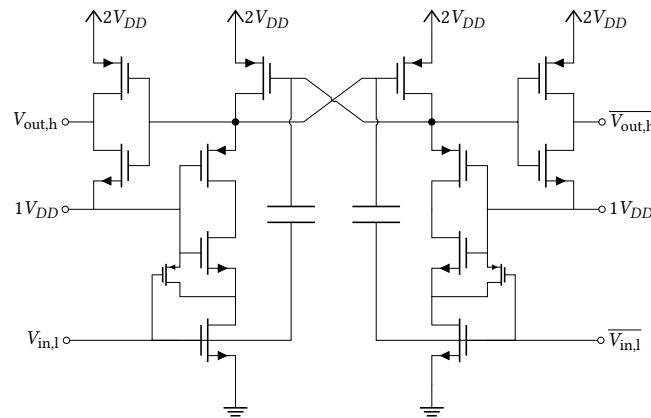

| 8.17 | The schematic of the level shifter responsible for shifting from $V_{SS}$ - $V_{DD,\text{core}}$ to $V_{DD,\text{core}} - 2V_{DD,\text{core}} = V_{DD,\text{dr}}$ . . . . .                                                                                                                                              | 180 |

|      |                                                                                                                                                                                                                                                                                                                                         |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.18 | Combining the CMOS driver model with the simplified LDMOS segment model from Fig. 8.15 to accurately reflect the driver's speed and power consumption. . . . .                                                                                                                                                                          | 180 |

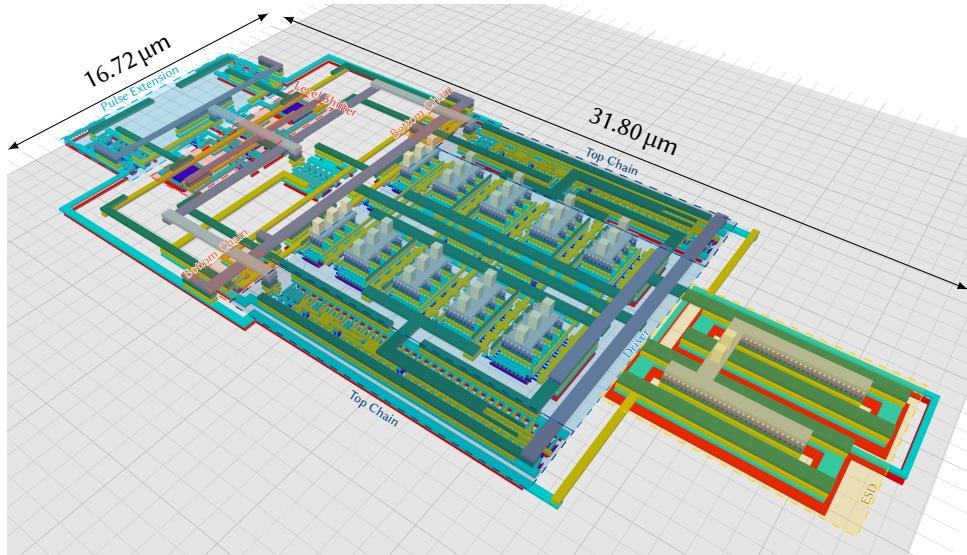

| 8.19 | 3D view of the complete realized driver structure, including ESD diodes, buffer chains, level shifter, and pulse extension. . . . .                                                                                                                                                                                                     | 181 |

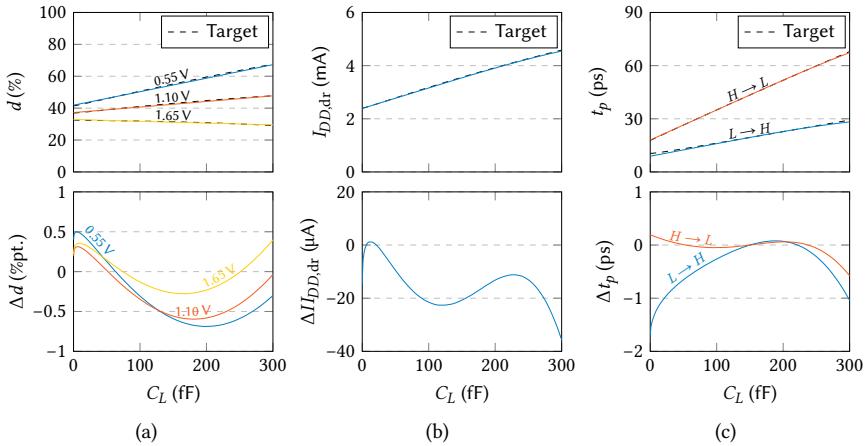

| 8.20 | Fitting a behavioral driver model (see Section B.2.4) to the post-layout simulation results while varying the load capacitance $C_L$ . . . . .                                                                                                                                                                                          | 182 |

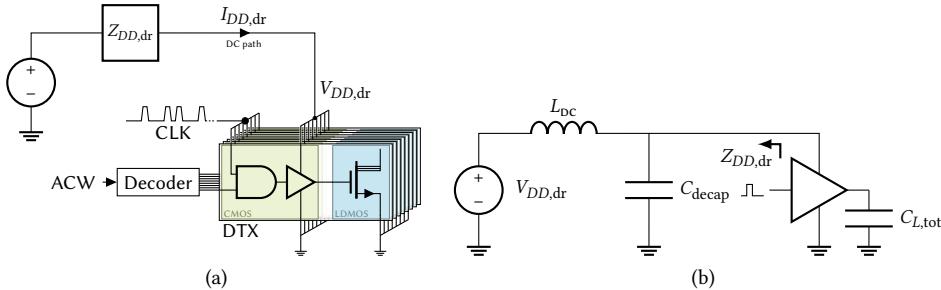

| 8.21 | Schematic of the CMOS driver supply path: (a) conceptual supply path and its impedance; (b) simplest schematic of a supply decoupling structure. . .                                                                                                                                                                                    | 183 |

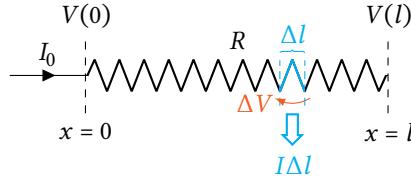

| 8.22 | Calculating the effective resistance of a distributed resistive line with a constant uniformly distributed current drawn, resulting in an effective $R/2$ at the end of the line. . . . .                                                                                                                                               | 184 |

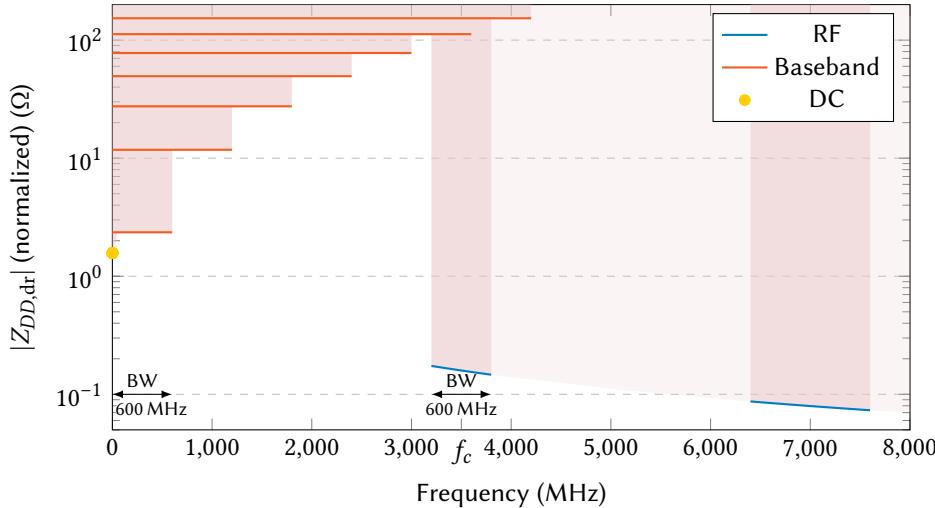

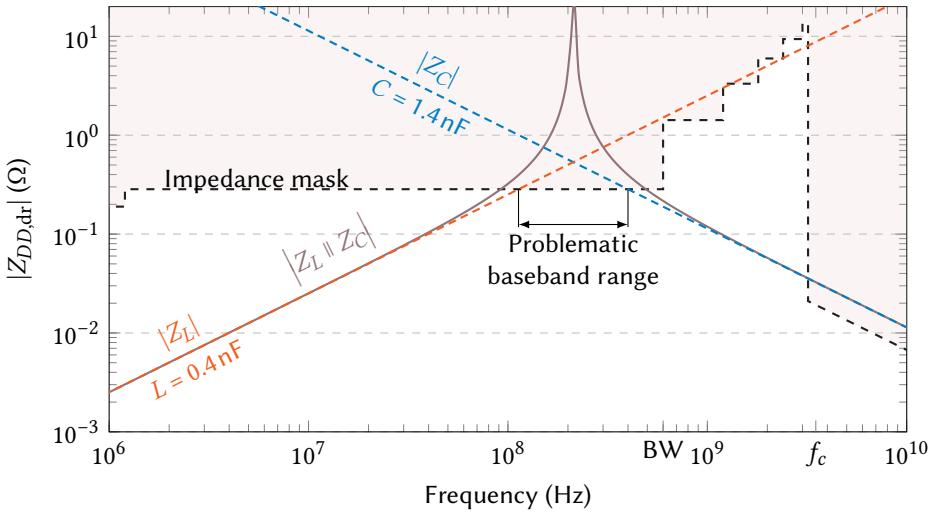

| 8.23 | The normalized impedance mask when assuming $I_{DD,dr,max} = 1\text{ A}$ and the same maximum $\Delta V_{DD,dr} = 1\text{ V}$ for the three relevant frequency regions: RF, baseband, and dc. The supply impedance $Z_{DD,dr}$ seen from the drivers should remain below this impedance mask, so out of the red shaded areas. . . . .   | 187 |

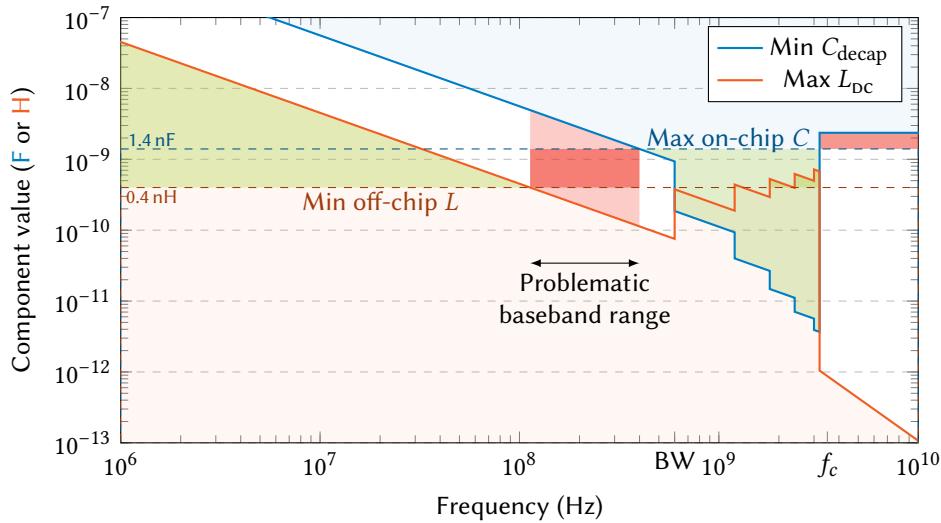

| 8.24 | The impedance mask translated to component values. If the maximum tolerable inductance is higher than the minimum implementable inductance, the impedance mask requirements can be met, and vice versa for the capacitance. These areas are shaded green. The frequency ranges are shaded red where neither requirement is met. . . . . | 189 |

| 8.25 | The actual impedance as seen by the driver when using only an (ideal) feed inductance and decoupling capacitance, while assuming realistic implementable values. . . . .                                                                                                                                                                | 190 |

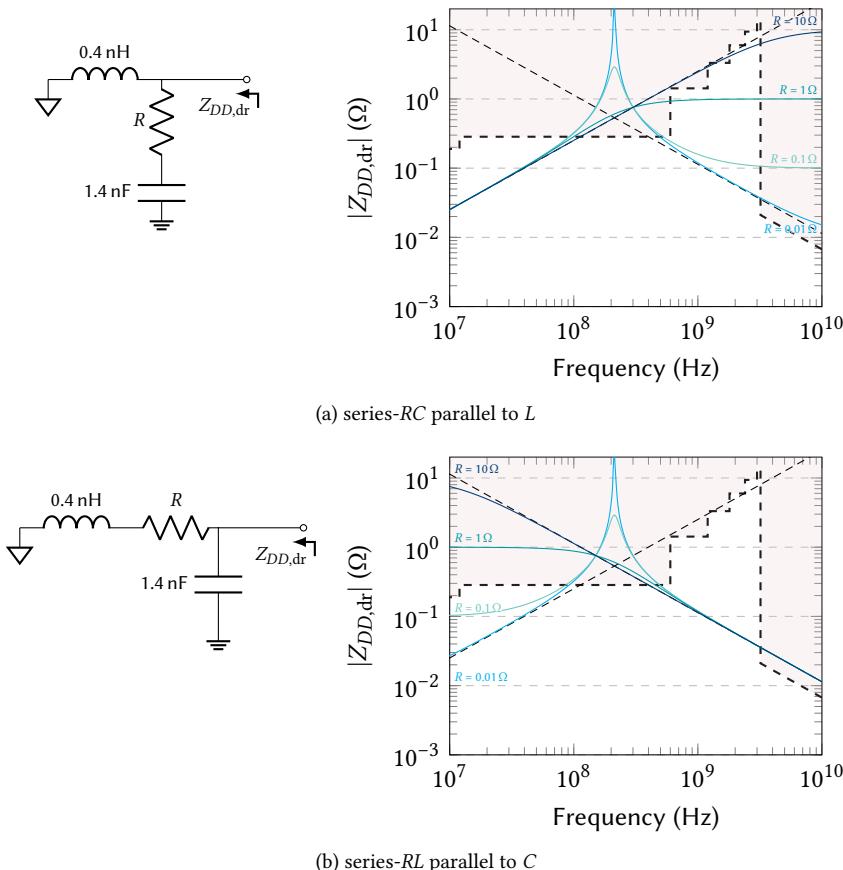

| 8.26 | Damping the inevitably occurring resonance peak, here within the unwanted baseband region. Here the resonance is damped by placing a resistance in series with (a) the decoupling capacitor, or (b) the feed inductance. Neither method meets the impedance mask requirements. . .                                                      | 191 |

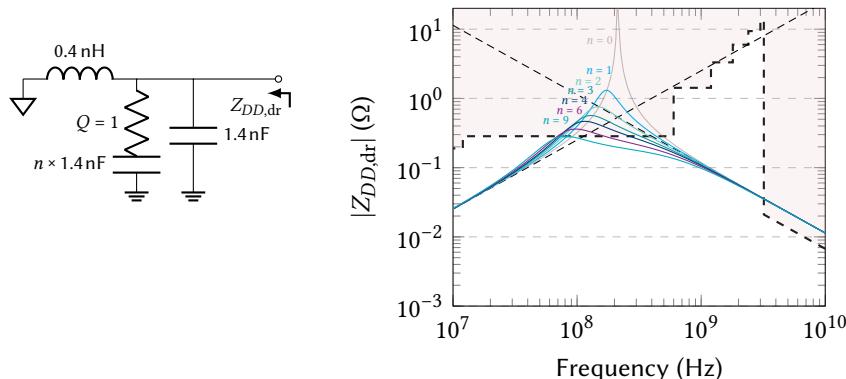

| 8.27 | Placing a capacitor with $Q = 1$ parallel to the nominal (high- $Q$ ) decoupling capacitor, damping the resonance peak effectively. . . . .                                                                                                                                                                                             | 191 |

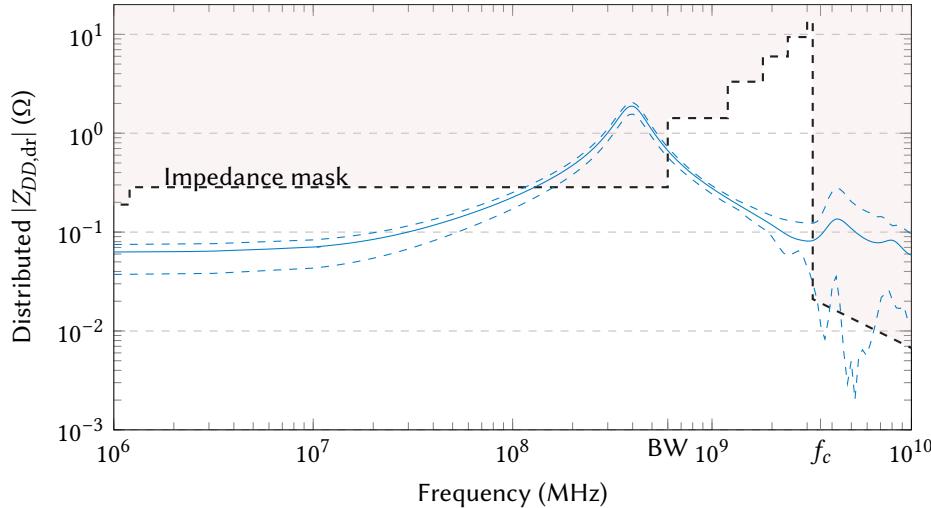

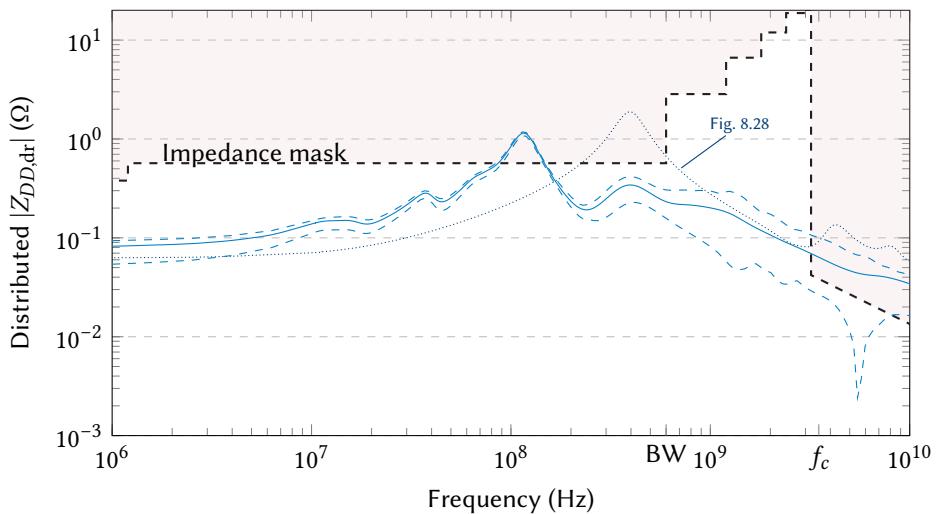

| 8.28 | The simulated distributed supply impedance per bank, assuming all drivers are active and an AC short at the PCB reference plane. Since the distributed impedance simulation contains 640 ports, all the impedances seen over the bank are averaged to estimate the effective impedance. . . . .                                         | 193 |

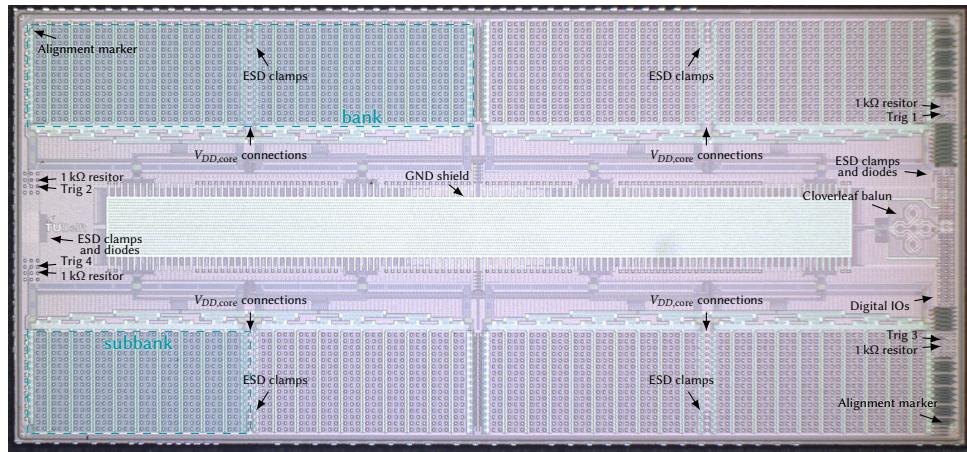

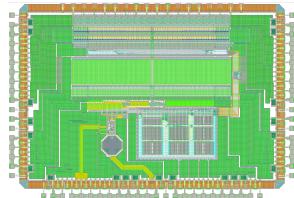

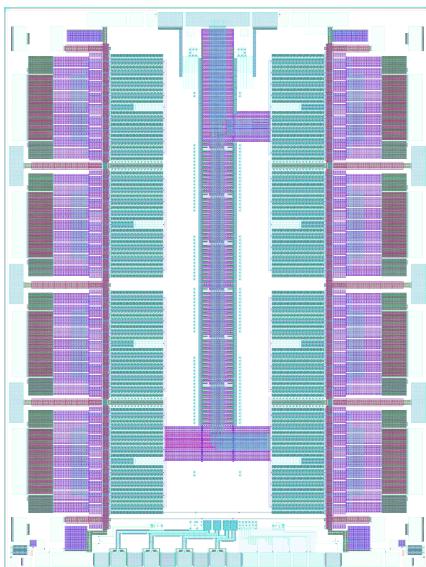

| 8.29 | Full chip micrograph of the realized CMOS controller. . . . .                                                                                                                                                                                                                                                                           | 195 |

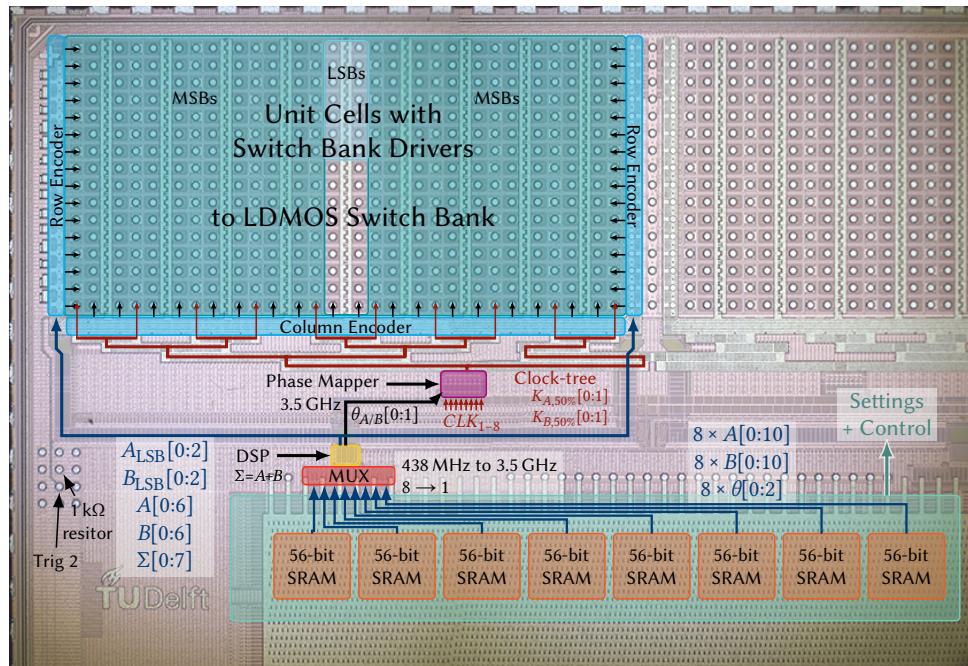

| 8.30 | Micrograph of the top left chip corner with the functional block diagram of one sub-bank. . . . .                                                                                                                                                                                                                                       | 195 |

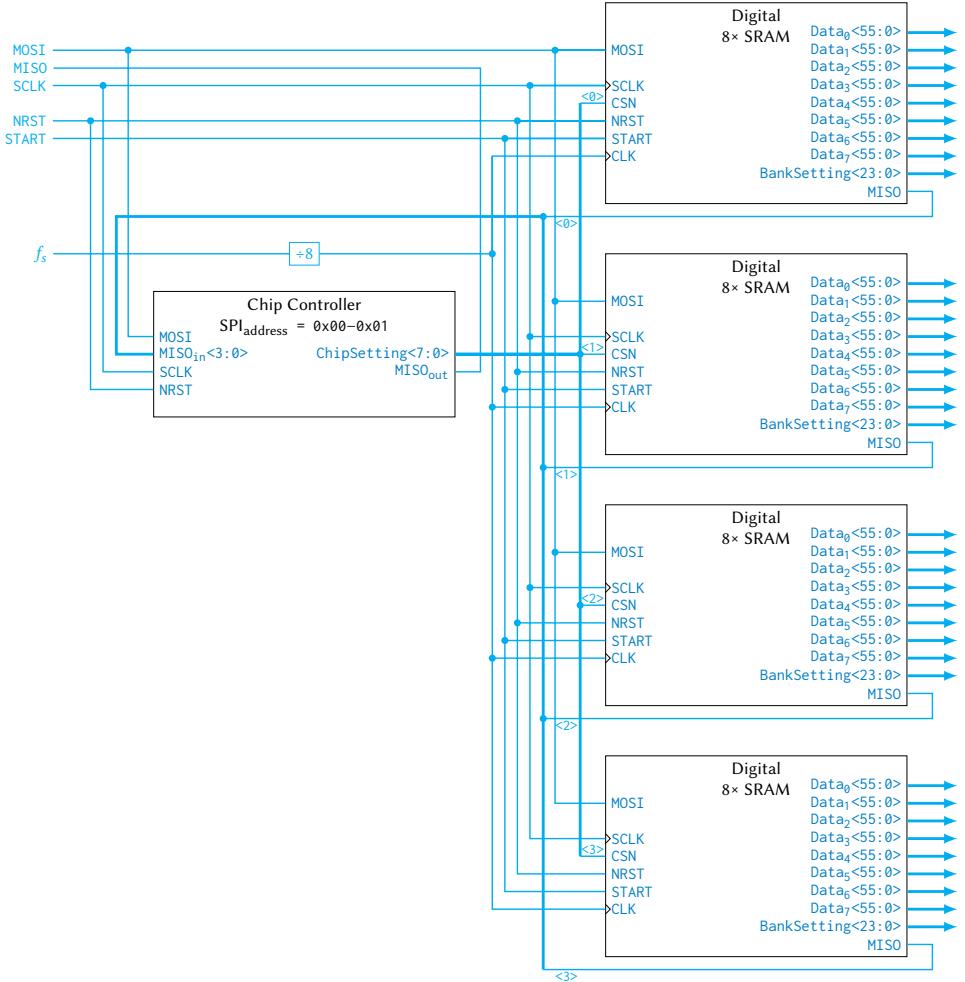

| 8.31 | Simplified digital block diagram, showing the chip's external interfacing. .                                                                                                                                                                                                                                                            | 196 |

| 8.32 | Cross section for verifying the flip-chip assembly. . . . .                                                                                                                                                                                                                                                                             | 197 |

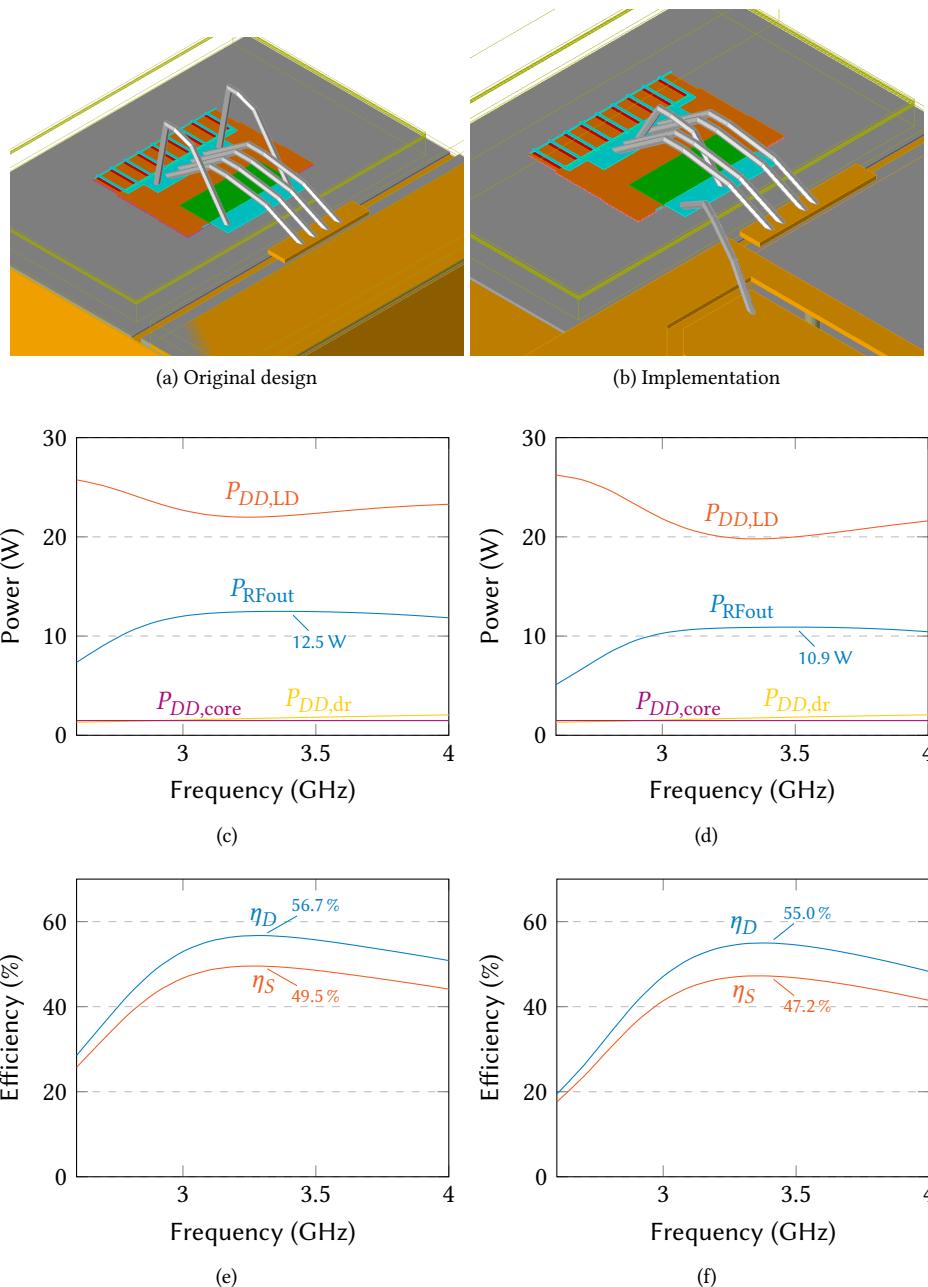

| 8.33 | Expected performance (simulated) of demonstrator I. The initial bond wire design was not possible (a) to realize in assembly due to bond wire height, requiring a smaller single shunt wire in the implemented version (b) that has a lower $Q$ , negatively impacting output power and efficiency. . . . .                             | 200 |

---

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

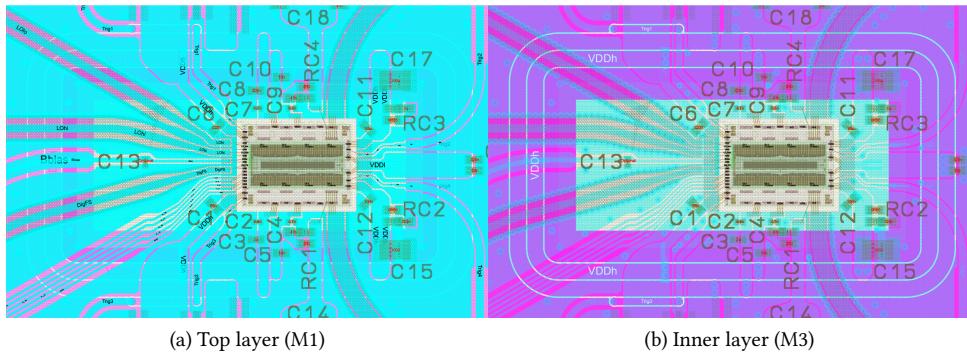

| 8.34 | A close-in view of the PCB design used for demonstrator I, showing the first and third metal layers surrounding the die assembly. The inner structure reveals the ring structure used for DC routing of the 1.1 V and 2.2 V supplies, the top layer shows the decoupling structures present, as well as the various input and output lines. . . . .                                                                                             | 201 |

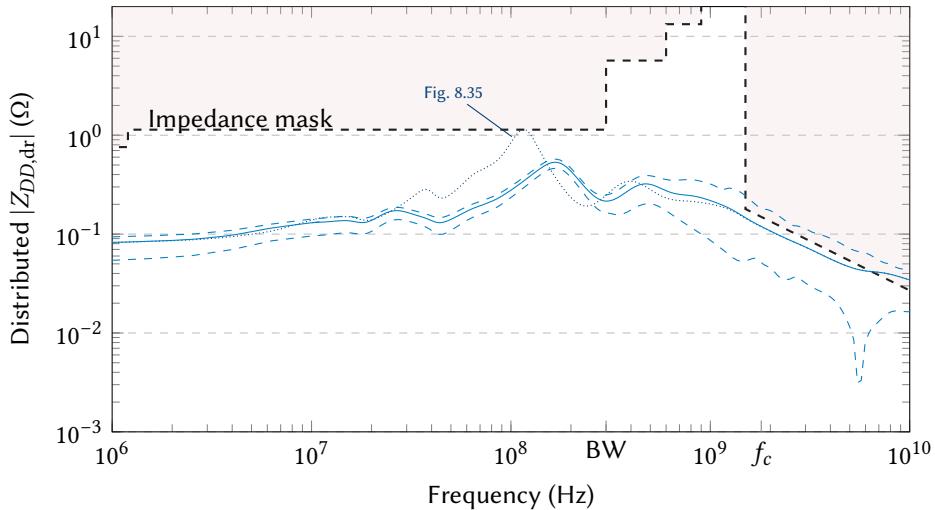

| 8.35 | The simulated distributed supply impedance of demonstrator I per sub-bank, assuming only the drivers of two sub-banks are active. . . . .                                                                                                                                                                                                                                                                                                       | 202 |

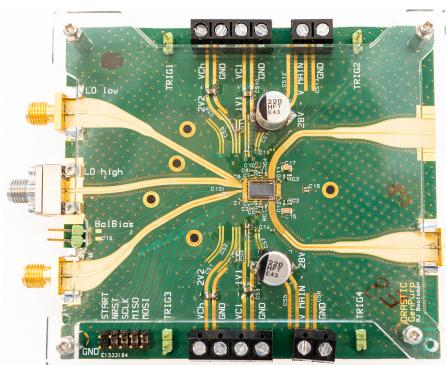

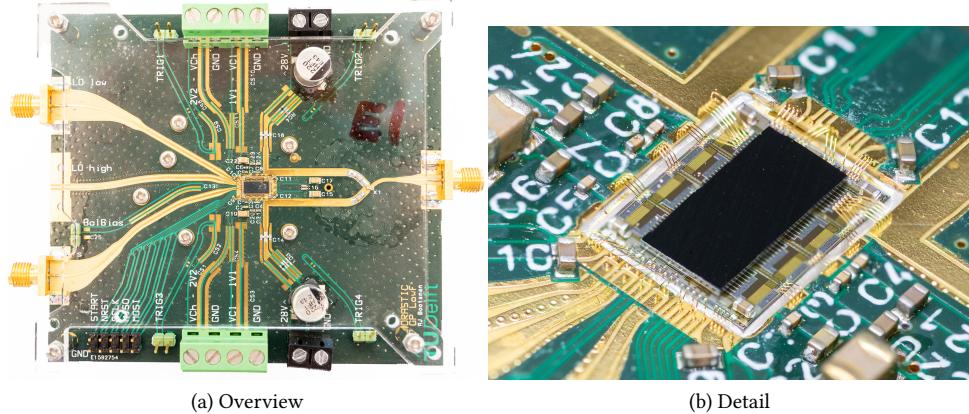

| 8.36 | Photo of the realized demonstrator I. . . . .                                                                                                                                                                                                                                                                                                                                                                                                   | 202 |

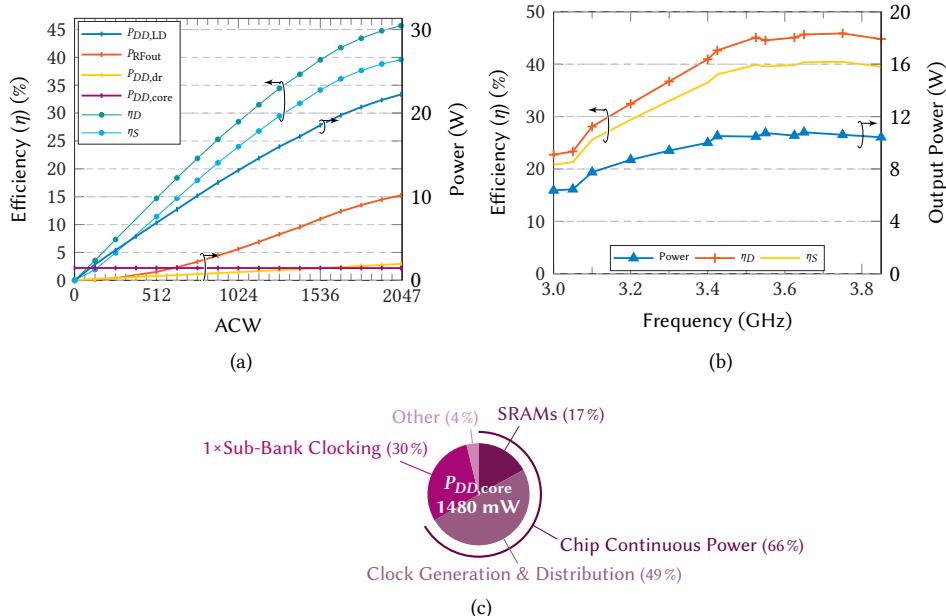

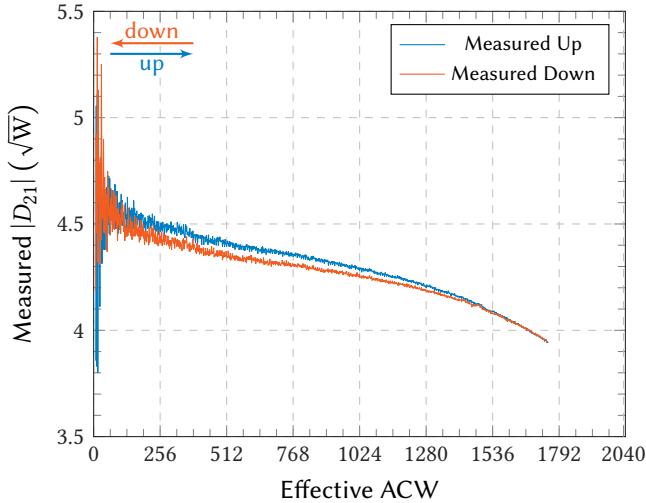

| 8.37 | Pulsed CW measurements with 12.5% time duty-cycle pulses, showing RF output power, drain and system efficiencies, and continuous $P_{DD,\text{core}}$ power breakdown. . . . .                                                                                                                                                                                                                                                                  | 203 |

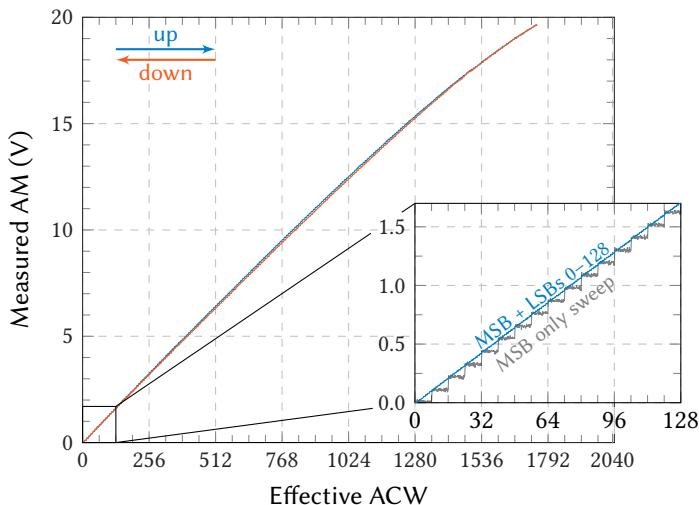

| 8.38 | Measured ACW-AM curve of the high-resolution DTX. In the main graph only the MSB segments are used, while in the zoomed graph both the MSBs and the second layer of 7 thermometer coded LSBs are used. . . . .                                                                                                                                                                                                                                  | 203 |

| 8.39 | Measured dynamic transfer of the high-resolution DTX only using the MSB segments. . . . .                                                                                                                                                                                                                                                                                                                                                       | 204 |

| 8.40 | Photo of the realized demonstrator XI. . . . .                                                                                                                                                                                                                                                                                                                                                                                                  | 205 |

| 8.41 | The simulated distributed supply impedance of demonstrator XI per sub-bank, assuming all drivers of sub-banks Q2.2 and Q4.2 are active, and with added on-chip SMD MLCCs. Here the impedance mask is adjusted for $f_c = 1.8$ GHz while keeping the fractional bandwidth the same. Since the distributed impedance simulation contains 160 ports, all the impedances seen over the sub-bank are averaged to estimate the effective impedance. . | 206 |

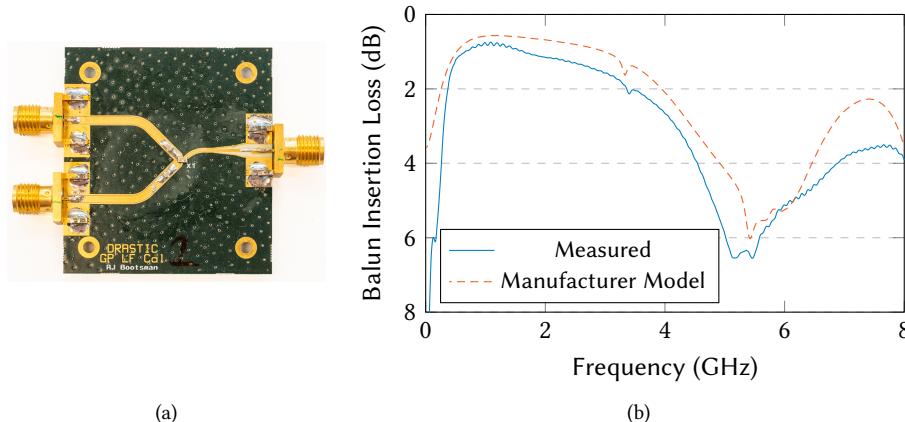

| 8.42 | Measurements of the calibration board for deembedding the commercial of-the-shelf balun and DC-blocking capacitors from the DTX measurement. .                                                                                                                                                                                                                                                                                                  | 207 |

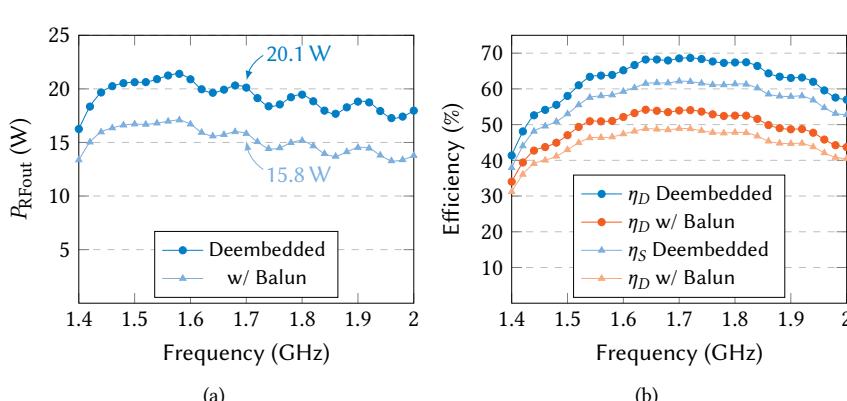

| 8.43 | Measured output power and efficiencies of the DTX at peak RF output power vs. frequency, with and without deembedding of the balun. . . . .                                                                                                                                                                                                                                                                                                     | 207 |