### Integrated Digital and Analog Circuit Blocks in a Scalable Silicon Carbide CMOS Technology

Romijn, Joost; Vollebregt, Sten; Middelburg, Luke M.; el Mansouri, Brahim; van Zeijl, Henk W.; May, Alexander; Erlbacher, Tobias; Zhang, Guoqi; Sarro, Pasqualina M.

DOI

10.1109/TED.2021.3125279

Publication date 2022

**Document Version**Final published version

Published in

IEEE Transactions on Electron Devices

Citation (APA)

Romijn, J., Vollebregt, S., Middelburg, L. M., el Mansouri, B., van Zeijl, H. W., May, A., Erlbacher, T., Zhang, G., & Sarro, P. M. (2022). Integrated Digital and Analog Circuit Blocks in a Scalable Silicon Carbide CMOS Technology. *IEEE Transactions on Electron Devices*, *69*(1), 4-10. Article 9614653. https://doi.org/10.1109/TED.2021.3125279

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Integrated Digital and Analog Circuit Blocks in a Scalable Silicon Carbide CMOS Technology

Joost Romijn<sup>®</sup>, *Member, IEEE*, Sten Vollebregt<sup>®</sup>, *Senior Member, IEEE*, Luke M. Middelburg<sup>®</sup>, Brahim El Mansouri, Henk W. van Zeijl, *Member, IEEE*, Alexander May, Tobias Erlbacher<sup>®</sup>, Guogi Zhang<sup>®</sup>, *Fellow, IEEE*, and Pasqualina M. Sarro<sup>®</sup>, *Fellow, IEEE*

Abstract—The wide bandgap of silicon carbide (SiC) has attracted a large interest over the past years in many research fields, such as power electronics, high operation temperature circuits, harsh environmental sensing, and more. To facilitate research on complex integrated SiC circuits, ensure reproducibility, and cut down cost, the availability of a low-voltage SiC technology for integrated circuits is of paramount importance. Here, we report on a scalable and open state-of-the-art SiC CMOS technology that addresses this need. An overview of technology parameters, including MOSFET threshold voltage, subthreshold slope, slope factor, and process transconductance, is reported. Conventional integrated digital and analog circuits, ranging from inverters to a 2-bit analog-to-digital converter, are reported. First yield predictions for both analog and digital circuits show great potential for increasing the amount of integrated devices in future applications.

Index Terms—4H-SiC, integrated SiC electronics, silicon carbide, silicon carbide CMOS, wide bandgap.

#### I. INTRODUCTION

SILICON carbide (SiC) is a wide-bandgap material that has been extensively researched over the past decades, especially for the application in power electronics [1], [2]. Together with galium nitride (GaN), the future market of wide-bandgap materials in power electronics is expected to be booming [3]. This foresight and the developed technologies pave the way for application in other fields as well [4]–[7], such as harsh environment sensing [8], [9] and ultraviolet detectors, though there are challenges for the next generation of devices to overcome [10].

The bandgap of 4H-SiC is 3.2 eV, which is almost three times larger than that of silicon [11]. This property allows

Manuscript received August 9, 2021; accepted October 29, 2021. Date of publication November 15, 2021; date of current version December 29, 2021. This work was supported by the Dutch Technology Foundation (STW), which is part of The Netherlands Organization for Scientific Research (NWO), and which is partly funded by the Ministry of Economic Affairs, under Project 16247. The review of this article was arranged by Editor D. Triyoso. (Corresponding author: Joost Romijn.)

Joost Romijn, Sten Vollebregt, Luke M. Middelburg, Brahim El Mansouri, Henk W. van Zeijl, Guoqi Zhang, and Pasqualina M. Sarro are with the Laboratory of Electronic Components, Technology and Materials (ECTM), Department of Microelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: j.romijn@tudelft.nl).

Alexander May and Tobias Erlbacher are with the Fraunhofer Institute for Integrated Systems and Devices Technology IISB, 91058 Erlangen, Germany.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3125279.

Digital Object Identifier 10.1109/TED.2021.3125279

Fig. 1. Photograph of the 4 in SiC device wafer in the Fraunhofer IISB technology.

for applications in higher operation temperatures, ultraviolet photodetection, radiation exposure resistance, and overall harsher environments [12], [13]. Development of discrete SiC components, such as MOSFETs and sensors, for operation in harsh environments is one side of the coin, whereas the other is the integration with on-chip electronics to allow for complete systems to be exposed to these harsh conditions.

A decade ago, Raytheon Systems Limited developed a proprietary 1.2 µm SiC CMOS technology, called high temperature silicon carbide (HiTSiC), and demonstrated integrated circuits [14], [15]. The group of Mantooth at the University of Arkansas demonstrated a comparator [16], 8-bit digitalto-analog converter (DAC) [17], voltage and current references [18], gate driver [19], complex digital circuits [20], protection circuits in voltage regulators and switch-mode converters [21], digitally controlled pulsewidth modulation (PWM) generator [22], and data converters [23]. However, the HiTSiC technology was discontinued in 2018. Other inhouse SiC CMOS technologies are reported by General Electric Global Research Center in the United States of America, for example [24], [25]. But in strong contrast with silicon services like Europractice, accessible SiC CMOS fabrication technologies are scarce to nonexistent.

Additionally, a promising SiC bipolar junction transistor (BJT) technology for high temperature and harsh environments, called high temperature power electronic systems with SiC integrated circuit (HOTSiC), was developed by the group of Zetterling at the KTH in Sweden [26], [27]. It is implemented by mesa etching in a complex epitaxial layer stack on top of a monocrystalline SiC wafer. In this technology, an OR/NOR gate [28], emitter-coupled logic (ECL)-based logic circuits [29], operational amplifier [30], differential amplifier [31], high current linear voltage regulator [32], and 8-bit DAC [33] were implemented and characterized up to 500 °C. Though BJTs and CMOS are the most popular flavors in silicon-based technologies, JFET [34], [35] and MESFET [36],

0018-9383 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

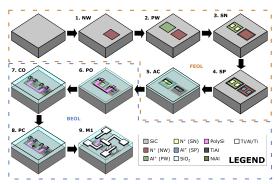

Fig. 2. Schematic of the fabrication steps of the Fraunhofer IISB 4H-SiC CMOS technology. The FEOL includes the definition of the doped NW, PW, SN, and SP regions, as well as the definition of the active area. The BEOL includes the definition of the polysilicon and metal interconnect layers, with corresponding silicide contacts and vias.

[37] technologies have also been researched in the favor of stable operation at high temperatures. Although the MOSFET gate dielectric reliability has been a concern [38], [39], more recent work contradicts the poor reliability prediction and predict much longer lifetimes [40]. Moreover, CMOS technologies are typically preferred in mixed-signal circuit designs and have lower power consumption.

More recently, a promising new SiC CMOS technology candidate arose. This state-of-the-art 4H-SiC CMOS [41], [42] was developed by the Fraunhofer Institute for Integrated Systems and Devices Technology (IISB), based in Erlangen, Germany. The group of Mantooth at the University of Arkansas reported high-temperature memory SRAM cells [43] in this technology and Fraunhofer IISB demonstrated compatible UV photodetectors [44], [45] and temperature sensors [46].

This work reports on the state-of-the-art open 6  $\mu$ m SiC CMOS technology, developed at Fraunhofer IISB, by providing an overview of the technology and results of implemented devices and circuits on a multiproject wafer design (Fig. 1). The completeness of this work is illustrated by the derivation of a selection of technology parameters for this technology and the inclusion of high-temperature operation up to 200 °C. The potential of this technology is moreover, reflected by some integrated analog and digital building blocks, that have been realized with good yield values. Future implementations in this technology will benefit from this work using the reported technology parameters and use of the building blocks toward increased performance and integration.

#### II. TECHNOLOGY OVERVIEW

The fabrication process steps of the Fraunhofer IISB 4H-SiC CMOS technology are illustrated in Fig. 2 for an inverter, where each step corresponds to a design layer. The starting substrate is a 350- $\mu$ m thick 100 mm n-type 4H-SiC wafer with a 1–2  $\mu$ m epitaxial n-type >1 × 10<sup>18</sup> cm<sup>-3</sup> buffer layer and an 8- $\mu$ m epitaxial n-type 5 × 10<sup>14</sup> cm<sup>-3</sup> top layer. The front-end-of-line (FEOL) implements the doped regions by ion implantation, forming the n-well (NW), p-well (PW), shallow n-type (SN), and shallow p-type (SP), which are activated by a 1700 °C anneal for 30 min. The NW and SN are formed by N+ implantation and the PW and SP by Al+ implantation. The active area (AC) is implemented by wet etching the field

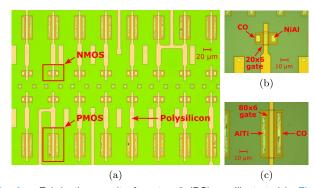

Fig. 3. Fabrication result after step 8 (PC), as illustrated in Fig. 2, of (a) multiple devices, (b) single  $20 \times 6$  nMOS, and (c)  $80 \times 6$  pMOS device. The formed silicides inside the contact openings are clearly visible. Note that none of the implanted regions can be observed.

oxide at the ohmic contact and MOSFET channel locations, followed by thermal gate oxidation. The resulting gate oxide thickness is 50 nm and the field oxide is 400 nm.

The back-end-of-line (BEOL) starts with implementation of a 500-nm polysilicon layer (PO), for the gate and short interconnects. An oxide passivation layer of 400 nm is deposited followed by the definition of ohmic contacts (CO) to the SN and SP layers in two steps. First, the openings to the SP layer are opened using a lithography mask, which is followed by the deposition and patterning of 80 nm/300 nm Ti/Al inside the openings. The procedure is repeated to form the openings to the SN layer and implements 50 nm NiAl patterns inside these openings. Rapid thermal annealing (RTA) at 980 °C is employed to form silicides in the contact openings, which ensures ohmic contacts from the metallization stack to the doped regions in the substrate. This is possible due to the high thermal stability of the present layers other than the contact metals. The final result is shown in Fig. 3. It should be noted that the patterned area of the metals in the contact openings is smaller than the etched openings, to avoid diffusion of these metals between the SiC-SiO<sub>2</sub> interface and generally into SiO<sub>2</sub> during the RTA. As a result, the CO design layer actually requires three separate lithography masks. Other metal stacks are investigated by Fraunhofer IISB [47], and ideally a single stack can be used to contact both the SN and SP regions simultaneously. The process then continues by opening the contacts to the polysilicon (PC). The metallization is completed by deposition and patterning of a 50 nm/700 nm/20 nm Ti/Al/Ti interconnect layer (M1). This reduces the thermal budget to 400 °C and should be adhered to in future implementations of multiple metal interconnect layers.

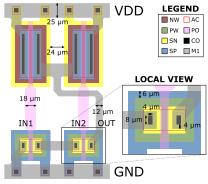

The dimensions of a NAND logic gate are included in Fig. 4 to illustrate the dimensions for the Fraunhofer IISB technology. This work includes a single metal interconnect layer, and polysilicon can be used as a second interconnect layer, at the cost of a larger sheet resistance and resulting in reduced frequency performance. The MOSFETs are implemented in the corresponding low-doped well that is connected to a highly doped guard ring. This helps reduce crosstalk or latch-up between the devices, but also means that one of the well types is electrically connected to the substrate. In this technology, n-type SiC substrates are used, which results in the electrical connection of all pMOS wells to the substrate. Devices that

#### TABLE I

MEAN VALUES OF THE SHEET RESISTANCES IN THE TECHNOLOGY AT ROOM TEMPERATURE, DERIVED FROM WAFER-LEVEL RESULTS OF 35 DIES. EACH DIE-LEVEL MEASUREMENT CONSISTS OF THE IV EXTRACTION FROM THE RESPECTIVE STRUCTURES, BIASED IN THE LINEAR REGION, FOLLOWED BY A LINEAR CURVE FIT. THE NW LAYER IS NOT REPORTED, AS IT IS CHALLENGING TO MEASURE DUE TO ITS IMPLEMENTATION DIRECTLY IN THE N-TYPE SUBSTRATE

| Layer          | Design ID | Sheet resistance                                   |

|----------------|-----------|----------------------------------------------------|

| P-well         | PW        | $(431 \pm 19) \mathrm{k}\Omega\mathrm{sq}^{-1}$    |

| Shallow n-type | SN        | $(1.03 \pm 0.01) \mathrm{k}\Omega\mathrm{sq}^{-1}$ |

| Shallow p-type | SP        | $(40.4 \pm 1.3) \mathrm{k}\Omega\mathrm{sq}^{-1}$  |

| Polysilicon    | PO        | $(14.0 \pm 0.1) \Omega \mathrm{sq}^{-1}$           |

| First metal    | M1        | $(47 \pm 3) \mathrm{m}\Omega\mathrm{sq}^{-1}$      |

Fig. 4. Layout design example of a NAND logic gate in the Fraunhofer IISB SiC CMOS technology, highlighting several feature sizes. The inset shows the local feature sizes of an nMOS device, which is identical for the pMOS or scaled for the channel width. The logic gate is built from 20  $\mu\text{m}\times6~\mu\text{m}$  nMOS and 80  $\mu\text{m}\times6~\mu\text{m}$  pMOS devices. Note that the PC layer is not used in this logic block.

have channel widths above 200  $\mu$ m are implemented through multiple fingers in parallel, within the same well and including a single guard ring.

#### III. PERFORMANCE

#### A. Technology Parameters

The reported structures are measured on wafer-level using a MicroTech Cascade probe station that is fitted with seven probe needles. The probe station is paired to an Agilant 4156C Precision Semiconductor Parameter Analyzer and IC-CAP measurement software. Measurements on higher temperature levels are performed on chip-level. The wafer-level results of the sheet resistance are listed in Table I. To evaluate the performance of the technology, the MOSFET threshold voltage, subthreshold slope, slope factor, and process transconductance are extracted from device measurements and reported in Table II.

The  $I_{\rm ds}/V_{\rm gs}$  curves of a selection of SiC nMOS and pMOS geometries at different temperature levels are measured and depicted in Fig. 5. The nMOS drain current scales as expected with the W/L ratio, which is less evident for the pMOS as it shows saturation effects. The pMOS current driving capability is very low, such that even the attached measurement equipment is a too large load. This is attributed to the relative large contact resistance and can be improved by optimizing the silicide to the p-type areas. The curves do show that this saturation effect is greatly reduced for increased W/L ratios, so that interfacing with off-chip loads is feasible.

Fig. 5. Measured  $I_{\rm ds}/V_{\rm gs}$  curves at different temperature levels with marked threshold voltage on die (0,0) of (a) 20  $\mu$ m  $\times$  6  $\mu$ m nMOS, (b) 60  $\mu$ m  $\times$  6  $\mu$ m nMOS, (c) 250  $\times$  6  $\mu$ m nMOS, (d) 80  $\mu$ m  $\times$  6  $\mu$ m pMOS, (e) 200  $\mu$ m  $\times$  6  $\mu$ m pMOS, and (f) 500  $\mu$ m  $\times$  6  $\mu$ m pMOS SiC devices. The devices are biased in the linear region at 0.2 and -2 V for nMOS and pMOS, respectively. The source and drain currents are equal, indicating no leakage current.

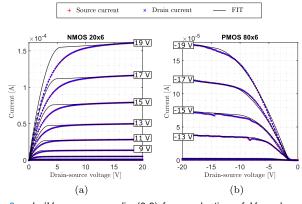

Fig. 6.  $l_{\rm ds}/V_{\rm ds}$  curves on die (0,0) for a selection of  $V_{\rm gs}$  values and (a) 20  $\mu{\rm m} \times$  6  $\mu{\rm m}$  nMOS and (b) 80  $\mu{\rm m} \times$  6  $\mu{\rm m}$  pMOS devices. The curves are fitted to the unified model for manual analysis [48] and are achieved by assuming a  $V_{\rm dsat,n}=2$  V,  $V_{\rm dsat,p}=-1$ ,  $\lambda_n=0.003$ , and  $\lambda_p=0.01$ . To account for deviation in the linear region, the transition point in the nMOS curves is moved to lower  $V_{\rm ds}$  by a factor 1/3 and the pMOS curves are shifted to higher  $V_{\rm ds}$  by -1.6 V. The source and drain currents are equal, indicating no leakage current.

The drain current magnitude for both nMOS and pMOS is highly dependent on temperature levels and shows less saturation effects for higher temperature. Furthermore, other parameters such as the mobility also improve with higher temperature, reaching 18.8 and  $9.8 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  for the largest nMOS and pMOS, respectively. Related to this limited current driving capability is the increased  $V_{ds}$  bias, which reduces the saturation effect and allows extraction of some technology parameters. However, this increased bias is likely to shift the threshold voltage toward more negative values and reduce the

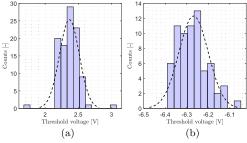

Fig. 7. Threshold voltage distributions of (a) nMOS and (b) pMOS devices, with a normal distribution fit in the dashed line that yields  $2.37\pm0.15$  and  $-6.27\pm0.07$  for the nMOS and pMOS distribution, respectively. All device geometries in Fig. 5 are considered which totals 102 devices for each plot. The amount of histogram bins are 15 and 11 for the nMOS and pMOS result, respectively.

#### **TABLE II**

MEAN VALUES OF THE THRESHOLD VOLTAGE  $V_{\rm TH}$ , SUBTHRESHOLD SLOPE S, SLOPE FACTOR n, PROCESS TRANSCONDUCTANCE PARAMETER k', AND MOBILITY  $\mu$  IN THE TECHNOLOGY AT ROOM TEMPERATURE, DERIVED FROM WAFER-LEVEL RESULTS OF 35 DIES. THE SINGLE DEVICE YIELD IS HIGH (>97%), WITH ONLY ONE DIE CONSISTENTLY BROKEN. THE  $\mu_p$  STANDARD DEVIATION IS HIGH DUE TO SIGNIFICANT NONLINEARITY IN THE  $I_{\rm DS}/V_{\rm GS}$  CURVES

| nMOS devices |                                                                   |                                                                  |                                                                |  |

|--------------|-------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|--|

| size         | $20  \mu m \times 6  \mu m$                                       | $60  \mu \mathrm{m} \times 6  \mu \mathrm{m}$                    | $250  \mu \text{m} \times 6  \mu \text{m}$                     |  |

| $V_{th,n}$   | $(2.23 \pm 0.12) \mathrm{V}$                                      | $(2.39 \pm 0.12) \mathrm{V}$                                     | $(2.48 \pm 0.07) \mathrm{V}$                                   |  |

| $S_n$        | $(0.20 \pm 0.03)  \mathrm{V}  \mathrm{dec}^{-1}$                  | $(0.20 \pm 0.01)  \mathrm{V}  \mathrm{dec}^{-1}$                 | $(0.18 \pm 0.02)  \mathrm{V}  \mathrm{dec}^{-1}$               |  |

| $n_n$        | $3.4 \pm 0.5$                                                     | $3.3 \pm 0.2$                                                    | $3.1 \pm 0.4$                                                  |  |

| $k'_n$       | $(0.45 \pm 0.37)  \mu A  V^{-2}$                                  | $(0.46 \pm 0.37)  \mu A  V^{-2}$                                 | $(0.48 \pm 0.37)  \mu A  V^{-2}$                               |  |

| $\mu_n$      | $(14.2 \pm 2.6)  \mathrm{cm}^2  \mathrm{V}^{-1}  \mathrm{s}^{-1}$ | $(14.5 \pm 0.4) \mathrm{cm}^2 \mathrm{V}^{-1} \mathrm{s}^{-1}$   | $(14.5 \pm 0.3) \mathrm{cm}^2 \mathrm{V}^{-1} \mathrm{s}^{-1}$ |  |

| pMOS devices |                                                                   |                                                                  |                                                                |  |

| size         | 80 µm × 6 µm                                                      | $200  \mu \mathrm{m} \times 6  \mu \mathrm{m}$                   | $500  \mu \mathrm{m} \times 6  \mu \mathrm{m}$                 |  |

| $V_{th,p}$   | $(-6.25 \pm 0.07) \mathrm{V}$                                     | $(-6.28 \pm 0.07) \mathrm{V}$                                    | $(-6.26 \pm 0.05) \text{ V}$                                   |  |

| $S_p$        | $(0.25 \pm 0.07) \mathrm{V} \mathrm{dec}^{-1}$                    | $(0.26 \pm 0.09)  \mathrm{V  dec^{-1}}$                          | $(0.26 \pm 0.08) \mathrm{V} \mathrm{dec}^{-1}$                 |  |

| $n_p$        | $4.2 \pm 1.1$                                                     | $4.4 \pm 1.5$                                                    | $4.3 \pm 1.3$                                                  |  |

| $k_p'$       | $(0.33 \pm 0.26) \mu\mathrm{AV^{-2}}$                             | $(0.39 \pm 0.30)  \mu A  V^{-2}$                                 | $(0.38 \pm 0.29)  \mu A  V^{-2}$                               |  |

| $\mu_p$      | $(0.1 \pm 0.1)  \mathrm{cm}^2  \mathrm{V}^{-1}  \mathrm{s}^{-1}$  | $(0.2 \pm 0.2)  \mathrm{cm}^2  \mathrm{V}^{-1}  \mathrm{s}^{-1}$ | $(0.1 \pm 0.1) \mathrm{cm^2  V^{-1}  s^{-1}}$                  |  |

subthreshold swing. The reported asymmetry of the threshold voltages could be addressed in future work by means of a blanket p-type ion implantation to shift both nMOS and pMOS threshold voltages toward more positive levels.

The  $I_{\rm ds}/V_{\rm ds}$  curves for a selection of  $V_{\rm gs}$  values and minimum size nMOS and pMOS devices are measured and depicted in Fig. 6. The nMOS drain current shows both quadratic and linear increase in magnitude for lower and higher  $V_{\rm gs}$  values, respectively, illustrating that both saturation and velocity saturation are relevant. For the pMOS device, the behavior is close to linear increasing drain current, indicating mostly velocity saturation. The unified model for manual analysis [48] is fitted to the curves by empirical determination of the fitting parameters. To achieve a good fit, the transition point from linear to saturation of the nMOS devices is moved to lower  $V_{\rm ds}$  levels and the starting point of the pMOS fit is shifted to higher  $V_{\rm ds}$  levels. This shift for the pMOS also validates the higher  $V_{\rm ds}$  used for the  $V_{\rm th}$  extraction.

The threshold voltages  $V_{\rm th}$  are extracted using the secondderivative method [49] and the distribution of the extracted values is given in Fig. 7. The subthreshold slopes S are extracted by considering the maximum of the inverse slope and are used to calculate the slope factors n [48]. The reported slope factors are far from the established silicon-based technologies [50], [51] that typically have n < 2. The process

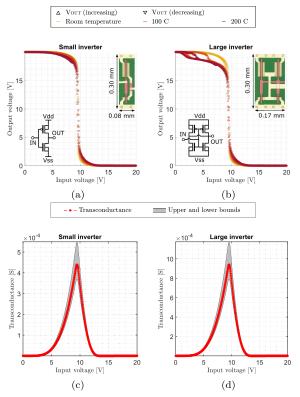

Fig. 8. Measured  $V_{\rm out}/V_{\rm in}$  curves at different temperature levels of (a) minimum size inverter and (b) large inverter and the calculated  $G_m/V_{\rm in}$  curves of (c) minimum size inverter and (d) large inverter on die (0,0). The lower and upper limits of  $G_m$  are determined by considering the standard deviation of n and the insets show the respective circuits and micro photographs. The inverter yield is >97% over 35 dies for both variants, with only one die consistently broken.

transconductance parameter k' is extracted at high  $V_{\rm gs}$  and  $V_{\rm ds}$ , as the corrections to the fit do not allow extraction in the linear region. Therefore, k' is extracted at  $V_{\rm ds}=20~{\rm V}$  and  $V_{\rm gs}>5~{\rm V}$  or  $V_{\rm gs}<-12~{\rm V}$  for nMOS or pMOS, respectively. Finally, the device mobility is extracted in linear mode.

#### B. Digital and Analog Circuit Blocks

This SiC CMOS technology is currently rated for operation at a 20 V supply voltage with input and output signals in the same range. Future work would benefit from reducing this for better matching with standard ICs. The  $V_{\rm out}/V_{\rm in}$  responses of two inverter variants are given in Fig. 8(a) and (b), with corresponding circuits and micro-photographs in the insets. The small inverter is implemented in the minimum size nMOS (20  $\mu$ m × 6  $\mu$ m) and pMOS (80  $\mu$ m × 6  $\mu$ m). The large inverter connects two minimum size devices in parallel, which doubles the device W/L ratio. The only significant effect by increased temperature is a lower high output level of the large inverter. The switching voltages are found at the maximum  $I_{\rm dd}$  current and equal (9.2  $\pm$  0.7) V and (9.2  $\pm$  0.5) V for the small and large inverter, respectively. The switching voltage  $V_m$  is calculated [48] through

$$V_{m} = \frac{\alpha \left(V_{\text{th},n} + \frac{V_{\text{dsat},n}}{2}\right) + \beta \left(V_{\text{dd}} + V_{\text{th},p} + \frac{V_{\text{dsat},p}}{2}\right)}{\alpha + \beta}$$

(1)

where  $\alpha = k_n V_{\text{dsat},n}$  and  $\beta = k_p V_{\text{dsat},p}$ . This results in a switching voltage of 9.4 V, which is close to the measured

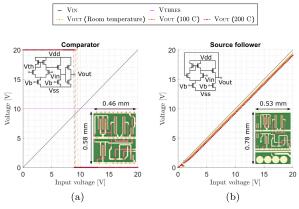

Fig. 9. Measured  $V_{\rm out}/V_{\rm in}$  curves at different temperature levels of (a) comparator for a threshold of 10 V and (b) source follower on die (0,0). Both circuits are biased at 1.5 V using an off-chip source and the insets show the respective circuits and micro photographs. All body contacts are connected to  $V_{\rm SS}$  or  $V_{\rm dd}$  for nMOS and pMOS, respectively.

value and therefore validates the parameters in Table II, as the inverter matches the assumption of high  $V_{\rm ds}$  and  $V_{\rm gs}$  for each device. Furthermore, a suggestion can be made for the geometry ratio of future implementations by calculating the ratio [48] for  $V_m=1/2\cdot V_{\rm dd}$  through

$$\frac{W_p/L_p}{W_n/L_n} = \frac{k'_n V_{\text{dsat},n} \left( V_m - V_{\text{th},n} - \frac{V_{\text{dsat},n}}{2} \right)}{k'_p V_{\text{dsat},p} \left( V_{\text{dd}} - V_m + V_{\text{th},p} + \frac{V_{\text{dsat},p}}{2} \right)}$$

(2)

which evaluates to 6 at room temperature, indicating that the current design ratio of 4 should be increased. Certainly, future improvements to the pMOS device should re-evaluate this ratio. The inverter logic gate can also be considered as a push-pull-based transconductance amplifier, with the inverter transconductance  $G_m$  given by adding the gate–drain small signal transconductance of the nMOS and pMOS devices [50]. The resulting  $G_m/V_{\rm in}$  curves are given in Fig. 8(c) and (d) and the maximum transconductance is found at the switching voltage and equals to approximately 0.22–0.33 mS and 0.44–0.66 mS for the small and large inverter, respectively.

The dc characteristics of NAND and NOR logic gates over 26 dies were verified through investigation of every input combination and the resulting output voltage, with a tolerance of 10% ( $V_{\text{low}}$  < 2 V and  $V_{\text{high}}$  > 18 V). Two NAND gates are considered, one with the layout in Fig. 4 and one with an additional polysilicon crossover, with wafer-level yields of >93% and >88%, respectively. Similarly, two NOR gates are measured, both with a wafer-level yield of >88%. With a few logic gates, a digital 1-bit multiplexer (20 MOS devices,  $0.44 \text{ mm} \times 0.58 \text{ mm}$ ) was implemented and verified over 26 dies with a wafer-level yield of >93%. Inverters and passgates are combined to implement a 1-bit analog multiplexer (8 MOS devices, 0.48  $\mu$ m  $\times$  0.58  $\mu$ m) and its operation was verified over 26 dies with a wafer-level yield of >92\% or >84% for a maximum offset of 1 V (5% of total range) or 0.5 V (2.5% of total range), respectively. Increasing the device count further, a D-flip-flop block (66 MOS devices,  $1.54 \ \mu m \times 0.58 \ \mu m$ ) was implemented and its operation verified over 26 dies with a wafer-level yield of >93%. This indicates that the true yield of single logic gates must be much

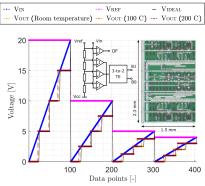

Fig. 10. Measured  $V_{\rm out}/V_{\rm in}$  curves of the 2-bit ADC at different temperature levels, for input ranges set by  $V_{\rm ref}$  at 20, 10, 5, and 4 V on die (-3, -2). The circuit is biased at 1.5 V using an off-chip voltage source and the insets show the respective circuit and micro-photograph. The comparator in Fig. 9(a) and 20 k $\Omega$  SN resistors are used in this design.

higher than the given lower boundary, to achieve such high yield for the D-flip-flop.

A two-stage amplifier, implemented using an nMOS differential input pair and a common drain stage, with an output inverter, is considered as a comparator. The two stages are biased through a single off-chip voltage source of 1.5 V. The switching behavior of the comparator is measured for every integer  $\{1, 2, ..., 19\}$  V level of the threshold voltage  $V_{\text{thres}}$ input for a linear increase sweep of the input voltage  $V_{\rm in}$ over the entire range. The comparator  $V_{\text{out}}/V_{\text{in}}$  response for a  $V_{\text{thres}}$  of 10 V is given in Fig. 9(a), with corresponding circuit and device micro-photograph. When constraining the switching offset voltage to a maximum of 1 V (5% of total range) or 0.5 V (2.5% of total range), the comparator yield over 26 dies is >88% or >73%, respectively, at room temperature. Increased temperature also significantly increases the comparator offset and thus reduces its yield if considering the same maximum allowed offset.

A unity-gain buffer, or source follower, is implemented using the same two-stage amplifier architecture as in the comparator. The  $V_{\rm out}/V_{\rm in}$  response is given in Fig. 9(b), with the corresponding circuit and device micro-photograph. Typical behavior is the output of  $\sim 0$  V for low input levels (<2 V) and some devices also show clipping for high input levels. When constraining the mean offset voltage between input and output to a maximum of 1 V (5% of total range) or 0.5 V (2.5% of total range), the source follower yield over 26 dies is >92% or >80%, respectively, at room temperature. Similar to the comparator, the source follower offset increases with temperature.

Digital and analog blocks are combined in a 2-bit resistive ladder analog-to-digital converter (ADC) with a tunable input range (68 MOS devices) through  $V_{\rm ref}$ , of which the response of four ranges is depicted in Fig. 10. The ideal ADC response  $V_{\rm ideal}$  is included and the two digital output bits  $B_0$  and  $B_1$  are used to calculate the corresponding output voltage  $V_{\rm out}$ . The overflow bit OF is not measured due to the 7 probe maximum taken into account in the layout design. The maximum differential nonlinearity (DNL) equals to  $1.5 \pm 0.5$  LSB, the maximum integral nonlinearity (INL) equals to  $1.3 \pm 0.5$  LSB, and the yield is >75% over 28 dies

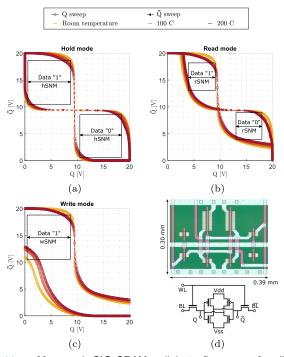

Fig. 11. Measured  $Q \not = Q$  SRAM cell butterfly curves for different temperature levels of (a) hold, (b) read, and (c) write mode including (d) circuit and micro-photograph on die (0, -2). A sweep of Q or Q and the maximum size squares are drawn for SNM derivation and a single sweep is depicted for the write mode in favor of readability. All body contacts are connected to  $V_{\rm SS}$  or  $V_{\rm dd}$  for nMOS and pMOS, respectively.

at room temperature. The larger offset of the comparators at higher temperatures translates to larger offsets of the ADC, especially in the lower operating ranges.

Finally, the characterization curves of a static random access memory (SRAM) cell in different modes, commonly known as the butterfly curves, are extracted to find the respective static noise margins (SNMs) that give indication of the data state stability. The reported SNM values are taken from the minimum between the data 0 and 1 cases. The wafer-level results over 28 dies have a yield of >85%. The hold mode, or standby mode, characteristics are depicted in Fig. 11(a) and represents two inverters connected in parallel in opposite direction as WL, BL, and BL are connected to ground. The corresponding hSNM equals to 7.1  $\pm$  10 V, which is close to the ideal value of 10 V considering the technology supply voltage. The read mode characteristics are depicted in Fig. 11(b), which shows the effect of read stress on the ability of the device to pull the measured terminals to 0 V as WL, BL, and BL are connected to  $V_{\rm dd}$ . As a consequence, the SNM is inevitably reduced and the corresponding rSNM equals to  $4.4 \pm 0.7$  V. The write mode characteristics for the data 1 case are depicted in Fig. 11(c), of which the SNM derivation is slightly different as the largest square is drawn between the corresponding read and write mode curves. In this mode, WL and BL are connected to  $V_{\rm dd}$  and BL to ground when sweeping Q, while BL and BL are swapped when sweeping  $\bar{Q}$ . The corresponding wSNM equals to 7.5  $\pm$  0.9 V, which is even closer to the ideal value than the hSNM. All noise margins are reduced for the higher temperature levels, while retaining correct function. In comparison, the aforementioned results in the same technology of the group of Mantooth at the University of Arkansas found an hSNM and rSNM of 4.65 and 1.90 V, respectively, and did not report the wSNM [43]. The devices in this work have improved SNM values with a factor of 1.5 and 2.3 for the hSNM and rSNM, respectively.

The reports from devices to mixed-signal circuit implementations provide a thorough overview of the capabilities of the described technology. This open technology can be used in future implementations toward sensor integration and characterization in harsh environments.

#### IV. CONCLUSION

The state-of-the-art 6  $\mu$ m 4H-SiC CMOS technology overview is given and design considerations are provided. The presented devices were additionally measured up to a temperature of 200 °C. A selection of technology parameters is extracted from devices on wafer-level through dc analysis, including the threshold voltage, subthreshold slope, slope factor, and process transconductance parameter. The CMOS devices are not characterized by a steep subthreshold slope (see Table II), so a slower transition between the off and on state is expected. This implies that future digital SiC CMOS electronics designed in this technology will need to operate at low frequencies. Furthermore, the minimum size inverter is used for the validation of parameters and a recommendation for increasing the future nMOS and pMOS device geometry ratio is provided. Future implementations would moreover benefit from the investigation of device gate lengths below 6  $\mu$ m to reduce circuit footprints.

The single MOS device yield figures are high, considering the still premature level of integrated mixed signal technologies. Designed circuits with increased device count show similar yield levels >70%, further indicating great potential for future integration of higher device counts. The investigated blocks are inverters, NAND gates, NOR gates, 1-bit digital multiplexers, 1-bit analog multiplexers, D-flip-flops, push-pull transconductance amplifiers, comparators, source followers, 2bit ADC and SRAM cells. Compared to previous work in the same technology, the SRAM cells have greatly improved the SNM values. The performance does not compare with the state-of-the-art silicon implementations, but shows correct function and could therefore be used in environments where silicon-based devices would not be functional at all. Future work will benefit from including higher-level interconnect and analysis of on-chip passives.

#### **ACKNOWLEDGMENT**

The authors would like to thank the Delft University of Technology Else Kooi Laboratory staff and the Fraunhofer Institute for Integrated Systems and Devices Technology (IISB) Laboratory staff for processing support.

#### REFERENCES

- [1] J. Hornberger, A. B. Lostetter, K. J. Olejniczak, T. McNutt, S. M. Lal, and A. Mantooth, "Silicon-carbide (SiC) semiconductor power electronics for extreme high-temperature environments," in *Proc. IEEE Aerosp. Conf.*, vol. 4, Mar. 2004, pp. 2538–2555.

- [2] F. Roccaforte et al., "Challenges for energy efficient wide band gap semiconductor power devices," Phys. Status Solidi A, vol. 211, no. 9, pp. 2063–2071, Sep. 2014, doi: 10.1002/pssa.201300558.

- [3] IEEE Power Electronics Society. (2019). International Technology Roadmap for Wide Bandgap Power Semiconductors (ITRW). [Online]. Available: https://resourcecenter.ieee-pels.org/ roadmap/PELSPRO0020.html

- [4] P. M. Sarro, "Silicon carbide as a new MEMS technology," Sens. Actuators A, Phys., vol. 82, nos. 1-3, pp. 210-218, May 2000. [Online]. Available: http://www.sciencedirect.com/science/article/pii/ S0924424799003350

- [5] M. Mehregany, C. A. Zorman, N. Rajan, and C. H. Wu, "Silicon carbide MEMS for harsh environments," Proc. IEEE, vol. 86, no. 8, pp. 1594-1609, Aug. 1998.

- [6] D. G. Senesky, B. Jamshidi, K. B. Cheng, and A. P. Pisano, "Harsh environment silicon carbide sensors for health and performance monitoring of aerospace systems: A review," IEEE Sensors J., vol. 9, no. 11, pp. 1472-1478, Nov. 2009.

- R. Maboudian, C. Carraro, D. G. Senesky, and C. S. Roper, "Advances in silicon carbide science and technology at the micro- and nanoscales," J. Vac. Sci. Technol. A, Vac., Surf., Films, vol. 31, no. 5, Sep. 2013, Art. no. 050805, doi: 10.1116/1.4807902

- [8] L. M. Middelburg et al., "Maintaining transparency of a heated MEMS membrane for enabling long-term optical measurements on sootcontaining exhaust gas," Sensors, vol. 20, no. 1, p. 3, Dec. 2019.

- J. Mo, L. M. Middelburg, B. Morana, H. W. van Zeijl, S. Vollebregt, and G. Q. Zhang, "Surface-micromachined silicon carbide Pirani gauges for harsh environments," IEEE Sensors J., vol. 21, no. 2, pp. 1350-1357,

- [10] P. French, G. Krijnen, and F. Roozeboom, "Precision in harsh environments," Microsyst. Nanoeng., vol. 2, no. 1, pp. 1-12, Oct. 2016.

- W. Martienssen and H. Warlimont, Handbook of Condensed Matter and Materials Data. Germany: Springer, 2005.

- [12] T. Kimoto and J. A. Cooper, "Physical properties of silicon carbide," in Fundamentals Silicon Carbide Technology. Hoboken, NJ, USA: Wiley, 2014, ch. 2.

- [13] M. B. J. Wijesundara and R. G. Azevedo, Silicon Carbide Microsystems for Harsh Environments. USA: Springer, 2011.

- [14] R. A. R. Young et al., "High temperature digital and analogue integrated circuits in silicon carbide," Mater. Sci. Forum, vols. 740-742, pp. 1065-1068, Jan. 2013.

- [15] E. Ramsay et al., "High temperature CMOS circuits on silicon carbide," Mater. Sci. Forum, vols. 821-823, pp. 859-862, Jun. 2015.

- [16] A. Rahman, K. Addington, M. Barlow, S. Ahmed, H. A. Mantooth, and A. M. Francis, "A high temperature comparator in CMOS SiC," in Proc. IEEE 3rd Workshop Wide Bandgap Power Devices Appl. (WiPDA), Nov. 2015, pp. 236-240.

- [17] A. Rahman, S. Roy, R. C. Murphree, H. A. Mantooth, A. M. Francis, and J. Holmes, "A SiC 8 bit DAC at 400 °C," in Proc. IEEE 3rd Workshop Wide Bandgap Power Devices Appl. (WiPDA), Nov. 2015, pp. 241-246.

- [18] A. Rahman, A. M. Francis, S. Ahmed, S. K. Akula, J. Holmes, and A. Mantooth, "High-temperature voltage and current references in silicon carbide CMOS," IEEE Trans. Electron Devices, vol. 63, no. 6, pp. 2455-2461, Jun. 2016.

- [19] M. Barlow, S. Ahmed, H. A. Mantooth, and A. M. Francis, "An integrated SiC CMOS gate driver," in Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC), Mar. 2016, pp. 1646–1649.

- [20] N. Kuhns et al., "Complex high-temperature CMOS silicon carbide digital circuit designs," IEEE Trans. Device Mater. Rel., vol. 16, no. 2, pp. 105-111, Jun. 2016.

- [21] A. Rahman et al., "High-temperature SiC CMOS comparator and op-amp for protection circuits in voltage regulators and switch-mode converters," IEEE J. Emerg. Sel. Topics Power Electron., vol. 4, no. 3, pp. 935-945, Sep. 2016.

- [22] S. Roy et al., "A SiC CMOS digitally controlled PWM generator for high-temperature applications," IEEE Trans. Ind. Electron., vol. 64, no. 10, pp. 8364-8372, Oct. 2017.

- [23] A. Rahman et al., "High temperature data converters in silicon carbide CMOS," IEEE Trans. Electron Devices, vol. 64, no. 4, pp. 1426-1432, Apr. 2017.

- [24] Z. Stum, V. Tilak, P. Losee, E. Andarawis, and C. Chen, "300 °C silicon carbide integrated circuits," Mater. Sci. Forum, vols. 679-680, pp. 730-733, Mar. 2011.

- [25] R. Ghandi et al., "Silicon carbide integrated circuits with stable operation over a wide temperature range," IEEE Electron Device Lett., vol. 35, no. 12, pp. 1206-1208, Dec. 2014.

- [26] L. Lanni, B. G. Malm, M. Östling, and C.-M. Zetterling, "Lateral p-n-p transistors and complementary SiC bipolar technology," IEEE Electron Device Lett., vol. 35, no. 4, pp. 428-430, Apr. 2014.

- [27] C.-M. Zetterling et al., "Bipolar integrated circuits in SiC for extreme environment operation," Semicond. Sci. Technol., vol. 32, no. 3, 2017, Art. no. 034002. [Online]. Available: http://iopscience.iop.org/ 10.1088/1361-6641/aa59a7

- [28] L. Lanni, B. G. Malm, M. Östling, and C.-M. Zetterling, "500 °C bipolar integrated OR/NOR gate in 4H-SiC," IEEE Electron Device Lett.,

- vol. 34, no. 9, pp. 1091–1093, Sep. 2013. [29] L. Lanni, B. G. Malm, M. Östling, and C.-M. Zetterling, "ECL-based SiC logic circuits for extreme temperatures," in Silicon Carbide and Related Materials (Materials Science Forum), vol. 821. Freienbach, Switzerland: Trans Tech Publications, 2015, pp. 910-913.

- [30] R. Hedayati, L. Lanni, S. Rodriguez, B. G. Malm, A. Rusu, and C. M. Zetterling, "A monolithic 500 °C operational amplifier in 4H-SiC bipolar technology," IEEE Electron Device Lett., vol. 35, no. 7,

- pp. 693–695, Jul. 2014. [31] Y. Tian, L. Lanni, A. Rusu, and C.-M. Zetterling, "Silicon carbide fully differential amplifier characterized up to 500 °C," IEEE Trans. Electron Devices, vol. 63, no. 6, pp. 2242-2247, Jun. 2016.

- [32] S. Kargarrazi, H. Elahipanah, S. Rodriguez, and C.-M. Zetterling, "500 °C, high current linear voltage regulator in 4H-SiC BJT technology," IEEE Electron Device Lett., vol. 39, no. 4, pp. 548-551, Apr. 2018.

- [33] R. Hedayati, L. Lanni, B. G. Malm, A. Rusu, and C.-M. Zetterling, "A 500 °C 8-b digital-to-analog converter in silicon carbide bipolar technology," IEEE Trans. Electron Devices, vol. 63, no. 9, pp. 3445-3450, Sep. 2016.

- [34] D. J. Spry et al., "Processing and characterization of thousand-hour 500 °C durable 4H-SiC JFET integrated circuits," in High Temperature Electronics. USA: Int. Microelectron. Assembly Packag. Soc., 2016.

- [35] A. C. Patil, X.-A. Fu, M. Mehregany, and S. L. Garverick, "Fullymonolithic, 600 °C differential amplifiers in 6H-SiC JFET IC technol-

- ogy," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2009, pp. 73–76. [36] M. Sudow *et al.*, "An SiC MESFET-based MMIC process," *IEEE Trans.*

- Microw. Theory Techn., vol. 54, no. 12, pp. 4072–4078, Dec. 2006. C. Codreanu, M. Avram, E. Carbunescu, and E. Iliescu, "Comparison of 3C-SiC, 6H-SiC and 4H-SiC MESFETs performances," Mater. Sci.

- Semicond. Process., vol. 3, nos. 1–2, pp. 137–142, Mar. 2000. [38] J. A. Cooper, Jr., "Advances in SiC MOS technology," Phys. Status Solidi A, vol. 162, no. 1, pp. 305–320, Jul. 1997. R. Singh and A. R. Hefner, "Reliability of SiC MOS devices," Solid.

- State. Electron., vol. 48, pp. 1717–1720, Oct./Nov. 2004. [40] L. C. Yu, G. T. Dunne, K. S. Matocha, K. P. Cheung, J. S. Suehle, and K. Sheng, "Reliability issues of SiC MOSFETs: A technology for hightemperature environments," IEEE Trans. Device Mater. Rel., vol. 10,

- no. 4, pp. 418–426, Dec. 2010. [41] A. Abbasi *et al.*, "Characterization of a silicon carbide BCD process for 300 °C circuits," in Proc. IEEE 7th Workshop Wide Bandgap Power Devices Appl. (WiPDA), Oct. 2019, pp. 231–236.

- [42] M. Albrecht, T. Erlbacher, A. Bauer, and L. Frey, "Improving 5 V digital 4H-SiC CMOS ICs for operating at 400 °C using PMOS channel implantation," Mater. Sci. Forum, vol. 963, pp. 827-831, Jul. 2019.

- A. Abbasi et al., "High temperature memory design, implementation, and characterization in 1 µm SiC CMOS technology," in High Temperature Electronics Network. U.K.: Int. Microelectron. Assembly Packag. Soc., 2019.

- [44] C. D. Matthus, A. Burenkov, and T. Erlbacher, "Optimization of 4H-SiC photodiodes as selective UV sensors," in Proc. Eur. Conf. Silicon

- Carbide Rel. Mater. (ECSCRM), Sep. 2016, pp. 622–625. [45] L. D. Benedetto, G. D. Licciardo, T. Erlbacher, A. J. Bauer, and A. Rubino, "A 4H-SiC UV phototransistor with excellent optical gain based on controlled potential barrier," IEEE Trans. Electron Devices, vol. 67, no. 1, pp. 154–159, Jan. 2019. [46] C. D. Matthus *et al.*, "Feasibility of 4H-SiC *p-i-n* diode for sensitive

- temperature measurements between 20.5 K and 802 K," IEEE Sensors J., vol. 19, no. 8, pp. 2871–2877, Apr. 2019. [47] S. Kim *et al.*, "Ohmic contact mechanism for Ni/C-faced 4H-n-SiC

- substrate," J. Nanomater., vol. 2019, Dec. 2019, Art. no. 5231983.

- [48] J. M. Rabaey, A. Chandrakasan, and B. Nikolić, Digital Integrated Circuits (Prentice Hall Electronics and VLSI Series). USA: Pearson,

- A. Ortiz-Conde, F. J. G. Sánchez, J. J. Liou, A. Cerdeira, M. Estrada, and Y. Yue, "A review of recent MOSFET threshold voltage extraction methods," Microelectron. Rel., vol. 42, nos. 4-5, pp. 583-596, Apr./May 2002.

- [50] L. H. Rodovalho, "Push-pull based operational transconductor amplifier topologies for ultra low voltage supplies," Analog Integr. Circuits Signal

- Process., vol. 106, pp. 111–124, Jan. 2021. L. H. Rodovalho, O. Aiello, and C. R. Rodrigues, "Ultra-low-voltage inverter-based operational transconductance amplifiers with voltage gain enhancement by improved composite transistors," Electronics, vol. 9, no. 9, p. 1410, Sep. 2020.