# Multichannel LC ADC to Record Atrial Electograms

Aurojyoti Das

# Multichannel LC ADC

to Record Atrial Electrograms

by

Aurojyoti Das

to obtain the degree of Master of Science in Electrical Engineering

at the Delft University of Technology,

to be defended publicly on Friday August 23, 2019 at 10:00 AM.

Student number: 4737652

Thesis Project: August, 2018 - August, 2019

Thesis committee: Prof. dr. ir. W. A. Serdijn, TU Delft, supervisor

Dr. Ir. C. J. M. Verhoeven, TU Delft

Dr. V. Valente, University College London & TU Delft

Ir. S. Rout, TU Delft

# ABSTRACT

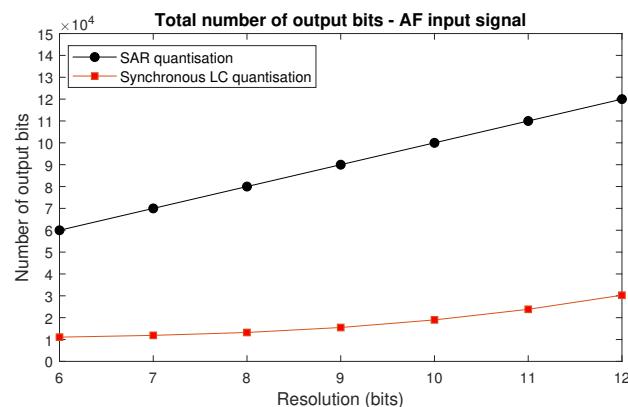

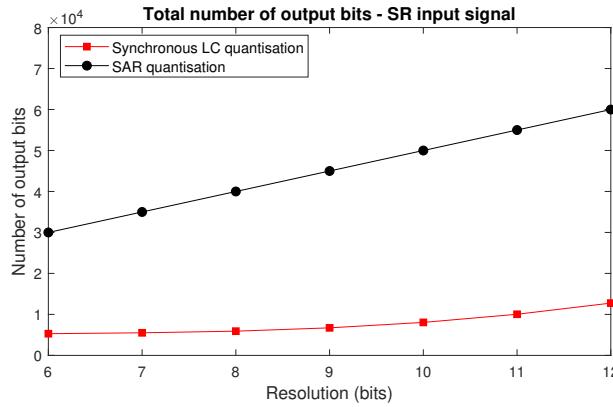

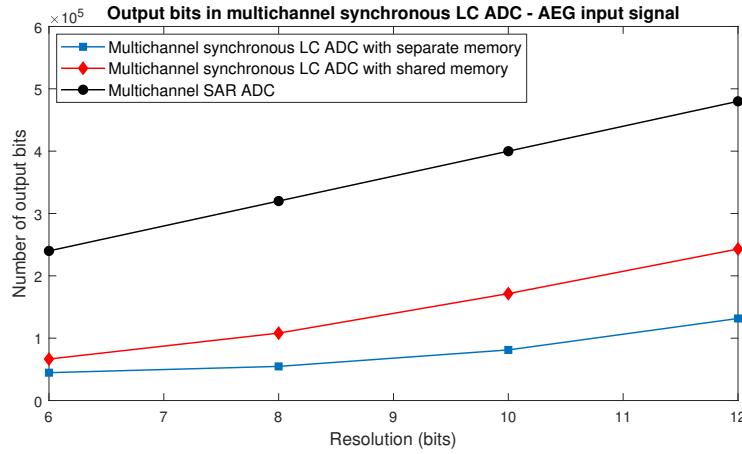

Biosignals such as electroencephalogram (EEG), electrocorticogram (ECoG), atrial electrogram (AEG) etc. are being recorded from multiple channels simultaneously to improve the spatial resolution of the signals. Conventional multichannel synchronous Analog-to-Digital Converters (ADCs) are used to convert the analog continuous time signals into discrete digital values. Several biosignals have a sparsity in time domain as they have fast-rising peaks in between periods of low activity. Use of conventional synchronous ADCs for conversion of such signals is not an efficient approach as their operation is constant, irrespective of the activity of the input signals. Asynchronous ADCs such as level-crossing (LC) ADCs exploit the sparsity of biosignals and thus their operation is activity-dependent. However, multichannel configurations of LC ADCs do not yet exist. This problem is investigated in this work and a new ADC architecture is presented that can combine synchronous sampling with level-crossing quantisation method while converting input signals from several channels simultaneously. The synchronous LC ADC presented in this work achieves 3.37 times reduction in quantisation steps and 6 times reduction in number of output bits generated during conversion of AEG signals as compared to conventional synchronous ADCs. The problem in existing LC ADCs of data overhead in adaptive resolution technique is solved through a novel method named split resolution technique which is also presented in this work.

# PREFACE

*Aurojyoti Das,

Delft, August 2019*

अनुगच्छति प्रवाह

(Anugacchati Pravahah)

Translation: Go with the flow

**The sanskrit expression stated above is the guiding light for this work. As in life and in engineering, the input affects everything. Rather than trying to manipulate the input fruitlessly, it is better to exploit what the input has to offer; it is better to go with the flow. The following work is inspired by this wisdom, and implements the same in a biosignal recording system.**

# ACKNOWLEDGEMENTS

I am grateful to several people who have helped me, accompanied me and inspired me in this journey. Firstly I would like to thank Wouter for the freedom and support he gave me in exploring ideas on my own and also for inspiring me to look for different perspectives which are normally not considered. I would like to thank Alessandro and Sampi for guiding me throughout the project and supporting me whenever I needed their help.

I am grateful to everyone in Bioelectronics group for their engaging discussions and the fun times we spent together. I will miss the movie nights, borrel and the (often long) monthly meetings.

I thank my friends at 'ME house' for all the fun evenings, chai sessions and weekend parties. I would not have survived without their support. I am grateful to Shoubhik for helping me even with the smallest doubts.

I thank my friends and family back home whose love and support encouraged me and kept my spirits up. Lastly, I would like to thank my parents for always believing in me and for encouraging me to take up new challenges every day.

*Aurojyoti Das

Delft, August 2019*

# CONTENTS

|                                                                     |     |

|---------------------------------------------------------------------|-----|

| Title                                                               | i   |

| Abstract                                                            | iii |

| Preface                                                             | v   |

| Acknowledgements                                                    | vii |

| 1 Introduction                                                      | 1   |

| 1.1 Background                                                      | 1   |

| 1.2 Problem Statement                                               | 1   |

| 1.3 Research Questions                                              | 3   |

| 1.4 Structure of Report                                             | 3   |

| 2 Level Crossing ADC                                                | 5   |

| 2.1 Synchronous Recording vs Asynchronous Recording                 | 5   |

| 2.2 Level Crossing ADC                                              | 6   |

| 2.2.1 Fixed Window LC ADC                                           | 6   |

| 2.2.2 Floating Window LC ADC                                        | 7   |

| 2.3 Literature Review                                               | 7   |

| 2.4 Conclusions                                                     | 10  |

| 3 System Level Design Considerations                                | 11  |

| 3.1 System Requirements                                             | 11  |

| 3.2 Modelling Level Crossing ADC                                    | 12  |

| 3.3 Split Resolution: A Proposed Alternative to Adaptive Resolution | 15  |

| 3.4 Architectures Considered for Multichannel LC ADC                | 19  |

| 3.4.1 Spatially Correlated Sampling                                 | 19  |

| 3.4.2 Time-Multiplexed LC ADC                                       | 19  |

| 3.4.3 Asynchronous Multiplexed LC ADC                               | 20  |

| 3.4.4 Encoding Output from Multiple Channels                        | 22  |

| 3.4.5 Coarse-Fine Architecture                                      | 22  |

| 3.4.6 Synchronous LC ADC                                            | 23  |

| 3.5 Comparison of Architectures                                     | 26  |

| 3.6 Conclusions                                                     | 26  |

| 4 Proposed Multichannel LC ADC                                      | 29  |

| 4.1 Modelling of synchronous LC ADC                                 | 29  |

| 4.2 Estimation of Quantisation Clock Frequency                      | 30  |

| 4.3 Activity-Dependent Quantisation                                 | 32  |

| 4.4 Activity-Dependence of Output                                   | 33  |

| 4.5 Modelling Split Resolution technique in synchronous LC ADC      | 35  |

| 4.6 Modelling of MLC ADC                                            | 36  |

| 4.7 Shared reference memory for multichannel synchronous LC ADC     | 37  |

| 4.8 Conclusions                                                     | 38  |

| 5 Circuit Implementation of Multichannel Synchronous LC ADC         | 41  |

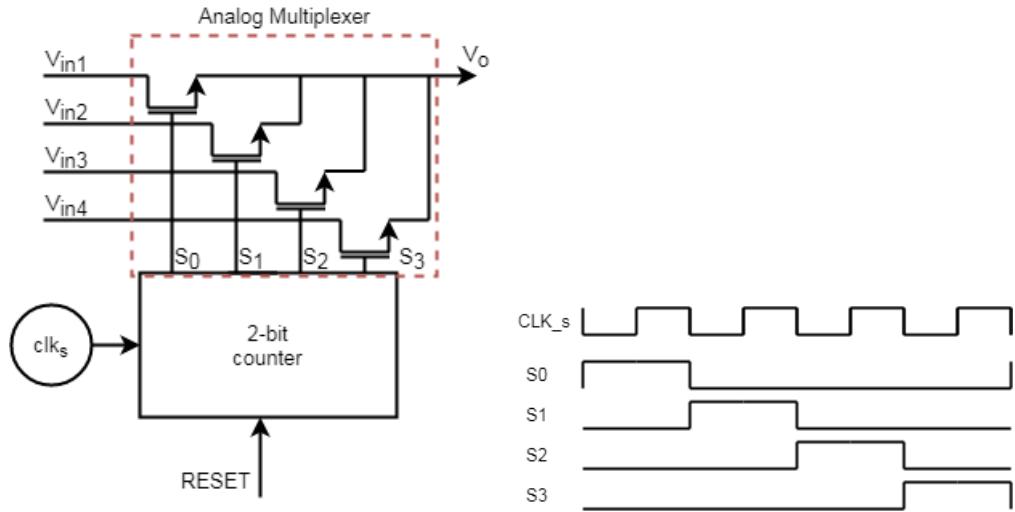

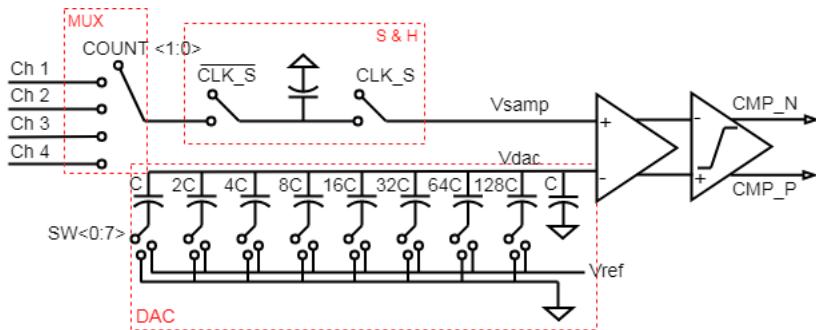

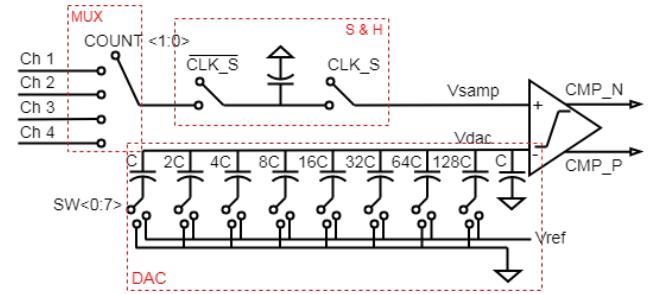

| 5.1 Multiplexing Block                                              | 41  |

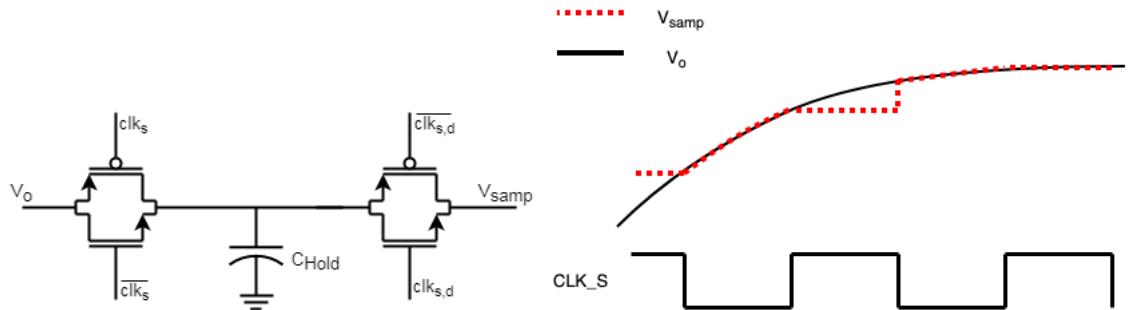

| 5.2 Sample & Hold                                                   | 42  |

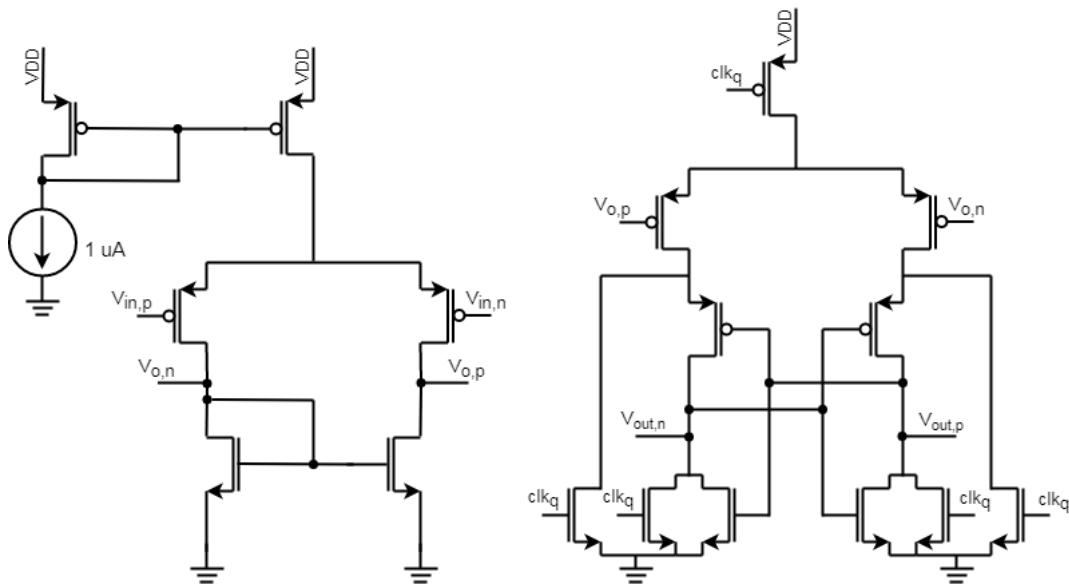

| 5.3 Comparator and Preamplifier                                     | 42  |

| 5.4 DAC                                                             | 43  |

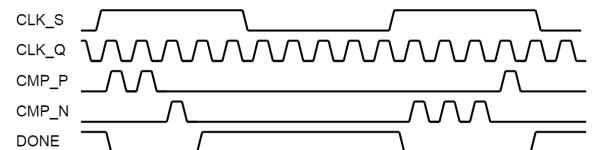

| 5.5 Control Logic Block                                             | 43  |

---

|       |                                                                                                                    |    |

|-------|--------------------------------------------------------------------------------------------------------------------|----|

| 5.6   | Reference Multichannel SAR ADC Design for comparison of performance . . . . .                                      | 45 |

| 5.7   | Conclusions . . . . .                                                                                              | 45 |

| 6     | Results and Discussion . . . . .                                                                                   | 47 |

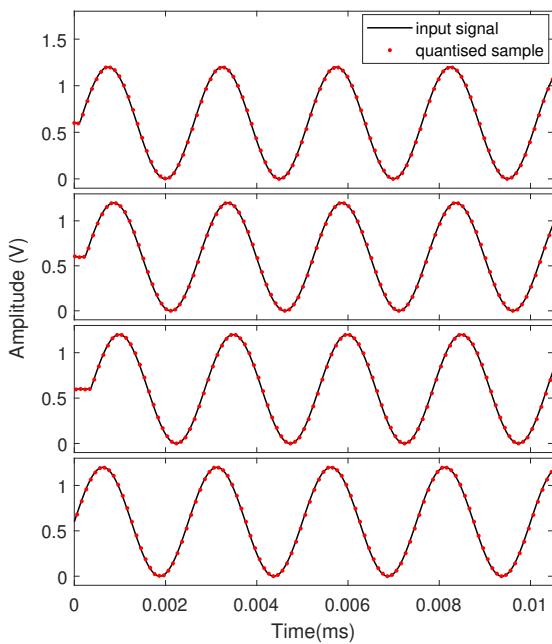

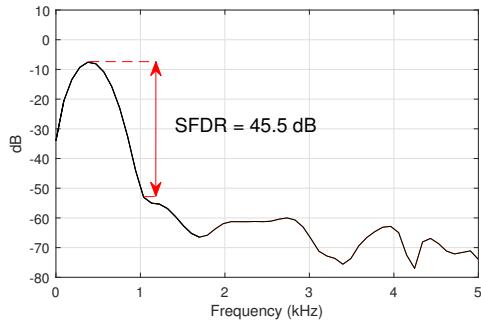

| 6.1   | Results for sinusoidal input . . . . .                                                                             | 47 |

| 6.2   | Results for AEG input . . . . .                                                                                    | 50 |

| 6.3   | Discussion . . . . .                                                                                               | 51 |

| 6.4   | Conclusions . . . . .                                                                                              | 52 |

| 7     | Conclusions and Future Propositions . . . . .                                                                      | 53 |

| 7.1   | Conclusions . . . . .                                                                                              | 53 |

| 7.2   | Summary of contributions . . . . .                                                                                 | 54 |

| 7.3   | Recommendations for Future Work . . . . .                                                                          | 55 |

|       | Appendices . . . . .                                                                                               | 57 |

| A     | Models . . . . .                                                                                                   | 59 |

| A.1   | VerilogA model for single-channel synchronous LC ADC . . . . .                                                     | 59 |

| A.1.1 | Sample and Hold . . . . .                                                                                          | 59 |

| A.1.2 | Comparator . . . . .                                                                                               | 59 |

| A.1.3 | Control logic block and DAC . . . . .                                                                              | 60 |

| A.2   | VerilogA model for multi-channel synchronous LC ADC . . . . .                                                      | 61 |

| A.2.1 | Counter for Analog MUX . . . . .                                                                                   | 61 |

| A.2.2 | Analog MUX . . . . .                                                                                               | 61 |

| A.2.3 | Logic control block and DAC . . . . .                                                                              | 62 |

| A.3   | MATLAB model of single channel synchronous LC ADC . . . . .                                                        | 63 |

| A.4   | MATLAB model of single channel synchronous LC ADC with split resolution . . . . .                                  | 64 |

| A.5   | MATLAB model of multichannel synchronous LC ADC with a shared memory across all channels . . . . .                 | 65 |

| B     | Digital Logic . . . . .                                                                                            | 67 |

| B.1   | Control Logic Block of synchronous LC ADC with 8-bit quantiser resolution and split resolution technique . . . . . | 67 |

| B.2   | Control Logic Block of multichannel synchronous LC ADC with 10-bit resolution . . . . .                            | 70 |

| B.3   | Control Logic Block of SAR ADC . . . . .                                                                           | 72 |

| C     | Simulation Setup . . . . .                                                                                         | 73 |

| D     | Paper accepted at BioCAS 2019 . . . . .                                                                            | 75 |

|       | Bibliography . . . . .                                                                                             | 81 |

# 1

## INTRODUCTION

### 1.1. BACKGROUND

Developments in bio-signal recording systems have enabled deeper investigation of medical conditions. Down-scaling of transistor feature sizes and design of low-power circuits have enabled use of microchips in implants and wearable devices. Bio-signals from several locations can now be recorded simultaneously by using a single device. The increased density of acquired data points provides a better understanding of the underlying medical conditions. These benefits however come at a cost of increased design complexity of the device and higher power consumption owing to increased data transmission rates. Power consumption is particularly exacerbated for wireless modes of data transmission which is critical for implantable and wearable devices. This project explores possibilities of finding a solution to these problems through a novel data conversion approach.

### 1.2. PROBLEM STATEMENT

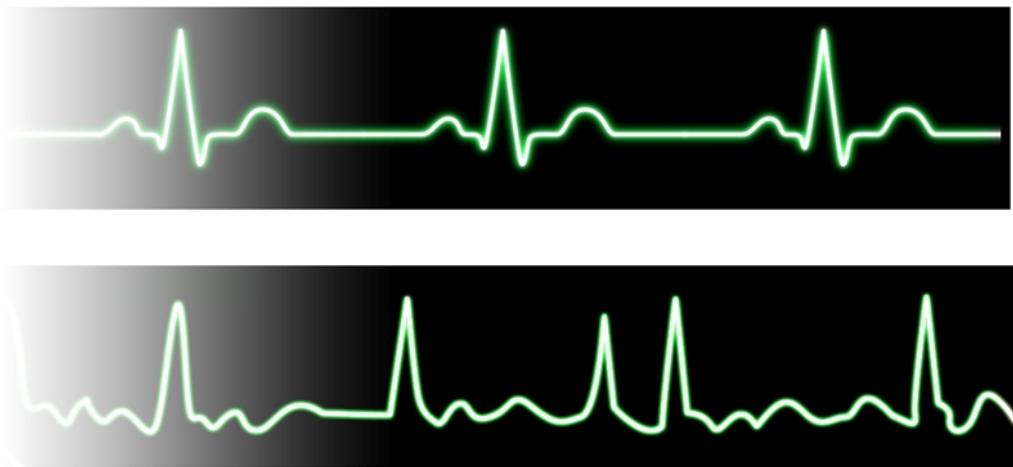

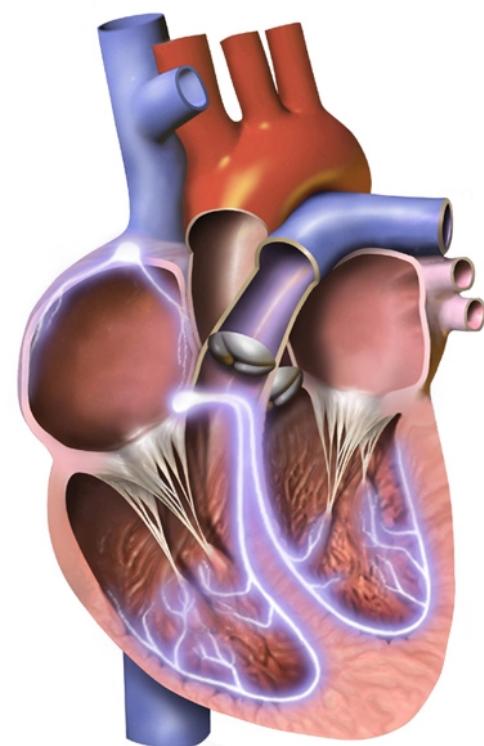

Atrial fibrillation (AF) is a medical condition which causes irregularities in the electrical impulses conducted across the heart and thus adversely affects its regular rhythm. While electrocardiograms (ECGs) can help in detection of AF, they cannot help in localising the origin of AF sources and identification of the substrate perpetuating AF. Electrical paths of conduction through the cardiac muscles need to be analyzed to determine the source of the condition and to formulate methods for therapy. Atrial electrograms (AEGs) are recorded from the atrial myocardium to accomplish this [1].

Recording of AEGs from multiple locations simultaneously is helpful in the analysis of the condition [2]. However, the current setup used for recording the AEGs from multiple locations involves transmitting the analog input signals across a long cable which is then conditioned and converted into digital values. This setup suffers from addition of interference and disturbance to the input signal captured by the electrodes.

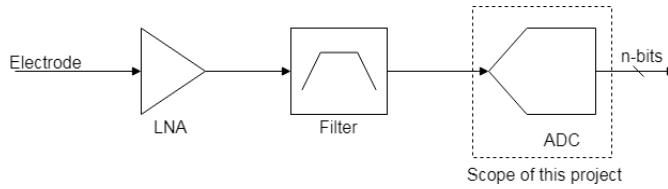

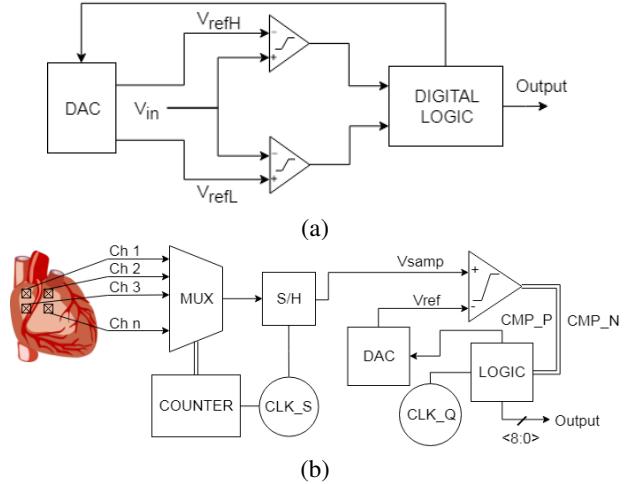

This problem can be mitigated by using an IC positioned near the recording patch which consists of the analog front ends (AFEs) for all the recording channels. The AFE consists of a low noise amplifier (LNA), a filter and an analog to digital converter (ADC) which amplify, filter and convert the analog signal into the discrete digital values, respectively. Block diagram of an AFE is shown in Fig.1.1. The converted signal is then stored in a digital memory and can be used later for signal analysis. The challenge in creating an IC for a multichannel recording system is to fit the AFEs for all the channels together within the area and power constraints.

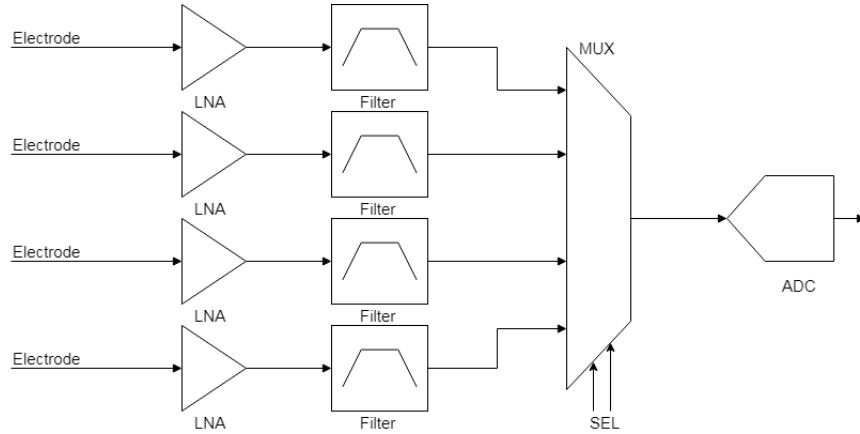

Different approaches could be adopted to design such a multichannel recording system. A separate AFE could be used for each channel and signal could be converted in each AFE independently. This approach is not very efficient as it would require a large area for the IC and power would be consumed in ADCs for each separate channel. Another approach could be to share some components of the AFE among several channels, as shown in Fig.1.2. In this approach the ADC is time-shared among several channels and at a given instant of time the signal from one of the channels undergoes conversion in the ADC [3]. This is repeated

Figure 1.1: Conventional analog front end (AFE) with low noise amplifier (LNA), filter and analog to digital converter (ADC).

Figure 1.2: Multichannel analog front end with time-shared ADC.

for each of the channels in a round-robin fashion within a fixed number of clock cycles. Hence, a substantial amount of area can be saved through this approach. At the same time the time-multiplexed ADC needs to operate multiple times faster than a regular ADC to maintain the same sampling rate for each channel. The multiplicative factor depends on the number of channels being multiplexed to the ADC. Time-multiplexing is a good approach for bio-signal recording systems as the bandwidth of bio-signals is limited to a few KHz and hence an ADC with a sampling rate in the range of kS/s would be applicable.

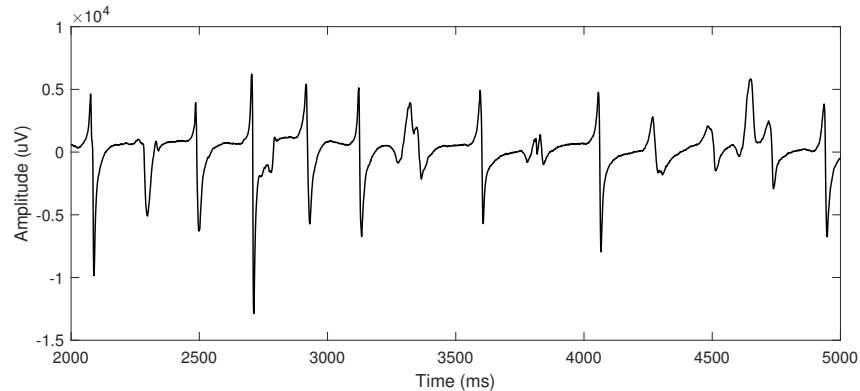

Figure 1.3: Example of a typical atrial electrogram.

Several types of ADCs such as Nyquist Rate ADCs and  $\Sigma\Delta$  ADCs are used in such AFEs. In recent times the SAR ADC has gained popularity owing to its simple operating principle and low power consumption [4]. It follows the synchronous sampling principle, i.e. it generates a sample with every clock cycle as per the sampling rate. However, some signals have minimal activity for considerable duration of time, as shown in Fig. 1.3. This can be seen as sparsity in time domain. For these kind of signals, the synchronous recording method is not efficient as the signal is sampled even though there is no change in the input signal. In this

scenario, asynchronous recording methods are a better choice [5]. In the asynchronous recording method a constant sampling rate is not used, but rather the signal is sampled only when a property (such as amplitude) of the input signal changes.

Level-crossing (LC) sampling is one such asynchronous recording method. In LC sampling the signal is sampled when it crosses a preset reference level. Thus when the signal is stagnant at any amplitude, no samples are generated. The output of synchronous ADCs is an  $n$ -bit digital value whereas in LC ADCs the output is just 2 bits which denote the time and direction of level-crossing. Hence, the number of output wires are reduced to just 2. This can be further reduced to 1 by using an encoding scheme [6]. This reduces the amount of data generated by the ADC as well. These advantages make the LC ADC an attractive option in applications where wiring complexity and storage space are critical.

### 1.3. RESEARCH QUESTIONS

While synchronous ADCs such as SAR ADCs are used in multichannel configurations by using the time-multiplexing approach [3], multichannel asynchronous ADCs have not yet been developed. As explained above, they offer an advantage over synchronous ADCs in the conversion of biosignals. Moreover, the AEG signal, much like the ECG signal has its own unique characteristics. Exploiting these characteristics could also be helpful in making the recording system more efficient. Hence, this project aims to answer the following research questions -

1. Can the level-crossing sampling approach be implemented in a multichannel configuration?

2. Can prior knowledge of the input signal (in this case, AEG) be helpful in designing a more efficient ADC?

This project aims to develop a multi-channel LC ADC which can satisfy the requirements of the multi-channel atrial electrogram recording system.

### 1.4. STRUCTURE OF REPORT

The operating principle of LC ADCs and its existing implementations reported in literature are discussed in Chapter 2. The architectures considered to design the multichannel LC ADC and the system level design considerations are discussed in Chapter 3. The model implementations of the proposed multichannel LC ADC (MLC ADC) architecture in VerilogA and MATLAB are discussed along with their results in Chapter 4. The circuit implementation of the proposed MLC ADC is discussed in Chapter 5. The results and conclusions from the models and circuit implementation are discussed in Chapter 6. Finally, the conclusions of the project and recommendations for future work are discussed in Chapter 7.

# 2

## LEVEL CROSSING ADC

In this chapter the operating principle of asynchronous sampling methods such as LC sampling is explained in detail. Features of the existing LC ADCs reported in literature are discussed and some of their disadvantages are listed which would be addressed in this work.

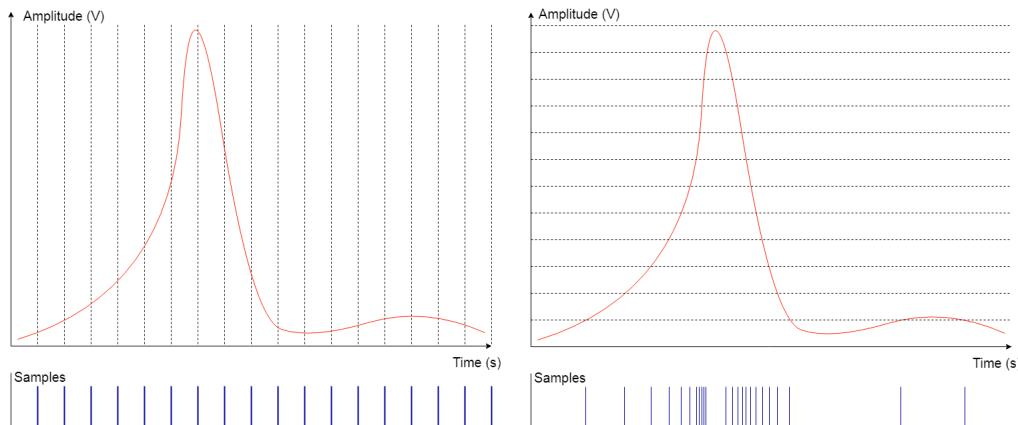

### 2.1. SYNCHRONOUS RECORDING VS ASYNCHRONOUS RECORDING

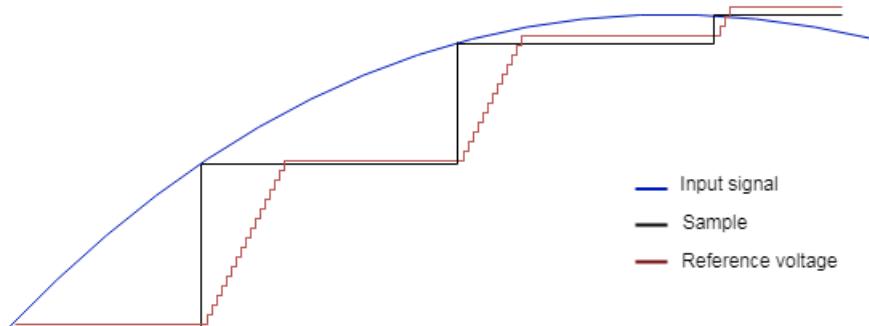

Recording of continuous-time analog signals in discrete digital form can be performed through two different methods. The synchronous recording method creates samples of the input signal at regular, fixed time intervals and then converts them into discrete digital values. The sampling rate is required to adhere to the Nyquist criterion i.e. it should be at least twice that of the bandwidth of the input signal. Moreover, the amount of data generated is fixed at each interval. This form of sampling is shown in Fig.2.1(a). As can be observed, even for signals that remain inactive for significant periods of time, the sampling rate is constant and the same amount of data is generated at each sampling interval. This is an inefficient method of conversion.

Figure 2.1: (a) Example of synchronous recording (b) example of asynchronous recording.

Asynchronous recording however is driven by the signal directly. The rate of sampling and thus the amount of data generated is dependent on the rate of change of the signal. For slow moving signals the number of samples generated is low and for peaks number of samples generated is high. Hence, there is an inherent compression of the data generated in this sampling paradigm. Example of LC sampling is shown in Fig.2.1(b). As can be observed in the figure the number and density of samples generated increases when the signal slope increases and vice versa.

## 2.2. LEVEL CROSSING ADC

The Level Crossing ADC is different from conventional Nyquist-rate ADCs as it implements an asynchronous recording paradigm rather than the synchronous recording paradigm. Use of this asynchronous recording approach obviates the requirement of a clock signal as well since the whole operation is asynchronous. The ADC tracks the input signal and generates output bits when the input signal crosses one of the reference voltage levels. The reference voltage levels are defined by the target quantiser resolution and the full scale voltage level of the input signal, whose relation is shown in Eq.2.1.

$$V_{ref} = \frac{V_{in,p-p}}{2^M} \quad (2.1)$$

where  $M$  is the quantiser resolution and  $V_{in,p-p}$  is the full scale input signal. Another voltage reference with same magnitude is also defined for sampling signals below the  $V_{cm}$  level (mean level of the input signal). These two reference levels together are referred to as the 'reference window'. If the input signal stays within the reference window, there is no output generated by the ADC. Hence, the conversion process is entirely signal-driven. The output of the LC ADC does not have any aliasing as the sampling is done in continuous time.

In synchronous recording, the amplitude is determined by the ADC and the time interval of sampling is fixed. However, in the LC ADC which uses asynchronous sampling the amplitude levels are fixed while the time interval of sampling is undetermined. This property of LC ADCs is exploited in continuous time DSPs as there the timing information of the samples is not required. However, for LC ADCs to be compatible with discrete-time/synchronous DSPs, the time of generation of samples needs to be quantized. Hence, the source of quantization error in asynchronous sampling is the oversampling ratio (ratio of timer speed/input signal bandwidth) rather than the LSB value of the quantizer. The resulting SNR due to time quantization in LC ADCs (Eq.2.2) is derived in [7].

$$SNR = 20 \log OSR - 14.2 \text{ dB} \quad (2.2)$$

where  $OSR$  is the Over-Sampling Ratio of the ADC. There are broadly two ways of implementing level crossing sampling[8] - the 'Fixed Window' architecture and the 'Floating Window' architecture.

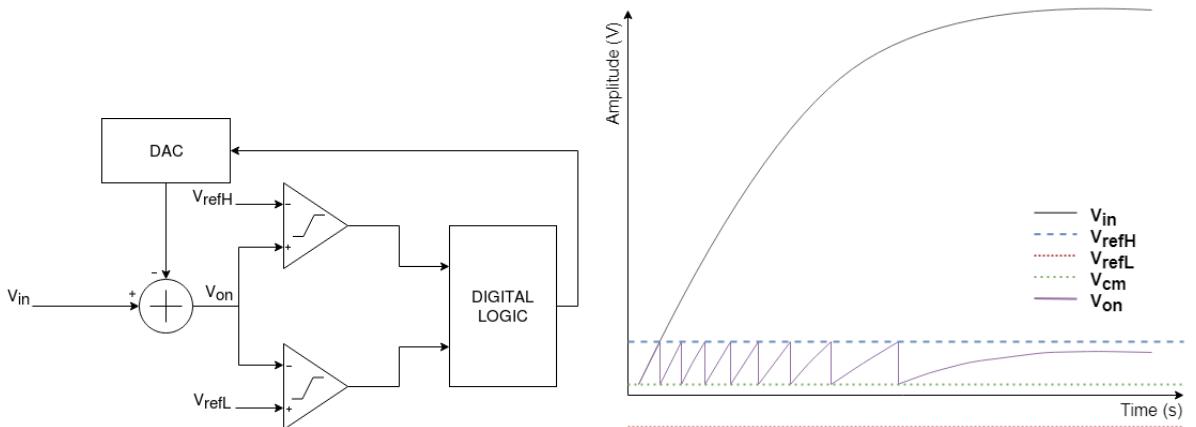

### 2.2.1. FIXED WINDOW LC ADC

In the fixed window architecture the input signal is tracked continuously and as soon as it crosses the reference levels a certain voltage is subtracted (or added) to it so that it reaches the common mode / mean voltage ( $V_{cm}$ ). The input signal is again tracked, and this operation is repeated. The block diagram of a Fixed Window Level Crossing ADC and its operation are shown in Fig.2.2.

Figure 2.2: (a) Block diagram of fixed window LC ADC and (b) timing waveform of fixed window LC ADC.

Figure 2.3: (a) Block diagram of floating window LC ADC and (b) timing waveform of floating window LC ADC.

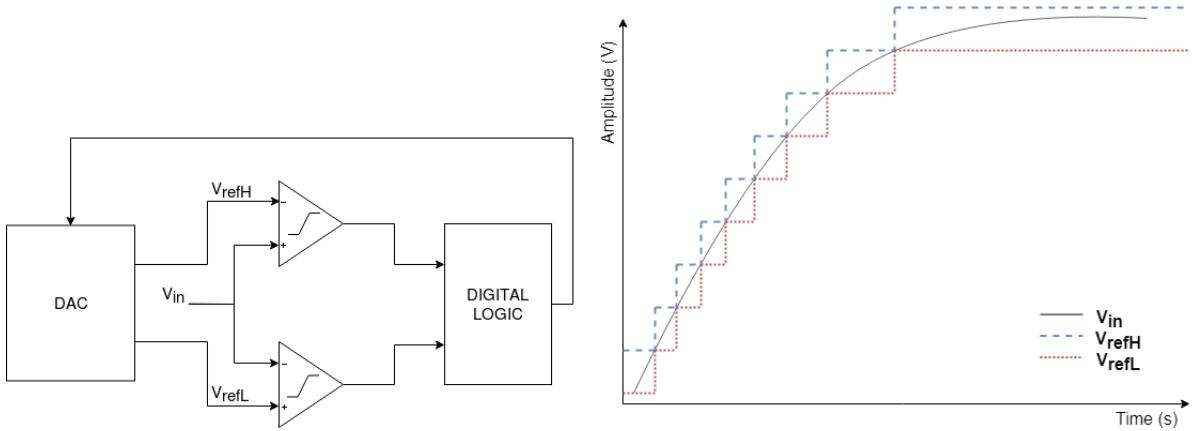

### 2.2.2. FLOATING WINDOW LC ADC

In the floating window architecture the reference window itself follows the signal as it crosses one of the reference levels of the window. The reference levels of the window are incremented (or decremented) by 1 LSB step (equivalent to the reference voltage level) depending on which direction the input signal is traversing. The block diagram of a Floating Window Level Crossing ADC and its operation is shown in Fig.2.3.

The type of DAC to be used in the ADC depends on the selected architecture. While the floating window architecture requires a multi-bit DAC, the fixed window architecture requires a 1-bit DAC. In [9], it was demonstrated that the fixed window LC ADC is smaller and more power-efficient owing to its 1-bit capacitive DAC.

## 2.3. LITERATURE REVIEW

Several LC ADCs are reported in literature. While most of the designs are fully asynchronous, some like [7] are pseudo-asynchronous to be better compatible with digital blocks that follow the ADC. However, the design still uses two comparators. Some designs have fully asynchronous frontend, DSP and DAC [10] which obviate the need for a clock signal in the whole signal processing chain. Such designs cannot be easily integrated into systems which require storage of the output in traditional digital memory. Different methods of storing and tracking the input signal are designed as well. An analog storage element is used in [7] to store and track the input signal instead of using a DAC. Similarly, a buffer with reset function is used in [8]. Using a buffer instead of a DAC simplifies the design of the LC ADC but at the same time it introduces an error in the sampling. The buffer takes some time to recover after being reset and to start tracking the input signal again. The input signal is not tracked in this time and is lost. In [11] a floating window LC ADC implementation is presented which is powered by a 300mV supply. A QRS detection circuit is also implemented along with the LC ADC which uses the output of the LC ADC and timing information of the samples to perform the QRS detection. In [12], the LC ADC is designed to be fully synchronous and uses a single path for level crossing operation. Instead of using two comparators as in conventional LC ADCs the design compares the signal with two reference voltage levels in different clock cycles using the same comparator. Similarly in [13] a single comparator and a threshold detection circuit is used to determine the level crossing of the signal. LC ADCs generally use asynchronous comparators which are affected by the slope of the input signal. In [14], the reference window size is changed according to the slope of the signal, thus ensuring similar response from the comparators for all signal slopes. This approach however requires an extra DAC and thus causes overhead in area and circuit design.

Operating principle of the LC ADC can be likened to that of the  $\Delta$  Modulator used in  $\Sigma\Delta$  ADCs. These ADCs can perform conversion with high resolution even though they use a very low resolution quantiser.

This is achieved by noise shaping of the quantisation noise. Noise shaping is added to an LC ADC in [15] to achieve better SNR performance. Moreover, no DACs are used in the design and the loop-delay is reduced considerably enabling the ADC to be used for applications in the Intermediate Frequency range (10MHz - 50MHz). Due to the increased bandwidth of the input signals the resolution of the resulting ADC is reduced to a lower range. The problem of realizing the required dynamic range in a low-voltage system is resolved in [16] by converting the input voltage into a current by using a Programmable Voltage-to-Current Converter (PVCC) which is then fed into the LC-ADC.

Chopping is generally used in AFEs to move the 1/f noise out of the band of the input signal bandwidth. This is accomplished by up-modulating the input signal to a frequency above the 1/f knee frequency and then down-modulating it at the same frequency. However, LC ADCs operate in the continuous time domain. A clockless method of chopping is introduced in [17] which uses the input signal frequency along with a pseudo-random number sequence to generate the chopping control signal.

The relation between quantiser resolution, timer resolution and the resulting SNR and dynamic range is derived in [18], which can be written as Eq.2.3.

$$BW = \frac{1}{\pi\sigma 2^M}, \quad DR \leq \frac{1}{2^{M-1}} \quad (2.3)$$

where  $BW$  is the input signal bandwidth,  $\sigma$  is the loop delay of the quantiser,  $M$  is the quantiser resolution and  $DR$  is the dynamic range of the LC ADC. This shows that there is a limitation on the maximum dynamic range achievable in an LC ADC for a given signal bandwidth. The dynamic range of the ADC can be increased by increasing the quantiser resolution but at the cost of reducing the maximum input signal bandwidth. At the same time the number of samples generated in an LC ADC increases exponentially as its quantiser resolution increases[19]. The amount of data generated is increased two-fold for every extra bit of resolution increased in the quantiser. Hence, for higher resolutions the LC ADCs produce much higher amount of data as compared to conventional synchronous ADCs. This issue overshadows the benefits of activity-dependent operation found in LC ADCs.

These limitations can be overcome by using adaptive resolution techniques in which the quantiser resolution is changed according to the slope of the signal [18],[20]. While in [18], the slope detection is done off-chip in an FPGA, in [20] the slope detection is done on-chip based on the time elapsed between token generation. The operation of an adaptive resolution LC ADC is shown in Fig.2.4. Even though the adaptive resolution technique reduces the the number of samples generated, it increases the amount of data generated by the ADC. The event of change of resolution and the degree of change are not recorded in the pulses generated by the LC ADC. They are however needed so that the signal can be accurately reconstructed. Hence, additional bits need to be added to the output to specify where the resolution was changed and by how much. This increases the amount of data generated by the ADC as a whole and increases power consumption in the data transmission block, especially if it uses a wireless mode of transmission.

LC sampling is combined with a SAR-based quantiser in [21] to implement a fixed window LC ADC. Here, the SAR ADC is used as a residue quantiser while the level crossing sampling is implemented in the digital domain. The output of the residue quantiser is used to perform the subtraction of the input signal through a DAC. An AR algorithm is also implemented in the digital domain to reduce the amount of output data generated. In [22] an activity-dependent SAR ADC was reported in which the number of quantisation steps for each sample is dependent on the signal activity as compared to its previous sample. The quantised reference voltage level of the previous sample is used as the starting point of quantisation for the next sample. Thus, if the difference between two samples is less than one LSB step then the quantisation of the new sample is completed in just two quantisation steps. However, the output of the ADC is constant for each sample and thus it does not reduce the output like LC ADCs.

A multichannel implementation of the LC ADC has not yet been reported. Existing multichannel ADCs [3] sample the input signal synchronously and hence do not exploit the benefits of asynchronous sampling. Compressed Sensing is an important feature which is being integrated into biosignal recording systems

Figure 2.4: Operation of Adaptive Resolution technique in Floating Window LC ADC. The window size is changed according to the slope of the input signal.

Table 2.1: Advantages and disadvantages of an LC ADC

| Advantages                     | Disadvantages                   |

|--------------------------------|---------------------------------|

| simple design                  | continuous-time comparators     |

| small area                     | total number of output bits     |

| signal dependent operation     | unsuitable for high resolution  |

| optimisation to reduce samples | resolution is bandwidth-limited |

[23]. These features require complex algorithms or circuitry and put an overhead on the frontend in terms of area, power and design complexity. Several biosignal recording systems record signals from multiple channels simultaneously to improve the spatial resolution of the recorded signals. While some systems such as in [24] use one ADC for each channel, some like [25] use time-multiplexed ADCs. In [26], 1024 input channels are used to record neural signals and 64 time-multiplexed SAR ADCs are used to record from all the channels. The amount of data produced in such systems would be quite large. Thus, data compression would be required to minimise the data size transmitted outside the device. The number of input channels in biosignal recording systems will increase in the future and the data would need to be transmitted wirelessly. Therefore, reduction in the amount of data produced would become critical in such systems.

Thus, the following problems in existing LC ADCs need to be addressed-

1. Large amount of data generated in LC ADCs at high quantiser resolutions.

2. Extra data required to encode the change in quantiser resolution in adaptive resolution technique.

3. Absence of multichannel LC ADC architectures to record from several input channels simultaneously.

The advantages and disadvantages of LC ADCs as compared to conventional synchronous ADCs are summarised in Table 2.1.

## 2.4. CONCLUSIONS

LC ADCs are a way to implement the asynchronous recording method. They can be designed using one of the two architectures - fixed window and floating window architectures. There are several LC ADCs reported in literature which address specific problems associated with conventional synchronous ADCs or improve performance over existing LC ADCs. However, there are still some issues which have not been addressed or can be addressed in a better way. Moreover, multichannel configurations of LC ADCs have not yet been designed. Proposed solutions to these problems are discussed in the next chapter.

# 3

## SYSTEM LEVEL DESIGN CONSIDERATIONS

The working principle and existing designs of LC ADCs are discussed in detail in the previous chapter along with some problems in these implementations. In this chapter the proposed solutions to the problems are discussed. Different solutions considered to address the problems and the procedure adopted to select the best solutions are also discussed.

### 3.1. SYSTEM REQUIREMENTS

The AEG signals being recorded have a maximum amplitude of  $80mV_{p-p}$  and the minimum amplitude that needs to be recorded is  $0.1mV_{p-p}$ . Hence, the required dynamic range (DR) is calculated as per Eq.3.1 to be 800. As shown in the previous chapter, the relation between the target DR and the quantiser resolution required in an LC ADC is given by Eq.2.3. This gives the required quantiser resolution,  $M$  to be 11-bits. The target bandwidth for the input AEG signals is set to be 400Hz. The LC ADC should be able to quantise the signals in the given bandwidth reliably. The signal characteristics of the AEG signal are summarised in Table3.1.

$$DR = \frac{V_{max}(p-p)}{V_{min}(p-p)} \quad (3.1)$$

Table 3.1: Signal properties of atrial electrograms

| Property                     | Value   |

|------------------------------|---------|

| Max amplitude ( $mV_{p-p}$ ) | 80      |

| Min amplitude ( $mV_{p-p}$ ) | 0.1     |

| Bandwidth (Hz)               | 0.5-400 |

Table 3.2: Target specifications of proposed LC ADC

| Property                    | Value |

|-----------------------------|-------|

| Number of channels          | 192   |

| Dynamic Range (dB)          | 58.06 |

| Bandwidth (Hz)              | 400   |

| Quantiser Resolution (bits) | 11    |

The AEG signals are recorded simultaneously from 192 electrodes. Using an ADC for each channel is not a viable approach as a large area of the IC would be used by ADCs. The power consumption would also be much higher since each ADC would operate and draw power simultaneously. A single ADC cannot convert signals from all 192 channels either. Hence, a number of ADCs can be used with each ADC

converting input signals from several channels simultaneously. As mentioned in chapter 2 a multichannel LC ADC currently does not exist. The architecture for an LC ADC needs to be designed such that multiple channels can be serviced together. The different topologies considered that could fulfill the listed criteria are described in subsequent sections.

As discussed in the previous chapter the number of output samples generated by the LC ADC doubles with the addition of every bit of resolution. The target resolution of the LC ADC is 11 bits which is quite high for an LC ADC. This implies that the number of output samples generated would also be high. Hence, techniques such as adaptive resolution need to be applied to reduce the number of samples generated without compromising on the quality of the output. These techniques are also discussed in subsequent sections. The target specifications of the LC ADC are listed in Table 3.2.

3

### 3.2. MODELLING LEVEL CROSSING ADC

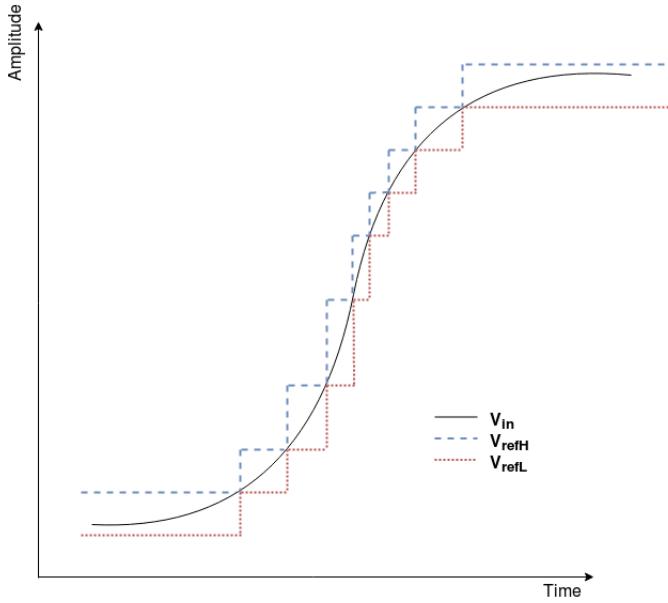

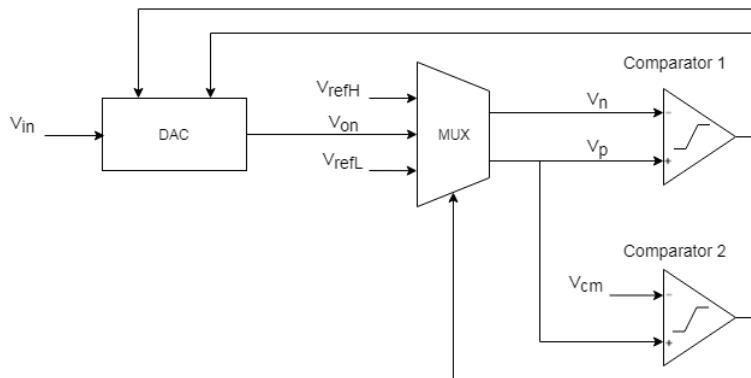

VerilogA models are developed to analyse the behavioral operation of the LC ADC. The fixed window LC ADC design and the floating window LC ADC design are used as reference for the models. The model for fixed window LC ADC as shown in Fig. 3.1 consists of a DAC, a multiplexer (MUX) and two comparators. The logic block shown in Fig. 2.2 is included inside the DAC in the verilogA model. The multiplexer is used to select the reference level which is supplied to the comparator. Moreover, the signals for each input polarity of the comparator are also selected through the MUX. The reference level is selected depending on the output of the other comparator which determines the direction of the input signal. This is accomplished by comparing the output signal of the DAC with the common mode voltage ( $V_{cm}$ , in this case 0V). If the signal is ramping up then the output of the DAC is compared with the upper reference level. Otherwise the lower reference level is compared with the output of the DAC as the reference (connected to negative polarity input of the comparator). Operation of the fixed window LC ADC model is shown in

Figure 3.1: Model of Fixed Window Level Crossing ADC.

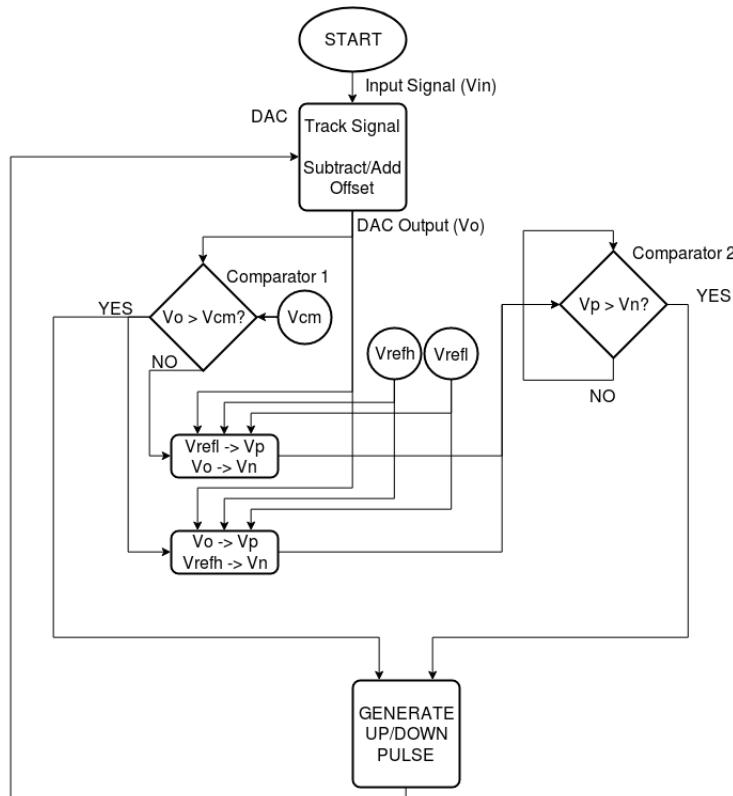

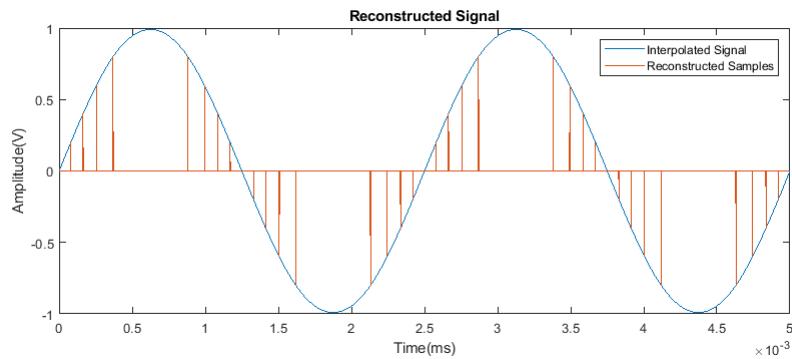

the flowchart in Fig. 3.2. As soon as a level-crossing is detected by the comparators in either direction, the comparators' output signals are fed back to the DAC which then subtracts (or adds) a voltage equivalent to the LSB voltage to the input signal. Hence, the DAC keeps tracking the input signal while ensuring its output stays within the reference window. The simulation waveforms are shown in Fig. 3.3. The input here is a  $2V_{p-p}$  signal while the LSB voltage is 200mV. Hence, ten reference levels are crossed by the input signal during conversion. The output signals from the comparators are used to reconstruct the input signal, shown in Fig. 3.4.

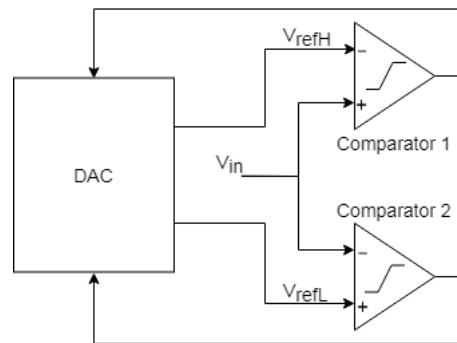

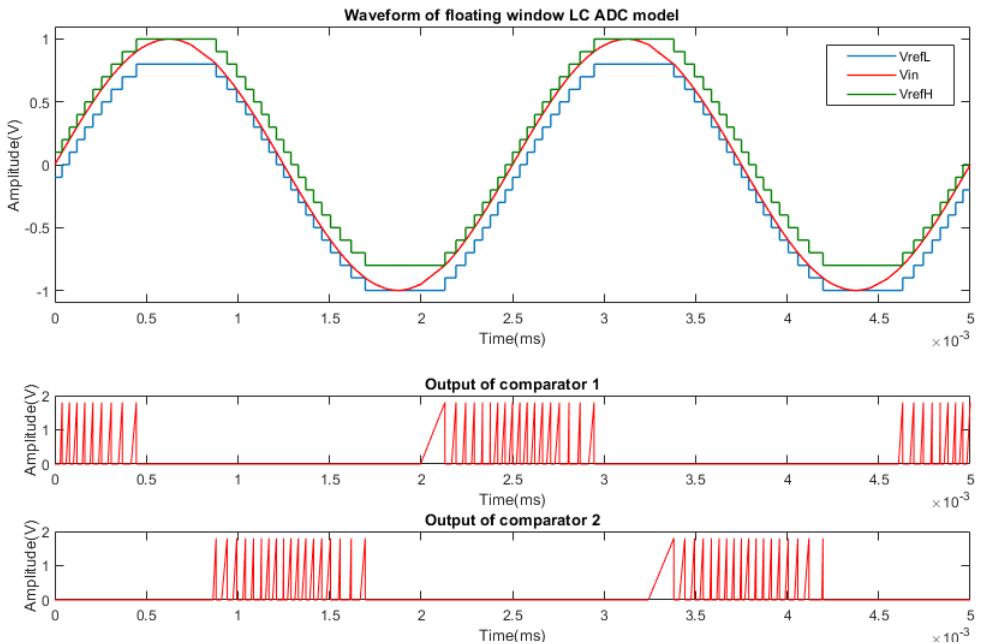

The block diagram of the model for floating window LC ADC is shown in Fig. 3.5. The reference window in this model is updated every time the input signal crosses either of the reference levels. The reference window is thus shifted by 1 LSB step in the direction in which the signal crosses the reference window. The DAC receives feedback from both comparators and changes the reference levels accordingly. The simulation waveforms are shown in Fig. 3.6. The input signal with 1 V<sub>p</sub> is converted sampled with 10 reference levels.

Figure 3.2: Flowchart for operation of VerilogA Model of LC ADC.

Figure 3.3: Operation of LC ADC model built with VerilogA. The top plot shows the input signal and the output of the DAC. The two plots below show the outputs of the comparators.

Figure 3.4: Reconstructed signal from samples by spline interpolation.

Figure 3.5: Block diagram of model of floating window LC ADC.

Figure 3.6: Waveforms illustrating operation of floating window LC ADC model.

### 3.3. SPLIT RESOLUTION: A PROPOSED ALTERNATIVE TO ADAPTIVE RESOLUTION

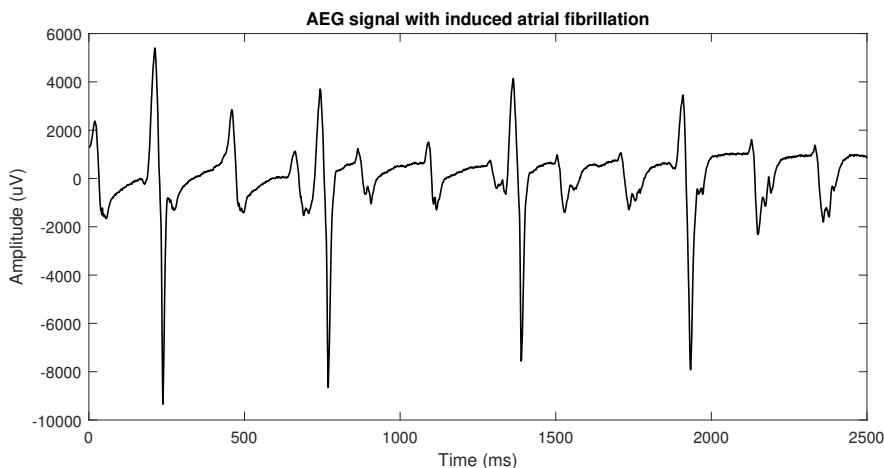

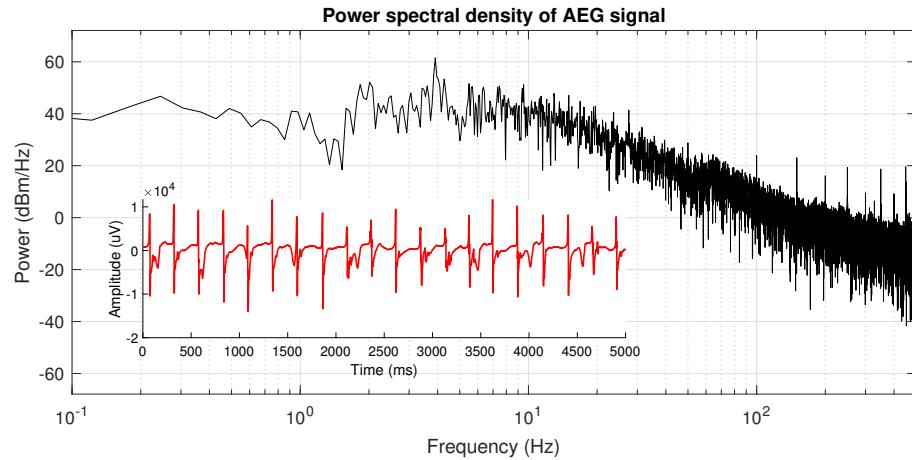

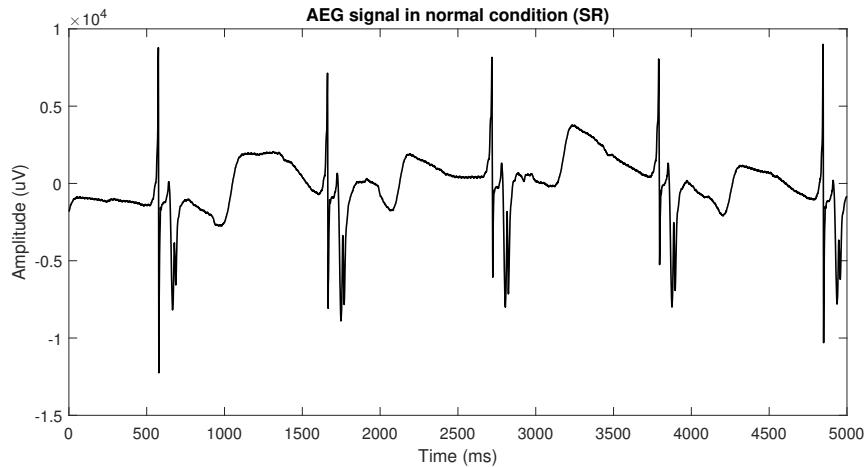

As explained in the previous chapter the adaptive resolution techniques reported in literature increase the total amount of data generated in the ADC. Hence, a novel method of data reduction, named Split Resolution (SR) technique is proposed which does not require additional bits to show change in resolution. AEG signals are similar to ECG signals as they have fast and high peaks in between periods with relatively low-amplitude and low-frequency signals. An example of AEG signal is shown in Fig.3.7. Most of the signal activity is confined within a narrow range of amplitude close to the common mode. The spikes are narrow and reach relatively higher amplitudes compared to the remaining parts of the signal. The spikes therefore contribute significantly to the total number of samples generated by the LC ADC. A threshold can be set beyond which when the signal increases, the resolution of the LC ADC is reduced. The threshold level and the degree of reduction of resolution can be programmed in the LC ADC. The advantage of this method is that no extra memory is required to store the moment and degree of change of resolution. The parameters are programmed in the LC ADC prior to recording. During reconstruction the number of levels can be counted from  $V_{cm}$  in either direction to determine the exact moment of application of split resolution and thus reconstruct the signal accurately. Moreover, the change in resolution can be made gradually in steps, such that if the spike is high enough then the resolution can be decreased gradually instead of abruptly all at once. Even then the number of LSB steps crossed for each resolution setting can be fixed and hence, extra memory is not required.

Figure 3.7: AEG signal with atrial fibrillation condition. Source: EMC Rotterdam.

Figure 3.8: Methods for implementation of Split Resolution technique in LC ADC.

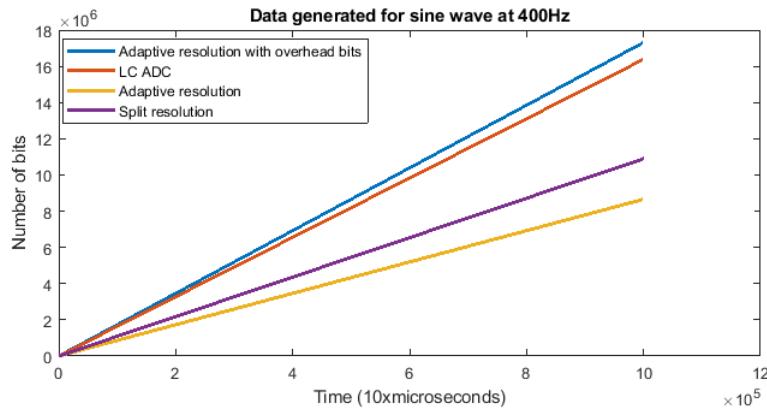

Figure 3.9: Plot for amount of data generated in different level crossing algorithms for a sinusoidal input signal at 400Hz.

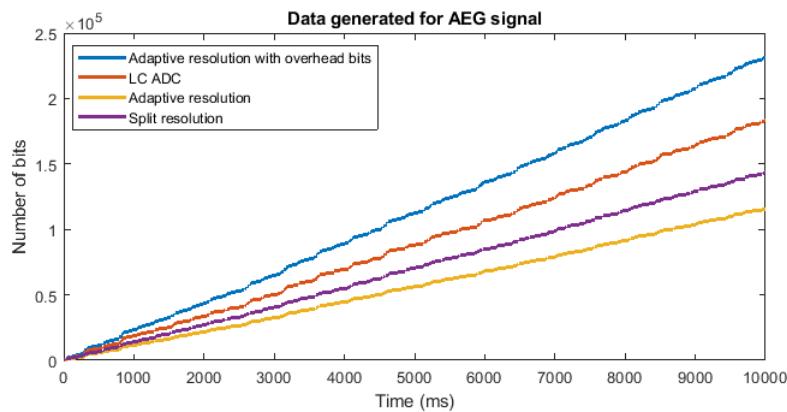

Figure 3.10: Plot for amount of data generated by different level crossing algorithms for an AEG signal.

The disadvantage of the proposed split resolution technique is that the accuracy of location of the peaks are reduced. However, since the LC ADC itself has a high resolution it would not degrade the resolution at the peaks substantially. Implementing the split resolution technique would help in reducing the number of samples generated by the LC ADC.

Three methods for implementation of the SR technique in an LC ADC are proposed. These are illustrated in Fig.3.8 and described below -

1. Dropping Samples in Output Logic - The output logic block combines the output pulses of the comparators and encodes the output accordingly. The Split Resolution technique can be applied here by removing pulses from the output stream. If a one-bit reduction is applied, every other pulse can be removed from the stream.

2. Changing gain of Variable Gain Amplifier (VGA) - The input signal coming from the electrodes need to be filtered and amplified so that the signal can be properly converted in the ADC. The amplifiers used for such applications have a constant gain. However, if the gain is changed according to the amplitude level of the signal then the effective number of quantisation levels required can be changed. Thus, as the signal crosses a threshold, the gain can be reduced so that the ADC would need less number of level crossings to sample the peak.

3. Varying reference window size in DAC - The DAC used in LC ADCs decides the reference window size. Hence, the window size can be varied in the DAC by using feedback from the comparators. In the Fixed Window architecture the offset injection can be varied and in the Floating Window architecture the reference levels generated can be varied.

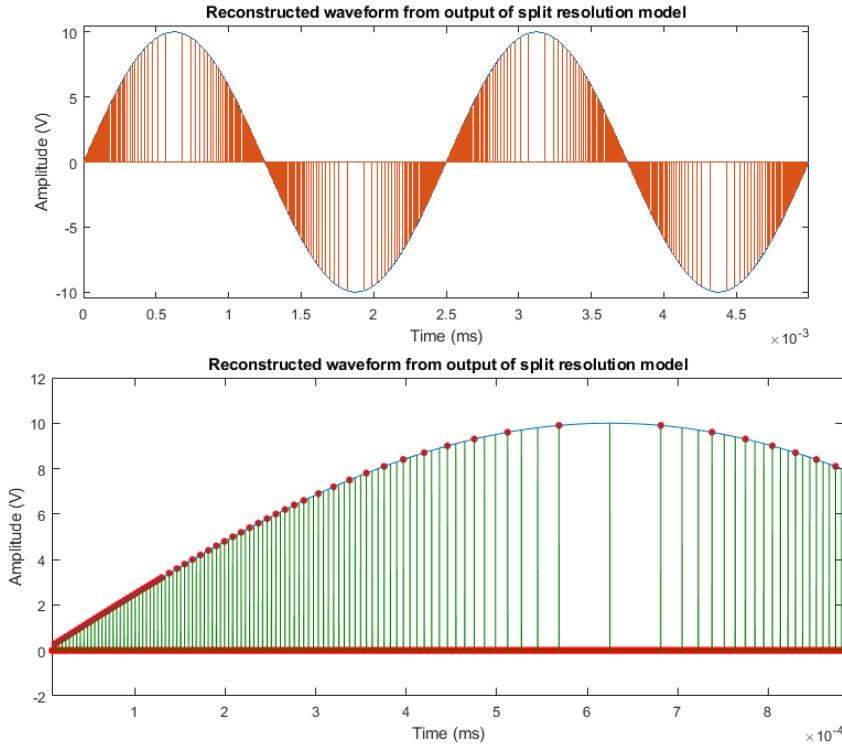

Figure 3.11: (a) signal reconstructed from output samples of LC ADC model with split resolution technique (b) reconstructed signal showing samples dropped (not marked with red) in the output after application of split resolution technique in the digital output block.

Effectiveness of the Split Resolution technique is checked by performing a comparative estimation study of the different LC ADC operation modes in MATLAB. In the modelling setup for the adaptive resolution technique the slope of the input signal is estimated and the resolution is decreased in two steps (by a bit in each step) according to certain thresholds in slope. Similarly for the split resolution technique thresholds are defined in amplitude and resolution of the quantiser is reduced in two steps (with a bit in each step) when the signal crosses the preset thresholds.

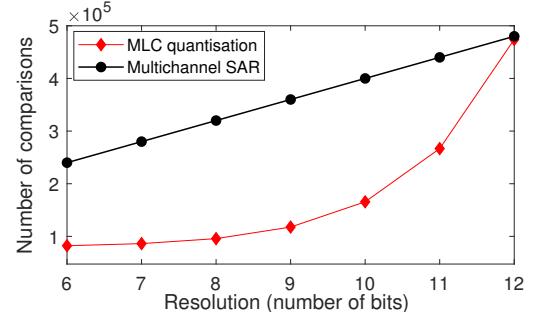

Fig.3.9 shows the number of output bits generated by the different ADCs for a sinusoidal input signal at 400 Hz over a duration of 10 seconds. Similarly, Fig.3.10 shows the amount of data generated by the ADCs for an example AEG signal over a duration of 10 seconds. The estimation illustrates that the adaptive resolution technique produces lower amount of data compared to the level crossing sampling and the split resolution techniques. However, considering the overhead due to the addition of slope information or change of resolution the amount of data increases considerably, even more than that of a normal LC ADC.

The three methods for implementation of the split resolution (SR) technique are implemented in the VerilogA model of the fixed wave LC ADC and their operation is verified. The reconstructed signal from the output sample of the model with SR technique applied in the digital output block is shown in Fig.3.11.(a). The output pulses are removed in steps, as shown in Fig.3.11.(b). Similarly the waveforms of other methods are shown in Fig.3.12.

The implementation of SR technique in the input amplifier introduces sudden changes in the output of the DAC. This also affects the output pulses in the comparators. The other two methods do not cause such disturbances as they do not affect the input signal directly and are easier to implement as well. Hence, they are opted to be implemented in the LC ADC design.

Figure 3.12: (a) waveform illustrating operation of SR technique implemented in the DAC (b) waveform illustrating SR technique applied in the variable gain amplifier.

### 3.4. ARCHITECTURES CONSIDERED FOR MULTICHANNEL LC ADC

Several architectures and design ideas are considered to design the multichannel LC ADC. The system level design considerations of all the architectures considered are explained below -

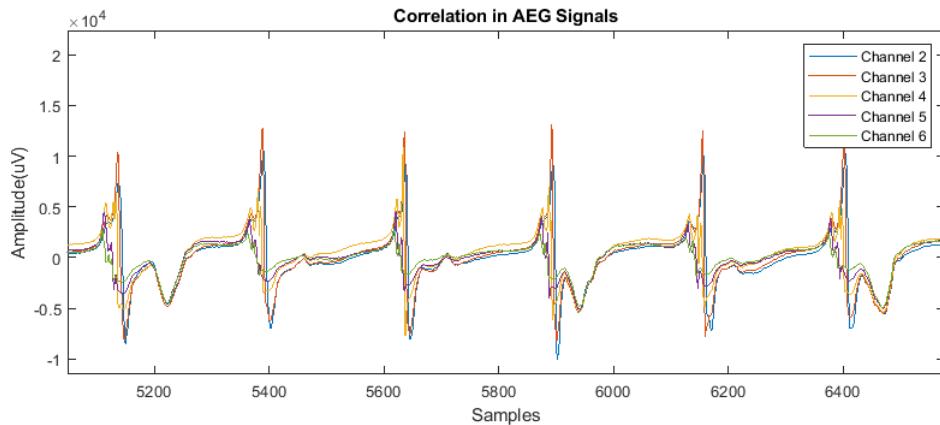

#### 3.4.1. SPATIALLY CORRELATED SAMPLING

AEG signals obtained from EMC are studied in order to find signal properties which could be exploited in sampling and quantising the signal. Since the recording patch consists of electrodes at regular intervals, the electrical impulse propagating over the surface of the atrium would be observed as a wave across the electrodes. This property is observed in the signal analysis of the recorded AEG signals, as shown in Fig.3.13. Hence, this property is considered for designing a difference-based cluster of ADCs with a single high-resolution ADC and several low-resolution ADCs for the adjacent channels. The intention is to use the high-resolution ADC to obtain a high-resolution recording from one channel and use that as a reference for recording the difference in signals from the adjacent electrodes. However, the problem with this approach is that even though the signals from adjacent channels have a similar pattern they have different amplitudes which cannot be resolved through a direct correlation with the reference signal. Moreover, the correlation among the signals from adjacent channels are not always the same, even though a pattern could be observed. Hence, this approach can not be implemented without using overly complicated algorithms to estimate the difference of signals between adjacent channels and thus may not be practically viable.

Figure 3.13: Illustration of correlation in AEG signals from adjacent channels.

#### 3.4.2. TIME-MULTIPLEXED LC ADC

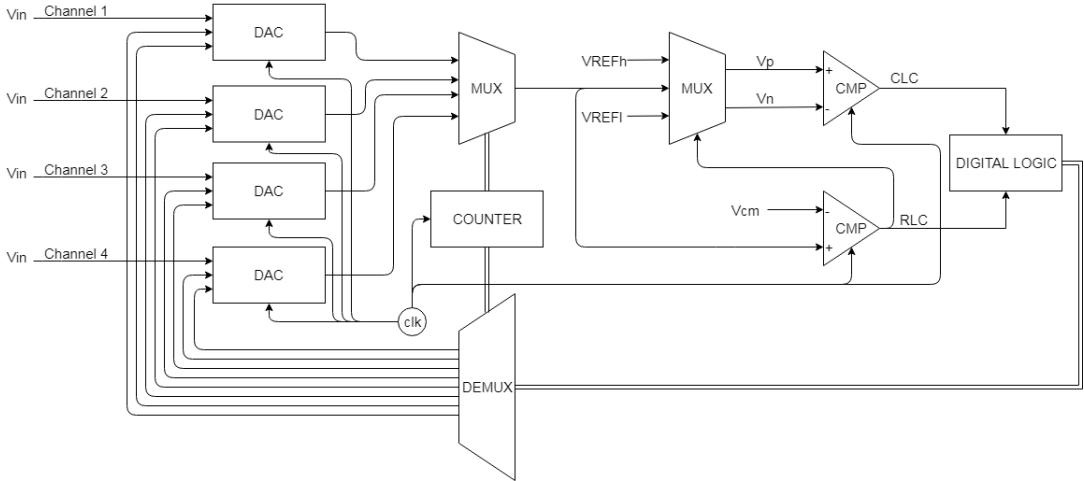

Another approach considered is to time-multiplex the input channels as is done in multichannel SAR ADCs [27]. A specific period of time is provided to each channel within which the level crossing has to be detected. The architecture is shown in Fig.3.14. In this architecture the feedback to each channel is also synchronised with the counter through a DEMUX block. Each channel has a DAC which tracks the signal and affects the input signal according to its corresponding feedback signal. This method forces the asynchronous LC ADC to behave synchronously, since the level crossing can now be detected at specific time points only. The clock thus needs to be fast enough so that it does not miss a level crossing in any of the channels. This means that it needs to be able to switch to each channel before two consecutive level crossings have occurred for that channel. The clock speed required to ensure that all level crossings are detected for every channel can be calculated by Eq.3.2.

$$\begin{aligned}

F_s &= 1/((Vdd/2)^M * (1/(2 * \pi * Vdd * BW))) \\

&= 1/((1.8/2048) * (1/(2 * \pi * 1.8 * 400))) \\

&= 5.147 \text{ MHz}

\end{aligned} \tag{3.2}$$

In this architecture the signal bandwidth( $BW$ ), peak-to-peak amplitude ( $Vdd$ ) and number of quantisa-

Figure 3.14: Architecture for time-multiplexed LC ADC for 4 channels.

tion levels( $2^M$ ) are considered to calculate the required clock speed. It should be noted here that the clock speed is dependent not only on the signal bandwidth but also on the slope of the signal. At the maximum slope of the signal the least amount of time would be taken for it to cross adjacent reference levels. Hence, the multiplicative factor  $2\pi$  signifies the maximum slope of the signal. Using the same relation for the current scenario the minimum clock speed required would be greater than 5MHz. This calculated clock speed is required per channel. Hence, for an  $n$ -channel multiplexed ADC the clock speed would be  $n * 5\text{MHz}$ .

Even at this clock speed, the maximum error in timing resolution that can be encountered is almost equivalent to 1 LSB. This is due to the fact that the minimum time taken by the signal between two consecutive level crossings is considered to calculate the clock speed of the timer. If a level-crossing occurs in a channel immediately after it was checked for a level-crossing, it would be detected the next time this channel is checked, i.e. after the calculated minimum time. This problem is illustrated in //Fig. This problem can be mitigated by increasing the timer frequency.

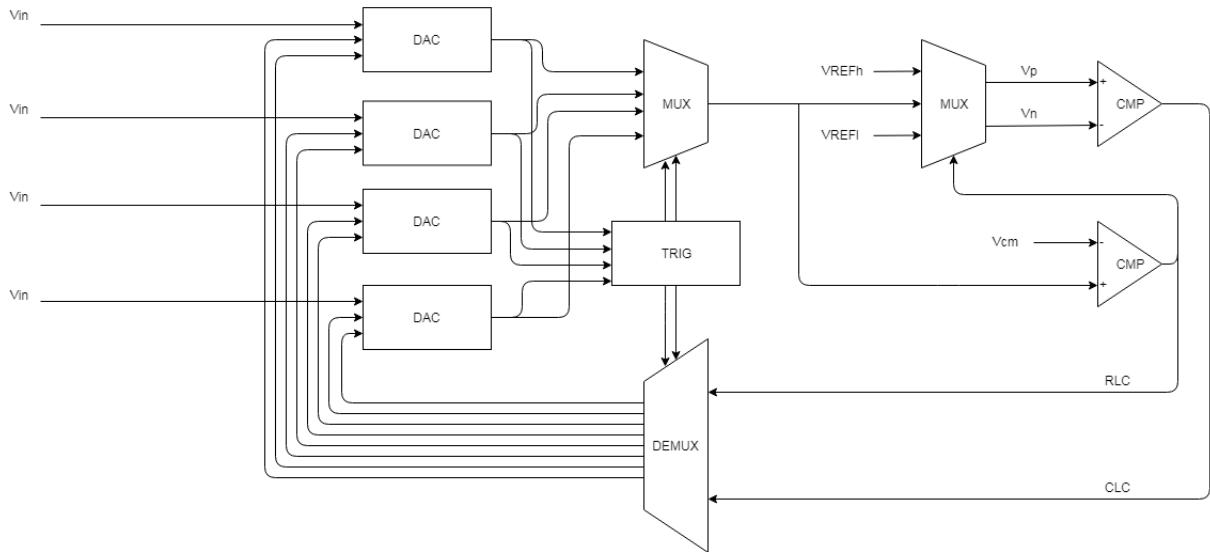

### 3.4.3. ASYNCHRONOUS MULTIPLEXED LC ADC

In the approach considered above, the time-multiplexing approach is found to be unsuitable as then the timer frequency required is substantially high and thus defeats the continuous-time property of the LC ADC. Hence, a different approach is sought to design the multichannel LC ADC which does not involve synchronising the operation with a clock. The architecture in Fig.3.15 is considered to implement this. In this approach the same multiplexing technique is retained while removing the clocked counter for selection of the channels. An asynchronous triggering mechanism is used instead of the clocked counter. The trigger acts as an interrupt which retains access to the ADC until the Level Crossing event is fully registered as an output pulse by the ADC. The triggering mechanism is intended to be engaged when a level crossing event is about to happen.

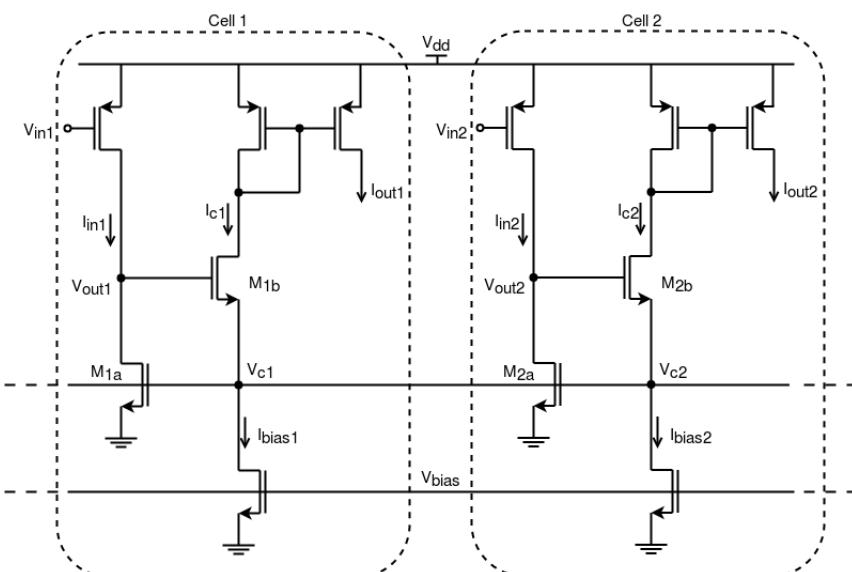

A Winner Take All (WTA) circuit [28] shown in Fig.3.16 can be used in this approach for triggering the interrupt and for selecting the channel. A WTA circuit consists of several branches through which similar magnitudes of current flow and it selects the branch with the highest magnitude of current. In the circuit if the currents ( $I_{in1}$  and  $I_{in2}$ ) are identical, then the output currents  $I_{out1}$  and  $I_{out2}$  are also identical as the biasing conditions for both cells are the same. If there is a difference in the magnitude of input currents such that  $I_{in1} > I_{in2}$ , the output voltage difference increases such that  $V_{out1} > V_{out2}$ . Thus, as  $V_{out2}$  decreases,  $M_2$  shuts down and thus  $I_{c2}$  reduces to 0. This causes all the bias current to flow through  $M_{1b}$  and therefore  $I_{c2} = 2 \cdot I_{bias}$ . In this case cell 1 has won the control as it had more input current.

Designs of WTA circuits reported in the literature show that differences of upto nA can be differentiated in WTA circuits[29]. In this architecture the voltage in DACs can be tracked in the WTA circuit and the one

with the highest voltage is selected as its corresponding channel would have the level crossing first. When the level crossing occurs and it is detected in the comparators then offset injection occurs in the DAC and the next channel with the highest voltage is then selected. Thus, the selection of channels is done entirely asynchronously.

However, the WTA circuits consume a considerable amount of power, which even exceeds the power consumption of a single channel LC ADC reported in literature [9]. Hence, the benefits obtained in avoiding synchronisation of the multiplexer are far outweighed by the cost of power consumption of the WTA circuit. The speed of operation of WTA circuits is inversely proportional to the number of branches it tracks on. This implies that with higher number of channels the speed of the WTA circuit is also affected. Even though the multiplexing can be achieved asynchronously, a timer is still required that can resolve the timing of generation of samples accurately. Moreover, additional bits would be required to specify which channel generated the level-crossing sample. Hence, overhead in the amount of data generated would also occur.

Figure 3.15: Architecture for asynchronously multiplexed LC ADC for 4 channels.

Figure 3.16: Schematic of Winner Take All (WTA) circuit implemented in CMOS.

### 3.4.4. ENCODING OUTPUT FROM MULTIPLE CHANNELS

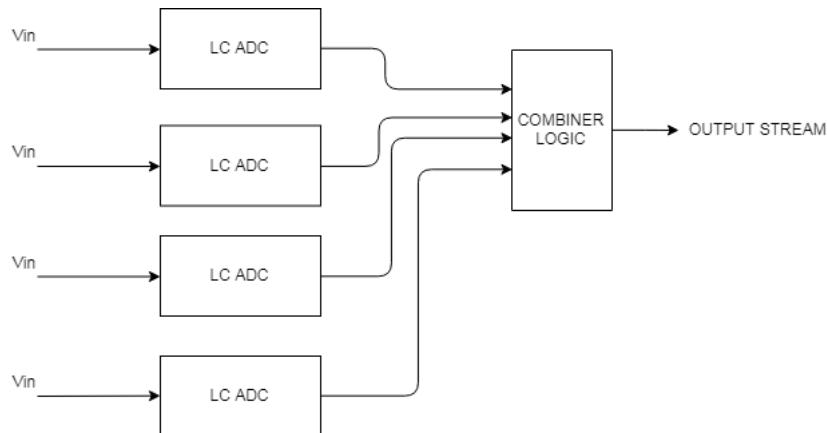

The signal acquisition device can be made with a single LC ADC for each channel. Since LC ADCs are quite small (0.045mm<sup>2</sup>) [9], this method is possible to be implemented in an IC. However, if 192 ADCs are put in the IC, it would lead to twice as many output wires as well. Considerable amount of area and logic would be required to route the wires to a digital storage/transmission system and to synchronise the data, respectively. This problem can be resolved by combining the output wires in a digital logic and streaming the output pulses from several channels together through a single wire/port as shown in Fig.3.17. This can be implemented through an asynchronous circuit.

3

The challenge in designing this block would be in handling the simultaneous output pulses from multiple channels. Memory buffers can be used to handle signals coming in several channels together. It is difficult to use an asynchronous digital block to generate an output stream of data as a clock is needed to synchronise the data rate. Otherwise the receiver block would not be able to process the data sent from the ADC reliably. Thus a clock signal is required to ensure a constant baud rate which can be synchronised with the receiver before storage in a memory device. The clock signal to be used here should be as fast as the output generation rate of the ADC. Since the output generation rate of the ADC is dependent on the slope of the input signal and quantiser resolution, it should be faster than the maximum number of samples generated per second. This calculation can be related to 3.2 which is equivalent to 5.14MHz for the given scenario. Even in this method extra bits would be required to specify the channel generating the sample, thus increasing the total amount of data generated.

Figure 3.17: Architecture for combination of output wires in a Digital Logic block.

### 3.4.5. COARSE-FINE ARCHITECTURE

The coarse-fine architecture is a popular architecture used in synchronous ADCs. In this architecture a high-resolution ADC is composed of two medium/low-resolution ADCs which give a combined output of the desired resolution. The residue of the signal quantised by the 'coarse' ADC is amplified and fed to the 'fine' ADC to quantise. Thus the MSB bits are derived from the coarse ADC while the LSB bits are derived from the fine ADC. This approach reduces the stringent requirements on the individual components of a high-resolution ADC.

The design constraints of the LC ADC become tighter for every bit added to the resolution of its quantiser. With every additional bit the required speed of the timer doubles and the amount of data produced doubles as well. Moreover, the halved LSB voltage requires more accuracy in matching of the DAC, comparator etc. Hence, a coarse-fine architecture can be a good solution for the LC ADC in this case. Two LC ADCs with lower resolution can be cascaded to make a higher resolution LC ADC.

However, a regular coarse-fine architecture also relies on the fact that the signal being quantised in both the ADCs is a sampled signal. Since the LC ADC operates on the continuous-time signal, the residue of the input signal from the coarse ADC would still be in continuous time. This can be sampled in the fine LC

ADC as is done in the coarse LC ADC. However, since the conversion in the fine LC ADC needs to be completed before the next conversion in the coarse LC ADC, the clock frequency for driving the fine LC ADC needs to be as fast as the minimum time between the level crossings of the signal. The data generated in total from both the ADCs would be the same as that of the single LC ADC with the same overall quantiser resolution. Hence, this approach helps in relaxing the design of the analog components but doesn't aid in reducing the required clock speed or amount of data generated.

### 3.4.6. SYNCHRONOUS LC ADC

As observed in the methods discussed above, the continuous time sampling approach is not suitable to implement in multichannel configurations. Hence, a different approach needs to be adopted in which the sampling is performed synchronously and the quantisation is performed based on the level-crossing approach. In this method the sample is quantised by counting the number of LSB steps required by the quantiser to reach the sample amplitude from mean (half of the common mode input range). However, this approach is rather inefficient as in the worst case the quantiser would need to count  $2^{M-1}$  LSB steps to reach the sample amplitude. Moreover, if the signal is stagnant at a high amplitude for considerable period of time then a large number of quantisation steps would be required for each sample.

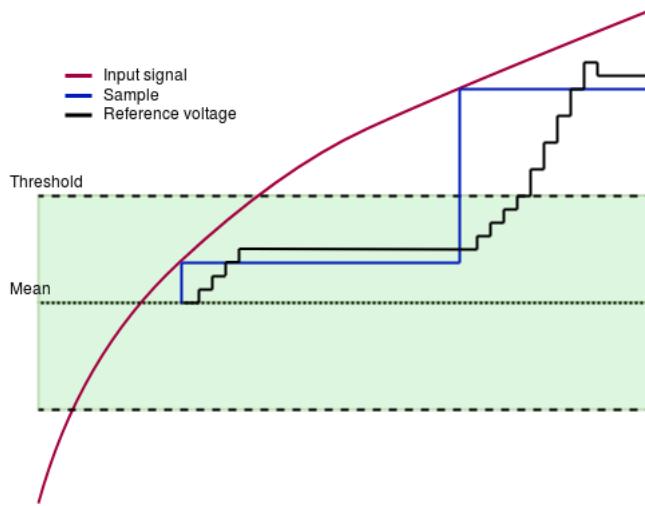

This problem can be mitigated by using the previous sample as the starting point for quantisation of each new sample. Instead of counting the difference of the sample amplitude from the mean in terms of number of LSB steps, the difference in amplitudes of the current sample and the previous sample could be counted instead. Since the level crossing sampling scheme allows the quantiser to remember the exact amplitude level of the input signal at each moment, this property can be used to implement the proposed scheme. The operation of the proposed method is illustrated in Fig. 3.18.

Figure 3.18: Operation of Synchronous LC ADC.

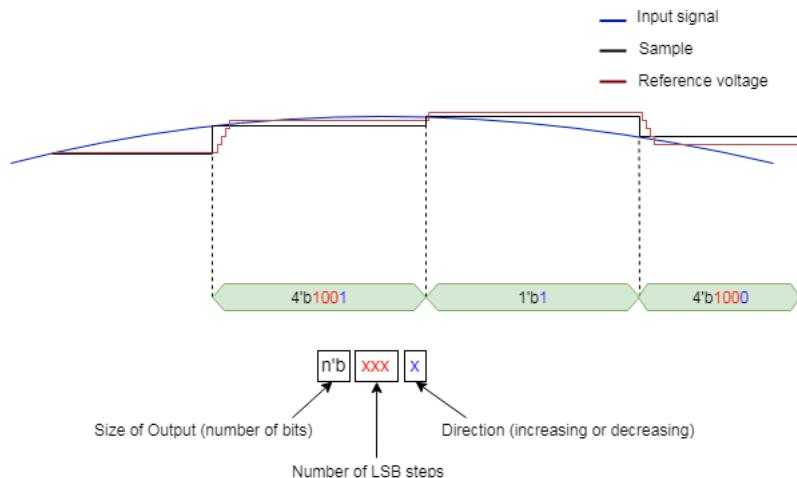

Conventional synchronous ADCs provide the quantised value of the sample at the output. Thus, an  $n$ -bit ADC provides an  $n$ -bit output for every sample. Since the proposed LC ADC is activity dependent, its output should also adhere to this property. Hence, the output of the proposed LC ADC denotes the difference in amplitude from the previous sample in terms of number of LSB steps counted by the quantiser. This quantity is encoded as a binary number along with a separate bit for direction. The maximum number of LSB steps that can be covered by the quantiser in the proposed ADC is  $2^M$ . Hence, a maximum of  $M+1$  bits would be given at the output for the worst case. It should be noted that for most samples this worst case condition would not apply, since the difference in amplitude between successive samples of biosignals is rarely as high as  $V_{ref}$ .

The proposed method will improve the performance of the ADC considerably, especially for temporally sparse signals such as ECG, AEG etc. These biosignals don't change in amplitude for considerable periods of time. The number of LSB steps covered for each sample would therefore be quite less. While the SAR algorithm uses the same number of quantisation steps for each sample irrespective of the signal activity, this approach would make the quantisation process entirely dependent on the signal activity. If the signal does not change in between samples then the proposed level-crossing quantiser would be able to deter-

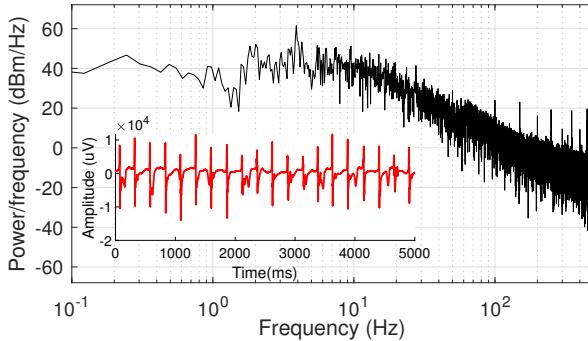

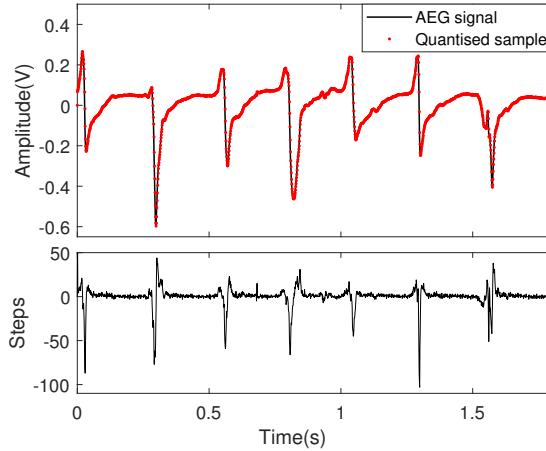

mine this in just one quantisation step. As can be observed in Fig. 3.19 most of the high-amplitude content of the AEG signal appears in the low frequency region. Hence, the average number of quantisation steps required for most samples would be low. The amount of data generated is related to the number of LSB steps covered. Thus the average amount of data produced would also be lower as compared to conventional synchronous ADCs. This is also lower than the output of the time-multiplexed LC ADC architectures proposed previously, in which every level crossing generates data.

3

Figure 3.19: Power spectrum of an AEG signal (inlay: an AEG signal).

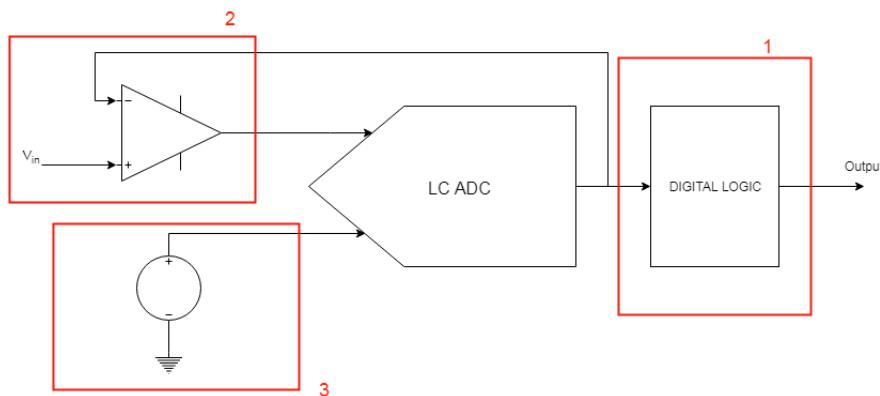

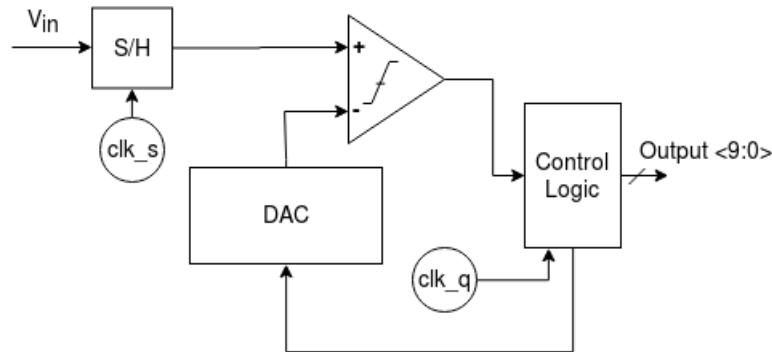

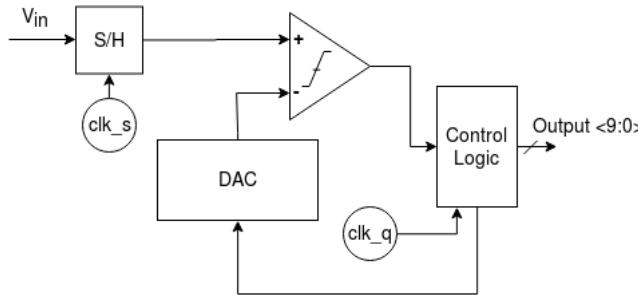

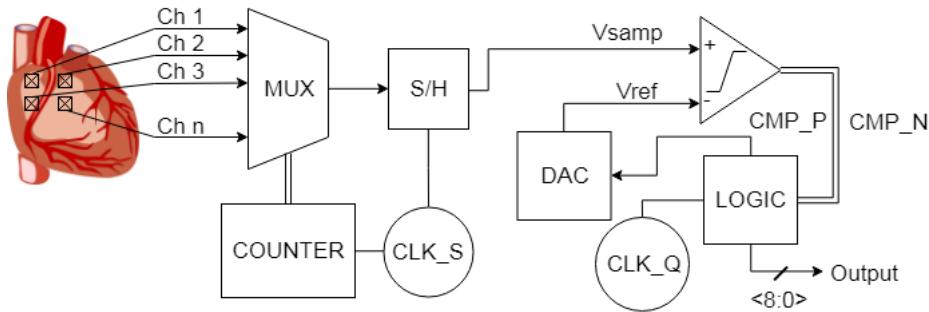

Conventional LC ADCs require two comparators to determine the level-crossing. Since the proposed ADC is based on the level-crossing sampling approach, two comparators were considered at first. However, this implies that two DACs are required to generate the two reference levels. A better approach is to use a single comparator and perform the quantisation with one changeable reference voltage. The reference voltages of the window can be loaded in subsequent steps and compared with the sample. The block diagram of the proposed synchronous LC ADC is shown in Fig. 3.20.

Figure 3.20: Block diagram of the proposed synchronous LC ADC.

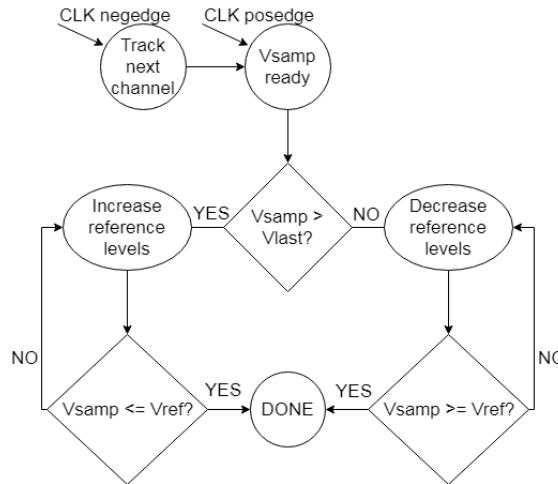

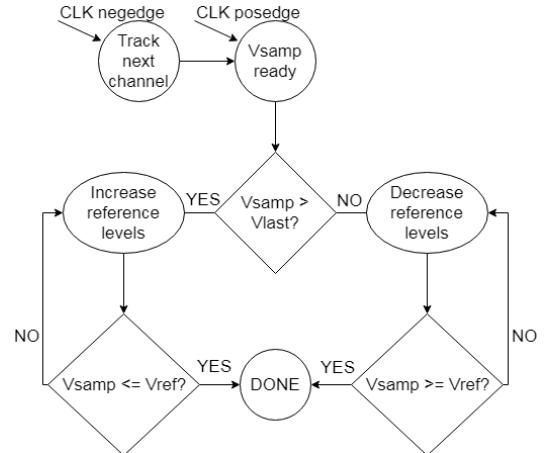

The flowchart representing operation of this method is shown in Fig. 3.21. Every new sample is compared with the highest reference level reached for the previous sample. Based on the output of the comparator the direction of counting in the quantiser is determined. A new reference level is loaded and the compared with the sample until the output of the comparator is opposite to that of its output for the first comparison. E.g. Let the previous sample be at 22.5 mV and the highest reference level thus determined to be 23 mV (for 1 mV quantiser resolution) and the current sample be at 47.2 mV. Then the output of the first comparison will be high, showing that the amplitude of the sample is greater than the reference level. Hence, the quantiser will increase the reference level by 1 LSB step i.e., 1 mV and compare again. This process

Figure 3.21: Flowchart of operation of proposed synchronous LC ADC.

is repeated until the comparator output is low, signifying that the reference level is now greater than the sample. The quantisation process is now complete and the difference in amplitude (i.e. +23) is given as output from the ADC. The format of output of the ADC is discussed in the next chapter.

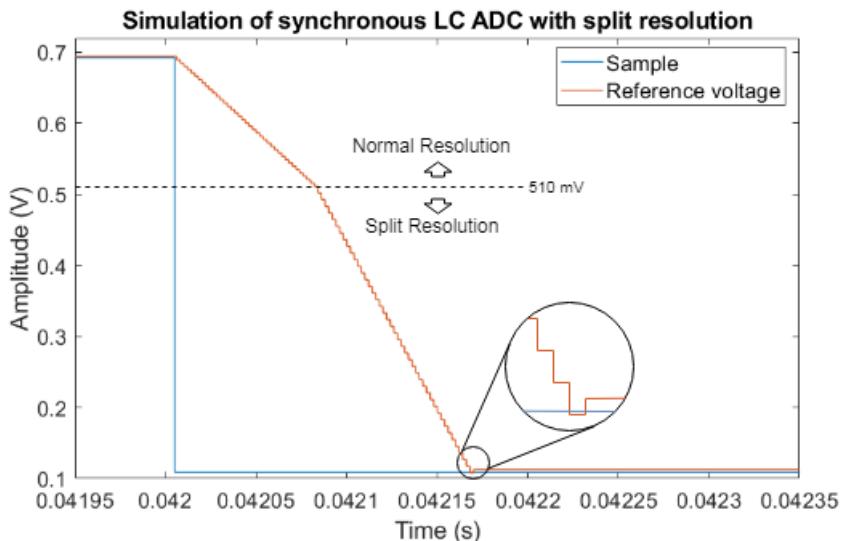

Figure 3.22: Illustration of operation of split resolution technique in the synchronous LC ADC.

The quantisation process in the proposed method is synchronised by a clock signal. Unlike the conventional SAR algorithm in which the quantisation process has a fixed number of steps for each sample, the proposed method has a variable number of quantisation steps depending on the input signal activity. Hence, the clock signal frequency must be able to accommodate the highest number of steps required for quantisation of the input signal. In the worst case the number of steps required could be  $2^M$ , if the difference between two successive samples is equal to the maximum amplitude. However, as discussed above, this condition would not occur for sparse signals such as AEGs, ECGs etc. The maximum number of steps required for quantisation of the signal can be estimated through modelling of the synchronous LC ADC while using typical biosignals as input.

The number of quantisation steps required for each sample in the proposed method can be reduced by introducing the split resolution technique. As described previously the rapid changes in signals are related to peaks which reach high amplitudes. Hence, for samples with amplitudes outside a specific (programmed) amplitude range, the resolution for quantisation can be reduced while quantising beyond the preset am-

plitude range. This method introduces an error of  $+/ - 1$  LSB as sample amplitude may be within  $+/ - 2$  LSB of the final reference level. This error can be corrected by adding another step in which the quantiser reduces the reference voltage level by 1 LSB (instead of 2 LSBs as used in the split resolution technique) and compares again with the sample. The sample is then quantised accurately. This process is illustrated in Fig. 3.22.

### 3.5. COMPARISON OF ARCHITECTURES

3

Several architectures can be considered to implement multi-channel configuration of level-crossing sampling. However, each architecture exhibits some advantages and disadvantages which affect the performance and cost of operation or design. Hence, a qualitative analysis was performed to determine the best architecture for implementation of the multi-channel LC ADCs. The advantages and disadvantages of each architecture are listed in Table 3.3.

The asynchronous sampling paradigm is incompatible with the synchronicity inherent in time-multiplexed systems. Even if synchronicity is introduced into the asynchronous ADC, it degrades the performance while increasing the cost of operation (higher clock speed). This problem was observed in the time-multiplexed LC ADC architecture, the output combiner architecture and the coarse-fine architecture. While circuits such as WTA can resolve this problem, they too increase the cost of operation (higher power consumption). Hence, the asynchronous sampling approach needs to be replaced by the synchronous sampling approach.

Combining level crossing quantisation with synchronous sampling is a good approach to combine the best features of both synchronous and asynchronous recording methods. The synchronous LC ADC architecture as shown above implements this approach. This architecture has activity-dependent operation and activity-dependent output. It uses a single dynamic comparator instead of two continuous-time comparators and thus decreases the power consumption considerably. It can be scaled for higher sampling rates and higher number of channels easily. Moreover, it is not troubled by most of the problems faced by the other architectures. Hence, this architecture is found to be the optimum architecture that meets all the requirements of a multi-channel LC ADC. The performance of the synchronous LC ADC and its advantages over other ADC architectures are quantified through modelling. The method of modelling and the results are discussed in the next chapter.

### 3.6. CONCLUSIONS

The adaptive resolution technique as discussed in the previous chapter suffers from data overhead which increases the total amount of data generated in the LC ADC. Thus, Split Resolution technique was introduced that solves the data overhead problem in adaptive resolution techniques. The various methods for implementation of the split resolution technique are also discussed along with model simulations.

Several architectures can be considered to implement the multi-channel LC ADC. As the level-crossing sampling implements asynchronous sampling while time-multiplexed systems are inherently synchronous, they are not compatible. Thus, a novel approach is introduced in which sampling is performed synchronously while quantisation is performed according to the level-crossing quantisation method. This makes the operation of the quantiser activity-dependent. Moreover, the output data generated is also activity-dependent. The modelling and model simulations of the proposed synchronous LC ADC architecture are discussed in the next chapter.

Table 3.3: Comparison of Architectures.

| Architecture                      | <i>Advantages</i>                                                                                                                                                    | <i>Disadvantages</i>                                                                                                                                                      |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spatially Correlated Sampling     | <ul style="list-style-type: none"> <li>• Exploits correlation of signal between adjacent channels</li> </ul>                                                         | <ul style="list-style-type: none"> <li>• Complex circuit design</li> <li>• Degraded performance of ADC due to large differences in multi-channel input signals</li> </ul> |

| Time-multiplexed LC ADC           | <ul style="list-style-type: none"> <li>• Simple circuit design</li> <li>• Dynamic comparators are used instead of continuous-time comparators</li> </ul>             | <ul style="list-style-type: none"> <li>• Very fast quantisation clock signal required</li> <li>• Operation is no longer activity dependent</li> </ul>                     |

| Asynchronously Multiplexed LC ADC | <ul style="list-style-type: none"> <li>• Activity-dependent operation</li> </ul>                                                                                     | <ul style="list-style-type: none"> <li>• High power consumption in WTA circuit</li> </ul>                                                                                 |

| Multichannel Output Encoding      | <ul style="list-style-type: none"> <li>• Reduced number of output wires</li> </ul>                                                                                   | <ul style="list-style-type: none"> <li>• Very fast clock signal required to synchronise output</li> <li>• Minimal reuse of ADC components</li> </ul>                      |

| Coarse-Fine Architecture          | <ul style="list-style-type: none"> <li>• Less constraints on individual LC ADC design</li> </ul>                                                                     | <ul style="list-style-type: none"> <li>• Not activity dependent</li> <li>• Very fast quantisation clock signal required</li> </ul>                                        |

| Synchronous LC ADC                | <ul style="list-style-type: none"> <li>• Activity dependent operation</li> <li>• One dynamic comparator used</li> <li>• Output data is activity-dependent</li> </ul> | <ul style="list-style-type: none"> <li>• Fast quantisation clock signal required</li> <li>• Complex circuit logic required</li> </ul>                                     |

# 4

## PROPOSED MULTICHANNEL LC ADC

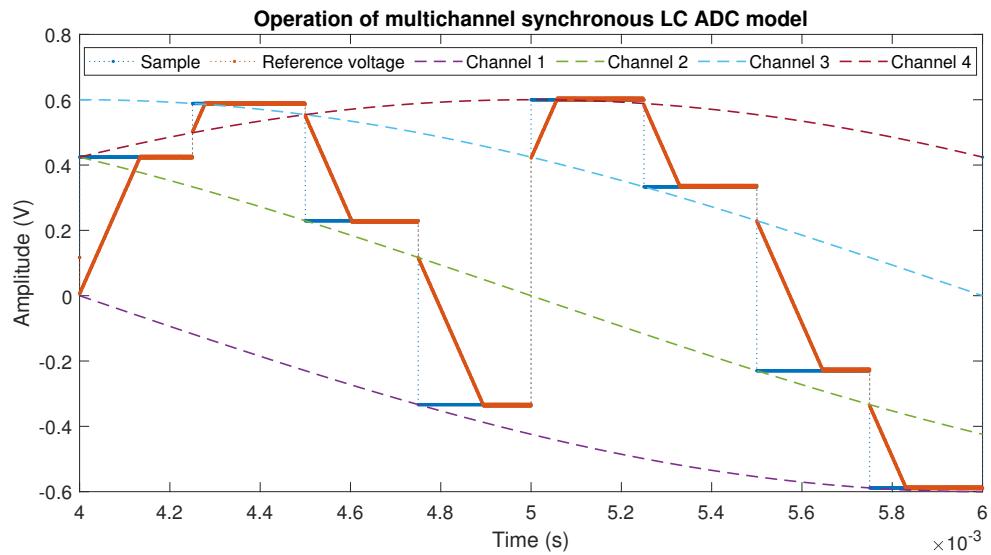

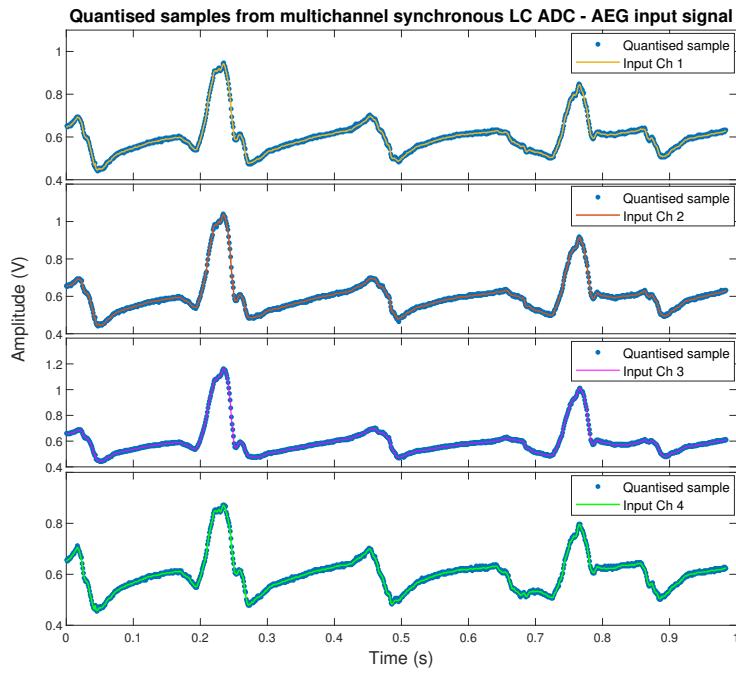

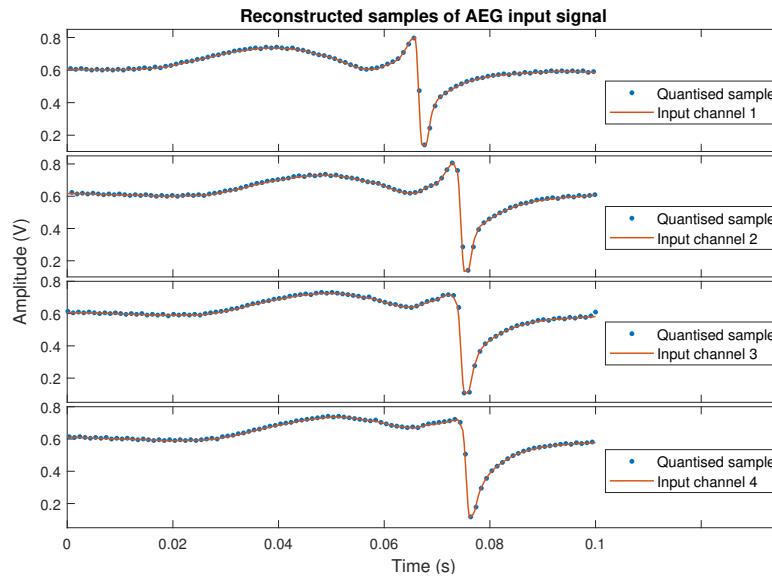

The proposed multichannel synchronous LC ADC was introduced in the previous chapter along with its major features. This chapter discusses the models used to test the functionality of the proposed ADC at the system level and to quantify the performance of the ADC as compared to conventional synchronous ADCs.

### 4.1. MODELLING OF SYNCHRONOUS LC ADC

The VerilogA model of the LC ADC as shown previously operates asynchronously and converts the analog input signal into digital form in the continuous time domain. However, the proposed synchronous LC ADC samples the input signal synchronously and then quantises the sample using level-crossing approach. The operation is different from that of the asynchronous LC ADC. Hence, the model is modified accordingly.

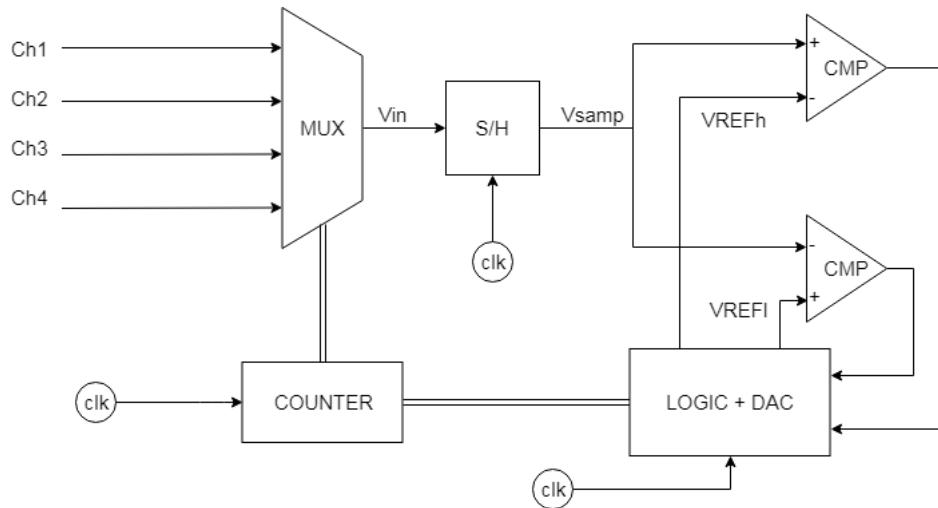

Figure 4.1: Block diagram of synchronous LC ADC.

The VerilogA model of a single channel LC ADC shown previously is modified to operate synchronously while a clock input is also provided to the ADC. The VerilogA code of the model can be found in Appendix A.1. The block diagram of the model is shown in Fig.4.1. A Sample and Hold block is added to hold the sample while it is quantised. The sample is compared with the quantised reference voltage of the previous sample. Otherwise the reference voltage is changed in steps of 1 LSB each until the amplitude of the sample is crossed by the reference voltage. The number of steps moved in either direction are counted and given as output for that sample. The output of the comparator is checked in each iteration to determine the end of the quantisation process. This reference voltage is the starting point for quantisation of the next sample.

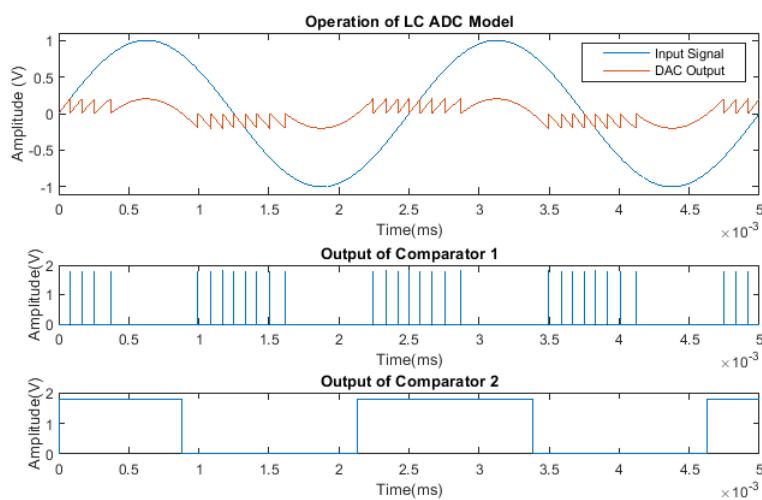

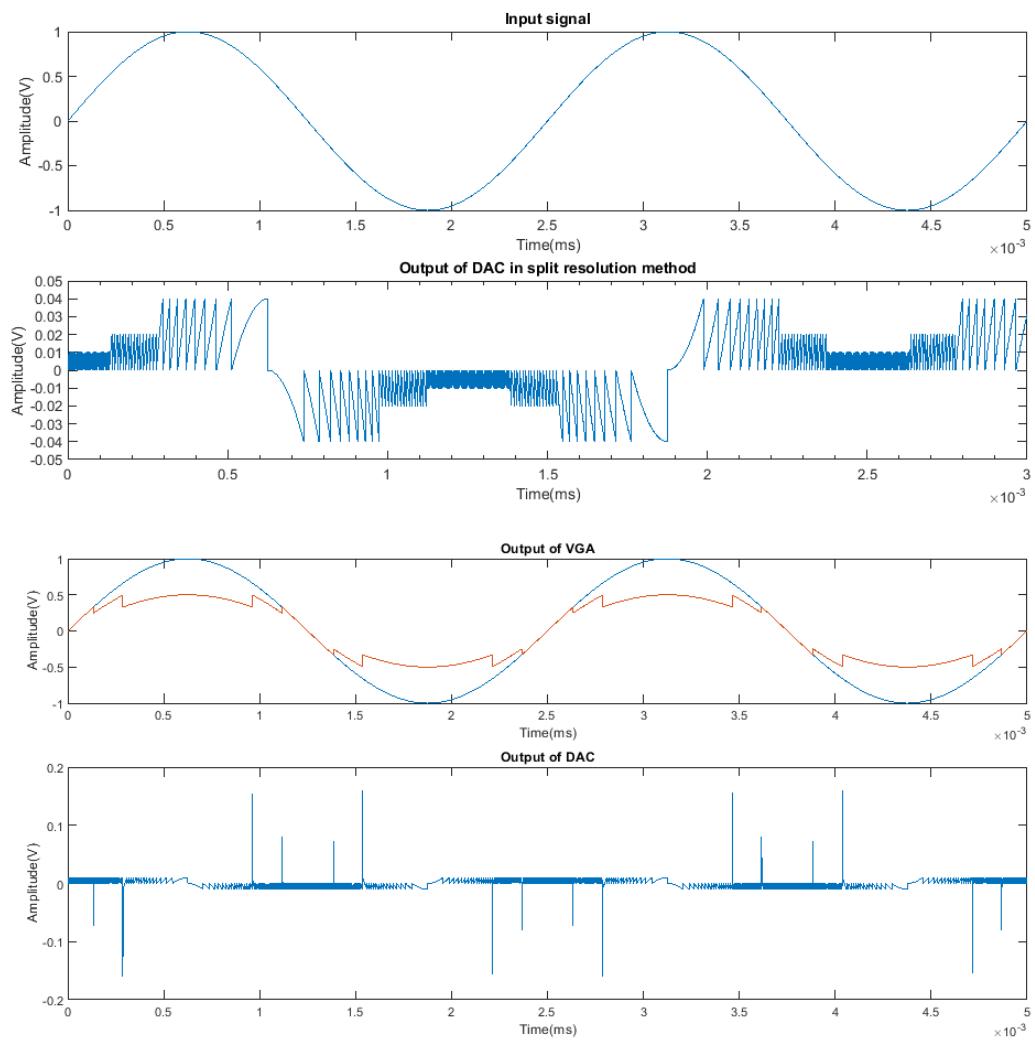

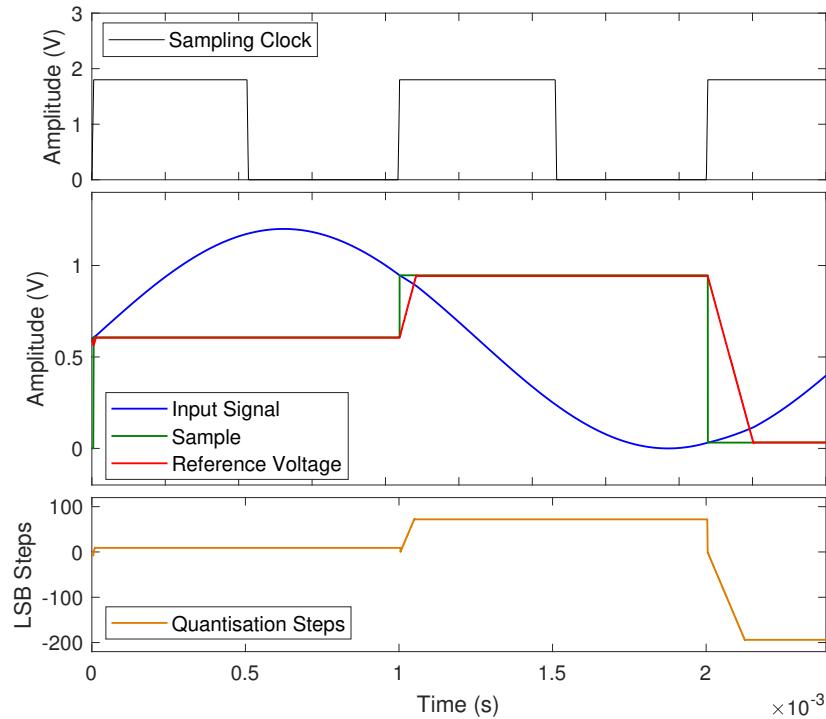

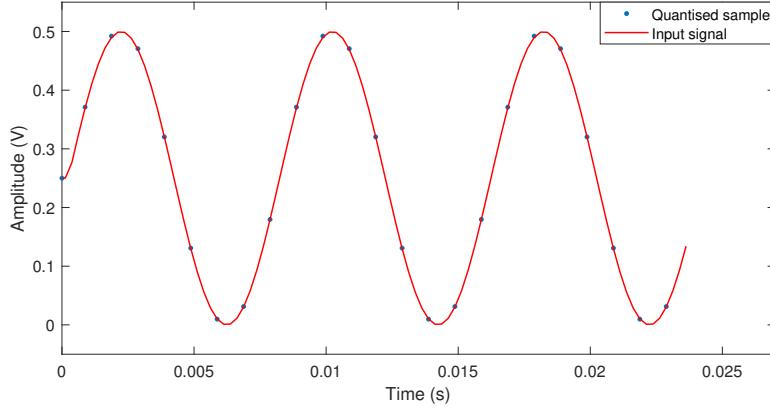

The model is simulated with a sinusoidal input signal at 400 Hz. The input signal has a peak-peak amplitude of 1.2 V. The quantiser is configured with LSB step size of 4.6875 mV. Thus, the quantiser quantises the sample at 8 bits of resolution. The quantisation process is synchronised with a 1 MHz quantisation clock signal. The sampling is performed at 1 kS/s. The quantisation clock frequency used here is much

Figure 4.2: Operation of VerilogA Model of Synchronous LC ADC.

higher than required. The method of estimation for the required quantisation clock frequency for a particular input signal will be discussed later. The input signal, the sample captured in the S&H block, the quantised value and the ADC output are shown in Fig. 4.2.

## 4.2. ESTIMATION OF QUANTISATION CLOCK FREQUENCY

In conventional synchronous ADCs the quantisation process is synchronised with a specific clock signal. The quantisation clock frequency is determined on the basis of the quantisation method. For instance, the SAR algorithm requires 'n' clock cycles to complete the quantisation for each sample, where 'n' is the quantiser resolution. Thus, the quantisation clock frequency for a SAR ADC would be -

$$F_{q,SAR} = n.F_s \quad (4.1)$$

where  $F_s$  is the sampling rate of the SAR ADC. However, in the proposed synchronous LC ADC architecture, the quantisation process is not fixed to a specific number of quantisation steps. The number of quantisation steps required is dependent on the signal activity. Hence, the quantisation clock frequency must be set according to the worst case, i.e. the most number of quantisation steps required for a sample of the input signal.

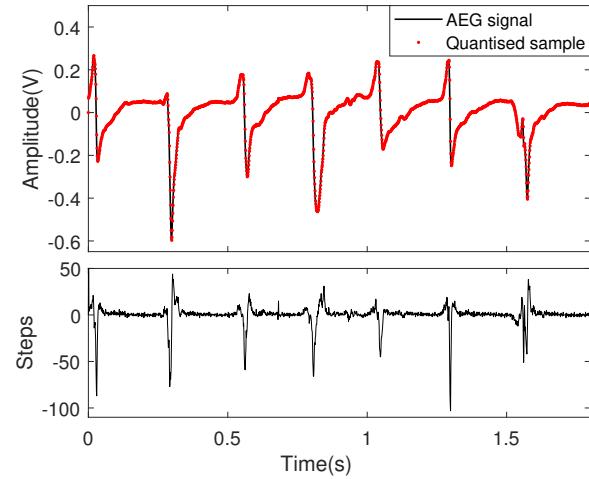

Ideally, the worst case would denote  $V_{max}$  or the common mode input range. The quantiser would then require  $2^M + 1$  clock cycles to complete the quantisation. However, as discussed in the previous chapter, the AEG signals have higher amplitudes at lower frequencies. Hence, the worst case condition would never occur but the maximum number of quantisation steps required for a specific signal needs to be estimated. This can be performed in a MATLAB model in which the synchronous LC ADC's quantisation process is modelled and the input signal is sampled (Appendix-A.3). The number of quantisation steps required for each sample are then calculated, and the maximum value is used to calculate the frequency of the quantisation clock. A margin is added to the estimate to ensure error-free operation. The estimate of number of quantisation steps required for samples a typical AEG signal is shown in Fig. 4.3. As can be observed in the plot, the maximum number of quantisation steps required for the AEG signal sampled at 1 kS/s is 100. 2 clock cycles are required for each quantisation step. Hence, 200 clock cycles are required for the

Figure 4.3: Estimation of number of quantisation steps required for an AEG signal. The plot above shows the input AEG signal and the quantised samples. The plot below shows the number of quantisation steps required to complete the quantisation for each sample.

Figure 4.4: Example of atrial electrogram in sinus rhythm (SR) condition.

quantisation of the sample. The quantisation is completed in half the time period of the sampling clock signal. Hence, if the sampling rate is 1 kS/s then the quantisation clock frequency needs to be:

$$F_{q,SLC} = 1/(500e - 6/(200)) = 400 \text{ kHz} \quad (4.2)$$

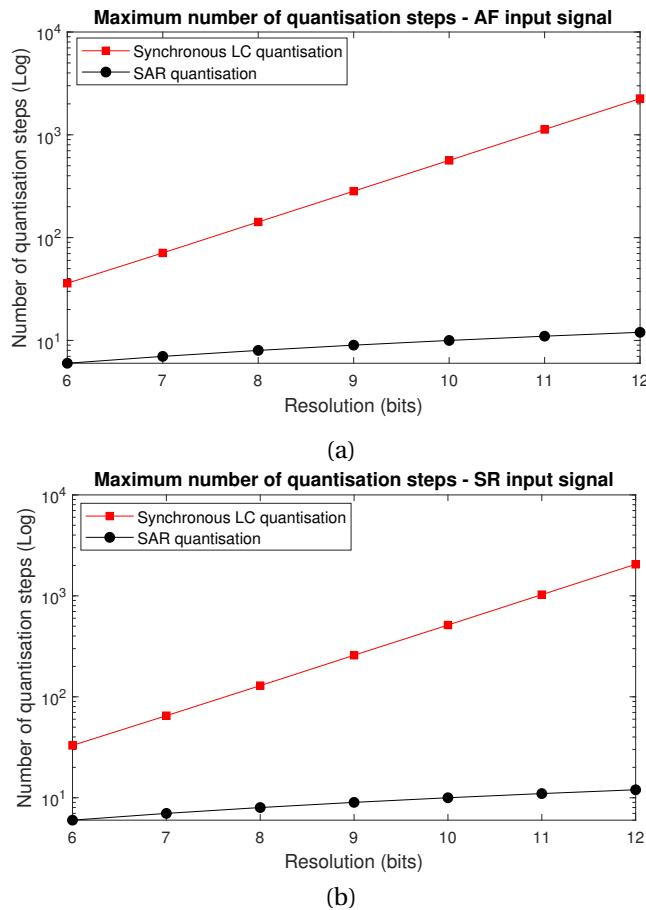

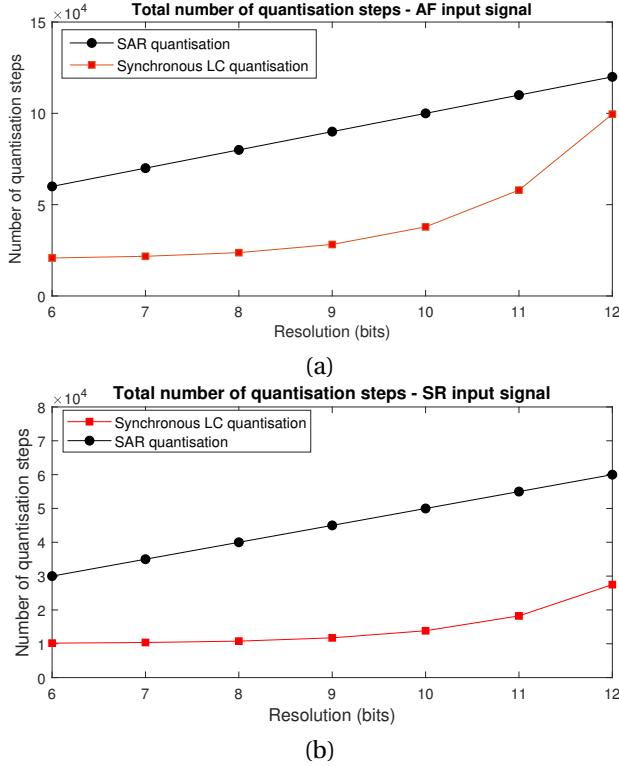

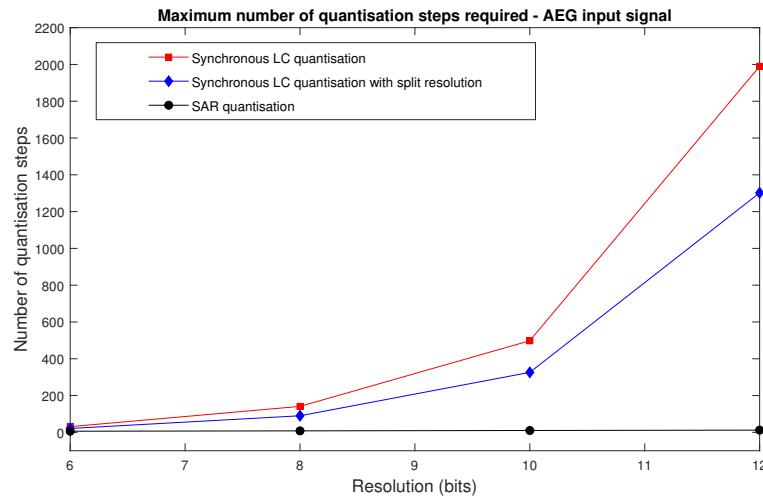

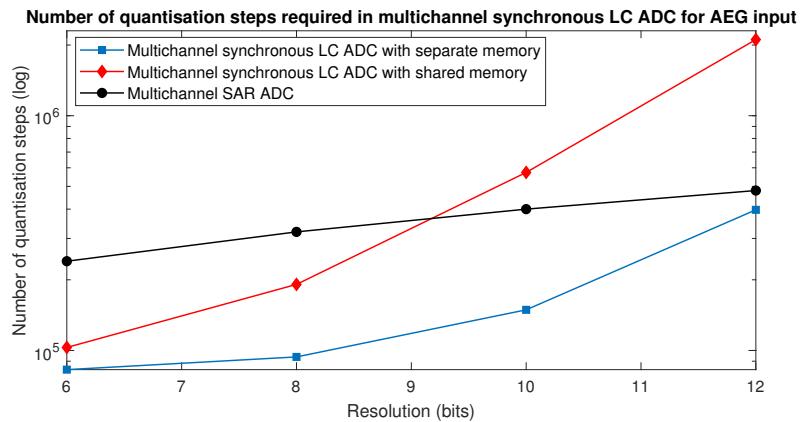

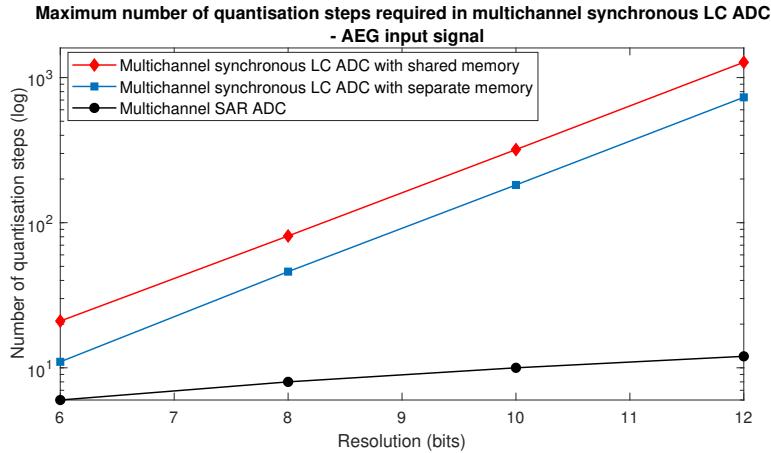

The maximum number of quantisation steps required for quantisation of AEG input signals with induced AF condition and with normal SR condition are determined using the model for different quantiser resolutions. The results are shown in Fig. 4.5. The example of an AEG signal with AF condition was shown in Fig. 1.3. The example of an AEG in sinus rhythm i.e. normal condition is shown in Fig. 4.4. As can be seen from the results the maximum number of quantisation steps required for quantisation of AEG signals is much higher in the proposed synchronous LC ADC than in the conventional SAR ADC. Moreover, the results are similar for both AEG signals (with AF condition and with SR condition). It should be noted however that the maximum number of quantisation steps is required in the synchronous LC ADC for very few samples and not for every sample. It can also be observed that the maximum number of quantisation steps required is doubled for every extra resolution bit as expected.

Figure 4.5: Maximum number of quantisation steps required for (a) atrial electrogram with induced AF (b) atrial electrogram in sinus rhythm, determined in MATLAB model simulations.

### 4.3. ACTIVITY-DEPENDENT QUANTISATION

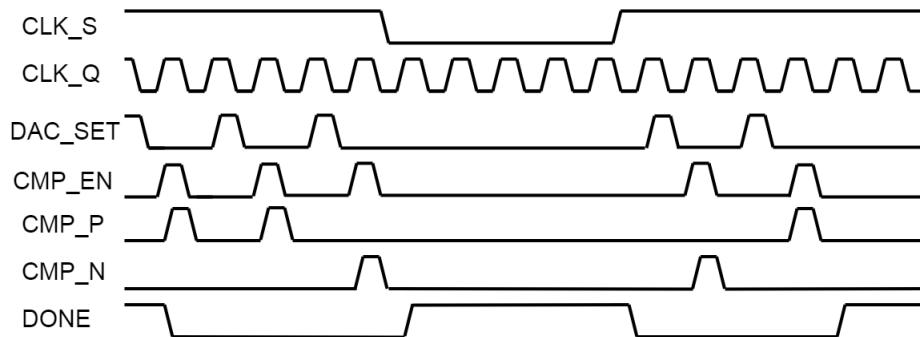

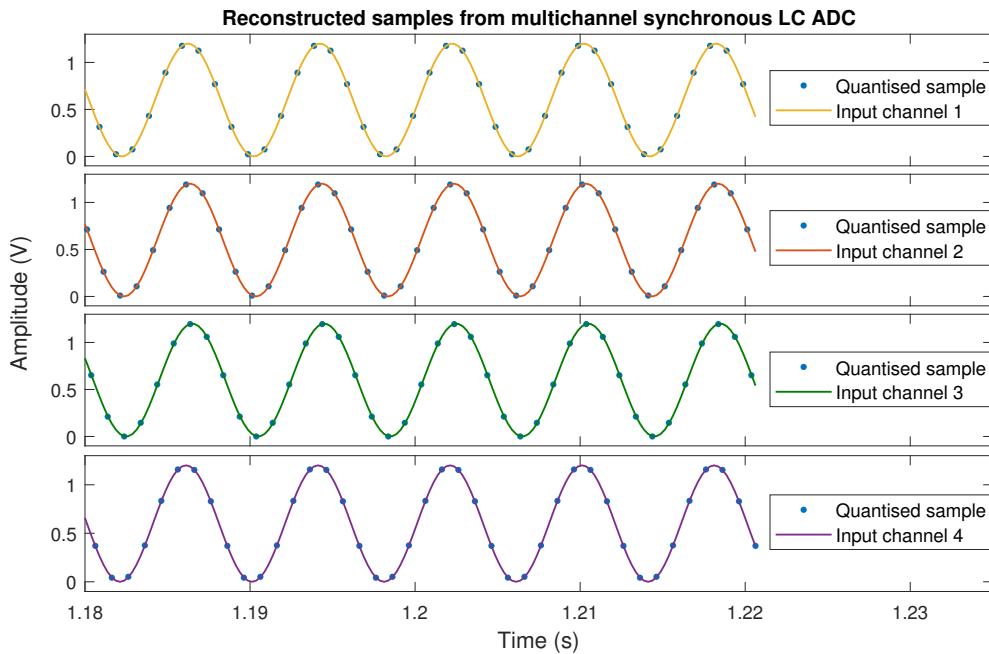

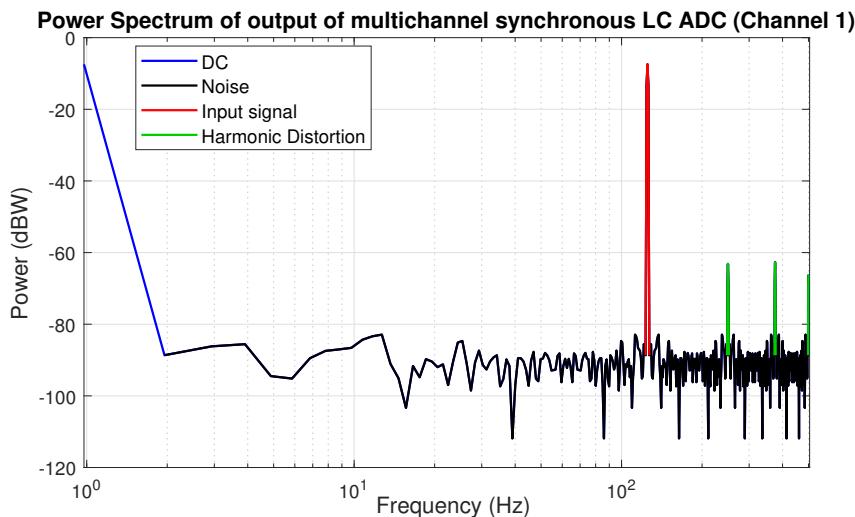

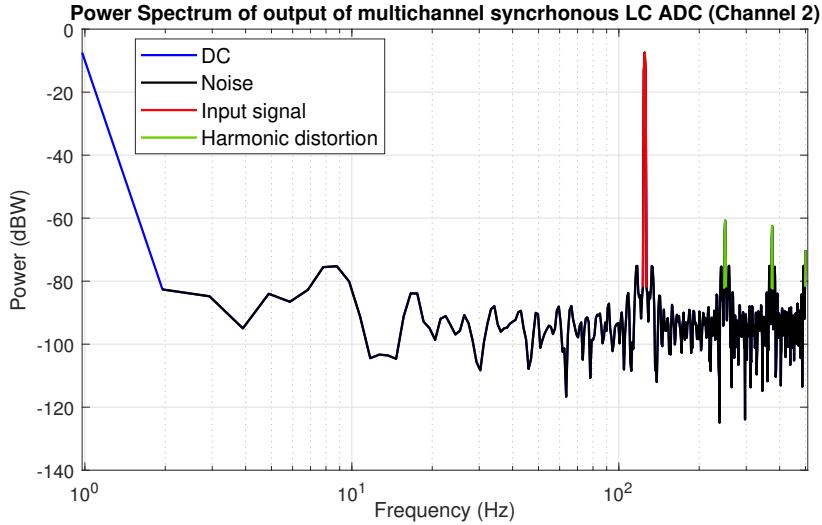

The quantisation process of the proposed synchronous LC ADC is dependent on the activity of the input signal, as illustrated in the model simulations above. While conventional synchronous ADCs use the same number of quantisation steps for each sample, the quantisation process in the synchronous LC ADC is variable.