# Computer Engineering Mekelweg 4, 2628 CD Delft The Netherlands http://ce.et.tudelft.nl/

### MSc THESIS

## Exploring Tile-Based Rasterization Alternatives for Mobile Devices

M.C.A. van der Weide

#### CE-MS-2010-19

#### Abstract

Tile-based rasterization was recently proposed as a solution for enabling three dimensional computer graphics on low-power mobile devices. In tile-based rasterization the screen is decomposed into independent parts, called tiles, that are processed sequentially by a simple embedded graphics accelerator. By keeping these tiles small, on-chip memory can be used to store intermediate rasterization values. This reduces a major source of power dissipation when compared to a conventional graphics pipeline, the external traffic between the rasterization hardware and the framebuffer.

In the GRAphics AcceLerator (GRAAL) project a tile-based rasterization solution utilizing a scenebuffer resident in external memory was proposed. The scenebuffer contains the rasterization instructions needed to process all the screen tiles and is reused for the rasterization of every tile. Several sorting algorithms were introduced to prevent unnecessary accesses to the graphics accelerator.

In this thesis we first argue that there is not enough available hardware budget to implement this sorting in hardware and that performing the sorting in software requires serious effort from the embedded microprocessor. Therefore, we propose two alternative tile-based rasterization solutions for mobile devices. First, direct rasterization, were the embedded accelerator is used directly to process a number of locally stored rasterization instructions for all tiles. Experimental results indicate that the external traffic is 80% when compared to non tile-based rasterization, but unfortunately scenebuffer rasterization results in only 25% of the external traffic of non tile-based rasterization. Second, hierarchical rasterization, a combination of scenebuffer and direct rasterization. Experimental results indicate that there is a wide range of system topologies that outperform scenebuffer rasterization from an external traffic point of view (up to 22% reduction over scenebuffer) and from a software workload point of view (up to 57.8% reduction over scenebuffer). More importantly, some topologies reduce both the external traffic and the software workload when compared to scenebuffer rasterization even some topologies assuming a smaller hardware budget.

**Delft University of Technology**

### Exploring Tile-Based Rasterization Alternatives for Mobile Devices GRAAL revisited

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

COMPUTER ENGINEERING

by

M.C.A. van der Weide born in Hellevoetsluis, The Netherlands

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

## Exploring Tile-Based Rasterization Alternatives for Mobile Devices

by M.C.A. van der Weide

#### Abstract

Tile-based rasterization was recently proposed as a solution for enabling three dimensional computer graphics on low-power mobile devices. In tile-based rasterization the screen is decomposed into independent parts, called tiles, that are processed sequentially by a simple embedded graphics accelerator. By keeping these tiles small, on-chip memory can be used to store intermediate rasterization values. This reduces a major source of power dissipation when compared to a conventional graphics pipeline, the external traffic between the rasterization hardware and the framebuffer.

In the GRAphics AcceLerator (GRAAL) project a tile-based rasterization solution utilizing a scenebuffer resident in external memory was proposed. The scenebuffer contains the rasterization instructions needed to process all the screen tiles and is reused for the rasterization of every tile. Several sorting algorithms were introduced to prevent unnecessary accesses to the graphics accelerator.

In this thesis we first argue that there is not enough available hardware budget to implement this sorting in hardware and that performing the sorting in software requires serious effort from the embedded microprocessor. Therefore, we propose two alternative tile-based rasterization solutions for mobile devices. First, direct rasterization, were the embedded accelerator is used directly to process a number of locally stored rasterization instructions for all tiles. Experimental results indicate that the external traffic is 80% when compared to non tile-based rasterization, but unfortunately scenebuffer rasterization results in only 25% of the external traffic of non tile-based rasterization. Second, hierarchical rasterization, a combination of scenebuffer and direct rasterization. Experimental results indicate that there is a wide range of system topologies that outperform scenebuffer rasterization from an external traffic point of view (up to 22% reduction over scenebuffer) and from a software workload point of view (up to 57.8% reduction over scenebuffer). More importantly, some topologies reduce both the external traffic and the software workload when compared to scenebuffer rasterization even some topologies assuming a smaller hardware budget.

**Laboratory** : Computer Engineering

Codenumber : CE-MS-2010-19

Committee Members :

Advisor: Sorin Cotofana, CE, TU Delft

Member: R. van Leuken, CE, TU Delft

Member: S. Wong, CE, TU Delft

Member: S. Cotofana, CE, TU Delft

Member: K. Bertels, CE, TU Delft

## Contents

| Li           | st of | Figur  | es                                    | vi   |

|--------------|-------|--------|---------------------------------------|------|

| Li           | st of | Table  | es es                                 | vii  |

| $\mathbf{A}$ | ckno  | wledge | ements                                | ix   |

| 1            | Inti  | roduct | ion                                   | 1    |

|              | 1.1   | Tile-E | Based Rasterization on mobile devices | . 3  |

|              | 1.2   | Resea  | rch Objectives & Contributions        | . 4  |

|              | 1.3   | Overv  | view                                  | . 8  |

| <b>2</b>     | Mo    | bile G | raphics                               | 11   |

|              | 2.1   | Design | n Criteria                            | . 11 |

|              | 2.2   | Proble | ems with Conventional Rasterization   | . 12 |

|              | 2.3   | Tile-E | Based Rasterization                   | . 13 |

|              | 2.4   | Tile-E | Based Rasterization Hardware: GRAAL   | . 15 |

|              | 2.5   | Scene  | buffer Tile-Based Rasterization       | . 18 |

|              |       | 2.5.1  | Basic Concept                         |      |

|              |       | 2.5.2  | External Traffic                      | . 20 |

|              |       | 2.5.3  | Sorting Algorithms                    | . 21 |

|              |       | 2.5.4  | Overlap Determination                 | . 23 |

| 3            | Dir   |        | le-Based Rasterization                | 27   |

|              | 3.1   |        | ation of Previous Work                |      |

|              | 3.2   | Direct | t Tile-Based Rasterization            |      |

|              |       | 3.2.1  | Basic Concept                         |      |

|              |       | 3.2.2  | Overlap Representation                |      |

|              |       | 3.2.3  | Tile Selection                        |      |

|              |       | 3.2.4  | Databack Reduction                    |      |

|              | 3.3   |        | are and Hardware Modifications        |      |

|              |       | 3.3.1  | Software                              |      |

|              |       | 3.3.2  | External Traffic                      |      |

|              |       | 3.3.3  | Hardware                              |      |

|              | 3.4   |        | rchical Rasterization                 |      |

|              |       | 3.4.1  | Basic Concept                         |      |

|              | 3.5   | Summ   | arv                                   | 43   |

| 4            | $\mathbf{E}\mathbf{x}\mathbf{p}$ | erimei | ntal Platform                                 | 45  |

|--------------|----------------------------------|--------|-----------------------------------------------|-----|

|              | 4.1                              | Bench  | marks                                         | 45  |

|              | 4.2                              | Applic | eation and Geometry Stages                    | 46  |

|              | 4.3                              | Raster | rization Stage Simulation                     | 47  |

|              |                                  | 4.3.1  | Measuring Datafront Traffic                   | 49  |

|              |                                  | 4.3.2  | Measuring Databack Traffic                    | 54  |

| 5            | Exp                              | erimei | ntal Results                                  | 61  |

|              | 5.1                              | Evalua | ating Datafront Traffic                       | 61  |

|              | 5.2                              | Evalua | ating Databack Traffic                        | 65  |

|              | 5.3                              | Compa  | aring Scenebuffer versus Direct Rasterization | 72  |

|              | 5.4                              | Combi  | ned Rasterization                             | 76  |

|              | 5.5                              | Attem  | pt to system level evaluation                 | 81  |

| 6            | Con                              | clusio | as                                            | 87  |

|              | 6.1                              | Summ   | ary                                           | 87  |

|              | 6.2                              | Contri | butions                                       | 89  |

|              | 6.3                              | Recom  | mendations                                    | 91  |

|              |                                  | 6.3.1  | Tile List Overlap Representation              | 92  |

|              |                                  | 6.3.2  | Dynamic Size of Sections                      | 92  |

|              |                                  | 6.3.3  | Modifying the Rasterization Order             | 93  |

|              |                                  | 6.3.4  | Reducing Texture Traffic                      | 94  |

| $\mathbf{A}$ | App                              | endix  | : Computer Graphics                           | 97  |

|              | A.1                              | Comp   | uter Graphics                                 | 97  |

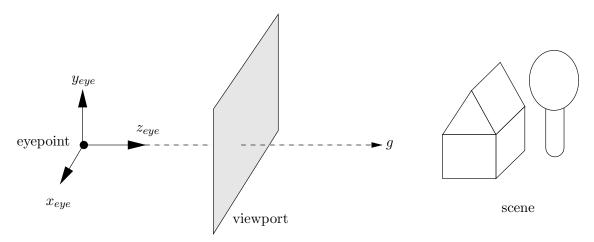

|              |                                  | A.1.1  | Scene Definition                              | 97  |

|              |                                  | A.1.2  | Selecting an Eyepoint and Viewport            | 99  |

|              |                                  | A.1.3  | Projecting the Scene on the Viewport          | 100 |

|              |                                  | A.1.4  | Rasterization of the Projection               | 102 |

|              |                                  | A.1.5  | Interpolation of per pixel Parameters         | 104 |

|              | A.2                              | Graph  | ics Pipeline                                  | 106 |

|              |                                  | A.2.1  | Application Stage                             | 107 |

|              |                                  | A.2.2  | Geometry Stage                                | 108 |

|              |                                  | A.2.3  | Rasterization Stage                           | 108 |

| Bi           | bliog                            | graphy |                                               | 117 |

## List of Figures

| 2.1  | Conventional fullscreen rasterization organization                                                                                         | 12 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Effort versus time in Tile-based Rasterization with four Parallel Rasterizers.                                                             | 14 |

| 2.3  | Effort versus time in Tile-based rasterization with a single Rasterizer                                                                    | 15 |

| 2.4  | GRAAL pipeline with internal buffers for the stencil, depth, and color                                                                     |    |

|      | values                                                                                                                                     | 16 |

| 2.5  | Phase one (application, geometry, and pre-sorting) in a scenebuffer ras-                                                                   |    |

|      | terization scenario                                                                                                                        | 19 |

| 2.6  | Phase two (post-sorting and rasterization) in a scenebuffer rasterization                                                                  |    |

|      | scenario                                                                                                                                   | 19 |

| 2.7  | Definition of the datafront and databack traffic components                                                                                | 20 |

| 2.8  | Sorting a triangle to bins in the scenebuffer                                                                                              | 22 |

| 2.9  | Determining the tile overlap via a bounding box test                                                                                       | 24 |

| 2.10 | Determining the inside of a triangle based on linear edge functions                                                                        | 25 |

| 3.1  | Direct tile-based rasterization concept in steps                                                                                           | 31 |

| 3.2  | Representing the triangle inside the buffer with a tilemask                                                                                | 33 |

| 3.3  | Rasterization progress for tile $(i, j)$                                                                                                   | 36 |

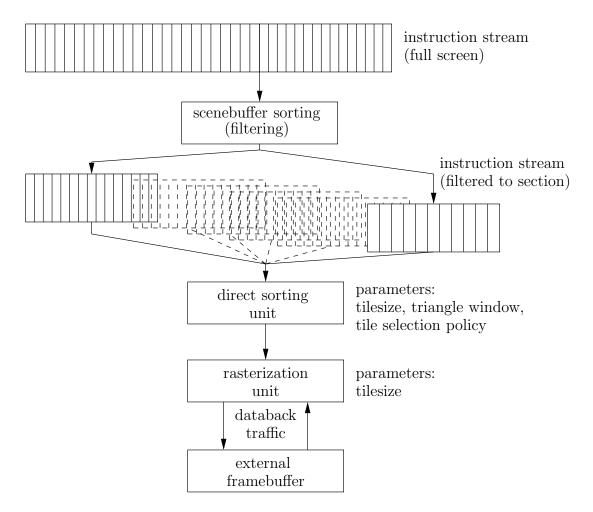

| 3.4  | Direct (Tile-Based) rasterization system topology                                                                                          | 37 |

| 3.5  | Direct Sorting unit major hardware components                                                                                              | 40 |

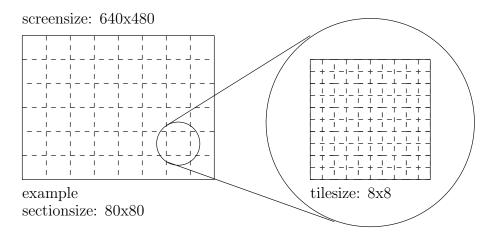

| 3.6  | Screen division into sections and recursive section division into tiles. $\dots$                                                           | 42 |

| 3.7  | System diagram for hierarchical tile-based rasterization                                                                                   | 43 |

| 4.1  | Instruction stream generated by the modified mesa3d library                                                                                | 47 |

| 4.2  | Triangle Mesh.                                                                                                                             | 53 |

| 4.3  | Construction of the databack traffic simulator                                                                                             | 57 |

| 4.4  | Depth image exported during rasterization simulation of the dino bench-                                                                    | •  |

|      | mark                                                                                                                                       | 60 |

|      |                                                                                                                                            |    |

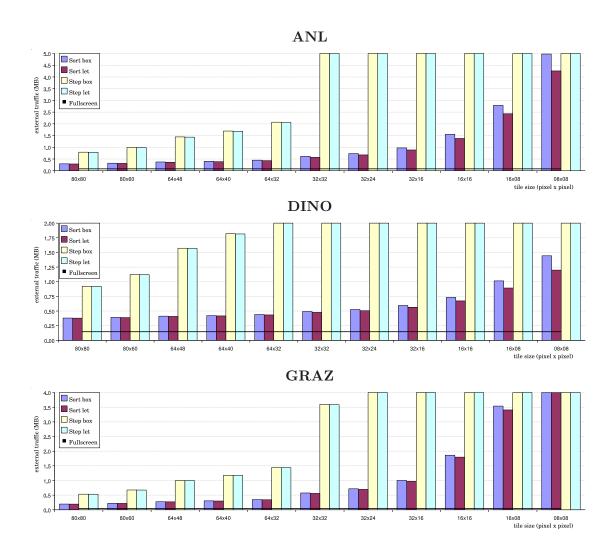

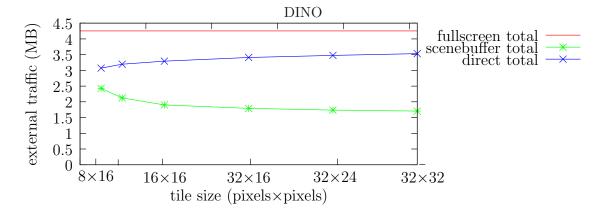

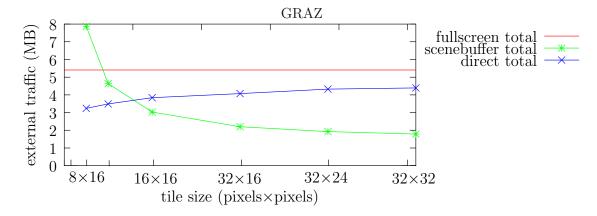

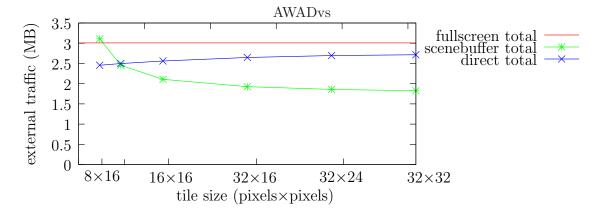

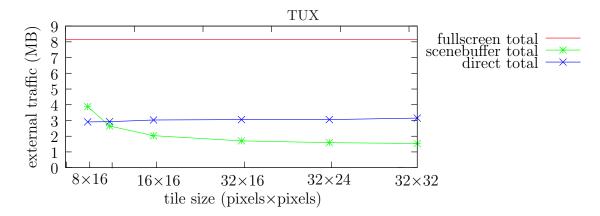

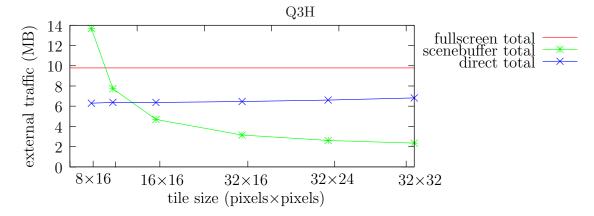

| 5.1  | Average datafront per frame during the rasterization of the ANL, DINO,                                                                     |    |

|      | and GRAZ benchmarks utilizing four different sorting algorithms in a                                                                       | 62 |

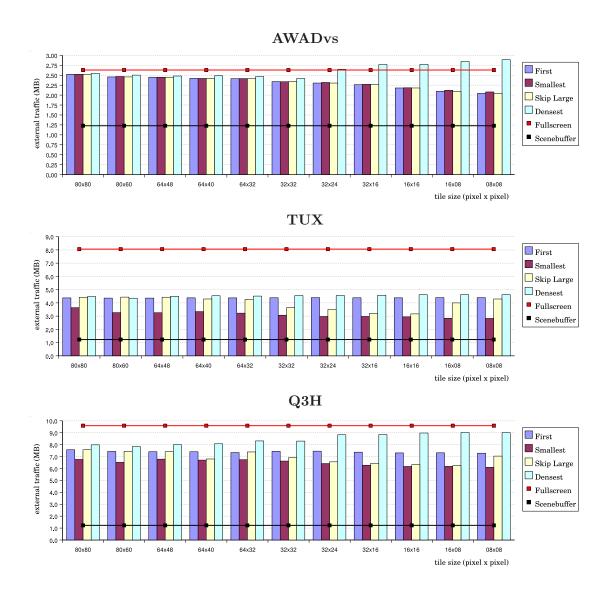

| 5.2  | scenebuffer tile-based rasterization scenario with varying tile sizes Average data_front per frame during the rasterization of the AWADvs, | 02 |

| 0.2  | TUX, and Q3H benchmarks utilizing four different sorting algorithms in                                                                     |    |

|      | a scenebuffer tile-based rasterization scenario with varying tile sizes                                                                    | 63 |

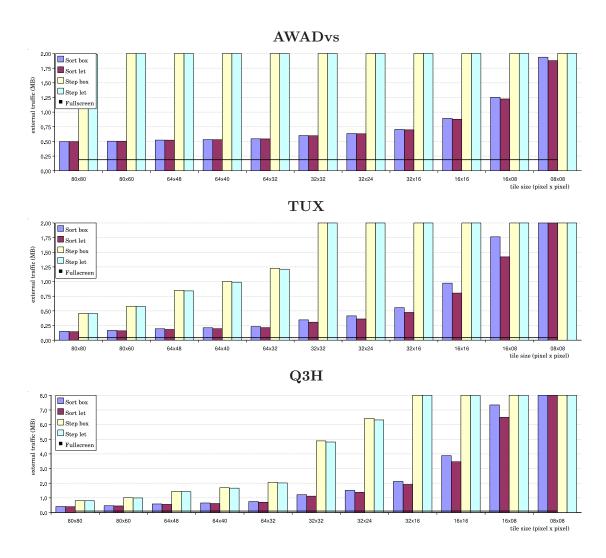

| 5.3  | Average external traffic in the databack per frame during the rasteriza-                                                                   |    |

|      | tion of the ANL, DINO, and GRAZ benchmarks utilizing four different                                                                        |    |

|      | tile selection mechanisms in a direct tile-based rasterization scenario with                                                               |    |

|      | varying tile sizes                                                                                                                         | 66 |

| 5.4  | Average external traffic in the databack during the rasterization of the                                                                   |    |

|      | AWADvs, TUX, and Q3H benchmarks utilizing four different tile selection                                                                    |    |

|      | mechanisms in a direct tile-based rasterization scenario with varying tile                                                                 |    |

|      | sizes                                                                                                                                      | 67 |

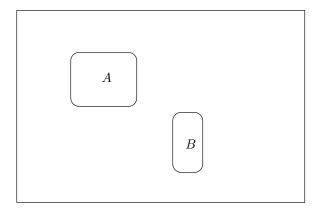

| 5.5  | Positioning of two non-overlapping Shapes $A$ and $B$ in a screen                    | 68       |

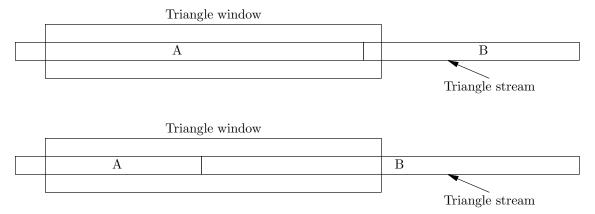

|------|--------------------------------------------------------------------------------------|----------|

| 5.6  | Advance of the triangle window in a direct rasterization scenario                    | 68       |

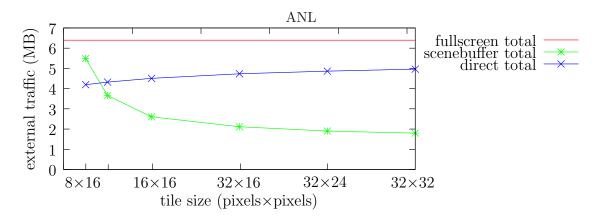

| 5.7  | Comparing the external traffic between a fullscreen, scenebuffer, and di-            |          |

|      | rect rasterization scenario during the ANL benchmark                                 | 73       |

| 5.8  | Comparing the external traffic between a fullscreen, scenebuffer, and di-            |          |

|      | rect rasterization scenario during the DINO benchmark                                | 73       |

| 5.9  | Comparing the external traffic between a fullscreen, scenebuffer, and di-            |          |

|      | rect rasterization scenario during the GRAZ benchmark                                | 74       |

| 5.10 | Comparing the external traffic between a fullscreen, scenebuffer, and di-            |          |

|      | rect rasterization scenario during the AWADvs benchmark for smaller tile             |          |

|      | sizes                                                                                | 74       |

| 5.11 | Comparing the external traffic between a fullscreen, scenebuffer, and di-            |          |

|      | rect rasterization scenario during the TUX benchmark for smaller tile sizes.         | 75       |

| 5.12 | Comparing the external traffic between a fullscreen, scenebuffer, and di-            |          |

|      | rect rasterization scenario during the Q3H benchmark for smaller tile sizes.         | 75       |

| 5.13 | Example system partitioning in sections and tiles for a hierarchical ras-            |          |

|      |                                                                                      | 77       |

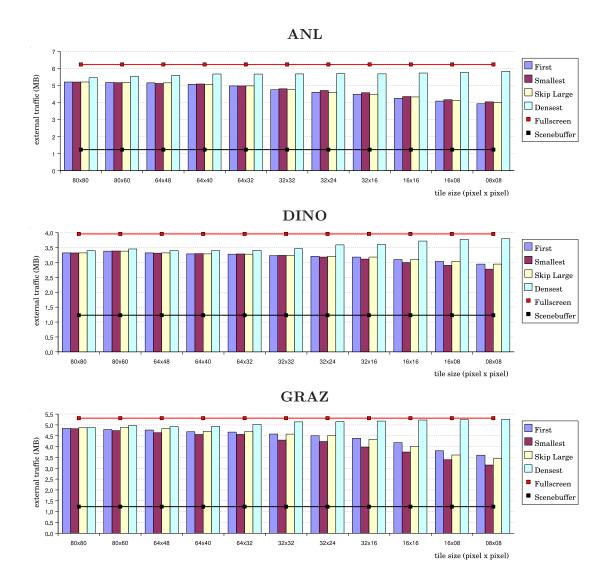

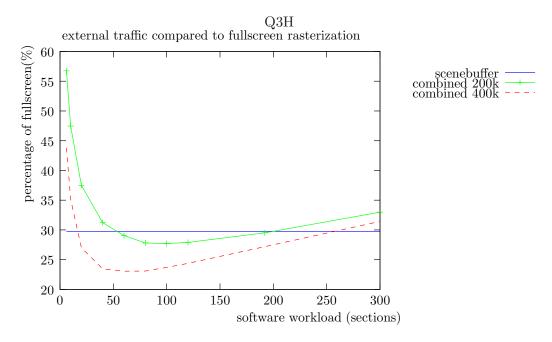

| 5.14 | Comparing the external traffic in $(\%)$ of the full<br>screen rasterization traffic |          |

|      | • 9                                                                                  | 79       |

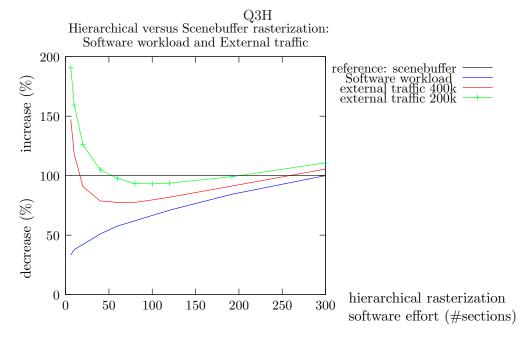

| 5.15 | The reduction of external traffic (in $\%$ ) and the reduction in software work-     |          |

|      | load (in %) of hierarchical rasterization when compared with scenebuffer             |          |

|      | rasterization                                                                        | 84       |

| 6.1  | Decreasing the section size towards the center of the screen                         | 93       |

| 6.2  | <u> </u>                                                                             | 93<br>93 |

| 0.2  | Decreasing the section size at regions with high level of detail                     | 90       |

| A.1  | The eye coordinate system                                                            | 99       |

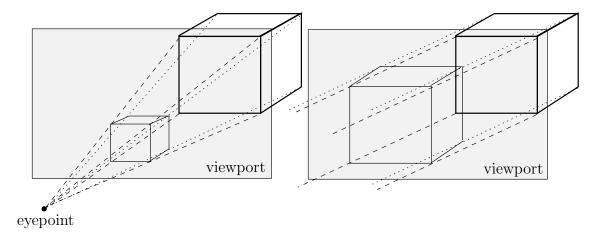

| A.2  | Perspective (left) versus parallel (right) projection                                | 00       |

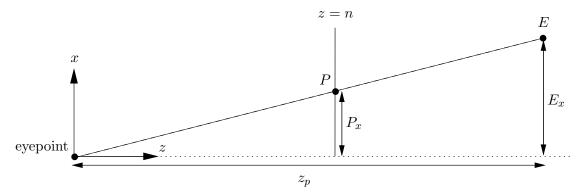

| A.3  | Calculating the projection $P$ of a point $E$                                        | 01       |

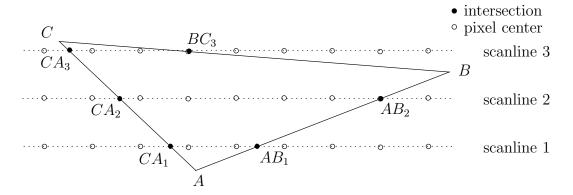

| A.4  | Determining the intersections of scanlines and triangle edges                        |          |

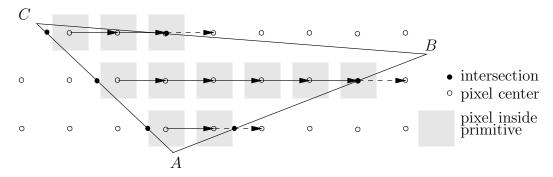

| A.5  | Traversal of a triangle primitive with scanline conversion                           | 03       |

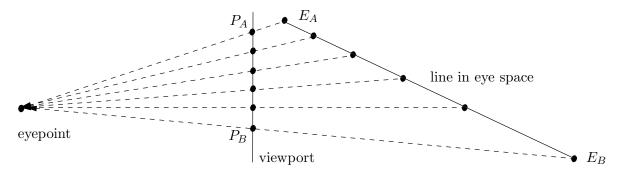

| A.6  | Equidistant interpolation steps in screen space map to non-equidistant               |          |

|      | interpolation steps in eye space                                                     | 05       |

| A.7  | Linear interpolation parameter mismatch                                              | 05       |

| A.8  | Three computation stages in a graphics pipeline                                      | 06       |

| A.9  | Defining the viewing volume                                                          | 07       |

| A.10 | Rasterization Pipeline in Computer Graphics                                          | 10       |

|      |                                                                                      |          |

## List of Tables

| 4.1  | Assumed parameter storage sizes                                                                                                                          | 52  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2  | Bounding box size for $640 \times 480$ applications for different screen divisions.                                                                      | 52  |

| 4.3  | Fragment value sizes in databack traffic in bytes                                                                                                        | 56  |

| 5.1  | Avarage external traffic in the datafront of a fullscreen rasterization scenario for the selected frames. (Equal to the datafront of a direct rasteriza- |     |

|      | tion scenario.)                                                                                                                                          | 62  |

| 5.2  | Reduction of databack traffic (in %) when compared to a fullscreen approach during rasterization of the ANL benchmark utilizing the proposed             | -   |

|      | tile selection policies                                                                                                                                  | 69  |

| 5.3  | Reduction of databack traffic (in %) when compared to a fullscreen approach during rasterization of the DINO benchmark utilizing the proposed            |     |

|      | tile selection policies                                                                                                                                  | 70  |

| 5.4  | Reduction of databack traffic (in %) when compared to a fullscreen approach during direct rasterization of the GRAZ benchmark utilizing the              |     |

|      | proposed tile selection policies                                                                                                                         | 71  |

| 5.5  | Reduction of databack traffic (in %) when compared to a full<br>screen ap-                                                                               |     |

|      | proach during direct rasterization of the AWADvs benchmark utilizing the                                                                                 |     |

|      | proposed tile selection policies                                                                                                                         | 71  |

| 5.6  | Reduction of databack traffic (in %) when compared to a fullscreen approach during direct rasterization of the TUX benchmark utilizing the               |     |

|      | proposed tile selection policies                                                                                                                         | 71  |

| 5.7  | Reduction of databack traffic (in %) when compared to a fullscreen approach during direct rasterization of the Q3H benchmark utilizing the               |     |

|      | proposed tile selection policies                                                                                                                         | 71  |

| 5.8  | Calculated hardware budget for memory elements in a direct rasterization                                                                                 | 70  |

| F 0  | scenario based on a triangle window of 32 with varying tile sizes                                                                                        | 72  |

| 5.9  | Maximum available triangle window for different section sizes assuming a 200k gates budget and a 400k gates budget                                       | 78  |

| 5.10 | Traffic (in MB/frame) for the scenebuffer and for two hierarchical raster-                                                                               | 10  |

| 0.10 | ization solutions.                                                                                                                                       | 79  |

| 5.11 | Total amount of triangle to tile overlap per frame for the q3h benchmark.                                                                                | 81  |

|      | Software workload in instructions for a set of rasterization scenarios. (*: acquired by running a hierarchical approach with only 1 section, effectively |     |

| 5.13 | running a direct rasterization scenario.)                                                                                                                | 83  |

|      | and the external traffic reduction in a hierarchical rasterization scenario                                                                              | 84  |

| Λ 1  | Triangle vertex parameters                                                                                                                               | 100 |

## Acknowledgements

Great thanks goes out to my advisor for giving me the room, time, and space to determine my own path in this research. Although this path generally did not took me from point A to B in a straight line it thought me a great many things about myself and life in general. I am sure the path will keep winding and provide me with new challenges along every step.

Further thanks is due to my family and friends for always being there for support and provide me with a life with excitement and joy. Eventhough, this more then once distracted me from completing the work currently under viewers eye.

No thesis, or any other accomplishment for that matter, however small it may be, can ever be achieved without the aid of the most precious and loving people in the world,

Special thanks to my parents.

M.C.A. van der Weide Delft, The Netherlands July 2, 2010

Introduction

The field of computer graphics is a continuously growing and commercially attractive market. In [12] the results of a study in worldwide revenue in the entertainment sector were presented. This economic study indicates that the video gaming industry is going to be the main driving force in the entertainment sector by 2009, replacing the role of non-interactive entertainment like films and music. The total worldwide revenue in the video game industry in 2009 was estimated to be approximately \$55 billion. More importantly, this study shows a considerable increase in the total revenue for wireless gaming on mobile terminals growing from \$281 million in 2004 to \$2.1 billion in 2009. This evaluated to a 49.3 % annual increase. By now these figures have been materialized by two major players that are involved in mobile devices; sony and nintendo, of which the former has sold 60 million as of march 2010 [35] devices (PSP) and the later has sold 128 million as of march 2010 [34] devices (Nintendo DS). These figures clearly show an increasing market for mobile gaming platforms.

This commercial interest in mobile gaming has triggered the introduction of a new field in research that provides for an intriguing design challenge for system engineers. In the traditional computer gaming industry the system solutions that enable computer graphics are usually realized with maximum performance in mind, resulting in the range of power consuming graphics cards available for personal computers today. This is in contrast to the field of mobile graphics, where power consumption and assembly cost are two important additional design criteria used to evaluate possible system solutions. One cannot simply suffice with a conventional approach to implementing computer graphics on a mobile device.

Driven by the economically-powerfull entertainment industry the research in mobile graphics proves to be attractive and implementing graphics acceleration on mobile devices is a field of particular interest. As a result a widespread industry standard for computer graphics, called OpenGL [32], has now a mobile counterpart in the form of OpenGL ES [24]. Moreover, ARM Ltd, a leading supplier of embedded Intellectual Property (IP) cores, has recently started offering a range of embedded solutions for computer graphics [9] alongside their embedded microprocessors.

To reduce power consumption on mobile devices one can often resort to System-on-Chip (SoC) design. In this design methodology several system components are combined onto a single chip to reduce the distance between components, resulting in increased performance and faster data communications. By combining several system functions on a single chip assembly costs are reduced and a final additional benefit for SoC design is reduced power consumption due to the external traffic elimination.

External traffic is a major source of power dissipation [21] mainly induced by the high capacitance of printed circuit board connections when compared to connections on

a chip. A large factor in this higher capacitance is the length of the connections. By implementing several system modules on a single chip communication between these modules is done via a small on-chip connection, usually a bus, instead of a longer off-chip connection. Examples of a on-chip bus is the AMBA system bus [28] especially created for use in conjunction with ARM processing cores.

A critical component for any graphics system is the framebuffer, a region of memory that contains the color information for every pixel on the display for a certain frame, which is the desired image to display. This memory is read pixel by pixel in order to display the resulting image on a raster device. The computer graphics process is responsible for generating the contents of the framebuffer before it can be displayed. Most computer graphics hardware (and software) is optimized for processing triangles, because it simplifies the computations and because every object can ultimately be created from triangles.

During the last stage of the graphics process, the rasterization stage, the abovementioned framebuffer is continuously filled with color values corresponding to triangles that are to be displayed on the screen. The rasterization is performed triangle by triangle, and for each triangle it results in color and depth values to be stored in the framebuffer. The depth value is used to determine which triangle is in front. Some computed colors will ultimately be replaced by the colors of another triangle and some colors can ultimately be blended with a new color in order to generate a final color value. The key notion to observe in this process is the fact that the framebuffer is also frequently accessed to retrieve previously computed color (and especially depth) values during rasterization.

Unfortunately, even for small displays as widely used in mobile devices, a large amount of data is required to be stored in the framebuffer. The physical hardware required to store this amount of data can easily exceed the hardware budget available for mobile graphics on a SoC. For example, a 640x480 size display already requires a framebuffer of over 1 Megabyte. In DRAM memory one storage cell costs the equivalent of approximately one gate [22]. A framebuffer of 1 Megabyte implemented in DRAM on-chip would therefore require around 8 million gates. This can easily exceed the typical hardware budget for mobile graphics.

A DRAM memory cell is created with a single transistor and a trenched or stacked capacitor, in order to create such a capacitor on chip extra fabrication steps are required during the processing of the wafer. This means the production process to make a chip which contains DRAM memory is more costly that a normal fabrication process where only transistors are created. However, a normal fabrication process only allows the construction of SRAM memory cells, which require 6 gates per cell [22], resulting in an even larger memory area if the framebuffer was implemented on the SoC. For mobile devices, the framebuffer is therefore considered to be too large to be implemented on the SoC and is assumed to be implemented on an external memory chip.

Thus, the problem with implementing a conventional computer graphics solution on mobile devices is characterized by the fact that the framebuffer is too large to be implemented on-chip and that the access rate to the framebuffer during rasterization is high. This results in large external traffic between the graphics hardware and the framebuffer during rasterization, which in turn results in high power consumption for the total system. This is undesirable for mobile devices because these are powered with a limited power supply in the form of batteries. The key to mobile graphics is therefore to reduce the amount of external traffic during rasterization in order to result in low power dissipation.

#### 1.1 Tile-Based Rasterization on mobile devices

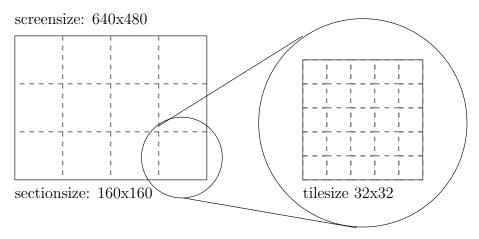

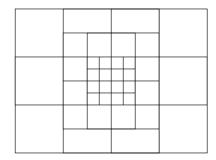

Instead of using a traditional rasterization solution, where triangles are processed for the entire screen at a time, tile-based rasterization, where triangles are processed only for a part of the screen at a time, has been considered for implementation on mobile devices [16]. In tile-based rasterization, originally used in high performance parallel rasterization, the screen is divided into small sections, called tiles. All the rasterization insructions that compose a scene, mainly triangle instructions, are duplicated for all the tiles they belong to, which allows all the tiles to be processed independently.

In high performance rasterization tiles are processed in parallel by multiple rasterizers and the total screen is processed faster when compared to a fullscreen rasterization scenario. A single rasterizer used in tile-based rasterization can suffice with a small local framebuffer and the large global framebuffer is constructed by combining the final color values of the smaller local framebuffers. Researchers in the same field have proposed similar approaches under the name of bucket- [13] or chunk- [10] rendering.

The same concept is used for mobile graphics to decompose the screen, however instead of using several rasterizers in parallel all the tiles are processed by the same hardware accelerator serially. The main advantage of tile-based rasterization for mobile graphics is that the local framebuffer required during the rasterization of a tile can be stored on the same chip as the microprocessor and graphics accelerator. This reduces the external communication during rasterization and results in a lower power consumption when compared to fullscreen rasterization.

The main disadvantage of tile-based rasterization is that it requires a sorting stage before rasterization in order to be effective. In this sorting stage triangles are examined in order to determine the tiles they are present in. Without this sorting stage the rasterization hardware wastes valuable time and resources by computing the overlap of triangles that might not even be present in the selected tile. A significant amount of hardware workload can be removed by prior sorting because triangles are usually only present in a small number of tiles.

Previous research [16] proposed a framework for developing tile-based rasterization hardware for mobile devices. Within this framework a novel design for an embedded tile-based rasterizer called GRAphics AcceLerator (GRAAL) was proposed. GRAAL is an OpenGL compliant rasterizer for use in a tile-based rasterization scenario. Within this work design tradeoffs have been researched [19] and intelligent hardware solutions were proposed [17][14][15]. A brief overview of the rasterizers implementation is given in this thesis. However, our work is not limited to this exact rasterizer, it can be extended in general to any tile-based rasterizer.

Parallel to the work performed to find intelligent hardware solutions for the implementation of GRAAL, research was done on the sorting performed prior to rasterization of the triangles on the GRAAL hardware [2]. This research assumed that the sorting is performed per frame, a single image to be displayed on the screen. During this sorting all triangles in a frame are stored in a region of external memory called the scenebuffer. The scenebuffer allows the tiles to be processed serially, where each tile is only processed once. As a result GRAAL can discard any intermediate parameter values required during rasterization of a tile, namely depth and stencil values. Only the final color values necessary for visualization on a screen are stored into the external framebuffer. This approach reduces the traffic from GRAAL to the external framebuffer during the rasterization of presorted triangles.

Several algorithms were proposed to create the scenebuffer [8]. These algorithms can be implemented in software running on the microprocessor or can alternatively be implemented in hardware if there is enough hardware budget available. The main disadvantage of all algorithms is the increase of traffic to the external memory in order to create the scenebuffer. The amount of traffic generated during sorting is dependent on the number of tiles and thus on the tile size. It was found that an optimal tile size with respect to the traffic to the external memory is  $32 \times 32$  pixels [7].

From here we will refer to this rasterization concept proposed in the previous work as scenebuffer (tile-based) rasterization.

#### 1.2 Research Objectives & Contributions

In the previous research [2] an assumption was made with respect to the available hard-ware budget for graphics acceleration inside the SoC. The budget was based on estimations by ARM that additional hardware available for mobile graphics was limited to 200k to 500k gates. Spending a larger hardware budget on graphics hardware can make the resulting chip too expensive and the entire mobile devices would be too expensive.

We note in this thesis that a tile-based rasterizer of 32×32 pixels consumes a large part of the available hardware budget for the tilebuffer memory array alone. This leaves no hardware budget for the scenebuffer sorting steps. This means that the scenebuffer sorting is to be performed by software running on the microprocessor. This increase of software workload reduces the generation rate of triangles by the software and can diminish the overall system performance and is thus an undesirable effect of the previously proposed tile-based rasterization solution.

In this thesis we focus on a new rasterization concept that is aimed to reduce the sorting workload on the software side of the system running on a general purpose processor. Note that this microprocessor is the core of the chip and it is not solely reserved for graphical computations and should therefore not be strained by graphics computations. Our objectives for this research were the following:

• Explore a new tile-based rasterization concept were sorting is performed in hardware prior to rasterization. In this rasterization concept the notion is dropped that a frame must be fully sorted before rasterization can start. By doing so it takes a middle path between traditional rasterization where the process is performed for a single primitive and scenebuffer rasterization where the rasterization is essentially performed per frame. Intuitively speaking, when compared to scenebuffer rasterization the software workload is reduced, however we introduce additional external traffic when compared to scenebuffer rasterization.

- Determine the feasibility of this new tile-based rasterization solution. We aim to determine the hardware modifications required to the existing tile-based architecture in order to create a simple sorting scheme in hardware to reduce the software workload on the microprocessor.

- Develop a framework for determining the amount of external traffic during the rasterization in this new tile-based rasterization concept. We use the amount of external traffic as an indication of the amount of consumed power since external traffic is the major source of power dissipation.

- Within this framework we investigate certain important parameters, such as the tile size and the chosen sorting algorithm, and determine their effect on the total amount of external traffic. With the identification of the most important parameters the rasterization concept can be optimized.

- Finally, and most importantly, we compare the external traffic figures of the different rasterization concepts acquired by simulating benchmarks from a mobile benchmark suite [6]. By comparing the traffic figures of traditional, scenebuffer, and our new rasterization concept we can determine the merit of our new rasterization concept.

In order to reduce the workload on the microprocessor we wish to move the sorting from software to hardware. This software was required in order to utilize a tile-based rasterizer. However, storing all triangles in a frame in hardware cannot be done without exceeding the hardware budget. Therefore we explore a tile-based rasterization concept were the sorting is not performed on all the triangles in a frame, but on a limited amount of triangles that are stored on chip.

Note that by sorting only a number of triangles of a frame instead of all the triangles in a frame we can no longer discard intermediate rasterization values, like color and depth values, from the rasterization hardware before the end of the frame is encountered. Therefore when a tile is processed, based on the triangles currently available in the hardware buffer, all temporary rasterization values need to be stored into the framebuffer in the external memory. At the time of the next processing visit to the same tile these values have to be retrieved from the framebuffer. This, off course, results in increased external traffic when compared to scenebuffer rasterization. Clearly this increased external traffic is problematic and as such should be minimized as much as possible. We address this problem critically in this thesis.

Our contributions to the field of mobile graphics are the following:

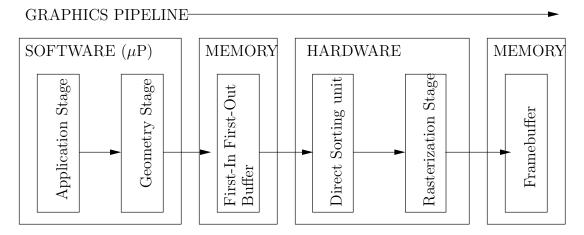

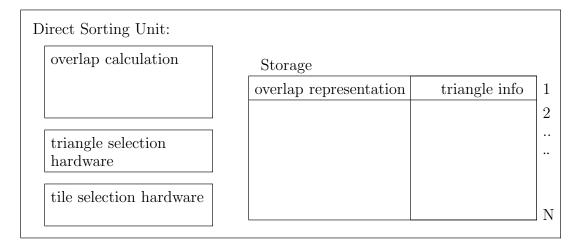

• We present direct (tile-based) rasterization scenario as a new approach for low power rasterization on mobile devices. Given that the sorting that was previously done in software is now performed in hardware a limited number of rasterization primitives need to be stored on chip. The so called direct-sorting unit, a hardware component functioning as a interface between the microprocessor and the graphical processor, is providing this service and it is mainly composed of memory to store the triangle data.

We present simple hardware modifications to the memory arrays inside a tile-based rasterizer that prevent unnecessary reads and writes to the external memory. Instead of retrieving the entire tiles color, depth, and stencil values we only retrieve the necessary values during rasterization. By preventing these external memory transactions the external traffic, and in direct relation the power dissipation, is increased less dramatically.

• We observe that scenebuffer and direct rasterization are not mutually exclusive in a system solution. Therefore we can combine direct sorting in hardware and scenebuffer sorting in software into a single rasterization solution for mobile graphics, where the sorting workload can be easily balanced between hardware and software. We refer to this approach as hierarchical (tile-based) rasterization and it is ideal for reducing the complexity for both sorting concepts. The scenebuffer sorting algorithm can sort the incoming triangles to a smaller amount of bins, reducing the sorting workload in software, while the direct-sorting algorithm sorts a lower amount of tiles, reducing the required hardware needed to maintain triangle to tile overlap data and increasing the number of triangles stored on chip.

Introducing hierarchical rasterization vastly increases the design space for a system engineer implementing mobile graphics. In embedded microprocessors were the microprocessor is heavily strained the system engineer can choose to restrict the scenebuffer sorting to 20 sections instead of 300 sections as in scenebuffer rasterization. The rest of the sorting required for tile-based rasterization is then performed in hardware in the direct-sorting unit, greatly reducing the strain on the microprocessor.

The biggest strength of hierarchical rasterization is the introduced possibility to balance the workload between hardware and software. If performance of a certain system is low moving workload from the microprocessor to hardware can be necessary to improve the performance on the microprocessor. If in this case the hardware budget is not increased the price is paid with increased external traffic resulting in a higher power consumption. If a higher power consumption is unwanted the hardware budget should be increased. Likewise, performance can be sacrificed to reduce power consumption. Another option might be to maintain a relatively high software workload and reduce the hardware budget for the tile-base rasterizer which results in smaller and therefore cheaper more competitive chips due to higher yields (we present an example of this case in our result section). The possibilities are numerous and provide a welcome addition to tile-based rasterization.

In order to compare different rasterization concepts from a external traffic point of view we created a high-level simulator that calculates traffic figures, in total byte accesses to the frame- and scenebuffer in external memory. The simulator can calculate the external traffic for a number of frames in a given testbench suite in a matter of minutes.

When compared to the simulator provided by previous work, a register-level SystemC simulator, this is much faster because the provided simulator would take several hours just to rasterize one frame. In addition the simulator is highly configurable; therefore one can easily perform a exhaustive search of different system topologies in order to find an optimal solution.

We utilized the created simulator to explore the effects of several design considerations. We ran simulations on fullscreen, scenebuffer, direct, and hierarchical rasterization implementations. Each rasterization implementation was run several times while varying important design options. These simulations give us results that indicate the best choices for some important design considerations. Some important results we found are the following:

- Results indicate that scenebuffer sorting algorithm based on sorting the scenebuffer to bins as proposed in [8] results in the lowest amount of external traffic and is less dependent on the number of tiles as the other sorting algorithms from previous work. This does not deviate from the results found from previous work. The overall tendency in scenebuffer rasterization is that reducing the number of tiles, achieved by increasing the size of the tilebuffer inside the tile-based rasterizer, results in less external traffic.

- In contrast, results obtained while simulating our proposed direct tile-based rasterization scenario suggest that the total traffic to the external framebuffer is reduced when decreasing the tile size. By choosing a smaller tile size the hardware buffer inside the tile-based rasterizer, containing intermediate pixels values for the current tile, can be reduced and the hardware budget is lowered. Unfortunately reducing the tile size increases the number of tiles in the screen and the memory array of the direct-sorting unit increases cancelling the budget gain from the tilebuffers. This clearly indicates that various tradeoffs are possible.

- We present and compare simulation results for four sorting heuristics with varying degrees of complexity, which can easily be implemented in hadware inside the direct-sorting unit. The goal of these heuristics is to choose an appropriate tile to process based on the triangles currently stored inside the direct-sorting unit. Results indicate that a selection policy aimed at selecting tiles that hold small triangles is the best heuristic for minimizing the amount of traffic between the tile-based rasterizer and the external framebuffer. Intuitively speaking this can be justified as follows: (i) Making sure the smallest triangles, with a low amount of overlap to different tiles, can be discarded from the sorting unit quickly creates room for new triangles. (ii) Introducing new triangles as fast as possible reduces the number of tile switches and consequently reduces the external traffic.

- On average the total external traffic in the direct rasterization scenario is larger then in the scenebuffer rasterization scenario. Averaged over the set of chosen benchmarks the direct rasterization reduces the total external traffic to 80 % when compared with a fullscreen rasterization system. While the experimental results of a scenebuffer rasterization scenario suggests reduction of the total external traffic

to 25 % when compared to a fullscreen rasterization. Nevertheless, the direct rasterization scenario can prove usefull for mobile graphics since it alleviates the workload on the software running on the microprocessor and works well for small tile sizes.

- The most promising results where obtained during the simulation of a hierarchical rasterization scenario. Our results suggest that hierarchical rasterization is able to reduce the external traffic when compared to scenebuffer rasterization, while reducing the software workload on the microprocessor related to sorting triangles to bins. Our results indicate that the external traffic is reduced to 90.8 % when compared to scenebuffer rasterization when sorting triangles to only 20 sections instead of 300 sections as in scenebuffer rasterization, additionally resulting in a 42.3 % software workload reduction. The external traffic in a hierarchical rasterization approach can even by reduced to approximately 78% when compared to scenebuffer rasterization when sorting to 60 or 80 sections.

- We also present external traffic figures that suggest that the external traffic in a hierarchical rasterization scenario can be less (93%) then the external traffic in a scenebuffer rasterization scenario even when less hardware (50%) when compared to scenebuffer rasterization is used to construct the direct-sorting unit and the tile-based rasterizer. Even in this case the amount of software workload is considerably reduced when compared to the workload in a scenebuffer rasterization scenario.

#### 1.3 Overview

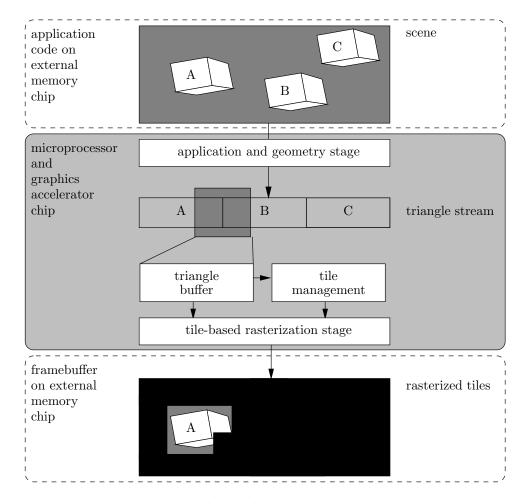

We start in Chapter 2 by presenting issues relevant for implementing computer graphics on mobile devices. We discuss the design criteria to be considered in mobile graphics and argue why a fullscreen rasterization scenario, as used in most comtemporary graphics devices, is not desirable for a mobile device. We provide some background on tile-based rasterization and present a small overview of the previous work.

Following, in Chapter 3 we start with an analysis of the previous work and then present the direct sorting scenario that moves the triangle sorting from the software side of the system to a unit implemented in hardware. We discuss the important aspects in direct rasterization, namely the tile selection policy, determining and representing the triangle to tile overlap, and the number of triangles stored in the hardware. We present hardware modifications to GRAAL that reduces external traffic. We conclude the chapter by presenting a hierarchical approach that uses both software sorting to a scenebuffer and direct hardware sorting, the resulting hierarchical system can be easily optimized for varying system requirements.

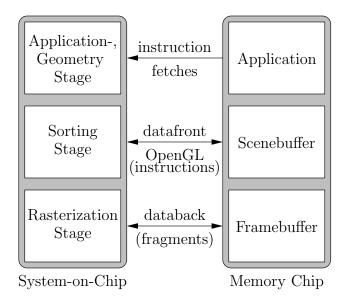

Next, Chapter 4 discusses the simulation platform in which we performed our experiments. We start by listing the benchmark elements used to evaluate various graphics pipeline configurations under realistic graphics workloads for mobile devices. Since our work is mainly targeted on the rasterization process we simply simulate the first stages of the graphic pipeline with a modified version of an existing graphics solution and work with an instruction stream as input for the rasterization stage. Our main focus lays on

1.3. OVERVIEW 9

the traffic to the external memory. The computation of this traffic is split in two parts, traffic related to sorting and traffic related to storing and retrieving fragment values.

Chapter 5 presents the results obtained from our experiments. We first ran experiments on a single rasterization scenario while varying certain design tradeoffs in order to find the best solution for a system implementation. Afterwards we compare the varying rasterization scenarios on a traffic point of view. We conclude this chapter with an attempt to system level comparison between a hierarchical rasterization scenario and a pure scenebuffer rasterization scenario with interesting results.

In Chapter 6 we provide a short summary of this report, present our main contributions to the field of mobile graphics, and provide some additional research topics for future work. Finally, Appendix A is added to provide a background on computer graphics and the graphics pipeline for readers unfamiliar with the concepts.

Mobile Graphics

he computations used in traditional computer graphics are no different for mobile devices. For the readers unfamiliar with the computations in computer graphics we included a background on this topic in Appendix A. The design constraints relevant for mobile devices, which are described in Section 2.1, necessitate however the search for new hardware acceleration solutions. The reasons why the conventional approach of hardware acceleration for the rasterization stage, here referred to as fullscreen rasterization, are not optimal for mobile devices is discussed in Section 2.2. A promising rasterization alternative for mobile devices is tile-based rasterization, detailed in Section 2.3. Previous work on tile-based rasterization scenario is presented in Section 2.5, the special rasterization hardware it requires is discussed in Section 2.4.

#### 2.1 Design Criteria

The field of mobile graphics is a special subset of traditional computer graphics with its own set of design considerations. The actual computations needed are equal to traditional computer graphics, but the system implementations are subject to different design constraints. In traditional computer graphics, systems were designed following a brute force approach with a high level of parallelism. The main design issues are induced by the high resolutions and the high performance required for an optimal user experience. As a result, contemporary graphics pipelines are optimized to accommodate high resolutions and high throughput and therefore exhibit massive energy consumption.

Mobile graphics, however, have to deal with issues related to the mobility of the resulting products as well as the user experience. This means the products are smaller, with lower resolution displays, are used closer to the eyes of the user and, most importantly, are powered by a limited power supply in the form of batteries.

The maximum resolution typical in contemporary mobile devices is around  $640 \times 480$  pixels and the size of the screen is around 3 by 3 inches. But this is expected to substancially increase for future mobile devices. Due to these small size displays mobile devices are used at a short distance to the user eye. Because the user is very close to the screen the area of projection for a single pixel onto the users eye is actually larger then for a personal computer [1]. This means that every pixel must be rendered at a high quality and implies no hardware can be saved by reducing the color depth, i.e., the amount of bits used to represent color values.

Mobile devices are implemented with a special mobile microprocessor. These processors are optimized for low-power and only support a simple instruction set. Furthermore, these microprocessors often operate at much lower frequencies than desktop computers. Therefore implementing the graphical computations on a mobile microprocessor alone, without hardware acceleration, is not feasible while still providing adequate performance.

To implement low power computer graphics a lot of research in the field of mobile graphics was started in industry and at different universities. One of the possible steps to reduce power consumption in the graphics system is to implement parts of the graphics pipeline in a System-on-Chip (SoC) design. In SoC design the different hardware units that make up a system are localized onto a single chip to increase performance and to reduce communication overhead.

For example, the microprocessor and the graphics accelerator could be implemented on the same chip in a SoC design. This reduces the distance between these components and thus removes the need for power- and time-consuming communication between the components, which would have been required when both components were on separate chips. Therefore the overall power consumption is reduced and the system performance can be increased.

#### 2.2 Problems with Conventional Rasterization

The straightforward approach to creating a computer graphics SoC is to move the hard-ware of a conventional graphics accelerator onto the same chip as the microprocessor. However, directly moving the rasterization process onto the microprocessor chip as it is usually implemented in conventional graphics systems does not result in a very effective system.

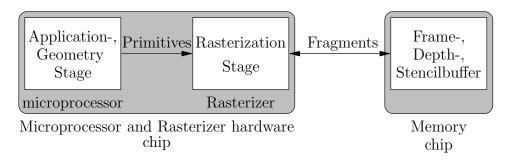

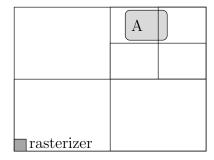

Because the conventional hardware rasterization scenario performs the rasterization of each and every single triangle for the entire screen at once, we call this rasterization approach a fullscreen rasterization scenario. If the conventional graphics pipeline, where every rasterization primitive (mostly triangles) are directly processed and its effects on the image are directly stored to the framebuffer, is ported to a SoC we obtain a system topology as depicted in Figure 2.1.

Figure 2.1: Conventional fullscreen rasterization organization.

The framebuffer, a memory region that holds the color information for every pixel in the screen is to large to be stored on chip and is therefore located on a separate memory chip. For simplicity we assume that the application stage and geometry stage (See Appendix A for details) are both performed in software running on an embedded microprocessor, since our main focus is the hardware acceleration of the computationally intensive rasterization stage.

During rasterization temporary pixel values, such as stencil, depth, and color values, are stored in memory for every pixel in the screen. The amount of data that needs to be stored during rasterization is significant. For example, a small  $640 \times 480$  pixel image with 32 bits for color values in RGBA format, 24 bit fixed point depth values, and 8 bits for stencil values already requires a storage capacity of approximately 20 Megabit in order to contain the intermediate parameter values for all the pixels on the screen. Even when assuming that a costly production process is used that allows the creation of embedded DRAM memory, requiring approximately 1.5 gates per stored bit [27][26], the implementation of this memory on-chip exceeds the hardware budget for mobile graphics easily.

During the rasterization stage we move from computations on rasterization primitives to computations on individual fragments. A fragment is a triangles infuence on a single pixel. A triangle that spans several pixels results in an equal amount of generated fragments. For the correct rasterization of these fragments we need a considerable amount of pixel values stored inside the frame-, depth-, and stencilbuffer located on the separate memory chip. Because a triangle can be visible in any part of the screen each pixel value can be accessed at any time. Unfortunately, these off-chip memory accesses are one of the most power consuming operations in a system [21]. The overall total power consumption of a fullscreen rendering approach implemented on a SoC is therefore still very high. This means that a fullscreen rasterization scenario is not an appropriate solution for the rasterization stage in mobile devices.

#### 2.3 Tile-Based Rasterization

The study in low-power solutions that enable computer graphics on mobile devices is a growing field. In this field tile-based rasterization was recently introduced as a promising solution for low-power embedded 3D graphics on mobile devices. Compared to the conventional rasterization solutions, tile-based rasterization is able to significantly reduce the fragment traffic between the rasterizer and the color, depth, and stencil framebuffers. We note in here that tile-based rasterization was originally developed for high-performance parallel rasterization and breaks down the rasterization of an entire screen into smaller sections, called tiles.

The basic working principle behind this rasterization approach is that there are no data dependencies between tiles during rasterization. A pixels color is essentially only dependent on its location and not on the data values of any of the surrounding pixels. Therefore the rasterization of each tile can be done individually and the final fullscreen result can be acquired by simply combining the rasterization result for all separate tiles into a single large image. Additionally, since there are no data dependencies between pixels the rasterization process is highly scalable and there are no limitations to the chosen tile size.

In high performance graphics tile-based rasterization is used to speed up the rasterization of high resolution applications by processing each tile on a separate rasterizer. For example, an application with a resolution of  $8000 \times 6000$  can be broken down and rasterized by 100 simple hardware accelerators with a resolution of  $800 \times 600$  pixels. The hardware in these individual rasterizers is less complex then a single  $8000 \times 6000$  ras-

terizer and each rasterizer individually requires less memory to store the frame-, depth-, and stencilbuffers. Smaller memory is often faster to access and consumes less power per access.

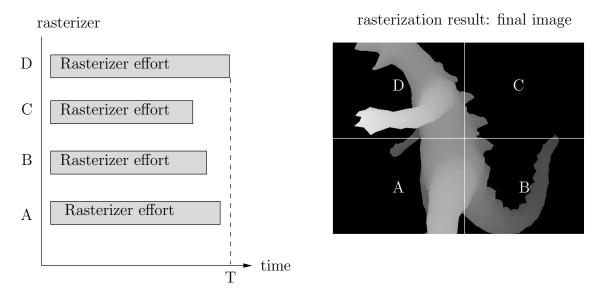

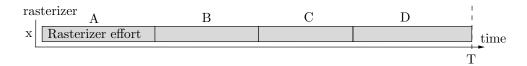

In high performance parallel rendering, consider the case were the rasterization of an image is done by four separate rasterizers A, B, C, and D. Figure 2.2 illustrates the effort in time for each of the separate rasterizers during the tile-based rasterization of the image on the right. The triangle density in the four parts of the screen is different and hence the required effort for each rasterizer is different. However, because the workload is distributed among four rasterizers the total time needed for rasterization is reduced when compared to the time required by a single rasterizer. After a certain period of time denoted by T, the time required for the rasterization of the densest part of the screen, all rasterizers are done processing and the final image is complete.

Figure 2.2: Effort versus time in Tile-based Rasterization with four Parallel Rasterizers.

In mobile devices tile-based rasterization can be used as a low-power solution for rasterization. The tile size is scaled down sufficiently in order to store the temporary stencil, depth, and color values needed to rasterize a tile on the same chip as the rasterization hardware. This means that all values required during the rasterization of a tile are stored locally and the performance of the rasterization hardware on chip is increased due to lower latencies while retrieving and storing fragment values. The rasterization of the entire screen is performed one tile at a time for each and every screen tile on the same rasterization hardware.

Figure 2.3 illustrates the rasterization effort in time for the tile-based rasterization of the same image as before, but now performed with only a single rasterizer. As expected because less hardware is used, the total time it takes to process the screen is longer. However, the main advantage of tile-based rasterization is that during rasterization the temporary fragment values are stored in a small on-chip memory instead of a large off-chip memory. The hardware rasterizer on the SoC features memory containing the

Figure 2.3: Effort versus time in Tile-based rasterization with a single Rasterizer.

stencil, depth, and color values of the pixels in the current tile. Each tile is processed once and during the rasterization no fragments values are required from the external depth-, stencil, or framebuffers. By rasterizing the tiles one by one the external memory accesses are reduced to the storing of final color values only. This reduces the power consumption related to fragment traffic significantly when compared to a fullscreen rasterization scenario.

Unfortunately, a single triangle instruction can influence any number of tiles, sometimes even the entire screen, and can therefore not be discarded until all the tiles influenced by it completely rasterized. This is the main disadvantage of tile-based rasterization for mobile devices. Due to the small available hardware budget tiles can only be processed one at a time. The instructions needed to correctly rasterize the screen have to be stored somewhere until the final image is completely rasterized.

The following sections present in more detail relevant tile-base rasterization aspects as follows: Section 2.4 provides background on previous work done in designing the hardware required for a tile-based rasterizer. Section 2.5 presents information on the previous work done on sorting the instructions of a frame.

#### 2.4 Tile-Based Rasterization Hardware: GRAAL

The tile-based rasterization scenario requires a special tile-based rasterizer. Previous work [16] presented a framework for designing graphics hardware for mobile devices based on the tile-based rasterization concept. In this work hardware was designed that can be used to construct a tile-based rasterization unit on a mobile SoC. The framework is called GRAphics AcceLerator (GRAAL) and for simplicity we refer to the hardware unit designed in that framework with the same name.

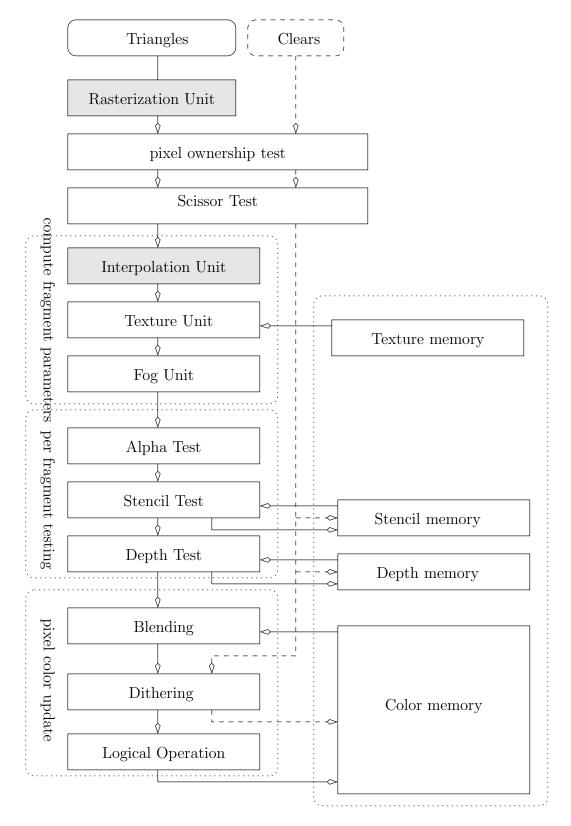

Like a contemporary graphics system, as presented in Section A.2, is constructed with several pipeline units, GRAAL is similarly constructed with hardware units forming a pipeline and is fully compliant to the OpenGL Graphics API [32]. However, since GRAAL only performs the rasterization of a small tile, instead of the entire screen, the intermediate parameter values are stored locally in special memory buffers. This means no external traffic related to fragment values required during the rasterization of a tile and the associated power consumption with that traffic is removed from the system.

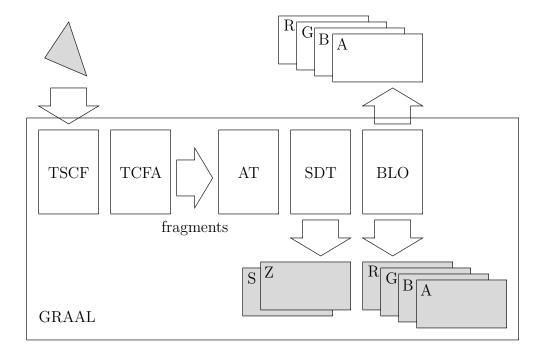

The pipeline structure within GRAAL is given in Figure 2.4. The first stage of the pipeline determines the overlap of the incoming triangles to the current tile. Pixels that are identified as inside a triangle are passed to the second stage where the fragment parameters are interpolated based on the pixel location and parameter values corresponding to the triangles vertices. After the second unit the fragments are subjected to a selec-

Figure 2.4: GRAAL pipeline with internal buffers for the stencil, depth, and color values.

tion of the OpenGL graphics tests that are important for mobile devices. Some of the OpenGL functionalities, like fog and dithering have not been implemented yet. Based on the outcome of the OpenGL tests updates are made to tile sized stencil,- depth-, and framebuffers located within the GRAAL hardware. The entire rasterization pipeline of GRAAL consists of five consecutive stages:

- Triangle Scan Convert to Fragments (TSCF) stage,

- Triangle Compute Fragments Attributes (TCFA) stage,

- Alpha Testing (AT) stage,

- Stencil and Depth Testing (SDT) stage,

- Blending and Logical Operation (BLO) stage.

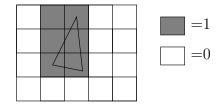

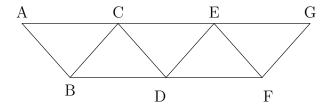

In the first (TSCF) pipeline stage the incoming triangles are converted into fragments via the linear edge Equations (2.9), (2.10), and (2.11). For an 8 × 8 pixel window the edge function results are systolically computed in three clockcycles [14]. The result, the indication that pixels are outside or inside the current triangle, is stored in a special logic-enhanced memory [17] the size of a tile. After this process the logic-enhanced memory contains a stencil pattern of the triangle for the current tile, ones indicating that the corresponding pixel is inside the triangle and zeroes indicating that the corresponding pixel is outside the current triangle. The logic-enhanced memory simplifies passing pixel locations inside the triangle to the next pipeline stage.

The following (TCFA) stage queries the logic-enhanced memory in the first stage for the fragments inside the current triangle. Subsequently, this stage determines the parameter values for the fragment by linearly interpolating the depth (z) and the color values (r, g, b, and a). When texture mapping is enabled the parameters needed for perspective correct texture mapping (s/w, t/w, and 1/w) are also interpolated as mentioned in Section A.1.5.

Interpolation for all the parameters is done via Equation (A.15), where  $p_{init}$ ,  $dp_i/dx$ , and  $dp_i/dy$  for every parameter are calculated only once for an initial fragment within the triangle. All following fragments are computed with an iterative calculation based on the initial fragment from the triangle. The divisions in this stage are performed by a clever reciprocation hardware implementation [19] that trades precision for speed without visually reducing the image quality.

When texture mapping is enabled this unit is also responsible for texture mapping. The texture parameters s/w and t/w are divided by the 1/w parameter in order to acquire the hyperbolically interpolated values. The perspective correct parameters s and t are used to determine which texels to fetch from the texture memory in external memory. The fragments are generated by the logic-enhanced memory in a predetermined pattern that increases the hit ratio in a texture-pull architecture with a texture cache [14][25]. Research in [3] indicates that a small texture cache of 256 bits is already sufficient to achieve hitrates in the range of 90%.

After all the attributes for a fragment are computed it is passed to the next three stages of the pipeline. The TCFA stage then returns to query the logic-enhanced memory in the TSCF stage for the following fragments inside the current triangle. If the logic-enhanced memory signals that there are no more fragments in the current triangle, indicated by all zeros in the memory, the TSCF stage is ready to start the rasterization of the next triangle.

After the first two pipeline stages all operations are performed on fragments only. This is indicated by the horizontal arrow in Figure 2.4. The next two stages of the pipeline, alpha test (AT) and stencil depth test (SDT), perform configurable OpenGL tests as defined by the running 3D application. GRAAL supports the alpha, stencil, and depth test as specified by OpenGL. The SDT stage has internal memory for storing the required stencil and depth values for the current tile. This memory is referred to as the Tile Stencil Depth Buffer (TSDB). The storage of depth values and stencil values in this unit are combined in order to obtain a single 32 bit stencildepth value for easier transfer over a 32 bit bus.

The blending and logical operation (BLO) stage performs the blending of incoming fragment colors with the colors in the framebuffer or the logical operations on these color values. The framebuffer is again a small memory able to contain the color values for the pixel in the current tile. This memory is referred to as the Tile Color Buffer (TCB). The TCB is constructed from four separate 8 bit memories, one byte for each color component in RGBA.

#### 2.5 Scenebuffer Tile-Based Rasterization

As mentioned in the previous section, the main disadvantage of tile-based rasterization on mobile devices is the need to store the instructions during the rasterization. A solution to this problem was presented and intensively studied in previous work [2].

#### 2.5.1 Basic Concept

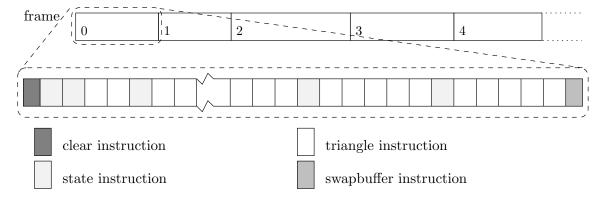

The basic concept behind scenebuffer tile-based rasterization is to simply store the incoming instructions, as generated by the geometry stage, in memory until all the instructions for a frame are generated. The end of a frame is indicated with a special instruction. In OpenGL this is the glSwapBuffers command. The rasterization hardware subsequently executes the stored instructions for every tile one after another. The memory were the instructions are stored until they are passed to the rasterizer is called the scenebuffer, therefore we refer to this rasterization approach as a scenebuffer tile-based rasterization scenario.

The instructions stored in the scenebuffer are mostly triangle instructions. Instructions that modify the rasterizer settings, called state instructions, are usually limited in number when compared to triangle instructions. Fortunately, most triangles in computer graphics are limited in area and therefore only visible in a limited number of tiles. Hence there is no need to process each triangle for every tile and a significant amount of workload on the rasterization hardware can be saved by sorting the triangles to tiles prior to rasterization.

Several sorting algorithms were proposed in previous work [8] and are discussed in further detail in Section 2.5.3. The sorting can be implemented before triangles are stored in the scenebuffer or after triangles are retrieved from the scenebuffer or a combination of both. We refer to sorting before or after the storing phase as pre-sorting and post-sorting, respectively.

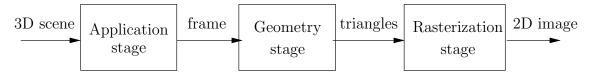

The graphics pipeline in such a system is essentially a two phase process. Strictly speaking it is no longer a pipeline because the geometry stage has to be finished before the rasterization can start. The first two stages of the graphics pipeline, the application and the geometry stage, require no significant modifications if we want to adopt a tile-based rasterization approach. However due to the limited gate budget for embedded computer graphics we most likely have to implement the geometry stage in software.

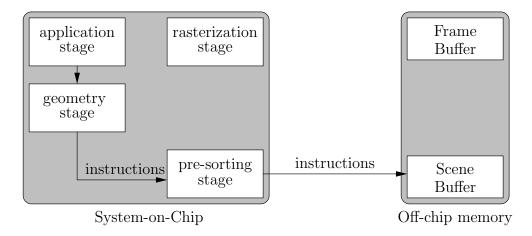

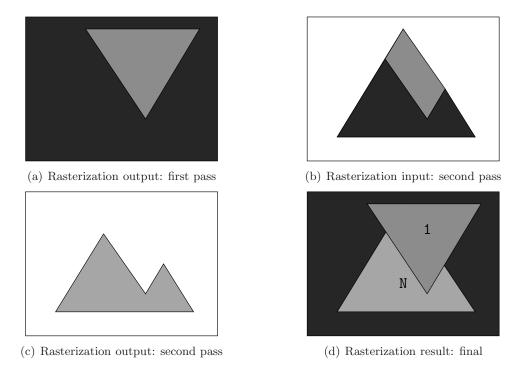

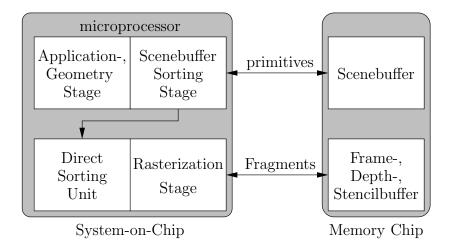

Figure 2.5 depicts the first phase in the 3D rendering system implemented in a scenebuffer rasterization scenario. The 3D application is executed on the microprocessor. OpenGL instructions are generated via the application and geometry stages running on the microprocessor. The resulting data can be seen as a stream of instructions (triangles, clears and state modifications) to be issued to the rasterizer hardware in order to create an image of the frame.

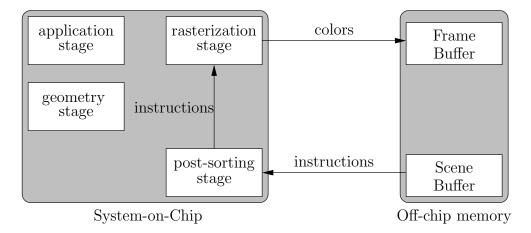

If pre-sorting is used the sorting stage maintains an individual scenebuffer for every tile, called a bin. If no pre-sorting is used all instructions are simply stored to a single scenebuffer. In the second phase, depicted in Figure 2.6, the instructions stored in the scenebuffer are retrieved for every tile. In post-sorting a quick check is made if the

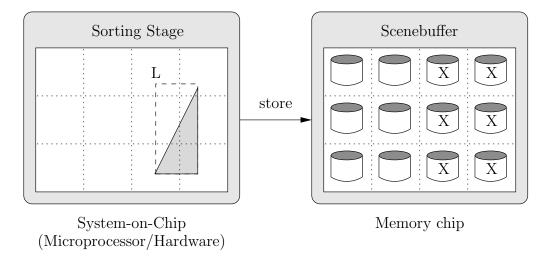

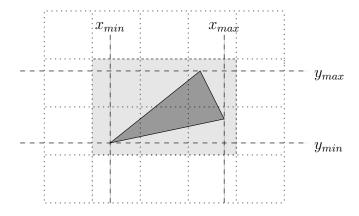

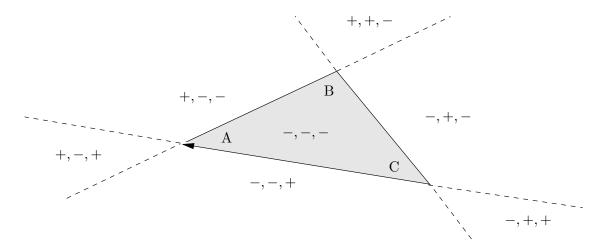

Figure 2.5: Phase one (application, geometry, and pre-sorting) in a scenebuffer rasterization scenario.

Figure 2.6: Phase two (post-sorting and rasterization) in a scenebuffer rasterization scenario.

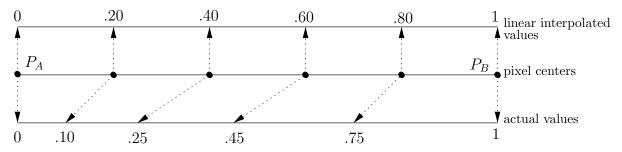

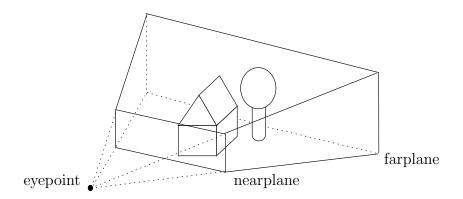

triangles are present in the current tile. If not it is discarded without being send to the rasterizer, resulting in no hardware workload.