# Cryogenic Digital CMOS Memories for Quantum Computing

R.A. Damsteegt

# Cryogenic Digital CMOS Memories for Quantum Computing

by

R.A. Damsteegt

to obtain the degree of Master of Science

at the Delft University of Technology,

to be defended publicly on Monday August 29, 2022 at 10:00 AM.

Student number: 4573625

Project duration: September 1, 2021 – August 29, 2022

Thesis committee: Dr. F. Sebastian, TU Delft, supervisor

Dr. ing. R. K. Bishnoi, TU Delft

Prof. dr. ir. G. Gaydadjiev, TU Delft

*This thesis is confidential and cannot be made public until August 29, 2027.*

An electronic version of this thesis is available at <http://repository.tudelft.nl/>.

# Abstract

Scalable universal quantum computers require classical control hardware, physically close to the quantum devices at cryogenic temperatures. Such classical controllers need digital memory for various applications, ranging from high-speed queues to high-speed and low-speed lookup tables and working memory. The power consumption of the memories should be within the available cooling power at these temperatures. To obtain the best memory design with the lowest power consumption, cryogenic-CMOS characteristics need to be taken into account during design. This thesis aims to develop a model that can be used to find the optimal memory cell design for each application, while taking area, latency, error rate, and power constraints into account. A model is developed to estimate the error rate and power consumption of a memory core for four cell designs, namely three embedded dynamic cell designs and one static cell design, over a range of applications in terms of memory operation frequency and read/write operation ratio. The model is constructed using room temperature and 233 K simulation data of individual cells and peripherals from a TSMC 40 nm technology. To estimate the error rate and power consumption at 4.2 K, the model is extended with empirical cryogenic-CMOS characteristics, such as an increase in threshold voltage and a steeper subthreshold slope, since good device models at this temperature are not available. To verify and improve the memory model, a test chip in TSMC 40 nm technology is designed, which includes eight fully-custom memories with two threshold-variations of each of the four cell designs to mitigate the cryogenic-CMOS threshold voltage increase. These memories are connected to an on-chip programmable microcontroller through a bus which enables flexible and high-speed testing without the need for high-speed I/O. This chip design is taped out and will be measured to verify and refine the model. At room temperature, the static cell design outperforms the dynamic cells in all memory applications with less than  $10^7$  operations per second. However, at cryogenic temperatures, the embedded dynamic cell designs become feasible for applications with more than 300 operations per second, due to the significantly reduced refresh rate. The best embedded dynamic cell design depends on the read/write memory operation ratio required by the application. After verification and improvement of the memory model based on the measurement results from the test chip, this model can be used to find the best cell design for a given application based on its operation frequency and read/write operation ratio. Apart from comparing the performance of a single memory design at room temperature and 4.2 K, this work also allows for direct comparison between the different memory cells designs, designed with the same technology, architecture, peripherals, and by the same design rules. Since only a single architecture is used with a single design for each of the peripherals, further optimisation is required for a cryogenic-optimised full memory design.

# Acknowledgements

I would like to start by thanking my supervisor Dr. Fabio Sebastian for this interesting project, which allowed me to combine my knowledge in both Electrical Engineering and Computer Engineering. I have thoroughly enjoyed the collaboration during the past year and learned a lot during the frequent meetings, both online and in person, mainly about the analog side of electronics.

Secondly, I would like to thank Ramon Overwater for being my daily supervisor. His help made the entire process a lot smoother by providing both technical support on practicalities and feedback and critical questions, either during or outside the meetings. Our shared interest in digital electronics resulted in helpful discussions on digital design and implementation.

I would also like to thank Rajendra Bishnoi and Georgi Gaydadjiev for joining my thesis committee.

I would like to thank the Coolgroup members for helpful and fun discussions whenever I went to Delft.

Finally, I would like to thank my parents, brother, sister, and friends for the support, a stable environment to work from home, and fun distractions whenever I was not working.

*R.A. Damsteegt

Nieuw-Lekkerland, August 2022*

# Contents

|          |                                                       |           |

|----------|-------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                   | <b>1</b>  |

| 1.1      | Motivation . . . . .                                  | 1         |

| 1.2      | Thesis objective . . . . .                            | 1         |

| 1.3      | Outline . . . . .                                     | 2         |

| <b>2</b> | <b>Background</b>                                     | <b>3</b>  |

| 2.1      | Digital CMOS memories . . . . .                       | 3         |

| 2.1.1    | Memory architecture . . . . .                         | 3         |

| 2.1.2    | Memory cell designs . . . . .                         | 4         |

| 2.2      | Quantum computing . . . . .                           | 10        |

| 2.2.1    | Classical controller architectures . . . . .          | 10        |

| 2.2.2    | Memory applications . . . . .                         | 10        |

| 2.3      | Cryogenic CMOS . . . . .                              | 11        |

| 2.3.1    | Effects on technology . . . . .                       | 11        |

| 2.3.2    | Cryogenic digital memories . . . . .                  | 12        |

| <b>3</b> | <b>Modelling</b>                                      | <b>15</b> |

| 3.1      | Applications . . . . .                                | 15        |

| 3.1.1    | Application space . . . . .                           | 16        |

| 3.2      | Memory metrics . . . . .                              | 16        |

| 3.2.1    | Area . . . . .                                        | 17        |

| 3.2.2    | Latency . . . . .                                     | 18        |

| 3.2.3    | BER . . . . .                                         | 20        |

| 3.2.4    | Power . . . . .                                       | 24        |

| 3.2.5    | Trade-offs . . . . .                                  | 28        |

| 3.3      | Memory cells . . . . .                                | 29        |

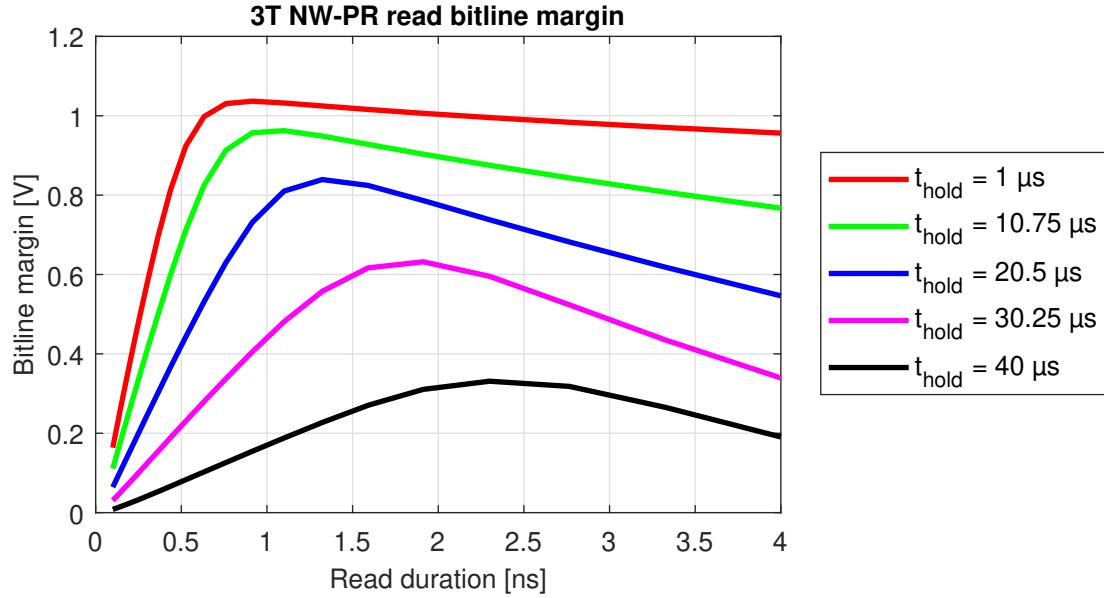

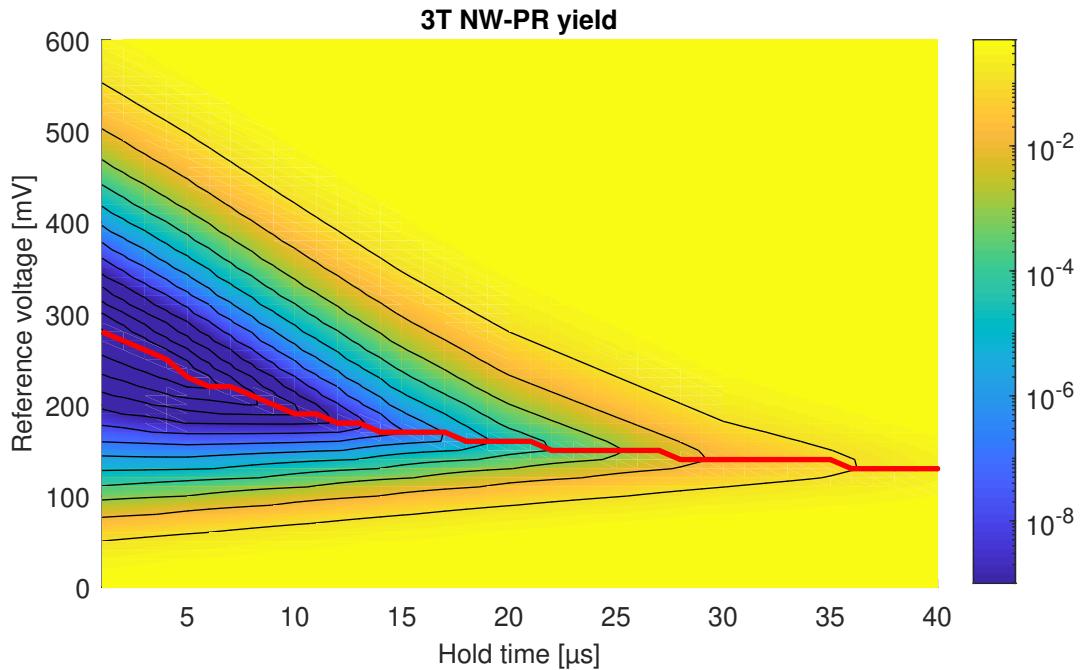

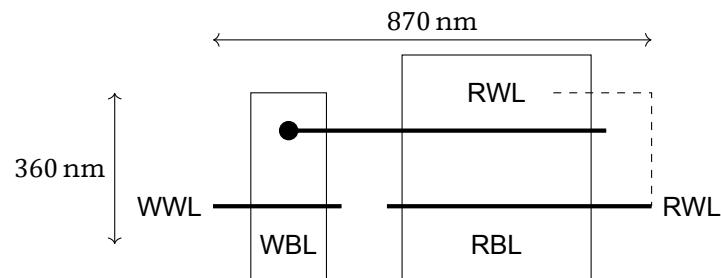

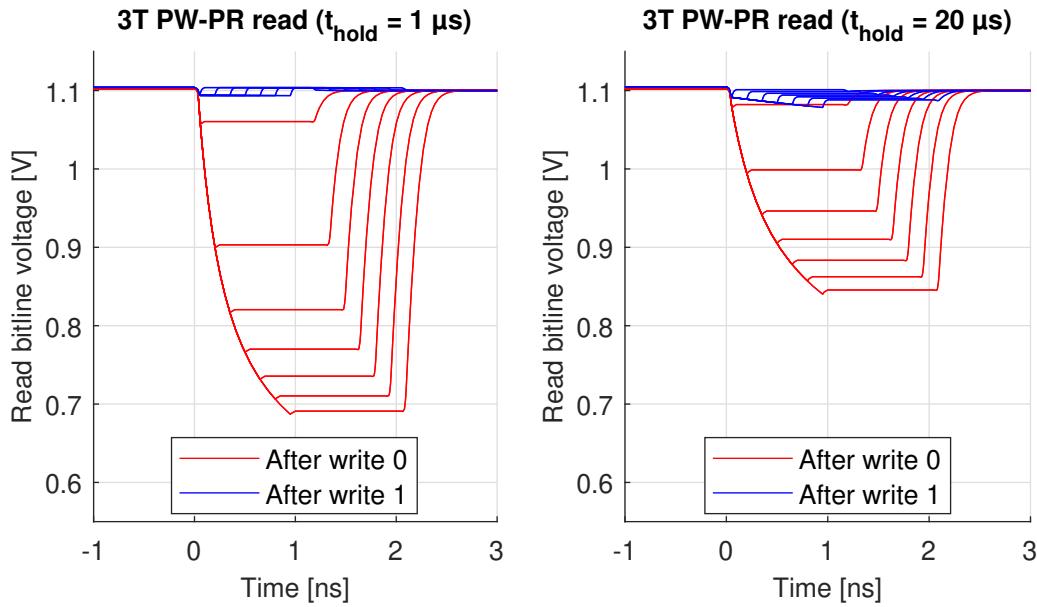

| 3.3.1    | Dynamic 3T NW-PR . . . . .                            | 29        |

| 3.3.2    | Dynamic 3T PW-PR . . . . .                            | 31        |

| 3.3.3    | Static 6T . . . . .                                   | 34        |

| 3.3.4    | Comparison . . . . .                                  | 36        |

| 3.4      | Moving to 4.2 K . . . . .                             | 37        |

| 3.4.1    | Cryo-CMOS . . . . .                                   | 37        |

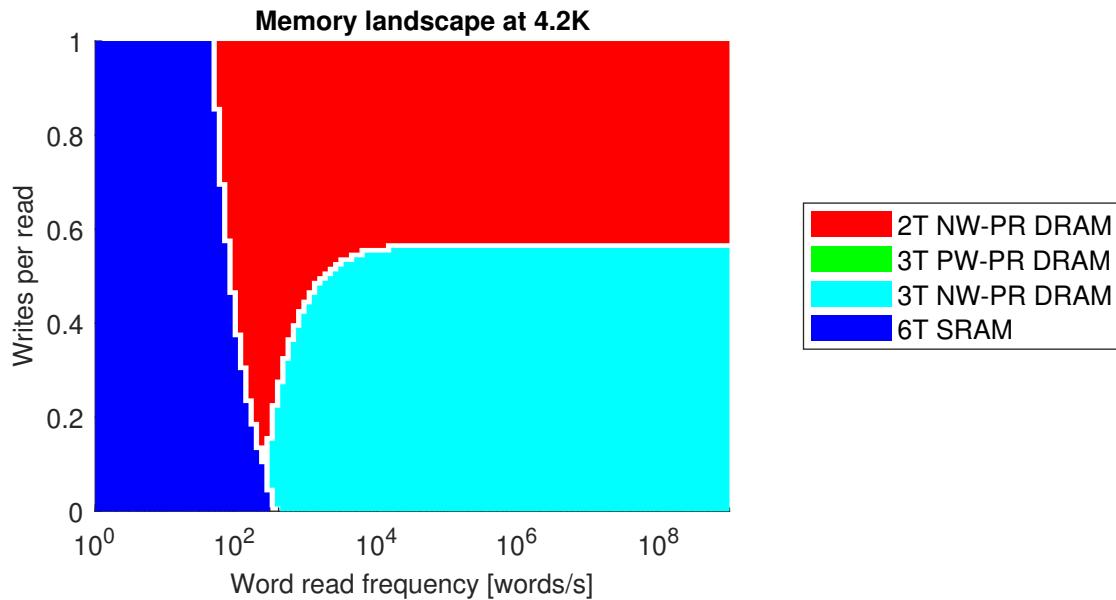

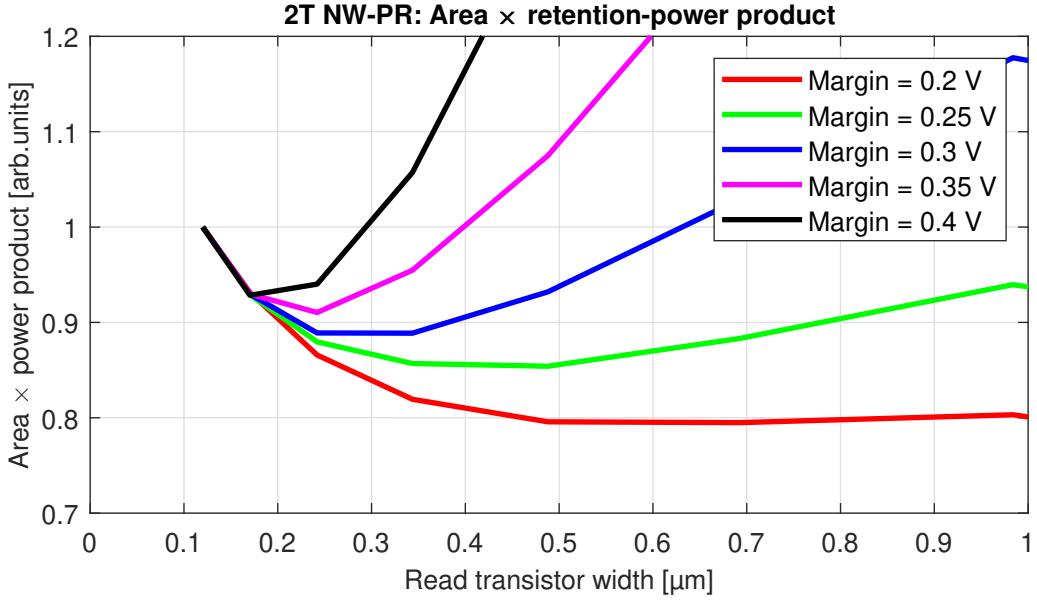

| 3.4.2    | Cryogenic results . . . . .                           | 39        |

| 3.5      | Model limitations and possible improvements . . . . . | 40        |

| 3.6      | Conclusion . . . . .                                  | 41        |

| <b>4</b> | <b>Memory design</b>                                  | <b>43</b> |

| 4.1      | Dynamic memories . . . . .                            | 43        |

| 4.1.1    | Cell arrays . . . . .                                 | 43        |

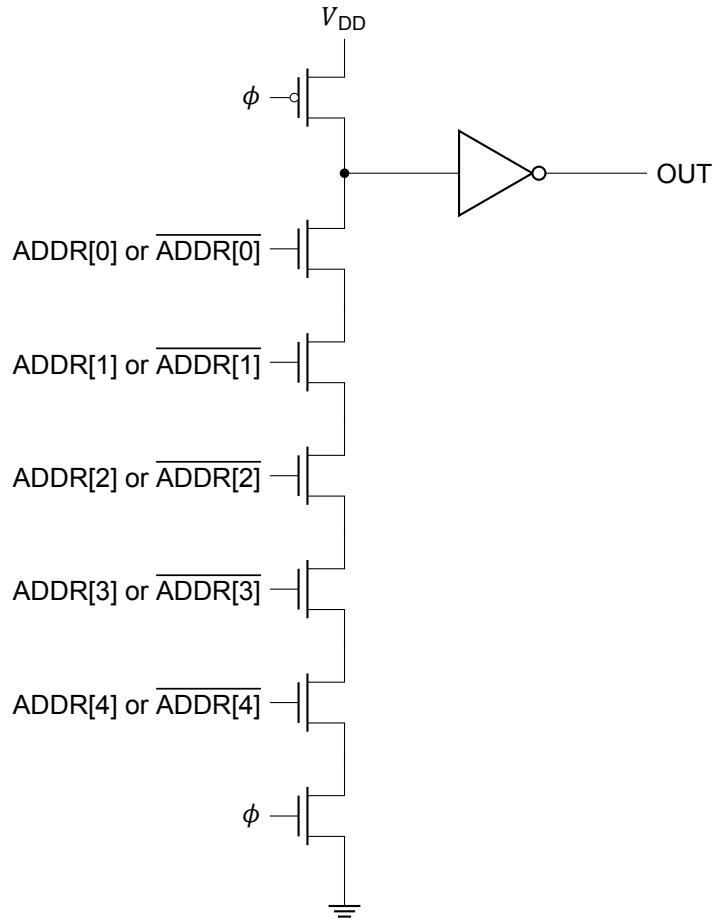

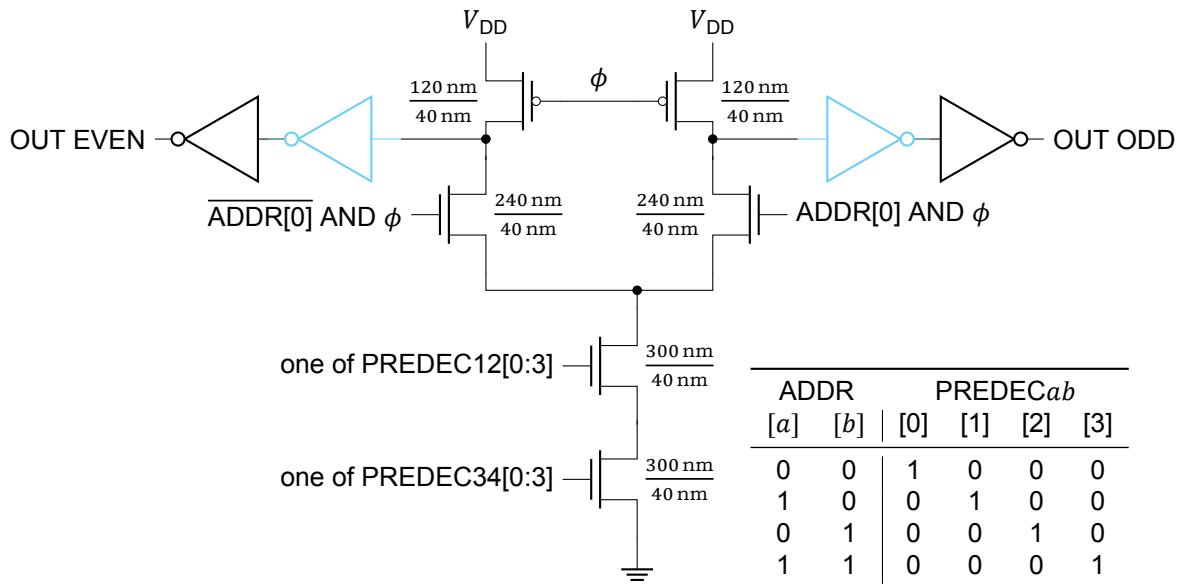

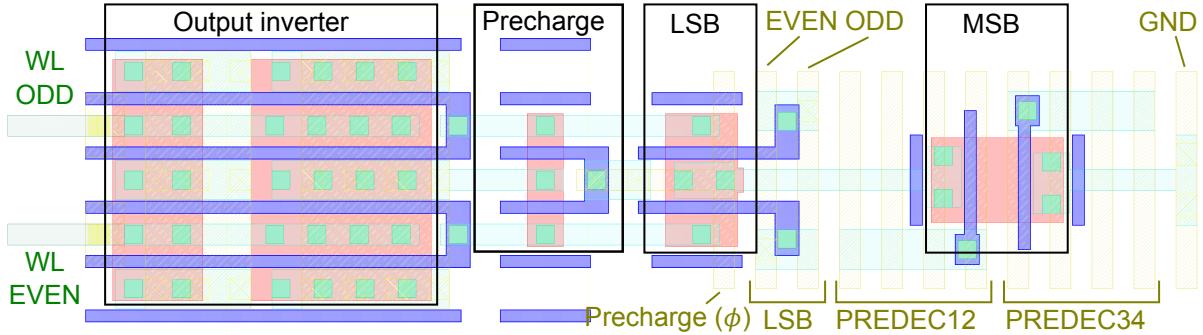

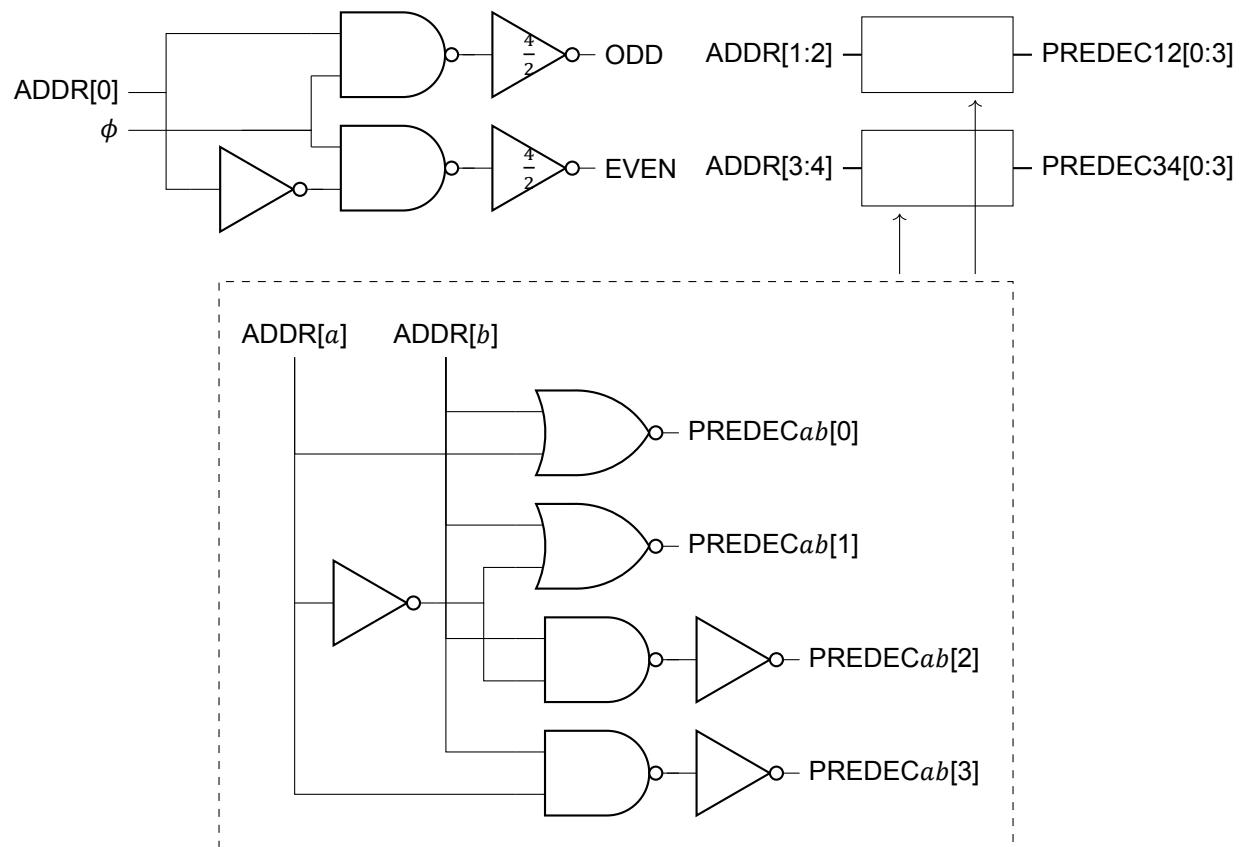

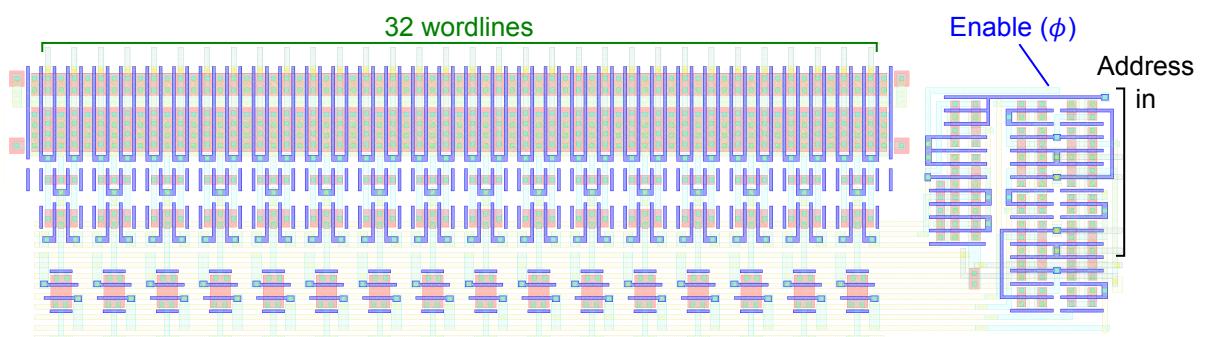

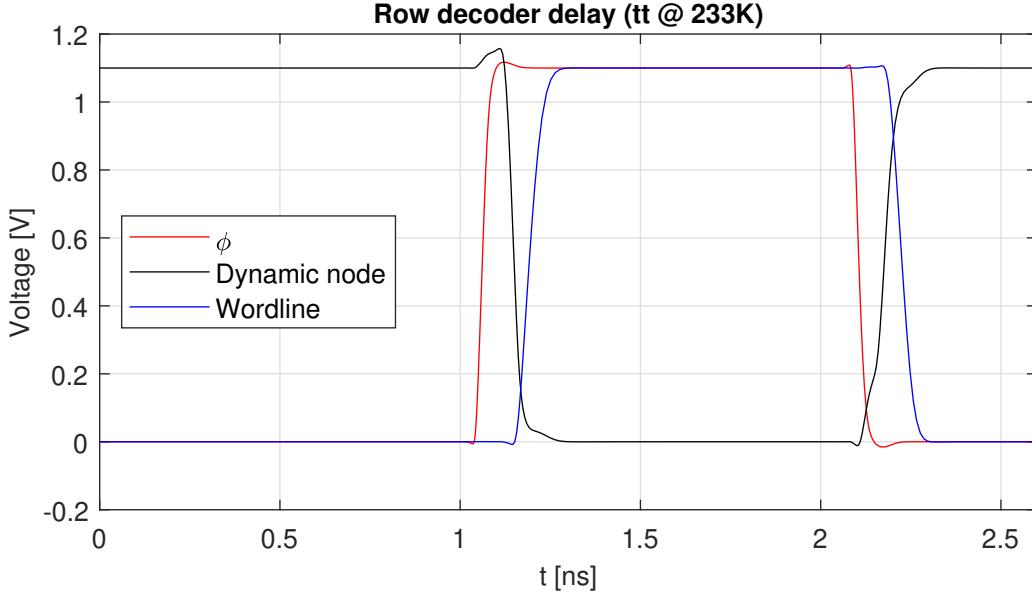

| 4.1.2    | Row decoder . . . . .                                 | 49        |

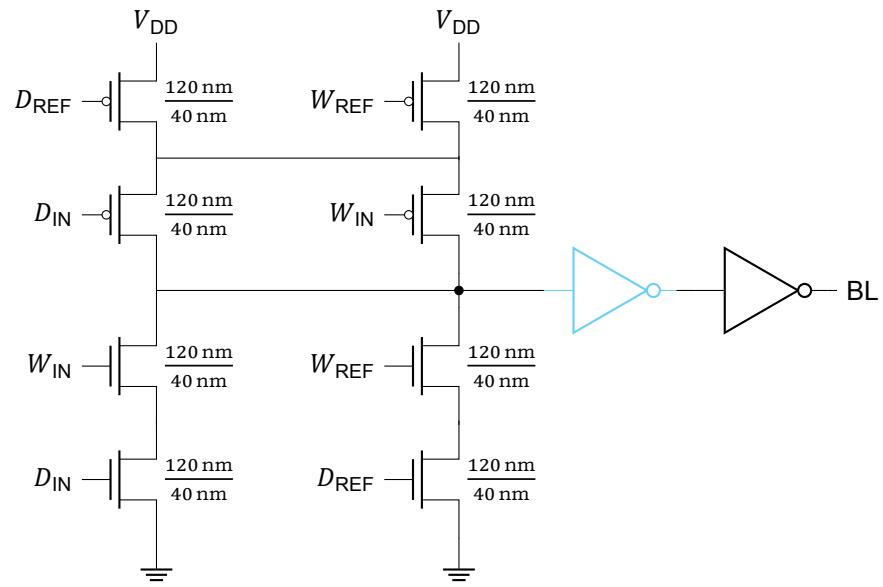

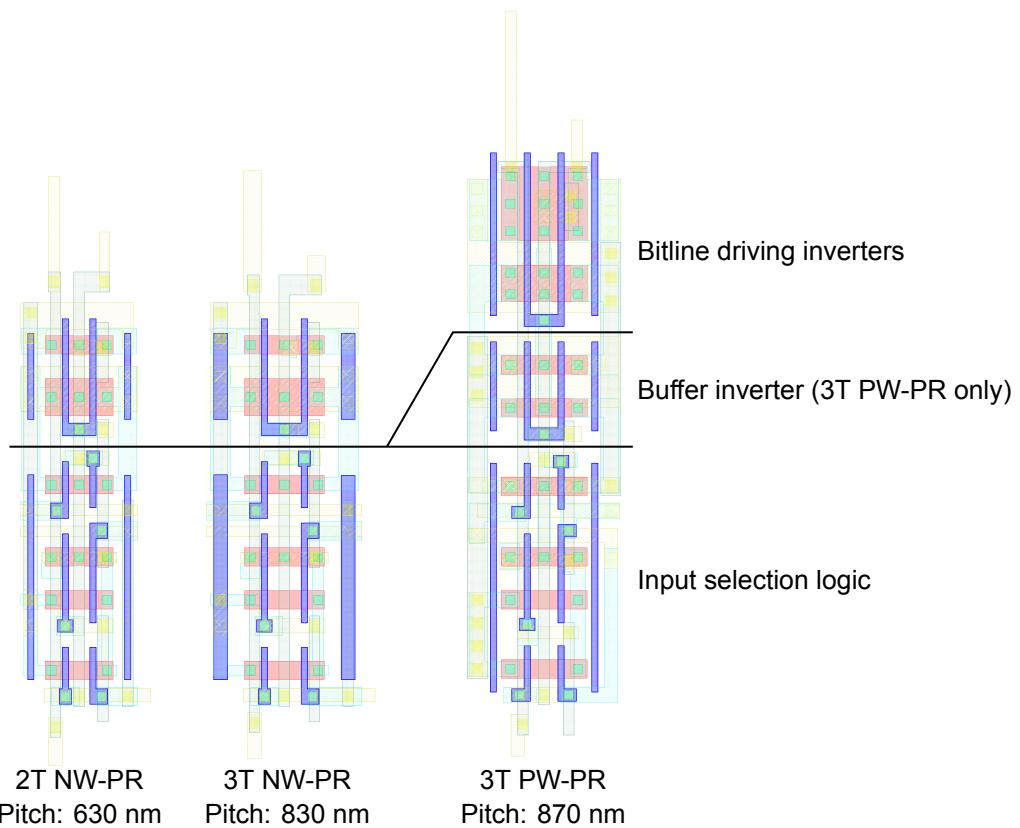

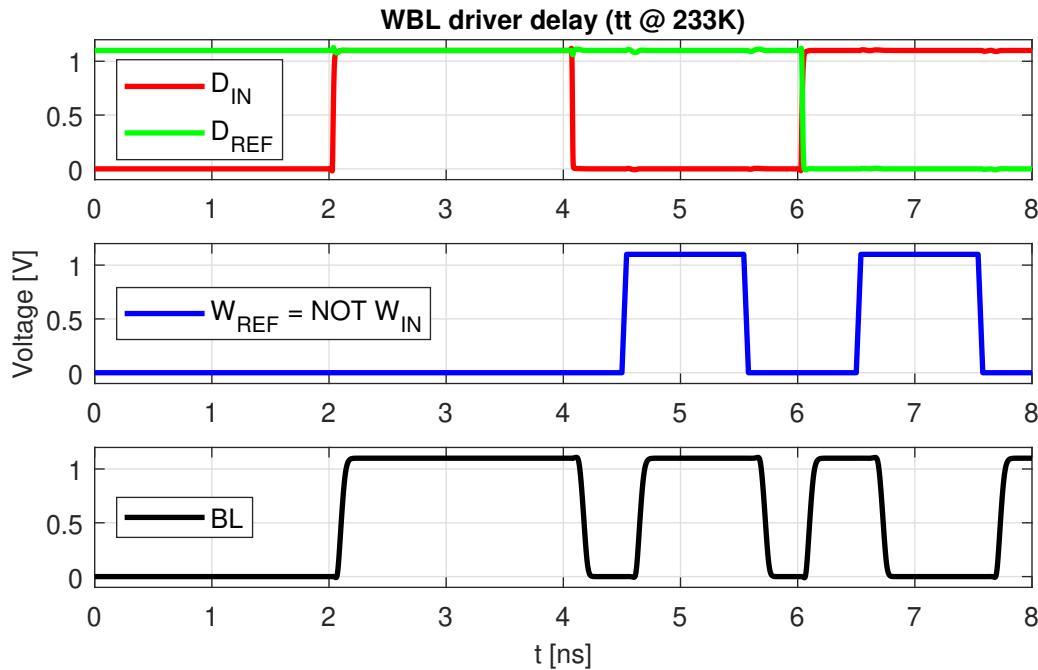

| 4.1.3    | Write bitline driver . . . . .                        | 53        |

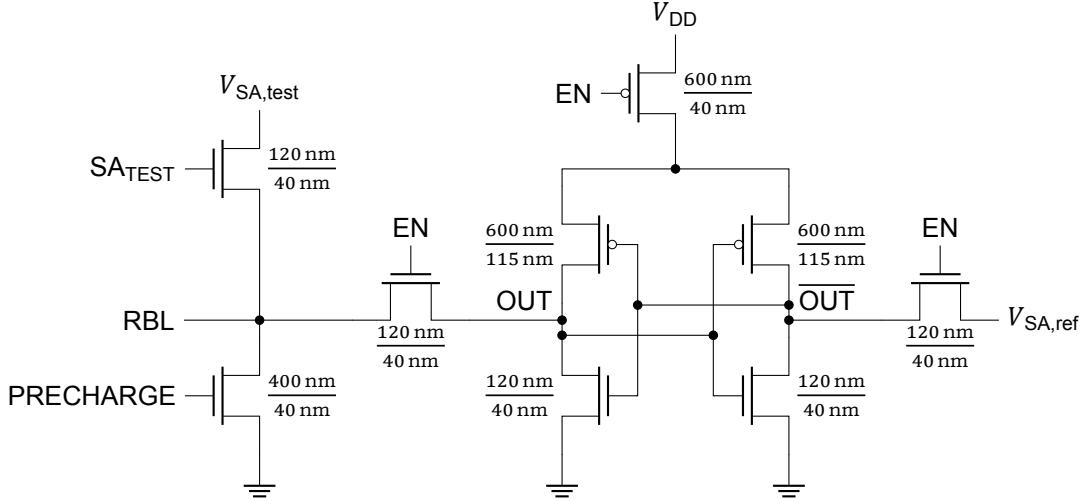

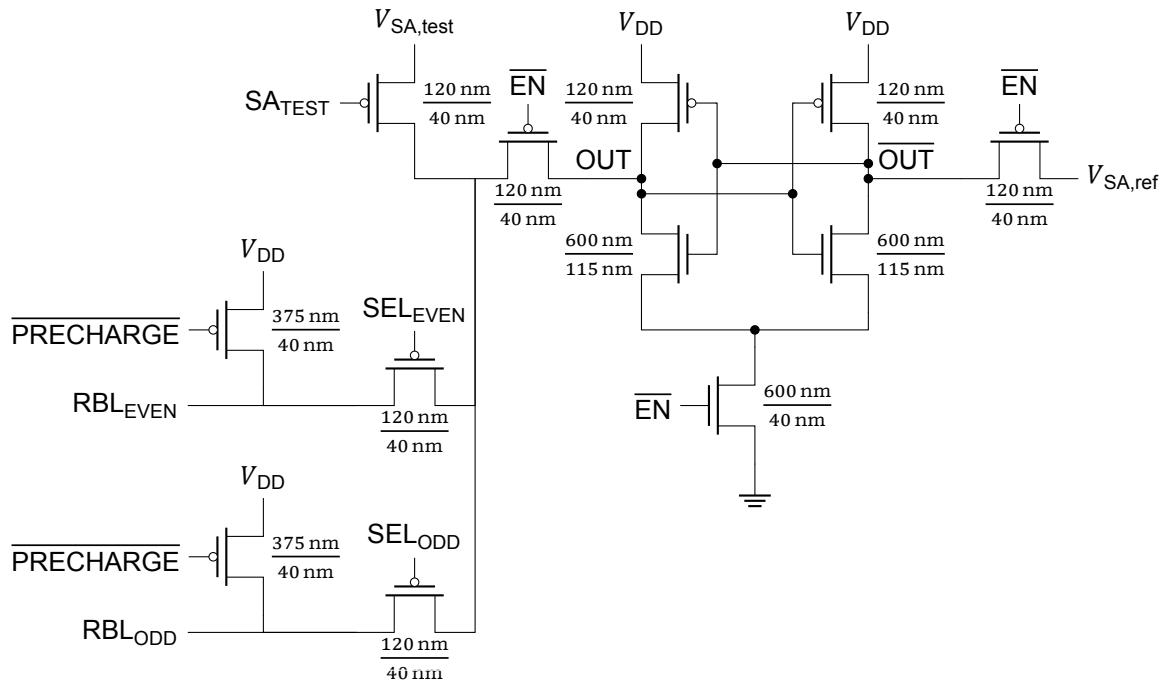

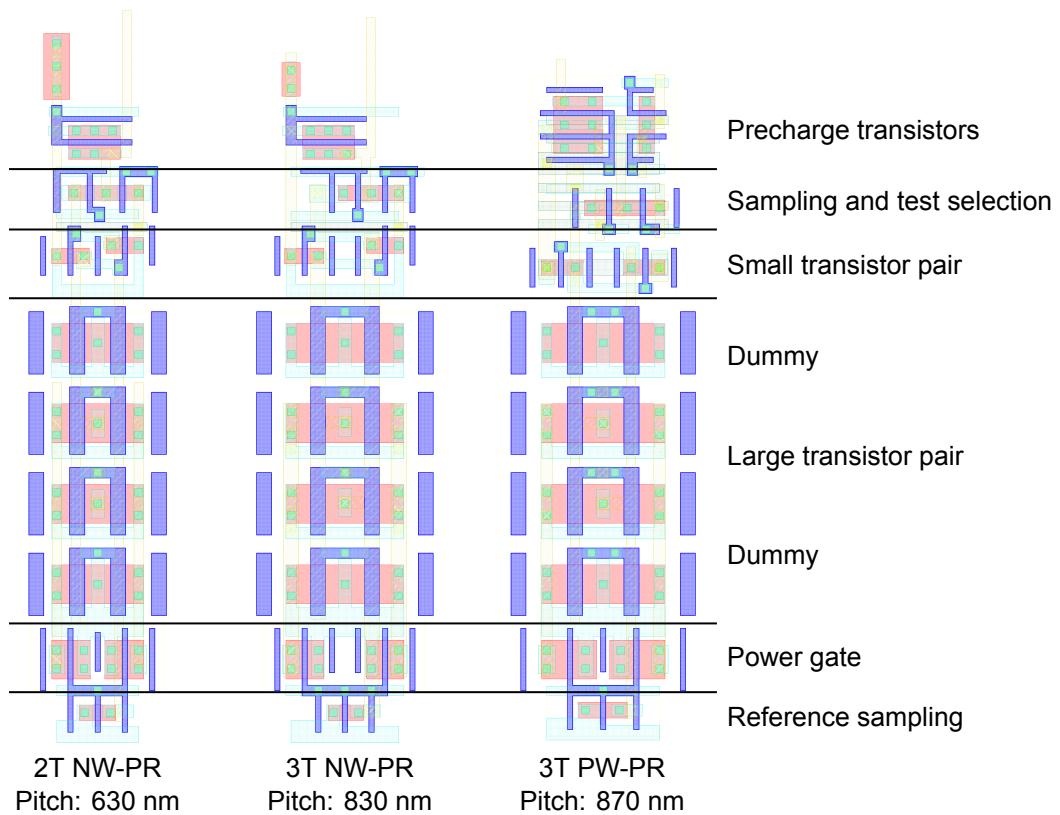

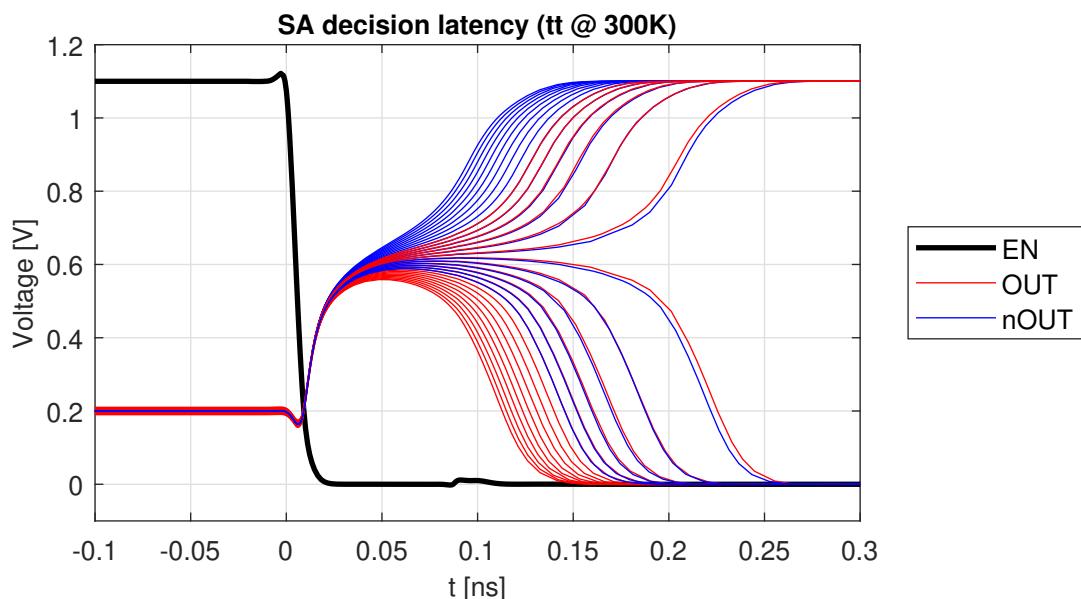

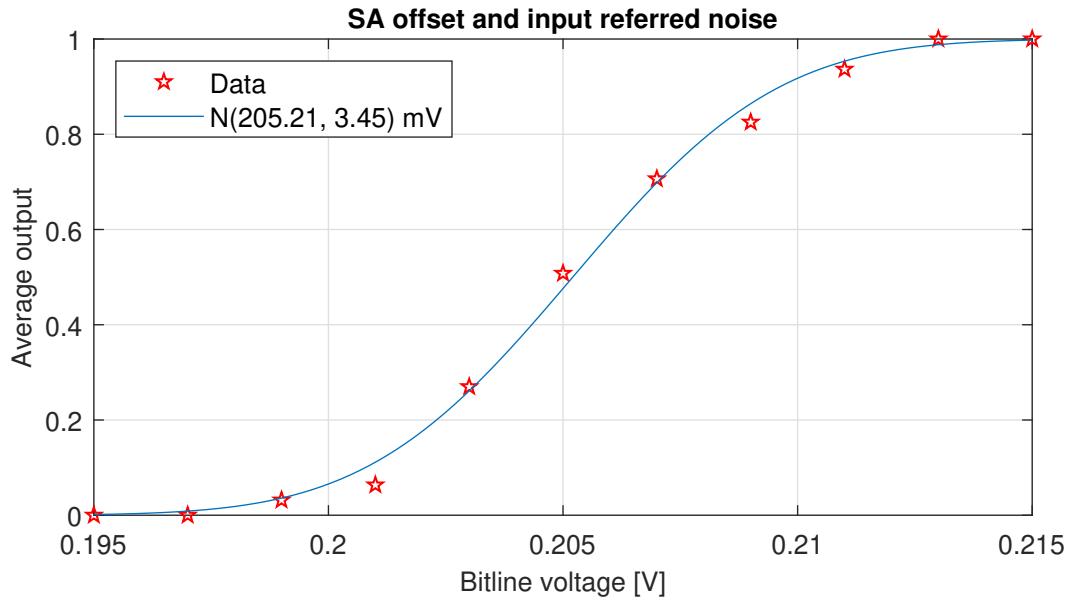

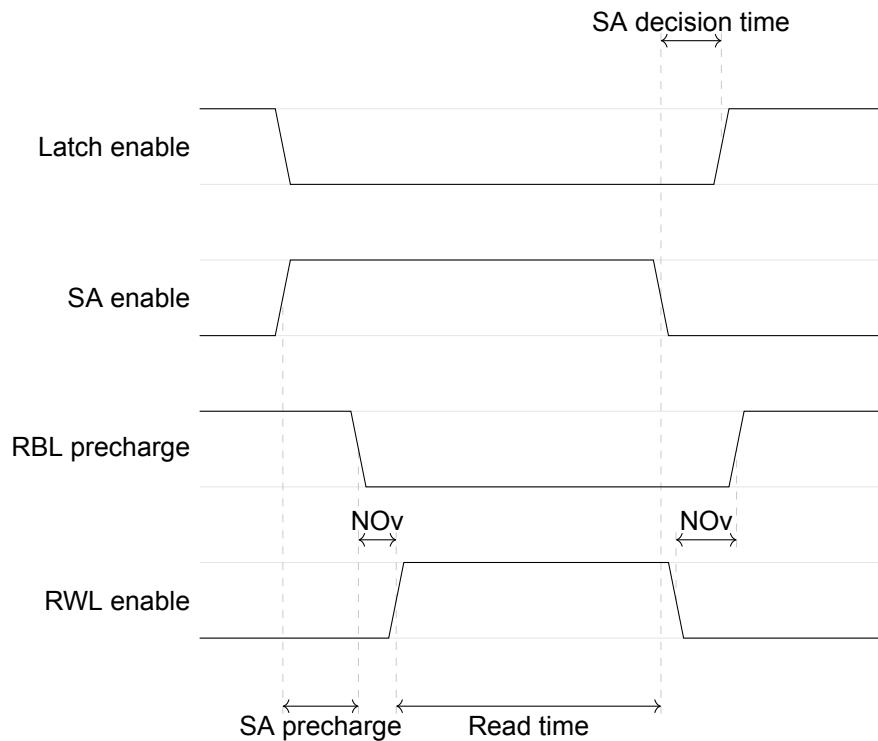

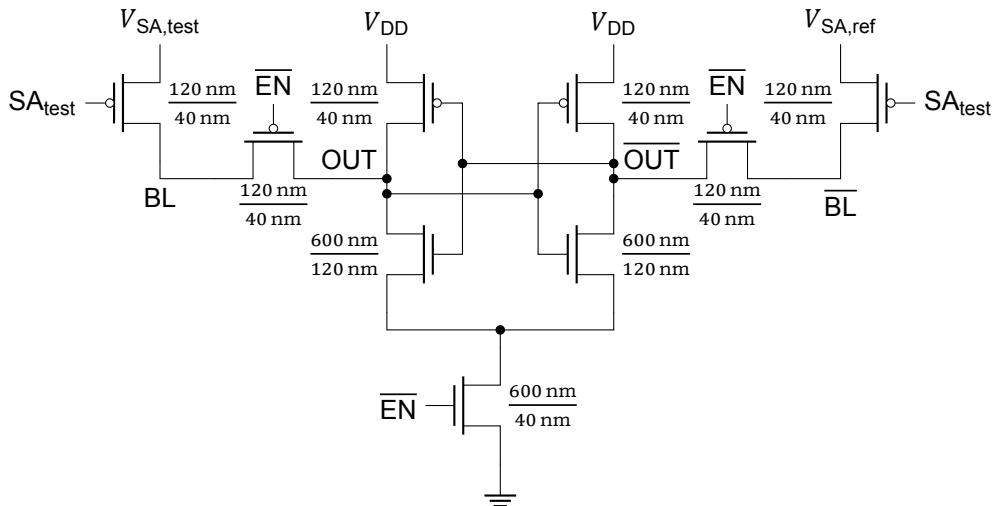

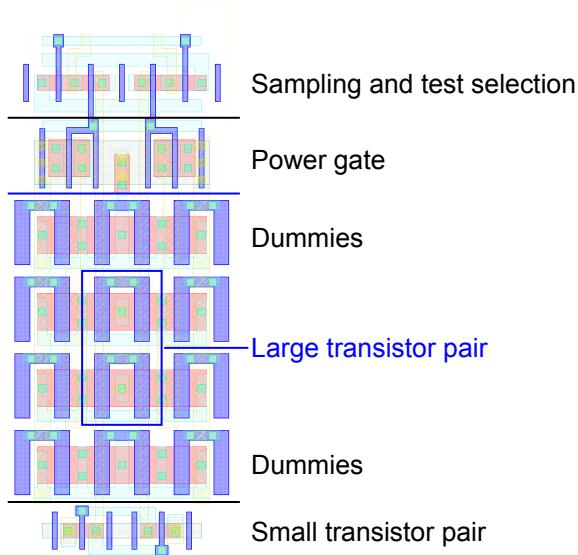

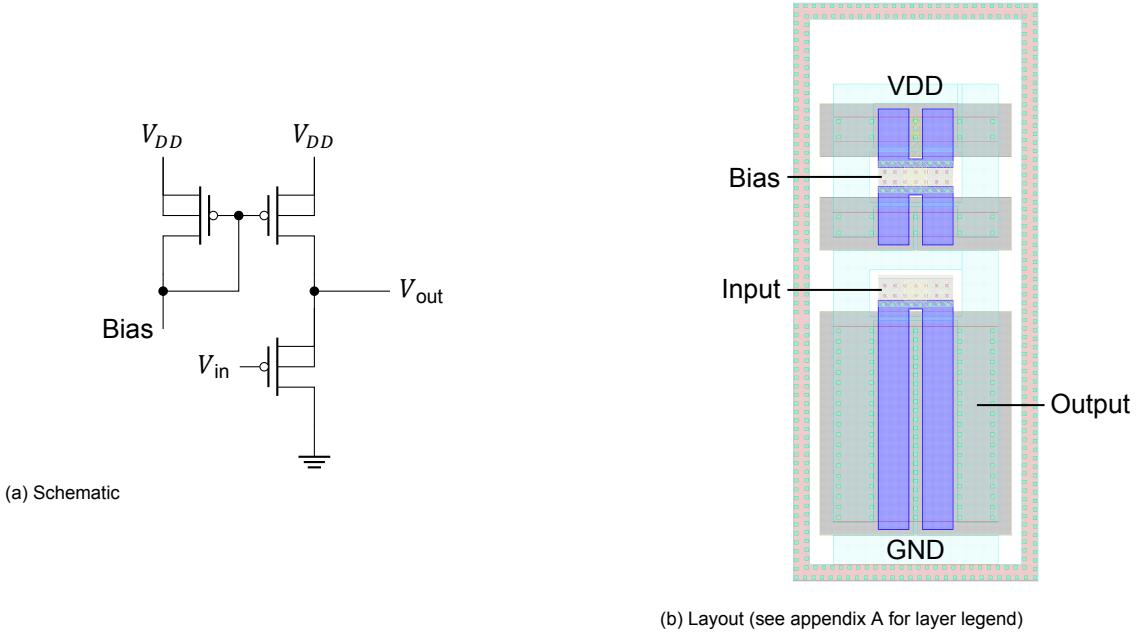

| 4.1.4    | Sense amplifier . . . . .                             | 55        |

| 4.1.5    | Latch . . . . .                                       | 57        |

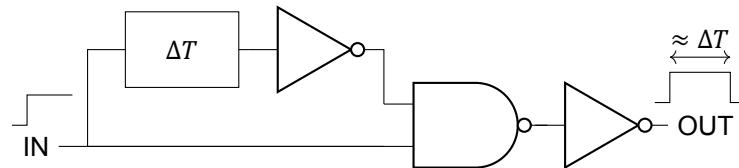

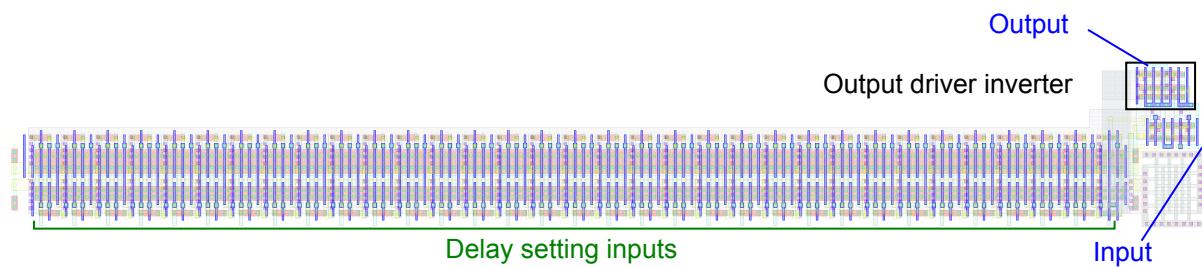

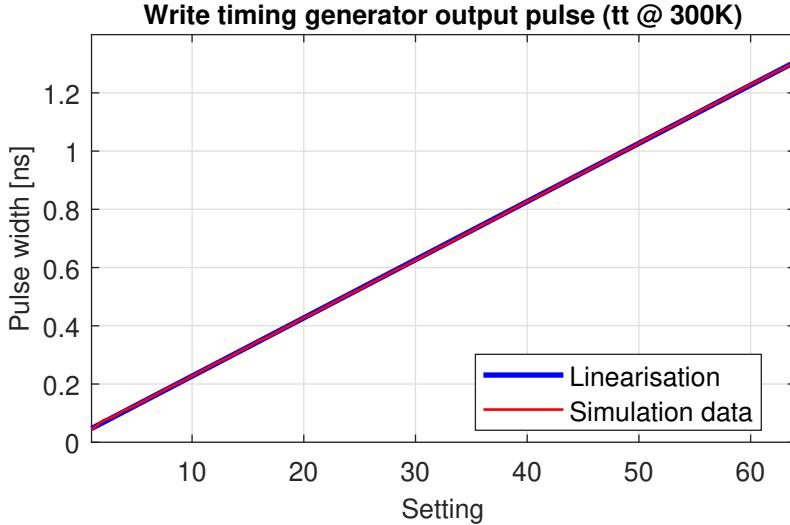

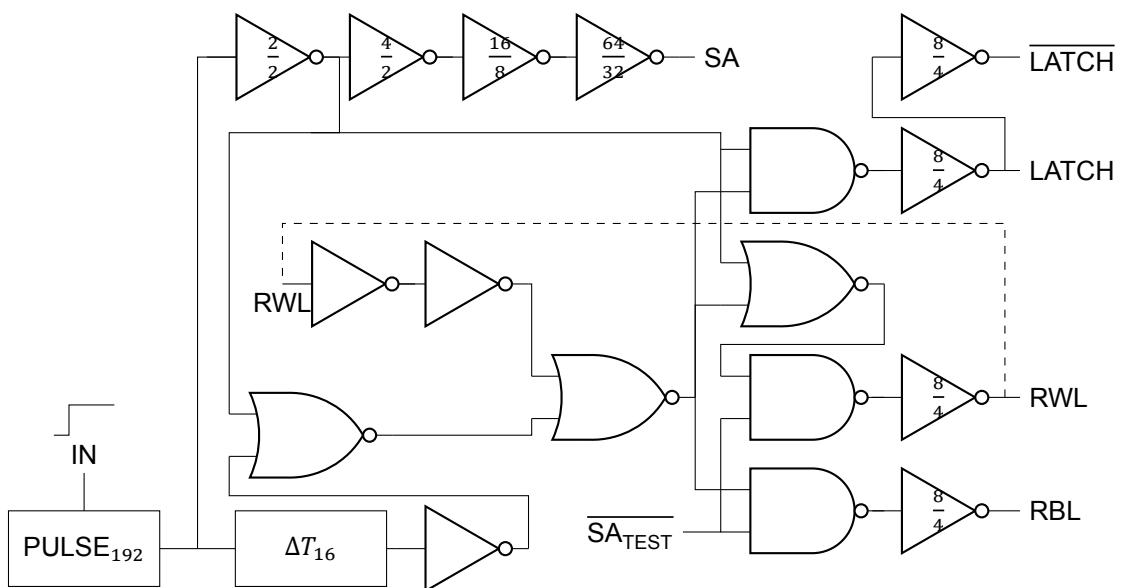

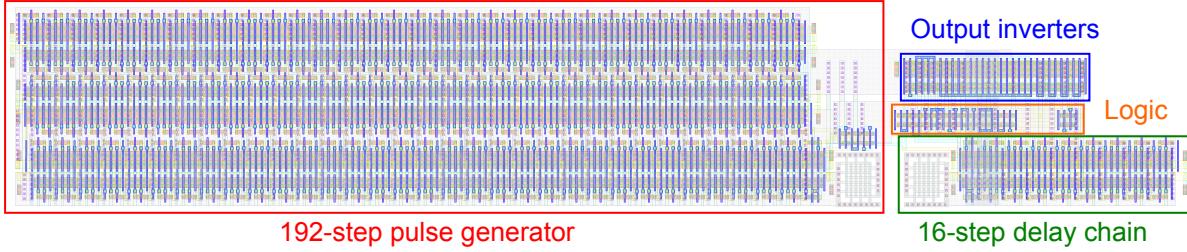

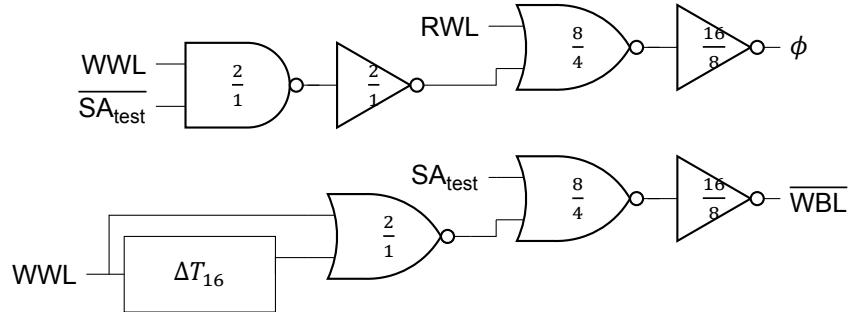

| 4.1.6    | Timing generation . . . . .                           | 59        |

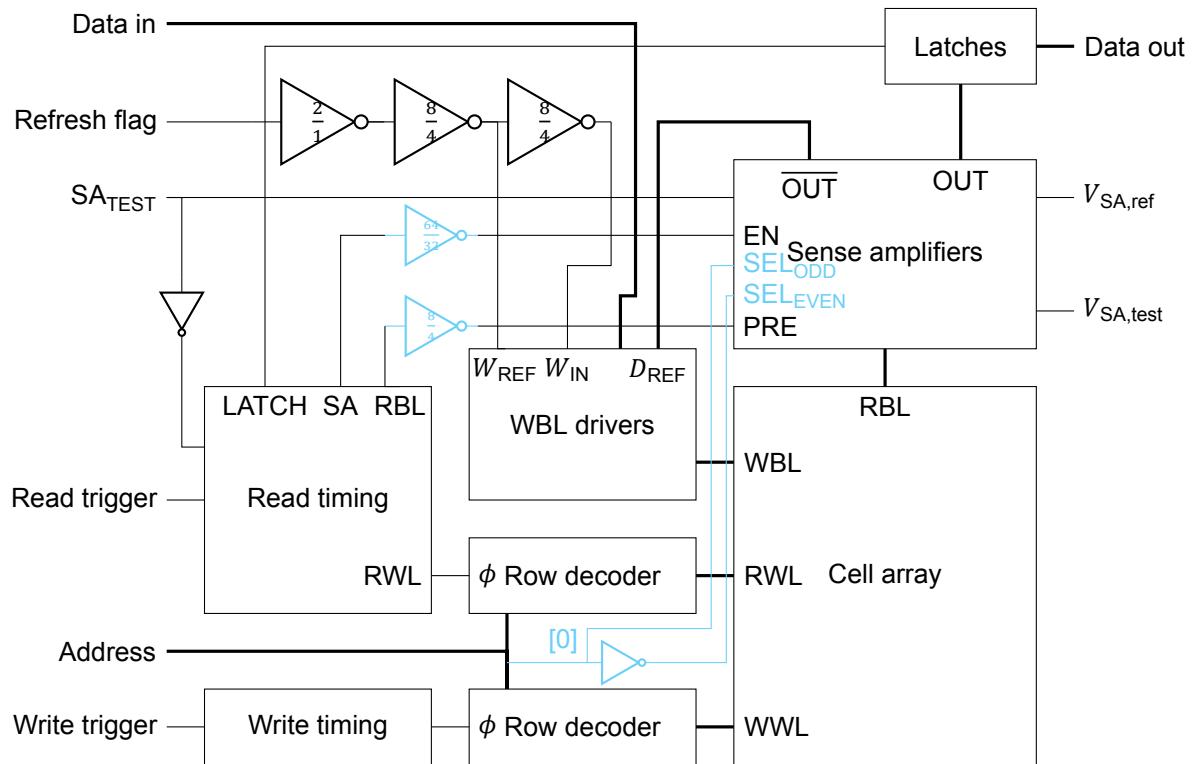

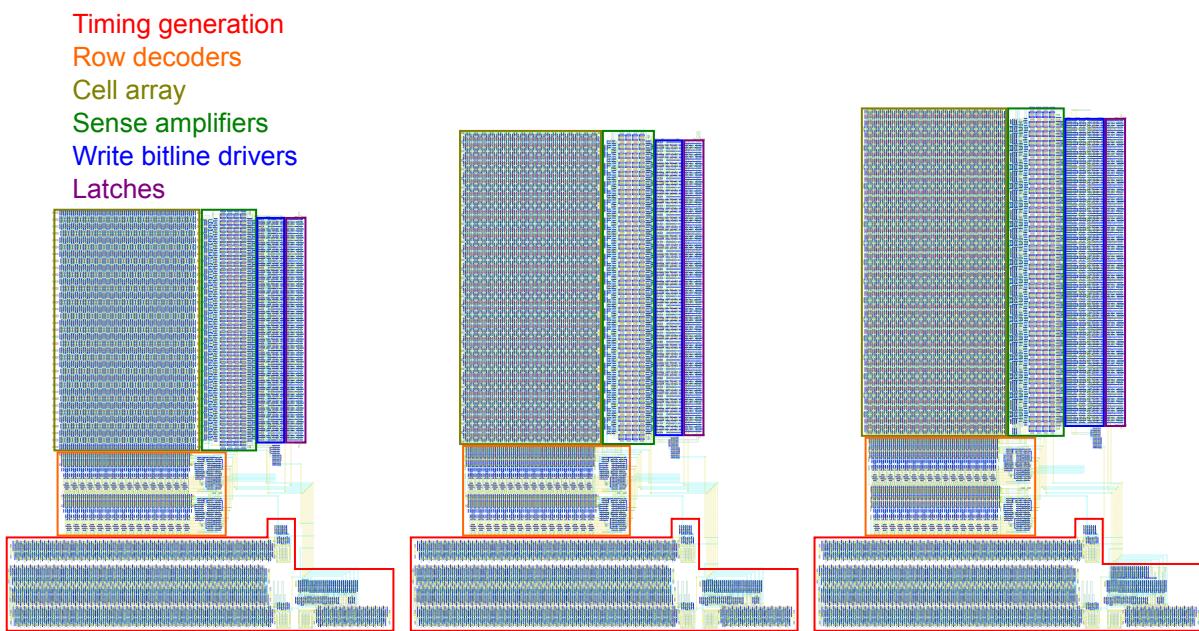

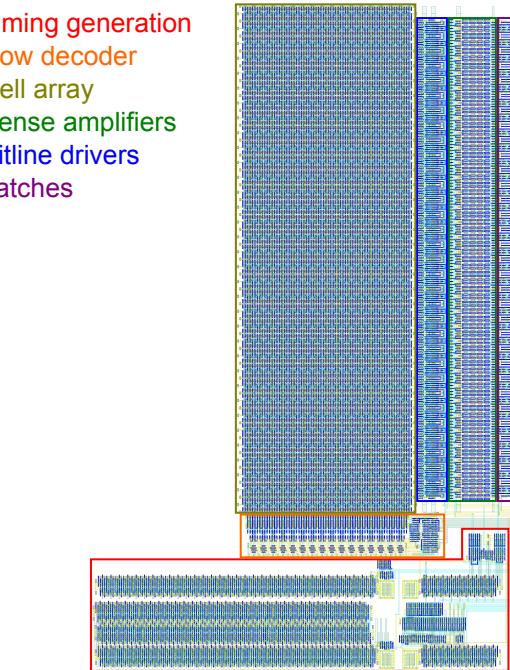

| 4.1.7    | Full memories . . . . .                               | 65        |

|          |                                          |            |

|----------|------------------------------------------|------------|

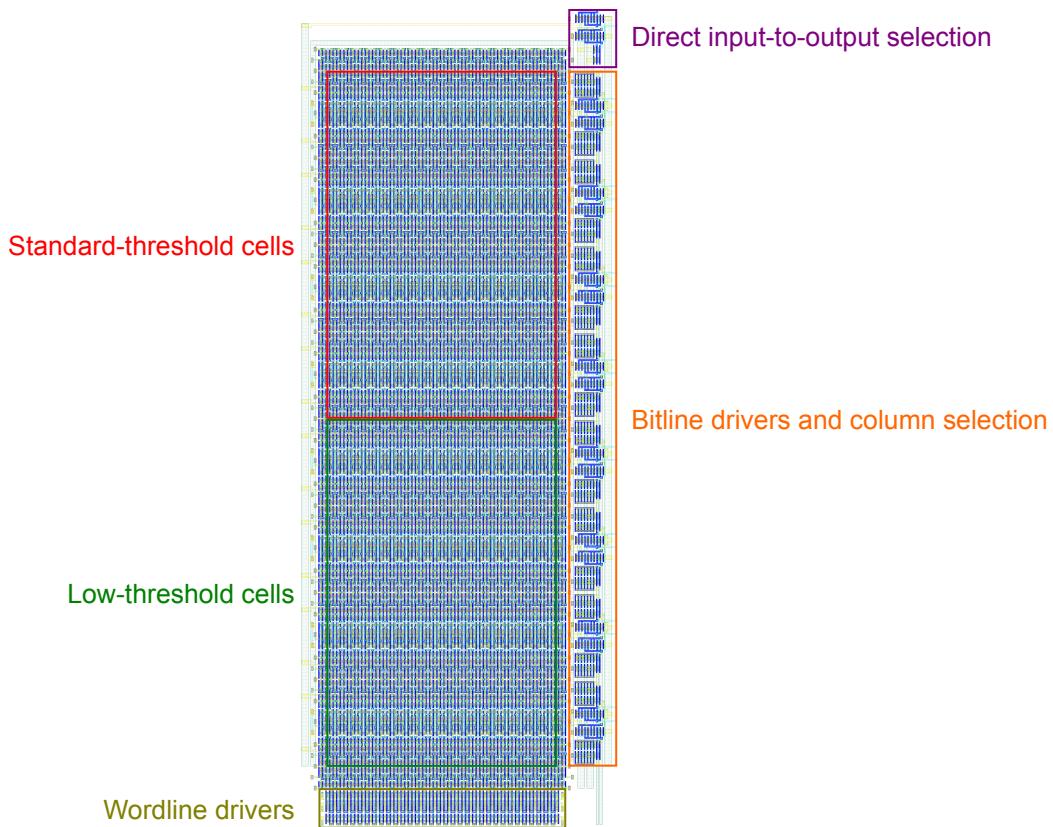

| 4.2      | Static memory . . . . .                  | 67         |

| 4.2.1    | 6T cell array. . . . .                   | 67         |

| 4.2.2    | Bitline driver. . . . .                  | 69         |

| 4.2.3    | Sense amplifier . . . . .                | 69         |

| 4.2.4    | Row decoder and latch. . . . .           | 71         |

| 4.2.5    | Timing generation . . . . .              | 71         |

| 4.2.6    | 6T cell memory . . . . .                 | 72         |

| 4.2.7    | SNM array . . . . .                      | 72         |

| 4.3      | Conclusion . . . . .                     | 76         |

| <b>5</b> | <b>Design of test chip and test plan</b> | <b>77</b>  |

| 5.1      | Testing . . . . .                        | 77         |

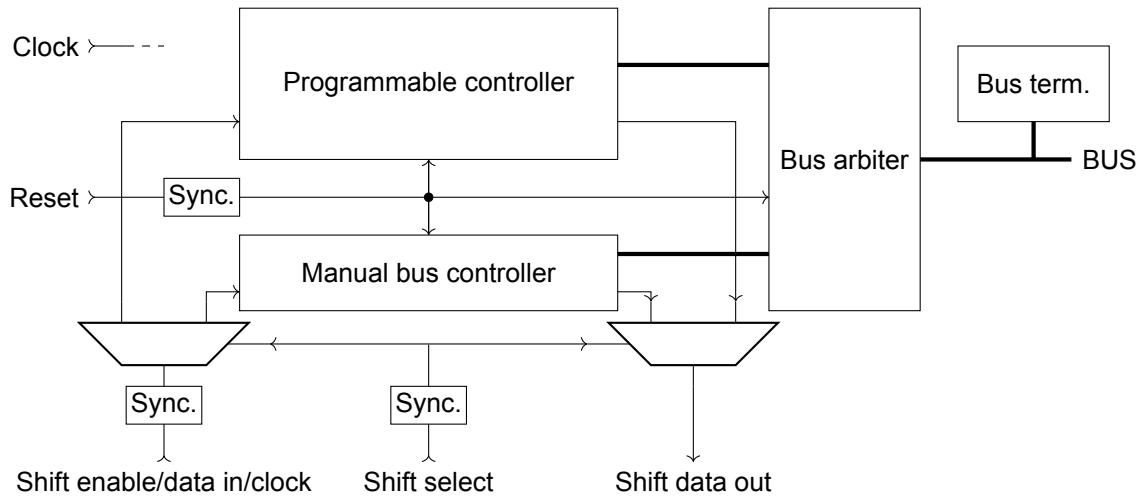

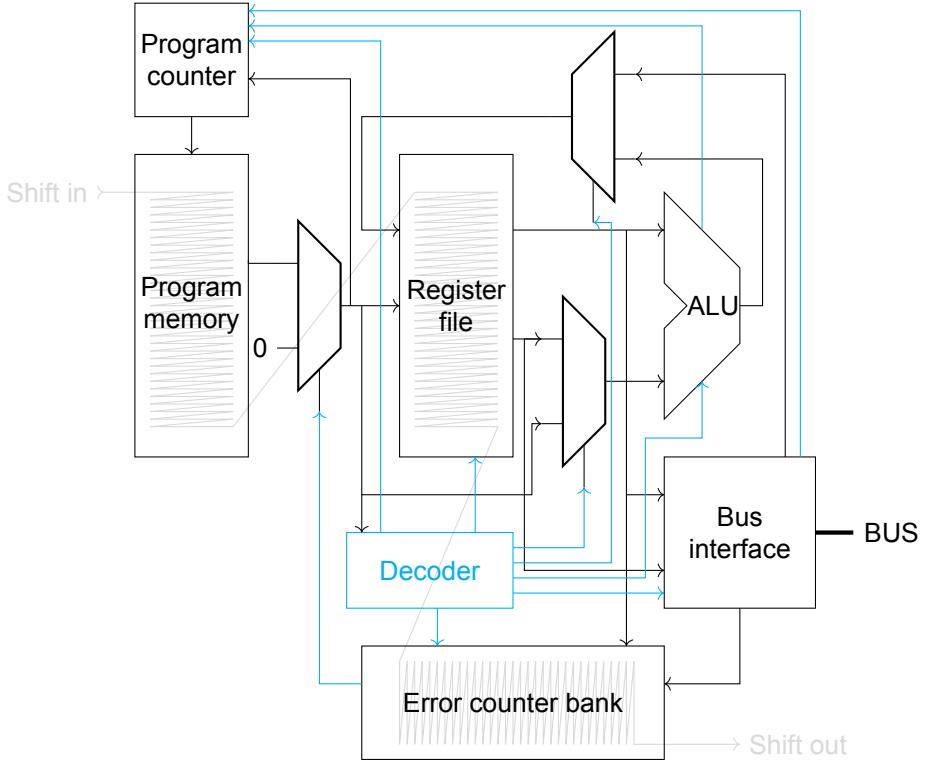

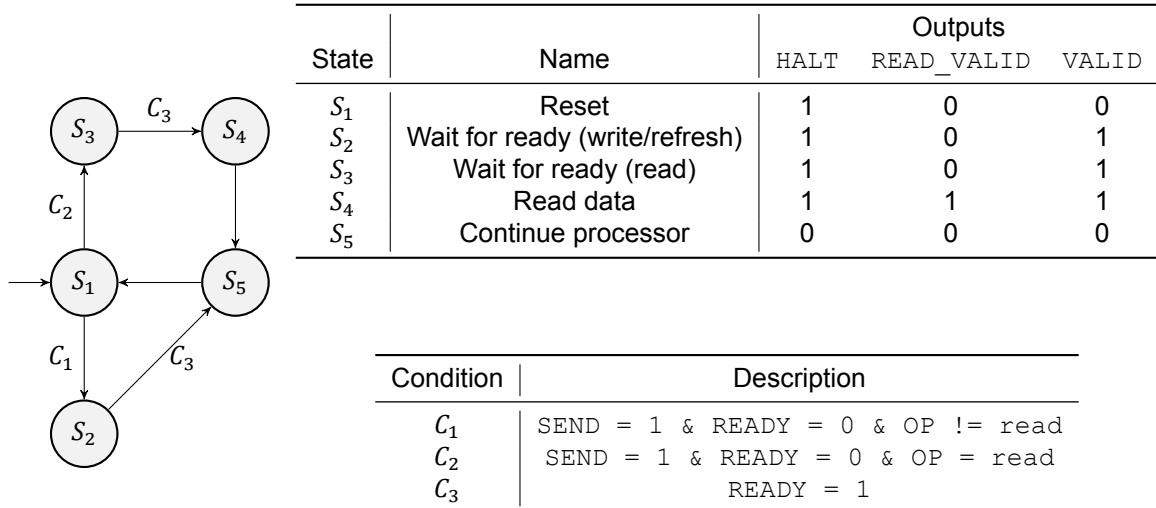

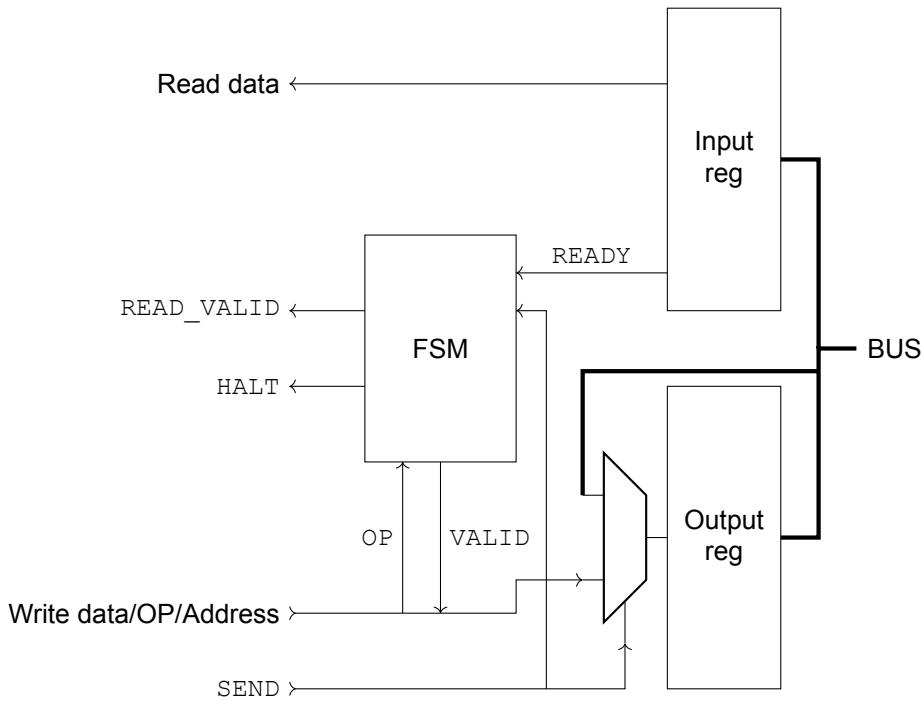

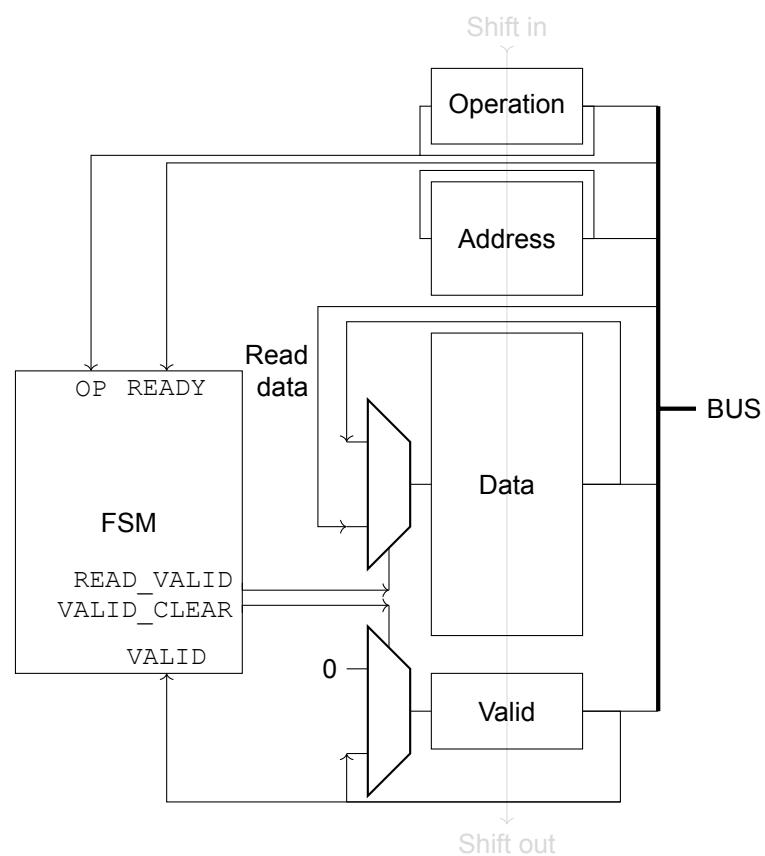

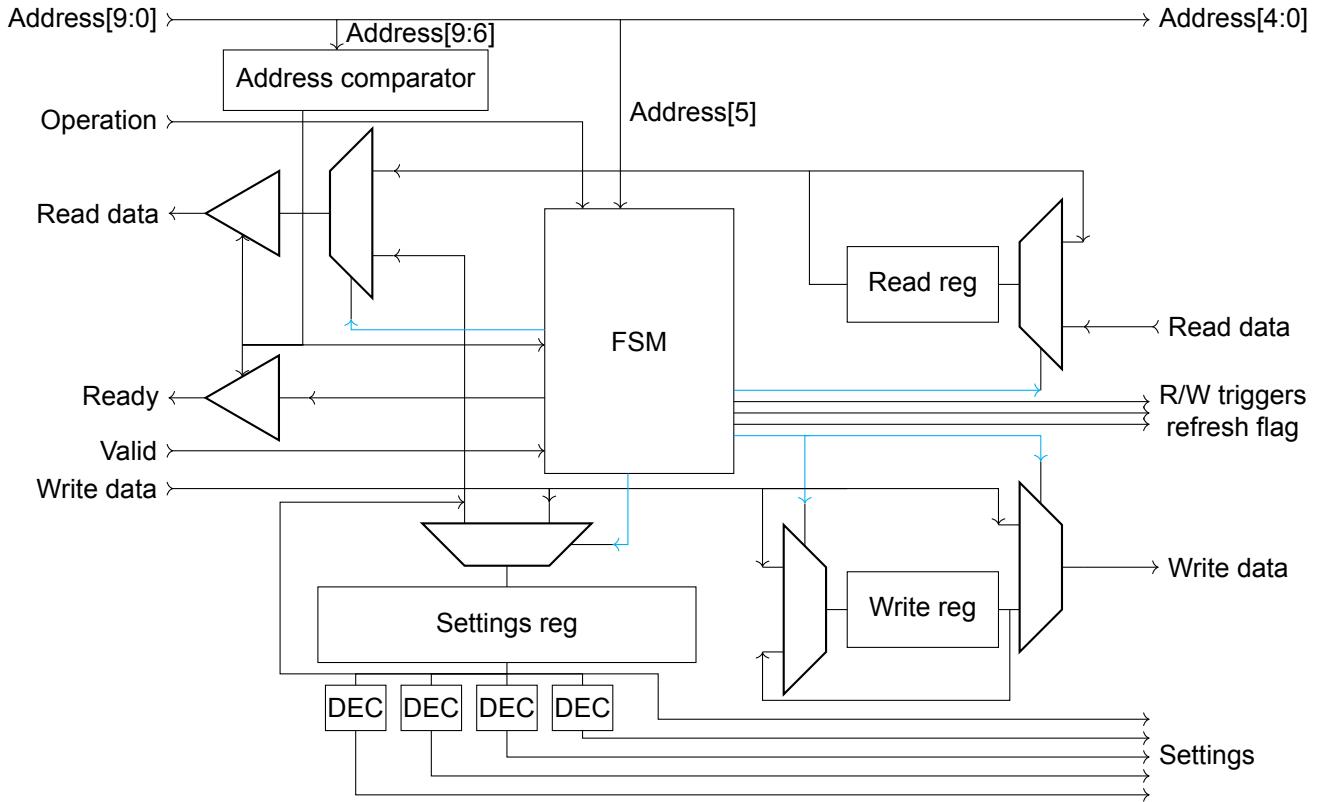

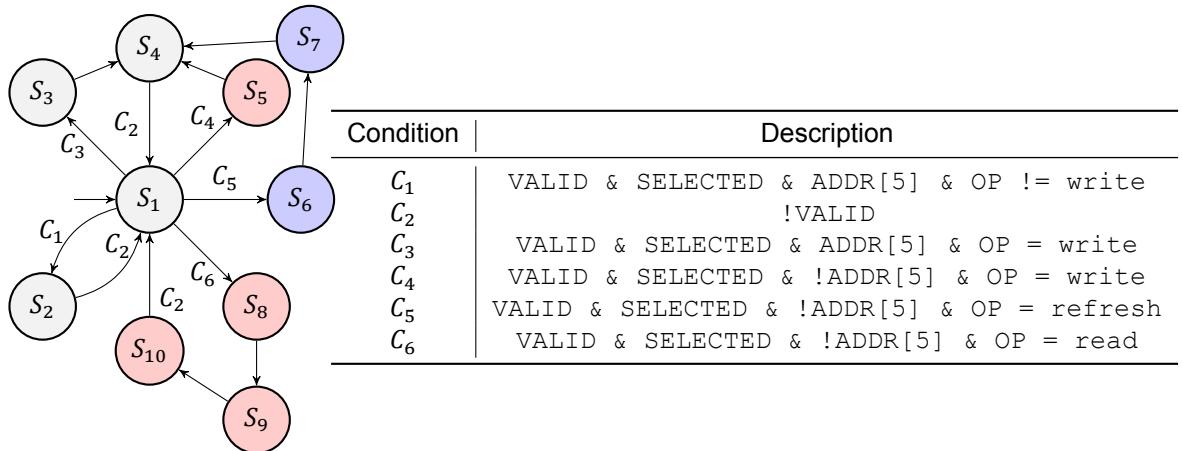

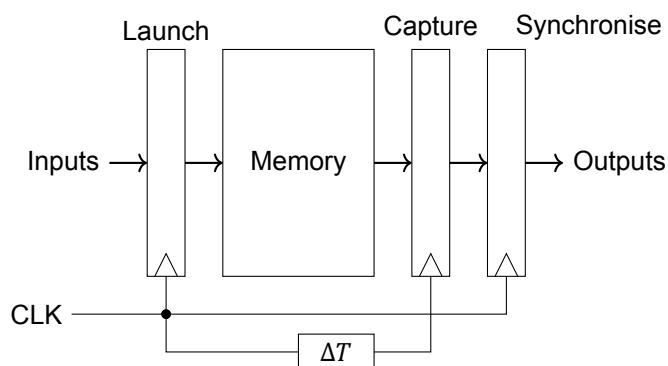

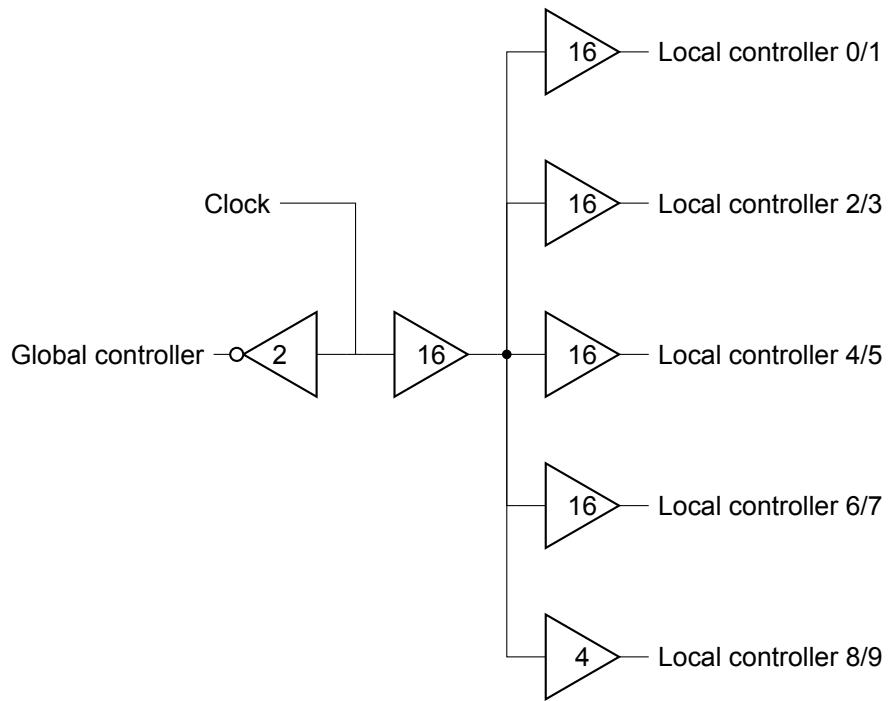

| 5.1.1    | Bus architecture . . . . .               | 77         |

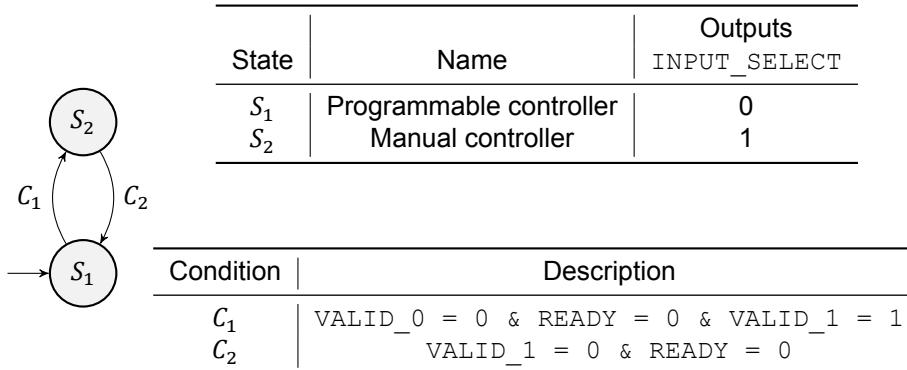

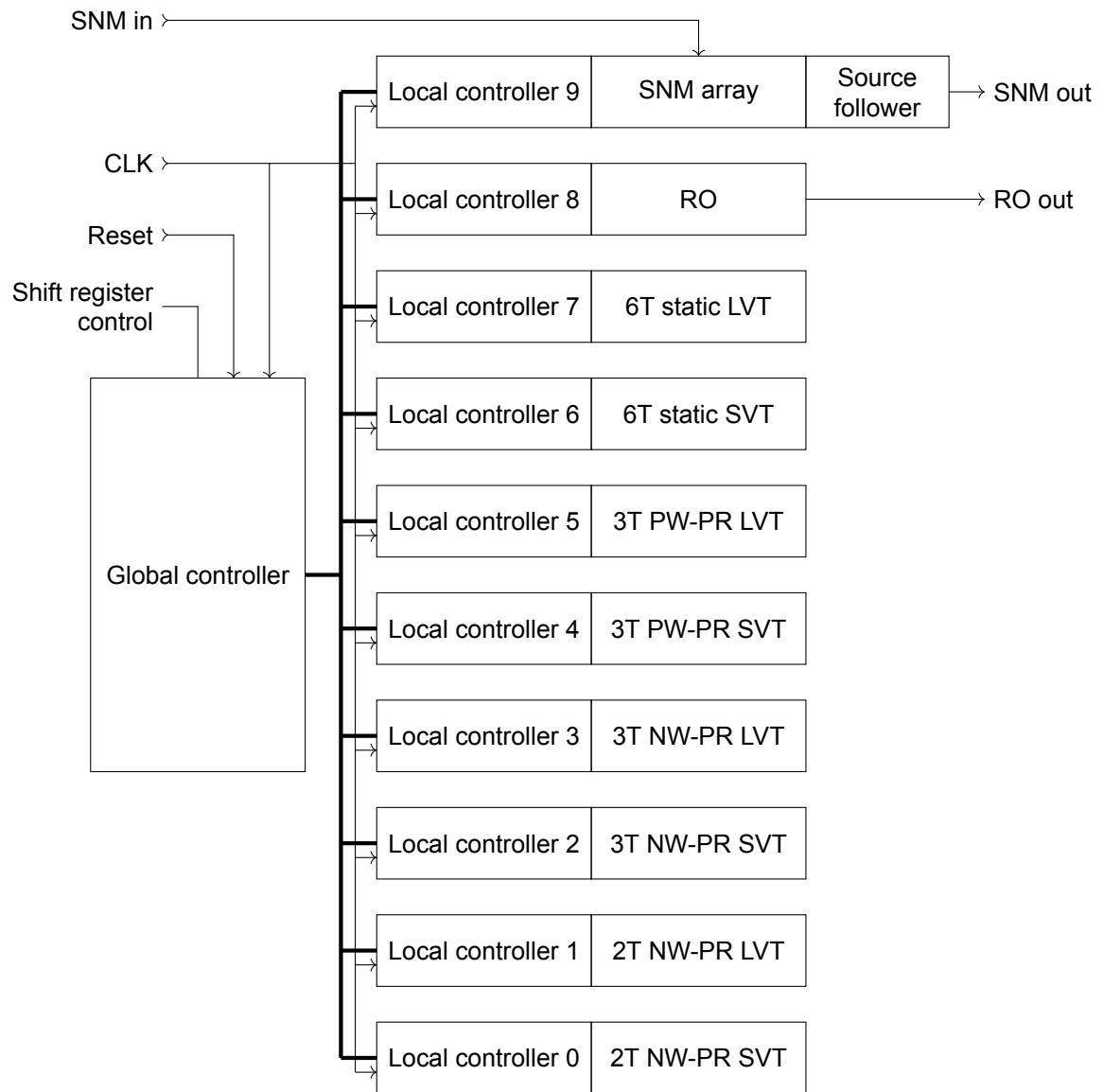

| 5.1.2    | Global controller . . . . .              | 79         |

| 5.1.3    | Local controller . . . . .               | 85         |

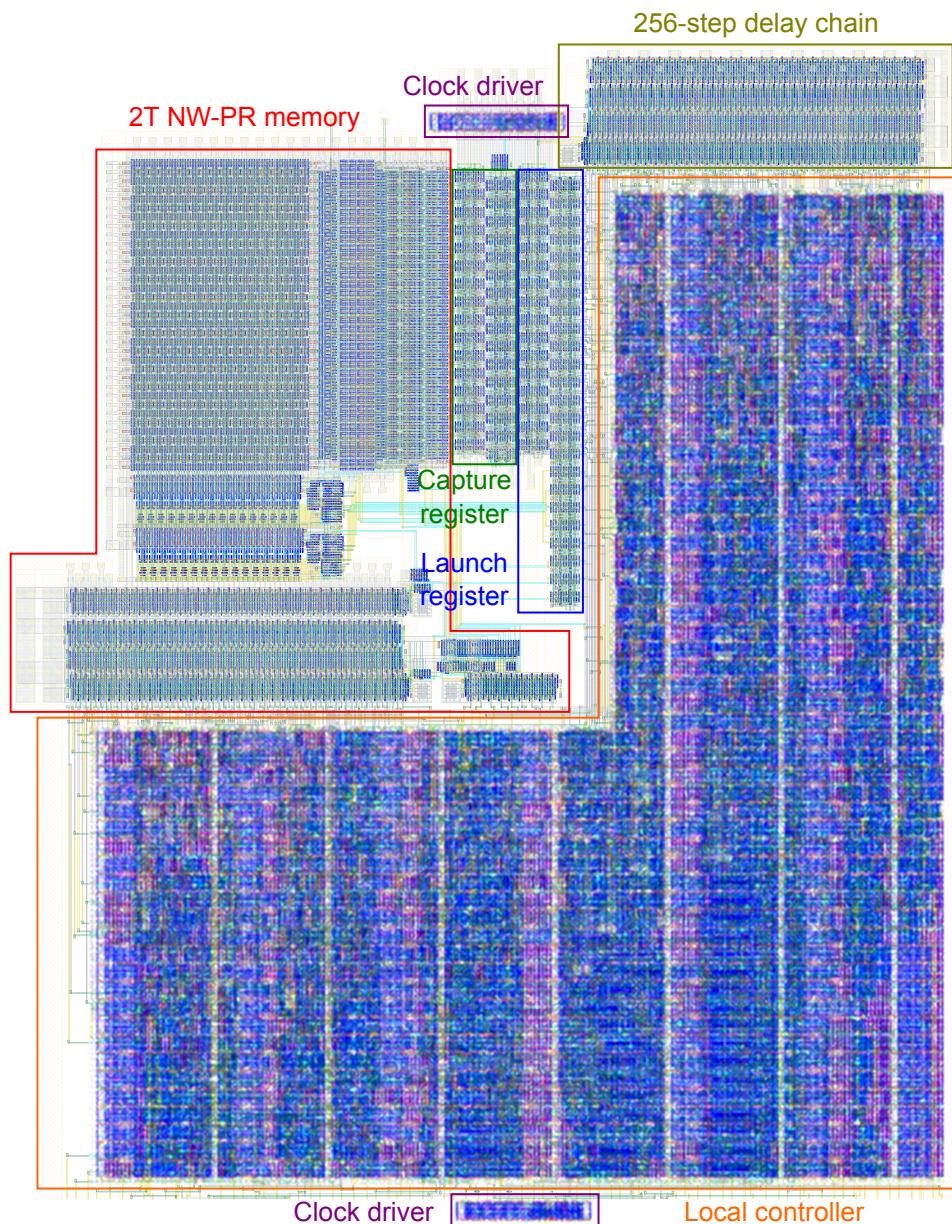

| 5.2      | Top level . . . . .                      | 89         |

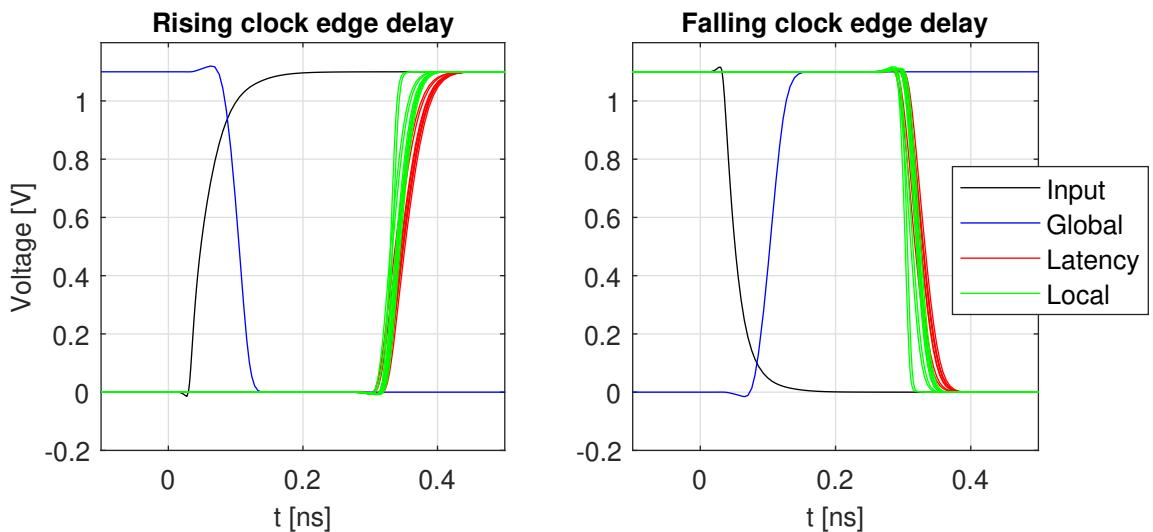

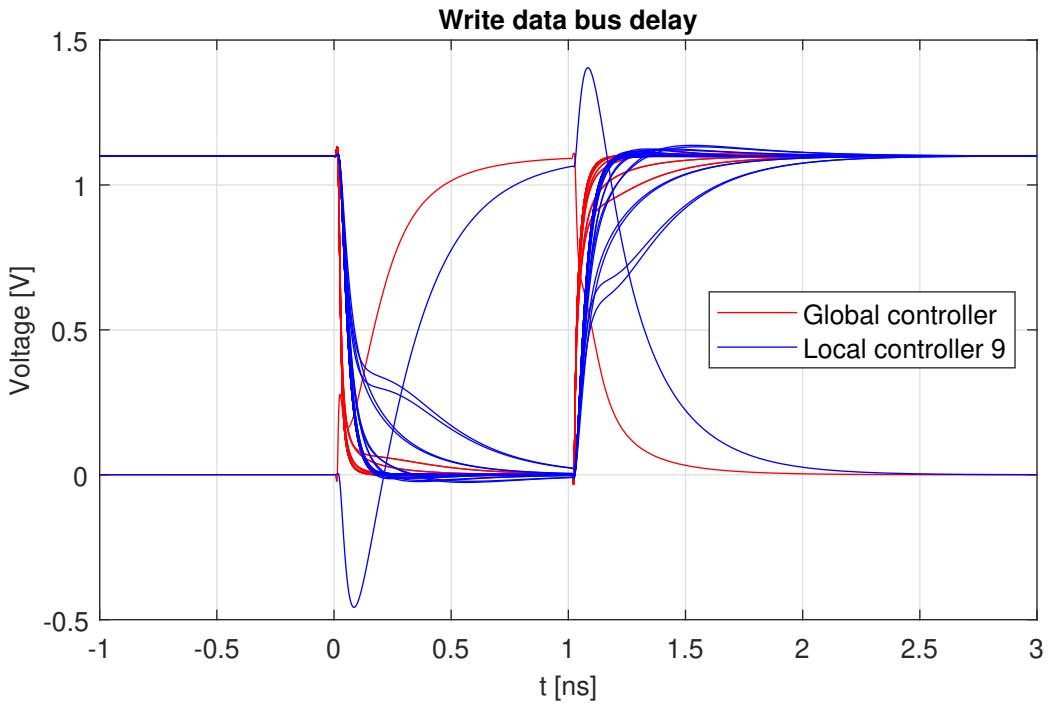

| 5.2.1    | Clock and data distribution. . . . .     | 89         |

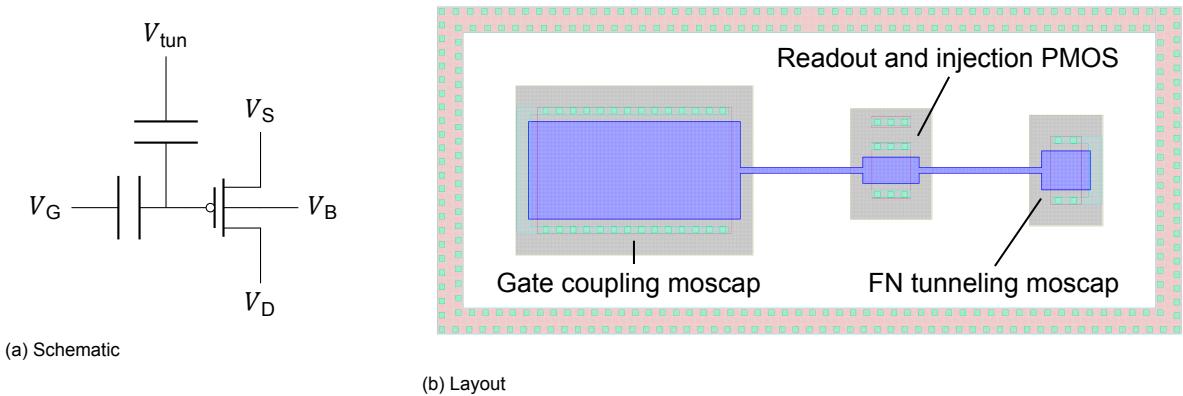

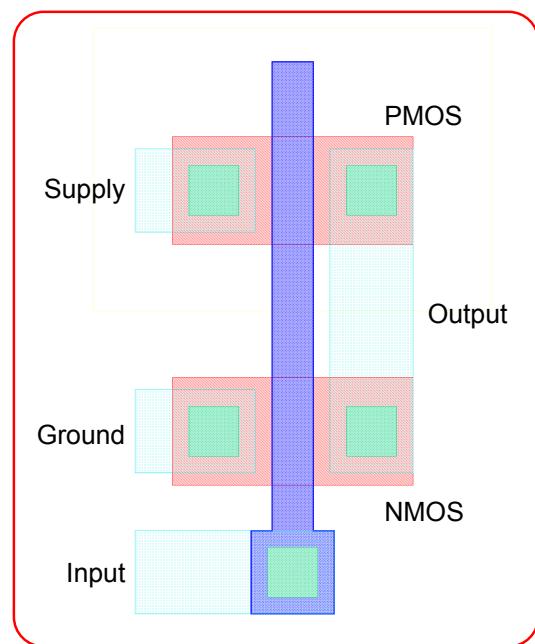

| 5.2.2    | Floating gate device . . . . .           | 93         |

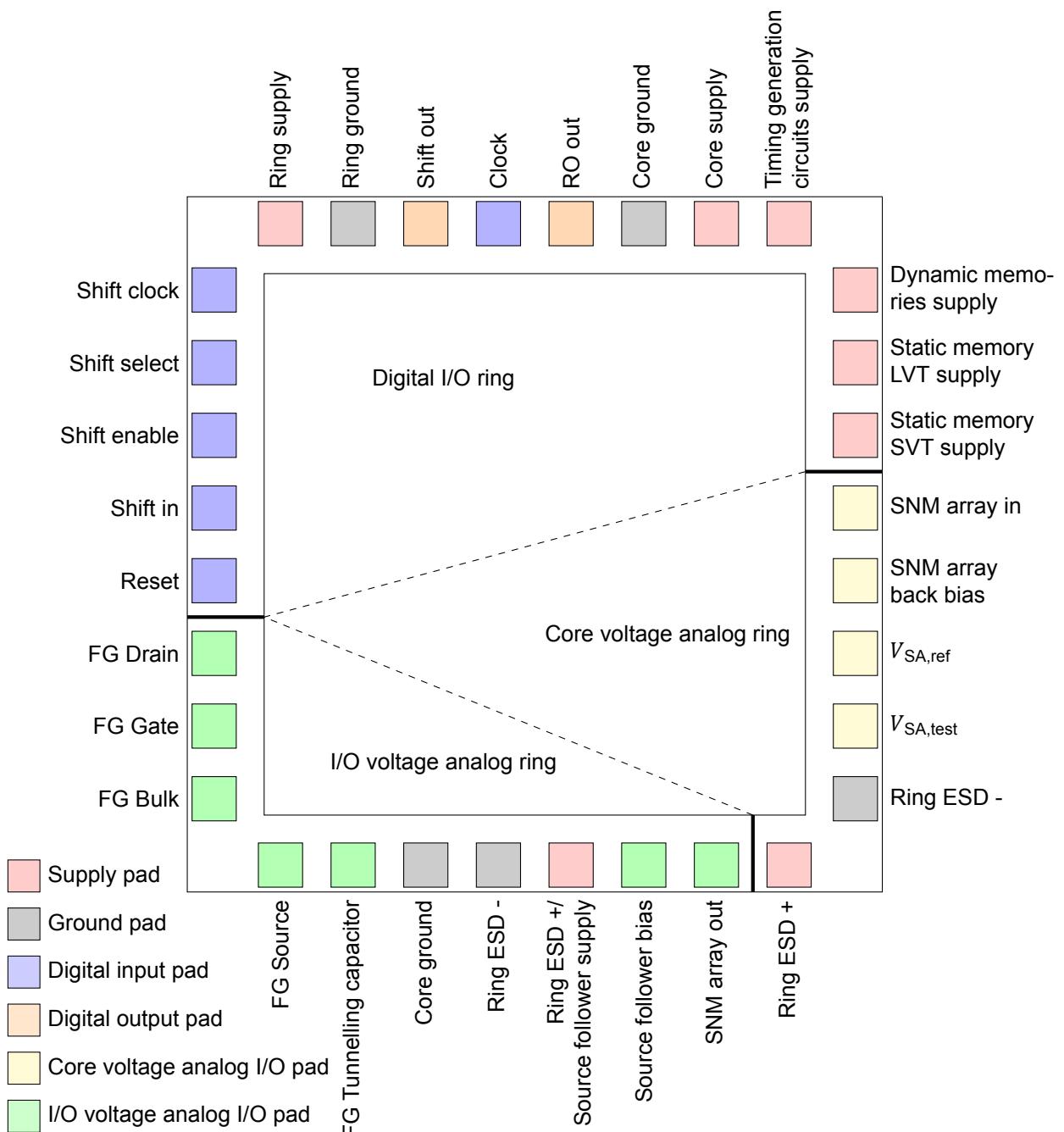

| 5.2.3    | Pad ring . . . . .                       | 93         |

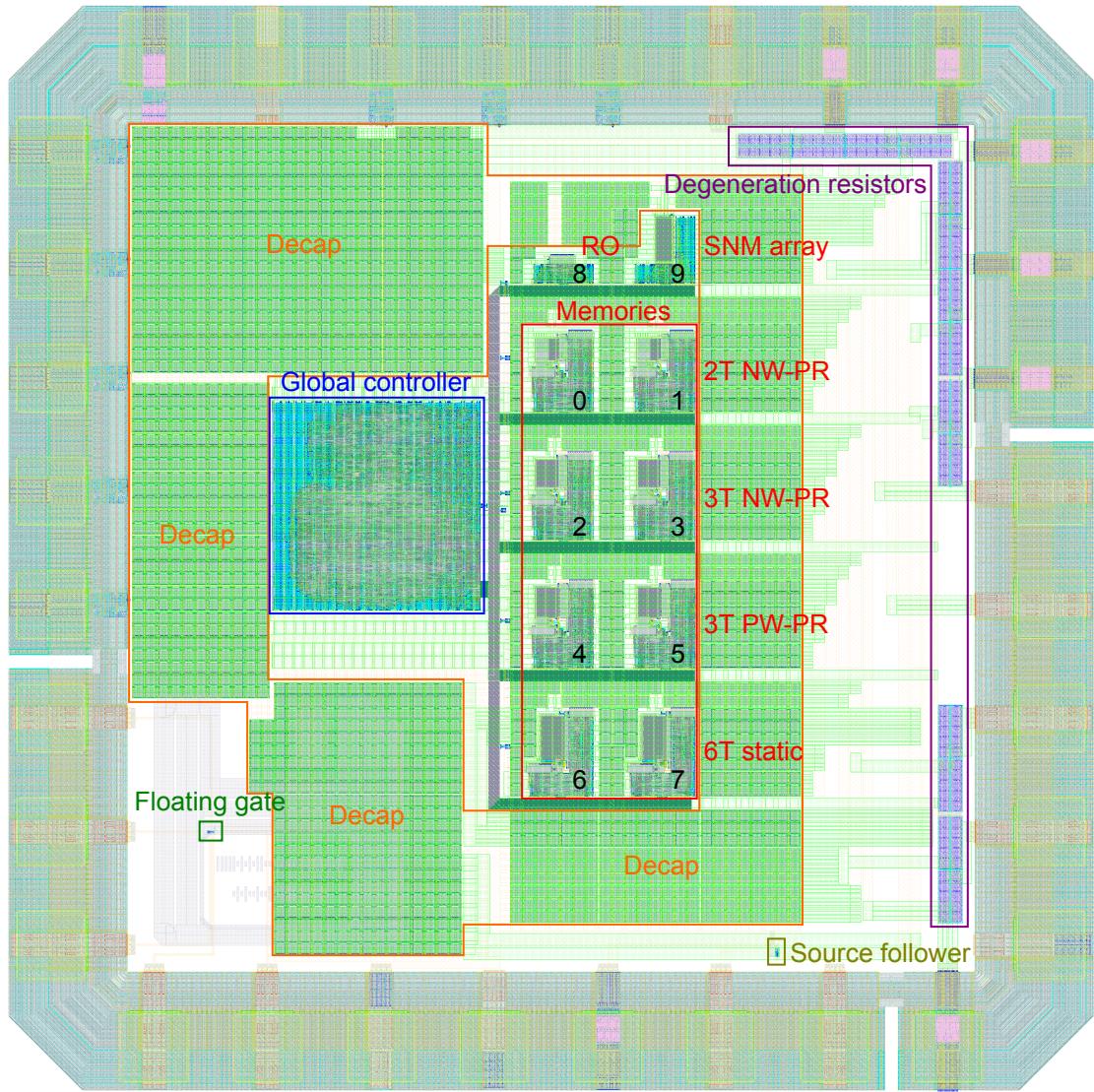

| 5.2.4    | Complete layout . . . . .                | 94         |

| 5.2.5    | Verification . . . . .                   | 94         |

| 5.3      | Test plan . . . . .                      | 94         |

| 5.4      | Conclusion . . . . .                     | 99         |

| <b>6</b> | <b>Conclusion and future work</b>        | <b>101</b> |

| 6.1      | Conclusion . . . . .                     | 101        |

| 6.2      | Discussion . . . . .                     | 101        |

| 6.3      | Future work . . . . .                    | 102        |

| <b>A</b> | <b>Layout legend</b>                     | <b>103</b> |

# Introduction

In this chapter, the motivation for this thesis work is explained. This is followed by the objective of this thesis. Finally, the outline of the thesis is presented.

## 1.1. Motivation

Quantum computers can theoretically outperform classical computers for certain problems by using superposition, entanglement, and interference of quantum states [1], [2]. The quantum states are encoded in qubits, which are implemented using quantum-mechanical systems such as, for example, single electron spins [3], [4] or superconducting transmons [5], [6]. Operations on these quantum states are executed by classical electronics that generate varying electric and magnetic fields through voltage and current pulses. The shapes, timing, and magnitudes of the pulses are determined by a classical controller running a quantum algorithm.

The classical controller that schedules and executes the operations on the quantum states requires digital memory to store programs, readout results, and waveforms of the pulses that are required to execute the quantum operations. Additionally, memory is required to hold quantum operations to align the timing of the operations, keep track of classical data and control flow, and interface with a host computer in a heterogeneous computing system. In order to build a scalable quantum computer, the classical electronics should be integrated close to the qubits [7], [8]. Since most qubit implementations currently still need to be cooled to millikelvin (mK) temperatures to limit the amount of thermal noise [9], [10], the current operational temperature of the classical electronics is proposed to be around 4.2 K. This increases the available cooling power in fridges and allows for testing using liquid helium. This requires the digital memories to also operate at these cryogenic temperatures. Eventually, the classical electronics and the qubits are envisioned to be integrated together at an intermediate temperature.

At 4.2 K, the available cooling power is still limited. This requires the memory power consumption to be minimised while meeting all other application constraints such as the maximum area, latency, and error rate. Due to a lack of device models that are valid at 4.2 K, a memory model can be used to predict performance based on room temperature simulation results combined with empirical cryogenic-CMOS characteristics.

At cryogenic temperatures, transistor leakage decreases significantly [11]. Dynamic memories may provide high-density and low-power storage opportunities that can not be matched by static memories, due to the increased retention time of charge on the storage capacitance [12]–[15].

## 1.2. Thesis objective

In this work, a model is developed to investigate the trade-offs associated with the selection of a memory cell design at both room temperature and cryogenic temperatures. The target application of this work is various memory applications in a classical controller for quantum computing, but the results could also be useful for memory designs in spaceflight, cryogenic experiments, and high performance computing. Since memory design is an extremely broad topic, this thesis is limited to the selection of the memory cell type by comparing four cell designs: three embedded dynamic cell designs, where data is stored

in the form of charge on a capacitance, and one static cell design, where data is stored in a bi-stable circuit.

Previous work on cryogenic memories mainly focused on the characterisation and comparison of single memory designs at various temperatures, from room temperature down to 4.2 K. Due to variations in memory designs and the used technologies, results of various works can not be quantitatively compared with each other. This work aims to compare various cell designs directly by keeping the technology and architecture as similar as possible with the goal of finding the best memory cell design for cryogenic memory applications.

The model, based on simulations of individual memory components in a TSMC 40 nm process at room temperature and 233 K, is developed for selection of the best memory cell design for a given application. The 'best' design is based on a combination of area, latency, error rate, and power consumption constraints. Due to the limited cooling power available at these low temperatures, a low power consumption will be the main target. This model helps to find the best cell design without having to simulate entire memory designs and includes cryogenic-CMOS characteristics without the need for complete device models.

To verify the model, a test chip is designed in TSMC 40 nm with eight fully-custom memory designs using the various cell designs. Two variations of every cell design are implemented using different threshold voltage devices to mitigate the increase of threshold voltage at cryogenic temperatures. The memories can be measured at both room temperature and 4.2 K using an on-chip programmable microcontroller, and the results can be used to verify and refine the model.

### 1.3. Outline

This thesis will start with necessary background on digital CMOS memories and cell designs, quantum computing and the associated digital memory applications, and cryogenic CMOS and cryogenic digital memories in chapter 2. This is followed by a modelling effort to investigate the trade-off between different memory designs at cryogenic temperatures in chapter 3. In chapter 4, the design of the actual memories for tape-out are explained. Chapter 5 covers the design of the testing architecture up to the complete top level IC design and describes the test plan. Finally, the thesis is concluded in chapter 6, together with an overview of suggested future work.

# 2

## Background

In this thesis, the trade-off between different digital CMOS memory cell designs for applications in quantum computing is investigated. This chapter will cover the necessary background information required to understand the following chapters. First, an overview of digital CMOS memories is given, starting with a general overview of how such a memory works, followed by a more detailed description of the operation of several memory cell designs. Next, the quantum computing application will be covered with the necessity for digital memories and some of the memory requirements. Finally, cryogenic CMOS is covered with the changes to the technology at low temperatures and an overview of the literature on cryogenic memories.

### 2.1. Digital CMOS memories

Before going into the memory applications and the effects of cryogenic temperatures on memories, the general architecture of digital CMOS memories and the cell designs of interest are shown. The purpose of a memory is to store digital information using a write operation and being able to retrieve it after an arbitrary amount of time using a read operation. Of course, it is important that the data does not change between the write and read operation.

The structure of this section is as follows. First, the components of a general memory architecture are shown and it is explained how they operate together to form a functioning memory. This is followed by an overview of five memory cell designs that will be used throughout the remainder of this thesis with specifics about their operation.

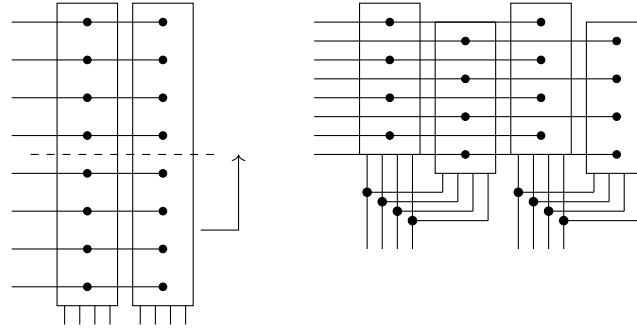

#### 2.1.1. Memory architecture

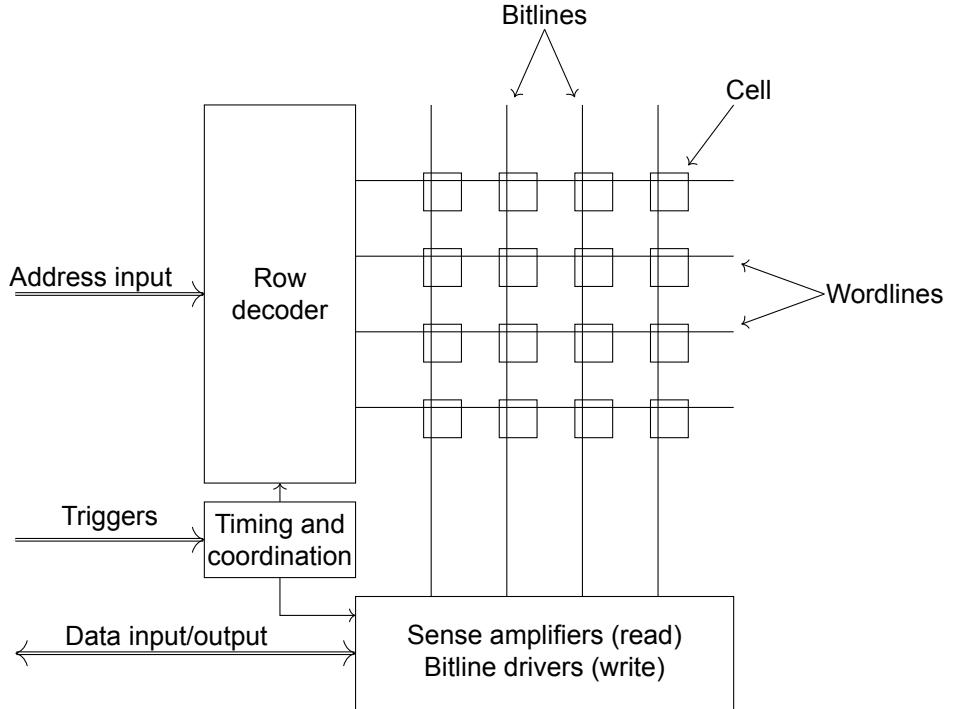

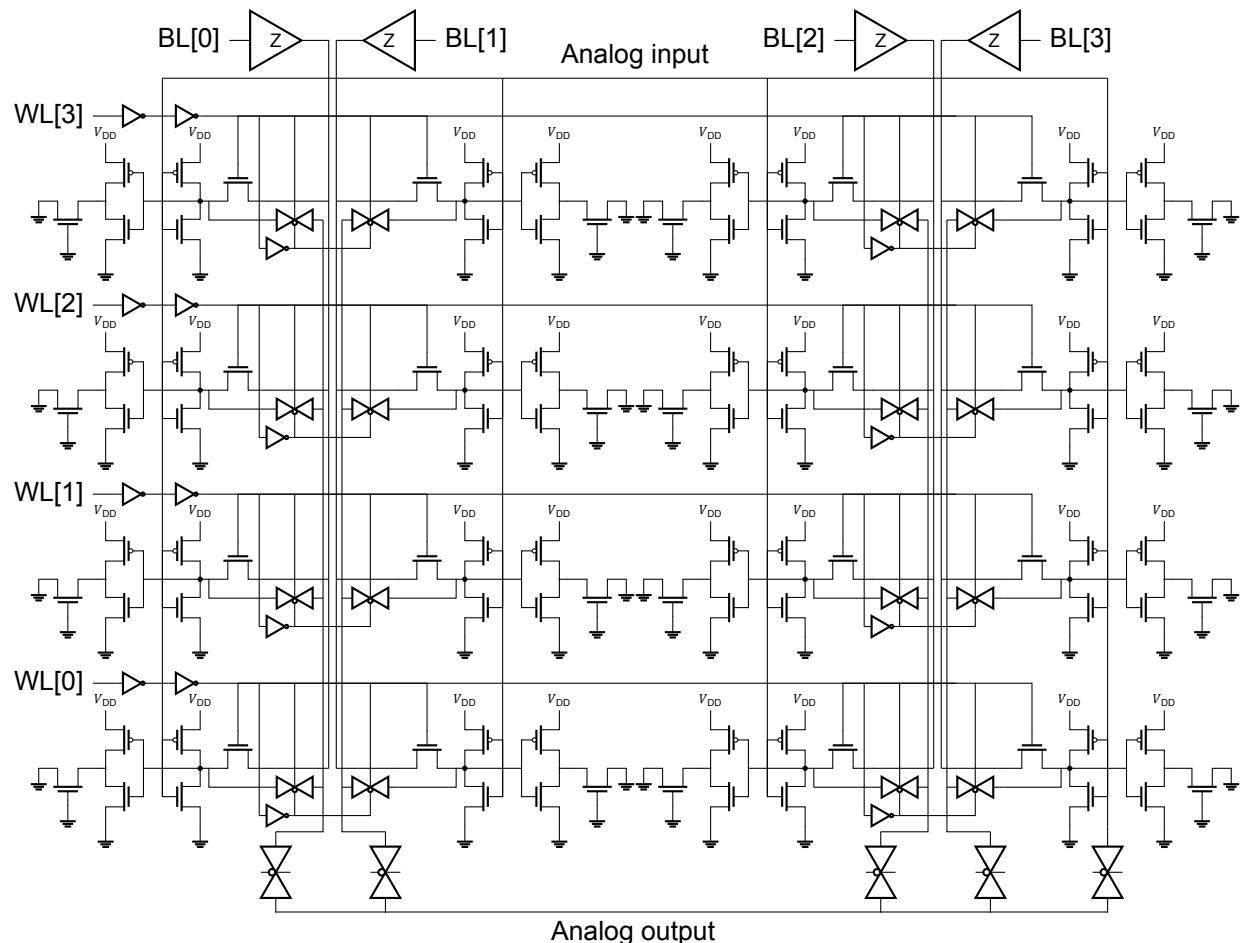

A basic memory architecture is shown in fig. 2.1. A two-dimensional array of cells is shown which is connected to several peripherals. Horizontally neighbouring cells (a *row* or *word*) share a *wordline* (WL), while vertically neighbouring cells (a *column*) share a *bitline* (BL). The wordlines can be seen as the control path, used to select a row of interest based on the address which is decoded by the row decoder. The bitlines can be seen as the data path, used to move data from the data input to the cells using the *bitline drivers* or from the cells to the data output using the *sense amplifiers*.

The memory has three modes of operation: *hold*, *write*, and *read*. In the hold mode, no row is selected and all cells hold the data in their internal state. In the write mode, a single wordline is driven by the row decoder and all bitlines are driven by the bitline drivers based on the input data. The cells in the selected row copy this data to their internal state, overwriting the previous state. In the read mode, again a single wordline is driven by the row decoder. However, now the selected cells develop a voltage on the bitlines based on their internal state. The sense amplifiers use the bitline voltage to determine the internal state of the selected cells, by comparing it with another bitline or a reference voltage, and present this data to the output.

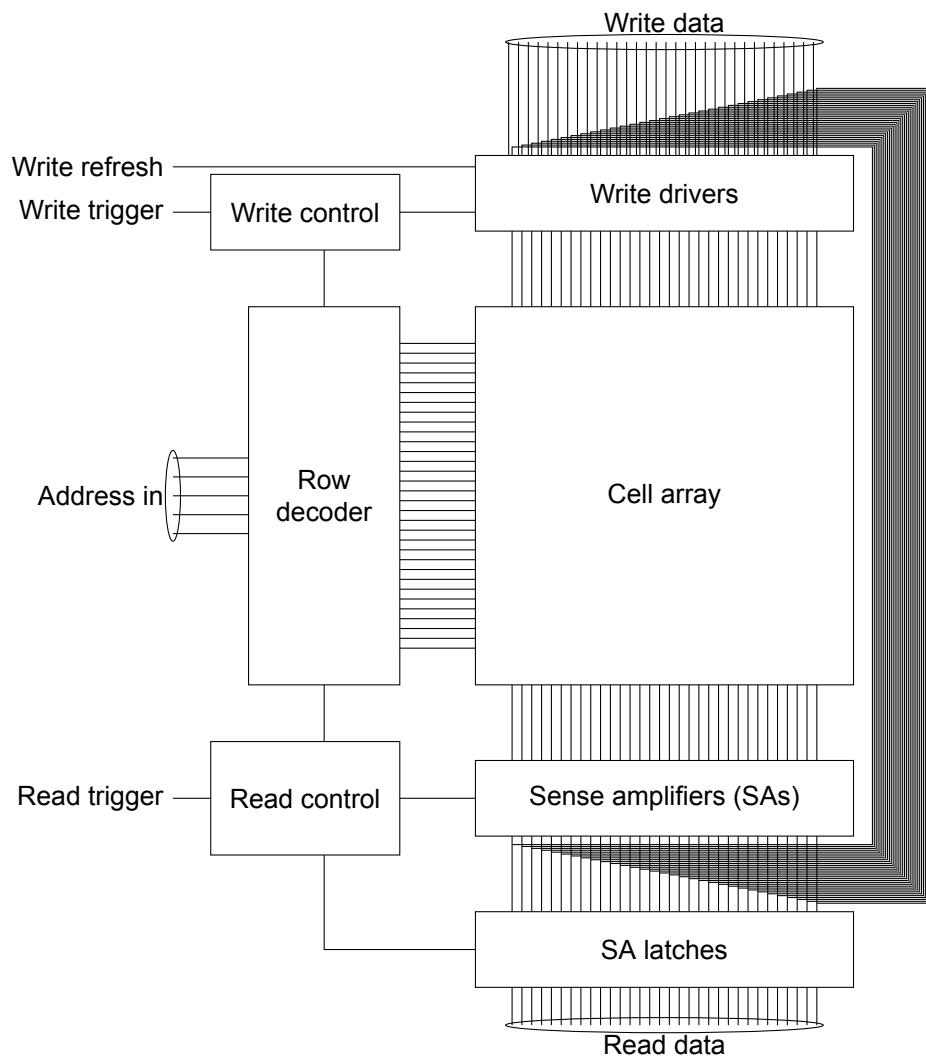

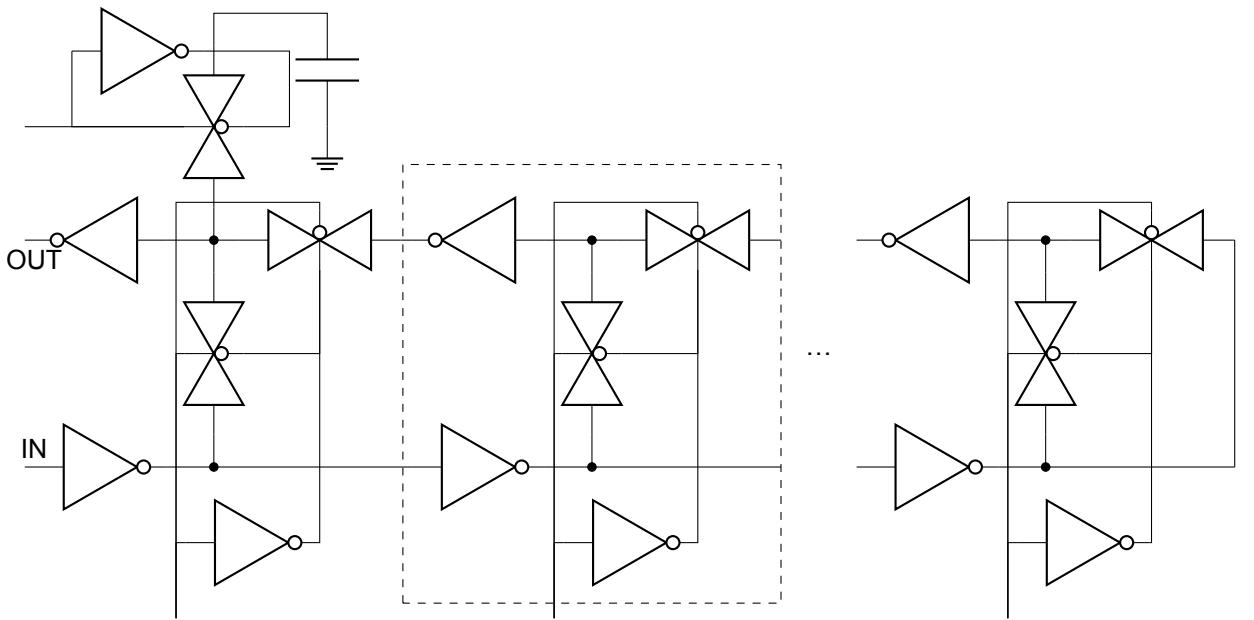

A more detailed view of a memory architecture is shown in fig. 2.2. The *timing-and-coordination* block is split into a *read control* and *write control* block, and the sense amplifiers and bitline drivers are also separated. Additionally, the output of the sense amplifiers is fed back into the write drivers. Dynamic cells, which store data in the form of charge on a floating node, slowly lose their data due to

Figure 2.1: Basic memory architecture with a  $4 \times 4$  cell array.

leakage and therefore require to be refreshed. This means that the cell is read and rewritten before the data is lost, refreshing the charge stored on the floating node. The direct connection from the sense amplifiers to the bitline drivers allows for refreshing without needing external hardware to ensure the data feedback. Finally, the sense amplifiers are followed by set of latches. They are used to isolate the sensitive sense amplifier circuits from the output of the memory and ensure that the data output always presents valid read data.

### 2.1.2. Memory cell designs

In this section, the schematics and operational details of four dynamic cell designs and one static cell design are explained.

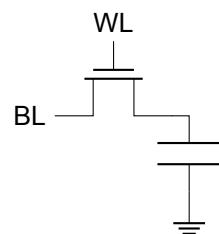

#### 1T1C dynamic cell

The 1T1C cell design is the most used dynamic memory cell due to its high integration density. It consists of a single pass transistor (1T) for access to a capacitor (1C) on which charge is stored, as shown in the schematic shown in fig. 2.3. With the use of special processes, such as trench capacitors, the capacitor can be implemented vertically with a capacitance in the order of 20 fF to 50 fF [16], [17], which results in tiny cells that can hold large amounts of charge.

Due to the special processes used, this cell design is rarely embedded in logic designs. Without these processes, a large cell area is required to get sufficient storage capacitance. It is therefore not considered as a viable cell design in the remainder of this thesis.

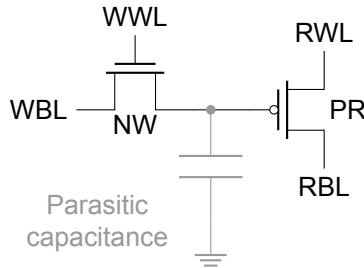

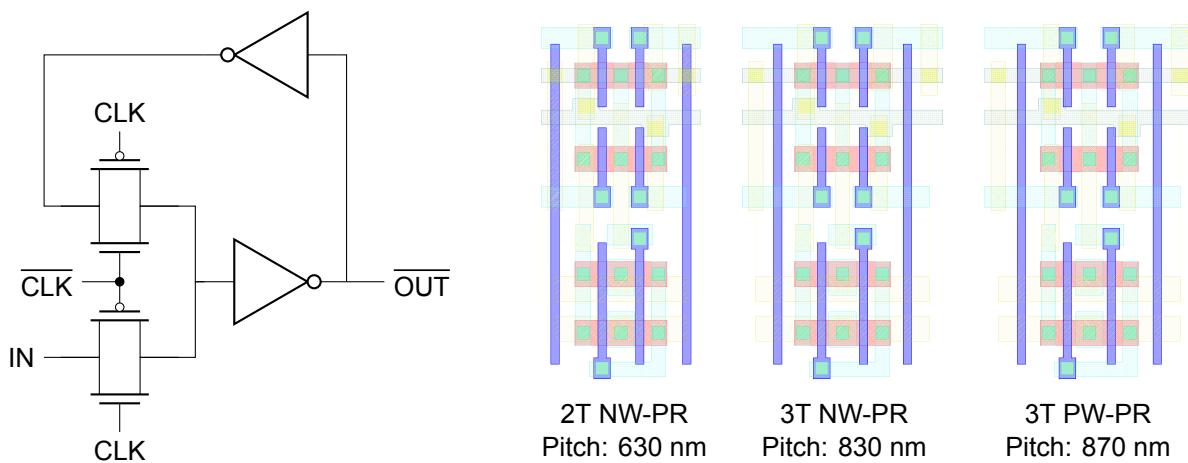

#### 2T NW-PR dynamic cell

The first gain cell to cover is the dynamic 2T NW-PR memory cell. The cell name describes its schematic, which is shown in fig. 2.4, since it consists of two transistors (2T), uses an NMOS transistor for write operations (NW), and a PMOS transistor for read operation (PR). It is called a gain cell, because the gain of the readout PMOS is used to convert the storage-node voltage into a readout current. The main difference with the memory architecture described in the previous section, is the use of two wordlines (RWL/WWL) and two bitlines (RBL/WBL) per cell, one set for a write operation (W prefix) and one set for a read operation (R prefix). The general memory architecture still holds, but two row decoders are used, one for each set of wordlines (RWL and WWL), the sense amplifiers are

Figure 2.2: General memory architecture with a  $32 \times 32$  cell array with refresh data shortcut.

Figure 2.3: 1T1C dynamic memory cell schematic.

connected to the read bitlines (RBL), and the write drivers are connected to the write bitlines (WBL). In the following paragraphs, the three operation modes of this cell are covered.

Figure 2.4: 2T NW-PR dynamic memory cell schematic.

**Write** To start a write operation, the WWL is pulled high which opens the NMOS pass transistor. If the WBL is driven low, the capacitance of the *storage node* (gate capacitance of PR + parasitic capacitance, in the order of 450 aF) is discharged completely. If the WBL is driven high, the storage node is charged to roughly the WBL voltage minus the threshold voltage of NW. The write operation is ended by pulling the WWL low again. This causes the storage-node voltage to drop slightly due to the coupling between the WWL and the storage node. During the entire operation, the RWL and RBL are pulled low.

In this thesis, WWL boosting is not considered. By increasing the WWL beyond the nominal supply voltage, larger voltages can be written to the storage node. However, this could lead to premature device failure and requires additional design effort to ensure that voltages beyond the supply voltage can be handled.

**Hold** In the hold mode, the WWL, RBL, and RWL are pulled low. Ideally, this completely disconnects the storage node from the remainder of the circuit and the charge is maintained. However, if the WBL voltage is opposite of the stored voltage, sub-threshold (leakage) current through NW causes the storage-node voltage to drift, which weakens the stored state. Since the WBL is shared between different cells, this will be the case for roughly half the cells. This limits the total duration that the data is valid, also called the *retention time*. Other leakage sources include gate-oxide tunnelling or gate-induced drain lowering (GIDL) [18], reducing the retention time further.

**Read** In the read mode, the RWL is pulled high while the RBL has been precharged low. If the storage-node voltage is low, sufficient overdrive across PR will cause inversion and RBL will be charged. If the storage-node voltage is high, PR will remain in cutoff and the RBL will remain discharged. After a certain amount of time, the *read time*, the RBL voltage is compared with a reference voltage to determine the original cell state: 0 if the RBL voltage is larger than the reference voltage, and 1 if the RBL voltage is smaller than the reference voltage.

Due to the voltage drop across NW, the storage-node voltage can never reach the supply voltage. As a result, it may seem that the output transistor should always experience at least some inversion during readout since the difference between the storage node and the RWL (at the supply voltage) is about one threshold voltage. This is not the case due to the gate-to-source coupling capacitance of PR. When the RWL is charged, the storage-node voltage is pulled up, resulting in a gate-to-source voltage that is lower than the threshold voltage. This coupling voltage step also occurs if the storage-node voltage is low, which reduces the maximum overdrive that can be obtained and therefore limits the speed of the readout.

Due to the readout transistor coupling, the same transistor type 2T NW-NR and 2T PW-PR cell alternatives do not work without wordline boosting. For example, a PMOS write transistor would result in a storage-node voltage equal to the supply (high) or a single threshold voltage (low). Including the voltage increase on the storage node due to the coupling, the readout transistor will be fully off in case of a high storage-node voltage and either off or in very weak inversion in case of the low storage-node voltage. As a result, only small voltage differences will be generated on the RBL and therefore the cell is hard to read. A similar reasoning holds for the 2T NW-NR cell.

Using the *bitline voltage margin* method described in [19], the 2T NW-PR design is chosen over the 2T PW-NR design. In this method, the difference between the bitline voltages after a read operation for both states, the *bitline margin*, is simulated. For a similar time between the write and read operation, the *hold time*, the bitline margin of the 2T NW-PR cell is larger than that of the 2T PW-NR cell. This makes it easier for the sense amplifiers to distinguish the two states.

Finally, the maximum difference between the two bitline voltages is limited to roughly one threshold voltage. Unselected cells ( $RWL = 0$ ) with a low storage-node voltage will cause a current from the RBL to the RWL when the RBL voltage exceeds the threshold voltage of PR. Besides limiting the maximum bitline voltage, it also increases the power consumption during read operations since the current is not used effectively. This puts an upper limit on the read time since the bitline voltage margin can only shrink once this limit has been reached and all additional energy is wasted.

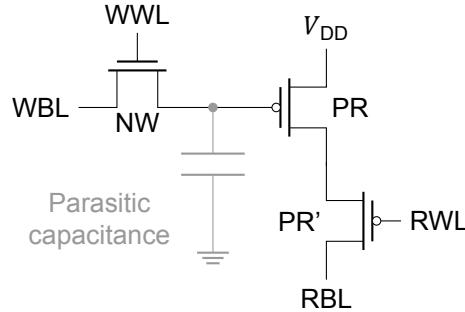

### 3T NW-PR dynamic cell

A second dynamic gain cell, the 3T NW-PR cell, is shown in fig. 2.5. It is a three transistor cell (3T) with an NMOS write pass transistor (NW) and a PMOS read transistor stack (PR and PR'). It consists of a 2T NW-PR cell (NW and PR) with the RWL always pulled high (read mode), but the RBL charging current is gated by a second PMOS transistor (PR'). As mentioned before, the gate-to-source coupling of the readout transistor is the reason that the 2T NW-PR cell works. This coupling is not present in this design, so instead the threshold of PR should be increased to ensure that the transistor is fully off when the storage node has been written high.

Figure 2.5: 3T NW-PR dynamic memory cell schematic.

This cell again has three operation modes which are similar to those of the 2T NW-PR cell design. The polarity of the RWL signal must be inverted, since it should be low when reading and high otherwise. The readout process is similar, where the RBL is charged towards the supply voltage if the storage-node voltage is low. Due to the additional gate, the readout leakage problem of the 2T NW-PR cell design is solved. Additionally, the overdrive on PR for a low storage-node voltage is larger since there is no coupling voltage step that increases the storage-node voltage during readout. This results in a faster readout than the 2T NW-PR cell.

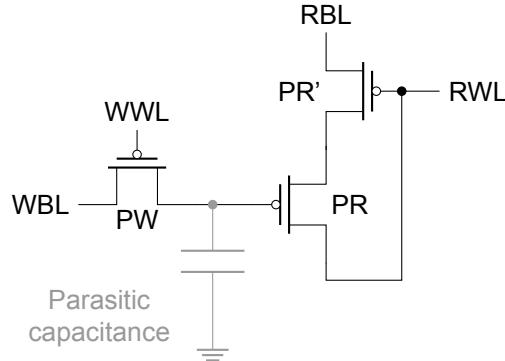

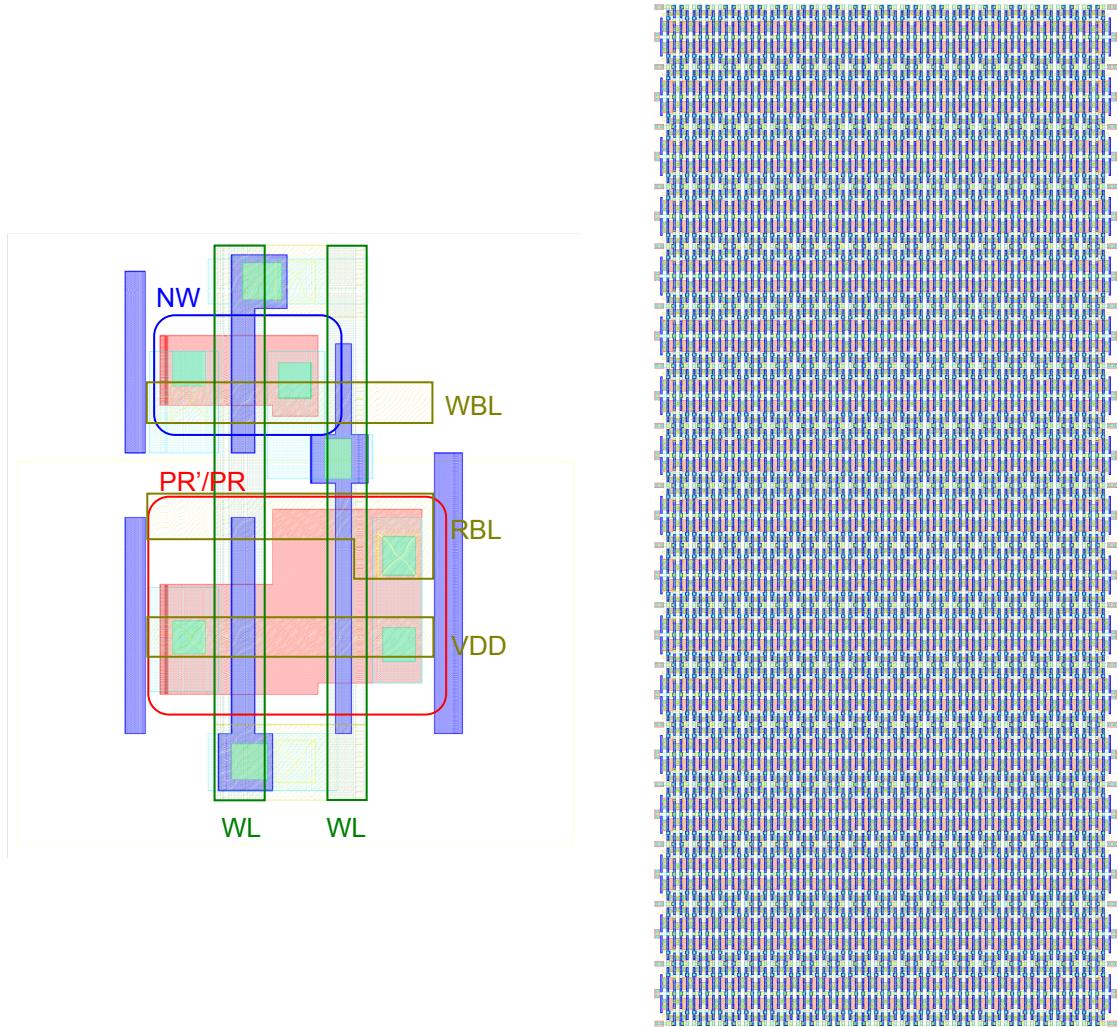

### 3T PW-PR dynamic cell

The final dynamic gain cell is a 3T PW-PR cell with *preferential boosting* [20]. It is a three transistor cell (3T) with both a PMOS write transistor (PW) and a PMOS read transistor stack (PR and PR'). The schematic is shown in fig. 2.6 and is similar to the 3T NW-PR cell schematic.

The term *preferential boosting* comes from [20] and indicates the connection between the PR drain and the RWL. Similar to the 2T NW-PR transistor, this direct connection between the RWL and PR will cause a voltage step (down instead of up) on the storage node due to the coupling capacitance between the storage node and the RWL. It is called preferential since the step increases the difference between the storage-node voltages. If the storage-node voltage is high, there will be no channel and the coupling capacitance will be low. As a result, the voltage step down on the storage node is small. If the storage-node voltage is low, there is a channel in PR and the capacitance between the storage node and the RWL is higher. In this case, the voltage step down on the storage node is larger and therefore the storage-node voltage difference during readout is increased.

Contrary to the other cell designs with PMOS readout transistors, the RBL will be discharged for this design since RWL must be pulled low to open PR'. As a result, the RBL can not be discharged below

Figure 2.6: 3T PW-PR dynamic memory cell schematic.

a threshold voltage. This slows down the readout process for this cell type, but the step down on the storage-node voltage ensures sufficient overdrive voltage. Similar to the 3T NW-PR cell, this cell does not suffer from the readout leakage problem due to the pass gate in the readout stack. Contrary to the other dynamic cell designs, the readout of this cell is non-inverting: a high written voltage leads to a high bitline voltage, while a low written voltage leads to a low bitline voltage. This requires additional inversions throughout the full memory design, compared to the other dynamic cell designs, to ensure the correct data polarity.

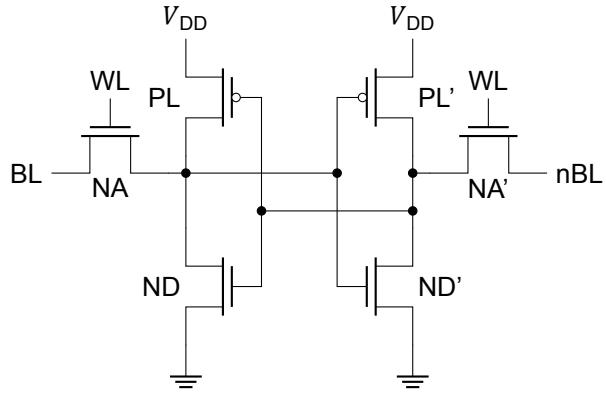

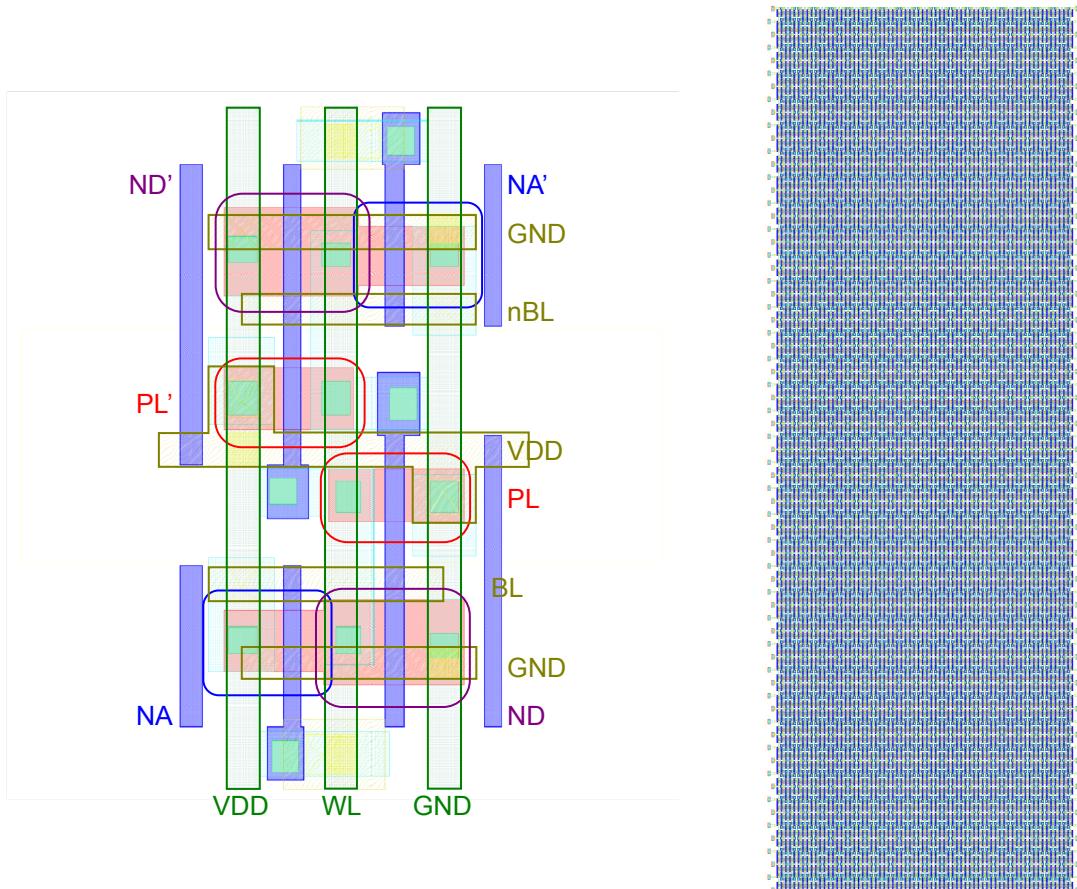

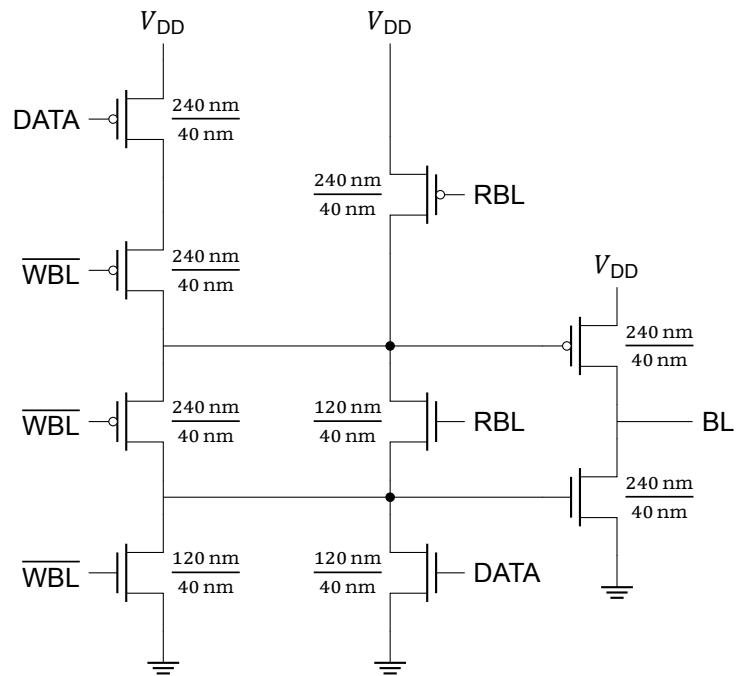

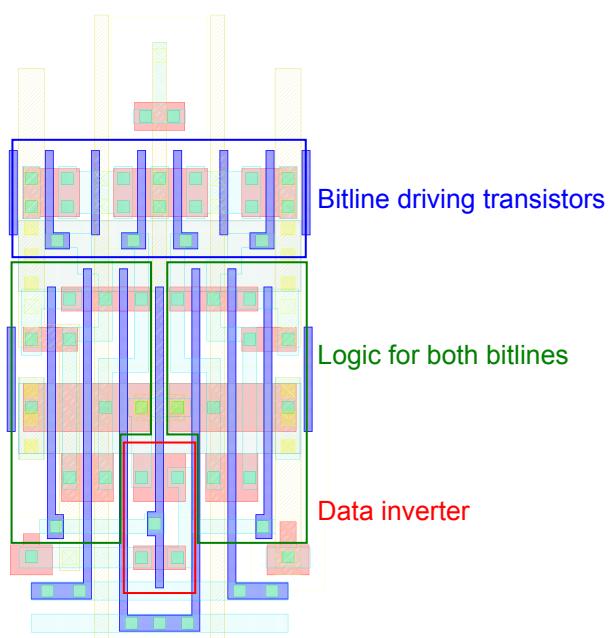

#### 6T static cell

The 6T static cell is the most used static memory cell and its schematic is shown in fig. 2.7. In this case, the data is stored in the state of a static bi-stable circuit consisting of two cross-coupled inverters. The cell does not require refreshing due to the static feedback, but is much larger than the dynamic cells since it requires six transistors (6T). The PMOS transistors are also called the *load* transistors (PL/PL'), the wordline transistors the *access* transistors (NA/NA'), and the inverter NMOS transistors the *driver* transistors (ND/ND'). It only has a single wordline (WL) for both read and write operations and uses a complementary bitline pair (BL/nBL) for both read and write operations instead of two separate bitlines. In the following paragraphs, the use of these lines in the three operation modes is explained.

Figure 2.7: 6T static memory cell schematic.

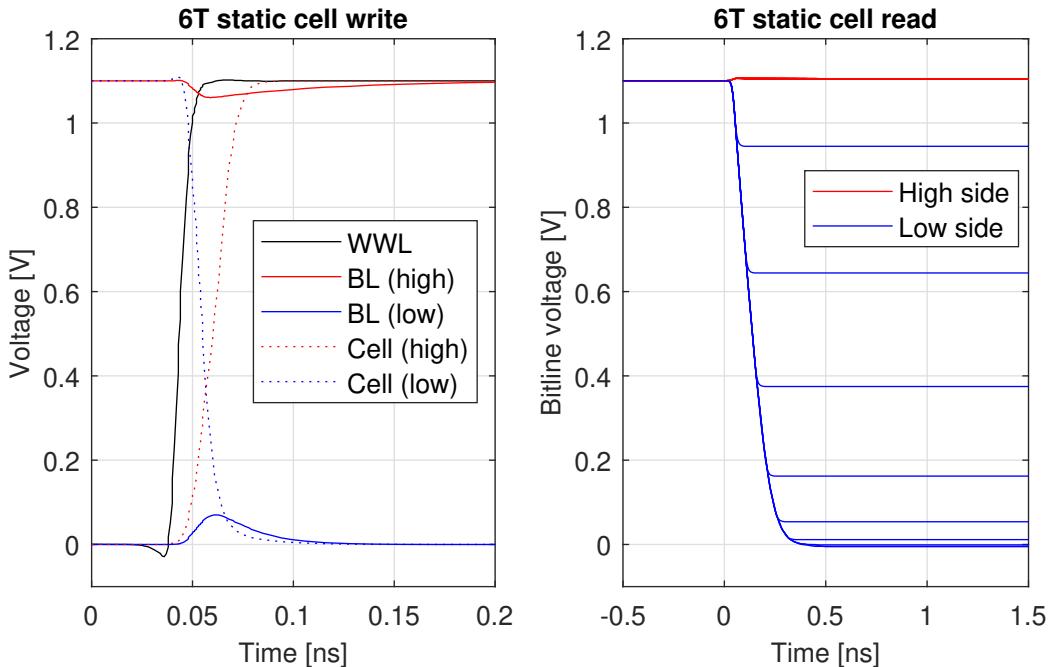

**Write** During a write operation, the WL is high and the BL/nBL are driven with the complementary data to be stored. This causes the internal cell nodes to follow the bitlines through the access transistors and the cross-coupled inverters to latch, thereby copying the state from the bitline pair to the cell.

**Read** During a read operation, the WL is also high but the BL/nBL are not driven. Instead, they are precharged to the supply voltage and left floating during the read operation. The driver on the low side of the cell will pull down the connected bitline through the access transistor. Since the pull-down is

Figure 2.8: Example transfer curves for the left and right inverter and pass transistor of a 6T static cell design, obtained from a two-point Monte Carlo simulation.

done through an NMOS with maximum overdrive, one of the bitlines is discharged extremely fast. By comparing the two bitlines, the low side can be determined and therefore the state can be retrieved.

**Hold** In the hold mode, the WL is low. This isolates the inverter pair from the bitline pair which means that no interaction takes place, neither write nor read, and the state is held by the inverter pair.

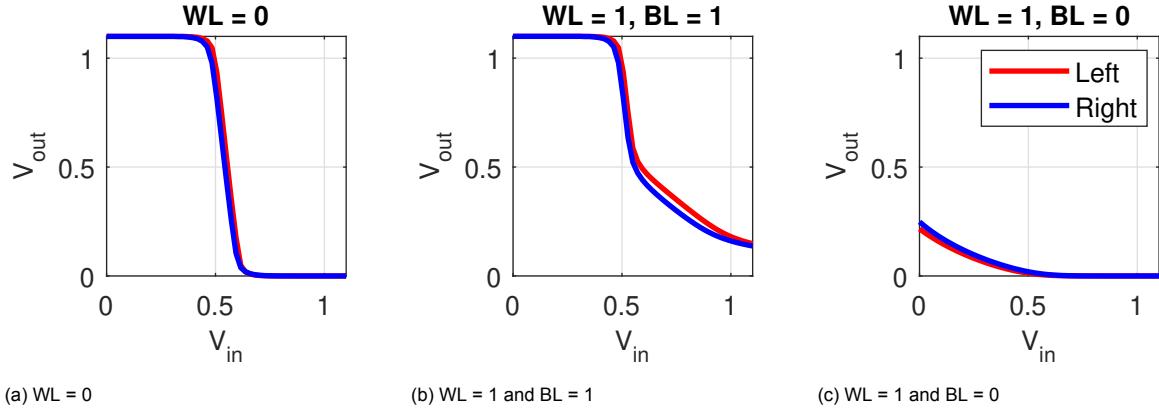

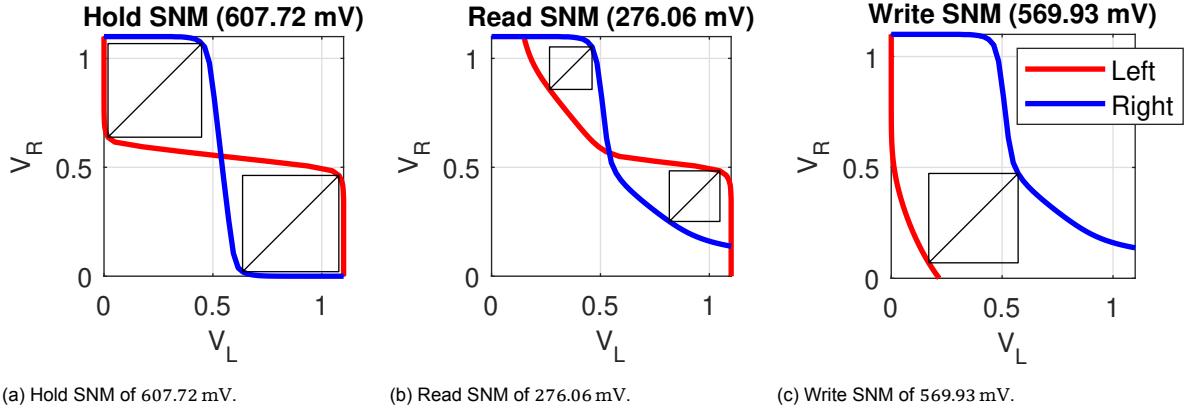

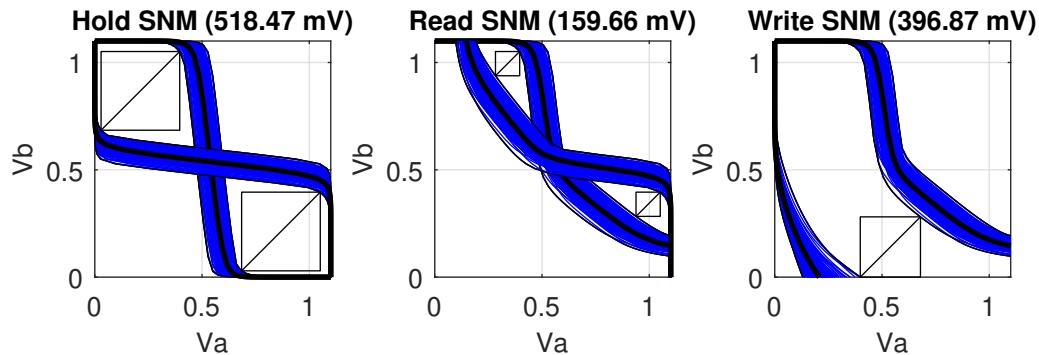

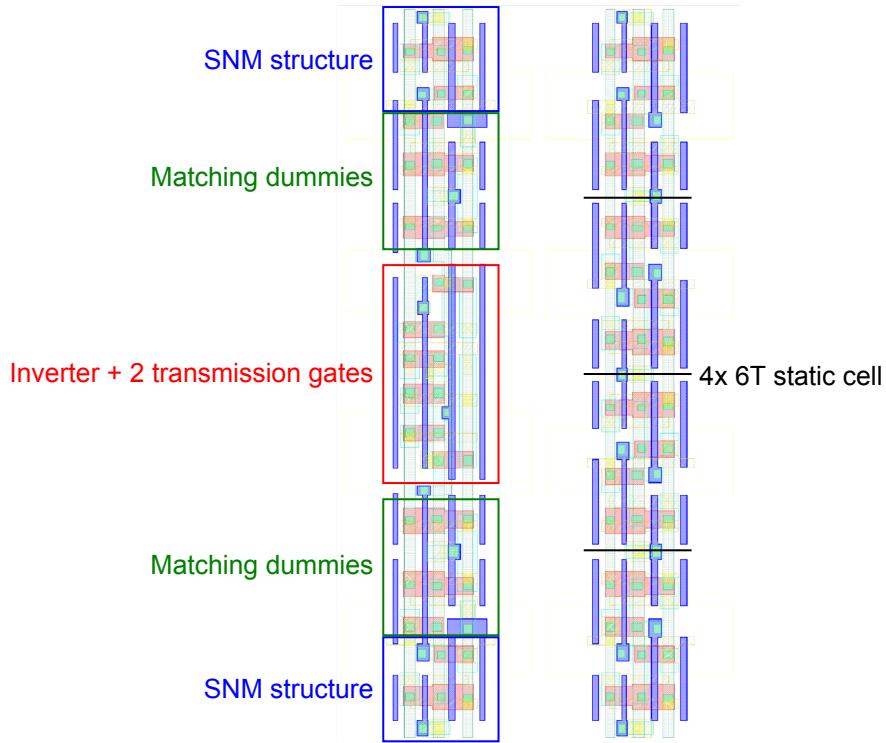

A tool often used in designing static memory cells is the *Static Noise Margin* (SNM) [21]. The SNM indicates the stability of the cell using two static (DC) transfer curves. These transfer curves are measured between the input and output of each inverter in three situations: with a low wordline (only the inverter), with a high wordline and a high bitline (inverter with a weak pull-up at the output), and with a high wordline and a low bitline (inverter with a strong pull-down at the output). This results in, for example, the transfer curves shown in fig. 2.8, obtained a two-point Monte Carlo simulation, for the left and right sections of the cell (PL/ND/NA and PL'/ND'/NA'). Ideally, they should be identical, but this is unlikely due to device mismatch.

The three transfer curves can be combined to find the SNM of the cell design in every operation mode. In the hold mode, the transfer curves from both sides with a low wordline are combined and plotted as shown in fig. 2.9a where the x- and y-axes indicate the two internal node voltages and the lines are the DC transfer curves of each inverter. The SNM is defined as the minimum of the two largest diagonal distances between these lines<sup>1</sup> and allows us to quantify the magnitude of a disturbance that is allowed until it would flip the cell. This margin should be positive and therefore requires that the lines cross, which means that there are two stable states.

During a read operation, both sides see a high wordline and initially a high bitline. These transfers can be combined and result in fig. 2.9b. The read SNM is again defined as the minimum of the largest differences between the curves and should be positive. This again means that two stable points are required, close to the two stable points in the hold mode. This ensures that a read operation does not disturb the state of the cell.

Similarly, in case of a write operation, one side sees a high wordline and low bitline, while the other side sees a high wordline and high bitline. A combination of these transfer curves is shown in fig. 2.9c. In this case, the smallest distance between the two curves should be maximised and the lines must not cross. As a result, there is only one stable point, which means that the cell can be forced into the desired state. For the shown example, BL is pulled low and nBL is pulled high such that the only stable state is the point where  $V_L$  is low and  $V_R$  is high. By flipping the high and low bitline sides, the figure should appear to mirror along the  $x = y$  axis, and the single stable state must be on the other side of the graph where  $V_L$  is high and  $V_R$  is low. For this specific example, this gives a slightly larger margin and is therefore not shown.

<sup>1</sup>The side length of the square is sometimes used instead of the diagonal, resulting in a  $\frac{\sqrt{2}}{2}$  scaling factor.

(a) Hold SNM of 607.72 mV. (b) Read SNM of 276.06 mV. (c) Write SNM of 569.93 mV.

Figure 2.9: SNMs for the example transfer curves shown in fig. 2.8 where  $V_L$  and  $V_R$  indicate the left and right node voltages of the cell, respectively.

## 2.2. Quantum computing

Quantum computing promises to solve certain problems in various fields that are intractable by classical computers using quantum algorithms [1]. A quantum computer is envisioned to be a heterogeneous system with a classical processor which loads quantum programs onto a quantum processor [22]. This is similar to the use of a modern general-purpose GPU. The quantum processor consists of a quantum device with qubits and a classical controller that performs the operations and readout on the quantum device by applying voltage and current waveforms. The quantum device and quantum computing in general are not the focus of this thesis and will therefore not be explained further. Instead, the focus is on the classical controller and the use cases for digital memories in them.

In this section, the use of digital memories in the classical controller for quantum computing is covered. Some proposed controllers are mentioned, their use of digital memory is listed and qualitative requirements for the memories are derived.

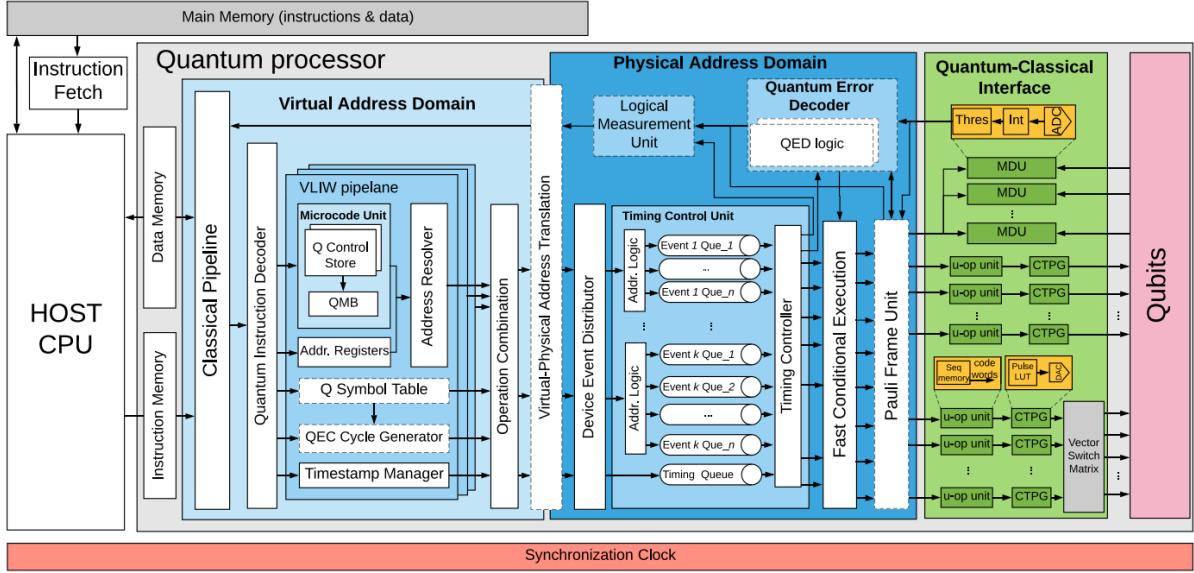

### 2.2.1. Classical controller architectures

Several classical controller architectures have been proposed for different qubit technologies and with various complexity [22]–[26]. The goal of these controllers is to provide an interface between software describing (mixed classical-)quantum algorithms and the quantum hardware. An example of such an architecture is shown in fig. 2.10. It consists of a classical pipeline for the classical instructions, which is used to perform computations with classical registers and control the program flow, and a quantum pipeline. The quantum pipeline is used to decode the quantum instructions, ensure that the timing of the instructions is correct, and apply the analog waveforms to the quantum device. The quantum pipeline can also perform readout of qubits on the quantum device and use the readout results to perform conditional quantum operations or return them to the classical pipeline.

### 2.2.2. Memory applications

Several memory applications can be found in the quantum processor part of the FT-QuMA architecture shown in the grey box in fig. 2.10. From left to right, the following memory applications are encountered:

- instruction and data memory,

- microcode control store,

- address registers,

- Q symbol table,

- logical measurement unit,

- timing control event queues,

- memory for the quantum error decoder (e.g. neural network [27], [28]),

- sequence memory,

Figure 2.10: Architecture of the FT-QuMA controller architecture from [22, fig. 4].

- pulse lookup table (LUT).

A more detailed example of the memory use in the quantum-classical interface is shown in [29]. It uses three memories, roughly equivalent to an instruction memory that only stores the quantum instructions, a sequence memory, and a pulse LUT.

For each of the memories, some details about how they are operated can be derived. For example, the microcode control store, sequence memory, and pulse LUT are written at most once per program and read-only at various speeds during execution. While the microcode control store only needs to retrieve data once per instruction, pulse LUTs may require output data rates of  $90 \text{ Gbit s}^{-1}$  [29]. On the contrary, the timing control event queues will have an equal number of write and read operations. The remaining memories are both read and written during operation, but typically read more than written. Finally, the sizes may also vary significantly, since a sequence memory may need only a handful of words while the instruction memory may need to store programs of significant size.

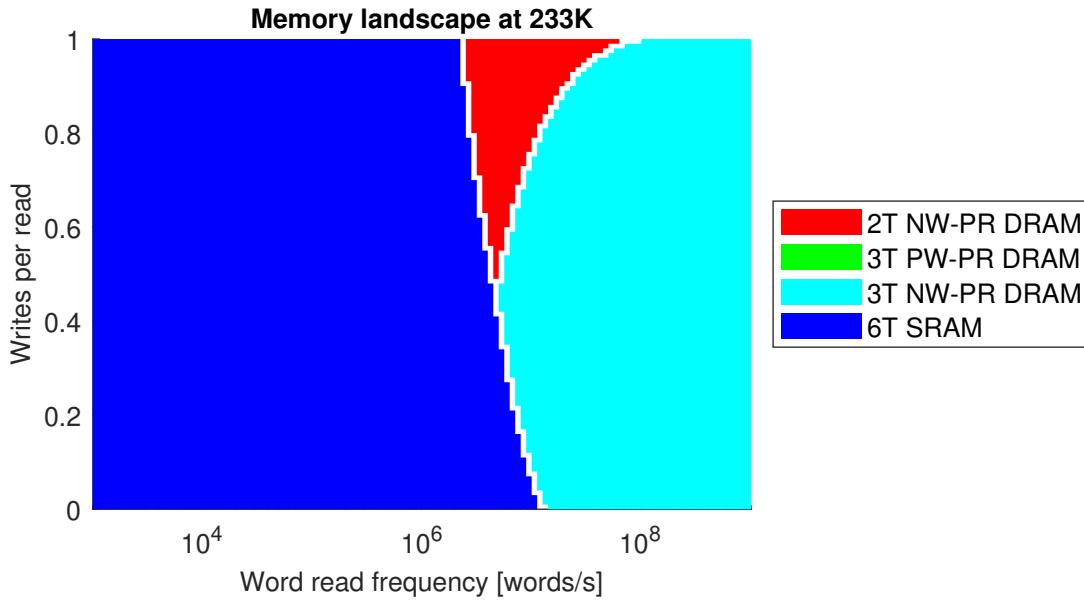

The different use cases determine what memory type is most efficient at that position. A memory that is rarely used will benefit from a design that needs very little standby power, while a frequently used memory with mostly read operations requires a design with a low read operation energy and a high bandwidth. This trade-off is investigated in more detail in chapter 3.

## 2.3. Cryogenic CMOS

To improve scalability, the classical controller should be located physically close to the qubits. Since the qubits require cryogenic operating temperatures, these control electronics should also be located at cryogenic temperatures [7], [8]. The qubits currently need to be cooled to temperatures of several mK, so dilution refrigerators are typically used. Since their cooling power is severely limited at these temperatures, the electronics are placed at a higher temperature plate around 4.2 K. This also allows for testing of the electronics using a dipstick into liquid helium at 4.2 K instead of using a dilution refrigerator, which is much faster and cheaper. In either case, the delay, losses, and load of the long cables needed to get out of the fridge or dewar to room temperature to connect to equipment have to be taken into account when designing the hardware.

In this section, several effects of the temperature on the technology are summarised. This is followed by an overview of the state-of-the-art of digital memories at cryogenic temperatures and the observed effects of the cryogenic environment on them.

### 2.3.1. Effects on technology

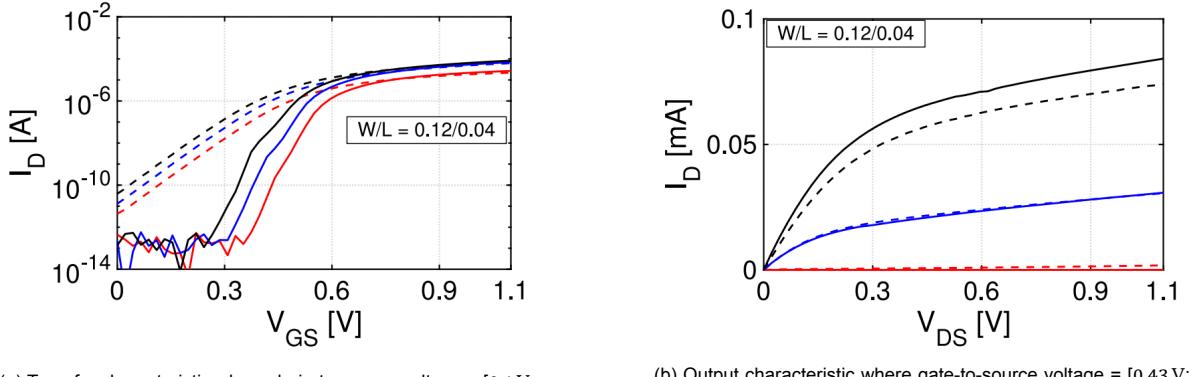

The effects of cryogenic temperatures on various CMOS technologies have been shown in literature [11], [30]–[34]. A typical MOSFET transfer characteristic is shown in fig. 2.11 at both 300 K and 4.2 K.

(a) Transfer characteristic where drain-to-source voltage = [0.1 V; 0.6 V; 1.1 V] [30, fig. 6c].

(b) Output characteristic where gate-to-source voltage = [0.43 V; 0.76 V; 1.1 V] [30, fig. 7c].

Figure 2.11: Measured transfer and output characteristics of thin-oxide NMOS in 40 nm CMOS with  $W/L = 120 \text{ nm}/40 \text{ nm}$  from [30]. Solid line: 4 K; dashed line: 300 K.

The main changes are as follows (exact values depend heavily on the technology and transistor sizing):

- The absolute threshold voltage of the devices increases roughly 100 mV to 200 mV due to scaling of the Fermi-Dirac distribution [35].

- The subthreshold slope becomes much steeper and decreases by roughly  $60 \text{ mV dec}^{-1}$ .

- The carrier mobility increases by approximately a factor 2 due to a reduction of phonon scattering [36].

Additional effects that are not visible in fig. 2.11 but reported in literature are:

- The capacitance and leakage of the active-region-bulk junction diode decrease due to an increased depletion region width due to carrier freeze-out and therefore an increased barrier voltage [37].

- The mismatch between matched pair devices increases [33].

- The resistance of the metal interconnect decreases by 20 % to 50 % [38]–[41].

- The resistance of the substrate increases due to freeze-out and causes a current kink and hysteresis in larger technology nodes ( $\leq 0.35 \mu\text{m}$ ) [30]. The current kink is not present in smaller technology nodes, but the increased substrate resistance may increase the latch-up risk [42].

- The channel noise decreases by a factor 10 due to the reduction in shot noise [38].

Combining some of the aforementioned changes results in the following functional differences. First of all, the leakage in the cutoff (subthreshold) region is significantly reduced both due to an increase in the threshold voltage and the steeper subthreshold slope. Second, the effect of the increase in threshold voltage on the output current at large overdrives is cancelled by the increase in carrier mobility, resulting in faster digital logic [30], [43]–[45].

### 2.3.2. Cryogenic digital memories

Digital memories at cryogenic temperatures have been topic of investigation in literature since 1979 [46]. There have mainly been two temperatures of interest, namely 77 K and 4.2 K. For speeding up regular computing, for example in data centres, 77 K is mainly of interest since it can be reached using liquid nitrogen which is cheap and easy to use. For use in lower temperature systems, such as quantum computing or superconducting computing, temperatures around 77 K are still used [47], but also 4.2 K is used since it can be reached using liquid helium [48]–[50].

In the remainder of this section, the changes in dynamic and static memories that have been reported in literature will be covered.

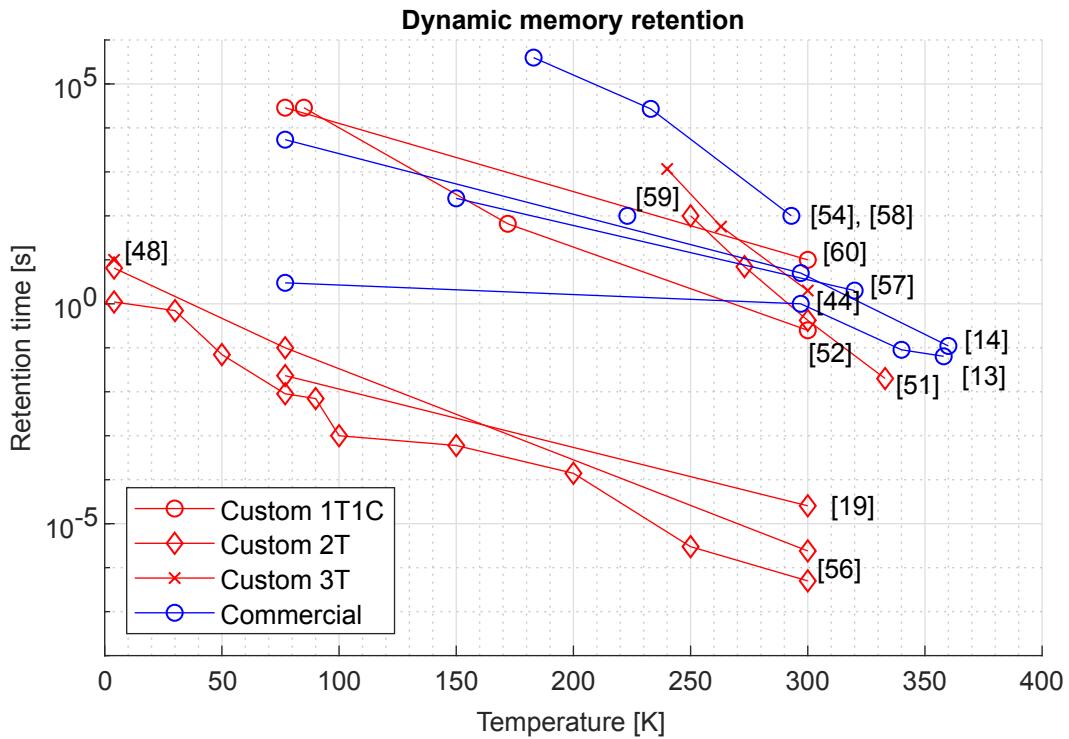

Figure 2.12: Retention time as function of temperature reported in literature. The red lines indicate various custom cell designs, while the blue lines indicate commercial DRAM products (all 1T1C).

### Dynamic memories

Literature focusing on dynamic memories at cryogenic temperatures can be split into two groups: design and characterisation of a custom memory, and the characterisation of commercial DRAM sticks. Due to the limited data retention time of dynamic memories and the associated power consumption due to refresh operations, the focus has mainly been on determining the retention time of the dynamic cells.

Due to the reduced leakage, the retention time of dynamic cells increases significantly. Several works report long to near-infinite retention times and therefore a potential refresh rate of zero at 77 K [44], [46], [51], [52] and therefore at 4.2 K [50], [53], which could save in area as refresh circuitry is no longer needed. This seems to mostly be the case for large technology nodes at 0.35  $\mu$ m or above, but the leakage at smaller nodes (0.18  $\mu$ m or smaller) can no longer be ignored [48]. Failure modes with low temperature dependence (low activation energy) such as tunnelling have been observed several times [13], [54], [55] and result in modern technologies in retention times in the order of several s [56]. Additionally, the effect of interference and disturb effects does not change and will require regular refreshes in order to protect the data [14], [57].

An overview of the retention times measured in literature can be seen in fig. 2.12. Due to the different ways retention time can be measured and the various technologies and cell types used, comparisons between different lines are not valid. However, a clear increase in retention time from 300 K to 4.2 K of roughly  $10^6$  can be seen, and most of the lines show approximately the same slope.

Apart from the increased retention time, an increase in speed has also been reported for both commercial DRAMs [61] and custom memories [56], [60], [62]. The access time decreases significantly for the unclocked memories (roughly halves), while the frequency of the clocked memories can be increased by 25 % to 30 %.

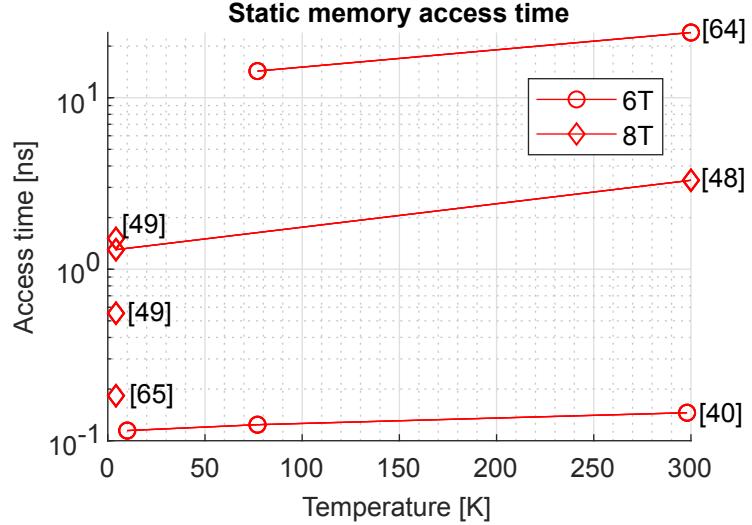

### Static memories

For static memories, the focus has mainly been on the increase in speed and static noise margins. An overview of the access time for static memory designs reported in literature is shown in fig. 2.13, with access time reductions between 20 % and 60 %. Static noise margins have been reported to

Figure 2.13: Static memory access time as function of the temperature reported in literature.

increase for low supply voltages due to the steeper subthreshold slope with threshold engineering [39] and by using write assist techniques [63]. Note however, that an SNM only shows static behaviour and that cells operating close to, or below, the threshold voltage may become very slow due to the steep subthreshold slope and increased mismatch.

# 3

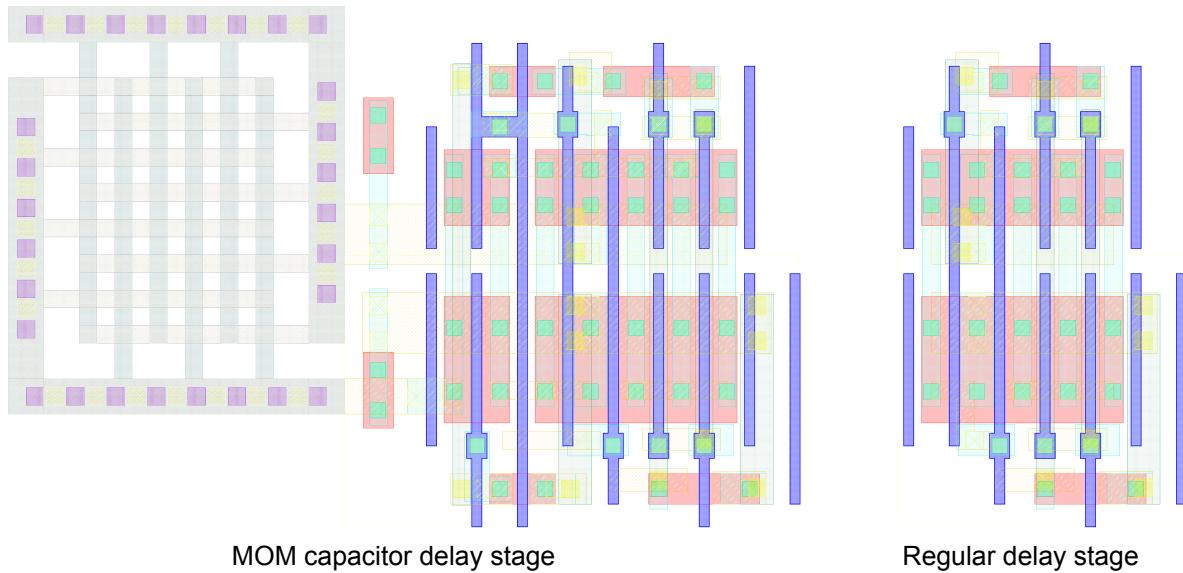

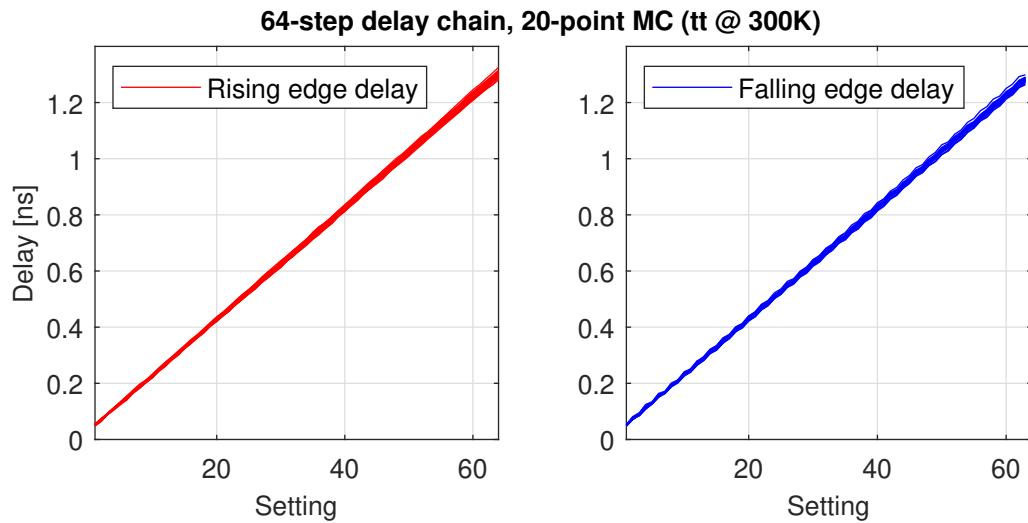

## Modelling

In this chapter, we will discuss the development of a model used to compare the performance and power consumption of the four memory cell designs at 4.2 K over a range of applications. Due to the lack of device models valid at this temperature, a memory model is first derived based on simulations at  $-40^{\circ}\text{C}$  (233 K) using mostly standard-threshold BSIM device models. At this temperature, some low-temperature effects such as reduced leakage are already visible. The resulting model is extended to 4.2 K by modifying it according to known cryogenic-CMOS effects and expectations based on previous work.

This chapter is structured as follows. We will first discuss how the memory application space is defined in section 3.1. In section 3.2, we will define the memory metrics of interest and show how they can be determined from simulation data by using the 2T NW-PR cell design as an example. The alternative cell designs will be treated in section 3.3 and the resulting memory metrics will be compared. In section 3.4 we will adapt the developed model to predict memory performance at 4.2 K and see the effects on the optimal memory design for various applications. Finally, we will reflect on the model, identify limitations, and propose improvements in section 3.5 and conclude the chapter in section 3.6.

### 3.1. Applications

In this section, we will investigate what is meant with a memory application and define an application space over which the memory designs will be evaluated.

A set of memory application requirements tells us how we want to use a memory and what the restrictions on the design are. This includes many aspects, leading to a huge design space. Some of these aspects can be derived from how we intend to use the memory and will largely determine the architecture. This includes, for example, the data access pattern (random or sequential), desired throughput, size of the array, size of a word/row, maximum latency, average read/write frequency, error tolerance, etc. Additionally, there are some aspects that limit certain metrics of a memory design, such as the area and power consumption. For each application, a different design is possible using architectural techniques. One of these is banking, where we access multiple arrays at the same time to increase the throughput, especially for sequential access patterns. The resulting design space is too large and specific for easy comparison.

Since our focus lies on memory cell design, we will use only a single architecture design. To keep the design simple, we will consider a single memory bank of 1 Kibit (1024 bit) with 32 words of 32 bit each, which is equal to 32 rows and 32 columns. Additionally, we will assume a random access pattern due to its versatility. This allows us to compare the performance of the memories based on the choice of cells without taking architectural differences into account. This also means that the possible memory application requirements space shrinks significantly since several requirements are now fixed or directly dependent on each other. For example, the throughput is now inversely proportional to the latency since the number of banks is fixed.

After reducing the application and design spaces, we are left with six application aspects. Two of these directly relate to how the memory is used, namely the *average read and write frequency*. We will use these values to define an application space. The remaining four put restrictions on several memory

metrics. They will limit the allowed *area*, *latency*, *error rate*, and *power consumption* of the memories and can be used to pick the memory design that delivers the best trade-off.

### 3.1.1. Application space

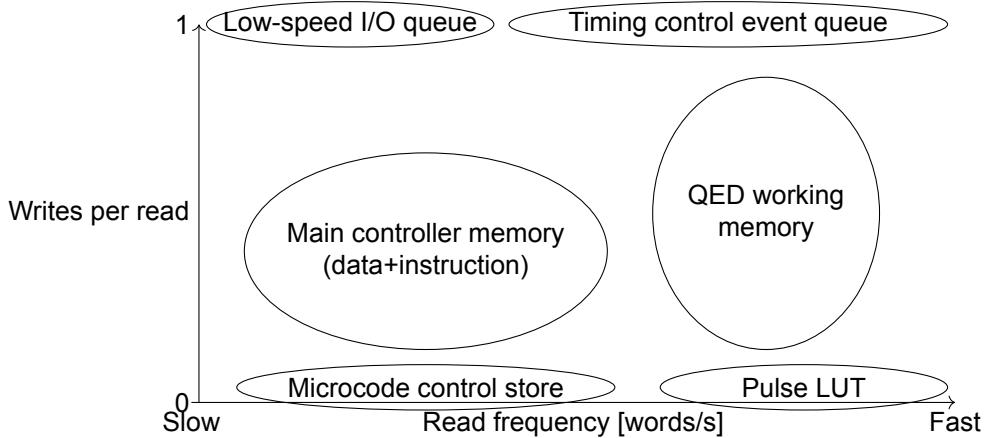

As explained before, the application space for this model has been reduced to only the frequency of read and write operations. Since the architecture of the different memories is the same, the application can only determine how we use it. Using the average number of read and write operations per second thus allows us to describe many different applications.

We can limit one dimension of the application space by replacing the write frequency with the average number of write operations per read operation. Since the read and write frequencies can differ significantly, the application space stays large. Note however, that the average write frequency is usually lower than the average read frequency<sup>1</sup>. We can therefore define the application space using an average read frequency, which can span many orders of magnitude, and a ratio of write operations per read operation, which is limited between 0 and 1.

The defined application space can be used to classify the applications mentioned in section 2.2.2 as shown in fig. 3.1. For example, a queue, such as the timing control event queues, will have a write/read operation ratio of 1, while a read-only memory, such as a LUT, has a write/read operation ratio of 0. Finally, working memory for a processor or controller will have a write/read operation ratio between 0 and 1, but exact values depend heavily on the program. The application of a memory then also defines whether it can be slow or needs to be fast. For example, a LUT storing bias voltages that need to be refreshed at low rates can be slow [66], while a pulse LUT for an arbitrary waveform generator (AWG) needs to be fast. The throughput of various memories in a hierarchical memory organisation can also vary several orders of magnitude [29].

Figure 3.1: Memory applications in the application space defined by the read frequency and the average number of write operations per read operation.

## 3.2. Memory metrics

In the previous section, we have seen how an application space was derived from the memory usage requirements. This leaves us with the restrictions on four remaining memory metrics: the area, latency, bit error rate, and power consumption. In this section, we will show how we can compute these metrics for the different memory designs and how they are related.

We will go through the memory metrics in the following order by using the 2T NW-PR cell type as an example. The schematic and operational details of this cell design can be found in section 2.1.2. We will first look at the area of the design, followed by its latency. Next, we will see how we can determine the Bit Error Rate (BER) and how it is related to the latency. Finally, we can calculate the power consumption of the design over the application space and see how all the metrics are related and their trade-offs.

<sup>1</sup>Writing data that is never read is a waste of resources, but may happen in certain applications such as caches.

### 3.2.1. Area

Of all the memory metrics, the area is the easiest to calculate. Nevertheless, it is important to consider since memories can get extremely large and can be responsible for more than half of the area consumption of a processor [67].

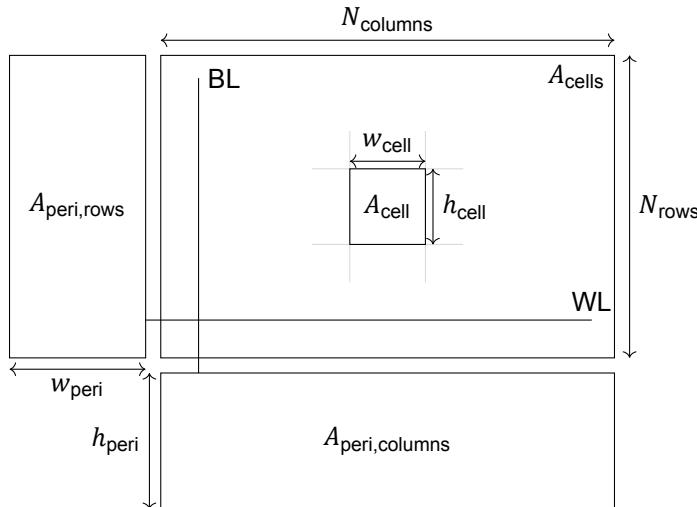

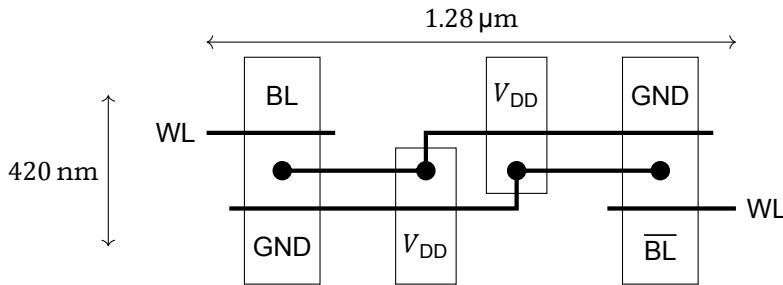

To calculate the total area, we can add the area of the cells and the peripherals. The total area of the cells can be estimated using eq. (3.1) where  $h_{\text{cell}}$  and  $w_{\text{cell}}$  indicate the height and width of the cell, while  $N_{\text{cells}}$ ,  $N_{\text{rows}}$ , and  $N_{\text{columns}}$  indicate the total number of cells, rows, and columns, respectively.

$$A_{\text{cells}} = N_{\text{cells}} \times A_{\text{cell}} = (N_{\text{rows}} \times N_{\text{columns}}) \times (h_{\text{cell}} \times w_{\text{cell}}) \quad (3.1)$$

The area of the peripherals can be estimated using eq. (3.2) where  $w_{\text{peri}}$  and  $h_{\text{peri}}$  indicate the width and height of the peripheral overhead. The row peripherals include the row decoders, while the column peripherals include bitline drivers, sense amplifiers, and data latches.

$$\begin{aligned} A_{\text{peri,rows}} &= N_{\text{rows}} \times h_{\text{cell}} \times w_{\text{peri}} \\ A_{\text{peri,columns}} &= N_{\text{columns}} \times w_{\text{cell}} \times h_{\text{peri}} \\ A_{\text{peri}} &= A_{\text{peri,rows}} + A_{\text{peri,columns}} \end{aligned} \quad (3.2)$$

A visual representation of the aforementioned areas can be seen in fig. 3.2. Note that this is a rough estimation of the area, taking only the cells, row decoders, and bitline stacks into account. Additional area will be required for the timing-and-coordination circuits and dummy structures to ensure cell matching.

Figure 3.2: Simplified memory layout used for area estimation.

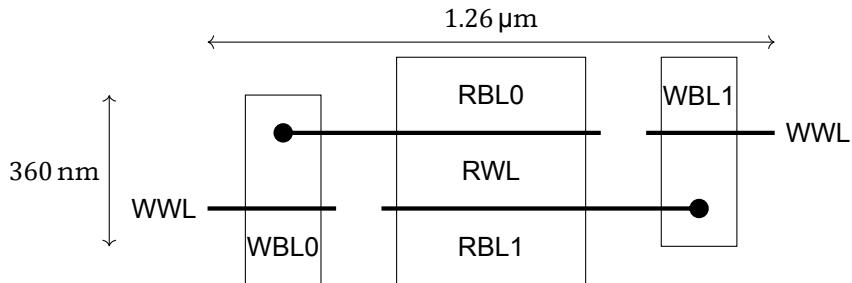

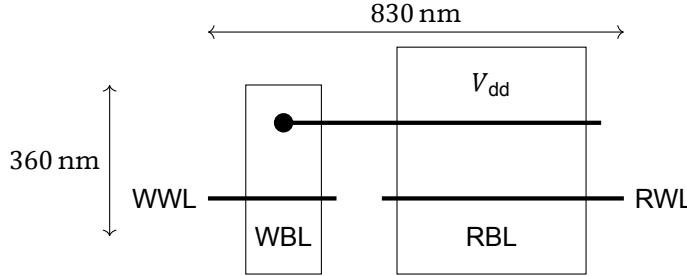

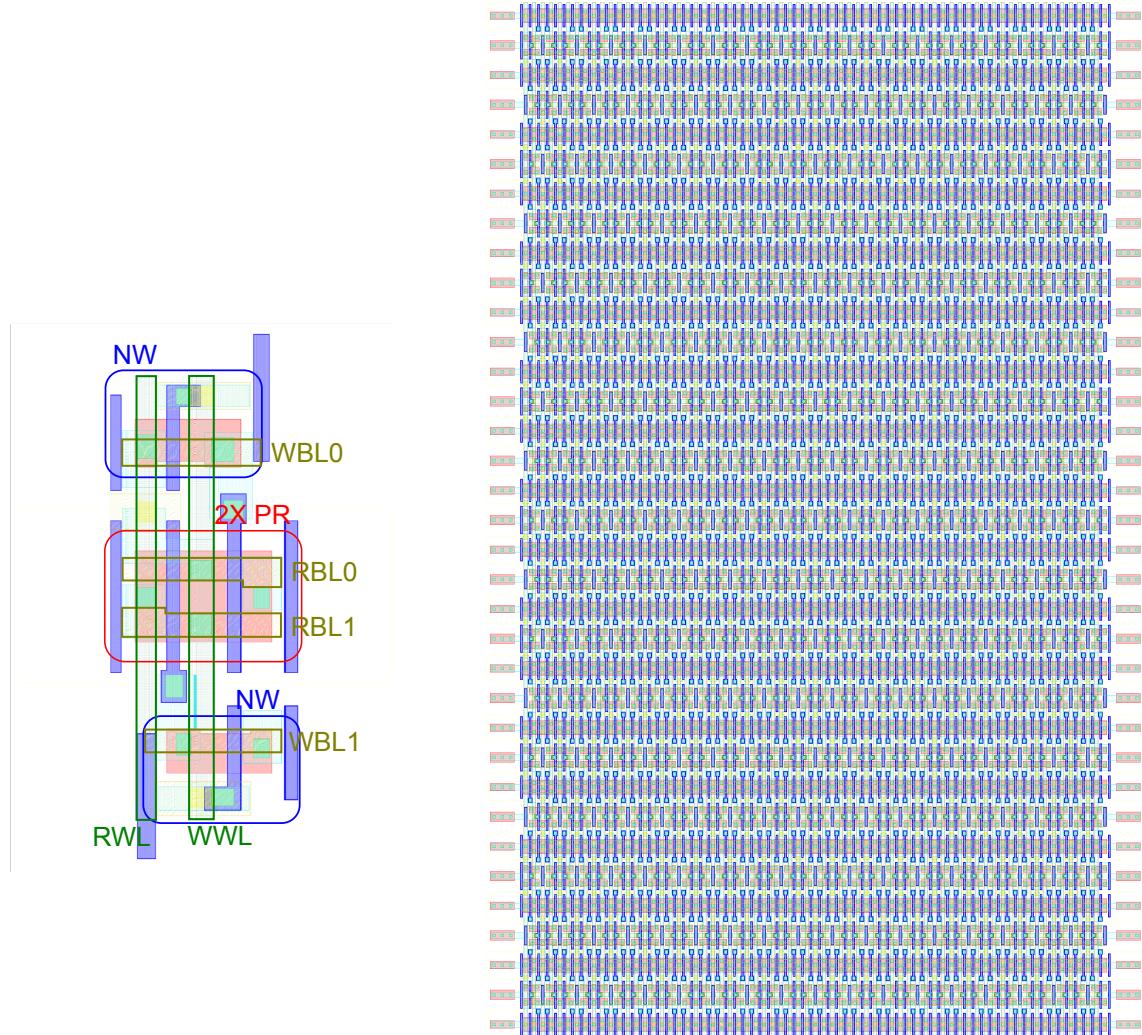

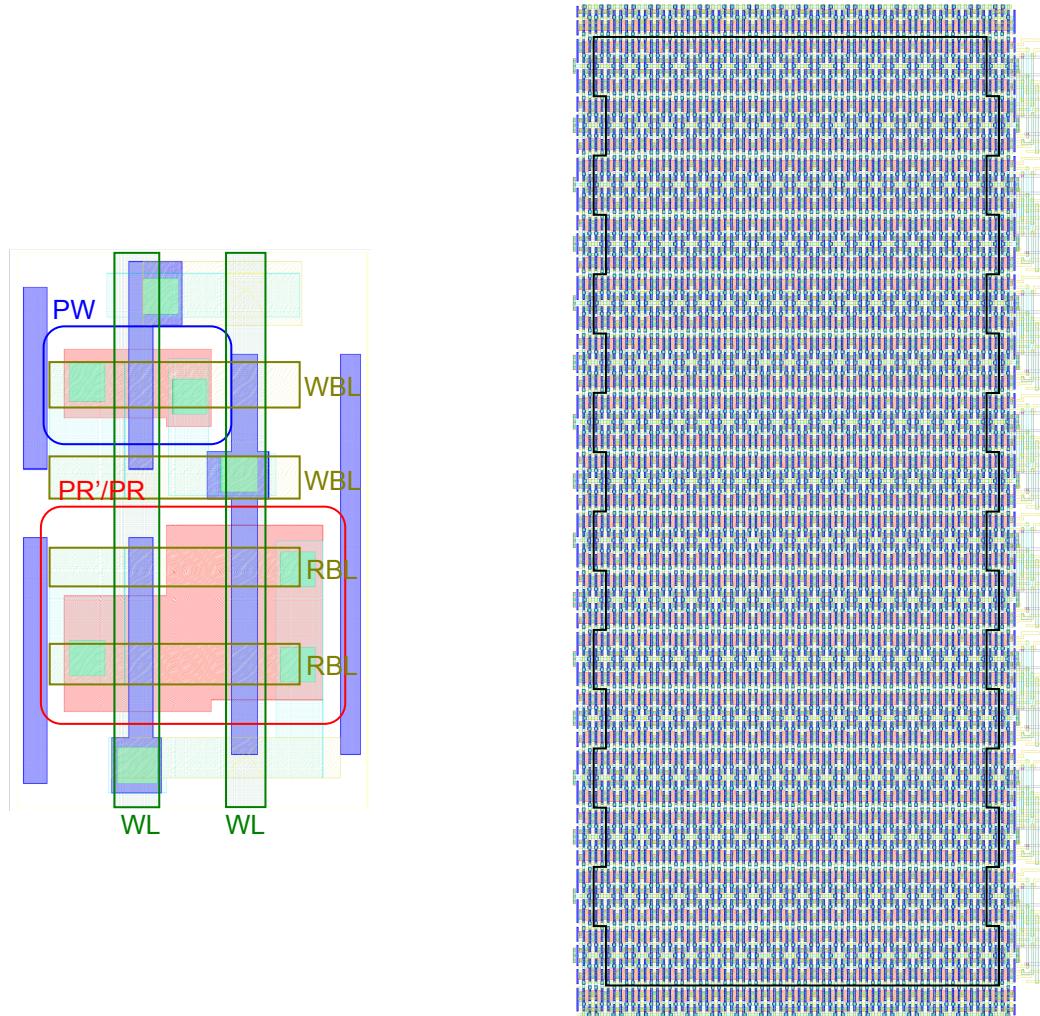

For the 2T NW-PR memory cell this leads to the following area estimation. Based on a preliminary layout schematically shown in fig. 3.3, we can estimate the dimensions in fig. 3.2, as reported in table 3.1. This leads to a cell area of  $0.2268 \mu\text{m}^2$  and a total area for the array of  $466 \mu\text{m}^2$  (for  $N_{\text{columns}} = 32$  and  $N_{\text{rows}} = 32$ ).

Table 3.1: 2T NW-PR array dimension estimations

| Dimension     | $w_{\text{cell}}$ | $h_{\text{cell}}$ | $w_{\text{peri}}$ | $h_{\text{peri}}$ |

|---------------|-------------------|-------------------|-------------------|-------------------|

| $\mu\text{m}$ | 0.63              | 0.36              | 8                 | 7                 |

Finally, it is instructive to observe some trends for the area metric. Increasing the total number of cells will linearly scale the total cell area, while scaling the peripheral area sublinear. This means that especially for larger arrays, the total cell area becomes the dominant area consumer. In the previously shown situation with 32 words of 32 bit, the cell area is only 41 % of the total area, but scaling the array to 64 words of 64 bit would result in a cell area of 59 % of the total area. It is therefore worthwhile to minimise the area of a single cell.

Figure 3.3: Simplified layout of a double 2T NW-PR cell design with the two write transistors (NW) on the outsides and the readout transistors (PR) stacked in the middle. These two cells share the same wordlines, but have different bitlines, which means that they are in the same row but different column. To obtain the area of a single cell, the width therefore has to be divided by 2.

### 3.2.2. Latency

The latency of a memory is defined as the time between the start of a memory operation and its completion. We will separately consider the write and read latency for write and read operations, respectively, in the remainder of this section. However, to simplify interaction with the memory, a single *combined memory operation latency* is defined as the largest of the two.

The duration of both operations is the result of the timing of the peripherals by the control circuits. It is therefore not an inherent property of the cell design itself, but the cell design must be taken into account to determine the optimal timing. This optimal timing is the result of a trade-off between the latency and other memory metrics, which is investigated in more detail in section 3.2.5.

#### Write latency

The write latency is mainly of interest for dynamic cells. The storage-node voltage of dynamic cells is written through a pass transistor. Depending on the type of pass transistor, one voltage level is passed strongly while another is passed weakly. For the 2T NW-PR cell, the N-type write pass transistor will strongly pass a low voltage (0 V) and weakly pass a high voltage (1.1 V). In the latter case, if the storage-node voltage starts at 0 V, the storage node will be initially charged quickly. However, as the storage-node voltage increases, the transistor current will decrease. This will lead to a slow settling towards a storage-node voltage of  $1.1 - V_{th}$ .

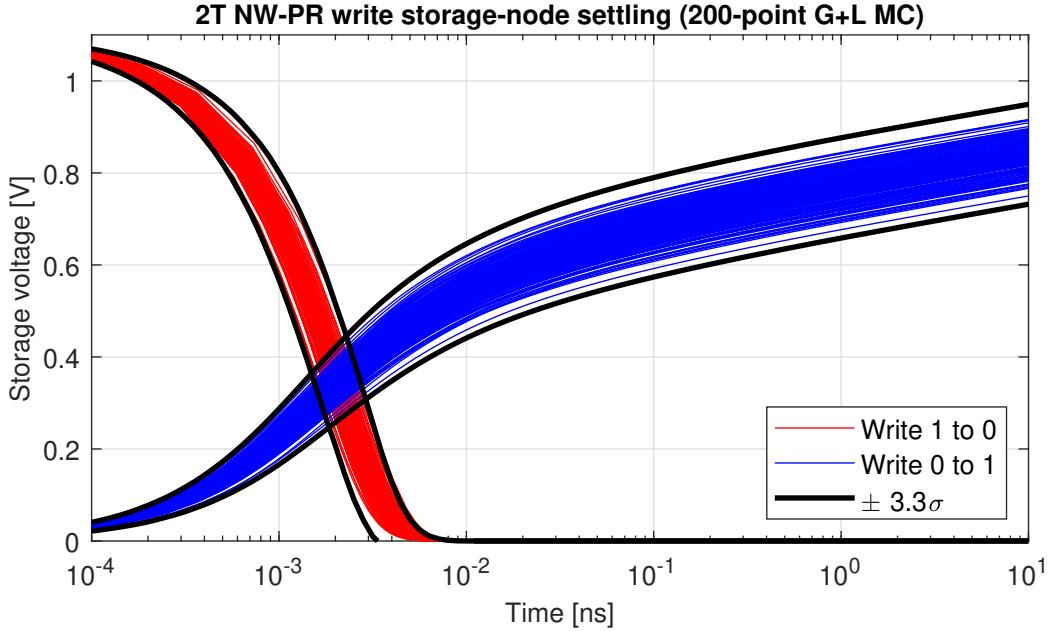

Figure 3.4 shows Monte Carlo simulation results of the settling of the storage-node voltage of a 2T NW-PR cell. The cell is initialised with 0 V or 1.1 V, the write bitline is connected to the opposite voltage, and the write wordline is pulled high. The red lines show settling of a strong write, while the blue lines show settling of a weak write. The black lines show the  $\pm 3.3\sigma$  spread, assuming a normal distribution at every time instance. The probability of being outside this range is  $\frac{1}{1024}$ , so one out of the 1024 cells is expected to lie outside this spread.

We can clearly see the difference between the strong and weak write. The strong state (red) is written completely within 10 ps. The weak state (blue) starts off as fast as the strong state, but quickly slows down due to the reducing transistor overdrive and ends up settling exponentially slower (note the logarithmic x-axis in fig. 3.4). Writing for longer will increase the difference in storage-node voltage between the two states and therefore lead to easier state detection when read. However, due to the slow settling the advantages quickly wear off. Therefore, setting the write duration equal to the read duration gives the best results as it gives the largest possible storage-node voltage difference without slowing down the combined operation latency.

For static cells, once a cell has flipped, writing longer does not give any advantage. This means that we have a strict lower bound for the duration of a write operation for a static cell to guarantee that it can be flipped, but going beyond it gives no advantage nor disadvantage as long as it does not slow down the combined operation latency.

For this model, we will fix the duration of a write instruction to 1 ns. This means that in all the simulations, we will perform write operations by opening the write pass gate (NW in fig. 2.4) for 1 ns. This is sufficient for a strong write as it is longer than 10 ps. For the weak write, it puts us around 80 mV into the settling region which starts around 100 ps at 700 mV. This will result in a total write operation latency that is slightly longer than 1 ns due to peripheral overhead. It is also similar to the read latency which we will look at next, which means that we get the longest possible write time without limiting the

Figure 3.4: 200-point Monte Carlo (global + local) simulation of the settling of the 2T NW-PR storage-node voltage during a write operation. Black lines indicate  $\pm 3.3\sigma$  ( $\frac{1}{1024}$ ) for every time instance of the two curve families.

combined operation latency.

#### Read latency

The required duration of a read operation depends on many factors. During a read operation a bitline is (dis)charged, the speed of which is determined by the cell strength and the total bitline capacitance. The read duration then determines the difference between the bitline voltages for the different cell states.

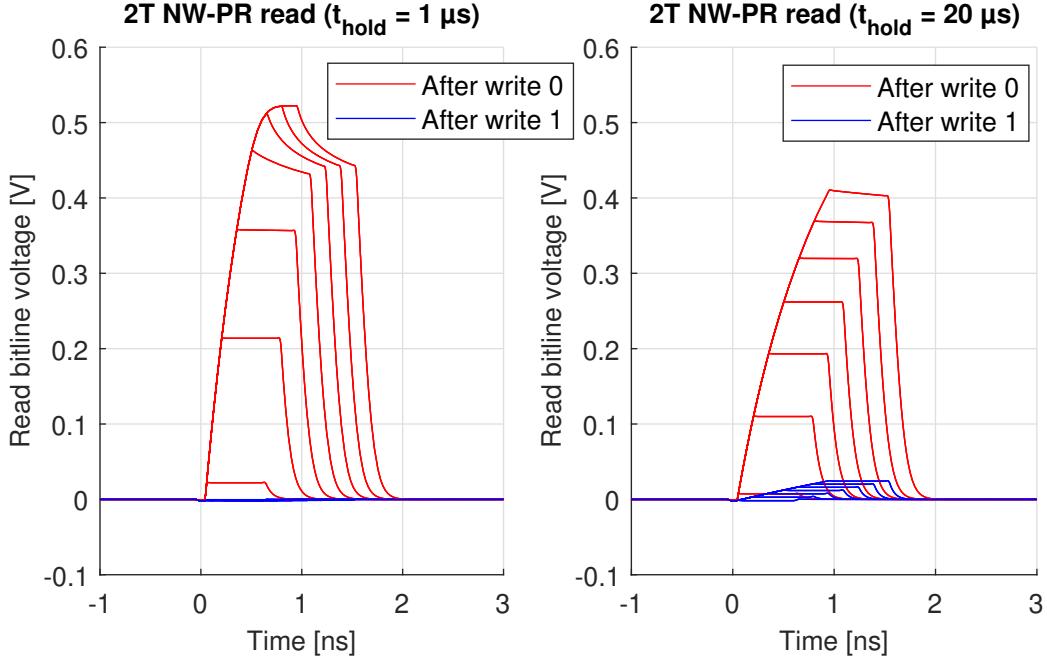

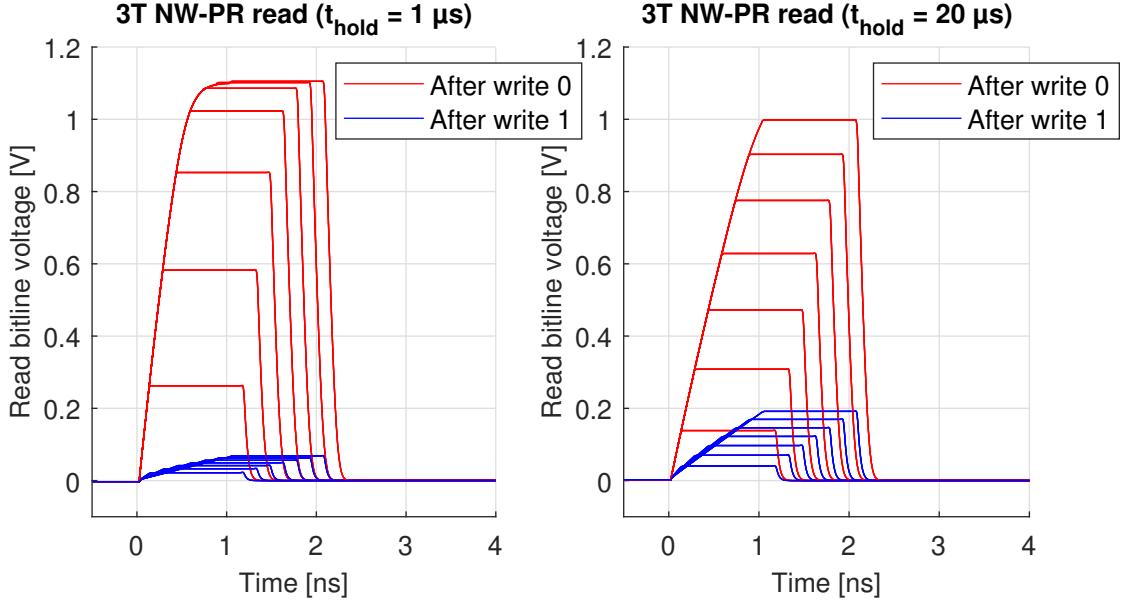

Figure 3.5 shows the bitline voltage for a 2T NW-PR cell during a read operation for various read durations from 100 ps to 1 ns. The shown process is as follows. First, the bitline is precharged to ground. Next, the read wordline is pulsed for 100 ps, 250 ps, 400 ps, 550 ps, 700 ps, 850 ps and 1000 ps. Finally, 500 ps after the falling edge of the read wordline, the bitlines are precharged to ground again. Reading for longer gives a larger bitline voltage difference between the two states, or 'bitline margin', since we follow the bitline charging trajectory for longer.

For dynamic cells, these bitline voltages not only depend on the read operation, but also on the time between successive writes and reads, or *hold time* ( $t_{\text{hold}}$ ). Between the write operation and the read operation, the storage-node voltage will increase or decrease due to leakage for the low or high writes, respectively. This will reduce the overdrive in case of a write-0, leading to a lower charging current. In case of a write-1, this eventually leads to inversion which increases the charging current. This can also be seen in the right plot of fig. 3.5, where the bitline is charged slower than in the left plot after a write-0. Additionally, the bitline is charged slowly after a write-1, which leads to a smaller bitline margin. However, the bitline margin is still increasing for an increasing read duration.

The left figure of fig. 3.5 shows the readout leakage that the 2T NW-PR cell design suffers from. Once the bitline voltage reaches approximately 0.52 V, there is a balance between the current supplied by the cell that is read and the leakage of other cells that have been written low. As soon as the read wordline is pulled down, the current from the cells that have been written low discharges the bitline again towards roughly 0.4 V.

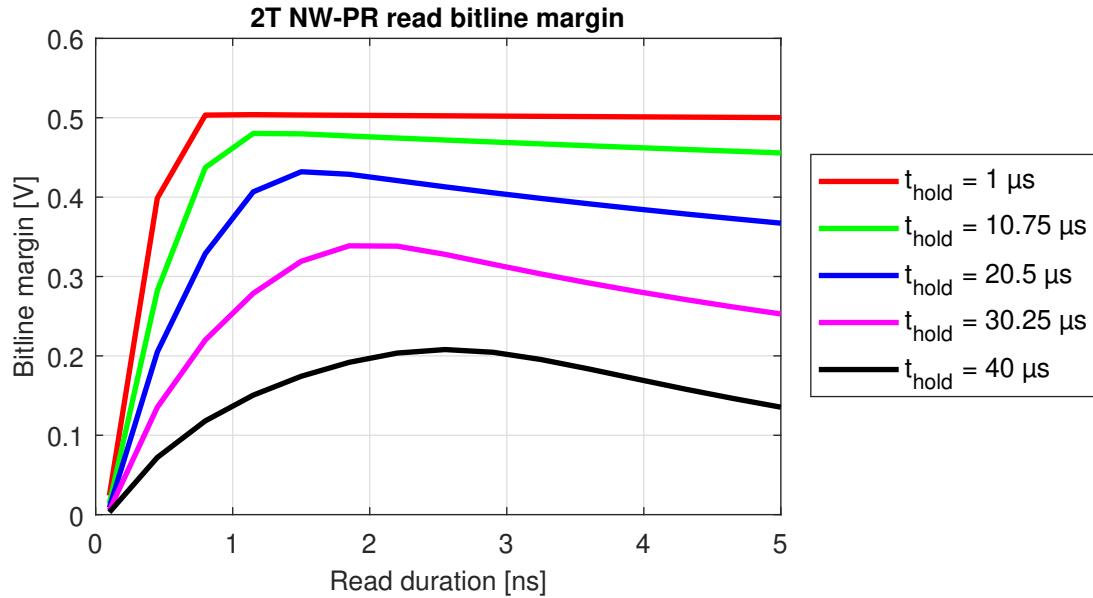

It may seem that reading longer will result in a better bitline margin, but this is not the case. In fig. 3.6, we can see that the maximum bitline margin is achieved for a read time of roughly 2.5 ns for a hold time of 40 μs. The initial increase in bitline margin is due to the bitline being charged faster in case of a write-0 than a write-1, as shown in fig. 3.5. However, once the bitline voltage for the write-0 starts to settle due to the readout leakage, the bitline voltage for the write-1 still increases, lowering the bitline margin again. This long hold time will however result in a relatively slow memory with a high read energy consumption for short hold times due to readout leakage. For example, for a hold time

Figure 3.5: 2T NW-PR read bitlines during a read operation with durations of 100 ps, 250 ps, 400 ps, 550 ps, 700 ps, 850 ps and 1000 ps. Left: read 1  $\mu$ s after write, right: read 20  $\mu$ s after write.

of 1  $\mu$ s, the leakage current with a maximum of almost 11  $\mu$ A starts to flow within 500 ps, resulting in an additional energy loss of over 22 fJ ( $> 10\%$  of the total read power, as calculated in section 3.2.4). In order to reduce this leakage, keep the latency low, and maintain sufficient bitline margin for various hold times, the read time is fixed to 1 ns.

Whatever the read time, the bitline margin of dynamic cells will collapse over time. This happens due to leakage, which brings the storage node voltages of the different states closer together. As a result, the (dis)charging current of the readout transistors for the different states get closer together. At a certain point in time, the two states can no longer be reliably distinguished. To determine when this happens, we need to take a look at the bit error rate.

### 3.2.3. BER

To determine when we need to refresh our memory, we need to know when the bit error probability of a read operation becomes too large. This is where the *Bit Error Rate* (BER) comes in. First, we will see how a noiseless yield can be computed. This is followed by a BER analysis to find the actual expected error rate including noise.

#### Noiseless yield

The *yield* metric will give use the probability of a good cell, where a good cell will always be read correctly within the refresh period in the absence of noise. To calculate this, we need mismatch information about the cells and sense amplifiers, and a reference against which the cell voltages are compared.

**Cell mismatch** To find mismatch information about the cell, Monte Carlo simulations of the read operation for various hold times are used. This will result in distributions of the bitline voltages for the two states over hold time. We should be able to determine, for a given hold time, the data state of the cell from the observed read bitline voltage.

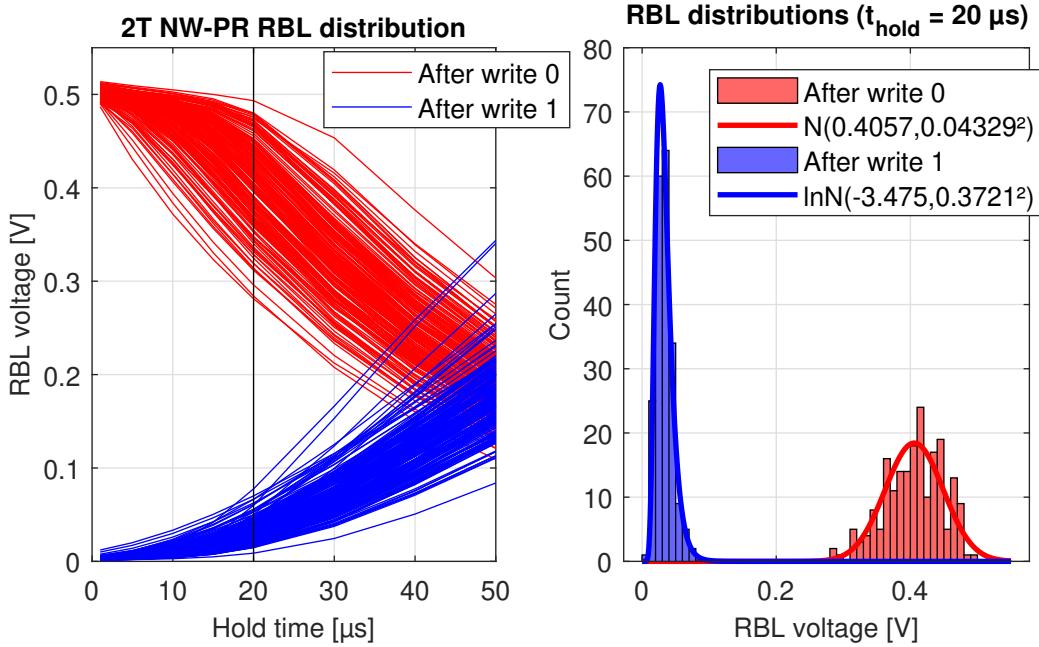

The left graph of fig. 3.7 shows the bitline curves for a 200 point Monte-Carlo simulation of the 2T NW-PR cell. If we take a vertical slice from this figure for a given hold time, we can fit the voltages to a distribution. The bitline voltages that belong to the 0-state best fit to a normal distribution, while the bitline voltages that belong the 1-state best fit to a log-normal distribution. This makes sense as the readout transistor is in strong inversion during a read of the 0-state, since the read wordline voltage is high while the storage-node voltage is low. This causes the readout current to be roughly proportional to

Figure 3.6: 2T NW-PR read bitline margin as a function of the read duration for various hold times.

the threshold and therefore the read bitline voltage mismatch to be proportional to the device mismatch. During a read of the 1-state, the readout transistor is in the subthreshold operating region, since both the read wordline voltage and the storage-node voltage are high. This causes the readout current to be exponentially dependent on the threshold and therefore the read bitline voltage mismatch to be exponentially proportional to the device mismatch. For example, at a hold time of 20  $\mu$ s, the bitline voltages follow the distributions shown in eq. (3.3) and in the right graph of fig. 3.7.

$$\begin{aligned} V_0 &\sim N(\mu, \sigma^2), \text{ where } \mu = 0.4057 \text{ and } \sigma = 0.04329 \\ V_1 &\sim \ln N(\mu, \sigma^2), \text{ where } \mu = -3.475 \text{ and } \sigma = 0.3721 \end{aligned} \quad (3.3)$$

**Sense amplifier mismatch** Mismatch information about the sense amplifier is harder to determine as it highly depends on the sense amplifier design. Based on simulations of a preliminary design, we find that the input-referred offset follows a normal distribution with zero mean and a standard deviation of roughly 16.5 mV. The exact value can always be adjusted based on the final design, so this value is assumed for all memories for now.

**Combining the statistics** For the yield, the probability that a random cell and sense amplifier with a specified reference voltage result in an incorrect read after a certain hold time is computed. The algorithm to do this is as follows:

1. *Obtain the distributions of the bitline levels at the given hold time from the cell mismatch information.* This is done by taking a vertical slice of the bitline graph and fitting the bitline voltages to a normal and log-normal distribution. An example of this is shown in fig. 3.7 with the 2T NW-PR cell for a hold time of 20  $\mu$ s.

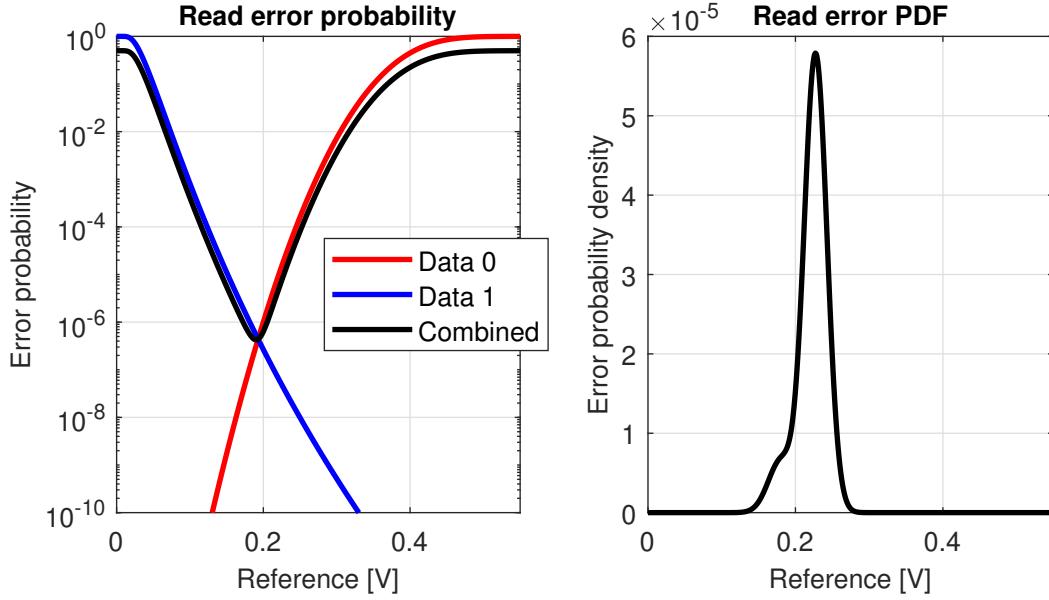

2. *Find the probability that a perfect decision against any reference is correct.* In this case, the bitline voltage distributions for the cell are assumed to be independent and any combination for the two states is assumed equally likely. The error probabilities for the two states from the distributions obtained in the first step is computed. Since the states are assumed to be equally likely, the combined error probability is given by the average error probability. This is shown in the left graph in fig. 3.8 for the example distributions from step 1 (eq. (3.3)).

3. *Multiply the perfect decision error probability density function with the reference probability density function.* The reference probability distribution follows a normal distribution with its mean

Figure 3.7: Left: 200-point Monte Carlo simulation (tt corner + local variation at 233 K) of the read bitline voltages for 2T NW-PR cells for various hold times. Right: distribution of read bitline voltages for a hold time of 20  $\mu$ s (black line in the left figure).

equal to the specified reference voltage and its standard deviation equal to the sense amplifier mismatch. For the example, a threshold voltage of 200 mV and the earlier determined sense amplifier mismatch of 16.5 mV are assumed. The resulting probability density function is shown in the right graph of fig. 3.8 and gives the combined probability of achieving a certain effective threshold voltage (applied threshold + sense amplifier offset) and that threshold leading to an incorrect read.

4. *Integrate the resulting probability density function to find the total probability of an incorrect read.* For the given example, this leads to a total read error probability of  $2.514 \times 10^{-6}$ . This means that, without noise, reading a random cell with a random sense amplifier and a reference voltage of 200 mV after 20  $\mu$ s has a probability of  $2.514 \times 10^{-6}$  of resulting in the wrong data, assuming equal write data probability.

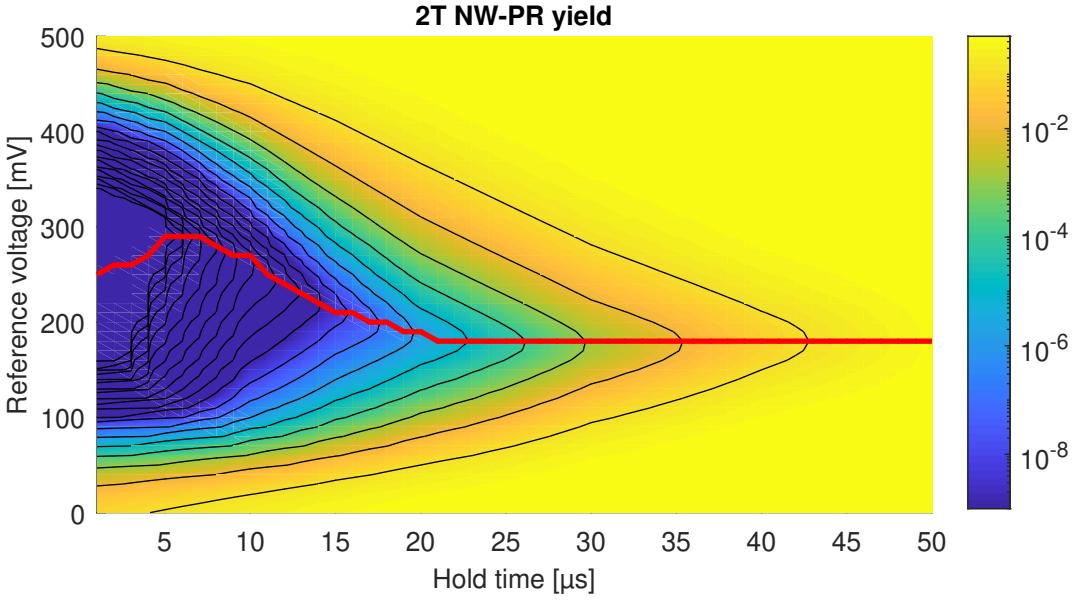

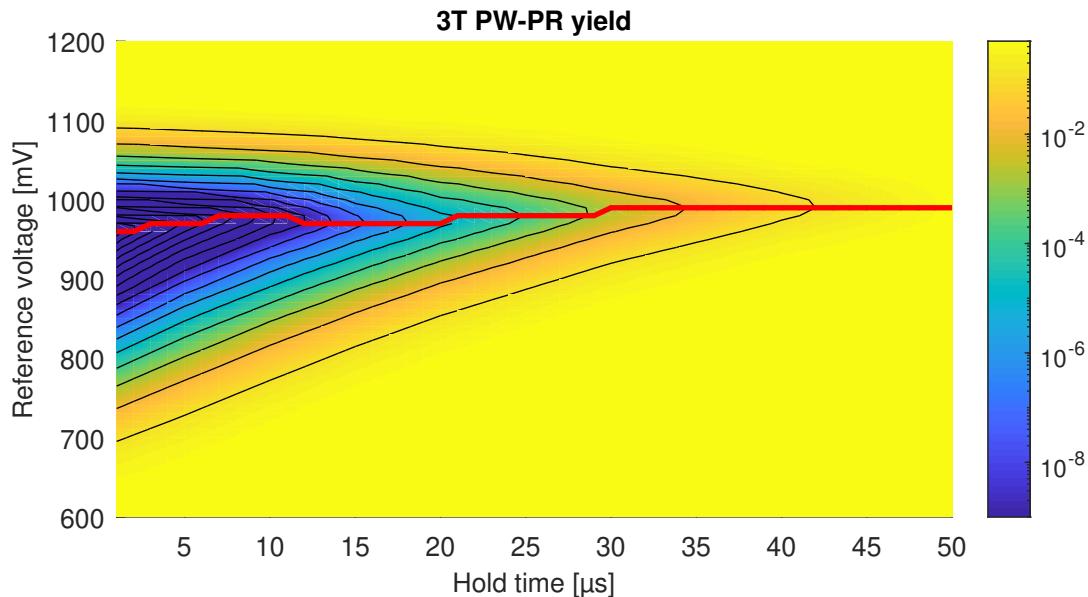

The previously described method to find the yield can now be applied for a range of hold times and reference voltages. The resulting values for each combination can be put into a graph, resulting in fig. 3.9, where the black lines indicate constant yield values equal to  $1 - 10^{-x}$  and the red line shows the reference voltage that gives the best yield for a given hold time. Given a desired yield, we can pick the optimal reference voltage that gives us the longest retention time. For example, if we pick a yield of  $1 - 10^{-6}$ , we find an optimal reference of roughly 190 mV (actually 186.8 mV) and a maximum hold time of 19.64  $\mu$ s. This means that the refresh rate must be 50.91 kHz to guarantee this yield for all read operations.

A yield of  $1 - 10^{-6}$  for 1 Kibit is plenty and the probability of getting a bad cell is very small, roughly one per 489 memories. However, some cells may be considered good cells in the absence of noise, but result in high error rates once noise is taken into account.

#### Noisy BER

To determine the BER including noise, a Monte Carlo simulation is used. In this simulation, a large number of memory cores are simulated with 1024 cells and 32 sense amplifiers, randomly selected from their respective distributions. For the cells, a random read bitline voltage for both data states is drawn from the distribution at a hold time of 20  $\mu$ s (eq. (3.3)), assuming the two distributions are independent. For the sense amplifiers, a threshold that includes a random input-referred offset is selected from a normal distribution around the chosen threshold of 190 mV with an input-referred offset standard deviation of 16.5 mV. For each cell and associated sense amplifier, the probability of an incorrect read

Figure 3.8: Left: probability of incorrect read of random cell with given reference voltage after a hold time of 20  $\mu$ s. Right: combined probability density of the effective reference level seen by a sense amplifier due to input-referred offset and that leading to an incorrect read with equal data probability.

decision is determined for both data states, including sense amplifier input-referred noise following a normal distribution with a standard deviation of 10 mV. In reality, the noise will be even smaller, in the order of 4 mV. However, 10 mV gives a reasonable idea of the cell BER distribution that can be expected and does not lead to numerical overflow<sup>2</sup>. Finally, the read error probabilities for both states are averaged, assuming equal data probability, to find the total read error probability.

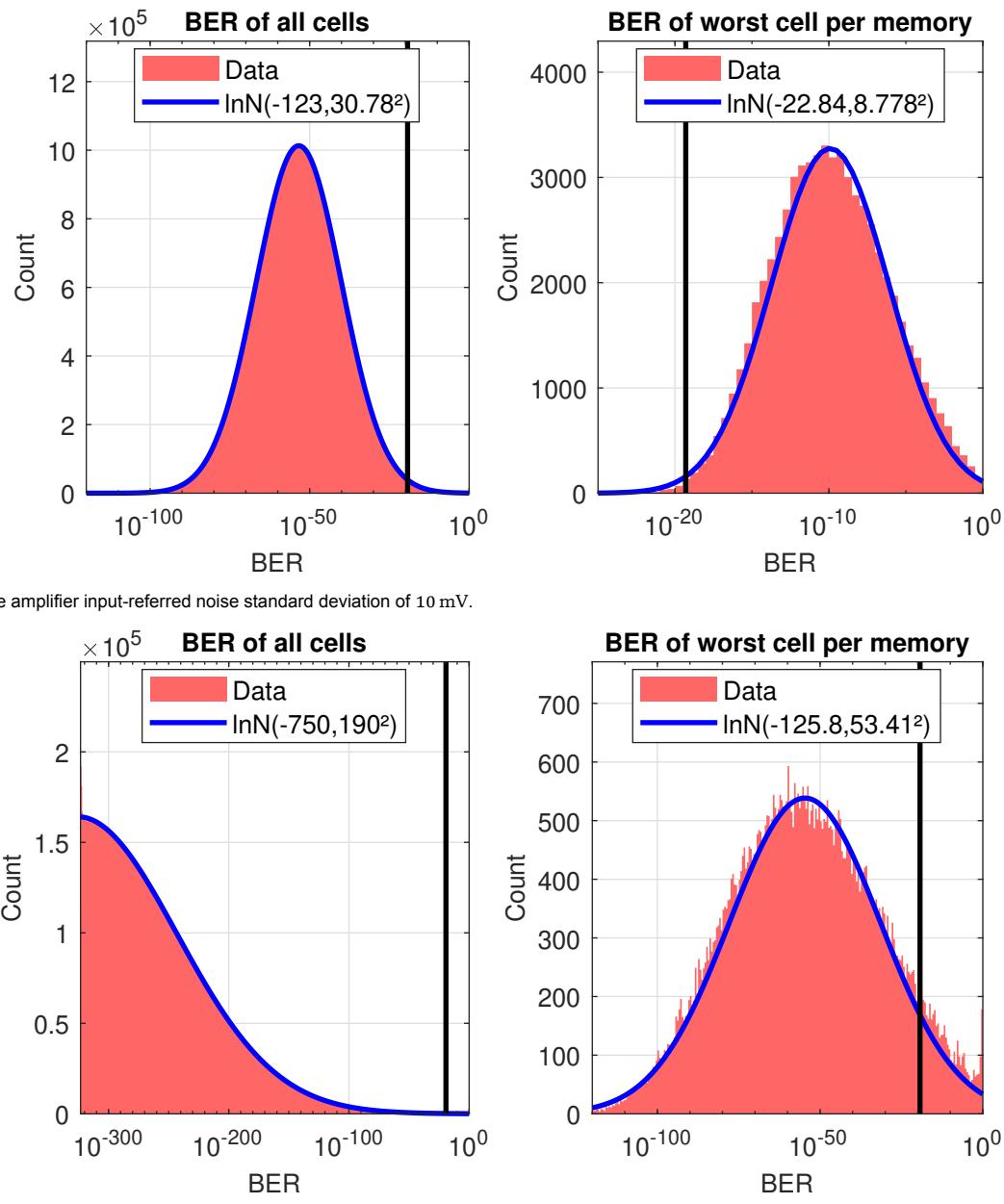

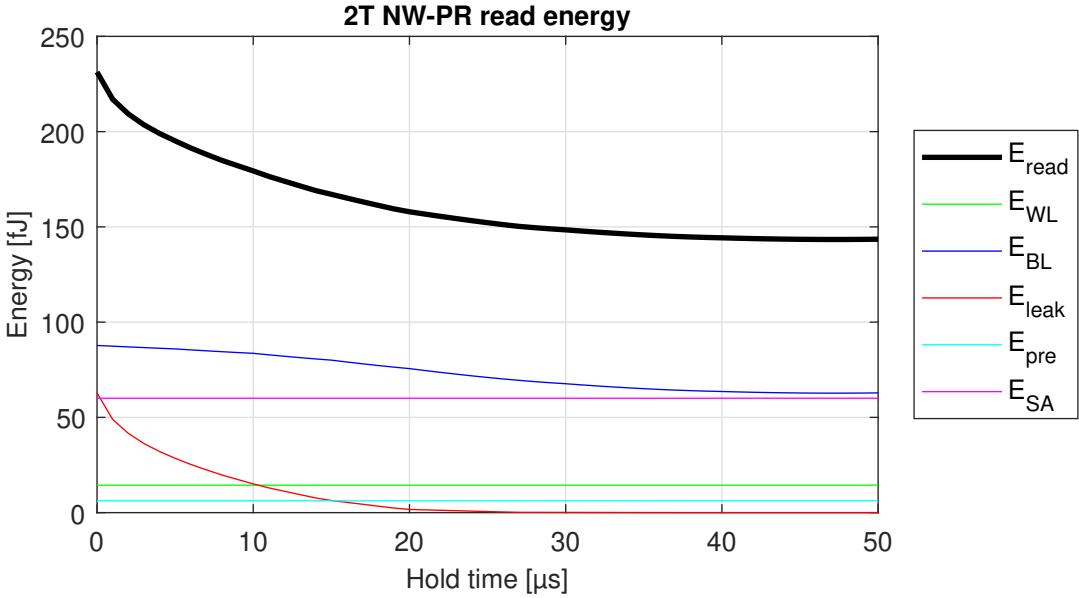

A histogram with the read error probability for all cells of  $2^{16} = 65536$  memory cores with 32 words of 32 bit ( $2^{26}$  cells in total) is shown in the left figure of fig. 3.10a and appears to follow a log-normal distribution<sup>3</sup>. The median cell has a BER of  $3.89 \times 10^{-54}$  and there is a probability of 99.9 % of getting a BER lower than  $10^{-12}$ . The worst performing cell of every memory is shown in the right figure of fig. 3.10a. This distribution also approximately follows a log-normal distribution, and means that in half the memories the BER for every cell is smaller than  $8.72 \times 10^{-11}$ , but the probability of getting a worst cell BER lower than  $10^{-6}$  is only 85.0 %.

The computed BER only holds for read operations performed 20  $\mu$ s after a write operation. This BER therefore limits the quality of the refresh read operation, as earlier reads will see much better bitline margins (for a hold time of 10  $\mu$ s, the worst cell BER is higher than  $6.22 \times 10^{-13}$  in 99.99 % of the memories). It is therefore instructive to see how long it would take, on average, for a bit to flip due to an incorrect refresh read operation. With a refresh rate of 50 kHz, a worst cell BER of  $10^{-6}$  results in one expected bit flip every 20 s due to refresh read operations alone. Note that this is only on the worst cell in the array. In half of the memories, the BER of the second worst cell is already smaller than  $4.82 \times 10^{-14}$ , and the probability of getting a second worst cell BER lower than  $10^{-8}$  is roughly 95.0 %. With a refresh rate of 50 kHz, a BER of  $10^{-8}$  results in an expected bit flip every 33.3 min. The cell performance quickly improves, but the number of errors is still high due to the large input-referred noise of the sense amplifiers.

The BER becomes a lot better for decreasing amounts of noise. If we decrease the input-referred noise standard deviation to 8 mV, the median cell BER becomes  $3.13 \times 10^{-83}$  and 99.98 % of the cells have a BER below  $10^{-9}$ . Additionally, the median worst cell BER becomes  $1.34 \times 10^{-15}$ , which corresponds with an expected refresh bit flip every 473 yr. For 83.9 % of the memories, the worst cell BER is smaller than  $10^{-9}$ , or one expected refresh bit flip every 5.55 h. The BER histograms for an

<sup>2</sup>With input referred noise standard deviations below 7 mV, the BER of some cells lies outside of the IEEE 754 Double-Precision Floating-Point range ( $< 4.94 \times 10^{-324}$ ), causing issues with distribution fitting.

<sup>3</sup>The BER has a limited support between 0 and 1, while a log-normal distribution has infinite support starting from 0. Nevertheless, the distribution shapes match very well.

Figure 3.9: 2T NW-PR cell inverse yield for a range of hold times and reference voltages.

input-referred noise standard deviation of 4 mV are shown in fig. 3.10b. The BER of more than half the cells lies outside the double-precision floating-point range and the probability of a cell having a BER worse than  $10^{-11}$  is roughly 0.0068 %, which corresponds to one expected refresh bit flip every 23.15 d. The median worst cell BER becomes  $5.43 \times 10^{-56}$  and the probability of getting a memory with a worst cell BER above  $10^{-11}$  is roughly 3.3 %.

Finally, note that the observed BER for most cells will be much larger than the values calculated using the Monte Carlo simulation. In reality, the BER is not only determined by noise during readout. It is also limited by *soft errors*, for example, due to radiation or interference. Radiation soft errors are reported for both dynamic memories [68], [69] and static memories [70], [71], and put a lower bound on the apparent BER. Using values reported in literature, the expected number of failures in time (FIT), where the time is defined as  $10^9$  h, for a 1 kbit array ranges from 0.004 to 10. In  $10^9$  h, we perform  $1.84 \times 10^{20}$  read operations for a refresh rate of 50 kHz on 1024 cells. If we assume these failures to be the result of an incorrect refresh read operation, the apparent refresh read error rate will be between  $2.17 \times 10^{-23}$  and  $5.43 \times 10^{-20}$ . This is larger than the noise-based worst cell BER of 93.5 % of the memories for an input-referred sense amplifier noise standard deviation of 4 mV. The black line in the right graph of figs. 3.10a and 3.10b indicates an apparent BER of  $5 \times 10^{-20}$ .