Delft University of Technology

## Advanced Testing and Reliability Enhancements for RRAMs

Xun, Hanzhi

**DOI**

[10.4233/uuid:58806228-60e2-48e9-9abc-2af03fa84006](https://doi.org/10.4233/uuid:58806228-60e2-48e9-9abc-2af03fa84006)

**Publication date**

2025

**Document Version**

Final published version

**Citation (APA)**

Xun, H. (2025). *Advanced Testing and Reliability Enhancements for RRAMs*. [Dissertation (TU Delft), Delft University of Technology]. <https://doi.org/10.4233/uuid:58806228-60e2-48e9-9abc-2af03fa84006>

**Important note**

To cite this publication, please use the final published version (if applicable).

Please check the document version above.

**Copyright**

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**

Please contact us and provide details if you believe this document breaches copyrights.

We will remove access to the work immediately and investigate your claim.

# Advanced Testing and Reliability Enhancements for RRAMs

Hanzhi Xun

# INVITATION

It is my pleasure to invite you to attend the public defence of my PhD thesis titled:

**Advanced Testing and Reliability Enhancements for RRAMs**

on Thursday, September 11, 2025, 10:00 a.m. in the Senaatszaal of the TU Delft Aula at Mekelweg 5, Delft.

I will introduce my research briefly at 9:30 a.m.

You are also welcome to attend the reception that takes place after the defence.

**Hanzhi Xun**

# **ADVANCED TESTING AND RELIABILITY ENHANCEMENTS FOR RRAMS**

# **ADVANCED TESTING AND RELIABILITY ENHANCEMENTS FOR RRAMS**

## **Dissertation**

for the purpose of obtaining the degree of doctor

at Delft University of Technology

by the authority of the Rector Magnificus prof.dr.ir. T.H.J.J. van der Hagen,

chair of the Board for Doctorates

to be defended publicly on

Thursday 11 September 2025 at 10:00 o'clock

by

**Hanzhi XUN**

Master of Science in Information, Production and Systems Engineering

Waseda University, Japan

Master of Engineering in Software Engineering

Xidian University, China

born in Xi'an, Shaanxi, China

This dissertation has been approved by the promoters.

Composition of the doctoral committee:

Rector Magnificus,

Prof.dr.ir. S. Hamdioui,

Dr.ir. M. Fieback,

Dr.ir. M. Taouil,

Chairperson

Delft University of Technology, promotor

Delft University of Technology, copromotor

Delft University of Technology

*Independent members:*

Prof.dr. G. Q. Zhang,

Prof.dr. H. W. Li,

Dr.ir. M. Ottavi,

Dr. B. Kruseman,

Prof.dr.ir. G. N. Gaydadjiev,

Delft University of Technology

ICT, Chinese Academy of Sciences, China

University of Twente, the Netherlands

NXP Semiconductors, the Netherlands

Delft University of Technology, reserve member

*Keywords:* resistive RAM, memristor, defects, defect modeling, fault modeling, test development, design-for-testability, reliability, Edge-AI, neuromorphic computing

*Printed by:* Ipskamp Printing, The Netherlands

*Front & Back:* Cover artwork by Hanzhi Xun

Copyright © 2025 by H. Xun

ISBN 978-94-6473-918-3

An electronic version of this dissertation is available at

<http://repository.tudelft.nl/>.

*Dedicated to:*

*my parents for raising me up and supporting me in education,

those who have used time to make me a better student, researcher, and human being.*

# CONTENTS

|                                                                      |              |

|----------------------------------------------------------------------|--------------|

| <b>Summary</b>                                                       | <b>xi</b>    |

| <b>Samenvatting</b>                                                  | <b>xiii</b>  |

| <b>Acknowledgements</b>                                              | <b>xv</b>    |

| <b>List of Figures</b>                                               | <b>xix</b>   |

| <b>List of Tables</b>                                                | <b>xxiii</b> |

| <b>1 Introduction</b>                                                | <b>1</b>     |

| 1.1 Emerging Memory Technologies . . . . .                           | 2            |

| 1.1.1 Memory Wall and Hierarchy . . . . .                            | 2            |

| 1.1.2 Emerging Memory Types . . . . .                                | 4            |

| 1.2 State of the Art in Memory Testing . . . . .                     | 10           |

| 1.2.1 Conventional Memory Testing . . . . .                          | 10           |

| 1.2.2 RRAM Testing . . . . .                                         | 11           |

| 1.3 Research Topics . . . . .                                        | 12           |

| 1.3.1 Complete Defect Space and Defect Modeling . . . . .            | 12           |

| 1.3.2 Fault Modeling, Validation, and Analysis . . . . .             | 13           |

| 1.3.3 High-Quality Test Design . . . . .                             | 13           |

| 1.3.4 Diagnosis of RRAM Defects . . . . .                            | 13           |

| 1.4 Contributions of the Thesis . . . . .                            | 13           |

| 1.4.1 Identification of Conventional and Unique Defects . . . . .    | 13           |

| 1.4.2 Testing for Conventional Defects . . . . .                     | 14           |

| 1.4.3 Testing for Unique Defects . . . . .                           | 14           |

| 1.4.4 Test Algorithm Generation and Design-for Testability . . . . . | 14           |

| 1.4.5 Reliability Analysis and Design-for Reliability . . . . .      | 15           |

| 1.4.6 Diagnosis for RRAM Yield Learning . . . . .                    | 15           |

| 1.5 Thesis Organization . . . . .                                    | 15           |

| <b>2 Background</b>                                                  | <b>17</b>    |

| 2.1 RRAM Device Technology . . . . .                                 | 18           |

| 2.1.1 Overview . . . . .                                             | 18           |

| 2.1.2 Placement Structure . . . . .                                  | 19           |

| 2.1.3 Switching Mechanism . . . . .                                  | 20           |

| 2.1.4 Stacked Composition of RRAM . . . . .                          | 21           |

| 2.2 RRAM Device Models . . . . .                                     | 22           |

| 2.2.1 Modeling Levels . . . . .                                      | 22           |

| 2.2.2 Overview of Compact Models . . . . .                           | 23           |

|          |                                                                   |           |

|----------|-------------------------------------------------------------------|-----------|

| 2.3      | Design Styles of RRAM Cells . . . . .                             | 26        |

| 2.4      | RRAM System Architecture and Circuit Design . . . . .             | 27        |

| 2.4.1    | RRAM Array Overview . . . . .                                     | 27        |

| 2.4.2    | Peripheral Circuits . . . . .                                     | 28        |

| 2.5      | Prototypes and Commercializations of RRAM . . . . .               | 32        |

| 2.5.1    | Prototypes . . . . .                                              | 32        |

| 2.5.2    | Commercializations . . . . .                                      | 34        |

| 2.5.3    | RRAM Applications . . . . .                                       | 36        |

| <b>3</b> | <b>RRAM Manufacturing, Defects, and Non-Idealities</b> . . . . .  | <b>39</b> |

| 3.1      | Manufacturing Process Overview . . . . .                          | 40        |

| 3.1.1    | Front-End-Of-Line . . . . .                                       | 40        |

| 3.1.2    | Back-End-Of-Line . . . . .                                        | 40        |

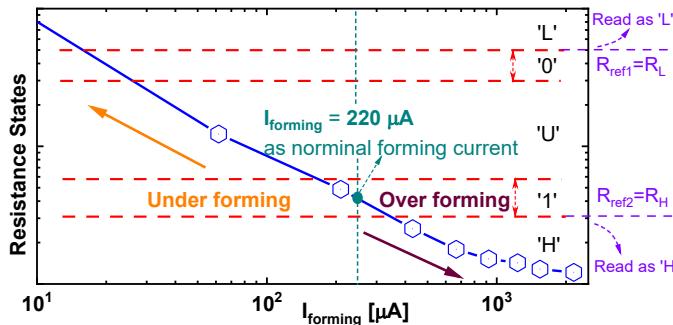

| 3.1.3    | Forming Process . . . . .                                         | 41        |

| 3.2      | RRAM Defects and Classifications . . . . .                        | 42        |

| 3.2.1    | Transistor-Related Defects . . . . .                              | 42        |

| 3.2.2    | RRAM Conventional Defects . . . . .                               | 43        |

| 3.2.3    | RRAM Unique Defects . . . . .                                     | 43        |

| 3.3      | Non-Ideality Issues in RRAMs . . . . .                            | 45        |

| 3.3.1    | Time-Zero Non-Idealities . . . . .                                | 46        |

| 3.3.2    | Time-Dependent Non-Idealities . . . . .                           | 47        |

| <b>4</b> | <b>Testing for Conventional Defects</b> . . . . .                 | <b>49</b> |

| 4.1      | Conventional RRAM Testing Approach . . . . .                      | 50        |

| 4.2      | Defect Modeling . . . . .                                         | 52        |

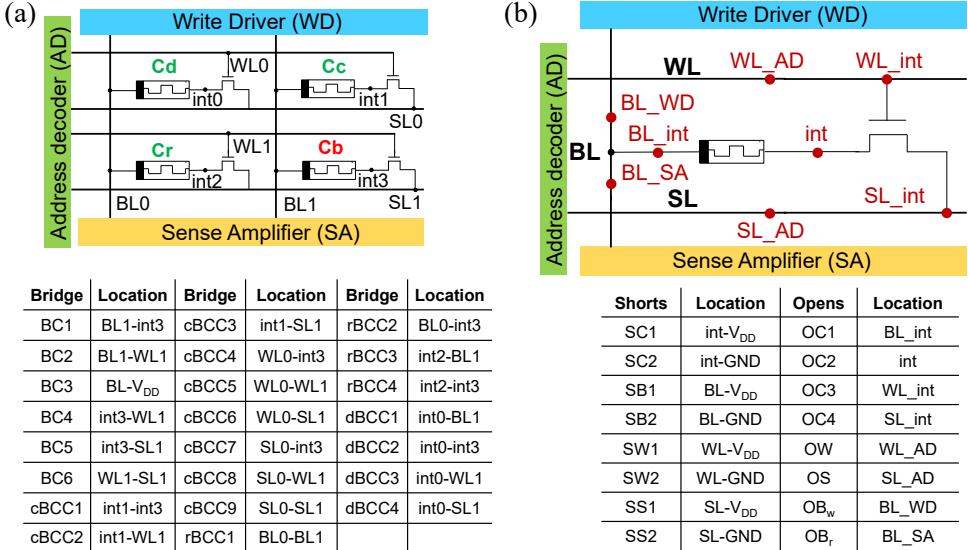

| 4.2.1    | Definition and Location of Bridges . . . . .                      | 53        |

| 4.2.2    | Definition and Location of Shorts . . . . .                       | 53        |

| 4.2.3    | Definition and Location of Opens . . . . .                        | 54        |

| 4.3      | Fault Modeling . . . . .                                          | 54        |

| 4.3.1    | Fault Space Definition and Classification . . . . .               | 54        |

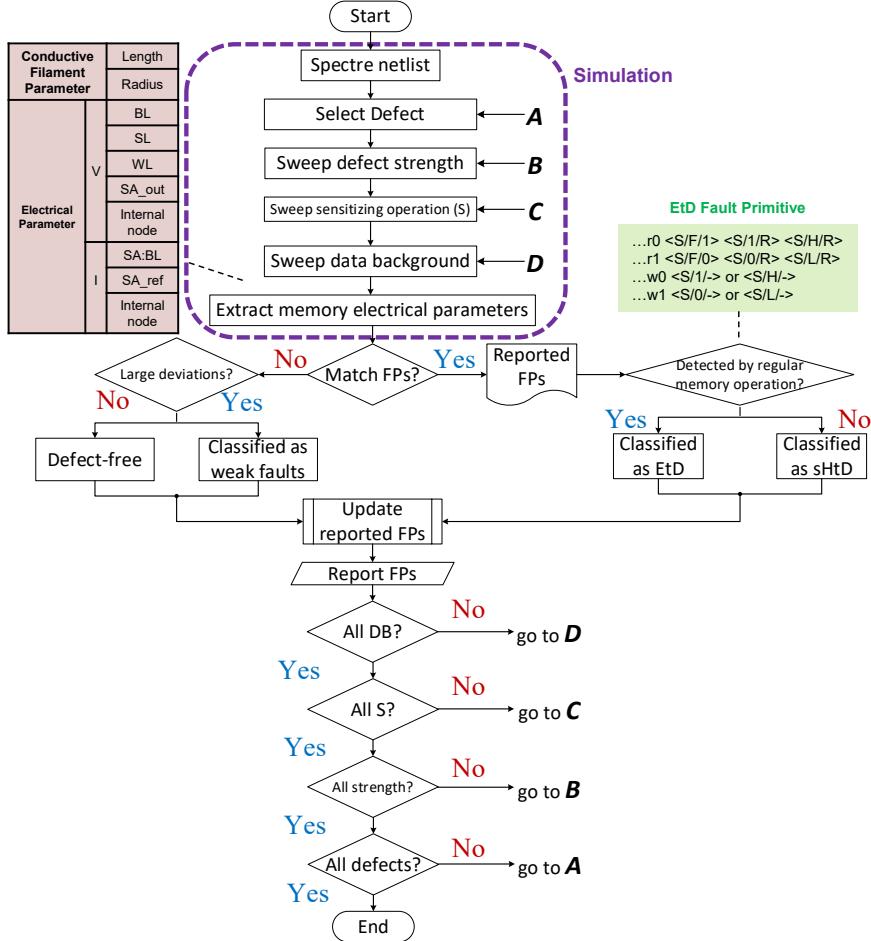

| 4.3.2    | Simulation Methodology . . . . .                                  | 55        |

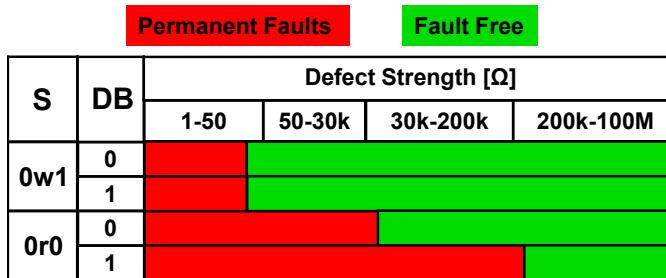

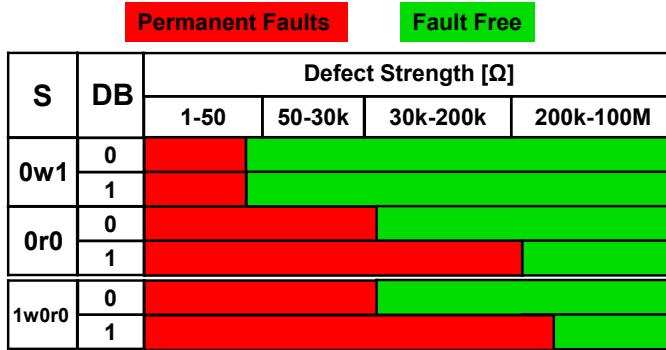

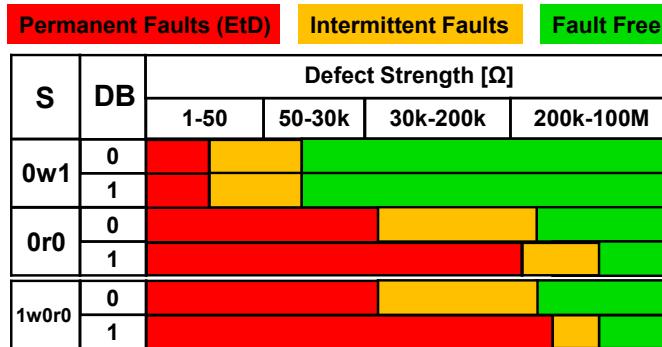

| 4.3.3    | Fault Modeling Results . . . . .                                  | 58        |

| 4.4      | Test Development . . . . .                                        | 62        |

| 4.4.1    | Data Background-Aware Test Approach Generation . . . . .          | 63        |

| 4.4.2    | Validation and Comparison with Existing Tests . . . . .           | 65        |

| <b>5</b> | <b>Device-Aware Test for Ion Depletion (ID) Defects</b> . . . . . | <b>67</b> |

| 5.1      | Introduction . . . . .                                            | 68        |

| 5.2      | Limitations of Conventional Defect Models . . . . .               | 68        |

| 5.3      | Device-Aware Test Approach . . . . .                              | 69        |

| 5.4      | Defect Characterization . . . . .                                 | 71        |

| 5.5      | Defect Mechanism . . . . .                                        | 74        |

| 5.6      | Device-Aware Defect Modeling of Ion Depletion . . . . .           | 77        |

| 5.6.1    | Physical Defect Analysis and Modeling . . . . .                   | 77        |

| 5.6.2    | Electrical Defect Modeling . . . . .                              | 80        |

| 5.6.3    | Fitting and Model Optimization . . . . .                          | 81        |

|          |                                                          |            |

|----------|----------------------------------------------------------|------------|

| 5.7      | Device-Aware Fault Modeling of Ion Depletion . . . . .   | 83         |

| 5.7.1    | Simulation Setup . . . . .                               | 83         |

| 5.7.2    | Fault Modeling and Results . . . . .                     | 84         |

| 5.8      | Device-Aware Test Development of Ion Depletion . . . . . | 85         |

| 5.8.1    | March Algorithms . . . . .                               | 85         |

| 5.8.2    | DfT Schemes . . . . .                                    | 86         |

| 5.9      | Comparison of Existing DfTs . . . . .                    | 88         |

| <b>6</b> | <b>Device-Aware Test for Over RESET (OR) Defects</b>     | <b>91</b>  |

| 6.1      | Introduction . . . . .                                   | 92         |

| 6.2      | Defect Characterization . . . . .                        | 92         |

| 6.3      | Defect Mechanism . . . . .                               | 93         |

| 6.4      | Device-Aware Defect Modeling of Over RESET . . . . .     | 94         |

| 6.4.1    | Physical Defect Analysis and Modeling . . . . .          | 94         |

| 6.4.2    | Electrical Defect Modeling . . . . .                     | 95         |

| 6.4.3    | Fitting and Model Optimization . . . . .                 | 95         |

| 6.5      | Device-Aware Fault Modeling of Over RESET . . . . .      | 97         |

| 6.5.1    | Simulation Setup . . . . .                               | 97         |

| 6.5.2    | Fault Modeling and Results . . . . .                     | 97         |

| 6.6      | Device-Aware Test Development of Over RESET . . . . .    | 98         |

| 6.7      | Comparison of Existing DfTs . . . . .                    | 99         |

| <b>7</b> | <b>Design-for-Testability Scheme for RRAM Faults</b>     | <b>101</b> |

| 7.1      | Introduction . . . . .                                   | 102        |

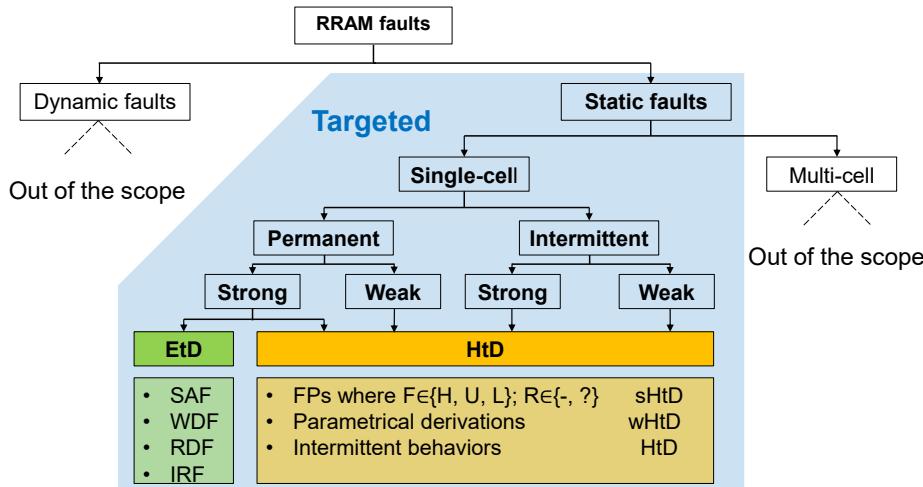

| 7.2      | Targeted RRAM Defects and Faults . . . . .               | 102        |

| 7.2.1    | RRAM Conventional Defects . . . . .                      | 102        |

| 7.2.2    | RRAM Unique Defects . . . . .                            | 103        |

| 7.2.3    | RRAM Faults . . . . .                                    | 103        |

| 7.3      | Limitation of Existing Works . . . . .                   | 104        |

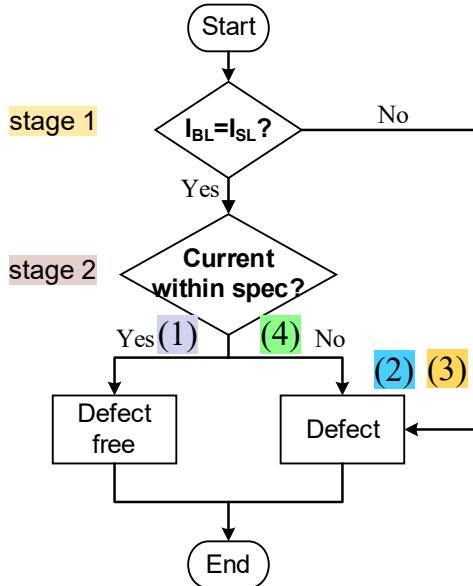

| 7.4      | Proposed DfT Methodology . . . . .                       | 104        |

| 7.4.1    | DfT Concept . . . . .                                    | 104        |

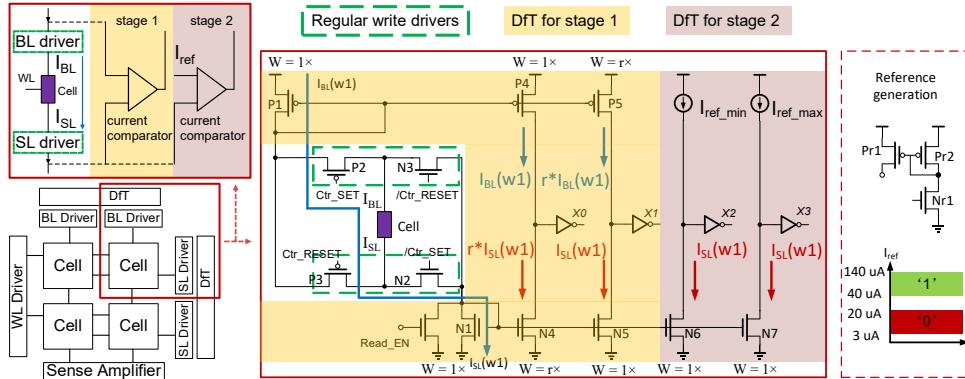

| 7.4.2    | Potential Implementations . . . . .                      | 107        |

| 7.4.3    | Selected Implementation . . . . .                        | 107        |

| 7.5      | Verification of DfT Methodology . . . . .                | 108        |

| 7.5.1    | Simulation Setup . . . . .                               | 109        |

| 7.5.2    | Results . . . . .                                        | 110        |

| 7.6      | Test Development . . . . .                               | 114        |

| <b>8</b> | <b>Design for Reliability for Read Disturb Faults</b>    | <b>115</b> |

| 8.1      | Introduction . . . . .                                   | 116        |

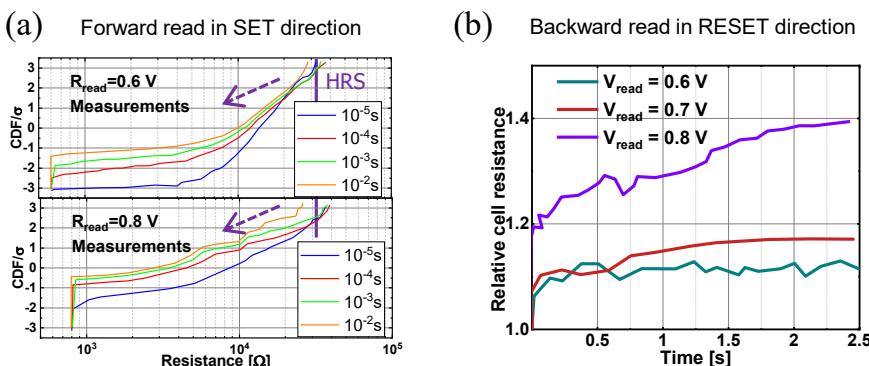

| 8.2      | Physics and Characterization of RDFs . . . . .           | 116        |

| 8.2.1    | Physical Phenomenon behind Resistance Drift . . . . .    | 116        |

| 8.2.2    | Device-Level RDF Characterization . . . . .              | 117        |

| 8.2.3    | Circuit-Level RDF Characterization . . . . .             | 118        |

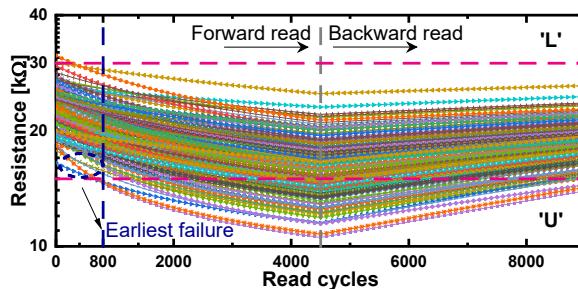

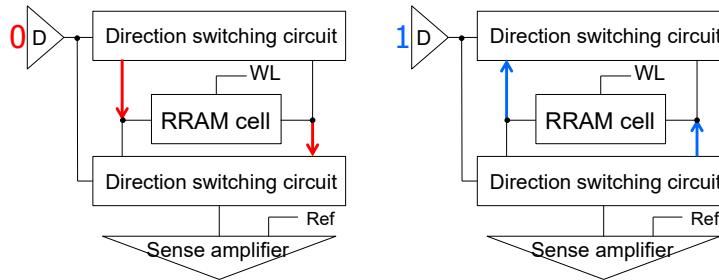

| 8.3      | The Bi-Directional Read Approach . . . . .               | 118        |

| 8.3.1    | Concept and Potential Implementations . . . . .          | 118        |

| 8.3.2    | Trade-Off for Approach Selection . . . . .               | 121        |

|                           |                                                                             |            |

|---------------------------|-----------------------------------------------------------------------------|------------|

| 8.4                       | <b>Validation</b>                                                           | 121        |

| 8.4.1                     | Simulation Set Up                                                           | 121        |

| 8.4.2                     | Validations for Storage Memory Array                                        | 121        |

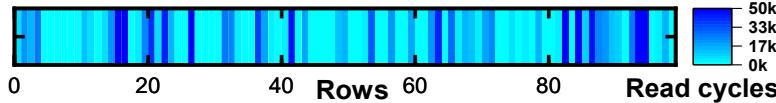

| 8.4.3                     | Validations for System-Level CIM Inference                                  | 124        |

| 8.5                       | <b>Discussion</b>                                                           | 125        |

| <b>9</b>                  | <b>Diagnosis for Conventional and Unique Defects</b>                        | <b>127</b> |

| 9.1                       | <b>Introduction</b>                                                         | 128        |

| 9.2                       | <b>Device-Aware Diagnosis Approach</b>                                      | 128        |

| 9.3                       | <b>Application of the Methodology for RRAMs</b>                             | 130        |

| 9.3.1                     | Targeted Defects and Their Characterizations                                | 130        |

| 9.3.2                     | Defect Modeling                                                             | 132        |

| 9.3.3                     | Feature Extraction                                                          | 132        |

| 9.3.4                     | Distinctive Feature Identification                                          | 132        |

| 9.3.5                     | Diagnosis Test Generation                                                   | 134        |

| 9.4                       | <b>Validation of Diagnosis Approach</b>                                     | 136        |

| 9.5                       | <b>Discussion</b>                                                           | 137        |

| <b>10</b>                 | <b>Putting All Together: Complete Industrial Test Development for RRAMs</b> | <b>139</b> |

| 10.1                      | <b>Introduction</b>                                                         | 140        |

| 10.2                      | <b>Defect and Defect Modeling</b>                                           | 140        |

| 10.2.1                    | Conventional Defects and Their Modeling in RRAM Array                       | 140        |

| 10.2.2                    | Unique Defects and Their Modeling in RRAM Array                             | 141        |

| 10.2.3                    | Defects and Their Modeling in RRAM Peripheral Circuits                      | 141        |

| 10.3                      | <b>RRAM Fault Modeling</b>                                                  | 142        |

| 10.3.1                    | Faults for Conventional Defects in RRAM Array                               | 142        |

| 10.3.2                    | Faults for Unique Defects in RRAM Array                                     | 145        |

| 10.3.3                    | Faults for Defects in Peripherals                                           | 146        |

| 10.4                      | <b>Test Development</b>                                                     | 146        |

| 10.4.1                    | March Algorithm Design                                                      | 147        |

| 10.4.2                    | Design-for-Testability Design                                               | 148        |

| 10.5                      | <b>Optimizing Test Solutions</b>                                            | 151        |

| <b>11</b>                 | <b>Conclusion</b>                                                           | <b>153</b> |

| 11.1                      | <b>Summary</b>                                                              | 154        |

| 11.2                      | <b>Future Research Directions</b>                                           | 156        |

| <b>Bibliography</b>       |                                                                             | <b>157</b> |

| <b>Nomenclature</b>       |                                                                             | <b>179</b> |

| <b>Curriculum Vitæ</b>    |                                                                             | <b>185</b> |

| <b>Main Publications</b>  |                                                                             | <b>187</b> |

| <b>Other Publications</b> |                                                                             | <b>189</b> |

# SUMMARY

This dissertation, conducted within the discipline of Electronic Science and Technology (specialization in Microelectronics and Solid-State Electronics), focuses on Resistive Random Access Memory (RRAM), an emerging non-volatile memory technology known for its high density and zero static power consumption. RRAM enables fast write and read operations in the nanosecond range and supports Computation-in-Memory (CIM), making it a strong candidate to replace Flash or even Dynamic Random Access Memory (DRAM). Recognizing its potential, both academic institutions and industry leaders have been actively developing RRAM prototypes, with some already reaching the commercial market. To ensure reliability, high-quality testing is essential for guaranteeing product quality.

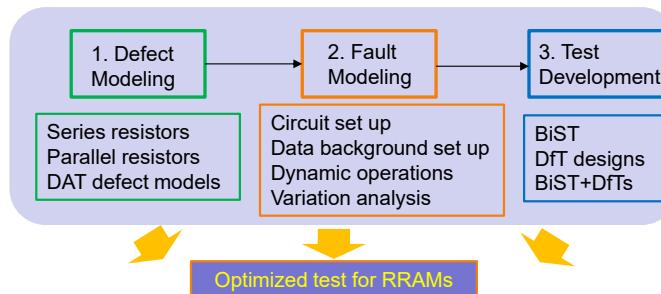

This dissertation mainly focuses on developing effective test methodologies and robust designs for RRAMs. We begin by examining the RRAM manufacturing process and identifying potential physical defects at each stage through a comprehensive literature review and silicon measurements. To facilitate in-depth analysis, we develop a complete and systematic RRAM simulation platform, integrating a MATLAB-based simulation controller and fault analysis scripts integrated with a complete RRAM circuit design. The controller automates and manages all simulation procedures, while the circuit design comprises a 1T-1R memory array along with essential peripheral components such as write drivers and sense amplifiers. To achieve fast and accurate electrical simulations, we introduce two compact models for RRAMs. These models are optimized and calibrated using extensive measurement data from RRAM devices. We further calibrate the model with industrial measurements from ST Microelectronics. It enables robust device/circuit co-design, accounting for PVT variations and ensuring the reliability and efficiency of RRAM systems.

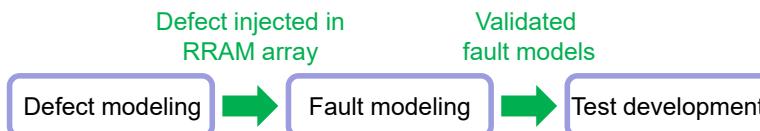

By using the simulation platform, we investigate RRAM testing for interconnects and contacts by using conventional defect/fault modeling and test designs. In this approach, physical defects are modeled as linear resistors (e.g., open, short, or bridge) and injected into the RRAM array netlist for fault analysis. Test development is then carried out based on the identified fault behaviors. Both intra-cell and inter-cell defects are analyzed, confirming the presence of not only single-cell faults but also multi-cell faults. While modeling interconnect defects as linear resistors is a well-established practice, this method has not been validated for defects inside the RRAM devices.

To tackle this challenge, we apply the Device-Aware Test (DAT) approach that can incorporate physical behaviors in RRAM devices. The DAT approach is applied to two observed unique defects, ion depletion and over RESET, as case studies in this dissertation. Based on this approach, accurate defect models, realistic fault models, and efficient Design-for-Testability (DfT) designs are provided.

While existing designs primarily focus on individual defects or a limited set of fault behaviors, this dissertation introduces a comprehensive Design-for-Testability (DfT)

framework tailored for RRAMs. The proposed framework is capable of effectively detecting both conventional and unique defects, ensuring broad defect coverage with optimized test cost. Furthermore, the framework is designed with robustness in mind, offering strong resilience against process variations that often compromise the effectiveness of traditional test solutions. By addressing both conventional and unique defects, the proposed DFT strategies establish a unified methodology that advances beyond existing fragmented approaches.

In addition to defect- and fault-oriented challenges, this dissertation also investigates time-dependent non-idealities inherent to RRAM technology. A key example is the Read Disturb Fault (RDF), which gradually degrades device reliability during repeated read operations. To overcome this limitation, we propose a bi-directional circuit architecture that can continuously monitor the device state and actively counteract RDF-induced degradation. By dynamically recovering the device state through controlled operations, this design-for-reliability scheme significantly extends the lifetime and stability of RRAM devices. Importantly, the proposed approach has been validated across both storage-class RRAM and CIM architectures, demonstrating its versatility and ensuring robust long-term system operation.

Finally, a diagnosis framework was presented that leverages accurate defect models and distinctive features to uniquely localize defects, enabling precise defect classification for yield learning and process optimization. Collectively, these contributions establish a holistic methodology for testing, reliability enhancement, and diagnosis of RRAMs, paving the way toward their dependable integration into future memory and computing platforms.

# SAMENVATTING

Dit proefschrift, uitgevoerd binnen de discipline Electronic Science and Technology (specialisatie in Micro-elektronica en Vastestofelektronica), richt zich op Resistive Random Access Memory (RRAM), een opkomende niet-vluchtlige geheugentechnologie die bekendstaat om haar hoge dichtheid en nul statisch stroomverbruik. RRAM maakt snelle schrijf- en leesbewerkingen in het nanosecondebereik mogelijk en ondersteunt Computation-in-Memory (CIM), waardoor het een sterke kandidaat is om Flash of zelfs Dynamic Random Access Memory (DRAM) te vervangen. Gezien het potentieel zijn zowel academische instellingen als industriële leiders actief bezig met de ontwikkeling van RRAM-prototypes, waarvan sommige al de commerciële markt hebben bereikt. Om de betrouwbaarheid te waarborgen, is hoogwaardige testmethodologie essentieel voor het garanderen van productkwaliteit.

Dit proefschrift richt zich voornamelijk op het ontwikkelen van effectieve testmethodologieën en robuuste ontwerpen voor RRAM's. We beginnen met het onderzoeken van het RRAM-productieproces en het identificeren van mogelijke fysieke defecten in elke fase via een uitgebreide literatuurstudie en siliciummetingen. Om diepgaande analyses mogelijk te maken, ontwikkelen we een volledig en systematisch RRAM-simulatieplatform, waarin een MATLAB-gebaseerde simulatiecontroller en foutanalysescripts geïntegreerd zijn met een compleet RRAM-circuitontwerp. De controller automatiseert en beheert alle simulatieprocedures, terwijl het circuitontwerp bestaat uit een 1T-1R-geheugenarray met essentiële perifere componenten zoals schrijfstuurprogramma's en sense amplifiers. Voor snelle en nauwkeurige elektrische simulaties introduceren we twee compacte RRAM-modellen. Deze modellen zijn geoptimaliseerd en gekalibreerd met uitgebreide meetgegevens van RRAM-apparaten, en verder verfijnd met industriële metingen van STMicroelectronics. Dit maakt robuust apparaat-/circuitontwerp mogelijk, waarbij PVT-variaties in rekening worden gebracht en de betrouwbaarheid en efficiëntie van RRAM-systemen worden gewaarborgd.

Met behulp van het simulatieplatform onderzoeken we RRAM-testen voor interconnecties en contacten, gebaseerd op conventionele defect-/foutmodellering en testontwerpen. In deze benadering worden fysieke defecten gemodelleerd als lineaire weerstanden (bijv. open, short of bridge) en geïnjecteerd in de RRAM-array netlist voor foutanalyse. Testontwikkeling wordt vervolgens uitgevoerd op basis van de geïdentificeerde foutgedragingen. Zowel intra-cellulaire als inter-cellulaire defecten worden geanalyseerd, wat bevestigt dat niet alleen single-cell fouten voorkomen, maar ook multi-cell fouten. Hoewel het modelleren van interconnect-defecten als lineaire weerstanden een gevestigde praktijk is, is deze methode nog niet gevalideerd voor defecten binnen de RRAM-apparaten zelf.

Om deze uitdaging aan te pakken, passen we de Device-Aware Test (DAT)-benadering toe, waarmee fysische gedragingen van RRAM-apparaten in rekening kunnen worden gebracht. Deze aanpak wordt toegepast op twee waargenomen unieke de-

fecten, ionendepletie en over-RESET, als casestudies in dit proefschrift. Op basis van deze aanpak worden nauwkeurige defectmodellen, realistische foutmodellen en efficiënte Design-for-Testability (DfT)-ontwerpen ontwikkeld.

Waar bestaande ontwerpen zich voornamelijk richten op afzonderlijke defecten of een beperkte set foutgedragingen, introduceert dit proefschrift een omvattend DfT-ramwerk dat specifiek is afgestemd op RRAM's. Het voorgestelde raamwerk kan zowel conventionele als unieke defecten effectief detecteren, wat resulteert in een brede defectdekking met geoptimaliseerde testkosten. Bovendien is het raamwerk ontworpen met robuustheid in gedachten, waardoor het een sterke weerstand biedt tegen procesvariaties die vaak de effectiviteit van traditionele testoplossingen ondermijnen. Door zowel conventionele als unieke defecten aan te pakken, vormen de voorgestelde DfT-strategieën een verenigde methodologie die verder gaat dan de bestaande gefragmenteerde benaderingen.

Naast defect- en foutgerichte uitdagingen onderzoekt dit proefschrift ook tijdafhankelijke niet-idealiteiten die inherent zijn aan RRAM-technologie. Een belangrijk voorbeeld hiervan is de Read Disturb Fault (RDF), die de betrouwbaarheid van het apparaat geleidelijk vermindert bij herhaalde leesbewerkingen. Om deze beperking te overwinnen, stellen we een bi-directionele circuitarchitectuur voor die de toestand van het apparaat continu kan monitoren en actief RDF-geïnduceerde degradatie tegengaat. Door de toestand van het apparaat dynamisch te herstellen via gecontroleerde operaties, verlengt dit design-for-reliability schema de levensduur en stabiliteit van RRAM-apparaten aanzienlijk. Belangrijk is dat de voorgestelde aanpak is gevalideerd voor zowel storage-class RRAM als CIM-architecturen, wat de veelzijdigheid aantoon en robuuste, langdurige systeemwerking waarborgt.

Tot slot wordt een diagnoseraamwerk gepresenteerd dat gebruikmaakt van nauwkeurige defectmodellen en onderscheidende kenmerken om defecten uniek te lokaliseren. Dit maakt een precieze defectclassificatie mogelijk, die waardevolle feedback biedt voor yield learning en procesoptimalisatie. Gezamenlijk vestigen deze bijdragen een holistische methodologie voor het testen, verbeteren van betrouwbaarheid en diagnosticeren van RRAM's, en banen zij de weg voor een betrouwbare integratie ervan in toekomstige geheugen- en computerplatformen.

# ACKNOWLEDGEMENTS

After four years of exploration, effort, and learning, I am now standing at the finish line of my PhD journey. This moment is not just a personal milestone, but also a reminder of the support, inspiration, and kindness I have received from many people along the way. This thesis, although bearing my name, is the result of collective guidance, collaboration, and friendship. I am sincerely grateful to everyone who has walked alongside me.

First and foremost, I would like to express my deepest gratitude to my promotor and supervisor, **Prof.dr.ir. Said Hamdioui**. Thank you for offering me the opportunity to pursue my PhD under your guidance. From the very beginning, you welcomed me into your group and provided everything I needed to grow, including research freedom, access to essential resources, the opportunity to supervise students, and participation in academic activities such as summer schools. These experiences broadened my academic perspective and helped me mature as a researcher. Throughout the years, you taught me how to think critically, communicate effectively in a scientific context, and face challenges with confidence. I still remember the many hours spent revising papers, polishing presentations, and carefully preparing for deadlines. Those intense sessions taught me valuable lessons that will stay with me long after this PhD. You consistently provided insightful guidance on the strategic direction of my projects. Your ability to see the bigger picture and your industrial background helped me connect my research to real-world applications. At the very beginning of my PhD, you told me that you would closely follow my development, always aiming to help me grow step by step until I met the standard of a PhD graduate. I hope that I have now reached that level. Your sense of responsibility and strong work ethic also left a deep impression on me. I have often seen you working late in the office, and even during your holidays, you remained available and supportive. Your dedication and commitment to your students are qualities I admire deeply and hope to carry forward in my own career. Thank you for your trust, your time, and your mentorship throughout this journey.

Next, I am also deeply grateful to my copromotor, **Dr.ir. Moritz Fieback**. Moritz, you've been a steady guide throughout my PhD journey. I especially appreciate the encouragement you gave me during the most stressful moments in my first year. You reminded me to breathe, take breaks, and not take everything too seriously. Your kind feedback on my first ETS paper draft gave me confidence when I needed it most. Furthermore, you thoroughly reviewed every paper I wrote, often through several versions filled with precise and insightful comments. But more than helping me fix a paper, you were teaching me how to become a better writer and thinker. That made a lasting difference. I also appreciated your sense of humor and your relaxed but effective way of working. You showed me that it's not just about working hard, but also about working smart—and enjoying the process along the way. Thank you as well for trusting me with teaching responsibilities and sharing your views on how to grow as an educator. In addition, I would like to sincerely thank **Dr.ir. Mottaqiallah Taouil**. Although not listed as my

official copromotor, you have undoubtedly played the role of a true mentor throughout my academic life. From the early stages of my PhD, you have been a constant source of support, both academically and personally. Our meetings were always filled with fresh ideas and your confident, solution-driven mindset often helped push projects forward when I was stuck. Beyond research, you genuinely cared about how I was doing, and I deeply appreciate the attention you paid to my well-being. Thank you for your guidance, your creativity, and your kindness.

I am grateful to the committee members of this thesis, **Prof.dr. Guoqi Zhang**, **Prof.dr. Huawei Li**, **Dr.ir. Marco Ottavi**, **Dr. Bram Kruseman**, and **Prof.dr. Georgi Gaydadjiev**. Your insightful feedback has been crucial in enhancing my thesis, and I eagerly anticipate witnessing the influence of our future collaborative efforts.

I would also like to thank my academic collaborators. First, **Dr. Hassen Aziza**, thank you for introducing me to the fundamentals of RRAM design, for the thoughtful discussions, and for sharing important measurement data. I am especially grateful that you always provide your feedback very fast and helpfully. I truly appreciate your openness and generosity, and I hope we can continue this productive collaboration in the future. Next, I would like to thank **Dr. Leticia Bolzani Poehls** and **Dr. Thiago Copetti** for the work we have done together. We explored meaningful topics and laid a strong foundation for future research. It has been a pleasure working with you both. My thanks also go to **Dr. Riccardo Cantoro** for the enjoyable and insightful collaboration. I learned a lot from our technical discussions on compute-in-memory systems and on the contrasting characteristics of FeFET. Beyond external collaborations, I am grateful for the opportunity to work with talented researchers at TU Delft. Thank you, **Dr. Rajendra Bishnoi** and **Dr. Anteneh Gebregiorgis**, for your valuable input and kind support throughout different phases of my work.

Thanks as well to both my paranympths, **Sicong Yuan** and **Erbing Hua**. Sicong, we started our PhD journeys around the same time and have worked closely ever since, not only because of our overlapping research topics, but also because of the friendship we've built along the way. Thank you for always being so generous—whether it was inviting us over for your home-cooked meals or sharing your thoughts and feedback on research ideas. I've learned a lot from our discussions and truly enjoyed your company over the years. Erbing, thank you for broadening my perspective by bringing in insights from materials science, and even beyond that—from social sciences and philosophy. Our conversations have often sparked new ways for me to think about research and its role. Both of you have been not just colleagues, but real companions throughout this journey. I will always treasure the memories we made, including our unforgettable road trip across Europe. I feel very lucky to have shared this PhD journey with you.

I would like to extend my thanks to all colleagues at the QCE department. Thanks to **Prof.dr. Rob Kooij** for your efforts in creating a nice working environment and supporting all different kinds of social events in the department. I also had the pleasure of sharing my workday with many other people in the department, including but not limited to **Dr. Abdullah**, **Dr. Abhairaj**, **Dr. Anteneh**, **Dr. Carlo**, **Dr. Guilherme**, **Dr. Heba**, **Dr. Lizhou**, **Dr. Mahdi**, **Dr. Micheal (Taha)**, **Dr. Moritz**, **Dr. Motta**, **Dr. Paul**, **Dr. Rajendra**, **Dr. Sumit**, **Dr. Theofilos**, **Dr. Troya**, **Alexandra**, **Ali**, **Amin**, **Arne**, **Asmaa**, **Asmae**, **Bea**, **Christian**, **Ediz**, **Emmanouil Anastasios**, **Emmanouil Arapidis**, **Erbing**, **Erik**,

**Ethan Zhang, Folkert, Fouwad, Francis, Geerten, Helen, Ignacio, Ismail, Konstantinos, Mahmood, Mainak, Mark, Pantazis, Shadid, Shayesteh, Sicong, Yash, Yong, and Zacharia.** Thanks for the nice lunches that we had together, the daily coffee walks, and many more events. Amin, Asmae, and Mainak, thanks for organizing social events and sport activities. Francis, Helen, and Paul, thank you for keeping everything in order and for ensuring that my work could be performed effectively. Erik, Mark, and Ediz, thanks for your great help in setting up the simulation environments.

I also want to express my gratitude to some of my Chinese PhD fellows at TU Delft, and friends I have ever met. Thank you for always being there, whether it was for a spontaneous lunch, a late-night walk, or simply sharing thoughts on research and life. These everyday moments made the PhD journey lighter and more enjoyable. I also want to thank my friends in China. Even though we have been separated by thousands of miles, your care and support always reached me across the distance. The occasional messages, phone calls, and genuine concern reminded me that I was never alone on this journey. Your presence, near or far, has meant a lot to me.

Last but most importantly, I would like to express my deepest thanks to my family. To my parents, who have always been my pillars of strength and my guiding lights. Your unwavering and unconditional support has shaped the person I am today and enabled everything I have achieved. I owe this journey to you. To my grandparents, uncles, aunts, brother, and sister, thank you for your love, wisdom, and contribution to a lovely and warm big family. Your presence in my life means more than words can say. And finally, I want to thank myself for being brave, for holding on during the toughest moments, and for never giving up. This journey has not been easy, but I am proud that I made it here. Many thanks to all of you!

*Hanzhi Xun

Delft, July, 2025*

# LIST OF FIGURES

|      |                                                                                                                                                                                           |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

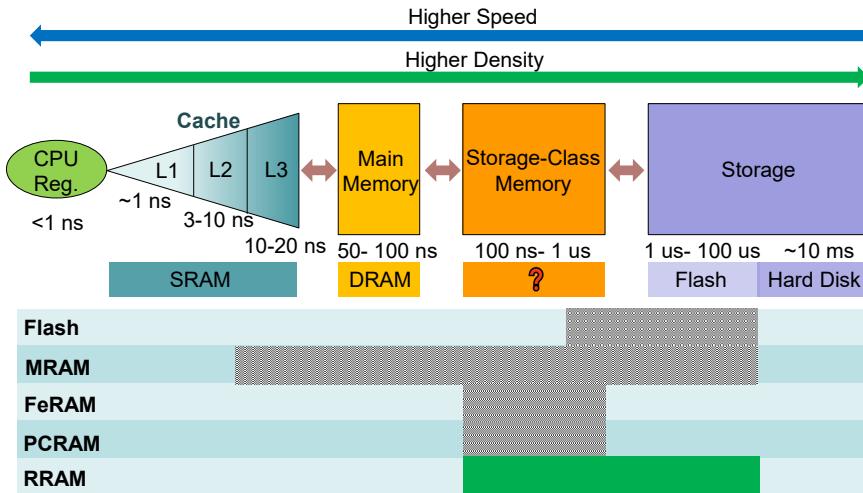

| 1.1  | The memory hierarchy in computer systems. . . . .                                                                                                                                         | 2  |

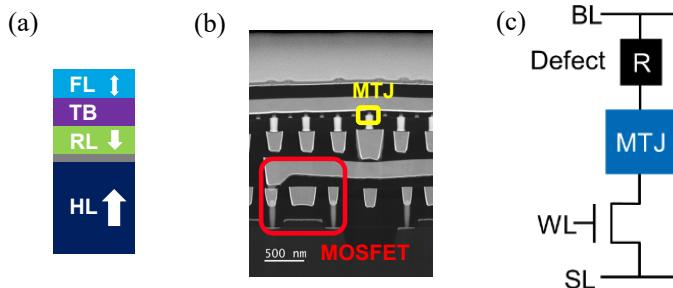

| 1.2  | (a) MTJ device structure, (b) TEM of MTJ, (c) 1T-1MTJ cell. . . . .                                                                                                                       | 4  |

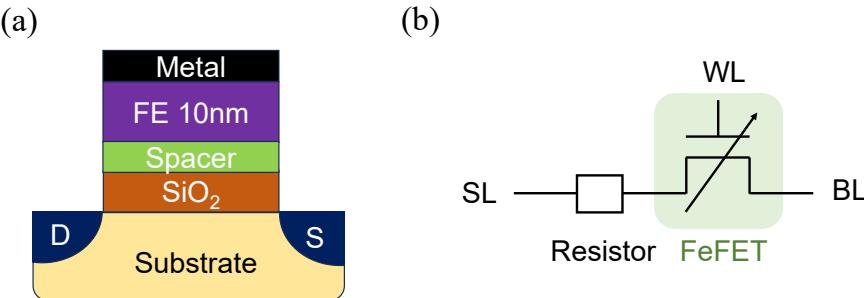

| 1.3  | (a) Device structure of FeFET, (b) 1 FeFET-1 Resistor cell structure. . . . .                                                                                                             | 5  |

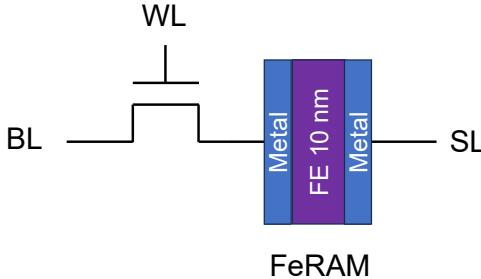

| 1.4  | Structure of FeRAM cell and device. . . . .                                                                                                                                               | 6  |

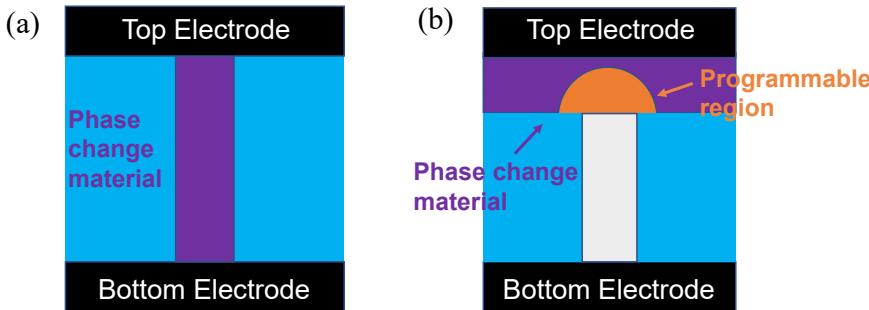

| 1.5  | Structure of the PCRAM. (a) Confined cell structure, (b) Planar cell structure. . . . .                                                                                                   | 7  |

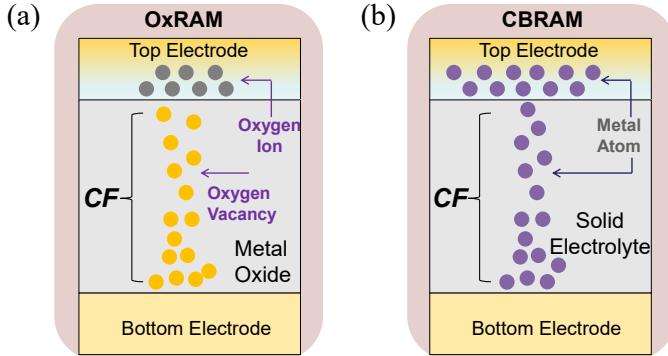

| 1.6  | Structure of RRAMs. (a) OxRAM, (b) CBRAM. . . . .                                                                                                                                         | 8  |

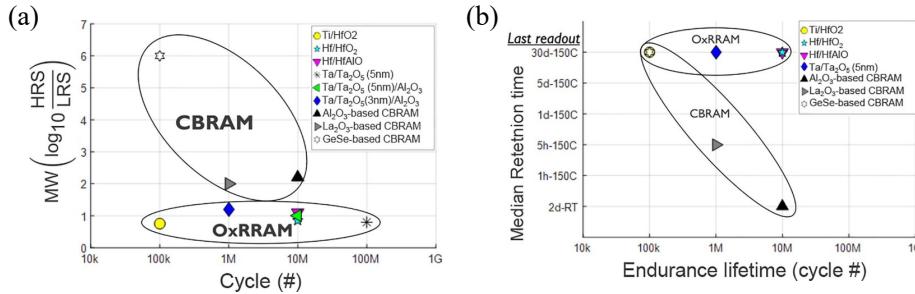

| 1.7  | CBRAM vs. OxRAM. (a) Endurance and MW, (b) Endurance and retention. . . . .                                                                                                               | 9  |

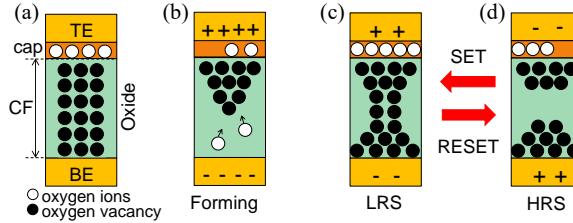

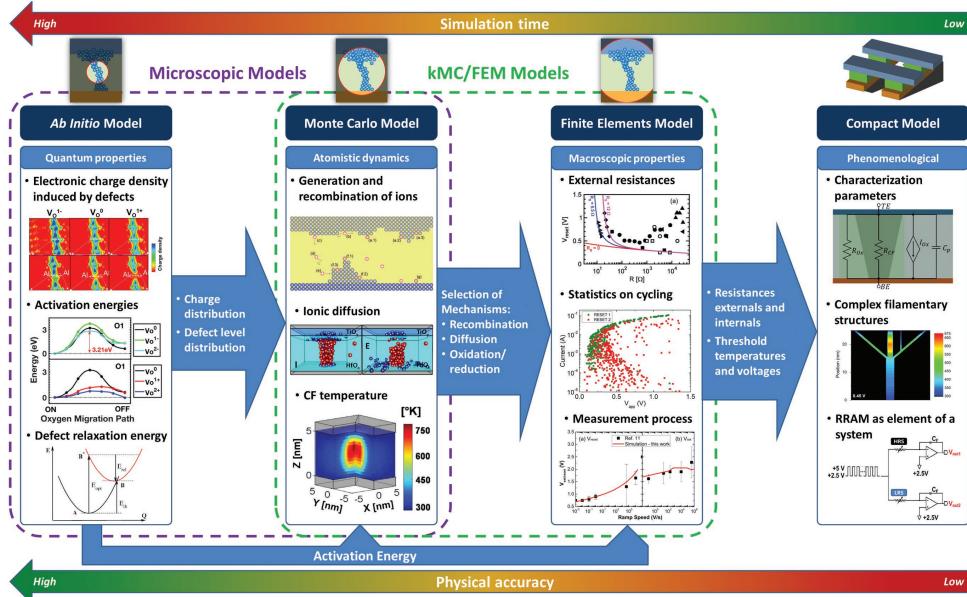

| 2.1  | Evolution of the conductive filament. (a) RRAM stack, (b) Forming, (c) SET, (d) RESET. . . . .                                                                                            | 18 |

| 2.2  | RRAM resistance states and corresponding logic values. . . . .                                                                                                                            | 18 |

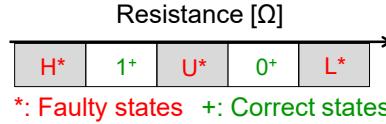

| 2.3  | RRAM device placement structure. (a) Cross structure (reprinted from [78]), (b) Between metal layers (reprinted from [79]), (c) 3D vertical RRAM structure (reprinted from [80]). . . . . | 19 |

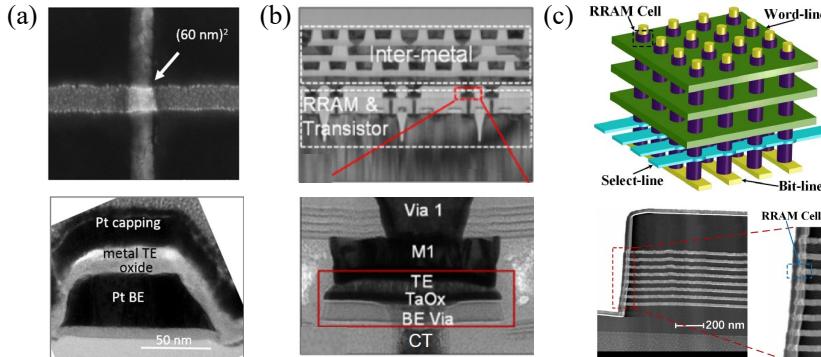

| 2.4  | RRAM switching modes. (a) Bipolar switching, (b) Unipolar switching, (c) Complementary switching. . . . .                                                                                 | 20 |

| 2.5  | The periodic table of elements with host metals of RRAM (reprinted in [85]).                                                                                                              | 21 |

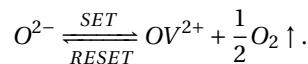

| 2.6  | Multiple levels of RRAM models based on [108]. . . . .                                                                                                                                    | 22 |

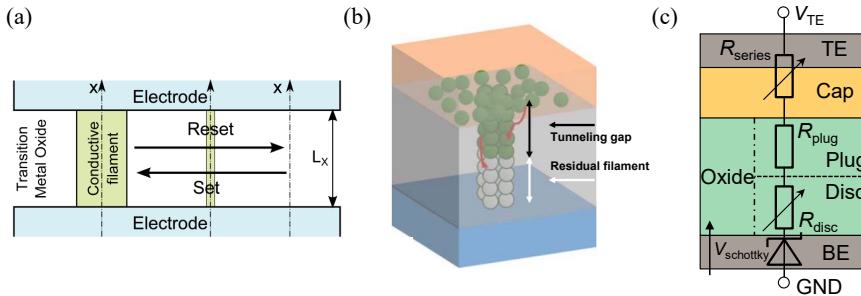

| 2.7  | Basic illustration of three compact RRAM models (reprinted from [110], [117], [118]). . . . .                                                                                             | 25 |

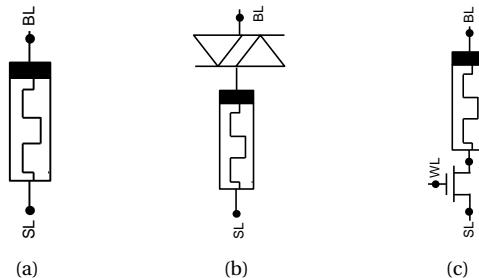

| 2.8  | RRAM cell designs. (a) 1R, (b) 1D-1R, (c) 1T-1R. . . . .                                                                                                                                  | 26 |

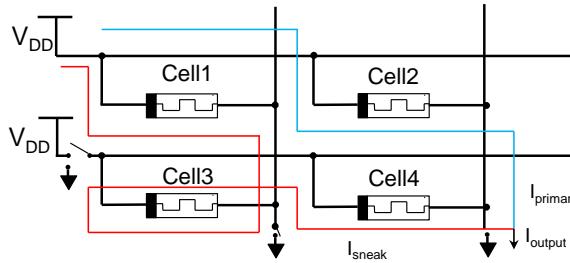

| 2.9  | Sneak path in a $2 \times 2$ 1R array. . . . .                                                                                                                                            | 27 |

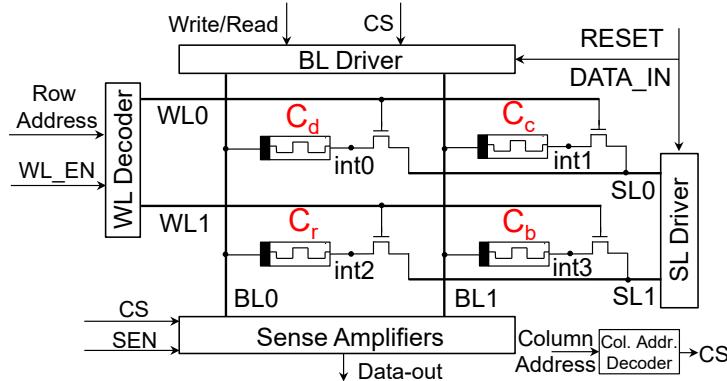

| 2.10 | A $2 \times 2$ RRAM circuit architecture. . . . .                                                                                                                                         | 28 |

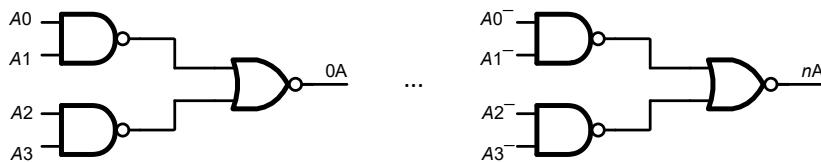

| 2.11 | Address decoder. . . . .                                                                                                                                                                  | 28 |

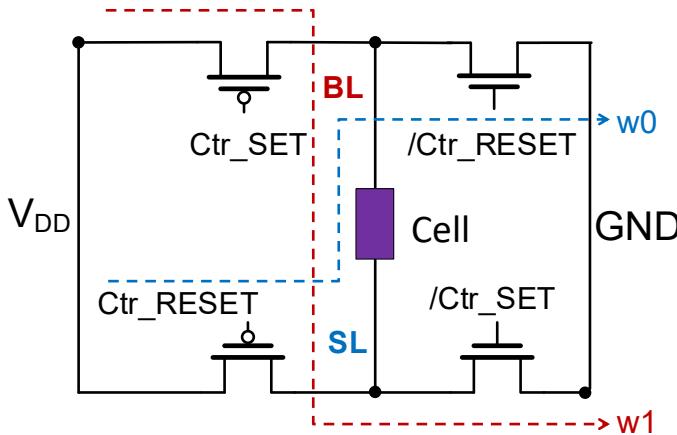

| 2.12 | The schematic of circuit with write drivers and the currents of $w_1$ and $w_0$ . . . . .                                                                                                 | 29 |

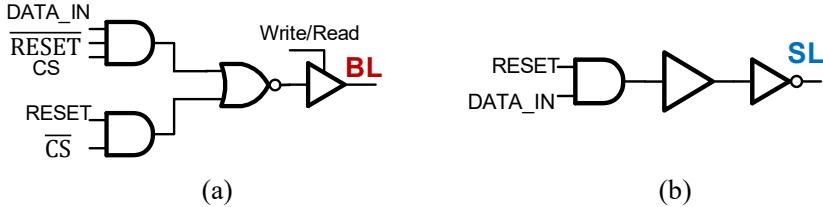

| 2.13 | Write drivers. (a) The BL driver, (b) The SL driver. . . . .                                                                                                                              | 30 |

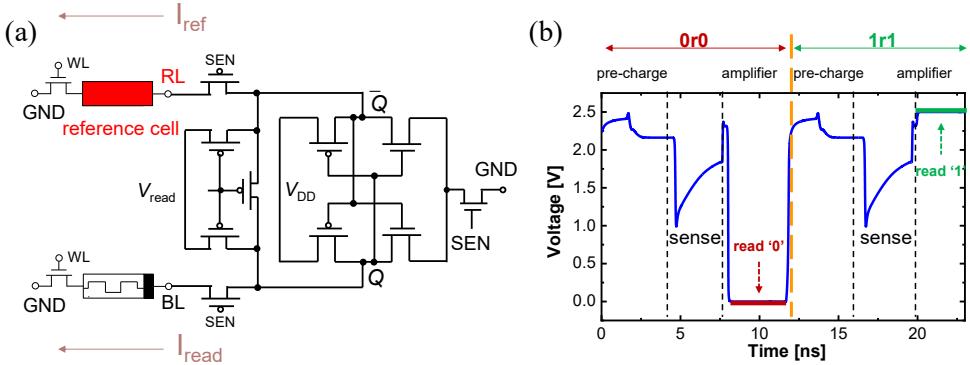

| 2.14 | Sense amplifier design [122] and read waveform. (a) The SA design, (b) The waveform of $0r_0$ and $1r_1$ operations. . . . .                                                              | 30 |

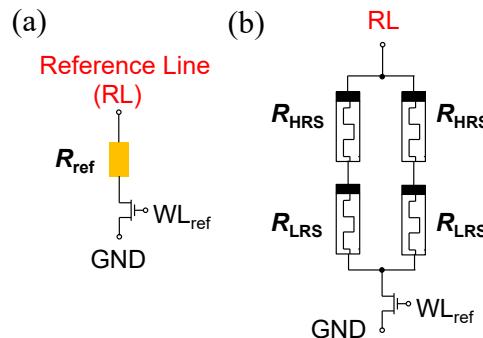

| 2.15 | The design of reference cells. (a) Reference using a resistor, (b) Reference composed of RRAMs. . . . .                                                                                   | 31 |

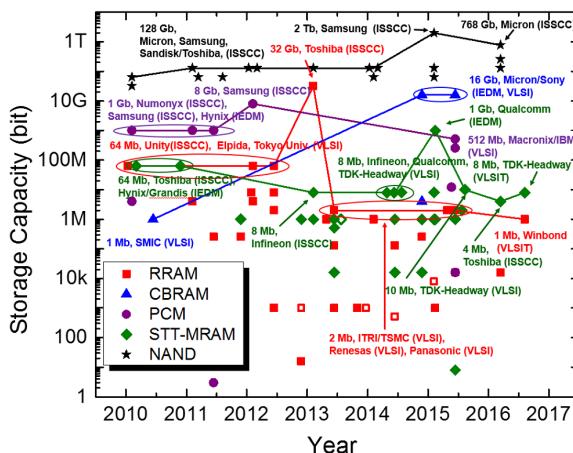

| 2.16 | Trends of emerging device technologies (reprinted from [123]). . . . .                                                                                                                    | 32 |

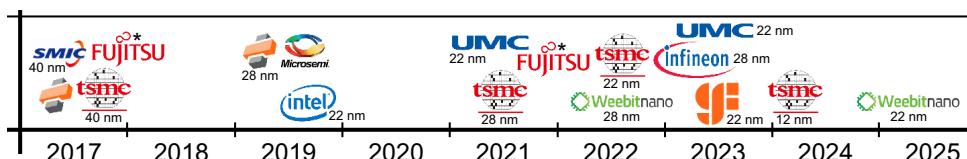

| 2.17 | Timeline of recent technology demonstrations of eNVM with respective CMOS nodes (reprinted from [152]). . . . .                                                                           | 34 |

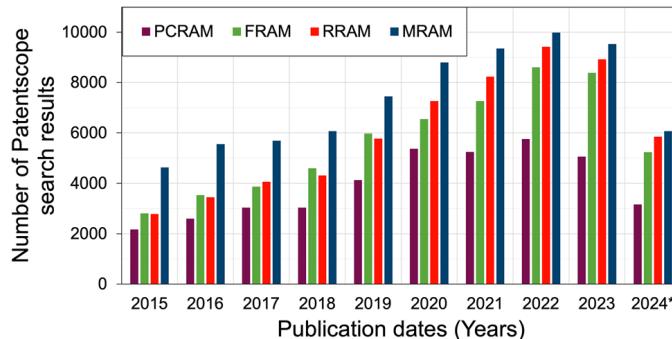

| 2.18 | Word IP organization patent scope search results from 2015 to July 2024 (reprinted from [152]). . . . .                                                                                   | 36 |

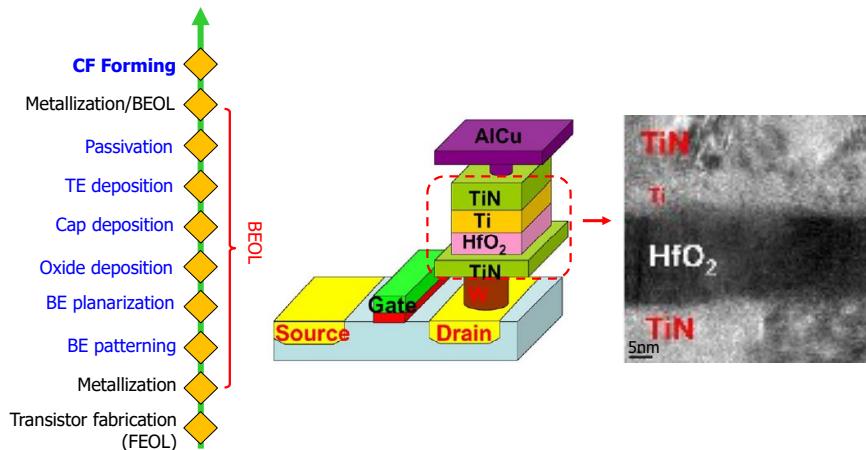

| 3.1  | General manufacturing process of RRAM (right part reprinted from [85]). . . . .                                                                                                           | 40 |

|      |                                                                                                                                                                                                                           |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

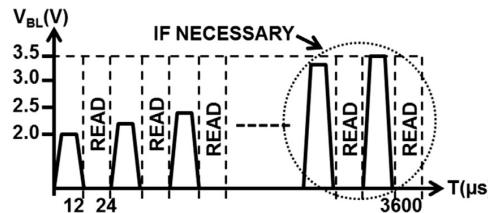

| 3.2  | Controllable forming pulse and read verification scheme (reprinted from [178]). . . . .                                                                                                                                   | 41 |

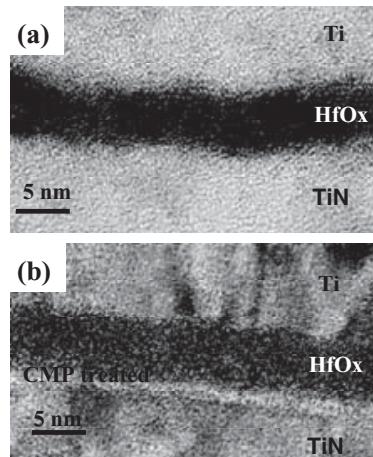

| 3.3  | The comparison between electrodes (reprinted from [190]). (a) Unpolished electrode, (b) Polished electrode after post-meatal annealing. . . . .                                                                           | 43 |

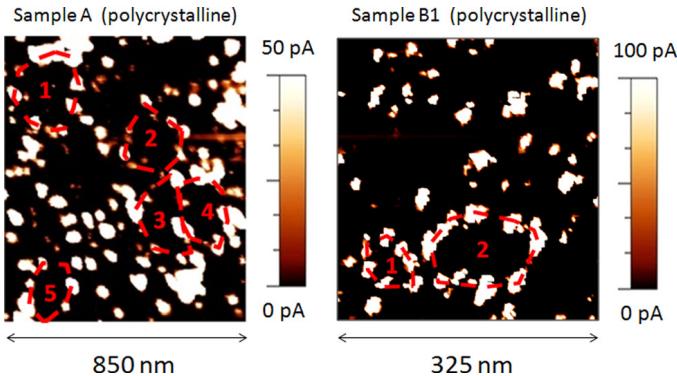

| 3.4  | Grain boundaries conduct current in oxide (reprinted from [191]). . . . .                                                                                                                                                 | 44 |

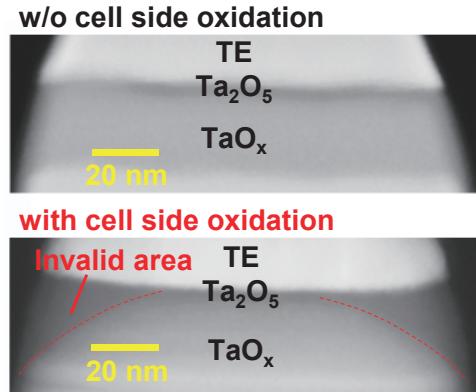

| 3.5  | Partial invalidation of sidewall (reprinted from [195]). . . . .                                                                                                                                                          | 45 |

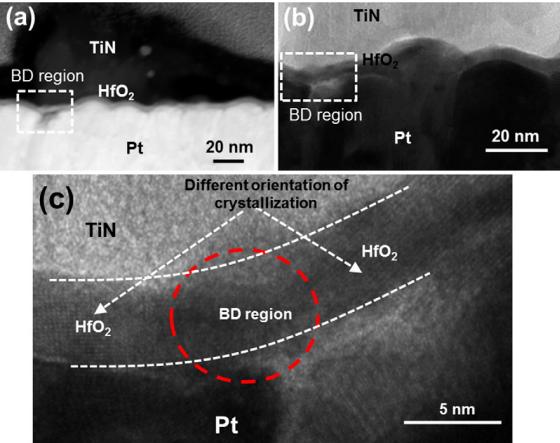

| 3.6  | The breakdown region image in the TiN/HfO <sub>2</sub> /Pt stack (reprinted from [192]). . . . .                                                                                                                          | 46 |

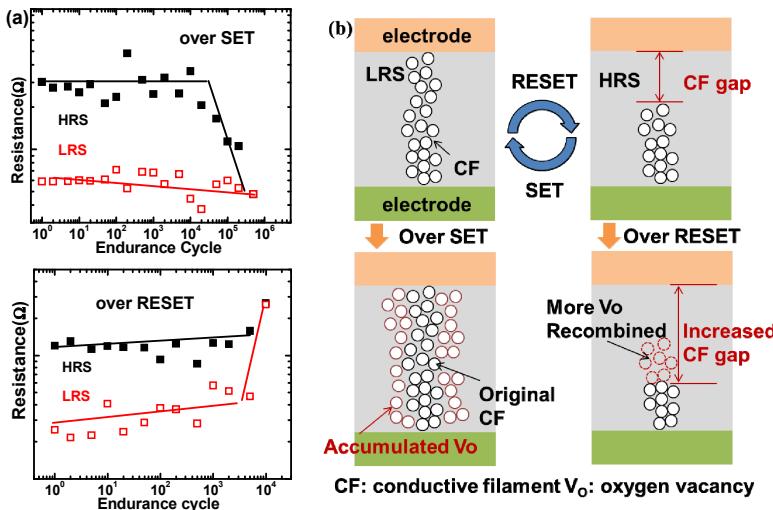

| 3.7  | Two typical endurance degradation characteristics (reprinted from [207]). (a) Experiments. (b) Schematics of endurance degradation mechanisms. .                                                                          | 48 |

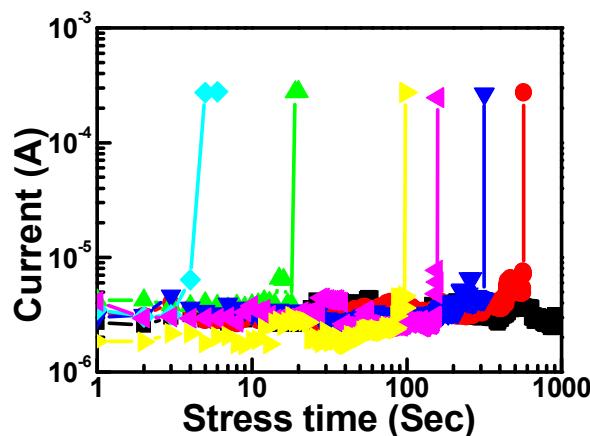

| 3.8  | The resistance of the device in HRS decreases under stress test (reprinted from [208]). . . . .                                                                                                                           | 48 |

| 4.1  | Process of conventional test development . . . . .                                                                                                                                                                        | 50 |

| 4.2  | Conventional defect space. (a) Bridges that intra or inter cells, (b) Shorts and opens that intra the cell. . . . .                                                                                                       | 52 |

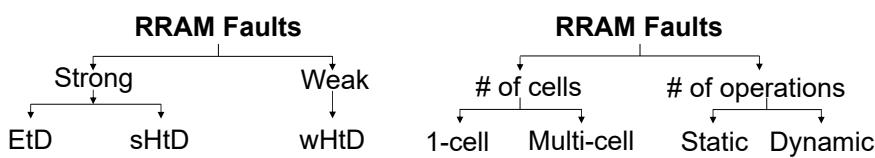

| 4.3  | Fault space and classification. . . . .                                                                                                                                                                                   | 55 |

| 4.4  | Fault space validation methodology. . . . .                                                                                                                                                                               | 57 |

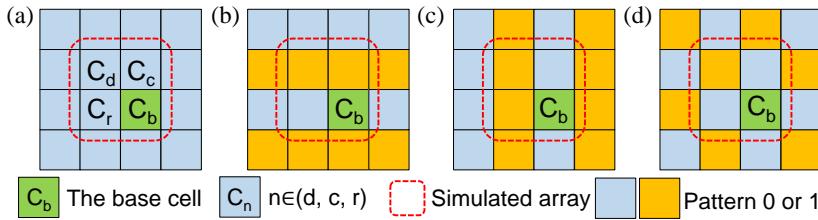

| 4.5  | RRAM simulation setup with common DBs. (a) Solid, (b) Row stripe, (c) Column stripe, (d) Checkerboard. . . . .                                                                                                            | 58 |

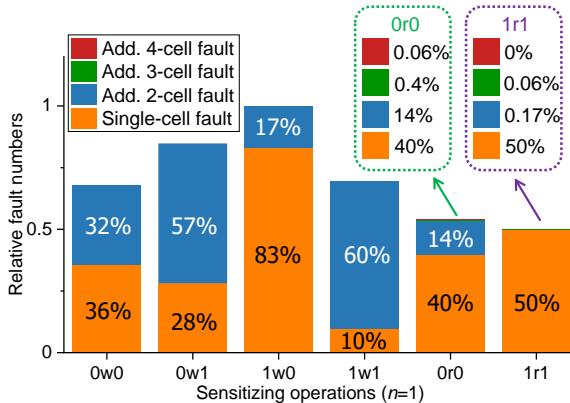

| 4.6  | Relative number of faults sensitized by static sequences. . . . .                                                                                                                                                         | 61 |

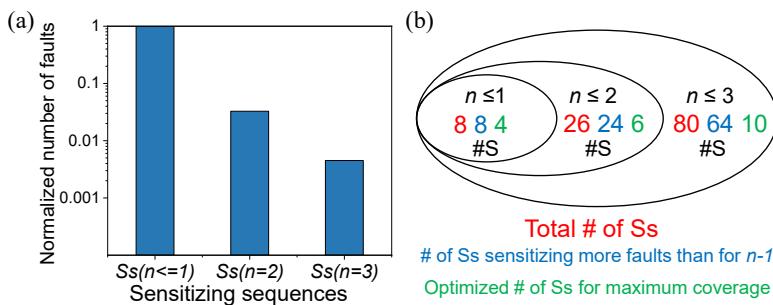

| 4.7  | Dynamic EtD faults sensitized as $n_{max}$ increases. (a) The normalized number of faults, (b) The number of sequences. . . . .                                                                                           | 61 |

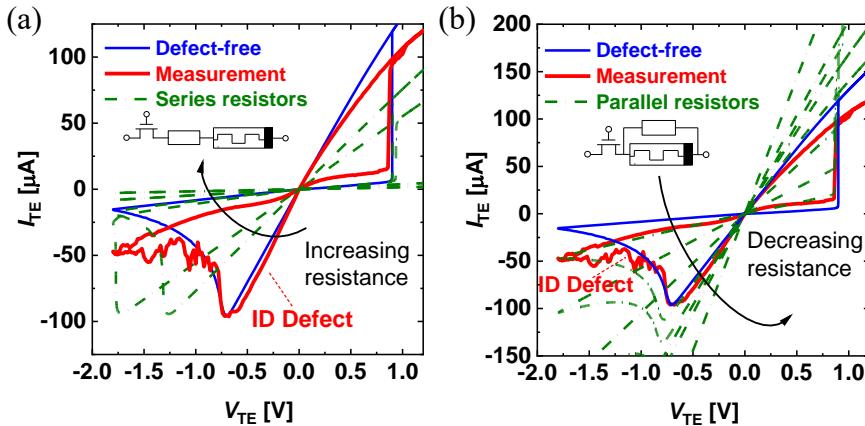

| 5.1  | Linear resistor defect models. (a) Series resistors, (b) Parallel resistors. .                                                                                                                                            | 69 |

| 5.2  | Process of DAT approach. . . . .                                                                                                                                                                                          | 70 |

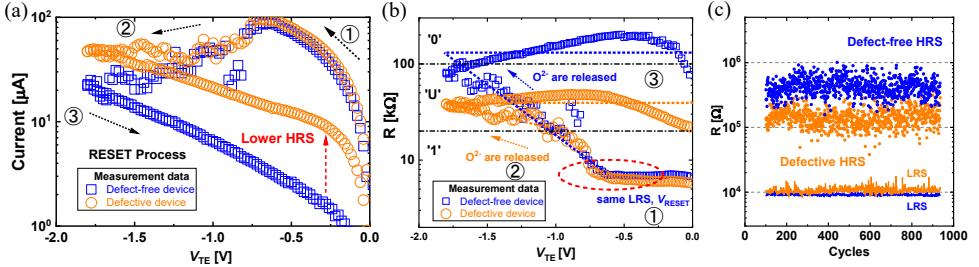

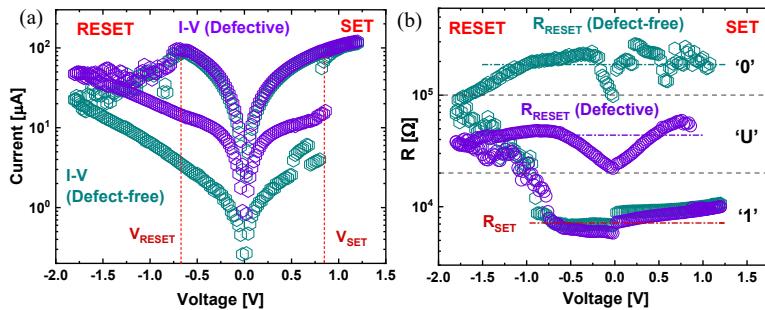

| 5.3  | Comparing defect-free and defective devices. (a) Measured I-V curve in the logarithmic y-axis, (b) Measured R-V curve in the logarithmic y-axis, (c) Measured $R_{RESET}$ and $R_{SET}$ in multiple (836) cycles. . . . . | 72 |

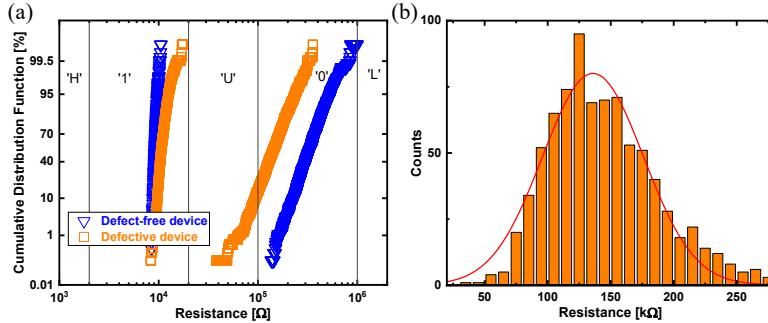

| 5.4  | Resistance distribution. (a) Measured $R_{RESET}$ and $R_{SET}$ of defect-free and defective devices, (b) Histogram of measured $R_{RESET}$ distribution. . . . .                                                         | 73 |

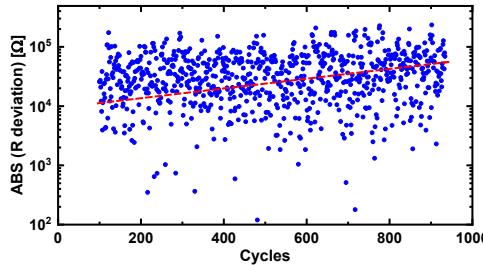

| 5.5  | The absolute value of $R_{RESET}$ deviation of the defective device as cycle increases. . . . .                                                                                                                           | 74 |

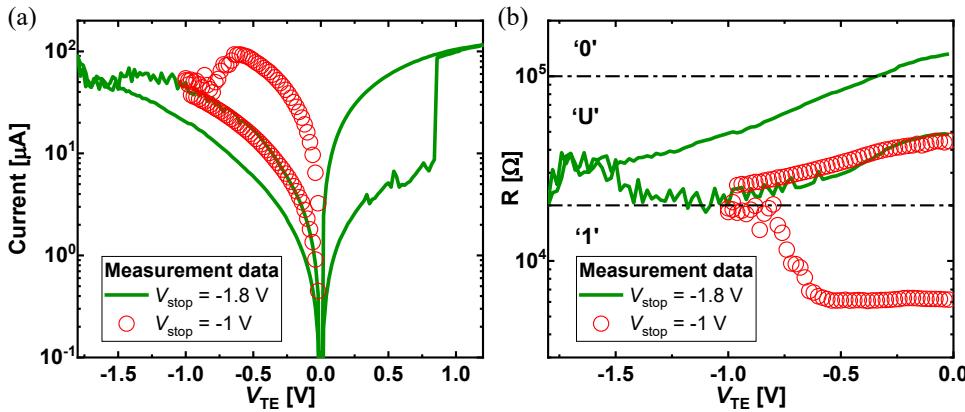

| 5.6  | Regular and weak RESET of the defective device with different $V_{stop}$ . (a) Measured I-V curve in the logarithmic y-axis, (b) Measured R-V curve in the logarithmic y-axis. . . . .                                    | 75 |

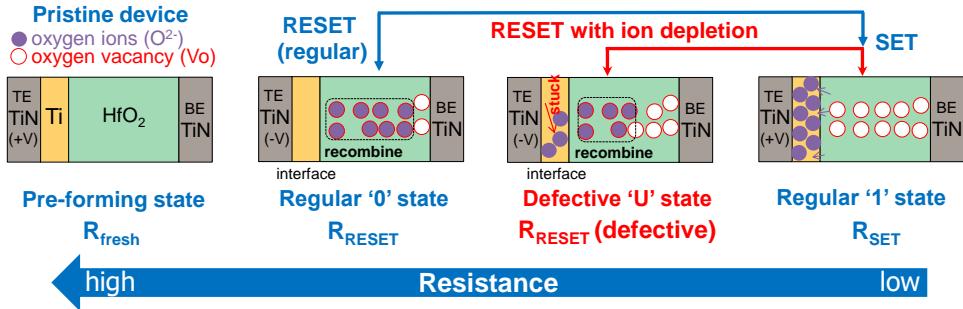

| 5.7  | The schematic view of ion depletion mechanism during RESET process. .                                                                                                                                                     | 76 |

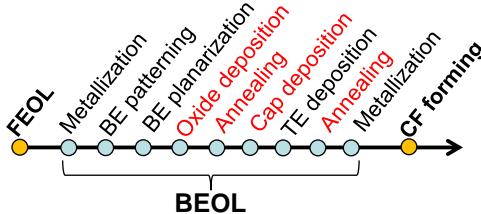

| 5.8  | Flow of RRAM manufacturing process [106], [177], [234], [235]. . . . .                                                                                                                                                    | 76 |

| 5.9  | The Verilog-A compact model diagram and defect-free device simulation model. (a) Equivalent circuit diagram of the JART VCM v1b model [110], (b) Defect-free device fitting in the logarithmic y-axis. . . . .            | 78 |

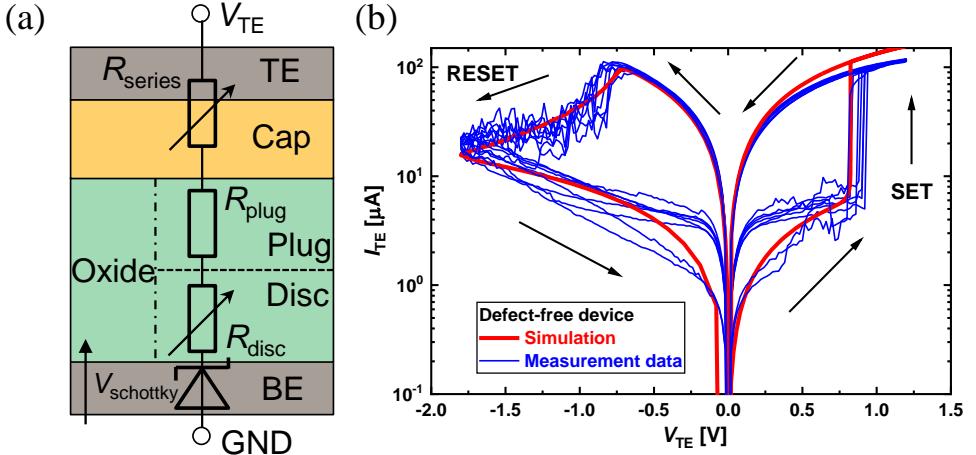

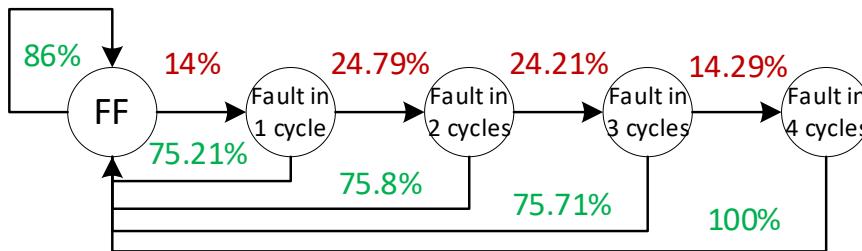

| 5.10 | State transition diagram showing probabilities of faulty 'U' states over multiple cycles. . . . .                                                                                                                         | 79 |

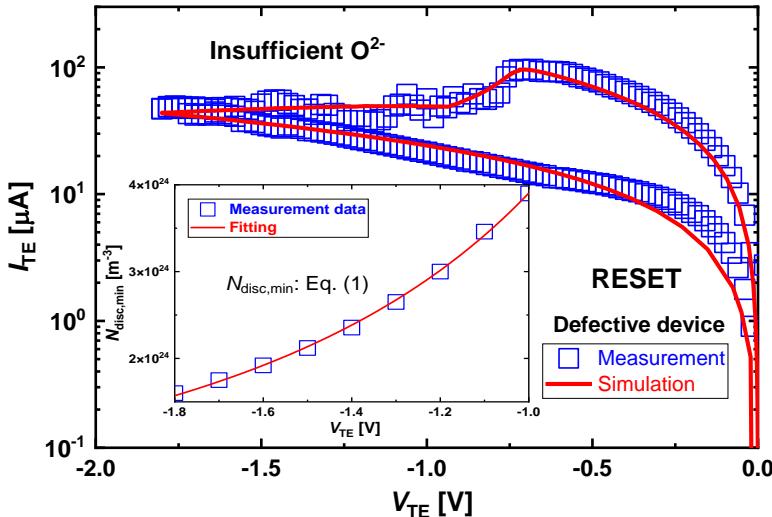

| 5.11 | The ion depletion defective device fitting in the logarithmic y-axis. . . . .                                                                                                                                             | 81 |

---

|                                                                                                                                                                                                                                                                                                                                                                                               |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

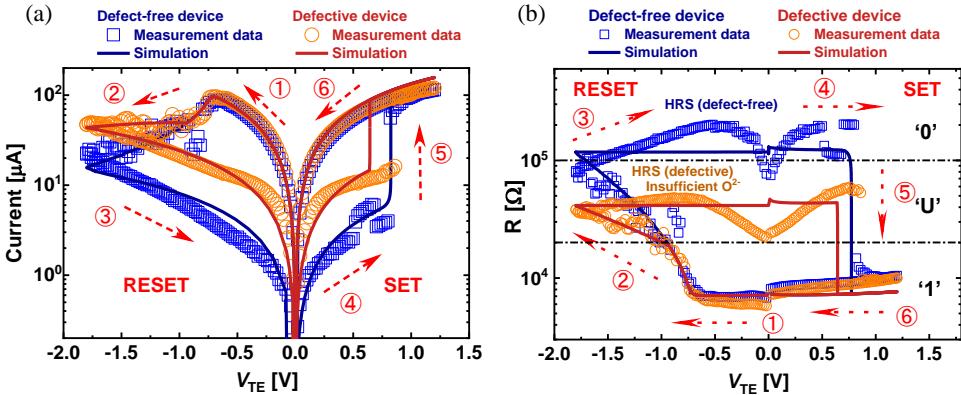

| 5.12 Defect-free and defective device simulation and measurements. (a) Simulation vs. measurements of the I-V curve, (b) Simulation vs. measurements of the R-V curve. . . . .                                                                                                                                                                                                                | 82  |

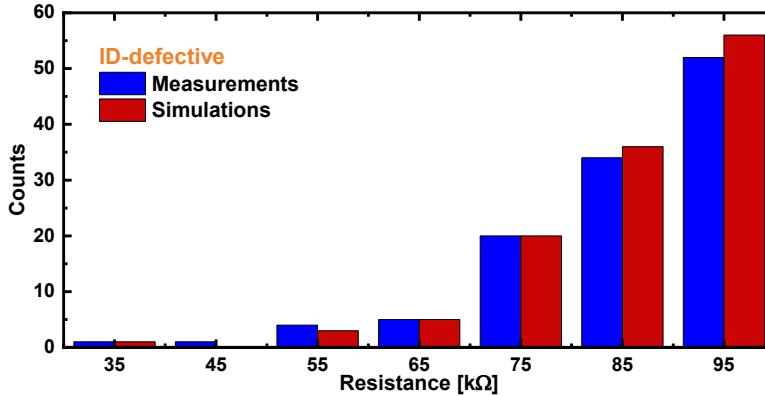

| 5.13 Histogram of defective $R_{RESET}$ distributions, measurements vs. simulations. . . . .                                                                                                                                                                                                                                                                                                  | 83  |

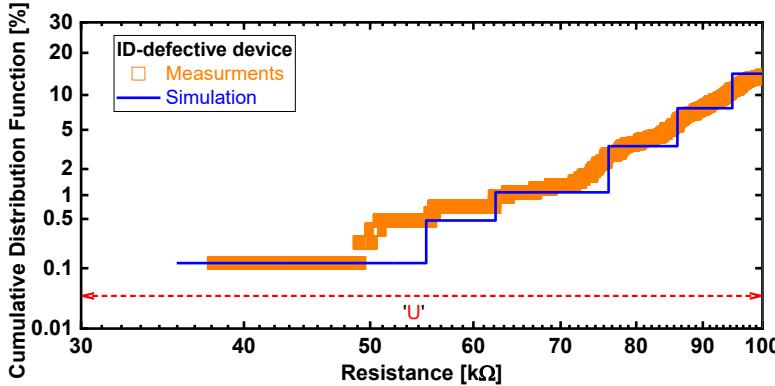

| 5.14 Cumulative probability of defective $R_{RESET}$ distributions, measurements vs. simulations. . . . .                                                                                                                                                                                                                                                                                     | 83  |

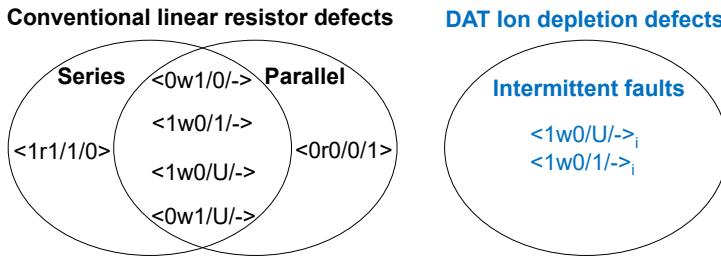

| 5.15 Static faults. . . . .                                                                                                                                                                                                                                                                                                                                                                   | 85  |

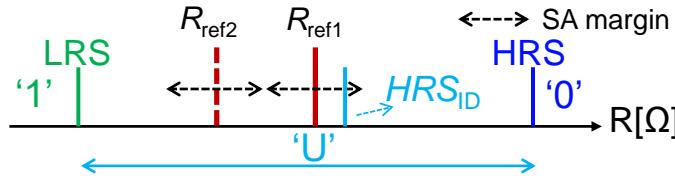

| 5.16 Resistances for faulty RRAM state. . . . .                                                                                                                                                                                                                                                                                                                                               | 86  |

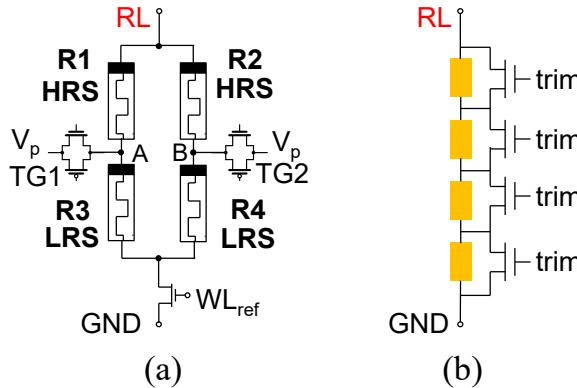

| 5.17 Reference resistance for DfT schemes. (a) Programmable reference cells, (b) Controllable reference trimming. . . . .                                                                                                                                                                                                                                                                     | 86  |

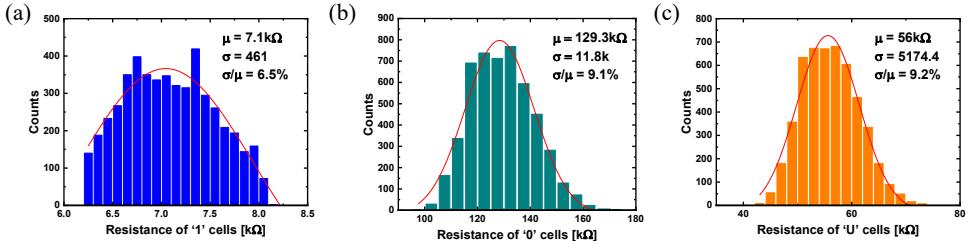

| 5.18 Histograms of the RRAM resistance distribution under variations. (a) Resistance of '1' cell (defect-free), (b) Resistance of '0' cell (defect-free), (c) Resistance of 'U' cell (ID-defective). . . . .                                                                                                                                                                                  | 88  |

| <br>                                                                                                                                                                                                                                                                                                                                                                                          |     |

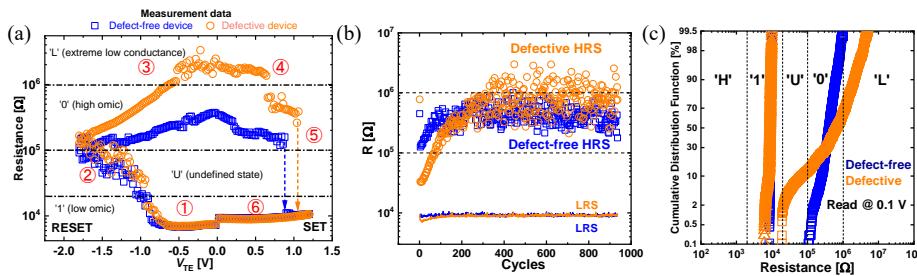

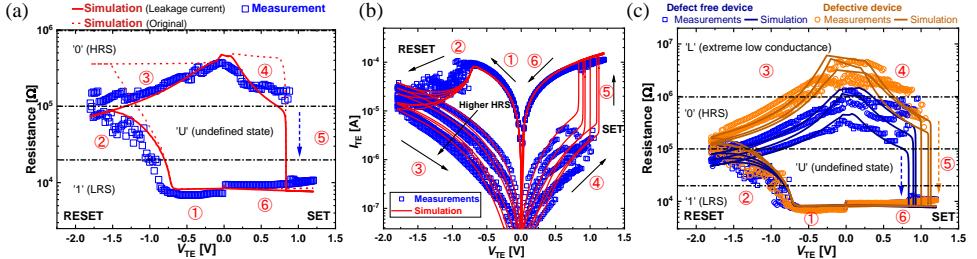

| 6.1 Comparing defect-free and defective devices. (a) Measured R-V curve in the logarithmic y-axis, (b) Measured $R_{RESET}$ and $R_{SET}$ in multiple (936) cycles, (c) Lognormal distributions of $R_{RESET}$ and $R_{SET}$ in multiple (936) cycles (read at 0.1 V). . . . .                                                                                                                | 93  |

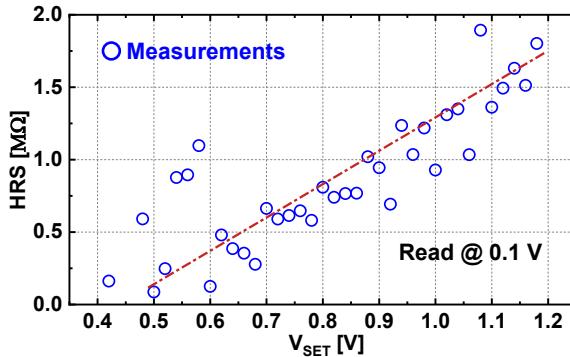

| 6.2 Dependence of $V_{SET}$ and HRS of the device during 936 cycles. . . . .                                                                                                                                                                                                                                                                                                                  | 93  |

| 6.3 Defect-free and defective device simulation and measurements. (a) The leakage current incorporated model fitting of the R-V curve, (b) Simulation vs. measurements of the I-V curve, (c) Simulation vs. measurements of the R-V curve. . . . .                                                                                                                                            | 96  |

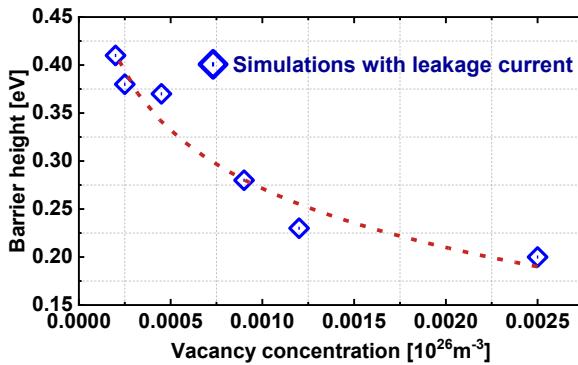

| 6.4 Reduced tunneling barrier height caused by OV concentration. . . . .                                                                                                                                                                                                                                                                                                                      | 96  |

| 6.5 Resistances for faulty RRAM state. . . . .                                                                                                                                                                                                                                                                                                                                                | 98  |

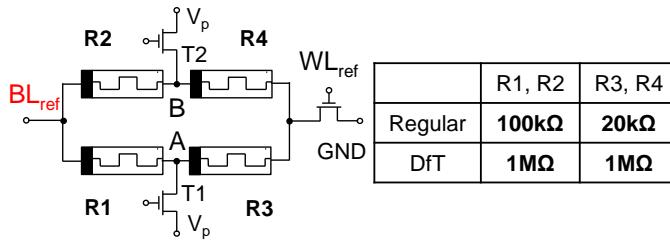

| 6.6 Modified reference cells. . . . .                                                                                                                                                                                                                                                                                                                                                         | 98  |

| <br>                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 7.1 Fault classification depends on functionality and permanent nature. . . . .                                                                                                                                                                                                                                                                                                               | 103 |

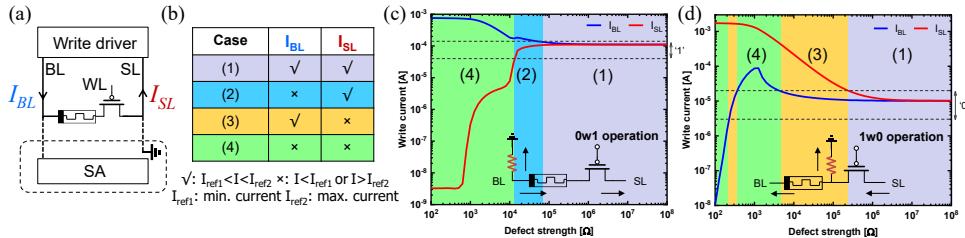

| 7.2 The concept of $I_{BL}$ and $I_{SL}$ conditions during the write operation. (a) The circuit high-level overview, (b) Four conditions of $I_{BL}$ and $I_{SL}$ , (c) $I_{BL}$ and $I_{SL}$ behavior as a function of one short defect located at the BL node, (d) $I_{BL}$ and $I_{SL}$ behavior as a function of one short defect located at the RRAM/transistor interconnection. . . . . | 105 |

| 7.3 The flow chart of the proposed DfT process. . . . .                                                                                                                                                                                                                                                                                                                                       | 106 |

| 7.4 Modified write driver circuit acting as DfT. . . . .                                                                                                                                                                                                                                                                                                                                      | 107 |

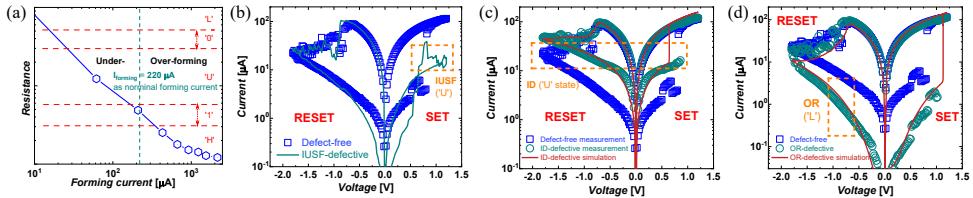

| 7.5 Targeted unique defects. (a) Characterization of forming defects [59], [106], (b) Comparison of IUSF-defective and defect-free devices [214], (c) Comparison of ID-defective and defect-free devices [65], (d) Comparison of OR-defective and defect-free devices [66]. . . . .                                                                                                           | 110 |

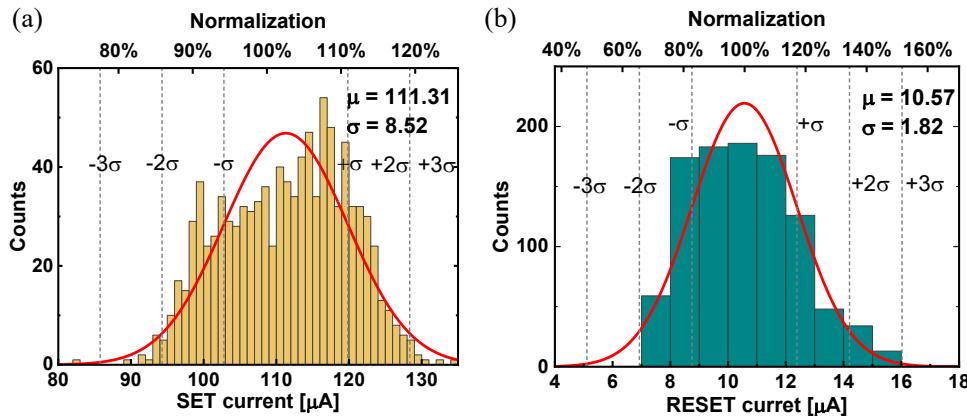

| 7.6 Histograms of the current distribution of defect-free circuit under variations. (a) SET ( $0w1$ ) current, (b) RESET ( $1w0$ ) current. . . . .                                                                                                                                                                                                                                           | 111 |

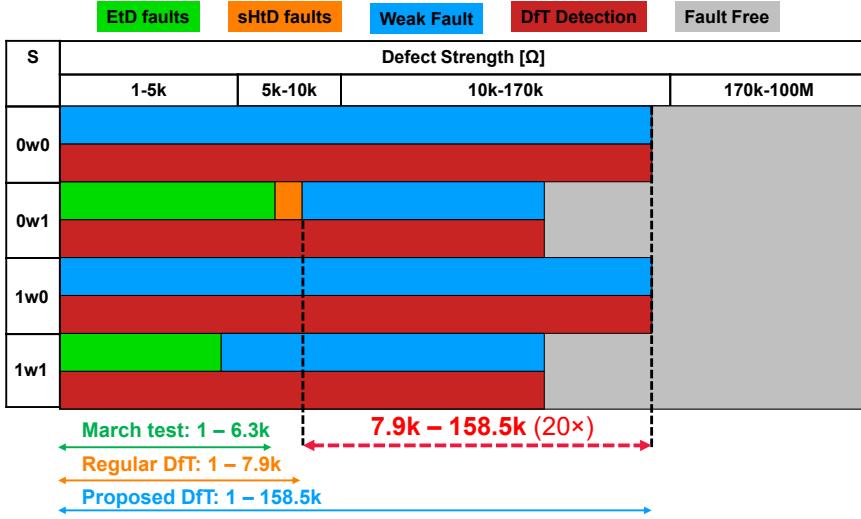

| 7.7 Fault map and detection range for defect cBCC4. . . . .                                                                                                                                                                                                                                                                                                                                   | 112 |

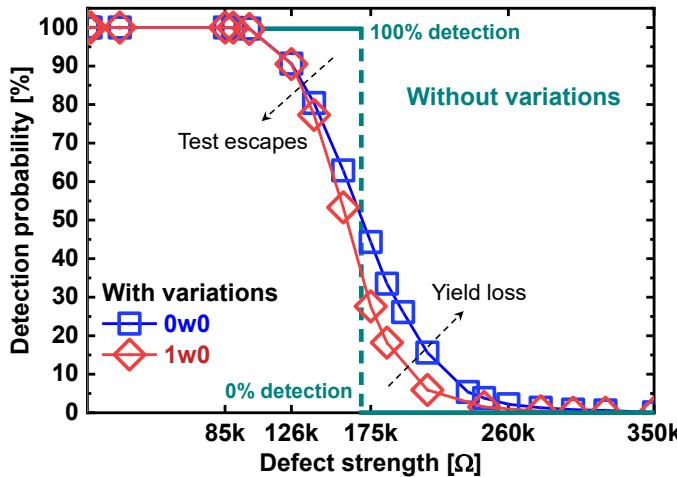

| 7.8 Variation analysis for defect cBCC4. . . . .                                                                                                                                                                                                                                                                                                                                              | 113 |

| <br>                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 8.1 Experiments [259]. (a) Forward read in SET direction, (b) Backward read in RESET direction. . . . .                                                                                                                                                                                                                                                                                       | 117 |

|                                                                                                                                                     |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.2 The resistance changes when performing forward and backward read operations. . . . .                                                            | 118 |

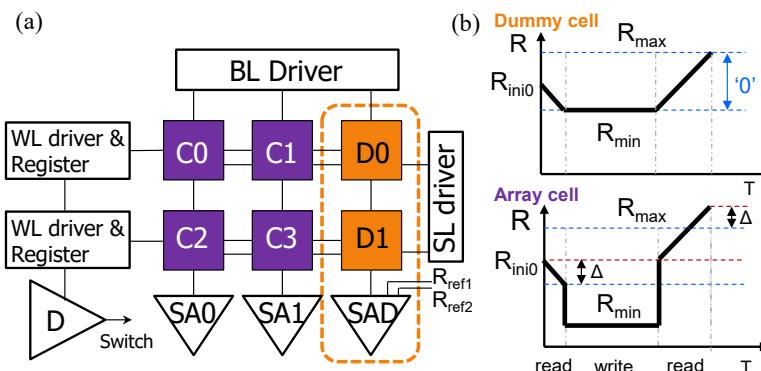

| 8.3 The bi-directional read circuit with alternate current paths shown in red and blue. . . . .                                                     | 119 |

| 8.4 Read cycle distribution across DNN array. . . . .                                                                                               | 120 |

| 8.5 The high-level implementation of the in-field test approach. . . . .                                                                            | 120 |

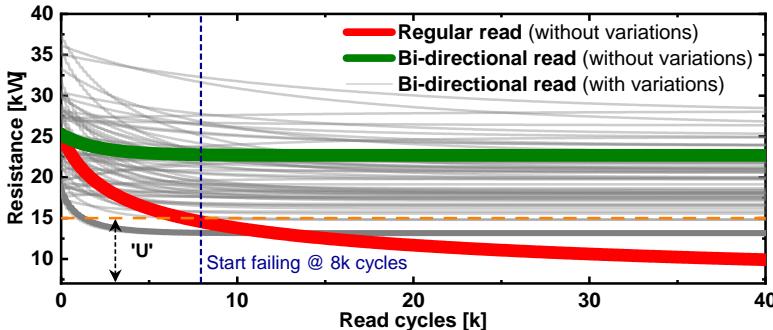

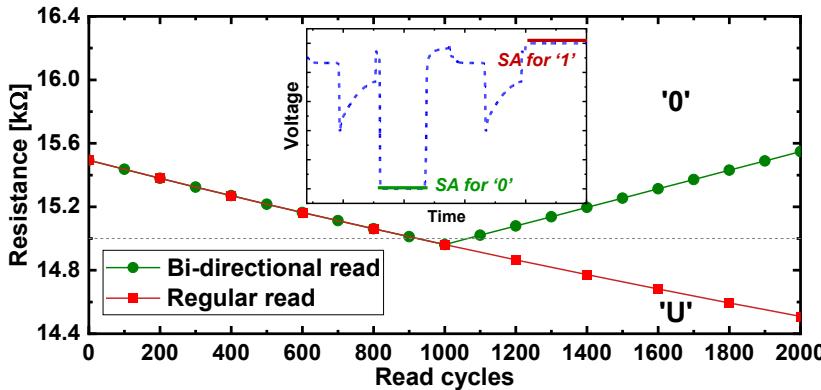

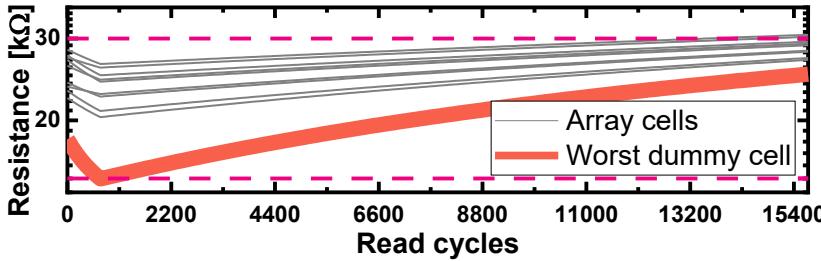

| 8.6 Resistance drifts for bi-directional read compared to regular read. . . . .                                                                     | 121 |

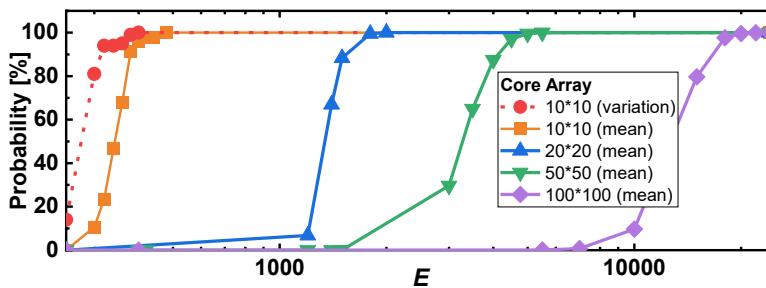

| 8.7 The probability of counting cells with RDF. . . . .                                                                                             | 122 |

| 8.8 The effectiveness of the in-field test and repair approach. . . . .                                                                             | 123 |

| 8.9 The worst case of the dummy cell setting with variations. . . . .                                                                               | 123 |

| 8.10 Inference accuracy enhancement by bi-directional read approaches. . . . .                                                                      | 124 |

| <br>                                                                                                                                                |     |

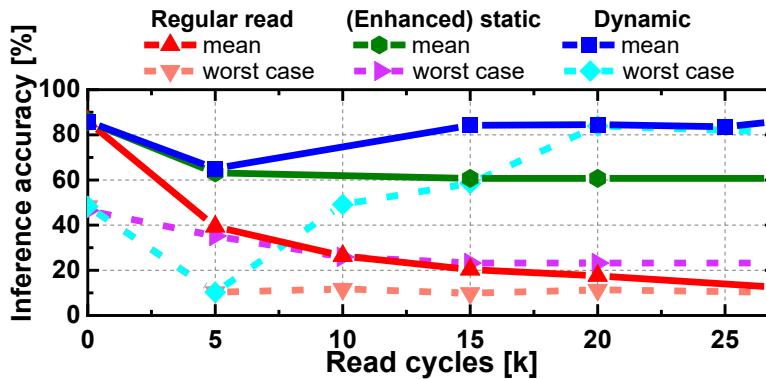

| 9.1 Framework of RRAM test and diagnosis development: (a) DAT process, (b) DA-diagnosis process. . . . .                                            | 129 |

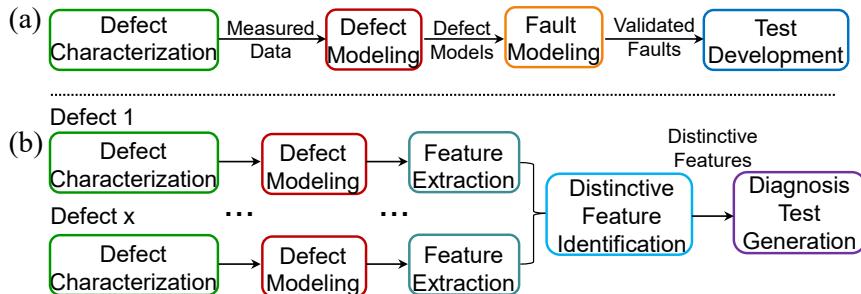

| 9.2 Physical mechanism of defects. (a) Conventional defects [43], [52], (b) Forming defects [59], (c) IUSF [214], (d) OR [66], (e) ID [65]. . . . . | 130 |

| 9.3 Characterization of defect-free and ID-defective device: (a) I-V measurement, (b) R-V measurement. . . . .                                      | 131 |

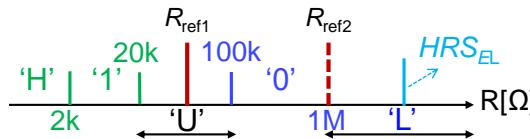

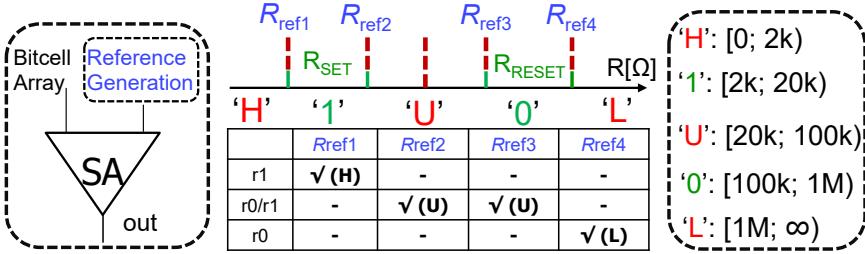

| 9.4 Reference settings and resistance state specifications. . . . .                                                                                 | 134 |

| 9.5 Diagnosis for forming defects. . . . .                                                                                                          | 135 |

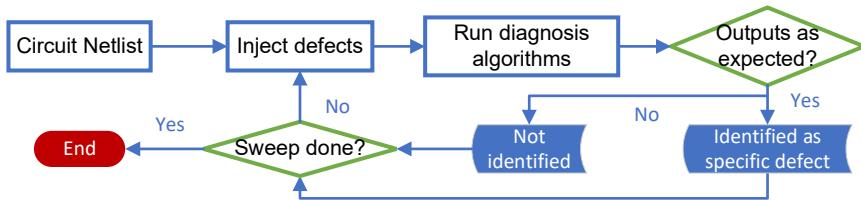

| 9.6 Flow chart of diagnosis algorithm verification. . . . .                                                                                         | 136 |

| <br>                                                                                                                                                |     |

| 10.1 Static fault analysis. . . . .                                                                                                                 | 143 |

| 10.2 Dynamic fault analysis without variations. . . . .                                                                                             | 144 |

| 10.3 Dynamic fault analysis with full variability model. . . . .                                                                                    | 145 |

| 10.4 Systematic and complete approach for the RRAM testing. . . . .                                                                                 | 151 |

# LIST OF TABLES

|      |                                                                                                                                                                                                                                                                                             |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1  | The benchmark of OxRAM vs CBRAM [35]. . . . .                                                                                                                                                                                                                                               | 9   |

| 1.2  | Comparison of conventional and emerging memories [10], [36]. . . . .                                                                                                                                                                                                                        | 10  |

| 2.1  | Evaluation of various RRAM compact models based on [109]. . . . .                                                                                                                                                                                                                           | 24  |

| 2.2  | Summary of RRAM prototypes from different institutions and companies. . . . .                                                                                                                                                                                                               | 33  |

| 3.1  | Overview of RRAM manufacturing defects across different process stages. . . . .                                                                                                                                                                                                             | 42  |

| 4.1  | Static coupling fault primitives. . . . .                                                                                                                                                                                                                                                   | 56  |

| 4.2  | Fault map for dBCC1 defect.    . . . . . | 58  |

| 4.3  | Fault map for rBCC1 defect. . . . .                                                                                                                                                                                                                                                         | 60  |

| 4.4  | Example to solve the DB-ILP. . . . .                                                                                                                                                                                                                                                        | 63  |

| 4.5  | Test algorithm validation map for rBCC1 defect. . . . .                                                                                                                                                                                                                                     | 65  |

| 4.6  | Test comparison with existing RRAM tests. . . . .                                                                                                                                                                                                                                           | 66  |

| 5.1  | Occurrence probability of ID ( $P_{ID}$ ) in % and maximal duration suffering from ID ( $D_{max}$ ), during 536 cycles. . . . .                                                                                                                                                             | 72  |

| 5.2  | Model parameters for JART VCM v1b [110]. . . . .                                                                                                                                                                                                                                            | 80  |

| 5.3  | Fault analysis results for ion depletion defect. . . . .                                                                                                                                                                                                                                    | 84  |

| 6.1  | Model parameters for JART VCM v1b [110]. . . . .                                                                                                                                                                                                                                            | 95  |

| 6.2  | Fault modeling results for OR defect. . . . .                                                                                                                                                                                                                                               | 97  |

| 7.1  | Targeted fault detection capabilities of existing tests for RRAMs. . . . .                                                                                                                                                                                                                  | 105 |

| 7.2  | Results of the MC analysis for defect cBCC4. . . . .                                                                                                                                                                                                                                        | 112 |

| 7.3  | The output and detection of proposed Dft for unique defects. . . . .                                                                                                                                                                                                                        | 114 |

| 9.1  | Feature dictionary of targeted defects. . . . .                                                                                                                                                                                                                                             | 132 |

| 9.2  | Overview of diagnosis for unique defects. . . . .                                                                                                                                                                                                                                           | 134 |

| 9.3  | Validation with OF-defective cell as an example. . . . .                                                                                                                                                                                                                                    | 136 |

| 10.1 | Overview of unique defects. . . . .                                                                                                                                                                                                                                                         | 141 |

| 10.2 | Collapsed fault set for conventional defects in RRAM array. . . . .                                                                                                                                                                                                                         | 143 |

| 10.3 | Overview fault set for unique defects. . . . .                                                                                                                                                                                                                                              | 145 |

| 10.4 | Collapsed fault set for interconnect and contact defects in peripherals. . . . .                                                                                                                                                                                                            | 146 |

| 10.5 | EtD fault detection capability of existing March tests for RRAMs. . . . .                                                                                                                                                                                                                   | 147 |

| 10.6 | Dft classification based on the applied operation (read or write) and the mode of application. . . . .                                                                                                                                                                                      | 149 |

| 10.7 | Dft classification depending on targets. . . . .                                                                                                                                                                                                                                            | 149 |

|                                                                         |     |

|-------------------------------------------------------------------------|-----|

| 10.8 Overview and evaluation of existing DfT designs for RRAMs. . . . . | 150 |

|-------------------------------------------------------------------------|-----|

# 1

## INTRODUCTION

*Resistive Random Access Memory (RRAM) has emerged as one of the leading non-volatile memory technologies, with commercial products coming after more than 40 years of research and development. As companies start ramping up efforts toward commercialization, the need for effective and cost-efficient testing solutions has become critical in ensuring the high quality of RRAM products. This dissertation focuses on investigating manufacturing defects introduced during RRAM fabrication, deriving corresponding fault models, and developing robust test solutions. The first chapter of this dissertation presents an introduction of the dissertation, including 1) a review of emerging non-volatile memory technologies; 2) an in-depth look at RRAMs, 3) the principles and philosophies of memory testing, 4) the research objectives and contributions of this thesis, and 5) an outline of the dissertation structure.*

## 1.1. EMERGING MEMORY TECHNOLOGIES

This section introduces the emerging memory technology, which is the research target of this dissertation. First, we describe the memory hierarchy and the motivation to develop emerging memories. Then, we introduced various types of emerging memories individually and overview the potential applications.

### 1.1.1. MEMORY WALL AND HIERARCHY

Figure 1.1: The memory hierarchy in computer systems.

The conventional digital computing hardware features physically separated processing and memory units [1]. The frequent and massive data movement between these units leads to time latency and power consumption penalties, the so-called Von Neumann bottleneck [2]–[4]. This is also known as the memory wall problem in von Neumann architecture due to the difference in the processing speed of the calculator and memory. Besides, the past development of digital electronics is primarily fueled by transistors' scaling, which is becoming increasingly cost-ineffective as a transistor's size approaches its physical limits [5], [6]. Therefore, fundamental changes to the paradigm of computing systems are critical.