# Design of a Fully Integrated CMOS Highly Temperature Stable Frequency Reference

**Tsiolis Georgios**

<u>Master Program:</u> Microelectronics

Delft University of Technology

<u>Supervisors:</u> Wouter A. Serdijn Arie Van Staveren Frank Kuijstermans

<u>Location:</u> National Semiconductor (Texas Instruments),

Delft Design Center

Period: summer 2010-autumn 2011

This essay contains all the results of the graduation project for the MSc program in Microelectronics that I followed at Delft University of Technology (August 2009-November 2011). The work presented here was conducted and completed in the Delft Design Center of the company National Semiconductor (already since October 2011 acquired by Texas Instruments) on a project of designing a frequency reference with low frequency drift over temperature deviations.

Tsiolis Georgios November 2011

## Contents

|           | Abstract                                                         | 1  |  |  |  |  |  |

|-----------|------------------------------------------------------------------|----|--|--|--|--|--|

|           | Acknowledgements                                                 | 2  |  |  |  |  |  |

| Chapter 1 | Introduction                                                     | 5  |  |  |  |  |  |

| Chapter 2 | Specifications requested and what is already available           |    |  |  |  |  |  |

|           | 2.1 Journey through the history of clock references              | 7  |  |  |  |  |  |

|           | 2.2 Numerical achievements, by university publications           | 8  |  |  |  |  |  |

|           | 2.3 Numerical achievements, by company products                  | 9  |  |  |  |  |  |

|           | 2.4 Placement of the requirements, expectations by our choices   | 9  |  |  |  |  |  |

| Chapter 3 | Oscillator design, The basic idea-topology and high level design |    |  |  |  |  |  |

|           | 3.1 Introduction                                                 | 11 |  |  |  |  |  |

|           | 3.2 Creating a periodical signal                                 | 12 |  |  |  |  |  |

|           | 3.2.1 Components Needed                                          | 12 |  |  |  |  |  |

|           | 3.2.2 Signal choices                                             | 13 |  |  |  |  |  |

|           | 3.3 Different topologies                                         | 14 |  |  |  |  |  |

|           | 3.3.1 Two thresholds oscillator                                  | 14 |  |  |  |  |  |

|           | 3.3.2 One threshold oscillator                                   | 15 |  |  |  |  |  |

|           | 3.4 Pros and cons of the various implementations                 | 16 |  |  |  |  |  |

|           | 3.4.1 Problems that occur in real life signals                   | 16 |  |  |  |  |  |

|           | 3.4.2 Comparing the several implementations                      | 17 |  |  |  |  |  |

|           | 3.4.2.1 Mathematical expressions for the first implementation    | 18 |  |  |  |  |  |

|           | 3.4.2.2 Mathematical expressions for the second implementation   | 22 |  |  |  |  |  |

|           | 3.4.2.3 Mathematical expressions for the third implementation    | 23 |  |  |  |  |  |

|           | 3.4.2.4 Mathematical expressions for the fourth implementation   | 25 |  |  |  |  |  |

|           | 3.5 Final choice and canceling the inherent imperfections        | 27 |  |  |  |  |  |

|           | 3.5.1 New implementation design                                  | 27 |  |  |  |  |  |

|           | 3.5.2 Mathematical expressions for the new design                | 30 |  |  |  |  |  |

|           | 3.5.3 Imperfections and ways to cancel them                      | 33 |  |  |  |  |  |

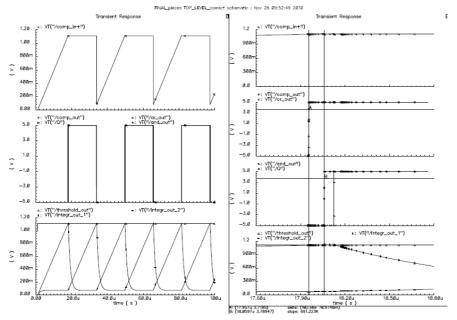

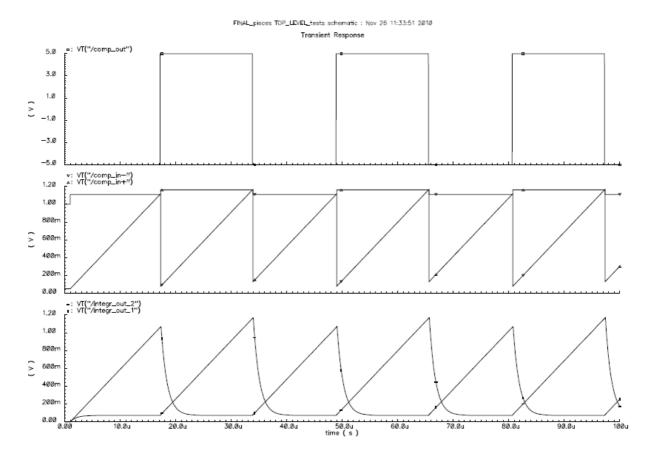

|           | 3.6 Cadence simulations                                          | 35 |  |  |  |  |  |

| Chapter 4 | Design of the stages of the oscillator                           |    |  |  |  |  |  |

|           | 4.1 Threshold(s), integrator                                     | 39 |  |  |  |  |  |

|           | 4.1.1 Need for constant voltage                                  | 39 |  |  |  |  |  |

|           | 4.1.2 Integrator, correct "zero" voltage                         | 39 |  |  |  |  |  |

|           | 4.1.3 Threshold                                                  | 41 |  |  |  |  |  |

|           | 4.1.4 Copying the current                                        | 42 |  |  |  |  |  |

|           | 4.2 Decision point 1 = logic gates, Switches                     | 47 |  |  |  |  |  |

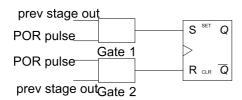

|           | 4.3 Memory                                                       | 48 |  |  |  |  |  |

|           | 4.4 Comparator design                                            | 50 |  |  |  |  |  |

| Chapter 5 | Final decisions and layout generation                            |    |  |  |  |  |  |

| ·         | 5.1 Remaining issues and choices                                 | 55 |  |  |  |  |  |

|           | 5.2 Output stage and input choices                               | 59 |  |  |  |  |  |

|           | 5.3 Issues not addressed                                         | 60 |  |  |  |  |  |

|           | 5.4 Layout                                                       | 61 |  |  |  |  |  |

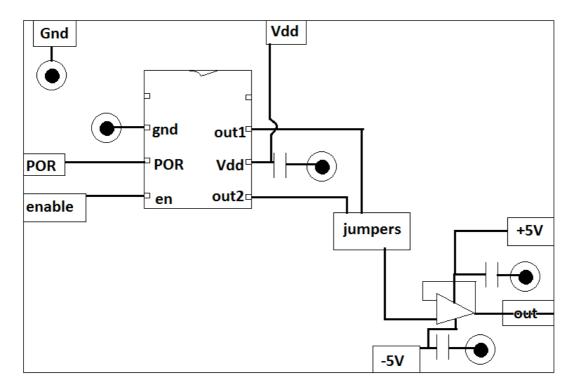

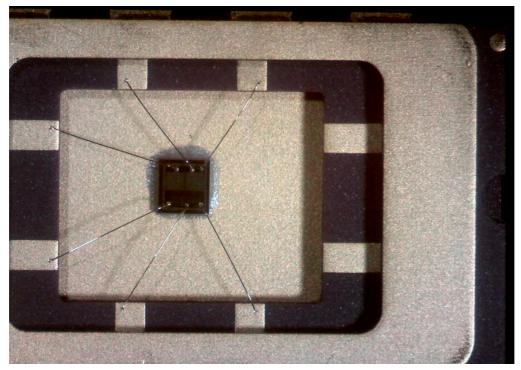

|           | 5.5 Measurements procedure                                       | 63 |  |  |  |  |  |

| Chapter 6 | Simulations VS Measurements                                      |    |  |  |  |  |  |

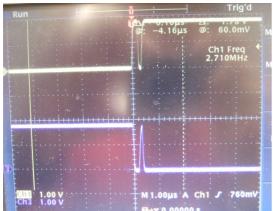

|           | 6.1 Time                                                         | 65 |  |  |  |  |  |

|           | 6.2 Voltages                                                     | 65 |  |  |  |  |  |

|            | 6.3 Currents                                   | 66 |  |  |  |  |

|------------|------------------------------------------------|----|--|--|--|--|

|            | 6.4 Phase Noise                                | 66 |  |  |  |  |

|            | 6.5 Supply                                     | 67 |  |  |  |  |

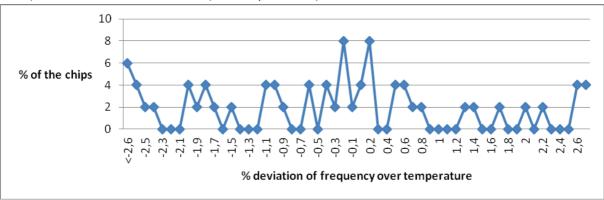

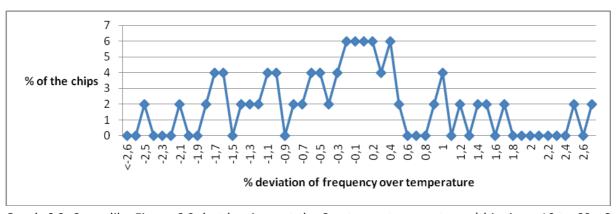

|            | 6.6 Over temperature                           | 67 |  |  |  |  |

|            | 6.7 Unexpected findings                        | 69 |  |  |  |  |

| Chapter 7  | Conclusion and Recommendations                 |    |  |  |  |  |

|            | 7.1 Contributions                              | 77 |  |  |  |  |

|            | 7.2 The Outcome compared to the Specifications | 78 |  |  |  |  |

|            | 7.3 Recommendations                            | 79 |  |  |  |  |

| Appendix   |                                                | 81 |  |  |  |  |

| References |                                                | 87 |  |  |  |  |

### **Abstract**

A new fully integrated frequency reference has been designed, fabricated and measured. The goal of the design procedure has been high stability of the frequency over temperature variations. This should be achieved using a CMOS technology without MEMS and crystals, while being restricted by a very low power budget. The frequency is designed based on an RC time constant, where both R and C are integrated on chip. The novel topology is minimizing the sources of error that affect the frequency being produced (minimum offsets and delays that spread over temperature). According to the simulations, the fabricated oscillator is a competitive one among the RC-time-constant based ones, but the measurements showed that the tradeoff between performance and integration (accompanied with power minimization) is worse than its counterparts (MEMs based or LC based all-silicon choices), or its quartz crystal based ancestor. Ways to increase the quality even further are proposed.

## Key words

Fully integrated, CMOS, all silicon, highly temperature stable, frequency reference, clock, RC time constant, no PLL, no MEMS, low power.

## Acknowledgements

"Music is all about beautifying the ugly sounds, resolving the sound collisions", my music teacher and mentor **Foivos Papadopoulos** used to say. He was right, for a continuous stream of harmonic sounds is plain boring, it sounds as if it lacks passion. Thereafter, as I was growing up, I found out that the same holds for life. The only person you should completely agree with is the one that shows up in your mirror. Conversation promotes disputes and inevitable opinion-collisions and conversation is the only way to resolve them. Resolving them is the beauty of life and human interaction. Hence, life is art, isn't it?

What about studying/teaching then? Things get complicated in this field. "Constructive criticism" is very close to "destructive criticism" and there are very few professors that can manage to encourage their students to study through constructive criticism. The majority chooses either the "fun" approach - never scold, only tender push, only with a smile and by being nice, or the ignorant approach - "your duties are described in this piece of paper, perform them or not, it's up to you". Out of those who choose the criticism way, most mess it up and end up being considered impolite or simply annoying.

I can safely conclude that the Dutch way didn't suit me - at first. Dutch lifestyle is based upon harmonious situations. Divide and conquer. "This is your life in the living room, so I don't care if you have no curtains. Live your life as long as it doesn't bother me, and I won't care what you do". This is reflected on professors as well. A professor will ask you to do what you should, always with a smile, but will not pressure you- pressure would be intrusion in your life, and that's not Dutch at all. The tender approach, which means never making you feel bad by showing you your flaws (which is by the way the basis of criticism), makes me feel bored and less productive.

In other words, I wasn't used to setting my environment in a free space, but adjusting it according to the limitations proposed/imposed by others. May they have been colleagues with whom we shared the journey of a yearly thesis project working chair by chair (Elena Papadomanolaki), or friends editing my stories, my babies, with comments that may hurt sometimes, but they are so constructive and educational (Marina Simini), or friends teaching me good manners - that's life in the adult world (Maria Tzedaki). I usually didn't have to criticize myself. I received the correct amount of criticism from around me and was resetting myself when necessary.

So did I receive a "lesser" lesson, overall, here in the Netherlands? Not at all. I learned how to operate in such a new environment the hard way. New style (Dutch) new place (Work) new age approach (Colleagues were on average in the middle between mine and my dad's age). Considering this recent past, **Arie van Staveren** deserves to be the first to be acknowledged. He is the man in charge at the company where I performed my research, and it came as a surprise to me how someone as knowledgeable as he is can be so accessible, fun even, and all his positive traits make him very special. **Frank Kuijstermans** and everyone else in the Delft Design Center of National Semiconductor (now Texas Instruments) who helped me along the way one way or the other are people I am thankful to. Last but not least, my connection to the university, **Wouter Serdijn**, whose wise and continuous guidance made things roll with this project.

I was lucky enough to be given great opportunities and be surrounded by charismatic and approachable people. I was foolish enough to make use of these people's kindness less than I could-

and sometimes less than I was asked to (!), and foolish enough to exploit my chances far from the maximum. But I am happy I understood my mistakes after literally months of struggling, and I'm ready for an even more constructive next step - wherever in the world that may be, even in a place with "Dutch mentality", the Netherlands obviously included.

But all work and no play, makes Jack a dull boy. Friends with whom I spent most of my free time the last years - travelling to Stockholm, Rome, New York, Washington, Antwerp, Brussels, and having endless over-beer-and-food discussions all over the Netherlands, especially in Rotterdam, Delft and Den Haag, will be held dear in my heart forever.

In conclusion, I want to thank everyone who added diversity to my life, and made it interesting, and I hope I gave something back in return. I want to thank those who helped me become a better person, and a better scientist. Those who created the collisions that made my life interesting by trying to smooth them. Some still need fixing, but that's upon the years to come.  $1\delta\omega\mu\epsilon\nu$ .

Γεώργιος Τσιώλης Georgios Tsiolis 1<sup>st</sup> of November, 2011

PS Family. Family was a skype/voip discount part of my life the last 2 years, as well as my friends back in Greece - and the USA (**Panos Papadatos**). It seems like their contribution was minor, but that's simply because when someone has got your back, you often take them for granted and ignore (forget?) them. I won't. I will tell you how much you all meant to me by keeping me rooted somewhere. There. Thank you all.

## **Chapter 1**

## Introduction

The goal of this project has been to design a frequency reference with the following three important characteristics:

- Very good frequency stability over varying temperatures (100ppm stability for a temperature deviation of more than 100oC)

- Very low current consumption (less than 100μA).

- No use of quartz crystal

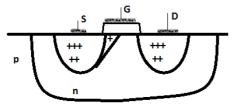

The design should be all silicon, in a CMOS technology in order to be fabricated easily on the same wafer with the rest of the chips needed for mobile phones, using a 1.8 V supply. The reason for the "no quartz crystal" specification is the general trend of trying to get rid of all non integrated components in electronic devices. Unfortunately nowadays, the most stable frequency references are based on crystals, so an external bulky off-chip component is needed. The reason for the low power consumption is the extension of battery life, and the high stability of frequency over changing temperatures is imposed by the demand for stable and robust driving of the digital circuitry in order to keep up correct operation of our device in all environments possible.

The essay is structured as follows. First all the strong points and weaknesses of the different existing approaches to such an all-silicon oscillator (MEMS based, RC time constant based or LC oscillators) will be discussed and one will be chosen to be implemented (Chapter 2).

After this choice, all steps of the design were met: high level design (system level in Chapter 3), implementation of the several parts (Chapter 4), final decisions and layout of the whole design (Chapter 5), measuring the chips after they came back from the factory, along with a comparison between measurements and simulation results (Chapter 6). All this procedure lasted 14 months, starting August 2010 and finishing October 2011. Conclusions for this design procedure and further improvements are analyzed in the end (Chapter 7).

Chapter 1: Introduction

### **Chapter 2**

## Specifications requested and what is already available

#### 2.1 Journey through the history of clock references

The history of electronic oscillators (clock references) started 60 years ago. The basic steps in this journey were the development of crystal oscillators "XO", by making use of the piezoelectric effect that couples the mechanical properties of the crystal with an electrical circuit [2], the introduction of transistors instead of vacuum tubs for the surrounding circuitry, the achievement of developing temperature compensated crystal oscillators "TCXO" (where the compensation was achieved over the years with many different ways), and nowadays the attempts for all silicon clocks, without the use of crystals, but using MEMS, RC time constant, or just the LC oscillation principle. Size has been continuously reducing several orders of magnitude, while accuracy –surprisingly- not much, only a couple orders of magnitude, with the oldest manufactured and perfected choice (quartz crystal based oscillator) still beating its rising opponents.

In the 50's already, very accurate ovenized crystal frequency references were created, using vacuum tubes for the surrounding circuitry and one oven for keeping the temperature of the crystal stable. Also, when possible, the circuitry was also added within the oven to keep same conditions for everything contributing to the frequency.

Further improvement in the stability of the generated frequency was made when it was noticed how important the orientation in which the crystal was being cut was. It was found already really early (1937, Bell Labs, [1]) that a GT-cut crystal had a temperature coefficient that remained practically zero over a large temperature range. So using a GT quartz crystal, double oven and vacuum tubes, a crystal resonator was developed in 1951 of accuracy in the level of  $10^{-3}$ [1].

After transistors became widely used (60's), the accuracy increased dramatically also because now the whole circuitry could be easily placed within the oven, thanks to the very small size of transistors. So already in the early 60's a 5MHz clock with accuracy of 5\*10<sup>-10</sup> burning 25Watts and size of approximately 10000cm<sup>3</sup> was developed[1]. Another improvement (during the 70's) was the introduction of power transistors as heating elements instead of resistance elements. That reduced dramatically the power being consumed. At that time mainly SC-cut crystals were being used and over wide temperature range, stability in the order of 10<sup>-9</sup> was achieved [1].

A different choice than using crystals in ovens, was to create temperature compensated crystal oscillators. In this case, varactor diodes are being used to transform the temperature behavior of the crystal into voltage, and then a thermistor network to match it and cancel it out, at least in temperature blocks, each block considered having linear behavior. Usually there were 3 different thermistor networks used, one for low, one for medium and one for high temperatures. Results of this method were to achieve accuracy of 5\*10<sup>-7</sup> over a huge temperature range [1].

This temperature compensation has changed forms within the last decades, of course going towards digital compensation, like a memory pre-programmed with the required compensation voltages, or a microcomputer implementing this digital compensation, or using dual excitation for more accurate control over the measurements, reaching 10<sup>-8</sup> accuracy, or even using external (off chip) compensation.

Nowadays the temperature controlled crystal oscillators are being produced in the accuracy level of  $10^{-8}$ [1]. Ultra stable ones go up to  $10^{-10}$  accuracy [3].

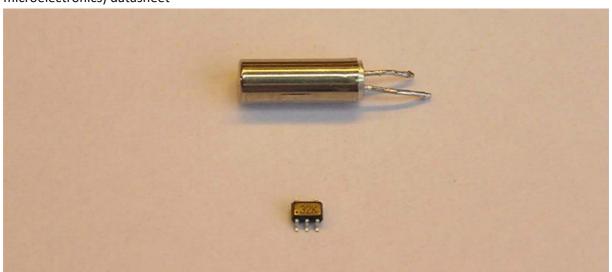

Last novelty, is every attempt to get rid of the crystal needed for the clock, and this has been achieved in several different ways, resulting in many different Silicon Oscillators. These all silicon oscillators conquer the crystal ones in terms of robustness to vibration, humidity, resistance to EMI effects and shock, not to mention the easier (on-wafer) production, which gains in size, cost and time. A photo comparing the two choices (an all silicon oscillator with one the uses a crystal) can be seen in appendix, A.1. Using a MEMS resonator, clocks were designed that had a frequency stability over temperature of 10<sup>-5</sup> [4], but the fact that MEMS are not CMOS compatible doesn't make them the first and most beloved choice. Using temperature compensated LC oscillators and then dividing that frequency to user-programmable range we see frequency stability accurate in the scale of 10<sup>-5</sup> [5]. Finally using internal RC constants the accuracy achieved over temperature remains in the range of few percent (10<sup>-2</sup>).

Applications where clock references (oscillators) are necessary are all digital circuitry that needs synchronizing, internet Ethernet connections, smart cards, peripheral communication like USB connection ports, flash drives, card readers, microcontroller references, microprocessor clock applications, display drivers, advanced battery chargers and many more.

#### 2.2 Numerical achievements, by university publications.

Some of the oscillators published in papers originating from university research are presented in Matrix 2.1.

Matrix 2.1: Oscillators published by universities, one Crystal based and many all-Si alternatives.

| Туре               | Freq (Hz) | Temp stability over  | Supply | Current | Comments             | Reference |

|--------------------|-----------|----------------------|--------|---------|----------------------|-----------|

|                    |           | 100oC(-20oC to       | (V)    | (A)     |                      |           |

|                    |           | 80oC approx)         |        |         |                      |           |

| Crystal (ovenized) | -         | ±2*10 <sup>-11</sup> | -      | -       |                      | [3]       |

| Fully integrated   | 50M       | ±1*10 <sup>-6</sup>  | 3.3    | 8m      | The LC oscillator is | [7]       |

| LC oscillator &    |           |                      |        |         | accompanied with     |           |

| divider            |           |                      |        |         | temp compensation    |           |

| Bypassed RC-time   | 100k-100M | 0.5*10 <sup>-4</sup> | 3.3    | -       |                      | [9]       |

| based *1           |           |                      |        |         |                      |           |

| RC-time based      | -         | ±1*10 <sup>-3</sup>  | 3.3    | -       | Uses current         | [10]      |

|                    |           |                      |        |         | reference, temp      |           |

|                    |           |                      |        |         | compensated up to    |           |

|                    |           |                      |        |         | second order.        |           |

| Bypassed RC-time   | 14M       | ±2*10 <sup>-3</sup>  | 1.8    | 25u     |                      | [19]      |

| based *1           |           |                      |        |         |                      |           |

| Bypassed RC-time   | 250k-1M   | ±5*10 <sup>-3</sup>  | 3.3    | 400u    | Requires an ideal    | [8]       |

| based *1           |           |                      |        |         | external resistor    |           |

| Ring oscillator    | 7M        | ±5*10 <sup>-3</sup>  | -      | -       |                      | [18]      |

| Ring oscillator    | 224M-974M | 8.6*10 <sup>-3</sup> | -      | 8.3m    |                      | [12]      |

| CMOS, RC based     | 16M       | ±2*10 <sup>-2</sup>  | 1.8    | -       |                      | [11]      |

<sup>\*1</sup> Bypassed RC time based oscillator implies (as will be analyzed in Chapter 7) an oscillator whose frequency is produced based on an RC time constant but this core is bypassed by a "master" sub-

network that is responsible for the accuracy of the produced frequency by controlling something in the RC network.

### 2.3 Numerical achievements, by company products

Some of the products (oscillators) by various companies are presented in Matrix 2.2.

Matrix 2.2: Company commercial oscillators, one crystal and many all-silicon alternatives.

| Product        | Туре          | Freq (Hz) | Temp stability           | Supply  | Current | Comments         |

|----------------|---------------|-----------|--------------------------|---------|---------|------------------|

| Name           |               |           | over 100oC(-20oC         | (V)     | (A)     |                  |

|                |               |           | to 80oC approx)          |         |         |                  |

| DS32B35        | Crystal (temp | 32k       | ±6*10 <sup>-6</sup>      | 3.3     | 260u    |                  |

| (Maxim)        | compensated)  |           |                          |         |         |                  |

| Si500S         | All Si        | 900k-200M | ±2*10 <sup>-5</sup>      | 1.8-3.3 | 10m     |                  |

| (Silicon Labs) |               |           |                          |         |         |                  |

| DSC1018        | MEMS          | 1M-150M   | ±5*10 <sup>-5</sup>      | 1.8     | 3m      |                  |

| (Discera)      |               |           |                          |         |         |                  |

| 3C02           | All-CMOS      | 6M-133M   | ±10 <sup>-4</sup>        | 1.8-3.3 | 2m      |                  |

| (IDT)          |               |           |                          |         |         |                  |

| MAX7377        | All Si        | 600k-10M  | ±5*10 <sup>-3</sup> (max | 2.7-5.5 | 3m      |                  |

| (MAXIM)        |               |           | 3*10 <sup>-2</sup> )     |         |         |                  |

| STCLx32k       | All Si        | 32k       | ±1.2*10 <sup>-2</sup>    | 1.8     | -       | Obsolete product |

| (STMicroelec   |               |           |                          |         |         |                  |

| tronics)       |               |           |                          |         |         |                  |

| LTC6909        | Bypassed RC-  | 12k-6.6M  | ±1*10 <sup>-2</sup>      | 2.7-5.5 | 400u    |                  |

| (Linear Tech)  | time constant |           |                          |         |         |                  |

All products below the thick line are specifically stating that they are Quartz free, PLL free, and all but the MEMS based one from Discera are MEMS free.

#### <u>2.4 Placement of the requirements, expectations by our choices.</u>

The project requested the design of a semiconductor-based oscillator, using a CMOS technology, with important characteristics ("critical parameters") to have temperature stability between -30oC and 85oC in the order of  $\pm 100$ ppm, which is  $\pm 10^{-4}$ , while burning less than 100uA. The rest of the non-critical characteristics are the load that has to be able to be driven by the oscillator (up to 12pF), the duty cycle (min-max 0.4-0.6xPeriod), the Jitter (120nS), the phase noise (-125dBc/Hz) and the power consumption on inactive mode (less than 2uA).

The first and very important choice that has to be made is how to approach our "all silicon, no quartz" oscillator, with which of the available choices:

- LC oscillators are producing results within our specifications, and they are basing their good behavior to the high quality (Q) LC-tank, requiring the on wafer design of an inductor.

- MEMS are facing more expensive fabrication process, but in return they manage to give very good results, within our specifications, based on the sealing that can be performed on their high quality factor mechanical elements on which the oscillation frequency is based.

RC-time constant based in general are struggling to get below 1% (10<sup>-2</sup>) accuracy over temperature.

A decision was made to implement the RC time constant based oscillator. For this type of oscillators it appears to be a difficult task to achieve accuracy sufficient for most applications [7], something that originates from a tradeoff – we are paying the price for less good performance in order to make use of the benefits this choice offers. The ease with which the frequency of this type of oscillators can be adjusted, the absence of inductors, the absence of PLL's and frequency dividers/multipliers, since the frequency is generated directly are some of them. Also competitive advantages are the facts that production of this oscillator type is cheap (standard CMOS technology is sufficient) compared not only to MEMS choice for example, but to the cost for quartz crystal oscillator stable over wide temperature range which remains relatively high [8] as well. As mentioned before, all the all-silicon oscillators are insensitive to vibration, shocks and EMI.

Our expectations are set in the following way: we will target to keep consumption within the limits and get the best possible result for temperature stability, minimizing or even cancelling any unwanted contribution(s).

### **Chapter 3**

## Oscillator design

## The basic idea-topology and high level design

#### 3.1 Introduction

The primary goal of every oscillator design is to create a stable (against all kinds of uncertainties) frequency. In this Chapter we will analyze how we built our oscillator, using a top down approach. That means that in this Chapter we are going to design with ideal blocks in system level, while in the next Chapter (Chapter 4) we will realize these ideal models using electronic components. This design methodology is well known as the one creates the best electronic circuits (this design procedure implies that Orthogonality, Simplicity and Hierarchy are being applied as described in [20]).

We have to state here that we are building an electronics oscillator. Even though the basic ideas that will be presented are not confined in electronics domain, but they could be implemented in other domains as well, and build –for example- a mechanical oscillator, we will introduce the basic components which are more suitable and easily realizable in electronics. In this Chapter we have to keep in mind the components electronic feasibility and when describing their function mathematically, will do so using electronic values. For example a threshold, is going to be implemented as a voltage threshold, so it will be named V<sub>th</sub> when using mathematical formulas.

In section 3.2 we are going to address the general problem of designing an oscillator, approaching the design from the signals point of view. Then in 3.3 we are going to present the possible choices for the topology of the oscillator, starting from the simplest possible one and trying to keep it as simple as possible, in 3.4 we will perform a crash test of all these simple implementations presented in 3.3, discussing about their advantages and disadvantages, and finally in 3.5 we will justify our final choice and try to cancel out any non-idealities this choice has already in this design level. Section 3.6 contains results from cadence simulations.

#### 3.2 Creating a periodical signal

#### 3.2.1 Components Needed

Our goal is to create a signal that repeats itself indefinitely. In order to get there, we firstly need to think about the components that are needed order to create this repetitive signal.

The simplest oscillator type (a one pole oscillator) can only build a relaxation oscillator and not a harmonic one [13]. Having this as a starting point, we suppose the output of our oscillator to be a square-wave-like signal. Therefore we have to find a way to time correctly the rise up and the fall down edges of the signal. So we need a *timing reference*. Time cannot be measured directly, but it has to be measured indirectly through a quantity that varies in time. For us that should be a quantity that makes sense in electronics domain. In this domain we can measure and create/change voltages, currents and components values via dynamic elements (L's C's and delay lines).

One oscillator that uses a timing reference and no amplitude modulation could be a cascade connection of a number of inverters. The timing reference would be the internal delay of the inverters. The first one would change its output after  $\tau_{delay}$ , and then the next one would read this as input signal, but also get delayed  $\tau_{delay}$  before changing its output etc. This is called a ring oscillator, and the problem with this approach is how little control we have on that delay (which is temperature, supply, load and process dependent and relates to threshold, slew rate and several other aspects). The idea of a ring oscillator was quickly abandoned, so we decide that the timing reference needs to be measured in some kind of *amplitude modulation*.

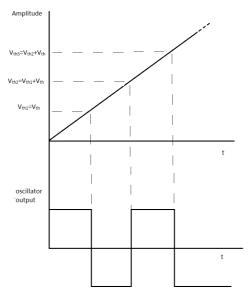

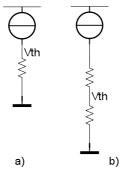

A simple idea would be to have a rising slope, as seen in Figure 3.1. The system would compare the value of the rising slope to a threshold  $V_{th}$ , and every time it would rise above the value of the threshold (or in Figure 3.1 above the value of [(previous threshold)+ $V_{th}$ ]), clock output would change (alternatively rising and falling edges of a square wave signal). So we count another 2 needs: the existence of *comparators*, and the creation of *threshold levels* to which the slope signal is compared.

Figure 3.1: Timing information being derived from comparing a slope value to a threshold

We are talking about voltage thresholds, but the same could also be made for current thresholds when using current comparators. As for the third possible choice of component values, that would be very hard to be implemented – for example a capacitance value changing and being compared to a "unit" capacitance.

Of course this slope needs to be created somehow. Implicitly another need is presented, the need to create a varying signal. The simplest way to get a constant-slope signal is to integrate a constant value. So we need an *integrator*, and the creation of a *constant value to be integrated*.

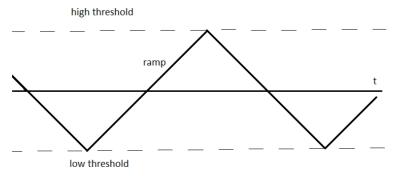

One problem that we didn't think of yet is the fact that our electronic circuit is going to have limited supplies, so voltages are going to be restricted between two values. The ideal Figure 3.1 is not implementable in electronics. A simple solution could be to integrate a positive value in order to reach a threshold, and then to change sign of integration, and reach another threshold, and so on (Figure 3.2). Each time the system reaches a threshold means a rising or falling slope in the output. This way we keep our signal restricted between two values, and this makes more sense for an

electronic implementation of the periodic signal. Still, this thought does not add new "needs" to our design, apart from the need for two thresholds instead of one, and two signs for the signal to be integrated.

Figure 3.2: Integrator's output showing integration of different signed values

The final implicit need is the need to remember where the system is and what needs to be done next. For example in Figure 3.1 the previous threshold needs to be remembered in order to add the same amount once again and find the next threshold and so on. In Figure 3.2 what needs to be remembered is if the "coming soon" change of the comparator output should cause an integration of the positive or the negative value. So we have presented the need for the memory, that we will call state memory.

Of course we shouldn't forget that already the integrator is an analog memory, which memorizes the integrated value (a voltage value representing the integral for our implementation). So we have to keep in mind that our oscillator- the simplest kind we present here- needs two memory functions in order to operate.

To sum up, in order to build the system that will create the simplest (possible) periodic signal (a first order oscillator), we need one timing reference, created by:

- One varying signal, by means of an integrator and value(s) to be integrated

- Comparator(s) and reference signal(s) to which the varying signal will be compared to

- A second memory(state memory) that will remember the state the system is in

Finally, as far as the topology is concerned, we have to implement feedback in our system, since the output of the state memory (somehow "in the end") needs to choose the sign of integration (somehow "in the beginning"). But this will be implemented in the coming section 3.3.

#### 3.2.2 Signal choices

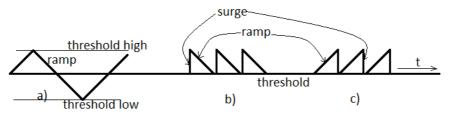

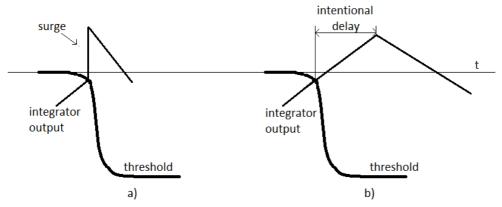

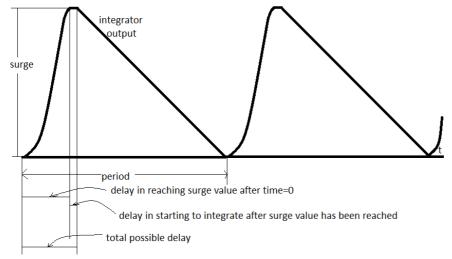

So far we discussed only about signals with a controlled slope (like the output of the integrator) and constant signals (like the input of the integrator). We could also use signals like those in Figure 3.3b and c: we will call them *surges*. Surge will be a predefined increase or decrease of the signal of the integrator. By using a surge we can make an oscillator based on only one threshold, but still restricted between two values. The idea is that integration starts, the slope crosses the threshold, the surge value is being added and that brings the system to the previous situation and then integration starts again (like in Figure 3.3.b for positive and c for negative surge value). Here the second threshold is implicit in the predefined value of the surge.

Figure 3.3: a) signals with slope b&c) using a surge signal

#### 3.3 Different topologies

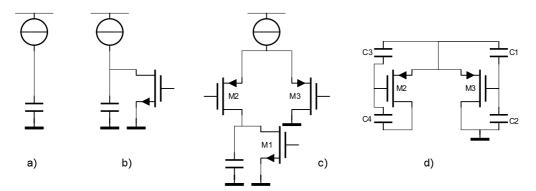

The discussion so far in section 3.2 on which components are needed to create a periodical signal, sums up in the following topology:

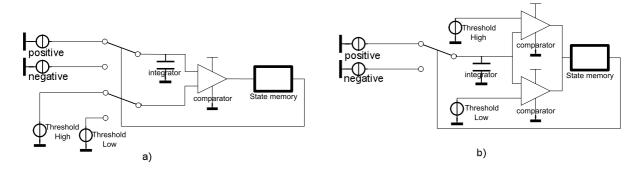

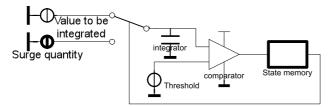

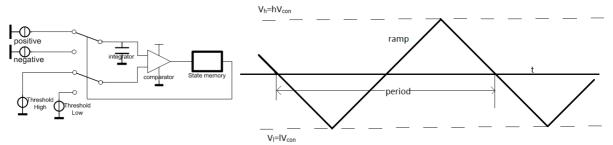

Figure 3.4: The basic oscillator a)in a block level diagram b)in an electronics domain block diagram

We notice the existence of decision points (on 3.4.b they are implemented by switches) that control which value (positive or negative value) has to be integrated and which threshold is being compared. After the slope (integrated value) is compared to the threshold by means of a comparator, the output of that comparator commands the state memory to change the position of the switches and therefore both the sign of value to be integrated and the threshold(s), according to the state saved in the memory.

From this simple idea, several different implementations can be derived. Of course we should keep in mind that innumerous different approaches to the topology of the oscillator could be created by adding more timing references. Here we only have one timing reference (time for the slope to get from one threshold to the other) and two memories (our integrator and a state memory). If we add more timing references or more memories the design becomes more flexible, but we will try to keep it as simple and efficient as possible.

#### 3.3.1 Two thresholds oscillator

If we want to implement our system with the presence of two thresholds (the high and the low) then we can define two different topologies: one with one comparator and a switch in front of the threshold-to-be-compared, choosing which threshold is in use every moment (identical to the general one from Figure 3.4), and one with two comparators, each one continuously hooked up to one of the thresholds. These can be seen respectively in 3.5 a and b.

Figure 3.5: Two thresholds oscillator a) with one comparator and a switch to choose the threshold b)with two comparators.

As can be seen in Figure 3.5a, the switch to choose which threshold is going to be compared is controlled by the state memory that controls also which value is going to be integrated.

#### 3.3.2 One threshold oscillator

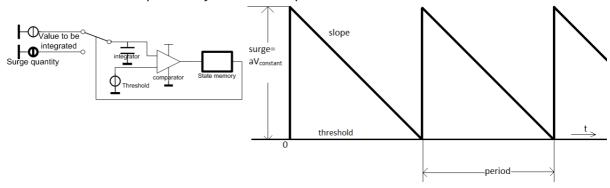

If we want to implement a single-threshold oscillator, then as discussed before there should be somewhere hidden the control over the second "threshold". One way to implement this is by the use of a surge quantity. In that case, when the slope crosses the threshold level, the surge value is being added to the integrator and then integration starts again. In this implementation we can even use ground as the threshold, and therefore "create" no threshold of our own. The general topology can be seen in Figure 3.6.

Figure 3.6: One threshold oscillator using a surge

We notice that this way only one value is being integrated (either positive or negative) and the change in the opposite direction is taken care of by the surge. Also the state memory once again is taking care of both switches: one to integrate the value or not, and another to add the surge quantity or stop it - actually they could be merged in one switch, and either the value to be integrated or the surge quantity would be connected to the integrator, like in Figure 3.6. In that case the memory must have some kind of connection to the surge quantity, so it knows when the surge quantity is added entirely to the integrator's value and then turn back the switch to the value to be integrated without change in the comparator's output (the state memory should have a way of knowing when the surge has been properly applied).

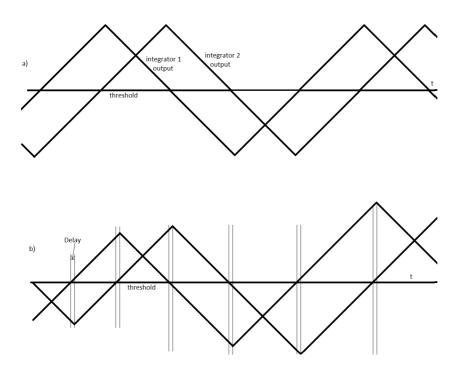

Another way to use only one threshold is by making a copy of our circuit, and creating a quadrature oscillator (which is no longer a first order oscillator, since we have two timing constants). Here a loop is formed. Crossing the threshold is not the end of integration. It just triggers the change in sign of integration of the following "copy" of the circuit (Figure 3.7). The upper and lower thresholds are not anymore present, and they are not needed. The system increases in complexity, in

power being dissipated and in area needed on chip, but this topology presents some benefits that will be discussed in the next section 3.4.

Figure 3.7: One threshold oscillator using a copy of the whole circuit

#### 3.4 Pros and cons of the various implementations

In this section we are going to discuss the problems that arise from the various implementations of the oscillator. In 3.4.1 we are going to address all problems that occur in real life implementations while in 3.4.2 we are going to compare the mathematical expressions that govern the above mentioned topologies, and compare them.

#### 3.4.1 Problems that occur in real life signals

As in any electronic circuit, the issues that decrease the quality of the performed operation in our oscillator and their effect should be minimized, are:

- o inaccuracies, due to offsets and delays

- o noise

- o distortion

- o process mismatch that implies frequency may have to be tuned to the correct value

- o temperature stability (especially in our design)

The latter four effects will be dealt with in the next Chapters, when we'll start talking about the actual electronic implementation of the circuit, and things like noise and distortion will make sense. Here, since we are doing an abstract analysis of the problem, and we use ideal blocks (i.e. mathematical expressions) we will only introduce inaccuracies (delays in time and offsets in values) and compare the implementations in subsection 3.4.2 based on that. What hides behind delays is "time domain errors", and what hides behind offsets is "amplitude domain errors".

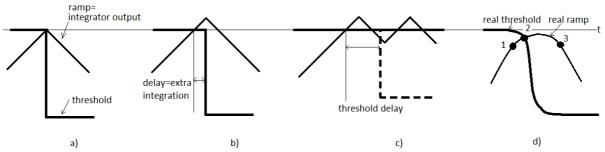

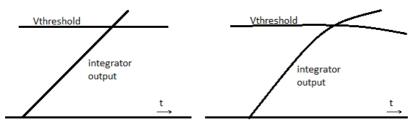

As far as the signals are concerned, an important statement must be made about the difference between ideal and real signals and transitions. In ideal signals, if we look at Figure 3.8.a (where for simplicity only the top of the integrator's triangular output is depicted) it's easy to perform many changes simultaneously. When the slope reaches the high threshold then we suppose that two things happen at the same time: a change in integration sign and a change in threshold level. The change in integration sign can be seen as a negative feedback action, and the change in threshold as a positive feedback action since it's the action that makes the whole system regenerative.

If now we move a step closer to real life signals, like in Figure 3.8.b, we see that since nothing happens instantly in real life, the slope signal will rise for a negligible (?) amount of time higher than the threshold in order to change the output of the comparator. Then the sign of integration changes

along with the threshold level. If the threshold is not changed fast, but gets delayed more than the signal needs to cross again the high threshold, integrator's output can end up in a deadlock situation, like in 3.8.c, where the threshold doesn't change in time and system starts oscillating around the threshold. This means that the threshold needs to change before the sign of integration changes, in order to prevent this state. So there is actually a battle of loops, and the winner has to be the positive feedback loop if we want an oscillation [13].

In 3.8.d we see how things happen in real signals and real circuits: the system "senses" the proximity to the threshold of the output of the integrator at point 1, and so the sign of integration starts to change, causing a decreased slope in the output signal. The threshold crosses the integrator output with a reduced slope at point 2, which can cause many issues: increased noise on the timing of the transition, and most of all unpredictable outcomes. Finally at point 3, the value to be integrated has completely changed sign and we consider from this point that the negative value is being integrated.

Figure 3.8: Zoom in the threshold crossing point: battle of the loops in a)ideal case b)ideal case with some comparator delay c) deadlock situation if threshold can't swap on time d)real case

In order to avoid this battle, we need to make sure that the two changes do not happen simultaneously. This can be taken care of by either inserting a surge (see Figure 3.9.a) that increases the value on the integrator, and gives time to the threshold to change safely, or just insert a time delay between the two actions (3.9.b)

Figure 3.9: Ways to avoid the battle of loops: a) with a surge b) with time delay

#### 3.4.2 Comparing the several implementations

Let's firstly name the implementations in the order they were presented, **first** the implementation of two thresholds and a switch to choose between them, **second** the one with two thresholds and two comparators, **third** the one using a surge and only one threshold and **fourth** the

quadrature one (two integrators, where threshold crossings of one decide for the switch of the sign of integration for the other) By preliminary inspection we can guess that

-first and second implementation will suffer from the battle of loops, so even though ideally their behavior will be good, in real life they will suffer from the fact that they suppose a sharp and simultaneous change in both integration sign and threshold value

-third implementation will not suffer from this problem but it will have put the delay of the surge in the loop (delay for the surge to "force" its value on the integrator), so the period will be dependent on that, so this brings in a huge unknown (how well can we control the timing of the surge that in real life will not happen instantly)

-fourth implementation seems as the most promising. If the system doesn't suffer much from the possible mismatch between the two copies of the timing reference and if we have the freedom to spend power for both of them, then this idea will implement the "time delay" way to avoid the battle of loops: one signal that is deciding for the other one to change sing of integration by crossing a threshold, keeps on rising (or falling) and we have decoupled the two changes.

For all the upcoming mathematical explanation of the behavior of the four implementations, we are going to consider that we are working in the voltage area of the electronics domain, so we have a  $V_{con}$  available, i.e. a constant voltage (for example a bandgap reference), and for the slope, we integrate a current on a capacitor.

#### 2.4.2.1 Mathematical expressions for the first implementation

Figure 3.10: first implementation

We have  $V_h = hV_{con}$ ,  $V_l = lV_{con}$ , because we suppose that the two thresholds are going to be created as portions of the constant voltage.

As for the slope, it will depend on the capacitor integrating the current, so:

$$slope = \frac{dVi}{dtCRC} - \frac{V_{con}}{in},$$

$$Th \frac{VVDW}{slope}hlV \frac{()()}{\frac{iV}{C}} - \frac{\frac{con}{RC}}{\frac{i}{RC}}$$

The interesting result here is that we seem not to depend on the constant voltage value. Factor "2" depends on the matching of the values to be integrated (the plus sign and the minus), h, l, R and C are all based on passive components for which we can expect the most accurate results.

#### OFFSETS IN FIRST IMPLEMENTATION

Offsets can appear in every signal's amplitude, in:

- -level of the values to be integrated (the currents), and these will be further analyzed

- -thresholds (the two "levels" which are important to the oscillation), and these will be further analyzed as well

- -comparator input, which will be ignored

- -memory output level, which will be ignored

- -switches, which will be ignored

We chose to ignore some of the offsets. The comparator input offset can be modeled with a constant offset in one of the two inputs of the comparator. If that's put in front of the input reading both thresholds, then that offset is going to shift both thresholds and the whole slope a  $V_{\text{offset}}$  higher or lower. So that has no effect on the frequency (which depends on the difference of the two offsets).

The memory output is supposed to be high or low supply (Vdd or Vss) If we suppose ideal sudden change of the memory output from low to high and vice verca, there's no change if low is Vss±offset or high is Vdd±offset. If the state switching is not sudden like in the ideal case where it lasts an indefinitely short amount of time, but there is a slope, then a small offset will shift that slope a bit to the right/to the left and introduce a timing error, concerning when the change of the memory state will be read by the following components (for example the switches). Timing errors will be discussed later, in the delays section.

Possible offset in the switches (supposing that the switches are going to add some non zero offset to the values they are delivering to the comparator) will introduce a delay, since the actual value will be "read" earlier or later.

Offset in Value to be integrated: If we get a change a% in the value of the currents, this means that we will get a change a% in the denominator of the period (the slope), so

$$T_{new} = \frac{\frac{100001V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}^{2}V_{cont}$$

So the period is changing to  $T_{old}*1/(1+a\%)$  or the frequency is changing to  $f_{old}*(1+a\%)$ .

Offset in Threshold(s): Now we suppose the value of thresholds changes by a%: Mathematically we can solve any case of each one of them changing or both of them changing by a different amount. Theoretically the same change on both of them cancels out (shifts the slope higher or lower by that offset). Suppose a case where there is some difference in the two offsets of the two thresholds, resulting in a change of the difference of them by a%. Then as observed in the final formula we get

$$Therefore [2]{HV()\%()}{slope} \qquad \frac{i}{C}$$

So the period is changing to  $T_{old}*(1+a\%)$  or the frequency is changing to  $f_{old}*1/(1+a\%)$

Comment: Change in the value to be integrated, translates in change in slope, which translates in the accuracy of the values of C and  $R_{\rm in}$ . They both change the slope of integration in the same way: they

appear in the denominator of the slope and so the changes transfer directly in the period. Moreover change in threshold translates to change in h-l which are based on passive components too (possibly resistive dividers), and as proven above changes to the h or l factors appear directly at the output.

#### **DELAYS IN FIRST IMPLEMENTATION**

Delays can appear in all transitions that are present in the circuit:

- -in the change of values to be integrated (if there is a delay in the change of integration from positive to negative value and vice verca)

- -in the thresholds to be compared (high/low: we have a switch controlling which is being compared)

- -in the comparator output change (from high to low and vice verca)

- -in the state memory output that controls both the switches.

All of them need to be analyzed.

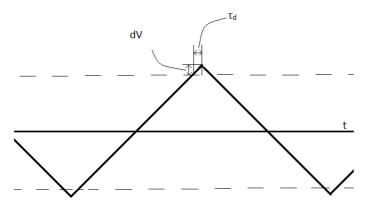

Delay in Value to be integrated: If we get a delay in "reading" the change from positive to negative value to be integrated, as large as  $\tau_d$ =a% of the period, then we see that until the change in integration sign is being noticed, the system will slightly keep integrating above the thresholds. So as seen in the following Figure 3.11, this  $\tau_d$  is added 4 times in the period. We can show that mathematically from the fact that  $\tau_d$ = $dV_{extra}$ /slope, so  $dV_{extra}$ =slope\* $\tau_d$  and this  $dV_{extra}$  needs to be added to the high (system is delayed from starting integrating downwards) and subtracted from the low value(system is delayed from starting integrating upwards), so

Figure 3.11:  $\tau_d$  in the change of the sign of integration

$$T_{new} = \frac{2}{2} \frac{\frac{hV_{CONEXWaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaconexwaco$$

So the period is changing by adding 4 times the delay induced, and the frequency is changing to  $f_{old}*1/(1+4a\%)$

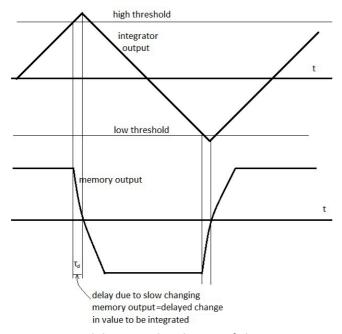

<u>Delay in Threshold(s)</u>: When there is a delay in the change of threshold, all we have to avoid is running into the worst case scenario of a deadlock situation as described in 3.4.1 and can be seen in Figure 3.8.c. If the threshold is changing faster than the integration slope (Figure 3.12), then we face no problem. In this point it should be mentioned that all of the above were proven by simulations in Cadence platform using ideal blocks, and adding non-idealities like delays and offsets.

Figure 3.12: how threshold delay is of no issue as long as it is less than the time the slope needs to get to the new threshold

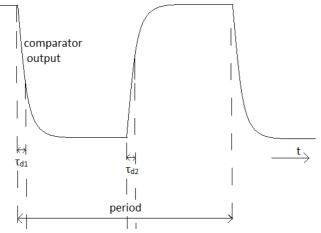

<u>Delay in Comparator slope:</u> The output of the comparator is used to trigger the change in the state memory which there after will change the sign of integration. Therefore purely by logic we can argue that there are 2 changes of the comparator output every period. If each change is delayed by  $\tau_d$  that will cause an extension of the period by twice that delay, like in Figure 3.13. Unfortunately when the state memory change is delayed, the system keeps integrating towards the wrong direction and that will have to be compensated for, like shown in Figure 3.11. Therefore this delay has to be added 4 times per period, and not just two.

Figure 3.13:  $\tau_d$  in the change of the comparator output

<u>Delay in State memory output:</u> Since the state memory output is actually our output, someone could think that a delayed signal gives only a phase error, and period would remain unchanged. But this signal is used also for controlling the switch of integration sign, so it will have some extra effect, obviously the same like a delay in the value to be integrated (a delay in the control signal of a perfect

switch happening here or a perfectly controlled non-ideal switch like in the "delay in value to be integrated" is the same thing: it causes the signal to change slower, see Figure 3.14). If we get a delay  $\tau_d$ =a% of the period, then the period is changing 4 times the delay induced, and the frequency is changing  $f_{old}*1/(1+4a\%)$ . Of course if it delays more the change in threshold, integrator runs into the deadlock situation of Figure 3.8.c, and this is a highly undesirable case.

Figure 3.14: delay  $\tau_d$  in the change of the state memory output is indeed a delay in this signal being "read and applied" so the same like the delay in changing the sign of integration

#### 3.4.2.2 Mathematical expressions for the second implementation

The second implementation (two thresholds hooked in two comparators, and not controlled by a switch) is mathematically the same as the first one. The expression for the period is the same, and the dependencies are almost the same. The only things different are the following:

- -offset in the comparator input is now not shifting both thresholds, so it cannot be neglected like in the first case. Here as can be seen in Figure 3.5.b a possible offset in one comparator will make integration last a bit more, and this will have to be corrected, so the period will be increased twice that dV cause by the offset. So if both comparators add a% and b% respectively, we will measure an increase in the period of 2a%+2b%. Of course there is always a chance that they could cancel out.

- -a delay in changing the threshold value is not valid here (since both comparators have the thresholds hooked up on their inputs all the time)

- -the delays could vary differently in the two comparator paths: if a comparator output slope would be present in only one of them, this would change the period in  $T_{old}(1+2a\%)$ . If they would be in both comparators the result would be  $T_{old}*(1+2a\%+2b\%)$  unless they are the same, in which case we end up in exactly the same equation like for the first implementation  $T_{old}*(1+4a\%)$ . Since it's a random error, there is always the chance they cancel each other with opposite signs.

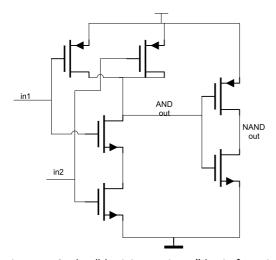

-the requirement of a digital block reading the two outputs of the comparators, and ordering the state memory to change or stay put. This could be an XOR for example, which would be in our signal path, and could also introduce delays, but that delay can be included in the general "memory" delay.

#### 3.4.2.3 Mathematical expressions for the third implementation

Figure 3.15: the third implementation

We implemented this idea, by taking the voltage across the capacitor as 0 (initial value), force it to rise with the predefined amount of surge, and then it integrates a negative value, so it reaches the threshold (ground in our case), and surge is added again etc.

$$slopes \frac{V}{R_{in}^{col}} V_{a}V \qquad con$$

$$Ta \frac{dV}{slope} \frac{aV_{con}}{\frac{V_{con}}{RC}} \qquad in$$

We supposed surge is indefinitely fast. If it's not, it is added in the period, as a constant  $t_{surge}$ , twice per period. If we would use another threshold instead of ground, then simply we would have on the numerator  $surge-threshold=aV_{con}-bV_{con}=(a-b)V_{con}$ .

The interesting result here is that period has the same expression like in the last two implementations, but the dependency here is a, instead of (h-l). Many of the results are expected to be similar.

#### OFFSETS IN THIRD IMPLEMENTATION

Like in the analysis for the first implementation, offsets that we care about can appear:

-in the level of the value to be integrated (the current-only with negative sign here)

-in the thresholds, one implicit in the surge value, or the other threshold (ground or any other) being used

Like in the first implementation, possible offsets in comparator output value and memory output are translated into delays and will be analyzed later. Also like in the first implementation, any offset in the input of the comparator appears like offset in the threshold, since the threshold is hooped up on the comparator input all the time. So it will be analyzed with the threshold's offset.

Offset in Value to be integrated: Like before, the expression is the same:

$$T_{new} = \frac{aV_{Concon}V_{Concon}}{\frac{ibi}{C}} \frac{aV_{Concon}V_{Concon}V_{Concon}}{ibih W_{O}(1\%)1\%}$$

So the period is changing to  $T_{old}*1/(1+b\%)$  or the frequency is changing to  $f_{old}*(1+b\%)$ .

Offset in Threshold(s): Now we suppose we change the value of the surge by b%. We have:

$$ThT = \frac{surge}{slope} \quad \frac{aVbaV}{i} \%$$

$$\frac{i}{C}$$

(1%)

So the period is changing to  $T_{old}*(1+b\%)$  or the frequency is changing to  $f_{old}*1/(1+b\%)$

Unlike an offset in the surge, possible offset to the threshold level (or the comparator input) will not affect our period. Taking for granted a stable surge of a specific positive value, in the presence of threshold offset everything will shift and be superimposed to that offset. So the surge is added to the offset, integration takes place down to that offset, the surge is added again on top of the offset etc. The timing is hidden in the accurate surge. If on the other hand the surge is somehow implemented as reaching some voltage level and not a constant quantity, then possible offset in the threshold (lifting the zero level for our case) would mean a change in the period once per period (that means multiplied by (1+b%)).

#### **DELAYS IN THIRD IMPLEMENTATION**

Delays can again appear in all transitions:

- -in the value to be integrated (if there is a delay in the transition from zero to surge value or from surge value to value to be integrated)

- -in the comparator output

- -in the state memory output that controls the switches operating the surge the ground and the integrating value.

We suppose that the surge has no delay, and even if it does, it can be included in the first delay that will be analyzed. Moreover the threshold is hooked on one input of the comparator, so there is nothing changing there that could introduce a delay.

Delay in Value to be integrated: If there is a delay  $\tau_d$ =b% of the period, in which we include both some delay when getting from zero to the surge value or getting from surge value to start integrating the negative value, then we can argue that this will be added once in every period, as seen in Figure 3.16.

This obviously includes also the possible delays caused by the switches that will "provide" to our circuit the surge value, and the value to be integrated.

As seen in the Figure 3.16, the period is changing by the delay induced, and the frequency is changing to  $f_{old}*1/(1+b\%)$ .

The reason why this delay changes once our period and not multiple times (like in the first and second implementation), is because we suppose that the integrator cannot integrate lower than zero level, since zero is one of the supplies, and moreover when the surge is being "added", the

integration process is stopped. Otherwise the system would keep integrating to negative values, while the surge would try to be "forced" on the integrator value.

Figure 3.16: delay in the change of value of integration

<u>Delay in Comparator slope</u>: The output of the comparator is used to trigger the change in the state memory which there after will change the sign of integration. Therefore it's exactly the same case like in analysis for the first implementation, but this time we do not integrate to the wrong direction and need the time to correct it, thanks to the surge, as analyzed in the previous paragraph. So we get that delay only once in our period (the output just saturates at zero level and waits for the surge). If we could integrate to negative values (like if the threshold would be an arbitrary one and not ground) then it will not affect our period at all, provided once again that the surge will be a constant quantity. Delay in the comparator will just be responsible for the part of under the threshold integration, and the highest point would be (surge) minus this part already integrated below the threshold.

<u>Delay in State memory output:</u> Here again, the state memory output is our output. It controls the switch that will apply the surge and the switch that will start applying the integrating value. Both these changes are performed with one change in state memory - we face the same questions as to how the surge is going to be implemented. Supposing surge and integrating process do not coexist but they are still controlled by one change in state memory output, that delay will be added once in every period.

#### 3.4.2.4 Mathematical expressions for the fourth implementation

For the fourth implementation we get the output seen on Figure 3.17a, based on a circuit like in Figure 3.7. If any delay or offset is inserted, then the whole oscillation falls apart, since system lacks one control parameter, one threshold (Figure 3.17b). The integration value will be rising to infinity because the possible delay in the first integrator will be "memorized" in the value of the other integrator that will change integration sign later, cross the threshold later, and if the same delay will be added once every period, this will lead to instability (real signals would be saturated by the supplies eventually).

Figure 3.17: a: ideal quadrature oscillator b: output with delay, using only one threshold

One solution to the problem [13] could be to include two Schmitt triggers (Figure 3.18.a) that would provide 2 more levels of control (so now system has one extra) by including their two thresholds to the zero threshold already in use. The zero crossing of the first integrator output ignites the change in the thresholds of the second Schmitt trigger, which forces the second integrator to change sign of integration, like in Figure 3.18.b. Unfortunately, in case a delay existed, that would be memorized like in 3.17.b, reaching a point where the change in integration sign would happen with reaching the —non modified- thresholds of the Schmitt triggers. Therefore the system would keep oscillating but would not be controlled by the zero crossing or the other integrator but rather by reaching the thresholds (Figure 3.18c-where only the delay and the thresholds of one of the two Schmitt triggers is drawn, in an attempt not to make the Graph too messy. We assume the same things happening in the middle between the delays drawn, for the crossings of zero of the other integrator and for the other Schmitt trigger.)

In case Schmitt triggers are unwanted (and usually they are, since their strong point is —more or less- just their flexibility) some extra control should be brought in the system, like limiting low value to zero. In that case, with the existence of a delay, the signal would clip on zero waiting for the next threshold crossing. Therefore the duty cycle would not be 50%. It would be perfectly repetitive, but still not completely under our circuit's control (Figure 3.18d)

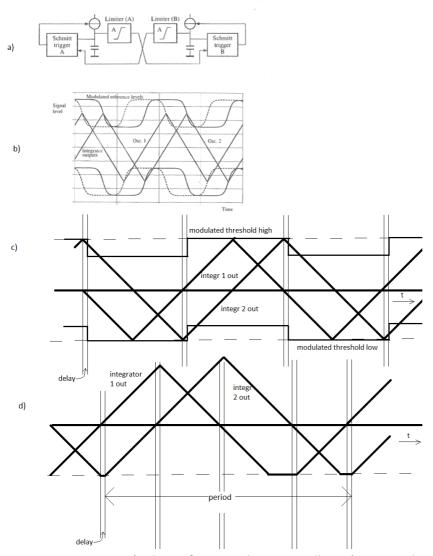

Figure 3.18: a: Westra's choice for a quadrature oscillator (picture taken from [13]) b:modulating the Schmitt trigger's thresholds(again from [13]) c: worst case scenario (for simplicity with ideal threshold modification) for delay d: if ground is added as another control

#### 3.5 Final choice and canceling the inherent imperfections

Transforming all the previous equations/formulas/assumptions in sensitivities, for the first 3 implementations that were mathematically analyzed, we get the Matrix 3.1.

We are not particularly satisfied by any of the analyzed topologies, but we see that some (third in particular and fourth as a general idea) have some interesting advantages. So we are going to create a hybrid by a combination of the best parts of all the previous analyses.

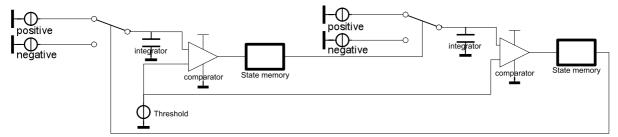

#### 3.5.1 New implementation design

The new design is the one shown in Figure 3.19, with signals like in Figure 3.20.

Matrix 3.1: Sensitivity Matrix; how much each component can affect the period of the signal for an a% change in the crucial parameter.

|                        | First implementation   | Second implementation     | Third implementation |  |

|------------------------|------------------------|---------------------------|----------------------|--|

| a%I offset in value to | ≈-a% (if both curre    | ents change the same      | ≈-a%                 |  |

| be integrated (current | percentage)            |                           |                      |  |

| 1)                     |                        |                           |                      |  |

| a%∆V offset in         | ≈a%                    |                           | surge: ≈a%           |  |

| threshold (Volt        |                        |                           | threshold and/or     |  |

| difference)            |                        |                           | comparator: 0        |  |

| a%ΔV offset in         | 0                      | ≈2a%+2b% if a% for        | 0                    |  |

| comparator input       |                        | one and b% for the        |                      |  |

|                        | second comparator      |                           |                      |  |

| Offset in binary       | NO EFFECT provided it  | 't affect the behavior of |                      |  |

| outputs of             | the switches being con | duces delays              |                      |  |

| comparator/state       |                        |                           |                      |  |

| memory                 |                        |                           |                      |  |

| a%T delay in sign      | ≈4a%                   |                           | ≈a%                  |  |

| change of value to be  |                        |                           |                      |  |

| integrated             |                        |                           |                      |  |

| Delay in Threshold     | NO EFFECT if fast      | NOT VALID                 | NOT VALID            |  |

| value switch           | enough                 |                           |                      |  |

| a%T delay in           | ≈4a%                   | ≈2a%+2b% if a and b are   | ≈a%                  |  |

| comparator output      |                        | delays per comparator     |                      |  |

| switch                 |                        | (if same, ≈4a%)           |                      |  |

| a%T delay in state     | ≈4a%                   |                           | ≈a% if one memory    |  |

| memory output          |                        |                           | change ignites both  |  |

|                        |                        |                           |                      |  |

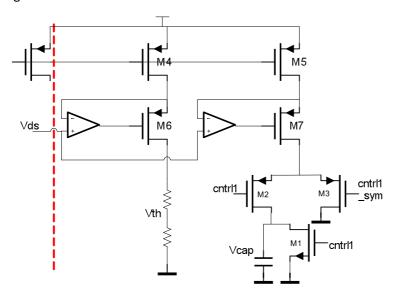

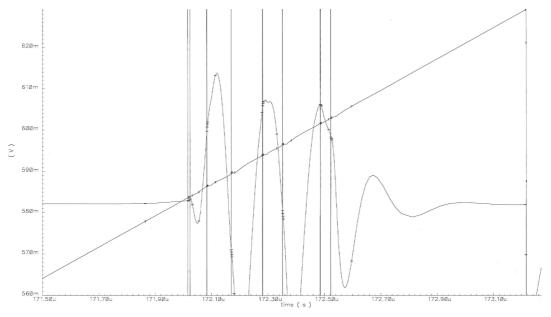

Figure 3.19: The new implementation of the oscillator

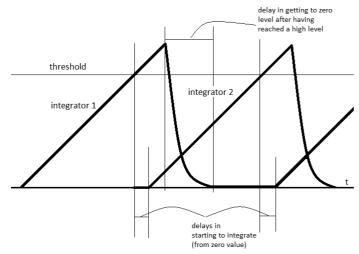

Figure 3.20: The signals in our final implementation

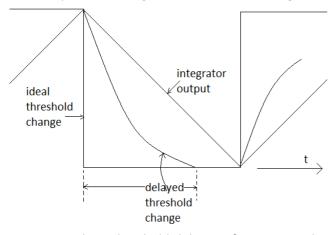

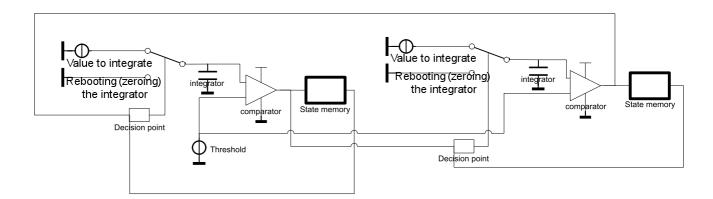

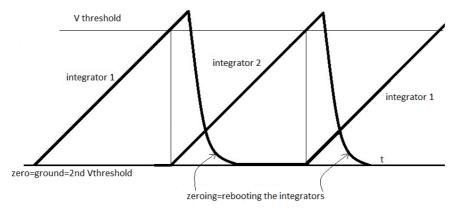

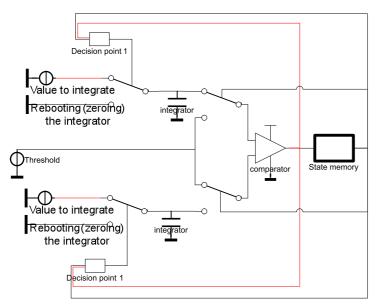

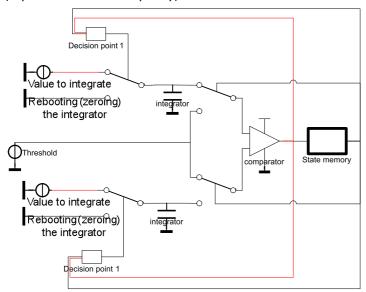

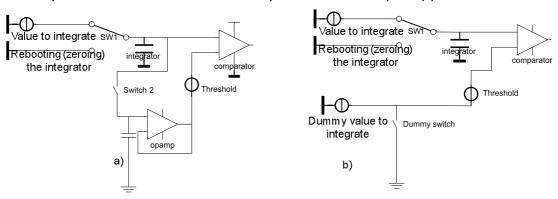

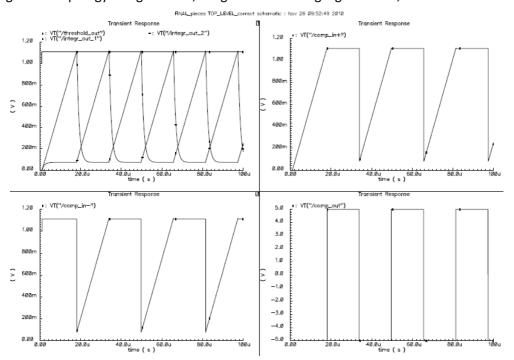

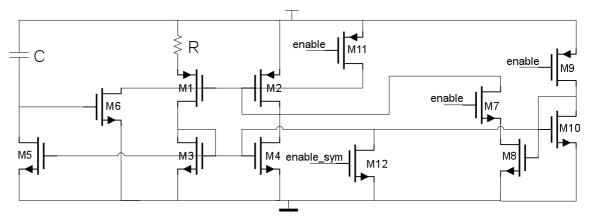

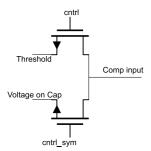

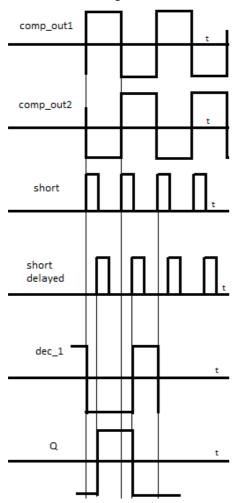

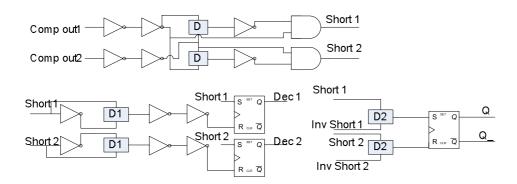

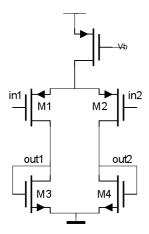

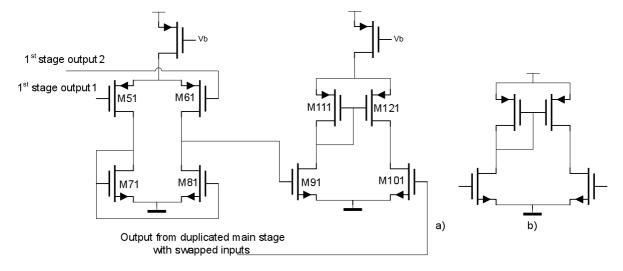

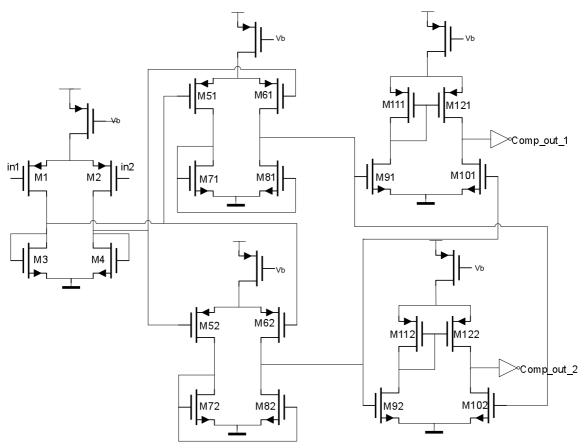

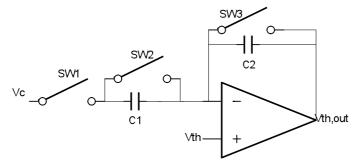

The idea is the following: In order to have enough controls, we keep zero (low supply, ground) as one threshold and create an extra one. So we will go for a two threshold oscillator, since this will be easier and better controlled than creating a surge (voltage) value, and making it (the surge) temperature independent and flexible enough to be added without imperfections to our integrator. Therefore we have solved the issue of fewer controls in the quadrature oscillator (4th implementation), but we will keep the basic idea of the quadrature oscillator that the crossing of a threshold of one integrator starts the integration in the other one, while the same one keeps integrating. This control is done by connecting the output of one comparator to the switch of the other timing reference via a decision point to "force" it to start integrating. In the meanwhile the integrator that crossed the threshold will keep integrating for some delay, which will be included in the state memory, but which will be shown that is arbitrary and not important for the timing of the circuit. After some time the output of the state memory of the first timing reference will finally change, and reboot the integrator (in electronics terms it is going to discharge the capacitor by connecting the ground to both sides of it), and wait for the crossing of the threshold of the other one, in order to start integrating again, giving time for the capacitor to safely discharge practically completely. The so called "decision point" in Figure 3.19 just takes care that when the memory commands, ground is being connected for discharge, while when the comparator of the other part commands, the integration starts – it will obviously be some logic function which we decoupled from the state memory since we want it to reply quickly.

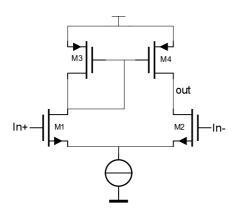

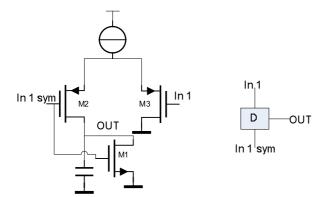

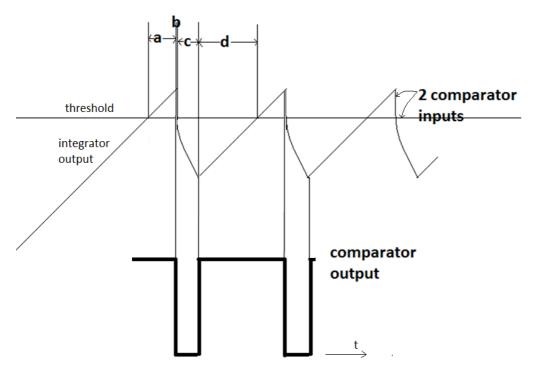

Another improvement we can make is to include the characteristic of the third (and first) implementation, where thanks to using just one comparator, we eliminated the effect of offset of the comparator. In order to vanish the effect of the comparator offset, we will have to use only one comparator and interchange the inputs, so the effect of offset vanishes (see also 3.6). The price to pay for having switches choosing what is being compared at the inputs of that (one) comparator is less to be paid than having two comparators, two possibly different delays through there comparators in the signal path along with their temperature dependencies and twice the power needed for the comparator.

So the final implementation is the one shown in Figure 3.21.

Figure 3.21: The final implementation of the oscillator (fast timing path marked red)

We have two separated control timing paths, a fast and a slow one (where by fast we characterize the one that is important for the timing of the oscillation and should be so fast as not to change our frequency, while by slow the one that is not important for the timing of the oscillation, even if the delays it introduces drift a bit over process or temperature). Integration takes place, until the threshold is crossed, then the change in the output of the comparator is taken into account in the decision point 1, which has to respond fast, in order to make the other integrator start integrating. Then, the slow path changes the output of the memory, and this will change two things: first change the position of the switches that choose the new pair of inputs that have to be compared (threshold and the other integrator's output in interchanged inputs of the comparator) and secondly discharge the first integrator.

#### 3.5.2 Mathematical expressions for the new design

$$TaR C2 \frac{dV}{slope}$$

$\frac{aV_{con} 20}{\frac{V_{con}}{R_{C}}}$  in

#### OFFSETS IN FIFTH IMPLEMENTATION

Offsets can appear in the levels of the following signals:

- -in the level of the values to be integrated (the current)

- -in the threshold (here only one "level" is important, the other one is ground).

There is also possibility for comparator offset at its input, but it disappears thanks to the topology that was designed. The way the comparator (input) offset disappears will be explained extensively in 3.6 showing cadence results. Moreover, if offsets appear in the second memory output and/or the level of the comparator output, we suppose they can only affect our frequency if they are translated in delay issues, and they will be analyzed later.

Offset in Value to be integrated: If we get a change b% in the value of the currents, means that we will get a change a% in the denominator of the period, so

$$T_{new} = \frac{222}{ibi} \frac{VaVCaVC}{\%} \frac{ibib}{ibib} \frac{1\%}{1\%} \frac{T}{1\%}$$

So the period is changing to  $T_{old}*1/(1+b\%)$  or the frequency is changing to  $f_{old}*(1+b\%)$ .

Offset in Threshold: Now we suppose we change the value of threshold by b%:

$$ThT = \frac{22(1\%)}{slope} \qquad \frac{aVbaY}{\frac{i}{C}} \%$$

So the period is changing to  $T_{old}*(1+b\%)$  or the frequency is changing to  $f_{old}*1/(1+b\%)$ .

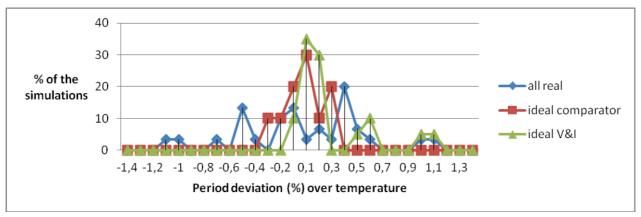

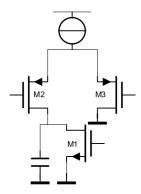

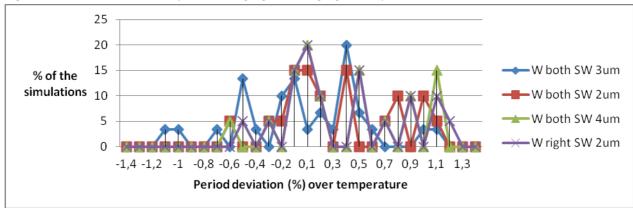

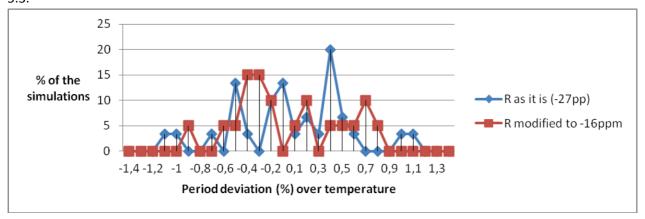

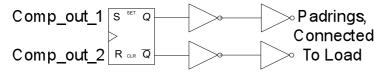

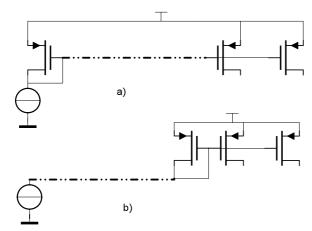

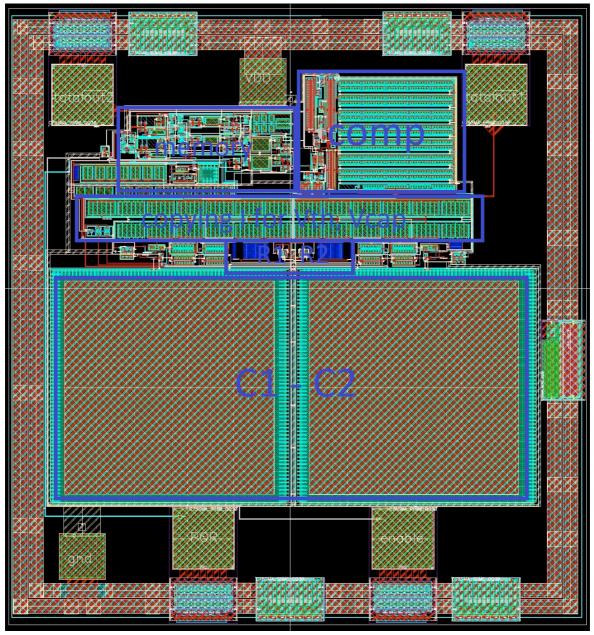

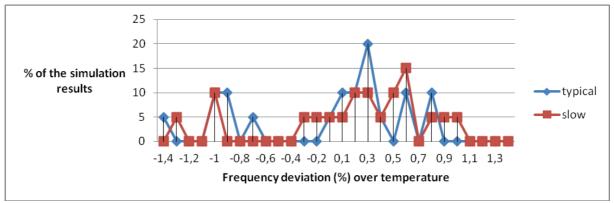

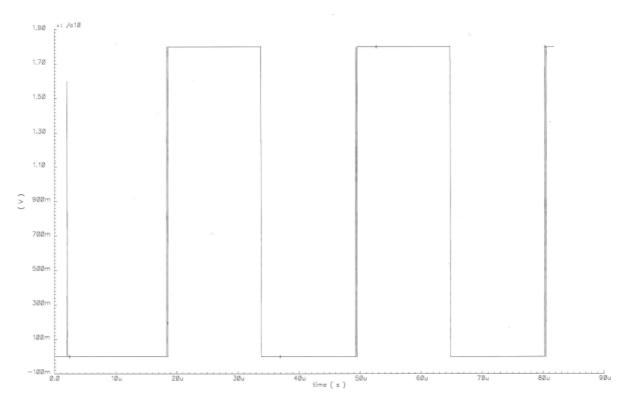

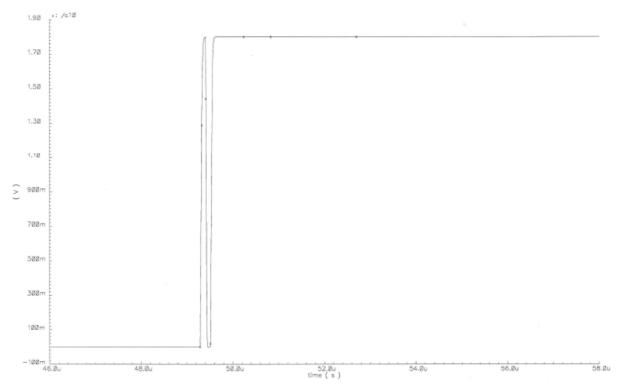

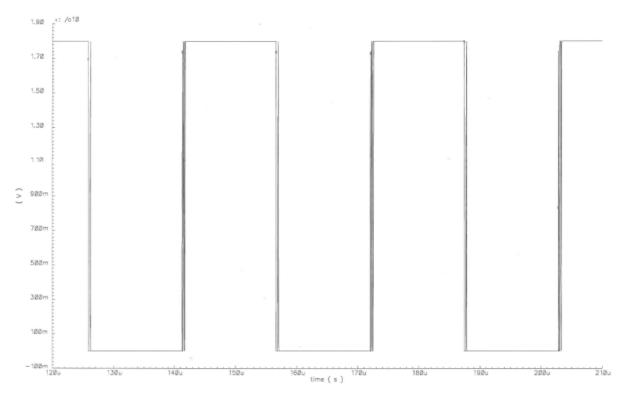

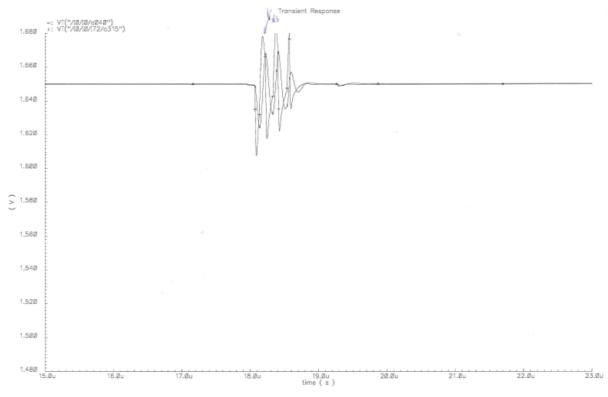

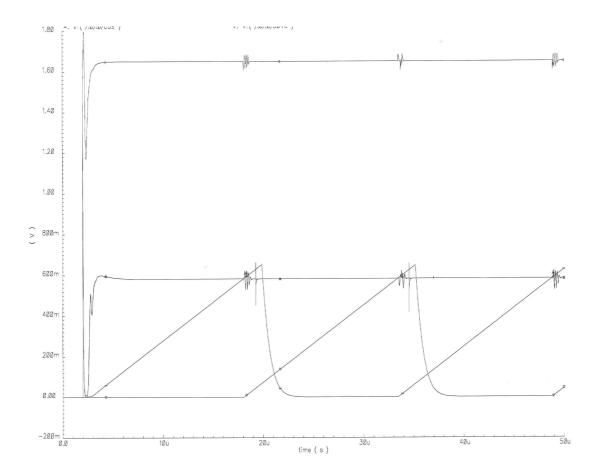

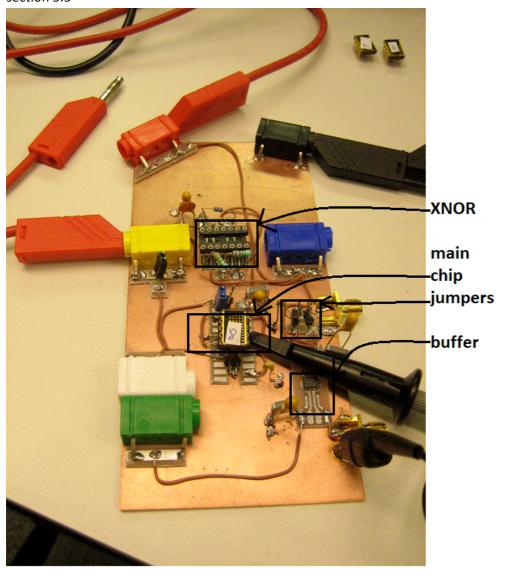

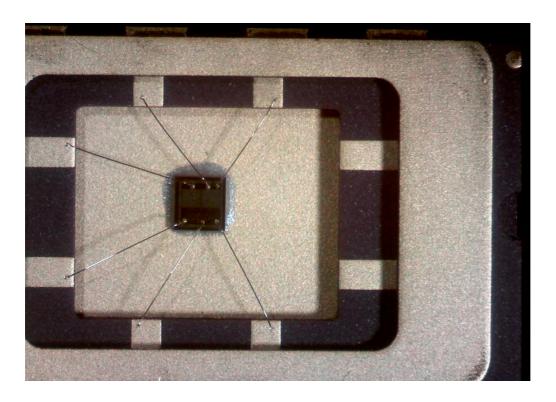

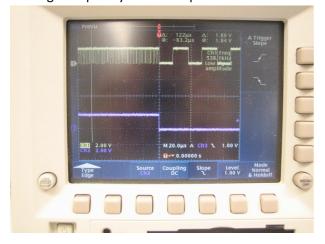

#### **DELAYS IN FIFTH IMPLEMENTATION**