### A Hybrid Magnetic Current Sensor With a Multiplexed Ripple-Reduction Loop

Jouyaeian, Amirhossein; Fan, Qinwen; Zamparette, Roger; Ausserlechner, Udo; Motz, Mario; Makinwa, Kofi A.A.

DOI

10.1109/JSSC.2023.3273389

**Publication date** 2023

**Document Version** Final published version

Published in

IEEE Journal of Solid-State Circuits

Citation (APA)

Jouyaeian, A., Fan, Q., Zamparette, R., Ausserlechner, U., Motz, M., & Makinwa, K. A. A. (2023). A Hybrid Magnetic Current Sensor With a Multiplexed Ripple-Reduction Loop. IEEE Journal of Solid-State Circuits, 58(10), 2874-2882. https://doi.org/10.1109/JSSC.2023.3273389

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A Hybrid Magnetic Current Sensor With a Multiplexed Ripple-Reduction Loop

Amirhossein Jouyaeian<sup>®</sup>, *Member, IEEE*, Qinwen Fan, *Senior Member, IEEE*, Roger Zamparette<sup>®</sup>, *Graduate Student Member, IEEE*, Udo Ausserlechner<sup>®</sup>, Mario Motz, *Member, IEEE*, and Kofi A. A. Makinwa<sup>®</sup>, *Fellow, IEEE*

Abstract—This article presents a hybrid magnetic current sensor for galvanically isolated measurements. It consists of a CMOS chip that senses the magnetic field generated by current flowing through a lead-frame-based current rail. Hall plates and coils are used to sense low-frequency (dc to 10 kHz) and high-frequency (10 kHz to 5 MHz) magnetic fields, respectively. With the help of on-chip calibration coils, the biasing current of the Hall plates is trimmed to match the sensitivity of the Hall and coil signal paths. The sensitivity drift of the coil path with temperature is compensated by using temperaturedependent gain-setting resistors, while the drift of the Hall path is compensated by biasing the Hall plates with a proportionalto-absolute-temperature (PTAT) current. The resulting sensitivity drift is less than 9% from -40 °C to 80 °C. The offset of the Hall plates is reduced by the current spinning technique, and the resulting ripple is suppressed by a multiplexed ripple-reduction loop (MMRL). Fabricated in a standard 0.18-μm CMOS process, the current sensor occupies 4.6 mm<sup>2</sup> and draws 7.8 mA from a 1.8-V supply. It achieves a gain variation of only  $\pm 2\%$  in a 5-MHz BW. It also achieves high energy efficiency, with an figure of merit (FoM) of 1.6 fW/Hz.

Index Terms—Galvanic isolation, hybrid current sensors, magnetic current sensing, ripple-reduction loop (RRL), temperature compensation, wide bandwidth.

#### I. INTRODUCTION

NTEGRATED magnetic current sensors are widely used to control power converters, for motor health monitoring and in automotive electronics. Although shunt-based current sensors achieve high accuracy [1], [2], [3], [4], magnetic current sensors are preferred in high-power applications due to their inherent galvanic isolation and low insertion loss [5]. Furthermore, their wide intrinsic bandwidth (BW > 1 MHz) makes them well suited for sensing switching transients and short-circuit currents [6], [7].

Magnetic current sensors can be realized with the help of fluxgates and magnetoimpedance sensors [8], [9], [10],

Manuscript received 14 December 2022; revised 2 April 2023; accepted 25 April 2023. Date of publication 18 May 2023; date of current version 26 September 2023. This article was approved by Associate Editor Piero Malcovati. (Corresponding author: Amirhossein Jouyaeian.)

Amirhossein Jouyaeian, Qinwen Fan, Roger Zamparette, and Kofi A. A. Makinwa are with the Electronic Instrumentation Laboratory, Microelectronics Department, Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS), Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: a.jouyaeian@tudelft.nl).

Udo Ausserlechner and Mario Motz are with Infineon Technologies AG, A-9500 Villach, Austria.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2023.3273389.

Digital Object Identifier 10.1109/JSSC.2023.3273389

[11]. However, these cannot be implemented in standard CMOS technology, which increases their manufacturing cost. Furthermore, they have a limited linear input range and so are often used in closed-loop current sensing schemes, which then have limited BWs ( $<200~\rm kHz$ ). In [8], a current sensor based on a CMOS chip and a co-packaged integrated fluxgate (IFG) is presented. To keep the IFG in its linear operating region, the external magnetic field is locally canceled by a co-integrated compensation coil. The sensor achieves a resolution of 11 mA<sub>rms</sub> in a 125-kHz BW and exhibits an input-dependent power consumption (100 mW at  $B_{\rm in}=2~\rm mT$ ).

Magnetic current sensors based on Hall plates can provide CMOS compatibility, low fabrication cost, and high linearity over a wide range [5], [12], [13], [14], [15]. Recently, the use of X-Hall sensors [13], [16], as well as the combination of a spinning-current Hall sensor and an un-spun Hall sensor [17], has been proposed as ways to extend their BW (up to 11.6 MHz [16]). However, this comes at the expense of resolution, due to the fundamental tradeoff between their thermal noise and their BW. In contrast, the differentiating characteristic of on-chip coils means that they can achieve much wider BW and higher resolution [17], [18], [19], but they cannot sense dc signals.

Combining Hall plates and coils enables the realization of CMOS-compatible hybrid sensors, which can achieve both wide BW and high resolution [17], [18], [19], [20], [21]. In [17] and [21], a hybrid sensor is used to detect the differential magnetic field produced by a current-carrying copper trace. However, its front end senses coil voltage, which limits its dynamic range (DR) at high frequencies. It also employs a large off-chip capacitor (10  $\mu$ F) to suppress the dc offset of the coil path, which would otherwise contribute significant error to the dc-sensing Hall path. The sensor achieves a resolution of 480 mA<sub>rms</sub> in a 3-MHz BW while consuming 38.5 mW.

In [19], a hybrid sensor based on a vertical Hall plate and a single optimized Rogowski coil is presented. It also senses coil voltage but achieves a wider BW (15.3 MHz). To obtain a flat frequency response, it employs a two-stage integrator with an on-chip pole-zero cancellation scheme. However, it requires trimming to compensate for pole-zero mismatch. Moreover, the outputs of the coil and Hall paths are combined by an off-chip crossover network. Compared to [17], it consumes more power (63.4 mW) and achieves worse resolution (710 mA<sub>rms</sub>).

In [18], a hybrid current sensor senses coil current rather than coil voltage. It employs a two-stage low-pass filter (LPF) and a robust pole-zero cancellation scheme to suppress coil-path offset and sensitivity drift with temperature.

0018-9200 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

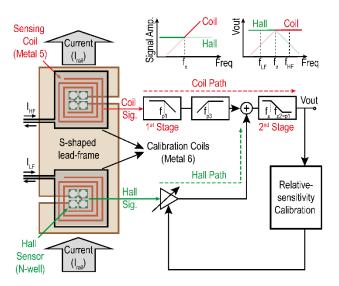

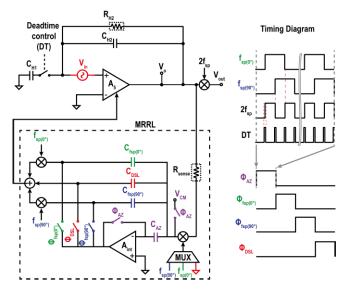

Fig. 1. Simplified system block diagram including the off-chip relative-sensitivity calibration scheme.

Compared to [17] and [19], it achieves  $7.5 \times$  better resolution (64 mA<sub>rms</sub>) and  $2 \times$  less power dissipation (19.5 mW). However, the use of the spinning-current technique to reduce Hall plate offset causes a significant residual ripple, which is  $\sim 4 \times$  larger than its resolution. In addition, the sensitivity of the Hall path is trimmed manually to match that of the coil path.

This article presents a hybrid magnetic current sensor that employs differential (gradiometric) coils and Hall plates to sense the magnetic field produced by a current-carrying lead frame. As in [18], a robust pole-zero cancellation scheme is used to suppress the offset of the coil path, while its sensitivity drift over temperature is compensated with the help of temperature-dependent gain-setting resistors. In contrast to [16], a multiplexed ripple-reduction loop (MRRL) is used to significantly suppress spinning ripple, while a proportional-to-absolute-temperature (PTAT) bias current compensates for the sensitivity drift of the Hall plates. Finally, the sensitivity of the Hall and coil paths is accurately matched by trimming the bias current of the Hall plates with the help of on-chip calibration coils.

This article is organized into three more sections. The proposed system, including the system architecture, the temperature compensation in both coil path and Hall path, the design of the MRRL, and the self-calibration scheme, is presented in Section II. Section III shows and discusses the measurement results. Finally, this article ends with conclusions.

#### II. PROPOSED HYBRID MAGNETIC CURRENT SENSOR

#### A. System Architecture

Fig. 1 shows a block diagram of the proposed current sensor. It consists of a CMOS chip mounted on an S-shaped current rail. The low-resistance (250  $\mu\Omega$ ) S-shaped lead frame concentrates the magnetic field seen by two coil/Hall plate pairs [18]. In addition, the current rail facilitates the use of a differential sensing scheme that rejects homogeneous interference, e.g., the Earth's magnetic field [17]. Each n-well Hall plate consists of four sub-plates connected in parallel, whose bias currents flow in four different directions to reduce

their combined offset and sensitivity to mechanical stress [22]. In contrast to [18], the Hall plates are not stacked, which leads to higher sensitivity and lower offset and enables operation from a single 1.8-V supply. Since the induced coil current is proportional to frequency, the coil path is designed to have an integrating characteristic, which is realized by a two-stage pole-zero cancellation scheme [18], [19], [20]. The first stage is an LPF with a pole at  $f_{p1}$ , and the second stage introduces another pole at  $f_x$  together with a zero at  $f_{z2}$ . This zero cancels the pole of the first stage  $(f_{p1})$ , thus turning the coil path into a first-order LPF with a pole  $f_{p2}$  (=  $f_X$ ) that defines the crossover frequency from the Hall to the coil paths. To suppress the offset of the first and second stages of the coil path, these stages are connected by an ac-coupling capacitor, which creates a parasitic pole at  $f_{p3}$ .

The output of the Hall plate is simply amplified and then added to the input of the coil path's second stage. In order to achieve a flat frequency response, the sensitivity of the Hall path must be adjusted to match the sensitivity of the coil path at  $f_x$ . As in [18], this is done by trimming the bias current of the Hall plates. The sensitivity of the coil and Hall path can be accurately determined by injecting known input currents  $I_{\rm HF}$  (at  $f_{\rm HP} > f_X$ ) and  $I_{\rm LF}$  (at  $f_{\rm LP} < f_X$ ) into two calibration coils located around the coil and Hall plates (Fig. 1).

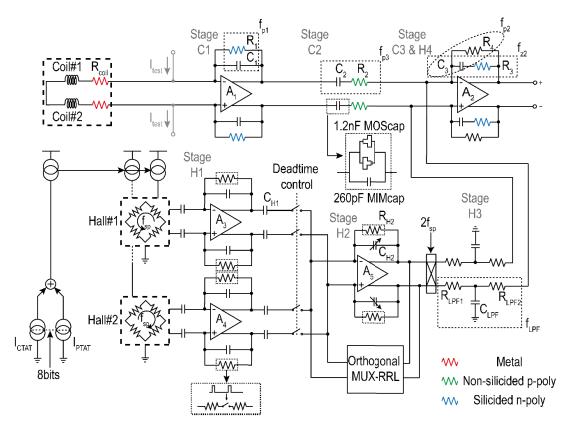

A simplified schematic of the two sensor paths is shown in Fig. 2. As in [18], the coil path consists of two stages. The input stage reads out the coil current and implements a pole  $f_{p1} = 200 \text{ kHz} (1/2\pi R_1 C_1)$ , thus limiting its output swing at higher frequencies. Compared to reading out the coil voltage, this approach greatly relaxes the design of the input stage.

As mentioned earlier, the 1st stage contributes a pole  $f_{p1}$ , while the 2nd stage contributes a pole  $f_{p2}$   $(1/2\pi R_4C_3) = 10$  kHz and a zero  $f_{z2}$   $(1/2\pi R_3C_3) = f_{p1} = 200$  kHz. This results in a coil path that behaves like a 1st-order LPF with a pole at 10 kHz  $(= f_X)$ . To ensure robust pole-zero cancellation,  $R_1C_1$  and  $R_3C_3$  are realized by the same type of components.

Although a 1st-order LPF could be implemented with a single stage,  $R_1$  would then be very large (6 M $\Omega$ , for  $C_1=25$  pF). Since the coil resistance is small ( $\sim 3$  k $\Omega$ ), the resulting dc gain would be quite large, causing the 1st stage to clip on its own millivolt-level offset. The two-stage architecture allows  $R_1$  to be 20 times smaller ( $f_{p1}=20$   $f_X$ ), thus ensuring that the input stage does not clip. Furthermore, its output offset will be blocked by  $C_2$ .

Together with  $R_2$ , however, the presence of  $C_2$  introduces a parasitic pole  $f_{p3}$ , which causes a dip in the overall transfer function (TF) around  $f_X$ . For a given coil path sensitivity, large capacitors are then needed to make  $f_{p3}$  as low as possible. In [16], these were realized by MIM capacitors, which occupied about 10% of the chip area. In this work,  $6 \times$  larger capacitors (1.5 nF) are realized in the same area by placing MOS capacitors under the MIM capacitors. The MOS capacitors are split into two halves, which are connected in an antiparallel fashion to reduce (by  $9 \times$ ) their voltage-dependent non-linearity. Over process corners, the resulting 230-Hz parasitic pole causes a 2.3% dip (worst case) in the sensor's TF.

Since the outputs of the Hall plates are quite small, they are first amplified by local capacitively coupled amplifiers (CCAs)

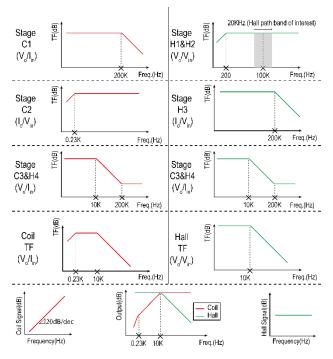

Fig. 2. Full system block diagram.

with a gain of 50  $(A_{3,4})$ , as shown in Fig. 2. Their outputs are summed by another CCA  $(A_5)$  with a gain of 12 and converted back to dc by a chopper demodulator. The offset caused by spinning-induced transients is reduced by deadband switches [18]. The amplified Hall signal is then applied to the output stage via a passive RC LPF with a pole at  $f_X$ , which, when combined with the TF of the coil path, results in a flat TF from dc to 8 MHz (the BW of the output stage), with an in-band gain variation of less than  $\pm 2.1\%$  (verified by Monte Carlo simulations). The Bode plots of the different stages of the coil and Hall paths are shown in Fig. 3.

#### B. Temperature Compensation

One drawback of Hall plates is their significant gain drift versus temperature (>20% from -70 °C to 170 °C [23]). In [23], this is compensated with the help of an on-chip temperature sensor. However, this requires (at least) a costly two-point trim. In [21], which employs a differential sensing scheme, on-chip calibration coils generate a common-mode magnetic field, with which the gain of the Hall plates can be continuously calibrated. An off-chip control loop then stabilizes their gain drift by adjusting their biasing current. This approach requires a separate readout for sensing the common-mode magnetic field and so consumes more power and chip area.

In this work, the TC of the Hall plates is approximately compensated by using a PTAT bias current ( $\sim$ 2.5 mA at room temperature). This current is implemented by forcing a PTAT voltage  $\Delta V_{\rm GS}$  (the difference in gate–source voltage between a pair of pMOS transistors biased at a fixed current ratio in their sub-threshold region) across a p-poly resistor.

Fig. 3. TFs of different stages in the coil path (left) and Hall path (right). The sensitivity of the coil path  $G_E$  can be expressed as

$$G_E = \begin{cases} \frac{R_1}{2\pi f x R_{\text{coil}} x R_2 x C_3}, & 10 \text{ kHz} < f < 200 \text{ kHz} \\ \frac{R_3}{2\pi f x R_{\text{coil}} x R_2 x C_1}, & f > 200 \text{ kHz}. \end{cases}$$

(1)

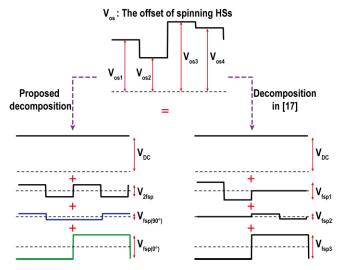

Fig. 4. Decomposition of a four-level Hall sensor offset into three orthogonal signals.

The sensing coil  $R_{coil}$  is made of metal with a large temperature coefficient (TC = 0.34%/K). By realizing  $R_{1,3}$ with silicided n-poly resistors (TC = 0.29%/K) and  $R_2$  with non-silicided p-poly resistors (TC = -0.02%/K), the coil path overall TC is reduced significantly, to about -0.03%/K.

#### C. Multiplexed Ripple-Reduction Loop

Although Hall plates can be easily realized in CMOS, they usually suffer from a large offset, typically about 10 mT [24].

This can be significantly reduced by the spinning-current technique, which involves changing the direction of the sensor's bias current periodically and thus converting offset into ac ripple [23], which can be suppressed by LPFs or by ripple-reduction loops (RRLs) [17]. The residual offset, which is mainly due to n-well inhomogeneity, can then be reduced to a few microteslas [12].

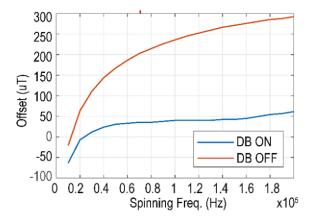

In this work, the modified spinning-current technique proposed in [25] is used to keep the Hall offset at dc, while the desired Hall voltage is upmodulated to twice the spinning frequency  $(2f_{sp} = 200 \text{ kHz})$ . This ensures that most of the offset is blocked by the CCAs, leaving only some components at  $f_{\rm sp}$ and  $2f_{sp}$ , which are again mainly due to n-well inhomogeneity. By ensuring that  $f_{sp}$  is much higher than  $f_X$ , this ripple will be significantly attenuated by the Hall-low-pass characteristic of the Hall path. However, the residual ripple is still quite significant and may limit sensor resolution [18].

To suppress the residual ripple further, RRLs can be used. As shown in Fig. 4, the residual ripple is a four-phase signal. This can be decomposed into three components, which are suppressed by three RRLs, [17]. In this work, however, we note that the spinning ripple can be decomposed into four different components: a dc offset, a square wave at  $2f_{sp}$ , and two quadrature square waves at  $f_{\rm sp}$ . The amplitude of these signals can be expressed as

$$V_{DC} = \frac{1}{4}(V_{os1} + V_{os2} + V_{os3} + V_{os4})$$

$$V_{2fsp} = \frac{1}{4}(V_{os1} - V_{os2} + V_{os3} - V_{os4})$$

$$V_{fsp(0^{\circ})} = \frac{1}{4}(-V_{os1} - V_{os2} + V_{os3} + V_{os4})$$

(4)

$$V_{2fsp} = \frac{1}{4}(V_{os1} - V_{os2} + V_{os3} - V_{os4})$$

(3)

$$V_{f \text{sp}(0^{\circ})} = \frac{1}{4} (-V_{\text{os}1} - V_{\text{os}2} + V_{\text{os}3} + V_{\text{os}4})$$

(4)

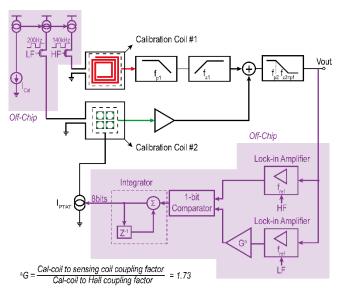

Fig. 5. Simplified single-ended multiplexing ripple-reduction loop (MRRL) and the timing diagram.

$$V_{f sp(90^{\circ})} = \frac{1}{4} (V_{os1} - V_{os2} - V_{os3} + V_{os4}).$$

(5)

The dc offset will be blocked by the CCA, while the ripple at  $2f_{\rm sp}$  cannot be distinguished from the desired Hall voltage. The other two ac components can then be suppressed by just two RRLs.

Since spinning ripple is a quasi-static error, the two RRLs can be efficiently realized by a single multiplexed RRL (MRRL) (Fig. 5). This is built around an opamp  $A_{int}$  and has four operating phases during which: 1) it auto-zeroes the offset of Aint, which would otherwise set the residual ripple amplitude; 2) it sequentially suppresses each of the two quadrature components; and 3) it suppresses the offset of  $A_5$  with a dc servo loop (DSL), which would otherwise be converted into extra ripple by the output chopper. Each quadrature component is detected by a chopper demodulator, integrated on an integration cap  $C_{fsp}$  to generate a correction signal, which is then upmodulated and fed back to  $A_5$  via an auxiliary input stage. The offset of  $A_5$  is detected in a similar manner, but with the chopper disabled. The switched-resistor technique is used to realize a large sensing resistor ( $R_{\text{sense}}$  > 100 M $\Omega$ ), resulting in narrow RRL notches (<1 kHz) that do not impact gain flatness.

By applying KCL at the output node of  $A_5$  ( $V_0$ ) and the virtual ground of  $A_5$ , the DSL TF  $((V_o/V_{in}))$  can be expressed

$$\frac{V_o}{V_{\text{in}}} = \frac{g_1}{\frac{(sC_{H1} + g_1)(sC_{H2}R_{H2} + 1)}{s(C_{H2} + C_{H1})R_{H2} + 1} + \frac{1}{R_o||R_s} + \frac{g_2}{\frac{1}{A_{\text{int}}} + sR_sC_{\text{DSL}}}}$$

(6)

where  $g_1$  is the transconductance of  $A_5$ ,  $g_2$  is the DSL parallel input pair transconductance, and  $R_o$  is the load resistor of  $A_5$ . By assuming that  $R_{H2}$  is large enough, the high-pass corner frequency of the DSL can be approximated as

$$f_{\rm DSL} = \frac{1}{2\pi R_{\rm s} C_{\rm DSL}} \cdot \frac{g_2}{g_1} \cdot \frac{C_{H1} + C_{H2}}{C_{H2}}.$$

(7)

Also, the DSL attenuation is

$$Att. = A_{int}. \frac{g_2}{g_1}. \tag{8}$$

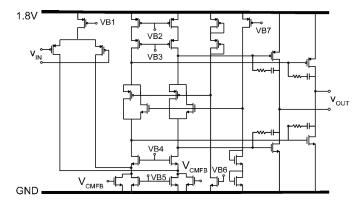

Fig. 6. Schematic of A1 and A2.

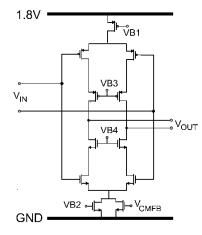

Fig. 7. Schematic of A3 and A4.

In this design,  $g_2 = 0.1g_1$ ,  $C_{\rm DSL} = 5$  pF,  $A_{\rm int} = 60$  dB,  $R_s = 100$  M $\Omega$ , and  $C_{H2} = 12C_{H1}$ , which leads to a DSL corner frequency  $f_{\rm DSL} = 400$  Hz and 40 dB attenuation.

By enabling the choppers before and after  $A_{int}$ , the DSL and its high-pass characteristic are converted to an RRL and a band-stop characteristic, respectively.

#### D. Amplifiers Implementation

$A_1$  and  $A_2$  are two-stage amplifiers with a folded-cascode input stage and a class-AB output stage (Fig. 6). In  $A_2$ , the output stage is required to drive an external 20-pF load capacitance, while in  $A_1$ , it is required to handle the large coil input currents at high frequencies. The equivalent input-referred noise of  $A_1$  is equal to the thermal noise resistance of  $R_{\rm coil}$  (3.3 k $\Omega$ ).

$A_3$  and  $A_4$  are current reuse telescopic amplifiers (Fig. 7) to match their noise contribution equal to the noise of Hall plate resistance  $R_{\rm Hall}$  (350  $\Omega$ ) with maximum noise efficiency.

#### E. Self-Calibration Scheme

To obtain a flat frequency response, the gain of the Hall plates can be trimmed to match with the coil path. This is achieved by adjusting the Hall plate's biasing currents with the help of an 8-bit PTAT current digital-to-analog converter (DAC), which can be used to trim the sensitivity of the Hall plates in steps of 1%.

As shown in Fig. 8, to realize the calibration scheme, two square-wave fixed currents (8 mA<sub>pp</sub>) at high (140 kHz) and

Fig. 8. Self-calibration scheme.

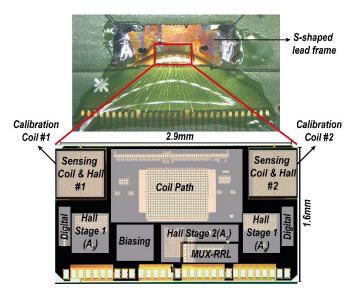

Fig. 9. Sensor die on a copper lead frame (top) and die micrograph (bottom).

low (200 Hz) frequencies are applied to the on-chip calibration coils. Since they are close to the sensors, these coils obviate the need to deliver large currents ( $\sim$  few amps) through the current rail for calibration. The magnetic fields generated by the calibration currents are detected by the sensing coils and Hall plates. The corresponding outputs are separated at the output of the final stage with two lock-in amplifiers. The outputs of the lock-in amplifiers are compared, and then, their difference is integrated to control the 8-bit current DAC. The large calibration-loop gain ensures that the difference is zero, and thus, the gain of the Hall and coil paths is matched. A 10-Hz measurement BW was used to achieve <1% trimming error. A G factor (1.73) is considered at the output of the lowfrequency lock-in amplifier to compensate for the different coupling factors between the calibration coil (metal 6) with the sensing coil (metal 5) and the Hall plate (substrate).

It should be mentioned that applying temperature compensation in both paths makes the overall TF robust to temperature drift, and thus, it only requires room-temperature calibration.

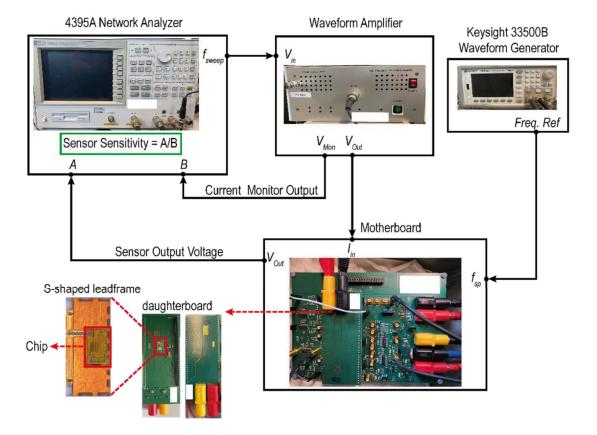

Fig. 10. Measurement setup.

To save the area, only the critical calibration coils were implemented on the chip, while the rest of the system was implemented off-chip.

#### III. MEASUREMENT RESULTS

The hybrid current sensor is fabricated in a standard 0.18-\$\mu\$m CMOS process (Fig. 9, bottom) and occupies 4.6 mm², which is mainly determined by the need to position the Hall/coil sensors above the slots of the S-shaped current rail. The die is isolated from the lead frame by non-conductive glue (Fig. 9, top). The chip is powered by an analog supply (1.8 V) and a digital VDD (1.8 V). All other bias currents/voltages are implemented on-chip. The sensor draws 7.8 mA, of which 5 mA is used to bias the Hall plates. To mitigate high-frequency crosstalk, two grounded on-chip shields are employed: one above the metal coil in metal 6, while the other is placed between the coil sensor and the Hall plate.

As shown in Fig. 10, a daughterboard printed board circuit (PCB) is mounted over a motherboard PCB to measure the sensor sensitivity. The daughterboard PCB includes the S-shape lead frame and the chip, while the motherboard consists of voltage regulators, differential-to-single-ended amplifiers, and an external clock reference. The calibration setup is also provided off-chip on the motherboard. A network analyzer that sweeps over the frequency is connected to a waveform amplifier with high current capability. The output of the waveform amplifier delivers the current to the current rail. The sensor sensitivity can be determined at different frequencies by measuring the ratio between the sensor

Fig. 11. Sensitivity versus temperature.

output voltage and the waveform amplifier current monitor output.

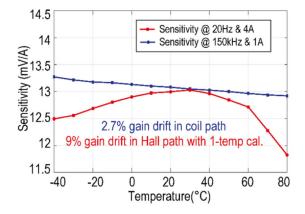

The sensitivities of the Hall and coil paths over temperature are shown in Fig. 11. The PTAT bias current effectively compensates for the linear component of the Hall plate's temperature dependency, resulting in a 9% gain drift in the Hall path. The 2.7% gain drift in the coil path is due to the expected residual TC of using different resistors.

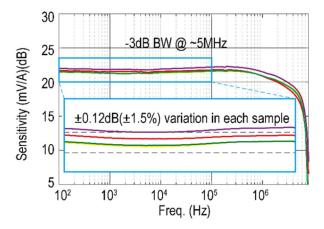

After trimming at room temperature, the measured TF of the sensor is shown in Fig. 12. Its 3-dB bandwidth is limited to 5 MHz by eddy currents induced in the current rail. Around  $f_X$  (dc-to-100 kHz), the measured gain variation is less than  $\pm 1.5\%$  ( $\pm 0.12$  dB), which is about  $6\times$  less than that reported in [18]. The spread above 200 kHz is caused by

Fig. 12. Sensitivity versus frequency magnitude.

Fig. 13. Uncalibrated offset versus  $f_{sp}$  w/ deadbanding on/off.

the manual alignment of the chips with the slots in the current rail.

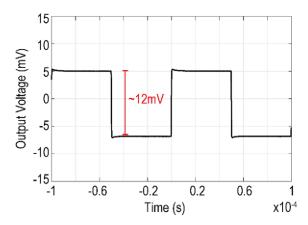

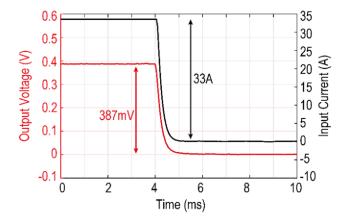

The DR of the sensor was determined experimentally. At dc, the self-heating of the current rail limits the maximum input current to  $\sim$ 33 A. As the input frequency is increased above  $f_X$ , the induced coil voltage increases, causing the input stage of the coil path to eventually clip. By injecting a test current into the coil path, it was found to have a BW of  $\sim$ 8 MHz, with the onset of clipping (THD = 3%) corresponding to 33 A<sub>rms</sub>(46 Ap) at 300 kHz in the current rail. As shown in Fig. 13, the use of deadbanding makes the Hall plate offset relatively independent of  $f_{\rm sp}$ . For a good tradeoff between offset and the filtering of residual spinning ripple,  $f_{\rm sp} = 99$  kHz was chosen. This results in the worst case offset of 57  $\mu T$  (4 samples), which corresponds to 130 mA in the current rail. The sensor's response to small (1 A) and large (33 A) steps is shown in Figs. 14 and 15, respectively. In the case of the large step, the slow fall time is mainly due to the limitations of the 33-A current supply.

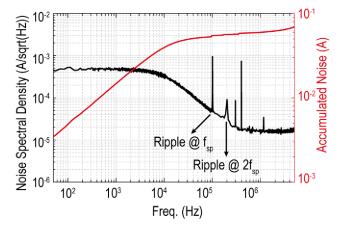

Fig. 16 shows the noise spectral density together with the accumulation noise. The MRRL suppresses the main spinning ripple (at  $f_{\rm sp}$  and  $3f_{\rm sp}$ ) by more than 20 dB. The total input-referred ripple corresponds to 16 mA<sub>rms</sub> (5  $\mu T_{\rm rms}$ ), which is about 20% less than that reported in [17]. In a 5-MHz bandwidth, the sensor's accumulated noise corresponds to 69 mA<sub>rms</sub> (20  $\mu T_{\rm rms}$ ). It should be mentioned that the current resolution depends on the proximity of the current rail to the

Fig. 14. Transient response for a 1- $A_{p-p}$  square-wave@10 kHz (After  $1024 \times$  averaging).

Fig. 15. 33-A step response.

Fig. 16. Noise spectral density and accumulated noise referred to current rail.

on-chip sensors. Thus, designs with on-chip current rails may have a higher current resolution at the expense of increased manufacturing cost and galvanic isolation. Finally, the residual ripple at  $f_{\rm sp}$  only causes a 2-mA step in the total accumulated noise. The residual ripple is mainly due to the limited BW of the CCAs. As a result, the ripple components are not perfect square waves, and thus, they are not completely canceled by the RRLs. Switching transients also contribute to the residual ripple.

| Source                                | This<br>work     | ISSCC'21<br>[16] | JSSC'17<br>[17]  | JSSC'19<br>[15] | JSSC'22<br>[8]       | APEC'19<br>[18] |

|---------------------------------------|------------------|------------------|------------------|-----------------|----------------------|-----------------|

| Sensor Type                           | Coil + Hall      | Coil + Hall      | Coil + Hall      | Hall            | IFG                  | Coil + Hall     |

| Technology (μm)                       | 0.18             | 0.18             | 0.18             | 0.35            | 0.25                 | 0.18            |

| Supply (V)                            | 1.8              | 1.8/3.3          | 5                | 3.3             | 1.8/5                | 1.8             |

| Area (mm²)                            | 4.6              | 4.6              | 8.75             | N/A             | 4+3.6                | 2.74            |

| Resolution (mA <sub>rms</sub> )       | 69               | 64               | 480              | 480             | 11°                  | 710             |

| Input Range (A)                       | ±46 <sup>a</sup> | ±25              | ±18 <sup>a</sup> | ±300            | ±53°                 | ±60             |

| Dynamic Range (dB)                    | 54               | 52               | 17               | 56              | 74                   | 39              |

| BW (MHz)                              | 5                | 1.8              | 3                | 1.7             | 0.125                | 15.3            |

| Power Consumption (mW)                | 14               | 19.5             | 38.5             | 13.2            | 100 <sup>d</sup> +13 | 63.5            |

| Gain Flatness                         | ±1.5%            | ±12%             | <u>N/A</u>       | <u>N/A</u>      | <u>N/A</u>           | ±3.7%           |

| Residual Ripple @f <sub>sp</sub> (μT) | 6                | 74               | 8                | <u>N/A</u>      | <u>N/A</u>           | <u>N/A</u>      |

| Residual Offset (μT)                  | 57               | 75               | 40               | 262             | <u>N/A</u>           | <u>N/A</u>      |

| FoM <sup>b</sup> [fW/Hz]              | 1.6              | 17.7             | 2281             | 5               | 8.5                  | 145             |

| DR + 10log(BW/Power)                  | 139              | 131              | 96               | 137             | 135                  | 122             |

TABLE I

PERFORMANCE SUMMARY AND COMPARISON

Table I summarizes the performance of the proposed hybrid current sensor and compares it with state-of-the-art magnetic current sensors. Compared to [18], the gain flatness and input-referred ripple are improved by  $6\times$  and  $16\times$ , respectively. This design also achieves the highest energy efficiency figure of merit (FoM)  $(3\times)$  and the lowest power consumption  $(1.4\times)$  of all hybrid sensors.

#### IV. CONCLUSION

In this work, a hybrid magnetic current sensor with wide BW (5 MHz) is proposed. A multiplexed RRL is employed to effectively deal with the Hall plate offset in different spinning phases. With this approach, the residual ripple at the spinning frequency is  $4 \times$  below the total integrated noise. The offset of the coil path is blocked by large on-chip capacitors (1.5 nF each), which are implemented in an area-efficient manner by placing MOS capacitors below MIM capacitors. The drift in the sensitivity of the coil path over temperature is compensated with the help of silicided poly resistors, which have nearly the same TC as the metal coils, while the drift of the Hall path is compensated by biasing them with a PTAT current. The resulting temperature drift is limited to 9% from -40 °C to 80 °C, mainly due to the residual drift of the Hall path. A one-time room-temperature calibration scheme with on-chip calibration coils is utilized to equalize the sensitivity of the Hall and coil paths. The overall sensor achieves the state-ofthe-art energy efficiency with an FoM of 1.6 fW/Hz.

#### ACKNOWLEDGMENT

The authors would like to thank Zu-yao Chang and Lukasz Pakula for chip bonding.

#### REFERENCES

[1] S. H. Shalmany, D. Draxelmayr, and K. A. A. Makinwa, "A ±36-A integrated current-sensing system with a 0.3% gain error and a 400-μA offset from -55 °C to +85 °C," *IEEE J. Solid-State Circuits*, vol. 52, no. 4, pp. 1034–1043, Apr. 2017.

- [2] R. Zamparette and K. Makinwa, "A ±2A/15A current sensor with 1.4 μA supply current and ±0.35%/0.6% gain error from -40 to 85 °C using an analog temperature-compensation scheme," in *Proc. Symp. VLSI Circuits*, Jun. 2021, pp. 1–2.

- [3] Z. Tang, R. Zamparette, Y. Furuta, T. Nezuka, and K. A. A. Makinwa, "A versatile ±25-A shunt-based current sensor with ±0.25% gain error from −40 °C to 85 °C," *IEEE J. Solid-State Circuits*, vol. 57, no. 12, pp. 3716–3725, Dec. 2022.

- [4] L. Xu, J. H. Huijsing, and K. A. A. Makinwa, "A ±4-A high-side current sensor with 0.9% gain error from -40 °C to 85 °C using an analog temperature compensation technique," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3368–3376, Dec. 2018.

- [5] P. D. Dimitropoulos, P. M. Drljaca, and R. S. Popovic, "A 0.35 um-CMOS, wide-band, low-noise Hall magnetometer for current sensing applications," in *Proc. IEEE Sensors*, Oct. 2007, pp. 884–887.

- [6] T. Funk and B. Wicht, Integrated Wide-Bandwidth Current Sensing. Berlin, Germany: Springer, 2020.

- [7] Z. Xin, H. Li, Q. Liu, and P. C. Loh, "A review of megahertz current sensors for megahertz power converters," *IEEE Trans. Power Electron.*, vol. 37, no. 6, pp. 6720–6738, Jun. 2022.

- [8] P. Garcha et al., "A duty-cycled integrated-fluxgate magnetometer for current sensing," *IEEE J. Solid-State Circuits*, vol. 57, no. 9, pp. 2741–2751, Sep. 2022.

- [9] I. Akita, T. Kawano, H. Aoyama, S. Tatematsu, and M. Hioki, "A 2.6 mW 10pTI \( \forall \text{Hz} 33 \) kHz magnetoimpedance-based magnetometer with automatic loop-gain and bandwidth enhancement," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2022, pp. 1–3.

- [10] M. Kashmiri, W. Kindt, F. Witte, R. Kearey, and D. Carbonell, "A 200 kS/s 13.5b integrated-fluxgate differential-magnetic-to-digital converter with an oversampling compensation loop for contactless current sensing," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 490–492.

- [11] M. F. Snoeij, V. Schaffer, S. Udayashankar, and M. V. Ivanov, "Integrated fluxgate magnetometer for use in isolated current sensing," *IEEE J. Solid-State Circuits*, vol. 51, no. 7, pp. 1684–1694, Jul. 2016.

- [12] J. C. van der Meer, F. R. Riedijk, E. van Kampen, K. A. A. Makinwa, and J. H. Huijsing, "A fully integrated CMOS Hall sensor with a 3.65  $\mu$ T  $3\sigma$  offset for compass applications," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2005, pp. 246–247.

- [13] M. Crescentini et al., "The X-Hall sensor: Toward integrated broadband current sensing," *IEEE Trans. Instrum. Meas.*, vol. 70, pp. 1–12, 2021.

- [14] M. Crescentini, S. F. Syeda, and G. P. Gibiino, "Hall-effect current sensors: Principles of operation and implementation techniques," *IEEE Sensors J.*, vol. 22, no. 11, pp. 10137–10151, Jun. 2022.

<sup>&</sup>lt;sup>a</sup>Extrapolated

$<sup>{}^{</sup>b}FoM = Power/(BW \times (Range/Resolution)^{2})$

<sup>&</sup>lt;sup>c</sup>Conversion rate =  $45\mu T/A$

dFull-range power

- [15] Y. Li, M. Motz, and L. Raghavan, "A fast T&H overcurrent detector for a spinning Hall current sensor with ping-pong and chopping techniques," *IEEE J. Solid-State Circuits*, vol. 54, no. 7, pp. 1852–1861, Jul. 2019.

- [16] S. F. Syeda, M. Crescentini, R. Canegallo, and A. Romani, "A broadband current-mode X-Hall sensor for smart power and metering applications," in *Proc. IEEE Int. Conf. Environ. Electr. Eng.*, *IEEE Ind. Commercial Power Syst. Eur.*, Sep. 2021, pp. 1–6.

- [17] J. Jiang and K. A. A. Makinwa, "Multipath wide-bandwidth CMOS magnetic sensors," *IEEE J. Solid-State Circuits*, vol. 52, no. 1, pp. 198–209, Jan. 2017.

- [18] A. Jouyaeian, Q. Fan, M. Motz, U. Ausserlechner, and K. A. A. Makinwa, "A 25A hybrid magnetic current sensor with 64 mA resolution, 1.8 MHz bandwidth, and a gain drift compensation scheme," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 82–84.

- [19] T. Funk, J. Groeger, and B. Wicht, "An integrated and galvanically isolated DC-to-15.3 MHz hybrid current sensor," in *Proc. IEEE Appl. Power Electron. Conf. Exposit. (APEC)*, Mar. 2019, pp. 1010–1013.

- [20] T. Funk and B. Wicht, "A fully integrated DC to 75 MHz current sensing circuit with on-chip Rogowski coil," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2018, pp. 1–4.

- [21] J. Jiang and K. A. A. Makinwa, "A hybrid multi-path CMOS magnetic sensor with 76 ppm/°C sensitivity drift and discrete-time ripple reduction loops," *IEEE J. Solid-State Circuits*, vol. 52, no. 7, pp. 1876–1884, Jul. 2017.

- [22] M. Motz et al., "A miniature digital current sensor with differential Hall probes using enhanced chopping techniques and mechanical stress compensation," in *Proc. IEEE Sensors*, Oct. 2012, pp. 1–4.

- [23] S. Huber, W. Leten, M. Ackermann, C. Schott, and O. Paul, "A fully integrated analog compensation for the piezo-Hall effect in a CMOS single-chip Hall sensor microsystem," *IEEE Sensors J.*, vol. 15, no. 5, pp. 2924–2933, May 2015.

- [24] P. Kejik, P.-F. Bourdelle, S. Reymond, F. Salvi, and P.-A. Farine, "Offset compensation based on distributed Hall cell architecture," *IEEE Trans. Magn.*, vol. 49, no. 1, pp. 105–108, Jan. 2013.

- [25] C. Schott, R. Racz, A. Manco, and N. Simonne, "CMOS single-chip electronic compass with microcontroller," *IEEE J. Solid-State Circuits*, vol. 42, no. 12, pp. 2923–2933, Dec. 2007.

Amirhossein Jouyaeian (Member, IEEE) received the B.Sc. and M.Sc. degrees from the Sharif University of Technology, Tehran, Iran, in 2015 and 2017, respectively. He is currently pursuing the Ph.D. degree with the Delft University of Technology, Delft, The Netherlands.

He joined the Kavoshcom Research and Development Group, Tehran, in 2018, where he was involved in designing Li-Fi systems. His current research interests include magnetic current sensors and other precision analog and mixed-signal integrated circuits

Qinwen Fan (Senior Member, IEEE) received the B.Sc. degree in electronic science and technology from Nankai University, Tianjin, China, in 2006, and the M.Sc. degree (cum laude) in microelectronics and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2008 and 2013, respectively.

From October 2012 to May 2015, she worked at Maxim Integrated Products, Delft, The Netherlands. From June 2015 to January 2017, she worked at Mellanox, Delft. In 2017, she rejoined the Delft

University of Technology, where she is currently an Assistant Professor with the ECTM. She has published more than 20 top scientific papers, including ISSCC, VLSI, JSSC, and APEC. She also holds multiple patents with industrial partners, including ADI, ASML, and Infineon. Her current research interests include precision analog, high-performance class-D audio amplifiers, smart power inverters in wide bandgap semiconductors, low-power dc-dc converters for energy harvesters, and low-power circuits for the IoT nodes.

Dr. Fan serves as an Associate Editor for Open Journal of the Solid-State Circuits Society (OJ-SSCS) and a TPC Member for the International Solid-State Circuits Conference (ISSCC), the VLSI Symposium on Technology and Circuits, and the European Solid-State Circuits Conference (ESSCIRC). She is also a Distinguished Lecturer of the SSCS Society.

Roger Zamparette (Graduate Student Member, IEEE) received the B.E. degree in electrical engineering from the State University of Santa Catarina-UDESC, Joinville, Brazil, in 2014, and the M.Sc. degree from the Federal University of Rio Grande do Sul-UFRGS, Porto Alegre, Brazil, in 2017. He is currently pursuing the Ph.D. degree with the Delft University of Technology, Delft, The Netherlands.

Udo Ausserlechner was born in Badgastein, Austria, in 1968. He received the M.Sc. degree in electrical engineering from the Faculty of Electrical Engineering, Technical University of Vienna, Vienna, Austria, in 1991, and the Ph.D. degree in physics from the Faculty of Natural Sciences, Technical University of Vienna, in 1996, where he developed a theory of the signals induced in pick-up coils of vibrating sample magnetometers and constructed a cryogenic 15-T magnetometer for studies in solid-state physics.

Since 1997, he has been a Microelectronic Circuit Design Engineer of integrated magnetic sensor ICs for automotive applications. He is currently with Infineon Technologies Austria AG, Villach, Austria. He has authored more than 150 granted patents in analog circuits and magnetic sensors. His main fields of work comprise integrated magnetic sensors (in particular Hall sensors), mechanical stress in plastic packages, equipment for testing magnetic sensors, and magnetic sensor arrangements for automotive applications.

Mario Motz (Member, IEEE) was born in Germany. He received the Diploma degree in technical cybernetics from TH Magdeburg, Magdeburg, Germany, in 1983.

In 1990, he worked as a Design Engineer for A/D and D/A converters in the semiconductor plant of Frankfurt/Oder, Germany. He joined Gaertner Elektronik in 1990 and ITT Intermetal (now Micronas AG), Freiburg, Germany, in 1991, where he designed Hall sensor ICs in CMOS technology. Since 1999, he has been with Siemens AG (now Infineon Technology.

nologies AG), Villach, Austria, where he is currently a Distinguished Engineer for analog/mixed-signal circuit design. His work is focused on precision sensor ICs, bandgaps and oscillators, ADCs, EMC-robust circuits and ultralow-power circuits, and compensation techniques for mechanical stress effects, offset, and sensitivity of sensors. He filed more than 150 patents and 12 IEEE publications as an author or a coauthor in these areas.

Kofi A. A. Makinwa (Fellow, IEEE) received the B.Sc. and M.Sc. degrees from Obafemi Awolowo University, Ife, Nigeria, in 1985 and 1988, respectively, the M.E.E. degree from the Philips International Institute, Eindhoven, The Netherlands, in 1989, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2004.

From 1989 to 1999, he was a Research Scientist with Philips Research Laboratories, Eindhoven, where he worked on interactive displays and digital recording systems. In 1999, he joined the Delft

University of Technology, where he is currently an Antoni van Leeuwenhoek Professor and the Head of the Microelectronics Department. This has led to 17 books, more than 300 technical articles, and more than 30 patents. His research interests include the design of mixed-signal circuits, sensor interfaces, and smart sensors.

Dr. Makinwa is a member of the Royal Netherlands Academy of Arts and Sciences. He is an ISSCC Top-Ten Contributor (with more than 60 articles) and was a co-recipient of 17 best paper awards, including from the IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC) (2), ISSCC (5), and the VLSI Circuits Symposium (2), among others. He was the Analog Subcom Chair of ISSCC and has served on the program committee of several other IEEE conferences. He is also one of the organizers of the Advances in Analog Circuit Design Workshop and the IEEE Sensor Interfaces Meeting. He has also served the Solid-State Circuits Society as a Distinguished Lecturer and was elected as a member of its Adcom.