# High-Pass ΣΔ Converter Design Using a State-Space Approach and Its Application to **Cardiac Signal Acquisition**

Rout, Samprajani; Serdijn, Wouter

DOI

10.1109/TBCAS.2018.2817926

**Publication date**

**Document Version** Accepted author manuscript

Published in

IEEE Transactions on Biomedical Circuits and Systems

Citation (APA)

Rout, S., & Serdijn, W. (2018). High-Pass ΣΔ Converter Design Using a State-Space Approach and Its Application to Cardiac Signal Acquisition. *IEEE Transactions on Biomedical Circuits and Systems*, *12*(3), 483-494. https://doi.org/10.1109/TBCAS.2018.2817926

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# High-pass $\Sigma\Delta$ converter design using a state-space approach and its application to cardiac signal acquisition

Samprajani Rout, Student Member, IEEE and Wouter Serdijn, Fellow, IEEE

Abstract—Cardiac signal acquisition with high linearity and accuracy of the high-pass cut-off frequency imposes a challenge on the implementation of the analog preprocessing and the analog-to-digital converter. This paper describes a state-space based methodology for designing high-pass sigma-delta (HP $\Sigma\Delta$ ) topologies, targeting high accuracy and linearity of the high-pass cut-off frequency. Intermediate functions are evaluated mathematically to compare the proposed HP $\Sigma\Delta$  topologies with respect to dynamic range. A sensitivity performance analysis of the noise transfer function with respect to integrator non-idealities and coefficient variations is also described. Finally, to illustrate the design approach, an orthonormal HP $\Sigma\Delta$  modulator is designed to be implemented in 0.18  $\mu$ m CMOS technology, is tested with real pre-recorded ECG signals.

Index Terms—State-space synthesis, high-pass sigma-delta converter, orthonormal, intermediate functions, sensitivity, ECG, baseline wandering.

### I. INTRODUCTION

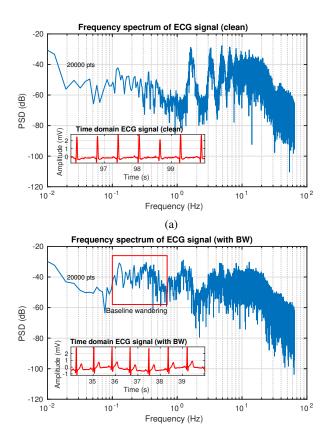

LECTROCARDIOGRAPHY (ECG), the recording of electric signals generated by the heart, is used as a diagnostic monitoring method for cardiovascular diseases (CVDs). It contains specific physiological information about the functioning of the heart. To meet the growing demand of the geriatric population and to reduce the burden on the public health-care system, there is a requirement of compact, inexpensive health-care devices that enable continuous ECG recording for the detection of cardiac arrhythmias that manifest themselves as aperiodic events over a period of days or weeks. Acquisition of the ECG is faced with the challenge of removal of the baseline wandering due to respiration or movements while recording. Baseline wandering (BW), which contributes to low frequency interference, is responsible for distortion of the acquired waveform and poses a challenge in accurate interpretation of the CVDs. In order to minimize the effect of baseline wandering, it is necessary to implement a high-pass filter with high linearity and an accurate cut-off frequency. As per the International Electrotechnical Commission (IEC) standards, the recommended ECG bandwidth extends from 50 mHz to 200 Hz. However, the baseline wander, which could be lying inband at the lower end, may require a higher high-pass cut-off frequency for its removal [1], [2]. It can be observed in Fig. 2a, derived from the MIT-BIH normal sinus rhythm database (Record 17453), [3], [4], that there is a large amount

Figure 1: Analog front-end for ECG acquistion

Figure 2: Power spectral density of (a) Clean ECG (b) ECG with baseline wandering (Data courtesy: MIT-BIH database [3])

of signal energy around the sub-Hz region. Fig. 2b, derived from the MIT-BIH normal sinus rhythm database (Record 16773), shows the effect of baseline wandering resulting from low frequency interference lying in the sub-Hz region.

With the bandwidth of the ECG signal extending from sub-Hz to 200 Hz [5], a major challenge for an ECG readout system lies in implementing the sub-Hz high-pass cut-off

S. Rout and W. A. Serdijn are with the Section Bioelectronics, Delft University of Technology, 2628 Delft, The Netherlands (e-mail: s.rout@tudelft.nl; w.a.serdijn@tudelft.nl).

frequency  $(f_{hof})$  as this translates into the realization of large time constants. To realize large time constants in the order of a few seconds, there exist techniques that employ pseudoresistors [6]–[8] or  $g_m$  blocks [9] or off-chip solutions such as using an IIR-filter [10] or a resistor [11]. Recently, a new technique to implement large time-constants has been introduced, employing duty-cycled resistors [12]. Although this technique is an attractive alternative, the position of the high-pass pole is still determined by the product of R and C, which is less accurate than a switched capacitor implementation. Moreover, the resistance would occupy a larger area as compared to a small sampling capacitor for the same  $f_{\rm hpf}$ . Pseudo-resistors, designed using transistors biased in the cut-off region to obtain extremely large resistances are not very robust to PVT variations. As these transistors are intrinsically non-linear, the resistances vary with the signal level, eventually leading to clipping at the extremes [13]. As there is quite some energy in the spectrum around the highpass cutoff frequency, a.o., due to baseline wandering, this leads to a reduced dynamic range. Also, as the momentary value of the resistance depends on the momentary value of the input signal, the RC time-constant is not fixed. Note, in such a case it would be better to talk about the dynamic eigenvalue of the non-linear differential equation implemented by the pseudo-resistor-capacitor combination. Depending on the choice of the implementation of the resistance, there is a trade-off between the area consumption, linearity around the  $f_{\rm hpf}$  cut-off and the accuracy of the  $f_{\rm hpf}$ . The existing solutions do not focus on achieving the same linearity around the highpass cut-off frequency as the rest of the signal band, although it is an important performance metric in order to acquire a low-distortion bio-signal waveform, especially in the case of cardiac signals aimed at diagnostic monitoring quality. Hence, when better linearity and accuracy are required, alternative techniques need to be developed.

In this paper, a synthesis procedure for developing  $HP\Sigma\Delta$  converters suitable for designing the high-pass filtering analog front-end for ECG signal acquisition is proposed.  $\Sigma\Delta$  ADCs take advantage of their noise shaping property to achieve low quantization noise and the use of 1-bit digital-to-analog converter ensures inherent linearity. As opposed to conventional low-pass  $\Sigma\Delta$  converters, a signal transfer that accommodates a general filter transfer is considered. Intermediate transfer function analysis evaluates the signal handling capabilities and the noise contributions of each of the integrators and thus helps in the overall ranking of the developed  $HP\Sigma\Delta$  topologies. Sensitivity of the developed  $HP\Sigma\Delta$  topologies to coefficient variations and non-idealities of the integrator is also investigated.

The rest of the paper is organized as follows. In Section II, the methodology to develop  $HP\Sigma\Delta$  topologies is proposed. The entire design procedure is demonstrated through design examples and compared qualitatively. In Section III, intermediate functions are derived for quantitative evaluation of the topologies. Further, the sensitivities to coefficient variations and to integrator non-idealities are described and evaluated in Section IV. Circuit design, simulation results and comparison with related prior art are explained in Section V. Finally, the

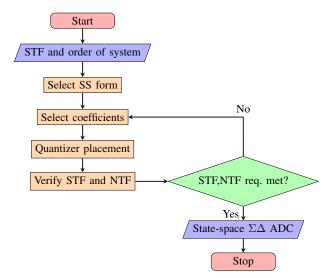

Figure 3: Flowchart of the state-space based approach for  $\Sigma\Delta$  topologies [14]

conclusions are summarized in Section VI.

### II. PROPOSED METHODOLOGY

System design incorporating digitization and filtering using an orthogonal design methodology allows us to arrive at topologies satisfying the signal and noise transfer function requirements while optimizing the performance metrics relevant to low power and low voltage designs such as dynamic range and sensitivity to coefficient variations. Conventionally,  $\Sigma\Delta$  modulator topologies have a low-pass filter signal transfer characteristic. However, in this approach, to accommodate a general signal transfer function including low-pass, high-pass, notch and band-pass filter characteristics, state-space forms can be used to design application-specific  $\Sigma\Delta$  modulator topologies. For the target application, viz. acquisition of a cardiac signal whose bandwidth extends from sub-Hz to 200 Hz [5], it is possible to implement the low-pass and the high-pass cut-off frequency separately. The implementation of the low-pass cut-off frequency can be readily merged with the front-end amplifier and will not be discussed in this paper. To implement the high-pass transfer function with good linearity and accuracy, it is embedded in the  $\Sigma\Delta$  converter, thus eliminating the need for a dedicated high-pass filter.

For a given state-space form, the coefficients are evaluated for their contributions to the signal and noise transfer function requirements. In this analysis, we have focused only on the inband properties of the modulator. The influence of the sampler on the transfer function in this region is negligible due to the large oversampling ratio (OSR). The placement of the quantizer depends on the requirement of the quantization noise transfer. A single quantizer is considered. Multiple quantizers can also be used and would lead to alternative topologies with different constraints [15], but this is considered beyond the scope of the paper. For the sake of simplicity and clarity, a 3<sup>rd</sup> order system is considered. A first order high-pass filter is considered sufficient for the application [16]. A higher order high-pass filter would come at an additional power and area

cost. However, the approach can be extended to higher orders as per the application specifications. The requirements of the transfer function for a  $3^{\rm rd}$  order system are:

- Signal transfer function (STF): a high-pass filter characteristic with at least one pole, the location of which can be set independently;

- Noise transfer function (NTF): a high-pass filter characteristic with all real zeros at the origin, leading to a 40 dB/dec slope in the signal band;

Fig. 3 shows the design procedure proposed to develop the desired state-space based high-pass  $\Sigma\Delta$  topologies [14]. Based on the resolution and the signal transfer requirements of the target application, the STF type, the order of the system and the state-space form can be chosen. The coefficients of the state-space forms correspond to physical components to be realized in silicon that play an important role in determining the noise, area and power consumption. The quantizer is placed such that the quantization NTF is satisfied. The STF and NTF of the topologies are verified through transfer function calculations. If the requirements of the STF and NTF are not met, the coefficients are re-evaluated until all the requirements are satisfied.

A linear, time-invariant dynamic system can be described using a set of first order differential equations. The general state-space description of an n<sup>th</sup> order system is given by

$$\dot{\mathbf{x}}(t) = \mathbf{A}\mathbf{x}(t) + \mathbf{b}u(t)$$

$$y(t) = \mathbf{c}^{\mathsf{T}}\mathbf{x}(t) + du(t)$$

(1)

where  $\mathbf{x}(t)$  is an  $n \times 1$  vector representing the integrator states or outputs, where n is the number of integrators, ideally equal to the order of the system,  $\mathbf{A}$  is an  $n \times n$  state matrix that describes how the integrators are interconnected through feedback and feedforward paths,  $\mathbf{b}$  is an  $n \times 1$  vector that describes how the input signal is applied to the integrators,  $\mathbf{c}$  is an  $n \times 1$  vector that contains the set of coefficients that multiply the output states and are summed together and d is a scalar that represents the feedthrough component from the input directly to the output. u(t) and y(t) are the input and the output signal, respectively. To illustrate the design procedure, biquad, observable canonical and orthonormal based  $\mathrm{HP}\Sigma\Delta$  ADC topologies are designed that satisfy the NTF and STF requirements, as described in the following paragraphs.

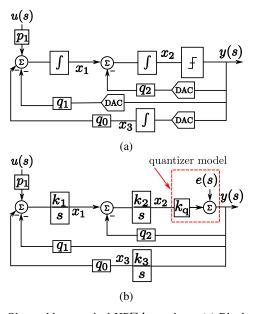

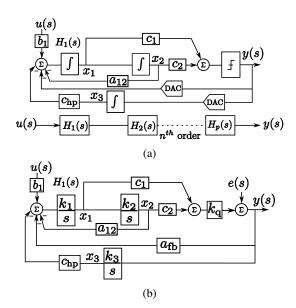

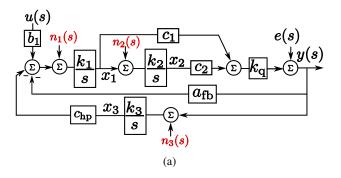

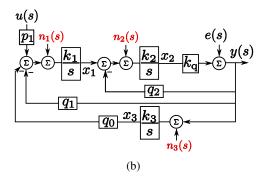

The observable canonical state-space form is investigated first. The observable canonical state-space form is used to develop the observable canonical  $\Sigma\Delta$  topology. The output of the system is fed back to the input of each of the integrators through coefficients that determine the poles of the system. The block diagram and the linear model of the observable canonical HPSD ADC topology are shown in Fig. 4.  $k_1$ ,  $k_2$  and  $k_3$  are the integrator scaling coefficients of the first, second and the high-pass integrator, repectively. The linear model of the quantizer is modeled as a gain  $k_q$ , a quantization error e(s) and a summing node. The value of  $k_q$  is given by  $2/a_N$  where  $a_N$  is the coefficient of the last integrator, for a single-bit,  $N^{\text{th}}$ -order modulator as described in [15]. In the proposed design,  $a_N$  is given by the scaling coefficient of the second integrator.

The STF and NTF of the observable canonical  $\mbox{HP}\Sigma\Delta$  topology can be expressed as

3

Figure 4: Observable canonical HP $\Sigma\Delta$  topology: (a) Block diagram; (b) Linear model [14]

$$STF = \frac{sp_1k_1k_2k_q}{s^3 + k_qk_2q_2s^2 + k_qk_1k_2q_1s + k_qk_1k_2k_3q_0}$$

$$NTF = \frac{s^3}{s^3 + k_qk_2q_2s^2 + k_qk_1k_2q_1s + k_qk_1k_2k_3q_0}$$

(2)

From (2), it can be seen that the STF and NTF requirements of the observable  $\Sigma\Delta$  topology are met. For the STF, there is at least one zero at DC (single-pole roll-off) and the three zeros at DC for the NTF. On solving the characteristic equation (CE) of (2), given by

$$s^{3} + k_{0}k_{2}q_{2}s^{2} + k_{0}k_{1}k_{2}q_{1}s + k_{0}k_{1}k_{2}k_{3}q_{0} = 0,$$

(3)

the location of the high-pass pole close to DC can be determined. The location of the pole predominantly depends on the value of  $q_0$ ,  $q_1$  and  $k_3$ .

Figures 5a and 5b show the biquad HP $\Sigma\Delta$  ADC and its linear model, respectively. The STF and the quantization NTF of the biquad HP $\Sigma\Delta$  ADC can be written as

$$STF = \frac{sb_1k_1k_q(c_1s + k_2c_2)}{s^3 + a_{12}k_1k_2s + k_qk_1(c_1a_{fb}s^2 + k_2c_2a_{fb}s + k_2k_3c_2c_{hp})}$$

$$NTF = \frac{s(s^2 + a_{12}k_1k_2)}{s^3 + a_{12}k_1k_2s + k_qk_1(c_1a_{fb}s^2 + k_2c_2a_{fb}s + k_2k_3c_2c_{hp})}$$

$$(4)$$

As can be seen from 4, the STF and the NTF satisfy the requirements.

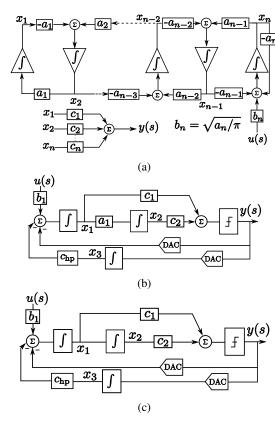

Orthonormal ladder filters [17], a state-space structure that is scaled for optimum dynamic range and less sensitive to component variations, can be used for realizing higher order arbitrary stable transfer functions [18]. Figures 6a, 6b and 6c show the state-space form, the  $HP\Sigma\Delta$  topology and the corresponding linear model of the orthonormal  $HP\Sigma\Delta$  ADC. The STF and the NTF equations of the orthonormal  $\Sigma\Delta$  topology can be written as

Table I: State-space based  $HP\Sigma\Delta$  topologies: A qualitative comparison

| SS topology  | Biquad HP $\Sigma\Delta$                                                                                      | Observable canonical $\mathbf{HP}\Sigma\Delta$                                                                                   | Orthonormal $\mathbf{HP}\Sigma\Delta$                                                                                                   |

|--------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Disadvantage | Biquads in cascade can be used to realize higher order structures but may require modification for stability. | The output is fed back to the input of each of the integrators which imposes tough swing requirements on the integrator.         | Existing orthonormal state-space form has to be modified in order to satisfy the STF requirement.                                       |

| Advantage    | Each biquad can be tuned independently while imposing relaxed swing requirements on the integrators.          | Only real NTF zeros can be produced while the rest of the topologies offer the freedom to choose between real and complex zeros. | Unique set of coefficients can be derived for any given stable transfer function. The calculation of the coefficients can be automated. |

Figure 5: Biquad  $\mbox{HP}\Sigma\Delta$  topology: (a) Block diagram; (b) Linear model

Table II: Coefficients of the  $HP\Sigma\Delta$  topologies

| Coeff.                      | Orthonormal $HP\Sigma\Delta$ | Coeff.         | Observable canonical $\mathbf{HP}\Sigma\Delta$ |

|-----------------------------|------------------------------|----------------|------------------------------------------------|

| $b_1$                       | 0.5                          | $p_1$          | 0.5                                            |

| $k_{1}, k_{2}$              | 0.5                          | $k_{1}, k_{2}$ | 0.5                                            |

| $a_{fb}, c_{hp}$ $c_1, c_2$ | 1                            | $q_1$          | 0.5                                            |

|                             | 0.5                          | $q_2, q_0$     | 1                                              |

| $k_3$                       | 0.0005                       | $k_3$          | 0.0005                                         |

$$STF = \frac{sb_1k_1k_q(c_1s + k_2c_2)}{s^3 + k_qk_1(c_1a_{fb}s^2 + k_2c_2a_{fb}s + k_2k_3c_2c_{hp})}$$

$$NTF = \frac{s^3}{s^3 + k_qk_1(c_1a_{fb}s^2 + k_2c_2a_{fb}s + k_2k_3c_2c_{hp})}$$

(5)

From (5), it can be seen that the STF has one zero at the origin. Also, the NTF has three zeros at the origin. The poles can be determined by solving the characterististic equation given by

$$s^{3} + k_{q}k_{1}(c_{1}a_{fb}s^{2} + k_{2}c_{2}a_{fb}s + k_{2}k_{3}c_{2}c_{hp}) = 0$$

(6

For frequencies very close to DC, the characteristic equation can be approximated as

$$s \approx -\frac{c_{\rm hp}k_3}{a_{\rm fb}} \Rightarrow f_{\rm hpf} = \frac{1}{2\pi} \frac{c_{\rm hp}k_3}{a_{\rm fb}} f_{\rm s}$$

(7)

and the high-pass pole location can be set. Note that the quantizer gain  $k_{\rm q}$  does not impact the location of the pole. This implies that the signal-dependent gain associated with  $k_{\rm q}$  and thus the momentary value of the input signal of the ADC

Figure 6: Orthonormal HP $\Sigma\Delta$  topology: (a) n<sup>th</sup>-order state-space form; (b) Block diagram; (c) Linear model [14]

does not change the exact value of the location of the pole, unlike in the case of pseudo-resistors. The reader is referred to the Appendix for the derivation and the approximations made.

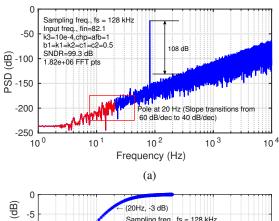

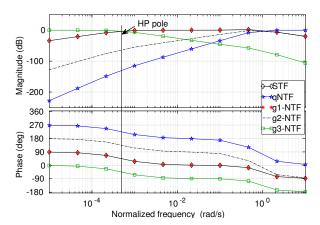

Figures 7a and 7b show the plots of NTF and STF, respectively. Sampling frequency  $f_{\rm s} = 128$  kHz, scaling coefficient  $k_3 = 2.0.0005$  and  $a_{\rm fb} = 1$  result in an high-pass cut-off frequency  $f_{\rm hpf}$  of 20 Hz, selected to observe the slope change clearly. A desired  $f_{\rm hpf}$  can be selected by appropriately setting  $k_3$ .

Table I summarizes the advantages and disadvantages posed by the various  $HP\Sigma\Delta$  topologies. While biquads can be tuned independently, they may be unstable at higher orders and require modifications to stabilize the system. For this reason, we will discuss only the orthonormal and observable canonical  $HP\Sigma\Delta$  topologies in the sequel.

## III. INTERMEDIATE FUNCTIONS

In this section, the sets of intermediate transfer functions (IF) [17] are derived to compare the thermal noise contributions of the integrators of the HP $\Sigma\Delta$  topologies. Flicker noise

Figure 7: System level plots of the orthonormal HP $\Sigma\Delta$  topology: (a) NTF, (b) STF [14]

is not considered here since circuit techniques to reduce its effect can be found in the literature and the reader is referred to [19] and [20] for more details. Although both thermal and flicker noise contribute to the total noise of the system, they are minimized through independent circuit techniques. The first set of intermediate functions from the input of the integrators to the output of the system,  $\mathbf{g}(s)$ , and the second set, from the input of the system to the output of the integrators,  $\mathbf{f}(s)$ , as shown in Fig. 8, can be expressed as

$$f_i(s) \triangleq \frac{x_i(s)}{u(s)}; \qquad g_i(s) \triangleq \frac{y(s)}{n_i(s)};$$

(8)

where u(s) and y(s) denote the input and the output of the system, and  $n_i(s)$  and  $x_i(s)$  represent the input thermal noise source and output of the i<sup>th</sup> integrator, respectively.

The IF  $\mathbf{f}(s)$  of the orthonormal HP $\Sigma\Delta$  modulator consists of a set of functions  $\{f_1(s), f_2(s), f_3(s)\}$  given by:

$$f_1(s) = \frac{b_1 k_1 s^2}{s^3 + k_0 k_1 (c_1 a_{\text{fb}} s^2 + k_2 c_2 a_{\text{fb}} s + k_2 k_3 c_2 c_{\text{hp}})}$$

(9)

$$f_2(s) = \frac{b_1 k_1 k_2 s}{s^3 + k_0 k_1 (c_1 a_{\text{fb}} s^2 + k_2 c_2 a_{\text{fb}} s + k_2 k_3 c_2 c_{\text{hp}})}$$

(10)

$$f_3(s) = \frac{b_1 k_1 k_3 k_q (sc_1 + k_2 c_2)}{s^3 + k_q k_1 (c_1 a_{\text{fb}} s^2 + k_2 c_2 a_{\text{fb}} s + k_2 k_3 c_2 c_{\text{hp}})}$$

(11)

The IF  $\mathbf{g}(s)$  of the orthonormal HP $\Sigma\Delta$  modulator consists of a set of functions  $\{g_1(s),g_2(s),g_3(s)\}$  given by:

$$g_1(s) = \frac{k_1 k_0 s(c_1 s + k_2 c_2)}{s^3 + k_0 k_1 (c_1 a_{\text{fb}} s^2 + k_2 c_2 a_{\text{fb}} s + k_2 k_3 c_2 c_{\text{hp}})}$$

(12)

$$g_2(s) = \frac{k_2 k_0 c_2 s^2}{s^3 + k_0 k_1 (c_1 a_{\text{fb}} s^2 + k_2 c_2 a_{\text{fb}} s + k_2 k_3 c_2 c_{\text{hp}})}$$

(13)

$$g_3(s) = \frac{k_1 k_3 k_0 c_{hp} (sc_1 + k_2 c_2)}{s^3 + k_0 k_1 (c_1 a_{fb} s^2 + k_2 c_2 a_{fb} s + k_2 k_3 c_2 c_{hp})}$$

(14)

The IF  $\mathbf{f}(s)$  of the observable canonical HP $\Sigma\Delta$  modulator consists of a set of functions  $\{f_1(s), f_2(s), f_3(s)\}$  given by:

$$f_1(s) = \frac{sp_1k_1(s + k_2q_2k_q)}{s^3 + k_qk_2q_2s^2 + k_qk_1k_2q_1s + k_qk_1k_2k_3q_0}$$

(15)

$$f_2(s) = \frac{sp_1k_1k_2}{s^3 + k_0k_2q_2s^2 + k_0k_1k_2q_1s + k_0k_1k_2k_3q_0}$$

(16)

$$f_3(s) = \frac{p_1 k_1 k_2 k_3 k_q}{s^3 + k_q k_2 q_2 s^2 + k_q k_1 k_2 q_1 s + k_q k_1 k_2 k_3 q_0}$$

(17)

The IFs  $\mathbf{g}(s)$  of the observable canonical  $HP\Sigma\Delta$  modulator consists of a set of functions  $\{g_1(s),g_2(s),g_3(s)\}$  given by:

$$g_1(s) = \frac{k_1 k_2 k_q s}{s^3 + k_q k_2 q_2 s^2 + k_q k_1 k_2 q_1 s + k_q k_1 k_2 k_3 q_0}$$

(18)

$$g_2(s) = \frac{k_2 k_q s^2}{s^3 + k_q k_2 q_2 s^2 + k_q k_1 k_2 q_1 s + k_q k_1 k_2 k_3 q_0}$$

(19)

$$g_3(s) = \frac{k_1 k_2 k_3 k_q q_0}{s^3 + k_q k_2 q_2 s^2 + k_q k_1 k_2 q_1 s + k_q k_1 k_2 k_3 q_0}$$

(20)

From Fig. 9, we can observe that the noise from the first, second and third integrator is first-order high-pass, second-order high-pass and low-pass filtered, respectively. It can be observed that the input signal is high-pass filtered with a slope of 20 dB/dec, while the quantization noise initially begins with a slope of 60 dB/dec but transitions to 40 dB/dec on encountering the pole associated with the high-pass cut-off frequency. The coefficients of both topologies are given in Table II.

To quantitatively evaluate the performance of the  $HP\Sigma\Delta$  topologies, a mathematical norm is necessary to measure the magnitudes of the signal level. The two signal types that are often used in such a performance analysis are:

- Sinusoidal input: for a sinusoidal input with a peak amplitude  $A_p$ , an appropriate mathematical norm of the signal is the  $L_{\infty}$  norm.

- Power spectrum: if the input signal is assumed to be white, the output power spectrum at the output of the integrators is calculated and the root-mean-square value is given by the  $L_2$  norm of the signal.

In our case, even though this is not exactly the case, as can be seen from Fig. 2, we assume a white input signal  $L_2$ -norm value of which is the root mean square of the power spectrum given by

$$||v||_2 = \left(\int_0^\infty v(t)^2 dt\right)^{\frac{1}{2}}$$

(21)

The dynamic range, given by the ratio of the maximum signal handling capability and the minimum level as determined by the internally generated noise can be optimized through scaling of the integrators. Integrator scaling is the process of readjusting the internal gain coefficients in order to adjust the internal signal swing to a range appropriate for the supply voltage such that the overall transfer function from the input to the output remains unchanged [21]. The  $L_2$ -norms of the set

Figure 8: Integrator input referred thermal noise sources: (a) Orthonormal HP $\Sigma\Delta$ ; (b) Observable canonical HP $\Sigma\Delta$  topology [14]

Figure 9: Frequency response of the IF-g(s) thermal noise transfer functions of the orthonormal HP $\Sigma\Delta$  topology [14]

Table III:  $L_2$ -norm calculations of the HP $\Sigma\Delta$  topologies

|                                                                   | Orthon                                                              | ormal H                                                                 | $\mathbf{P}\Sigma\Delta$                                     |                                    |                                                              |

|-------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------|--------------------------------------------------------------|

| Int.                                                              | $\begin{array}{ c c }\hline \textbf{Before}\\ \ f_i\ _2\end{array}$ | $\begin{array}{c} \mathbf{scaling} \\ \left\ g_i\right\ _2 \end{array}$ | $\begin{array}{c c} \textbf{Factor} \\ \alpha_i \end{array}$ | $\frac{\mathbf{After}}{\ f_i\ _2}$ | $\begin{array}{c} \mathbf{scaling} \\ \ g_i\ _2 \end{array}$ |

| First integrator<br>Second integrator<br>High-pass integrator     | 0.354<br>0.25<br>0.0158                                             | 0.866<br>0.7073<br>0.0158                                               | 2.8277<br>4.001<br>63.23                                     | 1<br>1<br>1                        | 0.3063<br>0.1768<br>0.00025                                  |

| $\sum_{i=1}^{3} \left\  g_i \left( j \omega \right) \right\ _2^2$ | 1.2                                                                 | 506                                                                     |                                                              | 0.1                                | .2506                                                        |

| Ob                                                                | servable                                                            | canonic                                                                 | al $\mathbf{HP}\Sigma\Delta$                                 |                                    |                                                              |

| First integrator<br>Second integrator<br>High-pass integrator     | 0.7501<br>0.177<br>0.0158                                           | 0.707 $1.00$ $0.0158$                                                   | 1.33<br>5.66<br>63.238                                       | 1<br>1<br>1                        | 0.5304<br>0.1768<br>0.00025                                  |

| $\sum_{i=1}^{3} \left\  g_i \left( j \omega \right) \right\ _2^2$ | 1.5                                                                 | 006                                                                     |                                                              | 0.3                                | 31266                                                        |

of IF's  $\mathbf{f}(s)$  and  $\mathbf{g}(s)$  are calculated and are tabulated in Table III. A scaling factor,  $\alpha_i$ , is calculated for each integrator, given by

$$\alpha_i = \frac{M}{\|f_i\|_2},\tag{22}$$

where M is the maximum acceptable signal magnitude at the integrator outputs. After  $\mathbf{f}(\mathbf{s})$  has been scaled,  $\mathbf{g}(\mathbf{s})$  is scaled by the inverse factor  $(\frac{1}{\alpha_i})$  as given in Table III. The total noise power of the integrators, given by  $\sum_i \|g(j\omega)\|_2^2$ , can be evaluated and used as a figure of merit [5] for comparing the noise performance of the  $\mathrm{HP}\Sigma\Delta$  topologies. The total

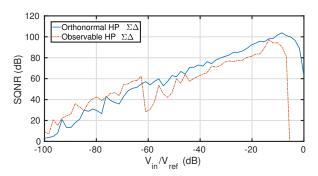

noise power for a 3^{rd} order system, given by  $\sum_{i=1}^{3} \|g_i(j\omega)\|_2^2$ for the orthonormal HP $\Sigma\Delta$  is 0.12, which is smaller than that of the observable HP $\Sigma\Delta$ , which is 0.31, which is a significant 3.9 dB difference. Therefore, the orthonormal  $HP\Sigma\Delta$  is a preferred choice for circuit implementation. The noise performance of the HP $\Sigma\Delta$  topologies can be further improved by balancing the integrator noise contributions, i.e., making  $g_i$  of the integrators equal. This can be carried out by appropriate capacitance sizing of the integrators, while keeping in mind the practical tradeoffs between noise and current consumption. The noise contributions of individual integrators can be seen in Table III. It can be observed that the total noise contribution of the observable canonical HP $\Sigma\Delta$  ADC is about 1.25 times that of the orthonormal HP $\Sigma\Delta$  ADC before scaling, while it is three times that after scaling. Therefore, the orthonormal HP $\Sigma\Delta$  ADC is a better topology with respect to noise performance.

Following the intermediate function analysis from a linearized model, the topologies are now compared using a nonlinear model of the HP $\Sigma\Delta$  topologies, which models the quantizer as a sign function on MATLAB. Fig. 10 shows the dynamic range comparison between the observable canonical and orthonormal HP $\Sigma\Delta$  topologies. It can be observed that the orthonormal HP $\Sigma\Delta$  topology has a larger dynamic range and can handle larger input signal amplitudes.

Figure 10: Simulated dynamic range performance of the  $\mbox{HP}\Sigma\Delta$  topologies

From system simulations, it follows that the difference between the noise performance of these types of modulators becomes more pronounced for higher orders, in favor of the orthonormal  $HP\Sigma\Delta$  modulator topology.

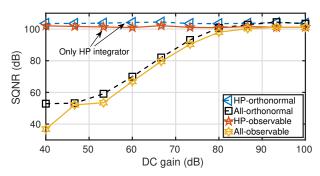

Figure 11: Effect of finite DC gain on the performance of the  ${\rm HP}\Sigma\Delta$  topologies

### IV. SENSITIVITY

In this section, the sensitivity of the noise transfer function to integrator non-idealities and coefficient variations is discussed. In order to determine the impact of integrator errors on the noise transfer function of the  $HP\Sigma\Delta$  topologies, the integrator errors are modeled and simulated at the system level. The effects of finite DC gain, finite GBW and time constant variation of the integrators on the performance of the system are investigated. Assuming an RC implementation, the ideal integrator transfer function (ITF) can be expressed as

$$ITF_{RC,i} = \frac{k_i f_s}{s} = \frac{1}{sRC} = \frac{\omega_u}{s}$$

(23)

Taking the finite DC gain effect of the integrator into account, the non-ideal integrator transfer function can be expressed as

$$ITF_{A_0} \approx \frac{k_i f_s}{s + \frac{k_i f_s}{A_0}},\tag{24}$$

where  $A_0$  is the finite DC gain of the integrator. Comparing (24) to the ideal ITF expressed in (23), it is observed that the pole is displaced to  $\frac{k_i f_s}{A_0}$ .

Fig. 11 shows the impact of finite DC gain of the high-pass integrators and compares the performance between orthonormal and observable canonical HP $\Sigma\Delta$  ADC topologies. It can be observed that, on lowering the DC gain of the high-pass integrator alone, the performance of the topologies does not degrade. The overall performance of the topologies mainly depend on the first or the second integrator.

The non-ideal ITF due to finite GBW can be expressed as [15]

$$ITF_{GBW}(s) = \frac{\frac{k_i f_s}{s} \frac{GBW}{GBW + k_i f_s}}{1 + \frac{s}{GBW + k_i f_s}},$$

(25)

where GBW is the gain-bandwidth product of the integrator.

From Fig. 12, one can observe how the performance of the  $HP\Sigma\Delta$  topologies depend on the GBW of the integrators. As the GBW product of the high-pass integrator decreases, the performance of the modulator degrades only marginally. At the lower end, the GBW values of the  $1^{\rm st}$  and  $2^{\rm nd}$  integrator are important to maintain the performance of the  $HP\Sigma\Delta$  topologies. To minimize the effect of finite GBW, a GBW value of  $0.7 \cdot f_s$  or higher would suffice.

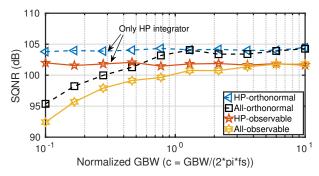

Figure 12: Effect of finite GBW on the performance of the  $\mbox{HP}\Sigma\Delta$  topologies

Figure 13: Effect of time constant variation on the performance of the  $HP\Sigma\Delta$  topologies

RC mismatch can be expressed as

$$ITF_{RC,\Delta_{RC}} = \frac{1}{sRC} \cdot \frac{1}{(1 + \Delta_{RC})} = \frac{k_i f_s}{s} \cdot \frac{1}{(1 + \Delta_{RC})}$$

(26)

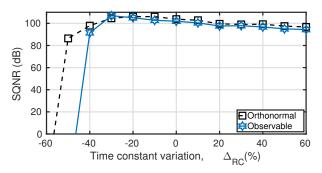

When the time constant increases, i.e. the gain of the integrator decreases, the performance of the  $HP\Sigma\Delta$  topologies degrades. The trend is similar to the effect of finite GBW on the performance. When the time constant decreases, i.e. the gain of the integrator increases, the modulator can become unstable beyond a threshold, as can be seen in Fig. 13. The overall performance of the high-pass modulator mainly depends on the first or the second integrator and not on the feedback integrator.

In case of filters, the sensitivity of the transfer function to the integrator non-idealities is dependent on the integrator time constant [17]. A higher integrator gain would result in larger sensitivity to the integrator non-idealities. Given that the gain of the integrator is proportional to the row sum given by [17]

$$|A_{ij}| + |b_i|, \tag{27}$$

where  $A_{ij}$  and  $b_i$  are elements of the  $\bf A$  and  $\bf b$  matrices respectively, the first and second integrator are expected to be more sensitive to the integrator non-idealities than the high-pass integrator, which confirms the observations made in Figures 11, 12 and 13. The row sum of the high-pass integrator is very low, and therefore, the sensitivity to finite DC gain, finite GBW and time-constant variation is marginal. But the row sums of the first and second integrator are quite large as compared to that of the high-pass integrator and hence they

Figure 14: Top level circuit block diagram of the CT orthonormal  ${\rm HP}\Sigma\Delta$  modulator [14]

suffer from larger sensitivities to integrator non-idealities. In general, the larger the row sum of the integrator, the larger the sensitivity to its non-idealities.

### V. CIRCUIT IMPLEMENTATION AND SIMULATION RESULTS

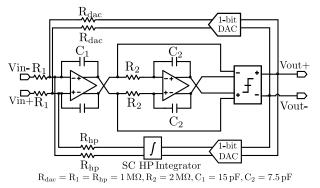

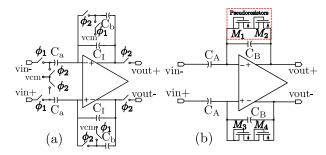

Illustrated in Fig. 14 is the top level schematic of the proposed orthonormal HP $\Sigma\Delta$  topology targeting the implementation of the high-pass cut-off frequency with good accuracy and linearity. Opamp-RC integrators are used to realize the first and second integrators to achieve good linearity. The amplifiers are designed using a two-stage opamp topology for the high current driving capability that is required to drive the large capacitances, minimizing the performance degradation due to slewing. A multiple-input dynamic comparator is used to realize the summer and the quantizer. A very large time-constant, parasitic-insensitive and area-efficient switchedcapacitor Nagaraj integrator [22] as shown in Fig. 15 is used to implement the high-pass integrator in the feedback loop. The location of the high-pass pole is determined by ratios of capacitors and by the clock frequency and, as such, offers a high accuracy and is robust to PVT variations.  $c_{hp}$  and  $a_{fb}$  are implemented as a ratio of resistors while  $k_3$  is implemented as a ratio of capacitors, both of which can be very accurate. The circuit consists of three different capacitors and operates in two non-overlapping phases. The input voltage is attenuated and integrated by capacitor  $C_{\rm I}$ . A charge equivalent to  $C_{\rm a}V_{\rm in}$ is transferred to the large capacitor  $C_{\rm I}$  during the first phase. In the second phase, the charge is redistributed between  $C_{\rm I}$ and  $C_b$ . Large capacitance  $C_I$  is used for both attenuation and integration, thus saving area. The gain and the unity gain frequency,  $f_u$  of the integrator are given by the factor  $(\frac{C_a}{C_l})(\frac{C_b}{C_l})$

$$f_{\rm u} = \frac{1}{2\pi} \frac{1}{\left[1 + \frac{C_{\rm b}}{C_{\rm I}}\right]} \frac{C_{\rm a}}{C_{\rm I}} \frac{C_{\rm b}}{C_{\rm I}} f_{\rm S},\tag{28}$$

respectively, where  $f_s$  is the clock frequency and is equal to the sampling frequency of the  $\Sigma\Delta$  modulator.

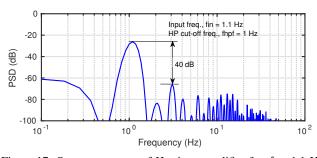

To avoid long simulation times,  $f_{\rm hpf}$  is set at 1 Hz and the circuit is tested for linearity at the same frequency. Lower  $f_{\rm hpf}$  can be realized by appropriately selecting the values of capacitances and the clock frequency, at the cost of larger area and power. To obtain a cut-off frequency of 1 Hz,  $C_{\rm a}=0.5$

Table IV: Performance of the CMOS orthonormal  $HP\Sigma\Delta$  modulator

| Technology                           | $0.18~\mu\mathrm{m}~\mathrm{AMS}$ |

|--------------------------------------|-----------------------------------|

| Supply voltage                       | 1.8 V                             |

| Sampling frequency                   | 128 kHz                           |

| Signal Bandwidth                     | 1 - 200 Hz                        |

| $HD_3@f_{in}=1.1 Hz, V_{in}=100 mVp$ | -78 dB                            |

| $\mathrm{SNDR}^1$                    | 68.1 dB                           |

| ENOB                                 | 11.02 bits                        |

| Total capacitance                    | 148.4 pF                          |

| Total power consumption              | $146 \mu \mathrm{W}$              |

<sup>&</sup>lt;sup>1</sup> transient thermal noise from noise  $f_{\min} = 1$  to  $f_{\max} = 200$  Hz; flicker noise disabled

Figure 15: Implementation of the high-pass cut-off frequency a) SC Nagaraj integrator [22] b) Harrison amplifier [6]

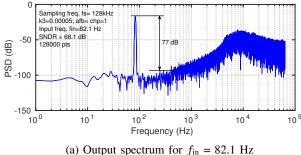

pF,  $C_{\rm I}$  = 45 pF and  $C_{\rm b}$  = 0.2 pF are chosen to realize the scaling coefficient of  $5 \cdot 10^{-5}$  that follows from (7) and (28). In the designed modulator, the high-pass cut-off frequency is implemented using ratios of capacitors, which is more accurate and robust to PVT variations as compared to pseudo-resistors or  $g_m$  based techniques. The first, the high-pass and the second integrator consume 76.6, 65.4 and 3.7  $\mu$ W respectively, while the digital blocks consume 0.4  $\mu$ W. To get an estimate of the noise contributions of the passive components, the thermal noise of the opamps and the quantization noise, a transient noise simulation is run with noise  $f_{\min}$  and  $f_{\max}$  being 1 Hz and 200 Hz respectively, after disabling the effect of flicker noise, and is shown in Figure 16a. Assuming that the flicker noise of the opamps can be optimized with available state-ofthe-art circuit techniques, the signal energy at the high-pass cut-off frequency region can be acquired with high fidelity. The 3<sup>rd</sup> harmonic distortion is at -78 dB for an input signal of 100 mV (peak value) at an input frequency of 1.1 Hz as shown in Figure 16b, which is better than the state-of-the-art performance. Designed and simulated in AMS 0.18  $\mu$ m CMOS IC technology and taking resistor noise, switched capacitor noise, opamp thermal noise, quantization noise and harmonic distortion into account, the orthonormal HP $\Sigma\Delta$  ADC achieves an effective number of bits (ENOB) of 11.02 bits. Table IV summarizes the performance of the designed modulator.

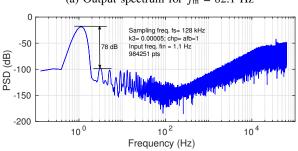

The proposed implementation of the high-pass cut-off frequency is compared with that of a "Harrison amplifier", i.e., the combination of an amplifier and a high-pass filter, as shown in Fig. 15 [6]. Figures 16 and 17 show the performance of the orthonormal HP $\Sigma\Delta$  modulator and the Harrison amplifier, respectively. The proposed design is benchmarked against a Harrison amplifier that consists of pseudoresistors designed using PMOS transistors [6] and an ideal amplifier. The high-pass filter is implemented using the pseudoresistors in parallel

(b) Output spectrum for  $f_{in} = 1.1 \text{ Hz} [14]$

Figure 16: Orthonormal  $HP\Sigma\Delta$  circuit simulations

Figure 17: Output spectrum of Harrison amplifier for  $f_{in}$ = 1.1 Hz

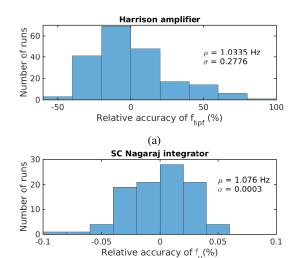

with the feedback capacitors  $C_{\rm B}$ . The linearity at the highpass cut-off frequency of the Harrison amplifier is tested and is shown in Fig. 17. The amplifier achieves an HD<sub>3</sub> of about -40 dB for an input amplitude of 10 mV at an input frequency of 1.1 Hz. The relative accuracy of unity gain frequency of the SC integrator is better than 0.1%. Together with the inaccuracies resulting from the ratio of resistances, the accuracy of the proposed method can be better than 1%. Monte Carlo simulations, accounting for process and mismatch variations, comparing the accuracies of the high-pass cut-off frequency set by the SC Nagaraj integrator and the Harrison amplifier, are shown in Figure 18.

### A. Testing with pre-recorded ECG signal

The orthonormal HP $\Sigma\Delta$  modulator is tested with a prerecorded ECG signal from the MIT-BIH Normal Sinus Rythym database (nsrdb) numbered as Record 16773 (Signal: ECG1). The designed system is run with 3 seconds of the ECG input signal to observe the effect of baseline wandering and the output is post-processed in MATLAB. The acquired digital signal output is low-pass filtered using a third-order Butter-worth filter and is reconstructed in the analog time

Figure 18: Histogram of the relative accuracies of the high-pass cutoff frequency: (a) Harrison amplifier, (b) SC Nagaraj integrator

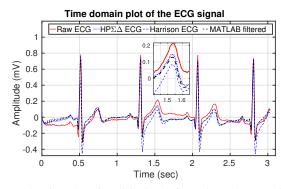

Figure 19: Time-domain ECG signal from the orthonormal HP $\Sigma\Delta$  modulator output compared with raw ECG (MIT-BIH), Harrison amplifier and MATLAB filtered output

domain. Fig. 19 shows the pre-recorded time-domain ECG input signal, the reconstructed signal from the output of the orthonormal HP $\Sigma\Delta$  modulator and the signal from the output of the Harrison amplifier, which are benchmarked against a MATLAB high-pass filtered signal of the raw ECG with BW. The distortion components present in the ECG signal acquired using pseudoresistors (with an ideal amplifier having no swing limitations) can be clearly seen in the time-domain. Distortion around the high-pass cut-off frequency of ECG signal can make accurate medical diagnosis a challenge. However, the waveform acquired by the orthonormal HP $\Sigma\Delta$  modulator has much better linearity and is closer to the MATLAB filtered waveform. Given that the signal is normal sinus rhythm and assuming that the strength of the beat is fairly uniform, the R-R interval is about 0.8 sec and the amplitude of the P-wave peak of the input ECG signal ranges from -0.054 to 0.058 mV, whereas, the reconstructed ECG peaks vary from 0 to 0.048 mV, which is a much smaller range. The occurrence of the P-wave peak for the input ECG with baseline wander and the reconstructed ECG are tabulated in Table VI. It can be observed that the effect of baseline wandering is greatly reduced in the reconstructed signal.

This work [Muller] [Rezaee] [Mohan] [Harrison] Year 2017 ISCAS 2013 [9] JSSC 2003 [6] JSSC 2012 [10] JETCAS 2011 [7]  $2^{\mathrm{nd}} \text{ HP}\Sigma\Delta$  $1^{\rm st}\ {\rm HP}\Sigma\Delta$ boxcar ADC Architecture amplifier amplifier Domain mixed-signal mixed-signal analog digital analog Bio-signal ECG ECG neural neural neural HPF technique SC Nagaraj integrator  $g_{\rm m}$ , current sources pseudoresistors IIR-filter (off-chip) pseudoresistors Bandwidth [Hz] 1-200 1-200 0.025 - 7.2k300 - 10k0.5 - 10k $-78 @ f_{in} = 1.1 \text{ Hz}$  $-62 @ f_{in} = 2.1 \text{ Hz}$ >-40 @ $f_{in} = 1.1 \text{ Hz}$ >-40 @ $f_{in} = 1.1 \text{ Hz}$  $HD_3$  [dB] Accuracy of  $f_{hpf}$ high process sensitive process sensitive very high process sensitive Technology  $0.18~\mu\mathrm{m}$  $1.5 \ \mu m$  $0.18~\mu\mathrm{m}$  $0.18 \ \mu m$ 65 nm

Table V: Comparison of the implementation of high-pass cut-off frequency  $(f_{hpf})$  with related work

Table VI: Reduction of baseline wandering

| ECG P-wave          | $1^{st}$ (s, mV) | 2 <sup>nd</sup> (s, mV)        | 3 <sup>rd</sup> (s, mV) | 4 <sup>th</sup> (s, mV) |

|---------------------|------------------|--------------------------------|-------------------------|-------------------------|

| Raw ECG<br>Rec. ECG |                  | (1.17, 0.024)<br>(1.17, 0.048) |                         |                         |

### B. Comparison with related work

Comparing the performance of the orthonormal HP $\Sigma\Delta$ modulator to the Harrison amplifier, it can be seen that the orthonormal  $HP\Sigma\Delta$  topology offers a much better alternative for the implementation of the high-pass cut-off frequency, in terms of linearity and accuracy. Pseudoresistors are used in [6] and [7] for lower area and power consumption at the expense of poor linearity and accuracy of the high-pass cut-off frequency. Due to process (P), voltage (V), and temperature (T) variations and poor circuit structures, pseudoresistors achieve a linearity of about -40 dB and compromise on the accuracy of the implementation of the high-pass cut-off frequency. Although the use of a  $g_{\rm m}$  stage in combination with current sources [9] leads to a power efficient solution, the  $g_{\rm m}$  of any transistor is inherently non-linear and is less robust to P, V and T variations. Off-chip digital solutions [10] can be used to obtain a highly accurate and linear high-pass cut-off frequency at the expense of power. Table V summarizes the metrics that characterizes the implementation of a high-pass cut-off frequency involving large time constants. For integrated on-chip solutions, the proposed system is among the most promising approaches for applications where good linearity and accuracy of the high-pass cut-off frequency is desired.

### VI. CONCLUSION

In this paper, a state-space based design methodology is proposed to develop HP $\Sigma\Delta$  ADC topologies. By using the statespace synthesis approach,  $\Sigma\Delta$  converters with arbitrary signal and quantization noise transfer functions can be synthesized. State-space techniques allow dynamic range optimization of the  $\Sigma\Delta$  converters with respect to signal swing and noise through state and noise scaling, respectively. This also minimizes the sensitivity of the topology to component variations [23]. From the intermediate-function analysis, it is seen that the noise from the high-pass integrator are low-pass filtered. Also, from the  $L_2$ -norm calculations, it is observed that the orthonormal HP $\Sigma\Delta$  ADC gives better noise performance than the observable HP $\Sigma\Delta$  ADC. Sensitivity analysis is carried out to investigate the impact of coefficient variations and nonidealities of the integrator. Finally, schematic simulations of a circuit designed in AMS 0.18  $\mu$ m CMOS IC technology verify the findings and match the system level results. The designed orthonormal HP $\Sigma\Delta$  is also tested with a real prerecorded ECG input signal and successfully reduces baseline wandering.

### **APPENDIX**

For the orthonormal HP $\Sigma\Delta$  topology (of Fig. 6c), the equations can be written as:

$$\[u(s)b_1 - a_{\text{fb}}y(s) - c_{\text{hp}}x_3(s)\] \frac{k_1}{s} = x_1(s),\tag{29}$$

$$x_1(s)\frac{k_2}{s} = x_2(s), (30)$$

$$\frac{k_3}{s}y(s) = x_3(s),$$

(31)

and

$$[x_1(s)c_1 + x_2(s)c_2]k_0 + e(s) = y(s),$$

(32)

where u(s) and y(s) are the input and the output of the system, respectively, and  $x_1(s)$ ,  $x_2(s)$  and  $x_3(s)$  are the integrator outputs of the first, second and the high-pass integrator, respectively. After solving the algebraic equations, we obtain the signal transfer function and the quantization noise transfer function given by

$$STF = \frac{k_1 b_1 s(c_1 s + k_2 c_2) k_q}{s^3 + k_q k_1 (s^2 c_1 a_{fb} + s(k_2 c_2 a_{fb} + k_3 c_{hp} c_1) + k_2 k_3 c_2 c_{hp})},$$

(33)

and

$$NTF = \frac{s^3}{s^3 + k_{\rm q}k_1(s^2c_1a_{\rm fb} + s(k_2c_2a_{\rm fb} + k_3c_{\rm hp}c_1) + k_2k_3c_2c_{\rm hp})}$$

(34

respectively. The poles can be determined by solving the characterististic equation given by

$$s^{3} + k_{q}k_{1} \left[ s^{2}c_{1}a_{fb} + s(k_{2}c_{2}a_{fb} + k_{3}c_{hp}c_{1}) + k_{2}k_{3}c_{2}c_{hp} \right] = 0 \quad (35)$$

Solving a cubic equation is non-trivial and to calculate the pole located very close to DC, 35 can be approximated to a  $2^{\text{nd}}$  order equation and can be written as

$$k_{q}k_{1}\left[s^{2}c_{1}a_{fb} + s(k_{2}c_{2}a_{fb} + k_{3}c_{hp}c_{1}) + k_{2}k_{3}c_{2}c_{hp}\right] = 0$$

(36)

or a 1st order equation given by

$$k_{q}k_{1}\left[s(k_{2}c_{2}a_{fb} + k_{3}c_{hp}c_{1}) + k_{2}k_{3}c_{2}c_{hp}\right] = 0$$

(37)

Assuming that  $k_3$  is very small, the associated term can be made zero. 37 can be written as

$$s \approx -\frac{c_{\text{hp}}k_3}{a_{\text{fb}}},\tag{38}$$

which defines the location of the high-pass pole.

### ACKNOWLEDGMENT

The authors would like to acknowledge the support and funding from the Netherlands Organisation for Scientific Research (NWO) and the Dutch Heart Foundation for project number 14728.

### REFERENCES

- J. A. Van Alste and T. Schilder, "Removal of base-line wander and power-line interference from the ecg by an efficient FIR filter with a reduced number of taps," *IEEE Transactions on Biomedical Engineering*, no. 12, pp. 1052–1060, 1985.

- [2] J. M. Leski and N. Henzel, "ECG baseline wander and powerline interference reduction using nonlinear filter bank," *Signal Processing*, vol. 85, no. 4, pp. 781–793, 2005.

- [3] G. B. Moody and R. G. Mark, "The impact of the MIT-BIH arrhythmia database," *IEEE Engineering in Medicine and Biology Magazine*, vol. 20, no. 3, pp. 45–50, May 2001.

- [4] Physiobank. [Online]. Available:https://physionet.org/.

- [5] IEC-60601-2-47 | Medical electrical equipment Part 2-47: Particular requirements for the basic safety and essential performance of ambulatory electrocardiographic systems, 2012.

- [6] R. R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 6, pp. 958–965, 2003.

- [7] H. Rezaee-Dehsorkh, N. Ravanshad, R. Lotfi, K. Mafinezhad, and A. M. Sodagar, "Analysis and design of tunable amplifiers for implantable neural recording applications," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 1, no. 4, pp. 546–556, 2011.

- [8] B. Gosselin, M. Sawan, and C. A. Chapman, "A low-power integrated bioamplifier with active low-frequency suppression," *IEEE Transactions* on *Biomedical Circuits and Systems*, vol. 1, no. 3, pp. 184–192, Sept 2007.

- [9] R. Mohan, S. Hiseni, and W. A. Serdijn, "A highly linear, sigma-delta based, sub-Hz high-pass filtered ExG readout system," in 2013 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2013, pp. 181–184.

- [10] R. Muller, S. Gambini, and J. M. Rabaey, "A 0.013mm<sup>2</sup>, 5μW, DC-coupled neural signal acquisition IC with 0.5V supply," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 1, pp. 232–243, 2012.

- [11] V. P. Rachim and W. Y. Chung, "Wearable Noncontact Armband for Mobile ECG Monitoring System," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 10, no. 6, pp. 1112–1118, Dec 2016.

- [12] H. Chandrakumar and D. Marković, "A 2 µW 40 mVpp linear-input-range chopper-stabilized bio-signal amplifier with boosted input impedance of 300 MΩ and electrode-offset filtering," in 2016 IEEE International Solid-State Circuits Conference (ISSCC), Jan 2016, pp. 96–97.

- [13] X. Zou, X. Xu, L. Yao, and Y. Lian, "A 1-V 450-nW fully integrated programmable biomedical sensor interface chip," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 4, pp. 1067–1077, April 2009.

- [14] S. Rout and W. A. Serdijn, "Structured electronic design of high-pass  $\Sigma\Delta$  converters and their application to cardiac signal acquisition," in 2017 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2017, pp. 2416–2419.

- [15] F. Gerfers and M. Ortmanns, "Continuous-time sigma-delta A/D conversion: Fundamentals, performance limits and robust implementations," 2006.

- [16] T. Denison, K. Consoer, W. Santa, A.-T. Avestruz, J. Cooley, and A. Kelly, "A 2 μw 100 nv/rthz chopper-stabilized instrumentation amplifier for chronic measurement of neural field potentials," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 12, pp. 2934–2945, 2007.

- [17] W. Snelgrove and A. Sedra, "Synthesis and analysis of state-space active filters using intermediate transfer functions," *IEEE transactions* on circuits and systems, vol. 33, no. 3, pp. 287–301, 1986.

- [18] D. A. Johns, W. M. Snelgrove, and A. S. Sedra, "Orthonormal ladder filters," *IEEE Transactions on Circuits and Systems*, vol. 36, no. 3, pp. 337–343, 1989.

- [19] S. Pavan, "Analysis of chopped integrators, and its application to continuous-time delta-sigma modulator design," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, no. 8, pp. 1953–1965, Aug 2017.

- [20] S. Billa, A. Sukumaran, and S. Pavan, "Analysis and design of continuous-time delta sigma converters incorporating chopping," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 9, pp. 2350–2361, Sept 2017.

- [21] K. K. Parhi, "VLSI digital signal processing systems: Design and implementation", New York, NY, USA: Wiley, 2007.

- [22] K. Nagaraj, "A parasitic-insensitive area-efficient approach to realizing very large time constants in switched-capacitor circuits," *IEEE Trans*actions on Circuits and Systems, vol. 36, no. 9, pp. 1210–1216, 1989.

- [23] G. Groenewold, "Optimal dynamic range integrators," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 39, no. 8, pp. 614–627, 1992.

Samprajani Rout was born in Cuttack, India in 1990. She received her M.Sc. degree in electrical engineering in 2016 from Section Bioelectronics, Delft University of Technology, The Netherlands and is currently working towards her PhD degree at the same group.

Her current research interests include algorithms and mixed signal circuit design for biomedical circuits and systems with a special focus on cardiac applications.

Wouter A. Serdijn (M'98, SM'08, F'11) was born in Zoetermeer ('Sweet Lake City'), the Netherlands, in 1966. He received the M.Sc. (cum laude) and Ph.D. degrees from Delft University of Technology, Delft, The Netherlands, in 1989 and 1994, respectively. Currently, he is a full professor in bioelectronics at Delft University of Technology, where he heads the Section Bioelectronics, and a visiting honorary professor at University College London, in the Analog and Biomedical Electronics group.

His research interests include integrated biomedical circuits and systems for biosignal conditioning and detection, neuroprosthetics, transcutaneous wireless communication, power management and energy harvesting as applied in, e.g., hearing instruments, cardiac pacemakers, cochlear implants, neurostimulators, portable, wearable, implantable and injectable medical devices and electroceuticals.

He is co-editor and co-author of the books Analog IC Design Techniques for Nanopower Biomedical Signal Processing (River Publishers 2016), Design of Efficient and Safe Neural Stimulators - a multidisciplinary approach (Springer, 2016), EMI-Resilient Amplifier Circuits (Springer 2013), Ultra Low-Power Biomedical Signal Processing: an analog wavelet filter approach for pacemakers (Springer, 2009), Circuits and Systems for Future Generations of Wireless Communications (Springer, 2009), Power Aware Architecting for data dominated applications (Springer, 2007), Adaptive Low-Power Circuits for Wireless Communications (Springer, 2006), Research Perspectives on Dynamic Translinear and Log-Domain Circuits (Kluwer, 2000), Dynamic Translinear and Log-Domain Circuits (Kluwer, 1998) and Low-Voltage Low-Power Analog Integrated Circuits (Kluwer, 1995). He authored and co-authored 8 book chapters, 3 patents and more than 300 scientific publications and presentations. He teaches Circuit Theory, Analog Integrated Circuit Design, Analog CMOS Filter Design, Active Implantable Biomedical Microsystems and Bioelectronics. He received the Electrical Engineering Best Teacher Award in 2001, in 2004 and in 2015.

He has served, a.o., as General Co-Chair for IEEE ISCAS 2015 and for IEEE BioCAS 2013, Technical Program Chair for IEEE BioCAS 2010 and for IEEE ISCAS 2010, 2012 and 2014, as a member of the Board of Governors (BoG) of the IEEE Circuits and Systems Society (2006—2011), as chair of the Analog Signal Processing Technical Committee of the IEEE Circuits and Systems society, and as Editor-in-Chief for IEEE Transactions on Circuits and Systems—I: Regular Papers (2010—2011). Currently, he is a member of the Steering Committee and an Associate Editor of the IEEE Transactions on Biomedical Circuits and Systems (T-BioCAS)

Wouter A. Serdijn is an IEEE Fellow, an IEEE Distinguished Lecturer and a mentor of the IEEE. In 2016, he received the IEEE Circuits and Systems Meritorious Service Award.