# M.Sc. Thesis

# High-Quality, Real-Time HD Video Stereo Matching on FPGA

Guanyu Yi B.Sc.

#### Abstract

Stereo matching is an important computer vision technique, which extracts the depth information of the scene by matching a pair of stereo images. It has numerous applications, such as view-point interpolation, 3DTV, object detection, etc. In the past decades, many algorithms have been proposed to improve the matching quality or to increase the speed. Due to the high computational complexity, it is still quite challenging to attain high matching-quality at real-time speed.

In this thesis, we propose a hardware design of stereo matching, which is capable of producing high-quality disparity maps at real-time speed. A high-quality stereo matching algorithm is efficiently implemented and hardware-oriented optimized, attaining huge speedup by parallel computing. The whole algorithm is implemented in a single EP3SL150 FPGA. The experimental results show that our design is capable of matching high-definition videos at real-time speed, i.e. 60 frame per second at  $1024 \times 768$  resolution. In terms of matching quality, our design is among the leading real-time methods, evaluated in the Middlebury stereo benchmark. As an application of the stereo matcher, we also build up a depth-scaling system for 3DTV, working together with a view synthesis module. The SoC system synthesizes high-quality virtual views at real-time speed.

# High-Quality, Real-Time HD Video Stereo Matching on FPGA

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

MICROELECTRONICS

by

Guanyu Yi B.Sc. born in Jilin, China

This work was performed in:

Circuits and Systems Group

Department of Microelectronics & Computer Engineering

Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology

# **Delft University of Technology**

Copyright  $\odot$  2011 Circuits and Systems Group All rights reserved.

# Delft University of Technology Department of Microelectronics & Computer Engineering

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "High-Quality, Real-Time HD Video Stereo Matching on FPGA" by Guanyu Yi B.Sc. in partial fulfillment of the requirements for the degree of Master of Science.

| Dated: 2011-August-29 |                               |

|-----------------------|-------------------------------|

| Chairman:             | prof.dr.ir. A.J. van der Veer |

| Advisors:             | dr.ir. Gauthier Lafrui        |

|                       | dr.ir. Rene van Leuker        |

| Committee Members:    | dr.ir. Georgi Kuzmanov        |

|                       |                               |

# Abstract

Stereo matching is an important computer vision technique, which extracts the depth information of the scene by matching a pair of stereo images. It has numerous applications, such as view-point interpolation, 3DTV, object detection, etc. In the past decades, many algorithms have been proposed to improve the matching quality or to increase the speed. Due to the high computational complexity, it is still quite challenging to attain high matching-quality at real-time speed.

In this thesis, we propose a hardware design of stereo matching, which is capable of producing high-quality disparity maps at real-time speed. A high-quality stereo matching algorithm is efficiently implemented and hardware-oriented optimized, attaining huge speedup by parallel computing. The whole algorithm is implemented in a single EP3SL150 FPGA. The experimental results show that our design is capable of matching high-definition videos at real-time speed, i.e. 60 frame per second at  $1024 \times 768$  resolution. In terms of matching quality, our design is among the leading real-time methods, evaluated in the Middlebury stereo benchmark. As an application of the stereo matcher, we also build up a depth-scaling system for 3DTV, working together with a view synthesis module. The SoC system synthesizes high-quality virtual views at real-time speed.

# Acknowledgments

This thesis work is performed at Imec (Leuven, Belgium) with support from the Circuit and System (CAS) group of Delft University of Technology (Delft, the Netherlands). I would like to take this opportunity to thank everyone who has helped me during my MSc thesis year.

First of all, I want to thank Dr. Gauthier Lafruit, Dr. Francesco Pessolano and Prof. Alle-Jan van der Veen for their agreement to provide and offer me the chance to perform my MSc thesis project in Imec. Their rich experience and scientific insights have led the entire search and development into the correct direction - dedicated hardware implementation of high performance dynamic programming stereo matching.

In the period of my MSc thesis year, I thank Ke Zhang for his excellently in developing the stereo matching algorithms with line-based dynamic programming and region growing. Ke also guided me into the stereo vision world and inspires me much on algorithm principles, computing data flow and hardware implementation. I thank Christine Lin in Imec-Taiwan for her advices on ASIC orientated hardware design. I thank Geert Vanmeerbeeck and Eddy De Greef for their collaboration on constructing hardware and software environments. I would like to thank Prof. Rene van Leuken for his invaluable suggestions for design optimization and improvements as well as all the hours he has spent on proofreading my thesis. I thank CK Liao and Josh Tu in Imec-Taiwan for their advices on algorithm improvements and synthesis tools advanced usage. I also would like to thank Gauthier Lafruit, Francesco Pessolano and Peter Lemmens for their outstanding management.

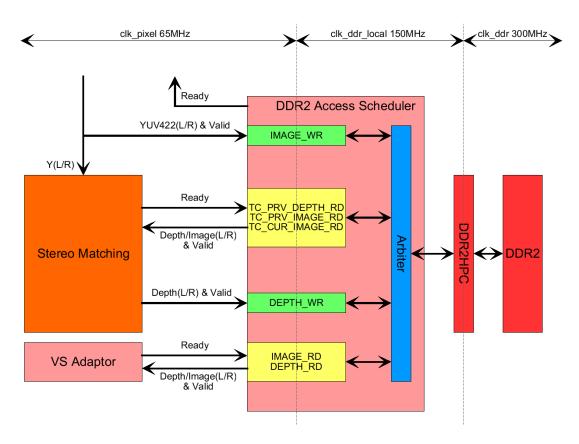

Special thanks are given to Gauthier Lafruit, Prof. Tian-Sheuan Chang and Hsiu-Chi Yeh. Without their support and contributions out 3D depth range adjustment system cannot work properly. Gauthier generates the idea of this system according to the 3D TV trend, and his ambition and enthusiasm is exactly the engine and power of the entire research and development. Gauthier guides, trusts and supports me no matter on the thesis work and life, and I faithfully appreciate his help offered over the whole year. Prof. Chang has proposed the view synthesis kernel and its implementation which is another key kernel in our system, and Hsiu-Chi Yeh has implemented the DDR2 SDRAM access scheduler which plays an important role in accessing DDR2 SDRAM with zero latency for frame-based storage. I am grateful to their collaboration on building our system.

The study and research in Delft and Leuven in the current two years is like a piece of music, which is composed by the melodies in TU Delft and Imec. The notes of international talented people make the melodies graceful, and the rhythms of my around friends make the melodies vivid. My wife and parents is exactly the main theme to make the melodies continue. The music will not be complete without anyone, and I appreciate encountering them in my life.

Finally I thank all my thesis defense committee members including Prof. Alle-Jan van der Veen, Prof. Rene van Leuken, Dr. Gauthier Lafruit and Prof. Georgi Kuzmanov. Guanyu Yi B.Sc. Delft, The Netherlands 2011-August-29

# Contents

| $\mathbf{A}$ | bstra                                   | $\operatorname{\mathbf{ct}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                          |

|--------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| A            | cknov                                   | wledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | vii                                                                        |

| 1            | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | oductionMotivationTarget of Stereo MatchingProblem DefinitionSolutions and ContributionsOverview of Chapters                                                                                                                                                                                                                                                                                                                                                                                                                                | 1<br>1<br>3<br>6<br>6<br>8                                                 |

| 2            | Ster 2.1 2.2 2.3                        | Related Existing Stereo Matching Instances Our Stereo Matching Algorithm  2.2.1 Matching Cost Computation  2.2.2 Disparity Computation/Optimization  2.2.3 Disparity Refinement  Design Targets                                                                                                                                                                                                                                                                                                                                             | 9<br>11<br>11<br>12<br>14<br>15                                            |

| 3            |                                         | reo Matching Algorithm Hardware-Oriented Optimization and Immentation  Parallel and Pipeline Architecture of Stereo Matching Algorithm Modification from Software to Hardware 3.2.1 Vertical Cost Aggregation Modification 3.2.2 Census Transform Vector Modification 3.2.3 Parameters and Multipliers Modification Stereo Matching Design 3.3.1 Median Filter 3.3.2 Census Transform & Support Region Builder 3.3.3 Reorder 3.3.4 Raw Cost Scatter 3.3.5 Dynamic Programming 3.3.6 Bypass FIFO and Disparity Output Logic 3.3.7 Refinement | 17<br>17<br>19<br>20<br>21<br>23<br>24<br>28<br>30<br>32<br>33<br>38<br>39 |

| 4            | 4.1                                     | Evaluation of Hardware Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47<br>47<br>47<br>49<br>51                                                 |

|              | 12                                      | Evaluation of Storog Matching Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54                                                                         |

|   |     | 4.2.1 FPGA Hardware Resources Utilization                   | 54 |

|---|-----|-------------------------------------------------------------|----|

|   |     | 4.2.2 Real-Time Performance                                 | 56 |

|   | 4.3 | Comparison with Related Instances                           | 57 |

| 5 | A R | eal-Time View Synthesis System with Stereo Matching on FPGA | 61 |

|   |     | Real-Time System Architecture on FPGA                       |    |

|   |     | View Synthesis                                              |    |

|   | 5.3 | DDR2 SDRAM Access Scheduler                                 | 64 |

| 6 | Cor | clusions and Future Work                                    | 69 |

|   | 6.1 | Conclusions                                                 | 69 |

|   | 6.2 | Chapters Summary and Contributions                          | 69 |

|   |     | Possible Future Work                                        |    |

# List of Figures

| 1.1  | Tsukuba disparity map                                    | 1               |

|------|----------------------------------------------------------|-----------------|

| 1.2  | Eyes see in 2D                                           | 2               |

| 1.3  | Eyes see in 3D                                           | 3               |

| 1.4  | Dual cameras                                             | 3               |

| 1.5  | Imec proposed personalized 3D depth range adjustment     | 4               |

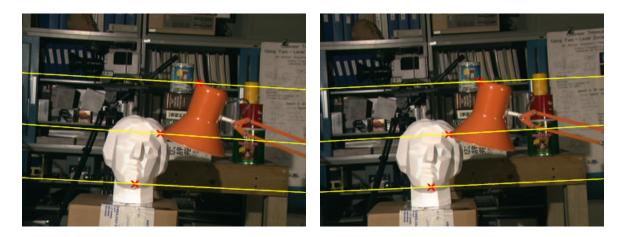

| 1.6  | Not rectified frames and not aligned corresponding lines | 4               |

| 1.7  | Rectified frames and epipolar lines                      | 5               |

| 1.8  | Basic concepts of stereo matching in epipolar geometry   | 5               |

| 1.9  | Complete setup system with FPGA on DE3 board             | 8               |

| 2.1  | O I                                                      | 11              |

| 2.2  | Scan-line optimization dynamic programming               | 13              |

| 2.3  | Half-occlusion point in tsukuba                          | 14              |

| 3.1  | Sequential stereo matching data flow                     | 18              |

| 3.2  |                                                          | 18              |

| 3.3  | Pipelined stereo matching functions                      | 19              |

| 3.4  | Vertical cost aggregation in support region              | 20              |

| 3.5  |                                                          | 21              |

| 3.6  |                                                          | 22              |

| 3.7  |                                                          | 22              |

| 3.8  |                                                          | 23              |

| 3.9  | -                                                        | 25              |

| 3.10 | 9                                                        | 25              |

| 3.11 |                                                          | 26              |

|      |                                                          | 26              |

|      |                                                          | $\frac{1}{27}$  |

|      |                                                          | <br>27          |

|      | 0                                                        | <br>29          |

| 3.16 |                                                          | <b>3</b> 1      |

|      |                                                          | 32              |

|      |                                                          | 34              |

| 3 19 | Minimum selector tree structure                          | 35              |

|      |                                                          | 36              |

|      |                                                          | 38              |

|      |                                                          | 40              |

|      |                                                          | $\frac{40}{40}$ |

|      |                                                          | $40 \\ 41$      |

|      |                                                          | $\frac{41}{42}$ |

|      | $\circ$                                                  | 42              |

|      |                                                          | 42              |

|      |                                                          | 44              |

| 3.29 | Tsukuba left and right depth maps after voting                                | 45 |

|------|-------------------------------------------------------------------------------|----|

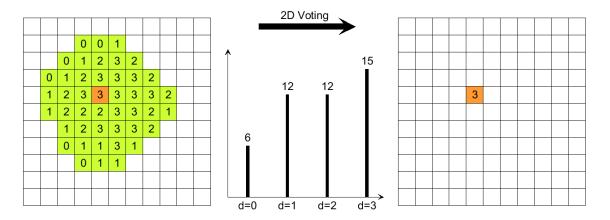

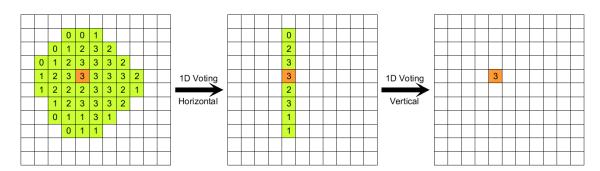

|      | Comparison of 2×1D voting and 2D voting                                       | 45 |

| 3.31 | Tsukuba final depth maps                                                      | 46 |

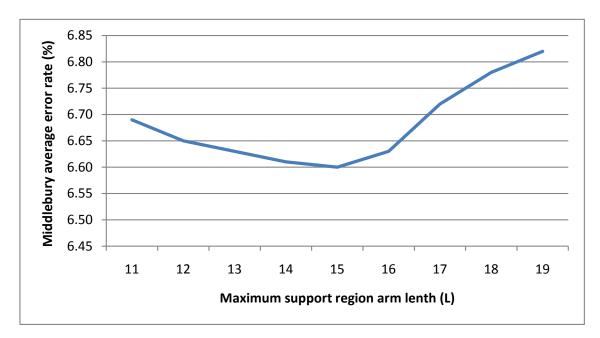

| 4.1  | Middlebury error rate and maximum support region arm length $L$               | 48 |

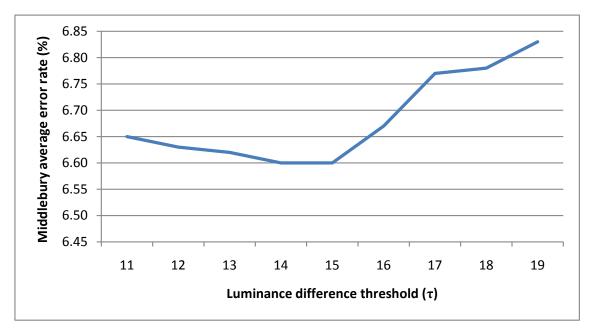

| 4.2  | Middlebury error rate and luminance difference threshold $\tau$               | 49 |

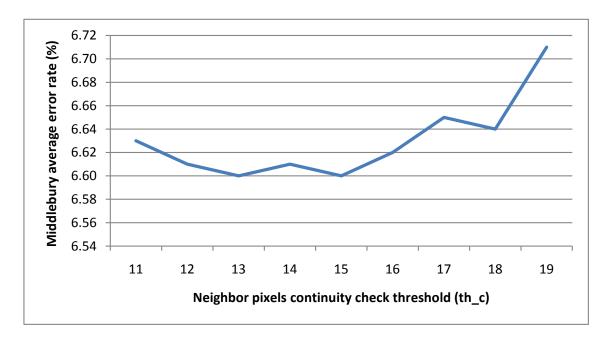

| 4.3  | Middlebury error rate and neighboring pixels continuity check threshold       |    |

|      | $th_c$                                                                        | 50 |

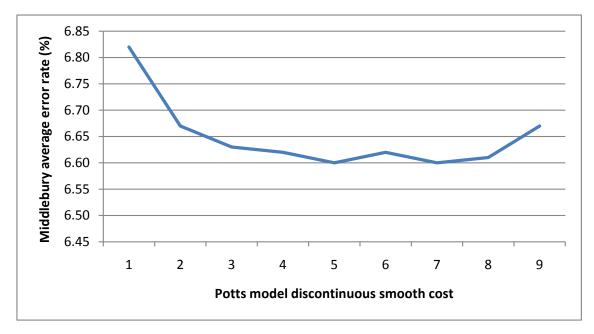

| 4.4  | Middlebury error rate and Potts model discontinuous smooth cost $\mathcal{C}$ | 51 |

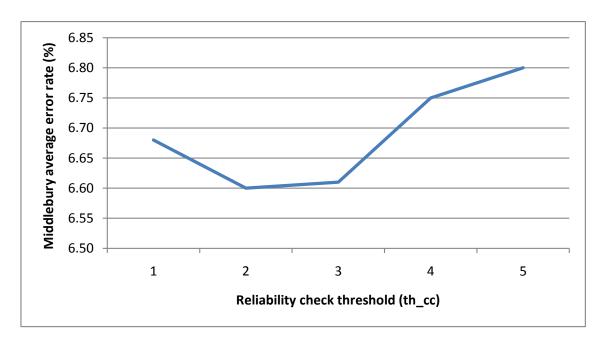

| 4.5  | Middlebury error rate and reliability check threshold $th_{cc}$               | 52 |

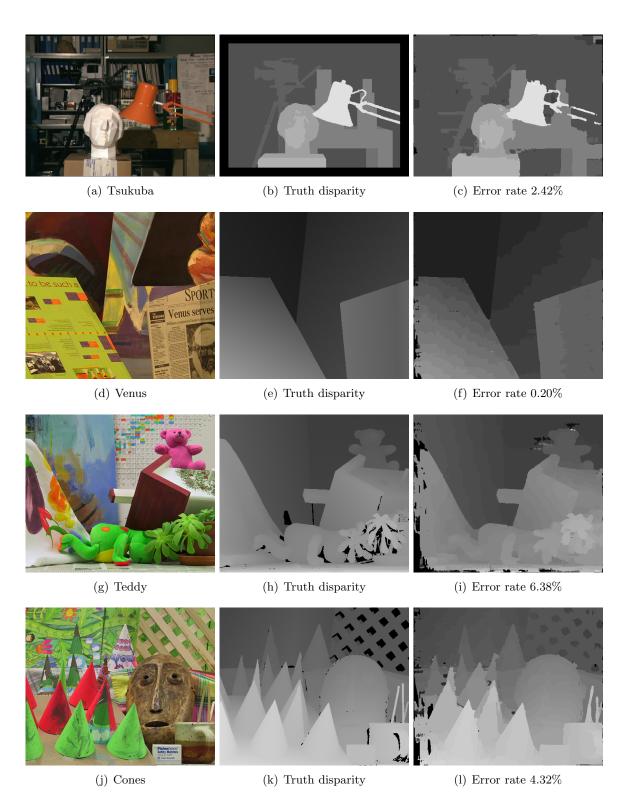

| 4.6  | Final Middlebury benchmark results                                            | 53 |

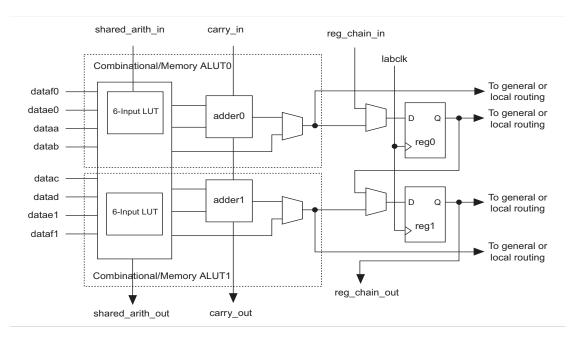

| 4.7  | High-level block diagram of Stratix III ALM                                   | 54 |

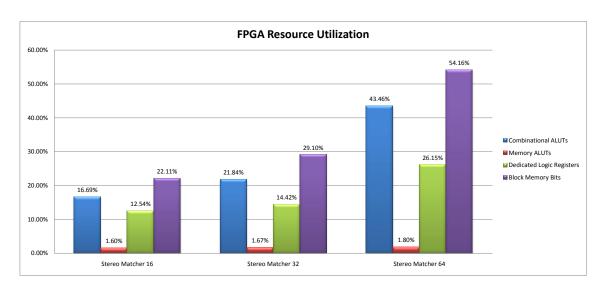

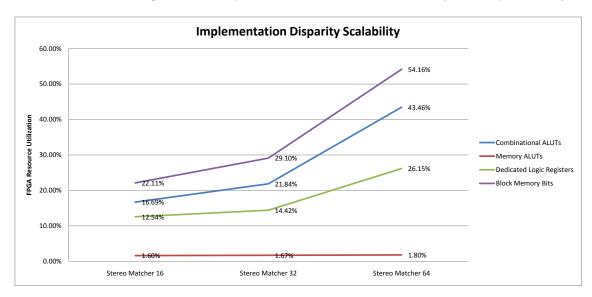

| 4.8  | FPGA resource utilization of various disparities                              | 56 |

| 4.9  | Stereo matcher implementation disparity scalability                           | 56 |

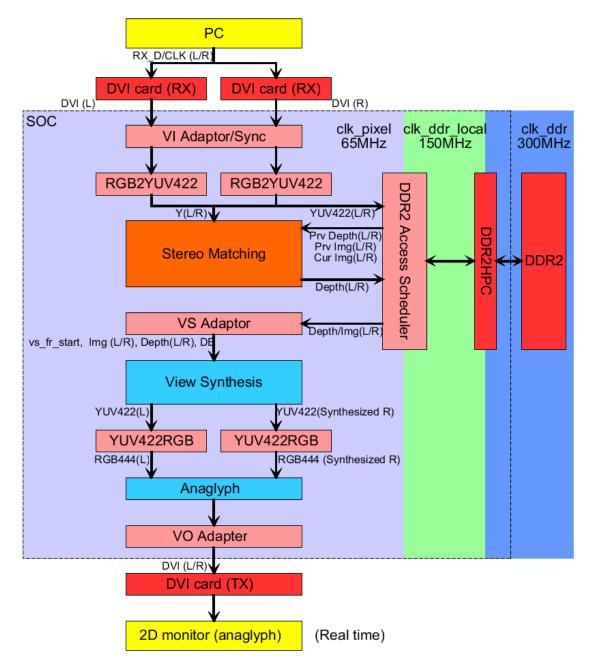

| 5.1  | On-chip system architecture                                                   | 62 |

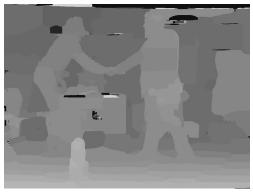

| 5.2  | Depth map and interpolated analyph frame with original frames                 | 63 |

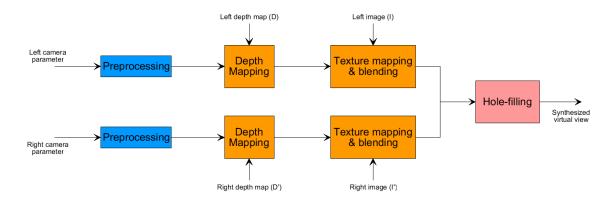

| 5.3  | View synthesis architecture                                                   | 64 |

| 5.4  | 3D depth range adjustment from full 3D to full 2D                             | 65 |

| 5.5  | DDR2 SDRAM access scheduler architecture                                      | 66 |

# List of Tables

| 3.1  | Median filter latency and memory usage                                     |

|------|----------------------------------------------------------------------------|

| 3.2  | Census transform and support region builder latency and memory usage 30    |

| 3.3  | Census transform and support region builder configurable parameters . 30   |

| 3.4  | Reorder latency and memory usage                                           |

| 3.5  | Reorder configurable parameters                                            |

| 3.6  | Raw cost scatter latency and memory usage                                  |

| 3.7  | Smooth minimum selector latency and memory usage                           |

| 3.8  | Smooth minimum selector configurable parameters                            |

| 3.9  | Back tracker latency and memory usage                                      |

| 3.10 | Back track reorder latency and memory usage                                |

| 3.11 | Bypass FIFO latency and memory usage                                       |

| 3.12 | Disparity output logic latency and memory usage                            |

| 3.13 | Consistency check latency and memory usage                                 |

|      | Consistency check configurable parameters                                  |

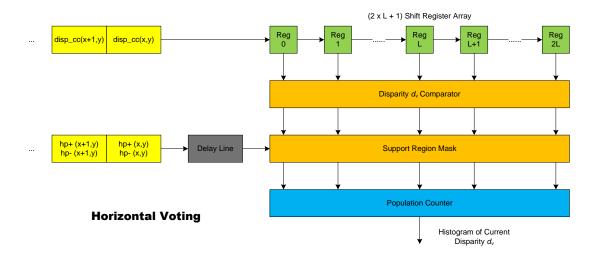

| 3.15 | Horizontal voting latency and memory usage                                 |

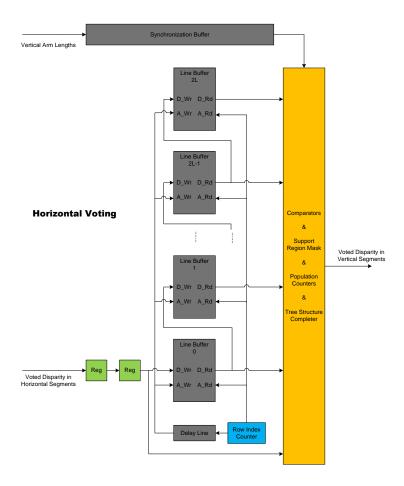

| 3.16 | Vertical voting latency and memory usage                                   |

| 4.1  | Hardware algorithm configurable parameters                                 |

| 4.2  | Support region builder configurable parameters                             |

| 4.3  | Middlebury error rate and maximum support region arm length $L$ 48         |

| 4.4  | Middlebury error rate and luminance difference threshold $\tau$ 49         |

| 4.5  | Dynamic programming configurable parameters                                |

| 4.6  | Middlebury error rate and neighboring pixels continuity check threshold    |

|      | $th_c$                                                                     |

| 4.7  | Middlebury error rate and and Potts model discontinuous smooth cost $C$ 51 |

| 4.8  | Refinement configurable parameters                                         |

| 4.9  | Middlebury error rate and reliability check threshold $th_{cc}$            |

| 4.10 | EP3SL150 on-chip memory features                                           |

| 4.11 | EP3SL150 hardware resource utilization summary                             |

| 4.12 | Stereo matcher 64 pipeline latency summary                                 |

|      | VGA signal timing format for various resolutions                           |

| 4.14 | Stereo matching algorithm Middlebury benchmark evaluation 58               |

| 4.15 | Stereo matching implementation processing speed evaluation                 |

| 4.16 | Hardware resource utilization between our implementation and Zhang . 59    |

Introduction

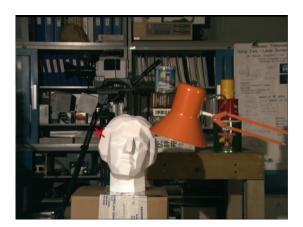

Stereo matching has traditionally been one of the most attractive research topics in computer vision domain, and is still being paid attention to from many researchers. The main function of stereo matching is to obtain depth information from a pair of images or videos whose corresponding pixels have displacement, that varies according to the depth of objects from the camera pair. The displacement in number of pixels is called Disparity. Normally disparity spans a certain range, called disparity range, which is an important parameter of any stereo matcher. The calculated depth map is often displayed as gray-scale intensities, as shown in Figure 1.1. Stereo matching extracts

(a) Left camera image

(b) Right camera image

(c) Ground left truth disparity map

Figure 1.1: Tsukuba disparity map

depth information for each pixel, and actually that is the 3D information from image or video pair. Therefore, the depth information can be further used in 3D applications, such as HD-3DTV, 3D reconstruction, virtual reality and so on.

A standard to evaluate and compare the results of different stereo matching algorithms is Middlebury stereo benchmark evaluation[38]. In this website evaluation, the generated depth maps is compared with the ground truth depth maps. The not identical depth map pixel values in the comparison will be considered as incorrect matched pixel, therefore the average error rate of the entire depth map are produced. The pictures shown in Figure 1.1 are the Tsukuba standard image pair and truth disparity map from the Middlebury stereo correspondence algorithms evaluation website.

### 1.1 Motivation

The main motivation of this thesis research and design is to implement real-time stereo matching on HD-3DTV with an FPGA prototype to pave the way for an ASIC implementation.

3DTV is an exciting technology developed since the late-1890's, which is now leading a new trend in the consumer household entertainment. The main difference between

3DTV (stereoscopic TV) and 2DTV (regular TV) is that the former uses depth information, thus the image will appear to consist of solid 3D objects and persons located in 3D space. The TV then looks like a true window to the real world and gives the audience a new experience of entertainment.

3DTV is becoming more and more popular, and it is estimated that by the end of 2015 there will be 22.2 million homes across 53 countries watching 3D programming. Therefore people will take more and more time on watching 3DTV. Then the problem comes: is it harmful to people who watches 3D programs for a long time?

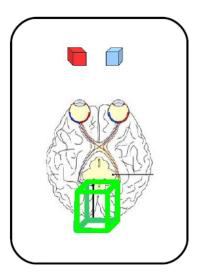

When looking to 2D programs people's eyes are focused on the subject, while the visual cortex of the brain analyzes the retinal disparities and then fuses the 2D images into 3D, as shown in Figure 1.2.

Figure 1.2: Eyes see in 2D

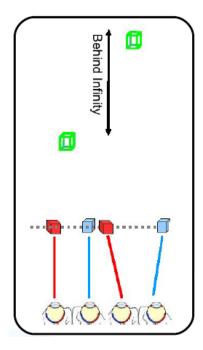

When looking to 3D programs people's eye-sight are parallel with 2.5 inch apart, which is shown in Figure 1.3. However, when objects are even further away with having left and right images too far apart, it will make the eyes diverging, which will cause eye strain and nausea. There are also other disparities that may cause eye strain and headache, for example, vertical disparity of the stereoscopic images of an object might cause one eye to track upward and the other downward, which probably is caused by imperfect lenses of dual cameras, as shown in Figure 1.4.

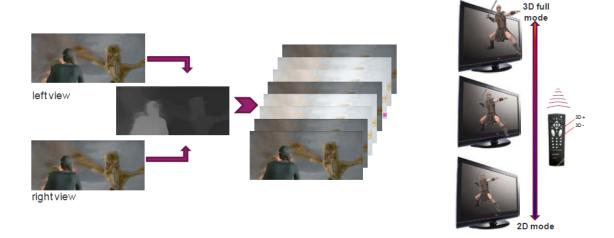

The eye strain and headache happens due to the mismatch between the 3D-display (eye focus) and real object locations in watching 3D video. Therefore, Imec proposed 'Personalized 3D Depth Range Adjustment', which is a nice solution to the problem, as shown in Figure 1.5. With this solution, users can easily modify the 3D depth range using a remote controller to satisfy personal visual comfort, furthermore, reduce eye strain headache and nausea.

Moreover, the most comfortable depth is also relative with the screen size, viewing distance and display type, which also makes it necessary to modify the 3D depth range according to the viewers' personalized visual comfort.

The proposed personalized 3D depth range adjustment system totally contains suc-

Figure 1.3: Eyes see in 3D

Figure 1.4: Dual cameras

cessively image acquisition, camera calibration, image rectification, stereo matching, DDR interface construction, view interpolation and video display. This thesis work focuses on the stereo matching part, which is the major processing bottleneck discussed in the following section.

# 1.2 Target of Stereo Matching

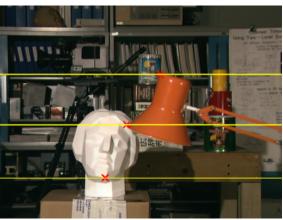

In the stereo videos, there should be one pixel in the right frame corresponding to a pixel in the left frame, which is the basis of stereo matching. The main task of stereo matching is to find the corresponding pixels (stereo pair). However, the stereo pairs in raw stereo videos taken from stereo cameras are often not on the same specific pixel line, as shown in Figure 1.6, which means that under this condition it has to complete a 2D search. Consequently, image rectification technology is imported to reduce the 2D search into 1D search, as shown in Figure 1.7, meaning that *Epipolar Geometry* is applied onto the stereo frames to perform image rectification, where the stereo pairs

Figure 1.5: Imec proposed personalized 3D depth range adjustment

Figure 1.6: Not rectified frames and not aligned corresponding lines

can be matched on one specific line, called epipolar line.

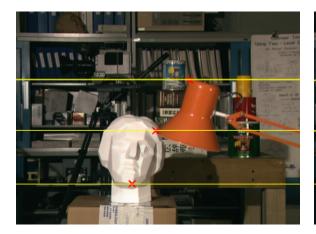

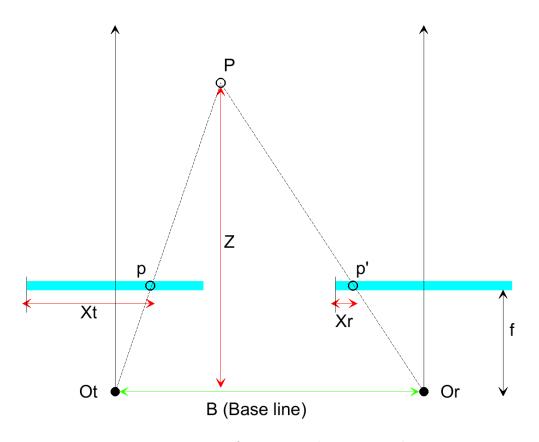

In Epipolar Geometry, some essential concepts in stereo matching are shown in Figure 1.8. The object point P corresponds to the pixel p from the left frame and the pixel p' from the right frame.  $O_t$  is the target optical center (left camera) and  $O_r$  is the reference optical center (right camera). The distance between the two optical centers is defined as the Baseline represented by B, which is parallel with by epipolar lines, and the length f from frame plane to B is the focal distance. In the case shown in Figure 1.8, the distance from P to B is defined as the depth E which is the actual distance between cameras and object point, and the distance from E to E is defined as the disparity E is defined as the stereo frames. According to Figure 1.8 and considering the similar triangles (E or E and E or E and E or E and disparity E and E are disparity E and E are disp

$$\frac{B}{Z} = \frac{(B + X_r) - X_t}{Z - f} \quad \Rightarrow \quad Z = \frac{B \cdot f}{X_t - X_r} = \frac{B \cdot f}{d} \tag{1.1}$$

Figure 1.7: Rectified frames and epipolar lines

Figure 1.8: Basic concepts of stereo matching in epipolar geometry

The equation above basically demonstrates that the more deep the object lies, the less disparity it has between the stereo pair in the input videos, and this principle is also the basis of stereo matching.

Image rectification is a very important procedure before stereo matching, because of its reduction on correspondence searching complexity from 2D into 1D. Since this

thesis work is mainly about the subject of stereo matching, the technology of image rectification will not be discussed further, and in the following discussion we will take for granted all the input stereo videos has already been rectified according to epipolar geometry.

### 1.3 Problem Definition

Last section lists the processing stages, in which stereo matching is the most time consuming part. Recently, only a marginal number of implementations could meet satisfactory quality with the constraint of real-time application, because of the high computational complexity of the stereo matching. For example, a three camera view-point interpolation prototype system[32] proposed by Sharp Corporation in 2009 could only meet a couple of frames per second for low-resolution images. The bottleneck of stereo matching has to be solved for real-time and high-quality interpolation results, particularly for our 3D depth range adjustment implementation, which should run at high frame rate and high definition -  $1920 \times 1080@60FPS$ .

Nowadays, a number of platforms such as multi-core CPU, GPU, DSP, FPGA and ASIC could be utilized for stereo matching design and implementation. At the same time, a lot of algorithms corresponding to each platforms have also been developed, however, almost none of them could satisfy both real-time and high-quality requirements. For instance, an implementation proposed by Zhang et al.[45] on GeForce8800 GTX GPU in 2009 meets high quality with an averaged Middlebury benchmark error rate 7.65%, but only reaches 12 frames per second with 450×375 resolution. In contrast, an FPGA implementation proposed by Jin et al.[20] in 2010 achieves 230 frames per second with 640×480 resolution, however, the accuracy reduces too much with averaged Middlebury benchmark error rate of 17.24%.

## 1.4 Solutions and Contributions

We propose a hardware friendly high-accuracy dynamic programming algorithm and a complete 3D depth range adjustment real-time system to meet the requirements. The high-accuracy algorithm is based on Accurate and Efficient Stereo Processing by Semi-Global Matching and Mutual Information proposed by Heiko Hirschmuller[16] and Cross-Based Local Stereo Matching Using Orthogonal Integral Images proposed by Zhang et al. [44] The former paper provides a basic dynamic programming method for stereo matching calculation, while the later paper offers a consistency check and refine method for post processing. We merge them together to create a new Scan-line Optimization Dynamic Programming algorithm for stereo matching. The whole design of this prototyping system, including image data synchronization, stereo matching, DDR interface, view interpolation and video display, is implemented on a single EP3SL150 FPGA from Altera.

Compared with Lu's implementation [47] which only uses a cross-based local stereo matching algorithm without dynamic programming on the same FPGA, our new implementation improved the averaged Middlebury benchmark error rate from 8.2% to

6.6%. Moreover, our new implementation supports high-definition video, which means it can support the resolution of  $1920\times1080@60FPS$  instead of  $1024\times768@60FPS$  in Lu's implementation.

We make the following main contributions, separated into two aspects, releasing a new algorithm and implementing the system on FPGA:

#### releasing a new algorithm that:

- Preserves high stereo matching accuracy with 6.6% averaged Middlebury benchmark error rate.

- Modifies *Mini-Census Transform* proposed by Chang et al.[4] to improve robustness near the object edges.

- Generates more smooth boundary depth maps due to scan-line optimization dynamic programming.

- Creates consistent real-time video using timing consistency over successive frames.

### Implementing the algorithm on FPGA that:

- Builds real-time stereo matching system to generate high-definition video on the resolutions of  $1024 \times 768@60FPS$  and  $1920 \times 1080@60FPS$ .

- Constructs a parallel and pipelined hardware architecture to meet the requirements of timing and resource usage.

- Makes the system structure independent on the disparity range. We have implemented on the FPGA EP3SL150 with maximum disparity range of 16, 32 and 64.

- Discarding the avalon interface used in Lu's implementation[47] to prepare a stereo matching core without industry IP for ASIC platform.

- Provides a complete system which could use the imported stereo videos to generate

depth map videos (results from stereo matcher) or anaglyph videos (results from

viewpoint interpolater) on standard DVI/HDMI monitors.

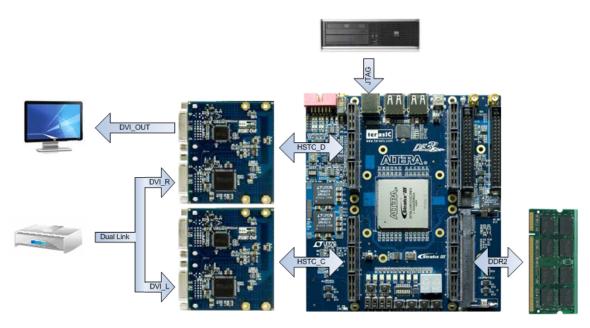

We utilize the DE3 board developed by Terasic to implement the whole system design. The board includes the EP3SL150 FPGA and a lot of peripherals, such as DDR2 SDRAM, USB and SD card. Two DVI extension boards are used to receive the stereo videos and transfer output videos to the monitor. In the setup system shown in Figure 1.9, the JTAG link is used to burn the configuration file compiled from PC into FPGA; DDR2 link is used to connect DDR2 SDRAM to save frames for timing consistency and viewpoint interpolating; HSTC interface is used to connect DVI extension boards for videos in and out. The main procedure is first configuring FPGA, and then the stereo videos comes into FPGA by dual link cable and two DVI extension boards, after that the output videos processed by FPGA goes out into the monitor from one DVI extension board.

Figure 1.9: Complete setup system with FPGA on DE3 board

# 1.5 Overview of Chapters

In this thesis work, Chapter 1 gives a brief introduction about our problem, solution and contribution. Chapter 2 introduce the stereo matching instances and our algorithm. Chapter 3 presents a dynamic programming algorithm and corresponding hardware modules design using a top-down approach. Chapter 4 evaluates the hardware algorithm and stereo matcher design, and compares our results with other state-of-the-art related implementations. Chapter 5 presents the complete real-time system design using stereo matcher as a block on FPGA and introduces other important kernels, such as view synthesis and DDR2 SDRAM access scheduler. Chapter 6, as the final chapter, gives the summary and conclusion of our thesis work and provides relative suggestions and developments for the future design and application.

Stereo Matching Algorithm

Approximately 20 years ago, stereo matching algorithms began to fast develop, and nearly all these different algorithms have been generally evaluated by Scharstein and Szeliski[35], who classified those algorithms into two main kinds: local and global algorithms. Local algorithm is the short name from local area based stereo matching algorithms, which emphasizes the cost of every pixel is aggregated from a local area formed by its neighboring pixels. While global algorithm stands for global optimization based stereo matching algorithm, which emphasizes the cost of every pixel is extracted from a frame or a line by some minimum cost selection method. These two kinds of algorithms are both robust for they both generate the cost by referring to other pixels, but compared with local algorithms, global algorithms often take more computational complexity and more storage resources.

We take the advantages of both local and global algorithms to generate our own algorithm in this thesis work. It is efficient for us to use local algorithms to deal with consistency check and refine processing which is less important than the stereo matching core part but has almost the same computational complexity as the core, while it is accurate for us to utilize global algorithms to perform stereo matching core part (dynamic programming part) to provide as precise results as possible. We can hence take the advantage from local algorithm to reduce computational complexity and save storage resources, and from global algorithm to obtain accurate stereo matching results.

Section 2.1 categories the related existing instances according to various hardware platforms. Section 2.2 presents the our stereo matching algorithm, including computation flow, cross-based local algorithm and scan-line optimization dynamic programming global algorithm. Section 2.3 lists the targets of our stereo matching design and implementation on FPGA, and introduces briefly the benefits of FPGA platform and implementation.

# 2.1 Related Existing Stereo Matching Instances

As mentioned before, the challenge of stereo matching is to solve the complex computation while keeping the highly accurate results. Based on such challenge a lot of methods approaching real-time and efficient stereo matching computation have been developed in the past two decades, while recently, some of them have obvious achievements towards either computational speed or matching accuracy. They will be shown in the following paragraphs by categories of different implementation platforms.

**CPU implementation** is the first prototyping platform for different algorithms developed, and its main disadvantage is the processing speed, but till now there are a lot of aggregation methods being able to accelerate its processing speed. An efficient segmentation-based cost aggregation strategy for local algorithm was proposed

by Tombari et al.[37], which achieves  $384 \times 288@5FPS$  with a disparity range 16 ( $D_{max} = 16$ ) on an Intel Core Duo 2.14GHz; and it only reaches  $450 \times 375@1.67FPS$  with  $D_{max} = 60$ . A dynamic programming algorithm proposed by Salmen et al.[34] achieves  $384 \times 288@5FPS$  with  $D_{max} = 16$  on a 1.8GHz CPU platform. Later a method of combining a multi-level adaptive technique with a multi-grid approach proposed by Kosov et al.[24] achieves  $450 \times 375@3.5FPS$  with  $D_{max} = 60$ . Another local algorithm of variable cross algorithm and orthogonal integral image technique for accelerating the aggregation over irregularly shaped regions proposed by Zhang et al.[44] achieves  $384 \times 288@7.14FPS$  with  $D_{max} = 16$  and  $450 \times 375@1.21FPS$  with  $D_{max} = 60$ . Although the processing speed performance of CPU is pretty bad, it has the advantage of very good matching accuracy, which is often less than 10% average error rates.

GPU implementation is another platform for various algorithms development. Yang et al. [42] proposed a global optimizing real-time algorithm (hierarchical belief propagation) on a GeForce 7900 GTX GPU, which achieves  $320 \times 240@16FPS$  with  $D_{max} = 16$ ; and its average error rate is 7.69%. Wang et al. [40] proposed an algorithm based on adaptive aggregation and dynamic programming, achieving  $320 \times 240@43FPS$  with  $D_{max} = 16$  on an ATI Radeon XL1800 GPU; but its average error rate is increased a little to 9.82% compared with Yang's work. Zhang et al. [46] implemented a variable cross algorithm and an orthogonal integral image technique on GeForce GTX8800 GPU, which reached  $384 \times 288@100.9FPS$  with  $D_{max} = 16$  and  $450 \times 375@12FPS$  with  $D_{max} = 60$  and error rate 7.60%. In current years, Humenberger at el. [17] improved the Census Transform on GeForce GTX 280 GPU and reached  $450 \times 375@105.4FPS$  with  $D_{max} = 60$  and error rate 9.05%. GPU implementations perform well till now, but it is not the suitable solution for highly integrated embedded systems because of the GPU's high power and memory consumption.

**DSP implementation** is also investigated for applying stereo matching algorithms. Chang et al.[3] propose a  $4\times5$  jigsaw matching template and parallel processing method to improve stereo matching performance on a VLIW DSP, which reaches  $384\times288@50FPS$  with  $D_{max}=16$  and  $450\times375@9.1FPS$  with  $D_{max}=60$ , however, the average error rate is high to above 20%.

The implementation types mentioned above are all software based platform, so that the computing logic and data paths related with hardware resource and utilization cannot be changed and configured, which means they do not have the potential for optimizing the existing algorithms. Moreover, these kinds of implementations all require very high clock frequency and data throughput. Compared with these obvious disadvantages, dedicated hardware design is taken into consideration for performance revolution recently. A high performance stereo matching algorithm with mini-census transform and adaptive support weight, as well as its corresponding real-time VLSI architecture was proposed by Chang et al.[4], which is implemented with UMC 90nm ASIC and achieves  $352 \times 288@42FPS$  with  $D_{max} = 64$ . Jin et al.[20] designed a complete pipeline hardware architecture with census transform and sum of hamming distances, which achieves  $640 \times 480@230FPS$  with  $D_{max} = 64$  and average error rate 17.24%. Seen from these two hardware implementations, their bottleneck is the on-chip memories which limits the image resolutions, although they have notable performance. Zhang et al.[47] implemented variable cross algorithm on FPGA, which achieves  $1024 \times 768@60FPS$

with  $D_{max} = 64$  and average error rate 8.2%. Zhang's work is excellent on both computational speed and matching accuracy aspects, but the algorithm he uses is a local algorithm, therefore it still has space for matching accuracy improvement. We list and compare all of the above implementations with ours in Chapter 4.

# 2.2 Our Stereo Matching Algorithm

Most stereo matching algorithms generally perform the following steps or a subset thereof, according to the taxonomy proposed by Scharstein and Szeliski[35]:

- 1. Matching cost computation

- 2. Cost aggregation

- 3. Disparity computation/optimization

- 4. Disparity refinement

For local algorithms, they often follow the steps as  $1\rightarrow 2\rightarrow 3\rightarrow 4$  with a simple Winner Takes All (WTA) strategy. However, for global algorithms, they often follow the steps as  $1(\rightarrow 2)\rightarrow 3\rightarrow 4$  to skip step 2 with global or semi-global reasoning. In our algorithm, dynamic programming is a kind of global one, so we will omit step 2 and describe other steps in the following subsections.

#### 2.2.1 Matching Cost Computation

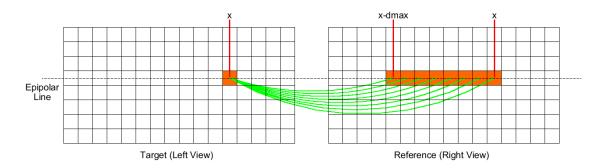

As introduced in the previous sections, the stereo pairs are matched in 1D along the epipolar line. In fundamental stereo matching cost computation method, the corresponding points in the reference frame to the points in the target frame are searched pixel by pixel along the epiploar horizontal line within a certain disparity range, as shown in Figure 2.1. In this fundamental searching method, the disparity range is

Figure 2.1: Fundamental stereo matching computation method

$[0...d_{max}]$ , while  $d_{max} = 7$  and total disaprity levels  $D_{max} = 8$ . According to Equation 1.1, the disparity range d depends on the depth Z, the length of baseline B and the focal length f. For a stereo pair, estimating the matching cost is defined as evaluating the probability of each match in the disparity range, which means the matching cost is

inverse to the probability. In the fundamental pixel by pixel method, the matching cost could be defined as *Absolute difference*, *Squared Difference*, *Hamming Distance* and so on, no matter the frames are gray or RGB colored.

The absolute difference matching cost is measured by Equation 2.1;

$$Cost(x, y, d) = |I(x, y) - I'(x - d, y)|$$

(2.1)

The squared difference matching cost is defined by Equation 2.2;

$$Cost(x, y, d) = (I(x, y) - I'(x - d, y))^{2}$$

(2.2)

In the equation above, I refers to the gray-scale intensity of a pixel from the target frame, while I' from the reference frame, and they have the relationship with the disparity d as the equation shows. In the basic example, the stereo pairs are determined by the minimum cost value as the Winner in WTA strategy, and the corresponding d is the chosen disparity of the pixel p(x, y) in the target frame.

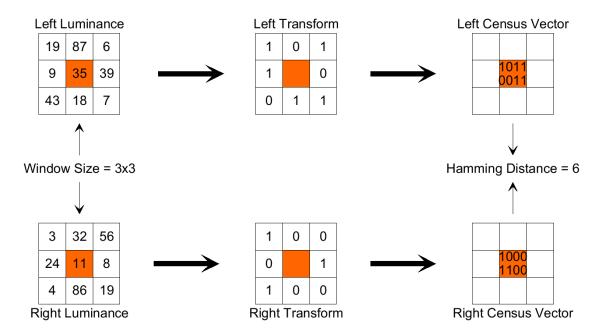

The hamming distance matching cost is what we use in our algorithm, which is normally obtained from converted frames. The conversion procedure is performed by converting the gray-scale intensity of each pixel into some kind of bit vectors. In our algorithm we modify the Mini-CensusTransform proposed by Chang et al.[4] to create our own Census Transform to do the conversion, and more detailed of the converting algorithm are introduced in Chapter 3.

# 2.2.2 Disparity Computation/Optimization

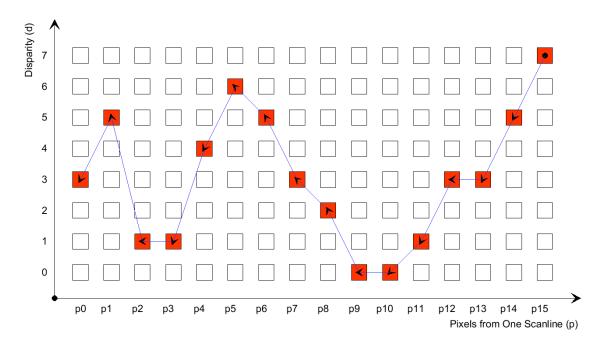

This step is to search the best disparity assignment which minimizes a cost function over the whole or subset of the whole stereo pair. We use a kind of semi-global algorithm - scan-line optimization dynamic programming - to perform this procedure. This algorithm searches for the best path within the *Disparity Space Image (DSI)* over the stereo pair in one line using the pixel-based matching cost, as shown in Figure 2.2.

The parameter  $\{p_j|j \in [0, W-1]\}$  is defined as the pixels in one row of the target frame, where W is the image width, and in this example W = 16. The chosen disparity  $d(p_j)$  is in a range of [0, D-1], and D=8 in this example. The matching cost of  $p_j$  at each disparity d is C(j,d), therefore, we obtain a  $W \times D$  cost matrix, as shown in Figure 2.2. The purpose of dynamic programming is to find an *optimal path* in the matrix with following two stages.

First stage is updating the matrix from left to right (j = 1 to j = W - 1) in one line according to Equation 2.3:

$$C(j,d) = C(j,d) + \min_{d' \in [0,D-1]} \{ C(j-1,d') + S(|d-d'|) \}$$

(2.3)

The cost term C(j,d) is to measure how well the assignment fits to the stereo pair, while the smoothness term S(|d-d'|) is to penalize the disparity variations and large variations are only allowed at depth borders, where d' is the disparity of the previous pixel. In the detailed case, the smoothness cost S(|d-d'|) has different computational equations depending on different models. For the Potts model, the smoothness cost is

Figure 2.2: Scan-line optimization dynamic programming

computed as Equation 2.4:

$$S(|d - d'|) = \begin{cases} 0, & d = d' \\ C, & d \neq d' \end{cases}$$

(2.4)

We see from Equation 2.4 that the smoothness cost of the Potts model depends only on whether the disparity from the previous pixel is the same as the disparity from the current pixel, so that the smoothness cost only has two possible values. For linear model the smoothness cost is shown in Equation 2.5:

$$S(|d - d'|) = \alpha |d - d'| \tag{2.5}$$

We see that smoothness cost of the linear model depends on the difference between the disparity from the current pixel and each disparity from the previous pixel, so that the smoothness cost has D possible values, which is much more complex than the Potts model on implementation especially for a parallel structure. The main target for this first stage is utilizing Equation 2.3 to establish links between (j, d) and  $(j-1, d^*)$ , where  $d^*$  is the chosen minimum d'.

**Second stage** is to track the so-obtained matrix from right to left to get the optimized path. First, we obtain the entry point at the end of each line  $(W-1, d(p_{W-1}))$  according to Equation 2.6:

$$d(p_{W-1}) = \arg\min_{d' \in [0, D-1]} C(W - 1, d')$$

(2.6)

Starting from the chosen disparity of the entry point we traverse backward (from j =

W-1 to j=0) along the path built in the first stage, assigning a disparity at each pixel, as shown in Figure 2.2. Then we obtain the disparity of every pixel and further the whole depth map.

The computational complexity of the first stage is  $O(D^2)$  utilizing a parallel structure according to Equation 2.4. Computational complexity directly affects hardware resource usage, especially logic combinational circuit usage, so it is better to reduce it by some optimization method. There is an envelope algorithm proposed by Pedro F. Felzenszwalb et al.[11] to reduce the computational complexity from  $O(D^2)$  to O(D), however, this algorithm is computed in a serial way, which means we have to adopt a serial structure to implement it. Considering our main bottleneck of implementation is the calculation speed not the hardware resource, it has more benefit for us to choose the parallel structure in the trade-off between hardware computational speed and hardware resource usage.

### 2.2.3 Disparity Refinement

There is a limitation about disparity estimation, because there may not always exist correspondences for every pixel in the target frame, such as *Half-Occlusion* pixels shown in Figure 2.3. In Figure 2.3, the pixels of the camera legs in target frame of Tsukuba

Figure 2.3: Half-occlusion point in tsukuba

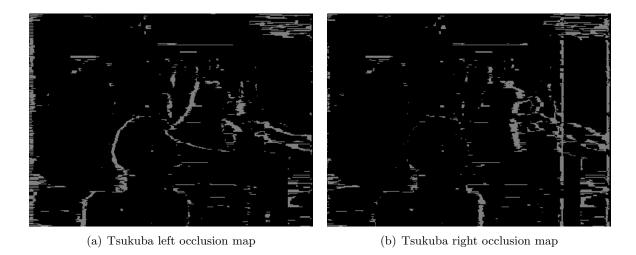

have no corresponding pixels in reference frame, because they are occluded by some front objects, and we called them half-occlusion pixels. In this case, *Consistency Check* procedure is often utilized to check these areas and make up them consistent. Before consistency check, it is necessary to make sure the depth map from the reference frame is also generated by the stereo matcher, then we could perform a target frame consistency check (correcting left depth map with right depth map) and a reference frame consistency check (correcting right depth map with left depth map) to fix detected mismatches by surface fitting or distributing neighboring valid disparity estimates[35].

After the consistency check, the disparity map is not nice enough for use, therefore some additional techniques are utilized to improve the reliability and accuracy of disparity map, such as *Sub-Pixel Estimations*[36] or *Disparity Voting*[28]. We choose disparity voting in a support region for our system, and the support region is based

on luminance difference before dynamic programming, which we introduce in detail in Chapter 3. Later after voting, it often has a final procedure of median filter to reduce the salt and pepper noise and make the disparity map more smooth.

Our dynamic programming algorithm can generate the high-quality of depth maps with the trade-off of increasing the computational complexity, however the computational complexity can be implemented and optimized on FPGA platform, therefore it is possible to create a real-time and high-quality stereo matcher on FPGA using our algorithm, and we have successfully performed it, whose evaluation is shown in Chapter 4.

# 2.3 Design Targets

For our total system has both real-time and accuracy requirements, we need to consider several aspects to suit our design targets on FPGA platform:

# 1. Real-time implementations

Our design should at least process 60 frames per second with configurable resolutions including high-definition resolution.

### 2. Accurate matching

Our design should achieve less than 7% average error rate

### 3. Implementation complexity

Our implementation should utilize only basic arithmetic blocks such as adders and comparators, and not employ complex blocks such as multipliers and dividers.

#### 4. Memory usage

Our FPGA prototyping implementation should reduce the memory utilization as low as possible for aiming at further ASIC implementation, and in detail the usage should not be over 50% of total memory on FPGA.

#### 5. Implementation without IP

Our architecture should be built on transparency models without IP for aiming at ASIC implementation and customers.

The advantage of FPGA or ASIC platform is the excellent flexibility in architecture design which decides the logic and data path. Therefore it provides the potential optimization and possible most efficient design environment. According to the related research and investigation, it is the customized hardware design that could lead us to the most suitable approach for our dynamic programming algorithm and parallel pipelined architecture. We choose the FPGA prototyping platform because of its highly configurable properties and great hardware resources for our huge parallel structure. Our FPGA board is Terasic DE3, which contains an Altera EP3SL150 FPGA core chip and a lot of peripherals such as JTAG UART port, DDR2-SDRAM, DVI extension borad, usb port, SD card port etc.

# Stereo Matching Algorithm Hardware-Oriented Optimization and Implementation

This chapter discusses in detail the algorithm we adopt for stereo matching, which is a mixture of a global [16] and a local algorithm [44]. The global one is applied on dynamic programming part, while the local one is utilized on refinement part. We do some modification on our algorithm to make it more hardware friendly, such as modifying census transform, changing architecture, reconfiguring parameters etc. For our whole hardware architecture, we take the pipeline structure to obtain the best data processing throughput across all the blocks under the pixel rate clock frequency, which means in such clock frequency there is one pixel going into the stereo matcher while there is one depth result coming out of the stereo matcher every clock cycle. That whether the processing is in scan-line order or not depends on our hardware critical path, which we discuss in detail in later sections.

We will discuss our algorithm modification and hardware architecture design in a top-down approach. Section 3.1 introduces the complete parallel and pipeline data processing structure of our stereo matcher. Section 3.2 introduces the algorithm modification of the hardware model compared with the software model. Section 3.3 introduces our design of stereo matcher function block one by one.

# 3.1 Parallel and Pipeline Architecture of Stereo Matching

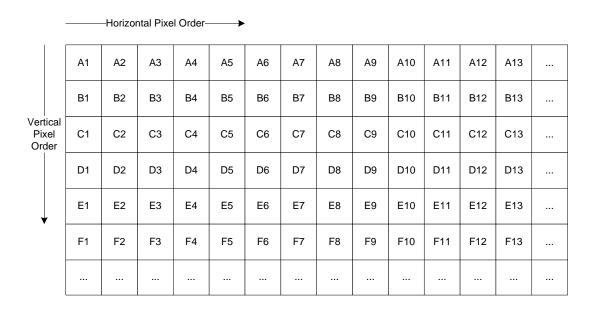

The basic stereo matching processing is a nesting loop on pixels and disparities, which is shown in Figure 3.1. Obviously the disparity loop of computing costs is the bottleneck of an effective computation, and it is also this loop that makes stereo matching very slow, especially when the stereo videos have large disparities. However, the sequential data flow has advantages: on one hand it saves hardware resources because every disparity of each pixel has to reuse the same resources, on the other hand it is a friendly structure for algorithm optimization and data compression. Consequently, such sequential structure is widely used in software based platform for not real-time application.

The content is different in configurable hardware platforms, rich in hardware resources and flexible architecture building, so that it is not necessary to reuse the hardware resources as the sequential structure does. We hence unroll the computational loop and adopt a parallel architecture as shown in Figure 3.2. Seen from the parallel structure, we unroll the disparity loop for each pixel and compute the corresponding costs independently at the same time in parallel to speed up our total computation procedure. The number of parallel paths is the maximum disparity, which is unlimited in the algorithm, but limited by the total hardware resources on FPGA board.

Figure 3.1: Sequential stereo matching data flow

Figure 3.2: Parallel stereo matching data flow

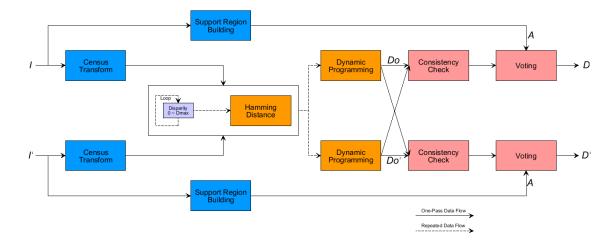

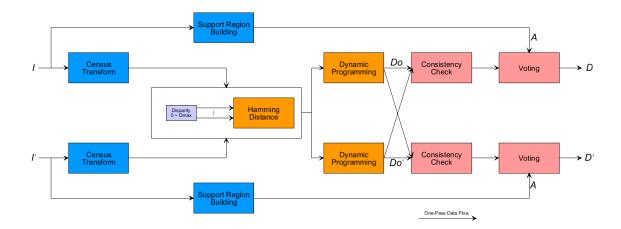

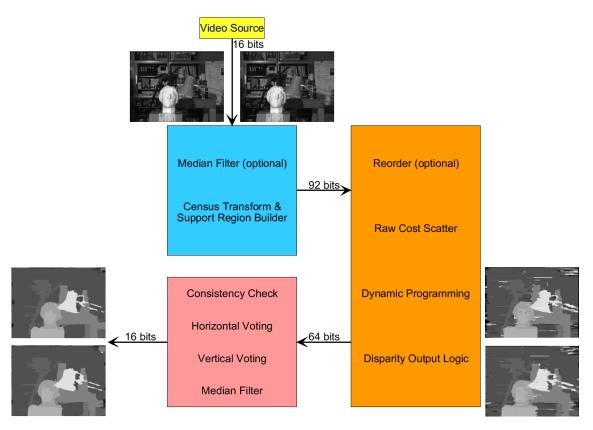

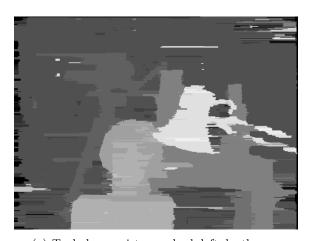

The structure shown is only for stereo matching part, and actually the total system is more complex including synchronization, RGB-YUV converter, stereo matcher, DDR scheduler, viewpoint interpolater, anaglyph creator, etc., which is discussed in Chapter 5. The total system is also used for stereo matching verification, and we are assuming here the other parts work fine to provide an ideal environment of pipeline processing. Under such conditions, the functions of stereo matcher is shown in Figure 3.3. Take Tsukuba as an example, the rectified stereo gray-scale frames go into the stereo matcher, and the data width of pixels from left and right frames are 16 bits. After median filter, support region builder and census transform, the 84 bits data of transformed census vectors and support region arms from left and right frames are passed to reorder for further processing. Reorder, raw cost scatter, dynamic programming, post reorder and disparity output logic are main function blocks of dynamic programming; they work out the depth map together using scheduled dynamic programming algorithm which is hardware and resource usage friendly. The 64 bits data generated by the scheduled

Figure 3.3: Pipelined stereo matching functions

dynamic programming goes into the refinement procedure, which is mainly used to make up the raw depth map, i.e. check and correct occlusion parts and voting for most frequently used disparity. After that the left and right depth maps are generated as the luminance 16 bits data. The total stereo matching is configurable for run-time parameters using control registers, which is convenient for setting resolution, maximum disparity and some threshold used in algorithm.

In the following section, we discuss the modification from the original algorithm of the software model to the hardware friendly algorithm. These modifications change the functions of algorithm because of hardware limitation or optimization, and we provide the comparison and evaluation of each modification.

# 3.2 Algorithm Modification from Software to Hardware

The software model is suitable for algorithm development or research, because it is a very flexible platform to make your thought into reality model without considering anything else. However, for the hardware model it is often considered more, such as computation complexity, hardware limitation and hardware optimization, so there are a lot of differences between software and hardware model. The disparity loop unrolling introduced in the last section is also a type of difference, but that doesn't change the main function of algorithm. In this chapter, what we discuss is called a modification,

which is actually changing the function to be more hardware friendly.

### 3.2.1 Vertical Cost Aggregation Modification

The software model proposed by Zhang et al.[44] computes the four direction arm lengths of each pixel to construct the support region for voting, which we discuss in detail in Section 3.3. The support region is shown in Figure 3.4. The vertical

Figure 3.4: Vertical cost aggregation in support region

cost aggregation is one step before dynamic programming processing, which is used to include more vertical relative luminance values to improve the quality of dynamic programming. In Figure 3.4, the aggregation area is the shadowed rectangular, whose number is a parameter limited by hardware resources, and after aggregation the total value need to be weighted by aggregated pixel numbers:

$$C(p,d) = \frac{\sum_{i=-v_p^-}^{v_p^+} C(p+i,d)}{v_p^+ + v_p^-}, \quad d \in [0, d_{max}]$$

(3.1)

In hardware implementation, building vertical windows will cost lots of line buffers, whose number depends on the vertical span of the window size, which we introduce in Section 3.3. The default vertical span for vertical cost aggregation is 5, so it has to spend 4 line buffers for that. Moreover, the structure we would like to implement on FPGA is parallel, which means it will cost at least  $4 \times D_{max}$  line buffers for vertical cost aggregation. Assuming the frame width is 1024 and the cost is 3 bits using minicensus transform[4], the total on-chip memory usage on vertical cost aggregation will be  $D_{max} \times 12Kbits$ . For a classical stereo matcher, the maximum disparity  $D_{max}$  should be at least 64, so that it will cost 768Kbits on-chip memory totally, which is not a small memory usage in our FPGA board.

Considering the point above, the hardware implementation doesn't adopt vertical

cost aggregation, and utilizes the concatenation census vector instead with the completely same result, which we are going to introduce next.

## 3.2.2 Census Transform Vector Modification

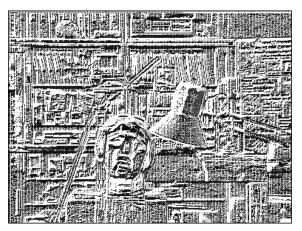

#### 3.2.2.1 Census Transform

Census transform is a kind of non-parametric local algorithm, which depends on the local pixel luminance values in a relative local window, and not on the pixel luminance itself, as shown in Figure 3.5. The direct result of census transform is that the

Figure 3.5: Census transform in a  $3\times3$  window

transformed vector attaches the structure information, as shown in Figure 3.6.

The main advantages of the census transform is increasing the robustness near the edge of objects where depth discontinuities occur. The stereo videos from stereo cameras often have gain and bias variations, and in such conditions the census transform is also good to reduce the effects of these variations. The main disadvantage of census transform is the original information attached to each pixel is weakened, but for our scan-line dynamic programming algorithm, the structure information is more important to increase the area smoothness than the luminance value itself. Another disadvantage is that the census transform often generates a long vector consuming many data, which depends on the window size and sampling pattern. For instance, a  $3\times3$  window shown in Figure 3.5 will generate 8 bits census vector, however, a  $5\times5$  window will generate 32 bits vector. The increase of vector length is exponential to the increase of window size when referring to all the neighboring pixels, which will consume too much hardware resources, so it is necessary to choose a hardware-friendly window size and census sampling pattern. In this thesis work, we take the window size by  $5\times5$  for a single

(a) Tsukuba original image

(b) Tsukuba census transform vector

Figure 3.6: Tsukuba census transform in a 3×3 window

central pixel, while take the sampling pattern by mini-census transform, which we introduce in detail next.

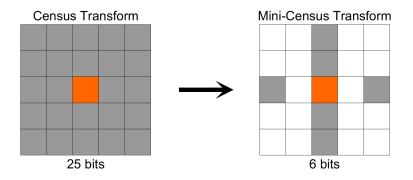

## 3.2.2.2 Census Transform Hardware Friendly Modification

The census transform hardware friendly modification has two separated parts, one is the sampling pattern selection, the other is the census vector concatenation optimization to replace the vertical cost aggregation.

In this work, we use the mini-census transform sampling pattern proposed by Chang et al.[4], as shown in Figure 3.7. Utilizing this mini-census transform, the luminance

Figure 3.7: Mini-census transform sampling pattern

value of each pixel is converted into a 6 bits vector, which saves very much data width compared with the full neighbor sampling pattern (32 bits). Moreover, the mini-census consumes less data width of raw cost which is the result of the following function block. For instance, the maximum raw cost extracted from luminance difference is 255 (8 bits), while the one extracted from the mini-census vector is only 6 (3 bits). So the data width for raw cost is significantly reduced using mini-census transform vector.

For the memory hungry vertical cost aggregation block mentioned in Section 3.2.1, we could also use census vector concatenation method instead:

$$CT(v_1) + CT(v_2) + CT(v_3) + CT(v_4) + CT(v_5) = CT(v_1 \& v_2 \& v_3 \& v_4 \& v_5)$$

(3.2)

In Equation 3.2 CT is the census transform calculation. Because the raw cost calculation of the census vector is hamming distance calculation, the cost aggregation procedure is the hamming distance aggregation, which could be replaced perfectly by computing the hamming distance of concatenation census vector once according to the property of the hamming distance. This equivalent replacement is shown in Figure 3.8.

Figure 3.8: Replacement of vertical cost aggregation with census vector concatenation

# 3.2.3 Parameters and Multipliers Modification

Stereo matching is a complex system, and there are a lot of parameters configurable for it. In the software model performed by C++, a number of weighted or floating point parameters are applied to the stereo matching, furthermore, many multipliers as the attachment are adopted for setting them. However, those floating point parameters and multipliers are not friendly to our hardware implementation at all, which also obey our original target of building a simple system for ASIC. So the hardware friendly modification here is to convert weighted parameters to unweighted ones, and use the

shifter and adder to build a basic multiplier, thus we could control the priority of more complex multiplier structure or more accurate result, which is a resource-accuracy trade-off.

In the following section, we divide the total algorithm by blocks and present them together with the related hardware design. We also provide every possible parameters setting, corresponding latency and on-chip memory usage for reference of each block. The latency computation is based on the required delay and pipeline stages, and the former is related with block functions such as line buffer delay and read latency, while the latter is related with timing analysis of each block to schedule critical paths. The on-chip memory usage from each block is useful for further memory optimization in ASIC design.

# 3.3 Stereo Matching Design

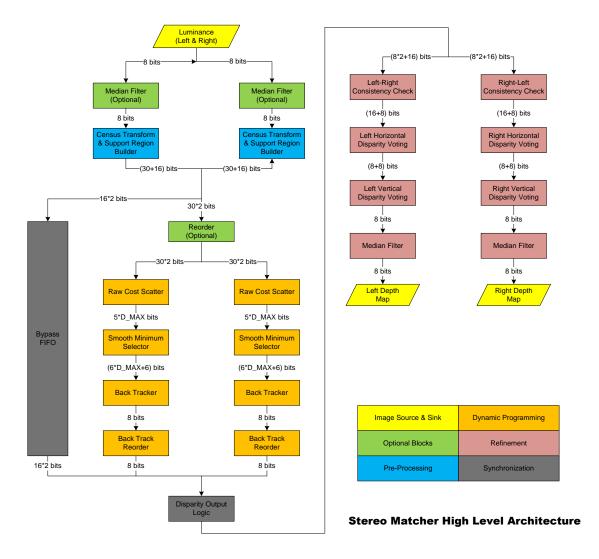

The high level architecture of stereo matcher is shown in Figure 3.9, including data flow, data width and colored function segment sets. The yellow set is the image source and sink, where the luminance values go into stereo matching while depth map (displayed by luminance) comes out. Considering left and right frames and depth maps of real-time video, the throughput of stereo matching is 16 bits at 65MHz pixel rate  $(1024 \times 768@60FPS)$  or more. The green set is some optional segments which could help to improve the performance when encountering particular bottlenecks, e.g. the median filter in the beginning could remove noise if the input stereo video is imperfect, and the reorder could improve critical path problems when the disparity range is pretty high. Adding or removing these optional segments will not effect the final result if there are not such bottlenecks. The blue set is pre-processing part for stereo matching, for the census transform generates census vectors prepared for dynamic programming while the support region builder generates arm lengths and 2D regions prepared for voting. The orange set is the core processing part: the dynamic programming. Its incoming is concatenated census vector from left and right census transform, while its outgoing is fundamental depth map for refinement. The pink set is the refinement part, which makes up the fundamental depth map to generate the final left and right depth map. The gray set is synchronization part used to bypass the arm lengths and synchronize them with corresponding pixels in order to make sure the correct information arrives at the correct place at the correct time.

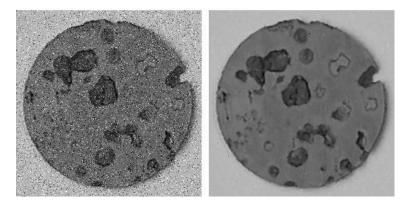

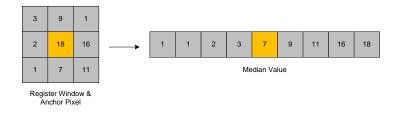

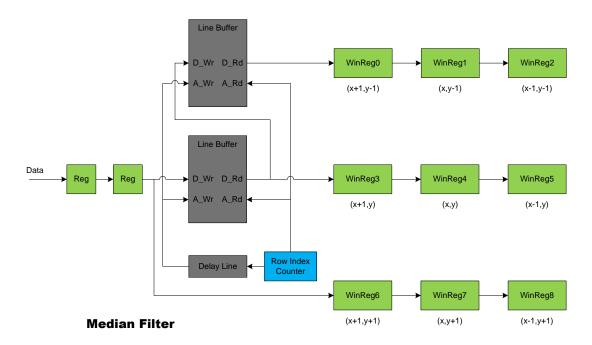

#### 3.3.1 Median Filter

The median filter is utilized to filter speckle noise such as 'salt and pepper' noise, as shown in Figure 3.10. If a  $3\times3$  window is applied, the abstract function of a median filter can be seen in Figure 3.11. The input data stream of median filter is luminance value from original stereo video in scan-line order, and after being processed the noise filtered luminance value comes out also in scan-line order synchronized with the input pixel rate. The left and right data flows are processed independently using two parallel median filters. The implementation of median filter should be divided into two main parts: one is building a window, the other is obtain the median value in this window.

Figure 3.9: Stereo matcher high level architecture

Figure 3.10: Noise removed by median filter

Figure 3.11: Median filter function

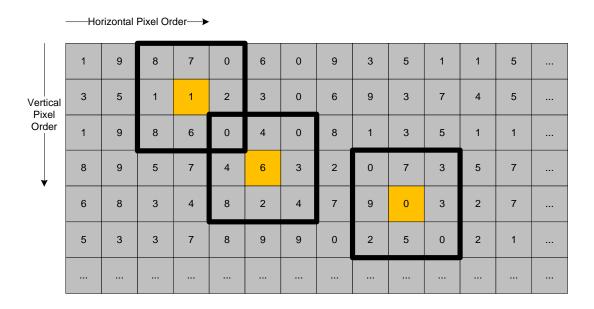

In this thesis work, the window size of our median filter is  $3\times3$ , and in order to keep a continuous data flow we use the sliding window pixel by pixel, as shown in Figure 3.12. The  $3\times3$  window slides over the complete frame and generates a new  $3\times3$  pixel

Figure 3.12: Sliding window in median filter in scan-line order

array in every valid pipeline cycle, and the boundary pixels are skipped over the sorting part therefore not filtered. It is necessary to utilize line buffers to save pixels in whole lines in order to construct the vertical part in a sliding window, as well as shift registers to build the horizontal part. The detailed RTL architecture is shown in Figure 3.13.

For building a  $3\times3$  window, 2 line buffers of on-chip ram and  $3\times3$  shift register array are used. The 2 line buffers are used to store 8 bits luminance of 2 lines corresponding to the top 2 lines of the window, and the depth of a line buffer depends on the maximum possible frame width (FW), e.g. the depth of the line buffer we used is 1024 so that any frame width lower than 1024 could be supported by this line buffer. The register array is adopted to save luminance value of the window for further use, where WinReg4 saves the anchor pixel. The registers near the input are for balancing the read latency of on-chip ram (2 cycles). The counter cyclically counts  $(0\sim FW-1)$  to read data out and write data in by providing read and write addresses for line buffers. The delay line

Figure 3.13: Median filter RTL architecture

is utilized for avoiding to overwrite the unread data in the same line buffer.

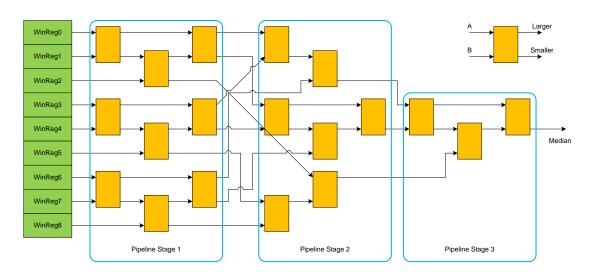

After building sliding window, the 9 luminance values in it go into a module to obtain their median value. The RTL architecture utilized by us is proposed by Vega-Rodriguez et al.[39], as shown in Figure 3.14. Totally 19 comparators 38 multiplexers

Figure 3.14: Median filter sorting

are used in this structure to sort the median value, and the basic segment shown in the top-right corner is composed of 1 comparator and 2 multiplexers for 2 unsigned inputs. The whole procedure is divided into 3 pipeline stages, which means this sorting segment has 3 cycles latency.

The total latency (the valid cycles used to obtain output from input) and memory usage for median filter are shown in Table 3.1. The latency is the valid cycles used to

|                 | Latency (cycles) | Memory usage (bits)             |

|-----------------|------------------|---------------------------------|

| Line Buffers    | FW               | $2 \times 2 \times FW \times 8$ |

| Input Registers | 2                | 0                               |

| Buffer Window   | 2                | 0                               |

| Sorting Array   | 2                | 0                               |

| Total           | FW + 6           | $32 \times FW$                  |

Table 3.1: Median filter latency and memory usage

obtain output from input for each block, while the memory usage includes the parallel median filter, and in the next blocks the memory usage calculated in the tables includes all the parallel segments, not the single one. The complete quantitative reports about the latencies and memory usage of every stereo matcher segments are listed in Chapter 4.

# 3.3.2 Census Transform & Support Region Builder

According to our concatenated census transform shown in Figure 3.8, the input luminance is transformed into a 30 bits vector considering vertical concatenation, which needs also a sliding window. The implementation of the census transform is also divided into two steps: one is constructing sliding window using line buffers and shift register array, the other is obtaining the census vectors by comparing neighboring pixels with vertical center anchor pixels according to the mini-census transform pattern and concatenating them. The first step uses the same architecture with median filter to build the sliding window, while the second step just applies comparators onto the register array obtained in the first step. Moreover, the first step shares the hardware resources with support region builder, because they share the same sliding window.

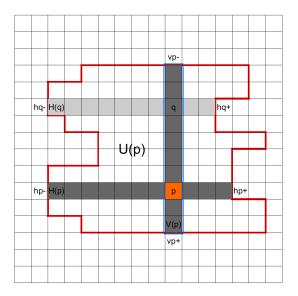

The support region builder is used to build a region with similar luminance for refinement, so it does not contribute to the dynamic programming. The key procedure of building a support region for an anchor pixel p is to determine its arm length in four directions, as shown in Figure 3.15. The intersection pixel of two orthogonal lines is called the anchor pixel, for which the support region is building. In the figure the anchor pixel p is the intersection of V(p) and H(p). Each anchor pixel has four direction arm lengths, i.e.  $\{h_p^-, h_p^+, v_p^-, v_p^+\}$  for p are the arm length of the left, right, up and down directions. The support region building depends on the luminance difference between the pixels in the two orthogonal lines and the anchor pixel, therefore the largest span in four directions is determined as:

$$r^* = \max_{r \in [1,L]} (r \prod_{i \in [1,r]} \delta(p, p_i))$$

(3.3)

In Equation 3.3,  $r^*$  is the largest span; pixel  $p_i = (x_p - i, y_p)$  and constant L is the maximum allowed arm length, which is a configurable parameter of support region

Figure 3.15: Support region of the anchor pixel p

builder;  $\delta(p, p_i)$  is the luminance difference between pixel p and  $p_i$  based on another configurable parameter  $\tau$ , which controls the luminance difference degree:

$$\delta(p_1, p_2) = \begin{cases} 1, & |Y(p_1) - Y(p_2)| \le \tau \\ 0, & otherwise \end{cases}$$

(3.4)

The parameter  $\tau$  has various performance implications according to the applications and image texture. According to the four arms provided, the total horizontal span and vertical span of anchor pixel p are:

$$\begin{cases}

H(p) = \{(x,y) \mid x \in [x_p - h_p^-, x_p + h_p^+], y = y_p\} \\

V(p) = \{(x,y) \mid x = x_p, y \in [y_p - v_p^-, y_p + v_p^+]\}

\end{cases}$$

(3.5)

Therefore, assembling all the horizontal arm lengths of the pixels on the vertical V(p) builds the complete support region U(p) of pixel p. The built arm lengths then passes dynamic programming by a bypass FIFO to prepare for voting.

The implementation of the support region builder is also divided into two main parts: one is the building window and the other is comparing candidates with the central pixel in the window to obtain the arm lengths.

The first window building step is similar with the window building of the median filter, and the number of required line buffers depends on the parameter L. The maximum arm length L needs  $2 \times L$  line buffers to provide a  $(2 \cdot L + 1) \times (2 \cdot L + 1)$  window, which is composed of shift register arrays. The optimized algorithm takes L = 15, so the hardware implementation has to select 30 line buffers to build a  $31 \times 31$  window which is used by both the support region builder and the census transform. The second step of these two segments are processed in parallel.

The second step is computing every  $\delta(p, p_i)$  in each direction in parallel by comparing every  $p_i$  with p simultaneously, and then passing the result into parallel priority encoders

to work out the largest span of each direction. The boundary problem occurs when the central pixel is near the boundary, e.g. the anchor pixel is in the last line of one frame. In such condition the window includes the pixels not belonging to the current frame, and the row counter and the column counter are adopted to avoid those incorrect pixels being processed.

The latency of census transform and support region builder is determined by the line buffers and operation pipeline stages, and the detailed value is listed in Table 3.2. The configurable parameters are listed in Table 3.3, and the effect of adjusting parameters is discussed together in Chapter 4.

|                        | Latency (cycles)      | Memory usage (bits)                      |

|------------------------|-----------------------|------------------------------------------|

| Line Buffers           | $L \times FW$         | $2 \times 2 \times L \times FW \times 8$ |

| Input Registers        | 2                     | 0                                        |

| Buffer Window          | L                     | 0                                        |

| Comparators + Encoders | 2                     | 0                                        |

| Total                  | $L \times FW + L + 4$ | $32 \times L \times FW$                  |

Table 3.2: Census transform and support region builder latency and memory usage

| Parameters | Current Value | Description                       |

|------------|---------------|-----------------------------------|

| L          | 15            | maximum support region arm length |

| au         | 15            | luminance difference threshold    |

Table 3.3: Census transform and support region builder configurable parameters

## 3.3.3 Reorder

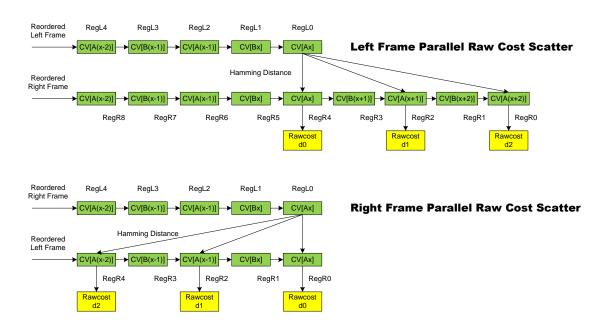

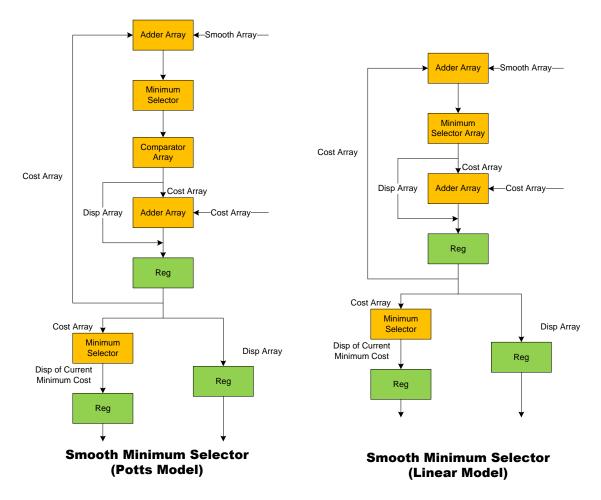

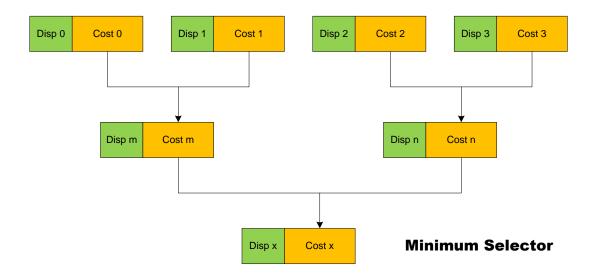

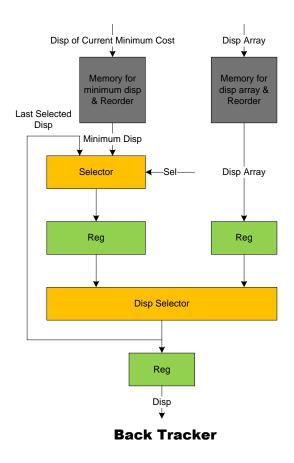

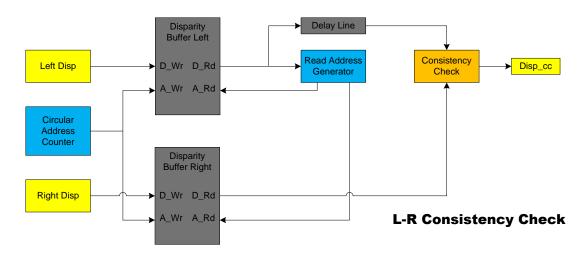

There is a loop for scan-line optimized dynamic programming, which cannot be unrolling to a parallel structure. The reorder kernel provides loop unrolling preparation if the critical path of that loop cannot meet the pixel rate frequency. It is optional because in most cases the maximum disparity is not too large and the pixel rate frequency is not too high. However in some special applications or conditions such as stereo matching for 1080p video with maximum disparity 256 or more, reorder is a necessary kernel performing static scheduling to improve the critical path with the cost of increasing on-chip memory utilization. In principal this loop unrolling is a space-time trade-off.