Delft University of Technology

## High temperature oxidation pre-treatment of textured c-Si wafers passivated by a-Si:H

Limodio, G.; D'Herouville, G.; Mazzarella, L.; Zhao, Y.; Yang, G.; Isabella, O.; Zeman, M.

**DOI**

[10.1016/j.mssp.2019.03.008](https://doi.org/10.1016/j.mssp.2019.03.008)

**Publication date**

2019

**Document Version**

Final published version

**Published in**

Materials Science in Semiconductor Processing

**Citation (APA)**

Limodio, G., D'Herouville, G., Mazzarella, L., Zhao, Y., Yang, G., Isabella, O., & Zeman, M. (2019). High temperature oxidation pre-treatment of textured c-Si wafers passivated by a-Si:H. *Materials Science in Semiconductor Processing*, 97, 67-70. <https://doi.org/10.1016/j.mssp.2019.03.008>

**Important note**

To cite this publication, please use the final published version (if applicable).

Please check the document version above.

**Copyright**

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**

Please contact us and provide details if you believe this document breaches copyrights.

We will remove access to the work immediately and investigate your claim.

***Green Open Access added to TU Delft Institutional Repository***

***'You share, we take care!' – Taverne project***

***<https://www.openaccess.nl/en/you-share-we-take-care>***

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# High temperature oxidation pre-treatment of textured c-Si wafers passivated by a-Si:H

G. Limodio\*, G. D'Herouville, L. Mazzarella, Y. Zhao, G. Yang, O. Isabella, M. Zeman

Delft University of Technology, Photovoltaic Material and Devices Group, P. O. Box 5031, 2600 GA, Delft, Netherlands

## ARTICLE INFO

### Keywords:

Thermal oxidation

Amorphous silicon passivation

Defect encapsulation

Silicon heterojunction solar cells

## ABSTRACT

This work shows an alternative surface cleaning method for c-Si wafers to replace the standard chemical procedures as RCA or  $\text{HNO}_3$  which involve hazardous chemicals or unstable processes. The method consists in a high-temperature oxidation treatment (HTO) performed in a classical tube furnace that incorporates organic and metal particles present on the c-Si surfaces in the growing  $\text{SiO}_2$  layer. The result is as a reliable pre-treatment method for obtaining less defective c-Si surfaces ready for solar cell fabrication after  $\text{SiO}_2$  removal. To test the surface passivation quality obtained with our alternative cleaning method, we grow amorphous silicon (a-Si:H) layers by plasma enhanced chemical vapor deposition on both sides of the c-Si wafer and systematically compare the effective carrier lifetime ( $\tau_{\text{eff}}$ ) and implied  $V_{\text{OC}}$  ( $iV_{\text{oc}}$ ) to the wafer treated with the standard cleaning in our laboratory. We optimize HTO treatment time reaching  $\tau_{\text{eff}}$  of  $\sim 6$  ms and  $iV_{\text{oc}}$  of 721 mV for the best sample. We ascribe the improved passivation quality using HTO to two concurrent factors. Firstly, the encapsulation of defects into  $\text{SiO}_2$  layer that is then etched prior a-Si:H deposition and secondly, to modification of the pyramids' morphology that facilitates the surface passivation. SEM pictures and reflection measurements support the latter hypothesis.

## 1. Introduction

In both semiconductor and photovoltaic industries, the cleaning of the crystalline silicon (c-Si) wafers to remove residues prior device fabrication is a crucial step. Therefore, wafers are dipped in chemical baths to remove organic and metallic impurities from the Si surfaces. The most commonly used procedure consists in a cycle of oxidation-etching steps in order to encapsulate all the surface contaminants into thin  $\text{SiO}_2$  grown on the c-Si surface and etch them away using highly diluted hydrofluoric acid (HF) [1–4]. This method is fundamental to achieve high performance devices. Indeed, a contamination-free Si surface will reduce defect density at interface, giving higher passivation quality than a not-treated surface [5,6]. This thin oxidation is often done via RCA cleaning [7] or ozone-based treatment [8]. Alternatively, the use of so-called nitric acid oxidation cycle (NAOC) results in comparable lower surface recombination velocity [9]. Both mentioned cleaning methods involve hazardous chemical substances that make the treatment costly owing to the disposal of the chemical waste, safety and environmental risks. Therefore, alternative cleaning methods might be attractive to reduce costs and simplify the fabrication of devices, such as c-Si solar cells. Attempts to reduce number of steps in the cleaning procedure were made by Lu et. al. [10], with promising values of

saturation current density ( $J_0$ ) below  $10 \text{ fA/cm}^2$ . Hydrogen plasma pre-treatment is eventually used to hydrogenate c-Si bulk [11]. Also, replacing the final HF etching step with hydrogen plasma etching was suggested by Mueller et. al. [12].

In this work, we propose a novel wafer cleaning method that consists in a single-step high temperature oxidation (HTO) followed by  $\text{SiO}_2$  etching in diluted HF solution. This method can be evidently deployed also in batch mode. As a result of volume expansion process, the HTO process consumes c-Si surface such that organic/metallic contaminants are encapsulated into  $\text{SiO}_2$  layer. Typically,  $\sim 50\%$  of the total  $\text{SiO}_2$  thickness is expanded into Si during thermal oxidation process [13]. Moreover, also impurity gettering is performed during this process. A similar approach has been developed in Ref. [14], with gettering and hydrogenation of the wafer through  $\text{SiN}_x$  layer and rapid thermal firing. We investigate the passivation quality of double-side textured wafers treated with HTO for variable treatment time by passivating the c-Si surfaces with a-Si:H layers growth via plasma enhanced chemical vapor deposition (PECVD). These a-Si:H layers provide both chemical and field-effect passivation. We compare the HTO-treated samples to a wafer treated with the standard wet-chemical oxidation NAOC method. The better passivation quality obtained with the optimized HTO treatment time is related also to morphology

\* Corresponding author.

E-mail address: [G.Limodio@tudelft.nl](mailto:G.Limodio@tudelft.nl) (G. Limodio).

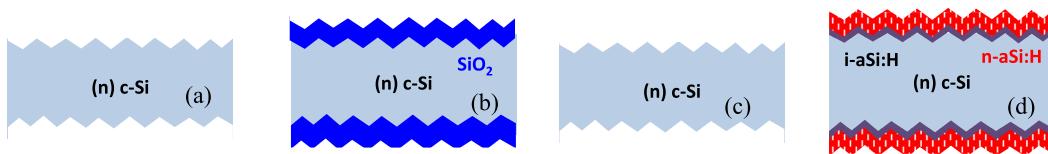

**Fig. 1.** Sample fabrication steps: (a) Chemical texturing of the wafer; (b) Thermal oxidation of double sided textured wafer; (c) Etching of SiO<sub>2</sub> in HF; (d) i/n a-Si:H stack PECVD deposition as a passivation layer.

modifications of the random pyramids that additionally facilitate the growth of high quality a-Si:H layer.

## 2. Experimental details

For symmetric samples fabrication, we use 4 inches n-type float zone (FZ) silicon wafers (c-Si) with polished <100> oriented surfaces, a resistivity of 2.5 Ω cm and initial thickness of 280 μm. The c-Si substrates are cleaned in a nitric acid (99% HNO<sub>3</sub>) bath for 10 min at 20 °C, followed by a dip in 69.5% HNO<sub>3</sub> at 110 °C to remove organic residuals and metallic contaminations, respectively. Samples are then chemically textured in a solution containing TMAH, AlkaText® and H<sub>2</sub>O to obtain random pyramids with <111> oriented facets on both sides of the wafer (Fig. 1 (a)).

Then, the wafers are subjected to HTO process in a tube furnace (Tempress Systems) at a temperature of 1050 °C in O<sub>2</sub> atmosphere. The treatment time is varied between 20 and 230 min that corresponds to a resulting SiO<sub>2</sub> film of from 40 to 200 nm-thick (Fig. 1 (b)). The temperature is reached with a ramp of 10 °C/min and the O<sub>2</sub> flow is set at 3 slm in a dry environment. After oxidation, we remove the SiO<sub>2</sub> layer by dipping the sample in 0.55% HF (step (c) in Fig. 1) with an etching rate of ~1 nm/m for the necessary time to make the silicon wafer surface hydrophobic. Instead, the reference wafer is treated with the so-called nitric acid oxidation cycle (NAOC) method, consisting in HNO<sub>3</sub> 99%, subsequent HNO<sub>3</sub> 69.5% and HF step, as described in Ref. [15], that we repeat three times [9]. Finally, the samples are loaded into the PECVD reactor where both sides of the c-Si substrate are covered by a stack of intrinsic and phosphorous doped a-Si:H layers with a thickness of 4.5 and 6 nm, respectively (step (d) in Fig. 1). Afterwards, the samples are annealed at 190 °C for 30 min to enhance passivation quality [16]. Quasi-steady-state photoconductance (QSSPC) lifetime measurements [17] are performed on the fabricated samples using a Sinton Instruments WCT-120 carrier lifetime setup. Effective lifetime ( $\tau_{\text{eff}}$ ), implied open-circuit voltage ( $iV_{\text{OC}}$ ) and recombination current density ( $J_0$ ) are extracted from the measured curves. Furthermore, the as-textured and the optimized HTO treated samples are further characterized by cross-sectional scanning electron microscopy (SEM XL50 Philips with acceleration voltage of 5 kV) and optical reflectance is carried out using a Pelkin Elmer Lambda UV-VIS near-infrared spectrophotometer.

## 3. Results and discussion

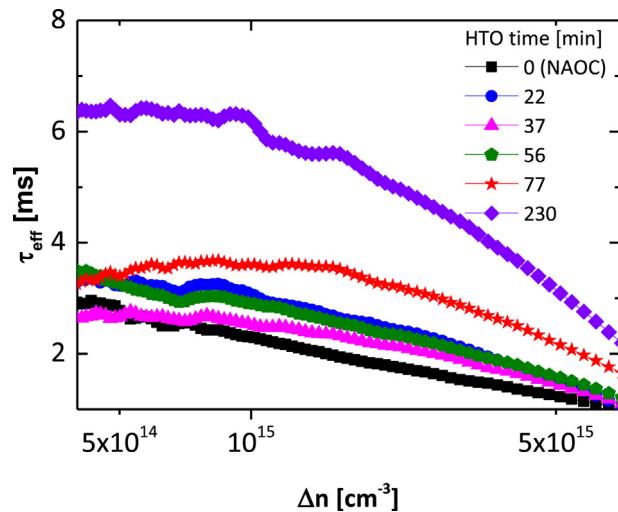

Fig. 2 shows the minority carrier lifetime against injection level for double-sided textured wafers passivated by i/n a-Si:H stack pre-treated with variable HTO time and compared to the reference pre-treated with NAOC. All the results shown here are after annealing at 190 °C for 30 min to improve chemical passivation [18]. The reference sample (black curve in Fig. 2) shows  $\tau_{\text{eff}}$  of ~2 ms extracted at  $10^{15} \text{ cm}^{-3}$  injection level. By increasing the HTO time, the measured lifetime progressively increases as compared to the value of the reference. For the shorter HTO times tested (from 22 to 56 min), the passivation quality improvement is limited only to the low injection level. We observe a slight decrease in lifetime of around 200 μs at low injection level when 37 and 56 min HTO treatment are applied. This is most likely due to different pre-conditioning of the PECVD chamber since the samples

**Fig. 2.** Minority carrier lifetime versus carrier density of double sided textured wafers passivated by 4.5/6 nm-thick a-Si:H for a variable HTO treatment time. The curves are measured after a post-deposition annealing at 190 °C for 30 min. Reference samples cleaned with NAOC is also added for comparison.

have been processed in different time slots. It is remarkable how similar values of lifetime at high injection level are achieved in the NAOC and 37 and 56 min HTO cases. When a sample is oxidized for 77 min, corresponding to ~100 nm-thick SiO<sub>2</sub>, lifetime improves significantly both in high and low injection level with  $\tau_{\text{eff}}$  of ~4 ms which doubles the value measured for NAOC reference.

By increasing the HTO time to 230 min (~200 nm-thick SiO<sub>2</sub> layer) the entire curve shifts up with  $\tau_{\text{eff}}$  of ~6 ms at  $10^{15} \text{ cm}^{-3}$  injection level.

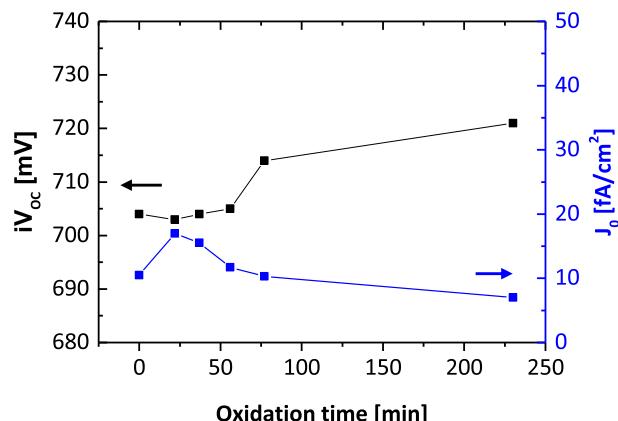

Fig. 3 displays the implied  $V_{\text{OC}}$  and  $J_0$  extracted from the curves in Fig. 2 as function of the HTO treatment time. We clearly note the effect described above with a progressive increase in  $iV_{\text{OC}}$  (i.e. surface

**Fig. 3.** Implied  $V_{\text{OC}}$  and saturation current density ( $J_0$ ) of double-sided textured wafers passivated by 4.5/6-nm thick i/n a-Si:H with NAOC or thermal SiO<sub>2</sub> pre-treatment as function of the oxidation time.

chemical passivation) with increasing thickness of the  $\text{SiO}_2$  layer. For the NAOC reference sample,  $iV_{\text{OC}}$  is 705 mV, while the highest  $iV_{\text{OC}}$  of 721 mV is measured for the sample treated with 230 min of HTO. The opposite trend is noted for  $J_0$ . For the NAOC reference,  $J_0$  is 12 fA/cm<sup>2</sup>, while for the sample pre-treated with 230 min of oxidation,  $J_0$  decreases to 7 fA/cm<sup>2</sup>.

We can conclude that the passivation quality of i/n a-Si:H stack is then affected by HTO treatment time and therefore by the grown  $\text{SiO}_2$  thickness. We tentatively explain the improved surface passivation obtained with HTO by the encapsulation of surface contaminants present on the Si surface within thermal  $\text{SiO}_2$ , which partially expands into the Si bulk. All these surface contaminants are then etched away by removing the  $\text{SiO}_2$  in HF solution. This results in a *clean* c-Si surface ready for passivation by a-Si:H stack. Increasing the HTO time,  $\text{SiO}_2$  goes deeper into the Si bulk and more impurities are removed from Si surface [19]. An enriched chemical passivation is achieved by  $J_0 < 10 \text{ fA/cm}^2$ . This indicates that more surface contaminants have been removed from the surface than in the NAOC case.

It is noteworthy to remark how the proposed HTO process is capable of improving performances in FZ wafers. By transferring this method to industrially-relevant Czochralski wafers (CZ), the encapsulation of surface impurities into  $\text{SiO}_2$  and stabilization of bulk lifetime by the so-called *tabula rasa* treatment [20] can be achieved at the same time.

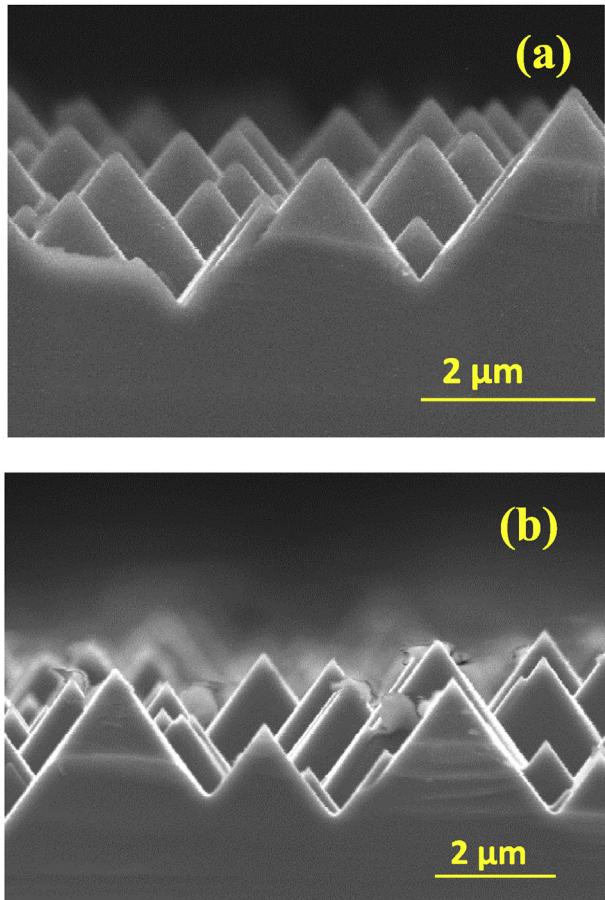

To further analyze the effect of HTO on the c-Si wafer surface, we rely on cross-sectional scanning electron microscopy (SEM). Fig. 4 (a) shows a SEM image of an as-textured wafer, while Fig. 4 (b) is the image taken after HTO treatment (230 min) and subsequent etching of  $\text{SiO}_2$ . The scale is slightly different due to different focus obtained to have optimal images. The reference textured wafer in Fig. 4 (a) has

**Fig. 4.** Cross-sectional Scanning Electron Microscopy (SEM) of textured wafers (a) after texturing and (b) 230 min of HTO treatment. Both images are taken after etching the  $\text{SiO}_2$  layer.

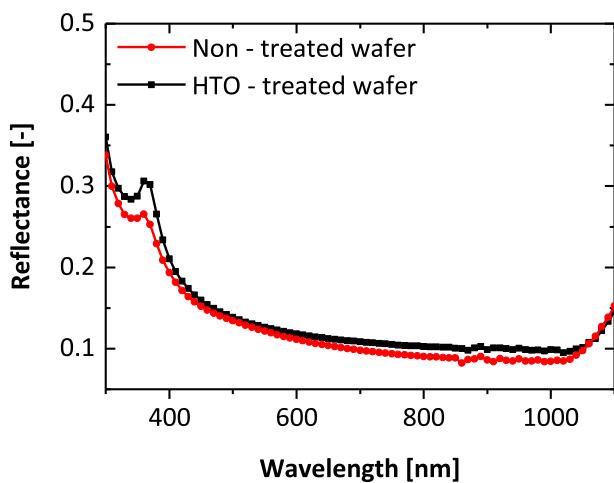

**Fig. 5.** Measured reflectance of reference (red line) and HTO-treated (black line) wafers.

steep valleys of the pyramids. On the other hand, the HTO-treated wafer has rounded valleys; therefore, the amount of defects is decreased. In general, the more the tip or the valley of a textured wafer is rounded, the less is the structural defect density associated to it [21]. Therefore, it is easier to obtain enriched chemical passivation. In particular, the more the valley is rounded, the more it is unlikely to have epitaxial growth of a-Si [22]. This concurs to the improved passivation properties. The images reveal residuals that are the results of a cut in 6-cm wide slab to fit the cross-sectional stage of SEM. The drawback of this procedure stays in the slightly reduced reflectivity due to not perfect light scattering and reduced optical path length in the c-Si wafer [23]. Fig. 5 shows the reflectance exhibited by the same wafers shown in Fig. 4. In the whole wavelength range, the reflectance is lower for the HTO-treated wafer. Therefore, light scattering is more efficient in the reference sample than the HTO-treated one. We can conclude that, although the pyramids' size is the same in both textured and HTO-treated cases, the pyramids' valleys are slightly more rounded in the HTO-treated case compared to as-textured wafer. This issue can be nevertheless overcome by using transparent conducting oxide layer or anti-reflective dielectrics, such as  $\text{MgF}_2$  or  $\text{SiO}_x$  [24].

#### 4. Conclusion

In conclusion, we investigate an alternative cleaning method suitable for textured c-Si wafers that does not involve the use of hazardous chemicals. This method consists in a high-temperature oxidation (HTO) treatment in a conventional furnace followed by an etching step HF solution prior further processing the substrate for device fabrication. To measure the passivation quality, the textured c-Si surfaces are covered with a-Si:H layers deposited by PECVD. Since the HTO encapsulates Si surface impurities, we perform a series of HTO treatment time to investigate the impact on chemical passivation. After HF etching, the wafers are immediately transferred to PECVD chamber to deposit 4.5/6 nm-thick i/n a-Si:H layer. These samples have been characterized using QSSPC method and compared to a sample equally passivated but pre-treated with 3 cycles of thin wet-oxidation and HF etching (NAOC). This analysis is carried out by passivating the textured wafer by 4.5/6 nm-thick i/n a-Si:H, but the conclusions drawn are the same for other a-Si:H layer thicknesses. We find out that increasing oxidation time, i.e. thermal  $\text{SiO}_2$  thickness, both carrier lifetime and implied  $V_{\text{OC}}$  progressively improved and exceeded the values measured on the reference sample treated with NAOC. The best HTO treatment time is found at 230 min with  $\tau_{\text{eff}}$  and  $iV_{\text{OC}}$  of 6 ms and 721 mV, respectively. Since the passivation layers stack is kept constant for all the samples fabricated, we can conclude that the improvement in chemical passivation are to

be ascribed to the removal of impurities from the c-Si surface and to the formation of rounded valleys after etching the thermally-grown  $\text{SiO}_2$ , as shown by cross-sectional SEM images. It is to remark that HTO process can be applicable also to planar wafers. The drawn conclusions are the same except for less defect density of the polished c-Si interface compared to textured one. This method could be further engineered and optimized for batch process compatible with mass production. Moreover, this method is also beneficial for industrial CZ wafers, since a *tabula rasa* could be performed at the same time with encapsulation of defects.

## Acknowledgment

The authors would like to thank ADEM program for funding this research and Martijn Tijssen for his help with PECVD reactor.

## References

- [1] W. Kern, D.A. Puotinen, *RCA Rev.* 31 (1970) 187.

- [2] Werner Kern, *J. Electrochem. Soc.* 137 (No. 6) (June 1990).

- [3] K. Sakamoto, K. Nishi, F. Ichikawa, S. Ushio, *J. Appl. Phys.* 61 (4) (1987) 1553–1555.

- [4] J. Haschke, et al., *AIP Conference Proceedings* 1999 (2018) 030001, <https://doi.org/10.1063/1.5049262>.

- [5] A. Froitzheim, K. Brendel, L. Elstner, W. Fuhs, K. Kliefoth, M. Schmidt, *J. Non-Cryst. Solids* 299–302 (2002) 663–667.

- [6] H. Angermann, *Appl. Surf. Sci.* 254 (Issue 24) (2008) 8067–8074.

- [7] L. Zhang, W. Liu, R. Chen, L. Jinning, F. Meng, Z. Liu, K. Toshima, A. Ota, T. Yoshihara, 2016 IEEE 43rd Photovoltaic Specialists Conference (PVSC), Portland, OR, (2016), pp. 0743–0746, <https://doi.org/10.1109/PVSC.2016.7749701>.

- [8] A. Danel, F. Jay, S. Harrison, C. Arnal, G. D'Alonzo, N. Nguyen, A.S. Ozanne, P.E. Hickel, D. Muñoz, P.J. Ribeyron, Proc. 26th European Photovoltaic Solar Energy Conference and Exhibition, Hamburg, Germany, (2011).

- [9] D. Deligiannis, S. Alivizatos, A. Ingenito, D. Zhang, M. van Sebille, R.A.C.M.M. van Swaaij, M. Zeman, *Energy Procedia* 55 (2014) 197–202.

- [10] X. Lu, M. Koppes, P.C. P Bronsveld, *AIP Conference Proceedings* 1999, (2018), p. 050005 <https://doi.org/10.1063/1.5049295>.

- [11] Fengyou Wang, Xiaodan Zhang, Liguo Wang, Yanjian Jiang, Changchun Wei, Jian Sun, Ying Zhao, *ACS Appl. Mater. Interfaces* 6 (17) (2014) 15098–15104, <https://doi.org/10.1021/am5031837>.

- [12] T. Mueller, M. Tang, J. Ge, J. Wong, 2015 IEEE 42nd Photovoltaic Specialist Conference (PVSC), New Orleans, LA, (2015), pp. 1–4, <https://doi.org/10.1109/PVSC.2015.7356324>.

- [13] B.E. Deal, A.S. Grove, *J. Appl. Phys.* 36 (12) (1965) 3770–3778 <https://doi.org/10.1063/1.1713945>.

- [14] Brett Hallam, Daniel Chen, Jianwei Shi, Einhaus Roland, Zachary C. Holman, Stuart Wenham, *Solar RRL Volume 2 (Issue 2)* (2018), <https://doi.org/10.1002/solr.201700221>.

- [15] G. Yang, A. Ingenito, N. v. Hameren, O. Isabella, M. Zeman, *Appl. Phys. Lett.* 108 (2016).

- [16] J.W.A. Schüttauf, C.H.M. van der Werf, M. Kielen, W.G.J.H.M. van Sark, J.K. Rath, R.E.I. Schropp, *J. Non-Cryst. Solids* Volume 358 (Issue 17) (1 September 2012) 2245–2248 <https://doi.org/10.1016/j.jnoncrysol.2011.12.063>.

- [17] R. Sinton, A. Cuevas, M. Stuckings, *Conference Record of the IEEE Photovoltaic Specialists Conference, 1996*.

- [18] A. Illiberi, K. Sharma, M. Creatore, M.C.M. van de Sanden, *phys. stat. sol. (RRL)* 4 (2010) 172–174, <https://doi.org/10.1002/pssr.201004139>.

- [19] J. Dabrowski, H.-J. Mussig, V. Zavodinsky, R. Baierle, M.J. Caldas, *Phys. Rev. B* VOLUME 65 (2002) 245305, <https://doi.org/10.1103/PhysRevB.65.245305>.

- [20] V. LaSalvia, M.A. Jensen, A. Youssef, W. Nemeth, M. Page, T. Buonassisi, P. Stradins, 2016 IEEE 43rd Photovoltaic Specialists Conference (PVSC), Portland, OR, (2016), pp. 1047–1050, <https://doi.org/10.1109/PVSC.2016.7749771>.

- [21] A. Moldovan, T. Dannenberg, J. Temmler, L. Kroely, M. Zimmer, J. Rentscha, *Energy Procedia* 92 (2016) 374–380, <https://doi.org/10.1016/j.egypro.2016.07.115>.

- [22] S. Olibet, C. Monachon, A. Hessler-Wyser, E. Vallat-Sauvain, S. De Wolf, L. Fesquet, J. Damon-Lacoste, C. Ballif, 23rd European Photovoltaic Solar Energy Conference, 1–5 September, (2008) Valencia, Spain.

- [23] H.-Y. Gong, Haibin Huang, Lang Zhou, Rengong Jingti Xuebao/Journal of Synthetic Crystals 44 (2015) 913–917.

- [24] D. Zhang, I.A. Diddya, R. Santbergen, R.A.C.M.M. van Swaaij, P. Bronsveld, M. Zeman, J.A.M. van Roosmalen, A.W. Weeber, *Sol. Energy Mater. Sol. Cell.* 117 (2013) 132–138 <https://doi.org/10.1016/j.solmat.2013.05.044>.