### A 28W -108.9dB/-102.2dB THD/THD+N Hybrid $\Delta\Sigma$ -PWM Class-D Audio Amplifier with 91% Peak Efficiency and Reduced EMI Emission

Karmakar, Shoubhik; Zhang, Huajun; Van Veldhoven, Robert; Breems, Lucien; Berkhout, Marco; Fan, Qinwen; Makinwa, Kofi A.A.

DOI

10.1109/ISSCC19947.2020.9063001

Publication date 2020

**Document Version**Final published version

Published in

2020 IEEE International Solid-State Circuits Conference, ISSCC 2020

Citation (APA)

Karmakar, S., Zhang, H., Van Veldhoven, R., Breems, L., Berkhout, M., Fan, Q., & Makinwa, K. A. A. (2020). A 28W -108.9dB/-102.2dB THD/THD+N Hybrid ΔΣ-PWM Class-D Audio Amplifier with 91% Peak Efficiency and Reduced EMI Emission. In *2020 IEEE International Solid-State Circuits Conference, ISSCC 2020* (pp. 350-352). Article 9063001 (Digest of Technical Papers - IEEE International Solid-State Circuits Conference; Vol. 2020-February). IEEE. https://doi.org/10.1109/ISSCC19947.2020.9063001

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## 23.4 A 28W -108.9dB/-102.2dB THD/THD+N Hybrid $\Delta\Sigma$ -PWM Class-D Audio Amplifier with 91% Peak Efficiency and Reduced EMI Emission

Shoubhik Karmakar<sup>1</sup>, Huajun Zhang<sup>1</sup>, Robert Van Veldhoven<sup>2</sup>, Lucien Breems<sup>2</sup>, Marco Berkhout<sup>3</sup>, Qinwen Fan<sup>1</sup>, Kofi A.A. Makinwa<sup>1</sup>

<sup>1</sup>Delft University of Technology, Delft, The Netherlands <sup>2</sup>NXP Semiconductors, Eindhoven, The Netherlands <sup>3</sup>NXP Semiconductors, Nijmegen, The Netherlands

Class-D amplifiers are often used in high-power audio applications due to their high power efficiency. They typically employ pulse-width modulation (PWM) at a fixed carrier frequency, which may cause electromagnetic interference (EMI). Setting this frequency (f<sub>PWM</sub>) below the AM band (535 to 1605kHz) helps mitigate this, but its harmonics still contain substantial energy and must be filtered out by bulky LC filters with low cut-off frequencies (f<sub>C</sub> = 20 to 40kHz), significantly increasing system cost and size. Stability considerations also constrain the amplifier's unity-gain frequency to be <  $f_{PWM}/\pi$  [1], compromising the audio-band loop gain required to suppress output-stage nonlinearity. Setting f<sub>PWM</sub> above the AM band helps increase f<sub>c</sub> and allows a higher loop gain [2]. However, this results in narrower pulses at higher power levels (higher modulation index), which cannot be faithfully produced by the output stage, thus exacerbating its non-linearity. Delta-sigma modulation ( $\Delta\Sigma M$ ) has fixed pulse widths and does not suffer from these narrow-pulse artefacts. However, the out-of-band noise of 1bit modulators then requires larger LC filters. Moreover, high-order loop filters must be used to achieve sufficient SQNR, which then require additional techniques to maintain stability as the modulation range approaches 100% [3].

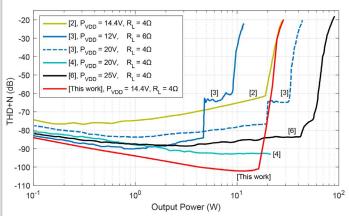

In this work, a  $3^{\circ\prime}$ -order 17-level hybrid  $\Delta\Sigma$ -PWM Class-D amplifier is proposed. Its hybrid modulation scheme allows a high  $f_{PWM}$  to be combined with fixed pulse widths, while the use of multilevel quantization significantly reduces its out-of-band noise and increases its stable modulation range. As a result, the proposed Class-D amplifier meets the CISPR-25 average EMI mask (150kHz to 30MHz) for automotive applications with 12dB margin, while using a relaxed LC filter ( $f_C$  = 100kHz). Overall, it achieves state-of-the-art performance compared to prior art shown in the Figure 23.4.6, with -102.2dB peak THD+N, -108.9dB peak THD and 109dB dynamic range (A-weighted), while obtaining a peak efficiency of 91% at its maximum output power of 28W (@10% THD).

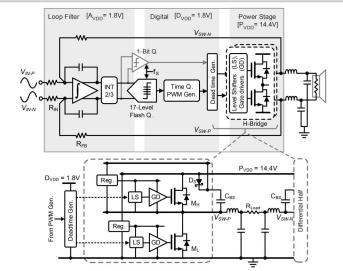

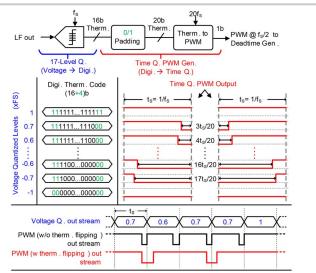

Figure 23.4.1 shows the system diagram of the proposed fully differential Class-D amplifier. It consists of a 3rd-order loop filter, a 17-level flash quantizer, a PWM generator, a high-voltage (HV) power stage and a resistive feedback network that defines a closed-loop gain of 8. The key block of the system is the PWM generator, which converts the output of the multi-level quantizer into the two-level signals needed to drive the output stage. As shown in Fig. 23.4.2, the various voltage levels output by the quantizer are mapped to a set of time-quantized PWM waveforms with the same average value [5].

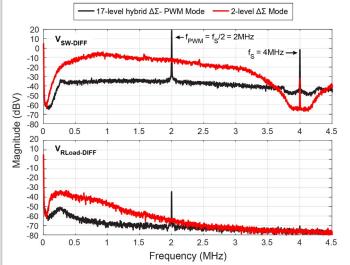

While this mapping results in less quantization noise than a 1bit modulator, it also results in a strong tone at the sampling frequency f<sub>s</sub>. Alternate PWM pulses are flipped in the time domain (from the end to the beginning of the period) to avoid a transition and smoothly follow on from the preceding pulse shape, beneficially reducing switching losses by half and doubling the minimum pulse width applied to the output stage. As pulse-flipping also shifts the main tone from f<sub>s</sub> to f<sub>s</sub>/2, setting  $f_S = 4MHz$  positions the main tone at 2MHz, avoiding the AM band with sufficient margin. In this work, a normalized time-quantization step of 0.1FS is used, resulting in 21 bipolar voltage and time steps distributed between (and including) ±1FS. Since narrow pulses will degrade linearity, the levels corresponding to ±{0.8, 0.9} FS are not used, reducing the number of discrete steps to 17. This results in a minimum pulse width of 75ns, comfortably wider than the minimum pulse width (~16ns) that the output stage can actually produce. The PWM generator is realized by on-chip digital logic. It uses an 80MHz (20×f<sub>s</sub>) master clock to serialize the 16bit thermometer code of the flash quantizer (or its flipped version), after appropriately adding 0/1 padding bits corresponding to the unused levels.

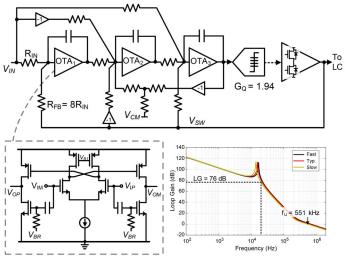

As shown in Fig. 23.4.3, high loop gain is achieved by using a 3<sup>rd</sup>-order loop filter with optimized NTF zeros. Input feedforward paths eliminate the signal content in the outputs of the first two integrators, relaxing the linearity requirements on the associated OTAs. The coefficients were optimized to achieve an SQNR of 123dB and avoid excessive noise in the AM band. To ensure robustness against process variation, which may introduce some 30% spread in its coefficients, the loop-filter capacitors are 2bit trimmable. For high GBW, the integrators are built

around two-stage feedforward OTAs which together draw 1.8mA from a 1.8V supply. This combination of multilevel quantization together with a high  $f_s$  results in a loop gain of >76dB (26dB higher than [6]) in the audio band irrespective of process spread, thus ensuring high linearity.

The fully differential H-bridge output stage is shown in Fig. 23.4.1. It consists of four identical N-LDMOS devices ( $M_{\rm H}$  and  $M_{\rm L}$ ) with an  $R_{\rm ON}$  of ~100m $\Omega$ , which results in >90% peak power efficiency. Schottky diodes ( $D_{\rm S}$ ) and off-chip bootstrap capacitors ( $C_{\rm BS}$ ) are used to derive the boosted supply voltages (~14V with respect to  $V_{\rm SW}$ ) of the  $M_{\rm H}$  gate drivers. As the maximum  $V_{\rm GS}$  of  $M_{\rm H}$  and  $M_{\rm L}$  is 5V, on-chip voltage regulators are used to create local 5V supplies relative to the sources of  $M_{\rm H}$  and  $M_{\rm L}$ , and power the respective gate drivers [7]. Level shifters transmit the control signals from the low-voltage digital domain ( $D_{\rm VDD}$  = 1.8V) to the HV domains. AD modulation is used to drive the two halves of the H-bridge, as the resulting outputs are then 180 degrees phase apart, producing significantly lower common-mode (CM) EMI than BD modulation [6]. In general, CM EMI is more problematic as it cannot be suppressed by using differential cabling.

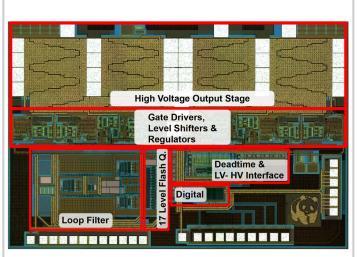

The prototype IC, shown in Fig. 23.4.7, was fabricated in a 0.18 $\mu$ m BCD process and occupies an active area of 4.8mm². An external LC filter (L=2.2 $\mu$ H, C=1.15 $\mu$ F) is used to suppress out-of-band noise.

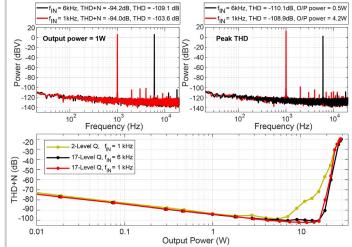

Figure 23.4.4 shows the in-band audio performance of the proposed Class-D amplifier with a 14.4V supply ( $P_{\text{VDD}})$  and a  $4\Omega$  load. When idling, it draws 17mAfrom P<sub>VDD</sub>, which is dominated by the switching loss of the HV output stage. At 1W output power, a THD+N of -94.0dB and -94.2dB is achieved, at input frequencies of 1kHz and 6kHz, respectively. With respect to the state-of-the-art [4], this is an improvement of 6.1dB for a  $4\Omega$  load. For the same output power and input frequencies, the CDA achieves a THD of -103.6dB and -109.1dB, respectively. The proposed Class-D amplifier can deliver 28W peak power at 10% THD and has an efficiency of 91%. Over its full power range, it achieves a peak THD+N of -102.2dB and -100.5dB, for input frequencies of 1kHz and 6kHz, respectively. Similarly, it achieves a peak THD of -108.9dB and -110.1dB, for input frequencies of 1kHz and 6kHz, respectively. For comparison, a 1bit quantizer was also implemented (Fig. 23.4.1). In this case, the THD+N performance starts to deteriorate at significantly lower power levels (~8W), indicating the onset of modulator overload; while the 17-level Class-D amplifier maintains <-80dB THD+N  $\,$ up to ~20W. This is comparable with [4], but is achieved with significantly lower supply voltage.

Figure 23.4.5 shows the measured CISPR-25 average radiated emission in the frequency range of 150kHz to 30MHz. Compared to the use of a 1bit quantizer, the 17-level technique results in an extra  $\sim$ 10 dB margin in the AM band. The reduced out-of-band energy is converted into tones above the AM band.

Figure 23.4.6 summarizes the performance of the Class-D amplifier and compares it with other state-of-the-art designs with similar supplies (12V to 25V) and loads (4 $\Omega$  to 8 $\Omega$ ). It achieves the highest THD (1W 0/P power) and peak THD+N, as well as the highest power efficiency. Thanks to the  $\Delta\Sigma M$ -PWM modulation technique, the Class-D amplifier is able to achieve high THD(+N) levels even at high output power levels, while satisfying the CISPR-25 average EMI mask using a relaxed LC filter with a 100kHz cut-off frequency.

Acknowledgements: The authors would like to thank Z. Chang, L. Pakula and R. van Puffelen from Delft University of Technology, Delft, The Netherlands, and Q. Sandifort from NXP, Nijmegen, The Netherlands, for their technical help and assistance with PCB assembly, tests and measurements.

#### References:

- [1] M. Berkhout, "An Integrated 200-W Class-D Audio Amplifier," *IEEE JSSC*, vol. 38, no. 7, pp. 1198-1206, July 2003.

- [2] Texas Instruments, TAS6424-Q1 Datasheet, Oct. 2017 [Online]. Available: http://www.ti.com/lit/ds/symlink/tas6424-q1.pdf

- [3] E. Gaalaas et al., "Integrated Stereo  $\Delta\Sigma$  Class D Amplifier," *IEEE JSSC*, vol. 40, no. 12, pp. 2388-2397, Dec. 2005.

- [4] E. Cope et al., "A 2×20W 0.0013% THD+N Class-D Audio Amplifier with Consistent Performance up to Maximum Power Level," *ISSCC*, pp. 56-57, Feb. 2018.

- [5] M. Kashmiri et al., "A Multi-bit Cascaded Sigma-Delta Modulator with an Oversampled Single-bit DAC," *IEEE ICECS*, pp. 49-52, Dec. 2009.

- [6] D. Schinkel et al., "A Multiphase Class-D Automotive Audio Amplifier with Integrated Low-Latency ADCs for Digitized Feedback After the Output Filter," *IEEE JSSC*, vol. 52, no. 12, pp. 3181–3193, Dec. 2017.

- [7] H. Ma et al., "Design and Analysis of a High-Efficiency High-Voltage Class-D Power Output Stage," *IEEE JSSC*, vol. 49, no. 7, pp. 1514–1524, July 2014.

Figure 23.4.1: Simplified block diagram of the fully differential CDA (Top) and simplified half-circuit schematic of the output power stage (Bottom).

Figure 23.4.2: The 17-level voltage-to-time-domain quantizer PWM conversion (Top) and typical time-domain output streams (Bottom).

Figure 23.4.3: Simplified single-ended schematic of the loop filter (Top) and loop-gain plot after trimming (Bottom).

Figure 23.4.4: Measured performance of the CDA for  $P_{VDD}$  = 14.4V and a  $4\Omega$  load: FFTs at 1W output power (Top-Left); FFTs at peak THD performance (Top-Right); THD+N across output power (Bottom).

| 25   |           |    |

|------|-----------|----|

| - V  | monnoholy |    |

| 5    |           |    |

| 0    |           |    |

| 0.15 | 1         | 10 |

Figure 23.4.5: Radiated emission of the fully functioning CDA across frequency.

| Parameter                                          | [2]                  | [:                 | 3]       | [4                   | 4]       | [6]                  | This work              |

|----------------------------------------------------|----------------------|--------------------|----------|----------------------|----------|----------------------|------------------------|

| Modulation<br>Scheme                               | PWM<br>(Digital In.) | ΔΣ<br>(Analog In.) |          | PWM<br>(Digital In.) |          | PWM<br>(Digital In.) | ΔΣ-PWM<br>(Analog In.) |

| Supply                                             | 14.4V                | 12V                | 20V      |                      | 20V      | 25V                  | 14.4\                  |

| Load                                               | 4Ω                   | 6Ω                 | 4Ω       | 8Ω                   | 4Ω       | 4Ω                   | 40                     |

| THD+N                                              | 0.02%                | 0.0032%*           | 0.0065%* | 0.0029%              | 0.004%*  | 0.004%               | 0.002%                 |

| (f <sub>IN</sub> =1kHz, P <sub>o</sub> =1W)        | -74.0dB              | -90dB              | -83.7dB  | -90.7dB              | -87.9dB  | -87.9dB              | -94.0dE                |

| THD<br>(f <sub>IN</sub> =1kHz, P <sub>O</sub> =1W) | -                    | 0.0012%<br>-98.4dB | -        | -                    | -        | -                    | 0.00066%<br>-103.6dE   |

| Peak THD+N                                         | 0.015%*              | 0.0032%*           | 0.0065%* | 0.0013%              | 0.0021%* | 0.0037%*             | 0.00078%               |

| (f <sub>IN</sub> = 1kHz)                           | -76.5dB              | -90.0dB            | -83.7dB  | -97.7dB              | -93.6dB  | -88.6dB              | -102.2dE               |

| P <sub>O-MAX</sub> (10% THD)                       | 27W                  | 10W                | 40W      | 20W                  | 20W      | 80W                  | 28W                    |

| DR (A wt.)                                         | -                    | 106dB              | -        | 115.5dB              | -        | 115dB                | 109dE                  |

| O/P Noise (A wt.)                                  | 42uVrms              | 50uVrms            | -        |                      | 20uVrms  | 34uVrms              | 31uVrm:                |

| Efficiency                                         | 86%                  | 88%                |          |                      | 90%      | >90%                 | 91%                    |

| SW Freq                                            | 2.1MHz               | < 0.7MHz           |          |                      | 0.4MHz   | 0.5MHz               | 2.0MH                  |

| Comp. Count [L, C]                                 | 2L, 2C               |                    | 2L, 2C   |                      | 2L, 2C   | 4L, 2C               | 2L, 20                 |

| / Values                                           | 3.3µH, 1uF           | 15μH, 1uF          |          |                      | -        | -                    | 2.2μH, 1.1ul           |

| LC filter cutoff                                   | 88kHz                | 41kHz              |          | -                    |          | 40kHz*               | 100kH:                 |

| Process                                            | -                    | 600n BCD           |          | 180n BCD             |          | 140n BCD             | 180n BCE               |

<sup>\*</sup> Values taken from plots

Figure 23.4.6: Performance summary and comparison with state-of-the-art CDAs.

### **ISSCC 2020 PAPER CONTINUATIONS**

Figure 23.4.7: Die micrograph of the Hybrid  $\Delta\Sigma$  -PWM Class-D Audio Amplifier.

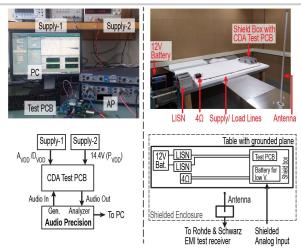

Figure 23.4.S1: Measurement setups: Left- Setup to characterize the audio performance using an Audio Precision (with AES17 filter enabled) test equipment; Right- Setup to measure radiated EMI (150kHz to 30MHz) using the guidelines and dimensions set by the CISPR25- Class5 standard.

Figure 23.4.S2: Measured out-of-band voltage spectrum of the Class-D Audio Amplifier: before LC filter (Top:  $V_{\text{SW-DIFF}}$ ) and after LC filter (Bottom:  $V_{\text{Rload-DIFF}}$ ).

Figure 23.4.S3: Comparison of THD+N across output power ( $f_{\text{IN}}$  = 1kHz) with state-of-the-art CDAs.