# Cryo-CMOS Readout of SNSPDs

for Diamond-based Quantum Computers

by

# Maoran Li

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Tuesday August 29th, 2023 at 9:00 AM.

Supervisor: Dr. Fabio Sebastiano

Co-supervisor: Luc Enthoven

Project Duration: September 2022 - September 2023

Faculty: Faculty of Electrical Engineering, Mathematics & Computer Science, TU Delft

Thesis Committee: Dr. F. Sebastiano, TU Delft, supervisor

Dr.ir. C.J.M. (Chris) Verhoeven, TU Delft

Cover: Photo by Maria Lysenko on Unsplash

Style: TU Delft Report Style, with modifications by Daan Zwaneveld

# Acknowledgement

I am extremely grateful to Dr. Fabio Sebastiano and Luc Enthoven for their support throughout the project for the past year. Weekly conversations and constructive feedback have been invaluable in my academic and personal growth. I would also like to express a special thank to Luc for being an incredible mentor. He is always available to answer my questions and is patient and supportive when it comes to tackling project issues, technical problems, and even personal matters. Being part of CoolGroup is a great experience, everyone is willing to help and the social gatherings are always enjoyable. Furthermore, I would like to thank my parents and friends for their understanding and encouragement, which has been a great source of comfort during the most difficult times.

Maoran Li Delft, August 2023

# **Abstract**

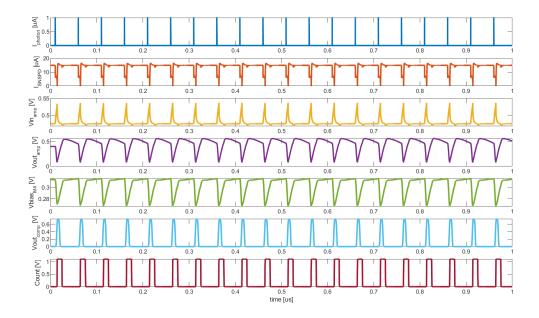

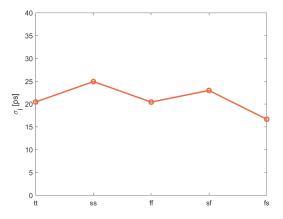

Single-photon detection is a critical step in both quantum computing and quantum information technology. For instance, the measurement of qubit states and the establishment of entanglement in nitrogen vacancy (NV) center quantum computing requires the detection of single photons. Superconducting nanowire single-photon detectors (SNSPDs) are very competitive devices due to their performance in high detection efficiency, high count rates, low dark count rates, and low jitter. However, the readout electronics are usually implemented at room temperature by connecting the dilution refrigerator through coaxial cables, while SNSPD need to work in a cryogenic environment that is close to the qubits. In order to have better integration and reduce the complexity of the wiring when the number of qubits increases, it is essential to position the electronics close to, or even integrated with, the SNSPD and qubits. In this thesis, a cryogenic CMOS readout for SNSPD is designed and taped-out using TSMC 40 nm technology. The SNSPD is designed for color-center quantum computing, which is anticipated to work in the wavelength range of 619-620 nm and 625-750 nm, and at a temperature of 1.8 K. The readout electronics are expected to operate at 4 K. The system is required to have a detection efficiency of more than 90 % and a dark count rate of less than 1 Hz. With the help of SPICE dynamic model, the SNSPD is reproduced in Cadence Spectre for circuit design. Active quenching is implemented in the readout architecture, allowing for an increased readout resistor, which improves the output slew rate and count rates without any latching while still keeping a high bias current for a higher detection efficiency. Under a -40 °C simulation, the readout system achieved count rates greater than 20 MHz, an average jitter of 25  $ps_{rms}$ , and a power consumption of 36  $\mu W$ , while simultaneously expecting to significantly suppress the dark count rates and after pulses.

# Contents

| Acknowledgement |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ab              | ostract i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| No              | omenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 1               | Introduction  1.1 Quantum Computing and Cryogenic Electronics  1.2 Single-Photon Detection  1.2.1 Single-Photon Detectors  1.2.2 SNSPD Readout  1.3 Thesis Objectives  1.4 Thesis Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 2               | SNSPDs for Diamond-based Color-Center Quantum Computing  2.1 Nitrogen-Vacancy Center Qubits 2.1.1 Structure and Energy Level 2.1.2 Need for Single Photon Detection  2.2 SNSPD 2.2.1 Device Configuration 2.2.2 Detection Mechanism 2.2.3 Performance and Nonidealities 2.2.4 SNSPD Readout Technique Comparison  10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 3               | SNSPD Model1-3.1 SNSPD SPICE Dynamic Model1-3.2 SNSPD SPICE Model Performance1-3.3 Model Limitations1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 4               | SNSPD Cryogenic Readout Circuit Design         4.1       System Overview       19         4.1.1       Architecture Decision       20         4.2       Analog Sub-circuits       20         4.2.1       SNSPD Biasing       20         4.2.2       Main Amplifier and Comparator       20         4.2.3       Amplifier Implementation       30         4.2.4       Current DAC for Anolog Subcircuits Biasing       30         4.2.5       Comparator Implementation       30         4.2.6       Feedback Amplifier       30         4.2.7       Mismatch and Robustness in Different Corners       31         4.3       Digital Sub-circuits       30         4.3.1       SR Latch       30         4.3.2       Current-Starve Delay Chain       30         4.4       System Performance       44         4.5       Layout       42         4.6       Measurment Plan       42 |  |  |

| 5               | Conclusion and Future Improvements45.1 Main Conclusion45.2 Further Improvements4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Ro              | forances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Contents | iv  |

|----------|-----|

| Contents | 1 4 |

| A | Addtional Basic Concepts                          | 51 |

|---|---------------------------------------------------|----|

|   | A.1 Kinetic Inductance                            | 51 |

|   | A.2 Thermoelectric Dynamics for Hot-Spot Dynamics |    |

|   | A.3 Damping coefficient                           | 51 |

| В | SNSPD Model SpectreText Code                      | 53 |

# Nomenclature

# **Abbreviations**

| Abbreviation | Definition                                          |

|--------------|-----------------------------------------------------|

| SNSPD        | Superconducting Nanowire Single-Photon Detector     |

| NISQ         | Noisy Intermediate-Scale Quantum era                |

| CMOS         | Complementary Metal-Oxide-Semiconductor             |

| QKD          | Quantum Key Distribution                            |

| SPAD         | Single-Photon Avalanche Diode                       |

| NV           | Nitrogen Vacancy                                    |

| PSB          | Phonon Side Band                                    |

| BS           | Beam Splitter                                       |

| ZPL          | Zero Phonon Line                                    |

| TDC          | Time-to-Digital Converter                           |

| QP           | Quasi-Particle                                      |

| SDE          | System Detection Efficiency                         |

| FWHM         | Full Width at Half Maximum                          |

| RMS          | Root Mean Square                                    |

| SPICE        | Simulation Program with Integrated Circuit Emphasis |

| ENBW         | Effective Noise BandWidth                           |

| DAC          | Digital-to-Analog Converter                         |

| LSB          | Least Significant Bit                               |

1

# Introduction

## 1.1. Quantum Computing and Cryogenic Electronics

Quantum computing has become one of the most exciting technologies due to its potential to accelerate computation exponentially. Traditional computers use bits to store and process information. Each bit is stored as either 0 or 1, and these logics are often controlled by low or high voltages. For a quantum computer, a "qubit" can be in a superposition state of the 0 state ( $|0\rangle$ ) and the 1 state ( $|1\rangle$ ) [1]. Hence, a qubit is in the quantum state of  $|\psi\rangle = \alpha_0 |0\rangle + \alpha_1 |1\rangle$ , where  $\alpha_0$  and  $\alpha_1$  are complex amplitudes with  $\alpha_0^2 + \alpha_1^2 = 1$ . If this qubit is measured on a computational basis, the result will be either  $|0\rangle$  with a probability of  $\alpha_0^2$  or  $|1\rangle$  with a probability of  $|\alpha_1|^2 = 1 - \alpha_0^2$ . Therefore, the advantage of a qubit being in a superposition of two classical states is that the information stored in qubits increases exponentially with the number of qubits. The n-qubit states can be in the superposition of the  $2^n$  computational basis with the form of  $|\psi_n\rangle = \alpha_0 |0\rangle + \alpha_1 |1\rangle + \cdots + \alpha_{2^n-1} |2^n - 1\rangle$ .

In the current NISQ (Noisy Intermediate-Scale Quantum) era, fault tolerance and scalability have become the most significant challenges because qubits are extremely noise sensitive. Any unwanted disturbance can limit the quantum computer from displaying its powerful computing capabilities. DiVincenzo proposed five criteria in 2000 for building a practical quantum computer [2]. Several quantum systems, including Josephson junctions in superconducting circuits [3], silicon electron spins [4], and spins of impurities in solids [5], have met these requirements to some extent. In most cases, qubits need to be cooled to an extremely low temperature (milli-Kelvins) in the dilution refrigerator, and initialization, operation, error correction, and readout are performed by room-temperature control systems through long wires [6]. However, with an increasing number of qubits in the quantum processor, connecting quantum chips from dilution refrigerators to the room-temperature control systems becomes increasingly intricate and costly because of the physical space and heat load of those wires.

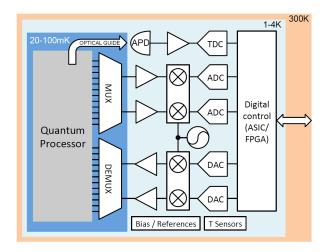

One of the solutions for the scalable quantum processor is positioning the electronics close to the qubits, as shown in Figure 1.1, to reduce the number of interconnects required in the dilution refrigerator. CMOS (Complementary Metal-Oxide-Semiconductor) technology is advantageous among the different semiconductor technologies since it can operate at temperatures as low as 30mK. Furthermore, it has been used to construct complex and power-efficient electronic interfaces for qubits due to its reliability and integration capability [8]. Therefore, cryo-CMOS is promising for the development of large-scale quantum computers.

Photon detection is necessary in both quantum computing and quantum information technologies. Quantum information technology involves using quantum mechanical objects to encode, communicate, manipulate, and measure information [9], and photons are the information carriers when the system utilizes optics. For example, in quantum communication, single photons traveling over a channel prevent eavesdroppers from gaining information in QKD (Quantum Key Distribution) [10]; in photonic quantum computing, qubit information is encoded in the quantum state of the photon by utilizing degrees of freedom such as polarization. This work is based on the color center quantum computing using the negatively charged states of Nitrogen-Vacancy (NV) center, known as  $NV^-$ , as the qubit. This type of qubit has a longer coherence time due to the excellent insulation from the external environment

**Figure 1.1:** A generic system for a scalable qubit array with most of the electronics components operating in cryogenic temperature [7].

provided by the diamond lattice and can be operated even at room temperature, making it advantageous compared to other qubits. The well-defined optical transition makes the detection of emitted photons essential for the state readout and initialization, as well as the establishment of entanglement. Therefore, single-photon detection is required.

## 1.2. Single-Photon Detection

#### 1.2.1. Single-Photon Detectors

There are various types of single-photon detectors still actively being investigated to push the photon detection limit. Silicon-based SPADs (Single-Photon Avalanche Diodes) absorb photons and generate an electron-hole pair. When the bias voltage is higher than the diode breakdown voltage, the current is self-sustained and will saturate as the charge multiplication (avalanche) process continues [11]. Another class of detectors relies on superconducting material, and can be divided into different types based on different operation mechanisms and topologies: transition edge sensor (TES), superconducting tunnel junction (SJT), microwave kinetic inductance detector (MKID), and superconducting nanowire single-photon detector (SNSPD) [12]. Due to its impressive performance in photon detection efficiency, dark count rate, jitter, and dead time, SNSPDs attract increasing interest [13]. In addition, it is used in this work also because of its advantage of simpler fabrication and the ability to work at cryogenic temperatures together with qubits and cryo-CMOS electronics, which is beneficial for high integration and scalability, compared to SPADs.

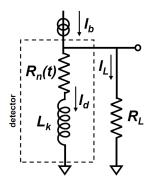

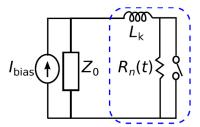

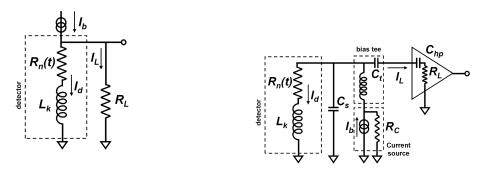

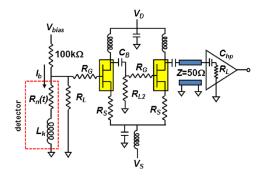

#### 1.2.2. SNSPD Readout

The concept of SNSPD reading single-photon information (the detailed detection mechanism will be explained in Section 2.2.2) is to connect it in parallel with a low resistance route. The dashed line box in Figure 1.2 represents the SNSPD, which is modeled by a variable resistor  $R_n(t)$  and kinetic inductance  $L_k$  (the detailed SNSPD modeling can be seen in Chapter 3). When the SNSPD is biased with a current of  $I_b = 20 \,\mu\text{A}$  and connected to a load resistor of  $R_L = 50 \,\Omega$ , the current initially biased in the SNSPD,  $I_b$ , will be diverted to the low resistance path ( $I_b = I_d + I_L$ ) since  $R_n(t)$  will become much larger than  $R_L$  in the detection phase. This results in a maximum voltage output of  $V_{out} = I_{L_{max}} \times R_L = I_b \times R_L = 1 \,\text{mV}$  after detecting a photon, thus allowing the photon signal to be converted to a voltage signal, which can then be further processed and read out in the following circuits. The voltage produced by the readout is restricted to the product of the load resistance and the bias current. Increasing the load resistance can result in a considerable gain in pulse amplitude, which is advantageous for the timing jitter. However, the maximum load resistance is restricted by the latching problem and the impedance

matching when using  $50~\Omega$  cables. Additionally, as the number of qubits increases, the required SNSPD increases, making wiring complicated. Consequently, a compact readout system that requires cryogenic electronics to be placed close to the qubits and SNSPD is necessary.

**Figure 1.2:** Typical SNSPD readout using a low-resistance path  $R_L$  [14].

## 1.3. Thesis Objectives

This work aims to design the first cryo-CMOS SNSPD readout circuit that is capable of operating at 4 K using TSMC 40 nm technology, which can then work closely with SNSPD and be utilized for the development of a diamond-based quantum computer. The main objectives are

- Gain an insight into the fundamentals of how NV center qubits and SNSPDs operate. Examine the performance of the SNSPD system and formulating the requirements for the readout circuits.

- Examine the influence of SNSPD and circuit parameters (readout resistance  $R_L$ , bias current  $I_{bias}$ , switching current  $I_{sw}$ , kinetic inductance  $L_k(t)$ , and hot spot resistance  $R_n(t)$ ) on the SNSPD's performance in terms of count rates, dark count rates, afterpulses, dead time, latching, and jitter.

- Investigate how the readout circuit (including circuit architecture and electrical parameters) impacts the performance of the SNSPD.

- Design a cryo-CMOS readout circuit meeting the performance required for the application.

The SNSPD single-photon readout system is designed to meet the specifications [15] listed in Table 1.1.

## 1.4. Thesis Outline

This thesis is structured as follows: Chapter 2 provides an overview of the fundamentals of diamond-based vacancy center quantum computing and the necessity of SNSPD and single-photon detection in this particular quantum system. It also covers the SNSPD single-photon detection mechanism and the associated non-idealities for assessing the SNSPD's performance. Chapter 3 focuses on modeling the SNSPD in SPICE and comparing the Spectre simulation performance with the device effective performance. Chapter 4 outlines the step-by-step process of designing the readout circuit exploiting the active quenching technique. This includes presenting the simulation results of the impact from different SNSPD parameters including  $R_L$ ,  $C_{pad}$ ,  $I_{bias}$ ,  $L_k$ , and  $R_n(t)$  for determining the system-level architecture, designing the transistor-level implementation of the analog and digital subcircuits, and simulating the performance. Then, the measurement plan will be briefly introduced, followed by the final chapter, which includes the conclusion and potential improvements.

1.4. Thesis Outline

Table 1.1: SNSPD Readout System Specification

| Specification                  | Required                                                             | Preference                         |

|--------------------------------|----------------------------------------------------------------------|------------------------------------|

| Operating Wavelength           | 619-620 nm (ZPL) + 625-750 nm (PSB)                                  |                                    |

| Operating Temperature          | SNSPD: 1.8 K; Readout electronics: 4 K                               |                                    |

| System Detection Efficiency    | >80%                                                                 | >90%                               |

| Dark Count Rate                | <5 Hz                                                                | <1 Hz                              |

| Dead Time                      | <100 ns                                                              | <50 ns                             |

| Count Rate                     | >10 MHz                                                              | >20 MHz                            |

| Jitter                         | $<100 \text{ ps}_{\text{FWHM}} (\lesssim 40 \text{ps}_{\text{rms}})$ |                                    |

| Latching                       | <1 μs                                                                | No latching                        |

| SNSPD bias Current             | <20 μA for NbTiN                                                     | with $\pm 1 \mu\text{A}$ tolerance |

| Supply Voltage                 | 1.1 V & 2.5 V                                                        |                                    |

| Power Consumption              | <100 μW                                                              | As low as possible                 |

| Area (for readout electronics) | <1 mm <sup>2</sup>                                                   |                                    |

# SNSPDs for Diamond-based Color-Center Quantum Computing

This chapter introduces diamond-based defect centers, the principles of entangling two remote qubits, the necessity of single-photon detection, SNSPD, and its readout system, and the system specifications. Defect centers can be created with different vacancies, such as SnV (tin-vacancy), SiV (silicon-vacancy) and NV (nitrogen-vacancy) [16]. This thesis focuses on NV centers as the target application.

## 2.1. Nitrogen-Vacancy Center Qubits

Diamond-based color centers are especially promising for realizing a large-scale distributed quantum computer due to their long-lived spin quantum states, well-defined optical transitions, and robust and efficient optical interfaces fabricated from diamond crystals [17].

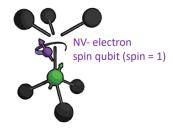

## 2.1.1. Structure and Energy Level

The NV center is a defect in the diamond lattice consisting of a nearest-neighbor pair of a nitrogen atom which substitutes for the carbon atom and a lattice vacancy, as shown in Figure 2.1a. It has spin degrees of freedom associated with its bound electrons and nearby nuclear spins. There are multiple types of spins in the defect diamond, and this work focuses on the electronic spin. The nitrogen-vacancy center has two charge states,  $NV^0$  and  $NV^-$ . The latter, negatively charged  $NV^0$  state [18] is used as a qubit. This extra electron is located at the vacancy site and forms a net spin S=1 pair with one of the vacancy electrons. The corresponding simplified Hamiltonian of the  $NV^-$  orbital ground state can be written as [19]:

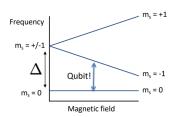

$$H = \Delta S_z^2 + \gamma_e \vec{B} \cdot \vec{S} \tag{2.1}$$

where  $\Delta \sim 2.87$  GHz is the zero-field splitting which represents the energy difference between  $m_s = \pm 1$  and  $m_s = 0$ ,  $m_s$  is the spin energy sublevels;  $\gamma_e$  is the gyromagnetic ratio so that a magnetic field  $\vec{B}$  parallel to the NV axis  $\vec{S}$  can split the  $m_s = \pm 1$  states through the Zeeman effect. Consequently, it produces a well-defined leveled system, and the lowest two levels ( $m_s = -1 \& m_s = 0$ ) can thus be used as a valid qubit as in Figure 2.1b shows.

#### 2.1.2. Need for Single Photon Detection

#### **Single-shot Readout**

The NV center qubit can be measured with a single-shot readout process. When exposed to resonant excitation, only the electron spin in the state of interest (for example, if we expect the state to be  $|0\rangle$ , then a resonant excitation for  $|0\rangle \rightarrow |1\rangle$  will be applied) will produce fluorescence light and emit photons, as shown in Figure 2.2, which makes the detection of the qubit states relatively simple. This readout technique has exceptionally high fidelity, making it one of the benefits of this diamond-based qubit, and can also be used in qubit initialization.

(a) Simplified physical structure of an NV center.

**(b)** Energy level structure of the NV center orbital ground state triplet with Zeeman splitting.

Figure 2.1: NV center qubit structure and its energy level [19]. (a) Green:  $^{14}N$  nitrogen atom with the nuclear spin I=1; Purple: one of a vacancy electron paired with an extra electron; Black:  $^{12}C$  carbon atoms with isotopic impurity  $^{13}C$  nuclei  $I=\frac{1}{2}$  in the diamond. (b)  $|m_s=0\rangle=|\uparrow\rangle$ ,  $|m_s=-1\rangle=|\downarrow\rangle$ , which will be used as a qubit.

Figure 2.2: Readout scheme of the qubit [20]. Straight line: applied readout laser for |0\; wavy line: corresponding fluorescence photon; dashed wavy line: fluorescence to unwanted states.

For the NV center qubit, such a readout scheme emits PSB (Phonon Side-Band) or ZPL (Zero Phonon Line) photons, which are then sent to the SNSPD, resulting in an electrical signal that is further processed by readout circuits. The PSB photons are used for state detection, whereas the ZPL photons are employed to create the entanglement that will be discussed in the next section.

#### **Heralded Entanglement Generation**

At cryogenic temperature, the phonon processes are suppressed, revealing the spectrally sharp optical transitions of the NV center [21]. This advantageous optical interface and narrow optical transition spectrums allow the NV centers to generate the entanglement of two distant electron spins. A detailed approach to the heralded entanglement [22], as depicted in Figure 2.3, involves the following steps:

**Figure 2.3:** Schematic for generating entanglement between distant spins [21]. Direct the locally emitted photons to the BS (Beam Splitter), and the following single photon detection events entangle the two distant qubits.

- 1. Initialize both qubits to the equally superposed state  $\frac{1}{\sqrt{2}}(|\uparrow\rangle + |\downarrow\rangle)$ .

- 2. Apply a pulse resonant with the optical transition of  $|\uparrow\rangle \to |e\rangle$ . Then spontaneous emission locally entangles the qubit with the photon number, leaving each qubit in the state  $\frac{1}{\sqrt{2}}(|1\uparrow\rangle + |0\downarrow\rangle)$ . And the

corresponding joint state would be  $\frac{1}{2}(|1_A1_B\rangle |\uparrow_A\uparrow_B\rangle + |0_A0_B\rangle |\downarrow_A\downarrow_B\rangle + |1_A0_B\rangle |\uparrow_A\downarrow_B\rangle + |0_A1_B\rangle |\downarrow_A\uparrow_B\rangle)$ . A and B represent the two NV centers.

3. Then the photons will be diverted to the BS (Beam Splitter) of:

$$\begin{cases} |0_{A}1_{B}\rangle \xrightarrow{BS} (i|0_{C}\rangle + |0_{D}\rangle)(|1_{C}\rangle + i|1_{D}\rangle) = i|01\rangle_{C} - |0_{C}1_{D}\rangle + |1_{C}0_{D}\rangle + i|01\rangle_{D} \\ |1_{A}0_{B}\rangle \xrightarrow{BS} (i|1_{C}\rangle + |1_{D}\rangle)(|0_{C}\rangle + i|0_{D}\rangle) = i|01\rangle_{C} - |1_{C}0_{D}\rangle + |0_{C}1_{D}\rangle + i|01\rangle_{D} \end{cases}$$

$$(2.2)$$

and interfere with each other coherently:

$$\begin{cases} |\Psi^{-}\rangle = |0_{A}1_{B}\rangle - |1_{A}0_{B}\rangle \xrightarrow{BS} - |0_{C}1_{D}\rangle + |1_{C}0_{D}\rangle \\ |\Psi^{+}\rangle = |0_{A}1_{B}\rangle + |1_{A}0_{B}\rangle \xrightarrow{BS} i |0_{C}1_{C}\rangle + i |0_{D}1_{D}\rangle \end{cases}$$

(2.3)

where C and D are the output port of the BS. If the photons emitted by the two NV centers are indistinguishable, that is, they are ZPL (Zero Phonon Line), then the detection of a single photon "click" on either output SNSPD port will project the qubits onto the maximally entangled state  $|\psi\rangle = \frac{1}{\sqrt{2}} \left(|\uparrow_A\downarrow_B\rangle \pm e^{-i\phi} \mid \downarrow_A\uparrow_B\rangle\right)$ .

#### **2.2. SNSPD**

#### 2.2.1. Device Configuration

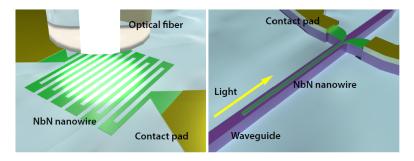

Superconducting nanowire single-photon detectors consist on an electrically and optically accessible, very narrow ( $\simeq 100$  nm) and ultrathin (4–5 nm) superconducting wire strip [23]. As can be seen in Figure 2.4 (left), one of the SNSPD configurations involves a meandering nanowire that is directly coupled to an optical fiber or through fiber-coupled small gradient index focusing lenses, which are similar in size to the fiber core diameter. However, this type of coupling requires a long and dense meander to compensate for the coupling loss and the low detection efficiency. An alternative configuration (on the

Figure 2.4: SNSPD Configuration [23]. Left: fiber coupled; right: waveguide integrated

right) would be the integrated waveguide: a single nanowire segment is placed on top of a photonic waveguide, so that photons are absorbed in the direction of their propagation. This allows for a drastic improvement in the light interaction length, thus increasing the absorption efficiency. Furthermore, the corresponding shorter wire reduces both geometric and kinetic inductance (A.1), which in turn reduces the response time of the SNSPD, allowing higher count rates.

#### 2.2.2. Detection Mechanism

At present, there is no comprehensive model that can accurately explain and forecast all experimental results for the SNSPD detection process to a microscopic extent [23]. This work uses the hotspot theory [24], [25] to explain the formation of the non-superconducting area in SNSPD after a photon is absorbed. The SNSPD is initially kept at a temperature below its superconducting critical temperature  $T_c$  and biased with a current  $T_{bias}$  that is below its critical current  $T_c$  (Figure 2.5a(i)). When a photon hits the

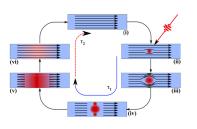

SNSPD, the energy it absorbs is transferred from the photon to the electrons in the nanowire. This leads to an avalanche of quasiparticles (QPs) (i.e., broken Cooper pairs) due to the electron-electron interaction, forming a localized region with a high concentration of excited electrons, known as a hot spot (Figure 2.5a(ii)). The amount of energy transferred and the magnitude of the superconducting energy gap will determine the degree to which the superconducting order parameter in a given area is reduced, resulting in the formation of a "resistive" region. Then this hot spot forces the supercurrent to flow around the resistance area, which leads to an increase in current density beyond the critical current density, thus forming a resistive barrier across the width of the nanowire (Figure 2.5a(iii,iv)). The flow of current through this resistive barrier produces more heat than is dissipated to the substrate, causing the hot spot to grow along the nanowire (Figure 2.5a(v)). Since the hot spot typically has a resistance of  $k\Omega$ , when connected to a small resistor,  $Z_0 = 50 \Omega$ , as illustrated in Figure 2.5b, the current in the SNSPD will be diverted to the low resistance path and results in a voltage across  $Z_0$  that can be used as a measure of the photon-hit event. Finally, as more current is diverted to the readout circuit, the heat generated in the SNSPD decreases, causing the hot spot to shrink (Figure 2.5a(vi)) until it eventually vanishes, allowing SNSPD to return to its original superconducting state and await the next photon (Figure 2.5a(i)).

(a) SNSPD detection cycle.

(b) SNSPD readout circuit schematic. Components in the blue dashed box represents the SNSPD electrical model;  $I_{bias}$  is the current used to bias the SNSPD;  $Z_0$  is the readout resistor.

Figure 2.5: SNSPD detection mechanism [24].

#### 2.2.3. Performance and Nonidealities

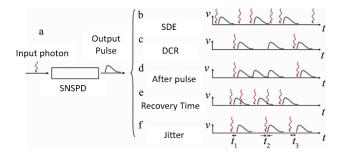

There are several parameters to judge the performance of an SNSPD and its readout circuit as shown in Figure 2.6:

Figure 2.6: SNSPD readout signal specifications and non-idealities, reproduced from [26].

• **SDE** (**System Detection Efficiency**) is the probablity the SNSPD will trigger when a photon is incident. It can be described by:

$$\eta_{SDE} = \eta_{coupling} \times \eta_{absorption} \times \eta_{intrinsic} \tag{2.4}$$

where  $\eta_{coupling}$  represents the probability of an incident photon being coupled to the SNSPD photosensitive surface;  $\eta_{absorption}$  is the probability that the nanowire absorbs the photons incident on the photosensitive surface of SNSPD; and  $\eta_{intrinsic}$  represents the probability that a photon absorbed by the nanowire generates a voltage pulse. These parameters are mostly related to material and structure. However, intrinsic efficiency  $\eta_{intrinsic}$  depends on the magnitude of the bias current  $I_{bias}$ , so it is possible to improve the intrinsic efficiency with the help of the design of the external biasing or readout circuit. The basic principle would be to make the trade-off between increasing  $I_{bias}$  and leaving the appropriate headroom for its superconducting-to-resistive-state switching current  $I_{SW}$ . The current level that determines whether SNSPD will be activated is denoted by  $I_{SW}$ . If the total current in the SNSPD due to the incident photon is greater than the switching current,  $I_{SNSPD,bias} + I_{photon} > I_{SW}$ , then the SNSPD will be activated.

- A dark count is an SNSPD triggering without a photon being incident as illustrated in Figure 2.6c. The primary physical causes of dark counts in SNSPDs are vortex-antivortex depairing [27] and blackbody radiation that is transmitted to SNSPDs through optical paths [28] (which can be reduced by optical filtering). The dark count rate generally increases as the bias current increases.

- After pulses: after detecting a photon, the SNSPD outputs two or more (N) voltage pulses instead of a single voltage pulse. The second to Nth voltage pulses are called afterpulses. It is noteworthy that afterpulses can also lead to dark counts, although the exact mechanism is not yet fully understood [29]. Therefore, it is clear that a lower  $I_{bias}$  (which is a trade-off to achieve a high SDE) can help reduce afterpulses and, consequently, the dark counts rate. The Active Quenching (AQ) technique [29], which will be discussed in the later section, can be used to significantly reduce afterpulses by directly cutting the  $I_{bias}$ , thus also reducing dark count rates.

- **Recovery time** is the time required for the SNSPD to recover after a detection event. The response recovery time of SNSPD is defined as the time required for the SDE to recover to 90% of the SDE at low photon flux after completing a photon detection event. As shown in Figure 2.6e, if two or more photons arrive at the SNSPD in quick succession, they cannot be detected effectively. The recovery time of an SNSPD is affected by two factors: the electrical time constant  $\tau_e = \frac{L_k}{R_L}$  (which is mainly determined by the kinetic inductance  $L_k$  of the device and can be reduced by increasing the load resistance  $R_L$ ) and the thermal time constant  $\tau_{th}$  (see Appendix A.3).

- Latching is another important phenomenon related to the recovery time that can greatly affect SNSPD performance. Essentially, this phenomenon is caused by rapid negative electrothermal feedback, which is usually used to reset the device [30]. In other words, latching is likely to occur when the ratio of the electrical to the thermal time constant  $\frac{\tau_e}{\tau_{th}}$  is too small: When the electrical time constant of the SNSPD ( $\tau_e = \frac{L_k}{R_L}$ ) is less than the thermal time constant  $\tau_{th}$ , the current returns too fast. This causes the heat produced by the returned current in the SNSPD to equal the heat dissipated to the substrate, resulting in the resistive region being clamped in a stable state. Therefore, the SNSPD now has a stable resistive region, which means that the current diverted to the readout circuit is unable to fully flow back to the nanowire. As a result, the nanowires are unable to continuously detect photons, thus preventing the SNSPD from operating continuously.

- **Jitter** indicates the uncertainty with which the SNSPD measure when a photon is incident. The input signal of an SNSPD is a photon, and the output signal is a voltage pulse. There is a delay between the output and the input, as illustrated in Figure 2.6f. This delay is not fixed, which causes jitter. The detailed expression of the jitter can be found in [31].

In this work, we are mainly interested in optimizing the electronic jitter  $\sigma_{electronic}$ . The jitter is given as

$$\sigma_{tot}^2 \approx \sigma_{electronic}^2 + \sigma_{others}^2$$

(2.5)

where  $\sigma_{others}$  includes the intrinsic jitter of SNSPD  $\sigma_{int}$ , the optical jitter  $\sigma_{opt}$ , etc. The jitter requirement indicated in Table 1.1 is of  $j_{jitter} < 100$  ps in terms of the FWHM (Full Width at Half Maximum). As the jitter of most SNSPDs follows the Gaussian distribution [32], the root mean square (rms) jitter can be approximated by [23]  $j_{FWHM} \approx 2\sqrt{2ln(2)}\sigma_{i,rms} \Rightarrow \sigma_{i,rms} \approx 42.46$  ps.

Assuming that the electronics jitter dominates the system jitter contribution, the jitter for the readout circuits in this work can be derived by

$$\sigma_{j,electronic,rms} \approx \sqrt{\sigma_{j,rms}^2 - \sigma_{j,SNSPD,rms}^2}$$

$$= \sqrt{42.46p^2 - 15p^2} \approx 40ps$$

(2.6)

where  $\sigma_{j,SNSPD,rms}$  is taken from the typical value of an SNSPD. To allow some headroom, in this work the rms jitter value is reasonable to set as  $\sigma_{electronic} \leq 35$  ps.

• The typical value of the specifications that an commercial SNSPD can achieve is shown in the Table 2.1

Table 2.1: Typical SNSPD (Table top detector provided by Pixel Photonics) Sepcifications [33]

| Specification               | Typical Value          |

|-----------------------------|------------------------|

| Operating Wavelength        | Visible to IR spectrum |

| Operating Temperature       | 2.5 ~ 3 K              |

| System Detection Efficiency | ≥ 70%                  |

| Dark Count Rate             | <100 Hz                |

| Count Rate                  | ≤ 60 MHz               |

| Jitter                      | <50 ps                 |

#### 2.2.4. SNSPD Readout Technique Comparison

#### **Passive Quenching**

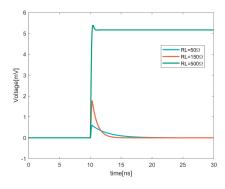

The traditional method of reading the signal produced by an SNSPD is known as passive quenching. This was previously introduced in Section 2.2.2. As a reminder, when a sufficient amount of current is diverted to the low-resistance readout path, the SNSPD is quenched due to the heat produced by the current being less than the heat dissipated to the substrate. The passive quenching method for SNSPD readout has a trade-off between latching, signal level, the gain requirement on the following amplifier, and eventually, the jitter performance. As is demonstrated in Figure 2.7, a small readout resistor  $R_L$  can

**Figure 2.7:** Impact of the load resistor  $R_L$  in passive quenching. As resistance increases, the slew rate on the rising edge increases, and the recovery time decreases. However, if  $R_L$  is too large, the system will latch (green curve).

reduce the risk of latching. However, the signal amplitude of the SNSPD is restricted by  $I_{bias} \times R_L$ , which requires stricter requirements on the gain of the subsequent amplifier. This results in a decrease in SNR due to the lower signal level and extra noise from the following circuits. Furthermore, the maximum count rate decreases due to the larger  $\tau_e = \frac{L_k}{R_L}$ , which is inversely proportional to the load resistance. Another problem comes from the impedance matching since the output signal will be transimitted

through the 50  $\Omega$  cables to the room temperature readout electronics. Therefore, changing  $R_L$  will also distort the output signal, as illustrated in Figure 2.8.

**Figure 2.8:** Impact of different load resistors  $R_L$  when using 50  $\Omega$  cables in tradition room temperature readout. Signals are distorted as can be seen from the bottom plots.

The volatge signal across the load resistor which is in parallel with the SNSPD will be further processed by the following readout circuits such as an amplifier. The amplifier can be either DC or AC coupled, as demonstrated in Figure 2.9. However, in practice, the load seen by the detector is not just a resistive

- (a) Typical SNSPD readout using a low-resistance path  $R_L$  to divert the (b) AC coupled amplifier with a bia tee.  $C_s$  indicates the parasitic bias current  $I_b$ . The amplifier will be DC coupled.

- capacitance;  $C_{hp}^{1}$  is the input capacitance of the amplifier.

Figure 2.9: SNSPD readout circuit schematic [14]. The dashed box models the SNSPD where  $R_n(t)$  is the time-dependent hot spot resistance;  $L_k$  is the kinectic inductance of nanowire.

element that is independent of the frequency as demonstrated in Figure 2.9a. This results in a nonlinear feedback that links the average count rate to the detection efficiency. In the cases of extremely high count rates, this feedback can even cause the detector to enter the latched state [14]. The count rate of both schemes will be restricted by the 50  $\Omega$  load resistor, as the recovery time  $\tau_{falling} \sim \frac{L_k(t)}{R_L}$  is larger. Furthermore, the AC coupled amplifier will limit the system count rate from charging and discharging the capacitor.

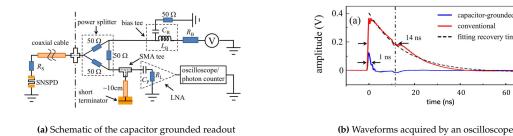

Figure 2.10 shows the improved SNSPD readout electronics. The gate electrode of a commercial high-electron-mobility transistor (HEMT) has a wideband high impedance, which is shunted in parallel with the DC readout resistor  $R_L$ . The HEMT is used in the typical common source setup, and its high gain and broad bandwidth effectively separate the SNSPD from the readout electronics. To provide extra gain, a second cascaded HEMT, common-source stage is used. The isolation provided by the preamplifier allows  $R_L$  to be different from the usual 50  $\Omega$  for impedance matching. However, the

improvement in this readout resistance is still limited, as the SNSPD will eventually enter the latched state as  $R_L$  increases. Another readout shceme is the capacitor grounded readout [34] to reduce the

Figure 2.10: Improved SNSPD DC readout with a preamplifier to removes the AC-coupled feedback [14].

current reset time and remove the coupling effect that limits count rates, as illustrated in Figure 2.11a. A resistor  $R_s$  connected in series with the detector is utilized to reduce the recovery time and thus enhance the maximum count rate. The input of the low noise amplifier (LNA) is paralleled with a short terminated coaxial cable through an bias tee which will equally split the SNSPD output into two pulses. One goes to the LNA directly while the other one is inverted in amplitude at the short termiator of the coaxial cable, and then arrives at the LNA with a time delay of  $\sim 1$  ns. Therefore, the overlapped input pulses of the LNA are cancelled out, resulting in much narrorwer ones, which charge on the LNA input capacitor with less energy. Also, the rising edges of the pulses are still maintained where the recovery time is decreased, as shown in Figure 2.11b.

Figure 2.11: Capacitor grounded radout sheme [34].

60

40

However, in each of this cases the output voltage is still limited to the load resistance and the bias current. And such load resistance has its maximum values restricted by the latching. And it is not preferable to solve these issues by decreasing the bias current because it will affect the detection efficiency. Therefore the readout schemes discussed above will limit the system performance from having high count rates and timing jitter which is due to the associated relative low signal to noise ratio.

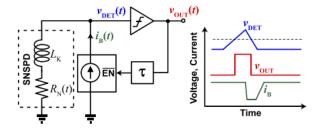

#### **Active Quenching**

In order to have a large readout resistor during the signal readout phase, and one that is small enough to avoid latching yet still large enough to quickly reset the SNSPD during the resetting phase, the active quenching technique [29] is utilized. As shown in Figure 2.12, a comparator is located at the SNSPD output. If the voltage of the signal  $v_{DET}$  exceeds the comparator threshold, the SNSPD bias  $i_B(t)$ is deactivated, forcing SNSPD to return to the superconducting state more rapidly. The comparator then rebiases the SNSPD after a time period of  $\tau$ , preparing it for the arrival of the next photon [29]. The deactivation of bias current during the quenching phase can significantly reduce afterpulses and

Figure 2.12: Conceptual block diagram of active quenching architecture and key waveforms describing its operation [29].

associated dark counts. Additionally, a larger  $R_L$  increases count rates due to a shorter recovery time on the falling edge and improves jitter performance due to a higher slew rate on the rising edge. Therefore, in this work, a cryo-CMOS readout circuit employing the active quenching (AQ) is designed to make a compact SNSPD readout system that can work at cryogenic temperature, while the performance of count rate, dark count rate, and jitter of the SNSPD can be simultaneously enhanced.

In conclusion, this chapter first provides a fundamental overview of NV center quantum computing, including the state measurement and entanglement establishment, which necessitate single-photon detection. Subsequently, the SNSPD detection mechanism was explored, followed by the presentation of the performance and imperfections of SNSPD. Finally, various state-of-the-art readout techniques were discussed. The following chapters will start introducing the circuit design process with the SNSPD SPICE model in Chapter 3.

# SNSPD Model

It is essential to construct a model that accurately portrays the SNSPD photon detection dynamics for the purpose of designing the readout circuit in the subsequent stages. This chapter first explains the model used to simulate the evolution of the SNSPD hotspot. Then, this SNSPD SPICE model will be implemented and simulated in Cadence Spectre, and its performance will be evaluated by comparing it with the laboratory data.

## 3.1. SNSPD SPICE Dynamic Model

SPICE does not include superconducting nanowires in its component list, making it difficult to model complicated superconducting nanowire detector structures quickly and easily. Karl K Berggren et al [35] present three circuit models to explain the expansion and annihilation process of hotspots:

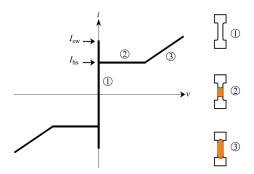

• The **curve-fitting model** replicates the current-voltage (i-v) relationship of the nanowire, as well as the transition into and out of the superconducting state. However, this model does not account for the physical description of the nanowire dynamics and is therefore too ideal for electrical circuit design consideration in this work. As demonstrated in Figure 3.1, ① is the superconducting state, ② is the hotspot state, and ③ is the state in which the entire nanowire becomes resistive. This curve-fitting model does not take into account the electrothermal dynamics of the hotspot region, which means that it cannot accurately interact with the external readout circuit. Thus, it is not suitable for the purpose of readout circuit design in this work.

Figure 3.1: The i-v curve used in curve-fitting model [35].

- The **dynamic model** includes the electrothermal dynamics of the nanowire, which is necessary when the dynamics of the nanowire interacts with the dynamics of the external circuit. Therefore, the rise and fall times (i.e.  $\tau_{rise} = \frac{L_k(t)}{R_n(t)}$  and  $\tau_{fall} = \frac{L_k(t)}{R_L}$ ), the recovery and dead times, latching, and jitter performance will be more accurately modeled than with the curve-fitting model. Therefore, this model will be sufficient for the purpose of this work.

- The **thermal device model** is the most comprehensive model that takes into account the effects of thermal relaxation in the superconducting state, allowing for a qualitative representation of

the afterpulses and related dark count. However, it is highly sensitive to the selection of model parameters and requires further validation with actual experimental data.

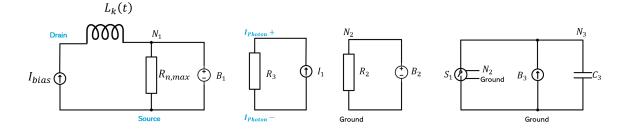

Due to its relatively complete description of electrothermal dynamics and realiability, the dynamic model is used in this work for modeling the SNSPD in SPICE. Figure 3.3 shows a schematic of the dynamic device model that uses nanowire electrothermal physics to model the evolution of the hot-spot resistance over time. The following is the explanation of the components used:

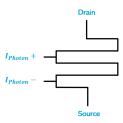

Figure 3.2: SNSPD symbol with terminals

Figure 3.3: SPICE schematic of SNSPD dynamic model with terminals emphasised in blue. The  $I_{bias}$  is the bais current source from external circuit which does not belong to the SPICE model.

- The kinetic inductance of SNSPD  $L_k(t)$  is current dependent (which is eventually time dependent), and the accurate expression is still unclear. Although the expression can be obtained by fitting the data from [36], it is still not very reliable since the performance is heavily dependent on the property of the SNSPD itself. Also, as shown in Figure 3.4, setting this inductance as a constant value shows little difference. Therefore, in this work, it is enough to take  $L_k(t)$  as a constant (i.e.,  $L_k(t) \approx L_{k0} = 130 \text{ nH}$ ).

- $R_{n,max}$  is the maximum resistance of the SNSPD hot spot that can be achieved if the entire nanowire is converted to a resistive state. This is used to restrict the unbounded growth of the hot spot. However, this resistance is usually not reached under normal operating conditions.

- **B1** represents the growth or shrinkage of the resistance of the hot-spot.

$$V(B1) = \frac{V(N3) + |V(N3)|}{2} \times I(B1)$$

(3.1)

The value of V(N3) does not physically correspond to the voltage, but is instead numerically equivalent to the resistance of the hotspot (will be explained in the following items). The absolute function of the expression guarantees a real-number value.

• The current source I1 and resistor R3 are employed to mimic the photon hit event. The current generated by the photon,  $I_{photon}$ , is produced by I1. R3 is an extremely samll resistor to sense the current that I1 provides. In Cadence Spectre, R3 can be replaced by the current probe device, such as the iprobe. Therefore, the photon-induced current in SNSPD can be represented by

$I_{photon} = I(R3)$ . This subcircuit mainly provides an interface terminal  $I_{photon+}$  between SNSPD and photon, which can be considered as the input of the SNSPD.

If the current in the SNSPD exceeds the switching current,  $I_{SW} - g \times I_{photon}$ , which will be set as a judging condition at the behavior source B2, a hotspot will be created. The gain factor, g, is used to guarantee that the photon can activate the SNSPD, but its value can be adjusted based on actual experiments to take into account the effects related to the photon energy.

- The SNSPD state is monitored and judged by B2 & R2. If the current generated by the photon surpasses the switching current, or the voltage across the hot-spot region is higher than the minimum voltage needed to keep the hot-spot, the SNSPD will switch to the resistor-like state, and the value of B2 will be 1. If not, the value of B1 will be 0 and the SNSPD will remain in the superconducting state.

- The subcircuit of hot-spot evolution, consisting of B3, C1, and S1, is used to calculate the total device resistance by integrating  $\frac{\partial R_{HS}}{\partial t}$  as shown in equation (3.2). The operation of switch S1 is depend on the value of V(B2). If S1 is closed, then the current in B3 will be directed to the ground, thus preventing any integration on C3. Otherwise, a capacitor C3 with a value of  $\frac{w}{2R_{SH}v_0}$  is

employed to integrate the B3 current  $f(i) = \frac{\psi \frac{i_D^2}{l_{SW}^2} - 2}{\sqrt{\psi \frac{i_D^2}{l_{SW}^2} - 1}}$  to simulate such current-dependent behavior

equal to the instantaneous hot-spot resistance  $R_{HS}$  and will be used in (3.1).

$$\begin{cases}

\frac{\partial R_{HS}}{\partial t} = \frac{R_{SH}}{w} \frac{\partial l}{\partial t} \\

\frac{dl}{dt} = v_{HS} = 2v_0 \frac{\psi \left(\frac{i_D}{l_{SW}}\right)^2 - 2}{\sqrt{\psi \left(\frac{i_D}{l_{SW}}\right)^2 - 1}}

\end{cases} (3.2)$$

$$\begin{cases} \frac{dl}{dt} = v_{HS} = 2v_0 \frac{\psi\left(\frac{i_D}{I_{SW}}\right)^2 - 2}{\sqrt{\psi\left(\frac{i_D}{I_{SW}}\right)^2 - 1}} \end{cases}$$

(3.3)

where  $i_D$  is the current flowing in SNSPD kinetic inductance;  $v_0 = \frac{\sqrt{h_c \kappa/d}}{c}$  is the characteristic normal domain velocity;  $h_c$ ,  $\kappa$ , c,  $T_d$  and  $\rho$  are the parameters related to the SNSPD material;  $T_S$ is the bath temperature of the SNSPD substrate;  $\psi = \frac{\rho I_{SW}^2}{h_c w^2 d(T_d - T_S)}$  is the Stekly parameter which measures the relative role of Joule self-heating in superconductors [37];  $R_{SH}$  is the sheet resistance of the resistive state in SNSPD; w is the width of the nanowire; l is the length of the hot spot. If B2 gives an output of 1, the switch S1 will close, meaning that the SNSPD will return to its superconducting state, thus all the current will be directed to the ground, causing V(N3) to be equal to zero, and the resistive region will consequently vanish.

• The two subcircuits with I1 and B2 are not directly connected to the rest of the circuits. The I1 subcircuit offers an SNSPD input terminal that simulates the interface between an incoming photon and an SNSPD, while the B2 subcircuit is an affiliated circuit that monitors the SNSPD's state to give the operational logic to S1 to regulate the development of the hotspot resistance determined on C3.

#### 3.2. SNSPD SPICE Model Performance

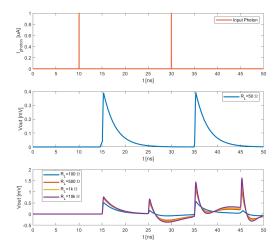

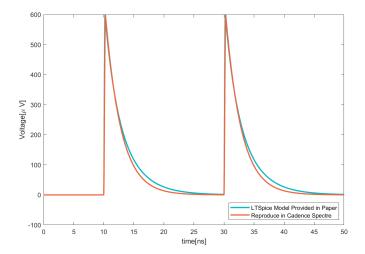

Since the circuit design in this work will be carried out in Cadence Spectre, it is essential in this section to compare the performance of the SNSPD dynamic model reproduced in Cadence Spectre against the reference SPICE model provided in [35]. The model has been implemented in Cadence Spectre (the spectreText code can be found in the Appendix B), but some parameters such as  $h_c$ ,  $\kappa$ , etc., are unknown and would require laboratory measurements to determine. Alternatively, we can fit to measurement data that are also used in [35]. The performance of the reproduced SNSPD model is demonstrated in 3.3. Model Limitations

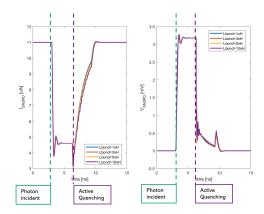

Figure 3.4. There are two consecutive photon hit events at t=10ns and t=30ns, and both Cadence Spectre (used in this work) and LTSpice (used by the [35]) show the expected SNSPD output response. The main difference is due to the performance of the different between Cadence Spectre and LTSpice, and the selection of the kinetic inductance  $L_k(t)$  where Cadence simulates with constant kinetic inductance, and LTSpice simulates with the varying  $L_k$ . However, this difference is not important for our use case since the slight discrepancy occurs during the falling edge, while this work mainly concentrates on the improvements of the rising edge, where the models match better. Moreover, the behavior of the falling edge will be different after the active quenching is implemented, which will be discussed in detail in Chapter 4. The circuit used for this simulation is the same as the one depicted in Figure 1.2. The dashed

**Figure 3.4:** Comparison between the model presented in [35] based on laboratory data and the reproduced model simulated in Cadence Spectre.

box representing SNSPD is replaced by the SNSPD model introduced above, which is connected in parallel with a  $R_L$  = 50  $\Omega$  load resistor and biased with  $I_{bias}$  = 15  $\mu$ A. The parameters associated with the SNSPD model, which is related to the SNSPD material, can be found in Appendix B.

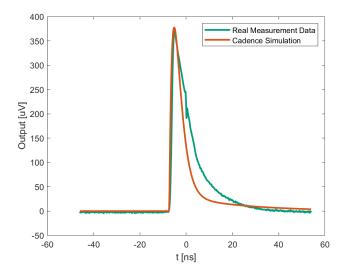

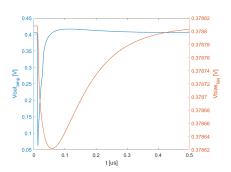

#### Comparison with the Laboratory Measurement Data

To further test the performance of the SNSPD model, a comparison between the simulation in Cadence Spectre and the real laboratory measurement data that is provided by *Pixel Photonics* [38] can be found in Figure 3.5. The simulation is still based on the same schematic in Figure 1.2 that the SNSPD is parallel connected to the load resistor. With  $R_L = 50~\Omega$  and the bias current of  $10~\mu$ A, the SNSPD can achieve the maximum output signal level of around 370 mV, rising edge slew rate of  $\sim 150~\text{MV/s}$ , and the recovery time of  $\sim 30~\text{ns}$ . Although the exact material parameters of SNSPD, such as device dimension, thermal conductivity  $\kappa$ , and heat capacity  $h_c$ , are still not known, the model can be tuned to closely match the measurement data due to the flexibility of these parameters in the model. By comparing the results, it can be seen that the main discrepancy is at the falling edge, where the time constant of  $\tau_{fall} \sim \frac{L_k(t)}{R_L}$  is smaller than in the real device. This trend is similar to the one shown in Figure 3.4. Therefore, it is reasonable to deduce that the difference is mainly due to the absence of the time-varying characteristic of  $L_k$  in the model.

#### 3.3. Model Limitations

There are several remarks about this dynamic model:

1.  $I_{SW}$  is employed rather than using the depairing critical current  $I_c$  to describe the current at which the device can no longer support a supercurrent. This is to stress that in practice, the depairing

3.3. Model Limitations

**Figure 3.5:** The comparison between the SNSPD model build in Cadence Spectre and real measurement data. Orange: simulation in Cadence Spectre; green: laboratory measurement data.

current is not the accurate factor that limits these devices and that vortex crossing, noise, and other elements may also contribute to the suppression of  $I_c$ .

- 2. The SNSPD SPICE model used in this work does not consider the physics of jitter, nor does it take into account the microscopic physics of hot-spot creation and the post-photon-arrival signal propagation delay in the nanowire. Additionally, the current  $I_{photon}$  used to simulate the photon-incident event may generate noise which could lead to false or missed counts, but this is not taken into consideration in the model.

- 3. The temperature dependence of the hot-spot resistance and the thermal parameters, which are not included in this model, can lead to afterpulses. However, the active quenching technique (see Section 2.2.4) should significantly suppress afterpulses.

In conclusion, the SNSPD model employed in Cadence Spectre is comparable to the LTSpice model presented in [35], with the distinction due to the constant  $L_k$  being negligible. Furthermore, the model encompasses a range of parameters related to the SNSPD's dimension and material properties, making it relatively simple to adjust to match experimental results. However, the model does not precisely replicate the electromagnetic transmission delay of the signal (for jitter performance), nor does it completely model the SNSPD kinetic inductance and thermoelectric characteristics of the hotspot, which may result in overlooking some nonidealities such as afterpulses. Additionally, future development should also take into account the effect from the photon side, including the statistical model of the photon and the noise in the  $I_{photon}$ .

# SNSPD Cryogenic Readout Circuit Design

This chapter will explain the detailed design process of the SNSPD cryogenic CMOS readout circuit. First, the development of the system architecture is introduced, which takes into account the quenching approach, the pad capacitance  $C_{pad}$ , the bondwire inductance  $L_{wire}$ , the load resistance (readout resistance)  $R_L$ , and the switch resistance  $R_{SW}$ . Then both the implementation of analog and digital subcircuits are discussed. An additional focus here is on the transistor parameters choice of the main amplifier and comparator with the derivation on their optimal transconductance. Finally, the performance of the system will be simulated and inspected.

## 4.1. System Overview

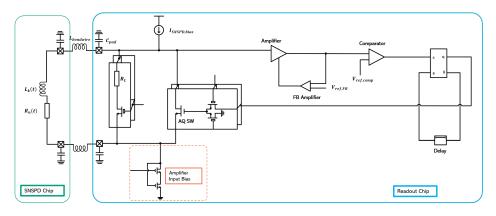

The overview schematic of the readout system is shown in Figure 4.1. The SNSPD chip and the readout chip will be placed near each other and connected through the bond wires  $L_{bondwire}$ . For the integration of diamond spin qubits with photonic circuits and CMOS electronics for routing, control, and readout of qubits on a large scale, these chips are expected to be 3D integrated in the future [39].

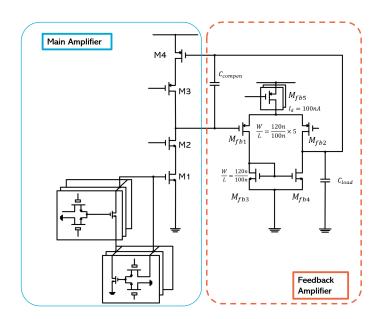

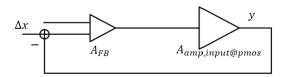

The biasing for SNSPD is indicated by the current source  $I_{SNSNPD,bias}$ , and the implementation at the transistor level can be seen in Section 4.2.1. When SNSPD is triggered, the voltage across the readout resistor  $R_L$  will be amplified by the main amplifier and the count decision will be made by the comparator (see Section 4.2.2). The count signal will be sent to the digital circuit (as seen in Section 4.3) and used to enable the active quenching process. The feedback amplifier (discussed in Section 4.2.6) is used to maintain the correct operating point of the amplifier. Eventually, the SNSPD is quenched by the active quenching switch (AQ SW) and returns to its superconducting state and waits for the next photon. The following sections will discuss the impact of some of the components such as pad capacitance, readout and active quenching switch resistance, etc.

Figure 4.1: Readout system schematic including SNSPD and readout analog and digital subcircuits.

#### 4.1.1. Architecture Decision

When it comes to implementing active quenching in practice, there are a few things to consider, which will be discussed in the following sections:

#### **Impact of Bias Disabling Methods**

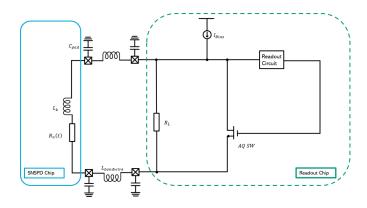

The proposed scheme to disable the SNSPD bias in [29] is to abruptly break the bias path. An alternative approach (used in this work) is to short the SNSPD and divert the bias current to ground as shown in the Figure 4.2. Instead of breaking the bias path, most of the bias current,  $I_{Bias}$ , will be diverted to the

Figure 4.2: Active quenching with short-bias scheme. Blue box: SNSPD chip; green dashed line box: cryogenic readout circuit. The pads and bondwires between these two chips are represented by  $C_{pad}$  and  $L_{bondwire}$ .  $R_L$  is the readout load resistor; AQ SW indicates the active quenching switch implemented by the NMOS. When the readout circuit successfully detects a photon signal, the active quenching switch (AQ SW) will be closed, shortening the bias current to the ground.

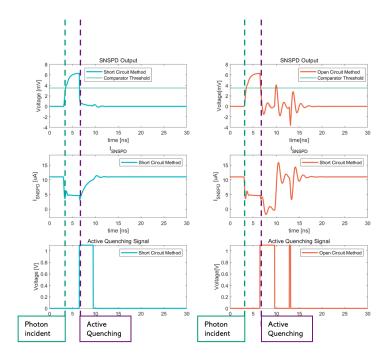

ground via the active quenching switch (AQ SW) when the readout circuit detects a photon signal. The comparison between the open and short bias scheme is shown in Figure 4.3, the top row displays the SNSPD output voltage for the short-scheme (blue curves) and open-scheme (orange curves). The middle row shows the current in SNSPD, and the bottom row shows the active quenching signal. When the voltage across the readout resistor exceeds the threshold, the comparator gives 1.1 V, and the SNSPD is correspondingly quenched. However, the open-bias scheme has a greater overshoot when the SNSPD is rebiased, which can lead to the voltage exceeding the comparator's threshold, resulting in an incorrect count. This is because when the short scheme is used,  $R_n(t)$  will be low at some point and the current will start flowing toward the SNSPD, whereas with the current switch scheme, all current is removed and then is instantaneously brought back to the SNSPD, as indicated in the SNSPD current plot during a time period of 5 ~ 10 ns. Therefore, the short-scheme is preferably used in this work instead.

#### Impact of Pads' Capacitance and Bondwires' Inductance

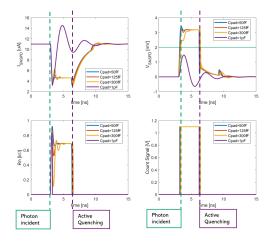

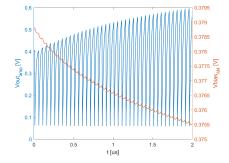

As can be seen in Figure 4.3, active quenching is beneficial in aiding SNSPD to return to the superconducting state; however, the oscillation and related overshoot can be a major problem, leading to false counts. Therefore, it is essential to investigate the effect of the capacitance of the SNSPD and the readout chip pad  $C_{pad}$  and the inductance of the bondwire  $L_{bondwire}$  (indicated in Figure 4.2), which are likely to be the main cause of such oscillations. As demonstrated in Figures 4.4 and 4.5, a larger pad capacitance has a greater impact on the readout response. As  $C_{pad}$  increases, the slew rate, which can be estimated by  $SR \approx \frac{I_{SNSPD}}{C_{pad}}$ , will decrease, resulting in a decrease in SNR and a deterioration in the jitter performance. When  $C_{pad}$  approaches 1 pF, the system does not function properly due to the large overshoot in the SNSPD current  $I_{SNSPD}$ . This is because when the overshoot is large enough, the current in the SNSPD can be below the latching current, causing the SNSPD to return to 0  $\Omega$  instead of being latched. This results in all the current flowing back to the SNSPD, which in turn causes the voltage across the load resistor to be too small to activate the comparator, as shown by the purple curves in Figure 4.4, while the effect of the bondwire is insignificant for the readout performance. In practice, a capacitance of approximately  $C_{pad} \sim 200$  fF and an inductance of around  $L_{bondwire} \sim 5$  nH are thought to be reasonable

**Figure 4.3:** Simulation results demonstrate that the open-bias quenching technique is less preferable for deactivating the SNSPD bias. The blue curves are the SNSPD output voltage, the current in the SNSPD, and the active quenching signal (from top to bottom) for the short-scheme and red curves represents the open-scheme; green curve is the comparator threshold. The photon hits t = 3ns and both schemes give a count signal. However, due to the more intense oscillation, the open-scheme is prone to produce other false counts (at  $t \approx 13$  ns in the bottom right plot).

approximations, which have also been demonstrated to be safe values based on these simulation results. Consequently, in the following simulations, we will use  $C_{pad} = 125$  fF and  $L_{bondwire} = 2$  nH.

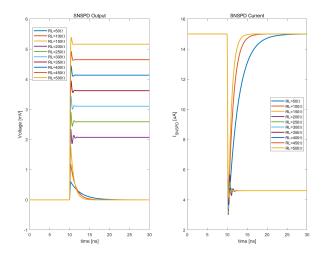

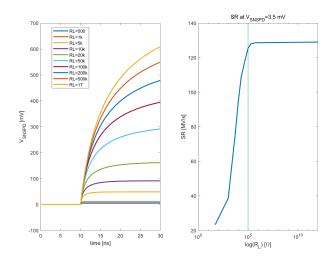

#### Impact of the Load Resistance

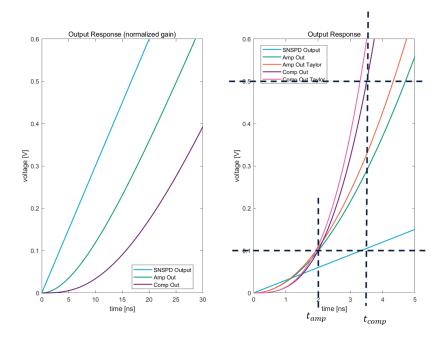

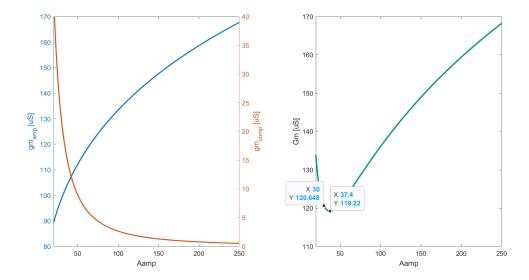

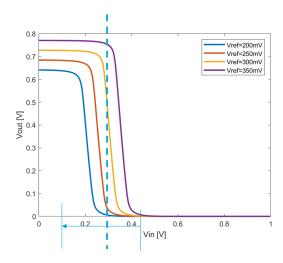

By varying the load resistance in the passive quenching scheme, we can determine the resistance at which latching occurs. In our SNSPD model ( $L_k(t) = L_k = 130$  nH,  $I_{bias} = 15$   $\mu$ A,  $I_{sw} = 18.5$   $\mu$ A), this value is estimated to be  $R_{latch} \approx 200$   $\Omega$ , as shown in Figure 4.6. Here,  $I_{SW}$  denotes the threshold current that when the current in SNSPD is greater than this value, the SNSPD will be triggered. However, the amplifier requirement and the jitter performance of the system are not optimal when using passive quenching with  $R_L \approx R_{latch} = 200$   $\Omega$ . Although active quenching allows for a large load resistance, one should take into account the noise that the resistor can introduce, which can have a detrimental effect on jitter. However, when at cryogenic temperatures, the thermal noise contribution can be significantly reduced. In principle, it is preferable to make the jitter as low as possible, which is beneficial for both the system performance and also the possible design headroom. Jitter can be defined as:

$$\sigma_{jitter} = \frac{\delta V_{noise}}{SR} \tag{4.1}$$

where  $\delta V_{noise}$  is the rms noise amplitude noise of the electronic circuit;  $SR = \frac{\partial V}{\partial t}|_{V=V_{decision}}$ . This means that the slew rate (SR) should be as high as possible. As shown in Figure 4.7 (passive quenching is used for the purpose of providing a clearer view of how  $R_L$  affects the output of the SNSPD), if the comparator threshold voltage is assumed to be  $V_{decision} = 3.5 mV$ , the SR at this point will nearly reach saturation after  $R_L \gtrsim 10 k\Omega$ , which implies that it is possible for choosing  $R_L$  as high as possible, but one should be aware of the increasing in noise and potential oscillations it may cause when  $R_L$  is relatively large, while the improvements on SR are limited. The possible explanation would be that since  $R_L$  is extremely large while  $R_n$  experiencing a growth starting from 0, there will be a very small portion of

**Figure 4.4:** Impact of the pad capacitance  $C_{pad}$  on the active quenching performance. Upper left: Current in SNSPD; upper right: Output voltage across the readout resistor  $R_L = 500\Omega$ ; bottom left: hotspot resistance of SNSPD; bottom right: count signal.

Figure 4.5: Impact of the bond wire inductance  $L_{bondwire}$  on the active quenching performance. Left: Current in SNSPD; right: Output voltage across the readout resistor  $R_L = 500\Omega$ .

**Figure 4.6:** By sweeping the load resistance  $R_L$ , the system was observed to latch when  $R_L \ge 200 \ \Omega$ .

current that can flow into the readout path. However, such a small current will still generate a 3.5 mV voltage on this large  $R_L$ , and the time to achieve this voltage value becomes unfigurable when  $R_L$  is large, so that the SR saturates based on  $SR = \frac{3.5 mV}{t |_{V=3.5 mV}}$ .

**Figure 4.7:** Impact of the readout resistor  $R_L$  on SNSPD readout performance. Left: Output voltage across different  $R_L$ . In each case, the SNSPD latches. Right: Slew rate at  $V_{decision} = 3.5$ mV with respect to  $R_L$  (in log scale), the green line indicates the value of  $R_L$  at which the SR will start saturating.

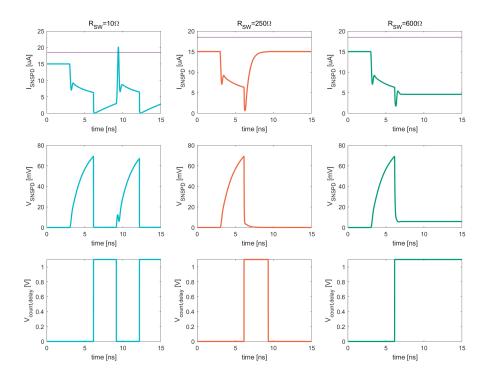

#### **Impact of the Active Quenching Switch Resistance**

The resistance of the active quenching switch  $R_{SW}$  is also a significant factor in the readout process. As demonstrated in Figure 4.8, simulations were conducted with three different closed-switch resistances:  $R_{SW}=10~\Omega$ ,  $250~\Omega$ ,  $600~\Omega$ . At t=3 ns, a photon is absorbed by the SNSPD, causing it to enter the normal resistive mode and then the current  $I_{SNSPD}$  flows into the readout resistor  $R_L$ , resulting in a sharply increasing voltage signal. When the voltage reaches the comparator threshold, the active quenching switch in parallel with the SNSPD and its load resistor will be activated after a delay of 3 ns. This will cause most of the current in the load resistor and SNSPD to be diverted to the switch path and eventually to the ground, resulting in the SNSPD returning to its superconducting state  $(R_n(t) \to 0~\Omega)$ . The significance of the closed switch resistance  $R_{sw}$  will be evident at this point. Since  $R_n(t) \sim 0~\Omega$ , there is a potential difference between the switch path and the SNSPD. The larger  $R_{sw}$  is, the greater the potential difference, thus the quicker the current that was just diverted into the switch path will flow back to the SNSPD.

As demonstrated in the first row of Figure 4.8, the transient SNSPD current waveform with different closed switch resistances reveals that during the time period  $t \in [6ns, 9ns]$ , when the current in the switch path returns to the SNSPD due to the potential difference, the speed of this current return in the  $R_{SW} = 10~\Omega$  case is much slower than in the  $R_{SW} = 250~\Omega$  case, leading to a more intense overshoot at the rebiasing operation (t = 9~ns, the switch opens). As a result, a false count is generated, which can be found in the corresponding blue curve count signal plot at left bottom corner. This flowback process is quite similar to the resetting stage in the passive quenching system. As  $R_{SW}$  increases, the rate of current flowing back from the switch path increases, eventually leading to a situation where the heat generated by the current in the SNSPD is equal to the heat dissipated to the substrate. This causes the SNSPD to remain in a resistive state, which means that the device is latched (as seen in  $R_{SW} = 600~\Omega$  in Figure 4.8), making the active quenching proposed previously ineffective. Therefore, the requirement on  $R_{SW}$  should be  $R_{sw} \parallel R_L < R_{latch}$  to prevent latching. Additionally,  $R_{sw} \parallel R_L$  should not be too small due to the risk of false counts caused by overshoot.

**Figure 4.8:** Impact of the active quenching switch resistance  $R_{SW}$  on the readout performance. Top row: Current in SNSPD  $I_{SNSPD}$ ; middle row: output voltage across  $R_L = 10 \text{k}\ \Omega$ ; bottom row: count signal with delay of  $t_{delay} = 3$  ns. The plots of the same color in different columns represent the different values of  $R_{SW}$ . The purple line in the first row indicates the current  $I_{SW}$  that SNSPD will switch to the resistive state. Photon hits at t=3 ns and active quenching is enballed at t=6 ns.

# 4.2. Analog Sub-circuits

In this section, the design consideration of the analog part of the readout system shown in Figure 4.1 will be discussed.

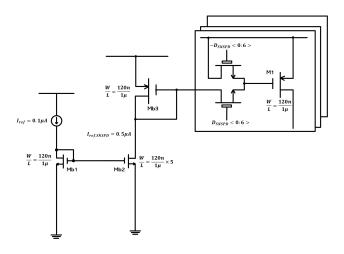

### 4.2.1. SNSPD Biasing

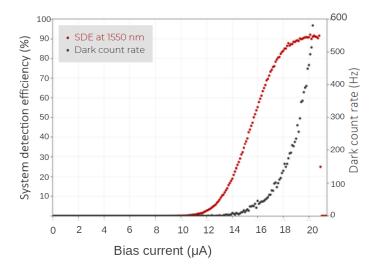

To begin with, the SNSPD should be correctly biased. The headroom of the bias current  $I_{SNSPD,bias}$  and the switching current  $I_{sw}$  is of great importance when biasing the SNSPD, as it is necessary to balance the detection efficiency and the risk of false triggering (higher  $I_{SNSPD,bias}$  means higher detection efficiency, but also a higher possibility of false triggering due to noise). However,  $I_{sw}$  is mostly dependent on the design and material of the SNSPD itself (see Section 3.1), and the preference value of  $I_{SNSPD,bias}$  will usually be provided by the manufacturer. As is demonstrated in Figure 4.9, when the bias current is set between 16 and 18  $\mu$ A, the system can achieve high detection efficiency while maintaining a relatively low dark count rate. Consequently, it is empirically preferable to set the SNSPD bias current to be:

$$\begin{cases} I_{SNSPD,bias} \in [80\%, 90\%] I_{sw} \\ \Delta_{I_{SNSPD,bias}} = \pm 1\mu A \end{cases}$$

(4.2)

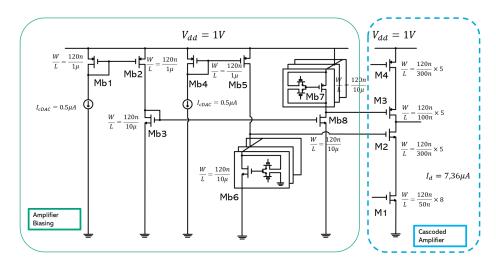

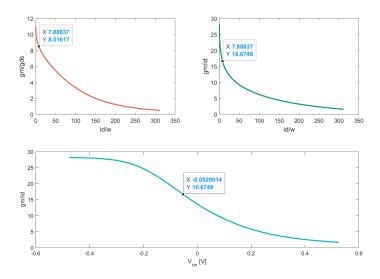

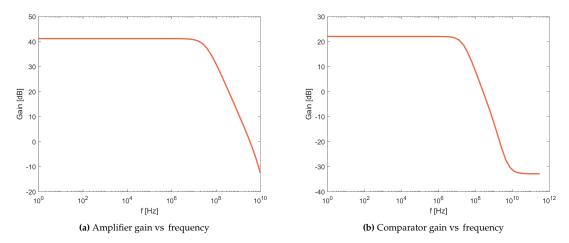

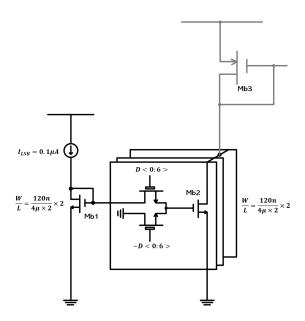

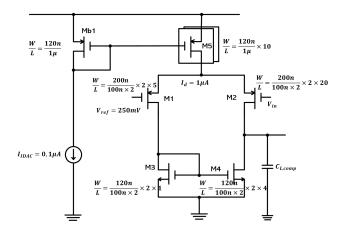

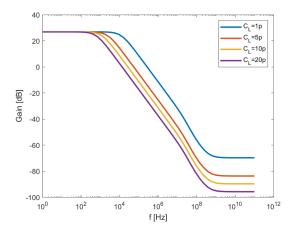

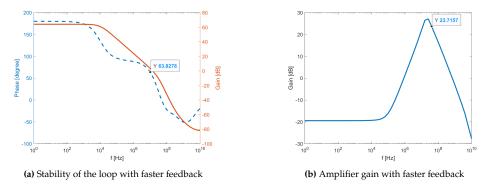

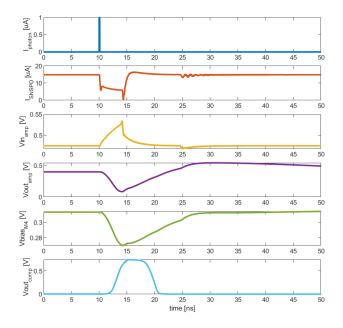

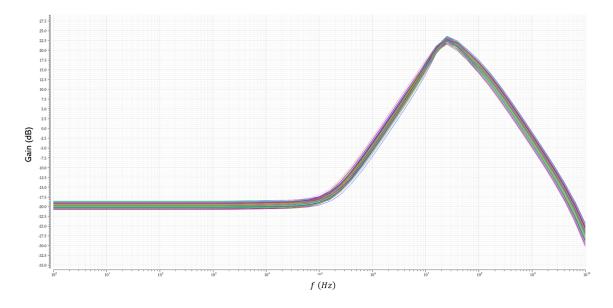

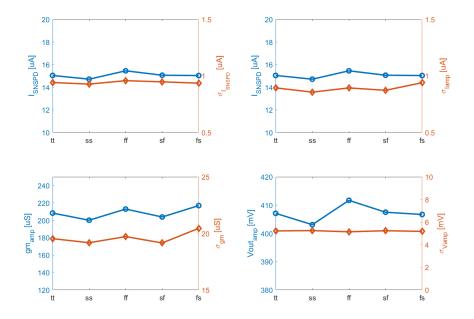

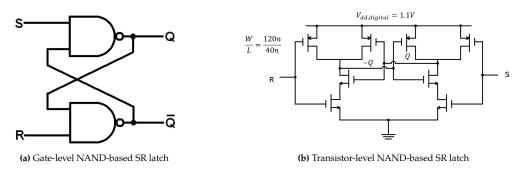

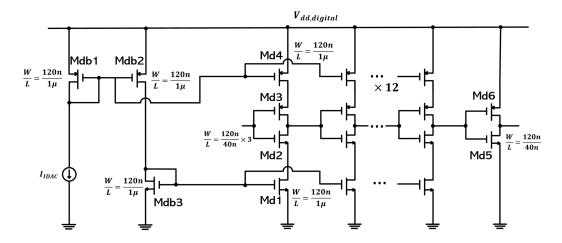

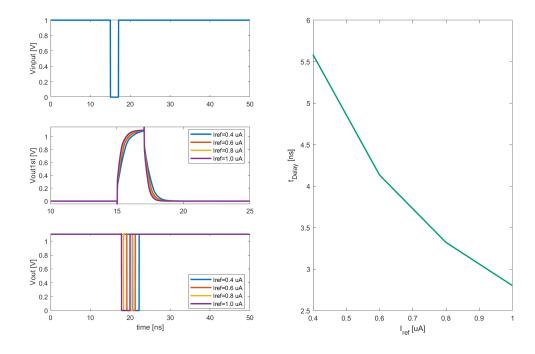

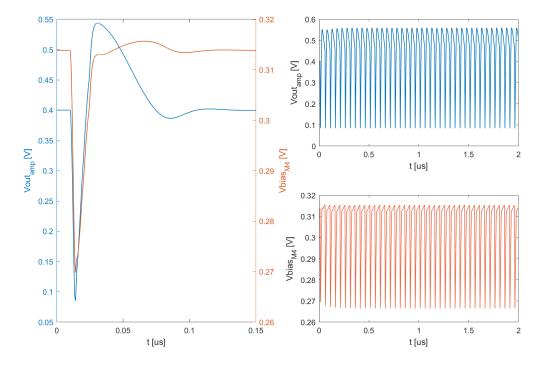

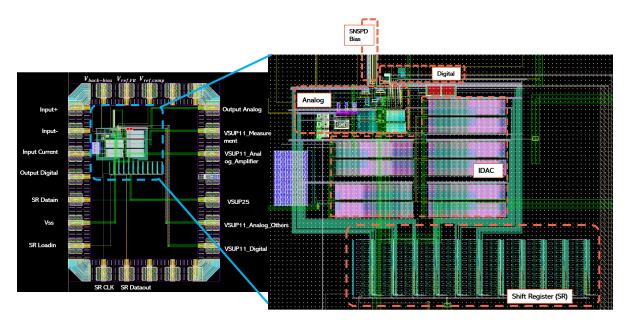

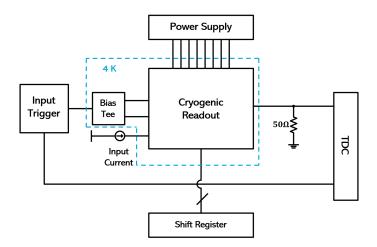

In this work, the SNSPD switch current were set to  $I_{sw} = 18.5 \,\mu\text{A}$  and the bias current  $I_{SNSPD,bias} = 15 \,\mu\text{A}$  which is approximately 81.2 % of  $I_{sw}$ . These values are flexible and can be adjusted as the paramters in the SNSPD model.