## Cryogenic CMOS Characterization for Quantum Computer Applications

't Hart, P.A.

10.4233/uuid:0ab4ca6c-dc69-4207-970f-d3b9f0d9c5b4

**Publication date**

**Document Version** Final published version

't Hart, P. A. (2022). Cryogenic CMOS Characterization for Quantum Computer Applications. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:0ab4ca6c-dc69-4207-970fd3b9f0d9c5b4

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# **Cryogenic CMOS Characterization**

for Quantum Computer Applications

P.A. 't Hart

# **Cryogenic CMOS Characterization**

## for Quantum Computing Applications

Cryogene CMOS Karakterisering voor Kwantumcomputer Applicaties

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op maandag 21 november 2022 klokke 1230h

door

## Pascal Alexander 't HART

Electrotechnisch ingenieur geboren te Gouda.

Dit proefschrift is goedgekeurd door de promotors:

Dr.ir. F. Sebastiano Prof.dr. A. Vladimirescu

Samenstelling der promotiecomissie:

Rector Magnificus Voorzitter

Dr.ir. F. Sebastiano Technische Universiteit Delft, promotor

Prof.dr. A. Vladimirescu UC Berkeley, co-promotor

Onafhankelijke leden:

Prof.dr.ir. L.M.K. Vandersypen Technische Universiteit Delft Technische Universiteit Delft

Prof.dr. D. Zito Aarhus Universitet

Prof.dr. S. van Waasen

Universität Duisburg-Essen

Dr.ir. H.P. Tuinhout

NXP Semiconductors

Keywords: Cryogenic, CMOS, Modeling, Device Mismatch, Self-heating

Copyright ©2022 P.A. 't Hart. Alle rechten voorbehouden. Niets uit deze uitgave mag worden verveelvoudigd, opgeslagen in een geautomatiseerd gegevensbestand, of openbaar gemaakt worden, in enige vorm of op enige wijze, hetzij elektronisch, mechanisch, door fotokopieen, opnamen, of op enig andere manier, zonder voorafgaande schriftelijke toestemming van de rechthebbende(n).

Copyright © 2022 P.A. 't Hart. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, by photocopying, recording, or otherwise, without the prior permission in writing from the proprietor(s).

ISBN/EAN: 978-94-6419-629-0

Monday Begins on Saturday Понедельник начинается в субботу - **Boris and Arkady Strugatsky**

# **Contents**

| 1 | Introduction                                   |                                                       |                                                   |    |  |  |  |

|---|------------------------------------------------|-------------------------------------------------------|---------------------------------------------------|----|--|--|--|

|   | 1.1                                            | 1 The Quest for Faster Computation                    |                                                   |    |  |  |  |

|   | 1.2                                            | ·                                                     |                                                   |    |  |  |  |

|   | 1.3                                            |                                                       |                                                   |    |  |  |  |

|   | 1.4                                            | Object                                                | tive and Scope of This Thesis                     | 4  |  |  |  |

|   | 1.5                                            | isation of This Thesis                                | 4                                                 |    |  |  |  |

| 2 | Cryogenic Device Characterization and Modeling |                                                       |                                                   |    |  |  |  |

|   | 2.1                                            | State-of-the-art of Cryogenic Device Characterization |                                                   |    |  |  |  |

|   | 2.2                                            | Cryoge                                                | Cryogenic Characterization Methods                |    |  |  |  |

|   |                                                | 2.2.1                                                 | Dipstick                                          | 11 |  |  |  |

|   |                                                | 2.2.2                                                 | Cryogenic Probe Station                           | 12 |  |  |  |

|   |                                                | 2.2.3                                                 | Dilution Refrigerator                             | 13 |  |  |  |

|   | 2.3                                            | Cryoge                                                | enic MOSFET Behaviour                             | 15 |  |  |  |

|   |                                                | 2.3.1                                                 | Threshold Voltage                                 | 15 |  |  |  |

|   |                                                | 2.3.2                                                 | Mobility                                          | 18 |  |  |  |

|   |                                                | 2.3.3                                                 | Subthreshold Slope                                | 20 |  |  |  |

|   |                                                | 2.3.4                                                 | Kink Effect                                       | 21 |  |  |  |

|   |                                                | 2.3.5                                                 | AC Behaviour                                      | 23 |  |  |  |

|   |                                                | 2.3.6                                                 | Noise                                             | 24 |  |  |  |

|   |                                                | 2.3.7                                                 | Device Mismatch                                   | 24 |  |  |  |

|   |                                                | 2.3.8                                                 | Self-Heating                                      | 24 |  |  |  |

|   | 2.4                                            | enic 40-nm MOSFET Modeling                            | 25                                                |    |  |  |  |

|   |                                                | 2.4.1                                                 | ANN-based Modeling for Cryo-CMOS                  | 25 |  |  |  |

|   |                                                | 2.4.2                                                 | Characterization Structures and Measurement Setup | 27 |  |  |  |

|   |                                                | 2.4.3                                                 | Measurement Results and Model Validation          | 29 |  |  |  |

|   |                                                | 2.4.4                                                 | Conclusion                                        | 30 |  |  |  |

|   | 2.5                                            | Conclu                                                | usions                                            | 31 |  |  |  |

| 3 | Cryogenic Device Matching 4                    |                                                       |                                                   |    |  |  |  |

|   | 3.1                                            |                                                       |                                                   |    |  |  |  |

|   | 3.2                                            | Strong                                                | g-Inversion Matching                              | 45 |  |  |  |

|   |                                                | 3.2.1                                                 | Experimental Setup                                | 46 |  |  |  |

|   |                                                | 3.2.2                                                 |                                                   | 49 |  |  |  |

## ii | Contents

|     |                                       | 3.2.3   | Strong-Inversion Mismatch Modeling          | 50  |  |  |  |

|-----|---------------------------------------|---------|---------------------------------------------|-----|--|--|--|

|     |                                       | 3.2.4   | Experimental Results                        | 51  |  |  |  |

|     |                                       | 3.2.5   | Discussion                                  | 52  |  |  |  |

|     |                                       | 3.2.6   | Conclusion                                  | 56  |  |  |  |

|     | 3.3                                   | Subthr  | reshold Matching                            |     |  |  |  |

|     |                                       | 3.3.1   | Experimental Setup                          |     |  |  |  |

|     |                                       | 3.3.2   | Parameter Extraction                        | 61  |  |  |  |

|     |                                       | 3.3.3   | Subthreshold Mismatch Modeling              |     |  |  |  |

|     |                                       | 3.3.4   | Experimental Results                        |     |  |  |  |

|     |                                       | 3.3.5   | Discussion                                  | 69  |  |  |  |

|     |                                       | 3.3.6   | Conclusion                                  |     |  |  |  |

|     | 3.4                                   | Stress  | Effects and Dummy Placement                 | 73  |  |  |  |

|     |                                       | 3.4.1   | Experimental Setup and Results              |     |  |  |  |

|     |                                       | 3.4.2   | Discussion                                  |     |  |  |  |

|     |                                       | 3.4.3   | Conclusion                                  | 77  |  |  |  |

|     | 3.5                                   | Conclu  | ısions                                      |     |  |  |  |

|     |                                       |         |                                             |     |  |  |  |

| 4   |                                       |         | -Heating at Cryogenic Temperatures          | 85  |  |  |  |

|     | 4.1                                   | Introd  | uction                                      | 85  |  |  |  |

|     | 4.2                                   |         | tructures and Measurement Setup             |     |  |  |  |

|     |                                       | 4.2.1   | Gate Test Structure                         |     |  |  |  |

|     |                                       | 4.2.2   | Diode Test Structures                       |     |  |  |  |

|     |                                       | 4.2.3   | Measurement Setup                           |     |  |  |  |

|     |                                       | 4.2.4   | Calibration                                 |     |  |  |  |

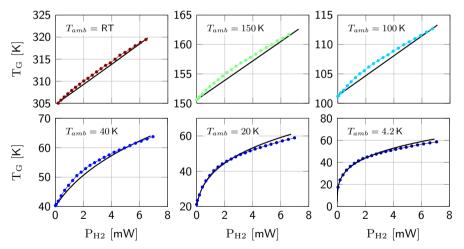

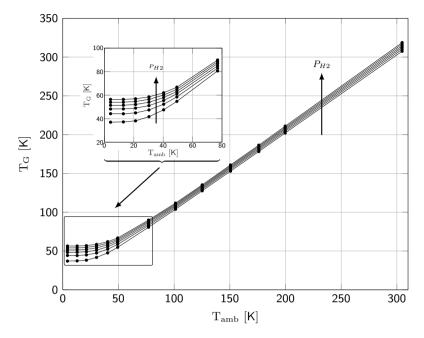

|     | 4.3                                   |         | mental Results                              |     |  |  |  |

|     |                                       | 4.3.1   | Gate-resistance Measurements                |     |  |  |  |

|     |                                       | 4.3.2   | Diode Measurements                          |     |  |  |  |

|     | 4.4                                   |         | eating: Discussion, Modeling and Take-Aways |     |  |  |  |

|     |                                       | 4.4.1   | Diode-Based Temperature Sensing             |     |  |  |  |

|     |                                       | 4.4.2   | Channel Temperature Sensing                 |     |  |  |  |

|     |                                       | 4.4.3   | Spatial Thermal Measurements                |     |  |  |  |

|     |                                       | 4.4.4   | Ultra-Wide-Temperature Self-Heating Model   |     |  |  |  |

|     |                                       | 4.4.5   | Self-Heating Impact on Cryo-CMOS Circuits   |     |  |  |  |

|     | 4.5                                   | Conclu  | ısions                                      | 104 |  |  |  |

| 5   | Con                                   | clusion |                                             | 111 |  |  |  |

| 3   | 5.1                                   |         | ch Overview and Contributions               |     |  |  |  |

|     | 5.2                                   |         |                                             |     |  |  |  |

|     | 5.2                                   | Future  | . Work                                      | 113 |  |  |  |

| Ρu  | blicat                                | tions   |                                             | 115 |  |  |  |

|     |                                       |         |                                             |     |  |  |  |

| Sil | Silicon Real-Estate                   |         |                                             |     |  |  |  |

| Su  | Summary Samenvatting Acknowledgements |         |                                             |     |  |  |  |

| Sa  |                                       |         |                                             |     |  |  |  |

| Ac  |                                       |         |                                             |     |  |  |  |

About the Author 131

[pascalthart@fernet  $\sim$ ]\$ cd TSMC\_Mismatch [pascalthart@fernet  $\sim$ /TSMC\_mismatch]\$ source sourceme [pascalthart@fernet  $\sim$ /TSMC\_mismatch]\$ virtuoso& [pascalthart@fernet  $\sim$ /TSMC\_mismatch]\$

# Chapter 1

## Introduction

## 1.1 The Quest for Faster Computation

Humans in general are not optimized for carrying out repetitive tasks, such as those required in large calculations: our attention is nonlinear, time variant and subject to many external factors, making us inefficient and error prone. Since ancient times people have been looking for ways to automate these tasks and came up with solutions in the form of what nowadays would be called a computer. One of the first computers, the Antikythera mechanism, was based on pure mechanics and most likely used for calculations related to astronomy [1]. As time progressed, electromechanical computers emerged, such as the Bombe, which was built specifically for Enigma deciphering [2]. Later on, the vacuum tube was invented and even larger machines were built, capable of faster and more complex calculations. A prime example of such a machine is the Electronic Numerical Integrator and Computer (ENIAC), used in the development of thermo-nuclear weapons [3]. Finally, the transistor was invented, leading to the development of CMOS, which enabled the speed and level of integration required to build today's (super)computer. An interesting thing to note is that the driving force behind the development of faster and higher capacity computers is strongly coupled to mankind's favourite occupations: waging wars, optimizing financial gains and gaming.

Although modern data centers are quite impressive, both in terms of their size and computing power, a certain class of problems is intractable even for classical supercomputers. Searching large data sets, prime factorization, but also modeling of complex systems, such as those found in molecules or the weather, are either too computationally complex or require a prohibitive amount of time to complete. Quantum computation is a new computing paradigm that holds the promise of solving such problems [4, 5]. At the basis of the quantum computer lies the quantum bit (qubit), which, in addition to the '0' and '1' state of the classical bit, can assume a composite state that is a superposition of two base states denoted by

$|0\rangle$  and  $|1\rangle$ . The state of a qubit can thus be represented by  $|\psi\rangle=\alpha|0\rangle+\beta|1\rangle$ , where  $\alpha$  and  $\beta$  are complex coefficients, satisfying the condition  $|\alpha|^2+|\beta|^2=1$ . All possible states of the qubit lie on a unit sphere, also known as a Bloch sphere, with the  $|0\rangle$  and  $|1\rangle$  base states located at the north and south pole, respectively. The two poles are equivalent to the two states of the classical bit, while all the composite states between the poles are exclusively available in qubits. These superposition states allow the quantum computer to encode much more information per bit as compared to a classical computer. A second property specific to qubits is entanglement. When a change in one qubit affects other qubits in a predictable way, these qubits are said to be correlated or entangled. Specific quantum algorithms exploit the existence of these quantum effects, i.e., superposition and entanglement, to enable an exponential computational speed up compared to its classical counterpart.

In order for these quantum effects to arise, and for the quantum states to be detectable, the qubits typically need to be cooled down to extremely low temperatures in the range between 10 mK and 100 mK. In order to perform quantum computation, the state of the qubits needs to be controlled and read-out by classical electronics, capable of the generation and measurement of specific electrical signals. Since the qubit state deteriorates in time, after an interval known as decoherence time, the controller in addition to this sensing time constraint, has as additional task to correct the errors introduced in the qubit state due to decoherence (Quantum Error Correction, QEC) during calculations [6].

## 1.2 Cryo-CMOS as Quantum Computer Enabler

The quantum computers of today comprise only a few tens of qubits, which are directly connected to room-temperature equipment located outside of the cryogenic refrigerator. This equipment consists of large commercial, or custom made signal sources and digitizers. Wires carry the signals from the room-temperature electronics, through the refrigerator, to the qubits that sit at deep-cryogenic temperatures.

This is still a workable solution for the small number of qubits in a research setting. However, in order to run any useful quantum algorithm, thousands to even millions of physical qubits are required [6, 7], making this approach unfeasible. The current approach can be compared with connecting a mega-pixel CCD through meters-long interconnect to read-out circuits: this solution does not scale, consumes a prohibitive amount of space (both the wires in the fridge and the equipment outside of it), is extremely costly and poses many reliability issues.

A possible approach that tackles most of the above-mentioned challenges, is the implementation of the control and read-out electronics into an integrated circuit that can be placed close to the qubits. This forces the controller to operate at deep-cryogenic temperatures comparable to those of the qubits [8, 9, 10, 11, 12, 13].

Nanometer CMOS is the platform of choice for the cryo-controller by virtue of its high level of integration and maturity, enabling the complex circuits required for the generation, detection and processing of the electrical signals by the controller. The key features of CMOS that make it a perfect fit for this application are its high speed of operation required for handling the microwave signals, and its power efficiency, which is of prime importance for operating within the limited power budget of the refrigerator. Most importantly, CMOS was proven to operate reliably down to deep-cryogenic temperatures [14]. This opens up the possibility to co-integrate the controller and the solid-state qubits onto a single substrate, enabling a scalable quantum computer.

These CMOS properties enable the design of cryogenic circuits in theory; however, in practice, designers need additional information on the low-temperature behaviour of MOSFETs in order to design circuits that operate as intended in a cryogenic environment. This behaviour is captured in compact models, used for simulating the circuits to ensure that the specifications are met.

#### The Importance of Cryogenic Device Modeling 1.3

Device characteristics at cryogenic temperatures can deviate significantly from their room temperature behaviour. For example, the threshold voltage of a MOSFET can increase by more than 100 mV when it is cooled down to 4.2 K, as shown in this thesis. If a designer is not aware of this shift, circuits that work as intended at room temperature can potentially fail at deep-cryogenic temperatures due to the resulting change in bias points, or even due to devices that are unable to be switched on.

Device characterization is an indispensable step in building models for circuit designers. Foundries characterize their technology over the standard military temperature range (-55 to 125 °C) and generally do not supply compact models (vet) that are valid at deep-cryogenic temperatures.

Therefore, designers of cryogenic circuits have to rely on back-of-the-envelope calculations and must build in margins to allow for parameter shifts, as they are unable to fully simulate their designs with use of the existing electrical simulators. These margins cause circuits to most likely occupy more silicon area than required and thus operate at lower speeds and with increased power dissipation compared to an optimized circuit. As the power budget is severely limited, this is a very important challenge of (current) cryogenic circuit design. Worst of all, circuits deviating from the stringent specifications for quantum control can lead to lower fidelity of quantum operations [15].

In order to overcome these challenges, cryogenic device characterization needs to be carried out, to investigate and capture the impact of low temperatures on different device parameters. A convenient temperature to operate cryogenic circuits at, is that of liquid helium, which lies around 4.2 K. Therefore, most characterizations

#### 4 | Chapter 1. Introduction

are carried-out at this temperature. Effort was already devoted to characterization and modeling at these temperatures by other groups, see Chapter 2 for an extensive overview. However, not much attention was spent on the impact of these extreme temperatures on device matching and self-heating in advanced processes. The work presented in this thesis, therefore, focuses on the design and characterization of test chips in an advanced 40-nm process, and the subsequent modeling of device mismatch and self-heating at cryogenic temperatures.

## 1.4 Objective and Scope of This Thesis

The objective of this thesis is to gain more insight into cryogenic MOSFET behaviour, with the aim to build models to be used by circuit designers developing the cryogenic controller. These models involve the primary DC behaviour and secondary effects such as device matching and self-heating.

In order to attain this objective, multiple dedicated test structures were designed and fabricated in a 40-nm bulk CMOS process, which is the intended platform for the cryogenic controller. All measurements carried out and presented in this thesis were performed on these 40-nm bulk CMOS test structures. All characterizations were carried out at DC in the temperature range from 300 K down to 4.2 K.

## 1.5 Organisation of This Thesis

This thesis is organized as follows. Chapter 2 details the cryogenic device characterization and modeling of  $I_D$ - $V_G$  and  $I_D$ - $V_D$  curves measured on large arrays of MOSFETs. The tools available for cryogenic characterization of test samples are described, followed by a summary of the low-temperature impact on the most common MOSFET parameters. The chapter concludes with the DC modeling of a 40-nm bulk CMOS process, employing Artificial Neural Network training.

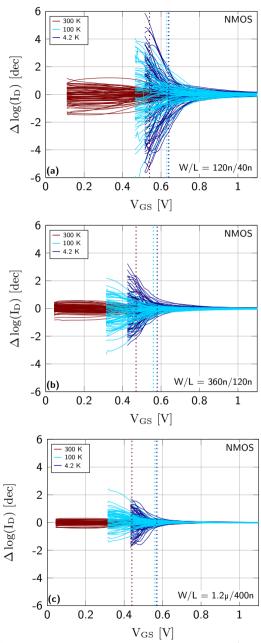

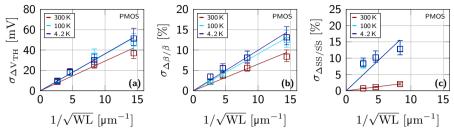

In Chapter 3 an extensive device mismatch study is presented of devices operated from 300 K down to 4.2 K. This chapter is split into two parts. The first part focuses on devices operated in the moderate- to strong-inversion regime, while the second part investigates specifically the matching behaviour of devices biased in the subthreshold regime. Models are presented able to predict drain-current mismatch in all regions of operation.

Chapter 4 presents an in-depth study on the self-heating of devices in a cryogenic environment. The channel temperature of a MOSFET as function of dissipated power and ambient temperature is extracted and modeled. To gain more insight into possible electro-thermal coupling between circuits, a spatial temperature profile up to  $30\,\mu m$  from the dissipating devices was measured.

Finally, conclusions are drawn and some suggestions for future work are given in Chapter 5.

# **Bibliography**

- [1] K. Efstathiou and M. Efstathiou, "Celestial Gearbox," *Mechanical Engineering* (*JEM*), vol. 140, no. 09, pp. 31–35, 09 2018.

- [2] G. Welchman, "The Hut Six Story: Breaking the Enigma Codes." M.& M.Baldwin, 1982.

- [3] H. H. Goldstine and A. Goldstine, "The Electronic Numerical Integrator and Computer (ENIAC)," *Mathematics of Computation*, vol. 2, pp. 97–110, 1946.

- [4] L. K. Grover, "A Fast Quantum Mechanical Algorithm for Database Search," in Proceedings of the Twenty-Eighth Annual ACM Symposium on Theory of Computing (STOC). New York, NY, USA: Association for Computing Machinery, 1996, p. 212–219.

- [5] P. Shor, "Algorithms for Quantum Computation: Discrete Logarithms and Factoring," in *Proceedings 35th Annual Symposium on Foundations of Computer Science (ASFCS)*, 1994, pp. 124–134.

- [6] A. G. Fowler, M. Mariantoni, J. M. Martinis, and A. N. Cleland, "Surface Codes: Towards Practical Large-Scale Quantum Computation," *Phys. Rev.* A, vol. 86, p. 032324, Sep 2012.

- [7] D. Wecker, B. Bauer, B. K. Clark, M. B. Hastings, and M. Troyer, "Gate-Count Estimates for Performing Quantum Chemistry on Small Quantum Computers," *Phys. Rev. A*, vol. 90, p. 022305, Aug 2014.

- [8] B. Patra, R. M. Incandela, J. P. G. van Dijk, H. A. R. Homulle, L. Song, M. Shahmohammadi, R. B. Staszewski, A. Vladimirescu, M. Babaie, F. Sebastiano, and E. Charbon, "Cryo-CMOS Circuits and Systems for Quantum Computing Applications," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 53, no. 1, pp. 309–321, 2018.

- [9] J. M. Hornibrook, J. I. Colless, I. D. Conway Lamb, S. J. Pauka, H. Lu, A. C. Gossard, J. D. Watson, G. C. Gardner, S. Fallahi, M. J. Manfra, and D. J.

- Reilly, "Cryogenic Control Architecture for Large-Scale Quantum Computing," *Phys. Rev. Applied*, vol. 3, p. 024010, Feb 2015.

- [10] H. Homulle, S. Visser, B. Patra, G. Ferrari, E. Prati, C. G. Almudéver, K. Bertels, F. Sebastiano, and E. Charbon, "Cryo-CMOS Hardware Technology: a Classical Infrastructure for a Scalable Quantum Computer," in *Proceedings of the ACM International Conference on Computing Frontiers (ICCF)*. New York, NY, USA: Association for Computing Machinery, 2016, p. 282–287.

- [11] E. Charbon, F. Sebastiano, A. Vladimirescu, H. Homulle, S. Visser, L. Song, and R. M. Incandela, "Cryo-CMOS for Quantum Computing," in *2016 IEEE International Electron Devices Meeting (IEDM)*, 2016, pp. 13.5.1–13.5.4.

- [12] E. Charbon, F. Sebastiano, M. Babaie, A. Vladimirescu, M. Shahmohammadi, R. B. Staszewski, H. A. Homulle, B. Patra, J. P. van Dijk, R. M. Incandela, L. Song, and B. Valizadehpasha, "Cryo-CMOS Circuits and Systems for Scalable Quantum Computing," in 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017, pp. 264–265.

- [13] F. Sebastiano, H. Homulle, B. Patra, R. Incandela, J. van Dijk, L. Song, M. Babaie, A. Vladimirescu, and E. Charbon, "Cryo-CMOS Electronic Control for Scalable Quantum Computing," in 2017 54th ACM/EDAC/IEEE Design Automation Conference (DAC), 2017, pp. 1–6.

- [14] R. M. Incandela, L. Song, H. Homulle, E. Charbon, A. Vladimirescu, and F. Sebastiano, "Characterization and Compact Modeling of Nanometer CMOS Transistors at Deep-Cryogenic Temperatures," *IEEE Journal of the Electron Devices Society (JEDS)*, vol. 6, pp. 996–1006, 2018.

- [15] J. van Dijk, E. Kawakami, R. Schouten, M. Veldhorst, L. Vandersypen, M. Babaie, E. Charbon, and F. Sebastiano, "Impact of Classical Control Electronics on Qubit Fidelity," *Phys. Rev. Applied*, vol. 12, p. 044054, Oct 2019.

# Chapter 2

# Cryogenic Device Characterization and Modeling

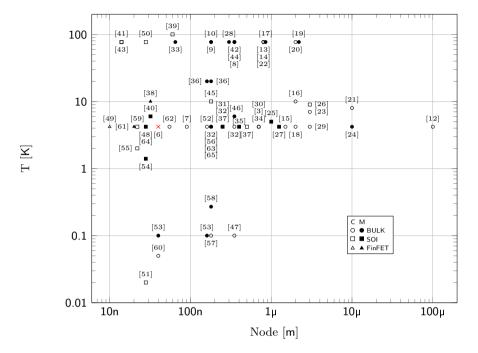

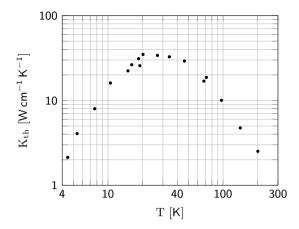

The introduction of CMOS in 1959 enabled many new applications that were previously unattainable with discrete components. Due to its power efficiency, high level of integration and maturity, CMOS enabled extreme miniaturization and integration onto a single die. In addition to these benefits over other technologies, CMOS was found to be suitable for operation in harsh environments, exhibiting radiation hardness [1, 2, 3] and the ability to operate at deep cryogenic temperatures, apparent from Fig. 1.

Interest in ultra-low temperature electronics is found in different niche areas. Electronics required to operate in space, for example, are subject to temperatures lying outside of the military temperature range (-55 to  $125\,^{\circ}\text{C}$ ) on both sides of this interval [3, 7, 1, 8]. Also here on Earth, observation of very distant objects in the solar system requires instrumentation able to detect signals with a very low signal-to-noise ratio. An approach to build such detectors is to cool them down to cryogenic temperatures in order to reduce their thermal noise [9]. Other applications for low-temperature electronics are found in experimental physics for sensors and sensor readout [10].

A relatively new application field for cryo-CMOS circuits is the control and readout of qubits in quantum processors, which is one of the main motivations behind this thesis [11]. As pointed out in Chapter 1, the availability of accurate device models that incorporate cryogenic device behaviour is paramount to ensure reliable circuit operation under these extreme conditions.

Therefore, this chapter starts with a description of the device behaviour of 40-nm bulk MOSFETs operated at deep-cryogenic temperatures, which needs to be

captured in the device models. In order to characterize devices at such low temperatures, special techniques are required, with the ones most commonly used briefly described in the first part of this chapter. The second part of this chapter describes a new modeling approach for the behaviour of 40-nm bulk-CMOS transistors.

This chapter is structured as follows. An overview of the state of the art of cryogenic MOSFET characterization is given in Section 2.1. Techniques for cooling devices to these extreme low temperatures are presented in Section 2.2, after which some of the most important cryogenic MOSFET effects are discussed in detail in Section 2.3. This chapter concludes in Section 2.4 with an Artificial-Neural-Network-based modeling approach of devices in the 40-nm process targeted in this thesis.

# 2.1 State-of-the-art of Cryogenic Device Characterization

Characterization of CMOS at deep-cryogenic temperatures dates back to the late 1960s [12]. Since that time many different technology nodes, ranging from 100  $\mu m$  to 14 nm and including bulk, Fully-Depleted Silicon-On-Insulator (FDSOI) and FinFET, have been characterized from room temperature (RT) down to deep-cryogenic temperatures as low as 20 mK.

A graphical overview of these efforts is shown in Fig. 1, in which the technology and type of work (characterized/modeled) are indicated. A large increase in the number of published research in the past couple of years can be seen, mainly due to the renewed interest in cryogenic characterization and modeling fueled by the development of the quantum computer. Fast and complex circuits are required for this application and thus the focus of device characterization and modeling with the quantum computer in mind is geared towards advanced CMOS technologies. The technology targeted in this thesis is a 40-nm one, indicated by a red cross in Fig. 1.

In order to enable the characterization of devices at such low temperatures, dedicated (cryogenic) equipment is required. The most common techniques for cryogenic device characterization will be discussed in the next section.

## 2.2 Cryogenic Characterization Methods

This section gives a brief overview of three common techniques that enable cryogenic characterization available in the group where this research was carried out. They are presented in order of increasing cooling capability, cycle time, complexity and cost.

Figure 1: Overview of cryogenic MOSFET characterization (C) and modeling (M). Reference numbers reflect the publication date from oldest (low number) to most recent (high number). The work in this thesis is indicated by a red cross  $(\times)$ .

#### 2.2.1 **Dipstick**

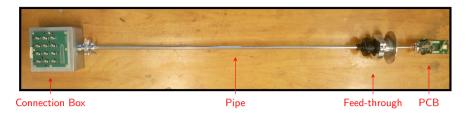

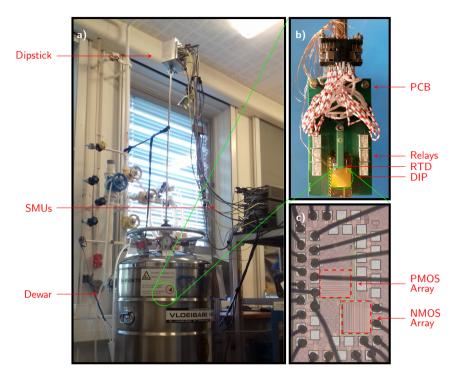

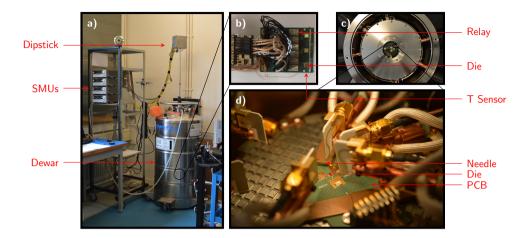

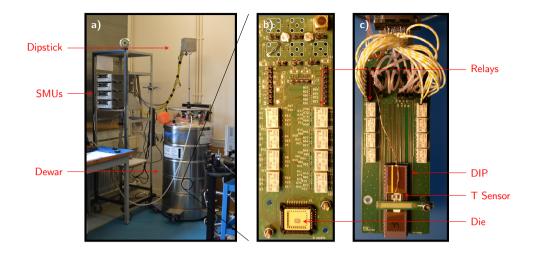

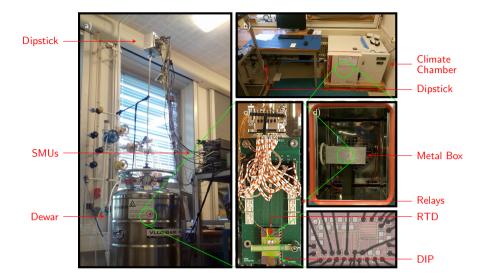

The dipstick is one of the most simple methods to cool samples down to 4.2 K based on cooling due to liquid helium or vapour. A typical dipstick is illustrated in Fig. 2. It consists of a stainless-steel pipe that carries interconnect wires between the sample holder at the cold end and the connection box at the room-temperature end. An airtight feed-through that mates with a Dewar containing liquid helium, in combination with the connection box, ensure as little helium loss to the environment as possible.

The sample temperature can be modulated in the range between approximately 250 K and 4.2 K by varying the height above the liquid helium level in the Dewar. It is measured by a cryogenic temperature sensor either clamped to the sample package or placed directly above the bare die.

As helium inevitably evaporates during storage, and especially during measurements, the setup is connected to a helium recovery system that collects, filters and re-liquifies the gas so it can be re-used in future experiments.

The samples to be characterized are mounted on a PCB placed in the sample

Figure 2: Photograph of the dipstick used in this work. Different parts are indicated.

holder, therefore, the dies need to be either mounted in a package (Ceramic DIP, CLCC, etc.) or glued and wirebonded directly on the PCB itself. This setup is limited to low-frequency characterization, in which no parasitic de-embedding and extensive impedance matching is required.

The main benefits of the dipstick are: it is cheap and can be built anywhere. Also, it allows for a fast cool-down, in the order of 10 minutes, and consumes little helium. Measurements can be taken continuously for 1-2 weeks at cryogenic temperatures without supervision. This is a big advantage, especially when measuring a large number of matched device pairs or large arrays. The cooling power at 4.2 K (when the sample is fully submerged in the liquid helium) lies around 1 W, depending on the geometry of the DUT. At higher power the helium starts to boil around the sample and the thermal contact worsens.

Some drawbacks of this technique are the lack of direct temperature control and temperature stability issues that can arise when the sample is in the helium vapour and the pressure of the recirculation system varies.

## 2.2.2 Cryogenic Probe Station

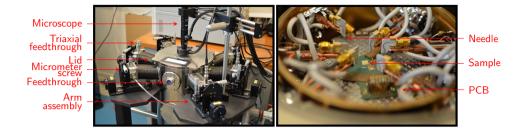

The cryogenic probe station solves some of the drawbacks of the dipstick, trading them off against increased cost and cycle time. The probe station shown in Fig. 3 left, consists of a vacuum chamber equipped with a looking glass and micro-meter actuated probe needle arms. A sample holder (chuck) is mounted in the center of the chamber, see Fig. 3 right, which is surrounded by multiple temperature and radiation shields, enabling the chuck to reach cryogenic temperatures by flowing helium through it. The temperature is controlled by integrated heater-diodes in the chuck.

Different types of needles can be mounted on the probe arms, such as DC needles (a single needle) and RF Ground-Signal-Ground (G-S-G) probes. The latter allow for precise impedance matching, required for high-frequency characterization.

One of the main benefits of the cryogenic probe station is the compatibility with on-wafer, high frequency characterization using G-S-G needles and a calibration substrate. Another benefit is the Proportional-Integral-Derivative (PID) temper-

Figure 3: Photograph of the Lakeshore CPX cryogenic probe station used in this work. Different parts are indicated. Left: overview of the probestation. Right: detailed view of the vacuum chamber with DC needles, sample and chuck visible.

ature control, which can be varied between (theoretically) 1.2 K, by pumping on the helium exhaust, and 400 K.

Drawbacks are its high cost and complexity of operation. The helium consumption is large compared to a dipstick and the probestation can only cool down for a limited amount of time (approximately 7 to 10 h) due to the helium flow through the chuck which evaporates the helium in the Dewar. Moreover, constant supervision is required. The number of needles is typically limited to 6.

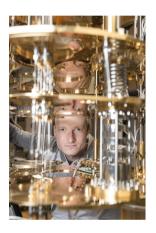

#### 2.2.3 **Dilution Refrigerator**

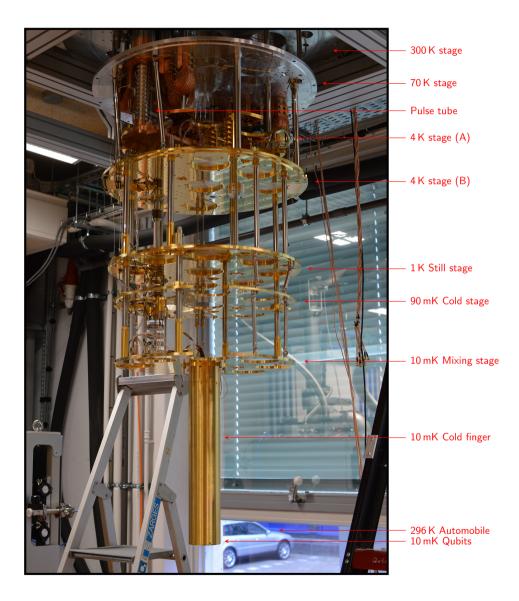

When sub-Kelvin characterization is required, a dilution refrigerator is the logical choice for the job. A photo of a dilution refrigerator can be found in Fig. 4. It can readily be recognized that these machines require a lot of space and peripherals such as cooling water and high-capacity power connections. Indicated in the figure are the different stages, each with a decreasing temperature moving from top to bottom of the dilution refrigerator. During normal operation the different stages shown in Fig. 4 are enclosed in metal cans brought under high vacuum. The exact theory of operation of these refrigerators lies beyond the scope of this thesis, however, in short the operation relies on the dilution of  $He^3$  with  $He^4$ , which is an endothermic process and thus removes heat from the fridge. The coldest part of the dilution fridge, the "cold finger" all the way at the bottom, can reach temperatures as low as 10 mK and has a cooling power of several  $\mu W$  at this temperature. The main benefit of the dilution refrigerator is its ability to cool samples to temperatures as low as 10 mK, a temperature unattainable with the other methods described above.

The main drawbacks are the cost, complexity (both in operation and experimental setup), the space it consumes and the cycle times, which lie in the order of a

### 14 | Chapter 2. Cryogenic Device Characterization and Modeling

week. The wiring can be complex and unreliable and is also limited in terms of connections. Also, the cooling power at the lowest temperatures is very limited, restricting characterizations to bias regimes that do not exceed that power budget.

**Figure 4:** Photograph of an opened Bluefors XLD dilution refrigerator used in QuTech. The most important parts and their respective operating temperature are indicated.

#### 2.3 Cryogenic MOSFET Behaviour

The first step towards device models able to accurately predict behaviour from RT down to deep-cryogenic temperatures, is the electrical characterization of devices over this temperature range. Many works have been published investigating MOS-FET behaviour in different technologies at cryogenic temperatures as indicated in Fig. 1.

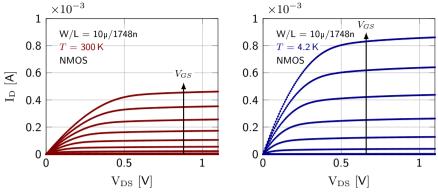

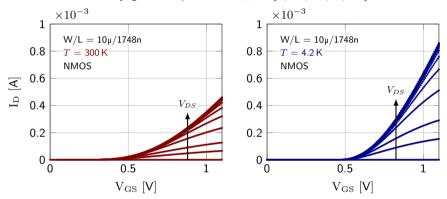

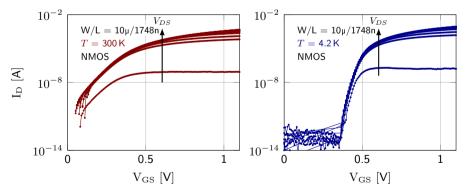

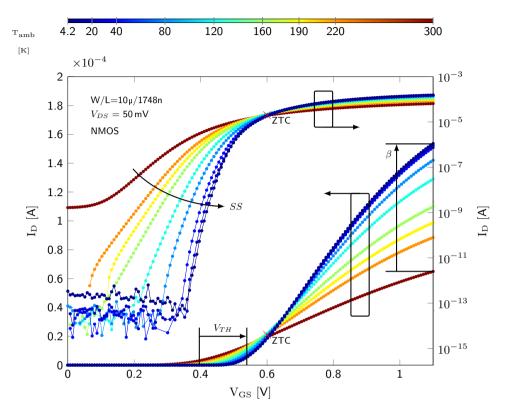

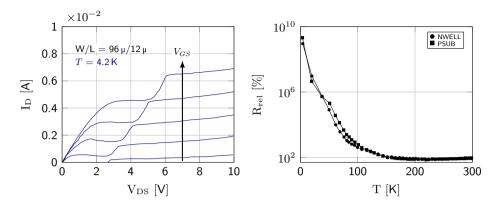

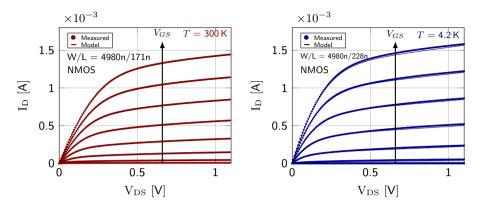

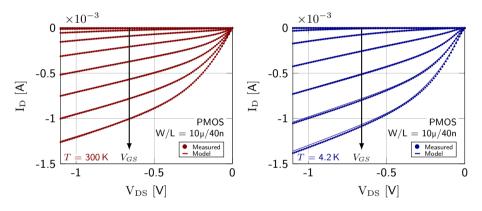

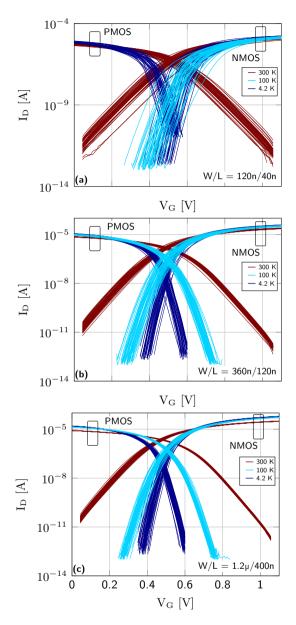

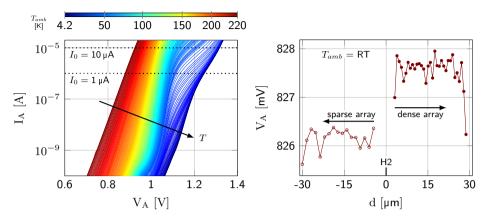

The most important curves in DC-MOSFET characterization are the drain current as a function of drain-source voltage  $(I_D$ - $V_D$  curves) and drain current as a function of the gate-source voltage ( $I_D$ - $V_G$  curves) shown in Fig. 5 and Fig. 6/7, respectively. The importance of accurate measurement of the drain current at different biases over temperature is immediately apparent, as many aspects of these curves change when deep-cryogenic temperatures are approached. For example, an increase in threshold voltage and mobility are both highlighted in Fig. 8, the former marked by a translation of the  $I_D$ - $V_G$  curve along the  $V_{GS}$  axis and the latter by a multiplicative factor increasing the drain current for high  $V_{GS}$ , respectively.

The increased drain current at high  $\left|V_{GS}\right|$  in Fig. 8 is related to the competing cryogenic effects of the threshold voltage and mobility increase. The improved mobility directly translates into an increased drain current, while the  $V_{TH}$  increase combats this effect by lowering the drain current, but to a lesser degree as seen in Fig. 8.

An interesting phenomenon, related to the interplay of the temperature sensitivity of the mobility and threshold voltage, is the Zero-Temperature-Coefficient (ZTC) bias point [66], indicated in Fig. 8. Depending on the operating regime, either  $V_{TH}$  (in moderate inversion) or  $\beta$  (in strong inversion) dominate the drain-current behaviour over temperature, and the cross-over point, where the two effects cancel each other out, is approximately temperature insensitive. Circuits exist that employ this bias point in order to generate a stable current/voltage reference over a wide temperature range [67].

The temperature sensitivity of the subthreshold slope SS can be observed in Fig. 8 by plotting the drain current on semi-logarithmic axes, the slope becoming steeper with decreasing temperatures.

From the measured drain-current data, the important modeling parameters previously mentioned can be extracted at different temperatures. A short description of their meaning, the method employed for their extraction and their behaviour over temperature is discussed in the following paragraphs.

#### 2.3.1 Threshold Voltage

The threshold voltage  $V_{TH}$  is the  $V_{GS}$  value that marks the onset of significant drain-current flow, and is one of the core parameters of compact MOSFET models. The threshold voltage was extracted using the Extrapolation-in-Linear-Region method (ELR) [68] throughout this thesis, for its simplicity and its successful ap-

### 16 | Chapter 2. Cryogenic Device Characterization and Modeling

**Figure 5:** Typical  $I_D$  as a function of  $V_{DS}$  ( $I_D$ - $V_D$ ) curves for a 40-nm process characterized at room and cryogenic temperature.  $V_{GS} = \{0, 0.1, 0.2, ..., 1.1\}$  V

**Figure 6:** Typical  $I_D$  as a function of  $V_{GS}$  ( $I_D$ - $V_G$ ) curves for a 40-nm process characterized at room and cryogenic temperature (lin scale).  $V_{DS} = \{0, 0.05, 0.1, 0.2, ..., 1.1\}$  V

Figure 7: Typical  $I_D$  as a function of  $V_{GS}$  ( $I_D$ - $V_G$ ) curves for a 40-nm process characterized at room and cryogenic temperature (log scale).  $V_{DS} = \{0, 0.05, 0.1, 0.2, ..., 1.1\}$  V

**Figure 8:**  $I_D$  vs  $V_{GS}$  ( $I_D$ - $V_G$ ) behaviour of a 40-nm process biased at  $V_{DS}=50\,\mathrm{mV}$  as a function of temperature. The most important parameter shifts and the Zero Temperature Coefficient (ZTC) point are indicated by arrows and a red cross, respectively. T={4.2, 20, 40, 80, 120, 160, 190, 220, 300} K.

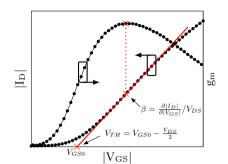

plicability in the mismatch study presented in Chapter 3. The ELR method is based on the long-channel linear equation:

$$I_D = \beta \left( (V_{GS} - V_{TH}) V_{DS} - \frac{V_{DS}^2}{2} \right),$$

(2.1)

where  $\beta$  is the current factor ( $\beta = \mu C_{OX} W/L$ , with  $\mu$  the carrier mobility,  $C_{OX}$ the gate-oxide capacitance and W and L the width and length of the MOSFET, respectively) and  $V_{TH}$  the threshold voltage. The threshold voltage is extracted by applying a first-order fit to the  $I_D$ - $V_G$  data at the point of maximum transconductance, as shown in Fig. 9 left. The value of  $V_{TH}$  is found from the intercept

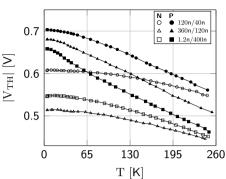

**Figure 9:** Threshold voltage extraction and behaviour. *Left*: schematic representation of the ELR threshold voltage extraction method. The capture of  $V_{TH}$  and  $\beta$  is indicated. *Right*: Extracted  $V_{TH}$  as a function of temperature for NMOS (N) and PMOS (P) device types and geometries.

with the  $V_{GS}$  axis by setting Eq. 2.1 equal to zero:

$$V_{TH} = V_{GS0} - \frac{V_{DS}}{2}. (2.2)$$

The behaviour of the threshold voltage from RT down to 4.2 K of PMOS and NMOS devices with different geometries can be seen in Fig. 9 right, which shows a linear increase down to a temperature of 50 K, below which the threshold voltage starts to saturate. These curves are compatible with those found and modeled by other groups [46, 69]. Different explanations are given for the increase and saturation at deep cryogenic temperatures. In [46], the saturation is explained by carrier freeze-out and field-assisted ionization while [69] attributes these effects to the temperature dependence of the bulk Fermi potential and interface traps close to the band edge.

The implications of an increased threshold voltage for circuit design is a reduced headroom, complicating designs that employ techniques such as cascoding, requiring an increased  $V_{DD}$ . Although a higher threshold voltage in combination with the increased SS reduces static leakage on one hand, and thus power consumption in digital designs, it limits the operating speed on the other.

## 2.3.2 Mobility

A second important parameter in MOSFET compact models is the carrier mobility  $\mu$ . In this thesis the exact value of the mobility is not extracted, as the current factor ( $\beta$ ) can be directly extracted from measured data and it is  $\beta$  that is relevant for the mismatch modeling presented in Chapter 3. However, the extracted current

**Figure 10:** Current factor  $(\beta)$  as a function of temperature for NMOS (N) and PMOS (P) device types and geometries.

factor can still be used to study mobility as it is proportional to  $\beta$ :

$$\beta = \mu C_{OX} W / L, \tag{2.3}$$

in which  $\mu$  represents the carrier mobility,  $C_{OX}$  the gate-oxide capacitance and W and L the width and length of the device, respectively. The latter three parameters are assumed to have negligible temperature dependence compared to  $\mu$ .

The current factor is extracted from the slope of the first order fit of the  $I_D$ - $V_G$  curve at maximum transconductance, see Fig. 9 left, the same fit employed for extraction of the threshold voltage in the previous paragraph:

$$\beta = \frac{\partial I_D}{\partial V_{GS}} / V_{DS}. \tag{2.4}$$

The behaviour of the current factor over the temperature range from RT down to 4.2 K for PMOS and NMOS devices of different sizes can be seen in Fig. 10. The mobility increase with temperature reduction is apparent with a saturating behaviour resembling that observed in the plots of the threshold voltage (Fig. 9) and subthreshold slope (Fig. 11).

The mobility improves down to a temperature of 40 K due to reduced phonon (lattice) scattering, below which Coulomb (impurity) scattering starts to dominate [70], similar to the impurity-limited resistance of metals at cryogenic temperatures, discussed in Section 4.4. Short devices exhibit a lower temperature dependence of  $\beta$ , as the halo implant increases the effective channel doping, reducing its temperature sensitivity [71].

From a circuit design perspective, the improved mobility observed at low temperatures results in more drain current for an equal overdrive compared to room temperature, resulting in faster switching.

## 2.3.3 Subthreshold Slope

The subthreshold slope SS is an important factor in low-power designs. Its inverse, the subthreshold swing, is defined as the  $V_{GS}$  increase required to raise the drain current by a decade for devices biased with  $V_{GS}$  below the threshold voltage. A steep subthreshold slope is preferred, as the MOSFET behaviour approaches the model of an ideal switch under this condition: a low-leakage "off" state and high-current "on" state selectable by a small change in  $V_{GS}$ , the latter enabling high switching speeds.

The carrier flow of MOSFETs biased in the subthreshold regime is diffusion-current driven and exponential in nature:

$$I_D \propto \exp\left(\frac{q(V_{GS} - V_{TH})}{nk_BT}\right),$$

(2.5)

with n the slope factor,  $k_B$  the Boltzmann constant, T the absolute temperature and q the electron charge.

The exponential regime can be clearly recognized in the  $I_D$ - $V_G$  plot shown in Fig. 8. The subthreshold slope is extracted by finding the slope of a first-order fit in this regime:

$$SS = \frac{\partial V_{GS}}{\partial \log(I_D)}.$$

(2.6)

Combining Eq. 2.5 and Eq. 2.6 yields an expression for the theoretical subthreshold slope as a function of temperature:

$$SS(T) = \ln\left(10\right) \frac{nk_B T}{q}. (2.7)$$

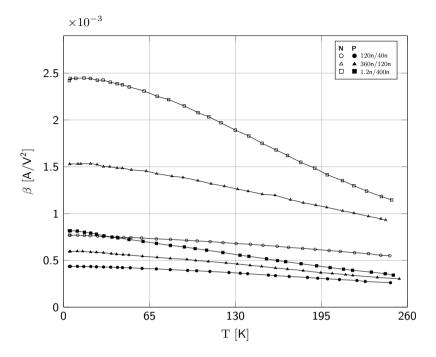

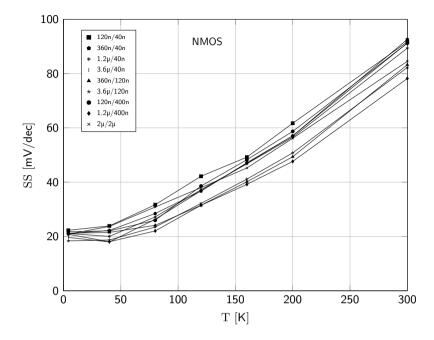

From Eq. 2.7, the subthreshold slope is expected to linearly improve with decreasing temperature, from a value around  $60\,\text{mV/dec}$  at RT to below  $1\,\text{mV/dec}$  at a temperature of 4.2 K. The extracted subthreshold slope as a function of temperature for NMOS devices with different geometries is shown in Fig. 11. The subthreshold slope exhibits the predicted linear behaviour down to 70 K, below which it starts to saturate to a value close to  $20\,\text{mV/dec}$ . The deviation from the

Figure 11: Subthreshold slope as a function of temperature for NMOS devices of different geometries.

model in Eq. 2.7 is in line with results found by others [15, 72, 53]. It was recognized by [72] that this saturation seems to be universally observed, irrespective of the device size or used technology (bulk, FDSOI, FinFET, etc.), which points to an intrinsic mechanism responsible for this effect. The subthreshold slope behaviour over temperature was successfully explained and modeled by taking the presence of band-tails into consideration [72], showing that in these cases an ideal switch cannot be obtained, even at deep-cryogenic temperatures.

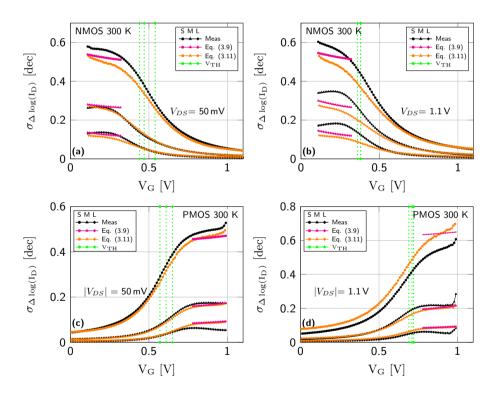

For circuit designers, the steeper subthreshold slope at cryogenic temperatures means a more ideal switching behaviour of the devices. However, due to the saturation, much less improvement is actually gained if Eq. 2.7 is used as predictor. Analog designs can suffer from additional non-ideal subthreshold behaviour that perturbates the ideal exponential I-V relationship. These and other subthreshold effects are discussed in more detail in Chapter 3.

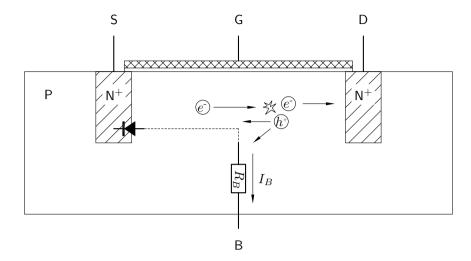

#### 2.3.4 Kink Effect

The kink effect is the name given to the sudden jump in drain current observed in the saturation region of (in this case) MOSFETs, as shown in Fig. 12. The effect

Figure 12: The kink-effect. *Left*: a typical example of the kink effect at cryogenic temperatures of a 3- $\mu$ m technology, replotted from [73].  $V_{GS} = \{1, 2, ..., 5\}$  V. *Right*: the NWELL and PSUB resistance relative to its room temperature value as function of temperature of a 40-nm technology, replotted from [74].

presents itself only in mature technologies (feature size of 0.35 µm and above) operated at deep-cryogenic temperatures. It is also observed at RT in SOI technologies or when, for example, the substrate connection is severed in bulk devices. The occurrence of the kink has been known for many years and the first explanations date back to the early 1990s [73]. As  $V_{DS}$  is increased, the horizontal electric field in the channel exceeds a critical value at a certain point, at which charge carriers attain enough energy to create additional "excess" electron-hole pairs through impact ionization, see Fig. 13 left, which marks the onset of the kink as explained next. These excess carriers leave the device through the drain and source, respectively, and add to the main current. However, a fraction of the minority excess carriers flow through the substrate impedance. The voltage dropped over this impedance raises the local substrate potential in the vicinity of the channel, lowering the threshold voltage through the body effect and increases suddenly the drain current of the device. The kink saturates as  $V_{DS}$  is further increased, as the parasitic bulk-source diode becomes forward biased, diverting the substrate current, effectively clamping the substrate potential.

At RT, the substrate impedance is low and the modulation of the substrate potential near the channel by the substrate current is negligible. However, at low temperatures the substrate impedance increases dramatically as shown in Fig. 12 right. When the substrate starts to freeze-out at temperatures below 100 K, the effect of the substrate current becomes apparent.

The onset of the kink shifts to higher  $V_{DS}$  values with increasing  $V_{GS}$  as visible in Fig. 12 left. On one hand, the vertical electrical field in the channel increases with  $V_{GS}$ , increasing effects such as surface scattering which reduces carrier mobility. For carriers to attain enough energy for impact-ionization, a higher horizontal field

Figure 13: A schematic representation of the mechanism behind the kink-effect.

$(V_{DS})$  is thus required. On the other hand, this horizontal field reduces at higher  $V_{GS}$  by the increased distance between the pinch-off point and the drain.

The kink effect is mainly a problem in mature bulk technologies and is not observed in technologies with feature size below  $0.35\,\mu m$ . The effect is absent in these technologies due to the increased vertical field driven by geometrical scaling, which impedes impact ionization as discussed above. The formation of electronhole pairs is further supressed by the scaling of the supply voltages. The kink effect has not been observed in the 40-nm processes characterized in this thesis and is thus not further discussed.

#### 2.3.5 AC Behaviour

Although this thesis focuses on DC device characteristics, the ability to simulate dynamic behaviour in circuits is required and therefore the impact of low temperatures on RF characteristics are of interest. Some important parameters are summarized in this paragraph.

For example, the current-gain cutoff frequency  $f_T$  continuously improves with decreasing temperature, up to a factor of approximately 1.6 in nanometer bulk CMOS RF circuits operated at 4.2 K compared to those at 300 K [7]. The maximum oscillation frequency  $f_{max}$  improves down to 50 K, below which it flattens-out due to the saturation of the gate resistance (see also Chapter 4) which is the main parameter that determines  $f_{max}$  [7].

#### 2.3.6 Noise

One of the reasons for cooling down sensitive circuits is to reduce their noise, a technique applied in, for example, circuits such as detectors/sensors for space observation. Thermal noise decreases dramatically when the ambient temperature is lowered from 300 K down to 4.2 K, however, a smaller noise reduction than the expected proportional decrease with temperature is found at cryogenic temperatures. This noise saturation has been attributed to shot noise starting to dominate at cryogenic temperatures [75, 76]. This excess noise requires more power to be burned in order to reach a certain specification, causing challenges in applications where power budgets are severely limited such as those cooled by dilution refrigerators. Another potential effect that can severely impact the noise performance of circuits is self-heating, extensively discussed in Chapter 4. Here it is shown that the channel temperatures in bulk CMOS devices can rise to up to 50 K (while in an ambient temperature of 4.2 K) already at low power levels ( $<1\,\mathrm{mW}$ ), thus increasing thermal noise.

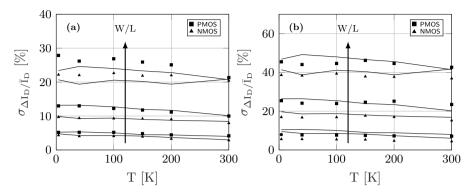

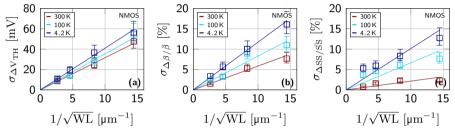

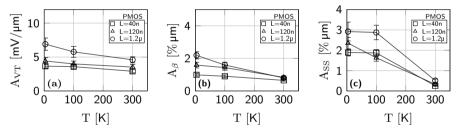

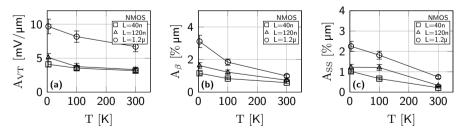

#### 2.3.7 Device Mismatch

Device mismatch is the effect parameter variability (such as  $\sigma_{\Delta V_T}$ ,  $\sigma_{\Delta\beta/\beta}$  and  $\sigma_{\Delta SS/SS}$ ) has on pairs of supposedly identical devices. It invalidates the assumption of perfectly matched devices, which many precision circuits base their operation on, necessitating the application of many circuit techniques to alleviate this problem. These techniques often result in designs requiring more silicon area and/or operate with increased power dissipation compared to the original design. Previous research (see Chapter 3) hints at an increased device mismatch at cryogenic temperatures, indicating a possible challenge for cryogenic high-precision circuit design. An in-depth study of device mismatch and the evaluation of the effectivity of dummy placement at deep-cryogenic temperatures is presented in Chapter 3.

## 2.3.8 Self-Heating

Self-heating occurs in (resistive) devices carrying an electric current, causing a local temperature increase due to Joule heating. As many device parameters exhibit a high temperature sensitivity, many undesired circuit effects can result, such as shifting of bias regimes, electro-thermal feedback loops and thermal runaway, i.e. a temperature rise that results in increased current, resulting in even more self heating, ultimately destroying the device.

Prior research (see Chapter 4) indicates a self-heating exacerbated at deep-cryogenic temperatures, with all its associated problems and challenges for cryogenic circuit design. Self-heating at cryogenic temperatures has therefore been extensively investigated, the methods and results presented in Chapter 4.

#### 2.4 Cryogenic 40-nm MOSFET Modeling

Cryogenic device models are indispensable for the reliable design of circuits for cryogenic operation, as pointed out in Chapter 1. Device behaviour at these low temperatures can be quite different from its room temperature equivalent, caused by the large temperature sensitivity of device parameters, the most important ones discussed in the preceding paragraphs.

Much effort has already been devoted to the characterization and modeling of MOSFETs operated at cryogenic temperatures in many different technologies and feature sizes, see Section 2.1 (in particular Fig. 1), and the physics of cryo-CMOS devices is mostly understood [53, 77].

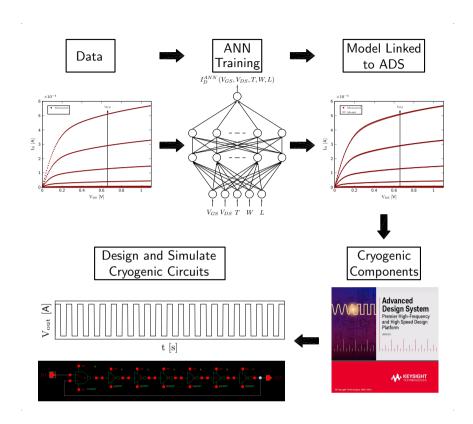

Despite all this work, there is not yet a consensus on a standard cryo-CMOS model, and it is unclear whether existing model extraction procedures can be effectively applied to cryogenic characteristics. As an alternative, the use of an Artificial Neural Network (ANN) and associated training (extraction) techniques is here proposed in collaboration with Keysight Technologies, to automatically construct cryo-CMOS simulation models without requiring any physics-based device model [78]. ANNs only require a discrete set of experimental data, e.g.,  $I_D = f(V_{GS}, V_{DS}, W, L, T)$ for a limited set of bias points. Since those data can be scattered (sampled without any gridding constraints over T, W, L and bias), significant cryogenic characterization effort can be saved. From these data, the ANNs that are automatically generated provide infinitely differentiable functions describing the device nonlinear current/voltage and charge/voltage relations, hence are well-suited for accurate analog-circuit simulations.

This section explores the potential of ANN models for cryo-CMOS devices by applying such modeling methodology to experimental data. After describing the basics of the ANN modeling flow for both the static and dynamic characteristics in Section 2.4.1, the measurement setup and test structures are presented in Section 2.4.2. Section 2.4.3 assesses the quality of the proposed model for a large number of cryo-CMOS devices. The performance of those models in predicting the behaviour of practical circuits is then benchmarked by comparing the simulations using the proposed models with the experimental data for a static circuit and with simulations using the foundry-provided model for a dynamic circuit, respectively.

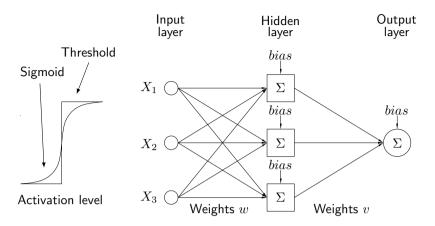

#### 2.4.1 ANN-based Modeling for Cryo-CMOS

ANNs are a powerful computational paradigm inspired by the human nervous system [79]. They have become mainstream tools of the artificial intelligence and machine learning communities. The Universal Approximation Theorem [79] proves that an ANN with at least one hidden layer with a sufficient number of univariate processing functions, or neurons, can arbitrarily fit any nonlinear function of any number of independent variables. ANN training is an automatic process of adjusting the internal weights and biases (parameters) of the ANN to enable the model

Figure 14: Schematic overview of the ANN structure illustrating the ANN layer structure and a plot of typical univariate neuron nonlinearity (sigmoid and threshold functions).

to match the training data. A typical single hidden layer structure is shown in Fig. 14, along with a plot of a typical univariate neuron nonlinearity, or threshold function. Mathematically this ANN can be represented by the following equation:

$$F(X_1, ..., X_N) = \sum_{i=1}^{L} v_i s \left( \sum_{k=1}^{N} w_{ki} x_k + a_i \right) + b_i,$$

(2.8)

in which  $v_i$  and  $w_{ki}$  are the weights, s the Sigmoid function and  $a_i$  and  $b_i$  are the biases.

Applying ANNs to device modeling is advantageous as there are no equation development or user-defined parameter extraction processes needed. The general modeling flow is shown in Fig. 15. Given the measured data, e.g., drain current from sampled bias points and over a wide range of temperatures and geometries (W/L), an ANN model is automatically trained (constructed).

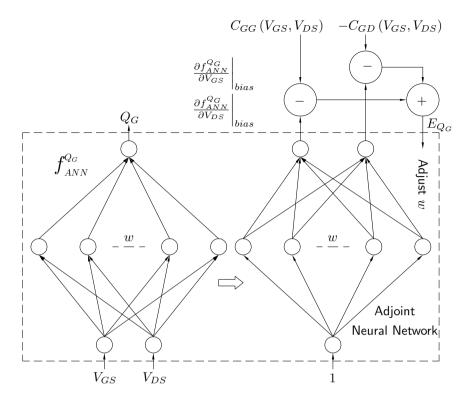

Unlike drain currents that can be directly measured at different bias conditions and used to train ANN functions with standard techniques to produce voltagecontrolled current source elements, the charge stored by device bias-dependent capacitances cannot be directly measured. Instead, the nonlinear charge functions (modeled by voltage-controlled nonlinear capacitors) can be generated by training ANNs to simultaneously fit the partial derivatives of the desired charge functions to bias-dependent capacitances (e.g.  $C_{GG}$  and  $C_{GD}$ ) that can be obtained from S-parameter data [80]. This requires a unique kind of automated "Adjoint training" [78] that essentially performs line-integration of measured data and is illustrated in Fig. 16. This approach is generally superior to a direct numerical line-integration approach for several reasons, as described in [81]. The implementation in this work, however, ignores the effect of independently biasing internal

Figure 15: Modeling flow: Given the measured data, an ANN model is automatically trained (constructed). The trained model is easily linked to a circuit simulator, for highlevel circuit simulation and design.

nodes (e.g. the bulk node), and effectively treats the device as having two independent terminal voltages, drain-source  $(V_{DS})$  and gate-source  $(V_{GS})$  voltages, assuming the bulk node to be tied to the source.

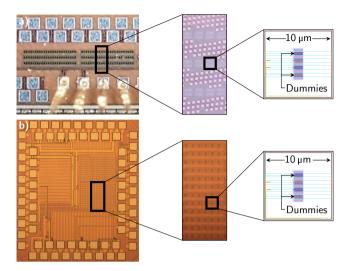

#### 2.4.2 **Characterization Structures and Measurement Setup**

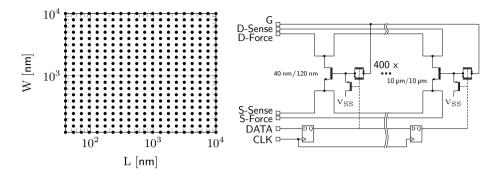

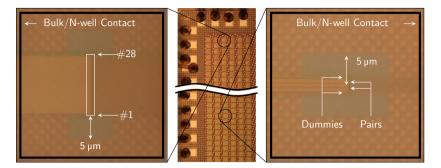

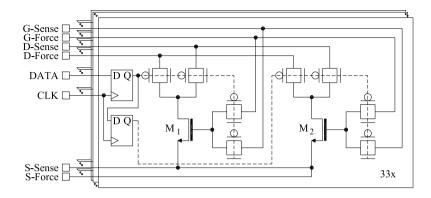

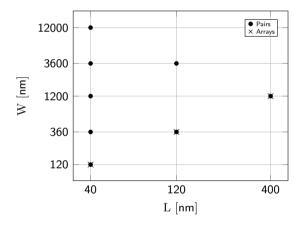

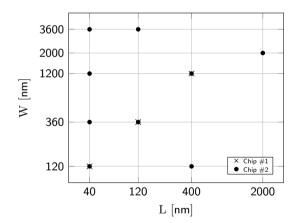

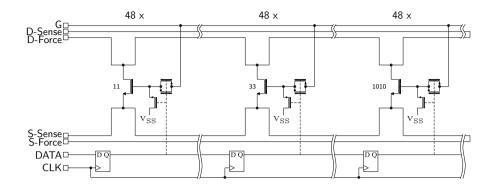

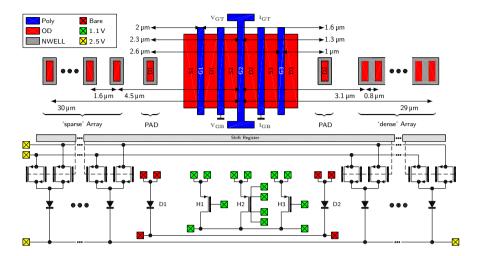

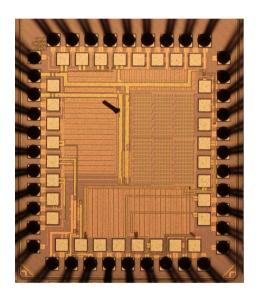

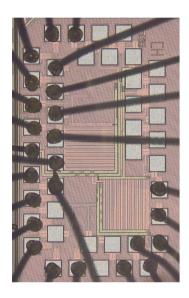

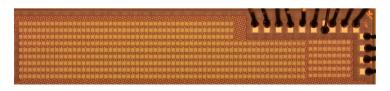

In order to measure  $I_D = f(V_{GS}, V_{DS}, W, L, T)$  for many different geometries, device types (PMOS, NMOS), bias points and temperatures as training set for the ANN, dedicated test structures have been designed and manufactured in the TSMC 40-nm bulk CMOS process. Two test structures were available, one for NMOS types and one for PMOS types, each comprising an array of 400 devices with different device geometries ranging from minimum (W=120 nm, L=40 nm)

**Figure 16:** Adjoint ANN training of the model gate terminal charge function from  $C_{GG}$  and  $-C_{GD}$  data. The Adjoint training method utilizes a more complicated ANN network, but ultimately returns an ANN model for the terminal charge  $Q_G$  (this figure) and similarly for  $Q_D$ , the drain charge, assuming a three-terminal device structure with the bulk node shorted to the source.

to large size (W=10  $\mu$ m, L=10  $\mu$ m), graphically summarized in Fig. 17 left. A diagram indicating the electrical connections and a chip micrograph can be found in Fig. 17 right and Fig. 18, respectively. All devices in the array share their drain and source connection, both wired in a Kelvin fashion to mitigate the effect of parasitic wire/interconnect resistance. Each device is individually selectable by connecting its gate to a common gate line through a pass gate controlled by a digital shift register, while all the other devices are shut off by connecting their gates to either  $V_{SS}$  or  $V_{DD}$  for NMOS or PMOS devices, respectively. The device bulk connection is tied to the appropriate rail.

The test dies were mounted in a Ceramic DIP (CERDIP) package, placed on a PCB at the end of a dipstick, as shown in Fig. 18. A set of relays allowed selection of either the NMOS of the PMOS array to mitigate undesired effects such

Figure 17: Test chip. Left: the available W/L combinations for both PMOS and NMOS devices. Right: schematic representation of the internal electrical connections to the NMOS array.

as leakage. The chip temperature was monitored by a Cernox temperature sensor brought in close thermal contact to the CERDIP package.

The electrical characterization was carried out by two Keithley 2636B Source Measurement Units (SMUs), measuring the drain current while sweeping both  $V_{\!GS}$  and  $V_{DS}$  over the range from 0 V to the nominal supply voltage  $(V_{DD}=1.1\,\mathrm{V})$ , with  $V_S$  fixed at the bulk potential.

Although the data was acquired on a regular grid for  $V_{DS}$  and  $V_{GS}$ , this is not strictly necessary for the ANN training. For instance, the W and L of the 400 geometries are not linearly, but logarithmically scaled from 40 nm to 10 µm, in order to sample the region closer to the minimum size more accurately, since those devices are more relevant for circuit design and more significant variations in their electrical behaviour are expected.

#### 2.4.3 Measurement Results and Model Validation

The ANN model was trained over the drain current data measured at 4.2 K, 100 K and 300 K, over a bias grid of 12  $V_{DS}$  values by 151  $V_{GS}$  values, and for the 400 geometries to learn the constitutive relation  $I_D = f(V_{DS}, V_{GS}, W, L, T)$ . The training required 24 hours on a 4-core intel i7 workstation with 32-GB RAM. The resulting model fitted the measured DC characteristics within a 1% RMS error. Examples from a few selected devices and temperatures are shown in Fig. 19 and

20, demonstrating the quality and applicability of the resulting models.

To assess the ability of the ANN to model dynamic behaviour, a dynamic ANN model based on the quasi-static approach described in Section 2.4.1 was generated from S-parameters obtained from simulations using the foundry-provided models at 300 K (the foundry models are not valid at 4.2 K) and measured I-V data. These models were then benchmarked by simulating a 500 MHz inverter-based ring

**Figure 18:** The measurement setup. a) Overview of the full dipstick setup. b) Detailed photograph of the PCB holding the sample. c) Die micrograph of the test chip.

oscillator employing 142 digital inverters and a NAND gate for start up. Although the dynamic model is limited to 300 K due to the present lack of measured cryogenic S-parameters, the oscillation frequency predicted by the ANN models for 300 K (525 MHz) accurately matched (within 6%) the predictions of the foundry-provided models (559 MHz).

### 2.4.4 Conclusion

These results demonstrate the utility of automatically generated ANN models for cryo-CMOS applications. By avoiding developing specific physics-based models and minimizing the required characterization data, the proposed modeling approach can significantly accelerate the development of the complex cryo-CMOS electrical interfaces for future large-scale quantum processors.

Figure 19: Measurements vs model:  $I_D$ - $V_D$  plots of an NMOS device at room and cryogenic temperature, showing both measured data and the models generated by the ANN modeling flow.  $V_{GS} = \{0, 0.1, 0.2, ..., 1.1\} \text{ V}.$

Figure 20: Measurements vs model:  $I_D$ - $V_D$  plots of a PMOS device at room and cryogenic temperature, showing both measured data and the models generated by the ANN modeling flow.  $|V_{GS}| = \{0, 0.1, 0.2, ..., 1.1\} \text{ V}.$

#### 2.5 **Conclusions**

In this Chapter, an overview of previous cryogenic characterization and modeling efforts was presented, from which it can be concluded that the recent developments around quantum computing sparked a new interest in this niche field. Three common techniques that enable electrical characterization of test chips at temperatures as low as 100 mK were presented, highlighting both the benefits and drawbacks of each method.

Devices operated at these extreme low temperatures exhibit behaviour that can

## 32 | Chapter 2. Cryogenic Device Characterization and Modeling

deviate significantly from those observed at room temperature. The effect of temperature on the most important parameters that govern the cryogenic operation of MOSFETs, such as the threshold voltage, mobility and subthreshold slope, have been shown from experimental data and some background on the underlying physical mechanisms was given.

In order to bring this information to the circuit designers in the form of cryogenic DC models, which enable reliable cryogenic circuit design, this chapter concluded with the description of a successful DC-modeling flow based on ANN training. In the following chapters, in-depth studies of more advanced DC effects, such as device matching and self-heating, are presented.

## **Bibliography**

- [1] M. Turowski and A. Raman, "Device-Circuit Models for Extreme Environment Space Electronics," in *Proceedings of the 19th International Conference Mixed Design of Integrated Circuits and Systems (MIXDES)*, 2012, pp. 350–355.

- [2] A. Gupta, M. Li, K. Yu, S. Su, P. Pandya, and H. Yang, "Radiation-Hard 16K CMOS/SOS Clocked Static RAM," in 1981 International Electron Devices Meeting (IEDM), 1981, pp. 616–619.

- [3] E. Simoen, A. Mercha, Y. Creten, P. Merken, J. Putzeys, P. De Moor, C. Claeys, C. Van Hoof, A. Mohammadzadeh, and R. Nickson, "Impact of Irradiations Performed at Liquid Helium Temperatures on the Operation of 0.7um CMOS Devices and Read-Out Circuits," in *Proceedings of the 7th Eu*ropean Conference on Radiation and Its Effects on Components and Systems (RADECS), 2003, pp. 369–375.

- [4] P. A. 't Hart, J. van Staveren, F. Sebastiano, J. Xu, D. E. Root, and M. Babaie, "Artificial Neural Network Modelling for Cryo-CMOS Devices," in 2021 IEEE 14th Workshop on Low Temperature Electronics (WOLTE), 2021, pp. 1–4.

- [5] P. A. 't Hart, M. Babaie, E. Charbon, A. Vladimirescu, and F. Sebastiano, "Characterization and Modeling of Mismatch in Cryo-CMOS," *IEEE Journal* of the Electron Devices Society (JEDS), vol. 8, pp. 263–273, 2020.

- [6] —, "Subthreshold Mismatch in Nanometer CMOS at Cryogenic Temperatures," *IEEE Journal of the Electron Devices Society (JEDS)*, vol. 8, pp. 797–806, 2020.

- [7] S.-H. Hong, G.-B. Choi, R.-H. Baek, H.-S. Kang, S.-W. Jung, and Y.-H. Jeong, "Low-Temperature Performance of Nanoscale MOSFET for Deep-Space RF Applications," *IEEE Electron Device Letters (EDL)*, vol. 29, no. 7, pp. 775–777, 2008.

- [8] L. Varizat, G. Sou, M. Mansour, D. Alison, and A. Rhouni, "A Low Temperature 0.35um CMOS Technology BSIM3.3 Model for Space Instrumentation:

- Application to a Voltage Reference Design," in 2017 IEEE International Workshop on Metrology for AeroSpace (MetroAeroSpace), 2017, pp. 74–78.

- [9] P. Martin, A. Royet, F. Guellec, and G. Ghibaudo, "MOSFET Modeling for Design of Ultra-High Performance Infrared CMOS Imagers Working at Cryogenic Temperatures: Case of an Analog/Digital 0.18um CMOS Process," Solid-State Electronics (SSE), vol. 62, no. 1, pp. 115–122, 2011.

- [10] G. De Geronimo, A. D'Andragora, S. Li, N. Nambiar, S. Rescia, E. Vernon, H. Chen, F. Lanni, D. Makowiecki, V. Radeka, C. Thorn, and B. Yu, "Front-End ASIC for a Liquid Argon TPC," in *IEEE Nuclear Science Symposuim Medical Imaging Conference (NSSMIC)*, 2010, pp. 1658–1666.

- [11] F. Sebastiano, H. Homulle, B. Patra, R. Incandela, J. van Dijk, L. Song, M. Babaie, A. Vladimirescu, and E. Charbon, "Cryo-CMOS Electronic Control for Scalable Quantum Computing," in 2017 54th ACM/EDAC/IEEE Design Automation Conference (DAC), 2017, pp. 1–6.

- [12] R. Zuleeg and K. Lehovec, "Temperature Dependence of the Saturation Current of MOST's," *IEEE Transactions on Electron Devices (TED)*, vol. 15, no. 12, pp. 987–989, 1968.

- [13] F. Gaensslen, V. Rideout, E. Walker, and J. Walker, "Very Small MOS-FET's for Low-Temperature Operation," *IEEE Transactions on Electron Devices (TED)*, vol. 24, no. 3, pp. 218–229, 1977.

- [14] F. Gaensslen and R. Jaeger, "Behavior of Electrically Small Depletion Mode MOSFETs at Low Temperature," *Solid-State Electronics (SSE)*, vol. 24, no. 3, pp. 215–220, 1981.

- [15] A. Kamgar, "Subthreshold Behavior of Silicon MOSFETs at 4.2 K," *Solid-State Electronics (SSE)*, vol. 25, no. 7, pp. 537–539, 1982.

- [16] G. Gildenblat, L. Colonna-Romano, D. Lau, and D. Nelsen, "Investigation of Cryogenic CMOS Performance," in 1985 International Electron Devices Meeting (IEDM), 1985, pp. 268–271.

- [17] A. Henning, N. Chan, and J. Plummer, "Substrate Current in N-Channel and P-Channel MOSFETs Between 77K and 300K: Characterization and Simulation," in 1985 International Electron Devices Meeting (IEDM), 1985, pp. 573–576.

- [18] H. Hanamura, M. Aoki, T. Masuhara, O. Minato, Y. Sakai, and T. Hayashida, "Operation of Bulk CMOS Devices at Very Low Temperatures," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 21, no. 3, pp. 484–490, 1986.

- [19] K. Wilson, P. Tuxbury, and R. Anderson, "A Simple Analytical Model for the Electrical Characteristics of Depletion-Mode MOSFET's with Application to Low-Temperature Operation," IEEE Transactions on Electron Devices (TED), vol. 33, no. 11, pp. 1731–1737, 1986.

- [20] J. Watt, B. Fishbein, and J. Plummer, "A Low-Temperature NMOS Technology with Cesium-Implanted Load Devices," IEEE Transactions on Electron Devices (TED), vol. 34, no. 1, pp. 28-38, 1987.

- [21] F. Balestra, L. Audaire, and C. Lucas, "Influence of Substrate Freeze-Out on the Characteristics of MOS Transistors at Very Low Temperatures," Solid-State Electronics (SSE), vol. 30, no. 3, pp. 321-327, 1987.

- [22] M. Aoki, K. Yano, T. Masuhara, and K. Shimohigashi, "Fully Symmetric Cooled CMOS," IEEE Transactions on Electron Devices (TED), vol. 36, no. 8, pp. 1429-1433, 1989.

- [23] S. Broadbent, "CMOS Operation Below Freezeout," in Proceedings of the Workshop on Low Temperature Semiconductor Electronics (WOLTE), 1989, pp. 43-47.

- [24] I. M. Hafez, G. Ghibaudo, and F. Balestra, "Flicker Noise in Metal-Oxide-Semiconductor Transistors from Liquid Helium to Room Temperature," Journal of Applied Physics, vol. 66, no. 5, pp. 2211–2213, Sep. 1989.

- [25] J. Wang, J. Chang, V. Raman, P. Vasudev, and C. Viswanathan, "Electrical Characterization of SOS n-MOSFETs at Cryogenic Temperatures," in IEEE SOS/SOI Technology Conference (SOI), 1989, pp. 41–42.

- [26] T. Elewa, F. Balestra, S. Cristoloveanu, I. Hafez, J.-P. Colinge, A.-J. Auberton-Herve, and J. Davis, "Performance and Physical Mechanisms in SIMOX MOS Transistors Operated at Very Low Temperature," IEEE Transactions on Electron Devices (TED), vol. 37, no. 4, pp. 1007-1019, 1990.

- [27] L. Deferm, E. Simoen, and C. Claeys, "The Importance of the Internal Bulk-Source Potential on the Low Temperature Kink in NMOST's," IEEE Transactions on Electron Devices (TED), vol. 38, pp. 1459-1466, Jun. 1991.

- [28] M. Kakumu, D. Peters, H.-Y. Liu, and K.-Y. Chiu, "Design Optimization Methodology for Deep-Submicrometer CMOS Device at Low-Temperature Operation," IEEE Transactions on Electron Devices (TED), vol. 39, no. 2, pp. 370-378, 1992.

- [29] E. Simoen, B. Dierickx, and C. Claeys, "Low-Frequency Noise Behavior of Si NMOSTs Stressed at 4.2 K," IEEE Transactions on Electron Devices (TED), vol. 40, no. 7, pp. 1296-1299, 1993.

- [30] E. Simoen and C. Claeys, "Impact of CMOS Processing Steps on the Drain Current Kink of NMOSFETs at Liquid Helium Temperature," *IEEE Transactions on Electron Devices (TED)*, vol. 48, no. 6, pp. 1207–1215, 2001.

- [31] Y. Feng, P. Zhou, H. Liu, J. Sun, and T. Jiang, "Characterization and Modelling of MOSFET Operating at Cryogenic Temperature for Hybrid Superconductor-CMOS Circuits," Semiconductor Science and Technology (SST), vol. 19, no. 12, pp. 1381–1385, oct 2004.

- [32] N. Yoshikawa, T. Tomida, M. Tokuda, Q. Liu, X. Meng, S. Whiteley, and T. Van Duzer, "Characterization of 4 K CMOS Devices and Circuits for Hybrid Josephson-CMOS Systems," *IEEE Transactions on Applied Superconductivity* (*TASC*), vol. 15, no. 2, pp. 267–271, 2005.

- [33] A. Siligaris, G. Pailloncy, S. Delcourt, R. Valentin, S. Lepilliet, F. Danneville, D. Gloria, and G. Dambrine, "High-Frequency and Noise Performances of 65-nm MOSFET at Liquid Nitrogen Temperature," *IEEE Transactions on Electron Devices (TED)*, vol. 53, no. 8, pp. 1902–1908, 2006.

- [34] Y. Creten, P. Merken, W. Sansen, R. Mertens, and C. van Hoof, "A Cryogenic ADC Operating Down to 4.2K," in 2007 IEEE International Solid-State Circuits Conference (ISSCC), 2007, pp. 468–616.

- [35] A. Akturk, M. Peckerar, M. Dornajafi, N. Goldsman, K. Eng, T. Gurrieri, and M. S. Carroll, "Impact Ionization and Freeze-Out Model for Simulation of Low Gate Bias Kink Effect in SOI-MOSFETs Operating at Liquid He Temperature," in 2009 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), 2009, pp. 1–4.

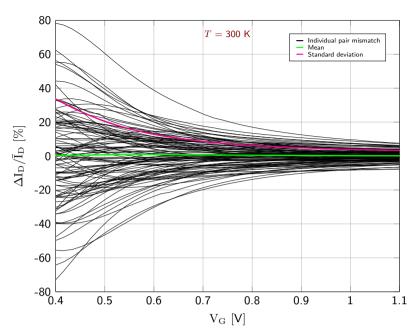

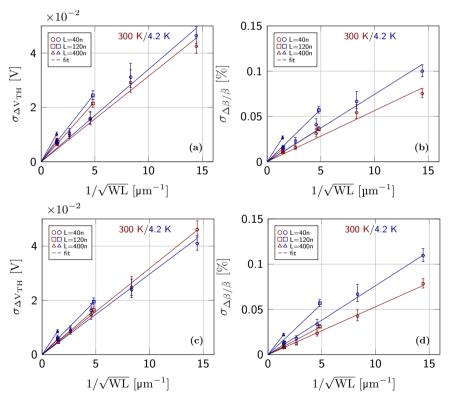

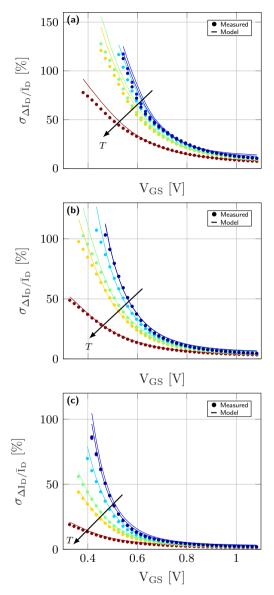

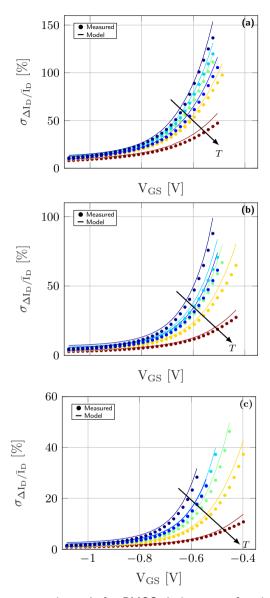

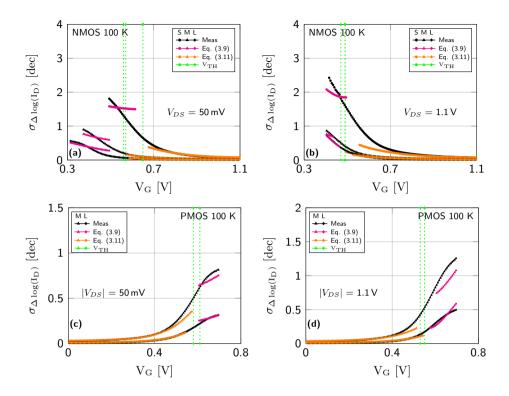

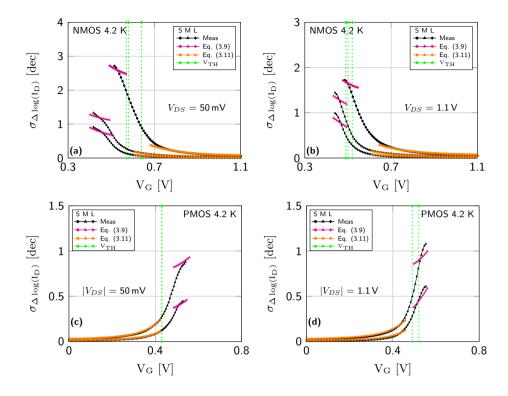

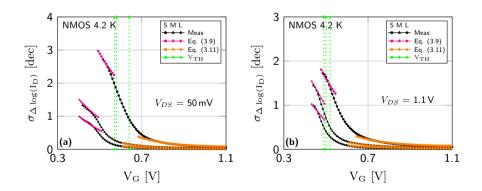

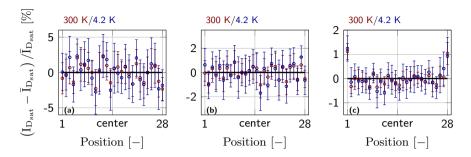

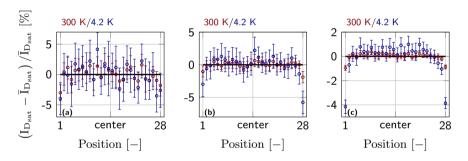

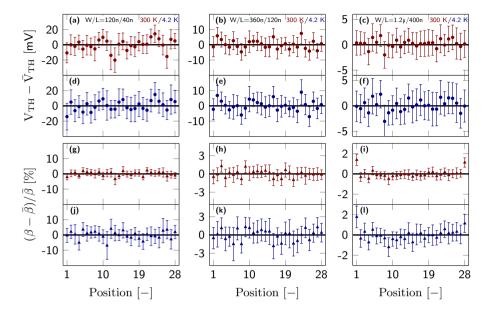

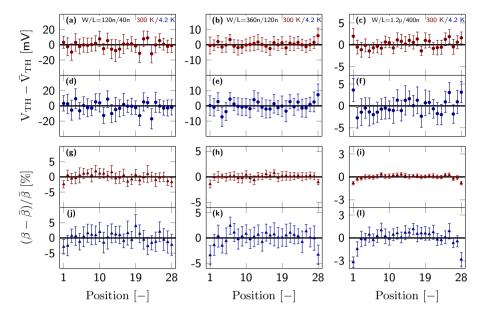

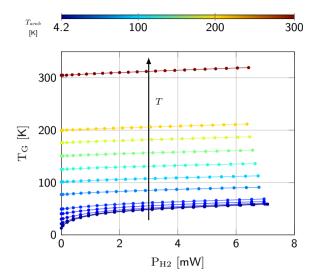

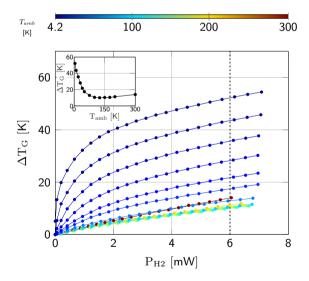

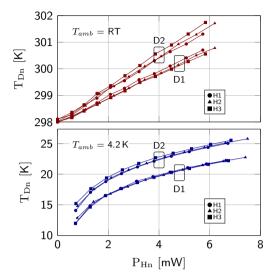

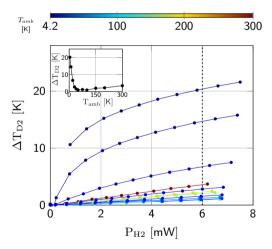

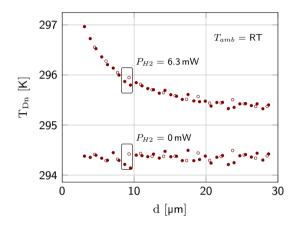

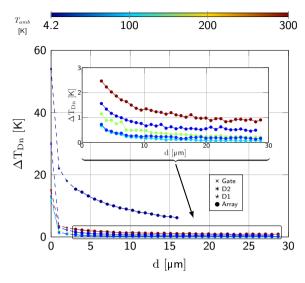

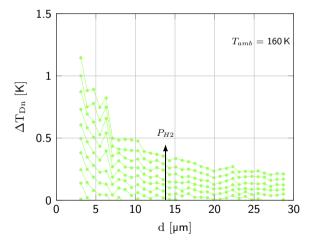

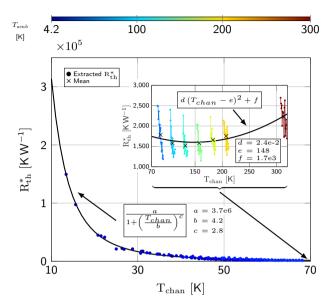

- [36] A. Akturk, M. Holloway, S. Potbhare, D. Gundlach, B. Li, N. Goldsman, M. Peckerar, and K. P. Cheung, "Compact and Distributed Modeling of Cryogenic Bulk MOSFET Operation," *IEEE Transactions on Electron Devices (TED)*, vol. 57, no. 6, pp. 1334–1342, 2010.