# An FM-UWB Transceiver for Autonomous Wireless Systems

Nitz Saputra

# An FM-UWB Transceiver for Autonomous Wireless Systems

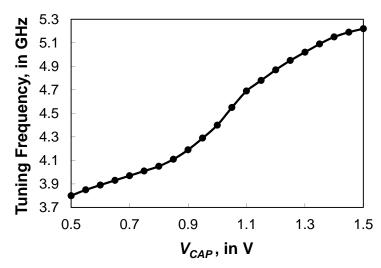

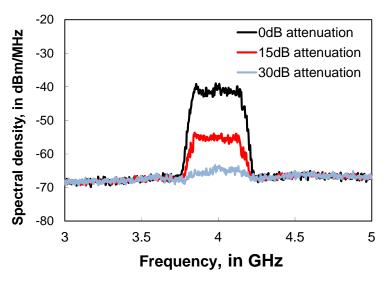

### Proefschrift

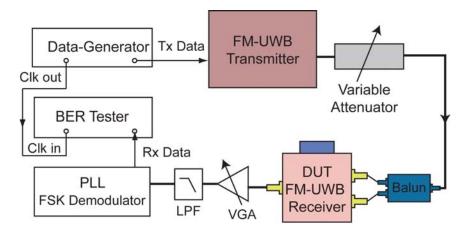

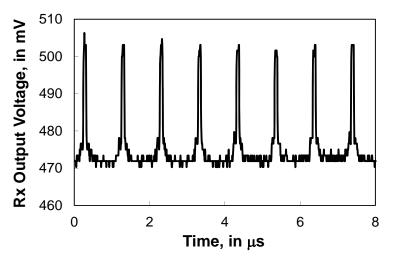

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

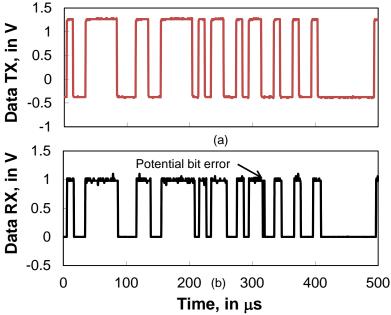

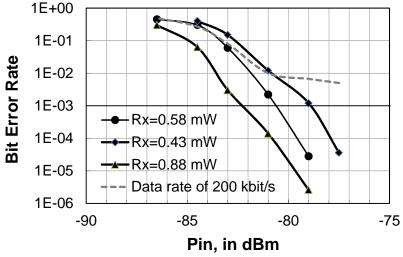

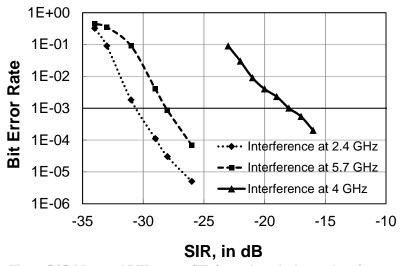

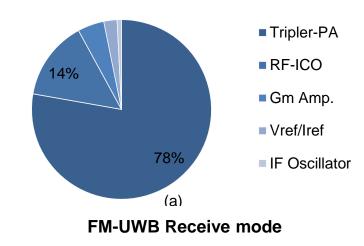

op woensdag, 5 September 2012 om 12:30 uur

door

NITZ SAPUTRA

Master of Science in Electrical Engineering, Technische Universiteit Delft, geboren te Bandung, West-Java, Indonesië. Dit proefschrift is goedgekeurd door de promotor:

Prof.dr. J.R. Long

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof.dr. J.R. Long, Technische Universiteit Delft, promotor

Prof.dr. K.A.A. Makinwa, Technische Universiteit Delft

Prof.dr.ir. P.G.M. Baltus, Technische Universiteit Eindhoven

Prof.dr.ir. F.E. van Vliet, Universiteit Twente

Prof.dr.ir. P. Reynaert, Katholieke Universiteit Leuven

Prof.dr. P. Andreani, Lunds Universitet

Dr. J.R. Farserotu, Centre Suisse d'Electronique et de Microtechnique

Prof.dr. P.M. Sarro, Technische Universiteit Delft, reservelid

ISBN: 978-94-6186-043-9

Copyright © 2012 by Nitz Saputra.

All rights reserved. This publication, or any derived parts thereof, may not be reproduced or distributed in any form or by any means, or stored in any data retrieved system, without the prior written permission of the copyright owner.

Printed in The Netherlands

# **CONTENTS**

| Chap | ter 1. Introduction                      |    |

|------|------------------------------------------|----|

| 1.1. | Motivation                               |    |

| 1.2. | Design challenges and overview           | 7  |

| 1.3. | Outline of the thesis                    |    |

| 1.4. | References                               | 12 |

| Chap | ter 2. Technical background              | 17 |

| 2.1. | Introduction                             |    |

| 2.2. | Digital Modulation                       |    |

| 2.3. | Ultra-wideband (UWB)                     |    |

| 2.4. | FM-UWB Modulation Scheme                 |    |

| 2.5. | Specifications for FM-UWB transceiver    | 26 |

| 2.6. | Conventional FM-UWB Transceiver          | 29 |

| 2.7. | Survey of Low Power CMOS Circuits        |    |

| 2.7. |                                          |    |

| 2.7. |                                          | 33 |

| 2.7. |                                          | 35 |

| 2.7. |                                          |    |

| 2.7. |                                          |    |

| 2.8. | Summary                                  |    |

| 2.9. | References                               |    |

| Chap | ter 3. FM-UWB Transmitter                | 41 |

| 3.1. | Introduction                             | 41 |

| 3.2. | FM-UWB Transmitter circuit designs       |    |

| 3.2. | .1. RF Carrier Oscillator                |    |

| 3.2. |                                          |    |

| 3.2. |                                          |    |

| 3.2. |                                          |    |

| 3.2. |                                          |    |

| 3.2. |                                          |    |

| 3.3. | Experimental Measurement                 |    |

| 3.4. | Summary and Conclusions                  |    |

| 3.5. | References                               |    |

| Chap | ter 4. FM-UWB Receiver                   |    |

| 4.1. | Introduction                             | 59 |

| 4.2. | Proposed FM-UWB Receiver                 |    |

| 4.3. | Circuit Designs                          |    |

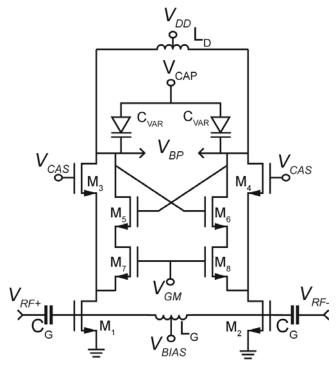

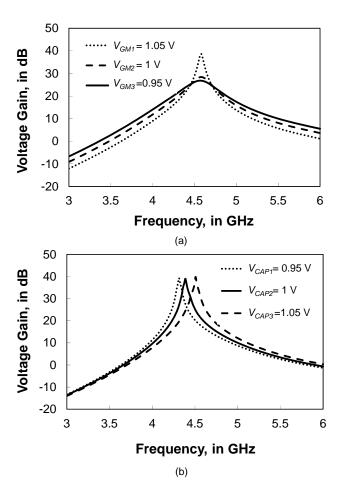

|      | .1. Regenerative Preamplifier and Filter |    |

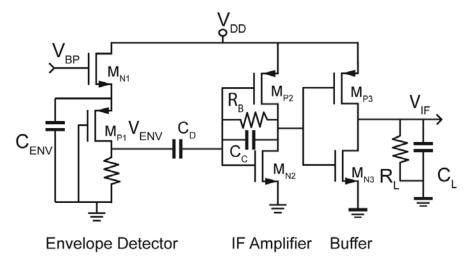

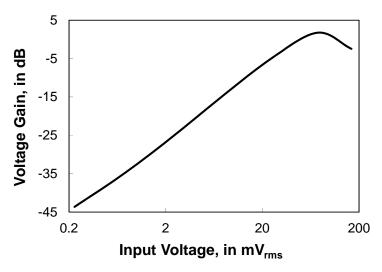

|      | .2. Envelope detector and IF amplifier   |    |

| 4.4. | Measurement Results                      |    |

| 4.5. | Conclusion and Summary                   |    |

| 4.6. | References                               |    |

| Chap | ter 5. FM-UWB Transceiver                | 79 |

| 5.1. | Introduction                             |    |

| 5.2. | Transceiver Architecture                 | 80 |

| 5.3.        | Transceiver Circuit Design                  | 81     |

|-------------|---------------------------------------------|--------|

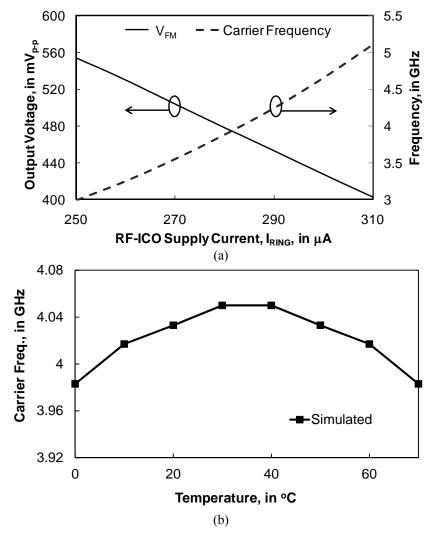

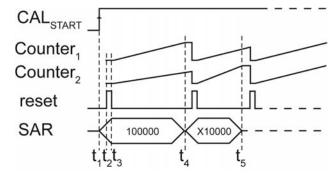

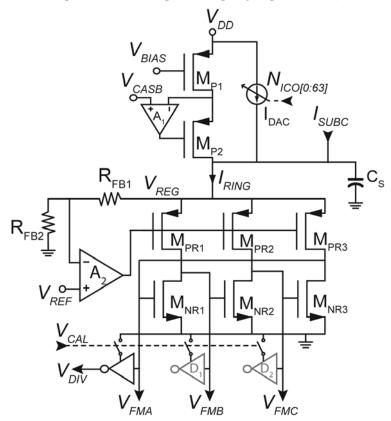

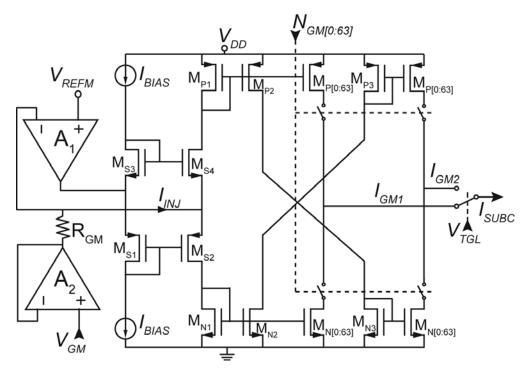

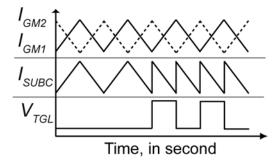

| 5.3.1.      | RF current-controlled ring oscillator       | 81     |

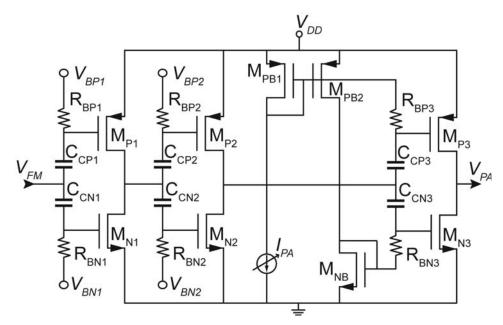

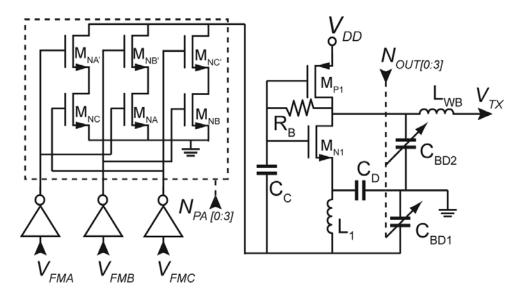

| 5.3.2.      | Frequency tripler and power amplifier       | 83     |

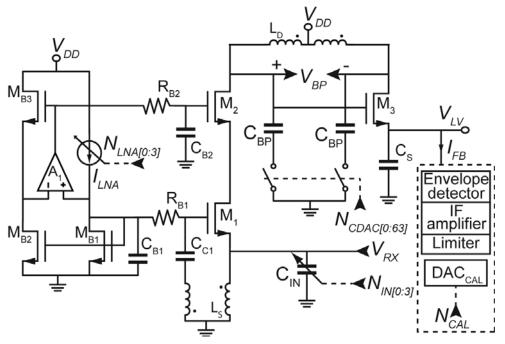

| 5.3.4.      | C r                                         |        |

| 5.3.5.      | Envelope detector, IF-amplifier and limiter | 90     |

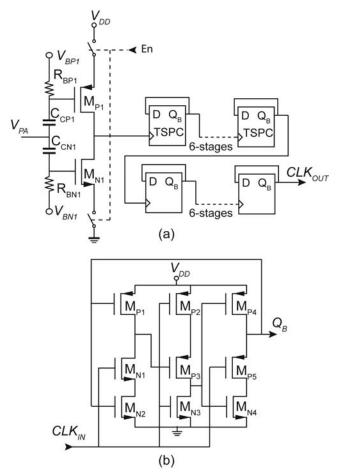

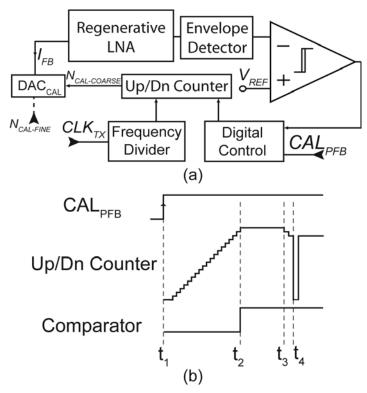

| 5.3.7.      | Positive feedback calibration               | 92     |

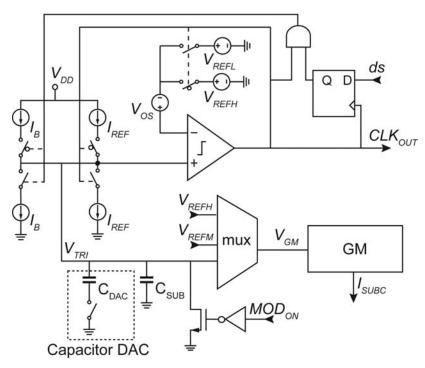

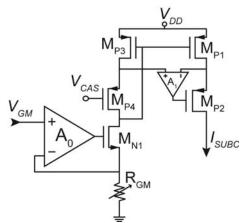

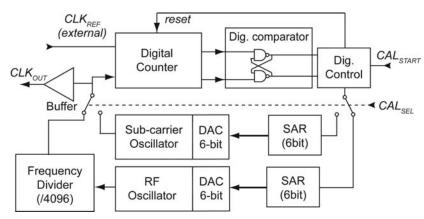

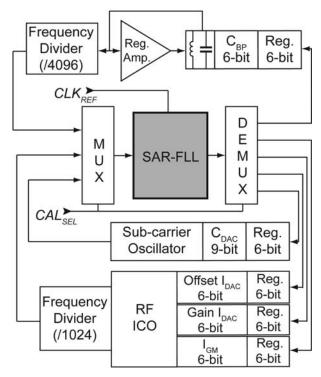

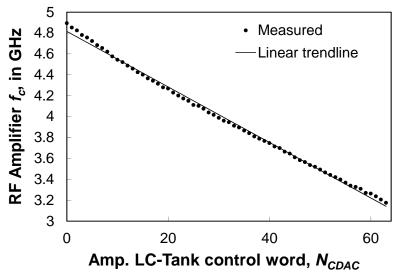

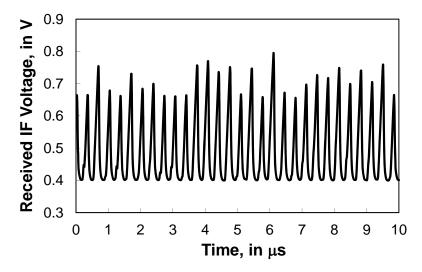

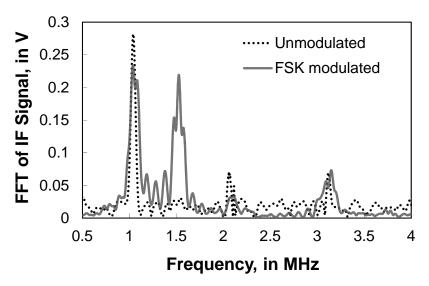

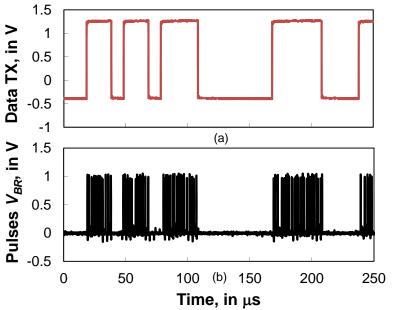

| 5.3.8.      | Frequency calibration                       | 93     |

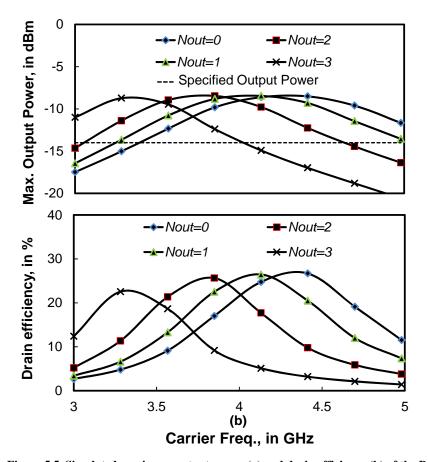

| <b>5.4.</b> | Measurement Results                         | 95     |

| 5.5.        | Conclusions                                 | 107    |

| 5.6.        | References                                  | 108    |

| Chapte      | er 6. Power Management for FM-UWB           | 109    |

| 6.1.        | Introduction                                | 109    |

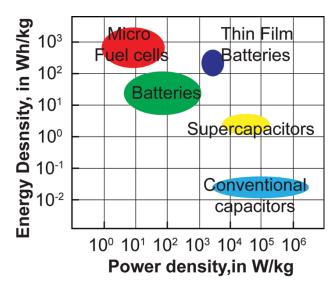

| <b>6.2.</b> | Power management background                 | 112    |

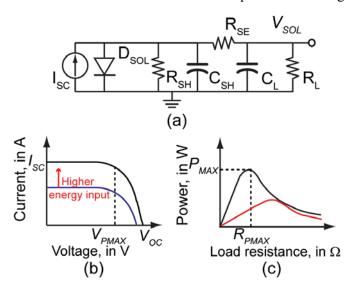

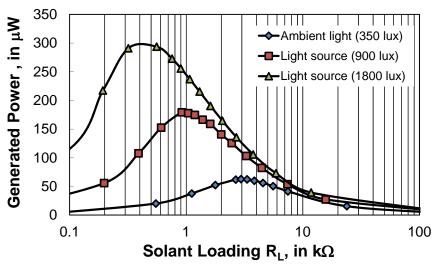

| 6.2.1.      | Solar cell                                  | 112    |

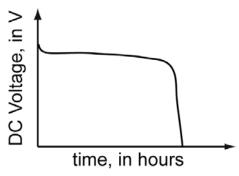

| 6.2.2.      | Battery                                     | 113    |

| 6.2.3.      | Supercapacitor                              | 115    |

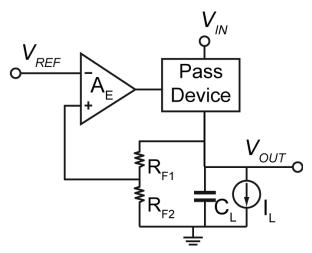

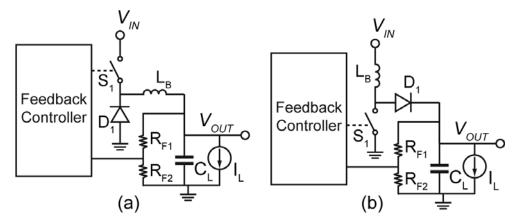

| 6.2.4.      | DC-DC converter                             | 116    |

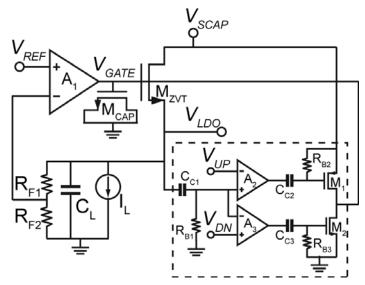

| <b>6.3.</b> | Power management circuit design             | 120    |

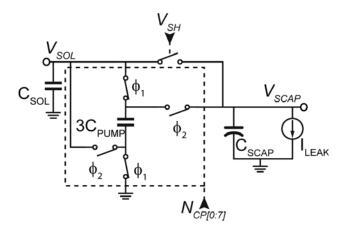

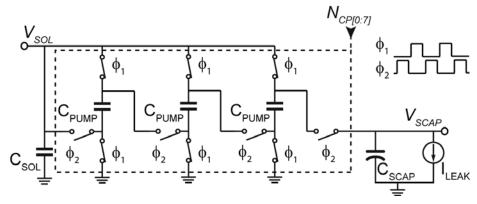

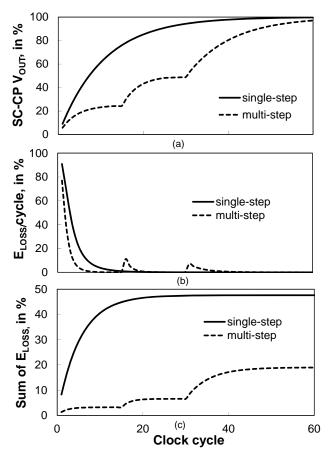

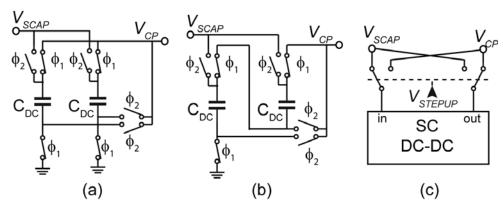

| 6.3.1.      | Switched-capacitor charge pump (SC-CP)      | 123    |

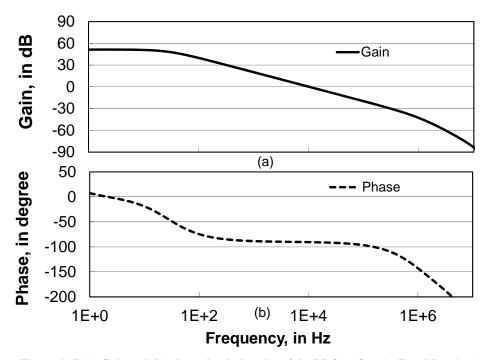

| 6.3.2.      | Low Drop-Out (LDO) Regulator                | 125    |

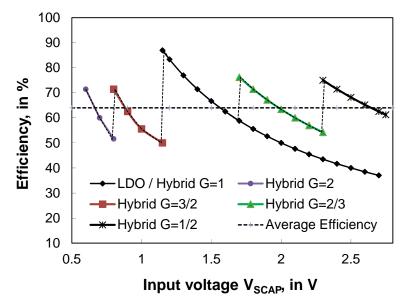

| 6.3.3.      | Switched-capacitor DC converter (SC-DC)     | 128    |

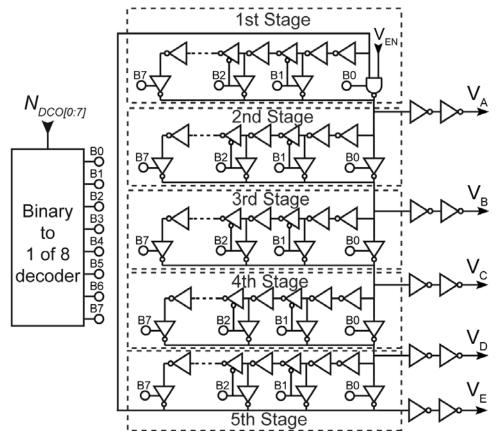

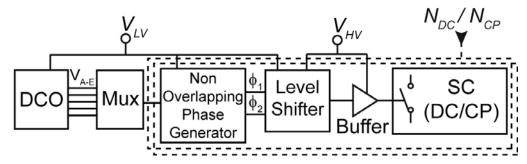

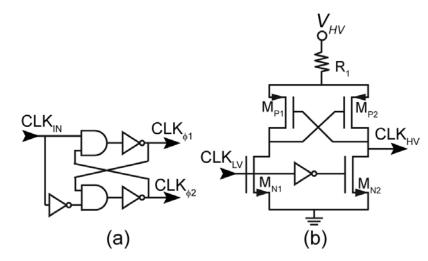

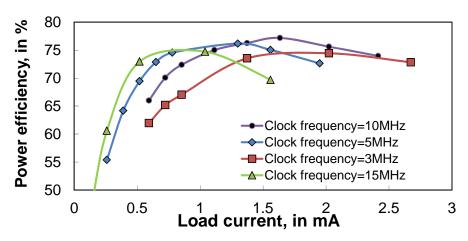

| 6.3.4.      | Clock generator                             | 130    |

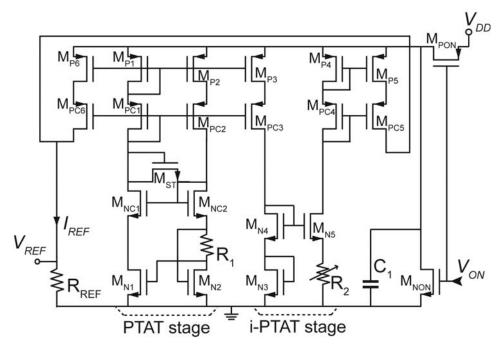

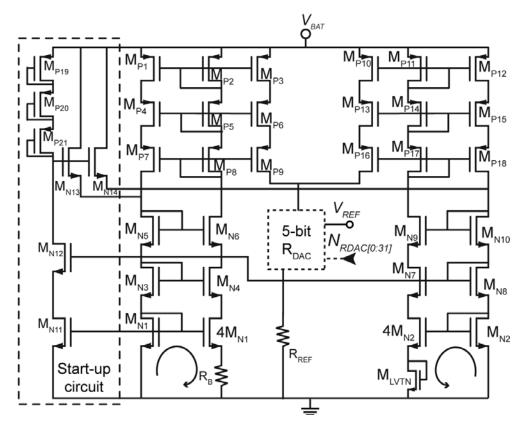

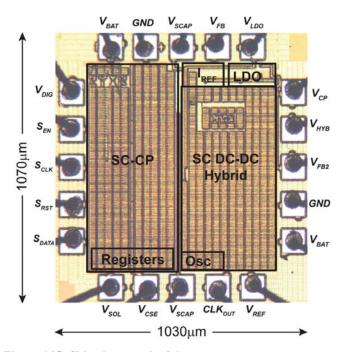

| 6.3.5.      | Bias Generator                              | 131    |

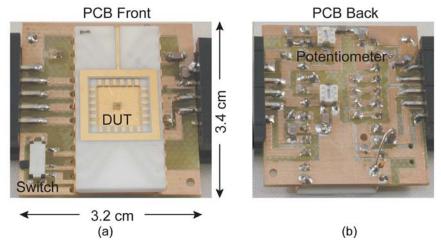

| 6.4.        | Measurement Results                         | 132    |

| 6.4.1.      | SC-CP characterization                      | 134    |

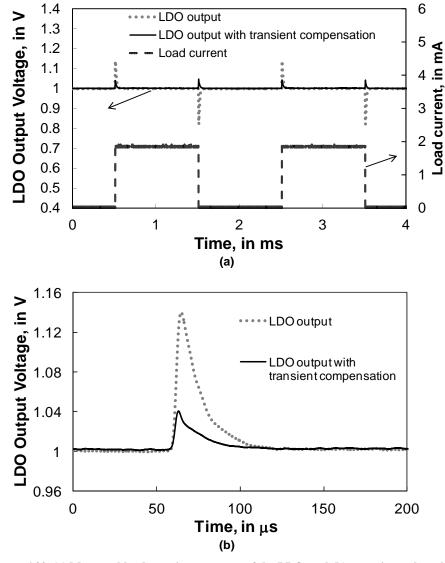

| 6.4.2.      | LDO characterization                        | 136    |

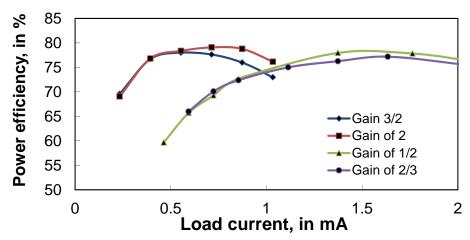

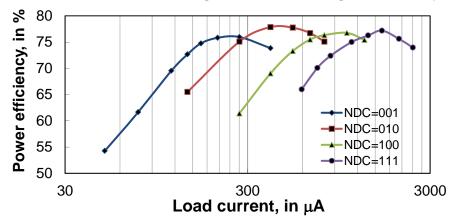

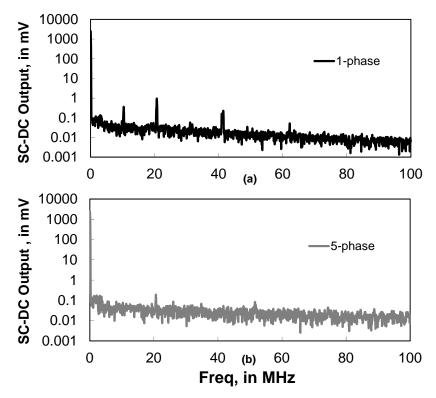

| 6.4.3.      | SC-DC characterization                      | 139    |

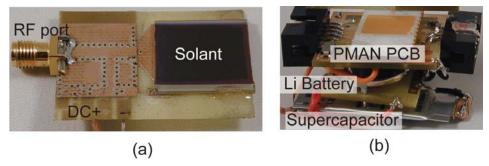

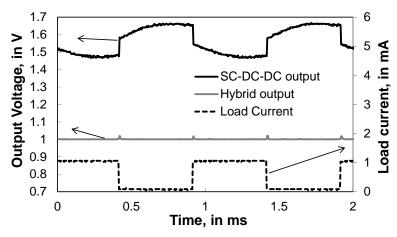

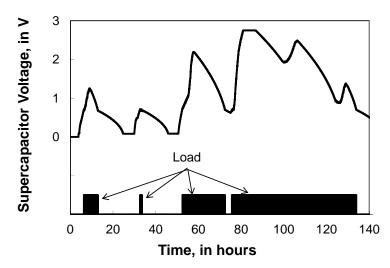

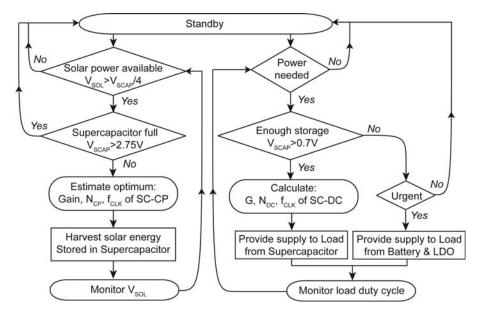

| 6.4.4.      | Power management sub-system                 | 141    |

| <b>6.5.</b> | Conclusions                                 | 143    |

| 6.6.        | References                                  | 144    |

| Chapte      | er 7. Conclusions                           | 147    |

| <b>7.1.</b> | Thesis Contributions                        | 149    |

|             | Suggestions for Future Research             |        |

| <b>7.3.</b> | References                                  | 151    |

| Summ        | ary                                         | 153    |

|             | vatting                                     |        |

|             | Abbreviations                               |        |

|             | Publications                                |        |

|             | wledgement                                  |        |

|             | r's Biography                               | 405    |

|             | a Divuiaviiv                                | I ()-} |

# CHAPTER 1. INTRODUCTION

Human are social beings who like to connect to one another, either in the form of active or passive communication. In active communication, two or more parties exchange information in a two-way fashion, while in passive observation one party receives information sent by another. Technology that provides a medium for information flows that enables such connectivity has always flourished. An active example is the telephone industry (both wired and wireless), a passive example is the television, and for both passive and active is the internet. The common element in these technologies is an interconnection network that allows information or data to be exchanged or spread.

The network can be established using a cable or a wireless channel. Wireless technology simplifies the connection process as it requires no cable installation and less infrastructure, which is attractive for aesthetic and also practical purposes. A wireless connection is advantageous in term of its flexibility and mobility, for example, when the sender and receiver change position, there is no cable that limits their movements or position. On other hand, there are also disadvantages to wireless, such as: slower transmission rate, security risk, and sensitivity to interference. Nowadays, the demand for wireless interconnectivity continues to increase and thus research on wireless communication methods has also flourished [1.1].

Recently, "the internet of things", whereby sensor-enabled physical objects can communicate with each other is under development [1.2]. These devices are able to sense their surrounding environment, and then automatically communicate and coordinate a response for various conditions. Furthermore, a better understanding of the environment locally and globally can be obtained by collecting a lot of data from these devices. Interconnection between devices on a grand scale could open a new potential for applications that could change people's lives. One potential application is precision farming, where data collected by wireless sensors in the ground enable crop conditions to be adjusted individually, e.g., by spreading extra fertilizer on areas that need more nutrients [1.3].

An autonomous wireless system could realize such a network. Autonomous implies that the device is independent from physical infrastructure, and draws so

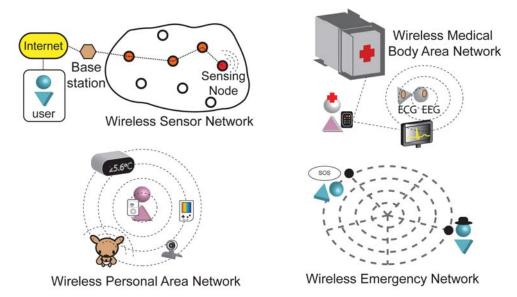

Figure 1.1. Applications for autonomous wireless network.

little net energy that it can be powered by a small battery and/or energy harvested from the local environment (e.g., using solar cell, etc.). Independence is important because the devices are deployed in a dynamic environment, where they could be self-configured, adapting, and communicating wirelessly. Autonomous wireless devices therefore can be installed in hard to reach places (e.g., underground to monitors soil or embedded in a bridge to monitor stress or strain), and must operate maintenance-free for years.

With a limited power source, the output power of the transmitter is kept low to conserve energy, while the receiver will a have lower sensitivity as the signal amplification is similarly limited. Thus, the link span between transmitter and receiver is shorter than for a conventional radio and is only suitable for applications that need local connectivity. At a longer distance, data can be relayed across transceivers forming a multi-hop network.

Autonomous wireless devices are constrained at present by their weight, volume and cost of the energy source (e.g., Li-ion battery). Therefore, energy efficiency is of paramount concern for the wireless link. Harvesting renewable energy from the surroundings will reduce the capacity of the battery required and prolong the operating time of the device when the transceiver is sending/receiving data, and the system is consuming maximum power. Embedded power management is therefore an essential part of the autonomous wireless system in order to conserve energy. The power management controller also monitors if energy can be harvested, estimates amount of energy left in the energy storage, and activates the device on based on priority. Overall, the power management sub-system ensures that the wireless device can be function as long as possible.

There are many other possible applications for such autonomous devices that could be linked to form a network (illustrated in Figure 1.1). One of the important

applications is wireless sensor networks (WSN). Sensors could be deployed to monitor defects due to aging or provide maintenance alerts in a plant, structure, or building. Sensors monitored via a wireless network avoid tedious and expensive inspection in order to collect data and allows the early detection of faults that improves safety [1.4].

Another application is wireless body-area networks (WBANs) or wireless personal-area networks (WPAN). These networks involve sensing our personal surrounding and provide connectivity between handheld devices and our environment. By automatically adapting the environment based on certain condition (e.g., turning on a heater when the temperature drops, or turning on music based on our mood as detected by a camera), a WPAN could ultimately improve our quality of life [1.5]. On a bigger scale, a smart home system could be created enabling automatic management of things such as energy consumption according to demand, monitoring of ambient conditions (e.g., temperature, lighting, music, etc.) and tracking of family members or their pets [1.6]. On an industrial scale, a smart building integrates building automation, telecommunication, facility management, and energy systems [1.7].

Wireless medical body-area networks (WMBAN) or wireless medical telemetry services (WMTS) facilitate continuous data streaming between patients being monitored and healthcare practitioners [1.8]. Monitoring wireless devices are usually compact enough so that they can be worn easily without discomfort. The network could monitor one's blood pressure or heart rate at home, and then transmit the data to a medical practitioner via a smartphone and/or personal computer. At a hospital, the network could monitor intensive care patients' conditions (e.g., their respiratory frequency, blood pressure, etc. [1.9]). A medical doctor could then be alerted in an emergency, which could potentially save a patient's life and improve the chances of surviving for critically ill patients. The wireless network also enables long-term surveillance for chronic patients, the handicapped or the elderly in real time. This promises to reduce the number of hospital visits and the work load of medical workers and healthcare professionals. Another application in the medical area is a bio-metric sensor such as non-invasive heart rate monitoring using radar [1.10].

Natural disasters, such as earthquakes or forest fires, require an emergency communication network [1.11]. A robust and highly redundant ad-hoc network formed by the interconnection of autonomous wireless nodes could provide a backup connectivity during a catastrophic event when infrastructure maybe damaged. The potential applications are not limited to the ones describes above. Other applications and opportunities are likely to emerge when autonomous short distance wireless transceiver devices are widely available [1.12].

#### 1.1. Motivation

An autonomous wireless system is an attractive technology that has a huge potential to improve the quality of human life as described in the previous section. The aforementioned applications motivate the development of wireless transceiver hardware for the system. Development of the physical layer, network protocols, and

4 Motivation

standardization are also needed. As more applications emerge and the technology develops, the performance of the system will improve while the cost reduces due to the increase in production volume and higher manufacturing efficiency. This trend will make the devices required to implement the system ubiquitous at an affordable price.

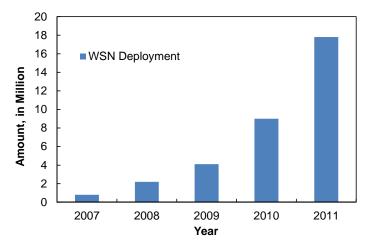

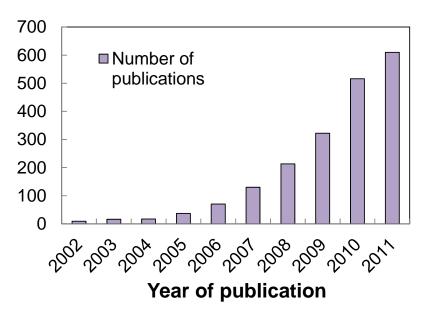

Autonomous wireless systems will likely be deployed on a large scale in the future. Figure 1.2 shows growth in WSN deployment (doubling every year) for the smart building sector, i.e., smart metering, smart home, industrial, healthcare, etc. Market research forecasts that tens of billion modules could be shipped over the next decade [1.14]. These devices would collectively require a lot of energy; assuming that each device consumes just an average of 1 mW, the total power consumption (assuming 10 billion devices) would be on the order of tens of megawatts. Therefore, energy should come from renewable sources collected through scavenging in order to be sustainable. Energy can be scavenged from many sources in the surrounding environment, such as mechanical vibration, light, heat, and microwaves radiation [1.15].

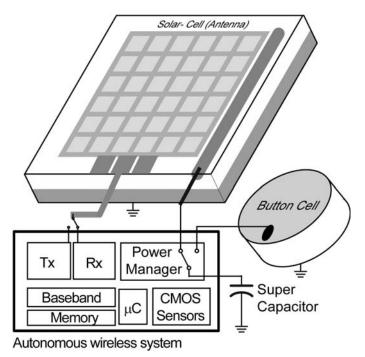

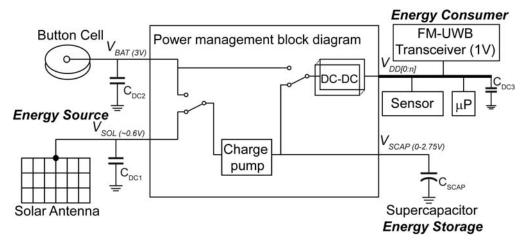

Figure 1.3 shows an example of integrated autonomous wireless system that might be implemented in the near future. The integrated wireless system consists of a wireless transceiver, baseband, embedded memory, micro-controller, power management, and CMOS sensors. A solar cell harvests energy and is also integrated together with the antenna for wireless transmission, while a button cell battery is a back-up power source. Harvested energy is stored temporarily on a supercapacitor or rechargeable battery. The ultimate goal is to build a device that operates for an indefinite period of time by managing energy harvesting and consumption itself, while sharing information collected by the CMOS sensors with other wireless devices.

Complementary metal-oxide semiconductor (CMOS) is a silicon integrated circuit (IC) technology that can integrate more than 1 billion transistors on-chip (at the current time of writing) to realize high performance analog, digital and RF circuits on the same die [1.16], [1.17]. System integration reduces the number of

Figure 1.2. WSN deployment in smart building sector [1.13].

external components and IC chips (e.g., a one chip system). The advantages of integration using CMOS are: lower cost in high volume production, small size, less input/output interfacing, and lower leakage or standby power consumption. Furthermore, the trend in scaling of CMOS transistors to even smaller dimensions in the future will push integration levels higher, improve RF performance and lower power consumption [1.18].

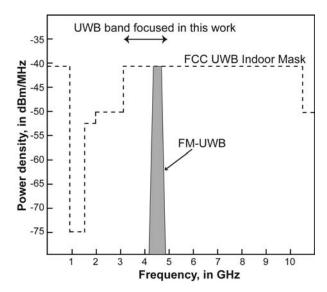

Wireless interfaces often utilize the unlicensed (e.g., ISM) bands currently occupied by WiFi, Bluetooth and Zigbee appliances. However, the potential number of short-range wireless devices operating in a body-area or wireless sensor network would crowd the same space, and the resulting congestion would degrade the quality of service and link availability. However, other frequency bands could be used. The US Federal Communications Commission (FCC) [1.19] authorized the unlicensed use of ultra-wideband (UWB) transceivers in the 3.1–10.6 GHz range. The bandwidth available for UWB provides us opportunity to work on a UWB wireless transceiver for an autonomous wireless system. Due to the overlap with other communication channels in this band, the FCC specified a power emission limit for UWB signals of -41.3 dBm/MHz between 3.1 and 10.6 GHz. The spectral density limit is not constant over the entire band as seen from the specific indoor mask proposed by the FCC is shown in Figure 1.4. In Europe, ETSI/CEPT proposed a similar mask [1.20]. However, the 3.1-5 GHz band used for the transceiver designed in this thesis is more restricted in Europe, i.e., the transceiver needs to employ a detect and avoid scheme, otherwise the transmitted power spectral density is limited to -70 dBm/MHz [1.21]. It should be noted that the transceiver operating frequency can be scaled easily. The effective isotropic radiated power (EIRP)

Figure 1.3. Building block for the envisioned autonomous wireless system.

6 Motivation

Figure 1.4. Ultra-wideband spectrum density.

spectral density limit and coexistence between UWB and other wireless standards is the subject of ongoing study [1.22].

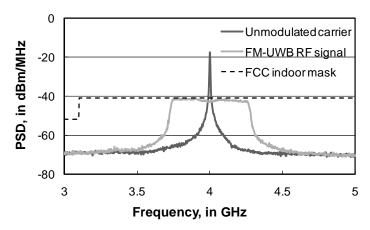

The work in this thesis focuses on the design of low power FM-UWB transceiver for short-distance, low data rate indoor applications. Simplicity in the transceiver architecture, robustness to interference, and low-cost access to unlicensed spectrum available worldwide motivates us to work on a low power FM-UWB transceiver for autonomous wireless systems. Frequency-modulated ultra-wideband (FM-UWB) is a low-complexity scheme for wireless data communication at rates up to 250 kbit/s across spans less than 10 m [1.23]. The FM-UWB radio does not require a local oscillator or carrier synchronization at the receiver, which results in a simple transceiver architecture that consumes little power in continuous operation [1.24]. FM-UWB is intrinsically robust against multipath fading and narrowband interference, while mitigation techniques (e.g., using a notch filter or applying detect and avoid schemes) can be added to enhance its robustness [1.25]. An FM-UWB physical layer for body area networking has also been developed [1.26]. FM-UWB was recently adopted into the IEEE standard by the IEEE802.15 task group 6 [1.27]. Short distance transmission allows for a working link at a transmit power less than -10 dBm, and also minimizes interference to other wireless systems nearby. Relatively low transmit power reduces the risk of radiation harmful to the human body, which is important in WBAN and WMBAN applications [1.5]. Uniform spectral density and steep spectral roll-off at a typical bandwidth of 500 MHz (see Figure 1.4) for the transmit signal power spectrum is easily realized. Co-existence with other communication systems may be accommodated by transmitting the signal within a selected portion of the bandwidth allocated for UWB systems, according to the cognitive radio paradigm [1.28]. The FM-UWB scheme will be analyzed and described in more detail in the following Chapter 2 of this thesis.

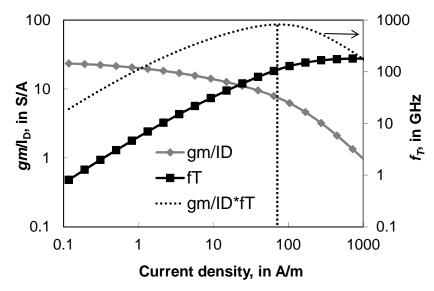

## 1.2. Design challenges and overview

Despite the advantages of implementing an autonomous wireless system in CMOS, the technology also introduces compromises in performance. For example, the transit frequency  $(f_T)$  of a transistor is lower in CMOS than in bipolar junction transistor (BJT) technology. Although there are disadvantages to CMOS compared with the BJT, there are incentives to use CMOS, e.g., seamless integration with digital circuits and manufacturing capacity.

In general, integrating the wireless system on a single chip adds an extra complexity and challenge. A circuit has to satisfy the desired specifications regardless of manufacturing process, supply voltage, or temperature (i.e., PVT) variations in order to increase its manufacturability and yield [1.33]. Robustness against interference and coexistence with other wireless systems is also necessary in a wireless application. In a wireless transmitter, unwanted interference with other

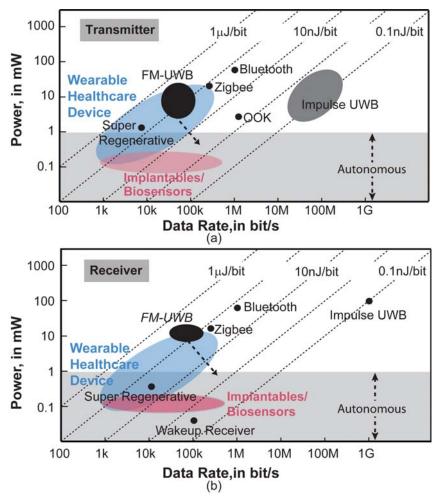

Figure 1.5. Energy efficiency of various wireless (a) transmitter and (b) receiver.

| Ref.   | Year | CMOS<br>Technology<br>(nm) | Modula<br>tion | Max. Tx<br>power<br>(dBm) | DC<br>power<br>(mW) | Tx<br>efficiency<br>(%) | Data<br>rate<br>(Mbit/s) | Energy per<br>bit<br>(nJ/bit) |

|--------|------|----------------------------|----------------|---------------------------|---------------------|-------------------------|--------------------------|-------------------------------|

| [1.42] | 2007 | 180                        | OOK            | -11.4                     | 3.8                 | 1.9                     | 1                        | 3.8                           |

| [1.43] | 2005 | 180                        | OOK            | -4.4                      | 1.6                 | 22                      | 0.005                    | 320                           |

| [1.44] | 2008 | 90                         | UWB            | -16.4                     | 4.36                | 0.52                    | 15.6                     | 0.28                          |

| [1.45] | 2006 | 130                        | BFSK           | -5                        | 1.12                | 28.2                    | 0.3                      | 2.3                           |

| [1.46] | 2010 | 180                        | BFSK           | -5.2                      | 1.15                | 26.2                    | 0.125                    | 9.2                           |

TABLE 1.1 Transmitter Performance Summary

TABLE 1.2 RECEIVER PERFORMANCE SUMMARY

| Ref.   | Year | CMOS<br>Technology<br>(nm) | Modula<br>tion | Sensitivity<br>(dBm) | SIR at<br>10 MHz<br>offset | DC<br>power<br>(mW) | Data rate<br>(Mbit/s) | Energy per<br>bit<br>(nJ/bit) |

|--------|------|----------------------------|----------------|----------------------|----------------------------|---------------------|-----------------------|-------------------------------|

| [1.43] | 2005 | 180                        | OOK            | -100.5               | N/A                        | 0.4                 | 0.005                 | 80                            |

| [1.47] | 2009 | 90                         | OOK            | -72                  | -10                        | 0.052               | 0.1                   | 0.52                          |

| [1.48] | 2010 | 180                        | BFSK           | -86                  | -10                        | 0.215               | 0.25                  | 0.84                          |

| [1.49] | 2007 | 90                         | UWB            | -99                  | -15                        | 35.8                | 0.1                   | 2.5                           |

| [1.51] | 2010 | 130                        | UWB            | -55                  | -15                        | 3.3                 | 1.3                   | 3.3                           |

devices is mitigated by limiting the output power, filtering, and accurate control of center frequency or bandwidth of the transmitted signal. A wide tuning range, along with a detect-and-avoid scheme can be employed to combat interference in the receiver [1.34]. This implies that the system must be reconfigurable, and on-chip calibration circuitry must be included to handle any PVT variations and interference. Electrostatic discharge (ESD) protection must also be included. The ESD event could damage the input output (I/O) part of the chip, or in worst case, damage the entire chip. ESD protection in the RF signal path adds parasitic capacitance which limits the bandwidth and could cause signal degradation and distortion [1.35].

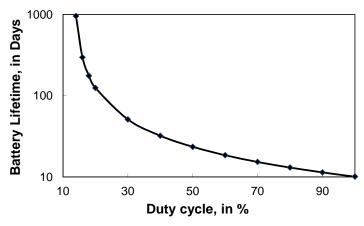

Improving energy efficiency, defined as ratio of power consumption (in Watts) to data rate (in bit/s), of the autonomous wireless system is the main challenge in this work. If a continuous operating lifetime of 50 days using a 10 gr Li-ion battery (energy density of 120 W-h/kg [1.36]) is desired, the transceiver should have an energy efficiency of less than 10 nJ/bit when operating at a data rate of 100 kbit/s. Conventional radio transceivers (e.g., WiFi, Bluetooth and Zigbee) consume approximately an order of magnitude more energy per bit transmitted as shown in Figure 1.5 [1.37]-[1.39]. This constrains their operating lifetime, battery size, and potential applications in autonomous systems.

Duty-cycling of a conventional wireless transceiver to scale the power consumption may not be possible if real-time data connectivity and high reliability are required. For example, many wireless health-monitoring devices require continuous data streaming between the patient being monitored and healthcare practitioners [1.40]. Health-monitoring devices use sensors that typically produce data rates in the range of 1-100 kbit/s, as opposed to multimedia applications that might stream video at 100 Mbit/s [1.41]. The FM-UWB scheme is suitable for lower data rate applications (see Figure 1.5), although improvement in energy

efficiency is required in order for it to compete with other radio schemes (e.g., wake-up receiver or super regenerative transceiver) in autonomous applications such as implantable biosensors.

Some narrowband and ultra-wideband radio technologies have demonstrated energy efficiency suitable for a wireless autonomous system. On the transmitter side (see Table 1.1), efficiency (measured as transmitted output power divided by the DC consumption, along with energy per bit) indicates the level of autonomy that may be achieved. On-off keying (OOK) modulation has been a popular choice for implementation of ultra low-power radio demonstrators. An OOK transmitter operating with an efficiency of 3.8 nJ/bit at 1 Mbit/s was reported in [1.42]. The super-regenerative transmitter designed by [1.43] also employs OOK modulation running at 5 kbit/s, and achieves 320 nJ/bit efficiency and 22% transmitter efficiency. Although similar in total power consumption, the energy efficiencies of these examples are radically different due to the factor 10<sup>3</sup> in their respective data rates. An external high-O SAW or BAW RF bandpass filter shapes the transmit output spectrum, but adds to the cost of components, their assembly, packaging, and testing. Time-domain impulse radio is a UWB technology suitable that offers the potential for improved energy efficiency at low data rates. However, the spectral side lobes emitted by an impulse UWB transmitter could interfere with other users. Also, the poor peak-to-average transmit power ratio at low data rates also affects the efficiency of the antenna driver adversely [1.44]. Binary frequency shift keying (BFSK) transmitters in [1.45] and [1.46] achieve transmitter efficiency of 28% and 26%, respectively. BFSK transmitter benefits from the high efficiency PA that can be designed for the constant envelope signal in BFSK. The transmitter in [1.45] uses a 0.4 V supply that is not commonly used. The transmitter in [1.46] directly couples the oscillator to the load through a matching network, which cause vulnerability to frequency pulling from strong interference.

On the receiver side (see Table 1.2), energy per bit indicates the receiver efficiency. Signal-to-interference ratio (SIR), measured when the bit-error rate (BER) deteriorates to 10<sup>-3</sup> due to narrowband interference in-band or at a small frequency offset (e.g., 10 MHz), indicates the robustness of the receiver. The narrowband 'wake-up' receiver monitors the wireless channel continuously and activates the main transceiver when addressed by the wireless network. An energy efficiency of 520 pJ/bit at a data rate of 100 kbit/s and -72 dBm RF sensitivity was reported for a prototype wake-up receiver [1.47]. However, the modest sensitivity and OOK modulation scheme used by the wake-up radio restricts its span and reliability in a wireless link. Also, an off-chip bulk acoustic wave (BAW) RF preselect filter is required to reject potential interferers in the wake-up radio design. which increases the size and cost of the receiver. The super-regenerative receiver in [1.48] achieves high energy efficiency and sensitivity by using BFSK modulation. However, the narrowband receiver is susceptible to multipath fading or interference effects because the front-end operates at a fixed input frequency and is not tunable. The receiver relies on the narrowband filter, and achieves an SIR of -10 dB at 10 MHz offset, but it degrades to 0 dB in-band. The UWB receiver in [1.49] also realizes good energy efficiency by duty cycling, but it requires synchronization to the received data, and possibly a wake-up receiver to detect incoming data.

| Parameters                     | [1.52]  | [1.53] | [1.54] | [1.55]  | [1.56]   |

|--------------------------------|---------|--------|--------|---------|----------|

| Year of publication            | 2006    | 2008   | 2009   | 2009    | 2011     |

| Technology                     | 180 nm  | 180 nm | 180 nm | 130 nm  | 180 nm   |

|                                | CMOS    | CMOS   | CMOS   | CMOS    | CMOS     |

| RF Tuning Range (GHz)          | 2.7-4.1 | 0.5-5  | 3-5.6  | 6.2-8.2 | 3.2-4.45 |

| $V_{DD}(V)$                    | 1.8     | 1.8    | 1.8    | 1.1     | 1.6      |

| Phase Noise (dBc/Hz at 1 MHz)  | -70     | -75    | -80.6  | -107    | -92      |

| Max. Output Power (dBm)        | -34     | -9     | -11    | -5      | -12.8    |

| Bandwidth (MHz)                | -       | 550    | -      | 550     | 700      |

| Sub-carrier Frequency (MHz)    | -       | 1      | -      | 1       | 51       |

| Data rate (kbit/s)             | 100     | 100    | -      | 100     | 1000     |

| Power Consumption (mW)         | 7.2-14  | 2.5-10 | 19.8   | 4.6     | 18.2     |

| Active Area (mm <sup>2</sup> ) | 0.7     | 0.25   | 0.77   | 0.062   | 1.4      |

| Energy Efficiency (nJ/bit)     | 72-140  | 70-100 | 198    | 46      | 18.2     |

TABLE 1.3 FM-UWB TRANSMITTER PERFORMANCE COMPARISON

TABLE 1.4 FM-UWB RECEIVER PERFORMANCE COMPARISON

| Parameters                      | [1.57]         | [1.58]                   | [1.59]                   | [1.60]         |

|---------------------------------|----------------|--------------------------|--------------------------|----------------|

| Year of publication             | 2006           | 2006                     | 2009                     | 2011           |

| Technology                      | 180 nm<br>CMOS | SiGe<br>BiCMOS<br>180 nm | SiGe<br>BiCMOS<br>250 nm | 180 nm<br>CMOS |

| RF band, in GHz                 | 3-5            | 3.1-4.9                  | 7.2-7.7                  | 3.4-4.3        |

| Power Consumption, in mW        | 19.8           | 10                       | 9.1                      | 9.6            |

| Receiver sensitivity, in dBm    | -65            | -46                      | -86.8                    | -70            |

| Data rate, in kbit/s            | 100            | 100                      | 50                       | 50             |

| Energy efficiency, in nJ/bit    | 198            | 100                      | 182                      | 192            |

| Active area, in mm <sup>2</sup> | -              | 0.72                     | 0.88                     | 1              |

Synchronization in IR-UWB requires complex hardware and additional power consumption [1.50]. The other UWB receiver in [1.51] operates at 1.3 Mbit/s, but has poor sensitivity (-55 dBm) and is confined to RF inputs below approximately 1 GHz. The UWB receiver obtains an in-band SIR of -15 dB, due to its spectral diversity.

A summary of existing FM-UWB transceivers reported in recent publications are listed in Table 1.3 and 1.4 for transmitters and receivers, respectively. Unfortunately, it is clear that the energy efficiency is nowhere near the 10 nJ/bit that would make it practical for an autonomous wireless system. The work in this thesis attempts to shows the suitability of FM-UWB for low power, low data rate

applications such as WSN, WMBAN, and WPAN, which will increase interest in FM-UWB transceiver development and implementation.

The main challenge in power management is to maintain energy efficiency across different operating conditions and voltage levels. It has to provide the wireless system with a clean supply voltage with minimal ripple. Both the input and output voltages have to be monitored. A digital controller sets the power manager configuration based on conditions such as the availability of energy to be harvested, amount of required current load, requirement on step up/down voltage conversion, etc. The DC to DC converter in the power management sub-system is constrained by the chip area required for passive components compared to the area occupied by transistors in an IC that can be produced economically. Realizing on-chip passive devices, e.g., a capacitor with a size of few nF or inductor with a size of few  $\mu$ H [1.61], will requires few mm² of die size.

Several challenges to realize an on-chip autonomous wireless system have been described. The work in this thesis attempts to address many of the key barriers to implementation and to propose and demonstrate solutions. The objective of the work described in this thesis is to realize a fully-integrated FM-UWB transceiver consuming less than 1 mW at an energy efficiency of better than 10 nJ/bit (see arrow trajectory in Figure 1.5). The power management sub-system will also be prototyped so that a battery and power scavenging devices can be used as energy sources.

#### 1.3. Outline of the thesis

This thesis is divided into seven chapters. Chapter 2 describes the technical background of a wireless transceiver. Several wireless modulation schemes relevant to low power wireless systems will be described and compared, and the FM-UWB scheme will be highlighted and analyzed in detail. A wireless link margin analysis and parameter-performance trade-offs for the transceiver are described in Chapter 2 along with the specification for the proposed autonomous transceiver. Conventional FM-UWB transceiver designs from the recent literature will be described and analyzed. The efficiency limitations of a wireless system are analyzed, and several CMOS circuit techniques from the literatures that attempt to improve power efficiency are described.

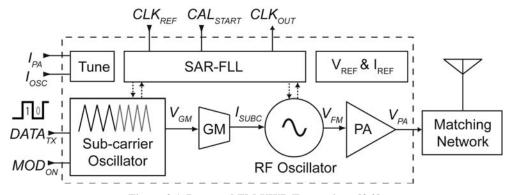

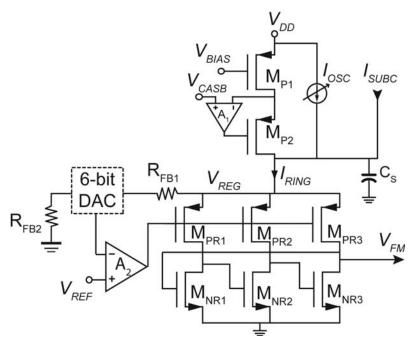

A proposed low-power FM-UWB wireless transmitter is the subject of Chapter 3. A fully-integrated transmitter prototype was implemented using 90 nm CMOS and tested as a proof of the concept. A current-controlled ring oscillator generates the RF carrier frequency, followed by a class-AB power amplifier (PA) to drive the antenna. A frequency calibration scheme utilizing the successive approximation technique and a frequency-locked loop (FLL) is also proposed and implemented. The transmitter has been characterized completely and the results validate the proposed architecture.

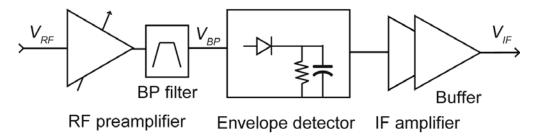

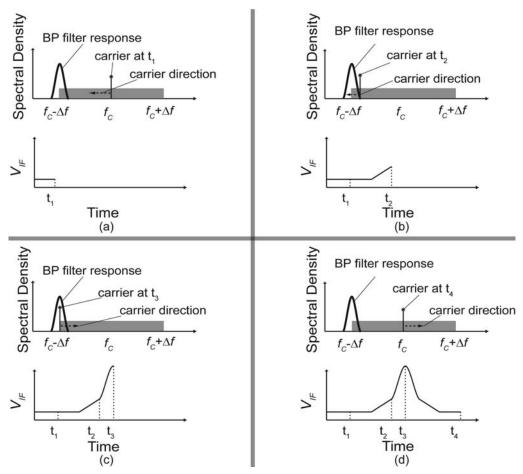

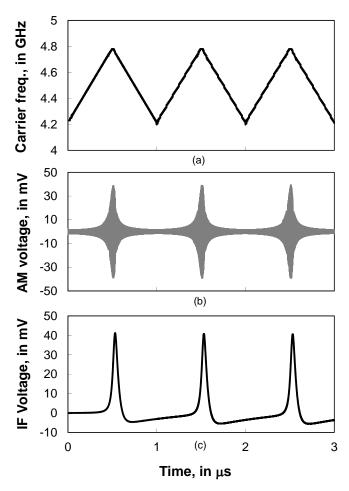

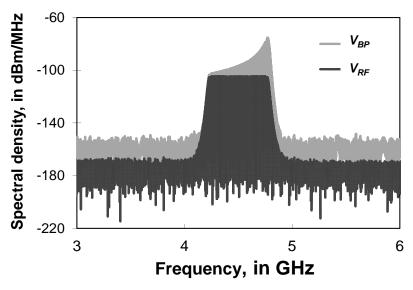

A wireless receiver design for FM-UWB using a regenerative RF preamplifier and an envelope detector is presented in Chapter 4. The receiver front-end was implemented in 65 nm CMOS, while baseband circuitry is implemented externally using off-chip components. The regenerative receiver is analyzed and compared

12 References

briefly with the conventional FM-UWB receiver. Measured data for the new design are compared with other low-power receivers.

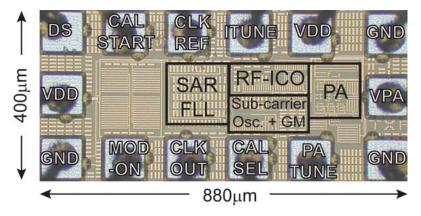

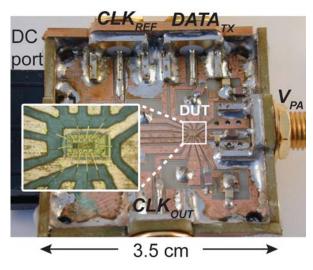

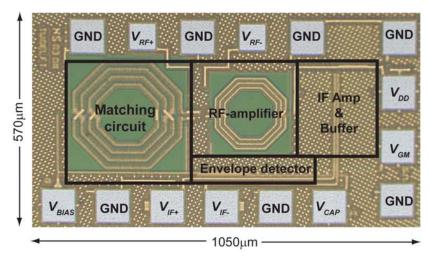

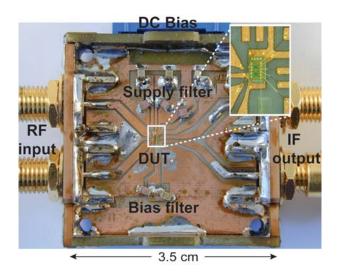

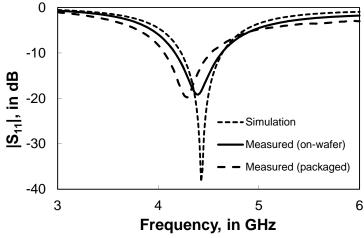

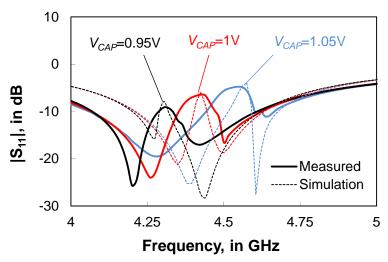

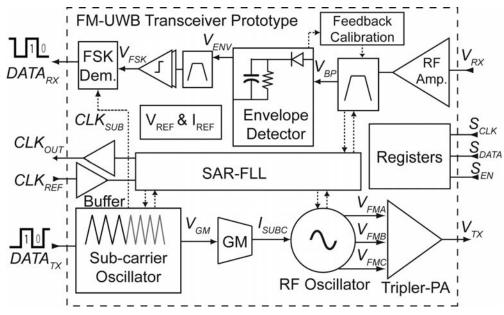

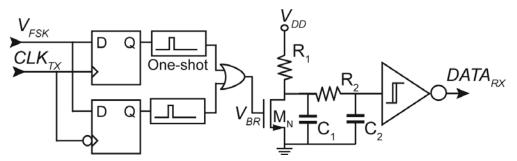

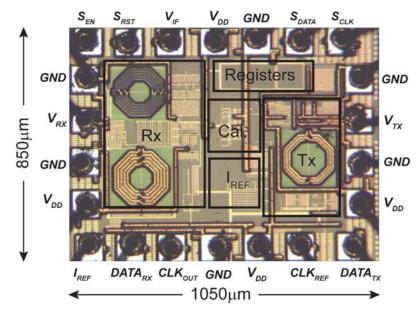

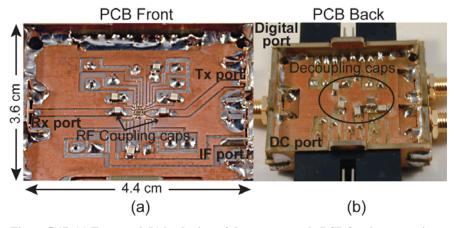

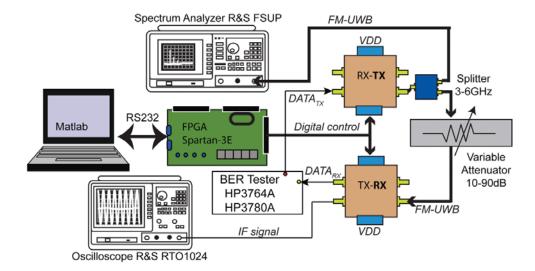

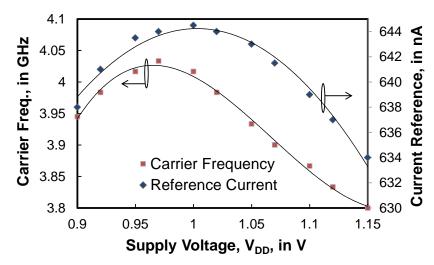

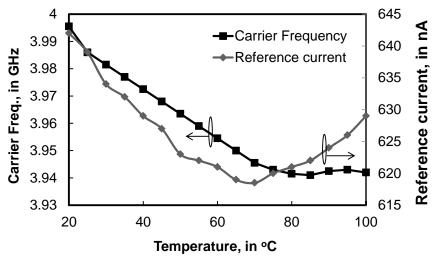

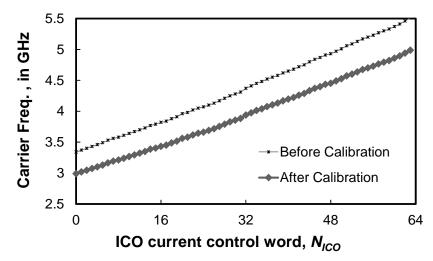

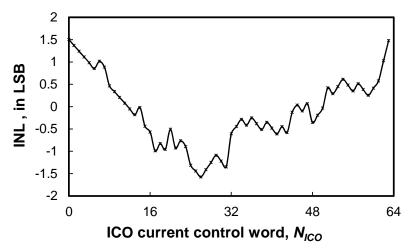

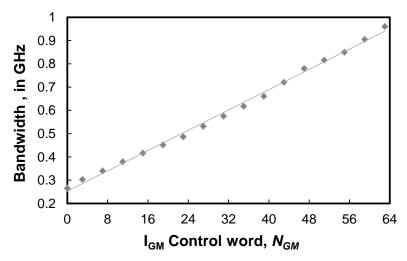

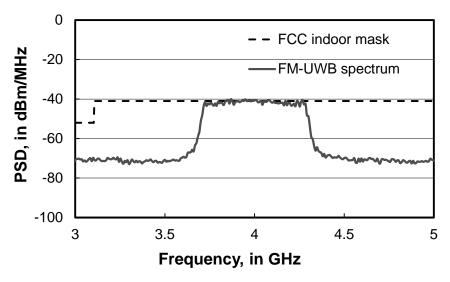

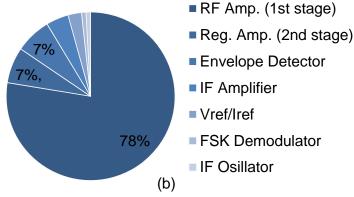

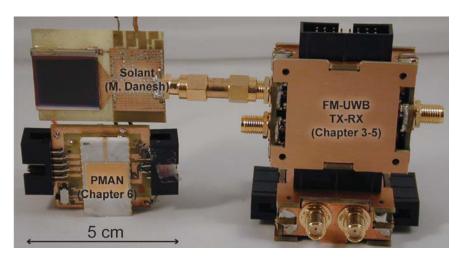

A fully-integrated FM-UWB transceiver prototype based on receiver and transmitter concepts described in Chapters 3 and 4 is the subject of Chapter 5. The RF-ICO generates a signal at one-third the operating frequency, which is then frequency multiplied by a tripler and amplified. The regenerative receiver front-end amplifier is implemented using an inductive positive feedback followed by envelope detector and IF amplifier. The transceiver was implemented in 90 nm CMOS and includes on-chip biasing, baseband processing, a serial input control port, and digital calibration circuitry.

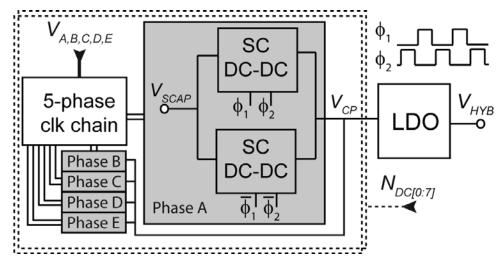

Chapter 6 describes a power management circuit suitable for an autonomous FM-UWB system. Building blocks including the DC-DC converter, battery, supercapacitor, and solar cell described in the first sections of this chapter. The power management sub-system uses a button cell battery and solar cell as energy sources, and a supercapacitor to store energy during transient conditions. A hybrid of a switched-capacitor and an LDO regulator is designed to provide a constant supply voltage for the transceiver with average conversion efficiency of 64%, and ripple of less than 0.1 mV in the output voltage.

Finally, the main findings and major contributions of this research work are summarized in Chapter 7. Suggestions for future work aimed at developing the concepts and presented prototypes conclude this thesis.

#### 1.4. References

- [1.1] J. M. Rabaey, J. Ammer, T. Karalar, S. Li, B. Otis, M. Sheets, T. Tuan, "PicoRadios for wireless sensor networks: the next challenge in ultra-low-power design," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2002, pp. 200-201.

- [1.2] A. Hamilton, "Time magazine's best invention of 2008: the internet of things." Available: http://www.time.com/time/specials/packages/0,28757,1852747,00.html.

- [1.3] M. Chui, M. Loffler, R. Roberts, "The internet of things". Available on: <a href="http://www.mckinseyquarterly.com/The Internet of Things 2538">http://www.mckinseyquarterly.com/The Internet of Things 2538</a>.

- [1.4] D. Steel, "Smart dust," UH ISRC technology briefing. Available: http://www.bauer.uh.edu/uhisrc/FTB/Smart%20Dust/Smart%20Dust.pdf

- [1.5] W. Rhee, N. Xu, B. Zhou, Z. Wang, "Low power, non-invasive UWB systems for WBAN and biomedical applications," *International conference on ICTC*, Nov. 2010, pp. 35-40.

- [1.6] S. Hussain, S. Schaffner, D. Mosychuck, "Applications of wireless sensor network and RFID in a smart home environment," *Proc. of communications networks and services research* conference, May 2009, pp. 153-157.

- [1.7] "What is a smart building?," Available: http://www.smart-buildings.com.

- [1.8] K. A. Townsend, J. W. Haslett, T. K. Tsang, M. N. El-Gamal, K. Iniewski, "Recent advances and future trends in low power wireless systems for medical applications," *Proc. System-on-Chip Real-Time Applications*, July 2005, pp. 476-481.

- [1.9] B. Gupta, E. Cianca, M. Ruggieri, R. Prasad, "End to end vital sign monitoring system with FM-UWB technology," *International conference on devices and communications*, Dec. 2011.

- [1.10] E. Cianca and B. Gupta, "FM-UWB for communications and radar in medical application," Wireless Personal Communications, Springer, Vol. 51, pp. 793-809, Dec. 2009.

- [1.11] P. Pawelczak, R. V. Prasad, L. Xia, I. G. M. M. Niemegeers, "Cognitive radio emergency networks-requirement and design," *IEEE Symp. on new frontiers in dynamic spectrum access* networks, Nov. 2005, pp. 601-606.

- [1.12] J. M. Rabaey, F. Burghardt, Y. H. Chee, et. al., "Short distance wireless, dense networks and its opportunities," 10th Euromicro Conference on Digital System Design Architectures, Methods and Tools, Oct. 2007.

- [1.13] Plextek, "Wireless sensor networks final report." Available: <a href="http://stakeholders.ofcom.org.uk/binaries/research/technology-research/wsn3.pdf">http://stakeholders.ofcom.org.uk/binaries/research/technology-research/wsn3.pdf</a>.

- [1.14] Onworld, "Smart technology research, we provide world class business intelligence on emerging wireless markets." Available: <a href="http://www.onworld.com">http://www.onworld.com</a>

- [1.15] M. Rahy, "ULP meets energy harvesting: A game-changing combination for design engineers," Texas Instrument white paper, 2008.

- [1.16] B. Jagannathan, R. Groves, D. Goren, et al, "RF CMOS for microwave and mm-wave applications," *Proc. of silicon monolithic integrated circuits in RF systems*, Jan. 2006, pp. 259-264.

- [1.17] Z. Luo, A. Steegen, M. Eller, et al., "High performance and low power transistors integrated in 65 nm bulk CMOS technology," *IEDM Technical Digest*, pp. 661-664, Dec. 2004.

- [1.18] P. H. Woerlee, M. J. Knitel, R. van Langevelde, et al, "RF-CMOS performance trends," *IEEE transaction on electron devices*, Vol. 48, No. 8, pp. 1776-1782, Aug. 2001.

- [1.19] Revision of Part 15 of the Commission's Rules Regarding Ultra-Wideband Transmission Systems, First Report and Order, FCC 02-48, Federal Communications Commissions (FCC), 2002.

- [1.20] ECC decision of 24 March 2006 on the harmonized conditions for devices using ultrawideband (UWB) technology in bands below 10.6 GHz, C.E. document, 2006.

- [1.21] "Technical specification ultra-wideband (UWB) devices." Available on http://www.ida.gov.sg/doc/Policies%20and%20Regulation/Policies\_and\_Regulation\_Level2 /IDATSUWB.pdf

- [1.22] CEPT report to European Commission in response to: Harmonized radio spectrum use for ultra-wideband systems in the European Union, March 2005.

- [1.23] J. F. M. Gerrits, M. Kouwenhoven, P. van der Meer, J. R. Farserotu, and J. R. Long, "Principles and limitations of ultra-wideband FM communication systems," *EURASIP Journal on applied signal processing*, pp. 382-396, 2005.

- [1.24] J. F. M. Gerrits, H. Bonakdar, M. Detratti, et al, "A 7.2 7.7 GHz FM-UWB transceiver prototype," *IEEE International conference on ultra-wideband*, Sept. 2009, pp. 580-585.

- [1.25] J. F. M. Gerrits, J. R. Farserotu, J. R. Long, "Robustness and interference mitigation for FM-UWB BAN radio," *International symposium on medical information & communication technology*, March 2011, pp. 98-102.

- [1.26] M. Hernandez, R. Kohno, "UWB systems for body area networks," *Proc. on ISSSTA*, Oct. 2010, pp. 112-115.

- [1.27] IEEE Std 802.15.6-2012, IEEE standard for local and metropolitan area networks Part 15.6: Wireless Body Area Networks, Feb. 2012.

- [1.28] R. Tandra, "Fundamental limits on detection in low SNR," Master theses, UC Berkeley, 2005.

- [1.29] K. Vasanth, "Bipolar vs. CMOS: selecting the right IC for medical designs," EE Times, 2010. Available: http://www.eetimes.com/design/embedded/4211164/Bipolar-vs--CMOS--Selecting-the-right-IC-for-medical-designs.

- [1.30] S. Malevsky, J. R. Long, "A comparison of CMOS and BiCMOS mm-wave receiver circuit for applications at 60GHz and beyond," *Analog Circuit Design*, Springer, pp. 327-342, 2008.

- [1.31] R. Aigner, "SAW and BAW technologies for RF filter applications: a review of the relative strengths and weaknesses," *IEEE Ultrasonic symposium*, Nov. 2008, pp. 582-589.

- [1.32] Li Shengyuan, S. Sengupta, H. Dinc, P. E. Allen, "CMOS high-linear wide-dynamic range RF on-chip filters using Q-enhanced LC filters," *IEEE International symp. on circuits and systems*, May 2005, pp. 5942-5945.

- [1.33] P. Khademsameni, M. Syrzycki, "Manufacturability analysis of analog CMOS ICs through examination of multiple layout solutions," *Proc. symp. on defect and fault tolerance in VLSI systems*, 2011, pp. 3-11.

- [1.34] J. Lansford, "Detect and avoid (DAA) for UWB: implementation issues and challenges," *International symp. on personal, indoor and mobile radio communications*, Sept. 2007, pp. 1-5.

14 References

[1.35] P. Galy, J. Jimenez, P. Meuris, W. Schoenmaker, O. Dupuis, "ESD RF protections in advanced CMOS technologies and its parasitic capacitance evaluation," *IEEE International conference* on IC Design & Technology, May 2011, pp. 1-4.

- [1.36] CR2032 Lithium coin battery, http://www.microbattery.com.

- [1.37] J. C. Jensen, R. Sadhwani, A. A. Kidwai, et al. "Single-chip WiFi b/g/n 1x2 SoC with fully integrated front-end & PMU in 90nm digital CMOS technology," in *Proc. IEEE radio frequency integrated circuits symposium*, May 2010, pp. 447-450.

- [1.38] A. A. Emira, A. Valdes-Garcia, B. Xia, A. N. Mohieldin, A. Valero-Lopez, A. T. Moon, X. Chunyu, and E. Sanchez-Sinencio, "A dual-mode 802.11b/Bluetooth receiver in 0.25 µm BiCMOS," in IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, 2004, pp. 270-271.

- [1.39] W. Kluge, F. Poegel, H. Roller, M. Lange, T. Ferchland, L. Dathe, and D. Eggert, "A fully integrated 2.4 GHz IEEE 802.14.4-compliant transceiver for Zigbee<sup>TM</sup> applications," *IEEE Journal of Solid-State Circuits*, Vol. 41, No. 12, pp. 2767-2775, Dec. 2006.

- [1.40] J. Rousselot, J. D. Decotignie, "Wireless communication systems for continuous multi parameter health monitoring," *Proc. IEEE ICUWB*, Sept. 2009, pp. 480-484.

- [1.41] J. R. Long, W. Wu, Y. Dong, Y. Zhao, M. A. T. Sanduleanu, J. F. M. Gerrits, and G. van Veenendaal, "Energy-efficient wireless front-end concepts for ultra-lower power radio," in *Proc. IEEE CICC*, Sept. 2008, pp. 587–590.

- [1.42] D. C. Daly, A. P. Chandrakasan, "An energy efficient OOK transceiver for wireless sensor networks," *IEEE Journal of Solid State Circuits*, Vol. 42, No. 5, pp. 1003-1011, May 2007.

- [1.43] B. Otis, Y. Chee, and J. Rabaey, "A 400μW-RX 1.6mW-TX super-regenerative transceiver for wireless sensor networks," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2005, pp. 396–397, 606.

- [1.44] P. P. Mercier, D. C. Daly, and A. P. Chandrakasan, "A 19 pJ/pulse UWB transmitter with dual capacitively-coupled digital power amplifiers," in Proc. *IEEE radio frequency integrated circuits symposium*, June 2008, pp. 47-50.

- [1.45] B. W. Cook, A. Berny, A. Molnar, S. Lanzisera, K. S. J. Pister, "Low-power 2.4-GHz transceiver with passive RX front-End and 400-mV Supply," *IEEE journal of solid state circuits*, Vol. 41, No. 12, pp. 2757-2766, Dec. 2006.

- [1.46] J. Ayers, N. Panitantum, K. Mayaram, T. S. Fiez, "A 2.4GHz wireless transceiver with 0.95nJ/b link energy for multi-hop battery free wireless sensor networks," Symp. on VLSI circuits dig. tech. papers, June 2010, pp. 29-30.

- [1.47] N. M. Pletcher, S. Gambini and J. M. Rabaey, "A 52 μW, wake-up receiver with -72 dBm sensitivity using uncertain-IF architecture," *IEEE Journal of solid-state circuits*, Vol. 44, No. 1, pp. 269-280, Jan. 2009.

- [1.48] J. Ayers, K. Mayaram, T. S. Fiez, "An Ultralow-Power receiver for wireless sensor networks," IEEE Journal of Solid State Circuits, Vol. 45, No. 9, pp. 1759-1769, Sept. 2010.

- [1.49] F. S. Lee and A. Chandrakasan, "A 2.5 nJ/b 0.65 V 3-to-5 GHz subbanded UWB receiver in 90 nm CMOS," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2007, pp. 116–590.

- [1.50] P. P. Mercier, M. Bhardwaj, D. C. Daly, and A. P. Chandrakasan, "A 0.55V 16Mb/s 1.6mW non-coherent IR-UWB digital baseband with ±1ns synchronization accuracy," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2009, pp. 252-253.

- [1.51] N. van Helleputte, M. Verhelst, W. Dehaene, G. Gielen, "A reconfigurable, 130 nm CMOS 108pJ/pulse, fully Integrated IR-UWB receiver for communication and precise ranging," *IEEE Journal of Solid State Circuits*, Vol. 45, No. 1, pp. 69-83, Jan. 2010.

- [1.52] T. Tong, Z. Wenhua, J. Mikkelsen, T. Larsen, "A 0.18µm CMOS low power ring VCO with 1GHz tuning range for 3-5GHz FM-UWB applications," *Proc. of 10<sup>th</sup> IEEE International Conference on Communication Systems*, 2006, pp. 1-5.

- [1.53] A. Georgiadis, M. Detratti, "A linear, low power, wideband CMOS VCO for FM-UWB applications," *Microwave and Optical Technology Letters*, Vol. 50, No.7, pp. 1955-1958, July 2008

- [1.54] A. Tsitouras, F. Plessas, "Ultra wideband, low-power, 3-5.6 GHz, CMOS voltage-controlled oscillator," *Microelectronic journal*, Vol. 40, pp. 897-904, 2009.

- [1.55] M. Detratti, E. Perez, J. F. M. Gerrits, M. Lobeira, "A 4.6mW 6.25-8.25 GHz RF transmitter IC for FM-UWB applications," *Proc. of* the *ICUWB*, Sept. 2009, pp. 180-184.

- [1.56] B. Zhou, H. Lv, M. Wang, et al, "A 1Mb/s 3.2-4.4GHz reconfigurable FM-UWB transmitter in 0.18μm CMOS," Proc. IEEE RFIC Symposium, June 2011, pp. 1-4.

- [1.57] T. Tong, J. H. Mikkehen, T. Larsen, "A 0.18 µm CMOS implementation of a low power, fully differential RF front-end for FM-UWB based P-PAN receivers," *IEEE Singapore International conference on Communication systems*, Oct. 2006, pp. 1-5.

- [1.58] J. F. M Gerrits, J. R. Farserotu, and J. R. Long, "A wideband FM demodulator for a low-complexity FM-UWB receiver," *Proceeding of the 9<sup>th</sup> European Conference on Wireless Technology*, Sept. 2006, pp. 99-102.

- [1.59] Y. Zhao, Y. Dong, J. F. M. Gerrits, G. van Veenendaal, J. R.Long, and J. R. Farserotu, "A short range, low data rate, 7.2 GHz-7.7 GHz FM-UWB receiver front-End," *IEEE Journal of Solid State Circuits*, Vol. 44, No. 7, pp. 1872-1881, July 2009.

- [1.60] B. Zhou, J. Qiao, R. He, et al, "A gated FM-UWB system with data-driven front-end power control," *IEEE Transactions on Circuits and Systems I*, Vol. 58, No. 12, Dec. 2011.

- [1.61] C. Vaucourt, "Choosing inductors and capacitors for DC/DC converters," *Texas Instrument application report*, SLVA157, Feb. 2004.

# CHAPTER 2. TECHNICAL BACKGROUND

#### 2.1. Introduction

As stated in chapter 1, developing a low FM-UWB wireless transceiver is one of the main objectives of this thesis. This chapter begins with an overview of available wireless communication modulation methods. Subsequently, the FM-UWB modulation scheme will be described in more detail. Technical background for the conventional FM-UWB transceiver will be discussed. Specifications for an FM-UWB transceiver using CMOS technology and a link margin analysis will then be presented. Finally, a brief technical review of CMOS technology that relates to power consumption and various CMOS circuit techniques that enable low power design will be described.

# 2.2. Digital Modulation

This section will not attempt to list all existing wireless modulation techniques, instead it will focus on digital modulation techniques that are suitable for low power wireless systems. Digital modulation offers greater accuracy than analog in the presence of noise and distortion. The main tradeoff between each modulation scheme is receiver sensitivity for a certain signal to noise ratio (SNR), bandwidth efficiency, and complexity of the implementation.

Shannon's theorem states that the channel capacity, C in bit/s, is an upper bound on the data rate that can be transmitted, as given by

$$C = B \cdot \log_2(1 + \frac{S}{N}) = B \cdot \log_2(1 + \frac{Eb}{N_0} \frac{R}{B}),$$

(2.1)

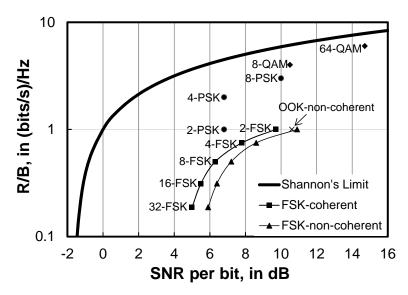

where a given average signal power, S, is transmitted through a communication channel that subject to additive white Gaussian noise (AWGN) of power N [2.2]. Eb is the energy per bit,  $N_O$  is the thermal noise spectral density. R/B, in bit/s/Hz is the ratio between data rate and signal bandwidth, also referred to as the spectral efficiency. As shown in Figure 2.1, a complex modulation scheme (e.g., QAM) packs many bits of data into each signal transition but requires higher SNR per bit

18 Digital Modulation

Figure 2.1.Spectral efficiency versus SNR per bit at BER =  $10^{-3}$  for various modulation schemes [2.3], [2.4].

for equivalent BER compared to a simpler modulation scheme. A complex modulation scheme also requires extra hardware, such as a fast, high-resolution ADC, complex baseband circuitry, and high-linearity PA that consumes more power. On the other hand, FSK modulation sacrifices bandwidth to achieve a lower SNR requirement. Although bandwidth can be traded to get better sensitivity (as in FSK modulation), both are bounded by the Shannon limit (see Figure 2.1). The asymptotic limit for SNR per bit as defined by equation (2.1) is -1.6 dB, assuming that the bandwidth is infinite. An error correcting code (ECC) can reduce the required SNR by a few dB at the cost of reduced data throughput due to computational overhead which consumes more power [2.3].

For a low power transceiver design, the priority goes to low complexity and high sensitivity for the modulation scheme, at the cost of bandwidth efficiency. Binary frequency shift keying (BFSK) and on-off keying (OOK) are typically the main choice of modulation scheme in low power narrowband applications (see Table 1.1 and Table 1.2).

OOK is the simplest modulation scheme, whereby the carrier is turned on or off to represent digital bits. For example, the transmitter can be turned off, when the transmitted bit is '0', making the transmitter power efficient. A digital coding scheme can be employed to maximize the "off" time of the transmitter [2.1]. The power amplifier for OOK can be implemented with a high efficiency non-linear amplifier. OOK modulated data can be received using an envelope detector, removing the need for a local oscillator and mixer. OOK typically uses a single frequency carrier, which simplifies the frequency synthesizer requirements. Two limitations of OOK modulation are that it is spectrally inefficient and that it is susceptible to interferers. An OOK modulated carrier includes harmonic tones which increases its effective bandwidth. Since the receiver detects the received bits

by sensing the energy within a specified band, any noise or interference will cause an error.

BFSK is a constant envelope signal, and hence a high efficiency non-linear power amplifier can be used in the transmitter. A BFSK receiver typically uses a limiter which reduces the susceptibility to fast fading. Non-coherent detection for BFSK is generally used at the cost of 1-2 dB less sensitivity compared to a (more complex) coherent demodulator.

# 2.3. Ultra-wideband (UWB)

Ultra-wideband (UWB) communication is defined as wireless data transmission in which the emitted signal bandwidth exceeds 500 MHz or 20% of its center frequency [2.5]. Unlike a traditional wireless standard, where data is confined within a specific band, the data energy in UWB is spread over a large portion of spectrum, giving it some immunity to multipath fading and interference.

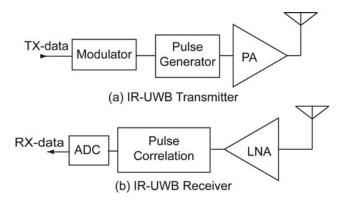

Figure 2.2. A typical transceiver block diagram for IR-UWB

Figure 2.3. BPSK modulation scheme for low data rate IR-UWB [2.13]

Transceivers operating in the unlicensed UWB range are constrained in their link span by the regulations (see Chapter 1), with an average transmit power density of -41.3 dBm/MHz and peak transmit power of 0 dBm [2.6]. However, the RF transmit power from a UWB device is consistent with the capabilities of an energy-efficient, short-range wireless transceiver. Co-existence with other UWB communication systems may be accommodated by transmitting the signal within a selected portion of the bandwidth allocated for UWB systems, and employing detect-and-avoid or a frequency hopping scheme in a cognitive-type radio system [2.7]. A cognitive radio may change its parameters by monitoring channel conditions, (i.e., avoiding interference) and thus allows efficient spectral reuse [2.8].

As shown in equation (2.1), UWB offers greater capacity due to the large bandwidth available and enables data throughput up to 1 Gbit/s across a short distance [2.9]. Choosing UWB modulation for a low data rate application might seem counterintuitive. Fortunately, information spread over a large bandwidth can be recovered with an additional gain in the SNR called a processing gain [2.3], [2.10] (i.e., ratio between bandwidth and data rate). Furthermore, as in other spread-spectrum modulation techniques (e.g., CDMA), low data rate UWB attains immunity to jamming in proportion to the processing gain. Hence, the specification for the transceiver can be relaxed, e.g., lower output power or higher noise figure. This presents an opportunity to implement a simpler and lower power transceiver for low data rate applications.

UWB does not specifically constraint to a certain waveform, though a popular choice is a time domain pulse [2.11]. The energy of the pulses emitted through the antenna occupies a large bandwidth at a certain time instant. This type of transmitter originated early in the 20<sup>th</sup> century in the form of a spark gap transmitter [2.12]. A typical impulse radio UWB (IR-UWB) transceiver (shown in Figure 2.2) promises a simple and power efficient architecture. The transmitted data is modulated using pulse position modulation (PPM) or BPSK. Figure 2.3 shows an example of an IR-UWB modulation scheme using BPSK. A burst of pulses is used in this example in order to boost the average output power without violating the maximum peak transmit power as per FCC ruling [2.6]. Pulses produced by the generator are then transmitted by the antenna through a power amplifier. The receiver amplifies the received pulses using an LNA and then the pulses are demodulated using correlation. An ADC quantizes the demodulated signal and regenerates the received data bit stream.

There are several practical challenges that so far have prevented a fast market adoption of IR-UWB transceivers. On the transmitter side, the pulses need to be accurately shaped such that the spectrum has a certain center frequency, bandwidth and spectrum density. This is not an easy task, because such pulse shaping requires an RF filter that is sensitive to manufacturing variation. Typically, the spectral side lobes emitted by an impulse UWB transmitter could interfere with other users. The power amplifier (PA), low noise amplifier (LNA), and the antenna must have a wide bandwidth and it is a challenge to make the wideband amplifiers power efficient. The LNA is typically power hungry, although recent development has shown promising results for reducing the power consumption [2.14]. The wideband amplifier is susceptible to in-band interference that could severely reduce the

dynamic range. Another practical challenge for the receiver is to synchronize blindly when it receives the transmitted pulses, thus requires accurate timing and also requires initialization time to acquire the correct synchronization.

Other types of modulation that utilize the UWB spectrum are emerging, for example: orthogonal frequency division multiplexing (OFDM), where data is transmitted using a multiple narrowband carriers [2.15], [2.16]. OFDM transceivers need a complex carrier generator system that involves a fast PLL, and are neither simple nor low power. Thus, OFDM-type UWB transceivers are limited to high data rate applications. For low data rate applications, a novel UWB modulation scheme that utilizes frequency modulation (FM) such that the transmitted signal occupies a wideband spectrum at a uniform spectral density will be presented in the following section.

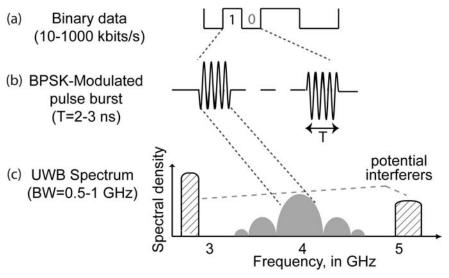

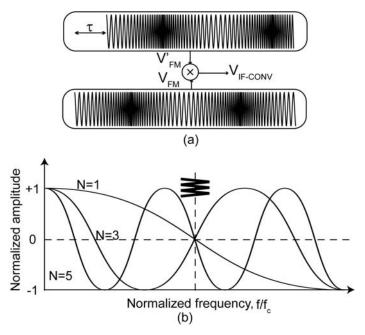

#### 2.4. FM-UWB Modulation Scheme

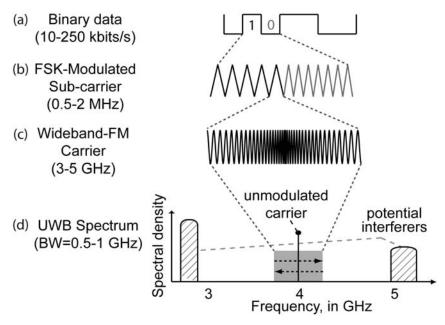

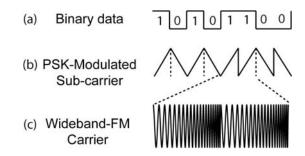

Frequency modulated ultra-wideband (FM-UWB) is well-suited to low-complexity, low power wireless transceiver implementations, and suitable for transmission links up to 10 m [2.10]. FM-UWB uses low modulation-index ( $m_i$ ) FSK (e.g.,  $m_i = 1$ ) to encode binary data at a rate of 10-250 kbit/s (typicaly100 kbit/s) onto a sub-carrier at an intermediate frequency (IF) of 0.5-2 MHz. This is followed by a high modulation index (e.g.,  $m_i = 500$ ) analog frequency modulation of an RF carrier, resulting in RF signal bandwidth of 0.5-1 GHz as shown in Figure 2.4, where the RF carrier is swept back and forth at constant speed. Uniform spectral density and steep spectral roll-off for the transmit signal are realized through the use of a

Figure 2.4. FM-UWB modulation scheme, where data (a) is FSK modulated onto a triangular sub-carrier (b). Subsequently wideband frequency modulation of RF carrier (c) results in UWB spectrum shown in (d).

triangular sub-carrier waveshape. The transmit bandwidth is determined by the sub-carrier amplitude that can be controlled and calibrated easily. Not only the bandwidth, but also the center frequency are controllable, allowing flexibility in the transmitted UWB spectrum.

The agility of FM-UWB also allows a robust wireless system that could avoid potential interferers by employing a frequency hopping scheme similar to frequency-hopped CDMA (FH-CDMA) [2.1], but using a regular frequency hop

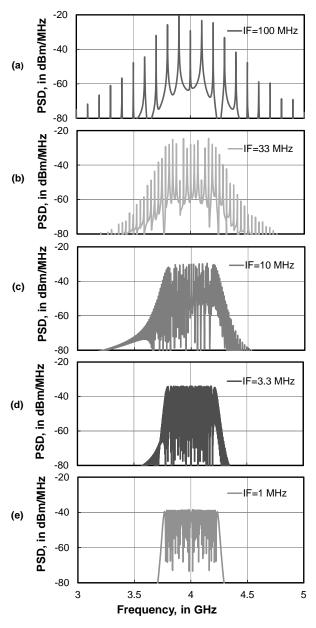

Figure 2.5. Simulated FM-UWB spectral density at 500 MHz bandwidth for different sub-carrier frequencies (IF).

instead of a random one. In this regard, FM-UWB has benefits associated with the spread-spectrum technique, such as immunity to jamming, a transmitting signal that is hidden in the background noise, and the ability to accommodate simultaneous transmission in the same frequency band (i.e., up to 15 users) [2.17]. FM-UWB accommodates multi-user capability in a network using time-division multiple access (TDMA), frequency division multiple access (FDMA), or sub-carrier FDMA sharing the same carrier frequency. In conclusion, FM-UWB offers robust, low-power and low-cost access to unlicensed spectrum available worldwide.

The FM-UWB transceiver operating frequency is defined by the regulators (see Figure 1.4), and preferably where maximum power could be transmitted in order to maximize link margin. The work in this thesis will focus on the 3-5 GHz band. A modulated signal bandwidth of at least 500 MHz is therefore required to conform to the definition of an UWB signal. Higher bandwidth means more spreading, and thus allows higher transmitted output power and link margin, but the transmitter consumes more power as a consequence. Flexibility to control the bandwidth is therefore advantageous for FM-UWB to be power efficient as channel conditions vary.

Figure 2.5 shows various FM-UWB spectra for different sub-carrier IFs. The higher the IF, the higher the spectral density and the more gradual the spectral rolloff. The sub-carrier IF needs to be at least one hundred times less than the RF bandwidth to obtain a large modulation index and create a uniform spectral density across the band. The IF should be limited to a frequency below 5 MHz, because above 5 MHz the spectrum is no longer uniform and power is concentrated at harmonics of the IF. Baseband data modulates the sub-carrier using BFSK modulation. Frequency deviation between symbols '0' and'1' needs to be at least equal to the data rate (i.e., modulation index  $m_i > 1$ ) to avoid intersymbol interference and relaxes the FSK demodulator sensitivity requirement. A higher IF can be chosen to accommodate a higher data rate and multi-user FDMA scheme [2.17]. The double modulation in the FM-UWB scheme limits the maximum data rate. A practical FSK demodulator, such as a PLL, requires that the carrier is at a higher frequency (e.g., > 10 times) than the data rate [2.18]. FM-UWB could (theoretically) employ a maximum data rate up to one-half of the minimum IF [2.19], however, it will need an accurate FSK demodulator. This thesis will focus only on data rates less than 250 kbit/s, which applicable to WSN, WPAN, and WMBAN applications.

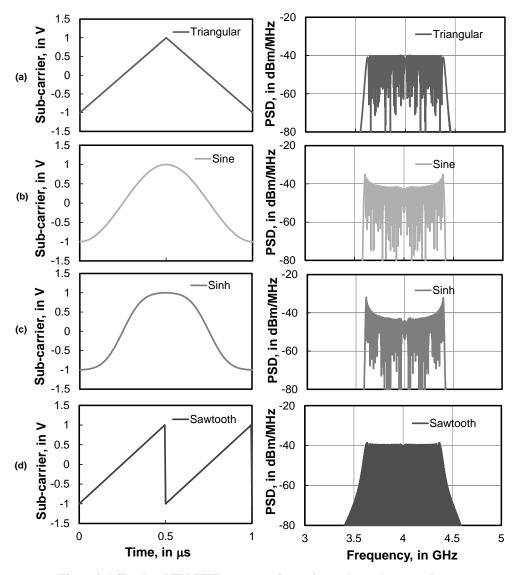

FM-UWB uses direct modulation, instead of up converting the modulated signal as in a conventional radio. Therefore, the sub-carrier wave shape determines the spectral density flatness and spectral roll-off. Figure 2.6 shows the simulated FM-UWB spectra for various sub-carrier wave shapes. Triangular and sawtooth sub-carriers have a uniform and flat spectrum density, thus they are suitable for FM-UWB. The triangular sub-carrier, which has a steeper roll-off and easier implementation, is therefore the preferable choice. Sine and hyperbolic sine functions create peaking at the edge of the signal band and steeper roll-off. As a consequence, the overall transmitted power must be reduced to conform to the spectral mask, and it could adversely affect the overall link margin. A low pass-

filtered triangular or sawtooth wave also exhibits similar peaking because the carrier power is not distributed evenly across the bandwidth.

Non-linearity in the carrier generator (e.g., frequency versus voltage in a voltage-controlled oscillator) will cause a non-uniform spectral density. This non-linearity only distorts the output spectral shape, and it is not critical for the FM-UWB communication. The output spectrum is usually distorted by the wireless condition (e.g., due to multipath), and is tolerable in an FM-UWB system [2.20]. Therefore, a linear carrier generator for FM-UWB is desired, but not necessary.

Multipath occurs when the same transmitted signals arrives at the receiver through different paths and hence with different time delays. The phase difference between these signals adds up constructively or destructively. This phenomenon

Figure 2.6. Simulated FM-UWB spectrum for various sub-carrier wave shapes.

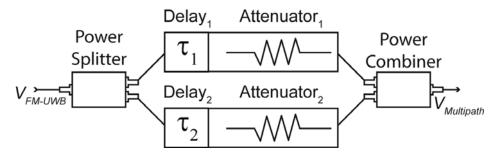

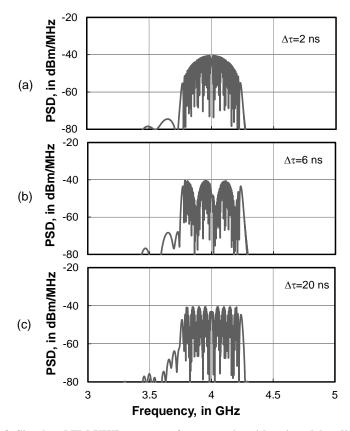

typically happens in an indoor environment, where walls could reflect wireless signals and cause them to arrive at the same point with different phases. Figure 2.7 shows a simulation setup for the multipath effect (2 paths) on an FM-UWB signal. Each path has a different time delay and magnitude, where the attenuation is simulated based on the free space path loss (see Equation 2.4). Note that, the signal is attenuated more for longer delays emulating a longer path. Figure 2.8 shows that the simulated FM-UWB spectrum suffers from the two path effect for various time delay differences. Multipath causes fading at specific frequencies that depends on

Figure 2.7. Setup used to simulate the multipath effect.

Figure 2.8. Simulated FM-UWB spectrum for two paths with a time delay difference of (a) 2 ns, (b) 6 ns, and (c) 20 ns.

Figure 2.9. PSK sub-carrier signal using a sawtooth waveform.

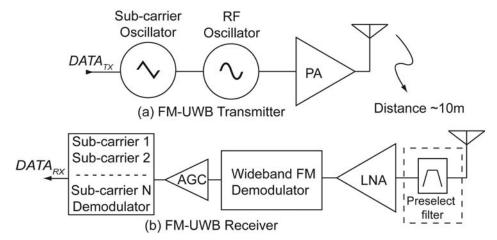

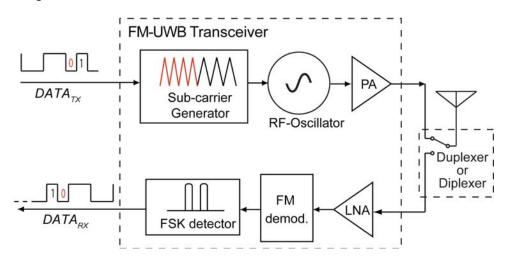

Figure 2.10. Block diagram of typical FM-UWB transceiver.

the delay time difference. A shorter delay difference causes fewer in-band nulls, but they are wider and deeper in bandwidth. The fading could also be time varying, which makes it difficult to compensate. Fortunately, the transmitted power of an FM-UWB signal is spread across a wide bandwidth, hence fading does not significantly degrade the signal, unlike the narrowband FM radio where receptions suffers when multipath fading occurs.

It is possible to use phase-shift keying (PSK) to modulate the sub-carrier signal while maintaining a uniform output spectral density by using a sawtooth wave shape. The sawtooth wave shown in Figure 2.9 represents a BPSK modulated signal, where the two phases are represented by an increasing or decreasing ramp. The phase that represents a data bit can be detected by a receiver employing a demodulator that distinguishes the direction of the sawtooth ramp. BPSK modulation opens a possibility for higher data rates or duty-cycled FM-UWB. However, these are beyond the scope of this thesis.

## 2.5. Specifications for FM-UWB transceiver

A generic transceiver block diagram suitable for FM-UWB is shown in Figure 2.10. The FM-UWB receiver does not require a local oscillator or carrier synchronization

TABLE 2.1 TARGET SPECIFICATIONS FOR THE FM-UWB TRANSCEIVER

| Parameters                                          | Values              |  |  |  |  |

|-----------------------------------------------------|---------------------|--|--|--|--|

| Supply voltage, V <sub>DD</sub>                     | 1 V                 |  |  |  |  |

| Process technology                                  | CMOS 65 or 90 nm    |  |  |  |  |

| RF range                                            | 3-5 GHz             |  |  |  |  |

| RF bandwidth                                        | > 500MHz            |  |  |  |  |

| Sub-carrier frequency                               | 0.5-4 MHz           |  |  |  |  |

| Data rate                                           | < 250 kbit/s        |  |  |  |  |

| Power dissipation, at 4 GHz                         | < 1 mW              |  |  |  |  |

| Energy efficiency                                   | < 10 nJ/bit         |  |  |  |  |

| Chip area                                           | < 1 mm <sup>2</sup> |  |  |  |  |

| Transmitter                                         | •                   |  |  |  |  |

| Phase noise, at 4 GHz and offset frequency of 1 MHz | < -62 dBc/Hz        |  |  |  |  |

| Output power                                        | > -14.3 dBm         |  |  |  |  |

| Spectral flatness within 500 MHz                    | < 3 dB              |  |  |  |  |

| Receiver                                            |                     |  |  |  |  |

| Receiver sensitivity                                | < -80 dBm           |  |  |  |  |

| Bit error rate                                      | 10 <sup>-3</sup>    |  |  |  |  |

| S <sub>11</sub>                                     | < -10 dB            |  |  |  |  |

| Signal-to-interference ratio (NBI at 4 GHz)         | < -20 dB            |  |  |  |  |

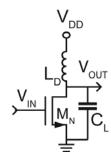

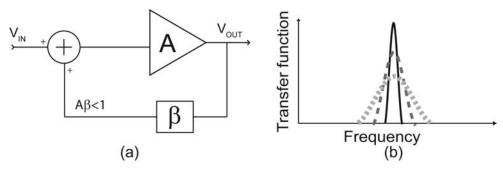

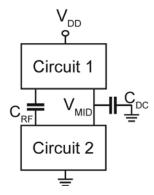

and the transmitter (in its simplest form) may be implemented using just a wideband voltage-controlled oscillator, which results in a simple transceiver architecture that consumes little power in continuous operation. Digital data transmitted from, for example a sensor, modulates the sub-carrier oscillator. Then, the sub-carrier wave directly modulates the RF carrier oscillator. A power amplifier (PA) acts as a buffer to drive the antenna. The receiver consists of an RF amplifier followed by a wideband FM demodulator. An AGC amplifier or limiter further amplifies the received sub-carrier. FSK demodulation of the received data intended for a different user is then required. Selectivity and robustness against out of band interference may be improved further by adding an optional preselect filter between the antenna and RF input. The UWB antenna could also be modified to provide a frequency notch to mitigate expected interference [2.21]. Compared to a conventional radio [2.22], the transceiver for FM-UWB is much simpler and hence better suited to low power applications.

The targeted specifications for the FM-UWB transceiver are summarized in table 2.1. CMOS is the technology choice for the FM-UWB transceiver prototypes developed in this thesis. IBM CMOS 65 nm and 90 nm technologies are employed [2.23], facilitated through MOSIS [2.24]. Standard devices in 90 nm CMOS typically use a 1 V supply to avoid breakdown of the active devices. In the various prototypes described in subsequent chapters, a single 1 V supply is chosen to power the RF front-end, analog and digital circuitry. A targeted power consumption of

1 mW is set for the receiver and transmitter to achieve an energy efficiency better than 10 nJ/bit at a data rate of 100 kbit/s. Chip area is minimized by using as few on-chip inductors as possible and the minimum number of bondpads. An (arbitrary) chip area of 1 mm<sup>2</sup> is the goal for the full transceiver.

The RF carrier frequency deviation in an FM-UWB system is typically > 250 MHz, which implies that phase or frequency jitter of the transmit source has less effect upon the received signal-to-noise ratio (SNR) than for a narrowband system. It has been shown that FM-UWB is able to tolerate transmitter phase noise as high as -73 dBc/Hz at 1 MHz offset with no significant degradation in bit-error performance [2.25]. The FM-UWB phase noise requirement is much relaxed compare to UWB-OFDM which requires of -87 dBc/Hz at 1 MHz offset [2.26]. RF carrier deviation for the FM signal compared to FM noise has to be higher than the required SNR. For a non-coherent BFSK demodulator at a BER of  $10^{-3}$ , the required SNR is 11 dB [2.10]. FM-UWB has a minimum frequency deviation of 250 MHz, which corresponds to maximum frequency jitter due to white noise,  $\sigma_f$  of 49 MHz. Obviously, the higher the modulated FM bandwidth, the higher is the tolerable frequency jitter. Frequency jitter can be related to time jitter,  $\sigma_T$  by the equation

$$\sigma_T = \frac{\sigma_f}{f_C^2} \,, \tag{2.2}$$

where  $f_C$  is the carrier center frequency. Equivalent phase noise at frequency offset  $\Delta f$  can be described as [2.27]

$$L(\Delta f) = \frac{f_C^3}{\Delta f^2} \sigma_T^2. \tag{2.3}$$

From equation (2.3) and the calculated frequency jitter requirement, the FM-UWB transmitter must have a phase noise better than -62 dBc/Hz at 1 MHz offset to satisfy the minimum SNR for the BFSK at BER of 10<sup>-3</sup>.

The spectral mask for UWB signals dictates that the maximum effective isotropic radiated power (EIRP) density is -41.3 dBm/MHz. For a 500 MHz modulation bandwidth, the power density limit translates into a total carrier power of -14 dBm, or 40  $\mu$ W. A margin of 4 dB is added to the PA output in order to compensate for losses in chip packaging, the antenna matching network and variations in the antenna gain. Spectral flatness indicates how uniform the in-band signal spectral density is, and it is limited to a maximum variation of 3 dB.

Assuming line of sight (LOS), path loss (PL) between transmitter and receiver at a short distance can be approximated by the Friis' free space equation

$$PL = \left(\frac{4\pi d}{\lambda}\right)^2,\tag{2.4}$$

where d is the distance between transmitter and receiver, and  $\lambda$  is wavelength. Equation (2.4) is accurate when the distance higher than one wavelength (7.5 cm for  $f_C = 4$  GHz). At shorter distances the antenna operates in the near field, and an advanced path loss model must be used [2.28]. Friis' equation is adequate in practice for calculating distances between the transmitter and receiver. A typical indoor FM-UWB link that covers a distance of 10 m translates into a free space

propagation loss of 66 dB at 5 GHz (assuming 0 dBi antenna gain). Thus, the sensitivity of the receiver required to accommodate a link span of 10 m is at least -80 dBm, as listed in Table 2.1.

Sensitivity of the receiver  $(P_{RX\_MIN})$  can be calculated using the link budget equation as follows

$$P_{RX MIN} = 10 \log(kTB_{RF}) + NF + SNR_{FSK} - G_P.$$

(2.5)

The 50  $\Omega$  thermal noise in a 500 MHz bandwidth corresponds to -87 dBm noise power, which gives 7 dB SNR at the input of a receiver 10 m away from the transmitter. The required SNR at the receiver baseband for demodulation of 2-FSK at a bit error rate (BER) of  $10^{-3}$  is 11 dB. FM-UWB may be considered a spread spectrum system with a processing gain ( $G_P$ ) determined by the ratio of the RF to data bandwidths. Assuming 100 kbit/s data rate, the bandwidth of the 2-FSK data signal is 200 kHz, giving a processing gain of 34 dB (ideally). However, the receiver output SNR is a quadratic function of the RF-input SNR due to the nonlinearity inherent in this type of non-coherent receiver. This results in an additional 6 dB degradation in SNR [2.10], so the overall margin for the receiver noise figure is the receiver input SNR (6 dB), minus the sum of the receiver penalty of 6 dB and required SNR<sub>FSK</sub> of 11 dB, plus the processing gain (34 dB), or 23 dB margin. The margin will be reduced by the non-ideality of the filter and losses from envelope detector (if it is used). At higher data rate, the sensitivity reduces because the 2-FSK data bandwidth increases and thus  $G_P$  decreases.

RF input matching (i.e.,  $|S_{11}| < -10 \text{ dB}$ ) is required to minimize energy reflection between the antenna and the receiver. The sensitivity to single-tone interference is defined by detecting the degradation in BER up to  $10^{-3}$ . Signal-to-interference ratio (SIR) measures the strength of the input signal compared to interference, and is negative when the interference power is stronger than input signal. An UWB radio should be able to withstand SIR of less than -20 dB from narrow band interference (NBI) [2.29]. The following section will review previous work on FM-UWB transceivers.

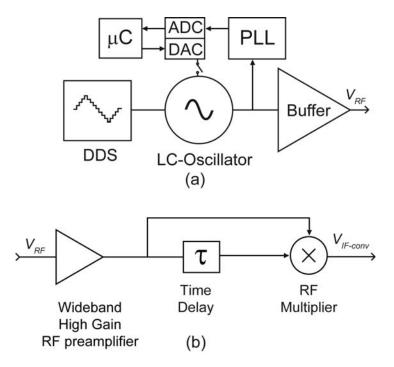

### 2.6. Conventional FM-UWB Transceiver

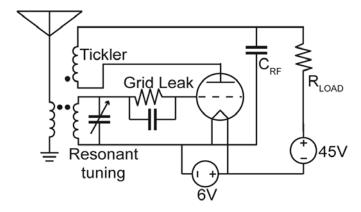

The existing FM-UWB transmitters and receivers that have been proposed recently are usually based on the RF front-end shown in Figure 2.11. The conventional FM-UWB transmitter shown in Figure 2.11a [2.30], [2.31] generates the RF carrier using an LC-oscillator. An LC oscillator is widely used in RF wireless transceivers because of its simplicity, low power consumption at high frequencies of oscillation, and low phase noise. The frequency of the oscillator depends on the resonant frequency of its LC (inductor and capacitor) tank,

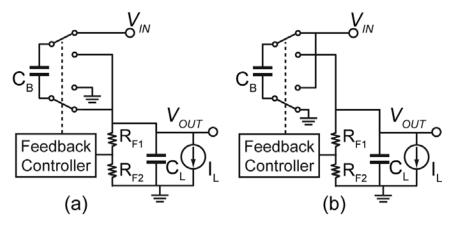

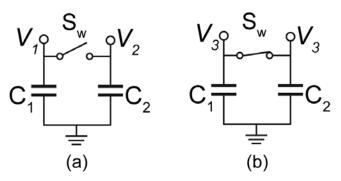

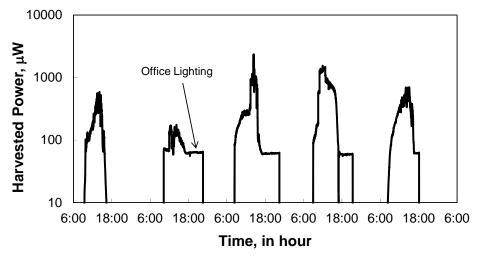

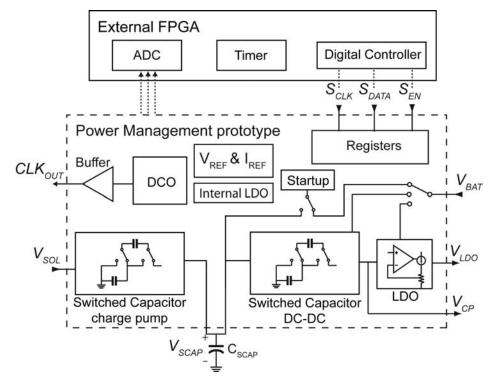

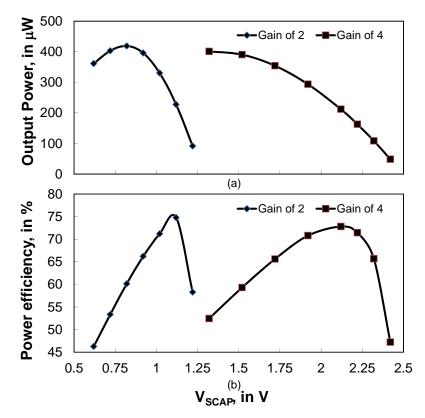

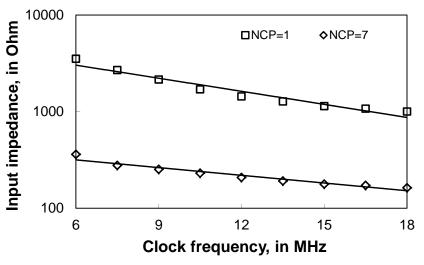

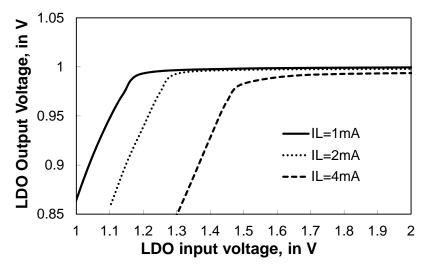

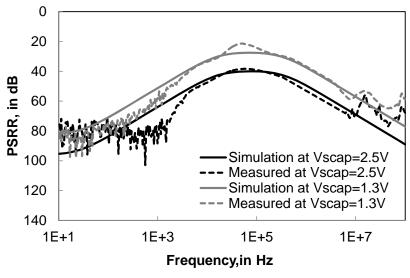

$$f_C = \frac{1}{2\pi\sqrt{LC}}. (2.6)$$