# Computer Engineering Mekelweg 4, 2628 CD Delft The Netherlands

http://ce.et.tudelft.nl/

### MSc THESIS

## Automated Implant-Processor Design

#### **Dhara Dave**

#### Abstract

CE-MS-2010-08

As we move towards an aging population, it is likely that an increasing number of people will require an increasing diversity of implants, but at a lower cost to the society. Also, as computer technology progresses, smaller, more powerful, and less battery intensive implants can be designed. However, present implant design methodology is highly inefficient at meeting these goals as it suffers from non-reuse of existing knowledge by relying heavily on custom designs and ASICs. The SiMS project was started with the goal of creating pre-designed, pre-tested, and pre-certified toolbox of components for biomedical implants that can be assembled in a modular fashion for various application scenarios. One of the most important components in such a tool-box is the processor. Designing such a processor is a non-trivial task and previous work has concentrated on studying the effect of changing the processor input-parameters (such as caches), one parameter at a time. The present work represents a shift in this methodology, as we now allow co-variation in all possible input parameters in order to find optimal configurations in terms of the output objectives power, performance, and area. Towards this end, we implement ImpEDE - "Implantable-processor Evolutionary Design-space Explorer" - a framework that performs multi-objective optimization of processor parameters, and hence gives as output a Pareto optimal set of processors. The frame-

work consists of a cache simulator and a cycle-accurate processor simulator running benchmarks and workloads designed for medical implants, in order to simulate the optimization objectives. A popular, highly configurable, multi-objective genetic algorithm, NSGA-II, performs the actual optimization. Supporting scripts add modularity by acting as the interface between the genetic algorithm and the simulators, enabling easy replacement with new simulators. The whole framework is parallelized such that extra computation cycles of the idle laboratory CPUs can be utilized, thereby giving a considerable speedup without requiring any special hardware. We perform experiments on the non-dominated solution fronts evolved by the framework on a sub-set of benchmarks, in order to optimize parameters of the genetic algorithm, with an aim towards speeding up convergence. We also examine the effects of changing the workload size run by the benchmarks. A solution Pareto optimal front consisting of optimal processor configurations across all benchmarks is found. This front is used as a reference in order to characterize the benchmarks in the ImpBench suite. Finally, the objective space of the reference front is compared to existing implant designs, and a set of "generic processors" are chosen such that all the existing implant applications studied can be covered.

## Automated Implant-Processor Design An evolutionary multiobjective exploration framework

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

COMPUTER ENGINEERING

by

Dhara Dave born in Ahmedabad, India

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

## Automated Implant-Processor Design

#### by Dhara Dave

#### Abstract

${f s}$  we move towards an aging population, it is likely that an increasing number of people will require an increasing diversity of implants, but at a lower cost to the society. Also, as computer technology progresses, smaller, more powerful, and less battery intensive implants can be designed. However, present implant design methodology is highly inefficient at meeting these goals as it suffers from nonreuse of existing knowledge by relying heavily on custom designs and ASICs. The SiMS project was started with the goal of creating pre-designed, pre-tested, and pre-certified toolbox of components for biomedical implants that can be assembled in a modular fashion for various application scenarios. One of the most important components in such a tool-box is the processor. Designing such a processor is a non-trivial task and previous work has concentrated on studying the effect of changing the processor input-parameters (such as caches), one parameter at a time. The present work represents a shift in this methodology, as we now allow co-variation in all possible input parameters in order to find optimal configurations in terms of the *output* objectives - power, performance, and area. Towards this end, we implement ImpEDE - "Implantable-processor Evolutionary Design-space Explorer" - a framework that performs multi-objective optimization of processor parameters, and hence gives as output a Pareto optimal set of processors. The framework consists of a cache simulator and a cycle-accurate processor simulator running benchmarks and workloads designed for medical implants, in order to simulate the optimization objectives. A popular, highly configurable, multi-objective genetic algorithm, NSGA-II, performs the actual optimization. Supporting scripts add modularity by acting as the interface between the genetic algorithm and the simulators, enabling easy replacement with new simulators. The whole framework is parallelized such that extra computation cycles of the idle laboratory CPUs can be utilized, thereby giving a considerable speedup without requiring any special hardware. We perform experiments on the non-dominated solution fronts evolved by the framework on a sub-set of benchmarks, in order to optimize parameters of the genetic algorithm, with an aim towards speeding up convergence. We also examine the effects of changing the workload size run by the benchmarks. A solution Pareto optimal front consisting of optimal processor configurations across all benchmarks is found. This front is used as a reference in order to characterize the benchmarks in the ImpBench suite. Finally, the objective space of the reference front is compared to existing implant designs, and a set of "generic processors" are chosen such that all the existing implant applications studied can be covered.

**Laboratory** : Computer Engineering

Codenumber : CE-MS-2010-08

Committee Members :

Advisor: Georgi Gaydadjiev

Advisor: Christos Strydis

Chairperson: Koen Bertels

Member: Paddy French

Member: A.J. van Genderen

For my family

# Contents

| Li            | st of              | Figure          | es                            | vii    |

|---------------|--------------------|-----------------|-------------------------------|--------|

| $\mathbf{Li}$ | st of              | Tables          | S                             | ix     |

| $\mathbf{A}$  | cknov              | wledge          | ments                         | xi     |

| 1             | <b>Intr</b><br>1.1 | oducti<br>Conte | ion<br>xt and Motivation      | 1<br>2 |

| <b>2</b>      | Bac                | kgrour          | nd and Related Work           | 5      |

|               | 2.1                |                 | iMS Project                   | 5      |

|               | 2.2                |                 | ed Work                       | 6      |

|               |                    | 2.2.1           | Implant Design                | 6      |

|               |                    | 2.2.2           | Processor Design              | 7      |

|               | 2.3                | Backg           | round                         | 9      |

|               |                    | 2.3.1           | Notes on Optimization         | 10     |

|               |                    | 2.3.2           | Single vs. Multi-optimization | 12     |

|               |                    | 2.3.3           | Heuristic Algorithms          | 13     |

|               |                    | 2.3.4           | Genetic Algorithms            | 16     |

|               |                    | 2.3.5           | Benchmarks and Workloads      | 18     |

|               |                    | 2.3.6           | Simulators                    | 19     |

| 3             | Exp                | erime           | ntal Setup                    | 21     |

|               | 3.1                |                 | bles Chosen                   | 21     |

|               |                    | 3.1.1           | Clock Frequency               | 22     |

|               |                    | 3.1.2           | Branch Prediction             | 22     |

|               |                    | 3.1.3           | Caches                        | 24     |

|               |                    | 3.1.4           | Buffers                       | 25     |

|               |                    | 3.1.5           | ALUs                          | 26     |

|               |                    | 3.1.6           | Other Options Considered      | 26     |

|               | 3.2                | Chron           | nosome Encoding               | 27     |

|               | 3.3                | Object          | tives                         | 27     |

|               | 3.4                | Consti          | raints                        | 28     |

|               | 3.5                | Bench           | marks & Data Sets             | 28     |

|               | 3.6                | Popula          | ation Size                    | 30     |

|               | 3.7                | Numb            | er of Generations             | 31     |

|               | 3.8                | Mutat           | ion                           | 31     |

|               | 3.9                | Crosso          | over                          | 33     |

|               |                    |                 | ion                           | 34     |

|               | 3.11               | Paralle         | elization & Optimization      | 35     |

|                           |       | 3.11.1 Parallelization Software                                       | 36         |

|---------------------------|-------|-----------------------------------------------------------------------|------------|

|                           |       | 3.11.2 RPC                                                            | 37         |

|                           |       | 3.11.3 Computing Resources Available                                  | 38         |

|                           |       | Real Time Constraints                                                 | 39         |

|                           | 3.13  | Additional Features                                                   | 40         |

| 4                         | Exp   | erimental Results                                                     | 43         |

|                           | 4.1   | Selecting Number of Generations                                       | 47         |

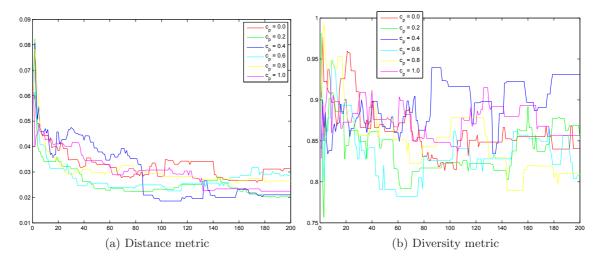

|                           | 4.2   | Selecting Crossover Probability                                       | 50         |

|                           | 4.3   | Combined Optimization for ImpBench                                    | 52         |

|                           | 4.4   | Impact of Workload Size                                               | 52         |

|                           | 4.5   | Extension with Real Time Constraints                                  | 54         |

|                           | 4.6   | Comparative study of the benchmarks                                   | 58         |

|                           | 4.7   | Case Study with Real Applications                                     | 60         |

| 5                         | Futi  | ure Work and Conclusions                                              | 65         |

|                           | 5.1   | Conclusions                                                           | 65         |

|                           |       | 5.1.1 Framework                                                       | 65         |

|                           |       | 5.1.2 Experimental Results                                            | 66         |

|                           | 5.2   | Future Work                                                           | 67         |

|                           |       | 5.2.1 Framework Improvements                                          | 67         |

|                           |       | 5.2.2 Accuracy and Granularity Improvements                           | 68         |

|                           |       | 5.2.3 Support for Additional Features                                 | 69         |

| Bi                        | bliog | raphy                                                                 | 77         |

| $\mathbf{A}_{\mathtt{J}}$ | ppen  | dices                                                                 | 78         |

| $\mathbf{A}$              | Pap   | ers                                                                   | <b>7</b> 9 |

|                           | A.1   | ImpEDE: A Multidimensional Design-Space Exploration Framework for     |            |

|                           |       | Biomedical-Implant Processors                                         | 79         |

|                           | A.2   | ImpBench Revisited: An Extended Characterization of Implant-Processor |            |

|                           |       | Benchmarks                                                            | 90         |

|                           | A 3   |                                                                       | 101        |

# List of Figures

| 2.1<br>2.2 | Implant design trends over the years[73]                                                                                                                                                                                    | 5        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.3        | steps                                                                                                                                                                                                                       | 7        |

| 2.4        | jective space [18, Figure 5, Page 15]                                                                                                                                                                                       | 11       |

|            | front of the objectives (deflection, weight) [18]                                                                                                                                                                           | 12       |

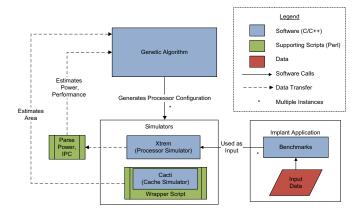

| 3.1<br>3.2 | Experimental Setup                                                                                                                                                                                                          | 22       |

| 0.2        | intact depending on the mutation probability $p_m$                                                                                                                                                                          | 32       |

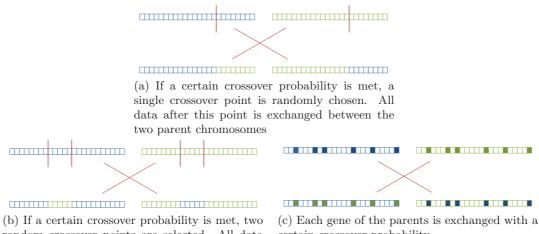

| 3.3        | Different crossover techniques, with each square representing a single gene (bit) in the chromosome. The top two chromosomes in each figure are the parent chromosomes, and the bottom two are the resulting children after |          |

| 0.4        | the crossover operation is applied                                                                                                                                                                                          | 34       |

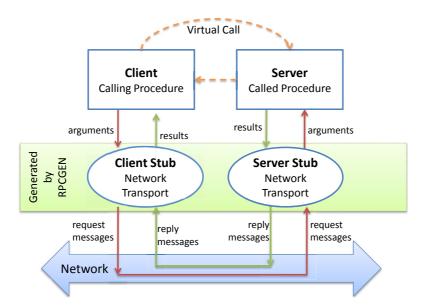

| 3.4<br>3.5 | Schematic of a remote procedure call                                                                                                                                                                                        | 38<br>40 |

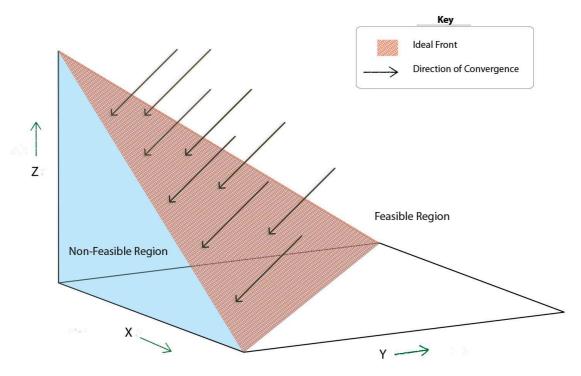

| 4.1        | Direction of convergence towards the true front in a hypothetical and                                                                                                                                                       |          |

| 4.1        | idealized minimization problem                                                                                                                                                                                              | 44       |

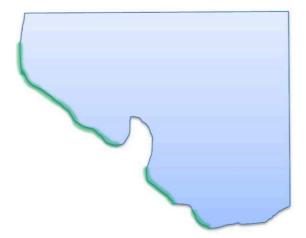

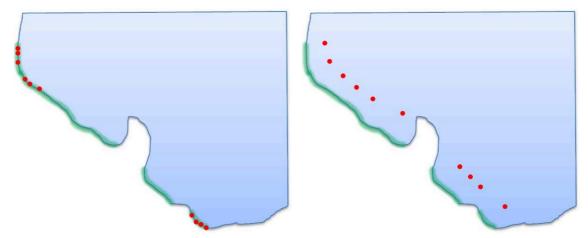

| 4.2        | The design space of a minimization problem (blue) and it's convex, discontinuous Pareto front (green)                                                                                                                       | 44       |

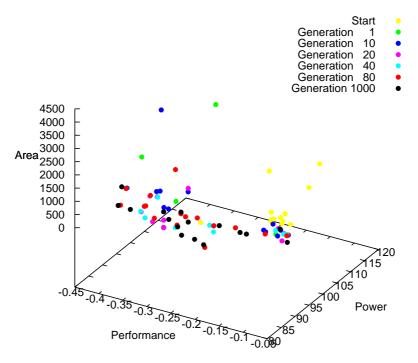

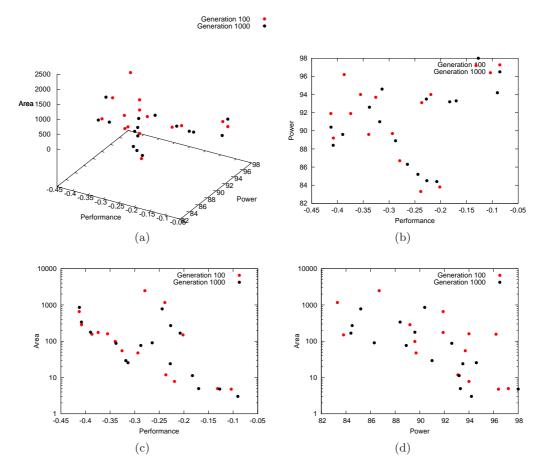

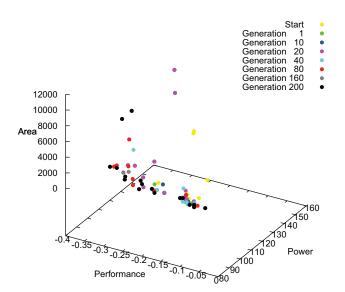

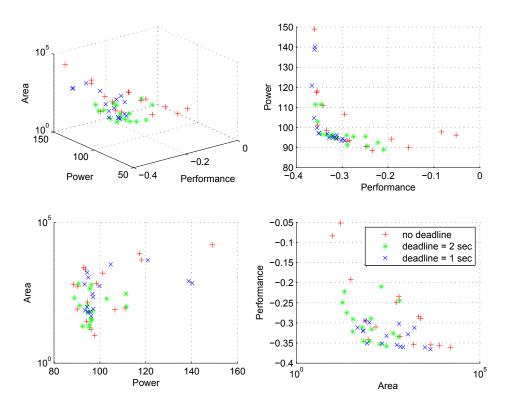

| 4.3        | Pareto fronts found at various generations (Benchmark: Checksum, 10KB)                                                                                                                                                      | 47       |

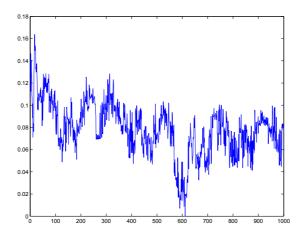

| 4.4        | The distance metric fluctuates widely                                                                                                                                                                                       | 48       |

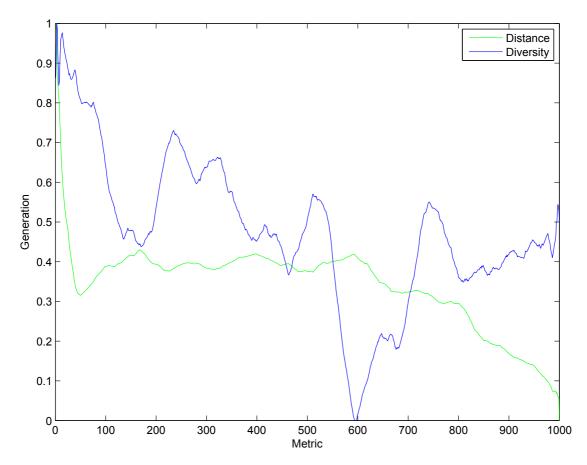

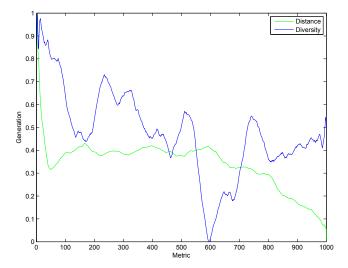

| 4.6        | Smoothed distance and diversity metrics over 1000 generations (Bench-                                                                                                                                                       |          |

| 4.7        | mark: checksum)                                                                                                                                                                                                             | 50       |

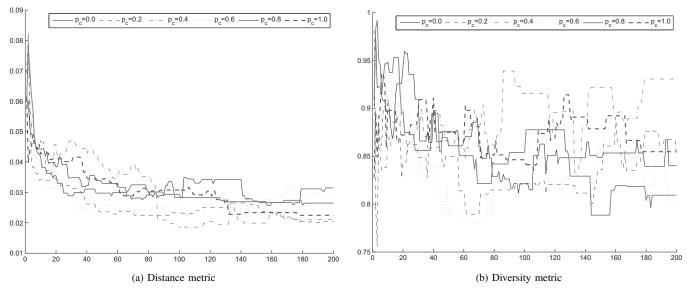

|            | (Benchmark:checksum)                                                                                                                                                                                                        | 51       |

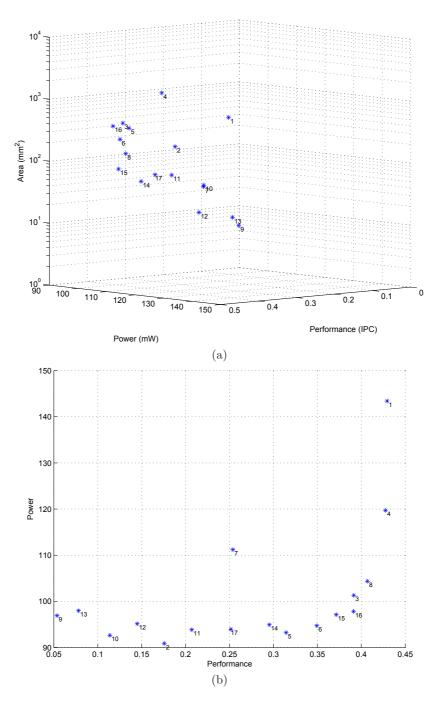

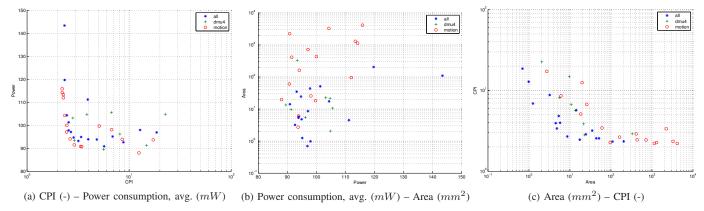

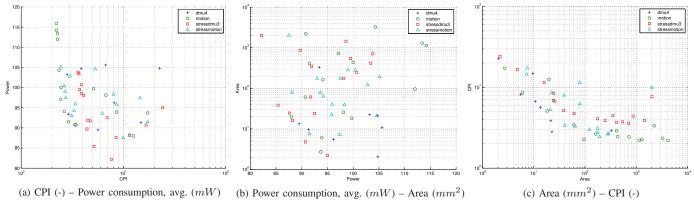

| 4.8        | Pareto front optimizing all benchmarks                                                                                                                                                                                      | 53       |

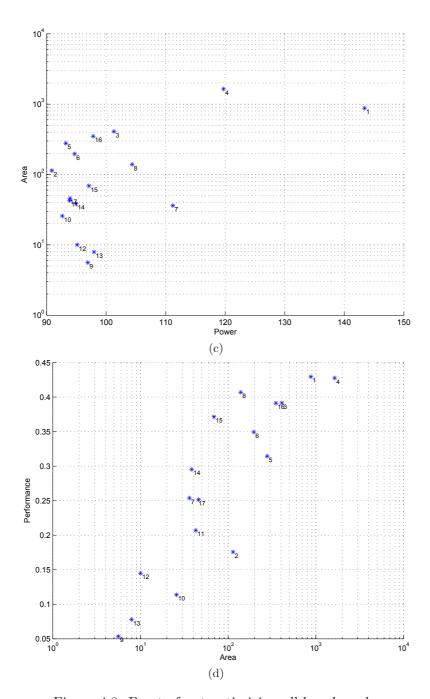

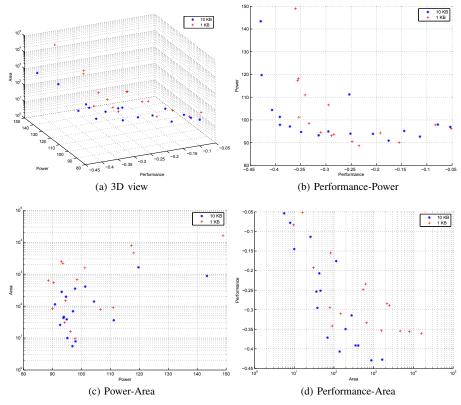

| 4.9        | Pareto fronts evolved with workload sizes of 10 KB and 1 KB                                                                                                                                                                 | 55       |

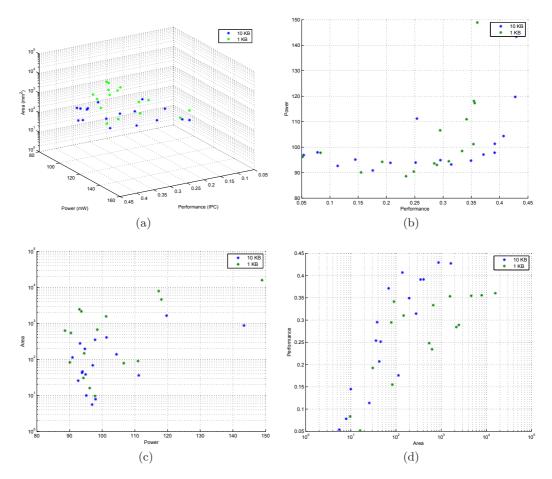

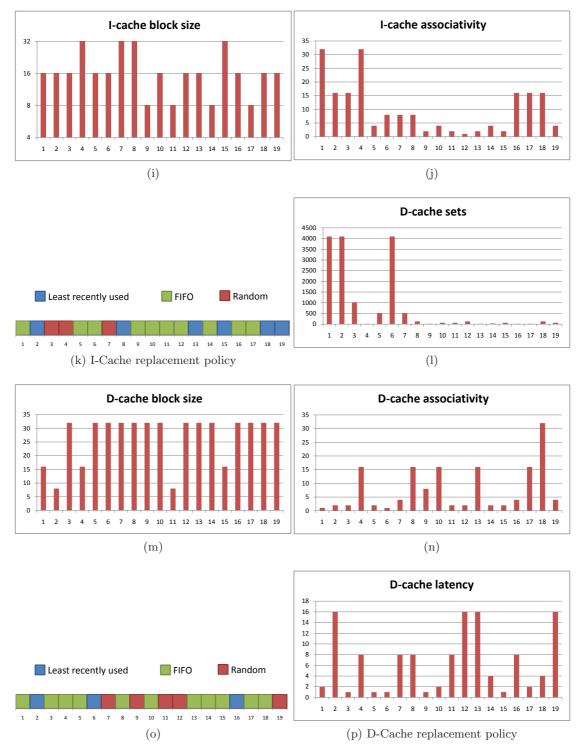

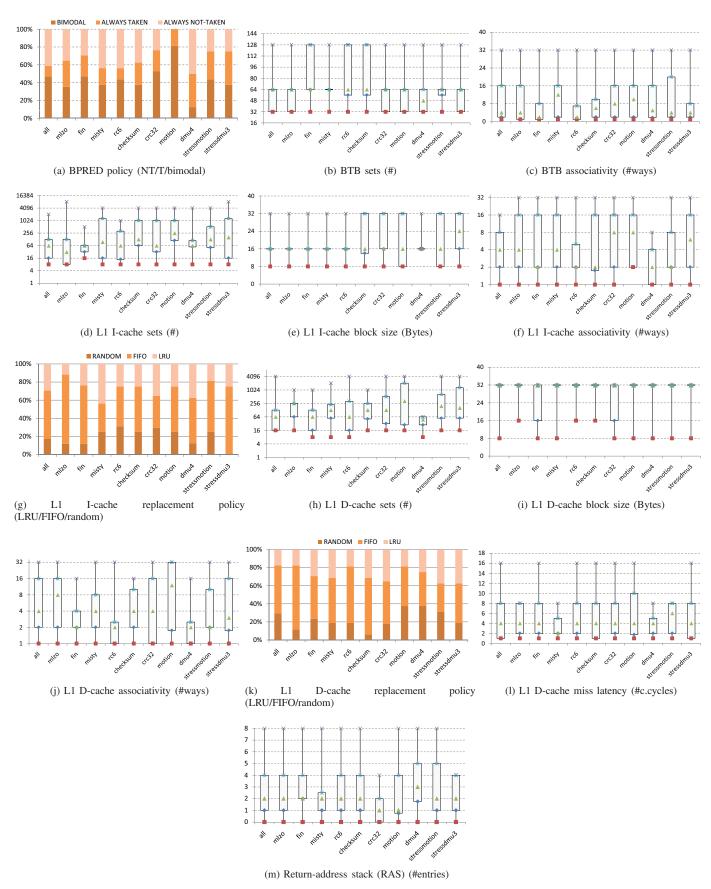

|            | Parameters of the Pareto optimal processor configuration                                                                                                                                                                    | 56       |

|            | Parameters of the Pareto optimal processor configuration                                                                                                                                                                    | 57       |

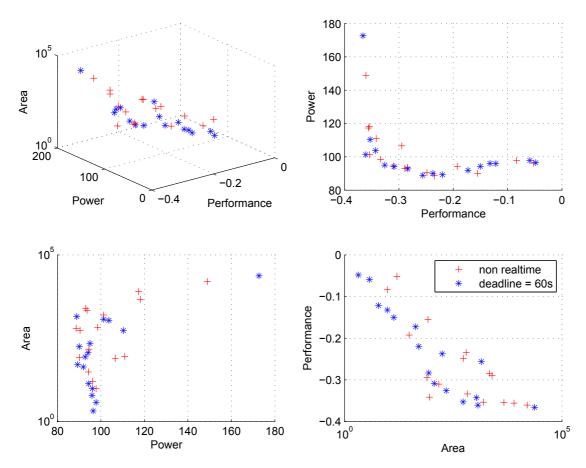

| 4.11       | relaxed deadline, therefore, not much change can be seen in terms of ranges.                                                                                                                                                | 58       |

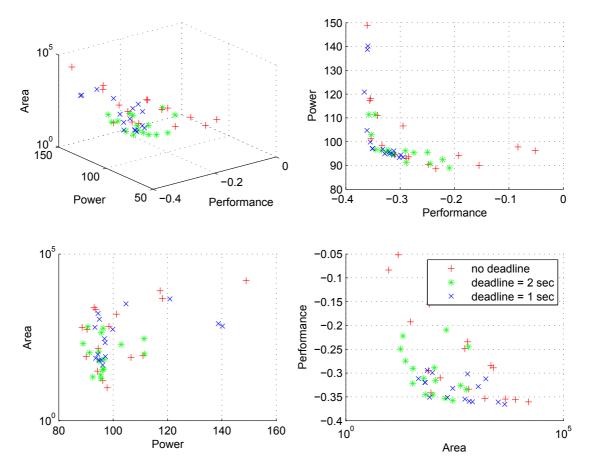

| 4.12       | As deadlines become tighter, more cutoff can be seen at the power end.                                                                                                                                                      | 90       |

| 1.12       | This is clearest in the Power-Performance graph                                                                                                                                                                             | 59       |

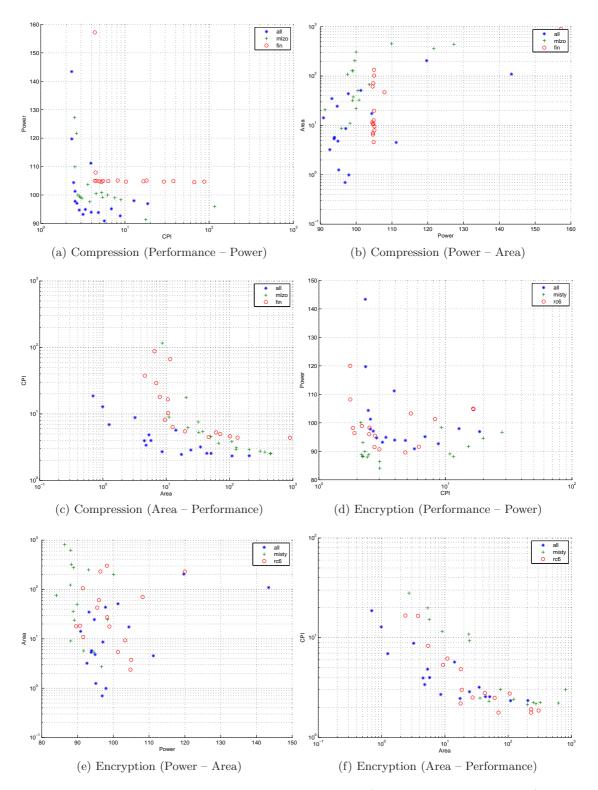

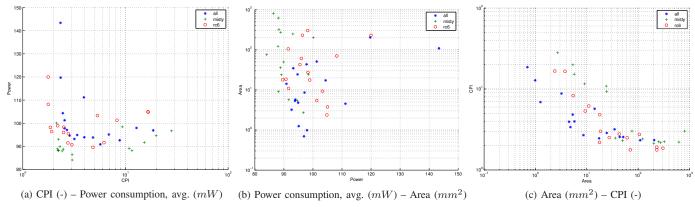

| 4.13       | Comparison of benchmark pairs - I (Compression, Encryption)                                                                                                                                                                 | 61       |

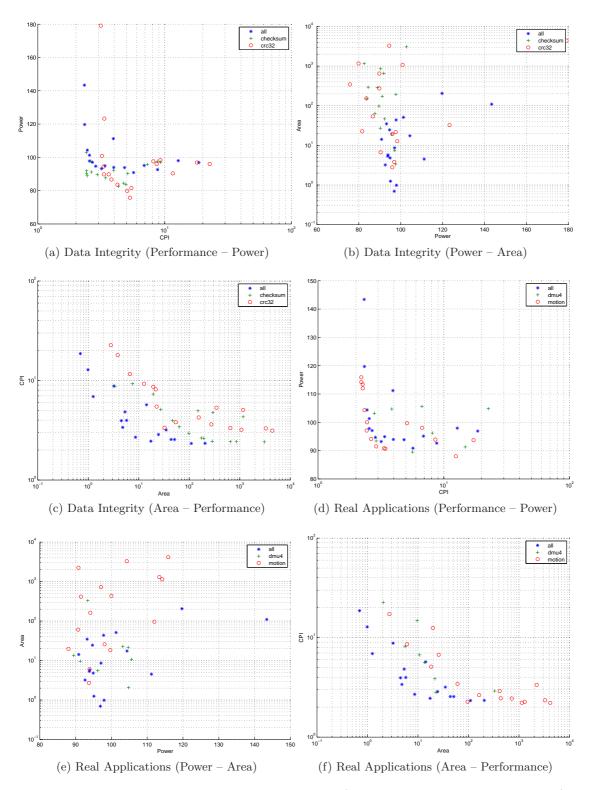

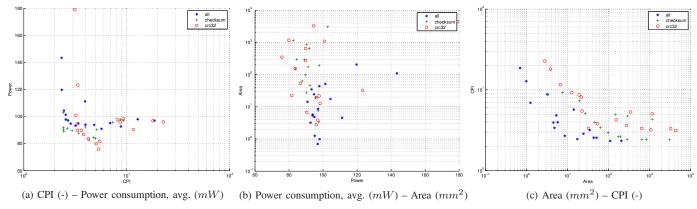

|            | Comparison of benchmark pairs - II (Data Integrity, Real Applications) .                                                                                                                                                    | 62       |

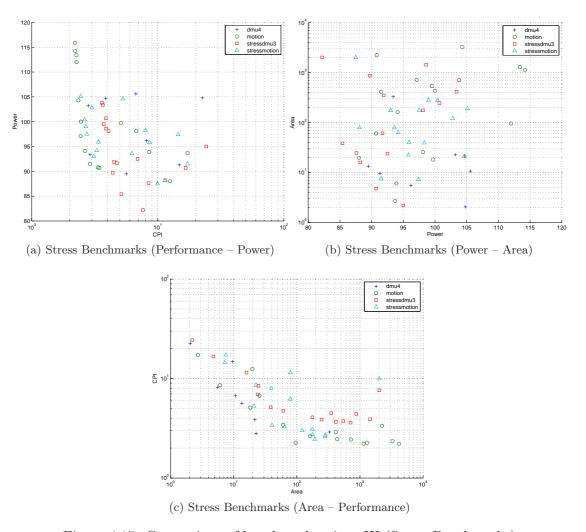

|            | Comparison of benchmark pairs - III (Stress Benchmarks)                                                                                                                                                                     | 63       |

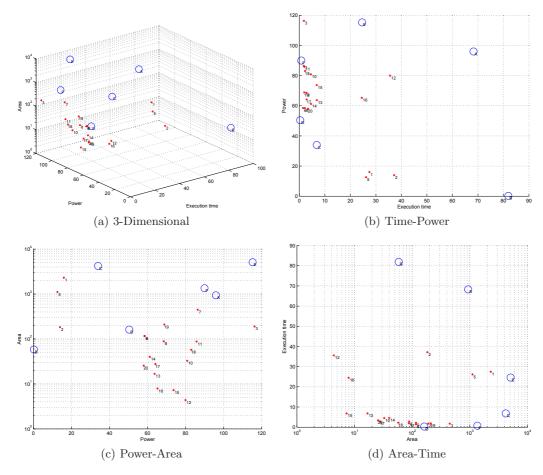

| 4.16       | The objective space for our designs and the real implants                                                                                                                                                                   | 64       |

# List of Tables

| 2.1 | XTREM (Modified) Architecture Details [74]                               | 6  |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | Overview of a few existing implant applications                          | 8  |

| 2.3 | Summary of methods using single objective optimization techniques to     |    |

|     | perform multi-objective optimization                                     | 14 |

| 2.4 | ImpBench benchmarks. (*) indicates typical values for $10-KB$ workloads, |    |

|     | except for DMU-variants which use their own special workloads. $[79]$    | 18 |

| n 1 | Decrees Decima Decrees and decided in this work                          | 26 |

| 3.1 | Processor Design Parameters considered in this work                      | 20 |

| 4.1 | Pareto-front distance and normalized-spread metrics and average simula-  |    |

|     | tion time per benchmark.                                                 | 60 |

# Acknowledgements

I would like to thank my advisors, for allowing me to propose and work on this thesis topic, and for the help, support and advice I got from them. Special thanks to my family and friends for all the patience and support. Last but not least I am extremely grateful to our system administrators, Erik de Vries and Eef Hartman for their enormous help with setting up the clusters, and fixing all the (many) problems that arose on the way.

Dhara Dave Delft, The Netherlands June 22, 2010

Introduction

In 1889, a report was published on how the application of electrical impulses to the human heart could help control its rhythm. It was nearly 70 years later that societal and technological conditions became favourable enough to use this knowledge. The first clinical implant on a human patient was in 1958, Sweden — Arne Larson was given an artificial pacemaker. It failed 2 hours later. A second one failed 2 days later. Arne Larson went on to receive 26 pacemaker implants in his lifetime. However, despite the initial hiccups, artificial pacemakers paved the way for a revolution of sorts in medical technology — implants were here to stay. Since then, many new kinds of implants have been developed. Recently, with declining chip sizes and costs, more and more applications are emerging that could not even be conceived of before.

Today, we are in the midst of another revolution — rapidly advancing technology has changed the way we live and work. One of the driving forces behind this revolution is rapid adaptability. As each new discovery or social trend makes older products obsolete, the old adage "Time is money" has never been more important. Each company tries to model its practices around frameworks that allow for less waste from previously generated knowledge, leading to quicker development and time to market; and hence, increased profits. This need for reutilization is a key factor in the drive towards modularity — components, both hardware and software, are encouraged to be modular and flexible so that new combinations can be assembled with minimum extra effort.

It is therefore, a little surprising that medical implants have not yet benefited from these insights. As studied by the authors of [71], medical implants are, more often than not, still developed from scratch. This leads to longer development times and additional costs. Ballooning health care costs and increasing social debates on medical spending makes this practice quite unacceptable. Needless to say, the faster the new implants come to the market, the more the patients benefit — both, in terms of improved quality of life and reduced cost.

Digital processors lie at the heart of any embedded system designed with modular components. Medical implants, being a special case of embedded systems, are no different. Today's embedded designer has a large arsenal of embedded processors to choose from, each coming with their own trade-offs and constraints in terms of power, performance, and area. While these three objectives are important for any processor, the class of processors for embedded systems exhibit extra constraints.

Medical implants constitute one such highly resource constrained application of embedded systems, and as such, its core component, the processor, is also subject to strict limitations. For example, the implant must be small enough to fit into the implant site. The power dissipation must not be so high that the processor heats up and damages the surrounding tissue. Since frequent surgery to replace batteries would be detrimental to the quality of life of the patient, as well as costly, the system must last long enough to finish its task without running out of power. Most implant applications perform real-time monitoring and/or control, therefore, the implant must be able to handle these without failing. Most importantly, since the application may be life-critical, the system must be extremely fault-tolerant and reliable — in this day and age, receiving 26 implants, as was the case for the first pacemaker, is just not acceptable. Since the processor is a major component of the design, it must also fulfill all these criteria. For these reasons, generic processors available in the market now might not work for implant applications, not least because most of them do not make any claims on reliability.

As we can see, there is a need for processors that can be used specifically for medical implants, and these processors must be generic enough to be used in a wide range of in vivo applications. This work aims to facilitate the design of such processors.

#### 1.1 Context and Motivation

One of the properties needed for modular design is the ability to choose components based on their black-box behaviour, rather than implementation details — i.e. as long as the behaviour of the component is accurately specified, one need not worry what goes on inside that component. This way, one can keep a wide-array of components with well-defined characteristics. Whenever there is a need to design an application, components with the desired characteristics can be chosen, and interconnected to each other with minimum knowledge of their internal working. Such design methodology has been used with huge success in modern PC design. A PC designer just needs to know the performance characteristics, power requirements, and pin connections of a modern processor. He generally does not need to know how the ALU is implemented or how the instruction pipeline works. Of course, knowing these can help improve the design choices one makes, but at first, they are not as important as the higher-level black-box parameters. The same principle can be used for embedded design, and consequently, implants design. For the scope of this work, we consider the black-box parameters to be area, power consumption, and performance of the processor – collectively known as the objectives. As we shall see, these are not the only design goals that can be added to the system, and other parameters may also be selected in the future. Indeed, it is extremely important to incorporate reliability as a design goal. However, as this is the first stage of implementation, we use a reduced set of design goals, and leave modeling reliability as a goal for future work.

As we shall see, this work was carried out in the context of the SiMS project at the Computer Engineering Department of Delft University of Technology. One of the various deliverables of this project is to propose a generic processor that can be used for medical implants. Designing this processor is not an easy task. It may also be the case that a one-size-fits-all approach may not be feasible given the diversity of implants being designed, and several "generic" processors might be required that among themselves cover a wide range of applications. Therefore, one needs to have a system that can help to choose "good" processor configurations. This system ideally, would map out the entire spectrum of the design space possible, listing the trade-offs between all the objectives. From examining these trade-offs, one can choose configurations that fit the desired design range. A good way for representing the available trade-offs for design is to use the concept of *Pareto Optimality*, which we use in this work.

Obtaining the full trade-offs spectrum as described above however, is a non-trivial task. One must explore all possible configurations of processors, compute the corresponding objectives of area, power etc, and from this, find the Pareto-dominant solutions to be included in the final trade-off set. Since typically the design parameters that affect a processor are numerous, computing the behaviour of all possible combinations of these is quite difficult, if not impossible. For example, in this work, we consider 13 processor design parameters [Table 3.1] represented by 36 binary bits. If one were to simulate all combinations, one would need to evaluate  $2^{36} = 68,719,476,736$  processor configurations! Therefore, we need a way to approximate the trade-off points without performing all possible simulations. Furthermore, even in an approximated scenario, thousands of configurations might have to be considered, evaluated, and compared to get a good approximation of the true Pareto front. Therefore, we need an automated method for doing so. Several search and optimization algorithms are available that can be used to perform this very task. In the next sections, we shall see why we chose a particular variant of genetic algorithms as the optimization algorithm, and how this algorithm works. We found that the selected algorithm had a very long computation time, and therefore, we describe how we parallelized the algorithm. Finally, we present several trade-off scenarios and the Pareto results the algorithm gives for each of these.

Note that although reliability is one of the major reasons for the need to design processors specifically for implants, the present work does not directly address reliability. Instead, we rely on the idea that processor design can be looked at from a black-box design perspective and provide a flexible and modular framework for doing so. Given such a framework, adding reliability as one of the black-box parameters is more easily done, and is left as future work. For the present work, we concentrate on the following:

1. As we shall see, previous work in the project used certain simulators (XTREM [11] and CACTI [66]). As a continuation of that work, we needed to retain the same simulators. However, future considerations required that this simulator be easily replaceable with another. We did not find an open source/free tool that allowed us to perform multi-objective design space exploration modularly with respect to different processors. Therefore, one deliverable of this work is a free and open design space exploration framework with modular interfaces that enable easy swapping between different processor simulators. We test the modularity of this framework and validate the results to some extent by introducing additional

realtime constraints in the system and observing the trends.

- 2. In addition to the above problem, the cycle-accurate processor simulators we use also have long simulation times. This necessitates that the DSE algorithm be run in parallel if possible. Further more, we had limited and dynamically changing (hardware) resources available for computation. Therefore, the above mentioned framework is also parallel, scalable, does not need special resources (instead utilizes idle computation cycles of laboratory machines), is easily deployable, and is resistant to dynamic network changes and failures in machines while computing.

- 3. As further performance optimization of the framework, we also experimented on selecting design parameters (number of generations and crossover probability) for the genetic algorithm in order to speed up its convergence and run-time. This is done by analyzing the distance and spread metrics of the various Pareto fronts found. As far as the authors are aware, such work does not exist in the context of multi-objective genetic algorithms.

- 4. We use the optimized tool for finding optimal processor configurations. The Pareto front so found is compared to real implant applications in terms of the power, performance and area objectives. We find that our processor configurations are competent in covering the requirements of most of these real applications, and suggest some design points from the front that can be used as starting points for the "generic processors" we require.

- 5. Finally, we demonstrate the usefulness of the framework in other related contexts by characterizing the benchmarks in the extended ImpBench suite using our DSE framework. This is done as follows: separate Pareto fronts are independently evolved for each of the benchmarks, which is compared to the front evolved that optimizes a combination of all these benchmarks. Such a study can help processor designers in selecting the benchmarks with appropriate characteristics for example a single representative benchmark that is closest in behaviour to the combined optimization front can be used instead of the entire suite in case rapid simulations are required. Also, processor designers may opt for a more sensitive benchmark with wide variations in power, performance and area for the allowed range of configurations or a benchmark that gives lesser (and hence more predictable) variations in objectives for the same allowed range of processor configurations. As far as we are aware, such a characterization of benchmarks using multi-objective genetic algorithms has not been done.

Background and Related Work

#### 2.1 The SiMS Project

As stated previously, the practice of redesigning entire implants from scratch is wasteful. The SiMS (Smart Implantable Medical Systems) project [24] at TU Delft aims to address this problem.

The goal of the SiMS project is to "deliver a systematic approach (thus, a framework) that provides medical researchers with a toolbox of ready-to-use, highly reliable sub-systems and models in order to construct (optimal) implants for various medical applications." The framework is envisioned to contain hardware and software components that are pre-tested and approved according to the required medical standards. These components can then be mix-and-matched to create different implants catering to different application scenarios. This will significantly reduce design time and costs of medical implants, in addition to providing greater reliability.

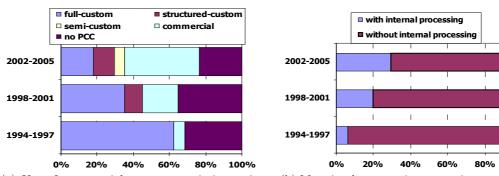

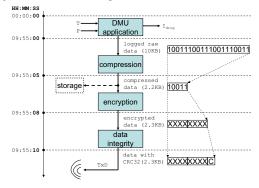

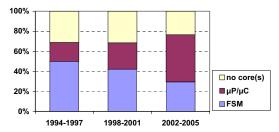

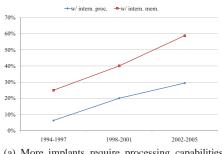

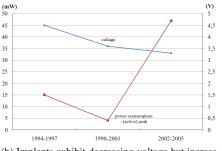

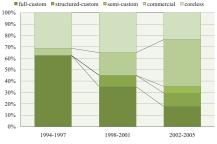

Current implant design still relies heavily on custom design as can be seen from Figure 2.1a. However, this needs to change since the goal is towards rapid development of implants using modular hardware components. Additionally, it is typically easier to implement more complex functionality on processors than on designs with no processing cores or on ASICs (Application Specific Integrated circuits) – this is important as the trend is towards implants that require more processing [Figure 2.1b]. Therefore, there is a need for implants processors that are generic enough to cover a wide range of application possibilities. Within the context of the project, Strydis et. al. [74] present the need for such a generic processor and suggest a few characteristics of such a processor. Table 2.1

(a) Use of commercial components is increasing \*PCC: Processing/Controlling Core

(b) More implants require processing capabilities

Figure 2.1: Implant design trends over the years [73]

| Feature                     | Value                                                      |

|-----------------------------|------------------------------------------------------------|

| ISA                         | 32-bit ARMv5TE-compatible                                  |

| Pipel. depth / Datap. width | 7/8-stage, super-pipelined / 32-bit                        |

| RF size                     | 16 registers                                               |

| Issue policy / Instr.window | in-order / single-instruction                              |

| I-Cache, L1                 | 64KB, 64-way assoc. (1cc hit/170cc miss)                   |

| D-Cache, L1                 | 32KB, 2-way assoc. (1cc hit/170cc miss)                    |

| TLB / BTB                   | 1-entry fully-assoc.                                       |

| Branch Predictor            | 2-bit Bimodal (32-entry ret. addr. stack)                  |

| Write Buffer / Fill Buffer  | 2-entry / 2-entry                                          |

| Mem. port no / bus width    | 1 port / 1 Byte                                            |

| INT/FP ALUs                 | 1/1                                                        |

| Clock freq. / Implem. tech. | $2~\mathrm{MHz}$ / $0.18~\mathrm{m}$ @ $1.5~\mathrm{Volt}$ |

Table 2.1: XTREM (Modified) Architecture Details [74]

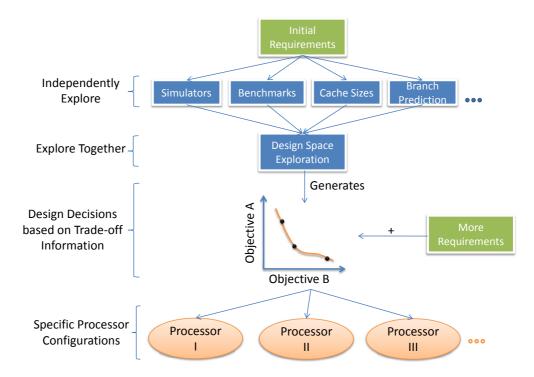

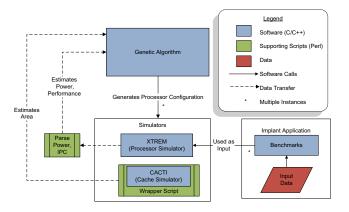

lists the processor configuration they used in their case study. Furthermore, Strydis et. al. used the XTREM simulator as a base for their work and *independantly* explore the effects of varying processor parameters on processor design in their papers on cache structures[72] and branch prediction [77]. The present work being a logical extension of their work, *co-varies* all such parameters, in order to get optimal configurations across all possible parameter combinations and across all benchmarks; for the three objectives of power, performance and area. Figure 2.2 provides an overview of the processor design methodology followed in the SiMS project, and the context of this work.

#### 2.2 Related Work

The related work of this thesis falls in two major fields - that of implant design, and that of design space exploration. The former, including existing implant design methodologies and the consequent need for generic implants has already been studied by Strydis et.al as part of the SiMS project. Therefore, we shall only briefly review these; the majority of this section is a discussion of the latter topic.

#### 2.2.1 Implant Design

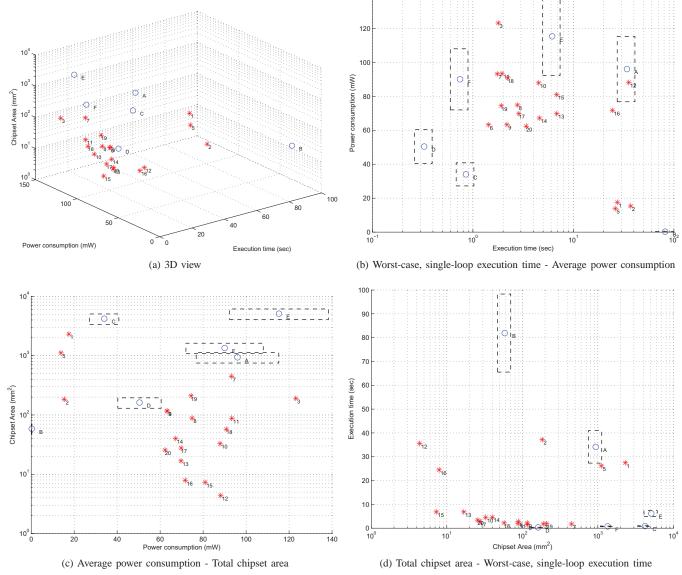

We present a brief overview of a few existing implant designs studied by Strydis [73] in Table 2.2. These designs were chosen from the study as they have listed power, performance and area characteristics; and therefore, can be compared with the processor configurations we derive from our exploration. This comparison is presented in Chapter 4, Section 4.7.

The performance metric listed in these applications is the worst case time to execute the (repetitive) task they are designed for. However, these tasks are highly application dependant and may vary widely. One way of ensuring a fair comparison is to normalize

Figure 2.2: Overview of the SiMS processor design methodology. Independant exploration has already been done by Strydis[72, 77], we focus on the other steps

the amount of data processed in a single iteration of the task. We note that each of these applications are simple stimulation or measurement tasks, with each loop simply processing the ADC data. Therefore, in order to normalize, we assume each loop reads 10KB ADC data at a time (possibly buffered). This approximation is the *best case* scenario for these applications as it assumes there is no (a) data-processing time or (b) buffering times. On the other hand, as we shall see, the performance listed for our processors is also for 10KB data, but the tasks run are the ImpBench benchmarks, which have non-trivial processing times. Therefore, with these assumptions, the real applications represent the *worst case* scenarios for our processors.

#### 2.2.2 Processor Design

For an in-depth analysis of designing processors from design space exploration to synthesis, the interested reader can refer to Gries[31], who contends that the two independant problems in design space exploration (DSE) are how to evaluate a single design point, and, how to cover the design space; and goes on to discuss both in detail. In the context of this work, the first of the problems is not an issue, as previous work in the project has already established the XTREM and CACTI simulators (refer Section 2.3.6). However, the question of how to cover the design space is important. The design space for a processor is huge, and while we would like to cover as much of it as possible, evaluating the space for every single processor configuration possible is virtually impossible. Many general techniques have been proposed in literature that

| # Author                               | Year | Application                                                                 | Functionality               | Chipset Area $(mm^2)$ | Peak<br>Power<br>(mW) | Worst-case<br>Single loop<br>Execu-<br>tion Time<br>(msec) | ADC<br>reso-<br>lution<br>(bits) | Worst-case Single loop Execution Time (Normalized) (sec) |

|----------------------------------------|------|-----------------------------------------------------------------------------|-----------------------------|-----------------------|-----------------------|------------------------------------------------------------|----------------------------------|----------------------------------------------------------|

| Smith<br>(a) et al.<br>[67, 59,<br>58] | 1998 | restoration of<br>paralyzed-muscle<br>functionality,<br>MES                 | stimulation/<br>measurement | 937.50                | 96.00                 | 10.00                                                      | 12                               | 68.27                                                    |

| Eggers (b) et al. [23, 22, 38]         | 2000 | ICP-based diagnosis for brain diseases                                      | measurement                 | 58.50                 | 0.24                  | 10.00                                                      | 10                               | 81.92                                                    |

| Rollins (c) et al. [63]                | 2000 | continuous ECG<br>for understanding<br>spontaneous car-<br>diac arrhythmias | measurement                 | 4209.67               | 34.00                 | 1.00                                                       | 12                               | 6.83                                                     |

| Valdastri<br>(d) et al.<br>[84]        | 2004 | gastric-pressure<br>monitoring                                              | measurement                 | 162.00                | 50.40                 | 0.04                                                       | 10                               | 0.33                                                     |

| Au-<br>Yeung<br>(e) et al.<br>[3]      | 2004 | continuous mon-<br>itoring of AEG,<br>delivery of atrial<br>ATP             | stimulation/<br>measurement | 5106.00               | 115.30                | 3.00                                                       | 10                               | 24.60                                                    |

| Liang (f) et al. [49]                  | 2005 | ENG                                                                         | measurement                 | 1350.00               | 90.00                 | 0.09                                                       | 10                               | 0.75                                                     |

Table 2.2: Overview of a few existing implant applications

explore the design space and search for optimal points. In Section 2.3.1 we take an in depth look at the possible generic optimization techniques, and the reasons for selecting a multi-objective genetic algorithm for this work. In this section, we shall briefly list some tools and techniques developed specifically for design space exploration of processors.

Hekstra et al. [35] explored the TriMedia CPU64 design using pruning – they first probe the design space in order to identify the architectural parameters that affect overall performance the most. The extreme values of these parameters provide 'corner cases', and help in bounding the space to be explored in detail.

DESERT [81] (DEsign Space ExploRation Tool) is a meta-programmable tool for pruning large design spaces using constraints. It represents the design space as a generic structure based on alternatives and parameters, and therefore can be used for diverse applications. Mohanty uses the MILAN [53] (Model based Integrated simuLAtioN) tool, based on DESERT, for pruning design spaces of heterogeneous multi-core systems. The authors of the Artemis (Architectures and Methods for Embedded Media Systems) [57] also work on exploration of heterogeneous multi-core environments, but focus more on modeling and simulation than techniques for DSE.

Cho et. al [9] content that micro-architecture design is better done by considering dynamic behaviour of workloads rather than designing for worst-case workload behaviour. They use wavelet-based multi-resolution decomposition and neural network based non-linear regression modeling to reason about workload dynamics (in terms of performance, power, and reliability) across the micro-architecture design space.

The PICO [43] framework designed at HP Labs, given C code, outputs application specific embedded computer systems optimized for cost vs. performance; where the 'computer system' consists of a EPIC/ VLIW (explicitly parallel instruction computing/very long instruction word) and an NPA (non-programmable accelerator). It uses a space walker – which may be a heuristic, or brute force depending on the search space – to search the design space. A 'component assembler' outputs HDL code for the processors specified by the space walker by assembling low-level components from their component library.

Xie et. al [88] provide an in depth discussion on design space exploration for 3D Integrated circuits, including CAD and design tools, and simulators. They use simulated annealing to automatically find floorplans for the ICs.

Stijn et. al [25] evaluate various automated single and multi-objective optimizations for exploring high performance embedded out-of-order processor designs. They found that a genetic local search algorithm outperforms all other techniques for their application.

Ascia, Catania and Palesi [2] propose using genetic algorithms to perform design space exploration in processors. They apply a genetic algorithm to optimize the memory hierarchy in terms of area, power and mean access time. However, they use a single-objective genetic algorithm and model the fitness function as a product of the three objectives. As we shall see in Section 2.3.2, such techniques face drawbacks that reduces their suitability for use with design spaces whose shapes are not known in advance<sup>1</sup>, as in our case.

Thiele et. al. [83] present domain specific design space exploration for network processor architectures. They specify models for packet specific tasks and network traffic ("encoding"); methods to estimate delays and queuing memory ("simulation"); and use an evolutionary algorithm to perform multi-objective design space exploration ("optimization"). This work is perhaps the closest to our work. However, to the best of our knowledge, design space exploration with respect to implantable systems has not been previously studied.

#### 2.3 Background

In this section, we formally describe the terminology used in the paper, and the two major categories of optimization - single-objective and multi-objective, and their applicability to our case. We then give a brief overview of various optimization heuristics, why we

<sup>&</sup>lt;sup>1</sup>Since the design space may well be non-convex, for which this method does not work

chose genetic algorithms as our heuristic of choice, and describe terminology associated with genetic algorithms. Finally, we give an overview of the simulators (XTREM and CACTI) and benchmark suite we employ (ImpBench).

#### 2.3.1 Notes on Optimization

Optimization is defined as "an act, process, or methodology of making something (as a design, system, or decision) as fully perfect, functional, or effective as possible; specifically: the mathematical procedures (as finding the maximum of a function) involved in this" [20]. In processor design, it would mean the process of finding as perfect a processor as possible; perfect being subject to the design objectives we would like to characterize the processor with.

Formally, an optimization problem is defined as [18, eqn. 2.1]:

$$\begin{array}{lll} \text{Maximinize/Minimize} & f_m(x), & m = 1, 2, ..., M; \\ \text{subject to} & g_j(x) \geq 0, & j = 1, 2, ..., J; \\ & h_k(x) = 0, & k = 1, 2, ..., K; \\ & x_i^{(L)} \geq x_i \geq x_i^{(U)}, & i = 1, 2, ..., n. \end{array}$$

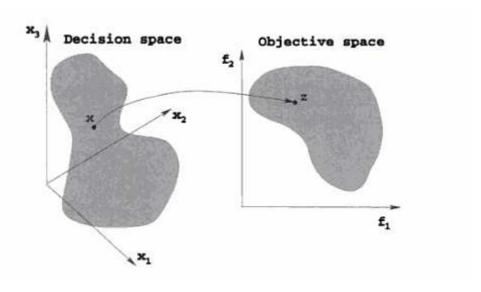

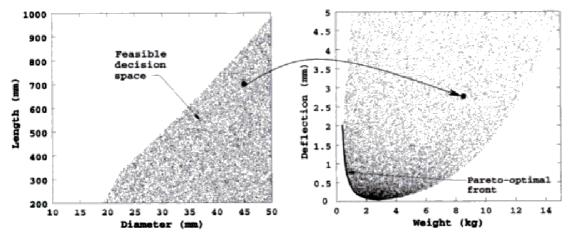

A feasible solution to this problem will consist of an n-dimensional vector  $x = (x_1, x_2, ..., x_n)^T$  that falls within the lower and upper variable bounds  $(x_i^{(L)} \text{ and } x_i^{(U)} \text{ respectively})$  and satisfies the j+k constraints. The n-dimensional region where the feasible solutions lie is known as the search space. We can evaluate each of the m objective functions on every point x in the search space. The resulting m dimensional space is known as the *objective space* or *design space* (Refer: Figure 2.3). In this work, we shall mostly refer to it by the latter name.

#### 2.3.1.1 Pareto optimality

Most classical optimization techniques focus on optimizing a single variable or multiple variables with respect to a single objective. However, many real engineering problems involve more than one objective. Furthermore, for multiple-objective problems, the objectives are often conflicting, such as minimizing chip-area while maximizing performance. In such a problem, there is no single optimal solution. Instead, there exist a number of solutions that are all optimal. In the absence of more case-specific information (which may be purely qualitative, or even be absent altogether), there is no way of saying which solution from this set of solutions is **the** optimal. In such cases, the decision makers can be provided with the entire set of optimal solutions and the trade-offs they represent. They can then make decisions based on these trade-offs and the particular manifestation of the problem, or, when more information is available. The most interesting set of trade-offs for a given problem is the set of *Pareto points* (Figure 2.4). A point in the design space is a Pareto point if there is no objective that dominates it. In this context, dominance is a strict partial order relation defined as (adapted from Deb [18], Coello[10]):

2.3. BACKGROUND 11

Figure 2.3: Representation of the decision variable space and the corresponding objective space [18, Figure 5, Page 15]

Let

$$\vec{u} = (u_1, ..., u_m) = (f_1(x_1), ..., f_m(x_1))$$

$\vec{v} = (v_1, ..., v_m) = (f_1(x_2), ..., f_m(x_2))$  where  $f_i = i^{th}$  objective function

Solution  $x_2$  dominates solution  $x_1$  if and only if:

$$\begin{array}{ll} u_i & \leq v_i, \quad \forall i \in \{1,2,...,m\} \\ \text{And,} & u_i & < v_i, \quad \exists i \in \{1,2,...,m\} \end{array}$$

In words, this implies: the solution  $x_2$  is said to dominate solution  $x_1$  if  $x_2$  is no worse than  $x_1$  in all objectives, and,  $x_2$  is strictly better than  $x_1$  in at least one objective.

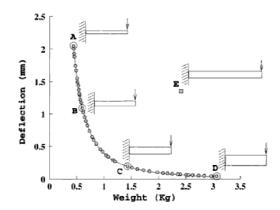

For example, in Figure 2.4b, E is not a Pareto-point since it is dominated by other points - there exist points which have a lower weight given the same deflection as E, and points that have a lower deflection given the same weight as point E. The Pareto points are A,B,C,D because they are non-dominated in the entire feasible objective space. The entire set of such Pareto points is known as the *Pareto front*.

In the context of this work, having the Pareto front of the problem available means that the decision makers can be given the whole spectrum of trade-offs pertaining to power, performance, and area. Since the aim is to have generic processors, they can then choose a few of these processor configurations that between themselves are representative of most of the medical implant applications.

(a) Feasible Decision Space and the Corresponding objective space in a real engineering problem (deflection and weight depend on length and diameter of a beam)

(b) The pareto front corresponding to the above problem. A,B,C,D are Pareto points and form the Paretofront; E is dominated by other points and hence is not a Pareto-optimal point.

Figure 2.4: It is easier to choose design parameters (length, weight) given the Pareto front of the objectives (deflection, weight) [18]

#### 2.3.2 Single vs. Multi-optimization

The classical single-objective optimization methods can be used to perform multiobjective optimization by reformulating the multi-objective optimization problem into a single-objective one. This can either be done by combining the objectives into a single aggregate objective [44], or by only considering one of the objectives and moving the rest to a constraint set [51]. The first approach can be implemented, for example, with finding the weighted sum of each of the objectives - instead of objectives X and Y, we optimize  $w_1X + w_2Y$ , where  $w_1$  and  $w_2$  are appropriate weights. However, this is difficult, because the objectives may be non-commensurable, their relative importance may not be quantifiable, and, the range of values they can take may not be known in advance. This makes it difficult to decide the weights by which each variable must be scaled, since even slight changes in the weights can lead to quite different solutions [46]. The second approach also faces almost the same drawback - to reformulate the objectives as constraints, the range of values of these former objectives must be known in advance. In spite of these limitations, these methods are attractive because they are simpler to understand and implement. In the first stage of implementation, we used a single-objective Genetic Algorithms that used the weighted-sums approach for finding the fitness of an individual. However, this was quickly abandoned as we could not logically assign the values of the weights since there was no rationalization for choosing one objective relative to the other without more information about the problem domain. Also, indeed we did not have the absolute upper and lower limits of the three objectives (power, performance, area).

The above methods provide the designer with only a single solution. By changing the aggregation method slightly, one can reduce the impact of the weight-selection process and, instead of a single solution, provide the designer with a Pareto-front solution. In case of the weighted-sums-approach, this can be done by iteratively changing the relative weights of the objectives and optimizing each of these sums. For example, for objectives X and Y, we optimize  $X + w_1Y, X + w_2Y...X + w_nY$ . This gives us n tradeoff points between X and Y depending on how much importance we attach to Y relative to X. However, this approach has its own drawbacks such as inability to ensure a uniformly distributed set of Pareto-optimal solutions, difficulty with problems having a non-convex objective space, and no guarantees on optimality beyond satisfying the first order optimality criteria [18, Chapter 3] [14]. The other classical methods "fixed up" for multi-objective optimization all face similar drawbacks, summarized in Table 2.3.

Therefore, we need a technique specifically developed for multi-optimization that does not face the above drawbacks. In the next section, we introduce NSGA-II, a Genetic Algorithm that does exactly this.

#### 2.3.3 Heuristic Algorithms

"Trying to find the global optimum of a multi-objective problem is an NP-Complete problem" [10]. Therefore, the best we can do is use a heuristic to approximate the solution space. In this section, we list some of the popular meta-heuristic techniques that can be applied to any search and optimization problem.

Random Optimization[68] At each iteration, the design space is sampled randomly, and the design point is evaluated with respect to the optimization objective. The best design point seen so far is saved, and the candidate solution point at the end of a fixed number of iterations is considered the final solution. The idea is that if the iterations are allowed to continue for a long enough time, the algorithm will eventually encounter the optimal solution. This approach does not have problems with local minima. However, convergence depends on the kind of design space and the quality of solution required – if there is exactly one optimal solution, it may not be found; on the other hand if there are several design points each having an optimal value, then there is better likelihood of finding one of them.

Table 2.3: Summary of methods using single objective optimization techniques to perform multi-objective optimization

| Method                       | Description                                                                                                                                                                                                                                 | Advantages                                                                                 | Disadvantages                                                                                                                                                                  | Formula                                                                                                                                                                                                                                                                  | Ref.                  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Weighted<br>Sum              | Select a weight $w_m$ for each objective function $f_m(x)$ , minimize the weighted sum                                                                                                                                                      | Simple, Intuitive,<br>Guaranteed for<br>Convex problems                                    | Adding non-commensurable Objectives, Hard to get uniform Pareto- point spread, Doesn't work for non-convex problems                                                            | Minimize $F(x) = \sum_{m=1}^{M} w_m f_m(x)$<br>subject to $g_j(x) \ge 0$ , $j = 1,, J$ ;<br>$h_k(x) = 0$ , $k = 1,, K$ ;<br>$x_i^{(L)} \le x_i \le x_i^{(U)}$ , $i = 1,, n$ ;                                                                                            | [14]                  |

| e-<br>Constraint             | Optimize one objective $f_{\mu}(x)$ , reformulate other objectives $f_m(x)$ $(m \neq \mu)$ as constraints                                                                                                                                   | Works for convex<br>and non-convex<br>problems                                             | If wrong value of $\epsilon$ is selected, may not give any solution. More the objectives, more $\epsilon_s$ need to be chosen from knowledge of problem domain                 | $\begin{array}{ll} \text{Minimize} & f_{\mu}(x), \\ \text{subject to} & f_{m}(x) \leq \epsilon_{m}, \qquad m = 1,, M, \ m \neq \mu; \\ g_{j}(x) \geq 0, & j = 1,, J; \\ h_{k}(x) = 0, & k = 1,, K; \\ x_{i}^{(L)} \leq x_{i} \leq x_{i}^{(U)}, \ i = 1,, n; \end{array}$ | [33]                  |

| Weighted<br>Matrix<br>Method | Generic case of Weighted Sums method. Minimize distance measure $l_p$ of any solution $x$ from the ideal solution $z^*$ . Depending on value of $p$ chosen, minimize weighted sum, Euclidean distance or highest deviation (for large $p$ ) | Guranteed to<br>find each Pareto-<br>optimal solution                                      | Needs normalization of objectives - Bounds of objectives must be known, Need to independently optimize each of $M$ objectives before problem is optimized (for getting $z^*$ ) | Minimize $l_p(x) = \left(\sum_{m=1}^{M} w_m   f_m(x) - z_m^* ^p\right)^{1/p}$<br>subject to $g_j(x) \ge 0$ , $j = 1,, J$ ;<br>$h_k(x) = 0$ , $k = 1,, K$ ;<br>$x_i^{(L)} \le x_i \le x_i^{(U)}$ , $i = 1,, n$ ;                                                          | [18,<br>Charter<br>3] |

| Benson's<br>Method           | Similar to Weighted Matrix method, except the reference solution $z^0$ is a randomly chosen feasible non-Pareto solution.                                                                                                                   | If appropriate $z^0$ is chosen, can find solutions in the non-convex Pareto optimal region | Additional constraints introduced for restricting solution in region dominating $z^0$ , non-differentiable objective function                                                  | $\begin{array}{ll} \text{Maximize} & \sum_{m=1}^{M} \max(0,(z_m{}^0 - f_m(x))), \\ \text{subject to} & f_m(x) \leq z_m{}^0 & m = 1,,M; \\ & g_j(x) \geq 0, & j = 1,,J; \\ & h_k(x) \geq 0, & k = 1,,K; \\ & x_i^{(L)} \leq x_i \leq x_i^{(U)}, & i = 1,,n; \end{array}$  | [6]                   |

| Value<br>Function<br>Method  | Also called utility function method. The user provides a value function $U$ relating all objectives, this function is maximized                                                                                                             | Simple idea, if<br>value function<br>information is<br>available                           | Solution depends<br>on value function<br>chosen, Need a<br>value function<br>applicable over the<br>entire search space                                                        | $\begin{array}{ll} \text{Maximize} & U(F(x))), & F(x) = (f_1(x),,f_M(x))^T \\ \text{subject to} & g_j(x) \geq 0, & j = 1,,J; \\ & h_k(x) \geq 0, & k = 1,,K; \\ & x_i^{(L)} \leq x_i \leq x_i^{(U)}, \ i = 1,,n; \end{array}$                                            | [26]                  |

2.3. BACKGROUND 15

Hill Climbing[64] As a kind of greedy algorithm, it makes locally optimal choices at each iteration in an attempt to find the global optima. The algorithm starts with a random initial solution to the problem at hand. The solution is then mutated, and if the mutation results in a better solution than the previous one, the new solution is kept; otherwise, the current solution is retained. The algorithm is repeated until no mutation can be found that causes a more optimal solution than the current solution, and the current solution is returned as the result. The drawback is that often, the algorithm gets stuck at local optima and can not find the global optimum – although methods have been suggested to counter this. Also, for a noisy design space, there may be problems in converging.

Simulated Anealing[45] Inspired by the annealing process in mettalurgy, each step of the algorithm replaces the current solution by a random "nearby" solution. The nearby solution is chosen with a probability that depends on the difference between the corresponding function values of the current and nearby solution, as well as a global parameter T (called temperature), that is gradually decreased during the process. This dependency is such that the current solution changes almost randomly when T is large, but increasingly slowly towards (local) optima as T goes to zero. As was the case of hill climbing, this method may also get stuck in local optima, but with a lesser likelihood of doing so, due to the initial wide range of searches.

Tabu Search [27] This algorithm is similar to the hill climbing approach, except that the algorithm keeps track of solutions already examined through memory structures. The solutions recently examined and discarded are marked as 'taboo' and therefore can not be re-visited. Therefore, the search performs faster by avoiding unnecessary re-evaluations. Since it is so similar to the hill climber, it faces the same drawbacks.

Ant Colony Optimization[21] The algorithm searches for an optimal path in a graph; based on the behavior of ants seeking a path between their colony and a source of food. Ants wander from the colony to random places in search for food and then return to the colony. On the path they take to return, they deposit a trail of pheromones. If an ant travelling back encounters a pheromone trail, it follows this trail instead of a new path, thereby depositing more pheromones on it and strengthening the path. As time passes, trails also lose pheromone. This processes of addition and removal of pheromones eventually leaves behind optimal trails. This behaviour is extended to the design space to find optimal solutions – ant colony algorithms are regarded as populated metaheuristics with each solution represented by an ant moving in the search space. Ants mark the best solutions and take account of previous markings to optimize the search. The drawback is that real life problems are sometimes difficult to formulate as equivalent ant-colony problems.

Evolutionary Algorithms [28] These algorithms solve the problem of convergence local optima, are widely studied and applied, and, in our opinion, easier to formulate

as a search problem for our application. Detailed discussion on this algorithm can be found in Section 2.3.4.

#### 2.3.4 Genetic Algorithms

Evolutionary Algorithms are a class of Artificial Intelligence algorithms that mimic Darwin's theory of natural selection to solve search and optimization problems. Genetic Algorithms (GAs) are a special class of Evolutionary Algorithm, defined by their pioneers [28] as "probabilistic search procedures designed to work on large spaces involving states that can be represented by strings." Simple as this may sound; Genetic Algorithms are extremely powerful and can be applied without much modification to a large class of problems. They overcome many of the problems associated with other search techniques, such as — the convergence does not depend heavily on the chosen initial solution; the algorithm has mechanisms to not get stuck at local-optima; discrete, noisy, and dynamic search spaces are efficiently handled; and the algorithm can easily be parallelized [18, Page 82].

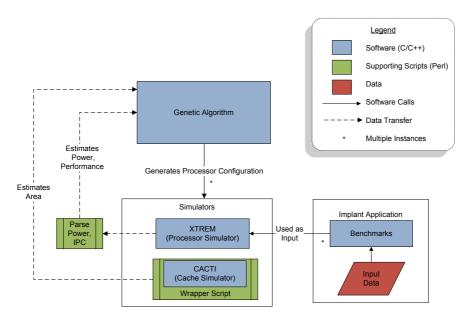

The basic Genetic Algorithm encodes the input variables as a string of bits, known as a chromosome. A chromosome belongs to an individual, which represents one particular solution point in the search domain. A collection of these individuals forms a population. Therefore, the population represents the mutually independent solutions under consideration. The algorithm tries to evolve the population in such a manner that the *fitness* of the population minimizes (or maximizes). The fitness here is represented by a problem-specific fitness function, and quantitatively represents the search or optimization objective. Each evolutionary step of the algorithm creates a new (child) population from the previous step's (parent) population by selectively choosing fit individuals to be propagated into the next generation. These individuals are then subject to change via cross over (Chapter 3, Figure 3.3) – exchange of genetic material - and mutation (Chapter 3, Figure 3.2) - destruction of some encoded information and introduction of new, random information – in order to drive the search into new and previously unexplored directions [86]. Some genetic algorithms ensure that the best solutions found so far are preserved. This approach, known as elitism, helps ensure that the random processes do not destroy good solutions; the algorithm always moves towards a better solution, never leading to a worse one. The basic GA steps and components are shown in Figure 2.5.

The definitions above are for a single objective genetic algorithm. In case of multi-objective GAs, the population represents the candidate solutions that lie on the (approximate) Pareto front. The algorithm in this case then tries to evolve the entire solution front towards the true (but unknown) Pareto front. The selection procedure in this case becomes slightly different than that in the single objective version. In the single objective algorithm, deciding which individuals from a population get to reproduce and move on to the subsequent generations is done by sorting the individuals according to their fitness - in the simplest implementation, the top few individuals from the sorted list get through to the next generations, others are

(b) An Individual consists of a Chromosome (c) A Population consists of N Individuals (encoded attributes) and its fitness (quality w.r.t. The objectives)

Figure 2.5: Schematic and components of a Genetic Algorithm

discarded; more complicated strategies use a probabilistic selection approach on the selected individuals. Since now we want to collectively better the entire population, simple sorting will not work. We need a mechanism that ensures that the front found at every generation moves forward. The algorithm that we use for this work, called NSGA-II, uses 'non-dominated sorting' specially designed for multi-objective GAs to accomplish this. The interested reader can refer to the detailed working of NSGA-II in [19].

We chose NSAGA-II as it is state of the art, and is one of the most widely used and studied multi-objective algorithms in literature, along with its competitor, SPEA2 [90]. Moreover, the NSGA-II sources are freely available from the authors. We use a modified version of this original source code in our work.

| benchmark         | name         | size  | dyn. instr.*  | dyn. $\mu ops^*$ |

|-------------------|--------------|-------|---------------|------------------|

|                   |              | (KB)  | (average) (#) | (average) (#)    |

| Compression       | miniLZO      | 16.30 | 233186        | 323633           |

|                   | Finnish      | 10.40 | 908380        | 2208197          |

| Encryption        | MISTY1       | 18.80 | 1267162       | 2086681          |

|                   | RC6          | 11.40 | 863348        | 1272845          |

| Data integrity    | checksum     | 9.40  | 62560         | 86211            |

|                   | CRC32        | 9.30  | 418598        | 918872           |

| Real applications | motion       | 9.44  | 3038032       | 4753084          |

|                   | DMU4         | 19.50 | 36808080      | 43186673         |

|                   | DMU3         | 19.59 | 75344906      | 107301464        |

| Stressmarks       | stressmotion | 9.40  | 288745        | 455855           |

|                   | stressDMU3   | 19.52 | 124212        | 224791           |

Table 2.4: ImpBench benchmarks. (\*) indicates typical values for 10 - KB workloads, except for DMU-variants which use their own special workloads. [79]

#### 2.3.5 Benchmarks and Workloads

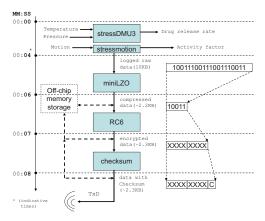

The performance of a processor depends not only on its internal components but also on the applications that run on it. Therefore, to get an accurate representation of the suitability of a generic implant processor, we need to run a set of benchmarks to characterize it that are representative of the application domain. The ImpBench benchmark suite [78] is proposed for this very purpose, we use an extended version of the ImpBench suite[79]. The applications included in the suit are classified as lossless compression, symmetric-key encryption, data integrity, and synthetic programs that are representative of actual applications. A brief overview of the benchmarks can be found in Figure 2.4. We use these benchmarks for evaluating the fitness of the individuals in our Genetic Algorithm.

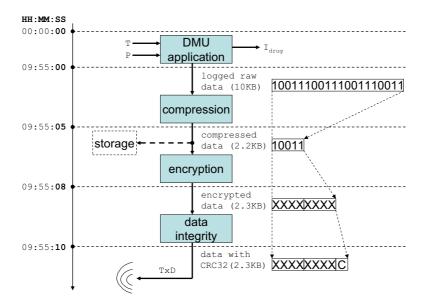

The behaviour of programs also depend on the inputs given to the program. To get a true representation of a processor, we must therefore also choose a suitable workload and workload size for running the benchmarks. For profiling the benchmarks in the ImpBench suit, 7 representative workloads have been selected based on real data. The different benchmarks perform differently with respect to these workloads - the "motion" application and the compression algorithms depend heavily on both the type of input data and the size of the input data [75], encryption and data-integrity algorithms only depend on the input data size [76], the DMU application is a tight kernel reading its own fixed input values and hence does not depend on the either the input size or the input data. All benchmarks (except DMU) show worst case behavior (in terms of IPC) with the EMGII input type[61]. Therefore, we use EMGII as the workload for all our experiments. We also selected the higher available workload size of 10KB. In Chapter 4 we will study the effect of changing this workload size to the lower size of 1KB.

#### 2.3.6 Simulators

Ideally, to characterize a given processor configuration, one would make an HDL implementation of the processors, synthesize this, and thus compute its power, performance and area requirements. However, we need to implement thousands of processor configurations to feed the Genetic Algorithm (GA) in its exploration of the design space. This process is cumbersome if done manually, and difficult to automate. Therefore, we need simpler simulators to approximate the behaviour of the processors. These simulators model processor behaviour as function evaluations. Needless to say, this will introduce approximations into the values found. A designer requiring a certain processor can select promising candidates from the design space found by the GA while keeping this approximation in mind.

The primary simulator we use is XTREM [11], a modified version of SimpleScalar [4]. The XTREM simulator is a cycle-accurate, microarchitectural, power- and performance-functional simulator for the Intel XScale core [74], with an average performance error of only 6.5% and an average power error of only 4% [11]. Moreover, the simulator is open, free, and readily available.

XTREM has a 32-bit ARMv5TE-compatible ISA with a 7/8-stage pipeline, a 32-bit datapath, 16 registers, in-order instruction execution, and 2 MHz clock frequency. It supports modelling of, among other things, L1 and L2 caches, different branch predictor schemes, ALUs, write and fill buffers, memory ports, and bus width. It was chosen because of its precision, ease of use, availability, and as mentioned before, because previous work in the project has been done using this simulator. However, while using, we did find flaws in the simulator. Therefore, the future work on the project should replace this simulator.

The second simulator we use is the popular CACTI (Cache Access Latency and Power Estimation Tool), which is "An integrated cache and memory access time, cycle time, area, leakage, and dynamic power model" [47]. Specifically, we use CACTI 3.0, which includes modelling support for the area of caches, caches with independently addressed banks, fully-associative caches, a power model, technology scaling, among other things. We use CACTI for modeling the areas of the caches and the branch prediction table, which are used to approximate the total processor area. This is justified as the major component of the chip area are cache structures <sup>2</sup>rather than processing blocks, with the processing block size hardly changing from design to design <sup>3</sup>. In fact, according to [70], caches take caches consume approximately 90% of transistor count, taking up 60% of the area. Also, as we shall see, the way our design works, there is minimal change in the processing blocks, but we do vary the cache configurations. Therefore, modeling the area through the cache structures gives a good relative metric to comparison area.

$<sup>^1\</sup>mathrm{For}$  the processor modeled by XTREM, core size is 0.13765  $cm^2$  whereas the cache size is about 0.20647  $cm^2[70]$

<sup>&</sup>lt;sup>2</sup>The size of the ARM cores hardly changed from ARM2 (30,000 transistors) to ARM6 (35,000 transistors), whereas the cache sizes changed from no cache to 4KB cache. The total transistor count changed from 30,000 in ARM2 to 360,000 transistors in ARM6(including MMU, caches, write back buffer)[12].

Experimental Setup

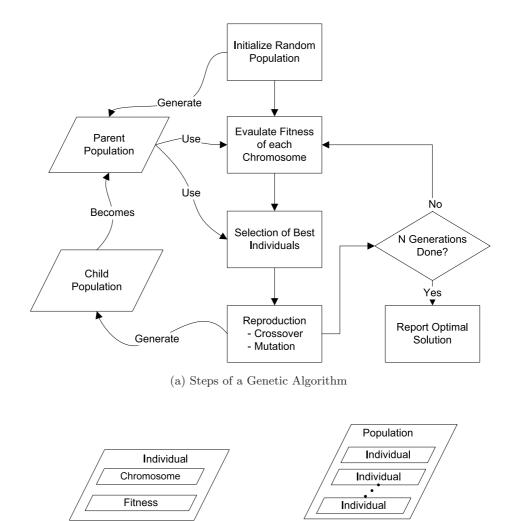

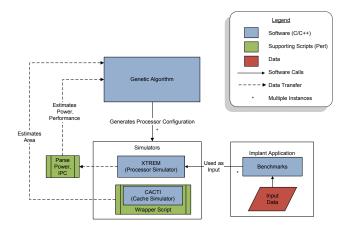

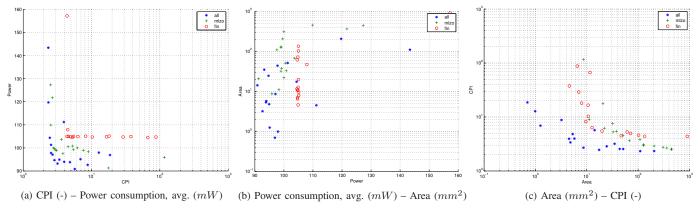

As stated previously, there is a need for automating the optimization process that searches for good processor configurations. In addition to this, we also need a way to automate the process of creating different processor configurations and evaluating them. We delegate this task to two simulators, XTREM [11] and CACTI [66]. The first takes into account all 13 of our processor input parameters and simulates the performance and power requirements of the processor so formed, while we use the later to approximate the area of the processor.