M.Sc. Thesis

## A Continuous Calibration Method For the Transfer Stabilization of Successive Detection Logarithmic Amplifiers

Author: Ing. Vincent R. Bleeker Supervisor: Dr. ir. Wouter A. Serdijn

**Challenge the future**

## A Continuous Calibration Method for the Transfer Stabilization of Successive Detection Logarithmic Amplifiers

## THESIS

# Submitted in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

### in

## MICROELECTRONICS

by

Vincent Robert Bleeker born in Zaandam, the Netherlands

Microelectronics Department of Electronics Faculty of Electrical Engineering, Mathematics and Computer Science DELFT UNIVERSITY OF TECHNOLOGY

June 2012

#### DELFT UNIVERSITY OF TECHNOLOGY

## Abstract

## Faculty of Electrical Engineering, Mathematics and Computer Science Department of Electronics

Master of Science

#### by Ing. V.R.Bleeker

To ensure efficient and reliable operation of power amplifiers it is very important to precisely measure and control the power of the signal they transmit. A device most often used to do precise power measurements of RF systems is the so-called RF power detector. As this detector is used as measurement device the precise measurement ability of the RF power detector is very important. For the precise predictability of the output power of power amplifiers the transfer of the RF power detector has to be fixed and accurately known.

In this thesis we develop a new calibration method for the transfer stabilization of logarithmic power detectors. Via thorough investigation at system level and circuit level it is shown that the proposed method can be used to continuously calibrate the transfer of a logarithmic RF power detector to a predefined and fixed position over mismatch, part-to-part spread, temperature and input frequency.

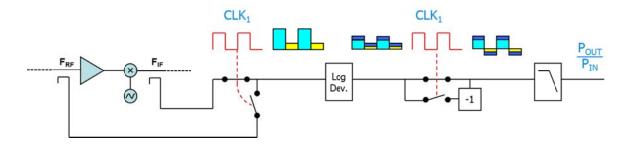

The method depends on a novel switching algorithm around a log device that is capable to do continuous slope, intercept and dynamic range correction on the transfer of the logarithmic power detector. When accurate enough, the method would make calibration of each individual device unnecessary. Furthermore a new method is presented that can be used to extend the dynamic range of log detectors. System simulations show that the calibration method leads to the wanted transfer stabilization of the logarithmic power detector.

A critical part of the new logarithmic transfer calibration method is the need of an accurate multiplication procedure at the input of the logarithmic device. For this accurate multiplication a new accurate gain fixation procedure for a non-linear high bandwidth gain stage was developed. A big part of the thesis is dedicated to the investigation and circuit implementation of this new accurate and fast gain fixation procedure. The gain stabilization method leads to the implementation of a new innovative gain fixation system, including several new architectural innovations. One of these innovations is the implementation of a new accurate ripple blocking system with relative small form factor and fast response time. Simulation results of the circuit implementation of the gain stabilization system prove that the accuracy of the gain stabilization of the non-linear high bandwidth gain stage is well within the required specifications.

## **Table of Contents**

| 1 | INTROD     | UCTION                                                                                                                            | 16 |

|---|------------|-----------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1 RF Po  | wer Detection                                                                                                                     | 16 |

|   |            | F POWER DETECTOR                                                                                                                  |    |

|   |            | FINITION OF SIGNAL POWER IN RF SYSTEMS                                                                                            |    |

|   |            | L CREST-FACTOR                                                                                                                    |    |

|   |            | TANCE OF PRECISE POWER MEASUREMENTS                                                                                               |    |

|   |            | JALITY MEASURE OF RF POWER DETECTORS                                                                                              |    |

|   |            | of RF Power Detectors                                                                                                             |    |

|   | 1.7.1      | Diode Detector                                                                                                                    |    |

|   | 1.7.2      | RMS Detector                                                                                                                      |    |

|   | 1.7.3      | Logarithmic Detector                                                                                                              |    |

|   | 1.7.4      | Conclusion                                                                                                                        |    |

|   |            | CATIONS                                                                                                                           |    |

|   | 1.8.1      | Measuring of the output of a transmitter                                                                                          |    |

|   | 1.8.2      | Measuring of the input of a receiver                                                                                              |    |

|   | 1.8.3      | Power gain calculation                                                                                                            |    |

|   | 1.8.4      | Voltage standing-wave ratio measurement                                                                                           |    |

|   | -          | CT DEFINITION                                                                                                                     |    |

|   |            |                                                                                                                                   |    |

|   |            |                                                                                                                                   | -  |

| 2 | SUCCESS    | SIVE APPROXIMATION LOG DETECTOR                                                                                                   | 40 |

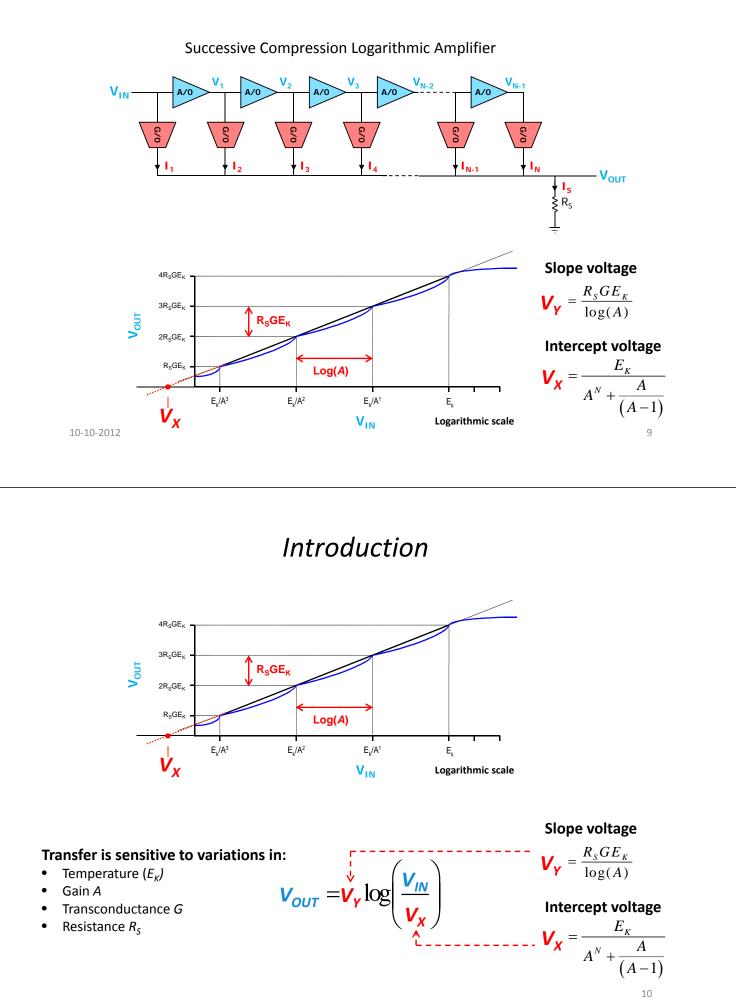

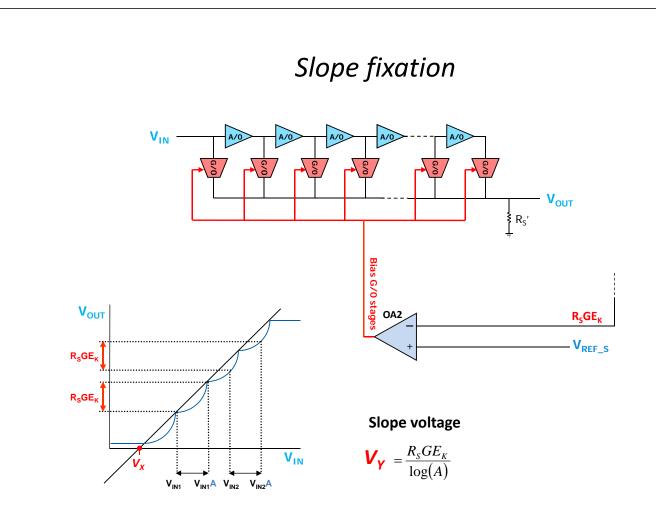

|   | 2.1 Opera  | TION OF A SUCCESSIVE APPROXIMATION LOG DETECTOR                                                                                   | 40 |

|   |            | EAL LOG DETECTOR TRANSFER FUNCTION                                                                                                |    |

|   |            | vise Linear Approximation of the LOG-function                                                                                     |    |

|   | 2.3.1      | Implementation with A/1 gain-cells                                                                                                |    |

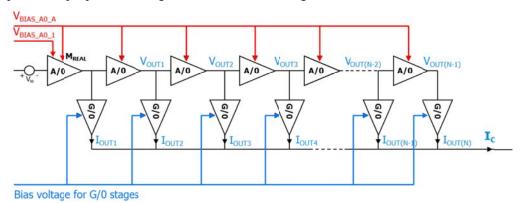

|   | 2.3.2      | Implementation with A/O gain-cells                                                                                                |    |

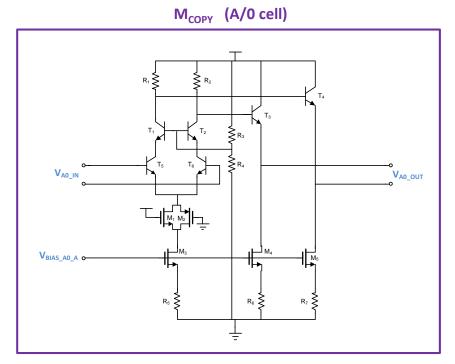

|   | 2.3.3      | Circuit implementation of an A/O cell                                                                                             |    |

|   | 2.3.4      | G/0 stages to decouple the slope calibration                                                                                      |    |

|   |            | TANT TRANSFER FUNCTION CHARACTERISTICS                                                                                            |    |

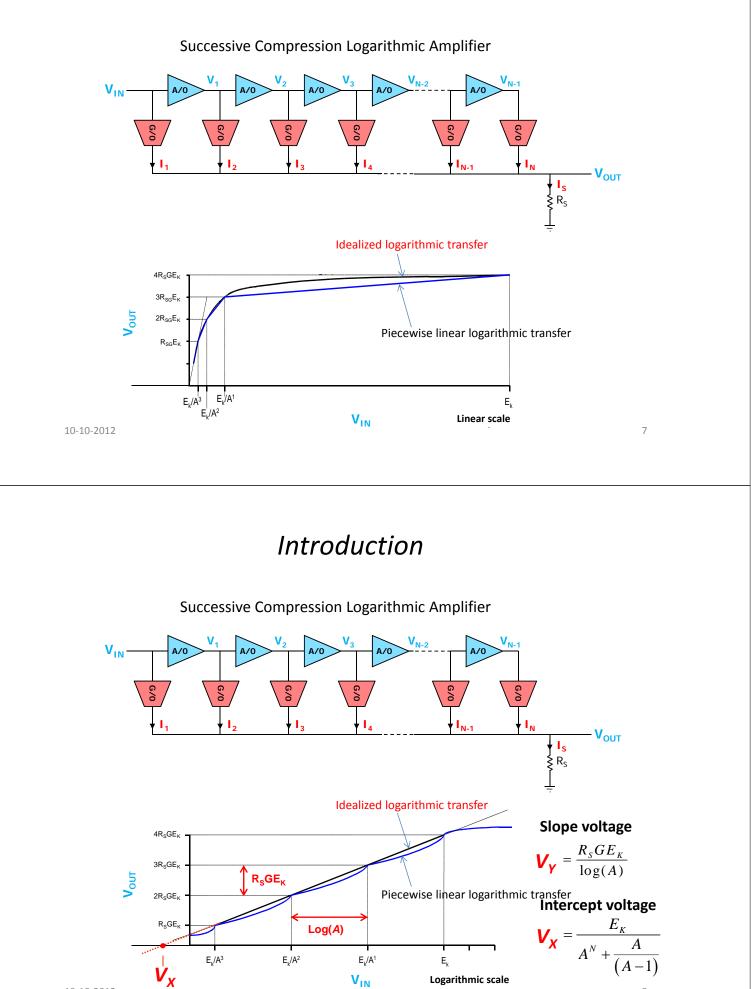

|   | 2.4 INPOR  | Slope and Intercept                                                                                                               |    |

|   | 2.4.2      | Log-conformance error                                                                                                             |    |

|   |            |                                                                                                                                   |    |

| 3 | STABILIZ   | ING THE LOG DETECTOR TRANSFER                                                                                                     | 60 |

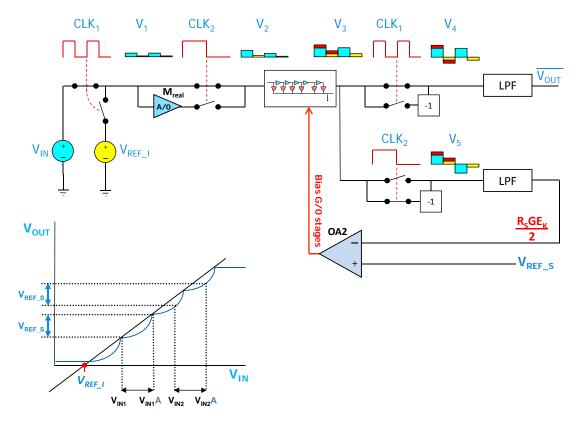

|   | 3.1 INTER  | EPT FIXATION ALGORITHM                                                                                                            | 61 |

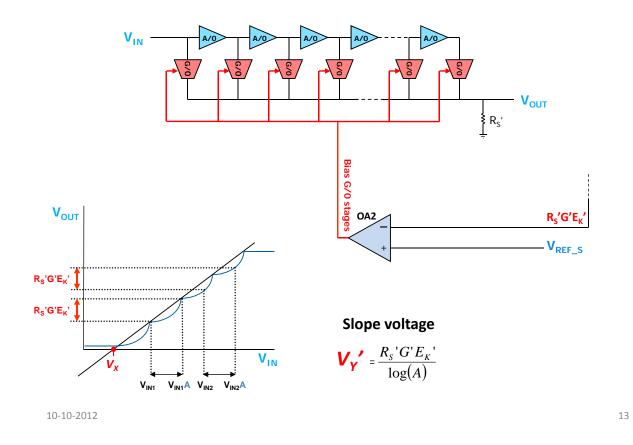

|   |            | FIXATION                                                                                                                          |    |

|   | 3.2.1      | Fixing the multiplication factor                                                                                                  | 69 |

|   | 3.2.2      | Extending dynamic range                                                                                                           |    |

|   |            | HING FREQUENCY CONSIDERATIONS                                                                                                     |    |

|   |            | SYSTEM OVERVIEW                                                                                                                   |    |

| _ | -          |                                                                                                                                   |    |

| 4 | SYSTEM     | LEVEL VERIFICATION                                                                                                                | 88 |

|   | 4.1 DEFIN  | NG THE IDEAL TRANSFER                                                                                                             | 88 |

|   | 4.2 VERIFI | CATION OF THE IDEALIZED SLOOP FIXATION METHOD                                                                                     | 89 |

|   | 4.3 THE LO | OG CONFORMANCE SENSITIVITY TO DEVIATIONS IN THE SLOPE FIXATION SYSTEM                                                             | 92 |

|   | 4.3.1      | Sensitivity to deviations in the control systems                                                                                  | 94 |

|   | 4.3.1.     | L Sensitivity of the system accuracy to the individual error sources                                                              |    |

|   | 4.3        | .1.1.1 Sensitivity to the individual error sources of the A/0 control system                                                      | 98 |

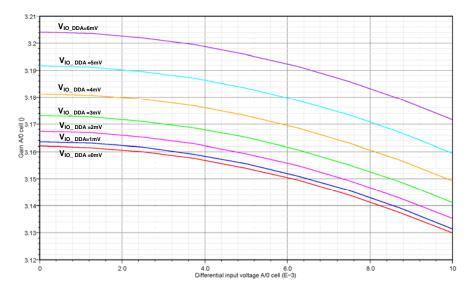

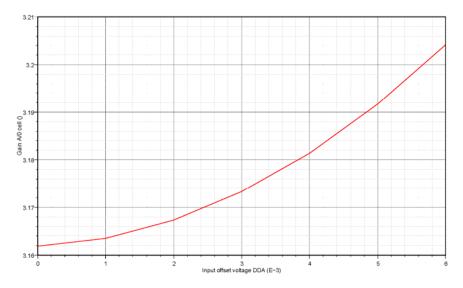

|   |            | Input offset voltage at error amplifier OA1                                                                                       |    |

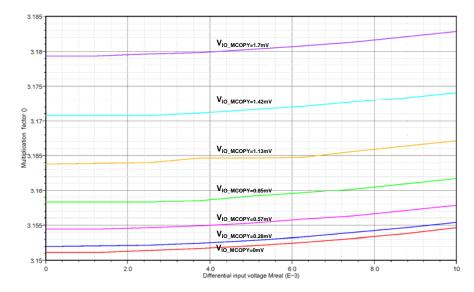

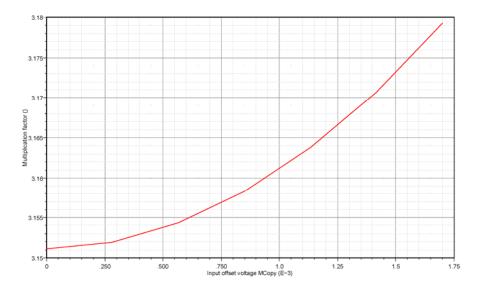

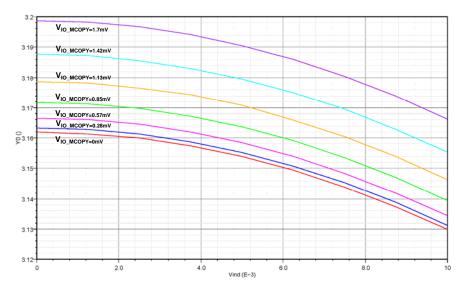

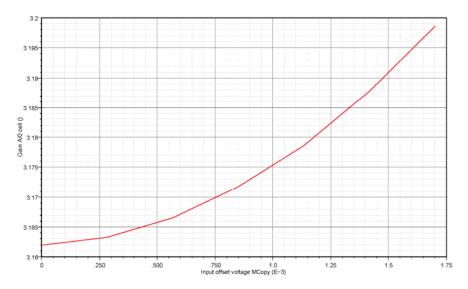

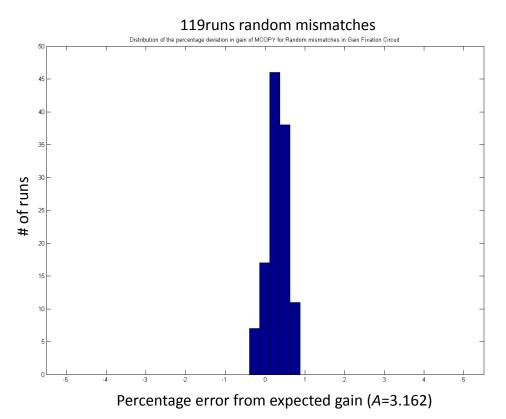

|   |            | Input offset voltage of the multiplication cell M <sub>COPY</sub>                                                                 |    |

|   |            | Deviation in the attenuation factor of the divider block                                                                          |    |

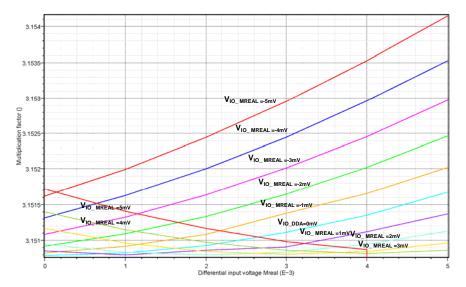

|   |            | Mismatch between the two multiplication cells                                                                                     |    |

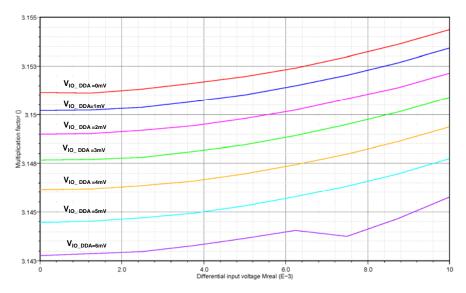

|   | 4.5        | .1.1.2 Error sources that alter the accuracy of the bias control system of the G/0 cells<br>Deviation in reference voltage of OA2 |    |

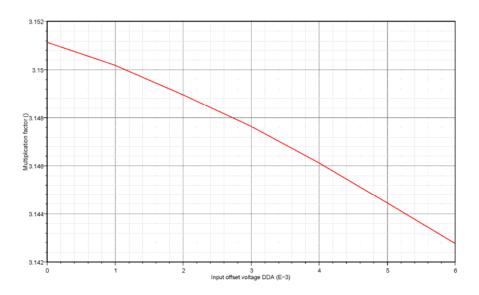

|   |            | Input offset at OA2                                                                                                               |    |

|   |            | Deviation in the expected ratio between resistors $R_{s1}$ and $R_{s2}$                                                           |    |

|   |            | · · · · · · · · · · · · · · · · · · ·                                                                                             |    |

|   |            | Splitting error of the current divider                                                                        | 105 |

|---|------------|---------------------------------------------------------------------------------------------------------------|-----|

| 5 | I          | IPLEMENTATION OF THE LOGARITHMIC TRANSFER STABILIZATION METHOD                                                | 106 |

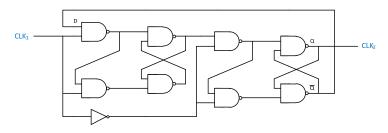

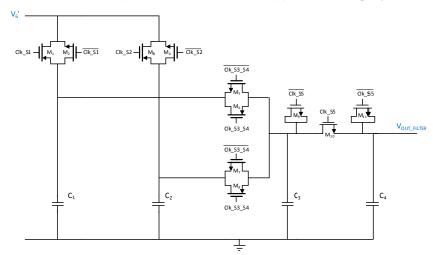

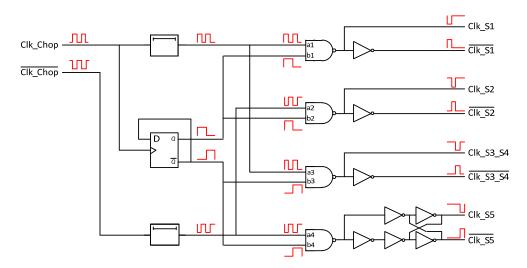

|   | 5.1        | CLOCK CIRCUITRY                                                                                               | 106 |

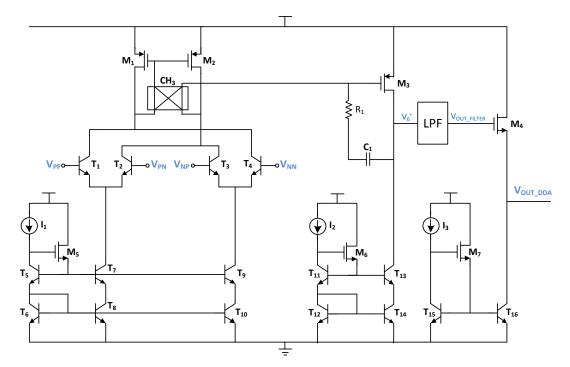

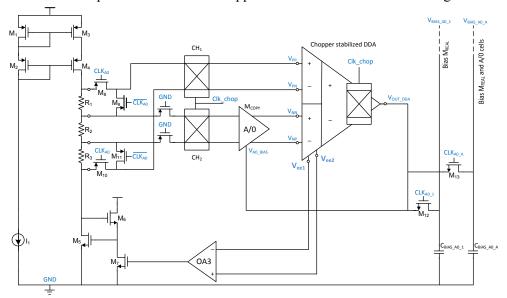

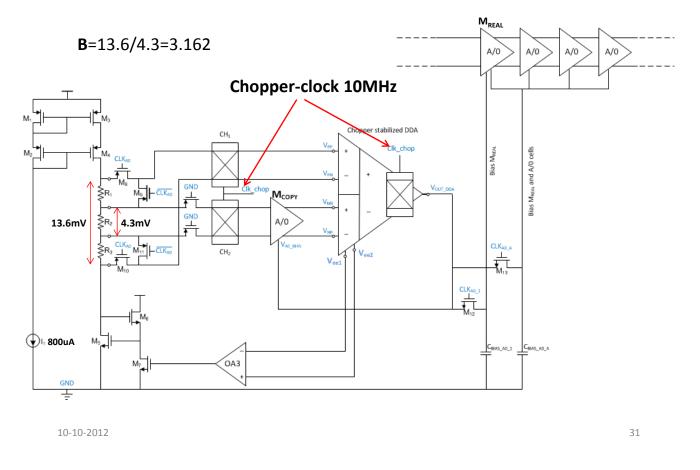

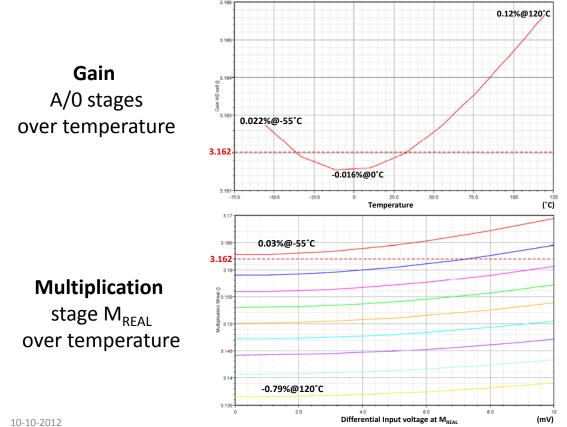

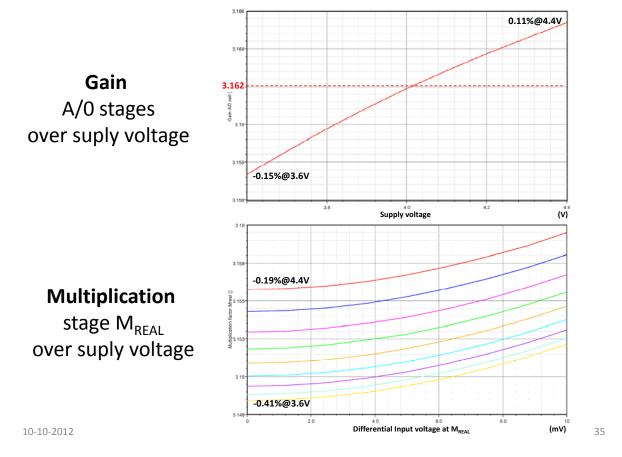

|   | 5.2        | MULTIPLICATION/GAIN FIXING CIRCUITRY                                                                          | 107 |

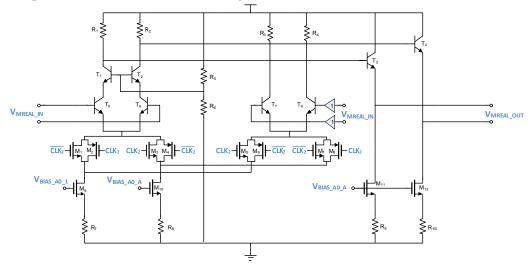

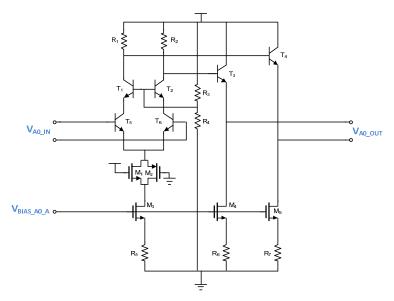

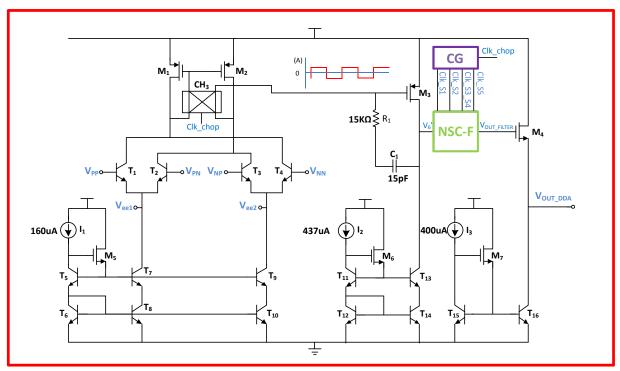

|   | 5.         | 2.1 The multiplication cell (A/0 cell)                                                                        |     |

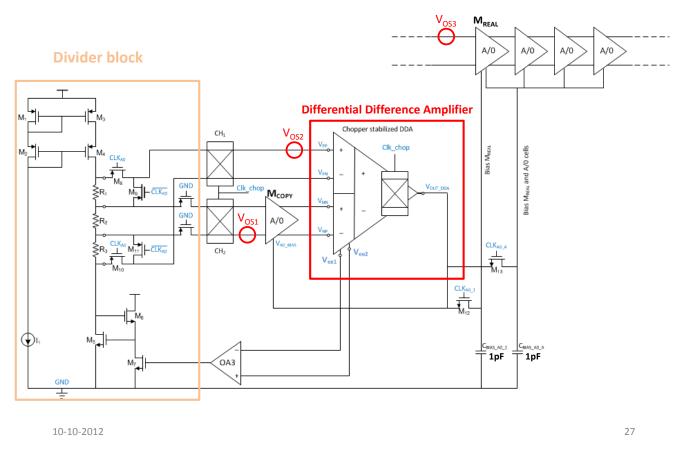

|   | 5.         | 2.2 The divider block                                                                                         |     |

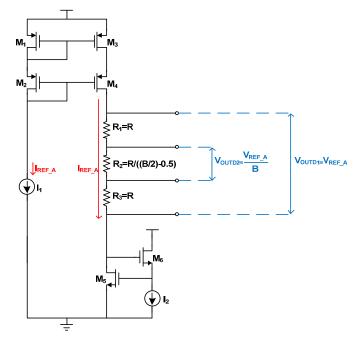

|   |            | 5.2.2.1 Circuit implementation                                                                                | 109 |

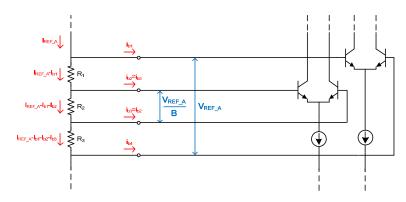

|   |            | 5.2.2.1.1 The resistive ladder                                                                                | 109 |

|   |            | 5.2.2.1.2 The reference current                                                                               |     |

|   |            | 5.2.2.1.3 Common mode range bias                                                                              |     |

|   |            | 5.2.2.2 Loading effect                                                                                        |     |

|   | 5          | 2.3 The error amplifier                                                                                       |     |

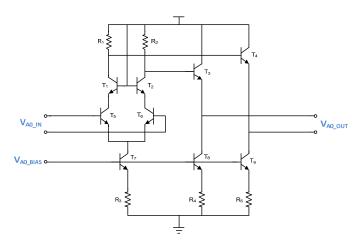

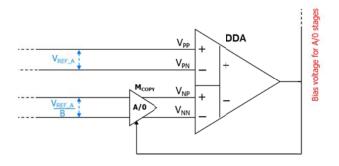

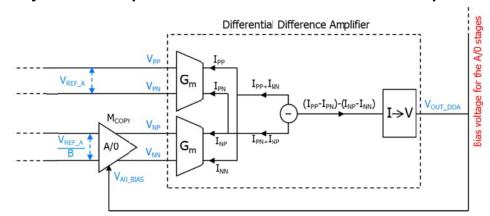

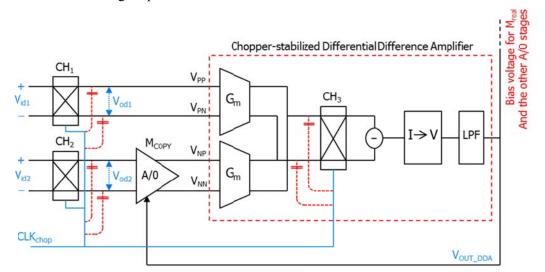

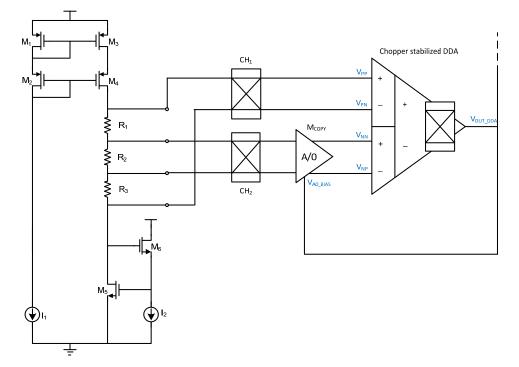

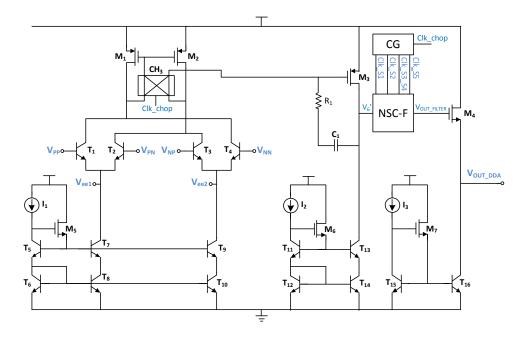

|   | 5.         | 5.2.3.1 The DDA used as error amplifier                                                                       |     |

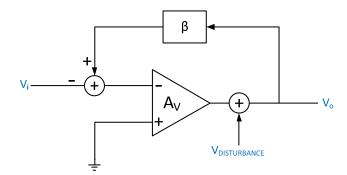

|   |            | 5.2.3.2 System level operation of the DDA in the feedback loop                                                |     |

|   |            | 5.2.3.2.1 Loop gain of the feedback configuration                                                             |     |

|   |            | 5.2.3.3 The importance of matched input transconductance cells                                                |     |

|   |            | 5.2.3.4 CMRR of the DDA                                                                                       |     |

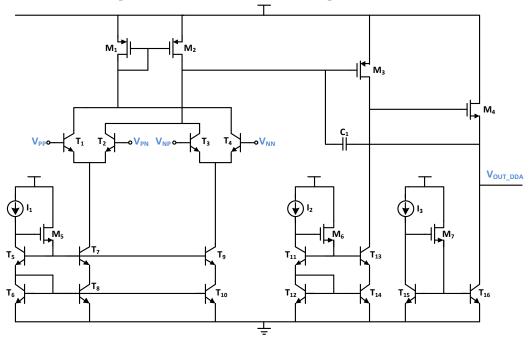

|   |            | 5.2.3.5 Circuit implementation of the DDA                                                                     |     |

|   |            | 5.2.3.5.1 The differential input stages                                                                       |     |

|   |            | 5.2.3.5.2 The tail current sources<br>5.2.3.5.3 The Active load                                               |     |

|   |            | 5.2.3.5.4 The trans-impedance stage                                                                           |     |

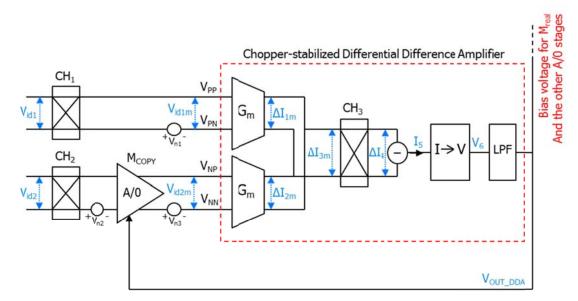

|   | 5          | 2.4 Reducing the sensitivity to non-idealities in the gain fixation system                                    |     |

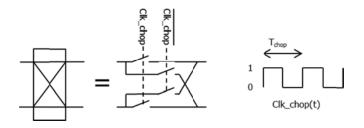

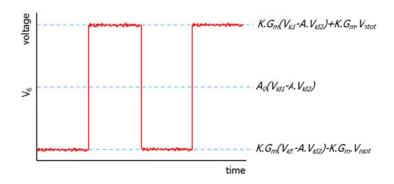

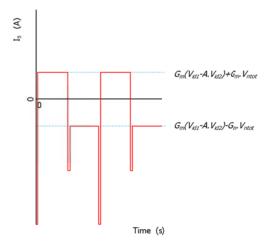

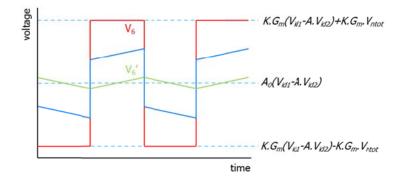

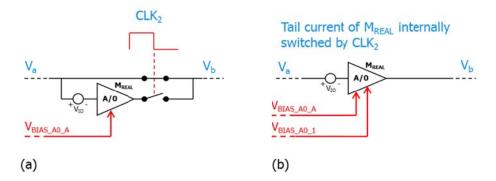

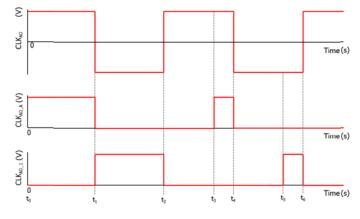

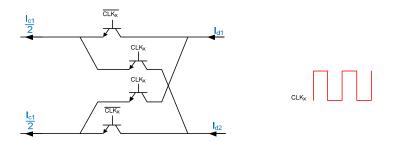

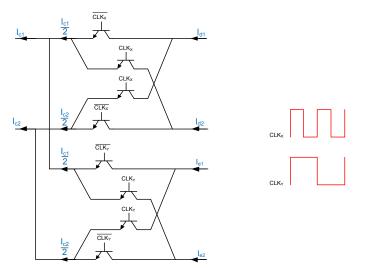

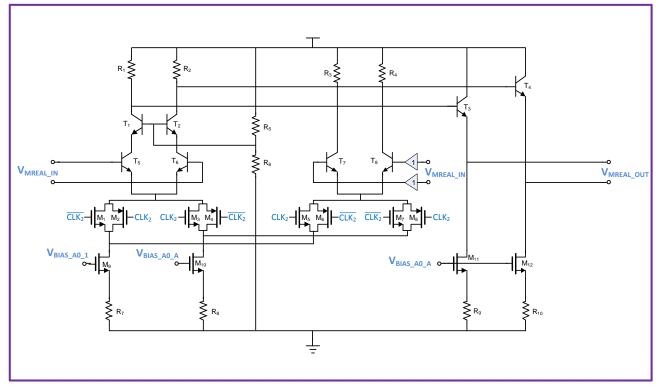

|   |            | 5.2.4.1 Chopping to reduce offset in the gain fixation system                                                 |     |

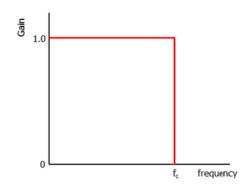

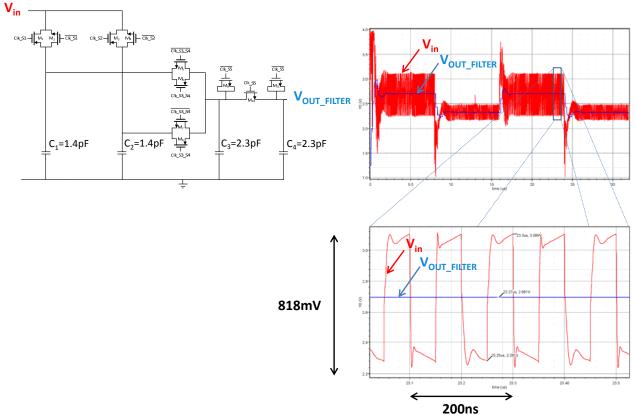

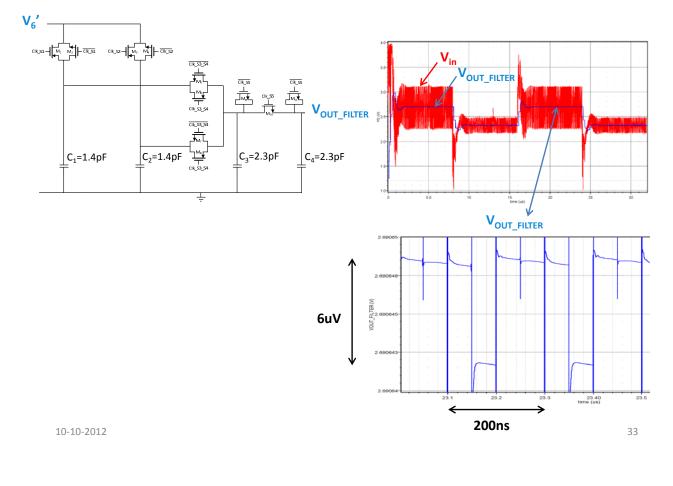

|   |            | 5.2.4.2 The low pass filter                                                                                   |     |

|   |            | 5.2.4.2.1 The ideal low pass filter                                                                           |     |

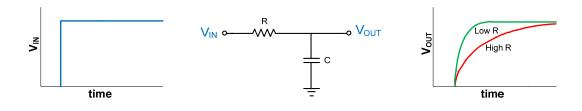

|   |            | 5.2.4.2.1.1 The Low pass RC filter                                                                            |     |

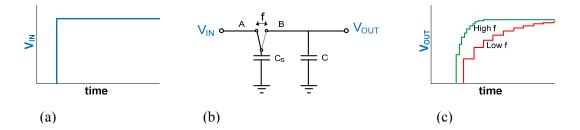

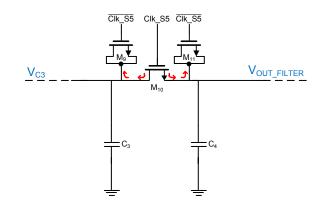

|   |            | 5.2.4.2.1.2 Switched capacitor filter                                                                         |     |

|   |            | 5.2.4.3 Limitations and non-idealities of the chopping circuit                                                |     |

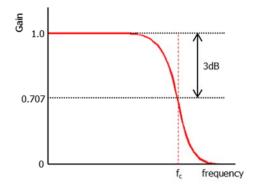

|   |            | 5.2.4.3.1 Limited bandwidth of the system                                                                     |     |

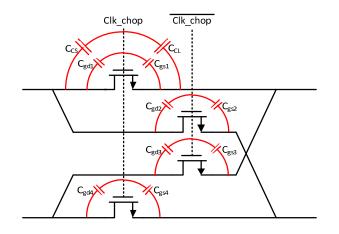

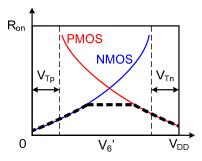

|   |            | 5.2.4.3.2 Residual offset caused by clock feed-trough<br>5.2.4.3.3 Non-idealities of MOS transistors switches |     |

|   | 5          | 5.2.4.3.3 Non-idealities of MOS transistors switches                                                          |     |

|   | 5.         | 5.2.5.1 Integrating trans-impedance amplifier                                                                 |     |

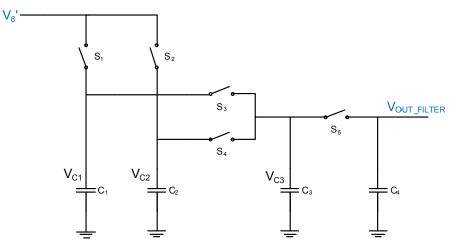

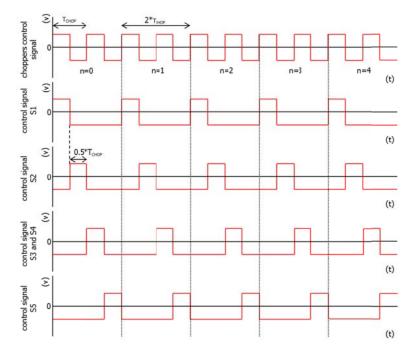

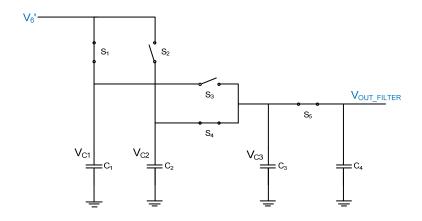

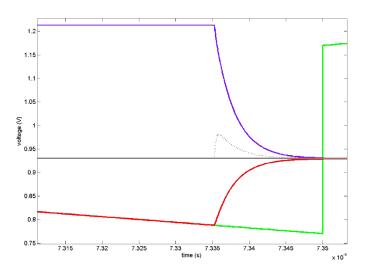

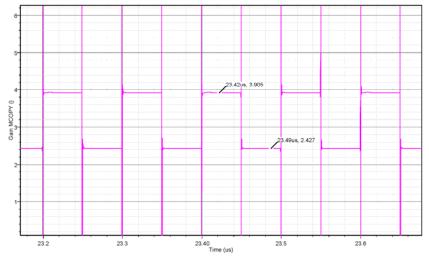

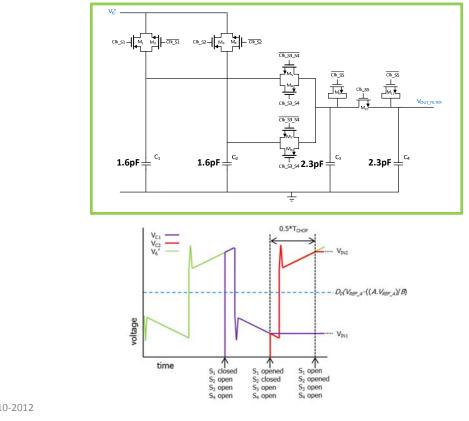

|   |            | 5.2.5.2 Novel output ripple blocking system for chopped systems                                               |     |

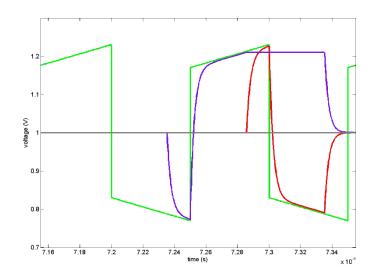

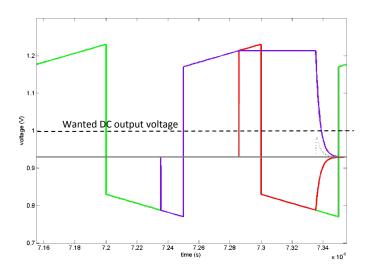

|   |            | 5.2.5.2.1 System level operation ripple blocking system                                                       |     |

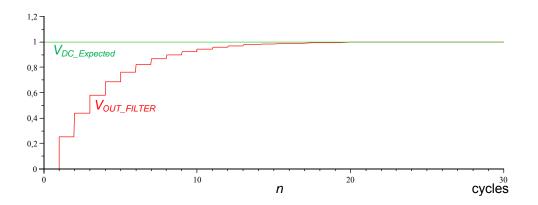

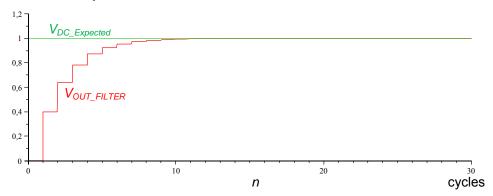

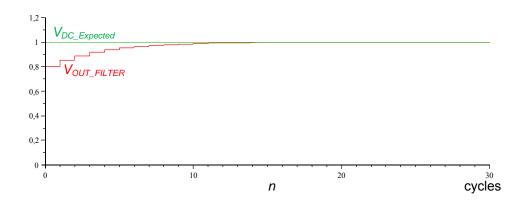

|   |            | 5.2.5.2.2 Response time                                                                                       |     |

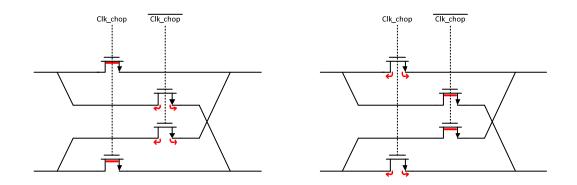

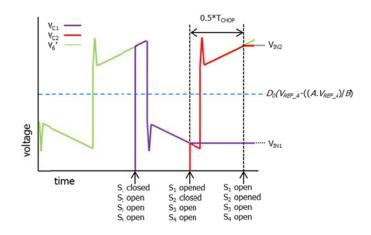

|   |            | 5.2.5.2.3 Insensitiveness to switching effects of the chopped system                                          |     |

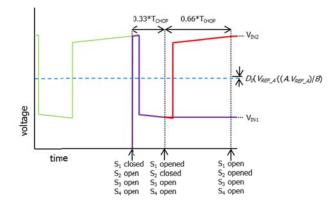

|   |            | 5.2.5.2.4 Low sensitiveness to duty cycle variations of chopper clock                                         |     |

|   |            | 5.2.5.2.5 A Power efficient and low noise approach                                                            |     |

|   |            | 5.2.5.2.6 Final circuit implementation of the ripple blocking system                                          |     |

|   |            | 5.2.5.2 Clock generator (CG) circuit for the notching switch capacitor filter                                 |     |

|   | 5          | 2.6 Final circuit implementation                                                                              |     |

|   | 5.         | 5.2.6.1 Input offset insensitive multiplication action method without switches in the RF path                 |     |

|   |            | 5.2.6.2 Automatic common mode input voltage adjustment circuit                                                |     |

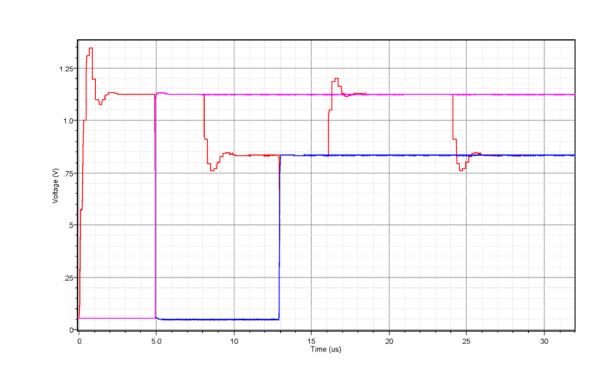

| 6 | S          | MULATION RESULTS                                                                                              |     |

| 7 |            | DNCLUSIONS                                                                                                    |     |

| 8 |            |                                                                                                               |     |

| 0 |            |                                                                                                               |     |

|   | 8.1<br>° 7 | PREVENTING HANG UP OF DETECTOR CONTROL SYSTEM                                                                 |     |

|   | 8.2        | CURRENT SPLITTING                                                                                             |     |

|   | 8.3<br>• • |                                                                                                               | -   |

|   | 8.4<br>° E | CURRENT SPLIT/COMMUTATING SWITCHES                                                                            |     |

|   | 8.5<br>8.6 | RIPPLE REDUCTION OF THE OUTPUT SIGNALS                                                                        |     |

|   | 8.6<br>8.7 | FULL CMOS IMPLEMENTATION                                                                                      |     |

|   | 8.7<br>。。  | NEW POWER GAIN CALCULATION ARCHITECTURE                                                                       |     |

|   | 8.8        | LINEAR GAIN STABILIZATION                                                                                     |     |

| 8.   | 9 Method  | TO EXTENDING THE DYNAMIC RANGE WHEN SLOPE IS FIXATION IS GUARANTEED | . 186 |

|------|-----------|---------------------------------------------------------------------|-------|

| APPE | NDIX A    | OVERALL ACCURACY ANALYSIS                                           | . 188 |

| APPE | NDIX B    | THE DETECTOR CELL                                                   | . 190 |

| 9    | ACKNOWL   | EDGEMENTS                                                           | . 192 |

| 10   | BIBLIOGRA | РНҮ                                                                 | . 194 |

## **Table of Figures**

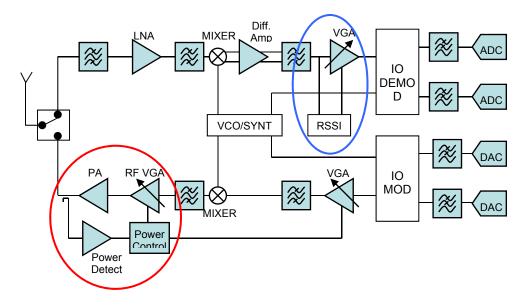

| Figure 1.1 Typical modern communications signal chain                                                                                                                                             | 17   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

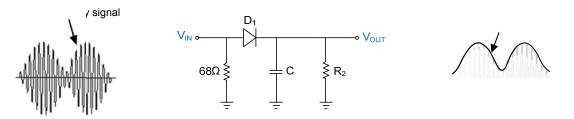

| Figure 1.2 Diode detector                                                                                                                                                                         | . 20 |

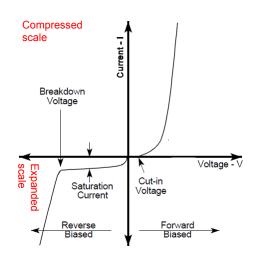

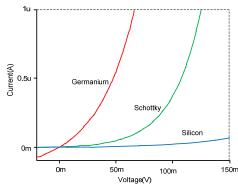

| Figure 1.3 I-V characteristic of a diode with some scales expanded and others compressed in order to reveal details.                                                                              |      |

| Figure 1.4 I-V characteristic of a different type of diodes                                                                                                                                       |      |

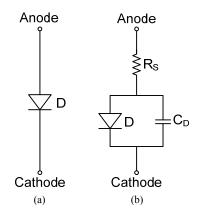

| Figure 1.5 The (a) ideal diode and (b) the more realistic diode model                                                                                                                             |      |

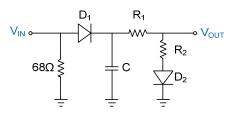

| Figure 1.6 A temperature compensated diode detector                                                                                                                                               |      |

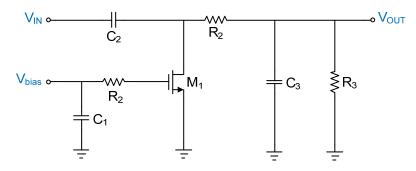

| Figure 1.7 A power detector with one FET                                                                                                                                                          |      |

| Figure 1.8 Thermal based approach with thermal detectors                                                                                                                                          |      |

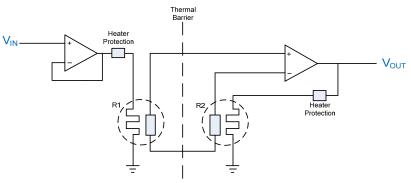

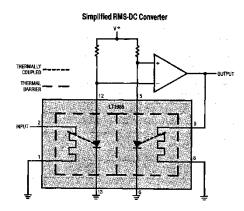

| Figure 1.9 Integrated thermal detection method [25]                                                                                                                                               |      |

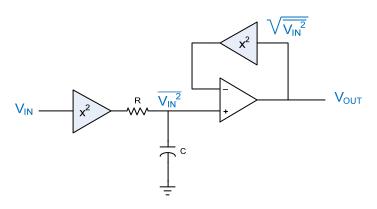

| Figure 1.10 Computation method used in explicit RMS detectors                                                                                                                                     |      |

| Figure 1.11 Computation method used in implicit RMS detectors                                                                                                                                     |      |

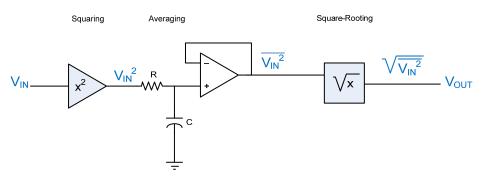

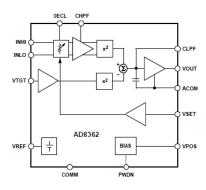

| Figure 1.12 RMS responding detector                                                                                                                                                               |      |

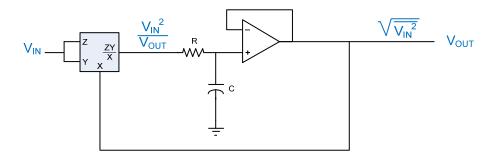

| Figure 1.13 RMS responding detector with a linear-in-dB characteristic                                                                                                                            | 29   |

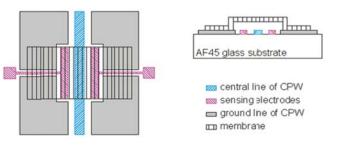

| Figure 1.14 RF Power sensor based on capacitive detection                                                                                                                                         |      |

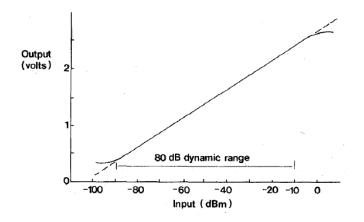

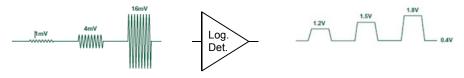

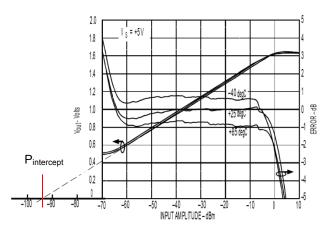

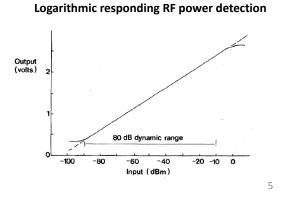

| Figure 1.15 Log Detector input/output transfer [31]                                                                                                                                               |      |

| Figure 1.16 Input burst and their associated log output [32]                                                                                                                                      | 30   |

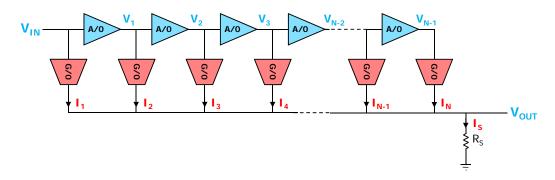

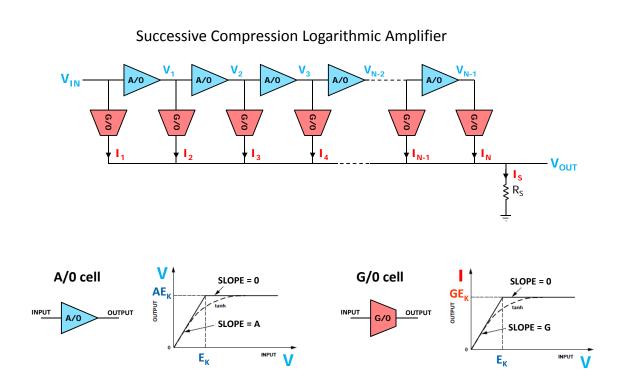

| Figure 1.17 Simplified architecture of a successive approximation logarithmic detector                                                                                                            | 31   |

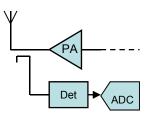

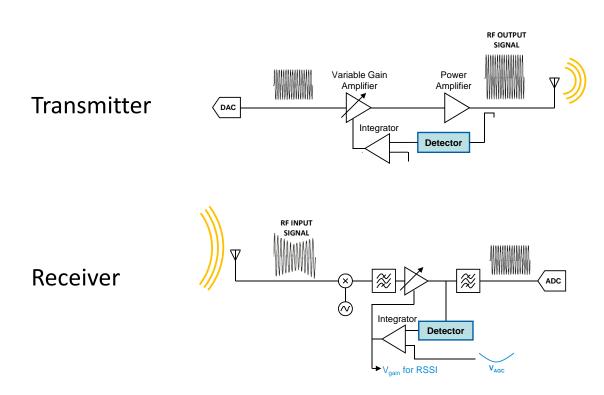

| Figure 1.18 Detector used for the power measurement at the output of a power amplifier                                                                                                            |      |

| Figure 1.19 Dynamic power control                                                                                                                                                                 |      |

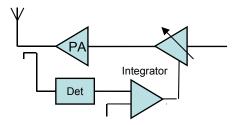

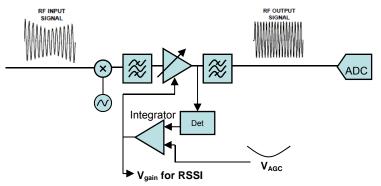

| Figure 1.20 Power detector used as part of automatic gain control to maintain a constant signal at ADC                                                                                            |      |

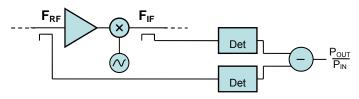

| Figure 1.20 Power gain calculation circuit                                                                                                                                                        |      |

| Figure 1.22 Voltage standing-wave ratio (VSWR) measurement                                                                                                                                        |      |

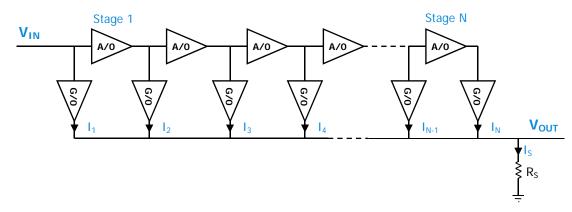

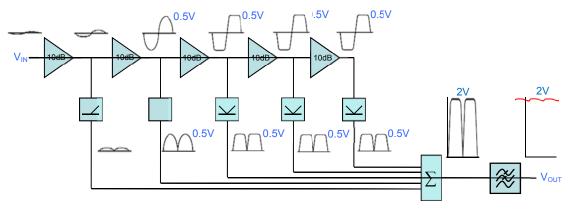

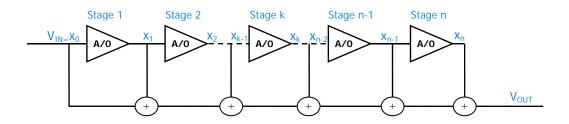

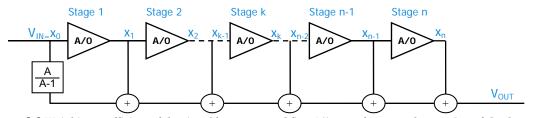

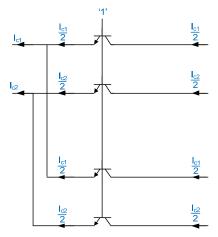

| Figure 2.2 Voltage standing-wave ratio (VSWR) measurement<br>Figure 2.1 Block Diagram of the Successive Approximation log detector                                                                |      |

|                                                                                                                                                                                                   |      |

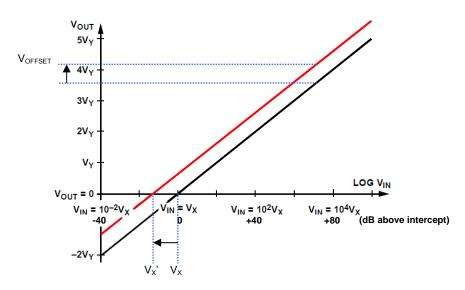

| Figure 2.2 Idealized response of a logarithmic detector. Adding an offset voltage to the output will lower the effective                                                                          | ?    |

| intercept voltage.                                                                                                                                                                                |      |

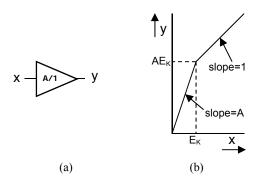

| Figure 2.3 (a) The symbol of the A/1 cell and (b) the transfer function of a A/1 cell                                                                                                             |      |

| Figure 2.4 An n-cell cascade built with A/1 cells                                                                                                                                                 |      |

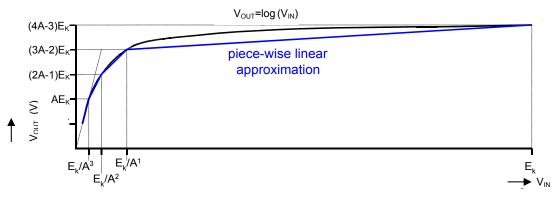

| Figure 2.5 Piece-wise linear approximation of a logarithmic transfer                                                                                                                              |      |

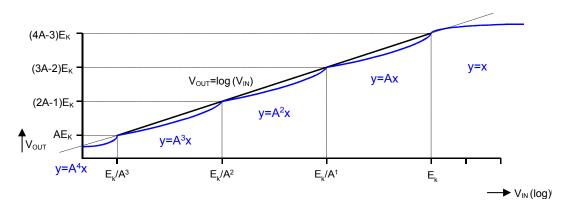

| Figure 2.6 Piece-wise linear approximation for logarithmic representation of $V_{IN}$                                                                                                             |      |

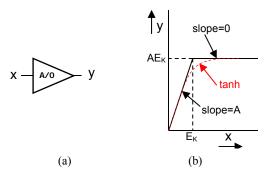

| Figure 2.7 (a) The symbol of the A/0 cell and (b) the transfer function of a A/0 cell                                                                                                             |      |

| Figure 2.8 Logarithmic approximation by summing the outputs of all of the stages                                                                                                                  | 47   |

| Figure 2.9 Weighing coefficient of the signal bypass around first A/0 stage for top-end correction of the dynamic range                                                                           |      |

|                                                                                                                                                                                                   |      |

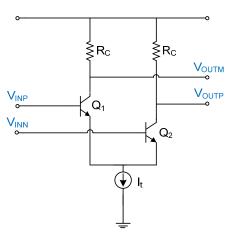

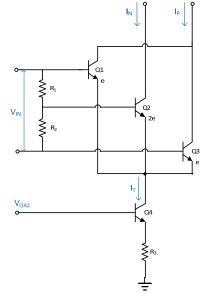

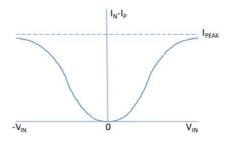

| Figure 2.10 Differential amplifier is used as A/0 cell                                                                                                                                            |      |

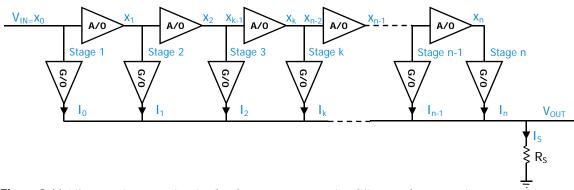

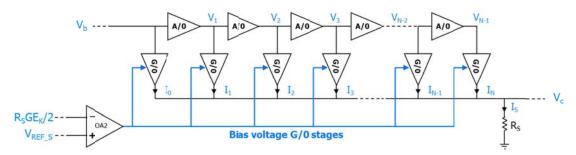

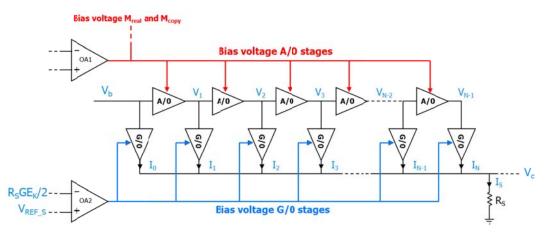

| Figure 2.11 A/O successive approximation log detector structure using G/O stages for summation                                                                                                    |      |

| Figure 2.12 Example of a practical log detector transfer [34] [42] [45]                                                                                                                           |      |

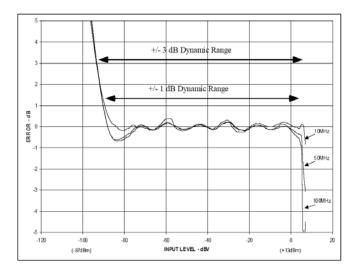

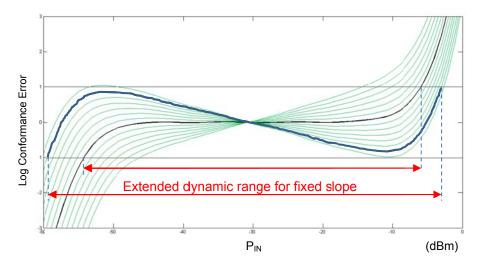

| Figure 2.13 Log Conformance example shows a dynamic range of approximately 95 dB for a log linearity of +/- 1dE [42]                                                                              |      |

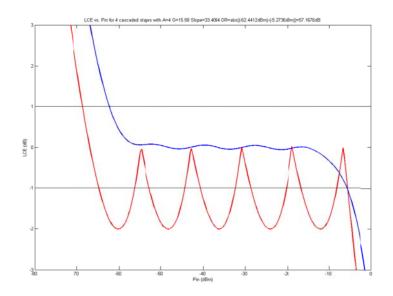

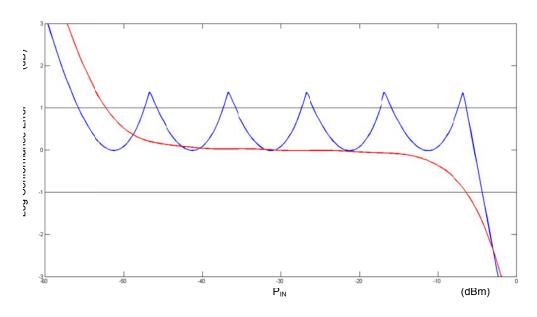

| Figure 2.14 Log conformance using A/0 cells (red curve) and tanh cells (blue curve)                                                                                                               |      |

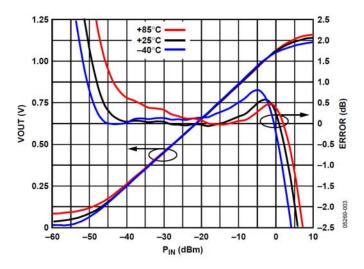

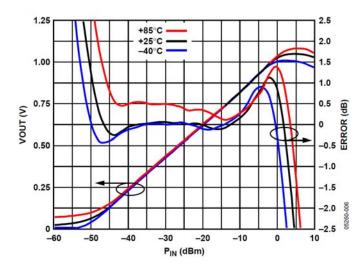

| Figure 2.15 Response of a logarithmic detector at a temperature of -40°C, 25°C and +85°C [48]                                                                                                     |      |

| Figure 2.16 Response of the logarithmic detector at a temperature of $-40^{\circ}$ C, 25°C and $+85^{\circ}$ C at higher frequency in                                                             |      |

| signal [48]                                                                                                                                                                                       |      |

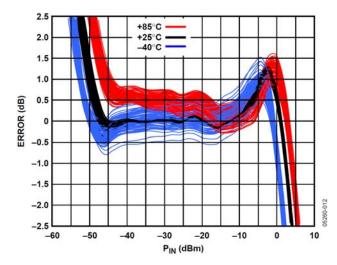

| Figure 2.17 Distribution of logarithmic conformance error curves of 80 individually calibrated log detectors. [48]                                                                                |      |

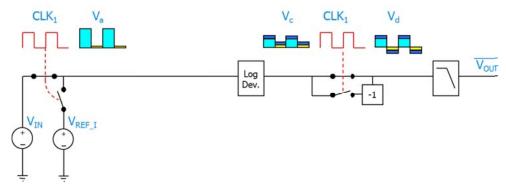

| Figure 3.1 System of the intercept fixation method                                                                                                                                                |      |

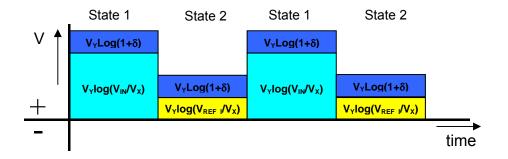

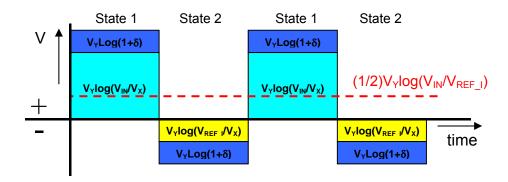

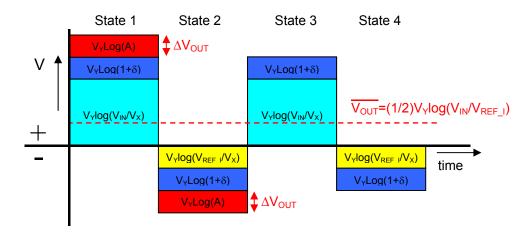

| Figure 3.2 Signal $V_c$ seen at output of logarithmic device                                                                                                                                      |      |

| Figure 3.3 Signal $V_d$ seen at output of the inverting switch                                                                                                                                    |      |

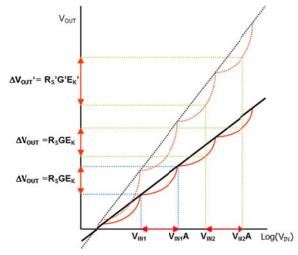

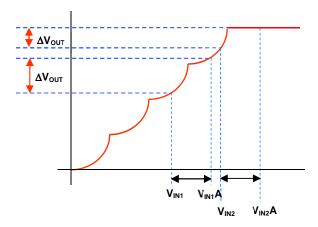

| Figure 3.4 The output change, $\Delta V_{OUT}$ , in response to an accurately known input multiplication, A, depends on the slo                                                                   |      |

| of the transfer                                                                                                                                                                                   | -    |

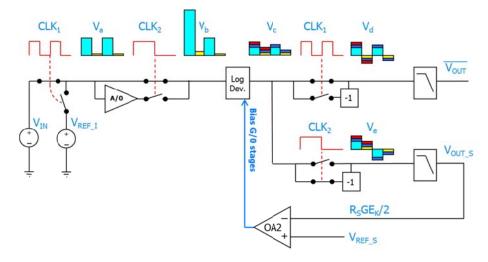

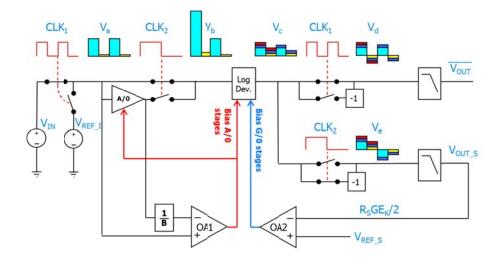

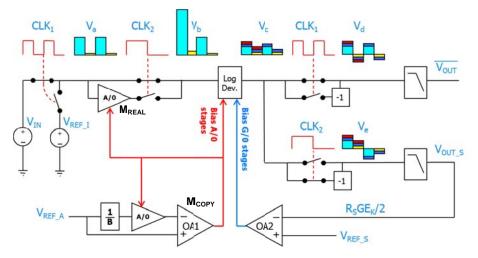

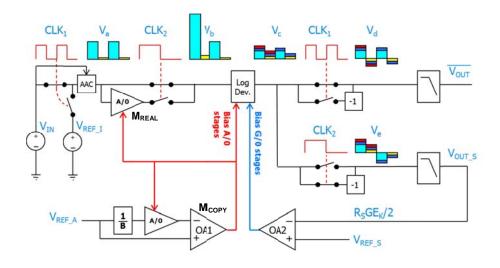

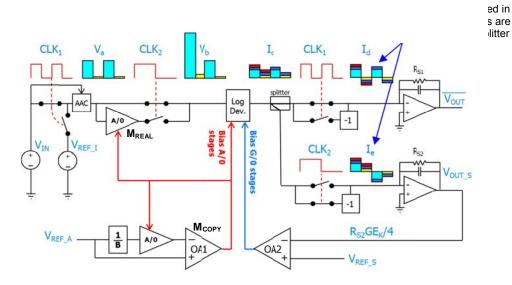

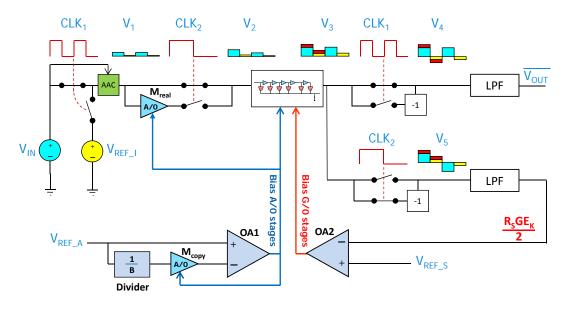

| Figure 3.5 System including intercept and slope fixation method                                                                                                                                   |      |

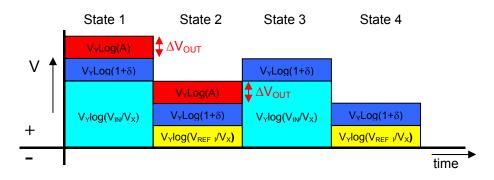

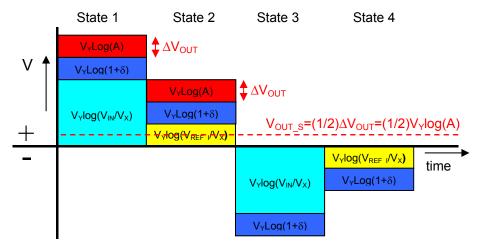

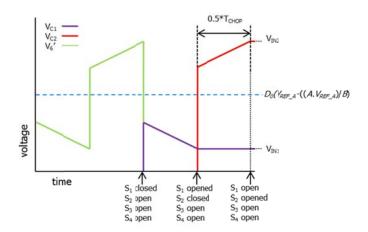

| Figure 3.6 Signal $V_c$ seen at the output of the logarithmic device                                                                                                                              |      |

| Figure 3.7 Signal $V_c$ seen at the output of the inverting switch                                                                                                                                |      |

| Figure 3.8 Signal $V_e$ seen at the output of the inverting switch                                                                                                                                |      |

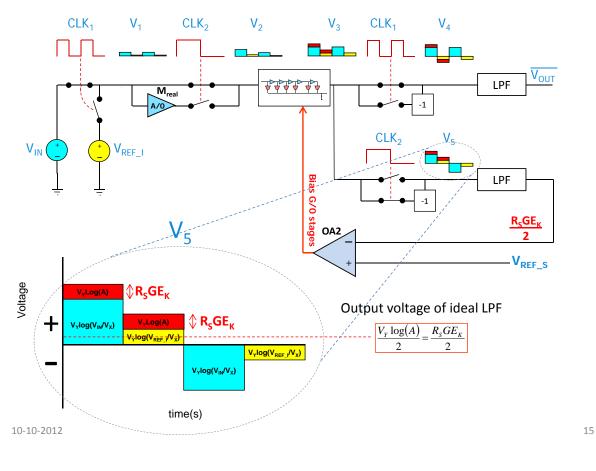

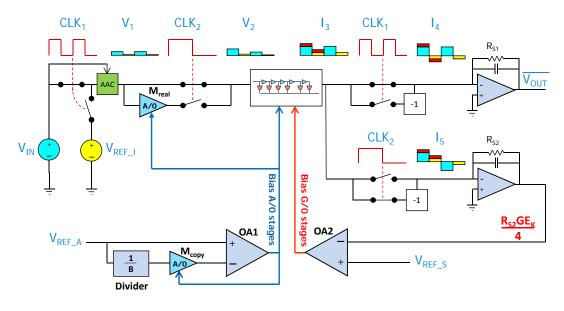

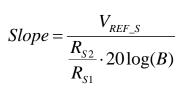

| Figure 3.9 G/0 cells are biased with output signal of error amplifier OA2                                                                                                                         |      |

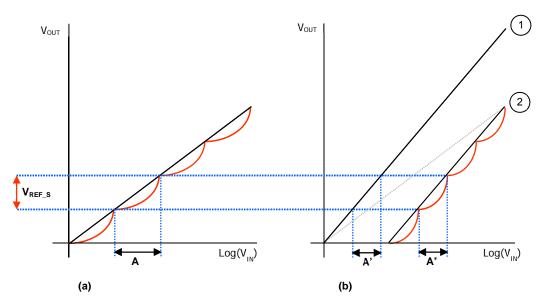

| Figure 3.9 G/0 certs are blased with output signal of error amplifier OA2<br>Figure 3.10 Feedback loop sets (a) correct slope for correct multiplication factor (b2) incorrect slope for deviated | 09   |

| multiplication factor and gain of A/0 stages.                                                                                                                                                     | 70   |

|                                                                                                                                                                                                   |      |

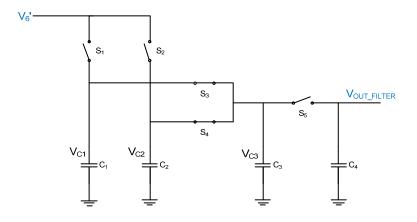

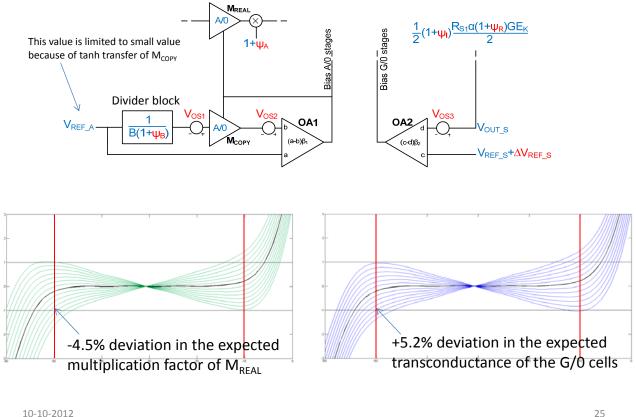

| Figure 3.11 Slope fixation system including the multiplication fixation system                                                                                                                    |      |

| Figure 3.12 The complete biasing structure of the logarithmic device                                                                                                                              |      |

| Figure 3.13 Feeding a DC reference voltage to a copy of the multiplication cell can lower the offset dependence                                                                                   |      |

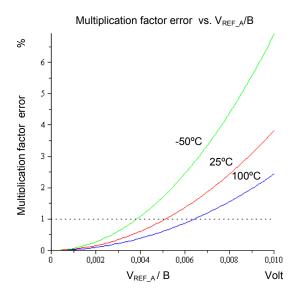

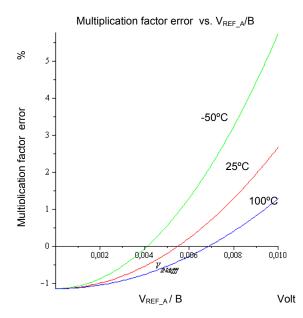

| Figure 3.14 The error in percentage of the multiplication factor vs. the normalized input voltage $V_{REF_{-A}}/B$                                                                                | 15   |

| Figure 3.15 The error in percentage of the multiplication factor with correction of 1.15% in B vs. the normalized in voltage $V_{REF A}/B$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

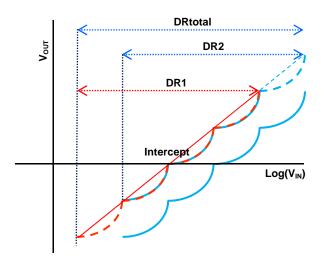

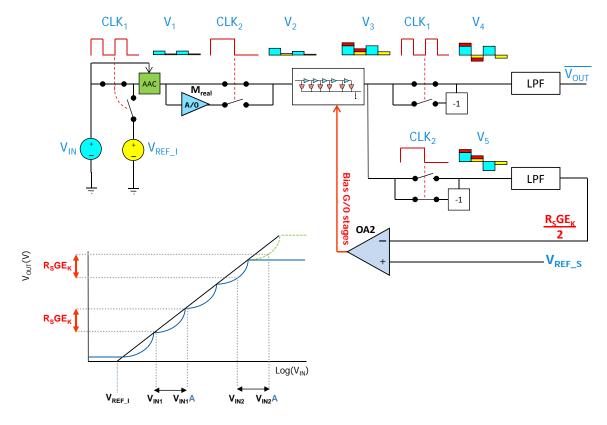

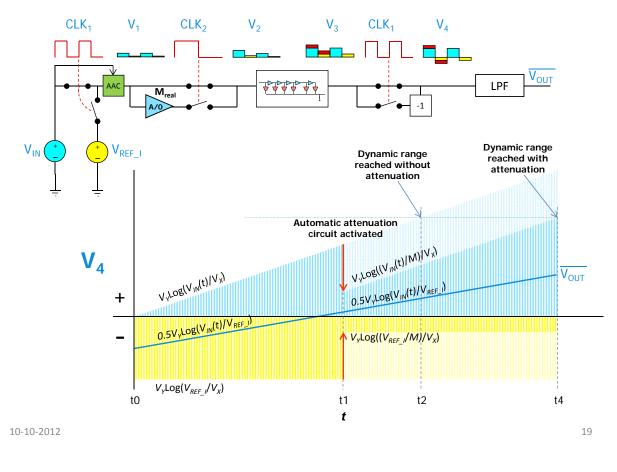

| Figure 3.16 Automatic Attenuating Control (AAC) circuit lowers large signal effect and extends the dynamic range the logarithmic device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | of          |

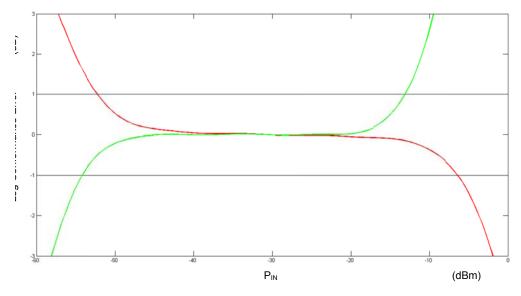

| Figure 3.17 Attenuation by ACC will result in a decrease of $log(V_{REF_{L}})$ (red) and $log(V_{IN})$ (green) by same amount.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Due         |

| to filtering with a relative high time constant the effect on $V_{OUT}$ will be negligible<br>Figure 3.18 Dynamic range shift when attenuation with value of A is used. Dynamic range in higher range will be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78          |

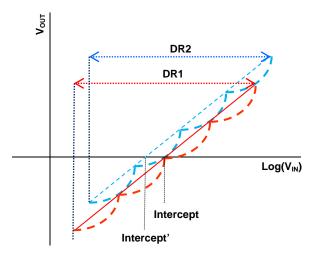

| extended by a factor A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| Figure 3.19 Interruption of transfer will occur when attenuation with value different than A is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

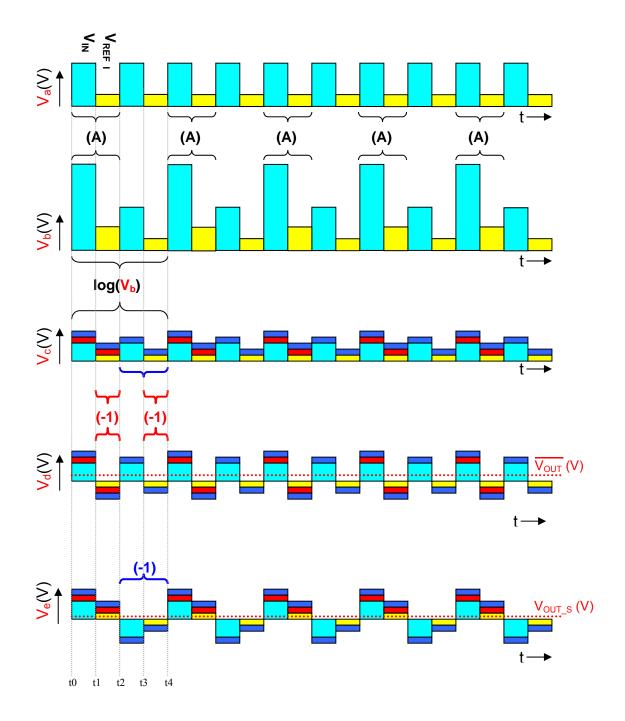

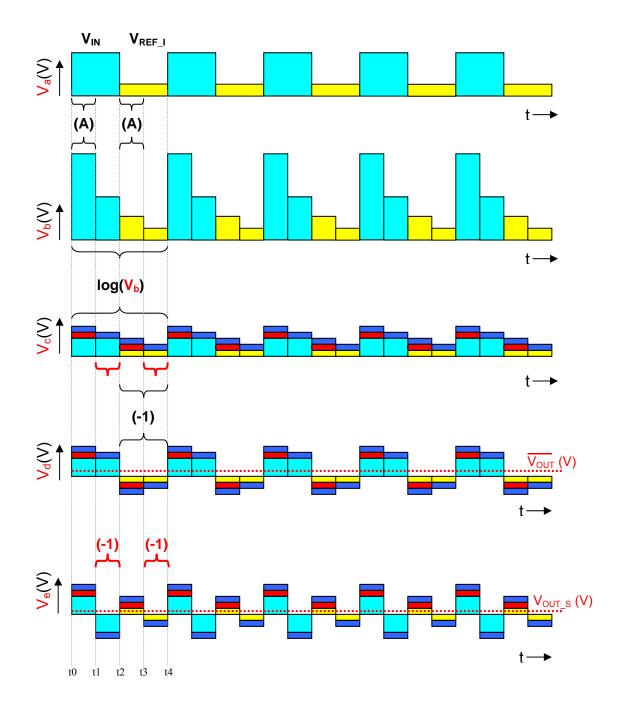

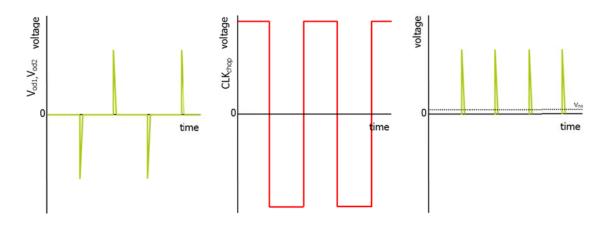

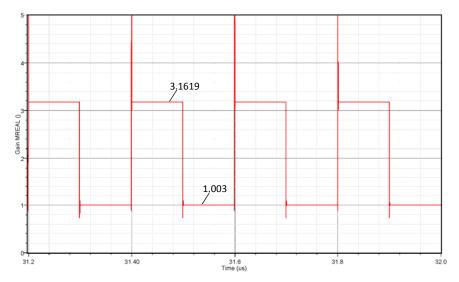

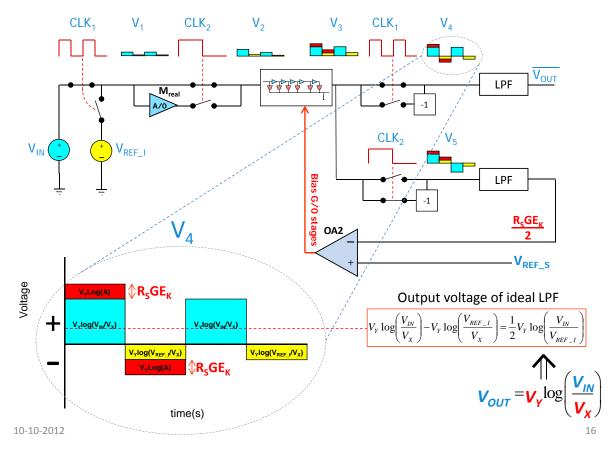

| Figure 3.20 Overview of signalling of the overall intercept and slope fixation method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

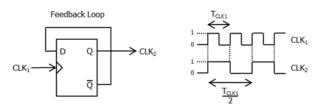

| Figure 3.21 When clock frequency $CLK_1$ and $CLK_2$ are exchanged, the values of the states between t1 and t3 of sig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| $V_e$ will exchange<br>Figure 3.22 Low-pass filters realized using an op-amp based integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

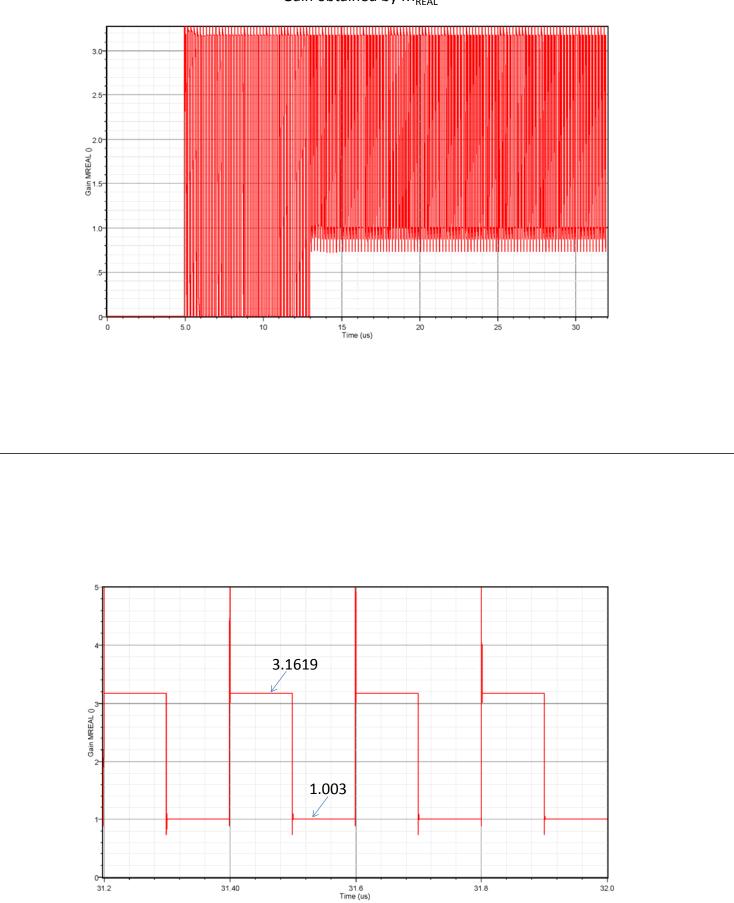

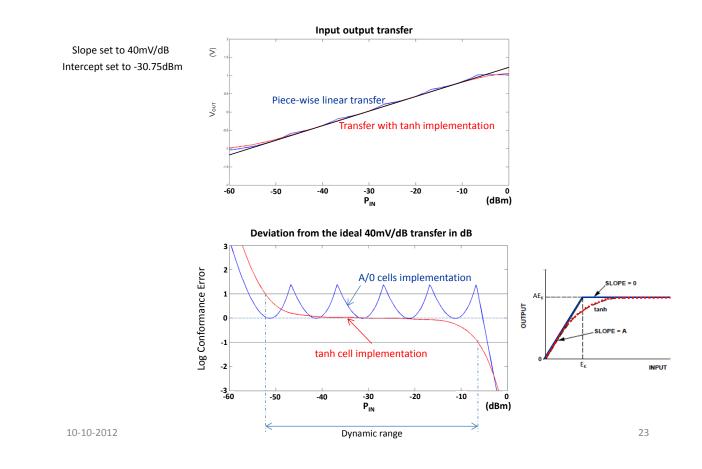

| Figure 4.1 Piece-wise linear log transfer (blue curve) with a slope of 40 mV/dB generated by a cascade of four idea $A/0$ cells each having a gain of 10 dB and the log transfer (red curve) when ideal $A/0$ cells are replaced by tanh ce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | al<br>ell's |

| Figure 4.2 Log Conformance Error for the log device implemented with the ideal A/0 cells (blue curve) and the Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |

| Conformance Error for the log device implemented with tanh cells (red curve).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

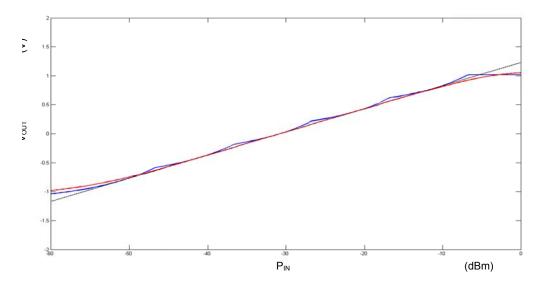

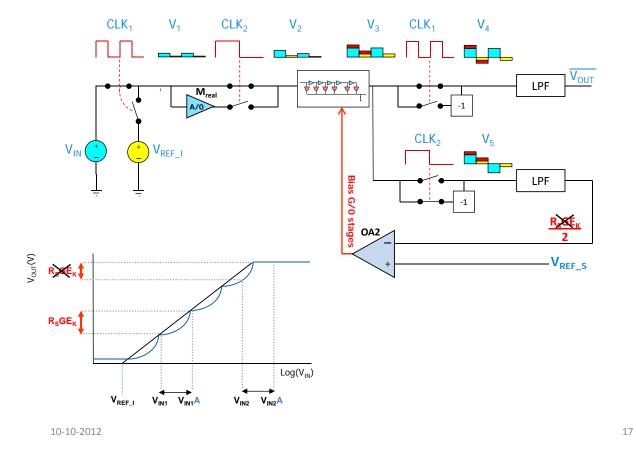

| Figure 4.3 Transfer of the slope and intercept fixated logarithmic device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| Figure 4.4 Smaller than expected output change caused by upper limit of dynamic range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91          |

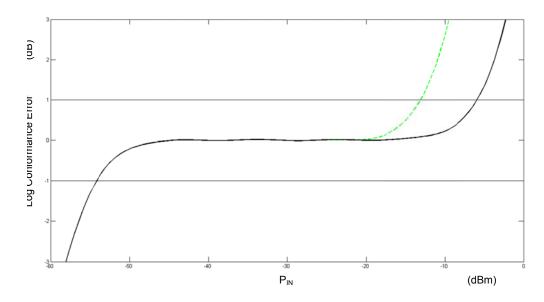

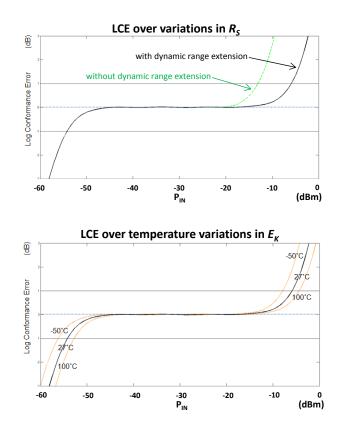

| Figure 4.5 Dynamic range extension obtained by the proposed AAC method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91          |

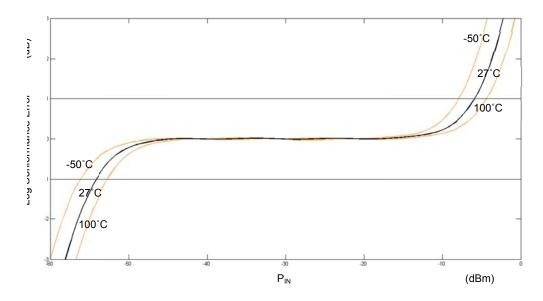

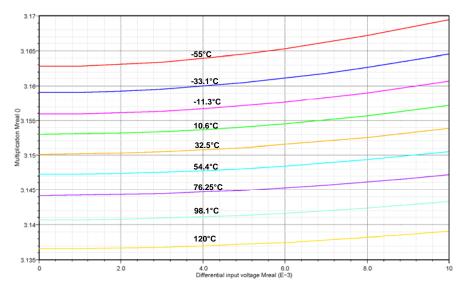

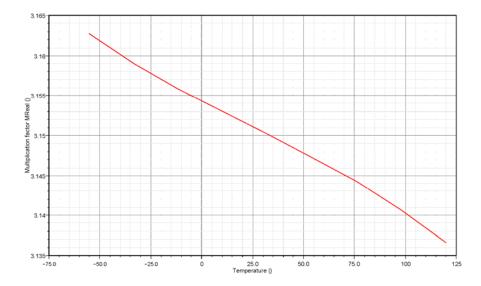

| Figure 4.6 Log conformance error deviation over temperature change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

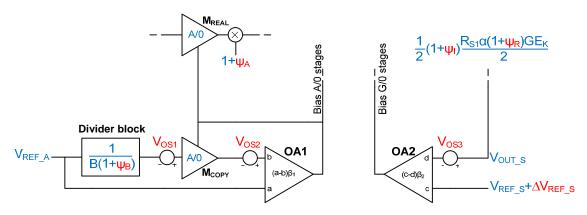

| Figure 4.7 Slope fixation system part including non-idealities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

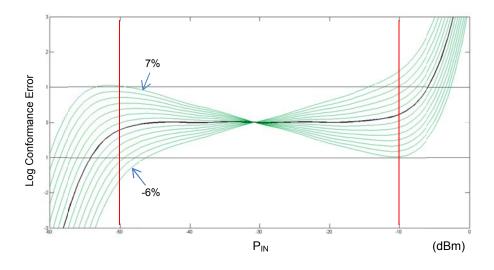

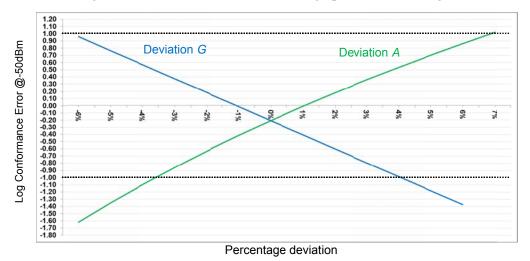

| Figure 4.8 Deviation of log conformance caused by a -6% to 7% change in the multiplication factor A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 95          |

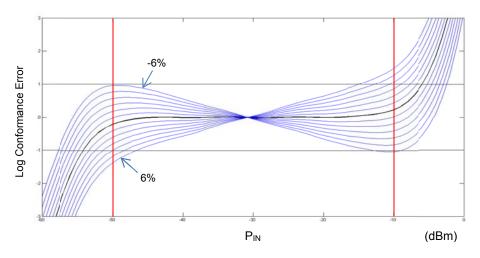

| Figure 4.9 Deviation of log conformance caused by a -6% to 6% change in transconductance G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 95          |

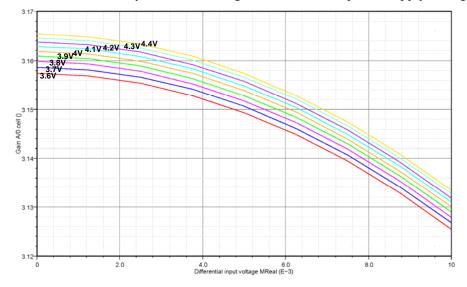

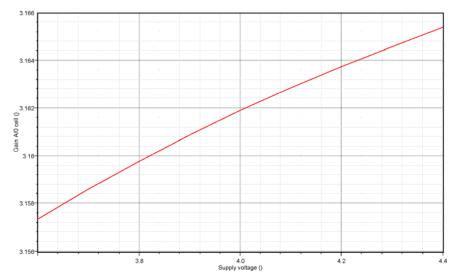

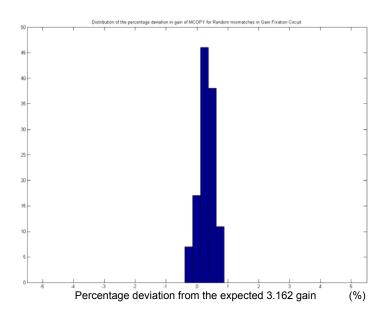

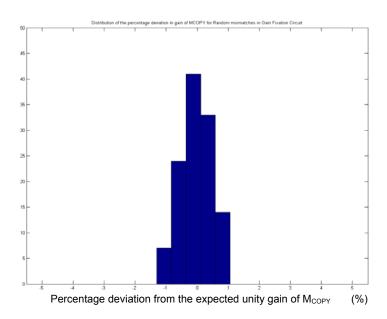

| Figure 4.10 Log conformance @-50dBm, for deviations in multiplication factor A (green line) and transconductane (blue line)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |