# **Analog Signal Processing for CMOS Image Sensors**

Snoeij, MF

**Publication date**

**Document Version** Final published version

**Citation (APA)**Snoeij, MF. (2007). *Analog Signal Processing for CMOS Image Sensors*. [Dissertation (TU Delft), Delft University of Technology].

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# ANALOG SIGNAL PROCESSING FOR CMOS IMAGE SENSORS

# ANALOG SIGNAL PROCESSING FOR CMOS IMAGE SENSORS

### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft op gezag van de Rector Magnificus Prof.dr.ir. J.T. Fokkema, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 4 september 2007 om 15:00 uur.

door

Martijn Fridus SNOEIJ

elektrotechnisch ingenieur geboren te Zaanstad

## Dit proefschrift is goedgekeurd door de promotoren:

Prof. dr. ir. A.J.P. Theuwissen Prof. dr. ir. J.H. Huijsing

### Samenstelling promotiecommissie:

Rector Magnificus voorzitter

Prof. dr. ir. A.J.P. Theuwissen Technische Universiteit Delft, promotor Prof. dr. ir. J.H. Huijsing Technische Universiteit Delft, promotor

Prof. dr. ir. G.C.M. Meijer Technische Universiteit Delft

Prof. ir. A.J.M. van Tuijl Universiteit Twente

Prof. dr. B.J. Hosticka Fraunhofer IMS Duisburg, Duitsland

Dr. J.E.D. Hurwitz Gigle Semiconductor, UK

Dr. J. Solhusvik Micron Technology Inc., Noorwegen

Reservelid:

Prof. dr. P.J. French Technische Universiteit Delft

Printed by PrintPartners Ipskamp, Enschede

ISBN: 978-90-9022129-8

Copyright © 2007 by M.F. Snoeij

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the author.

PRINTED IN THE NETHERLANDS

# Table of Contents

| 1. | Introduction                                                  | 1  |

|----|---------------------------------------------------------------|----|

|    | 1.1 History of Electronic Image Sensors                       | 2  |

|    | 1.2 Challenges                                                | 4  |

|    | 1.3 Motivation and Objectives                                 | 8  |

|    | 1.4 Organization of the Thesis                                | 9  |

|    | 1.5 References                                                | 10 |

| 2. | <b>CMOS Imager Analog Signal Processing at a Glance</b>       | 13 |

|    | 2.1 Architectural Overview of CMOS Image Sensors              | 13 |

|    | 2.2 Photosensitive Elements                                   | 16 |

|    | 2.2.1 Photodiodes                                             | 16 |

|    | 2.2.2 Photogates                                              | 20 |

|    | 2.2.3 Pinned Photodiodes                                      | 22 |

|    | 2.3 Front-End Analog Signal Processing                        |    |

|    | 2.3.1 Photodiode Front-End Readout Structure                  | 23 |

|    | 2.3.2 Photogate/Pinned Photodiode Front-End Readout Structure | 25 |

|    | 2.4 Back-End Analog Signal Processing                         | 27 |

|    | 2.4.1 Column Circuit Readout                                  | 27 |

|    | 2.4.2 Chip-Level A/D Conversion                               | 29 |

|    | 2.5 Advanced Analog Signal Processing Techniques              | 30 |

|    | 2.5.1 Sharing of Readout Circuitry Among Pixels               | 30 |

|    | 2.5.2 kT/C Noise Reduction through Soft and Active Reset      | 33 |

|    | 2.5.3 High Dynamic Range Readout                              | 34 |

|    | 2.5.4 Column-Level and Pixel-Level A/D Conversion             |    |

|    | 2.6 References                                                | 37 |

| 3. | Front-End Readout Circuitry                                   | 41 |

|    | 3.1 Front-End Readout Circuit Performance                     | 42 |

|    | 3.1.1 Signal Swing                                            | 42 |

|    |                                                               |    |

|    |     | 3.1.2 Linearity                                                                                                                                                                                                                                                        | . 45                                                                 |

|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|    |     | 3.1.3 Fixed Pattern Noise                                                                                                                                                                                                                                              | . 47                                                                 |

|    |     | 3.1.4 Power Consumption                                                                                                                                                                                                                                                | . 49                                                                 |

|    | 3.2 | Front-End Temporal Noise Sources                                                                                                                                                                                                                                       | . 50                                                                 |

|    |     | 3.2.1 Photon Shot Noise                                                                                                                                                                                                                                                | . 50                                                                 |

|    |     | 3.2.2 Reset Noise                                                                                                                                                                                                                                                      | . 52                                                                 |

|    |     | 3.2.3 Thermal Noise                                                                                                                                                                                                                                                    | . 52                                                                 |

|    |     | 3.2.4 1/f Noise                                                                                                                                                                                                                                                        | . 53                                                                 |

|    |     | 3.2.5 Comparison of Noise Sources                                                                                                                                                                                                                                      | . 56                                                                 |

|    | 3.3 | 1/f Noise Reduction Using Large-Signal Excitation (LSE)                                                                                                                                                                                                                | . 57                                                                 |

|    |     | 3.3.1 1/f Noise in Deep-Submicron MOS Transistors                                                                                                                                                                                                                      | . 57                                                                 |

|    |     | 3.3.2 LF Noise Reduction using Large-Signal Excitation (LSE)                                                                                                                                                                                                           | . 60                                                                 |

|    |     | 3.3.3 Application of LSE inside a CMOS Imager Front-End                                                                                                                                                                                                                | . 62                                                                 |

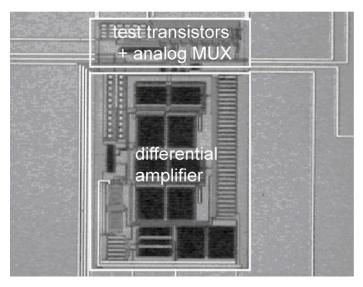

|    | 3.4 | LF Noise Measurements under Large Signal Excitation                                                                                                                                                                                                                    | . 64                                                                 |

|    |     | 3.4.1 Measurement IC                                                                                                                                                                                                                                                   | . 64                                                                 |

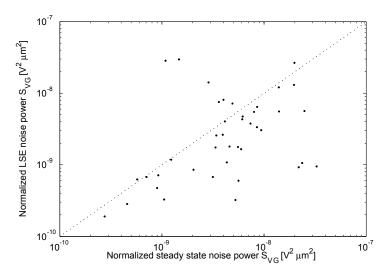

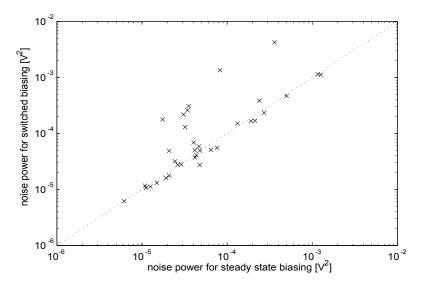

|    |     | 3.4.2 Measurement Results                                                                                                                                                                                                                                              | . 66                                                                 |

|    | 3.5 | Conclusion                                                                                                                                                                                                                                                             | . 69                                                                 |

|    | 3.6 | References                                                                                                                                                                                                                                                             | . 70                                                                 |

|    |     |                                                                                                                                                                                                                                                                        |                                                                      |

| 4. | Co  | olumn-Level Analog-to-Digital Conversion                                                                                                                                                                                                                               | 73                                                                   |

| 4. |     | 0 0                                                                                                                                                                                                                                                                    |                                                                      |

| 4. |     | Why Column-Level A/D Conversion?                                                                                                                                                                                                                                       | . 74                                                                 |

| 4. |     | Why Column-Level A/D Conversion?                                                                                                                                                                                                                                       | . 74<br>. 74                                                         |

| 4. | 4.1 | Why Column-Level A/D Conversion?                                                                                                                                                                                                                                       | . 74<br>. 74<br>. 78                                                 |

| 4. | 4.1 | Why Column-Level A/D Conversion?                                                                                                                                                                                                                                       | . 74<br>. 74<br>. 78<br>. 83                                         |

| 4. | 4.1 | Why Column-Level A/D Conversion?                                                                                                                                                                                                                                       | . 74<br>. 74<br>. 78<br>. 83                                         |

| 4. | 4.1 | Why Column-Level A/D Conversion?  4.1.1 Chip-Level, Column-Level and Pixel-Level A/D Conversion  4.1.2 Architectural Comparison  Column-Level ADC Architectures  4.2.1 Column-Level ADC Architecture Requirements  4.2.2 Column-Parallel Single-Slope ADC Architecture | . 74<br>. 74<br>. 78<br>. 83<br>. 83                                 |

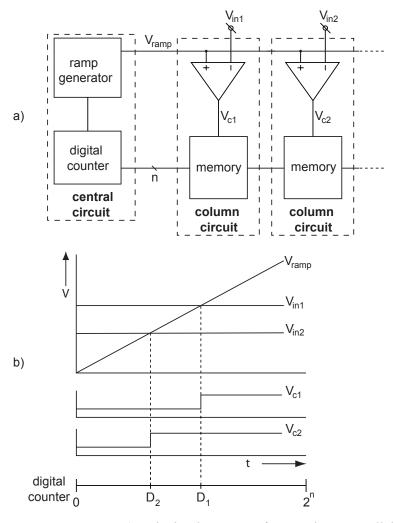

| 4. | 4.1 | Why Column-Level A/D Conversion?                                                                                                                                                                                                                                       | . 74<br>. 74<br>. 78<br>. 83<br>. 83<br>. 85                         |

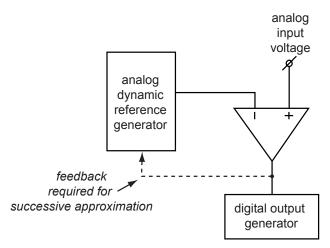

| 4. | 4.1 | Why Column-Level A/D Conversion?  4.1.1 Chip-Level, Column-Level and Pixel-Level A/D Conversion  4.1.2 Architectural Comparison                                                                                                                                        | . 74<br>. 74<br>. 78<br>. 83<br>. 83<br>. 85<br>. 87                 |

| 4. | 4.1 | Why Column-Level A/D Conversion?  4.1.1 Chip-Level, Column-Level and Pixel-Level A/D Conversion  4.1.2 Architectural Comparison                                                                                                                                        | . 74<br>. 78<br>. 83<br>. 83<br>. 85<br>. 87<br>. 92                 |

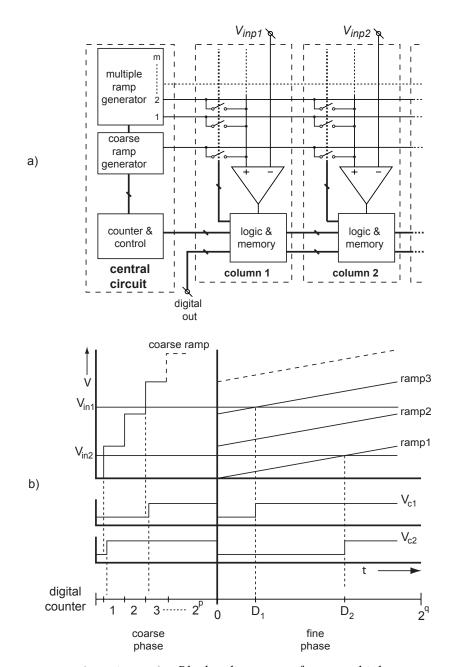

| 4. | 4.1 | Why Column-Level A/D Conversion?                                                                                                                                                                                                                                       | . 74<br>. 78<br>. 83<br>. 83<br>. 85<br>. 87<br>. 92<br>. 93         |

| 4. | 4.1 | Why Column-Level A/D Conversion?  4.1.1 Chip-Level, Column-Level and Pixel-Level A/D Conversion  4.1.2 Architectural Comparison                                                                                                                                        | . 74<br>. 78<br>. 83<br>. 83<br>. 85<br>. 87<br>. 92<br>. 93         |

| 4. | 4.1 | Why Column-Level A/D Conversion?  4.1.1 Chip-Level, Column-Level and Pixel-Level A/D Conversion  4.1.2 Architectural Comparison                                                                                                                                        | . 74<br>. 78<br>. 83<br>. 83<br>. 85<br>. 87<br>. 92<br>. 92         |

| 4. | 4.1 | Why Column-Level A/D Conversion?  4.1.1 Chip-Level, Column-Level and Pixel-Level A/D Conversion  4.1.2 Architectural Comparison                                                                                                                                        | . 74<br>. 78<br>. 83<br>. 83<br>. 85<br>. 87<br>. 92<br>. 92         |

| 4. | 4.1 | Why Column-Level A/D Conversion?  4.1.1 Chip-Level, Column-Level and Pixel-Level A/D Conversion  4.1.2 Architectural Comparison                                                                                                                                        | . 74<br>. 78<br>. 83<br>. 83<br>. 85<br>. 87<br>. 92<br>. 92<br>. 93 |

|           | 4.4.2 Dynamic Column Switching Simulations              |                  |

|-----------|---------------------------------------------------------|------------------|

| 5.        | A CMOS Imager with a Low-Power Colu<br>Single-Slope ADC | ımn-Level<br>115 |

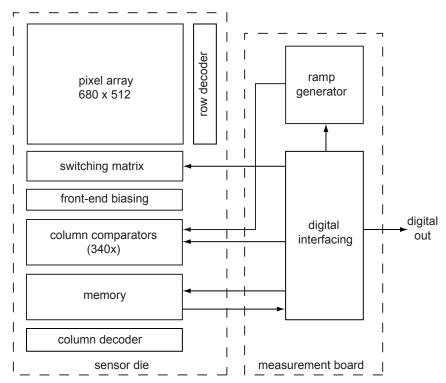

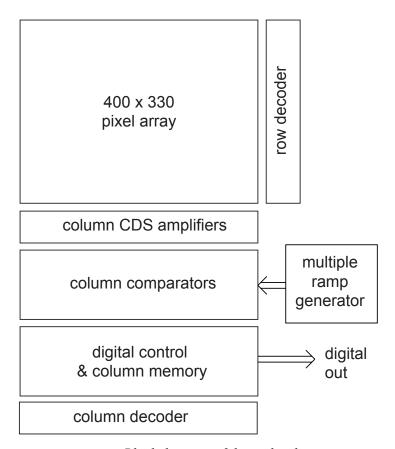

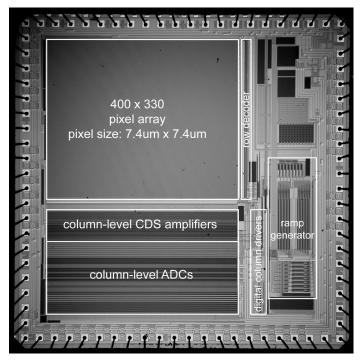

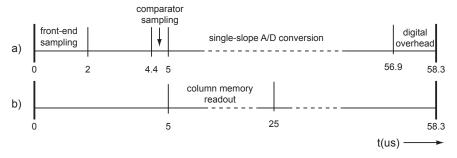

|           | 5.1 Sensor Overview                                     | 116              |

|           | 5.1.1 Design Goals                                      | 116              |

|           | 5.1.2 System-Level Overview                             | 116              |

|           | 5.1.3 Column ADC Requirements                           | 119              |

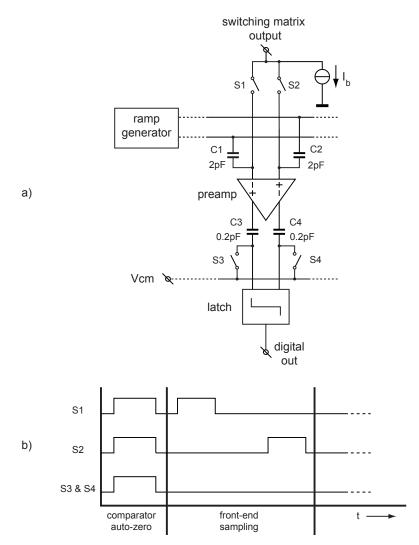

|           | 5.2 Column Comparator Design                            | 120              |

|           | 5.2.1 Comparator Input Circuitry                        | 120              |

|           | 5.2.2 Comparator Topology                               | 120              |

|           | 5.2.3 Offset and Delay Compensation                     | 123              |

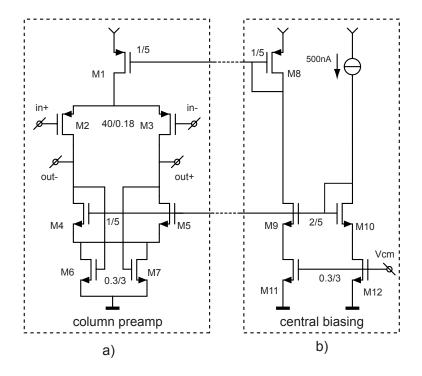

|           | 5.2.4 Preamp Design                                     | 126              |

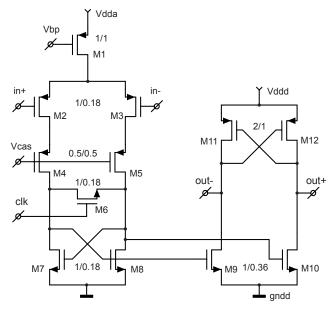

|           | 5.2.5 Regenerative Latch Design                         | 128              |

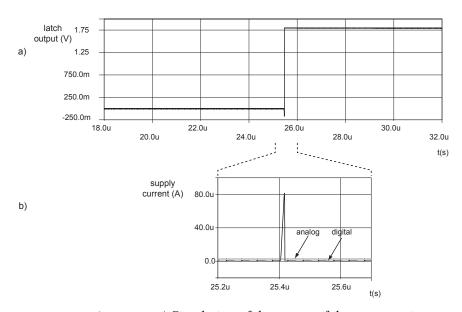

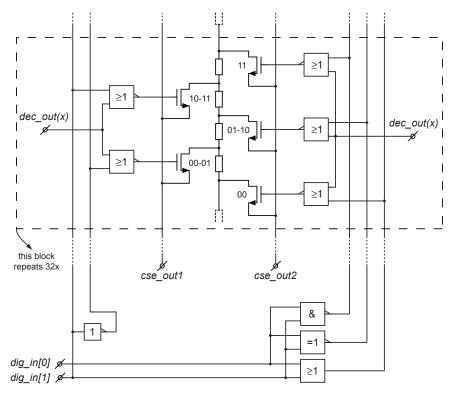

|           | 5.3 Dynamic Column Switching Circuitry                  | 130              |

|           | 5.4 Measurements                                        | 133              |

|           | 5.4.1 Comparator Measurements                           |                  |

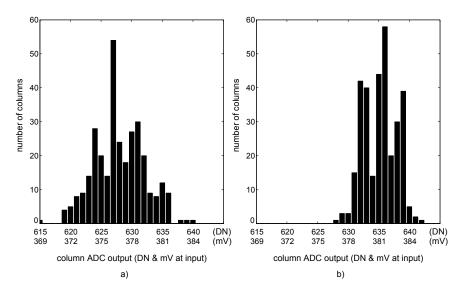

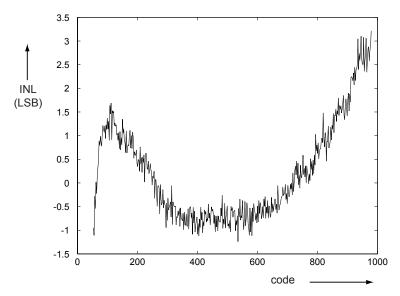

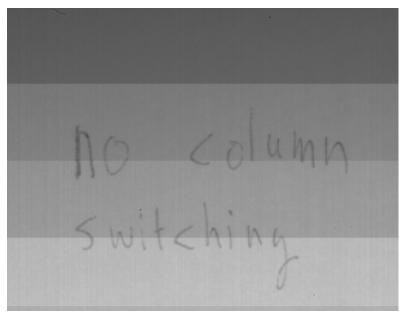

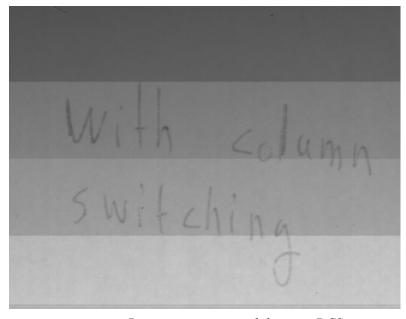

|           | 5.4.2 DCS Measurements                                  |                  |

|           | 5.5 References                                          | 141              |

| <b>ó.</b> | e e e e e e e e e e e e e e e e e e e                   | 145              |

|           | Single-Slope ADC                                        | 145              |

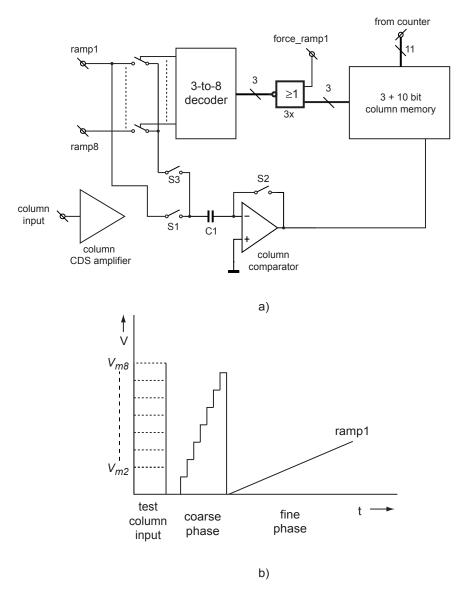

|           | 6.1 Sensor Overview                                     | 145              |

|           | 6.1.1 Design Goals                                      | 145              |

|           | 6.1.2 System-Level Overview                             |                  |

|           | 6.1.3 System-Level ADC Design Considerations            |                  |

|           | 6.2 Column-Level Circuitry                              |                  |

|           | 6.3 Multiple Ramp Generator Design                      |                  |

|           | 6.3.1 Ramp Generator Concept                            |                  |

|           | 6.3.2 Resistor Ladder Switching Logic                   |                  |

|           | 6.3.3 Output Amplifier Offset Auto-Calibration          |                  |

|           | 6.4 Measurement Results                                 |                  |

|           | 6.4.1 Single-Slope Mode Measurements                    |                  |

|           | 6.4.2 MRSS Mode Measurements                            | 166              |

|    | 6.4.3 MRMS Mode Measurements                                            | 169                           |

|----|-------------------------------------------------------------------------|-------------------------------|

|    | 6.5 References                                                          | 174                           |

| 7. | Conclusions                                                             | 175                           |

|    | 7.1 Main Findings                                                       | 175                           |

|    | 7.2 Future Work                                                         | 177                           |

|    | 7.2.1 1/f Noise Reduction in CMOS Image Sensors                         | 177                           |

|    | 7.2.2 Improvements to the MRSS/MRMS prototype                           | 178                           |

|    | 7.2.3 Perceptual Effects of using a Companding ADC                      | 181                           |

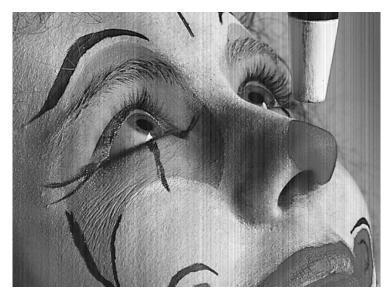

|    | 7.2.4 Perceptual Effects of Dynamic Column Switching                    | 181                           |

|    | 7.3 References                                                          | 102                           |

|    | Appendix A.Companding Quantization Calo                                 | culation                      |

|    |                                                                         |                               |

|    | Appendix A.Companding Quantization Calo                                 | culation                      |

|    | Appendix A. Companding Quantization Calc<br>Method                      | culation<br>183               |

|    | Appendix A.Companding Quantization Calc<br>Method<br>Summary            | culation<br>183<br>187        |

|    | Appendix A. Companding Quantization Calcondethod  Summary  Samenvatting | eulation<br>183<br>187<br>193 |

Introduction

"A picture is worth a thousand words." This simple truth has been known to mankind from the time of prehistoric cave drawings. Since then, techniques for creating images have continuously been refined over the ages, with the most recent step being the replacement of film-based cameras by digital cameras. The heart of a digital camera is an electronic device that converts optical information into electronic signals. Such an 'electronic eye' is called an image sensor or imager. These sensors have a large number of elements that convert light into electrical signals, which are subsequently processed by electronic readout circuits. The main goal of this thesis is to improve the quality of the image sensor by improving the readout circuitry.

In this introductionary chapter, a short overview of the history of electronic image sensors is given. The first section provides a short historical overview of the two main types of sensors, which are the CMOS imager and the CCD imager. Next, the challenges in designing CMOS imagers are discussed. Based on these challenges, the motivation and goals of this thesis are presented. It is shown that in order to improve the quality of CMOS imagers, system-level changes to the read-out circuitry are necessary. Such a system-level approach forms the core of this thesis. Finally, the structure of the thesis is presented.

# 1.1 History of Electronic Image Sensors

The ability to electronically record images, transport them over long distances, and then instantly display them by means of the television is clearly one of the most important inventions of the twentieth century. The development of the television was partly made possible by the development of electronic devices that could process information in the form of electric signals. However, before information can be processed, it has to be acquired; therefore, a sensor that converts light into an electrical signal is necessary.

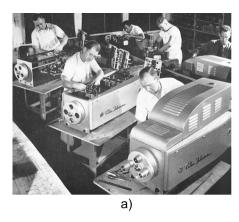

The first practical electronic image sensor was the Vidicon or imaging tube. As their name implies, these early sensors were based on vacuum tube technology. The resulting cameras had the same drawbacks as vacuum tube radios: they were bulky, heavy, and consumed a lot of power (Figure 1-1a).

With the invention of the transistor in 1947, a new class of *solid-state* electronic devices was born. The invention of the integrated circuit in 1958 by Jack Kilby [1.1] and Robert Noyce [1.2] was the decisive breakthrough for solid-state electronics. The ability to put a multitude of transistors together on a tiny silicon chip meant that more and more complex signal processing functions could be realized in a very small device. Not long after the demonstration of the first integrated circuit, several research groups realized that it was also possible to integrate light-sensitive elements onto a chip.

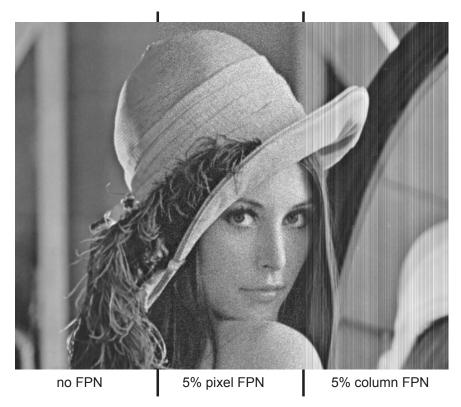

The first publication of such an attempt was in 1963 by Morrison of Honeywell [1.3], followed Horton of IBM in 1964 [1.4] and Schuster of Westinghouse in 1966 [1.5]. All these early devices used the semiconductor processes available at the time to create image sensors, which were bipolar, NMOS or PMOS processes. The photosensitive elements used in these early imagers were photodiodes or phototransistors. Although some improvements were made throughout the 1960's, these early solid-state imagers exhibited two major problems that impeded their commercial use. First of all, the limited lithographic resolution available in the semiconductor processes of that time severely limited the resolution of the resulting imagers. Secondly, other technology-related limitations led to large non-uniformity between different pixels, a phenomenon usually called fixed-pattern noise (FPN).

In 1969, a different solid-state imaging device, called the Bucket-Brigade Device, was invented by Sangster and Teer of Philips

Figure 1-1: a) Assembly line of the first color TV camera, 1954 (courtesy of RCA) b) Single-chip camera modules with the same functionality, 2004 (courtesy of Philips Semiconductors)

Research [1.6]. The original application for this device was an analog delay line, but the inventors soon realized it could also be used as an imager. In 1970, Boyle and Smith of Bell Labs made an improved device which they called a Charge-Coupled Device or CCD. This name has become nearly synonymous with a solid-state imager, although, in theory, a CCD can be used for many different applications. Compared to the early imagers that were made in MOS or bipolar processes, the CCD had the advantage of being a relatively simple device, making it easier to realize an imager with a sufficiently high resolution on a chip. Moreover, CCDs were relatively free of FPN.

Despite these advantages, it took more than a decade before the first commercial CCD imager came on the market, mainly because of fabrication and reliability problems. The first major application of CCDs was in consumer video cameras, where their smaller size and power consumption, compared to imaging tubes, were key advantages. After application in consumer application, CCDs were quickly adopted in the professional TV broadcasting scene, and the classical imaging tube disappeared completely.

The success of the CCD imager led to a near abandonment of research into MOS-based image sensors. In the early 1990's however, several groups led a resurgence in MOS imager research and development. Among these groups were the University of Edinburgh, Linköping University in Sweden and NASA's Jet Propulsion Laboratory (JPL). The

motivation for this research was that while CCDs had excellent performance, the specialized semiconductor process with which CCDs are fabricated made it very difficult to co-integrate large circuit blocks onto the same chip. Therefore, in order to create a complete camera system, at least two chips were necessary. However, if it were possible to realize an imager in a standard CMOS process, the signal processing could be integrated on a single chip, creating a camera-on-a-chip. Apart from the obvious benefit of creating smaller cameras, such miniaturization could also lead to lower cost and lower power consumption.

In the late 1990's, mobile telephony found very rapid adoption among consumers, creating a new high-volume market for portable electronic devices, where low power consumption and small system sizes are key requirements. Around 2000, the first mobile phones equipped with cameras became available. For this application, CMOS imagers are very well suited. Firstly, their power consumption is much lower compared to CCDs. Secondly, the complete camera can have smaller physical dimensions because the signal processing can be integrated on the same chip as the sensor (Figure 1-1b). This high-volume market has fuelled the rapid development of CMOS imagers.

Today, CMOS imaging is emerging as a mature technology alongside CCDs. Camera-equipped cell phones have more or less become a standard. The focus of CMOS imager development for this application is now on improving (perceived) image quality, and in particular, increasing the pixel count.

# 1.2 Challenges

Having discussed the history of CMOS imagers in the previous section, this section will take a brief look into the future. In particular, the challenges in designing future imagers will be discussed. Such a design is typically a system effort, where it is not possible to identify a single performance constraint or physical limit. Instead, a set of constraints, comprising both physical limits as well as customer requirements, has to be met. Since it is difficult to mathematically define the relation between these design constraints, no widely accepted figure-of-merit has been defined for CMOS imagers. However, it is possible to identify a number of parameters that are defining CMOS imager performance. Three of these parameters have a significant impact on the requirements for the analog readout circuitry:

- Signal-to-noise ratio and dynamic range

- Number of pixels / 'resolution'

- Power consumption

In the following sections, each of these performance parameters will be discussed.

### Signal-to-Noise Ratio and Dynamic Range

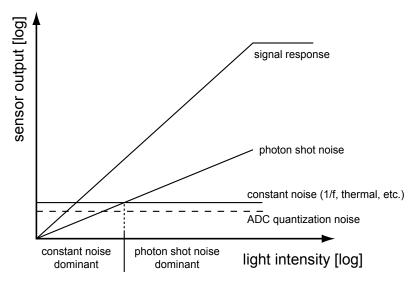

In many sensor interface systems, the maximum signal-to-noise ratio and dynamic range are nearly equal to each other. This is because the amount of noise in many systems can be considered constant, and therefore, the dynamic range, i.e. the ratio of the maximum over the minimum signal that the system can process, becomes equal to the maximum signal over the noise (since the noise limits the minimum signal that can be processed). However, the amount of noise in an image sensor is signal dependent because of the presence of photon shot noise, as will be explained in section 3.2.1. This noise source typically dominates at higher input signals, and therefore, the maximum signal-to-noise ratio will be less than the dynamic range.

In order to increase overall image quality, it is desirable to increase both dynamic range and signal-to-noise ratio. A lot of work has been done on increasing the dynamic range by increasing the maximum amount of input signal an imager can handle, for instance by using pixels with a logarithmic response [1.12], or using multiple capture [1.13]. A brief overview of these techniques will be given in sub-section 2.5.3. However, all these techniques only increase the dynamic range at the expense of signal-to-noise ratio. Moreover, other problems (fixed-pattern noise, extra in-pixel circuitry) make the adoption of these techniques in mainstream applications unattractive. Therefore, it would be more beneficial if the dynamic range can be increased by reducing the noise in the imager signal as much as possible.

The amount of noise on the imager's output signal depends on a number of noise sources. Some of these are fundamental in nature (such as photon shot noise), others are technology dependent (such as dark current), and yet others are circuit related (thermal noise, 1/f noise). An excellent performance analysis paper can be found in [1.14], where it is shown that the amount of circuit noise actually exceeds the technology related noise sources. However, at the start of this thesis work, it was unclear *which* circuit noise source was dominant, and if such noise could be reduced using circuit techniques.

#### Number of Pixels / 'Resolution'

The number of (mega)pixels an imager has is perhaps one of its most 'visible' performance parameters. Quite often, this number is assumed to be synonymous with the imager's resolution, i.e. its ability to resolve light variations in the spatial domain. However, this assumption is incorrect; apart from the amount of pixels, two other parameters are of key importance to the resolution of CMOS imagers. First of all, some of the charge carriers generated in the silicon due to incident light can diffuse from underneath one pixel to the other. The smaller the pixel size, the worse this effect becomes. Second, the optical system in front of the imager will also have a limited spatial resolution. Therefore, instead of the number of pixels, the so-called Modulation Transfer Function (MTF) is a correct measure of imager resolution. More information on how to determine MTF can, for instance, be found in [1.7].

In spite of being an incorrect performance parameter, the number of pixels is universally marketed as the sole performance parameter for imagers, in particular in consumer applications. As a result, customers are nowadays convinced that an 8 megapixel camera is 4 times better than a 2 megapixel camera. This market force has led to an interesting situation in imaging design, in particular for low-cost sensors for mobile applications.

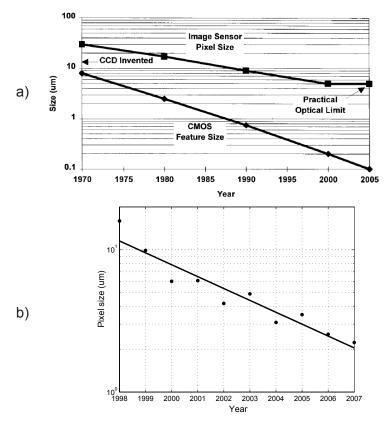

In order to increase the number of pixels, either the chip size has to increase, or the pixel size should shrink. It is very unattractive to increase the chip size, not only because a larger chip is more expensive, but also since it would require a larger optical format, and therefore, the camera as a whole would be larger, which is not acceptable in a mobile application. Therefore, shrinking the pixel size is the only way to produce an imager with a higher pixel count at the same cost. In his 1997 overview paper [1.8], Fossum predicted that pixel size would stabilize in the year 2000 at about 5µm, due to practical limitations of the optics (Figure 1-2a). Since the minimum process feature size would continue to shrink after 2000, this would mean that more transistors could be integrated on the same pixel for added functionality. However, rather the opposite happened, as is illustrated in Figure 1-2b. For this graph, an average pixel size of imagers published at the International Solid-State Circuits Conference (ISSCC) and the International Electron Devices Meeting (IEDM) was computed for each year between 1998 and 2007. It is clear that pixel sizes have continued to drop well below 5µm. In order to enable this decrease in pixel size, the number of transistors was actually reduced, by sharing

read-out transistors between several pixels [1.9-1.10]. Using this transistor sharing method, pixel sizes as small as 1.75µm have recently been reported [1.11]. Although the optics of cameras in mobile applications have improved, it is still doubtful if the use of such small pixels will increase the imager performance further.

Nevertheless, the marketing forces that drive increasing pixel count have not changed, and therefore, it can be expected that the pixel count will keep increasing as long as it does not result in significantly *lower* imager performance.

### **Power consumption**

Figure 1-2: a) Graph taken from Fossum [1.8], predicting a minimum pixel size of 5µm in 2000 b) Graph showing the average of published pixel sizes for each year from 1998-2007

Although the power consumption of the first generation of CMOS image sensors was already about an order of magnitude lower than CCDs, the recent focus on mobile, battery-powered applications has provided a strong motivation to further decrease power consumption. In a CMOS imager, the pixel array itself has a very low power consumption compared to that in a CCD imager, as there are no large CCD gates to charge and discharge during the readout process. In conventional CMOS imagers, most of the power is therefore consumed by the readout circuitry, in particular the analog-to-digital converter and digital circuitry [1.15].

# 1.3 Motivation and Objectives

As shown in the last section, the challenges in designing CMOS image sensors involve the improvement of three key performance parameters: the number of pixels, the signal-to-noise ratio and the power consumption. In improving each of these parameters, analog signal processing plays an important role.

Although the signal-to-noise ratio of a CMOS imager is partly defined by the properties of the light sensitive element, it is usually the front-end analog circuit that determines the noise floor of the image sensor. Therefore, any noise reduction in the analog readout circuit would directly lead to a better CMOS imager. While this challenge might seem simple, the fact that analog readout circuit has to be partially implemented inside the pixel itself leads to severe design constraints, as the amount of available chip area is minimal.

While the increase in pixel count does not directly require an improvement of the analog readout circuit, it does have an important indirect impact. A higher pixel count requires an increase in the bandwidth of the signal processing chain, since more pixels need to be read out in the same amount of time. This higher bandwidth requirement can have two negative effects on the performance of the imager. Firstly, it can increase the total amount of noise in the analog signal processing chain. Since the CMOS imager readout structure requires the sampling of data, the total amount of in-band noise usually determines the noise performance. Therefore, if the signal bandwidth increases, it typically results in a higher total in-band noise, unless the noise density of the circuit can be lowered, which requires more power.

A second consequence of the higher pixel count is that, if no system-level changes are made to the analog readout circuit, its power consumption will have to be increased in order to increase the bandwidth. This is very undesirable, since, as mentioned, a third challenge in CMOS imager design is actually to *lower* power consumption. Therefore, because of the requirement, on the one hand, to increase pixel count and thus signal bandwidth, and, on the other hand, the requirement to lower power consumption, system-level improvements to the analog readout circuit are imperative. Such improvements should lead to a better power efficiency of the circuit, i.e. less power consumption per readout operation. As mentioned in the previous section, the A/D converter is consuming most of the power in the analog readout circuit, and therefore, efforts to increase the power efficiency of the analog signal processing chain should be focused on the ADC.

In conclusion, the focus of this thesis can be summarized in two goals:

- Reduce the noise of the analog readout circuit as much as possible to increase the overall noise performance of a CMOS imager.

- Significantly improve the power efficiency of the analog signal processing chain as much as possible, in order to enable low-power high-resolution CMOS imagers.

# 1.4 Organization of the Thesis

The remainder of this thesis consists of six chapters. Chapter 2 provides an overview of the analog signal processing chain in conventional, commercially-available CMOS imagers. First of all, the different photo-sensitive elements that form the input to the analog signal chain are briefly discussed. This is followed by a discussion of the analog signal processing chain itself, which will be divided into two parts. Firstly, the analog front-end, consisting of in-pixel circuitry and column-level circuitry, is discussed. Second, the analog back-end, consisting of variable gain amplification and A/D conversion is discussed. Finally, a brief overview of advanced readout circuit techniques is provided.

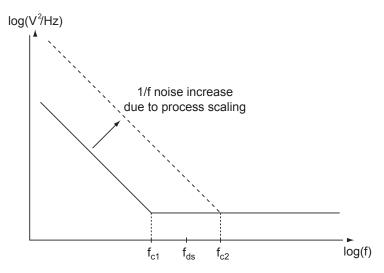

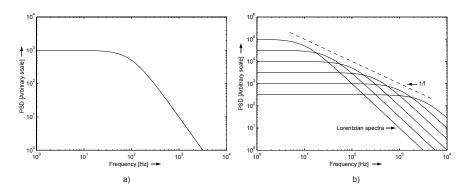

In chapter 3, the performance of the analog front-end is analyzed in detail. It is shown that its noise performance is the most important parameter of the front-end. An overview of front-end noise sources is given and their relative importance is discussed. It will be shown that 1/f noise is the limiting noise source in current CMOS imagers. A relatively

unknown 1/f noise reduction technique, called switched-biasing or large signal excitation (LSE), is introduced and its applicability to CMOS imagers is explored. Measurement results on this 1/f noise reduction technique are presented. Finally, at the end of the chapter, a preliminary conclusion on CMOS imager noise performance is presented.

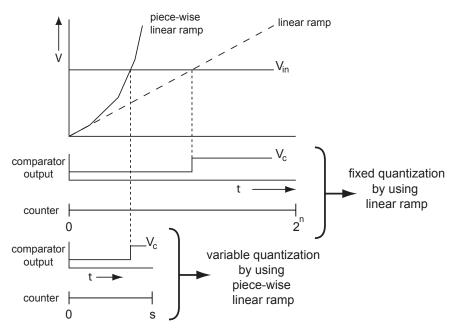

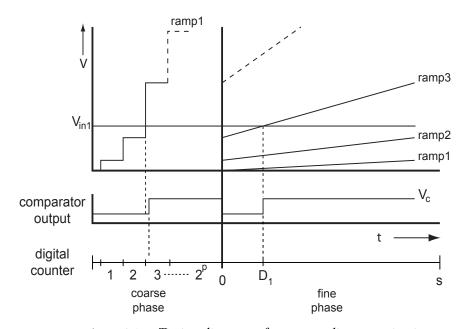

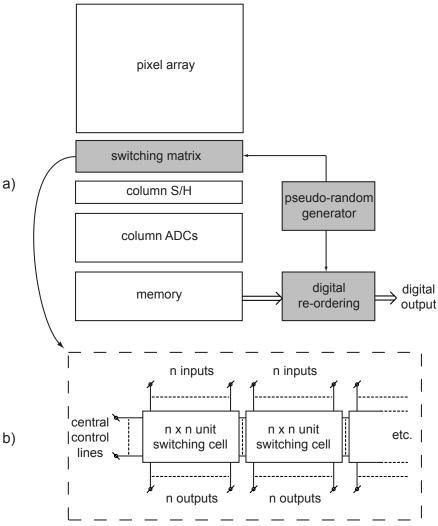

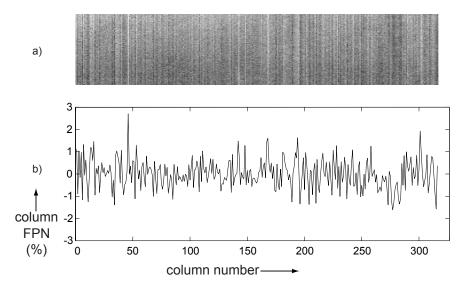

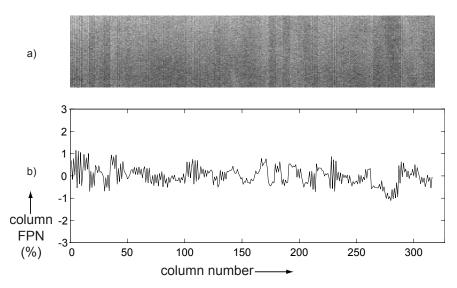

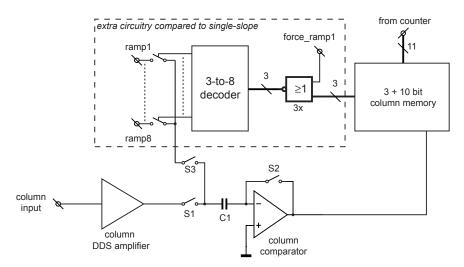

The main function of the back-end analog signal chain is analog-to-digital conversion, which is described in chapter 4. First of all, the conventional approach of a single chip-level ADC is compared to a massively-parallel, column-level ADC, and the advantages of the latter will be shown. Next, the existing column-level ADC architectures will be briefly discussed, in particular the column-parallel single-slope ADC. Furthermore, a new architecture, the multiple-ramp single-slope ADC will be proposed. Finally, two circuit techniques are introduced that can improve ADC performance. Firstly, it will be shown that the presence of photon shot noise in an imager can be used to significantly decrease ADC power consumption. Secondly, an column FPN reduction technique, called Dynamic Column Switching (DCS) is introduced.

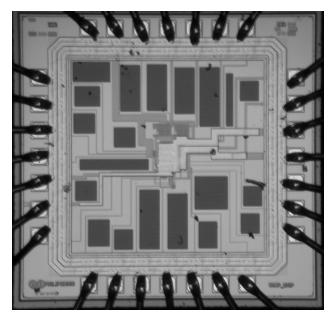

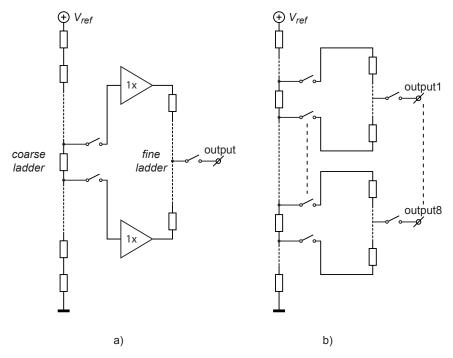

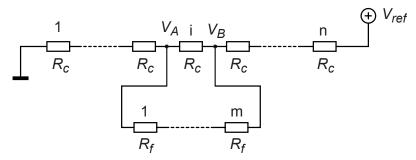

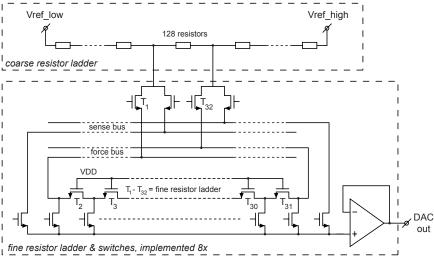

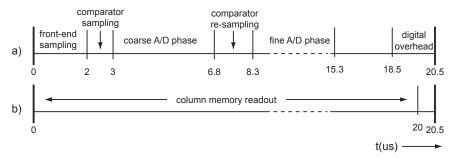

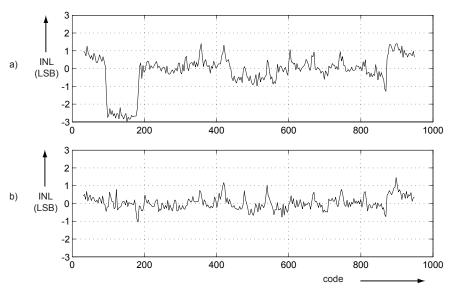

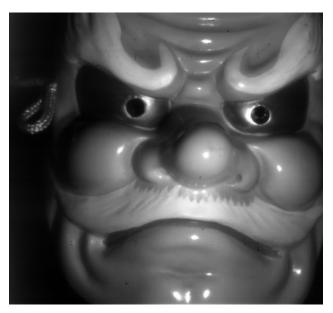

Chapter 5 and 6 present two realisations of imagers with column-level ADCs. In chapter 5, a CMOS imager with single-slope ADC is presented that consumes only 3.2µW per column. The circuit details of the comparator achieving this low power consumption are described, as well as the digital column circuitry. The ADC uses the dynamic column switching technique introduced in chapter 4 to reduce the perceptional effects of column FPN. Chapter 6 presents an imager with a multiple-ramp single-slope architecture, which was proposed in chapter 4. The column comparator used in this design is taken from a commercially available CMOS imager. The multiple ramps are generated on chip with a low power ladder DAC structure. The ADC uses an auto-calibration scheme to compensate for offset and delay of the ramp drivers.

Finally, chapter 7 presents the main conclusions of this thesis and gives suggestions for future work.

## 1.5 References

- [1.1] J.S Kilby, US Patent no. 3,138,743, issued June 1964

- [1.2] R.N. Noyce, US Patent no. 2,981,877, issued April 1961

- [1.3] S. Morrison, "A new type of photosensitive junction device," *Solid-State Electron.*, vol. 5, pp. 485–494, 1963.

- [1.4] J. Horton, R. Mazza, and H. Dym, "The scanistor—A solid-state image scanner," in *Proc. IEEE*, vol. 52, pp. 1513–1528, 1964.

- [1.5] M. A. Schuster and G. Strull, "A monolithic mosaic of photon sensors for solid state imaging applications," *IEEE Trans. Electron Devices*, vol. ED-13, pp. 907–912, 1966.

- [1.6] F.L.J Sangster, K. Teer, "Bucket-Brigade electronics", *IEEE Journal of Solid-State Circuits*, Vol. SC-4, pp. 131, 1969.

- [1.7] A.J.P. Theuwissen, *Solid-State Imaging with Charge-Coupled Devices*, Kluwer Academic Publishers, Dordrecht, 1995.

- [1.8] E.R. Fossum, "CMOS Image Sensors: Electronic Camera-On-A-Chip", *IEEE Transactions on Electron Devices*, Vol. 44, No. 10, pp. 1689-1698, Oct. 1997

- [1.9] H. Takahashi et al., "A 3.9µm Pixel Pitch VGA Format 10b Digital Image Sensor with 1.5-Transistor/Pixel", *IEEE International Solid-State Circuits Conference*, Vol. XLVII, pp. 108-109, Feb. 2004

- [1.10] M. Mori et al., "A 1/4in 2M Pixel CMOS Image Sensor with 1.75Transistor/Pixel", *IEEE International Solid-State Circuits Conference*, Vol. XLVII, pp. 110-111, Feb. 2004

- [1.11] K-B. Cho et al., "A 1/2.5 inch 8.1Mpixel CMOS Image Sensorfor Digital Cameras", *IEEE International Solid-State Circuits Conference*, Vol. L, pp. 508-509, Feb. 2007

- [1.12] S.J. Decker, R.D. McGrath, K. Brehmer and C.G. Sodini, "A 256x256 CMOS imaging array with wide dynamic range pixels and column-parallel digital output", *IEEE Journal of* Solid-State Circuits, Vol. 33, pp. 2081-2091, Dec. 1998

- [1.13] O. Yadid-Pecht and E. Fossum, "Wide intrascene dynamic range CMOS APS using dual sampling", *IEEE Transactions on Electron Devices*, vol. 44, pp. 1721-1723, Oct. 1997

- [1.14] A.J. Blanksby and J. Loinaz, "Performance Analysis of a Color CMOS Photogate Image Sensor", *IEEE Transactions on Electron Devices*, Vol. 47, No. 1, Jan. 2000

- [1.15] B. Pain, Course on CMOS Digital Image Sensors, *SPIE Photonics West*, San Jose, 2001

### Introduction

# CMOS Imager Analog Signal Processing at a Glance

2

This chapter gives an overview of the analog signal processing chain of a CMOS image sensor. It follows the signal path from input to output or 'from photons to bits'. The purpose of this chapter is to introduce the topic to the analog circuit designer who is not familiar with CMOS imagers. As such, it does not intend to give a complete overview of all the readout structures that have been published over the years, but rather introduces the reader to a typical structure as a basis for the rest of the thesis. The chapter starts with a brief architectural overview of a typical image sensor in section 2.1. Next, a typical analog signal processing chain is described from input to output. In section 2.2, the photosensitive elements are discussed. Section 2.3 details the function of the front-end readout circuitry, while section 2.4 describes the back-end readout circuitry. Finally, section 2.5 provides a brief overview of improvements and or alternative readout structures that have been proposed in recent years.

# 2.1 Architectural Overview of CMOS Image Sensors

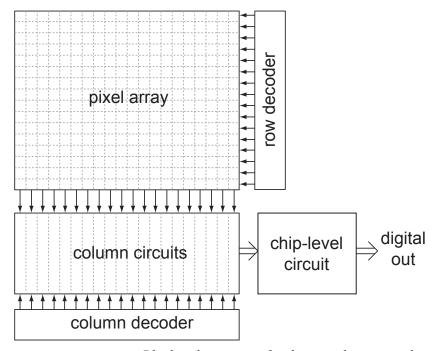

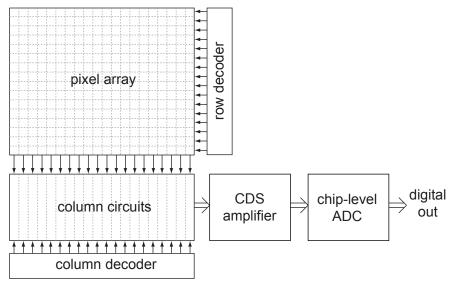

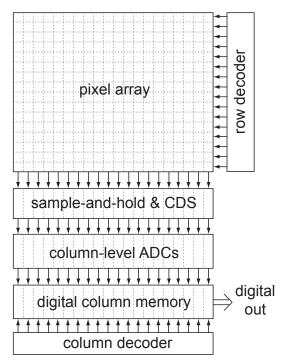

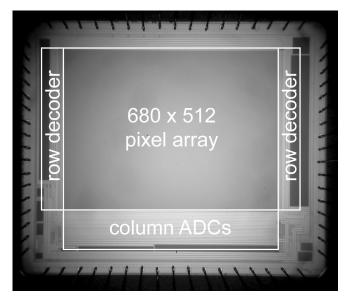

CMOS image sensors are possibly one of the most complex mixed-signal integrated circuits on the market today. They routinely contain several million transistors, and have a large quantity of both analog and digital circuitry. While there are a large number of variations possible in terms of resolution, frame-rate, readout features, etc., most analog signal processing chains follow a similar architecture, as is depicted in Figure 2-1. In this simplified block diagram, only analog circuit blocks are shown, while digital driver/control blocks are omitted for clarity. As can be seen in the figure, the analog signal processing chain can be divided into five main blocks.

The first block consists of the photosensitive pixel array itself. Apart from photosensitive elements, this block also contains some analog readout circuits implemented into each pixel. The second block consists of a set of column circuits that are located outside the pixel array. As its name implies, each column circuit is connected to a single column of the pixel array. The combination of in-pixel circuitry and column circuitry concurrently reads out a row of the pixel array. To this end, the row decoder outputs a control signal, which ensures that a single row of the pixel array is connected to the column circuits. The results of this readout operation are stored on capacitors in each column circuit.

Figure 2-1: Block diagram of the analog signal processing chain in a CMOS image sensor

The third block is the chip level circuit. Here, "chip-level" implies that only a single circuit is used to read out all signals of the chip, rather than having a row of identical circuits (the column circuits) or an array of identical circuits (the pixel array). The chip-level circuit is consecutively connected to each column circuit and reads out the result of the front-end readout operation stored in the column circuit. To this end, the column decoder outputs a control signal, which connects one column circuit to the chip level circuit. In the latter, an A/D converter digitizes the results, after which further digital processing can be performed.

While the analog readout system is physically separated into three blocks, the actual readout operation is a two-step process, as described above: First, the concurrent readout of a row of pixels and storage in the column circuits, and second, a consecutive readout of the column circuits. Since such a division into two parts is more convenient to describe the analog circuitry, it will be used throughout this thesis. To this end, the circuitry that performs the first readout operation will be called the *front-end readout circuitry*; it consists of both in-pixel electronics and a part of the column circuits up to the capacitors that store the results of the first readout. The circuitry that performs the second readout operation will

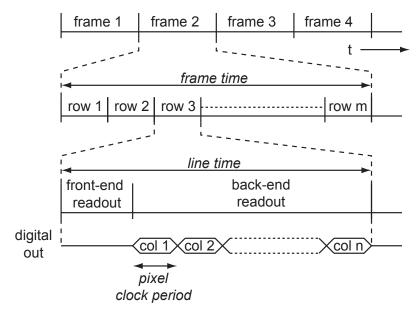

Figure 2-2: Typical timing diagram of the readout of a CMOS imager with a resolution of m x n pixels

be called the *backend readout circuitry*; it consists of remaining part of the column circuitry and the chip level circuitry.

Although CMOS image sensors can theoretically have a random-access readout mode, in which each pixel can be individually accessed, in most cases, a full image or frame is read out serially, as is illustrated in Figure 2-2. This can be done at a typical rate of about 30-50 frames/second, which means that the *frame time* is about 33-20ms. As described above, the imager is read out on a row-by-row basis; to this end, each frame time is divided into a number of line times. The amount of time available to read out a row of the imager equals the frame time divided by the number of rows. For a moderate resolution of about 500 rows or *lines*, this results in a *line time* of about 40-60µs.

During each line time, the two distinct readout steps are performed, as depicted in Figure 2-2. First, a front-end readout operation is performed, storing the outputs of a row of pixels into the column circuits. This operation can usually be performed within 3-5µs. The rest of the line time is used for the back-end readout. During this period, the chip-level circuit reads out the column circuits one by one. Assuming a moderate resolution of about 500 columns, the readout of each column circuit should be done in about 100ns. The chip-level circuit therefore needs to be able to operate at about 10MHz. This frequency is usually called the *pixel clock*, and is often also the clock frequency at which most of the imager operates.

### 2.2 Photosensitive Elements

As with all interface electronics, knowledge of the sensor itself is vital to be able to design a read-out front-end. Therefore, a brief overview of the photosensitive elements used in CMOS imagers will be given, aimed at explaining the requirements on the readout circuitry. The basic concepts will be explained for the simplest photosensitive device, the photodiode. After this, the added functionality provided by the photogate and pinned photodiode will be explained.

#### 2.2.1 Photodiodes

The basis of solid-state imaging is the photo-electric effect [2.1], which describes the interaction of electromagnetic radiation with matter. In the case of a solid-state imager, the electromagnetic radiation will be

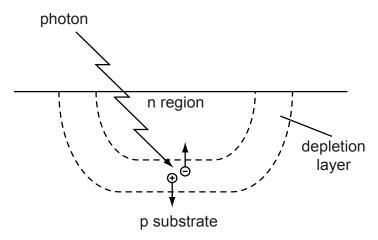

Figure 2-3: *Generation of photocurrent in a p-n junction*

visible light and the matter will be a semiconductor. When a semiconductor is exposed to light, the incident photons can transfer part of their energy to individual silicon atoms, resulting in the generation of electron-hole pairs. The main condition is that the wavelength of the light, and thus the energy of the photons, should be higher than the bandgap of the semiconductor, as the photon should have enough energy to lift an electron from the valence band into the conduction band. Luckily for solid-state imaging, the most widely used semiconductor material, silicon, has a bandgap low enough (1.1eV) to allow visible light to generate electron-hole pairs.

In order to detect the generated electron-hole pairs, the next step is to quickly separate the electrons from the holes, which would otherwise recombine within a short time. The simplest mechanism for separation is the electric field present inside the depletion region of a p-n junction of a diode (Figure 2-3). The electric field will cause the electrons to drift towards the n-doped silicon, while the holes drift towards the p-doped region. This results in a current across the p-n junction which flows in the reverse direction of the diode. In conclusion, a photodiode is an ordinary p-n junction that is exposed to light; this incident light results in a reverse current, often called photocurrent, through the diode.

While some of the earliest solid-state imagers attempted to measure the photocurrent directly, all modern solid-state imagers work in integrating mode [2.2]: the photocurrent is integrated onto a capacitance, and the voltage change across the capacitance is read out. There are two reasons for this. First, in a typical imager, the number of generated electron-hole pairs will be very small, resulting in a current of less than 1pA. It is very difficult to design simple interface electronics that can accurately measure such a small current. Second, an imager needs an array of photodiodes, which all have to be read out by analog circuitry. It is quite difficult to read out all these photodiodes concurrently; instead, read-out is usually done on a row-by-row basis, as will be shown later. This implies that the readout circuit has to be time-shared among the photodiodes, and as a result, each photodiode has to be read out in a short time. Therefore, reading out the integrated photocurrent is easier, as the energy stored in the integrating capacitor is larger than the instantaneous energy generated by the photodiode. Moreover, in photography applications where a flash gun is used, a direct readout of photocurrent would imply that all pixels have to be read out during the 'flash', which is impractical.

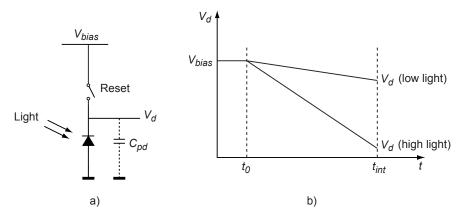

Integrating the photocurrent can be done by using the photodiode's own capacitance. When the diode is reverse-biased, the p and n regions effectively function as the isolated plates of a capacitor. The photodiode can therefore be operated as follows (Figure 2-4). First, a voltage is applied to reverse bias the diode using the reset switch shown in the figure. This reset operation effectively samples the voltage  $V_{bias}$  onto the parasitic capacitance of the diode, and therefore, the diode will stay in reverse bias when the external voltage source is removed. After the reset switch is opened at  $t_0$ , the biasing voltage will decrease if the diode is

Figure 2-4: a) Schematic of a photodiode in integrating mode. b) Plot of the voltage on the photodiode vs. time as photocurrent is integrated.

exposed to light, as this generates a photocurrent that is integrated onto the capacitor. Since the photocurrent is directly proportional to the amount of light, the resulting voltage decrease across the photodiode is, to first order, directly proportional to the amount of light and to the integration time. Therefore, by measuring the voltage over the diode after a certain integration time a measure of light intensity is acquired.

A number of noise sources limit the dynamic range and signal-to-noise ratio of a photodiode. While all of them will be discussed in chapter 3, one dominant noise source will be described here to explain the need for more complex photosensitive elements. As explained, the reset operation effectively samples the voltage  $V_{bias}$  onto the photodiode capacitance  $C_{pd}$ . Just as any other switched-capacitor circuit, this sampling operation exhibits sampling noise. As is well known, this sampling noise equals:

$$\overline{v_n} = \sqrt{\frac{kT}{C_{pd}}}$$

(2-1)

While this noise source is usually referred to as kT/C noise in the analog circuit design community, in the CMOS imager literature, it is mostly referred to as reset noise, as the noise is introduced onto the photodiode when it is reset. In image sensor design, in order to allow for comparisons between imagers, all noise sources are referred to the physical input of the sensor, which is the charge stored in the photodiode capacitance, usually expressed in a number of electrons. This charge is related to the voltage over the photodiode as follows:

$$v_{pd} = \frac{q}{C_{pd}} \cdot e_{pd} \tag{2-2}$$

where  $v_{pd}$  is the voltage over the photodiode,  $e_{pd}$  number of electrons stored into the photodiode capacitance, q the charge of an electron, and  $C_{pd}$  the capacity of the photodiode. The ratio of q and  $C_{pd}$  is usually called the *conversion gain*, since it determines the 'gain' of the charge-to-voltage conversion that effectively takes place at the photodiode capacitance. By combining Eq. (2-1) with Eq. (2-2), the sampling noise can be expressed as a number of noise electrons rms  $\overline{e_n}$ :

$$\overline{e_n} = \frac{\sqrt{kTC}}{q} \tag{2-3}$$

At first glance, this can look paradoxical to a circuit designer, as it seems now that, instead of decreasing, the sampling noise is increasing with the capacitance. However, the key insight is that the capacitance not only determines the noise level expressed in terms of charge, but also determines how this noise charge is converted into a noise voltage according to Eq. (2-2). As the charge-to-voltage conversion is inversely proportional to the capacitance, while the noise expressed in charge is only proportional to the square root of the capacitance, the noise voltage decreases with the square root of the capacitance. However, as in any other analog circuit, the choice of capacitance is a trade-off between noise performance and other parameters. In CMOS imagers, the required (small) pixel size usually constitutes an upper limit to the capacitance. In a typical imager, the photodiode capacitance is in the order of 1-10fF, leading to a noise voltage of 1-3mV rms (or 18-40 electrons rms). This is usually the dominant noise source, which can considerably limit the dynamic range of the photodiode-based imager.

There is however a conceptual solution for the reset noise. By sampling the voltage across the photodiode immediately after it is reset, the reset noise can be measured. Next, photocurrent is integrated onto the photodiode's capacitance for certain period, after which the voltage across the photodiode is sampled again. This second sample then contains the signal voltage (i.e. the decrease in photodiode voltage that is proportional to light) and the reset voltage. By subtracting the first sample from the second, the reset noise is removed from the second sample. However, this solution is not practical for most imagers, as each pixel's reset voltage would have to be sampled before integrating its photocurrent, and this sample would need to be stored until after the integration period. Therefore, an analog or digital memory would be required that can store a full frame, which would consume a very large amount of chip area. To solve this problem, alternative photosensitive elements have been developed, which can read out the reset noise after the integration of photocurrent is completed.

## 2.2.2 Photogates

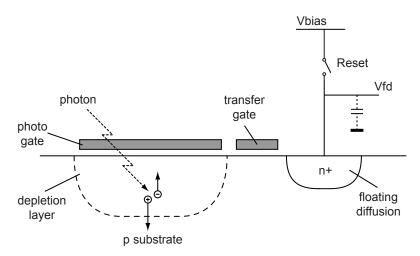

The problem of reset noise, as described in the previous section, can be solved by using a photogate as photosensitive element [2.3][2.10]. Figure 2-5 shows a cross-section of such a device. In a photogate, the electrical field that separates photon-generated electron-hole pairs is

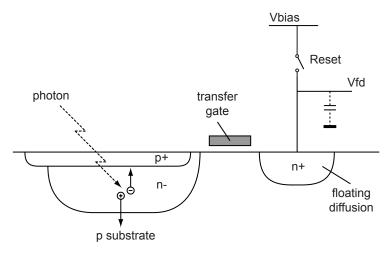

Figure 2-5: Cross-section of a photogate including floating diffusion read-out.

established by biasing the photogate at a positive voltage relative to the substrate. As a result, photon-generated electrons are attracted towards the photogate during charge integration, while the holes are pushed away. This creates a pocket of negative charge underneath the photogate. This charge is read out using a separate structure, consisting of a transfer gate and a so-called floating diffusion that are connected to the photogate.

The readout operation is performed as follows: Firstly, the floating diffusion is reset to a biasing voltage. As with the photodiode, the floating diffusion can be considered to be a capacitance onto which a voltage is sampled, and therefore, reset noise is generated. This reset noise is sampled by the readout circuit for compensation. Next, the photon-generated charge is transferred from underneath the photogate into the floating diffusion by pulsing the photogate. This transfer of charge is very similar to what is done in a charge-coupled device (CCD) and can be done in a fast ( $< 2\mu s$ ) and nearly lossless fashion. As a result, the voltage across the floating diffusion is proportional to the amount of photon-generated charge plus the amount of sampling noise. By sampling this value and subtracting the first sample containing only reset noise from it, an output value can be acquired that is free from reset noise.

In conclusion, the photogate solves the reset noise problem because it has a floating diffusion capacitance onto which the photon-generated charge can be transported *quickly*. As a result, the reset voltage and the signal voltage on the floating diffusion capacitance can be sampled in

quick succession, and therefore, no frame memory is required as would be the case with a photodiode readout. However, photogates have one distinct disadvantage. The presence of a gate on top of the photosensitive silicon significantly decreases the light sensitivity of the device.

#### 2.2.3 Pinned Photodiodes

The above-mentioned problem of photogates, i.e. their decreased light sensitivity compared to photodiodes, was solved with the development of the pinned photodiode [2.4-2.5]. Figure 2-6 depicts a cross section of a pinned photodiode. Compared to a normal photodiode, a very shallow p+ layer has been implanted near the silicon surface, thereby connecting (i.e. "pinning") the cathode of the photodiode to the substrate. The resulting structure is read out in the same way as a photogate, by transferring the photon-generated charge from the pinned photodiode to the floating diffusion. As is obvious from the figure, the pinned photodiode solves the photogate's problem of lower optical sensitivity. The pinned photodiode has some other advantages over both photodiodes and photogates, in particular a lower dark current. The main drawback is that it is more difficult to fabricate. In a pinned photodiode, the depletion region from the n-/p substrate junction should extend into the depletion layer of the p+/njunction in order for the device to work properly, i.e. the n- region must be fully depleted. In order for this to happen, both the p+ and n- doping levels

Figure 2-6: Cross-section of a pinned photodiode with floating diffusion readout structure

have to be accurately controlled. In spite of this process control difficulty, the pinned photodiode has become the most popular photosensitive elements for high-quality CMOS imagers [2.6].

# 2.3 Front-End Analog Signal Processing

In this section, the front-end part of the analog signal processing chain will be discussed. This front-end consists of the in-pixel circuitry, as well as a set of column circuits that are implemented outside the pixel array. The function of the front-end is to read out the voltage generated by the photosensitive element used in the pixel, and store this output voltage in the column, where it can be read out by the analog back-end. This process will first be explained for a typical front-end circuit used for a photodiode. After that, the front-end for a photogate or pinned photodiode will be discussed.

#### 2.3.1 Photodiode Front-End Readout Structure

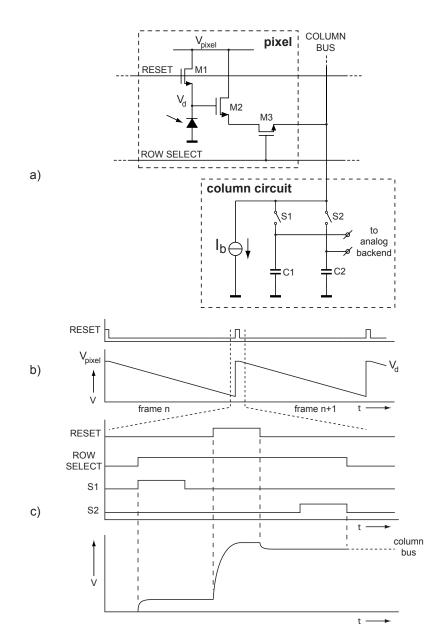

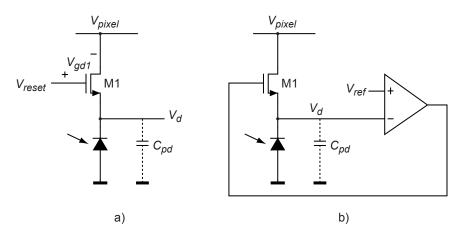

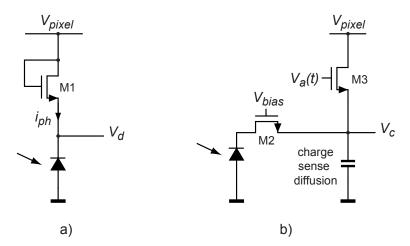

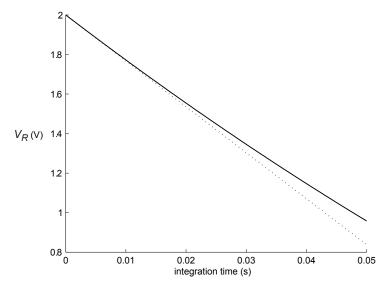

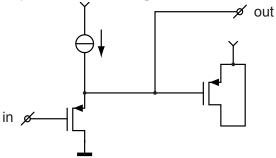

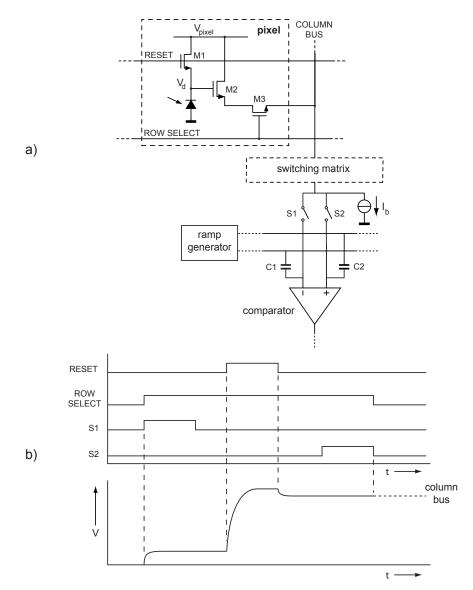

Figure 2-7a shows a circuit diagram of a typical analog front-end for a photodiode [2.7-2.9]. Here, a single pixel from the pixel array and a single column circuit from the row of column circuits are depicted. The pixel uses a photodiode as described in sub-section 2.2.1. Transistor M1 resets the photodiode, and precharges it to  $V_{\rm pixel}$ . After this reset, any light on the pixel will generate a current in the photodiode that will decrease its precharged voltage, thus integrating the current. At the end of each integration period, the voltage decrease is read out and the photodiode is again reset to  $V_{\rm pixel}$ , as indicated in Figure 2-7b.

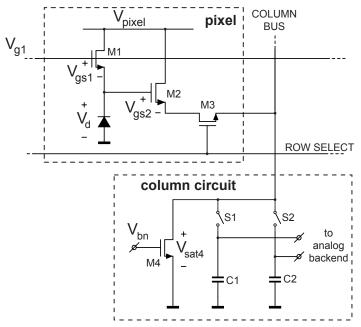

In Figure 2-7c, the timing of the readout operation is shown in more detail. For this readout, two transistors M2 and M3 are integrated into the pixel. Because three transistors are used, a pixel with a photodiode is often called a *3T pixel*. Transistor M3 is used as a switch that connects the pixel circuit to the column circuit via control line *row select*. This control line connects not one, but a full row of pixels to the set of column circuits, as the readout is performed on a row-by-row basis. When a pixel is connected to a column circuit, transistor M2 inside the pixel is biased with current source I<sub>b</sub> inside the column circuit and functions as a source follower. The resulting single transistor amplifier outputs the voltage across the photodiode onto the column bus with a gain close to unity.

Figure 2-7: a) Analog front-end circuit of a CMOS Imager using a photodiode b) Timing diagram of the integration of photocurrent c) Detailed timing diagram of the front-end readout operation

An important problem of the front-end is that transistor M2 has to be small enough to fit inside a pixel, which means that its parameters will spread a lot, resulting in a large pixel-to-pixel mismatch. If uncorrected, such mismatch would lead to large offsets that would be visible in the image. Moreover, transistor M2 will also have a relatively high 1/f noise because of its small size. To correct for this problem, a double sampling is applied, which is implemented using capacitors C1 and C2 and switches S1 and S2 located inside the column circuit. Firstly, the light-dependent photodiode voltage is sampled using C1 and S1. This voltage contains both signal and offset and 1/f noise. Next, the photodiode is reset using transistor M1 and the resulting reset voltage is sampled onto capacitor C2 using switch S2. This reset voltage contains the offset and 1/f noise of the transistor; therefore by subtracting this sample from the signal sample, the offset and 1/f noise is cancelled out.

It is crucial to understand that the above-described double sampling that corrects for offset and 1/f noise does not correct for kT/C noise generated when the pixel is reset. As discussed in sub-section 2.2.1, each photodiode reset samples kT/C noise onto the photodiode capacitance. Therefore, in our example, both the signal and the reset sample contain reset noise, and therefore it is often assumed that the subtraction of these samples cancels the reset noise. However, the subtraction of the samples does not cancel reset noise, as the reset noise in the two samples is not correlated. This can be understood by realizing that a reset operation is performed between the two sampling instances. With this reset operation, a new reset noise sample is taken, and therefore, the second sample has a different reset noise sample from the first sample. As a result, uncorrelated kT/C noise is subtracted, which actually leads to an increase of this reset noise with a square root of two. In order to distinguish the double-sampling operation described in a 3T pixel structure described above from a 'true' correlated double-sampling, where reset noise is compensated as well, the double sampling operation is usually called double-delta sampling (DDS).

# 2.3.2 Photogate/Pinned Photodiode Front-End Readout Structure

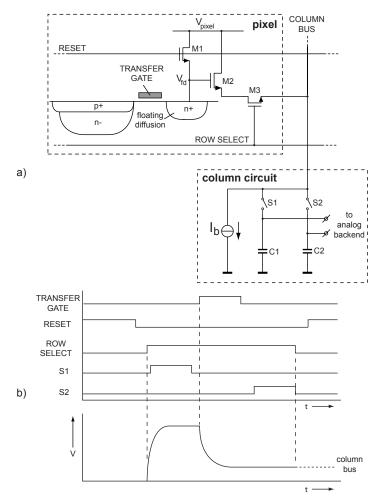

The front-end readout of imagers equipped with photogates [2.10-2.12] or pinned photodiodes is very similar to the readout operation

Figure 2-8: a) Analog front-end circuit of a CMOS imager using a pinned photodiode. b) corresponding timing diagram of the readout operation

described above. Figure 2-8a depicts the front-end circuit with a pinned photodiode and Figure 2-8b shows the corresponding timing diagram. As can be seen from the figure, the readout circuit itself is identical to the photodiode readout. Because of the addition of the transfer gate, photogate or pinned photodiode pixels are often called a *4T pixels*. The difference with a 3T pixel front-end is in the timing of the readout. As explained in sub-section 2.2.2, the floating diffusion is reset immediately before the

readout operation. In practice, it is advantageous to keep resetting the floating diffusion when it is not read out, as illustrated in the figure. This continuous reset can prevent an artefact called *blooming* when the sensor is exposed to a large amount of light. After the reset signal is made low, a first sample is taken using switch S1 and capacitor C1. This sample contains the kT/C noise generated with the reset of the floating diffusion, as well as offset and 1/f noise of the source follower transistor M2. Next, the transfer gate is pulsed, which quickly transfers the integrated photo-charge from the pinned photodiode to the floating diffusion. After this transfer is complete, a second sample is taken using switch S2 and capacitor C2. The second sample contains the signal, plus kT/C noise from the floating diffusion as well as offset and 1/f noise from M2.

As was explained in sub-section 2.2.2, the crucial advantage of photogates and pinned photodiode is the quick transfer of charge from the photosensitive element itself onto the floating diffusion. This allows the reset of the floating diffusion to be performed before the reading out the first of the two samples. As a result, the kT/C noise generated with the reset is correlated between the two subsequent readout samples, and is therefore cancelled together with the offset and 1/f noise of source follower M2. This results in a significantly lower noise level compared to a readout operation with a 3T pixel structure. Nonetheless, there are several noise sources and other non-idealities in a 4T pixel front-end that limit the performance of the sensor. These front-end performance limitation will be discussed in detail in chapter 3.

# 2.4 Back-End Analog Signal Processing

As described in the architectural overview of section 2.1, the function of the back-end of the analog signal processing chain is to read out the sampled signals inside the column and convert them in the digital domain. In this section, both sub functions will be discussed. In sub-section 2.4.1, the analog readout of the column will be detailed. Subsequently, the A/D conversion will be briefly discussed in sub-section 2.4.2.

#### 2.4.1 Column Circuit Readout

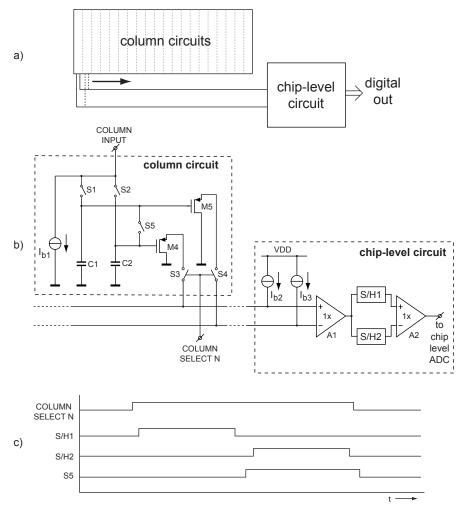

As described in section 2.3, the front-end readout circuit reads-out the pixel on a row-by row basis, reading out two samples per pixel that are stored on capacitors in each column circuit. These sampled voltages have

to be read-out from the column circuits and subtracted from each other to cancel offset, 1/f noise, and (when a 4T pixel is used) reset noise. Figure 2-9a depicts a simplified block diagram of the column and chip-level circuits. Each column circuit is consecutively connected to a common two-wire analog bus that connects it to the chip-level circuit. As discussed in section 2.2, the column decoder (not shown in the figure for clarity) outputs control signals to this end. In Figure 2-9b, detailed column

Figure 2-9: a) Block diagram showing the consecutive readout of columns b) Detailed column and chip-level readout circuit c) Corresponding timing diagram

and chip-level circuits are shown that perform the column readout [2.11][2.13]. As explained in the previous section, switches S1 and S2 and capacitors C1 and C2 are used to sample the front-end outputs, while current source Ib1 biases the front-end of the readout circuit. The remainder of the column circuit, consisting of transistors M4 and M5, and switches S3-S5 are used for reading out the column. The column circuit is connected to the common output rail using switches S3 and S4 that are controlled by the *column select* N input, which is output by the column decoder (not shown). This connects bias currents I<sub>b2</sub> and I<sub>b3</sub> located inside the chip-level circuit to transistors M4 and M5 that operate as source followers. These output the sampled voltage stored on C1 and C2 onto the common output rail. Differential amplifier A1 inside the chip-level reads out the common output rail and subtracts both outputted voltages. The output of amplifier A1 is sampled on sample-and-hold circuit S/H1. As explained in the previous section, the subtraction performed by amplifier A1 cancels the offset, 1/f noise and (in case of a 4T pixel front-end) reset noise of the front-end. Unfortunately, there is another source of offset in the circuit, caused by mismatch between source followers M4 and M5. This still leads to an offset error in the output sample sampled on S/H1. To correct for this offset, another readout is performed with switch S5 closed. Since this switch shorts the source follower inputs together, only the differential offset voltage caused by the source followers' mismatch is output. This offset is stored on sample-and-hold circuit S/H2. Finally, amplifier A2 subtracts the voltage stored in S/H1 and S/H2, thereby cancelling out the offset voltage of the source followers M1 and M2. This final output can be fed into the A/D converter, which will be discussed in the next section.

# 2.4.2 Chip-Level A/D Conversion

Since the analog chip-level readout circuit presented in the previous section condenses the parallel column-level front-end contain double samples into a single analog output, a chip-level A/D converter used in CMOS imagers is not different from standard ADC architectures that are known in literature. Therefore, the A/D converter itself will not be discussed in detail here. The main requirements for the A/D converter are a resolution of about 10-12 bits, depending on the sensor and interface electronic performance. As noted in the previous section, if a modest imager resolution of 500 x 500 pixels operating at 30 frames/second is considered, the column circuit read-out circuit that is connected to the

ADC input should read out each column within 100ns. This means that the ADC should have a sampling speed of at least 10MSPS.

The combination of modest resolution and relatively high speed favors the application of a Nyquist-rate ADC. In particular, the pipeline ADC architecture is very well suited for the application, as it enables a power efficient readout while requiring relatively little chip area.

As discussed in section 2.1, the back-end readout circuit described here has to work at a relatively high speed. For a modest imager resolution of about 500 x 500 pixels at a frame rate of 30 images per second, the time available to read out all column circuits is roughly 50µs. Therefore, each column needs to be read-out in 100ns, during which two sampling operations have to be performed, of which the result has to be digitized within the next 100ns. While this is easily possible with the number of pixels mentioned, the rapid development of ever-higher resolution imagers in recent years have made the chip-level readout structure more and more difficult. Therefore, in chapter 4, an alternative readout structure will be discussed, where an A/D converter is located inside every column. This eliminates the need for a high-speed analog readout by a chip-level circuit and is one of the main focus points of this thesis.

# 2.5 Advanced Analog Signal Processing Techniques

In the previous two sections, an overview was given of a typical analog signal processing chain. While this structure forms a basis for understanding analog signal processing in CMOS imagers, many refinements and/or alternatives to the typical solution were published over the years. In this section, a brief overview is provided of alternative and advanced analog signal processing techniques.

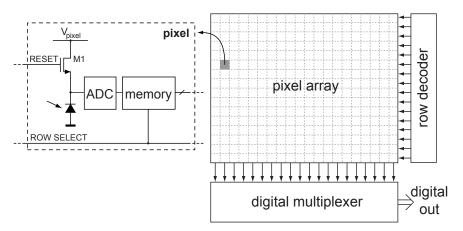

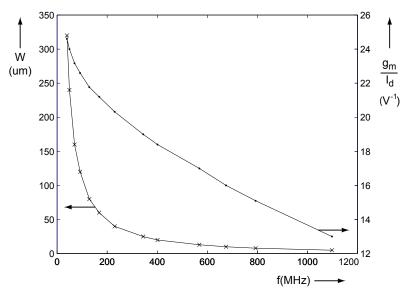

# 2.5.1 Sharing of Readout Circuitry Among Pixels

While the pixel circuit with a pinned photodiode features an excellent performance, it requires 4 transistors in each pixel. These transistors decrease the amount of pixel area available for the light sensitive part, and therefore reduce the *fill factor* of the pixel, i.e. the ratio of photosensitive area to total pixel area. In order to enable CMOS imagers with a higher resolution, the pixel size has been steadily decreasing to accommodate

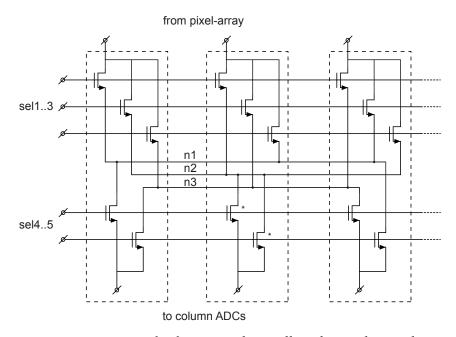

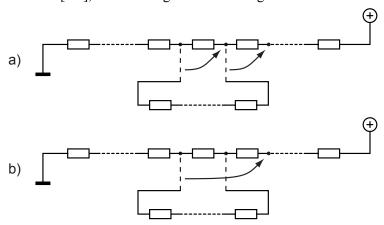

Figure 2-10: Shared pixel circuitry concept: a) 1.75 transistor/pixel concept published by Matsushita b) 1.5 transistor/pixel concept by Canon

more pixels on the same chip area. This reduces the fill factor, and therefore reduces the sensitivity and dynamic range of the pixels.

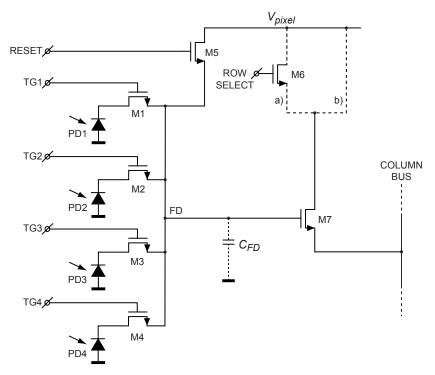

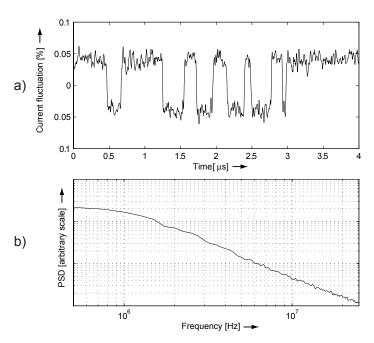

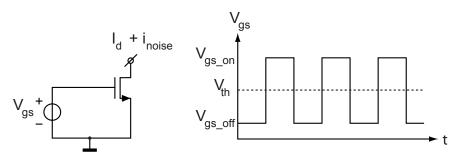

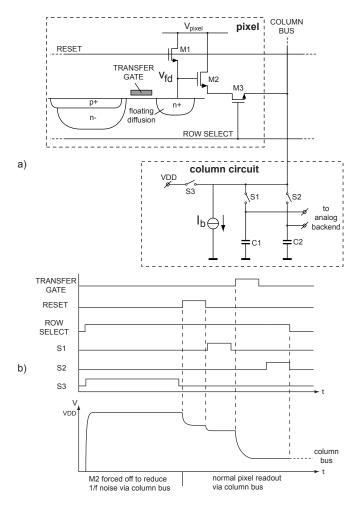

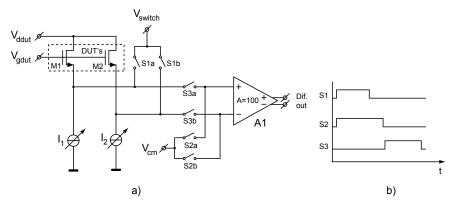

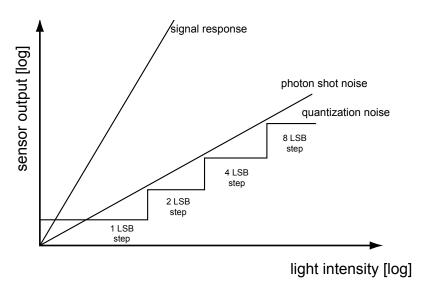

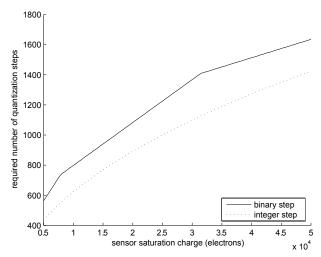

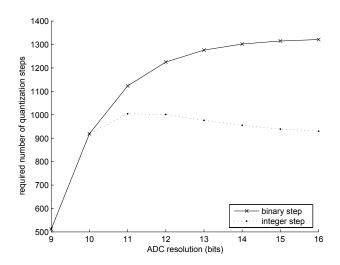

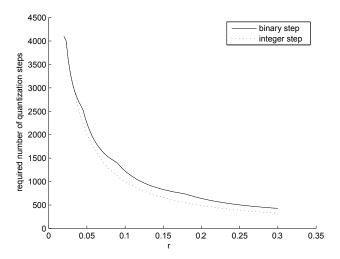

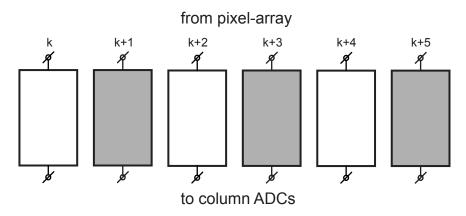

In 2004, Matshushita [2.14] and Canon [2.15] both presented a solution for this problem. In both cases, some of the transistors that are required for readout are shared among several pixels. This is illustrated in Figure 2-10. As can be seen from the figure, 4 pixels share some of the readout circuitry with one another. Each pixel has a pinned photodiode PD1..PD4 with a transfer gate M1..M4 similar to the structure shown in Figure 2-6. In contrast to a 4-transistor pixel however, the 4 pixels share one common floating diffusion (marked "FD" in the figure). This floating diffusion is reset with transistor M5 and read out with source follower M7. In the solution proposed by Matsushita [2.14], the source follower is connected to the column bus with another transistor M6 controlled by a row-select signal as discussed in section 2.3<sup>1</sup>. Therefore, as shown in