# Semantics for Tydi

The development of a formal foundation

for the Tydi hardware stream specification.

Harold Struik

# Semantics for Tydi

The development of a formal foundation

for the Tydi hardware stream specification.

by

Harold Struik

to obtain the degree of Master of Science

at the Delft University of Technology,

to be defended publicly on Friday the 30th of January.

Student number: 5651573

Project duration: 1 January, 2025 – 30 January, 2026

Thesis committee: Prof. Peter Hofstee, TU Delft, IBM, supervisor

Prof. Soham Chakraborty TU Delft

Zaid Al-Ars, External

*This thesis is confidential and cannot be made public until February, 2026.*

Cover: CERN computing centre in 2017. Copyright: Robert Hradil,

Monika Majer/ProStudio22.ch 2017-04-25

# Summary

The Tydi (Typed Dataflow Interface) specification was introduced to bridge a gap in the High Level Synthesis (HLS) domain, enabling engineers to easily define component interfaces, mapping complex, dynamically sized data structures onto hardware streams. While Tydi successfully defines the static bit-level layout, it lacks a formal description for the dynamic procedure of mapping elements in a stream onto hardware lanes. This ambiguity has hindered the development of Tydi related tools and its integration in HLS frameworks. This work introduces a layered formalism for Tydi, centred around a modular operational semantics. It defines a two-tiered type system that separates a flexible user-facing syntax, from a canonical, hardware-oriented representation, strengthening the link between a type's composition and runtime behaviour. The dynamic mapping is implemented by a configurable set of small-step semantics rules. These are derived from a user provided set of formal properties, replacing the specifications monolithic complexity levels with fine-grained control over interface logic. We define key structural determinism and progress metrics for the formalism, enabling the verification of interface implementations for streams of arbitrary type. This foundation enables developers to define verifiably correct, typed hardware stream interfaces as easily as software, while retaining control over critical engineering trade-offs. A simulator of the semantics has been implemented, and provides empirical verification of the formalism and an insightful overview of the parsing logic [48].

## Structure of the Thesis

This thesis is organized into seven chapters that progressively develop the formal foundation for the Tydi specification.

**Chapter 1: Introduction and Background.** This chapter introduces the data streaming paradigm and the specific challenges of designing stream interfaces in hardware. It presents the core concepts of the existing Tydi specification, including the distinction between logical and physical streams and the concept of “streamspace” used to map data over time.

**Chapter 2: Analysis: Towards a Formal Foundation.** An analysis of the status quo identifies a “specification gap” regarding the runtime behaviour of Tydi interfaces, placing the focus on the loss of hierarchy information between physical streams. The chapter evaluates existing formalisms (e.g. dependent type theory, operational semantics) and proposes a tiered formal framework. This framework separates the interface specification from its implementation, and the static and dynamic domains of the formalism.

**Chapter 3: The Formalism.** This chapter defines the core mathematical components of the proposed solution. It introduces: 1) The Normalisation Function ( $\llbracket \cdot \rrbracket$ ) to reduces the user exposed top-level type to a normalized type in Canonical Form, removing semantically ambiguous type compositions. 2) The Streaming Context ( $\Gamma$ ), is a stateful device encapsulating buffers and the parse tree. 3) Interface Properties and Semantics, which use small-step operational rules to define the mapping procedure, interacting with the streaming context. 4) The Implementation Complexity Metric (ICM), a method to quantify the logic cost of specific interface configurations.

**Chapter 4: Examples and Empirical Validation.** The functionality of the formalism is demonstrated through a full parsing example. The chapter also details the *TinyTydi* simulator, a Python-based tool implemented to provide empirical verification of the normalisation and operational semantics.

**Chapter 5: Verification of the Formalism.** This chapter provides formal proofs to verify the correctness of the framework. It proves that the normalisation function always produces Canonical Form, that parse trees terminate properly, and that the core ruleset adheres to Structural Determinism and Progress (finite parsing).

**Chapter 6: The Union Type: Handling Variant Data.** The formalism is extended to include the `Union` type, addressing the complexity of variant data in hardware. It introduces a “deferred parsing commit” mechanism to maintain determinism and synchronicity between tag and data streams.

**Chapter 7: Conclusion and Discussion.** The final chapter summarizes the research contributions. It discusses the implications for the Tydi specification, such as the potential for automated interface generation and verification, and outlines future work.

# Contents

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| <b>Summary</b>                                                    | <b>i</b>  |

| <b>1 Introduction and Background</b>                              | <b>1</b>  |

| 1.1 The data streaming paradigm . . . . .                         | 1         |

| 1.2 Designing stream interfaces in hardware . . . . .             | 2         |

| 1.3 The Tydi specification . . . . .                              | 3         |

| 1.3.1 Analogy: The Universal Lego Machine . . . . .               | 4         |

| 1.3.2 The Core Concepts of Tydi . . . . .                         | 4         |

| <b>2 Analysis: Towards a Formal Foundation for Tydi</b>           | <b>8</b>  |

| 2.1 Status quo and problem statement . . . . .                    | 8         |

| 2.2 Requirements for a formal foundation . . . . .                | 9         |

| 2.3 Evaluation of existing formalisms . . . . .                   | 10        |

| 2.4 Proposal for a tiered formal framework . . . . .              | 12        |

| 2.4.1 Types, normalisation, and streaming context . . . . .       | 12        |

| 2.4.2 Interface Properties and Semantics . . . . .                | 13        |

| 2.4.3 Connecting the layers of the formalism . . . . .            | 15        |

| <b>3 The Formalism</b>                                            | <b>17</b> |

| 3.1 Types, Normalisation and the Streaming Context . . . . .      | 17        |

| 3.1.1 Top-Level and Normalised Types . . . . .                    | 17        |

| 3.1.2 Normalisation Function . . . . .                            | 17        |

| 3.1.3 The Streaming Context . . . . .                             | 18        |

| 3.2 Interface Properties and Semantics . . . . .                  | 18        |

| 3.2.1 Interface Properties . . . . .                              | 19        |

| 3.2.2 Default interface semantics . . . . .                       | 20        |

| 3.3 Named Property-Sets . . . . .                                 | 20        |

| 3.3.1 The Core . . . . .                                          | 20        |

| 3.3.2 Complexity Levels . . . . .                                 | 21        |

| 3.4 The Implementation Complexity Metric . . . . .                | 22        |

| 3.4.1 From Semantics to Automata . . . . .                        | 22        |

| 3.4.2 Defining the Metric . . . . .                               | 23        |

| 3.4.3 Case Study: The Chat Message . . . . .                      | 23        |

| <b>4 Examples and Empirical Validation</b>                        | <b>25</b> |

| 4.1 Full chat message parsing example . . . . .                   | 25        |

| 4.2 Empirical Validation with the TinyTydi Simulator . . . . .    | 26        |

| <b>5 Verification of the Formalism</b>                            | <b>27</b> |

| 5.1 Correctness of Normalisation . . . . .                        | 27        |

| 5.2 Well-formed tree termination . . . . .                        | 28        |

| 5.3 Proving the Core . . . . .                                    | 29        |

| 5.3.1 Structural Determinism . . . . .                            | 29        |

| 5.3.2 Progress and Termination . . . . .                          | 29        |

| 5.4 Connecting the results . . . . .                              | 30        |

| 5.4.1 Proving other property-sets . . . . .                       | 30        |

| <b>6 The Union Type: Handling Variant Data</b>                    | <b>32</b> |

| 6.1 Design considerations for variant types in hardware . . . . . | 32        |

| 6.2 Formalism extension for the Union . . . . .                   | 37        |

| 6.2.1 Normalisation and Canonical Form . . . . .                  | 37        |

---

|                                       |                                                   |           |

|---------------------------------------|---------------------------------------------------|-----------|

| 6.2.2                                 | Default Semantics proposal . . . . .              | 38        |

| <b>7</b>                              | <b>Conclusion and Discussion</b>                  | <b>40</b> |

| 7.1                                   | Research overview . . . . .                       | 40        |

| 7.1.1                                 | Evolution of the Research Scope . . . . .         | 40        |

| 7.1.2                                 | Summary of Contributions . . . . .                | 41        |

| 7.2                                   | Related Work and Positioning . . . . .            | 41        |

| 7.2.1                                 | The Tydi Ecosystem . . . . .                      | 42        |

| 7.3                                   | Future Work . . . . .                             | 42        |

| 7.3.1                                 | Implications for the Tydi Specification . . . . . | 42        |

| 7.3.2                                 | Practical considerations . . . . .                | 43        |

| 7.4                                   | Discussion . . . . .                              | 44        |

| <b>References</b>                     |                                                   | <b>45</b> |

| <b>A Detailed Simulation Trace</b>    |                                                   | <b>49</b> |

| <b>B Full Parsing Example Diagram</b> |                                                   | <b>51</b> |

# Introduction and Background

This chapter will introduce the data streaming paradigm, the challenges it presents for hardware development and how Tydi aims to improve this. The last section presents an analysis of the shortcomings of the specification, laying the foundation for the core contributions of this work.

## 1.1. The data streaming paradigm

Early work on information systems began to recognize that data was no longer delivered in neat, static batches, but arrived continuously, unstructured, and in volumes too large for manual sorting. Figure 1.1 shows a quaint illustration from a 1992 Xerox paper, introducing Tapestry, a system for managing streams of documents in the advent of "electronic mail". In the same year, these researchers at Xerox built upon their experience of Tapestry to develop the notion of continuous queries. Such queries remain active over an append-only stream, only reporting results whenever new data satisfies a condition, effectively treating query evaluation as an ongoing process rather than a discrete event [49]. It introduces a rudimentary model of computation with streams of messages sent across interfaces, and providing semantics for composing and reasoning about such flows. These early systems mark the beginning of the data streaming paradigm, where computation is designed around the realities of unbounded, evolving information flows, rather than static evaluation.

**Figure 1.1:** From the 1992 paper: A mail operator, overwhelmed by piles of unstructured messages, depicting the practical pressures that motivated automated and continuous filtering rather than periodic, one-shot processing [23].

As detailed in a recent comprehensive survey by Frakoulis et al. [19], the evolution of the field can be categorised into three distinct generations, each addressing the growing complexity of data velocity and volume.

### First Generation (2000–2010): The Era of DSMS.

Although the notion of continuous queries was introduced by Tapestry in 1992, much of the foundational formalisation and system design for stream processing occurred in the late 1990s and early

2000s, where the field diverged from standard database management into Data Stream Management Systems (DSMS). Researchers recognized that the "one-size-fits-all" approach of traditional relational databases could not meet the low-latency requirements of real-time applications [47]. Systems such as *Aurora*, *Borealis*, and *TelegraphCQ* formalised the requirements for stream processing, establishing that systems must keep data moving and allow for "windowing", the ability to perform computations over finite slices of an infinite stream [1, 11]. While these systems successfully introduced sliding-window aggregation and continuous SQL-like queries, they targeted primarily on architectures that relied on increasing machine performance instead of parallelism, and maintained state in abstract, internal structures known as "synopses" [19].

**Second Generation (2011–2019): Scale-Out and Dataflow.** The paradigm matured significantly with the advent of the "Big Data" era and the introduction of the Dataflow model. Influenced by the scalability of MapReduce [17], focus shifted to distributed architectures. This modern approach decoupled the execution engine from the programming model, allowing developers to focus on *what* is being computed rather than *how* the stream is physically managed. The work by Akidau et al. clarified the critical distinction between *event time* (when an event occurred) and *processing time* (when the system observed it), providing a framework for balancing correctness, latency, and cost [3]. These systems (e.g., Apache Flink, Spark Streaming, Google Cloud Dataflow) introduced sophisticated state management, allowing for large, partitioned, and persistent user-defined state [10, 54].

**Third Generation (2020–Present): Edge and Hardware Acceleration.** We are currently witnessing a shift toward the third generation, characterized by the decentralisation of pipelines to the Edge and the use of specialized hardware. As noted by Zhang et al. and emphasized in recent surveys, the need for ultra-low latency is driving the adoption of hardware accelerators, such as FPGAs and GPUs, directly into the streaming pipeline [55, 19]. Projects like *Fleet* [50] demonstrate the potential of processing streams directly on FPGAs. While the software domain enjoys elegant, high-level frameworks [53, 20], the hardware domain is still lacking in standardized, type-safe interfaces for describing these complex data flows [22, 8, 13]. Recent formal work in the software domain has also addressed the potential of hardware oriented adaptations of stream processing formalisms [28, 31]. This sets the stage for the introduction of Tydi (Typed Dataflow Interface), an open hardware stream specification [40]. It expresses how complex, dynamically sized data structures can be exchanged between components using streaming interfaces, based on an intuitive, hardware-oriented type system.

## 1.2. Designing stream interfaces in hardware

Before we dive into Tydi, it is important to substantiate *why* working with streams is particularly difficult in the hardware domain. Designing hardware is fundamentally about managing spatial resources and enforcing timing constraints. Unlike software, where memory and dynamic containers can hide layout and temporal ordering, hardware requires explicit decisions about how many wires exist, their widths, where data is stored, and exactly when it is valid. In the domain of dataflow programming, channels that connect components are usually implemented as *streams*: FIFO, point-to-point links where transfers flow in order. Components that consume and produce streams, "streamlets", therefore need interfaces that describe both the shape of the data and the timing of its elements. A transfer is a set of data elements, sent simultaneously over a single physical stream. Complex, dynamically sized data, (e.g. a chat-message comprised of a single timestamp and a variable length sequence of characters), cannot be exposed as a single fixed-width port, so the data must be serialized. This serialisation requires designers to make various non-trivial design considerations: how to break the structure into smaller chunks of data; *primitives*, how to indicate sequence boundaries, how to drive the validity signals, and how to propagate back-pressure when downstream logic stalls. These tasks are repetitive and error-prone.

This difficulty is illustrated by the Fletcher framework, which predates the Tydi specification and directly motivated its development [37, 38]. Fletcher demonstrates that, even when a high-level software schema (Apache Arrow) precisely describes complex, nested data structures, translating this description into efficient hardware stream interfaces requires non-trivial interface logic. In Fletcher, a rudimentary form of Tydi is used to automatically generate interfaces that decompose complex data types into multiple coordinated streams, handling serialisation, boundary signalling, buffering, and back-pressure explicitly. While this approach proved that such interfaces can be generated automatically, it also illus-

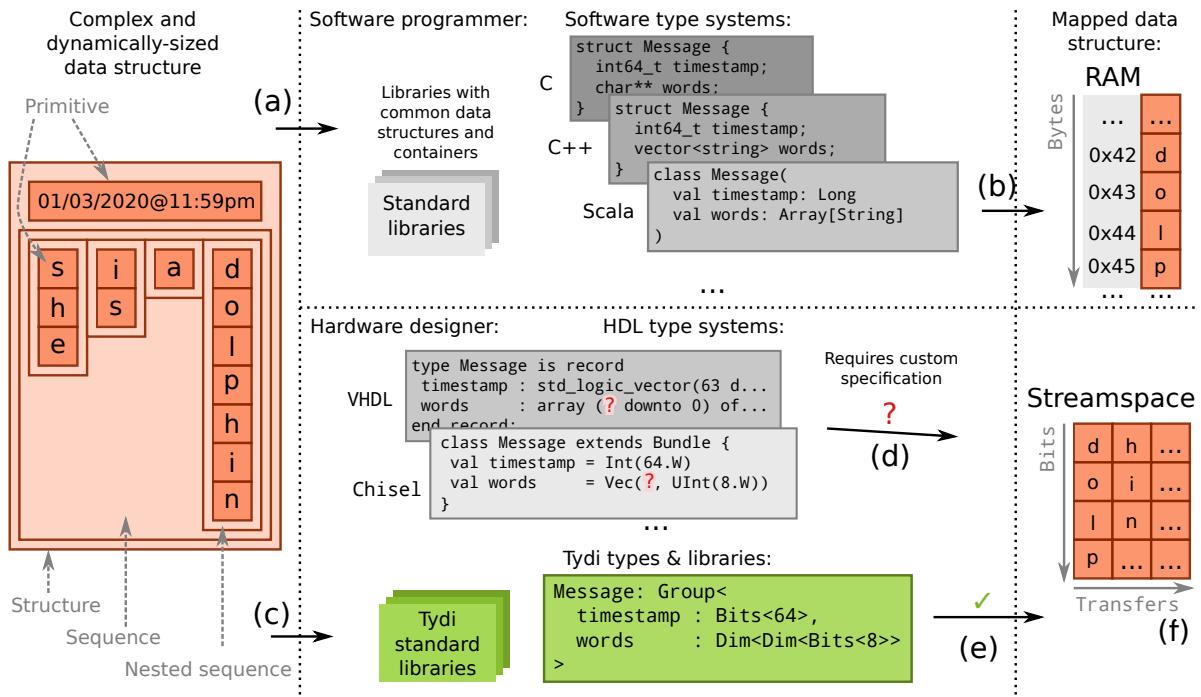

**Figure 1.2:** "To implement a data structure, programmers choose some types and containers, helped by language constructs and libraries. (a) Runtime engines and compilers take care of the mapping to RAM. (b) The same for contemporary HDLs (c) is prevented because dynamically sized structures are not inherently supported. When mapping to hardware streams (d) designers customize solutions to transport data structures over multiple stream transfers. Tydi is a specification that clearly and intuitively provides a mapping (e) and predefined containers for common types" [40].

trates how relatively trivial software data structures, already require complex implementations.

To implement stream interfaces, designers can opt for low-level bit protocols or resort to designing their own protocols, each requiring explicit boundary markers, parsing logic, and buffering. HLS tools handle simple aggregates but typically generate interfaces for primitive types only. Expressing more complex structures would still require manual control logic and custom conventions. As a result, interfaces accumulate implicit assumptions about packing, alignment, ordering, and throughput settings, limiting reuse and making composition difficult. Additional engineering considerations further complicate the implementation of these interfaces. For example, throughput scaling, alignment rules, per-lane strobes, and control-signal complexity; all of these interact with area and timing. Additionally, a wider transfer may reduce cycle count but increases wires; fine-grained strobes ease packing but will require more control logic, etc. These trade-offs may be revisited for every interface in a design. Because of this, hardware stream-processing systems are costly to design and maintain. Interfaces are bespoke, converters proliferate, and correctness relies on matching many low-level conventions. A standardised, type-oriented description of both the spatial layout and temporal behaviour, combined with explicit engineering parameters such as the number of lanes, can greatly reduce this burden. The Tydi specification intends to provide exactly this: a mapping from data types to well-defined stream interfaces that can be implemented consistently, and reused across components.

### 1.3. The Tydi specification

Due to the elaborate process needed to design an interface for a component that interacts with streams, Tydi was introduced to significantly improve this procedure, as an open, hardware-oriented specification for streaming complex, nested data types. Given a high-level logical type and a set of engineering parameters, Tydi prescribes both the spatial layout of signals on a component interface and the temporal mapping of data onto transfers over that interface. The original work illustrates its value by comparing the software and hardware perspectives of mapping a chat message to either memory, or a hardware stream, shown in figure 1.2. This chat message will be a recurring example throughout this work, comparing implementations and illustrating the impact of mapping procedures.

### 1.3.1. Analogy: The Universal Lego Machine

To build intuition for the challenges Tydi addresses, consider a Lego assembly machine as shown in figure 1.3. Suppose the machine is designed to build towers. Each tower always begins with a single foundation plate, followed by an arbitrary number of identical tower segments. The instruction booklet describes this structure, but the number of segments is not known in advance. To feed this machine, the interface must expose holes shaped like the required pieces: one hole for the foundation plate and one hole for tower segments. Unlike a standard Lego set where all pieces are available at the start, here the tower may be of any height, making it impossible to pre-allocate storage for "all" pieces; The machine must start building as soon as the first pieces arrive.

Figure 1.3: The lego tower construction box, operating on streams of tower segments, building towers of arbitrary height. The machine must start building as soon as the first pieces arrive.

This illustrates a critical *temporal* constraint: the order matters. The foundation plate must arrive first; only after it is accepted can the machine consume segments. The interface must therefore communicate not only *what* piece is provided, but also *when* it is valid, where the boundaries between towers lie, and when a tower is complete. In hardware, complex, nested, and variably sized data structures cannot be represented as a single fixed-width port. They must be serialized into elements arriving over time, with explicit signals marking structure and validity. The Tydi specification provides the formal "instruction booklet" to describe these shapes and when they are needed. If every layer of the tower requires 4 pieces, it is possible to expand the interface to 4 holes, however, if the component providing the pieces can only provide 2 pieces at a time, this would be a waste of resources. This illustrates how performance and resource requirements can further impact designing the interface.

For a normal Lego build, the steps of the instruction booklet describe, when which pieces are needed. For the Tydi example, you might need to stay on the same page of the Lego booklet, repeating the same steps until the supply of some types of pieces are used up, and then continuing with the rest of the booklet. This is however where the Lego analogy falls short, since stream interfaces may have much more elaborate conditions, requiring "skipping through the instruction booklet" in arbitrarily complex ways. Still, it highlights that interacting with streams in hardware is not an obvious procedure, especially when it needs to be defined using finite, statically known resources.

### 1.3.2. The Core Concepts of Tydi

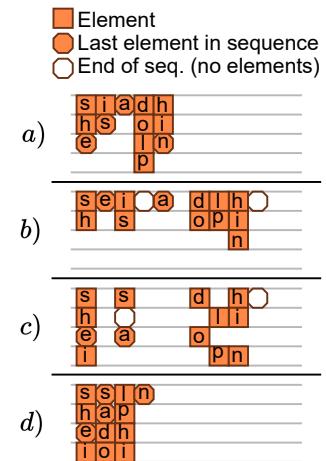

Similar to how Apache Arrow specifies data layouts in memory, Tydi specifies data layouts "in-flight" [6]. It defines a two-layer interface model that separates abstract stream descriptions from their concrete hardware realisation. At the top layer, a *logical stream* specifies the structure and behaviour of data exchanged between components, expressed using a small, hardware-oriented type system. At the lower layer, one or more *physical streams* implement this specification as concrete bundles of wires, complete with handshake, data, and control signals. This separation allows designers to reason about complex, dynamically sized data structures at a high level, while delegating bit-level layout and protocol details to a synthesis algorithm. Conceptually, the logical stream defines *what* data is communicated and how it is structured, while the physical stream defines *how* this contract is realised in hardware. Tydi defines "streamspace" as the 2d plane represented by the physical dimension of parallel lanes or wires, and the temporal dimension of transfers. An example of streamspace mappings is shown in figure 1.4.

**Logical streams.** Logical streams are defined using the Tydi type system, which distinguishes between data layout and temporal behaviour. Data layout is described using a small set of types: Null,

Figure 1.4: Comparing how 2D char seq.  $\{\{\text{she}\}, \{\text{is}\}, \{\text{a}\}, \{\text{dolphin}\}\}$  can be mapped to streamspace, where a) terminates inner sequences, b) allows delayed termination signals, c) no inner seq. termination + delayed signalling, and d) no inner seq. termination and enforced packing.

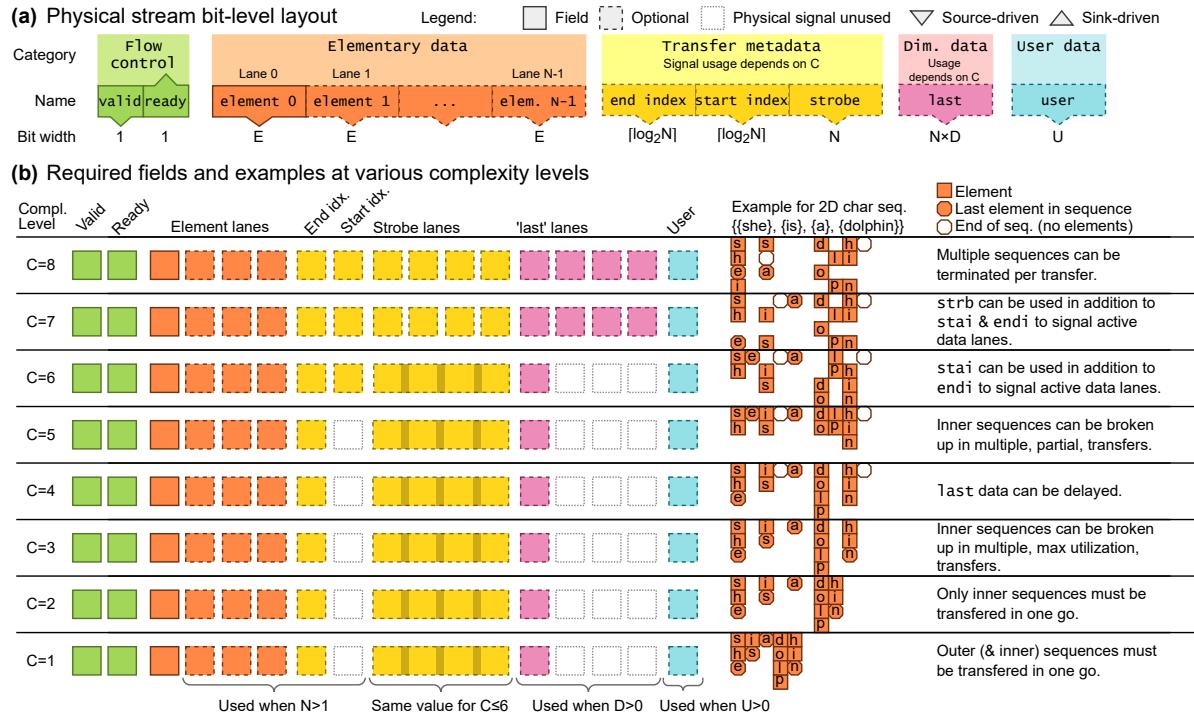

**Figure 1.5:** This figure shows (a) the layout of lanes for signals and data carrying wires, and (b) how each complexity level impacts the potential transmission of a 2 dimensional char array [15].

representing a singleton value; Bits( $b$ ), denoting a bit vector of width  $b$ ; Group, a product type containing named fields; and Union, a sum type representing a tagged variant. These element types describe how data is structured, but are agnostic to how it is transferred over time. Temporal structure is introduced by the logical Stream type of the form:

$$\text{Stream}(T_e, t, d, s, c, r, T_u, x)$$

It represents a sequence of elements of type  $T_e$ , together with a number of engineering parameters that determine its runtime behaviour. The *throughput* parameter  $t$  specifies the minimum number of elements transferred per handshake, and determines the degree of parallelism exposed at the interface. The *dimensionality*  $d$  captures the nesting depth of sequences, governing how many independent sequence boundaries must be represented. The *complexity* parameter  $c$  encodes ordering and packing guarantees made by the source, trading implementation simplicity against flexibility. Lower complexity levels impose stricter constraints on transfer patterns, while higher levels permit more relaxed scheduling. Synchronicity represents the relation between the dimensionality information of the parent stream and the child stream. The user defined data can be used to further customise the contract between source and sink. Figure 1.5 shows how a 2 dimensional char array can be transmitted for various complexity levels. Through recursive composition of Stream, Group, and Union types, logical streams can express arbitrarily complex, nested, and dynamically sized data structures, including inter-stream relations. The chat message example in figure 1.2 is typed using the Dim shorthand notation of a specific logical stream node, which adds an additional dimension to its subtype. This gives  $\text{Group}\langle \text{Bits}\langle 64 \rangle, \text{Dim}\langle \text{Dim}\langle \text{Bits}\langle 8 \rangle \rangle \rangle \rangle$ , defining a group of a 64-bit primitive, together with a 2 dimensional sequence of 8 bit primitives, representing the timestamp and chat message respectively.

**Physical streams.** A physical stream is the concrete hardware realisation of a logical stream, defined:

$$\text{PhysicalStream}(E, N, D, C, U)$$

Here  $E$  denotes the element payload fields,  $N$  the number of parallel element lanes,  $D$  the dimensionality,  $C$  the complexity level, and  $U$  the user-defined transfer fields. A physical stream is implemented as a bundle of signals, all synchronous to a shared clock.

At its core, each physical stream includes a `valid/ready` handshake pair, which governs flow control between source and sink. The data payload is carried on the `data` signal, consisting of  $N$  lanes, each encoding one element of type  $E$ . Sequence boundaries are communicated using the `last` signal, which contains  $D$  termination bits per lane, one for each level of nesting. Additional signals such as `stai`, `endi`, and `strb` provide fine-grained control over which lanes are active in a given transfer, enabling partial transfers and relaxed packing when permitted by the selected complexity level. An optional `user` signal carries auxiliary control or metadata alongside the data stream.

Not all signals are required in every configuration. Their presence and interpretation depend systematically on the parameters  $N$ ,  $D$ ,  $C$ , and  $U$ . In particular, increasing the complexity level enables progressively more flexible lane utilisation and sequence termination behaviour. Figure 1.5 provides an overview of which signals are used at each complexity level and how their streamspace representation evolves.

**Streamspace.** Underlying both logical and physical streams is the notion of *streamspace*. Rather than mapping data structures solely onto space (bits), Tydi models communication in a two-dimensional plane spanned by spatial resources (element bits and lanes) and temporal resources (stream transfers). Complex and dynamically sized data structures are therefore mapped not onto bit-vectors, but across multiple transfers over time. In this view, the logical stream defines the allowed complete streamspace representations of the data, where physical streams occupy specific regions of streamspace, with the relationships between regions on the plane delegated to the logical stream's responsibility. Streamspace provides the conceptual foundation for reasoning about nested sequences, parallelism, and ordering guarantees.

**Streamspace Types and the Container Library.** To facilitate concise and reusable descriptions of common data structures, Tydi introduces a set of streamspace types shorthand notation, and a standard container library. At the lowest level, shorthand notations such as `DIM`, `REV`, and `NEW` provide a more concise way to interact with the logical stream type.

- `DIM` introduces an additional dimension to its subtype:

$$\text{Dim}(T_e, t, c, T_u) \mapsto \text{Stream}(T_e, t, 1, \text{Sync}, c, \text{Forward}, T_u, \text{false})$$

- `REV` creates a physical stream that flows in the opposite direction of its parent, enabling request-response style interfaces:

$$\text{REV}(T_e, t, c, T_u) \mapsto \text{Stream}(T_e, t, 0, \text{Sync}, c, \text{Reverse}, T_u, \text{false})$$

- `NEW` introduces an additional physical stream at the same dimensional level, allowing independent streams to coexist without implicit ordering:

$$\text{NEW}(T_e, t, c, T_u) \mapsto \text{Stream}(T_e, t, 0, \text{Sync}, c, \text{Forward}, T_u, \text{false})$$

Building on these, the specification defines a library of container types that act as canonical mappings of familiar data structures, such as lists, vectors, structs, and variants, into streamspace. These containers are aliases for well-defined compositions of the underlying types.

**From Logical to Physical: Synthesis.** The connection between logical and physical streams is established by a synthesis algorithm defined in the specification. This algorithm traverses the logical stream type, extracts element and user fields, and computes the corresponding physical stream parameters. For each logical `Stream` node, the element type is flattened into a linear bit-level representation, the throughput parameter determines the number of lanes  $N$ , and the dimensionality and complexity parameters are carried over directly. The result is a canonical `PhysicalStream` description that prescribes the exact signal set and widths required for the interface.

This synthesis process is deterministic: any two tools or designers that start from the same logical stream type and parameters will derive bit-level compatible physical interfaces. By construction, this *should* eliminate the need for bespoke glue logic between independently developed components that adhere to the same Tydi specification. Additionally, when two interfaces are of the same logical stream type, but their properties differ, Tydi can assist their composition by synthesising the required glue logic.

**Putting it all together.** The core concepts of Tydi form an abstraction stack. Logical streams provide a precise, compositional description of complex data structures and their temporal behaviour. Physical streams realize these descriptions as concrete, parametrized hardware interfaces. The synthesis algorithm bridges the two layers, ensuring that high-level specification is properly lowered to its implementation. This separation of concerns is central to Tydi's goal: enabling reusable, type-safe, and verifiable stream interfaces, while preserving explicit control over performance and implementation complexity.

# 2

## Analysis: Towards a Formal Foundation for Tydi

### 2.1. Status quo and problem statement

Tydi successfully specifies how complex, dynamically sized data structures can be exchanged, by defining streaming interfaces based on an intuitive, hardware-oriented type system. However, there is a notable omission from the original specification, namely *how* a hardware interface must be implemented in order to adhere to the specification. To a certain extent this is to be expected, as such open hardware specifications are usually only prescriptive regarding the static layout of signals. However, Tydi also describes the temporal layout of data using its notion of *streamspace*. When two distinct parties develop interfaces in accordance with the specification, their implementations should be compatible for a matching type and complexity level. Any ambiguities in the specification inevitably result in occurrences where this is not the case.

The core problem arises from the lack of a formal description of the runtime mapping procedure. This omission has already hindered the development of Tydi-related tools and hardware utilities. Notably, the original authors have expressed that they attempted a more formal approach during the Fletcher development era, but abandoned it due to time constraints and complexity. The angle bracket notation for the type system is a quirk that originated from this attempt at a formalism.

Through further conversations with the original authors, I have identified that Tydi can be viewed as having three distinct layers: a high-level data structure specification, a low-level physical stream of wires, and a "mid-level" protocol layer. While the top and bottom layers are well-defined, their connection has been considered as a "gap" in the specification. More specifically, there are uncertainties regarding the transmission of data in nested streams, and how this is impacted by their inter-stream dependencies. The authors describe the current Tydi specification as a "factory" for interfaces: it is generic and flexible, but it lacks the prescriptive power to define exactly what a functioning hardware interface *should do* in complex scenarios, such as nested streams with interdependencies.

This indicates that the "hardware-oriented" type system does not provide intuitive assertions regarding how elements are actually transmitted. For example, when the existence of a `Group` type does not provide strong guarantees regarding how its fields are interleaved or concatenated over physical streams, any formalism interacting with the type must account for the larger structure by also evaluating the fields of the group. Allowing distinct types to correspond to equal *streamspace* mappings, (and thus technically compatible interfaces), is undesirable for verification.

The flexibility is a double-edged sword: while it enables standards such as JSON to be mapped to Tydi with ease, but it complicates the definition of a formal process for implementation; connecting the top to the bottom. The type of a Tydi stream remains only loosely coupled to its actual runtime behaviour, undercutting the effectiveness of its hardware-oriented nature. Therefore, a core challenge is to formally describe this "mid-level" runtime procedure such that it algorithmically determines an

interface implementation from a flexible Tydi type and its engineering parameters, providing a provable bridge between high-level data structures and low-level physical streams. This can be seen as the semantic domain of the interface definition: How can we infer how data is transmitted, from the structure of a stream's type?

## 2.2. Requirements for a formal foundation

Tydi's core ambition is to allow hardware designers to describe complex, nested, and dynamically sized data structures at a high level, while retaining precise control over how these structures are transmitted over streaming interfaces. The absence of a description of the runtime procedure, mapping the typed data to streamspace, is an awkward omission. While the Tydi type determines *what* data is communicated, and using which signals, it does not effectively describe *how* this communication is actually achieved.

In this context, a quote comes to mind, attributed to Mark Manasse in the *Types and Programming Languages* book by Benjamin C. Pierce: *“The fundamental problem addressed by a type theory is to ensure that programs have meaning. The fundamental problem caused by a type theory is that meaningful programs may not have meanings ascribed to them. The quest for richer type systems results from this tension.”* [41] It highlights how the intention to give meaning to interfaces through static structure alone, the Tydi “hardware-oriented type system”, inevitably leaves some aspects of the runtime behaviour underspecified. The Tydi type system successfully defines what may be communicated, but falls short of giving explicit meaning to how this communication actually unfolds over time. The resulting ambiguity mirrors Manasse's tension, motivating the need for a richer formal foundation that connects interface types to a precise, incremental runtime semantics. To close this gap, the additional parameters such as synchronicity and complexity are introduced, alongside the type in the Logical Stream specification. How these relate physical streams after synthesis is currently phrased too informally, which has contributed to the existing ambiguities.

From an engineering perspective this has concrete consequences. Two independently developed interfaces that nominally adhere to the same Tydi type may still be behaviourally incompatible, since the specification leaves room for interpretation in the temporal packing of elements, especially when dealing with nested streams. To solve this, I set out to define a formal foundation for Tydi that establishes a precise, algorithmic way to derive the runtime behaviour of an interface from its type and configuration parameters alone. This is a prerequisite for reasoning about compatibility of senders and receivers, and for enabling verification of interface implementations.

At the same time, the formalism must respect the realities of hardware design. All stateful resources implied by this formal foundation, such as buffers, counters, or indices, must be statically bounded and known at design time. Approaches that rely on unbounded queues, memory, or make use of abstract notions of time, are fundamentally incompatible with hardware synthesis. The formal description must therefore remain hardware-aware, ensuring that every construct corresponds to implementable logic with well-defined resource requirements. More specifically, such a formalism must operate *incrementally*. Streaming interfaces process data element-by-element, potentially with arbitrary delays between transfers, and the formalism must mirror this behaviour. The runtime procedure should therefore be defined as an incremental mapping that consumes and emits data stepwise, rather than as a monolithic transformation over entire data instances. When dealing with streams, we cannot cache the ‘entire’ chat message, since the message has an arbitrary size.

Finally, an important requirement is accessibility. Tydi is explicitly intended as a practical tool for hardware engineers, and shouldn't require an exercise in advanced formal methods. While the formalism must be sufficiently rigorous to support proofs of correctness and determinism, it should avoid imposing heavyweight mathematical machinery on the end user. Ideally, the user-facing model remains intuitive and type-driven, with the formal rigour largely hidden away in the underlying formalism.

To conclude, initially I will focus on identifying the ambiguities and omissions, by constructing a formalism for a subset of the specification, while maintaining the ability to expand this formalism later. The process of determining which portions of the specification to include is an important design consideration in itself, potentially shedding light on how certain ambiguities arose in the first place.

## 2.3. Evaluation of existing formalisms

A natural starting point for formalising Tydi is the body of work on expressive type systems. In the context of stream interfaces, dependent, session, and refinement types are good candidates for further investigation.

**Dependent types** allow their definition to depend on their assigned value. In principle, dependent type theory can relate values and types closely enough to encode the detailed invariants governing the hierarchy of nested streams [36]. It can make structural properties (e.g. sequence lengths, alignment relationships, or numeric relations between nested dimensions) part of the type itself, so these properties are checked by the type system rather than expressed as separate interface properties. Recent applications to hardware include the modelling of parametrised DSP circuits in Idris, which captures relationships between data values and bit-level structures like wordlengths or register pruning [43]. Other approaches have utilized dependent types to reason about the physical structure of hardware interfaces and ensure they adhere to standards like AXI [33]. While these systems effectively describe the *static* layout and structural correctness of an interface, they do not provide an intuitive way for a hardware designer to express the temporal unfolding of a stream. As a result, dependent type systems remain a powerful verification tool but are not a good fit for Tydi’s goal of remaining an approachable design entry point.

**Session types** and behavioural type systems excel at verifying communication protocols and ensuring interface compatibility through duality [24]. They have been successfully applied to FPGA-based designs to guarantee communication-safety and deadlock-freedom in reconfigurable parallel kernels [34]. Furthermore, they induce a Labelled Transition System (LTS), mapping naturally to the Finite State Machine (FSM) logic for hardware implementations. However, a fundamental mismatch exists in semantic granularity: session transitions are atomic, whereas Tydi transfers are incremental. While a session type can describe which element comes next in a sequence, it lacks the ability to describe “how much” of that element is transmitted in a specific instance of time. It reasons about transmitting the entire chat message but does not provide sufficient control over the transmission of individual characters across physical lanes. Consequently, session types fail to account for the spatial lane-packing and complexity-level constraints inherent to Tydi’s concept of streamspace mapping.

**Refinement types** offer a middle ground by augmenting base types with logical predicates [21]. Attaching predicates to base types (e.g.  $\text{Bits}(64)\{t \mid t \leq \text{MAX\_TS}\}$ ), is convenient for checking value-level invariants such as valid ranges or non-empty sequences. In a Tydi context, they could formalise critical data invariants, such as ensuring a  $\text{Bits}(64)$  timestamp represents a valid POSIX range. However, refinement types share the same limitation as the aforementioned systems regarding temporal execution: they are essentially static. They can describe the *validity* of a data instance once it is fully assembled but offer no mechanism to govern the incremental, state-dependent logic required to pack partial elements into physical hardware lanes across multiple cycles.

More recently, **specialized type systems** have emerged to bridge the gap between abstract data and hardware timing. *Space-Time Types*, as implemented in Aetherling, use type-directed scheduling to map data-parallel programs onto hardware, with specific throughput requirements [18]. Similarly, *Timeline Types* in Filament provide a modular way to specify and enforce cycle-accurate timing and structural constraints for hardware modules [35]. However, these formalisms are not directly applicable to the Tydi problem due to their fundamental reliance on *static* scheduling. By ‘static scheduling’ I mean the compile-time, fixed assignment of computation and data transfers to specific cycles (typical of Aetherling), in contrast with the run-time, handshake-driven flow control found in latency-insensitive designs such as Tydi.

Aetherling explicitly targets “statically scheduled, streaming hardware” and operates on homogeneous, fixed-length sequences whose lengths must be known at compile time [18]. It is therefore optimized for designs that intentionally avoid the control-logic overhead of dynamic flow control. Filament likewise focuses on statically timed pipelines and explicitly contrasts its approach with latency-insensitive interfaces (i.e., valid/ready handshaking), which it identifies as inefficient for its target domains [35].

In contrast, Tydi is designed to support dynamically sized data structures and relies on latency-insensitive handshaking to manage dataflow over nested streams. Because it does not bake a cycle schedule into the type system, scheduling decisions emerge at run time from the interface properties and the actual

composition of data instance. Where Aetherling and Filament resolve timing into rigid, cycle-accurate constraints, Tydi deliberately leaves multiple valid physical mappings for the same logical structure. Consequently, these systems are well suited to regular, statically timed data-parallel kernels, but are too specialized to capture the flexible, state-dependent, and irregular mapping required for Tydi.

Since the **software streaming paradigm** is more mature, formal work in this domain could provide effective candidates for a Tydi formalism. Frameworks such as Kahn Process Networks and coalgebraic stream semantics provide elegant mathematical descriptions of streaming computation [27, 45, 16]. Interfaces can be reasoned about as specific category of stream transformers themselves, therefore these formalisms could describe their runtime procedures effectively. However, models from the software domain typically assume arbitrary buffers, not providing sufficient granularity regarding execution timing, which clashes with the finite resources and discrete timing inherent to hardware interfaces. Adapting such models to the hardware domain, which has been expressed as a valuable future work in recent studies [28], is far beyond the scope of this work.

**Interface automata and contract-based models** offer ways to reason about compatibility through assumptions and guarantees [4, 7]. While useful for higher level protocol reasoning, they struggle to scale to rich, nested data structures without incurring state-space explosion. Furthermore, algorithmically determining an automaton for arbitrary type and interface properties would be a significant challenge, certainly requiring additional formal frameworks. The concepts regarding defining interface contracts through automata are an insightful way to reason about Tydi implementations. I deem it feasible to extend these to a higher level of abstraction, which will require a mapping to the existing Tydi type system.

In essence, we are trying to determine the “meaning” of a Tydi type, where its meaning is concretely the runtime behaviour. This corresponds with the domain of formal semantics of programming languages, describing how the syntax of a system determines its execution. Two main styles of semantics are commonly distinguished: denotational and operational.

**Denotational semantics** gives each syntactic construct mathematical “meaning”, such as a set of behaviours or execution traces, where the meaning of a larger construct is built systematically from the meanings of its parts. For Tydi this view is useful: a type (plus interface properties) can be read as denoting the set of admissible streamspace traces or transfer sequences, which supports high-level equivalence reasoning and a compact specification of “what” behaviours are allowed. To a certain extent, this is what Tydi currently is, describing the complete streamspace mapping of a given Tydi type in one (ambiguous) step. The denotational style abstracts away the step-by-step mechanism that produces a trace and therefore lacks the temporal granularity required to reason iteratively about element-by-element packing, termination placement, or handshake-driven flow control.

**Operational semantics** instead describes execution as more granular state transitions. Small-step, rule-based operational semantics are naturally suited to cycle-accurate, hardware-aware descriptions: a configuration can include the current parse configuration, and each rule corresponds to an incremental transfer or controller action. This style has been applied effectively to hardware languages, in the origins of structural operational semantics and recent, cycle-accurate rule-based treatments such as Bluespec/Koika [42, 9]. Moreover, techniques exist to relate stepwise and whole-execution views: the big-stop extension presents a mapping from small-step derivations to big-step judgments, allowing compact high-level proofs to be connected to low-level transition traces[26]. In order to map these methodologies to the Tydi specification, additional structure is required. Since these semantic frameworks naturally integrate with the type theory domain they are strong candidates for integrating in a Tydi formalism.

**To summate**, the survey of existing formalisms shows that no single approach meets Tydi’s combined needs for usability, hardware awareness, and incremental, cycle-accurate behaviour. Dependent and refinement systems capture rich static invariants but are heavyweight or essentially atemporal; sessions capture protocol definitions but lack the fine-grained spatial/temporal control that Tydi requires; and static, schedule-driven type systems (Aetherling/Filament) are ill-suited to dynamically sized, latency-insensitive streams. The software formalisms are interesting tools to reason about streamlets, but are fundamentally incompatible with the hardware domain, and would require a significant amount of work to effectively describe Tydi. Semantics, in particular the operational style, provide a natural way to

describe Tydi's incremental streamspace mapping procedure, but would still need to be connected to its type system to be used effectively.

## 2.4. Proposal for a tiered formal framework

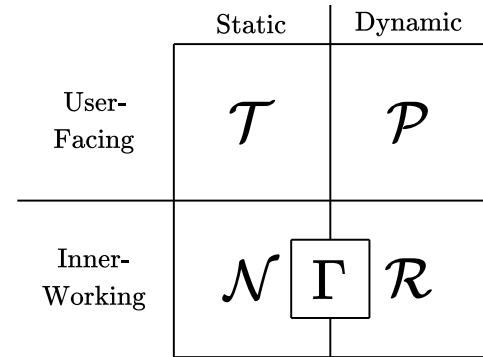

By zooming out and evaluating what Tydi currently is, and what it intends to be, I note that the specification can be split in two distinct ways. One axis separates the *user-facing* from the *inner-working*, while the other divides Tydi's *static* from its *dynamic* domain. The user-facing parts of Tydi are intended to be accessible: a hardware-oriented type system, naming conventions, and the layout of data signals for a particular physical stream. The inner-workings are abstracted away; the algorithms synthesising logical streams into bundles of physical streams, the (currently non-existent) description of how streamspace mappings are actually achieved, how Tydi conformant interfaces are implemented, *why* they are compatible, etc. From the other perspective, static concepts are the hardware-oriented type system, the signal layouts and naming conventions, while dynamic concepts include engineering parameters like complexity levels, inter-stream synchronisation, and the implementation of streamspace mappings at runtime. This split allows us to apply requirements only to the relevant domain of the formalism; not encumbering the user-facing with semantic rigour, and not requiring accessibility from the type systems at the inner-working. Figure 2.1 provides a visual representation of these domains.

Formalisms can now be mapped to their most suitable domain, further aiding reasoning about what experts have referred to as the "specification gap". As noted in my conversations with the original authors, Tydi acts as a generic factory of sorts. While it succeeds at the high-level (data structures) and low-level (physical wires), it lacks a prescriptive "middle layer" or protocol layer to define how the dynamic domain is actually implemented. My intuition is that, in the 4 split view, the principle gap exists in the inner-working level, between the static and the dynamic domain.

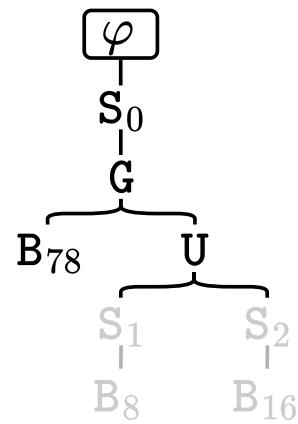

This section proposes a tiered formal framework for Tydi, where an interface specification consists independently of (1) the type  $\mathcal{T}$ , and (2) a set of its dynamic interface properties  $\mathcal{P}$ . Each can be translated to the inner-working level, where the interface type is mapped to a more hardware-oriented, unambiguous normalised form  $\mathcal{N}$ , and the dynamic interface properties to its corresponding semantics, implemented by a ruleset  $\mathcal{R}$ . In order to actually implement an interface, the gap needs to be bridged between the static and the dynamic, which is achieved by a stateful device represented by  $\Gamma$ . Figure 2.1 shows how these two ways to split the formalism, effectively categorise the responsibilities for each aspect of Tydi.

### 2.4.1. Types, normalisation, and streaming context

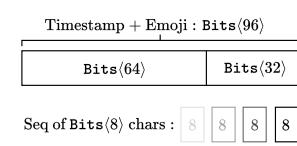

The existing synthesis algorithm concatenates all primitive Bits fields that correspond to the same physical stream in "Natural Order". This natural ordering is the order of appearance, as written down, or more specifically, pre-order DFS traversal of the type hierarchy. After synthesis, the physical stream node becomes difficult for a formalism to interact with, since the overarching type hierarchy is lost, the inter-stream relationships are hardly evident. The concatenation is still required however, since it ensures that all primitives that correspond to the same physical stream, are transmitted as one. If we can define a procedure that restructures the type while remaining in the type domain, we can derive a hardware-oriented view of the stream while maintaining inter-stream relations. One such method could concatenate the primitive fields "in-place". When extending the chat message example by adding a 32bit emoji field that is transmitted *once* per message, we get:  $\text{Group}(\text{Bits}(64), \text{Dim}(\text{Dim}(\text{Bits}(8))), \text{Bits}(32))$ . The synthesis algorithm would create two physical streams, one for the timestamp + emoji, carrying 96bit elements, and another for the individual characters that comprise the message. The hierarchy between these two physical streams

**Figure 2.1:** The two ways to split the formalism, showing the proposed top-level type  $\mathcal{T}$ , and its normalised form  $\mathcal{N}$ , the interface properties  $\mathcal{P}$  and its corresponding ruleset  $\mathcal{R}$ , with the stateful device  $\Gamma$  connecting the static to the dynamic.

**Figure 2.2:** A hardware view of the registers holding a normalised timestamp + emoji, and a register for the single character input stream

is now obscured, their respective type not contained in an overarching structure. I propose a normalisation method that maintains the hierarchy, for example by normalising the emoji example to:  $\text{Group}\langle\text{Bits}\langle 96 \rangle, \text{Stream}\langle\text{Bits}\langle 8 \rangle, d = 2 \rangle\rangle$ . This way we can separate the type in which an interface is defined from the type used by physical streams. Figure 2.2 shows the register view of this approach. The user-facing type maintains its flexibility, while the "inner-working" type contains the hierarchy of physical streams, while satisfying a Canonical Form (CF) that removes semantically ambiguous structures.

### The Normalisation Function

The mapping between these domains can be defined by a normalisation function  $\|\cdot\| : \mathcal{T} \rightarrow \mathcal{N}$ , which reduces a flexible top-level type  $\mathcal{T}$  to a normalised type  $\mathcal{N}$ . A Canonical Form specification can enforce properties that remove semantically ambiguous structures in the normalised type. It should disallow directly nested streams or groups, since semantically,  $\text{Stream}\langle\text{Stream}\langle T, d = 1 \rangle, d = 1 \rangle \equiv \text{Stream}\langle T, d = 2 \rangle$ , similarly any group composition of the form  $\text{Group}\langle T_1, \dots, \text{Group}\langle T'_1, \dots, T'_m \rangle, \dots, T_n \rangle$  is semantically equivalent to  $\text{Group}\langle T_1, \dots, T'_1, \dots, T'_m, \dots, T_n \rangle$ . Singular groups can be reduced:  $\text{Group}\langle T \rangle \equiv T$ . The index of a primitive in a group in the normalised domain does not carry any semantic implications, therefore it should be moved to a consistent location by always placing it at the head.

These procedures guarantee that at most one primitive exists per stream node, and its location in the type is deterministic, while maintaining the hierarchy of the streams. Additionally, the Tydi shorthand notations for the stream node (Dim, New, etc), and the container types (ConcatStruct, PackedVariant, RASElem etc), are all defined by the streamspace types (Bits, Group, Union, etc). The type system that the dynamic formalism interacts with should ideally not include the shorthand and container types. Just like the synthesis function reduces the shorthand notations to bundles of physical streams, my proposal separates the top level from the normalised type, allowing for flexibility, and extensibility at the top level, while retaining the semantic clarity in the normalised domain.

### The Streaming Context

As we've seen, the normalised type in canonical form provides a deterministic structure for the dynamic formalism to interact with. However, since we explicitly decoupled the static from the dynamic specification, we have thus far not considered how the type of an interface, actually impacts the runtime behaviour. As shown in diagram 2.1, the dynamic, operational domain interacts with the static, type domain through a streaming context  $\Gamma$ . The streaming context is stateful and deterministically instantiated by the normalised type  $\mathcal{N}$ . It exposes the fixed set of "dials and switches" by which the dynamic formalism can operate; the dynamic formalism never uses  $\mathcal{N}$  directly, it only manipulates  $\Gamma$ .

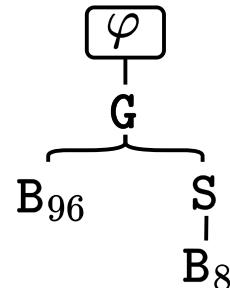

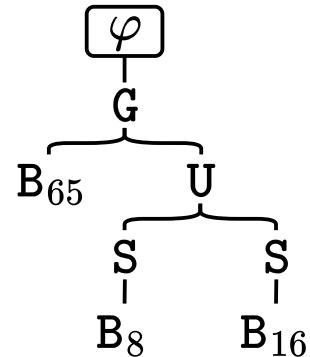

Concretely,  $\Gamma$  materializes the explicit buffers, per-stream wire layouts, how the component's internal streams are connected with the tydi interface and a parse tree that maintains the state of the hierarchy of nested streams. All these components should have exact sizes at instantiation, since we cannot define buffers or trees of arbitrary size. The parse tree is constructed based on the normalised type to maintain the hierarchical relations between streams. By terminating nodes in a tree, various behaviours and interleavings can be implemented. For example, this gives the tree shown in figure 2.3. The root  $\varphi$  of this tree encapsulates the normalised type in a stream with a singular dimension. It carries the termination information of the outer sequence. Like an API of sorts, the streaming context exposes a set of operations to the dynamic formalism, that can use them to implement interface behaviour. These operations can for example inspect the current state of the streaming, send data, update buffers etc. The dynamic formalism would therefore be defined as a set of transitions on this streaming context,  $\Gamma \rightarrow \Gamma'$ .

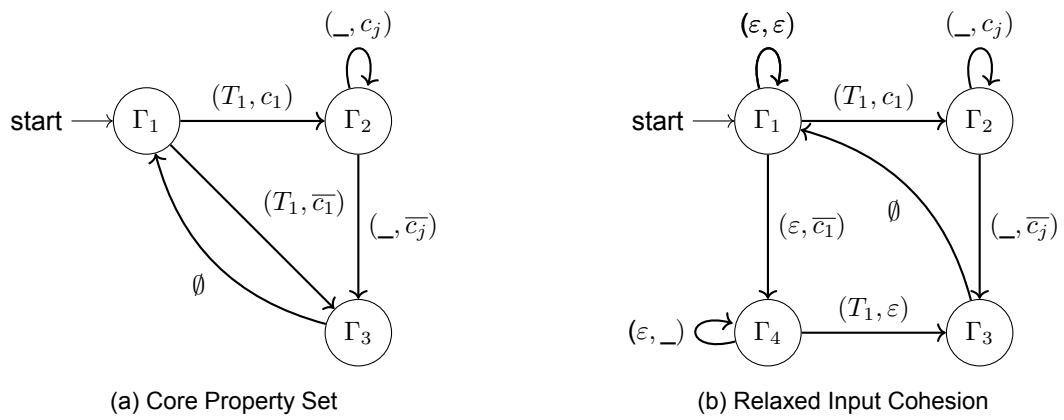

#### 2.4.2. Interface Properties and Semantics

The dynamic domain of the formalism also has its own user-facing and inner-working split. In the current specification, the parts of Tydi that specify the dynamic properties of a stream are intertwined with the static; The Logical Stream definition contains the stream's type and parameters impacting the static signal layout, alongside the synchronicity and complexity levels impacting the dynamic nature

**Figure 2.3:** The parse tree for the normalised chat message example where  $\varphi$  indicates the root in focus.

For the chat message

of the interface. The complexity level is the main dynamic interface property, directly determining the allowed streamspace mappings. A notable feature of Tydi is the use of this parameter to balance the complexity of the implementation logic of the sending and receiving interfaces. However, it is never substantiated *how* the complexity levels actually achieve this balancing.

A larger perspective on defining hardware interfaces, allows us to reason about constraints on inputs of an interface, and guarantees it provides regarding its output. The interface of a component can be considered a streamlet of a specific kind, where its inputs are the way it is connected to the component, and its output is the set of wires connecting to the interface of a receiving component. When reasoning about the implementation complexity of an interface, we cannot only rely on the properties of the output of the interface, we must also consider the way this interface is connected to the internals of the component.

For example, component 1 processes chat messages and we want to construct a sending interface for component 1, incrementally sending a chat message to component 2. If component 1 internally takes more time for certain letters, it cannot always guarantee that the next letter will be available for sending. The implementation of the sending interface will need to take this into account. Crucially, if the output of the sending interface, also does not guarantee that the stream of letters is sent without interruptions, the internal "slowness" of component 1 has less of an impact on the implementation complexity of its sending interface. Whereas, if the sending interface *does* guarantee a continuous stream of letters, this will require additional logic and buffering, increasing the complexity.

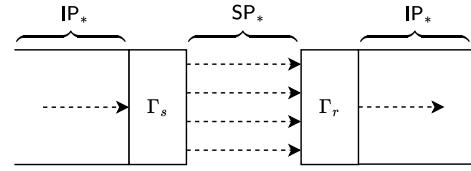

I note a dual: strong input constraints and weak output guarantees decrease implementation complexity, while weak input constraints and strong output guarantees increase implementation complexity. This aligns well with the field of formal interface contracts. Such contracts can be used to reason about compatible interfaces, formalising their assumptions/constraints and their guarantees, providing strong connection to their compositional behaviour in the hardware domain [7, 4]. The classes of properties describing such constraints and guarantees, can be differentiated as shown in Figure 2.4. It shows how the properties describing the internal streams of the component, are separated from those describing the streamspace mapping, the communication between components. When considering the compatibility of interfaces, only the Streamspace Properties are relevant. As such I define interfaces as compatible if the Streamspace Properties of the sender and receiver are identical. Concretely, I distinguish the properties as follows:

**IP<sub>\*</sub> Internal-Stream Properties:** predicates over normalised element streams inside a component. Examples include element ordering, presence/absence of empty elements, and per-element termination markers.

**SP<sub>\*</sub> Streamspace Properties:** predicates over sequences of transfers. Examples include transfer utilisation, element alignment, and sequence-termination. The original Tydi complexity levels *only* describe properties in this domain.

This allows describing the original complexity levels, but also other combinations of interface properties. The original authors have expressed that the hierarchy of complexity levels is somewhat arbitrary, obscuring the fact that interfaces might have properties that do not fit neatly in a specific level. For instance, if an interface requires a high-complexity feature like lane offset but adheres to low-complexity constraints otherwise, it must currently be described as "high complexity". The sets of dynamic interface properties would alleviate this restriction, allowing the designer of an interface to pick the exact interface properties that suit their needs.

#### Named Property Sets

At the user facing level, I initially proposed that each interface property relates to a specific transition in the semantics, forming a convex hull of rules where each subset would describe a valid interface. This was however needlessly complicated, making individual properties less intuitive, the underlying semantics exceedingly complex, while allowing the description of rather ill-advised interfaces (e.g. an

**Figure 2.4:** The sending and receiving component with their respective interfaces  $\Gamma$  and internal stream properties  $IP_*$ . The transmission is governed by the streamspace properties  $SP_*$ .

interface that has no delays on its internal streams, but introduces delays in its streamspace mapping). Therefore, I propose to usage of “Named Property Sets”, similar to the complexity levels, but without the inherent hierarchy. Each property set  $\mathcal{P}$  maps to a corresponding semantics  $\mathcal{P}$  at the inner-working level. This is related to the idea that motivated the original Standard Container Library, providing engineers with a shorthand notation corresponding to higher level structures that one may be more familiar with. The first named property set that should be introduced is a “core”, implementing a rudimentary mapping procedure.

### Semantics

The property sets are strictly related to sets of transitions, expressed in an operational small-step semantics. Each transition is can be seen as a “rule”, governing the allowed behaviour of some interface. The terminology of rule and transition is generally used interchangeably. Rule-based, hardware-oriented approaches such as Bluespec/Koika give a valuable perspective on how one might implement formal hardware descriptions, while remaining explicit about resource bounds needed for synthesis, and providing the methodologies used to verify the formalism [9]. It is my intention to first define a set of default rules required for interacting with the streaming context. These rules will be shared among all rulesets, and can be extended with the transitions that are needed to implement the behaviour specified by the property-set. To make the semantics tractable and focused on the mapping behaviour I introduce three simplifying but deliberate abstractions up front:

1. **Temporal granularity (handshaked transfers).** Time is quantified in handshaked transfers (valid/ready occurrences). I abstract over inter-transfer cycles and sub-cycle timing. This concentrates the semantics on *when* and *which* elements are presented and acknowledged, rather than on low-level timing artefacts that are irrelevant for the purpose of this work.

2. **Deferral of bit-level layout.** The explicit layout of lanes and signals are omitted from the proposed formalism, since these can be inferred from the original specification. Omitting these details reduces clutter in the semantics.

3. **Staged support for Union.** The initial formalism excludes the `Union` (variant) from the core development. This choice isolates the canonical mapping behaviour for sequences, groups, and sequences. The semantics and proofs are constructed such that the `Union` can be reintroduced as an extension of the formalism. Its inclusion is presented in chapter 6, and illustrates how the framework is an effective foundation for the entire Tydi specification.

### Proving functionality

A formal foundation for Tydi facilitates rigorous verification of the interfaces that it defines. I need to verify the correctness of the mapping of an arbitrary data instance of a given type. A key challenge is ensuring that this holds true, not just for the core ruleset, but also for any potential alterations of its semantics. Therefore, I will base the correctness argument on two fundamental properties that *any* valid ruleset  $\mathcal{R}$  must adhere to: 1) *Structural Determinism*: For any valid streaming context  $\Gamma$ , exactly one transition rule must be applicable at all times. This can be enforced by defining rules with mutually exclusive and exhaustive premises [2]. 2) *Progress (Finite Parsing)*: For any finite instance, its mapping must be implemented in finite transitions. I ensure this by requiring that every rule (or finite sequence of rules) advances the context by strictly decreasing a well-founded metric (e.g., by consuming input or terminating a node), thus guaranteeing termination. This method is inspired by Kôika, an operational semantic description for Bluespec System Verilog (BSV), enabling formal reasoning about its execution, maintaining a hardware aware, cycle-accurate perspective [9]. These arguments will only work if the normalisation always maps a top level type to canonical form, and if terminating streams always validly terminate the parsetree. Therefore, these processes will need to be verified beforehand.

#### 2.4.3. Connecting the layers of the formalism

While the original specification hardly mentions the receiving perspective of streamspace, it doesn't really need to since the signal layout is static, and the streamspace mapping is inexact. The receiving interface is mentioned in the specification, regarding the balancing of hardware implementation logic complexity of the sender and receiver. It is however never substantiated how this balancing of logic is actually achieved. Since this work provides sufficient detail to describe the actual mapping procedure, it is important to specify how this connects to the receiving interface, and the balancing of implementation

complexity, as these are valuable aspects of the specification. This section will address both these subjects, finalising in a brief overview of the proposed formalism, how it relates to the requirements identified in the previous chapter and where it deviates from the original specification.

### The receiving interface

For the purpose of this work I focus on the sender interface, illustrating how its internal stream and streamspace properties give rise to the semantics describing its runtime mapping procedure. The semantics of the receiving interface can be implemented as the dual of the sending interface, given that the its ruleset is structurally deterministic and injective. More specifically,  $\Gamma \xrightarrow{\tau} \Gamma'$  denotes the sender small-step transition that emits a transfer (observation)  $\tau$ . We require that for every context  $\Gamma$  there is at most one outgoing step:  $|\{(\tau, \Gamma') \mid \Gamma \xrightarrow{\tau} \Gamma'\}| \leq 1$ . This reads as, “the number of possible pairs of transfer and successor state  $(\tau, \Gamma')$ , that can be reached from a given context  $\Gamma$  is at most one.” For injectivity, distinct predecessors cannot reach the same successor under the same observation:  $(\Gamma_1 \xrightarrow{\tau} \Gamma') \wedge (\Gamma_2 \xrightarrow{\tau} \Gamma') \Rightarrow \Gamma_1 = \Gamma_2$ .

### A Perspective on Implementation Complexity

The original specification mentions balancing the required hardware logic to implement a sender-receiver interface set, but does not substantiate how different configurations actually achieve this. My proposed separation of Internal-Stream Properties ( $IP_*$ ) and Streamspace Properties ( $SP_*$ ) does more than define compatibility; it directly governs the implementation complexity of the sending and receiving logic. This idea is natural to the field of interface automata [4], where relaxing input assumptions or strengthening output guarantees strictly influence the state space a component must manage. Therefore, the proposed interface properties also enable the design of a quantifiable *Implementation Complexity Metric (ICM)*. I propose defining a mapping from the semantic definition of an interface, to its automata or FSM equivalent, and analysing the state space. Such a metric will allow us to formally reason about the trade-offs between interface implementations of specific types, and their resulting hardware logic cost.

### Deviations from the original specification

Besides starting with a subset of the type system, excluding the union, there are fundamental differences. In the proposed formalism, all streams in a type must adhere to the same properties, while Tydi allows interleavings where only some nested physical streams are not synchronised to their parent streams.

Tydi distinguishes complexity level 1 and 2 from the rest, by reasoning about the valid signal not going down. Since the proposed formalism abstracts the temporal resolution of streamspace as “handshaked transfers”, it is not expressive enough to reason about signal validity between those transfers. For this formalism, the gaps that are shown between the transfers corresponding to complexity level 2 in figure 1.5, are indistinguishable from the directly adjacent transfers. To represent such a gap, an empty transfer would need to sent, with a handshake taking place.

### An overview of the proposal

The proposed tiered formal framework addresses the “specification gap” by distinguishing between the user-facing definition and the inner-working semantics. An interface is specified by a top-level type  $\mathcal{T}$  and a set of properties  $\mathcal{P}$ . The type  $\mathcal{T}$  is algorithmically reduced to a hardware-oriented Normalised form  $\mathcal{N}$  via a normalisation function  $\llbracket \cdot \rrbracket$ . This normalised type instantiates a stateful Streaming Context  $\Gamma$ , which bridges the static and dynamic domains. The runtime behaviour, the mapping of data to streamspace, is then governed by a ruleset  $\mathcal{R}$  derived from the properties  $\mathcal{P}$ .

# 3

## The Formalism

Building on the findings from the analysis, this chapter defines the formalism. It is structured to mirror the path from design intent to hardware behaviour. The highest level of abstraction encompasses the entire definition of an interface. It is defined as a tuple:  $\text{InterfaceSpecification} := (\mathcal{T}, \mathcal{P})$  consisting of the static type of the interface  $\mathcal{T}$ , and the set of dynamic interface properties  $\mathcal{P}$ . The *top-level type* ( $\mathcal{T}$ ) expresses the type of the interface. The *normalised type* ( $\mathcal{N}$ ), is defined to be of Canonical Form (CF) when it adheres to a set of conditions, disallowing semantic ambiguous structures. The normalisation function ( $\llbracket \cdot \rrbracket$ ) algorithmically maps  $\mathcal{T}$  to  $\mathcal{N}$  and enforces the Canonical Form. A stateful *streaming context* ( $\Gamma$ ) is defined, instantiated using the normalised type  $\mathcal{N}$ , and the user specified number of lanes  $L$ . It encapsulates all runtime state, including input buffers ( $I$ ), a navigable *parse tree* ( $Z_{\mathcal{N}}$ ) and transfer buffers  $T_B$ . The type agnostic, incremental mapping procedure, is defined by the provided interface property set  $\mathcal{P}$ . A mapping procedure  $\mathcal{R}$  is based on its corresponding property set, and defined as a ruleset composed of *small-step operational semantics* ( $\rightarrow$ ) transitions that operate on  $\Gamma$ . Deterministic sequences of such transitions are abstracted by *multi-step transitions* ( $\rightarrow^*$ ), enabling reasoning about the mapping of a complete data instance as a sequences of *cycles*. Finally, it is shown how an interface specification can algorithmically map to an Abstract Finite State Machine, which is used to define an *Implementation Complexity Metric* (ICM). This provides a method for quantifying the complexity of the logic required to implement a given interface specification in hardware.

### 3.1. Types, Normalisation and the Streaming Context

#### 3.1.1. Top-Level and Normalised Types

We define the *top-level Type*  $\mathcal{T}$  as a grammar, shown in figure 3.1. Here,  $\text{Bits}(n)$  represents a primitive type with  $n$  bits,  $\text{Group}(\mathcal{T}_1, \dots, \mathcal{T}_k)$  forms a group of  $k$  fields.  $\text{Dim}(\mathcal{T})$  annotates adding a dimension, defining a sequence, or lifting a sequence to a higher dimension through nesting  $\text{Dim}(\text{Dim}(\mathcal{T}))$ . The *normalised type*  $\mathcal{N}$  adapts  $\mathcal{T}$  by introducing an explicit stream constructor. Here,  $\text{Stream}(\mathcal{N}, d)$  is a stream of normalised type  $\mathcal{N}$  with dimension  $d$ .

$$\begin{aligned} \mathcal{T} &::= \text{Bits}(n) \quad (n \in \mathbb{N}) \\ &\quad | \quad \text{Group}(\mathcal{T}_1, \mathcal{T}_2, \dots, \mathcal{T}_k) \quad (k \geq 1) \\ &\quad | \quad \text{Dim}(\mathcal{T}) \\ \mathcal{N} &::= \text{Bits}(n) \quad (n \in \mathbb{N}) \\ &\quad | \quad \text{Group}(\mathcal{N}_1, \mathcal{N}_2, \dots, \mathcal{N}_k) \quad (k \geq 1) \\ &\quad | \quad \text{Stream}(\mathcal{N}, d) \quad (d \in \mathbb{N}^+) \end{aligned}$$

Figure 3.1: The top-level and normalised types

#### 3.1.2. Normalisation Function