# PARALLEL ALGORITHMS FOR SOLVING SYSTEMS OF LINEAR EQUATIONS AND THEIR MAPPING ON SYSTOLIC ARRAYS

# **K. JAINANDUNSING**

TR diss 1696 hlygg4

5179002

79 diss 1696

PARALLEL ALGORITHMS FOR SOLVING SYSTEMS OF LINEAR EQUATIONS AND THEIR MAPPING ON SYSTOLIC ARRAYS

# PARALLEL ALGORITHMS FOR SOLVING SYSTEMS OF LINEAR EQUATIONS AND THEIR MAPPING ON SYSTOLIC ARRAYS

# Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus, prof.drs. P.A. Schenck, in het openbaar te verdedigen ten overstaan van een commissie aangewezen door het College van Dekanen op dinsdag 3 januari 1989 te 14.00 uur

door

K. JAINANDUNSING

geboren te Paramaribo electrotechnisch ingenieur

Dit proefschrift is goedgekeurd door de promotor prof.dr.ir. P. Dewilde

- To my parents -

# **CONTENTS**

|    | PREFACE                                                           |   |   | iii<br>vii |

|----|-------------------------------------------------------------------|---|---|------------|

|    | INTRODUCTION                                                      |   |   | 1          |

|    | SYSTOLIC ARRAYS                                                   |   |   | 12         |

|    |                                                                   | • | • | 12         |

|    | A CLASS OF HIGHLY STRUCTURED ALGORITHMS FOR SOLVING SYSTEMS OF    |   |   | 29         |

|    | LINEAR EQUATIONS                                                  | • | • | 29         |

|    | 2.1 FEED FORWARD COMPUTATION OF $\mathbf{X} = A \cdot \mathbf{D}$ | • | ٠ | 34         |

|    | 2.2 THE CLASS OF FEED FORWARD ALGORITHMS                          | • | • |            |

|    | 2.3 NUMERICAL STABILITY OF THE ALGORITHMS                         | ٠ | • | 50<br>54   |

|    | 2.4 SEMI-DIRECT NATURE OF THE GENERALIZED SCHUR ALGORITHM         |   |   |            |

|    | 2.5 GENERALIZATIONS OF THE FEED FORWARD METHODS                   | • | • | 59         |

| 3. | MAPPING REGULAR RECURRENT ALGORITHMS TO FIXED SIZE SYSTOLIC       |   |   |            |

|    | ARRAYS                                                            |   |   | 65         |

|    | 3.1 TESSELLATION OF FULL SIZE ARRAYS                              |   |   | 66         |

|    | 3.2 STRATEGY I: LOCAL PARALLEL, GLOBAL PIPELINED                  |   |   |            |

|    | PARTITIONING                                                      |   |   | 69         |

|    | 3.3 STRATEGY II: LOCAL SEQUENTIAL, GLOBAL PARALLEL                |   |   |            |

|    | PARTITIONING                                                      |   |   | 81         |

| ,  | DESIGN OF A SYSTOLIC ARRAY FOR SOLVING SYSTEMS OF LINEAR          |   |   |            |

|    |                                                                   |   |   | 105        |

|    | EQUATIONS                                                         |   |   | 105        |

|    | 4.1 INTRODUCTION                                                  |   |   | 103        |

|    | 4.2 FEED FORWARD SOLVERS                                          |   |   | 118        |

|    | 4.3 FULL SIZE SYSTOLIC ARRAYS FOR THE QR AND SC SOLVER            |   |   | 122        |

|    | 4.4 FIXED SIZE SYSTOLIC ARRAYS FOR THE QR AND SC SOLVER           |   |   |            |

|    | 4.5 DESIGN OF A HOUSEHOLDER PROCESSOR ELEMENT                     | ٠ | ٠ | 129        |

|    | CONCLUSIONS                                                       |   |   | 141        |

|    | APPENDIX A                                                        |   |   | 143        |

|    | APPENDIX B                                                        |   |   | 147        |

|    | APPENDIX C                                                        |   |   | 153        |

|    | APPENDIX D                                                        |   |   | 159        |

|    | CONVENTIONS, SYMBOLS AND DEFINITIONS                              |   |   | 169        |

|    | REFERENCES                                                        |   |   | 173        |

|    | SAMENVATTING                                                      |   |   | 181        |

|    | AROUT THE AUTHOR                                                  |   |   | 185        |

#### PREFACE

The research presented in this thesis has three points of focus. The first is the development of algorithms for solving systems of linear equations with a maximum degree of parallelism and pipelining. The second is the development of partitioning strategies for the design of systolic arrays with the number of processor elements independent of the size of the problem. And the last is the synthesis of a concrete systolic array, with a fixed number of processor elements, for the algorithms developed.

The thesis has the following outline. Chapter 1 is introductory. It is divided in two main sections. Section 1.1 starts by summarizing the conventional direct methods for solving systems of linear equations. It is shown that a systolic implementation of feed forward direct methods such as Faddeev's execute almost twice as fast than a systolic implementation of direct methods with backsubstitution. The backsubstitution is identified as the bottleneck in such systolic implementations. Unfortunately, Faddeev's feed forward direct method needs pivoting to be numerically stable, while pivoting is hard to implement on a systolic array. The problems discussed in this section form the motivation for the development of the feed forward direct methods of Chapter 2. Section 1.2 starts by summarizing the basic concepts of mapping a regular recurrent algorithm on a full size systolic array. That is, an array with the number of processor elements proportional to the size of the problem. Next, it continues with the introduction of partitioning strategies for full size systolic arrays. Application of these strategies results in reduced size systolic arrays. That is, systolic arrays with a fixed number of processor elements, independent of the size of the problem.

Chapter 2 presents a class of feed forward direct methods for solving non singular systems of linear equations. These methods obtain the solution  $\mathbf{x}$  of  $A\mathbf{x} = \mathbf{b}$ ,  $A \in \mathbb{R}^{N \times N}$ ,  $\mathbf{b} \in \mathbb{R}^{N \times 1}$ , through combination of an LU, LQ or  $LL^t$  factorization of the matrix A and

an updating or downdating of the Cholesky factorization of the matrix  $LL^t + bb^t$  or  $LL^t - \mathbf{bb}^t$ , respectively, or an LU factorization of the matrix  $[L - \mathbf{b}]^t$ . The matrix L is the lower triangular factor in either of the three factorizations of the matrix A. Section 2.1 explains how the solution x is computed from the up- or downdating of the Cholesky factorization or from the LU factorization of the matrix  $[L -b]^t$ . Section 2.2 shows how an LU. OR or LL<sup>t</sup> factorization of the coefficient matrix is combined with the methods in Section 2.1, so that a class of feed forward direct methods is obtained. These methods compute the solution of a non singular system of linear equations by a single factorization. Thus the backsubstitution bottleneck is avoided in systolic implementations. The class contains a feed forward direct method which uses only orthogonal transformations as elementary operations. Hence, the method is stable for the general class of non singular systems of linear equations, unlike Faddeev's feed forward direct method (without (partial) pivoting). Section 2.3 presents a numerical analysis of the feed forward methods of Section 2.2. Section 2.4 shows that the method which combines an LL<sup>t</sup> factorization of the coefficient matrix with a downdating of a Cholesky factorization is in fact a semidirect method. Section 2.5 explains how the methods of Section 2.2 can be generalized to perform computations of the kind  $CA^{-1}B + D$ , where the matrices A, B, C and D are of proper dimensions and value. This generalization is similar to the extension of Faddeev's feed forward direct method.

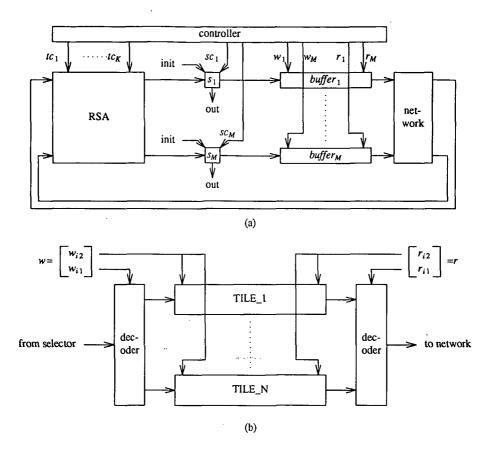

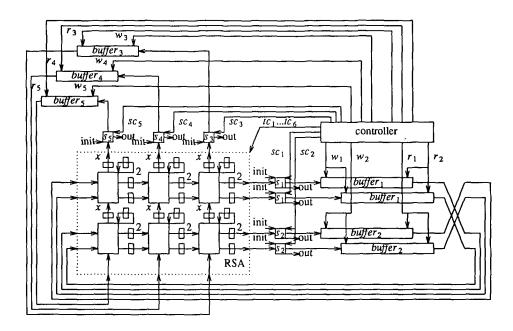

Chapter 3 presents the LPGP and LSGP partitioning strategies to partition a full size systolic array into a reduced size systolic array. In an LPGP (local-parallel-global-pipelined) partitioning of a full size array the array is tessellated into congruent tiles of, say, p processor elements each. The computations of different tiles are executed in pipeline on the reduced size array, which has p processor elements and the same interconnection topology as the full size array. In an LSGP (local-sequential-global-parallel) partitioning of a full size systolic array the array is again tessellated into congruent tiles of p processor elements each. But, in this case the processor elements in a tile are replaced by a single processor element in the reduced size array. This processor element executes the tasks of the p processor elements in sequence. In general the reduced size systolic array has a different interconnection topology than the full size array. Section 3.1 presents the

tessellation of a full size systolic array. Section 3.2 presents the LPGP partitioning strategy and Section 3.3 presents the LSGP partitioning strategy.

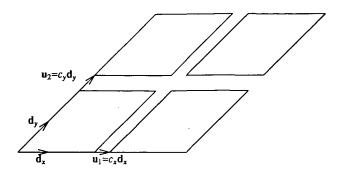

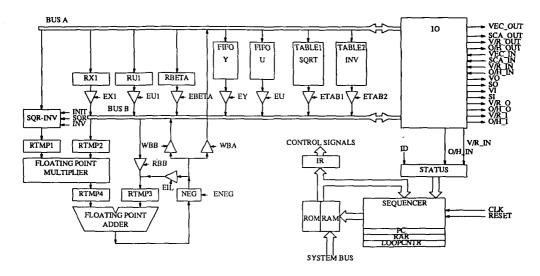

Chapter 4 presents the design of a reduced size systolic array for two of the feed forward direct methods of Section 2.2. The purpose of this chapter is to illustrate the design of a practical reduced size systolic array for these two methods. Section 4.1 introduces the design constraints. Section 4.2 summarizes the two methods in terms of orthogonal and hyperbolic Householder transformations. Section 4.3 illustrates the design of full size systolic arrays for these methods. Section 4.4 illustrates the LPGP partitioning of the full size systolic arrays of Section 4.3 and their unification into a single reduced size array. Section 4.5 presents the architecture of a Householder processor element of the reduced size array. The architecture is that of an innerproduct-step processor, which serializes the computation of a Householder transformation of a vector.

## Finally, Chapter 5 contains the conclusions of the thesis:

- systolic implementations of the feed forward direct methods execute roughly twice as fast as systolic implementations of the direct methods with factorization and backsubstitution:

- the class of feed forward direct methods contains a method which is numerically robust and stable without (partial) pivoting, for the complete set of non singular systems of linear equations;

- 3. it is possible to design systolic arrays for which the I/O bandwidth is closely matched to that of devices attached to the inputs and outputs of the systolic array or for which the number of processor elements is independent of the size of the problem that has to be executed on the array or both;

- 4. systolic arrays can be designed which execute more than one algorithm, with a minimum of control overhead.

I am greatly indebted to Dr.Ir. E.F. Deprettere for his professional advise and guidance in solving the problems I encountered during my Ph.D. research. Dr.Ir. E.F. Deprettere was my main source of stimuli in understanding these problems. I would also like to thank him for his sincere friendship in the past 4 years and his patience, while reading the preliminary drafts of the thesis.

Delft, K. Jainandunsing

October 1988

# **SUMMARY**

## SYSTEMS OF LINEAR EQUATIONS

Conventional direct methods for solving systems of linear equations consist of either a factorization of the coefficient matrix followed by a backsubstitution [Golu1983], or of a factorization of an augmented matrix [Fadd1959]. None of the two classes provide good solutions for implementations on systolic arrays. Methods of the first class are sequential in nature. I.e., the factorization of the coefficient matrix has to be completed before the backsubstitution can be done. This obstructs the acceleration of such direct methods when implemented on a systolic array.

A method of the second class is due to Faddeev [Fadd1959]. It computes the solution from a single LU factorization of an augmented matrix. This method, and feed forward direct methods in general, do not require a backsubstitution step. Therefore, highly parallel implementations on systolic arrays are possible. However, the LU factorization without (partial) pivoting is in general not numerically stable. Unfortunately, (partial) pivoting is hard to implement on an array where the length of interconnections between processors is independent of the size of the array, as is the case for systolic arrays. In this thesis feed forward direct methods are studied which rephrase the backsubstitution in terms of an updating or downdating of a Cholesky factorization, or in terms of an LU factorization. Combining this with an LU, LQ or LL<sup>1</sup> factorization of the coefficient matrix A yields a whole class of feed forward direct methods, which do not suffer from the backsubstitution bottleneck. One of these algorithms uses only orthogonal transformations as elementary operations and is therefore numerically stable for the general class of non singular systems of linear equations. The feed forward direct methods that are presented here have simple and highly parallel systolic implementations.

#### SYSTOLIC IMPLEMENTATION

A systolic array is defined here (see also [Rao1985] or [Rao1988]) to be an array of synchronously operating processor elements which are interconnected in a regular mesh with interconnections of length independent of the size of the array. Their regular topology is a desirable feature for area-efficient VLSI implementations and the absence of interconnections of arbitrary length eliminates communication delays which depend on the size of the array. Due to the massive parallelism of systolic arrays, systolic implementations of computationally intensive algorithms are given much attention. Most matrix-based signal processing algorithms, including the ones presented in this thesis, can be expressed as regular recurrent algorithms (see for instance [Unge1958], [McCl1959], [Ahme1982], [Depr1982], [Fort1985], [Delo1986], [Jain1986a]). Such algorithms can be automatically mapped to full size systolic arrays ([Mold1983], [Rao1985], [Fris1986], [Rao1988]). However, since the number of processor elements in a full size systolic array increases whenever the size of the problem grows, it is important to know how to partition large problems so that they can be executed on a systolic array with a small number of processor elements [Hell1985], [Mold1986], [Hori1987], [Neli1988].

Two strategies are developed in this thesis to partition a full size systolic array into a reduced size systolic array. The LPGP (local-parallel-global-pipelined) partitioning strategy tessellates the full size systolic array into congruent tiles of, say, p processor elements each. The computations of different tiles are executed in pipeline on a reduced size systolic array of p processor elements which has the same interconnection topology as the full size systolic array. The LSGP (local-sequential-global-parallel) partitioning strategy also tessellates the full size array into congruent tiles of, say, p processor elements each. The processor elements in a tile are replaced by a single processor element which executes the tasks of these processor elements in sequence. In this case the topology of the reduced size array is different from that of the full size systolic array. The LPGP partitioning keeps all memory for intermediate results outside the reduced size array. The LSGP partitioning causes local memory to increase, and reduces the I/O

bandwidth of the processor elements. Combining the two strategies results in array designs in which the number of processor elements is independent of the size of the problem and which have an I/O communication bandwidth which matches that of attached peripheral devices (such as disks, a host computer, etc.) as close as possible.

### SYSTOLIC ARRAY DESIGN

The partitioning theory is applied to the design of a reduced size systolic array for two feed forward methods; 1) the method consisting of a combination of an LQ factorization of the coefficient matrix A and an updating of a Cholesky factorization and 2) the method consisting of an  $LL^t$  factorization of the coefficient matrix A and a downdating of a Cholesky factorization. This application illustrates the practical use of the partitioning theory for designing reduced size systolic arrays. The two methods are stated in terms of orthogonal and hyperbolic Householder transformations, respectively. A processor element of the reduced size array is implemented as an innerproduct-step processor, which serializes the computation of a Householder transformation of a vector.

# 1.1 SOLVING SYSTEMS OF LINEAR EQUATIONS : DIRECT METHODS AND SYSTOLIC IMPLEMENTATIONS

Non singular systems of linear equations  $A \mathbf{x} = \mathbf{b}$  can be solved by iterative, direct or semi-direct methods. The iterative methods, like the Jacobi and the Gauss-Seidel method [Golu1983], improve iteratively on an initial guess  $\mathbf{x}_0$  of the solution vector. The direct methods, on the other hand, use matrix factorization (and backsubstitution) to obtain the solution directly. Semi-direct methods, like the conjugate gradient method [Golu1983], obtain the solution by computing the minimum of the quadratic functional  $f(\mathbf{x}) = \frac{1}{2}\mathbf{x}^t A \mathbf{x} - \mathbf{x}^t \mathbf{b}$ , which is reached for  $\mathbf{x} = A^{-1}\mathbf{b}$ . Theoretically the conjugate gradient method computes the minimum in a finite number of steps. However, the method is iterative in practice, due to roundoff errors and an error criterion is needed to halt the solution process.

The iterative and semi-direct methods do not change the coefficient matrix during the iterations. If the matrix is sparse, no fill-ins are created and the data can be efficiently stored in the (main) memory of the computer, even if the matrix is very large. Therefore, these methods play an important role in the solution of very large and sparse systems of linear equations.

The direct methods do create fill-ins in a sparse coefficient matrix, since factors of a sparse matrix are generally not sparse. These methods are more suited for solving dense systems of linear equations and no error criterion is needed to terminate the solution process.

### 1.1.1 DIRECT METHODS

The direct methods for solving non-singular systems of linear equations,  $A \mathbf{x} = \mathbf{b}$   $(A \in \mathbb{R}^{N \times N}, \mathbf{b} \in \mathbb{R}^{N})$ , can be divided in two classes:

- 1. direct methods with backsubstitution;

- 2. feed forward direct methods.

We shall give a quick presentation of these two classes.

#### DIRECT METHODS WITH BACKSUBSTITUTION

These methods compute either an LU, QR or  $LL^t$  (Cholesky) factorization of the matrix A, followed by a backsubstitution step. Let us denote by  $X^t$  either the lower triangular factor in an LU factorization, the orthogonal factor Q, in a QR factorization, or the lower triangular factor L, in an  $LL^t$  factorization and let us denote by  $R_X$  the corresponding upper triangular factor for each of these cases. Then, we can summarize the direct methods with backsubstitution as follows:

$$A = X^t R_{Y}, (1.1.a)$$

$$\mathbf{y} = X^{-t}\mathbf{b},\tag{1.1.b}$$

$$\mathbf{x} = R_{\mathbf{X}}^{-1} \mathbf{y}. \tag{1.1.c}$$

Computation of the factorizations is done by using either embeddings of elementary  $2\times2$  transformations or Householder transformations [Golu1983]. The discussion of factorizations with Householder transformations is deferred to Chapter 4. In case of an LU factorization the  $2\times2$  transformations are of the form:

$$\begin{bmatrix} 1 & 0 \\ \alpha & 1 \end{bmatrix}, \alpha \in \mathbb{R}.$$

In case of a QR factorization they are of the form:

$$\begin{bmatrix} \cos(\alpha) & -\sin(\alpha) \\ \sin(\alpha) & \cos(\alpha) \end{bmatrix}, \quad \alpha \in \mathbb{R}.$$

And, in case of an  $LL^t$  factorization they are of the form:

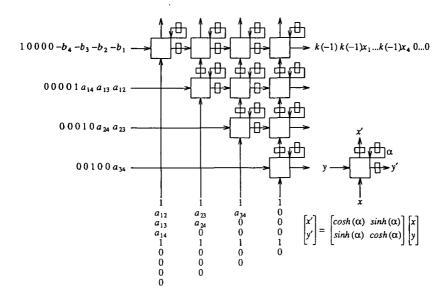

$$\begin{bmatrix} \cosh(\alpha) & \sinh(\alpha) \\ \sinh(\alpha) & \cosh(\alpha) \end{bmatrix}, \quad \alpha \in \mathbb{R}.$$

**Remark**: The hyperbolic transformations are used in Schur-Cholesky *LL*<sup>t</sup> factorization algorithms (see Section 2.2 and [Dewi1981], [Depr1982] and [Delo1984]). These algorithms are less known than the Cholesky factorization algorithm as found in [Golu1983]. For the Schur-Cholesky *LL*<sup>t</sup> factorization algorithms it has been illustrated that they can be mapped onto highly parallel systolic arrays of processor elements (see for instance [Ahme1982] and [Delo1986]).

The three types of elementary transformations can be represented by the following parameterized form [Walt1971]:

$$\Theta(m;\alpha) = \begin{bmatrix} \cos(m^{1/2}\alpha) & -m^{1/2}\sin(m^{1/2}\alpha) \\ m^{-1/2}\sin(m^{1/2}\alpha) & \cos(m^{1/2}\alpha) \end{bmatrix}, \quad m \in \{0,1,-1\}.$$

(1.2)

Case m = 0, m = 1 and m = -1 are known as the so-called linear (Gauss), orthogonal (Givens) and hyperbolic (Minkowsky) rotation, respectively. The matrix  $\Theta(m;\alpha)$  is orthogonal with respect to the following signature matrix:

$$S(m) = \begin{bmatrix} 1 & 0 \\ 0 & m \end{bmatrix}. \tag{1.3}$$

That is,

$$\Theta^{t}(m;\alpha)S(m)\Theta(m;\alpha) = S(m)$$

(1.4.a)

and for  $m = \pm 1$  we also have :

$$\Theta(m;\alpha)S(m)\Theta^{t}(m;\alpha) = S(m). \tag{1.4.b}$$

Property (1.4.a) is referred to as S(m)-orthogonality of  $\Theta(m;\alpha)$ , or just orthogonality in case m = 1.

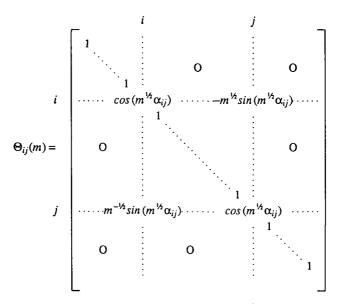

A QR or LU factorization is obtained by premultiplication of the matrix A by embeddings of the 2×2 orthogonal or linear rotations (m=1 or 0, respectively) of the following form:

(1.5)

For the appropriate choice of  $\alpha_{ij}$ , premultiplication by  $\Theta_{ij}(m)$  eliminates the entry  $a_{ij}$  of A. The product  $\prod_{i,j}^{\leftarrow} \Theta_{ij}(0)$ , where the pairs (i,j) are such that all elements in the strictly lower triangular part of the matrix A are eliminated, is a lower triangular matrix which is the inverse of the lower triangular factor L in the LU factorization of the matrix A. The product  $\prod_{i,j}^{\leftarrow} \Theta_{ij}(1)$ , where the pairs (i,j) are the same as in the case of the LU

factorization, is an orthogonal matrix which is the inverse of the orthogonal factor Q in the QR factorization of the matrix A. The LU factorization of indefinite matrices is numerically unstable without (partial) pivoting [Golu1983]. A small entry on the diagonal of the matrix A will blow up certain coefficients  $\alpha_{ij}$  in (1.5). This is impossible for the QR factorization, since the absolute value of the sine and cosine function is bounded by 1.

The use of hyperbolic rotations is restricted to the case where an  $LL^t$  factorization of the matrix A is computed. That is, in case A is symmetric positive definite. We defer the discussion of computing Cholesky factors by means of hyperbolic rotations to Chapter 2.

#### FEED FORWARD DIRECT METHODS

A not too well known feed forward direct method is due to Faddeev [Fadd1959]. This method avoids an explicit backsubstitution step and obtains the solution from a single LU factorization of an augmented matrix. In fact, it was this method that motivated the search for the algorithms that will be considered in Chapter 2. Faddeev's method is stated in the following proposition.

### Proposition 1.1:

Let  $A \in \mathbb{R}^{N \times N}$  be a non singular matrix and  $\mathbf{b} \in \mathbb{R}^N$ . Let  $\mathbb{L} \in \mathbb{R}^{2N \times 2N}$  be the inverse of the lower triangular factor of the LU factorization of the augmented matrix  $[A^t \mid -I_N]^t$  and let  $[R^t \mid O]^t$  be the corresponding upper triangular factor,  $R \in \mathbb{R}^{N \times N}$ . Then, the solution  $\mathbf{x}$  of the system of linear equations  $A\mathbf{x} = \mathbf{b}$  satisfies the following equation:

$$\mathbb{L} \begin{bmatrix} A & \mathbf{b} \\ -I_N & 0 \end{bmatrix} = \begin{bmatrix} R & * \\ 0 & \mathbf{x} \end{bmatrix}. \tag{1.6.a}$$

#### Proof:

Partition the  $2N \times 2N$  matrix L as follows:

$$\mathbb{L} = \begin{bmatrix} L_{11} & L_{12} \\ L_{21} & L_{22} \end{bmatrix}, \text{ with } L_{11}, L_{12}, L_{21}, L_{22} \in \mathbb{R}^{N \times N}.$$

(1.6.b)

Substituting (1.6.b) in (1.6.a) gives:

$$L_{21} = L_{22}A^{-1}. (1.7)$$

Thus,

$$L_{21}\mathbf{b} = L_{22}A^{-1}\mathbf{b} = L_{22}\mathbf{x}. (1.8)$$

And by observing that  $L_{22} = I_N$ , it follows that:

$$L_{21}\mathbf{b} = \mathbf{x} \tag{1.9}$$

and (1.6.a) follows.

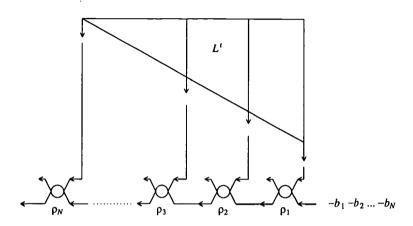

Faddeev's method is not only capable of solving Ax = b, but it can also compute the Schur complement of a matrix. This is easily understood by applying Faddeev's method to a block matrix:

$$\mathbb{L} \begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} R & * \\ O & E \end{bmatrix}, \tag{1.10}$$

with appropriate L. Using (1.6.b) in this equation gives:

$$E = (D - CA^{-1}B), (1.11)$$

which is the Schur complement of the augmented matrix  $\begin{bmatrix} A & B \\ C & D \end{bmatrix}$ . Choosing the dimensions and values of the matrices A, B, C and D appropriately we can:

1. solve for multiple right hand sides, i.e., AX = B, where  $B \in \mathbb{R}^{N \times M}$ ;

- 2. compute innerproduct accumulations, i.e.,  $d c^t b$ ;

- 3. compute matrix-vector product accumulations, i.e.,  $\mathbf{d} \mathbf{c}^t B$ ;

- 4. compute matrix-matrix product accumulations, i.e., D CB.

The LU factorization in Faddeev's method is numerically stable only when the matrix A is positive definite. In case the matrix A is indefinite, pivoting strategies must be used to guarantee numerical stability. In [Nash1988] it is shown how the numerical stability of Faddeev's method can be improved, by using Givens rotations to compute the upper triangularization of the matrix A, after which linear rotations are applied to eliminate the matrix C, using the diagonal elements of the upper triangular factor of the matrix A as pivots. This method is not completely stable, since the linear rotations may still explode if the matrix A has a large condition number. A different approach is given in Chapter 2 of this thesis, see also [Jain1986b], where a numerically robust feed forward direct method is described which uses only Givens rotations.

#### 1.1.2 SYSTOLIC ARRAYS

#### DEFINITION

Systolic arrays are defined to be arrays of synchronously operating processor elements, connected in a regular mesh with interconnections of length independent of the size of the array. This definition is the same one given in [Rao1985]. The first introduction of systolic arrays dates back to 1958 [Unge1958], [McC11958]. With the maturing of VLSI technology they were re-introduced and their potential for compact integration was recognized [Kung1979a], [Leis1981]. Since then, many authors have illustrated how different numerical (see for instance [Kung1979b], [Kung1982], [McWh1983], [Kung1988], [Chua1985], [Schr1985], [Delo1986], [Nava1986], [Jain1986b] and [Krek1988]) as well as combinatorial algorithms, such as sorting and transitive closure

algorithms (see for instance [Lipt1986], and [Kung1988]), can be executed on systolic arrays.

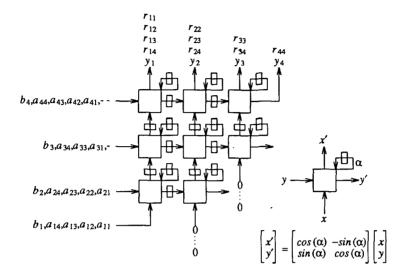

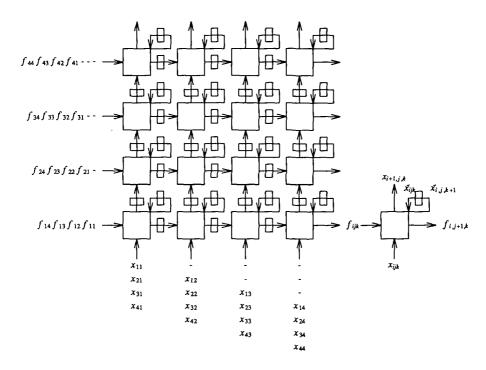

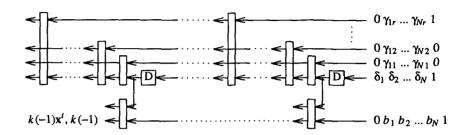

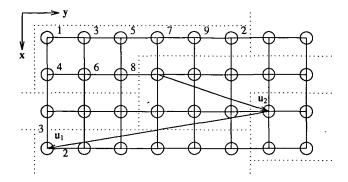

## SYSTOLIC ARRAYS FOR SOLVING SYSTEMS OF LINEAR EQUATIONS

Systolic arrays for the LU and QR factorization of matrices have been presented by different authors [Gent1981], [Leis1981], [Ahme1982]. Linear arrays for the back-substitution were presented in [Leis1981], [Gent1981]. In Figure 1.1(a) a systolic array is shown for the QR factorization of a 4×4 matrix  $A = [a_{ij}] = QR$ , with  $R = [r_{ij}]$ . At the same time the array also computes  $\mathbf{y} = Q^t \mathbf{b}$ , as requested in (1.1.b), with  $\mathbf{y} = [y_1 \cdots y_4]^t$  and  $\mathbf{b} = [b_1 \cdots b_4]^t$ . Since the processor elements of the array operate synchronously, the input data at the inputs at the left of the top two processor elements must be delayed one and two time steps, denoted by "-" and "---", respectively. The squares denote processor elements, which are assumed to have zero processing delay. An interconnection with a delay is denoted by an arrow through a rectangle. An unnumbered rectangle denotes a single delay unit. Otherwise, the number denotes the number of delay units associated with the interconnection.

Each processor element computes the angle needed to zero out an entry in the computation of the upper triangular factor of the coefficient matrix, and applies rotations over this angle on the rest of its input data. The angles  $\alpha$  are stored locally at the processor elements, while the computation of the upper triangular matrix factor progresses upwards in the array. The entries of the upper triangular factor R and the vector  $\mathbf{y}$ , leaving at the top of the array, must be stored and re-ordered for backsubstitution on the bidirectional linear array in Figure 1.1(b).

The entries  $y_i$  of the vector  $\mathbf{y} = Q^t \mathbf{b}$  are propagating to the right, while the computed entries  $x_i$  of the solution vector  $\mathbf{x}$  propagate to the left. Notice that the arrays in Figure 1.1(a) and 1.1(b) are completely different. Not only in terms of processor elements but also in terms of data flow. Also notice that the backsubstitution array starts its computations with  $y_4$  and  $r_{44}$ . These are the last elements produced by the factorization array of Figure 1.1(a), so that there is no concurrency between the computations in the

Figure 1.1. (a) Systolic array for the QR factorization.

two arrays. This lack of concurrency is a serious bottleneck in systolic implementations of the direct methods with backsubstitution.

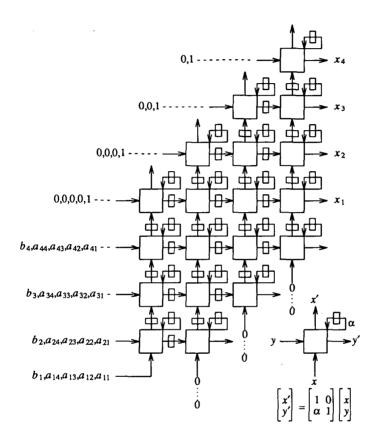

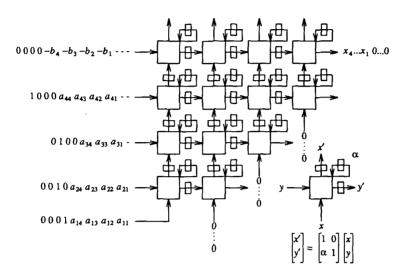

A systolic array for Faddeev's method is shown in Figure 1.2 for an example where  $A \in \mathbb{R}^{4\times 4}$ . Each processor element computes a coefficient  $\alpha$  needed to zero out an element in the computation of the LU factorization of the matrix  $[A^t \mid -I]^t$ . Once this coefficient is computed, the processor element applies linear rotations with this coefficient on the rest of its input data.

Comparing the combination of the factorization and backsubstitution array to the array for Faddeev's method, the simplicity of the last one is striking. But, more important, as shall be illustrated next by a calculation of the number of time steps needed to compute the solution of  $A \mathbf{x} = \mathbf{b}$  by the arrays for both methods, the backsubstitution is a bottleneck in a systolic implementation. From a generalization of Figure 1.1(a) it follows that the QR factorization of an  $N \times N$  matrix takes 3N-2 time steps to compute the upper triangular factor and the transformation of the right hand side vector. And from a generalization of Figure 1.1(b) it follows that the backsubstitution requires 4N-3 time steps

Figure 1.1. (b) Systolic array for the backsubstitution.

to be completed on the linear array (N-1) steps to load the array with the elements of the transformed right hand side, 2N-1 time steps to compute all elements of the solution vector and N-1 time steps to shift the last computed element of the solution vector out of the array). Due to lack of parallelism or pipelining between the computations of the QR factorization and the backsubstitution, the total number of time steps to compute the solution is the addition of the number of time steps for each of them. Hence, the total number of time steps is 7N-5 in this case. On the other hand, from a generalization of the array in Figure 1.2, we find that only 3N time steps are required to compute the solution in this case. This is roughly equal to the number of time steps required for the QR factorization. And Faddeev's array computes the solution roughly twice as fast as the combination of the QR factorization and backsubstitution array. Unfortunately, the Faddeev array is only useful for solving positive definite systems of linear equations, because

Figure 1.2. The Faddeev array for solving systems of linear equations.

pivoting, which is not straight forwardly done on such arrays due to lack of global communication paths, is not needed in such cases<sup>1</sup>. In Chapter 2 we derive a class of feed

<sup>1.</sup> In [Royc1988] it was shown that one can devise LU factorization algorithms with partial pivoting, which can be mapped to systolic arrays. However, the sacrifice being made in these algorithms is that the rows of the upper triangular factor are not naturally ordered at the outputs of the array. Thus, the output at which an entry of the solution vector appears will be depending on the coefficient matrix A. This property implies additional overhead for locating the entries of the solution vector at the outputs of the array in practical implementations.

forward direct methods of which some do not suffer from such pivoting problems. It will appear that the methods of this class can be mapped onto a triangular array, similar to the one in Figure 1.1(a), which is smaller than the array for Faddeev's method.

# 1.2 MAPPING REGULAR RECURRENT ALGORITHMS TO SYSTOLIC ARRAYS

Matrix operations, such as matrix-matrix multiplication and matrix factorization, have a highly regular computational structure. These operations are expressed in the form of multi-dimensional recurrence equations (which will be referred to as regular recurrent algorithms) [Kung1979b], [Mead1980]. The dependencies among the computations in these algorithms are, or can be forced to be regular. This regularity simplifies the analysis of the algorithms in the context of parallel execution of their computations [Karp1967] and it facilitates simple mappings of the algorithms on systolic arrays [Mold1983], [Rao1985], [Fris1986], [Rao1986]. The techniques used in this thesis for scheduling and mapping of the algorithms of Chapter 2 on systolic arrays are to be found in [Rao1985]. For convenience of the reader we shall give a brief review of these techniques in Section 1.2.1.

The synthesis techniques for systolic arrays, presented in [Rao1985] and [Fris1986], yield systolic arrays which are scaled to the size of the problem. Such arrays are called full size systolic arrays (FSA's). However, in practice we cannot go on adding or deleting processor elements in a systolic array when the size of the problem changes. Instead, the systolic array must be embedded in an environment which handles fluctuations of the problem size. Different strategies can be followed to partition a large problem on a small size array. Most notable are the strategies described in [Mold1986], [Hori1987], [Neli1988].

Unfortunately, the partitioning solutions described there have certain shortcomings. The partitioning strategy described in [Mold1986] divides the problem in parts which are

solved in sequence on the small size array. Each processor element of the array is assigned a sequence of computations, for each part. However, although a processor element may have finished its computations for a part, it has yet to wait until the rest of the processor elements of the array have completed their computations for the part, before it can start with the computations of the next part. This implies inefficient use of computational resources.

The partitioning strategy described in [Neli1988] clusters groups of, say, p processor elements on a single processor. The p processor elements in a group are scheduled in sequence and may therefore, be replaced by a single processor element. The analysis of this strategy was carried out only for 1-D groups of processor elements. Independently, in [Hori1987] the 1-D results were generalized for the clustering of 2-D groups of processor elements. However, questions were left open such as how the groups are positioned relatively to each other and under which conditions such 2-D groups do exist. In Section 1.2.2 the two types of partitioning strategies are reviewed and in Chapter 3 it is shown how to eliminate the shortcomings of the strategies described in [Mold1986], [Hori1987], [Neli1988].

# 1.2.1 SYNTHESIZING SYSTOLIC ARRAYS FROM REGULAR RECURRENT ALGORITHMS

#### REGULAR RECURRENT ALGORITHMS AND DEPENDENCY GRAPHS

A regular recurrent algorithm has the following definition<sup>2</sup>.

<sup>2.</sup> In [Mold1983], [Rajo1987], [Bu1988], [Dong1988], [Royc1988] and [Wong1988] systematic procedures are presented for the derivation of such algorithms from code written in a von Neumann high level programming language.

**Definition** 1.1: a regular recurrent algorithm is defined to be a 7-tuple  $\{I^n, V, C, F_V, F_C, s, D\}$ , where:

- In is the index set of the algorithm, which is a lexicographically ordered collection of tuples (i<sub>1</sub>,...,i<sub>n</sub>), where the i<sub>1</sub> to i<sub>n</sub> assume values in (a sub set of) Z. A tuple (i<sub>1</sub>,...,i<sub>n</sub>) is called an index point and to each index point there is associated an index vector i = [i<sub>1</sub>...i<sub>n</sub>]<sup>t</sup>.

- 2. V is a set of indexed variables that are defined at every point in the index set. A variable a at index point i will be denoted by a (i) or a<sub>1</sub>.

- 3. C is a set of control variables, which are defined with the same denotational conventions as the variables in V.

- 4.  $F_V$  is a set of functional relations among the variables of V, restricted to be such that, if  $a(\mathbf{i})$  is computed using  $a(\mathbf{i} \mathbf{d})$ , then  $\mathbf{d}$  is a constant vector, called displacement vector, independent of  $\mathbf{i}$  and the extent of the index space (if  $(\mathbf{i} \mathbf{d})$  falls outside  $\mathbf{I}^n$ , then  $a(\mathbf{i} \mathbf{d})$  is an input variable of the algorithm).

- 5.  $F_C$  is a set of functions, which define functional relations between the variables of C in a way similar to  $F_V$ .

- 6. s is a selector which selects functions from  $F_V$ , depending on the value of the variables in C.

- 7. D is the set of displacement vectors in the algorithm.

**Definition** 1.2: The index set  $I^n$  and the set of displacement vectors D define a dependency graph  $G=\{I^n,D\}$  of the algorithm, where  $I^n$  is the set of vertices and D is the set of directed edges.

The algorithm is said to be regular since the dependencies among the variables are constant. Let  $I^3 = \{(i_1, i_2, i_3) \mid 1 \le i_1 \le N, l_1(i_1) \le i_2 \le u_1(i_1), l_2(i_1, i_2) \le i_3 \le u_2(i_1, i_2)\}$  be a lexicographically ordered index set and  $D = \{d_1, \dots, d_w\}$ . Let  $C = \{a_1, \dots, a_p\}$ ,

$V = \{a_{p+1},...,a_w\}$ ,  $F_V = \{F_1,...,F_q\}$ , where  $F_i(a_{p+1}(\mathbf{i})...a_w(\mathbf{i})) = (a_{p+1}(\mathbf{i}+\mathbf{d}_1)...a_w(\mathbf{i}+\mathbf{d}_w))$ . Let  $F_C = \{F_{q+1}\}$ , where  $F_{q+1}(a_1(\mathbf{i})...a_p(\mathbf{i})) = (a_1(\mathbf{i}+\mathbf{d}_1)...a_p(\mathbf{i}+\mathbf{d}_p))$ . And let s be a selector function from  $V_C$  to  $F_V$ . The regular recurrent algorithm defined by the above is given in Figure 1.3. The selector function is implemented by the case statement and the statement "initializations" refers to the set of input variables of the algorithm. The algorithm is said to be in *input standard* form, because all variables in the domains of the functions  $F_i$ , i=1,...,q+1, are at the same index point.

#### MAPPING REGULAR RECURRENT ALGORITHMS ON FULL SIZE SYSTOLIC ARRAYS

From the dependency graph of the algorithm we can determine a schedule for the computations at the index points. One possible schedule S is the lexicographical order of the index points. This schedule corresponds to the sequential order in which the algorithm in Figure 1.3 is defined. Of all possible schedules we restrict ourselves to linear schedules [Rao1985]. This means that we identify an ordered set of parallel hyperplanes in the index space, which contain only index points in which computations can be scheduled simultaneously. Hyperplane k is characterized by the equation  $s^i i = \rho_k$ , where  $\rho_k$  is a constant and s is the normal of the plane. In order to make this vector unique, we choose it to be a vector which is such that there is at least one coprime pair of entries. This vector is referred to as the schedule vector and the hyperplane is referred to as the schedule plane. The sequence  $\{\rho_1, \dots, \rho_n\}$ , where  $\rho_{i+1} > \rho_i$ , is a new sequence of schedule events for the computations of the algorithm. The fact that all points in a schedule plane are independent (i.e., they can be scheduled in parallel) means that there are no displacement vectors in a schedule plane. Hence, the innerproducts of the schedule vector s and any displacement vector in the dependency graph is non-zero. Moreover, in order to have causality it is further required that these innerproducts are positive. This leads to the inequality:

$$\mathbf{s}^t[\mathbf{d}_1 \cdots \mathbf{d}_{w}] \ge [1 \cdots 1]. \tag{1.12}$$

So far the index points in the dependency graph have been partitioned into sets of points which are scheduled in parallel. By mapping index points, scheduled at different

```

initializations; for i_1 = 1 to N

for i_2 = l_1(i_1) to u_1(i_1)

for i_3 = l_2(i_1, i_2) to u_2(i_1, i_2)

case [a_1(\mathbf{i}) \cdots a_p(\mathbf{i})]

[cv_{11} \cdots cv_{1p}] : (a_{p+1}(\mathbf{i} + \mathbf{d}_{p+1}) \cdots a_w(\mathbf{i} + \mathbf{d}_w)) = F_1(a_{p+1}(\mathbf{i}) \cdots a_w(\mathbf{i}));

\vdots

\vdots

[cv_{q1} \cdots cv_{qp}] : (a_{p+1}(\mathbf{i} + \mathbf{d}_{p+1}) \cdots a_w(\mathbf{i} + \mathbf{d}_w)) = F_q(a_{p+1}(\mathbf{i}) \cdots a_w(\mathbf{i})); endcase

(a_1(\mathbf{i} + \mathbf{d}_1) \cdots a_p(\mathbf{i} + \mathbf{d}_p)) = F_{q+1}(a_1(\mathbf{i}) \cdots a_p(\mathbf{i})); endfor endfor

```

Figure 1.3. A regular recurrent algorithm with three nested loops.

time steps ...,  $\rho_i$ ,  $\rho_{i+1}$ , ..., to a single processor element we can minimize the number of processor elements needed for the execution of the algorithm. Let the integer vector  $\mathbf{t}$  define a line  $\mathbf{i} + v\mathbf{t}$ ,  $\mathbf{i} \in I^n$  and  $v \in \mathbb{Z}$ , on which all index points are not simultaneously scheduled. The vector  $\mathbf{t}$  is made unique requiring that it has at least one coprime pair of entries. Then, with an  $(n-1)\times n$  transformation matrix T,  $T\mathbf{t} = 0$ , we can map all such index points  $\mathbf{i} + v\mathbf{t}$  to a single processor element at location  $\mathbf{i} = T(\mathbf{i} + v\mathbf{t}) = T\mathbf{i}$ . This processor element executes the computations for all the points  $(\mathbf{i} + v\mathbf{t}) \in I^n$ , for  $v \in \mathbb{Z}$ . We refer to  $\mathbf{t}$  as the *projection vector*. The collection  $I^{n-1} = \{\vec{\mathbf{i}} \mid \vec{\mathbf{i}} = T(\mathbf{i} + v\mathbf{t}), \mathbf{i} \in I^n, v \in \mathbb{Z}\}$  is referred to as the *processor space* and is envisualized as the set of processor elements in the full size array (FSA). A processor element  $\vec{\mathbf{i}} = T(\mathbf{i} + v\mathbf{t})$  is scheduled at events  $\{s^i(\mathbf{i} + v\mathbf{t}) \mid v \in \mathbb{Z}\}$ . The set of interconnections in the FSA is given by  $\vec{\mathbf{D}} = \{\vec{\mathbf{d}} \mid \vec{\mathbf{d}} = T\mathbf{d}, \mathbf{d} \in \mathbf{D}\}$  and the number of delay units along an interconnection  $\vec{\mathbf{d}} = T\mathbf{d}$  is given by  $\alpha = s^i\mathbf{d}$ . (Note that if  $s^i\mathbf{t} = 0$  we would map index points, at which computations are scheduled simultaneously, on the same processor element. This is not allowed

and therefore, it is required that  $s^t t \neq 0$ ).

Summarizing, a procedure for synthesizing full size systolic arrays from regular recurrent algorithms is as follows:

1. Find a solution s of the inequality:

$$\mathbf{s}^t[\mathbf{d}_1 \cdots \mathbf{d}_w] \geq [1 \cdots 1].$$

- 2. Select a direction of projection t, such that  $s^t t \neq 0$ .

- 3. Transform the index set of the algorithm according to the rule:

$$\begin{bmatrix} T \\ \mathbf{s}^t \end{bmatrix} \mathbf{i} = \begin{bmatrix} \overline{\mathbf{i}} \\ \rho_k \end{bmatrix}. \tag{1.13}$$

4. Transform the dependencies of the dependency graph according to the rule:

$$\begin{bmatrix} T \\ \mathbf{s}^t \end{bmatrix} (\mathbf{d}_1 \cdots \mathbf{d}_w) = \begin{bmatrix} \begin{bmatrix} \overline{\mathbf{d}}_1 \\ \alpha_1 \end{bmatrix} \cdots \begin{bmatrix} \overline{\mathbf{d}}_w \\ \alpha_w \end{bmatrix} \end{bmatrix}. \tag{1.14}$$

- 5. Identify the set of processor elements of the FSA as the image  $I^{n-1} = \{\overline{i}\}$  of the index set  $I^n$  under the map T. Identify the set of the interconnections between the processor elements as the image  $\overline{D} = \{\overline{d}_j\}$  of the set D under transformation T.

- 6. Identify the schedule sequence  $S(\overline{\mathbf{i}})$  of a processor element  $\overline{\mathbf{i}} = T(\mathbf{i} + v\mathbf{t})$ ,  $v \in \mathbb{Z}$ , as the sequence  $S(\overline{\mathbf{i}}) = \{\rho_v \mid \rho_v = s^t(\mathbf{i} + v\mathbf{t}), (\mathbf{i} + v\mathbf{t}) \in I^n \text{ and } v \in \mathbb{Z}\}$ , which is sorted on the values  $\rho_v$ .

- 7. Identify the delay along an interconnection  $\overline{\mathbf{d}}_j = T \, \mathbf{d}_j$ , as  $\alpha_j = \mathbf{s}^t \, \mathbf{d}_j$ .

In this procedure the order of steps 1) and 2) may be reversed. Steps 1) and 2) define a space-time partitioning of the algorithm, since the transformation  $T(\mathbf{i} + v\mathbf{t})$  specifies the spatial coordinates of the processor elements in the FSA and  $\mathbf{s}'(\mathbf{i} + v\mathbf{t})$  specifies the time coordinates at which processor elements are scheduled. Steps 1) to 7) have been implemented in SYSTARS [Omtz1987], [Omtz1988], a CAD tool for designing systolic

arrays from regular recurrent algorithms.

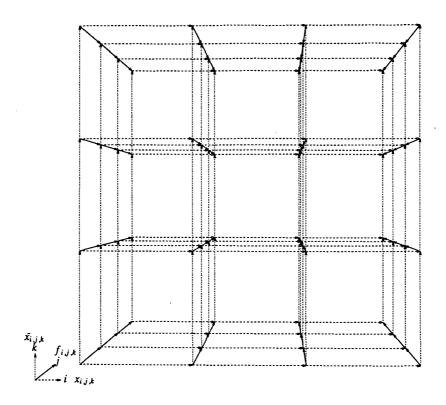

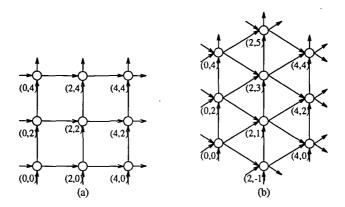

To illustrate the above procedure, we give an example of designing an FSA for the matrix-matrix multiplication  $FX = \tilde{X}$ , where  $F = [f_{ij}]$ ,  $X = [x_{ij}]$  and  $\tilde{X} = [\tilde{x}_{ij}]$  are  $N \times N$  matrices. The matrix-matrix multiplication is written as a regular recurrent algorithm as shown in Figure 1.4.

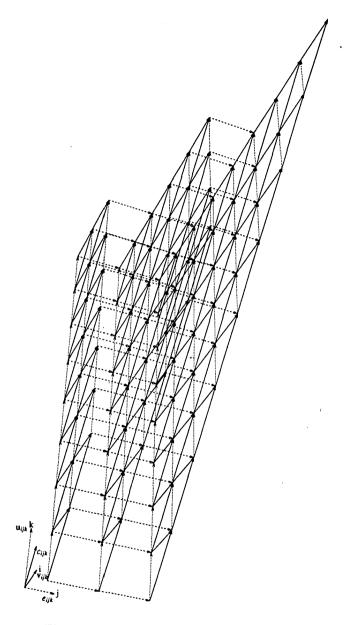

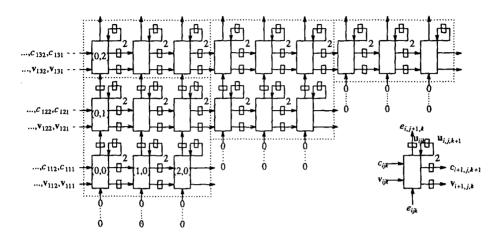

The index set  $I^3$  of this algorithm is the subset  $I^3 = \{(i,j,k) \mid 1 \le i,j,k \le N\}$  and the set of displacement vectors is  $D = \{[0 \ 1 \ 0]^t, [1 \ 0 \ 0]^t, [0 \ 0 \ 1]^t\}$ . The dependency graph  $DG = \{I^3,D\}$  is depicted in Figure 1.5, for N = 4. At a vertex (i,j,k) the variables  $f_{i,j+1,k}, x_{i+1,j,k}$  and  $\tilde{x}_{i,j,k+1}$  are computed and communicated to nodes at relative position  $[0\ 1\ 0]^t, [1\ 0\ 0]^t$  and  $[0\ 0\ 1]^t$ , respectively.

Let us make the choice  $s = [1 \ 1 \ 1]^t$  for the schedule vector and  $t = [0 \ 0 \ 1]^t$  for the projection vector. Then, we may choose for the transformation T:

$$T = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \end{bmatrix}.$$

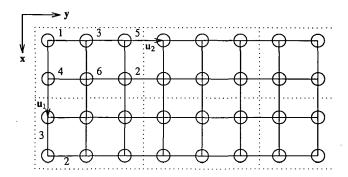

By applying the transformation  $[T^t \mid s]^t$  to the index vectors of  $I^3$  and the displacement vectors of D we obtain a 4×4 systolic array for matrix-matrix multiplication as shown in Figure 1.6. The orientation of the interconnections and the number of delays per interconnection are found from (1.14).

At the inputs at the bottom of the array we find the columns of the matrix X and at the inputs at the left we find the rows of the matrix F. The elements of the matrix X are computed iteratively according to Figure 1.4 and stored in the delays of the loops. Note that variations in the projection vector  $\mathbf{t}$  cause variations in the topology of the systolic array. Similarly, variations in the schedule vector  $\mathbf{s}$  cause variations in the number of delay units along the interconnections of the systolic array.

```

f_{i,0,k} = f_{ik}; /* initialization */

x_{0,j,k} = x_{kj}; /* initialization */

\bar{x}_{i,j,0} = 0; /* initialization */

for i = 1 to N

for j = 1 to N

for k = 1 to N

f_{i,j+1,k} = f_{i,j,k};

x_{i+1,j,k} = x_{i,j,k};

\bar{x}_{i,j,k+1} = \bar{x}_{i,j,k} + f_{i,j,k}x_{i,j,k};

endfor

endfor

```

Figure 1.4. Regular recurrent algorithm for matrix-matrix multiplication.

#### 1.2.2 MAPPING LARGE PROBLEMS TO SMALL SYSTOLIC ARRAYS

A systolic array designed by the procedure outlined in the previous section, has a size which is proportional to the "accidental" size of the problem. Execution of the problem with a different size requires a re-scaling of the array. Here we face a difficulty with ever growing sizes of the problem. In practical situations there is a limit to the up-scaling of a systolic array, due to technological and economic reasons. Hence, it is important to look for partitioning strategies which can solve this scaling problem, so that once the array has been designed it does not have to be re-scaled for a particular problem size.

The partitioning strategies introduced here, act directly on the full size array. The number of processor elements of this array is directly proportional to the size of the problem at hand<sup>3</sup>. The FSA is reduced to a desirable size, yielding a so-called reduced size

Figure 1.5. Dependency graph of matrix-matrix multiplication for N = 4.

array (RSA). It correctly executes the problem partitions and is again systolic.

Common to partitioning strategies is the tessellation of the FSA in tiles of, say, p processor elements each. The way in which the computations in these tiles are scheduled will determine the RSA and how the problem partitions are scheduled on the RSA. The

<sup>3.</sup> Partitioning of the problem itself [Hell1985] is equivalent to the partitioning of the full size array, since problem and array are equivalent with respect to the dependency graph. This equivalence is due to the fact that the transformation matrix in (1.13) is non-singular.

Figure 1.6. A full size systolic array for 4×4 matrix-matrix multiplication.

various ways in which an FSA can be partitioned can be traced to either of the following three cases (or combinations of these) of scheduling the computations of the tiles on a (yet to be designed) RSA.

- All computations in a tile of the FSA are executed by a single processor element of the RSA. Thus the RSA has as many processor elements as there are tiles in the FSA. In general the processor elements and the topology of the RSA are different from those of the FSA.

- 2. The computations of all tiles in the FSA are executed in pipeline on an RSA. The RSA has the same number of processor elements as a tile and the same interconnections as the FSA. Pipelining among the computations of a single tile, if existing in the FSA, as well as the sequence of computations in a tile is preserved in the

RSA.

3. The same as the previous case, except that there is no pipelining among the computations of different tiles.

We shall briefly discuss these three cases in sequence.

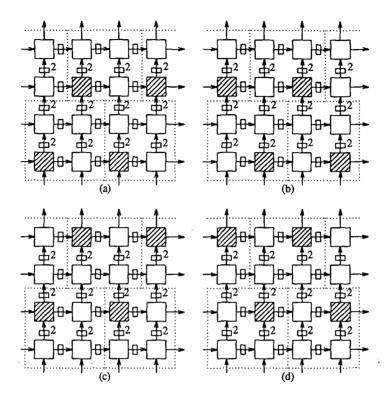

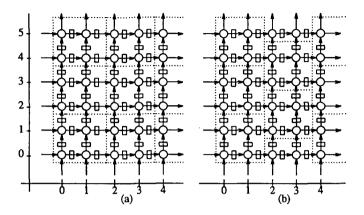

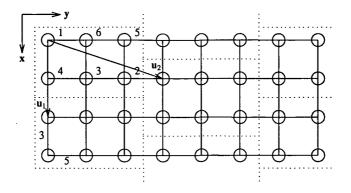

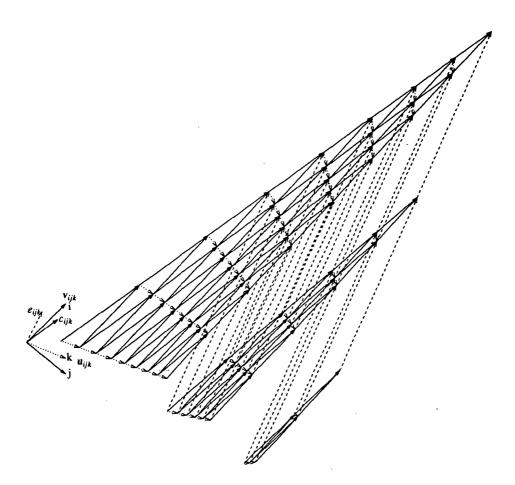

#### Case 1:

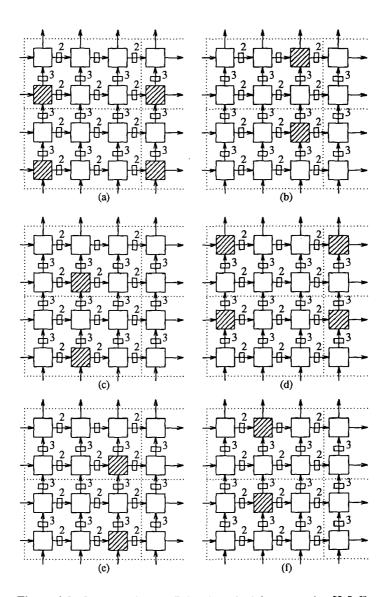

As an example of the first case we partition the  $4\times4$  matrix-matrix multiplication example. Choosing schedule vector  $\mathbf{s} = [1\ 2\ 4]^t$ , we obtain a pattern of activity as shown by the snap shots in Figure 1.7. The self-loops are omitted for the sake of clarity and the active processor elements are hatched. In this pattern we can distinguish tiles of 4 processor elements each. In a tile one and only one processor element is scheduled at any time.

Hence, the 4 processor elements in a tile may be replaced by a single one, a so-called cluster processor. In this way the full size array of 16 processor elements is reduced to an array of only 5 processor elements. This method of partitioning is referred to as the *local-sequential-global-parallel* (LSGP) partitioning strategy. The name refers to the fact that the processor elements in a tile are scheduled sequentially, while processor elements in different tiles may be scheduled in parallel. A tile is referred to as *cluster*. The processor elements in a cluster are called virtual processor elements. The processor elements in the RSA are the cluster processors.

The cluster processors have selectors which select the correct input (a feed back from the processor element itself, or an output of another cluster processor) at the right time. These selectors require control information which is derived from the sequencing of activities in a tile. The cluster processors also have state registers which store the intermediate results.

Observe that there is always one and only one processor element active at a schedule time step when shifting the pattern of tiles across the FSA. For instance, we can shift the pattern over a distance of one column of processor elements to the right and still there is

Figure 1.7. Snapshots of the tiles in the FSA for schedule vector  $s^t = [1 \ 2 \ 4]^t$ .

one and only one processor element active in a tile, at a schedule time step. Depending on the shape of the FSA the pattern of tiles may be shifted in a position where the FSA is covered by a minimum of tiles. For instance, the positioning of the pattern of tiles in Figure 1.7 requires 5 tiles to cover the complete FSA. Shifting the pattern over a distance of one row up needs 8 tiles to cover the complete FSA. And since the number of tiles is equal to the number of cluster processors in the RSA, it follows that the positioning in Figure 1.7 results in only 5 cluster processors, compared to the 8 processors of the second positioning.

The LSGP partitioning strategy was considered in [Neli1988] for 1-D clusters, and in [Hori1987] for 2-D clusters. The analysis given in [Hori1987] does only find a set of

24 1. INTRODUCTION

processor elements which may be clustered, but leaves open questions such as how the clusters are positioned relatively to each other and under what conditions which type of 2-D clusters can be proven to exist. As can be seen from Figure 1.7 ( $s^t = [1\ 2\ 4]$ ) and Figure 1.8 ( $s^t = [2\ 3\ 6]$ ) the clusters can form different patterns, due to different relative positions. Moreover, the relative positions seem to be predetermined by the choice of schedule vector. For example, the relative positions of clusters in Figure 1.8 are not possible for schedule vector  $s^t = [1\ 2\ 4]$  in Figure 1.7. In Chapter 3 an analysis is given to show under what circumstances which 2-D (and 1-D) clusters with certain relative positions exist.

## Case 2:

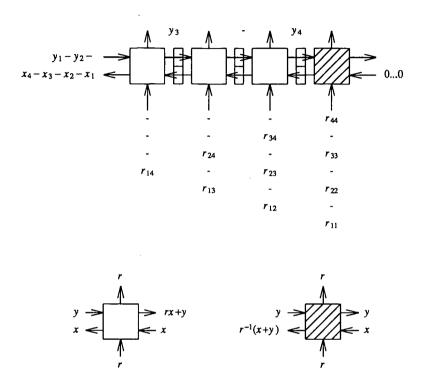

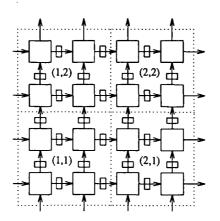

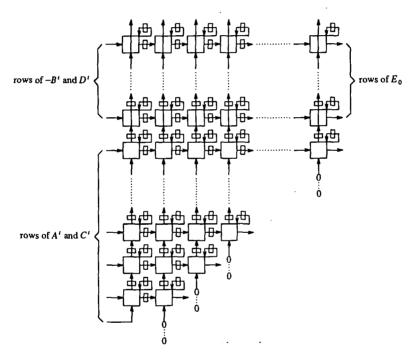

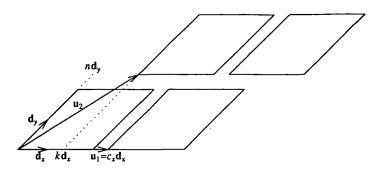

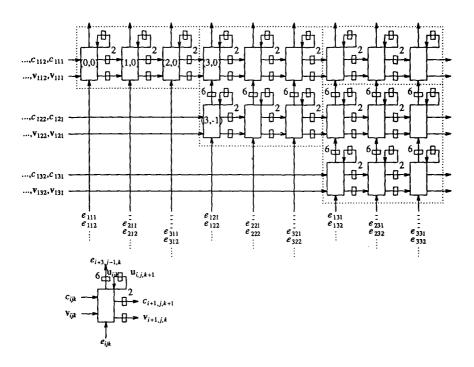

As an illustration of the second case of partitioning we tessellate the matrix-matrix multiplication array of Figure 1.6 in 4 tiles, as shown in Figure 1.9.

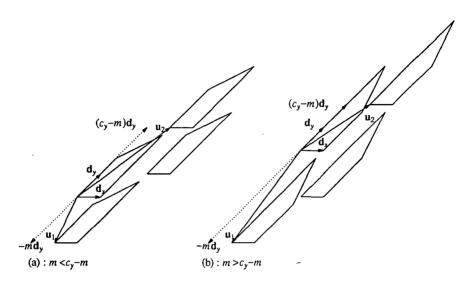

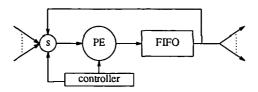

In this partitioning strategy the RSA is identical to a single tile of processor elements in the FSA. The computations of a tile are scheduled on the RSA in the same way as they are scheduled in the tile itself, whereas the computations of different tiles are pipelined on the RSA. This partitioning method is referred to as the *local-parallel-global-pipelined* (LPGP) partitioning strategy. The name refers to the fact that the processor elements in a tile are scheduled in parallel, while the tiles are scheduled in pipeline on the RSA.

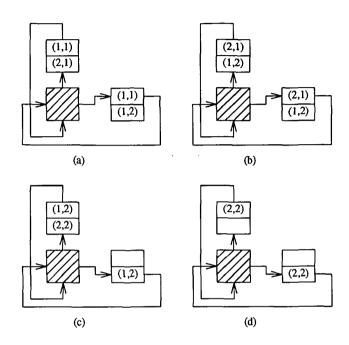

Let us denote (in clockwise direction, starting at the bottom left tile) the tiles in Figure 1.9 by (1,1), (1,2), (2,2) and (2,1), respectively. Now, since all computations inside tile (1,1) precede the computations in the other tiles, the computations for this tile are the first ones to be scheduled on the RSA. The initialization data for the computations of tile (2,1) are collected in the buffers connected to the horizontally oriented outputs of the RSA (see Figure 1.10). Similarly, the initialization data for the computations of tile (1,2) are collected in the buffers connected to the vertically oriented outputs of the RSA.

After the last computation of the bottom left processor element of tile (1,1) has been scheduled on the bottom left processor element of the RSA, the computations in either tile (1,2) or tile (2,1) may be scheduled on this processor element. In this way the

Figure 1.8. Same as Figure 1.7, but for schedule vector  $s^t = [2\ 3\ 6]$ .

computations of different tiles are pipelined on the RSA. We may arbitrarily select the next tile, for instance tile (2,1). Now the data collected in the buffers at the vertically

26 1. INTRODUCTION

Figure 1.9. Tessellation of the matrix-matrix multiplication array.

oriented outputs of the RSA are part of the initializations of the computations of tile (2,2). After the last computation of the bottom left processor element of tile (2,1) has been scheduled on the RSA, the computations of tile (1,2) are scheduled. The data which is collected in the buffers at the horizontally oriented outputs of the RSA are the rest of the initializations for the computations of tile (2,2). Finally, the computations of tile (2,2) are scheduled on the RSA, after the last computation of the bottom left processor element of tile (1,2) has been scheduled.

#### Case 3:

٠,

The third case is identical to the second one, except that the computations of the next tile are scheduled only after the RSA has finished all the computations of the previous tile. That is, the computations in different tiles are executed sequentially on the RSA. The disadvantage of this case, compared to the previous one, is obvious. This partitioning method is referred to as the *local-parallel-global-sequential* (LPGS) partitioning strategy. The name refers to the fact that the processor elements in a tile are scheduled in parallel, while the tiles themselves are scheduled sequentially on the RSA. Partitioning strategies with such schedules are found in [Fort1985], [Hell1985] [Mold1986].

Figure 1.10. Snapshots for the contents of the buffers of the RSA.

The LSGP and the LPGP strategies are two partitioning methods which offer important advantages in the design of practical systolic arrays of fixed dimensions. These advantages are the following. In general the processor elements operate at a much higher I/O bandwidth than busses which supply data to and receive data from the processor elements. If clusters are large enough in an LSGP partitioning, there will be a considerable number of processor elements in each cluster, which do not communicate with processor elements outside the cluster. Since the LSGP partitioning has the effect of serializing the computations in the clusters, the I/O bandwidth of the cluster processors is reduced by a certain factor. Careful choices of cluster sizes may lead to a close match of the I/O bandwidths of the cluster processors and the busses, be it at the expense of increased local memory.

In the LPGP partitioning strategy the I/O bandwidth of the processor elements is unaffected by the partitioning. Moreover all memory to hold the initialization data for the

28 1. INTRODUCTION

computations of the tiles is kept outside the RSA itself. This means that the number of processor elements of the RSA and the amount of local memory of a processor element is independent of the size of the instance of the problem. Thus, a combination of the two partitioning strategies may well serve the purpose of solving such important design issues such as I/O bandwidth matching and problem size independency. In Chapter 3 of this thesis a detailed analysis is given of both partitioning strategies. Additional problems, that appear at the boundaries of an FSA when tessellated, are also discussed<sup>4</sup> there.

<sup>4.</sup> These are problems caused by an incomplete number of processor elements in tiles that may extend across the boundaries of a tessellated FSA. See e.g., Figure 1.7 and Figure 1.8.

# 2. A CLASS OF HIGHLY STRUCTURED ALGORITHMS FOR SOLVING SYSTEMS OF LINEAR EQUATIONS

In this chapter a class of feed forward methods is presented for solving non singular systems of linear equations  $A\mathbf{x} = \mathbf{b}$ ,  $A \in \mathbb{R}^{N \times N}$  and  $\mathbf{b} \in \mathbb{R}^{N}$ . The presentation has the following outline. First, in Section 2.1 it will be assumed that the lower triangular factor L and the inverse  $X^{-1}$  of the remainder X in the factorization A = LX are given. It is then explained how the solution  $\mathbf{x}$  is obtained from the augmented matrix:

$$\begin{bmatrix} L^t & X^{-t} & 0 \\ -\mathbf{b}^t & 0^t & 1 \end{bmatrix},$$

by applying a series of either linear, orthogonal or hyperbolic rotations to this matrix.

Next, in Section 2.2 it is shown how the factors  $L^t$  and  $X^{-t}$  are properly generated and combined with the result of Section 2.1, to give simple feed forward methods for solving  $A\mathbf{x} = \mathbf{b}$ . In Section 2.3 the numerical stability of the methods is discussed and in Section 2.4 it is shown that one of the methods is in fact a semi-direct method, in contrast to the rest, which are all direct methods. Finally, in Section 2.5 it is shown how the methods of Section 2.2 can be generalized to perform computations of the kind  $CA^{-1}B + D$ . This generalization is similar to the generalization of Faddeev's method [Fadd1959].

# 2.1 FEED FORWARD COMPUTATION OF $x = A^{-1}b$

Let  $A \in \mathbb{R}^{N \times N}$  be a non-singular matrix and let  $\mathbf{b} \in \mathbb{R}^N$  be a column vector. The solution of the equation:

$$A\mathbf{x} = \mathbf{b} \tag{2.1}$$

may be expressed in terms of a given lower triangular factorization:

$$A = LX (2.2.a)$$

where L is a lower triangular matrix and the matrix X is one of the following:

- 1. X = U is upper triangular (LU factorization of A);

- 2. X=Q is orthogonal  $(QQ^t = Q^tQ = I)$  (LQ factorization of A);

- 3.  $X=L^t$  is the upper triangular Cholesky factor of the matrix A in case it is symmetric positive definite ( $LL^t$  factorization of A).

Hence, denoting

$$L\mathbf{y} = \mathbf{b},\tag{2.2.b}$$

Equation (2.1) becomes

$$Xx = y. (2.2.c)$$

Equations (2.2.b) and (2.2.c) can be rewritten as follows:

$$\begin{bmatrix} \mathbf{y}^t & 1 \end{bmatrix} \begin{bmatrix} L^t \\ -\mathbf{b}^t \end{bmatrix} = 0, \tag{2.3.a}$$

$$\begin{bmatrix} \mathbf{y}^t & 1 \end{bmatrix} \begin{bmatrix} \mathbf{X}^{-t} \\ 0 \end{bmatrix} = \mathbf{x}^t. \tag{2.3.b}$$

The computation of  $\mathbf{x}$  in (2.3.b) is based on the following observation. The matrix  $[L \mid -\mathbf{b}]^t$  in (2.3.a) is a rectangular  $(N+1)\times N$  matrix, so that it can be reduced to an upper triangular form, with zero last row, by applying a proper sequence of rotations to the matrix. Then, since the last row, say  $\mathbf{r}$ , of this product of rotations satisfies  $\mathbf{r} \begin{bmatrix} L^t \\ -\mathbf{b}^t \end{bmatrix} = 0$ , it must be proportional to  $[\mathbf{y}^t \ 1]$ , given that A is non-singular. Therefore, when this row is

substituted for  $[y^t \ 1]$  in (2.3.b), the result will be a vector proportional to the solution vector  $x^t$ .

Thus, let the sequence of rotations applied to  $[L \mid -\mathbf{b}]^t$  be denoted by the  $(N+1)\times(N+1)$  matrix  $\Theta(m)$ , with  $m \in \{0,1,-1\}$ :

$$\Theta(m) = \prod_{i=1}^{r} \Theta_i(m), \tag{2.4.a}$$

with:

$$\Theta_{i}(m) = \begin{bmatrix} I_{i-1} & & & & \\ & \cos\left(m^{\frac{1}{2}}\alpha_{i}\right) & & -m^{\frac{1}{2}}\sin\left(m^{\frac{1}{2}}\alpha_{i}\right) \\ & & & I_{N-i} \\ & & & & \cos\left(m^{\frac{1}{2}}\alpha_{i}\right) \end{bmatrix}$$

$$(2.4.b)$$

and such that:

$$\Theta(m) \begin{bmatrix} L^t \\ -b^t \end{bmatrix} = \begin{bmatrix} R(m) \\ 0^t \end{bmatrix}, \tag{2.5}$$

where R(m) is upper triangular. That is, the angles  $\alpha_i$  are chosen such that an upper triangularization of the matrix  $[L \mid -\mathbf{b}]^t$  is obtained in the recursion:

$$\begin{bmatrix} L_i^t \\ -\mathbf{b}_i^t \end{bmatrix} = \prod_{j=1}^{i} \Theta_j(m) \begin{bmatrix} L^t \\ \mathbf{b}^t \end{bmatrix}, \quad i=1,2,...,N,$$

(2.6.a)

where:

$$\mathbf{b}_{i}^{t} = [0 \cdots 0 \ b_{i}^{(i)} \cdots b_{N-i}^{(i)}]. \tag{2.6.b}$$

The matrix  $\Theta(m)$  is  $\Sigma(m)$ -orthogonal, i.e.,

$$\Theta^{t}(m)\Sigma(m)\Theta(m) = \Sigma(m), \tag{2.7}$$

with:

$$\Sigma(m) = \begin{bmatrix} I_N \\ m \end{bmatrix}. \tag{2.8}$$

For  $m = \pm 1$ , we also have that :

$$\Theta(m)\Sigma(m)\Theta^{t}(m) = \Sigma(m). \tag{2.9}$$

As yet we have to prove that the angles  $\alpha_i$  exist for given lower triangular matrix  $L = [l_{ij}]$  and vector  $\mathbf{b} = [b_i]$  in either of the cases  $m \in \{0, 1, -1\}$ . For m = 0,  $\alpha_i = -\frac{b_1^{(i)}}{l_{ii}}$  (allowing pivoting in case of zero pivots). Using linear rotations, m = 0, amounts to an LU factorization in (2.5), with  $U = [R^t(0) \mid 0]^t$ . For m = 1,  $tan(\alpha_i) = -\frac{b_1^{(i)}}{l_{ii}}$  always exists, since the function  $tan(\alpha_i)$  has image  $\mathbb{R}$ . Using orthogonal rotations, m = 1, amounts to a QR factorization in (2.5), with  $R = [R^t(1) \mid 0]^t$ .

The use of hyperbolic rotations, m=-1, is restricted to special cases. Namely, to those cases where the elements of the matrix L and the vector  $\mathbf{b}$  are such that  $|\tanh(\alpha_i)| = |\frac{b_1^{(i)}}{l_{ii}}| < 1$ . Only then do the hyperbolic rotations exist. The following proposition states for which case  $\Theta(-1)$  in (2.5) exists.

### Proposition 2.1:

Let  $L \in \mathbb{R}^{N \times N}$  be a lower triangular matrix and  $\mathbf{b} \in \mathbb{R}^{N}$  a vector, such that :

$$LL^t - \mathbf{bb}^t > 0. ag{2.10}$$

Then, there exists a matrix  $\Theta(-1)$  as defined in (2.4.a) and (2.4.b) for m = -1, such that :

$$\Theta(-1) \begin{bmatrix} L^t \\ -\mathbf{b}^t \end{bmatrix} = \begin{bmatrix} R(-1) \\ 0^t \end{bmatrix}, \tag{2.11}$$

where R(-1) is upper triangular.

#### Proof:

For a proof we refer to Appendix A.

The case m = -1 may seem superfluous since it puts a restriction on the vector **b** (see (2.10)). But, as we shall see in Section 2.4, this case is important for computation of maximum entropy approximations of the solution vector.

The proportionality constant between the last row of the matrix  $\Theta(m)$  and  $[y^t \ 1]$  can be found from the properties of the matrix  $\Theta(m)$ , as follows. Write for the  $(N+1)\times(N+1)$  matrix  $\Theta(m)$ :

$$\Theta(m) = \begin{bmatrix} \Theta_{11}(m) & \theta_{12}(m) \\ \theta_{21}^t(m) & k(m) \end{bmatrix}, \ \Theta_{11}(m) \in \mathbb{R}^{N \times N}, \tag{2.12}$$

where k(m) is the proportionality constant. For m = 0 it follows from (2.4.a) and (2.4.b) that k(0) = 1. Hence,  $\theta_{21}(0) = y$  and, consequently:

$$\Theta(0) \begin{bmatrix} L^t & X^{-t} \\ -\mathbf{b}^t & 0^t \end{bmatrix} = \begin{bmatrix} R(0) & * \\ 0^t & \mathbf{x}^t \end{bmatrix}. \tag{2.13}$$

This equation expresses an LU factorization of the matrix  $[L \mid -\mathbf{b}]'$ . For m = 1 or m = -1 we substitute (2.12) in (2.9). This gives:

$$mk(m) + \theta_{21}^{t}(m)\theta_{21}(m) = m.$$

Hence, with  $y = k^{-1}(m)\theta_{21}(m)$  it follows that :

$$k(m) = (1 + my^t y)^{-1/2}$$

(2.14)

Thus:

$$\Theta(m) \begin{bmatrix} L^{t} & X^{-t} & 0 \\ -\mathbf{b}^{t} & 0^{t} & 1 \end{bmatrix} = \begin{bmatrix} R(m) & * & * \\ 0^{t} & k(m)\mathbf{x}^{t} & k(m) \end{bmatrix}, \ m \in \{1, -1\}.$$

(2.15)

`

$\Box$

Using the  $\Sigma(m)$ -orthogonality of  $\Theta(m)$ , we get from (2.15)  $LL^{t} + m\mathbf{b}\mathbf{b}^{t} = R^{t}(m)R(m)$ , so that (2.15) expresses an updating and a downdating of a Cholesky factorization for m = 1 and m = -1, respectively.

A numerically important property of the case m = -1, for  $LL' - \mathbf{bb}' > 0$ , is stated in the following theorem.

## Theorem 2.1:

Let  $L \in \mathbb{R}^{N \times N}$  be a lower triangular matrix and  $\mathbf{b} \in \mathbb{R}^{N}$ , such that the matrix:

$$\begin{bmatrix} 1 & -\mathbf{b}^t \\ -\mathbf{b} & LL^t \end{bmatrix},$$

is positive definite with all its main diagonal entries equal to 1 (this is accomplished by a trivial normalization). Then, the magnitude of all entries of the matrices  $L_i$  and the vectors  $\mathbf{b}_i$  in the recursion (2.6.a)-(2.6.b), for m = -1, is bounded by 1.

## Proof:

The proof is deferred to Section 2.2.3.

# 2.2 THE CLASS OF FEED FORWARD ALGORITHMS

In this section it is shown how the results in (2.13) and (2.15) are combined with the lower triangular factorization of the matrix A, to obtain feed forward methods for solving  $A\mathbf{x} = \mathbf{b}$ .

### 2.2.1 LU FACTORIZATION

Let A = LU be an LU factorization of the matrix A. Then, an LU factorization of the augmented matrix  $[A^t \mid I_N]$  will give:

$$\overline{U}[A^t + I_N] = [L^t + U^{-t}], \tag{2.16}$$

where  $\overline{U} = U^{-t}$ .  $L^t$  and  $U^{-t}$  are the matrix factors appearing in (2.3.a) and (2.3.b). I.e.,  $X^{-t} = U^{-t}$  in (2.3.b). Next, we show how either of the possible factorizations in (2.13) and (2.15) are combined with the LU factorization in (2.16), such that a feed forward method is obtained for solving Ax = b. Put:

$$U_{ij} = \begin{bmatrix} I_{j-1} & & & & \\ & 1 & & & \\ & & I_{i-j} & & \\ & & \alpha_{ij} & 1 & \\ & & & I_{N-i} \end{bmatrix}, i, j=1,...,N-1.$$

(2.17)

The entries of the first column of the strictly lower triangular part of the matrix  $[A^t \mid I_N]$  are eliminated by premultiplication with  $\prod_{i=1}^{N-1} U_{i1}$ , with appropriate  $\alpha_{i1}$ . Hence, the first row of the resulting matrix will be the first row of the matrix  $[L^t \mid U^{-t}]$ . Next the first rotation  $\Theta_1(m)$ , in the product  $\Theta(m)$  in (2.4.a) is applied to this row and the vector  $[-\mathbf{b}^t \mid 0^t]$ , such that the first entry of  $-\mathbf{b}^t$  is eliminated. Secondly, we eliminate the elements of the second column of the strictly lower triangular part of the matrix  $(\prod_{i=1}^{N-1} U_{i1})[A^t \mid I_N]$ , by premultiplication with  $\prod_{i=2}^{N-1} U_{i2}$ , with appropriate  $\alpha_{i2}$ . Thus, obtaining the second row of the matrix  $[L^t \mid U^{-t}]$ . Next, the second rotation  $\Theta_2(m)$ , in the product  $\Theta(m)$  in (2.4.a) is applied to this row and the vector that resulted from the application of the rotation  $\Theta_1(m)$  on  $[-\mathbf{b}^t \mid 0^t]$ .  $\Theta_2(m)$  is chosen such that the second element of this vector is eliminated. The above procedure is repeated until all the elements of the vector  $-\mathbf{b}^t$  are eliminated against the pivots of the matrix  $L^t$ .

Thus, we get the following feed forward computational scheme for Ax = b:

$$\Theta_{N}(m)(\Theta_{N-1}(m)U_{N-1,N-1}) \cdot \cdot \cdot \cdot (\Theta_{2}(m)\prod_{i=2}^{K-1}U_{i2})(\Theta_{1}(m)\prod_{i=1}^{K-1}U_{i1}) \begin{bmatrix} A^{t} & I_{N} & 0 \\ -\mathbf{b}^{t} & 0^{t} & 1 \end{bmatrix} =$$

$$\begin{bmatrix} R(m) & * & * \\ 0^t & k(m)\mathbf{x}^t & k(m) \end{bmatrix}$$

(2.18)

$(m \in \{0,1,-1\})$ . Note, that allowing m=-1 is constrained to the condition that  $LL^t - \mathbf{bb}^t > 0$ , where L is the lower triangular factor of the LU factorization of the matrix A.

Observe that (2.18) expresses an LU factorization of the matrix  $[A \mid -b]^t$  in case we use linear rotations for the  $\Theta_i(m)$  (m=0), i.e., :

$$\Theta_{N}(0)(\Theta_{N-1}(0)U_{N-1,N-1}) \cdot \cdot \cdot \cdot (\Theta_{2}(0)\prod_{i=2}^{N-1}U_{i2})(\Theta_{1}(0)\prod_{i=1}^{N-1}U_{i1})\begin{bmatrix} A^{t} \\ -\mathbf{b}^{t} \end{bmatrix} = \begin{bmatrix} R(0) \\ 0^{t} \end{bmatrix}.$$

(2.19)

Since the LU factorization of a matrix is unique, it follows that different orderings of linear rotations can be applied to obtain the result in (2.18). For instance, the following order of linear rotations (indicated by combinations (i,j) of row i and row j) gives the same result as in (2.18):

$$(N,N+1)$$

,  $(N-1,N)$ , ...,  $(1,2)$  followed by  $(N,N+1)$ ,  $(N-1,N)$ , ...,  $(2,3)$ , etc.

A possible regular, systolic processor array which uses the scheme of linear rotations in (2.19) is shown in Figure 2.1 for N = 4. This array is identical to the one in Figure 1.1(a), except that now the processor elements perform linear rotations and there is an extra row of linear rotors for the elimination of the elements of the vector  $\mathbf{b} = [b_1 \ b_2 \ b_3 \ b_4]^t$ .

Figure 2.1. Systolic array for the feed forward LU method.

## 2.2.2 QR FACTORIZATION

Let A = LQ be the LQ factorization of the matrix A. Then, a QR factorization of the matrix  $[A' \mid I_N]$  will give:

$$\overline{Q}[A^t \mid I_N] = [L^t \mid Q], \tag{2.20}$$

where  $\overline{Q} = Q$ .  $L^t$  and Q are the matrix factors appearing in (2.3.a) and (2.3.b). I.e.,  $X^{-t} = Q$  in (2.3.b). The factorizations in (2.13) and (2.15) are combined with the factorization in (2.20) in the same way as was explained for the LU factorization of  $[A^t \mid I_N]$ , but using circular rotations for the QR factorization of  $[A^t \mid I_N]$ . That is, putting:

$$Q_{ij} = \begin{bmatrix} I_{j-1} & & & \\ & \cos(\alpha_{ij}) & -\sin(\alpha_{ij}) & & \\ & & I_{i-j} & & \\ & \sin(\alpha_{ij}) & \cos(\alpha_{ij}) & & \\ & & & I_{N-i} \end{bmatrix},$$

(2.21)

we get the following feed forward computational scheme for Ax = b:

$$\Theta_{N}(m)(\Theta_{N-1}(m)Q_{N-1,N-1}) \cdot \cdot \cdot \cdot (\Theta_{2}(m)\prod_{i=2}^{N-1}Q_{i2})(\Theta_{1}(m)\prod_{i=1}^{N-1}Q_{i1})\begin{bmatrix} A^{t} & I_{N} & 0 \\ -\mathbf{b}^{t} & 0^{t} & 1 \end{bmatrix} =$$

$$\begin{bmatrix} R(m) & * & * \\ 0^t & k(m)\mathbf{x}^t & k(m) \end{bmatrix}$$

(2.22)

$(m \in \{0,1,-1\})$ . Note, that allowing m=-1 is constrained to the condition that  $LL^t - \mathbf{bb}^t > 0$ , where L is the lower triangular factor of the LQ factorization of the matrix A.

Observe that (2.22) expresses a QR factorization of the matrix  $[A \mid -\mathbf{b}]^t$  in case we use orthogonal rotations for the  $\Theta_i(m)$  (m = 1). I.e.,:

$$\Theta_{N}(1)(\Theta_{N-1}(1)Q_{N-1,N-1}) \cdots (\Theta_{2}(1)\prod_{i=2}^{N-1}Q_{i2})(\Theta_{1}(1)\prod_{i=1}^{N-1}Q_{i1}) \begin{bmatrix} A^{t} \\ -\mathbf{b}^{t} \end{bmatrix} = \begin{bmatrix} R(1) \\ 0^{t} \end{bmatrix}.$$

(2.23)

Since the QR factorization of a matrix is unique, it follows that different orderings of orthogonal rotations may be found by which the result in (2.23) is obtained. For instance, the following order of orthogonal rotations (indicated by combinations (i,j) of row i and row j) gives the same result as in (2.22):

$$(N,N+1)$$

,  $(N-1,N)$ , ...,  $(1,2)$  followed by  $(N,N+1)$ ,  $(N-1,N)$ , ...,  $(2,3)$ , etc.

A regular, systolic processor array which uses the scheme of rotations in (2.23) is

39

identical to the one in Figure 2.1, except that the processor elements perform Givens rotations.

## 2.2.3 SCHUR-CHOLESKY FACTORIZATION

If the coefficient matrix A is a symmetric positive definite matrix, a fast Cholesky factorization of the matrix is possible with the so-called *Generalized Schur* algorithm [Depr1982], [Delo1984]. This algorithm is a generalization of the Schur algorithm for the Cholesky factorization of a symmetric and positive definite Toeplitz or close to Toeplitz matrix [Dewi1978], [Lev1984]. First we shall present the generalized Schur algorithm and its properties, after which it is shown how to combine this algorithm with the factorizations in (2.13) and (2.15), in order to obtain feed forward algorithms.

# The Generalized Schur algorithm

### Theorem 2.2:

Let  $A = [a_{ij}] \in \mathbb{R}^{N \times N}$  be a symmetric positive definite matrix, normalized such that we can write

$$A = R_L + I_N + R_L^t, (2.24)$$

where  $R_L = [a_{ij}]$ , i > j, is the strictly lower triangular part of A. Put :

$$U = R_L + I_N \tag{2.25.a}$$

$$Y = R_L. (2.25.b)$$

Then, there exists a matrix product  $\Phi \in \mathbb{R}^{2N \times 2N}$ :

$$\Phi = \prod_{i=1}^{k-1} \prod_{i=j}^{k-1} \Phi_{ij}, \tag{2.26.a}$$

of embedded plane hyperbolic rotations:

$$\Phi_{ij} = \begin{bmatrix} I_i & & & \\ cosh(\alpha_{ij}) & sinh(\alpha_{ij}) & \\ & I_{N-j-1} & \\ sinh(\alpha_{ij}) & cosh(\alpha_{ij}) \\ & & I_{N+j-i-1} \end{bmatrix}, \qquad (2.26.b)$$

such that the Cholesky factor L' of the matrix A satisfies:

$$\begin{bmatrix} L^t \\ O \end{bmatrix} = \Phi \begin{bmatrix} U^t \\ Y^t \end{bmatrix} . \tag{2.27}$$

Proof:

We refer to Appendix B for the proof.

The hyperbolic rotations  $\Phi_{kk}$ ,  $\Phi_{k+1,k}$ , ...,  $\Phi_{N-1,k}$  in the planes (k+1,N+1), (k+2,N+2), ..., (N,2N-k), respectively, eliminate the elements on the (N-k+1)st diagonal of the matrix:

$$\prod_{j=1}^{\leftarrow} \prod_{i=j}^{\leftarrow} \mathbf{\Phi}_{ij} \begin{bmatrix} U^t \\ Y^t \end{bmatrix}.$$

The matrix  $\Phi$  is *J*-orthogonal, i.e.:

$$\mathbf{\Phi}^t J \mathbf{\Phi} = \mathbf{\Phi} J \mathbf{\Phi}^t = J,\tag{2.28}$$

with:

$$J = I_N \oplus -I_N. \tag{2.29}$$

The product form in (2.26.a) implies a *diagonal*-recursive form for the computation of the Cholesky factor of the matrix A:

$$U_0 = U$$

,  $Y_0 = Y$

$$\begin{bmatrix} U_j^t \\ Y_j^t \end{bmatrix} = \Phi_j \begin{bmatrix} U_{j-1}^t \\ Y_{j-1}^t \end{bmatrix}, \quad j = 1, ..., N-1$$

(2.30)

$$U_{N-1} = L$$

,  $Y_{N-1} = 0$ ,

where

$$\Phi_j = \prod_{i=j}^{N-1} \Phi_{ij}. \tag{2.31}$$

From Theorem 2.2 the factor  $L^t$  is obtained as required in (2.3.a). It remains to show how the factor  $X^{-t} = L^{-1}$ , is obtained for use in (2.3.b). For this purpose we need the following corollary as it follows from Theorem 2.2.

### Corollary 2.1:

The J-orthogonal matrix  $\Phi$  in (2.26.a) is of the global form:

$$\mathbf{\Phi} = \begin{bmatrix} L^{-1} & 0 \\ 0 & R^{-1} \end{bmatrix} \begin{bmatrix} U & -Y \\ -Y^t & U^t \end{bmatrix},\tag{2.32}$$

where

$$A = LL^{t} = RR^{t} \tag{2.33}$$

(L is lower triangular and R is upper triangular).

## Proof:

Let  $\Phi$  be partitioned in  $4 N \times N$  sub matrices: