**Delft University of Technology**

# Microstructure Analysis Based on 3D reconstruction Model and Transient Thermal Impedance Measurement of Resin-reinforced Sintered Ag layer for High power RF device

Hu, X.; Martin, H.A.; Poelma, R H.; Huang, J.L.; Rijckevorsel, H. ; Scholten, H.; Smits, E.C.P. ; van Driel, W.D.; Zhang, G.Q.

DOI 10.1109/EuroSimE56861.2023.10100799

Publication date 2023

**Document Version** Final published version

## Published in

Proceedings of the 2023 24th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE)

## Citation (APA)

Hu, X., Martin, H. A., Poelma, R. H., Huang, J. L., Rijckevorsel, H., Scholten, H., Smits, E. C. P., van Driel, W. D., & Zhang, G. Q. (2023). Microstructure Analysis Based on 3D reconstruction Model and Transient Thermal Impedance Measurement of Resin-reinforced Sintered Ag layer for High power RF device. In *Proceedings of the 2023 24th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE)* (pp. 1-7). (2023 24th International Conference on Thermal, Mechanical and Experiments in Microelectronics and Microsystems (EuroSimE) (pp. 1-7). (2023 24th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Multi-Physics Simulation and Experiments in Microelectronics 2023). IEEE. https://doi.org/10.1109/EuroSimE56861.2023.10100799

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Microstructure Analysis Based on 3D reconstruction Model and Transient Thermal Impedance Measurement of Resin-reinforced Sintered Ag layer for High power RF device

X. Hu<sup>a,b,1</sup>, H.A. Martin<sup>a,c,1</sup>, R.H. Poelma<sup>a</sup>, J.L. Huang<sup>b</sup>, H. Rijckevorsel<sup>b</sup>, H. Scholten<sup>b</sup>, E.C.P. Smits<sup>c</sup>, W.D. van Driel<sup>a</sup> and G.Q. Zhang<sup>a,\*</sup>

<sup>a</sup> Delft University of Technology, Department of Microelectronics, Mekelweg 4, 2628 CD Delft, The Netherlands

<sup>b</sup> Ampleon B.V., Halfgeleiderweg 8, 6534 AV Nijmegen, The Netherlands

<sup>c</sup> Chip Integration Technology Center (CITC), Transistorweg 5T, 6534 AT Nijmegen, The Netherlands

\* Corresponding author.

E-mail address: g.q.zhang@tudelft.nl (G.Q. Zhang)

X. Hu (x.hu-1@tudelft.nl) and H.A. Martin (h.a.martin@tudelft.nl) equally contributed to the present work.

**Abstract**—Resin-reinforced silver (Ag) sintering material is an effective and highly reliable solution for power electronics packaging. The hybrid material's process parameters strongly influence its microstructure and pose a significant challenge in estimating its effective properties as a thin interconnect layer. This research demonstrates a novel 3D reconstruction methodology for the microstructural investigation of the resin-reinforced Ag sintering material from OverMolded Plastic (OMP) packages. Based on the reconstructed models with different sintering parameters (temperature and time), the fraction of Ag and Resin volume distribution, the connectivity of silver particles, and the tortuosity factors were estimated. A 99% connectivity of sintered Ag particles was achieved with various sintering conditions, such as 200°C for 2 hours, 200°C for 4 hours, and 250°C for 2 hours. However, coarsening of Ag particles was promoted when sintered at 250°C. Increasing the sintering time at 200°C had insignificant changes. The estimated tortuosity factor also indicated that sintering at 250°C provides the shortest heat transport path between the semiconductor die and the package substrate. In order to quantify the microstructural findings, the OMP packages' thermal performance with different sintering conditions (temperature, time, and interconnect thickness) was experimentally assessed. Although the experimental measurements were less sensitive to the effective interface thermal resistances', the measurement results show a good correlation with the microstructural analysis. Sintering the Resin-reinforced Ag sintering material at higher temperatures (250°C) seems to improve the package thermal performance, and increasing the sintering time at 200°C has a negligible effect.

**Keywords**—Hybrid Ag Sintering, Pressureless Sintering, 3D Reconstruction, Microstructure Analysis, Tortuosity, Transient Thermal Impedance, LDMOS Body Diode Measurement

### I. INTRODUCTION

The importance of package reliability for power semiconductor devices is becoming more critical than ever, and the choice of die-attach material plays a significant role [1, 2]. High-temperature Pb-rich solders were preferred for power electronics because they offer several advantages, such as high melting point (> 300°C) and relatively low stiffness ( $\sim 45 - 60$  GPa). However, the toxicity of lead caused an increasing need for lead-free compositions. Sintering technology came up as an attractive alternative. Metal precursors in the form of pastes are fused under heat (and pressure), resulting in a significantly high melting point after processing ( $\sim 1000^{\circ}$ C) and superior thermal properties. Despite its benefits, sintering materials are relatively stiff ( $\sim 80 - 130$  GPa) and suffer from thermomechanical stresses. An overview of the current state-ofthe-art sintering materials over traditional solders and a review of various sintering techniques are given in [3, 4, 5].

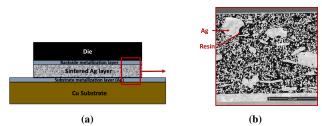

Resin-reinforced sintering material proposed by Sasaki et al. [6] is considered a promising strategy for maintaining favorable sintering properties with reduced stiffness. Thermoplastic resins added to the metal pastes occupy the porous regions during sintering, resulting in a relatively lower modulus [7]. However, the hybrid microstructure of this material makes it very different from traditional sintering materials. An indicative image of the resin-reinforced Ag sintering material is shown in **Figure 1**. Firstly, the composition is made of micro and nano-Ag particles surrounded by thermoplastic resin, which makes it difficult to judge to what degree the Ag particles have been sin-

#### 979-8-3503-4597-1/23/\$31.00 ©2023 IEEE

tered. Besides, the influence of process parameters (temperature and time) for resin-reinforced Ag sintering material has never been addressed. Furthermore, estimating thin interconnect's effective heat transport interactions toward the package's thermal performance remains challenging [8].

Figure 1: (a). A cross-sectional schematic of a semiconductor die sintered to a copper substrate by resin-reinforced Ag sintering material is shown. The backside of the die and the topside of the substrate are metalized with silver to promote adhesion to the dieattach layer. (b). A zoomed-in SEM image of the resin-reinforced Ag sintering material is shown. The sintered layer composes of micro and nano-Ag particles surrounded by thermoplastic resin.

This research investigates the microstructure of resinreinforced Ag sintering material under different processing conditions and its influence on the packaged device's thermal performance. In the next section, we discuss a 3D reconstruction technique to analyze the microstructure of the thin-interconnect material and an experimental methodology to analyze the packaged device's thermal performance. The subsequent section demonstrates the results of the microstructural analysis and transient thermal measurements. Both investigations concluded similar findings with key highlights on the sintering process parameter's influence on the resin-reinforced Ag sintering material's characteristics.

# **II. METHODOLOGY**

## A. Preparation of samples

Silicon-based Laterally Diffused Metal Oxide Semiconductor (LDMOS) high-power RF devices were assembled in Over Molded Plastic (OMP) packages. The semiconductor device's backside was metalized with Ag (~1 $\mu$ m) to promote adhesion to the interconnect material as shown in **Figure 1**. Once metalized, the devices were sintered to a silver-metalized (~6 $\mu$ m) copper substrate using resinreinforced Ag sintering material. The complete stack is then wire-bonded and over-molded. To analyze the influence of sintering conditions, the devices were sintered with different processing parameters: (i.) Bond-Line Thicknesses ( $20\mu$ m &  $60\mu$ m  $\pm$  10 $\mu$ m), (ii.) Sintering temperatures ( $200^{\circ}$ C &  $250^{\circ}$ C), and (iii.) Sintering time (2 hours & 4 hours). All samples were sintered by a pressureless process under an air ambient.

#### B. FIB milling and 3D modeling

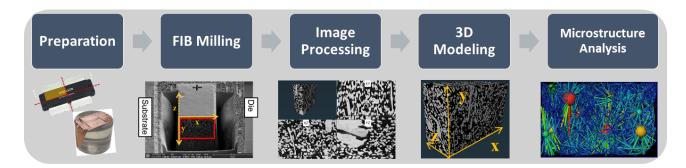

The workflow shown in Figure 2 was followed to analyze the microstructure of the sintered interconnect layer. The OMP packages were dissected and potted with epoxy resin for polishing. After polishing, the sample was set in the Scanning Electron Microscope (SEM) vacuum chamber integrated with a Focused Ion Beam (FIB). The region of interest (ROI) was chosen, and a protective Pt layer of  $1\mu$ m was deposited. Broad and deep U-shaped trenches were milled around the ROI with FIB currents up to 21nA. A reference mark on the ROI surface was made, and then the surface was milled at a fine pitch of 50nm to avoid missing tiny nano-particles. After every milling step, the sample surface was micrographed using SEM. The process described above is automatically implemented by Auto Slice & View 4 Software [9]. Accordingly, more than 200 steps of 50nm pitch were milled, and the micrographs obtained were transformed into a 3-dimensional model using AVIZO (A commercial software for data analysis) [10].

For image processing, the tilt of SEM images was corrected for alignment and a Gaussian filter was chosen to improve the SEM image contrast. The phase segmentation of the sintered Ag and the resin was implemented based on gray-scale thresholding. Finally, the rendered images were

**Figure 2:** The workflow to obtain microstructure information on the resin-reinforced Ag sintering material is shown. The assembled OMP packages were first dissected, and a section of the sample was potted with an epoxy compound for polishing. A Region of Interest (ROI) was chosen in the second step. Broad and deep U-shaped trenches were milled around the ROI using FIB. Sequentially, the region of interest is micrographed using a scanning electron microscope. For each sample, over two-hundred steps of 50nm pitch were continuously milled and micrographed. Tilt correction and phase segmentation are carried out in the image processing step. Subsequently, the rendered images were stitched together to create a 3D geometry of this material. The last step involves identifying the particle volume and connection path based on Generate Pore Network Model (GPNM) in AVIZO for further microstructure analysis.

stitched together as a 3D model for further analysis. To understand the interconnecting network of silver particles, a Generate Pore Network Model (GPNM) was used to identify the particle connection and calculate the tortuosity factor (**Figure 2**). A similar 3D reconstruction method-based FIB-SEM for Ag sintering materials has been described in [11]. The microstructural analysis is further discussed in the results section.

#### C. Transient Thermal Impedance

To experimentally analyze the influence of different sintering conditions on the packaged device's thermal performance, the transient thermal impedance of the OMP packages needs to be measured. The transient thermal impedance is a measure of how effectively the packaging materials can dissipate heat. It is determined by measuring the change in the device junction temperature for applied input power. The sintering parameters such as temperature, time, and Bond-Line Thicknesses (BLT) can affect properties such as thermal resistance and diffusivity, thereby affecting the transient thermal impedance measurement. Hence, to analyze the influence of the sintering parameters, the Junction-to-Ambient transient thermal impedance of the OMP packages was determined by measuring the device junction temperature. Similar experiments for thermal resistance evaluation of Pb solders, Pb-free solders, and Ag sintering materials have been studied in [12].

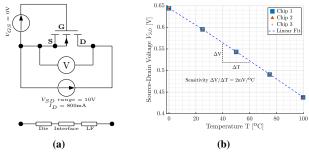

**Figure 3:** (a). The electrical circuit of the MOSFET connected with two source units and one measuring unit with 4-point Kelvin contacts is shown. The electrical resistance of the package is a summation of the semiconductor die, the interface, and the lead frame. The device was measured under reverse biased, i.e.,  $V_{GS} = 0$ ,  $V_{SD} = 10$ V range, and  $I_D = 1$ A. (b). The temperature dependence of the diode's voltage  $V_{SD}$  for three different LDMOS devices were measured and shown. A linear relation is observed with a sensitivity of  $\sim 2$ mV/°C.

The semiconductor device's Temperature Sensitive Electrical Parameters (TSEP) enable measuring the device junction temperature by translating the electrical output to temperature readings. The device was connected with 4-point Kelvin contacts for accurate measurements, as shown in **Figure 3a**. An LDMOS is a voltage-controlled device (i.e.,) the device is forward-biased when a positive voltage is applied between the gate-source  $(+V_{GS})$  and drain-source  $(+V_{DS})$  terminals, reverse-biased when the gate is closed ( $V_{GS} = 0$ ), and a negative voltage is applied between the drain-source terminal  $(-V_{DS} = V_{SD})$ . When

reverse-biased, the device operates through the intrinsic body diode (a PN Junction formed between the source and the drain terminals), which has higher sensitivity to the temperature. The effects of LDMOS body diode reverse bias have been studied in [13]. The temperature sensitivity of the diode voltage, i.e., the source-drain voltage ( $V_{SD}$ ) has a linear response to temperature with a sensitivity of  $\sim 2\text{mV}/^{\circ}\text{C}$  (**Figure 3b**).

To determine the package's thermal impedance, the semiconductor device must be heated, and the junction temperature needs to be simultaneously measured. Hence, a continuous drain current  $I_D$  of 1A was supplied through the body diode for 1000 seconds, resulting in device heating. The changes in the diode voltage  $V_{SD}$  due to device heating were simultaneously measured at a very high sampling rate of  $15\mu$ s per data point for 100 seconds and  $1\mu$ s per data point between 100 and 1000 seconds. The device and the packaging materials reach a steady state during 1000 seconds of heating, which enables the extraction of the die-attach layer properties by deconvolution of the resistance against the capacitance network through the structure-function explained in [14, 15, 16]. For deconvolution and extracting the resistance-capacitance network, TDIM-Master software provided by JEDEC was used [17]. The experimental measurement results are further discussed in the subsequent section.

#### **III. RESULTS**

#### A. Microstructure Analysis

A three-dimensional model was generated for each processing parameter based on the sequential FIB process and computational reconstruction methodology mentioned earlier.

- Model 1 200°C sintering temperature and 2 hours of sintering time

- Model 2 250°C sintering temperature and 2 hours of sintering time

- Model 3 200°C sintering temperature and 4 hours of sintering time

It is assumed that BLT does not influence the material's microstructure because it is a dimensional parameter. Hence, the discussion in this section did not involve the BLT parameter. A Representative Volume Element (RVE) needs to be specified for further steps. The Ag volume fraction of all three models was observed to be stable when the total volume was greater than 4500  $\mu m^3$ . Accordingly, the RVE of all three models was chosen for total volume in the range of 4500  $\mu m^3$ , which results in 2.2 × 10<sup>8</sup> voxels for each model.

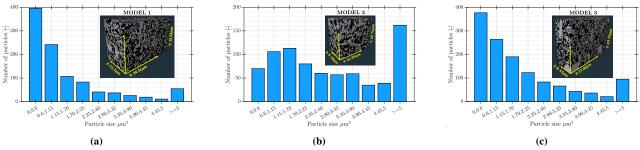

The volume fraction of silver and the resin was further determined. The proportion of sintered silver was less than 50% for all three models, which influences the effective thermal properties. To identify the interconnecting network of silver particles, a 26-neighbor-connectivity criterion (6 faces, 12 edges, and 8 vertexes) was defined for the connection between voxels [18]. The results indicated that the connectivity of the silver particles was above 99% for all three models, which suggests that those seemingly separated particles in Figure 1b were connected in threedimensional space. Subsequently, the particle volume distribution was obtained by separating the connected silver particles. The distribution is graphically shown in Figure 4 along with a 3D-rendered volume of each model. The particle volume distribution results suggest that increasing the sintering time from two to four hours at 200°C has a limited promotion effect on the formation of larger silver particles. Figure 4a and 4c indicate that the amount of small-volume particles ( $\leq 0.6 \mu m^3$ ) is much greater than that of large-volume particles ( $\geq 5\mu m^3$ ) when sintered at 200°C. However, sintering at higher temperatures (250°C) for two hours significantly promoted the formation of large particles  $\geq 5\mu m^3$  (Figure 4b) as compared to sintering at 200°C (Figure 4a & 4c).

To understand the Ag particle connectivity, the tortuosity factors of all three models were determined. The tortuosity factor is often used to describe the transport properties in porous materials. The Tortuosity factor  $\tau$  is defined in equation 1, where *D* is the intrinsic diffusivity of the conductive material,  $D_{eff}$  is the effective diffusivity of the hybrid material, and  $\varepsilon$  is the volume fraction [18].

$$\tau = \varepsilon \frac{D}{D_{eff}} \tag{1}$$

The tortuosity equation represents the diffusive flow of electrical current, heat transport, or mass transport in porous materials, which facilitates in determining the heat transport phenomenon of all three models shown in **Figure 4**. Using the Generate Pore Network Model (GPNM) in AVIZO, the tortuosity factor in all three principal directions (X, Y, and Z) were obtained through diffusion simulation, and the results are tabulated (**Table 1**). The tortuosity factor in the X-direction indicates heat transport along the die attach thickness (out-of-plane direction), and the YZ direction indicates the in-plane heat transport. Based on the estimated tortuosity factor, Model 2 indicates better thermal performance than Models 1 and 3.

The tortuosity factor in the X-direction for Model 2 (sintered at  $250^{\circ}$ C) is lower than Model 1 and 3 (sintered at  $200^{\circ}$ C), which suggests that the connection structure of silver particles in Model 2 has the shortest channel for heat dissipation along the die-attach thickness direction. Likewise, Model 2 also indicates the lowest tortuosity factor in the Y-direction. The tortuosity factor in the Z-direction, i.e., the milling direction exhibits a discrepancy as compared to the X and Y-direction, which can be due to insufficient length along the Z-axis. The anisotropy in the X, Y, and Z directions will not be addressed in this paper.

All microstructure findings are summarized in **Table 1**. The results indicate that all the aforementioned sintering conditions can achieve 99% connectivity of silver particles. However, sintering at 200°C does not lead to silver particles coarsening as observed from the particle volume distribution. Even prolonged sintering at 200°C has a limited effect in promoting silver particle growth. Sintering at 250°C for two hours results in silver particle coarsening, which was verified from particle volume distribution and

**Table 1:** The physical dimensions, the total volume, the fraction of Ag and Resin volume, the Tortuosity factor, and the Ag material's connectivity for all three models are tabulated below.

|                                                             |   | Model 1<br>(200°C/2h) | Model 2<br>(250°C/2h) | Model 3<br>(200°C/4h) |

|-------------------------------------------------------------|---|-----------------------|-----------------------|-----------------------|

| Dimension                                                   |   | $24.3 \times 15.6$    | $23.8 \times 20.7$    | 27.0 × 19.9           |

| $(\mathbf{X} 	imes \mathbf{Y} 	imes \mathbf{Z})$ [ $\mu$ m] |   | × 11.7                | × 9.3                 | × 8.4                 |

| Total<br>Volume [µm <sup>3</sup> ]                          |   | 4448.44               | 4613.38               | 4549.31               |

| Ag Volume<br>Fraction [%]                                   |   | 43.56                 | 47.90                 | 48.91                 |

| Resin Volume<br>Fraction [%]                                |   | 56.43                 | 51.60                 | 51.09                 |

| Tortuosity                                                  | X | 1.79                  | 1.73                  | 1.77                  |

|                                                             | Y | 1.77                  | 1.48                  | 1.62                  |

|                                                             | Z | 1.51                  | 1.70                  | 1.50                  |

| Connectivity [%]                                            |   | 99.75                 | 99.66                 | 99.81                 |

**Figure 4:** (a). The particle volume distribution is graphically shown with a 3D rendered volume of Model 1 (200°C sintering temperature and 2 hours of sintering time). A predominant amount of Ag particle volume is less than 0.6  $\mu m^3$ . (b). The particle volume distribution of Model 2 (250°C sintering temperature and 2 hours of sintering time) is shown. When sintered at 250°C, the Ag particles coarsen, and a majority of the volume is more than or equal to 5  $\mu m^3$  (c). The particle volume distribution of Model 3 (200°C sintering temperature and 4 hours of sintering time) is shown. The Ag particle volume distribution for Model 3 shows similarities with Model 1.

tortuosity factor calculation. Model 2, representing 250°C for two hours sintering condition, has the lowest tortuosity factor along the interconnect thickness, indicating that it has the shortest heat transport channel between the die and substrate. To further quantify the results from the microstructural analysis, the transient thermal impedance of OMP packages with varying sintering conditions was experimentally measured, and the results are presented next.

# B. Transient Thermal Impedance Measurement Results

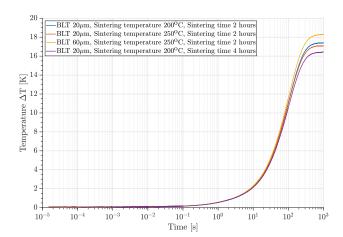

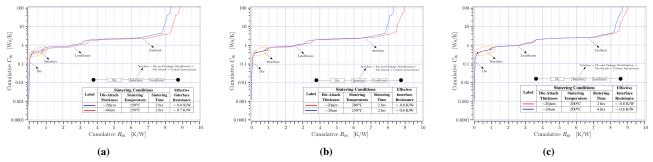

As discussed in the methodology section, the device junction temperature of the various OMP packages fabricated with different sintering parameters was experimentally measured and shown in **Figure 5**. The differences in the steady-state temperature measured correspond to the variations in the packages. Normalizing the measured temperature with the applied input power provides the Junction-to-Ambient transient thermal impedance. However, the steady-state thermal impedance does not indicate the changes in the interface material (die and substrate metallizations + die-attach layer + contact interactions). Hence, the individual layer resistance and capacitance network were deconvoluted using TDIM-Master software and shown in **Figure 6a, 6b, & 6c**.

- Figure 6a indicates the cumulative resistance capacitance network of each layer measured for packages with different BLT but similar sintering temperature and time. The different layers in the packages are marked in the graph. The interface layer indicates a marginal increase in the effective thermal resistance for packages with 60µm BLT than with 20µm BLT.

- Likewise, Figure 6b indicates the cumulative resistance against the capacitance of each layer for packages with different sintering temperatures but uniform BLT and sintering time. It can be observed that the package sintered at 250°C has slightly lower resistance than the package sintered at 200°C.

**Figure 5:** The device was heated by supplying continuous drain current  $I_D$  of 1A through the body diode for 1000 seconds and the change in device junction temperature  $\Delta T$  was simultaneously measured at a very high frequency of  $15\mu$ s for 100 seconds and  $1\mu$ s from 100 to 1000 seconds. Normalizing the junction temperature with the input power provides the Junction to Ambient transient thermal impedance. The changes in the steady-state temperature observed are due to the overall packaging variations.

• Lastly, the effect of sintering time was analyzed and shown in **Figure 6c**, where the cumulative resistancecapacitance network for packages with different sintering time is shown. **Figure 6c** shows a more or less negligible difference between sintering at 200°C for two and four hours.

From **Figure 6**, the effective interface thermal resistance of different OMP packages was estimated by rounding off to its nearest decimal and the results are shown in **Table 2**. Assuming that the packages are identical except for their sintering parameters, the variation in the estimated thermal resistance values should correspond to different sintering conditions. The estimated interface thermal resistance from the high-frequency measurements shown in **Figure 5.** was very much repeatable provided the devices were measured in the same condition. However, for an average of two samples per type, the estimated effective thermal interface resistances were within  $\pm 0.2$ K/W, which is

**Figure 6:** (a). The cumulative resistance-capacitance network is deconvoluted for packages with different BLTs and shown. The highlighted region indicates that the package with a  $20\mu$ m BLT has slightly lower interface resistance as compared to a package with a  $60\mu$ m BLT. (c). The cumulative resistance-capacitance results for packages with different sintering temperatures are shown. The highlighted region indicates that the packages sintered at  $250^{\circ}$ C have slightly improved thermal performance than the packages sintered at  $200^{\circ}$ C. (d). The cumulative resistance-capacitance network deconvoluted for packages with different sintering time is shown. Negligible differences were observed for packages sintered between two and four hours.

**Table 2:** The effective interface resistance for different sintering conditions was estimated by rounding off to its nearest decimal. The thermal resistances mentioned are the effective heat transport property of the interface, which is cumulative of the semiconductor die's backs side metallization ( $\sim 1\mu$ m), Ag sintering material ( $\sim 20/60\mu m \pm 10\mu$ m), the metallization layer on the package substrate ( $\sim 6\mu$ m), and the contact heat transport interaction.

| Sin                                            | Effective            |                                      |                               |

|------------------------------------------------|----------------------|--------------------------------------|-------------------------------|

| Bond-Line                                      | Sintering            | Sintering                            | Interface<br>Resistance       |

| <b>Thickness</b> $\sim 20 \mu \text{m}$        | Temperature<br>200°C | Time<br>2 hrs                        | $\sim 0.8 \text{ K/W}$        |

| $\sim 20\mu \text{m}$<br>$\sim 20\mu \text{m}$ | 200°C                | 2 hrs                                | $\sim 0.8$ K/W $\sim 0.6$ K/W |

| $\sim 20\mu \text{m}$<br>$\sim 60\mu \text{m}$ | 250°C                | $\frac{2 \text{ ms}}{2 \text{ hrs}}$ | $\sim 0.0$ K/W $\sim 0.7$ K/W |

| $\sim 20 \mu \mathrm{m}$                       | 200°C                | 4 hrs                                | $\sim 0.8 \text{ K/W}$        |

almost in the same range as the differences observed for various sintering conditions.

Although the transient thermal impedance methodology is less sensitive to quantitatively estimate the changes in the thin interconnect layer's thermal resistances due to different sintering conditions, the measurement results depicted in Figure 6 correlate with the observations from the microstructural analysis. The packages sintered at 250°C have a slightly lower interface thermal resistance than the packages sintered at 200°C. The same applies also for packages with a thicker BLT ( $\sim 60 \mu$ m) sintered at 250°C. As observed from the particle volume distribution (Figure 4), the experimental measurements shown in Figure 6. also indicates that varying the sintering time from two to four hours at 200°C does not cause any measurable differences in the interface layer. For future research, more samples are needed for larger data sets, and more sintering variations are recommended to quantify the results based on data distribution. Furthermore, the poor measurement sensitivity could be due to large thermal gradients on the die surface, which might require an active cooling block. However, considering that the experimental measurements and the microstructural analysis provide equivalent results suggests that sintering the resin-reinforced Ag sintering material at 250°C is more favorable for efficient package thermal performance.

# **IV. CONCLUSION**

To realize high-efficiency-high-power electronic packages, novel materials such as resin-reinforced Ag sintering with favorable properties are needed to transition towards reliable lead-free solutions. However, the material's microstructure is strongly determined by its processing conditions. Besides, extracting the influence of a thin interconnect's thermal resistance from a packaged product remains challenging. Hence, a novel 3D reconstruction technique was implemented for microstructural investigation. Based on the 3D reconstructed models, Ag particles have 99% connectivity for all sintering conditions, i.e., 200°C for 2 hours, 200°C for 4 hours, and 250°C for 2 hours. The particle volume distribution indicated that the Ag particles coarsening is promoted when sintered at 250°C, and prolonged sintering time at 200°C had insignificant changes. The estimated tortuosity factor also suggests that sintering at 250°C provides the shortest heat transport path between the semiconductor die and the package substrate.

In order to quantify the microstructural findings, the transient thermal impedance of the over-molded packages with different sintering conditions was further measured. The transient thermal measurement methodology had low sensitivity in detecting changes to a thin interconnect layer's thermal resistance for different sintering conditions. However, the measurement results highlighted similar findings to the microstructural analysis, i.e., the packages sintered at 250°C seem to have lower thermal resistance than packages sintered at 200°C. Furthermore, the measurement results for packages sintered at 200°C for two and four hours had a similar thermal resistance, which also aligns with the microstructural investigation. The 3D reconstructed microstructural study and the transient thermal measurement analyses suggest that resin-reinforced Ag sintering material appears to have improved thermal performance when sintered at 250°C with two hours of sintering time. However, the obtained results need further validation. This research aimed to demonstrate new methodologies and understand thin interconnect's behavior on a packaged product. Such techniques are required to characterize the emerging novel materials for interconnect technology and to meet the needs of power device packaging.

#### ACKNOWLEDGEMENT

Thanks to Hozanna Miro and Dustin Laur from the Kavli Nanolab Delft for knowledge support, and Dong Hu from the ECTM group of TU Delft for helping with FIB use. Also, thanks to Ana Guirado and Bert Otterloo from the Failure Analysis laboratory of Ampleon B.V. for sample preparation. This publication is part of the project named Fundamentals of Backside Metals System for 5G RF Power Modules, which is financed by the Dutch Research Council (NWO) under project number 17969.

#### REFERENCES

- Cyril Buttay et al. "State of the art of high temperature power electronics". In: *Materials Science and Engineering: B* 176.4 (2011). Microtechnology and Thermal Problems in Electronics, pp. 283–288. ISSN: 0921-5107.

- [2] Adeel Ahmad Bajwa et al. "Assembly and Packaging Technologies for High-Temperature and High-Power GaN Devices". In: *IEEE Transactions on Components, Packaging and Manufacturing Technology* 5.10 (Oct. 2015), pp. 1402–1416. ISSN: 2156-3950, 2156-3985.

- Wei Liu et al. "Recent Progress in Rapid Sintering of Nanosilver for Electronics Applications". In: *Micromachines* 9 (July 2018), p. 346.

- [4] Haidong Yan et al. "Brief review of silver sinter-bonding processing for packaging high-temperature power devices". In: *Chinese Journal of Electrical Engineering* 6.3 (2020), pp. 25–34.

- [5] Kim S. Siow, ed. Die-Attach Materials for High Temperature Applications in Microelectronics Packaging: Materials, Processes, Equipment, and Reliability. Cham: Springer International Publishing, 2019. ISBN: 978-3-319-99255-6 978-3-319-99256-3.

- [6] Noritsuka Mizumura and Koji Sasaki. "Development of lowtemperature sintered nano-silver pastes using MO technology and resin reinforcing technology". In: 2014 International Conference on Electronics Packaging (ICEP). Apr. 2014, pp. 526–531.

- [7] Koji Sasaki et al. "Development of low-temperature sintering nano-silver die attach materials for bare Cu application". In: 2017 21st European Microelectronics and Packaging Conference (EMPC) Exhibition. 2017, pp. 1–5.

- [8] Dongliang Zhao et al. "Measurement Techniques for Thermal Conductivity and Interfacial Thermal Conductance of Bulk and Thin Film Materials". In: *Journal of Electronic Packaging* 138.4 (Dec. 2016), p. 040802. ISSN: 1043-7398, 1528-9044.

- [9] SOFTWARE FOR ELECTRON MICROSCOPES: Auto Slice View Software. URL: https://www.thermofisher.com/nl/ en/home/electron-microscopy/products/software-em-3d-vis/auto-slice-view-4-software.html.

- [10] SOFTWARE FOR CT AND MICROSCOPY IMAGE DATA VI-SUALIZATION AND ANALYSIS: Avizo Software. URL: https: //www.thermofisher.com/nl/en/home/electronmicroscopy/products/software-em-3d-vis/avizosoftware.html.

- [11] W. Rmili et al. "Quantitative Analysis of Porosity and Transport Properties by FIB-SEM 3D Imaging of a Solder Based Sintered Silver for a New Microelectronic Component". In: *Journal of Electronic Materials* 45.4 (2016), pp. 2242–2251. ISSN: 0361-5235, 1543-186X.

- [12] Dongjin Kim et al. "Online Thermal Resistance and Reliability Characteristic Monitoring of Power Modules With Ag Sinter Joining and Pb, Pb-Free Solders During Power Cycling Test by SiC TEG Chip". In: *IEEE Transactions on Power Electronics* 36.5 (2021), pp. 4977–4990.

- [13] Arash Elhami Khorasani, Mark Griswold, and T. L. Alford. "Gate-Controlled Reverse Recovery for Characterization of LD-MOS Body Diode". In: *IEEE Electron Device Letters* 35.11 (2014), pp. 1079–1081.

- [14] Vladimir Székely and Tran Van Bien. "Fine structure of heat flow path in semiconductor devices: A measurement and identification method". In: *Solid-State Electronics* 31.9 (1988), pp. 1363–1368. ISSN: 0038-1101.

- [15] V. Székely. "A new evaluation method of thermal transient measurement results". In: *Microelectronics Journal* 28.3 (1997). Thermal Investigations of ICs and Microstructures, pp. 277–292. ISSN: 0026-2692.

- [16] M. Rencz et al. "Determining partial thermal resistances with transient measurements, and using the method to detect die attach discontinuities". In: Eighteenth Annual IEEE Semiconductor Thermal Measurement and Management Symposium. Proceedings 2002 (Cat.No.02CH37311). 2002, pp. 15–20.

- [17] JESD51-14 TRANSIENT DUAL INTERFACE TEST METHOD FOR THE MEASUREMENT OF THE THERMAL RESISTANCE JUNCTION-TO-CASE OF SEMICONDUCTOR DEVICES WITH HEAT FLOW THROUGH A SINGLE PATH. URL: https://www. jedec.org/standards-documents/docs/jesd51-14-0.

- [18] Jinlong Fu, Hywel R. Thomas, and Chenfeng Li. "Tortuosity of porous media: Image analysis and physical simulation". In: *Earth-Science Reviews* 212 (Jan. 2021), p. 103439. ISSN: 00128252.