Static and Dynamic Translinear Circuits

### Static and Dynamic Translinear Circuits

### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof.ir. K.F. Wakker, in het openbaar te verdedigen ten overstaan van een commissie, door het College voor Promoties aangewezen, op dinsdag 6 oktober 1998 te 16:00 uur

door

Jan MULDER

elektrotechnisch ingenieur geboren te Medemblik.

Dit proefschrift is goedgekeurd door de promotor:

Prof.dr.ir. A.H.M. van Roermund

### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof.dr.ir. A.H.M. van Roermund, Technische Universiteit Delft, promotor

Prof.dr.ir. J. Davidse, Technische Universiteit Delft Prof.dr.ir. P.M. Dewilde, Technische Universiteit Delft

Prof.dr.ir. B. Nauta,

Prof.dr.ir. E. Seevinck,

Universiteit Twente

Universiteit van Pretoria

Universiteit van Pretoria

Universiteit van Pretoria

Universiteit Delft

Technische Universiteit Delft

Technische Universiteit Delft

### Published and distributed by:

Delft University Press Mekelweg 4 2628 CD Delft The Netherlands

Telephone: +31 15 2783254 Fax: +31 15 2781661

E-mail: DUP@DUP.TUDelft.NL

ISBN 90-407-1710-9 / CIP NUGI 832

Copyright © 1998 by J. Mulder

All rights reserved.

No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without permission from the publisher: Delft University Press.

Printed in the Netherlands

## Contents

| 1 | Int | roduct            | ion                                                 | 1  |  |  |  |  |  |  |

|---|-----|-------------------|-----------------------------------------------------|----|--|--|--|--|--|--|

| 2 | Des | Design principles |                                                     |    |  |  |  |  |  |  |

|   | 2.1 | A gen             | eral approach to companding                         | 7  |  |  |  |  |  |  |

|   | 2.2 |                   | linear principles based on the exponential law      | 15 |  |  |  |  |  |  |

|   |     | 2.2.1             | Static translinear principle                        | 15 |  |  |  |  |  |  |

|   |     | 2.2.2             | Dynamic translinear principle                       | 18 |  |  |  |  |  |  |

|   | 2.3 | Voltag            | ge-translinear principles based on the square law   | 22 |  |  |  |  |  |  |

|   |     | 2.3.1             | Static voltage-translinear principle                | 22 |  |  |  |  |  |  |

|   |     | 2.3.2             | Dynamic voltage-translinear principle               | 24 |  |  |  |  |  |  |

| 3 | Ana | alvsis o          | of translinear circuits                             | 29 |  |  |  |  |  |  |

|   | 3.1 | •                 | rsis of static translinear circuits                 | 29 |  |  |  |  |  |  |

|   | 3.2 |                   | sis of dynamic translinear circuits                 | 36 |  |  |  |  |  |  |

|   |     | 3.2.1             | Global current-mode analysis                        | 36 |  |  |  |  |  |  |

|   |     | 3.2.2             | State-space current-mode analysis                   | 44 |  |  |  |  |  |  |

|   |     | 3.2.3             | Alternative analysis methods                        | 51 |  |  |  |  |  |  |

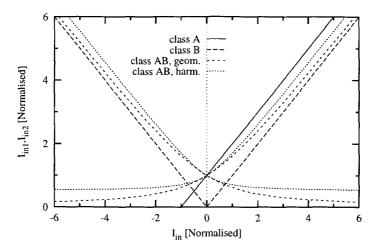

|   | 3.3 | Chara             | exteristics of different translinear filter classes | 55 |  |  |  |  |  |  |

|   |     | 3.3.1             | log-domain filters                                  | 56 |  |  |  |  |  |  |

|   |     | 3.3.2             | tanh filters                                        | 61 |  |  |  |  |  |  |

|   |     | 3.3.3             | sinh filters                                        | 65 |  |  |  |  |  |  |

| 4 | Syn | thesis            | of translinear circuits                             | 73 |  |  |  |  |  |  |

|   | 4.1 |                   | riew of the synthesis method                        | 74 |  |  |  |  |  |  |

|   | 4.2 | Trans             | linear transfer functions                           | 76 |  |  |  |  |  |  |

|   |     | 4.2.1             | Static transfer functions                           | 76 |  |  |  |  |  |  |

|   |     | 4.2.2             |                                                     | 78 |  |  |  |  |  |  |

|   |     | 4.2.3             | Dimension transformations                           | 79 |  |  |  |  |  |  |

|   | 4.3 | Defini            | tion of capacitance currents                        | 83 |  |  |  |  |  |  |

|   |     | 4.3.1             | State-space approach                                | 83 |  |  |  |  |  |  |

|   |     | 4.3.2             | Linear transformations                              |    |  |  |  |  |  |  |

vi Contents

|   |                                                              | 4.3.3 Single-state non-linear transformations                   | 89  |  |  |  |

|---|--------------------------------------------------------------|-----------------------------------------------------------------|-----|--|--|--|

|   |                                                              | 4.3.4 General non-linear transformations                        | 90  |  |  |  |

|   | 4.4                                                          | Translinear function decomposition                              | 91  |  |  |  |

|   |                                                              | 4.4.1 Non-parametric decomposition                              | 92  |  |  |  |

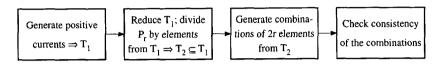

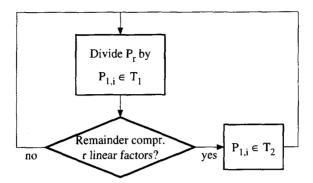

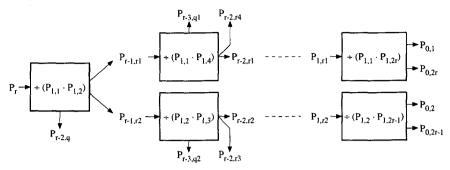

|   |                                                              | 4.4.2 An algorithm for non-parametric decomposition             | 96  |  |  |  |

|   |                                                              | 4.4.3 Parametric decomposition                                  |     |  |  |  |

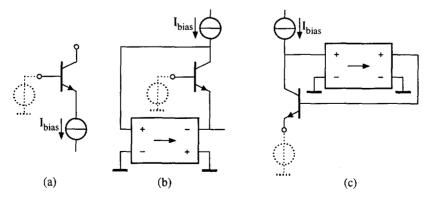

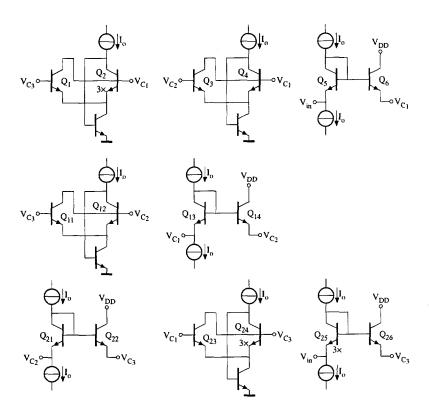

|   | 4.5                                                          | Hardware implementation                                         | 107 |  |  |  |

|   |                                                              | 4.5.1 Topology selection and biasing                            | 108 |  |  |  |

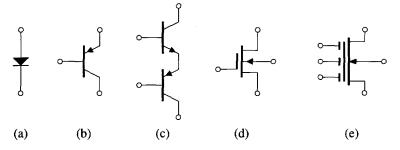

|   |                                                              | 4.5.2 Translinear devices                                       |     |  |  |  |

|   | 4.6 Alternative synthesis methods for dynamic translinear co |                                                                 |     |  |  |  |

|   |                                                              | 4.6.1 Synthesis based on exponential transformations            | 132 |  |  |  |

|   |                                                              | 4.6.2 Synthesis based on component substitution                 |     |  |  |  |

|   |                                                              | 4.6.3 Synthesis based on Bernoulli's differential equation      | 135 |  |  |  |

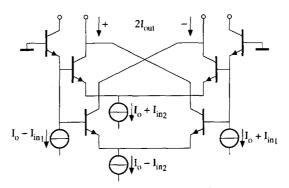

|   | 4.7                                                          | Class-AB operation                                              | 136 |  |  |  |

| 5 | Des                                                          | ice non-idealities                                              | 141 |  |  |  |

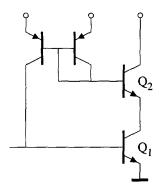

| • | 5.1                                                          | Base currents                                                   | 142 |  |  |  |

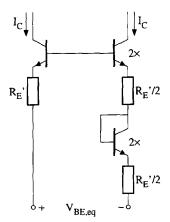

|   | 5.2                                                          | Parasitic resistances                                           |     |  |  |  |

|   | 5.3                                                          | Body effect                                                     |     |  |  |  |

|   | 5.4                                                          | Early effect                                                    |     |  |  |  |

|   | 5.5                                                          | Parasitic capacitances                                          |     |  |  |  |

| ÷ | 5.6                                                          | Mismatch                                                        |     |  |  |  |

| 6 | Noi                                                          | se 1                                                            | 157 |  |  |  |

| Ü | 6.1                                                          | Definitions of dynamic range and signal-to-noise ratio          |     |  |  |  |

|   | 6.2                                                          | Transistor noise sources                                        |     |  |  |  |

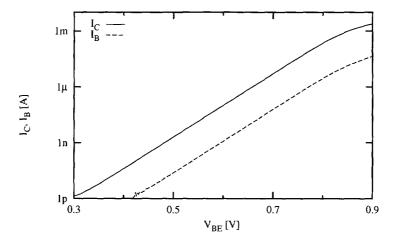

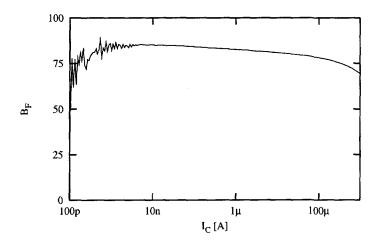

|   | ٠.٠                                                          | 6.2.1 Bipolar transistor                                        |     |  |  |  |

|   |                                                              | 6.2.2 Subthreshold MOS transistor                               |     |  |  |  |

|   | 6.3                                                          | Noise in non-linear circuits                                    |     |  |  |  |

|   | 6.4                                                          | Noise in static translinear circuits                            |     |  |  |  |

|   | •                                                            | 6.4.1 Noise analysis method                                     |     |  |  |  |

|   |                                                              | 6.4.2 Analysis examples                                         |     |  |  |  |

|   | 6.5                                                          | Noise in translinear filters                                    |     |  |  |  |

|   |                                                              | 6.5.1 Dynamic range considerations                              |     |  |  |  |

|   |                                                              | 6.5.2 Noise analysis method                                     |     |  |  |  |

|   |                                                              | 6.5.3 Analysis examples                                         |     |  |  |  |

| 7 | Vol                                                          | age-translinear circuits                                        | 191 |  |  |  |

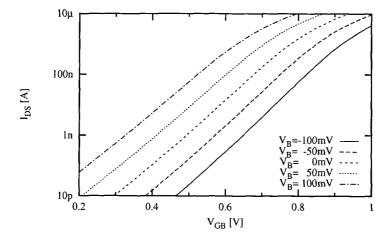

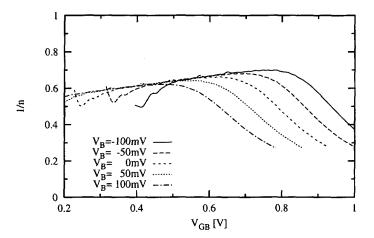

| • | 7.1                                                          | Square law conformance                                          |     |  |  |  |

|   | 7.2                                                          | Designability                                                   |     |  |  |  |

|   | 7.3                                                          | Analysis of dynamic voltage-translinear circuits                |     |  |  |  |

|   | 7.4                                                          | Characteristics of different voltage-translinear filter classes |     |  |  |  |

Contents vii

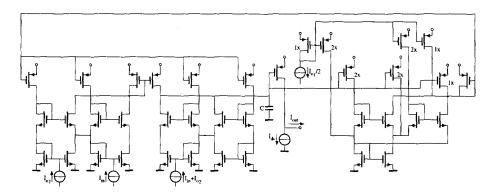

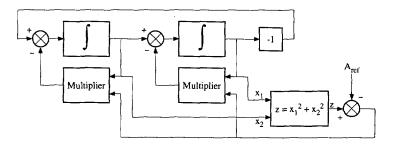

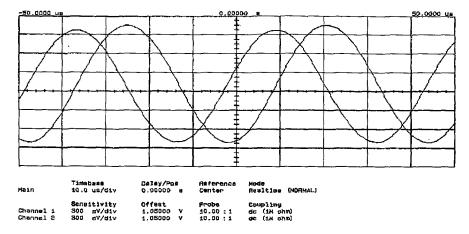

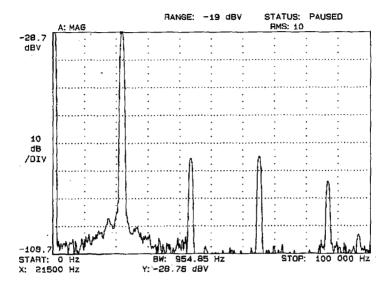

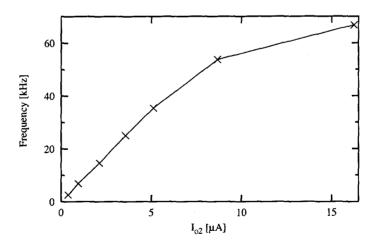

| 8                    | Rea            | lisatio  | ns                                                     | 197 |  |  |  |

|----------------------|----------------|----------|--------------------------------------------------------|-----|--|--|--|

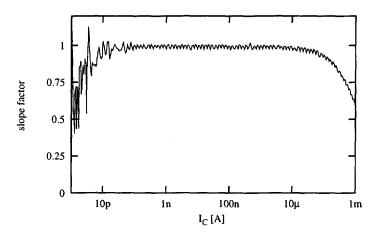

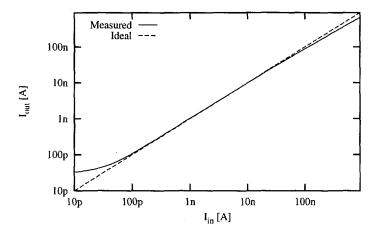

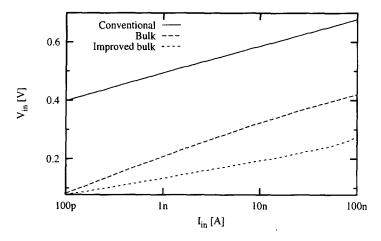

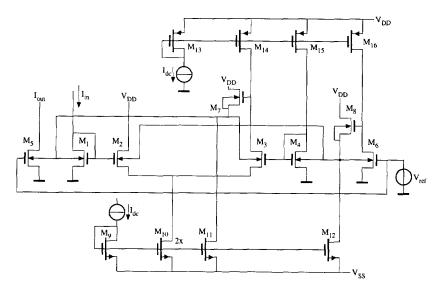

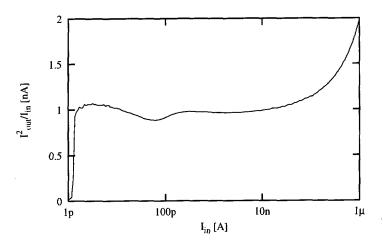

|                      | 8.1            | Subthr   | reshold MOS translinear circuits                       | 197 |  |  |  |

|                      |                | 8.1.1    | Bulk current-mirror                                    | 198 |  |  |  |

|                      |                | 8.1.2    | A sin x-circuit in MOS technology using the back-gate  | 200 |  |  |  |

|                      |                | 8.1.3    | High-swing cascode MOS current mirror                  | 203 |  |  |  |

|                      | 8.2            | A tran   | slinear integrator for audio filter applications       |     |  |  |  |

|                      |                | 8.2.1    | Design of the integrator                               | 206 |  |  |  |

|                      |                | 8.2.2    | An application example for hearing instruments         |     |  |  |  |

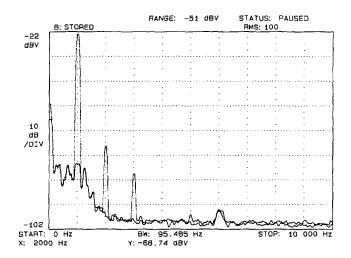

|                      |                | 8.2.3    | Measurement results                                    |     |  |  |  |

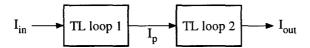

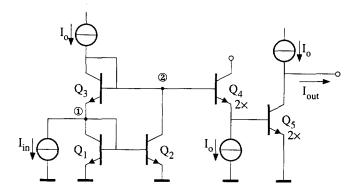

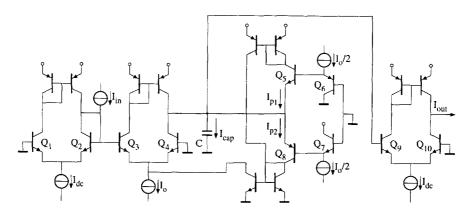

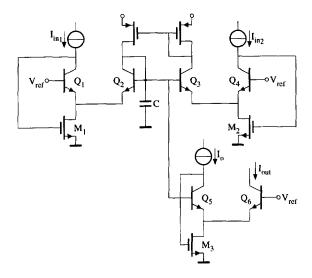

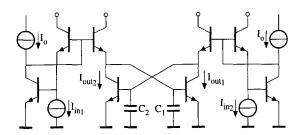

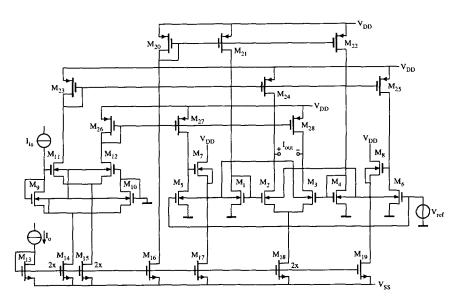

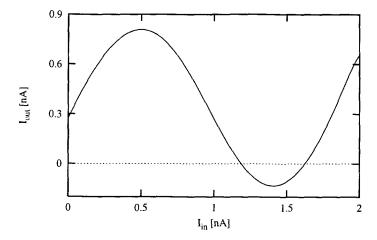

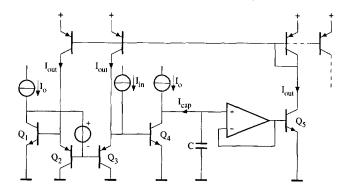

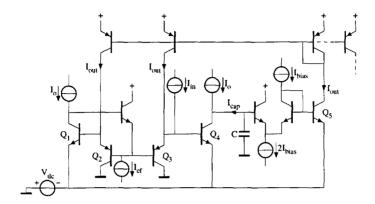

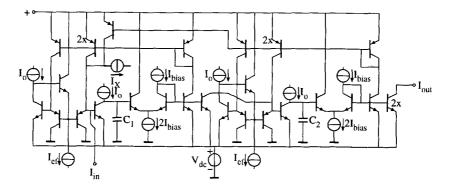

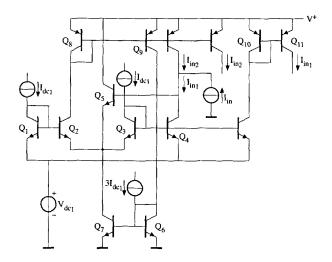

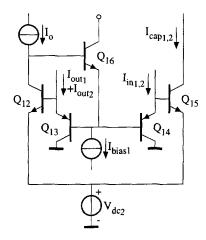

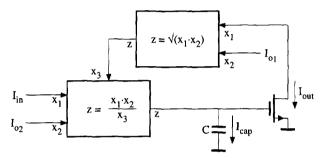

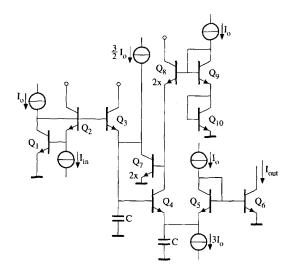

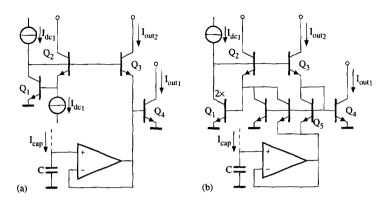

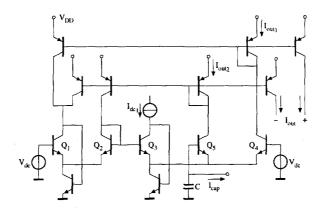

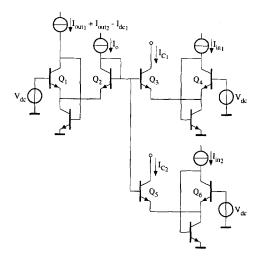

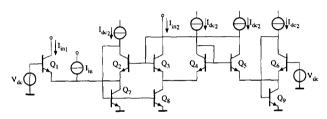

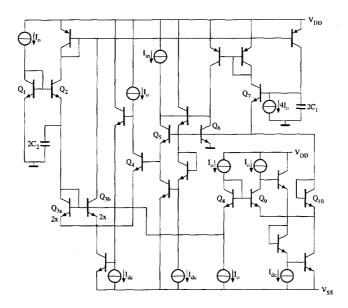

|                      | 8.3            | A 1-vo   | lt class-AB translinear integrator                     | 211 |  |  |  |

|                      |                | 8.3.1    | Block schematic of the integrator                      | 213 |  |  |  |

|                      |                | 8.3.2    | Design of the individual blocks                        |     |  |  |  |

|                      |                | 8.3.3    | Measurement results                                    |     |  |  |  |

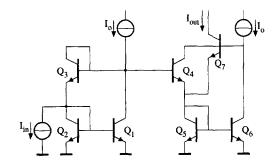

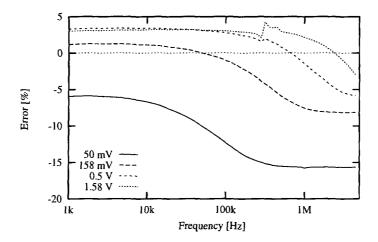

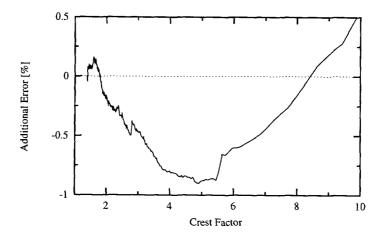

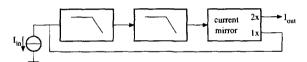

|                      | 8.4            | A dyna   | amic translinear RMS-DC converter                      |     |  |  |  |

|                      |                | 8.4.1    | Design of the RMS-DC converter                         |     |  |  |  |

|                      |                | 8.4.2    | Measurement results                                    |     |  |  |  |

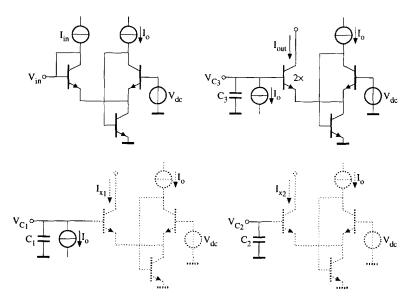

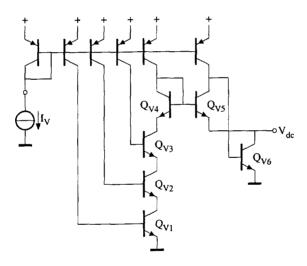

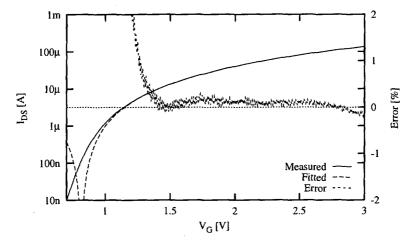

|                      | 8.5            | A 3.3-   | volt current-controlled voltage-translinear oscillator | 225 |  |  |  |

|                      |                | 8.5.1    | Square law conformance                                 |     |  |  |  |

|                      |                | 8.5.2    | Design of a voltage-translinear integrator             |     |  |  |  |

|                      |                | 8.5.3    | Design of the oscillator                               |     |  |  |  |

|                      |                | 8.5.4    | Measurement results                                    |     |  |  |  |

| _                    | ~              |          |                                                        |     |  |  |  |

| 9                    | Con            | clusior  | 18                                                     | 235 |  |  |  |

| A                    | $\mathbf{Add}$ | litional | design examples                                        | 239 |  |  |  |

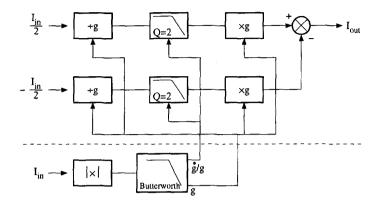

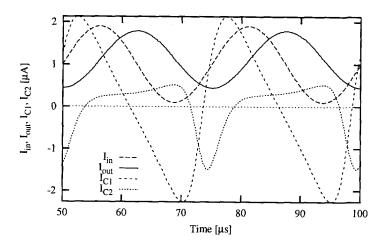

|                      | A.1            | A sylla  | abic companding translinear filter                     |     |  |  |  |

|                      |                | A.1.1    | Distortionless syllabic companding                     | 240 |  |  |  |

|                      |                | A.1.2    | Translinear implementation                             | 242 |  |  |  |

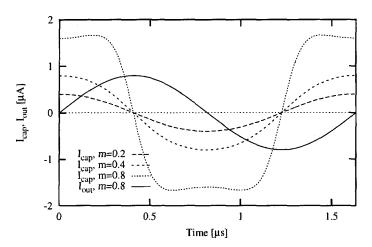

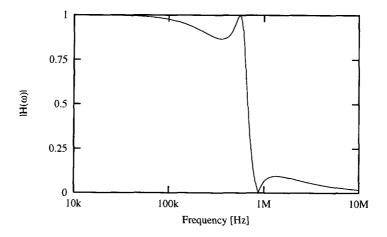

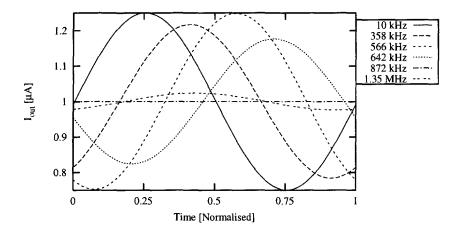

|                      |                | A.1.3    | Simulation results                                     | 245 |  |  |  |

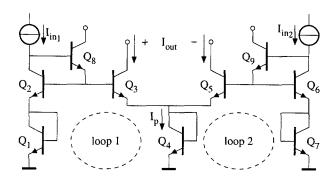

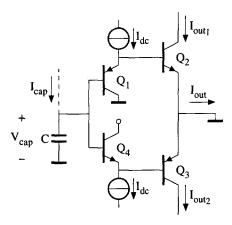

|                      | A.2            | A harn   | nonic mean class-AB integrator                         | 247 |  |  |  |

|                      |                | A.2.1    | Capacitance currents                                   | 249 |  |  |  |

|                      |                | A.2.2    | Design of the integrator                               | 250 |  |  |  |

|                      | A.3            | A seco   | nd-order low-pass filter                               | 254 |  |  |  |

|                      |                | A.3.1    | Design of the filter                                   | 254 |  |  |  |

|                      |                | A.3.2    | Simulation results                                     | 256 |  |  |  |

| Bi                   | bliog          | raphy    |                                                        | 259 |  |  |  |

| Su                   | mma            | ary      |                                                        | 271 |  |  |  |

| Samenvatting 2       |                |          |                                                        |     |  |  |  |

| Acknowledgements 279 |                |          |                                                        |     |  |  |  |

| viii                 | Contents |

|----------------------|----------|

| Biography            | 281      |

| List of publications | 283      |

Due to the ongoing trends towards lower supply voltages and low-power operation, the area of analogue integrated filters is facing serious challenges. The supply voltage severely restricts the maximum dynamic range achievable using conventional filter implementation techniques, such as opamp-MOSFET-C, transconductance-C and switched-capacitor. In ultra-low-power environments, linear resistors become too large for on-chip integration. The situation is even further complicated by high-frequency demands and the fact that the filter transfer function often has to be tunable.

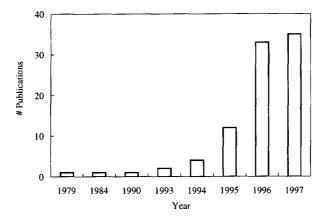

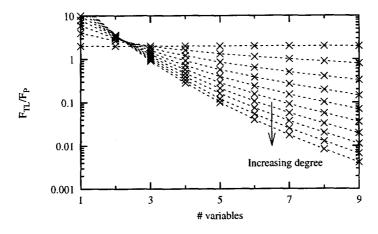

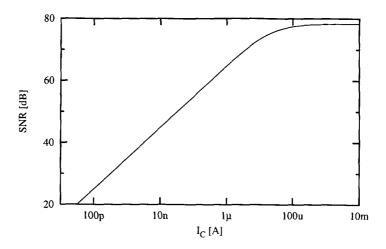

In the area of *continuous-time* filters, a promising approach to meet these challenges is provided by the class of 'Translinear Filters'. Due to the encouraging expectations, research efforts have increased rapidly and TransLinear (TL) filter design has become a trend. This is illustrated by Fig. 1.1.

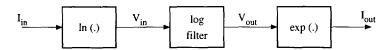

Translinear filters were originally introduced by Adams in 1979 [1]. Since Adams at the time did not recognise the TL nature of these circuits, he coined the term 'log-Domain Filters', based on the logarithmic relation between the voltages and currents. For many years, the idea of log-domain filtering was to gather dust. In 1990, Seevinck independently reinvented the TL filter concept, which he called 'Current-mode Companding' [2].

The filters presented by Adams and Seevinck were first-order. Interest in TL filters really took off in 1993, when Frey published a synthesis method enabling the design of higher-order log-domain filters [3]. In addition, Frey proposed a more general class of TL filters, which he termed 'Exponential State-Space Filters' [4].

From that time, many other researchers began to investigate these circuits. Tournazou et al. published an implementation in weak inversion MOS, showing the potential for low-power operation [5]. The first experimental results were published by Perry and Roberts [6]. In addition, they proposed an alternative

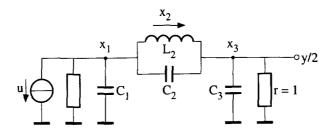

Figure 1.1: Publications on dynamic translinear circuits.

synthesis method based on the simulation of LC ladder filters. The first experimental results in subthreshold MOS were presented by Ngarmnil  $et\ al.\ [7]$ . Punzenberger  $et\ al.\$ demonstrated the suitability for low-voltage applications [8] and the favourable dynamic range specification resulting from class-AB operation: 65 dB at a 1.2 V supply voltage [9]. Different synthesis methods were proposed by various researchers [10–15]. A general analysis method was published by Mulder  $et\ al.\ [16]$ , who also coined the term 'Translinear Filter'. Alternative analysis methods were described in [14, 17, 18]. Application of the underlying design principle to non-linear dynamic functions was proposed by various researchers. These applications include oscillators [19–21], RMS-DC converters [22,23], mixer-filter combinations [24,25] and phase-locked loops [26–28]. A generalisation to strong inversion MOS was proposed independently by Mulder  $et\ al.\ [29]$  and Payne  $et\ al.\ [30]$ . At present, there are many research efforts in the area of noise analysis [31–39] and other second-order effects [40,41].

Translinear filters are based on the 'Dynamic Translinear Principle' [42], which is a generalisation of the conventional 'Static Translinear Principle' formulated by Gilbert in 1975 [43]. Both Static TransLinear (STL) and Dynamic TransLinear (DTL) circuits exploit specific properties of the exponential function. In STL circuits, the equivalence relation:

$$e^a \cdot e^b = e^{a+b}, \tag{1.1}$$

is used to realise a multiplication in the current domain by an addition in the voltage domain. In DTL circuits, the feature:

$$\frac{\mathrm{d}\mathrm{e}^{x(t)}}{\mathrm{d}t} = \mathrm{e}^{x(t)} \cdot \frac{\mathrm{d}x(t)}{\mathrm{d}t},\tag{1.2}$$

is used to implement the time derivative of a current by means of a product of currents, which in turn is realised by means of eqn (1.1).

### Static translinear circuits

The multiplication properties of the exponential function are fundamental to conventional TL circuits. The first TL circuits, a current amplifier and a multiplier, were proposed by Gilbert in 1968 [44,45]. Gilbert also formulated the (static) 'Translinear Principle' in 1975 [43]. In 1979, Hart formulated a slightly more general form of the TL principle by including PTAT¹ voltage sources in the TL loops [46].

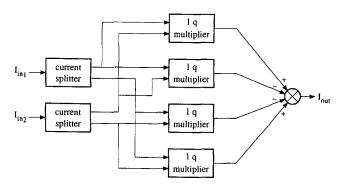

It was soon realised that STL circuits can be used to implement a wide variety of both linear and non-linear *static* transfer functions. Successively, many new circuits were published including: amplifiers [44], multiplier/dividers [45, 47–49], square function [50], square-root function [50], cross quads [51], digital signal processing [52–54], absolute value function [50], sine approximation [43], geometric and harmonic mean functions [50, 55], RMS-DC conversion [56, 57], vector magnitude circuits [43, 58] and frequency-doubling circuits [59, 60].

The design of most of these circuits was based on a heuristic approach. A systematic approach to the analysis and synthesis of STL circuits was developed by Seevinck [50]. Next to [50], overviews on STL circuit design can be found in [61–65].

Most theory and circuit designs were developed during the seventies. In more recent years, STL circuits have experienced a revival due to the trend towards low-voltage and low-power operation. Especially in the area of analogue VLSI (neural) networks, where a high functional density is of primary importance, STL circuits implemented by MOS transistors operated in the weak inversion region have found wide employment, see, e.g., [65,66].

### Voltage-translinear circuits

Translinear circuits are based on the exponential characteristics of the bipolar or subthreshold MOS transistor. In the strong inversion region, the MOS transistor is (approximately) described by a square law. More or less analogous to the class of TL circuits, the square law is the basis of the class of 'Voltage-TransLinear'' (VTL) circuits.

Static voltage-translinear circuits Translinear networks consist of closed loops of base-emitter junctions. Likewise, VTL circuits are characterised by

<sup>&</sup>lt;sup>1</sup>Proportional-To-Absolute-Temperature

<sup>&</sup>lt;sup>2</sup>The term 'Voltage-Translinear' proposed in [63,64] is used throughout this thesis as it clearly distinguishes between TL principles based on the exponential law and VTL principles based on the square law, as opposed to the term 'MOS Translinear' proposed in [67].

closed loops of gate-source voltages, and can be used to realise a variety of transfer functions based on the large-signal quadratic behaviour of the MOS transistor, see, e.g., [67–70]. Time-multiplexing techniques can be used to simulate VTL loops owing to the favourable properties of the MOS transistor to implement switches [71,72]. A formal description of the underlying fundamental design principle was described by Seevinck and Wiegerink in 1991 [67]. The structured analysis and synthesis of VTL circuits was treated in [70].

**Dynamic voltage-translinear circuits** The class of 'Dynamic Voltage-TransLinear Circuits' offers continuous-time *dynamic* transfer functions. These dynamic VTL circuits are based on a generalisation of the DTL principle to strong inversion MOS. This class of circuits was proposed independently by Mulder *et al.* [29] and Payne *et al.* [30] in 1996. Experimental results were published in [73].

### Background of the thesis

Since 1986, the Electronics Research Laboratory of the Delft University of Technology, Faculty of Information Technology and Systems, Department of Electrical Engineering, has had a project group for 'low-voltage low-power electronics'. As TL circuits and subthreshold MOS transistors are especially useful in this area of analogue electronics, a project was initiated to explore the use of subthreshold MOS transistors in TL circuits. In particular, the application of the back-gate was to lead to additional possibilities for low-voltage operation and to result in TL circuits with a higher functional density.

During the course of this project, DTL circuits became an active field of research, see Fig. 1.1, and investigations were extended in this direction. As a result, this thesis now deals with structured methodologies for the analysis and synthesis of both STL and DTL circuits.

Some of the work described in this thesis has been published in various papers, which are listed on page 283.

### Outline of the thesis

The TL and VTL principles are explained in Chapter 2 using a current-mode approach. Dynamic translinear and dynamic voltage-translinear filters are members of a more general class of 'externally-linear internally-non-linear' circuits, which is therefore discussed first.

Chapter 3 discusses the analysis of TL circuits. First, the analysis of STL circuits is reviewed. Based on this theory, two methods, called 'global analysis' and 'state-space analysis', are developed for the analysis of DTL circuits. Alternative analysis methods for DTL circuits proposed in the literature are

described as well. In addition, the characteristics of the three different classes of DTL circuits published to date are analysed.

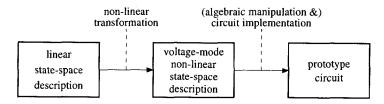

The reverse process of analysis is synthesis, which is treated in Chapter 4. Based on the synthesis theory of STL networks, a generalised design methodology is presented covering the synthesis of both STL and DTL circuits. A comparison is made with a number of alternative synthesis methods for TL filters described in the literature. Further, the concept of class-AB operation, which is closely related to synthesis, is treated.

The synthesis method described in Chapter 4 is based on ideal transistor behaviour. In Chapter 5, the deviations introduced by second-order effects are discussed. Methods to reduce or even eliminate the influences of these non-idealities are reviewed.

Noise is the topic of Chapter 6. The signal-to-noise-ratio and dynamic range properties of TL circuits are discussed and methods for the analysis of noise in both STL and DTL circuits are proposed. These methods incorporate the non-linear and non-stationary aspects of noise in TL circuits.

Chapter 7 is devoted to VTL circuits. Arguments are given to show that VTL circuits do not have much practical value.

Several realisations of TL and VTL circuits are presented in Chapter 8. Finally, Chapter 9 concludes the thesis.

### Design principles

The continuing trend towards lower supply voltages has increased interest in the application of companding¹ techniques [2,8,29,31,74–78]. This chapter discusses the design principles that are fundamental to the realisation of companding signal processors. In Section 2.1, an abstract approach is pursued to describe the general principle of distortionless companding. At a less abstract level, Sections 2.2 and 2.3 are geared toward the inherent companding characteristics of TransLinear (TL) and Voltage-TransLinear (VTL) circuits, respectively.

### 2.1 A general approach to companding

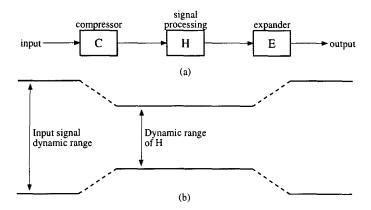

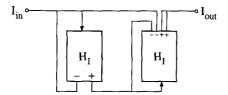

In a system employing companding, the Dynamic Range<sup>2</sup> (DR) of the signal being processed is different at various points along the signal path. The DR is altered by compression and expansion stages. The traditional set-up of a companding system is shown in Fig. 2.1(a). The input signal is first compressed, in block  $\mathcal{C}$ , before it is applied to  $\mathcal{H}$ , where the actual signal processing is performed. At the output of  $\mathcal{H}$ , the DR of the original input signal is restored through an expansion in block  $\mathcal{E}$ .

The benefit of companding is that a signal with a certain DR can be processed in a system block with a smaller DR than the signal [74]. This is illustrated in Fig. 2.1(b). The DR of a signal processing block  $\mathcal{H}$  is limited on two sides. At the upper level, the maximum amplitude of the input signal is limited by the generation of distortion for too large signals. At the lower level, the noise floor of the block determines the smallest signals that can be processed. Since the DR is limited on two sides, the influence of companding on the signal being

<sup>&</sup>lt;sup>1</sup> Companding is a combination of compressing and expanding.

<sup>&</sup>lt;sup>2</sup>The exact definitions of the dynamic range and the signal-to-noise ratio used throughout this thesis are formulated in Section 6.1.

Figure 2.1: (a) Traditional set-up of a companding system. (b) The dynamic range of the signal along the signal path.

processed can be explained from two points of view. At the upper level, large input signals are attenuated by the compressor  $\mathcal C$  down to a level where they can be processed by  $\mathcal H$  without causing excessive distortion. At the lower level, small input signals are amplified by  $\mathcal C$  to a level well above the noise floor of  $\mathcal H$ , making the signal less susceptible to noise and interference.

### Syllabic and instantaneous companding

Companding systems can be divided into two major classes: syllabic and instantaneous. These two classes differ with respect to the nature of the compression and expansion functions.

In a syllabic companding system, the transfer function of  $\mathcal{C}$  is determined by a compression signal, which is a function of some measure of the average strength of the signal being processed. The compression signal can be derived from the processed signal at any stage of the signal path, e.g., from the input or output, or even from a companion system with scaled signals [75]. A simple example of a compression signal is the envelope of the input signal, which can be generated through rectification followed by low-pass filtering.

In an instantaneous companding system, the output of  $\mathcal C$  is a function of the instantaneous value of the input signal. In other words, the transfer function of the compressor is static and non-linear. An example is the logarithmic I-V conversion performed at the input of a TL filter.

### Distortion

Companding methods cannot be applied without due caution. In the compressor, the DR of the input signal is decreased. This is a non-linear function and as a result harmonics of the input signal are generated. Nevertheless, the linearity of the overall transfer function of the complete signal path, shown in Fig. 2.1, can still be retained. A linear overall transfer function is obtained if the transfer function of  $\mathcal H$  is linear and frequency-independent, and the compression and expansion functions are inverse functions, i.e.,  $\mathcal C \circ \mathcal E = 1$ .

In practice, not only the DR, but also the bandwidth of  $\mathcal{H}$  will be limited, resulting in a frequency-dependent transfer function. This limited bandwidth can be unwanted when it is caused by parasitic reactive elements. It can also be intentional, e.g. when the function of the complete system is to filter the input signal in the frequency domain. The frequency-dependent transfer function of  $\mathcal{H}$  does not comply with the redistribution of the input signal information across the frequency spectrum by  $\mathcal{C}$ . As a result, distortion arises, even when  $\mathcal{C} \circ \mathcal{E} = 1$ .

The generation of distortion can also be explained with respect to the memory elements present in  $\mathcal{H}$  [76,79]. In the memory elements, the history of the signal is stored. The state of  $\mathcal{H}$  not only depends on the course of the processed signal, but also on the value of the (small-signal) gain of the compressor. If the compression gain changes in time, which is the case in a companding system, the coherence between the state of  $\mathcal{H}$  and the history of the processed signal is lost.

### Updating the state variables

To prevent the generation of distortion, the one-to-one relation between the state of  $\mathcal{H}$  and the processed signal has to be re-established. This is realised by updating the state variables in  $\mathcal{H}$  as a function of the time-variant compression gain [76, 79]. This applies both to syllabic and instantaneous companding systems.

The theory on distortionless syllabic companding is closely related to early work in control system theory (see [31] for an overview). The application of this theory at circuit level was first proposed by Blumenkrantz in 1994 in [76, 79], where the idea of updating the state variables, the 'Analog Floating Point Technique', is described. Implicitly, distortionless instantaneous companding at circuit level was described earlier, by Adams in 1979 in [1], where log-domain filters are introduced.

In [75], a general model for distortionless companding systems is described by Tsividis. The model incorporates both syllabic and instantaneous companding, showing that both types of distortionless companding are in fact based on the same mechanism of updating the state variables.

In the following, a general model of distortionless companding systems is described. The approach will be somewhat different from the one presented in [75].

### A first-order model

For a signal processor having a frequency-dependent transfer function, two basic functions are required to describe the process of distortionless companding. First, a dynamic transfer function is required because the distortion is caused by the frequency-dependent transfer function of  $\mathcal{H}$ . To gain insight, it is convenient to consider a first-order dynamic system. Further on, the results are generalised to higher-order dynamic systems. A first-order dynamic transfer function can be modelled by a single linear integrator. The input and output signals of this internal integrator are denoted by  $\dot{x}$  and x, respectively, where the dot represents differentiation with respect to time.

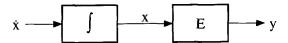

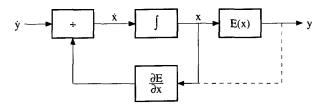

Secondly, compression and expansion functions are required. It is sufficient to model only the expansion function E, since the accompanying compression function can be derived from E. The input signal of E is the output signal x of the integrator. The output signal of E is denoted by y. The basic model thus obtained is shown in Fig. 2.2.

Figure 2.2: The two basic functions of a companding integrator.

The expansion function E is directly related to the type of companding. Therefore, in order to obtain a general model, both instantaneous and syllabic expansion functions have to be accommodated.

In an instantaneous companding system, the output signal y is a function of the instantaneous value of the integrator output x. Since all signals are implicitly a function of time t, the output y can be described as: y(t) = E(x(t)). For example, in a log-domain filter, the expansion function is given by  $y(t) = \exp x(t)$ .

In a syllabic companding system, the expansion function is controlled by one or more time-variant signals  $g_i(x(t),t)$ , where  $i \in [1,\ldots,N]$ , which can be represented by the column vector  $\vec{g}$ . Thus,  $\vec{g}(x(t),t)$  is a vector function. For example, in a traditional set-up, the expansion block is a variable gain amplifier, controlled by a single time-variant expansion factor g(x(t),t), i.e.,  $y(t) = g(x(t),t) \cdot x(t)$ .

<sup>&</sup>lt;sup>3</sup>In principle, other first-order dynamic transfer functions, such as a differentiator, can be used here just as well. The choice of an integrator complies with the general application of the integrator as the basic building block for filters [80,81].

The general model for the transfer function E of the expander  $\mathcal{E}$ , including both instantaneous and syllabic companding, is given by:

$$y(t) = E(x(t), \vec{g}(x(t), t)).$$

(2.1)

In principle, E = E(x(t), t) is an equally valid representation. However, eqn (2.1) clearly distinguishes between the two different types of companding.

The possible choices of E are restricted by the fact that, at all times, i.e., for all possible values of the signals  $g_i$ , E has to be a strictly monotonous function with respect to x. Otherwise, when different values of x are projected onto the same value of y, information is lost, resulting in irrecoverable distortion. As a consequence, at all times the function E has an inverse function  $E^{-1}$  given by:

$$x(t) = E^{-1}(y(t), \vec{g}(x(t), t)). \tag{2.2}$$

### The correct input signal

At the input of the internal integrator, shown in Fig. 2.2, the signal  $\dot{x}$  has to be supplied. The question is what this signal should look like in order to obtain a system with a linear transfer function from  $\dot{y}$  to y, the input and output signal, respectively, of the complete companding integrator. The correct signal  $\dot{x}$  can be calculated from the expansion function.

An expression for  $\dot{y}$  can be derived from eqn (2.1) by calculating the first derivative with respect to time. Since E is only implicitly a function of time, the chain rule has to be applied. This yields:

$$\dot{y} = \frac{\partial E}{\partial x}\dot{x} + \nabla_{\!g}E \cdot \left(\frac{\partial \vec{g}}{\partial x}\dot{x} + \dot{\vec{g}}\right),\tag{2.3}$$

where

$$\nabla_{g}E = \left(\frac{\partial E}{\partial g_{1}}, \dots, \frac{\partial E}{\partial g_{N}}\right).$$

From eqn (2.3), the signal  $\dot{x}$ , to be applied to the internal linear integrator, can be found:

$$\dot{x} = \frac{\dot{y} - \nabla_{g} E \cdot \dot{g}}{\frac{\partial E}{\partial x} + \nabla_{g} E \cdot \frac{\partial \vec{g}}{\partial x}}.$$

(2.4)

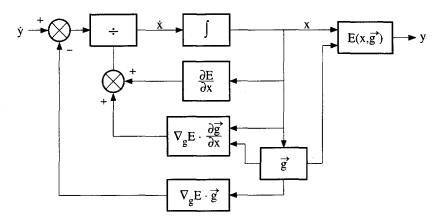

Figure 2.3 shows the system level implementation of this equation, resulting in a theoretically distortionless companding integrator.

Alternatively, applying the inverse function theorem,  $\dot{x}$  can be calculated from eqn (2.2). The first-order time derivative yields:

$$\dot{x} = \frac{\frac{\partial E^{-1}}{\partial y}\dot{y} + \nabla_{g}E^{-1} \cdot \dot{\vec{g}}}{1 - \nabla_{g}E^{-1} \cdot \frac{\partial \vec{g}}{\partial x}}.$$

(2.5)

Figure 2.3: Realisation of a theoretically distortionless companding integrator.

This equation results in a different system level implementation.

### An $n^{\text{th}}$ -order model

In general, the dynamic transfer function to which companding is applied is of order n. The dynamic behaviour of the internal signal processing block can now be represented by n integrators. The inputs and outputs of these internal integrators are described by the column vectors  $\vec{x}$  and  $\vec{x}$ , the elements of which are  $\dot{x}_j$  and  $x_j$ , respectively, where  $j \in [1, \ldots, n]$ . In principle, expansion can be applied to each of these integrators, resulting in n output signals  $y_j$ , represented by the vector  $\vec{y}$ . The expansion function does not have to be identical for each of the outputs  $x_j$ . In general, n different expansion functions  $E_j$ , represented by the vector function  $\vec{E}$ , can be defined. Each expansion function can depend on the complete state of the system, i.e., on all n state variables  $x_j$ . In general, the expansion vector  $\vec{E}$  can be described by:

$$\vec{y}(t) = \vec{E}(\vec{x}(t), \vec{g}(\vec{x}(t), t))$$

(2.6)

### The correct input vector

The input vector  $\vec{x}$ , to be supplied to the *n* internal integrators, in order to realise a system of *n* linear companding integrators, can be derived from eqn (2.6) by calculation of the first-order time derivative. This yields:

$$\dot{\vec{y}} = \mathbf{E}_x \dot{\vec{x}} + \mathbf{E}_g \left( \mathbf{G}_x \dot{\vec{x}} + \dot{\vec{g}} \right), \tag{2.7}$$

where  $E_x$ ,  $E_q$ , and  $G_x$  are Jacobian matrices given by:

$$\mathbf{E}_{x} = \begin{bmatrix} \frac{\partial E_{1}}{\partial x_{1}} & \cdots & \frac{\partial E_{1}}{\partial x_{n}} \\ \vdots & & \vdots \\ \frac{\partial E_{n}}{\partial x_{1}} & \cdots & \frac{\partial E_{n}}{\partial x_{n}} \end{bmatrix}, \quad \mathbf{E}_{g} = \begin{bmatrix} \frac{\partial E_{1}}{\partial g_{1}} & \cdots & \frac{\partial E_{1}}{\partial g_{N}} \\ \vdots & & \vdots \\ \frac{\partial E_{n}}{\partial g_{1}} & \cdots & \frac{\partial E_{n}}{\partial g_{N}} \end{bmatrix},$$

$$\mathbf{G}_{x} = \begin{bmatrix} \frac{\partial g_{1}}{\partial x_{1}} & \cdots & \frac{\partial g_{1}}{\partial x_{n}} \\ \vdots & & \vdots \\ \frac{\partial g_{N}}{\partial x_{1}} & \cdots & \frac{\partial g_{N}}{\partial x_{n}} \end{bmatrix}.$$

Expression (2.7) is a linear system in the n derivatives  $\dot{x}_j$ . The system can be solved for the vector  $\dot{\vec{x}}$ :

$$\dot{\vec{x}} = (\mathbf{E}_x + \mathbf{E}_g \mathbf{G}_x)^{-1} \left( \dot{\vec{y}} - \mathbf{E}_g \dot{\vec{g}} \right), \tag{2.8}$$

where  $^{(-1)}$  denotes the inverse matrix operation.

### Examples

The practical applicability of the distortionless companding principle cannot be derived from the general and abstract approach used above. The specific choice of the expansion function(s) and of the dimensions of the signals being processed will strongly influence to what extent a companding system is suitable for on-chip implementation. To conclude this section, some practical examples of distortionless companding systems are mentioned.

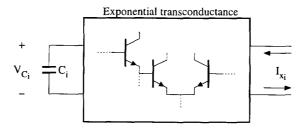

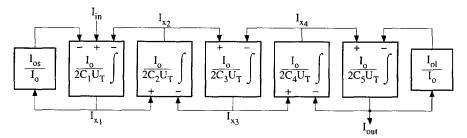

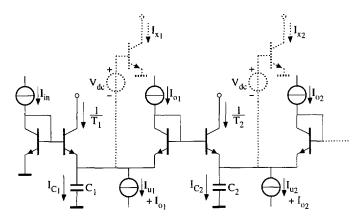

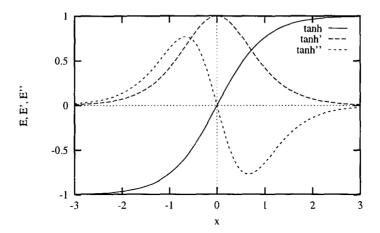

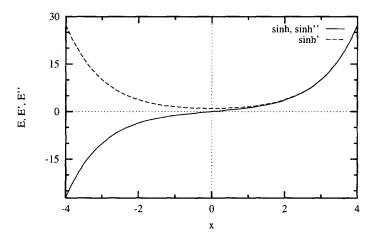

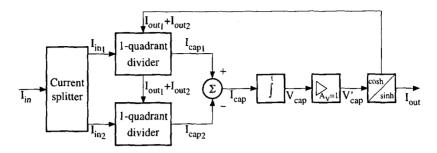

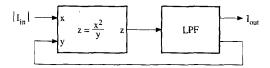

**Dynamic translinear circuits** Translinear filters, or Dynamic TransLinear (DTL) circuits in general, form a good example of instantaneous companding. In DTL circuits, the internal integrator, shown in Fig. 2.2, is a linear capacitor. The output of this integrator is expanded by exploiting the large-signal exponential transfer function of the bipolar transistor or the MOS transistor in the weak inversion region. The expansion function is different for the various classes of DTL circuits. For example, it is given by  $y(t) = \exp x(t)$  [1],  $y(t) = \tanh x(t)$  and  $y(t) = \sinh x(t)$  [10] for log-domain, tanh and sinh filters, respectively. The principle behind DTL circuits is treated in more detail in Section 2.2.2.

Dynamic voltage-translinear circuits Another example is given by the class of Dynamic Voltage-TransLinear (DVTL) circuits, which are also instantaneous companding. In DVTL circuits, again, the internal integrator is a linear capacitor. The output of this integrator is expanded by exploiting the large-signal quadratic behaviour of the MOS transistor in the strong inversion region. For a common-source output stage, the expansion function is given by

$y(t) = [x(t) - a]^2$  [29], where a is a constant. The principle behind DVTL circuits is treated in more detail in Section 2.3.2.

Syllabic companding Examples of syllabic companding systems are described in [75, 76, 79, 82], where the expansion function is given by y(t) = g(t)x(t). The systems differ mainly in the way the signal g(t) is generated. In [76, 79], where syllabic companding is applied to a  $\Sigma\Delta$  analogue-to-digital converter and an operational-transconductance-amplifier-based filter, g(t) is switched between different ranges. Within each range, g(t) is constant. At the switching instants, the state variables are updated by a compensation term, which has the shape of an impulse function. This impulse function can be implemented by a switched capacitor. A syllabic companding filter with a continuously varying compression factor g(t) is described in [75,82].

Instantaneous and syllabic companding Combinations of instantaneous and syllabic companding within one circuit are also possible [78, 83, 84]. An example is the syllabic companding TL filter described in Section A.1. Since TL filters are inherently instantaneous companding, the two types of companding are co-existent in a syllabic companding TL filter. Hence, the expansion function is given by  $y(t) = g(t) \exp x(t)$ .

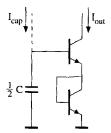

Non-linear capacitor The last case described here considers a non-linear capacitor. Virtually, in a non-linear capacitor, the two functions of integration and expansion, shown in Fig. 2.2, are performed in one device. The relation between the input current  $I_{\rm cap}$  and the charge Q on the capacitor is linear and is given by  $I_{\rm cap} = \dot{Q}$ . This equation describes a linear integration. The non-linear behaviour of a non-linear capacitor only applies to the relation between Q and the voltage  $V_{\rm cap}$  across the capacitor. Consequently, the transfer function of a non-linear capacitor can be split into two functions: a linear integrator followed by a non-linear static transfer function, the differential capacitance  $C(V_{\rm cap}) = \partial Q/\partial V_{\rm cap}$ . This static function can be regarded as the expansion function shown in Fig. 2.2.

An interesting example of a non-linear capacitor is the base-emitter capacitance  $C_{\pi}$  of a bipolar transistor in the region where the base-charging capacitance is dominant [85]. In this region, the logarithmic non-linearity of the diffusion capacitance is cancelled by the exponential V-I transfer function of the bipolar transistor, resulting in a theoretically linear integrator.

# 2.2 Translinear principles based on the exponential law

Both Static TransLinear (STL) and DTL circuits exploit the exponential largesignal transfer function of the bipolar transistor or the MOS transistor in the weak inversion region. The term 'translinear' is derived from the equation for the small-signal transconductance  $g_m$  of a bipolar transistor, given by:

$$g_m = \frac{\partial I_{\rm C}}{\partial V_{\rm BE}} = \frac{I_{\rm C}}{U_T},\tag{2.9}$$

where  $I_{\rm C}$  is the collector current,  $V_{\rm BE}$  is the base-emitter voltage and  $U_T$  is the thermal voltage kT/q. Equation (2.9) shows that the *trans*conductance is *linear* in the collector current.

The conventional, i.e., static, TL principle [43] can be used to implement a wide variety of linear and non-linear static transfer functions [50]. The STL principle is reviewed in Section 2.2.1.

The DTL principle [22] can be used to implement both linear and non-linear, frequency-dependent functions, i.e., linear and non-linear Differential Equations (DEs). The DTL principle can be regarded as a generalisation of the STL principle. In a broader context, DTL circuits are based on the theory of distortionless companding described in Section 2.1. The dynamic element is the capacitance. The exponential function, or a composite exponential function, is employed as the expansion function, which expands a capacitance voltage into a transistor current. In Section 2.2.2, the DTL principle is described using a current-mode point of view.

### 2.2.1 Static translinear principle

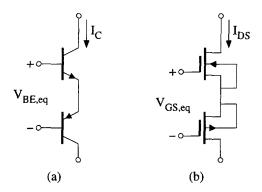

Although invented as early as 1968 [44,45], the (static) TL principle was first formulated by Gilbert in 1975 [43]. Translinear circuits are based on the exponential relation between voltage and current, characteristic for several semiconductor devices, such as the bipolar transistor, the diode and the MOS transistor in the weak inversion region.

In this section, the STL principle is explained using the expression for the collector current  $I_{\rm C}$  of the bipolar transistor. The important difference between bipolar transistors and MOS transistors in the weak inversion region is the slope of the exponential characteristic. The slope of the MOS transistor is characterised by the process-dependent parameter n [86], whereas the slope of the bipolar transistor is almost process-independent. With some minor modifications, the following theory is equally applicable to subthreshold MOS transistors.

The collector current of a bipolar transistor in the active region is given by:

$$I_{\rm C} = \lambda I_{\rm s} e^{\frac{V_{\rm BE}}{U_T}},\tag{2.10}$$

where  $\lambda$  is the emitter area scale factor and  $I_s$  is the saturation current of the unity transistor.

The STL principle applies to loops of semiconductor junctions with an exponential V-I relation. The slope of the exponential function has to be the same for all devices. A TL loop is characterised by an even number of junctions. The number of devices with a clockwise orientation equals the number of counter-clockwise oriented devices. Further, all devices have to operate at the same temperature.

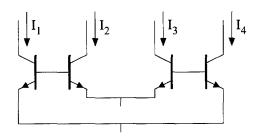

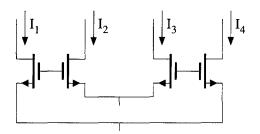

An example of a four-transistor TL loop is shown in Fig. 2.4. It is assumed that the transistors are somehow biased at the collector currents  $I_1$  through  $I_4$ . As the four transistors are connected in a loop, Kirchhoff's Voltage Law (KVL) can be used to describe the loop:

$$V_{\text{BE}_1} + V_{\text{BE}_3} = V_{\text{BE}_2} + V_{\text{BE}_4}. \tag{2.11}$$

Figure 2.4: A four-transistor translinear loop.

### Current-mode

Translinear circuits are typical examples of current-mode circuits [87]. That is, the behaviour of a TL circuit can be described best in terms of currents. The voltages are only of secondary interest. The voltage-mode description (2.11) can be transformed into a current-mode description using the exponential law (2.10) describing the bipolar transistor. This yields:

$$U_T \ln \frac{I_1}{\lambda_1 I_s} + U_T \ln \frac{I_3}{\lambda_3 I_s} = U_T \ln \frac{I_2}{\lambda_2 I_s} + U_T \ln \frac{I_4}{\lambda_4 I_s}, \tag{2.12}$$

where  $\lambda_i$  are the emitter area scale factors of the four transistors.

Since all transistors are supposed to operate at the same temperature, the slope of the exponential function, represented by  $U_T$ , is the same for all transistors. Therefore, the factor  $U_T$  can be eliminated from eqn (2.12). Further, the sum of two logarithmic functions equals the logarithm of the product of the

two arguments of these functions. Eqn (2.12) can thus be simplified to:

$$\ln \frac{I_1 I_3}{\lambda_1 \lambda_3 I_s^2} = \ln \frac{I_2 I_4}{\lambda_2 \lambda_4 I_s^2}.$$

(2.13)

The logarithm is easily eliminated from eqn (2.13).

The saturation current  $I_s$  is equal for all transistors, owing to the identical operating temperature.<sup>4</sup> The powers to which  $I_s$  is raised in the denominator at both sides of eqn (2.13) are equal to the numbers of devices in the TL loop connected clockwise and counter-clockwise, respectively. As these numbers are equal,  $I_s$  can be eliminated. This finally yields the familiar representation of TL loops in terms of products of collector currents:

$$I_1 I_3 = \lambda_{eq} I_2 I_4, \tag{2.14}$$

where  $\lambda_{eq} = \lambda_2 \lambda_4 / (\lambda_1 \lambda_3)$  is the equivalent area ratio of the TL loop.

### Application

Equation (2.14) shows that the STL principle can be used to implement the arithmetic operations of multiplication and division. The operations of addition and subtraction are easily implemented in the current-domain. Using the addition and subtraction operations, linear combinations of the input and output currents can be forced through the transistors comprising a TL loop. In combination with the multiplication and division operations supplied by the TL loop, a wide variety of polynomials  $\mathcal{P}_m$ , rational functions  $\mathcal{P}_m/\mathcal{P}_n$  and  $n^{\text{th}}$ -order root functions can be realised.

Some of the major advantages of TL circuits follow directly from eqn (2.14). During the derivation of the STL principle, all temperature-dependent and process-dependent constants, i.e.,  $U_T$  and  $I_s$ , are eliminated. As a consequence, the transfer function implemented by a STL circuit is theoretically temperature and process-independent. Further, a multiplication is implemented using a very simple circuit, the TL loop shown in Fig. 2.4. Thus, TL circuits are characterised by a very high functional density.

To conclude, the STL principle can be summarised in the following definition due to Gilbert [43]:

"A translinear circuit is one having inputs and outputs in the form of currents and whose primary functions arises from the exploitation of the proportionality of transconductance to current in certain electronic devices so as to result in fundamentally exact, temperature-insensitive algebraic transformations."

<sup>&</sup>lt;sup>4</sup>In principle, paired matching of the saturation currents is a sufficient condition.

### 2.2.2 Dynamic translinear principle

Though very versatile, the STL principle, derived in Section 2.2.1, is limited to frequency-independent transfer functions. By admitting capacitors in the TL loops, the TL principle can be generalised to include frequency-dependent transfer functions. To name the principle on which this new class of circuits is based, the term 'Dynamic Translinear Principle' was coined by Mulder *et al.* in [22]. This term was chosen to emphasise the TL nature of these circuits.

As a consequence of the exponential behaviour of the transistor, TL circuits are inherently instantaneous companding. The voltages in a TL circuit are logarithmically related to the currents. Due to this non-linear behaviour, adding a capacitor to a TL loop will in most cases result in severe distortion.

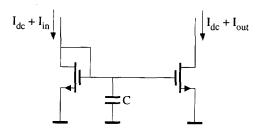

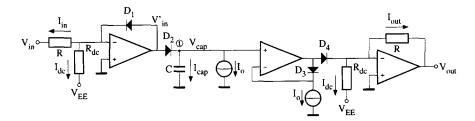

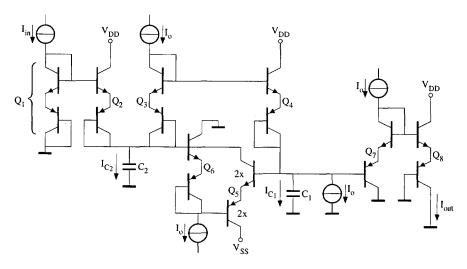

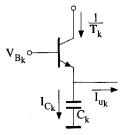

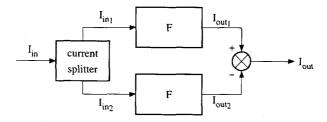

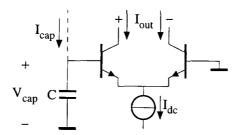

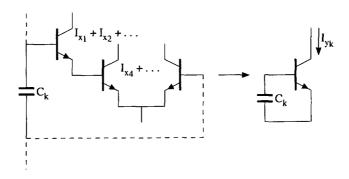

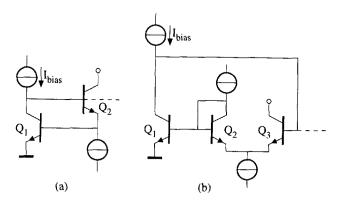

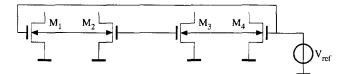

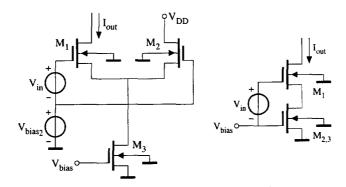

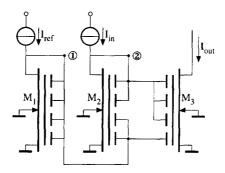

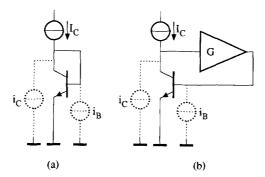

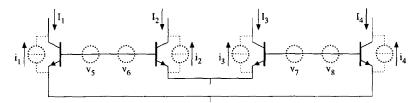

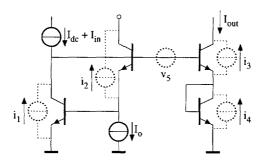

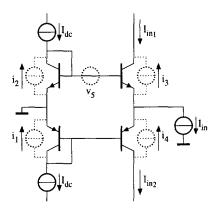

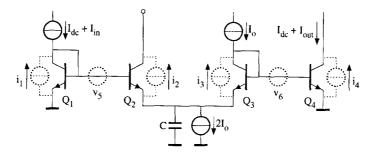

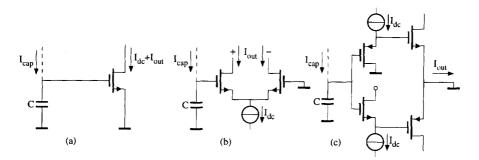

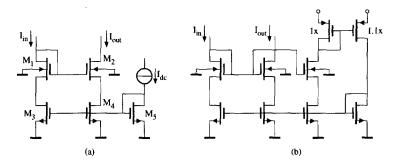

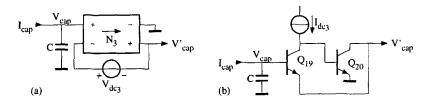

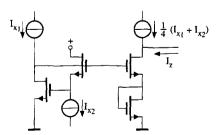

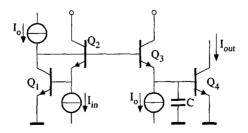

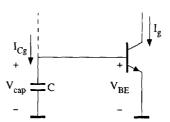

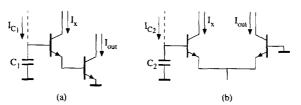

#### Current mirror

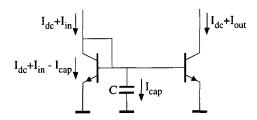

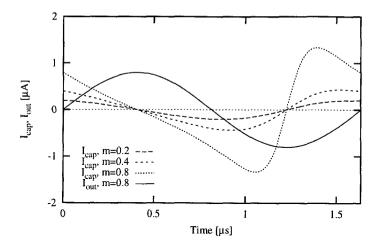

As an example, the generation of harmonic distortion is illustrated for the most simple TL circuit: the current mirror. Figure 2.5 shows a current mirror in which a capacitor C is connected in parallel with the diode-connected input transistor. The capacitor can be regarded as the internal integrator and the output transistor as the expander of a companding system, as shown in Fig. 2.2. The current mirror is biased in class A by a dc bias current  $I_{\rm dc}$ ; the ac input current  $I_{\rm in}$  is superposed on  $I_{\rm dc}$ .

Figure 2.5: A capacitor added to a current mirror.

For very small values of  $I_{\rm in}$ , the transconductance  $g_m$  of each of the two transistors comprising the current mirror is approximately constant. In that case, the transfer function from the capacitance voltage swing to the ac output current  $I_{\rm out}$  is linear. Consequently, the transfer function of the current mirror is described by a linear DE:

$$\frac{CU_T}{I_{dc}}\dot{I}_{out} + I_{out} = I_{in}.$$

(2.15)

The transfer function described by eqn (2.15) is that of a first-order low-pass filter.

For large input signal swings, the exponential expansion realised by the output transistor cannot be approximated by a linear transconductance. As a result, to accurately describe the transfer function of the current mirror, a non-linear DE is required. A general analysis method is presented in Chapter 3. For the circuit shown in Fig. 2.5 this results in:

$$CU_T \dot{I}_{\text{out}} + (I_{\text{dc}} + I_{\text{out}}) I_{\text{out}} = (I_{\text{dc}} + I_{\text{out}}) I_{\text{in}}.$$

(2.16)

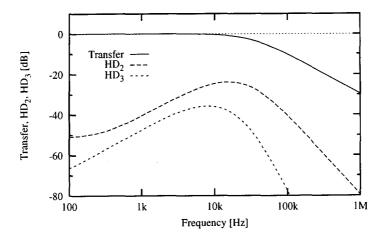

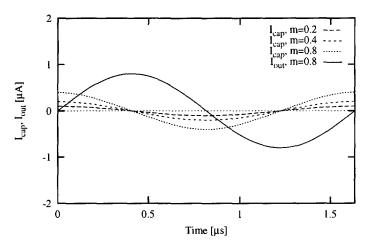

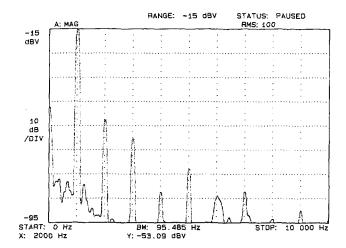

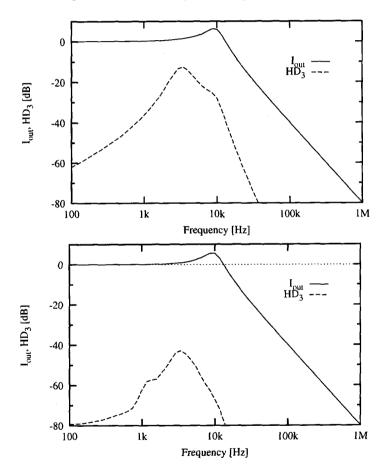

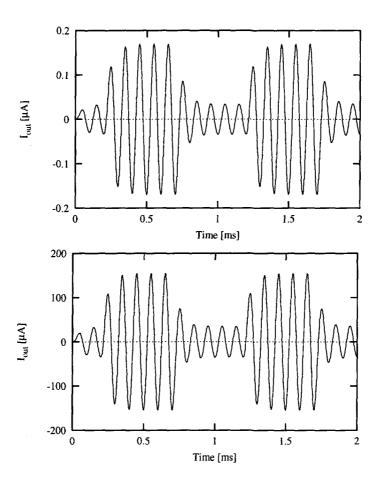

Figure 2.6 shows a large-signal ac simulation of the transfer function of the current mirror, and  $\mathrm{HD}_2$  and  $\mathrm{HD}_3$ , the second and third-order harmonic distortion components, respectively. The simulation is based on a harmonic balance method. In the simulation, the amplitude of  $I_{\mathrm{in}}$  is 90% of  $I_{\mathrm{dc}}$ ,  $I_{\mathrm{dc}}$  is 50  $\mu\mathrm{A}$  and C is 300 pF. Significant distortion is evident from the results shown.

Figure 2.6: Large-signal simulation of the transfer function, HD<sub>2</sub> and HD<sub>3</sub> of the current mirror shown in Fig. 2.5.

### Distortionless companding

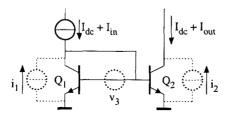

To prevent distortion in DTL circuits, the general principle described in Section 2.1 has to be obeyed. The DTL principle is a special case of this general principle, which applies to TL circuits. Instead of the abstract approach used in Section 2.1, a more practical approach is used here to derive the DTL principle. More specifically, a current-mode approach is used.

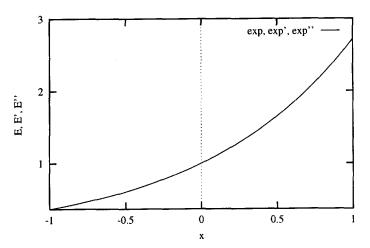

The exponential function has two very favourable characteristics. First, multiplication of two exponential functions  $e^a$  and  $e^b$  is equivalent to addition of the two arguments a and b, see eqn (1.1). This characteristic is exploited in

the STL principle. Second, the derivative of an exponential function equals the exponential function itself, see eqn (1.2). This characteristic is the basis of the DTL principle.

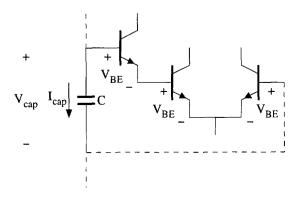

To calculate the derivative of eqn (2.10) for  $I_C$  with respect to time, the chain rule has to be applied, as  $V_{\rm BE}$  is a function of time. This results in:

$$\dot{I}_{\rm C} = I_{\rm C} \frac{\dot{V}_{\rm BE}}{U_T}.\tag{2.17}$$

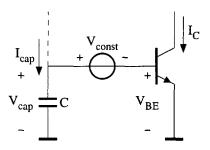

The derivative  $\dot{V}_{\rm BE}$  of the base-emitter voltage is very similar to the constitutive law describing a capacitance C. The relation between the capacitance current  $I_{\rm cap}$  and capacitance voltage  $V_{\rm cap}$  is given by:

$$I_{\rm cap} = C\dot{V}_{\rm cap}. \tag{2.18}$$

When  $\dot{V}_{\rm BE}$  in eqn (2.17) is multiplied by C, the product  $C\dot{V}_{\rm BE}$  can be regarded as the current through a capacitance C with a voltage  $V_{\rm BE}$  applied across it. This is illustrated in Fig. 2.7. Note that the dc voltage source  $V_{\rm const}$  does not influence the capacitance current. Thus, eqn (2.17) can be written as:

$$CU_T \dot{I}_{\rm C} = I_{\rm C} \cdot C\dot{V}_{\rm BE},\tag{2.19}$$

$$=I_{\rm C} \cdot I_{\rm cap}. \tag{2.20}$$

Note that the dimension of both sides of eqn (2.20) equals  $[A^2]$ .

Figure 2.7: Principle of dynamic translinear circuits.

Equation (2.20) directly states the DTL principle [22]: "A time derivative of a current is equivalent to a product of currents." At this point, the conventional STL principle comes into play. The product of currents on the Right-Hand Side (RHS) of eqn (2.20) can be realised very elegantly by means of this principle.

Equation (2.20) was derived for the structure shown in Fig. 2.7, which is typical for the class of log-domain filters. For these filters, the derivative is equivalent to the product of a capacitance current and one collector current. The principle is equally valid for other classes of TL filters, such as tanh and sinh filters. As shown in Section 3.3, these cases differ with respect to the currents comprising the product at the RHS of eqn (2.20).

### Application

The DTL principle can be used to implement DEs. A wide variety of signal processing functions is described by DEs. For example, filters are described by linear DEs. Examples of non-linear DEs for signal processing are harmonic and chaotic oscillators, PLLs and RMS-DC converters.

Addition, multiplication and linear derivatives are basic functions in DEs. The additions are easily implemented in the current domain. The multiplication operation can be implemented using the STL principle. To implement the derivatives, the DTL principle can be applied. A derivative is replaced by a product of currents, which is implemented by means of the STL principle.

Equation (2.20) reveals yet another characteristic of DTL circuits. In general, TL loops can be described by current-mode polynomials [50]. As shown in detail in Chapter 3, the relation between these current-mode polynomials and the DEs describing the transfer functions of DTL circuits is given by equations like (2.20). If the RHS of eqn (2.20) is implemented by (part of) a TL loop then the Left-Hand Side (LHS) is (part of) the DE describing the dynamic transfer function realised, which implies that the term  $CU_T$  is part of the DE. As a consequence, the transfer function becomes temperature-dependent through  $U_T$ . Fortunately, this temperature-dependence can be cancelled by making (some of) the currents in the DTL circuit PTAT<sup>5</sup> [1, 2].

#### Inductance

For theoretical completeness, it is interesting to investigate the possible application of an inductance instead of a capacitance as the dynamic element in a TL circuit. When an inductance L is used, eqn (2.17) has to be compared to the constitutive law of inductance given by:

$$U_L = L \,\dot{I}_L,\tag{2.21}$$

where  $U_L$  and  $I_L$  are the inductance voltage and current, respectively.

In this case, the derivative  $I_C$  of the collector current can be identified with the derivative  $I_L$  of the current through the inductance. Applying this identification to eqn (2.17) yields:

$$\frac{L}{U_T}\dot{V}_{\rm BE} = \frac{U_L}{I_{\rm C}}.\tag{2.22}$$

This equation states that the derivative of a voltage is equivalent to the division of a voltage by a collector current. As the RHS of this equation is not current-mode, it cannot be implemented by TL circuitry. The only solution is to convert  $U_L$  into a current using a transconductance. However, in that case,

<sup>&</sup>lt;sup>5</sup>Proportional-To-Absolute-Temperature

the inductance and the transconductance operate in the 'linear domain', not in the 'translinear domain'.

# 2.3 Voltage-translinear principles based on the square law

In the strong inversion region, the MOS transistor can be modelled by a square law. The validity of the square law model is not as good as the exponential law for the bipolar transistor. Especially not in modern sub-micron IC processes, where velocity saturation dominates almost the entire strong inversion region. This issue is treated in more detail in Section 7.1.

In IC processes where the square law is still valid, the MOS transistor can be used to implement a second type of TL circuits. In [64], the term 'Voltage-Translinear' was proposed. This term is derived from the equation for the small-signal transconductance  $g_m$  of the MOS transistor in the strong inversion region, given by:

$$g_m = \frac{\partial I_{\rm DS}}{\partial V_{\rm GS}} = \beta \left( V_{\rm GS} - V_{\rm th} \right), \tag{2.23}$$

where  $I_{\rm DS}$  is the drain-source current,  $V_{\rm GS}$  is the gate-source voltage,  $\beta$  is the transconductance factor and  $V_{\rm th}$  is the threshold voltage. Equation (2.23) shows that the transconductance is linear with the gate-source excess voltage.

Voltage-translinear circuits can be regarded as another special case of the general theory on distortionless companding treated in Section 2.1. In DVTL circuits, the dynamic element is the capacitor. The square law of the MOS transistor is applied as the expansion function. The DVTL principle can also be regarded as a generalisation of the conventional Static Voltage-TransLinear (SVTL) principle. Therefore, the SVTL principle is first reviewed in Section 2.3.1. The DVTL principle is derived in Section 2.3.2.

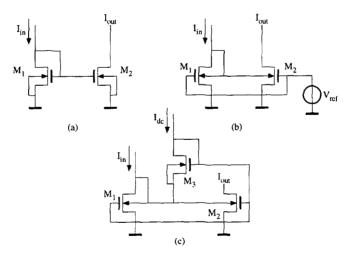

### 2.3.1 Static voltage-translinear principle

The VTL principle was first formulated by Seevinck and Wiegerink in 1991 [67]. Circuits based on this principle were however reported earlier. A linear transconductance is reported by Nedungadi in [68], published in 1984, which is based on a loop of four MOS transistors operating in the strong inversion region. The input of this transconductance circuit is a voltage and not a current. However, whereas current-mode input and output signals are fundamental in TL circuits based on the exponential function, voltage-mode input and output signals are allowed in VTL circuits. This is due to a fundamental difference between the exponential function and the quadratic function. The exponential

function is transcendental, whereas the quadratic function is a polynomial. As a consequence, it is impossible to obtain a linear relation between voltage and current using only exponential devices. For quadratic devices such a linear relation can be realised.

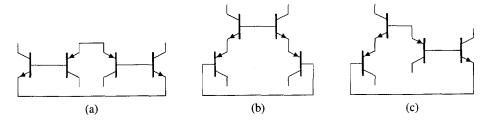

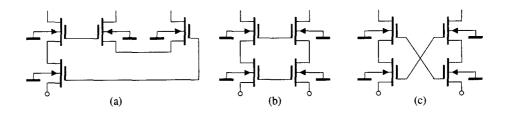

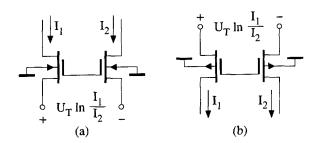

In general, the SVTL principle applies to loops of MOS transistors operated in the strong inversion region. A VTL loop is characterised by an even number of devices. The numbers of transistors connected clockwise and counter-clockwise are equal. Further, the transistors have to operate at the same temperature. Figure 2.8 shows an example of a four-transistor VTL loop. The transistors are assumed to be biased by currents  $I_1$  through  $I_4$ .

Figure 2.8: A four-transistor voltage-translinear loop.

The circuit shown in Fig. 2.8 can be described by the KVL as the four gate-source voltages  $V_{\rm GS_1}$  through  $V_{\rm GS_4}$  are connected in a loop:

$$V_{\text{GS}_1} + V_{\text{GS}_3} = V_{\text{GS}_2} + V_{\text{GS}_4}. \tag{2.24}$$

The MOS transistors comprising the loop are characterised by a quadratic relation between the gate-source voltage  $V_{\rm GS}$  and the drain current  $I_{\rm DS}$ . The square law model is given by:

$$I_{\rm DS} = \frac{\beta}{2} \left( V_{\rm GS} - V_{\rm th} \right)^2.$$

(2.25)

The transconductance factor  $\beta$  is given by:

$$\beta = \beta_{\square} \frac{W}{L},$$

where  $\beta_{\square}$  is the unity transconductance factor and W/L is the aspect ratio.

#### Current-mode

A current mode description of the loop shown in Fig. 2.8 can be obtained by substitution of eqn (2.25) in (2.24). This yields:

$$V_{\rm th} + \sqrt{\frac{2I_1}{\beta_1}} + V_{\rm th} + \sqrt{\frac{2I_3}{\beta_3}} = V_{\rm th} + \sqrt{\frac{2I_2}{\beta_2}} + V_{\rm th} + \sqrt{\frac{2I_4}{\beta_4}}.$$

(2.26)

Since the numbers of devices connected clockwise and counter-clockwise are equal, the threshold voltage can be dropped from eqn (2.26). Further, the common term  $\beta_{\square}$  in the transconductance factors  $\beta_1$  through  $\beta_4$  can be eliminated. This leaves a current-mode expression describing the loop:

$$\sqrt{\frac{I_1}{W_1/L_1}} + \sqrt{\frac{I_3}{W_3/L_3}} = \sqrt{\frac{I_2}{W_2/L_2}} + \sqrt{\frac{I_4}{W_4/L_4}}.$$

(2.27)

Hence, VTL loops can be described by the sums of square-roots of the drain currents. The drain currents are weighted by the aspect ratios of the transistors.

Equation (2.27) demonstrates an interesting characteristic of SVTL circuits: the transfer function of an SVTL circuit is both temperature and process-independent.

### Application

In the current domain, additions and subtractions are easily realised. Using these operations, linear combinations of the input and output currents can be forced through the MOS transistors comprising the VTL loop. In combination with the non-linear operation described by the general VTL loop equation (2.27), various linear and non-linear static transfer functions can be implemented.

### 2.3.2 Dynamic voltage-translinear principle

The conventional SVTL principle, described in Section 2.3.1, can only be used to implement static transfer functions. By admitting capacitors in the VTL loops, dynamic transfer functions can be realised. The term 'Dynamic Voltage-Translinear' is proposed to describe this new class of circuits.

Due to the quadratic behaviour of the MOS transistor in the strong inversion region, the voltages in a VTL circuit are related to the drain currents through square-root functions. This implies that instantaneous companding is an inherent characteristic. As a consequence, in general, a capacitor cannot be added to a VTL circuit without causing distortion.

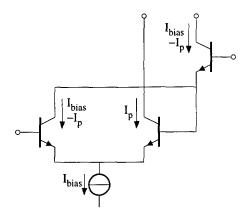

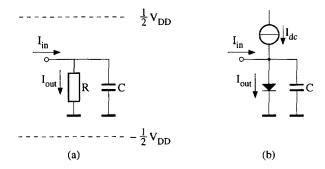

### Current mirror

The generation of distortion is illustrated with respect to the most simple VTL circuit. Figure 2.9 shows a current mirror where a capacitor C is added in parallel with the input transistor. The capacitor can be regarded as the internal integrator and the output transistor as the expander of a companding system, as shown in Fig. 2.2. The current mirror is biased in class A by a dc bias current  $I_{\rm dc}$ . The ac input current  $I_{\rm in}$  is superposed on  $I_{\rm dc}$ .

Figure 2.9: A capacitor added to a strong inversion MOS current mirror.

When the amplitude of  $I_{\rm in}$  is small with respect to  $I_{\rm dc}$ , the transconductance  $g_m$  of the output transistor is approximately constant. Therefore, the relation between the capacitor voltage and the output current  $I_{\rm out}$  is almost linear. The transfer function of the current mirror can be described by a linear DE:

$$\frac{C}{\sqrt{2\beta I_{\rm dc}}}\dot{I}_{\rm out} + I_{\rm out} = I_{\rm in}.$$

(2.28)

Equation (2.28) describes a first-order low-pass filter.

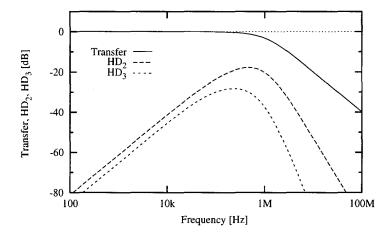

When the amplitude of  $I_{\rm in}$  is close to the value of the bias current  $I_{\rm dc}$ ,  $g_m$  cannot be approximated by a constant. Consequently, the transfer function of the current mirror has to be described by a non-linear DE:

$$\frac{C}{\sqrt{2\beta}}\dot{I}_{\text{out}} + \sqrt{I_{\text{dc}} + I_{\text{out}}}I_{\text{out}} = \sqrt{I_{\text{dc}} + I_{\text{out}}}I_{\text{in}}.$$

(2.29)

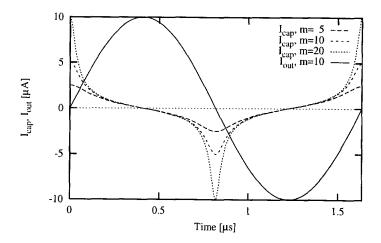

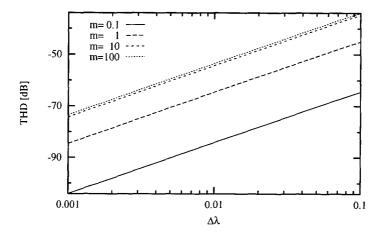

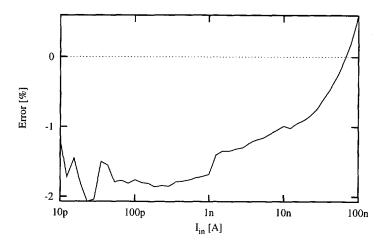

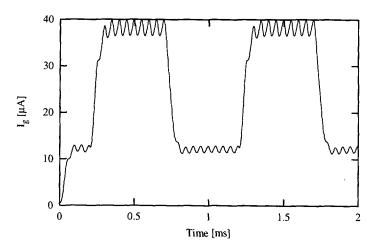

Figure 2.10 shows the result of a large-signal harmonic balance simulation of the current mirror using a realistic transistor model from a 2  $\mu$ m process. In the simulation, the amplitude of  $I_{\rm in}$  is 90% of  $I_{\rm dc}$ ,  $I_{\rm dc}$  is 50  $\mu$ A,  $V_{\rm th}=0.8$  V and  $\beta=50~\mu$ A/V². The plots of HD<sub>2</sub> and HD<sub>3</sub> show that the distortion is significant. In comparison with Fig. 2.6, the distortion generated in the bipolar transistor current mirror is much higher than for the MOS transistor current mirror. This is explained by the fact that the square function is far less non-linear than the exponential function.

Figure 2.10: Large-signal simulation of the transfer function, HD<sub>2</sub> and HD<sub>3</sub> of the current mirror shown in Fig. 2.9.

### Distortionless companding

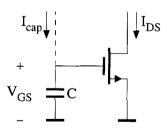

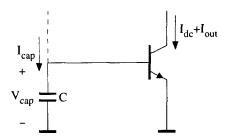

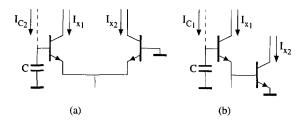

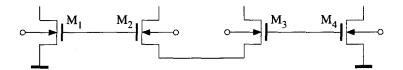

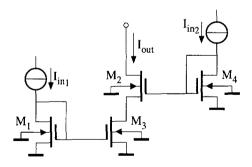

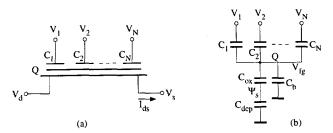

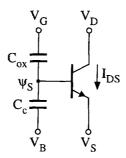

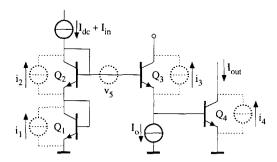

The generation of distortion can be prevented by applying the general principle described in Section 2.1. For strong inversion MOS transistors, this results in the DVTL principle, which is described here with reference to the circuit structure shown in Fig. 2.11. The MOS transistor shown in this figure is described by the square law, eqn (2.25). The derivative with respect to time of the drain current is given by:

$$\dot{I}_{DS} = \beta \left( V_{GS} - V_{th} \right) \dot{V}_{GS}. \tag{2.30}$$

The excess gate-source voltage  $(V_{\rm GS}-V_{\rm th})$  in this expression is quite inconvenient. It does not comply with the current-mode nature of VTL circuits. This factor can be replaced by a current-mode expression. Application of eqn (2.25) yields:

$$\dot{I}_{\rm DS} = \sqrt{2\beta I_{\rm DS}} \dot{V}_{\rm GS}. \tag{2.31}$$

In Fig. 2.11, the voltage  $V_{\rm GS}$  is applied across the capacitor C. Therefore, the constitutive law of the capacitance, eqn (2.18), describes the relation between the capacitance current  $I_{\rm cap}$  and the derivative  $\dot{V}_{\rm GS}$ . As a result,  $\dot{V}_{\rm GS}$  can be replaced by  $I_{\rm cap}$  and a completely current-mode expression for  $\dot{I}_{\rm DS}$  is obtained:

$$\frac{C}{\sqrt{2\beta}}\dot{I}_{\rm DS} = \sqrt{I_{\rm DS}}I_{\rm cap}.\tag{2.32}$$

Figure 2.11: Principle of dynamic voltage-translinear circuits.

Equation (2.32) directly states the DVTL principle: "A time derivative of a current is equivalent to a multiplication of a current and the square root of a current." The current-mode algebraic expression on the RHS of eqn (2.32) can be realised by applying the SVTL principle.

A linear derivative is a basic function of any DE. Consequently, the DVTL principle can be used to implement both linear and non-linear DEs.

Equation (2.32) reveals yet another important characteristic of DVTL circuits. Since the RHS of eqn (2.32) is implemented by (part of) a VTL loop, the LHS is (part of) the DE describing the dynamic transfer function of the loop. This implies that the factor  $C/\sqrt{2\beta}$  is part of the DE. Hence, the transfer function is process and temperature-dependent through  $\beta_{\Box}$ .

In the above, the VTL principle was derived for the one-transistor structure shown in Fig. 2.11. It is shown in Section 7.4 that the principle can easily be generalised to structures of two or more transistors, in analogy with the generic output structures of tanh and sinh TL filters.

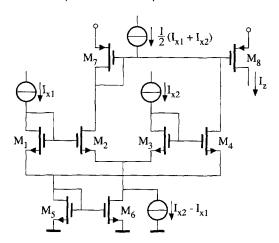

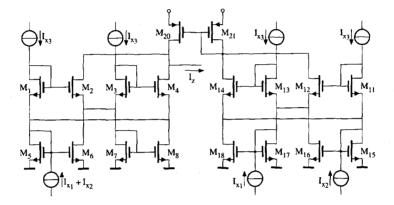

# Analysis of translinear circuits

Although synthesis is more powerful than analysis, it must go together with a generally applicable analysis method in the same domain. This is a prerequisite for structured electronic design. This chapter therefore explores the possible analysis procedures that can be applied to investigate the behaviour of Static TransLinear (STL) and Dynamic TransLinear (DTL) circuits, before synthesis methodologies are surveyed in Chapter 4.

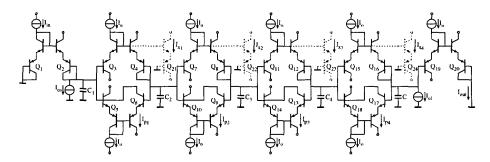

The analysis of STL circuits is reviewed in Section 3.1. The various methods for the analysis of DTL networks are treated next, in Section 3.2. Finally, Section 3.3 is devoted to the characteristics of the three different classes of TransLinear (TL) filters proposed in the literature, i.e., log-domain, tanh and sinh filters.

This chapter is concerned with the 'ideal' behaviour of TL circuits; ideal transistor models are assumed in all calculations. The analysis of second-order effects is deferred until Chapter 5. Throughout this chapter, the application of bipolar transistors is assumed. With some minor modifications, all theory presented is similarly applicable to TL circuits comprising alternative exponential devices.

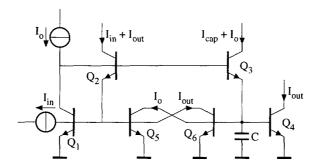

### 3.1 Analysis of static translinear circuits

Two types of equations are involved in the analysis of the ideal behaviour of STL circuits. First, the TL loop equations describe the multiplicative relation between the collector currents of the transistors comprising the loops. Secondly, the KCLs (Kirchhoff's Current Law) express the relation between the transistor

currents and the independent current sources applied to the circuit. Owing to the current-mode nature of both the TL loop equations and the KCLs, a relatively simple analysis method results.

In the analysis of STL circuits, three successive steps have to be performed:

- Determine the fundamental translinear loops;

- Calculate the collector currents;

- Solve the system of loop equations.

#### Determine the fundamental translinear loops

The STL principle, explained in Section 2.2.1, uniquely defines the characteristics of a TL loop. Based on this definition, the transistors comprising the TL loops can be separated from the transistors serving other purposes, such as buffering of base currents.

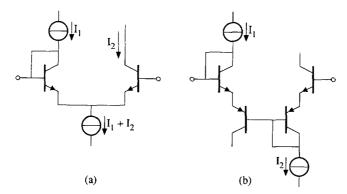

A TL circuit may consist of more than one TL loop. In general, TL circuits are characterised by a set of L fundamental loops [50]. These loops can be translated directly into a set of L TL loop equations, applying the well-known expression [43,50]:

$$\prod_{i} I_{C,Q_{2i}} = \lambda \prod_{i} I_{C,Q_{2i-1}},\tag{3.1}$$

where  $\lambda$  is the emitter area scale factor of the loop,  $I_{C,Q_i}$  represents the collector currents of the transistors comprising the loop, and the products on the Left-Hand Side (LHS) and Right-Hand Side (RHS) are over the clockwise and counter-clockwise connected transistors, respectively.

In this context, simple current mirrors are not accounted for in the set of L fundamental loops. This is due to the fact that the TL loop formed by a current mirror is trivial as it contains no multiplications of collector currents. In other words, a current mirror can only realise a linear transfer function.

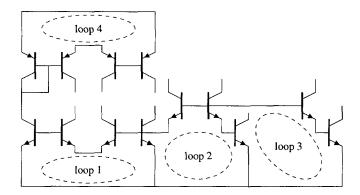

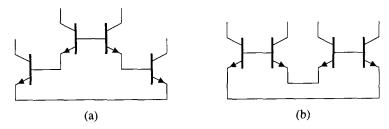

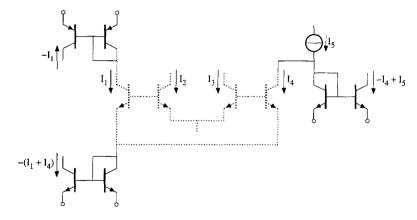

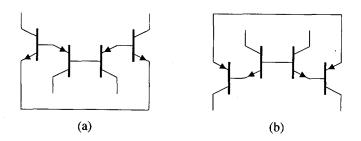

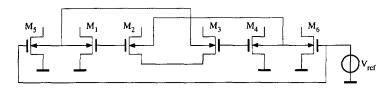

Different loops in a TL circuit can either be disjunct or coupled. Coupled loops can be coupled directly or indirectly. These three situations are illustrated in Fig. 3.1. Two TL loops are said to be *coupled directly* if they have one or more base-emitter junctions in common. Thus, the base-emitter junctions span a non-separable graph. Two loops are said to be *coupled indirectly* if they are part of the same non-separable graph, but have no base-emitter junctions in common. Two loops are called *disjunct* if they are part of two unconnected graphs.

If coupled loops exist in a circuit, more than L different TL loops can be identified. However, only L loops are fundamental. Note that the set of fundamental TL loops is not uniquely determined.

For the analysis of the circuit to succeed, it is important to find a complete set of fundamental TL loops, while excluding all loops that are not fundamental.

Figure 3.1: A circuit comprising four translinear loops. Loop 1 and 2 are coupled directly. Loop 1 and 3 are coupled indirectly. Loop 1 and 4 are disjunct.

For TL circuits where the base-emitter junctions span a non-separable planar graph, the number of fundamental loops is related to the number of base-emitter junctions B and the number of circuit nodes N by [50]:

$$L = B - N + 1. \tag{3.2}$$

In large circuits containing many coupled TL loops, eqn (3.2) can be used to confirm whether the complete set of fundamental loops has been found.

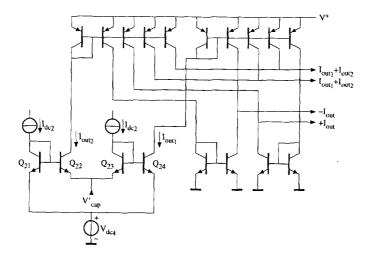

#### Calculate the collector currents

The TL loop equations (3.1), resulting from the first analysis step, describe the TL loops in terms of products of collector currents. The second analysis step comprises the calculation of the collector currents in terms of the input and output currents,<sup>1</sup> denoted both by  $I_j$ , where  $j \in \mathbb{N}$ . These calculations are based on the KCLs derived for each node of the circuit. Since the resulting system of KCL equations is linear, it is easy to solve, i.e., to obtain the collector currents in terms of the input and output currents. Often, the collector current expressions can even be obtained directly by inspection of the circuit schematic. In general, the collector currents are thus described by:

$$I_{\mathcal{C},Q_i} = \sum_j c_j I_j,\tag{3.3}$$

where  $c_i$  are constant coefficients.

An important distinction has to be made between single-loop and multiple-loop TL circuits. In a circuit comprising only one TL loop, all collector currents

<sup>&</sup>lt;sup>1</sup>For simplicity, dc bias sources are considered as being input currents.

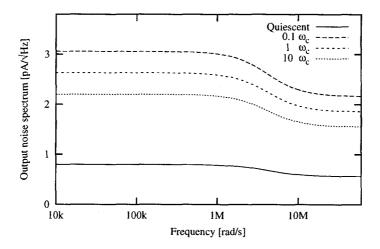

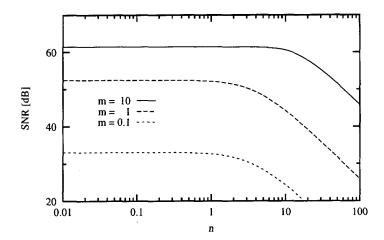

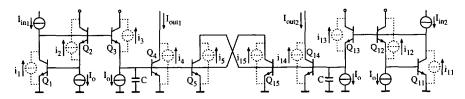

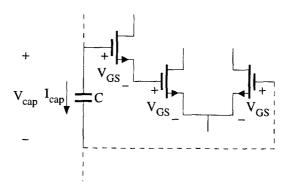

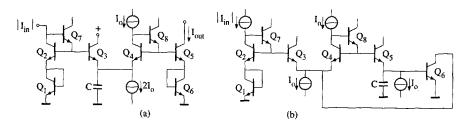

can be expressed as linear combinations of the input and output currents. In general, this is not true for multiple-loop circuits. If a multiple-loop circuit has Z linearly independent output currents, where  $Z \leq L$ , then a maximum of L-Z currents are possibly non-linearly related both to the input currents and to the Z output currents. Consequently, if Z < L, it is not possible, based on the KCLs only, to express all collector currents as linear combinations of the input and output currents.