## Investigation into the design domains' interdependencies of an inverter

case study of an aerospace inverter for extreme conditions

Nefeli Tsiara

# Investigation into the design domains' interdependencies of an inverter

case study of an aerospace inverter for extreme conditions

MASTER OF SCIENCE THESIS

For the degree of Master of Science in Electrical Power Engineering at Delft University of Technology

Nefeli Tsiara

February 15, 2016

Faculty of Electrical Engineering, Mathematics and Computer Science  $\cdot$  Delft University of Technology

The work in this thesis was supported by Aeronamic B.V.

Copyright  ${\mathbb C}$  Electrical Engineering. All rights reserved.

## DELFT UNIVERSITY OF TECHNOLOGY DEPARTMENT OF ELECTRICAL ENGINEERING

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled

Investigation into the design domains' interdependencies of an inverter

CASE STUDY OF AN AEROSPACE INVERTER FOR EXTREME CONDITIONS

by

#### Nefeli Tsiara

in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE ELECTRICAL POWER ENGINEERING

|                | Dated: February 15, 2016 |

|----------------|--------------------------|

| Supervisor(s): | Dr. Jelena Popovic       |

|                | Dr. Mark Gerber          |

| Reader(s):     | Dr. Henk Polinder        |

|                | Dr. Marjan Popov         |

### Abstract

The continuous development of power electronic converters has opened new opportunities for the More-Electrical Aircraft (MEA) concept, where the conventional power sources (pneumatic, hydraulic, mechanical) are replaced with electric sources to support secondary loads in the aircrafts. It is expected that more efficient, lighter and lower maintenance solutions can be obtained with high power density power electronics. In order to obtain optimal designs for power system integration, new methodologies employing multi-objective optimization have been reported. However, the application of multi-objective optimization is more powerful with multi-domain modeling, which is not always a straightforward task. The reason is that power electronics design is a complex design problem, mainly because of the multi-disciplinary nature of its physical aspects (domains), including electric circuit behavior, thermal performance, electromagnetic compatibility issues and packaging constraints. Therefore, a subsequent modeling effort for the power electronics design is necessary to fully exploit the advantages of optimization techniques. To obtain a comprehensive insight in the system behavior, the mutual dependencies of the power electronics' design domains need to be characterized and quantified. This thesis investigates into the interdependencies between the design domains of an inverter for aerospace applications.

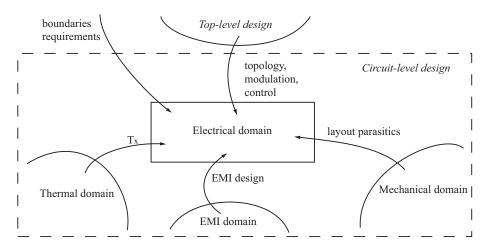

In this thesis project a design methodology is developed based on the multi-domain approach. The converter design is treated as a system in a top level design aspect, leading to the selection of a topology, modulation and control strategy. In addition, the circuit level design is effectively decoupled into the electrical, EMI, thermal and mechanical design domains, which are treated independently. The boundaries of the design levels and domains are determined and the links between the design domains are established though their mutual dependencies. Based on this methodology, a design framework for an aerospace inverter is realized in software using analytical modeling. This framework is used to investigate the mutual dependencies of the design domains and the impact of the design choices on the inverter performance. The interdependencies of the design domains are manipulated using design variables, similar to an optimization problem, by employing parametric sweep. A high efficiency and high power density aerospace inverter is designed, according to the specifications of Aeronamic B.V. and aerospace regulations.

Keywords: multi-domain modeling, aerospace, inverter, design domains, boundaries, interdependencies, power density

ii Abstract

## **Table of Contents**

|   | Abs  | stract                                                          | 1         |

|---|------|-----------------------------------------------------------------|-----------|

| 1 | Intr | roduction                                                       | 1         |

|   | 1-1  | Problem statement                                               | 1         |

|   | 1-2  | Thesis objective                                                | 2         |

|   | 1-3  | Thesis contribution                                             | 2         |

|   | 1-4  | Thesis outline                                                  | 3         |

| 2 | Pow  | ver electronics converter design – a systematic approach        | 5         |

|   | 2-1  | Introduction                                                    | 5         |

|   | 2-2  | Background and motivation                                       | 5         |

|   |      | 2-2-1 Virtual prototyping in power electronics                  | 6         |

|   |      | 2-2-2 The multi-domain modeling approach                        | 7         |

|   | 2-3  | Design methodology                                              | 12        |

|   |      | 2-3-1 Boundaries and requirements                               | 14        |

|   |      | 2-3-2 Top level design                                          | 15        |

|   |      | 2-3-3 Electrical domain                                         | 16        |

|   |      | 2-3-4 EMI domain                                                | 20        |

|   |      | 2-3-5 Mechanical domain                                         | 25        |

|   |      | 2-3-6 Thermal domain                                            | 27        |

|   |      | 2-3-7 Summarizing the interdependencies in the converter design | 31        |

|   | 2-4  | Summary                                                         | 33        |

| 3 | Aer  | rospace inverter - top level design                             | <b>35</b> |

|   | 3-1  | Introduction                                                    | 35        |

|   | 3-2  |                                                                 | 35        |

|   | 3-3  |                                                                 | 37        |

|   |      | 3-3-1 Classification of the available topologies                | 37        |

|   |      |                                                                 |           |

Table of Contents

|   |     | 3-3-2 The candidate topologies                          | 41       |

|---|-----|---------------------------------------------------------|----------|

|   |     | 3-3-3 Selection of the appropriate topology             | 43       |

|   | 3-4 | Modulation selection                                    | 47       |

|   |     | 3-4-1 Classification of the modulation strategies       | 47       |

|   |     | 3-4-2 Selection of modulation strategy                  | 48       |

|   | 3-5 | Control and system level operating point                | 48       |

|   |     | 3-5-1 Machine operation under drive limitations         | 48       |

|   |     | 3-5-2 Minimum current sizing                            | 51       |

|   |     | 3-5-3 Drive limitations of the designed system          | 55       |

|   |     | 3-5-4 Top-level design points of the inverter           | 57       |

|   | 3-6 | Summary                                                 | 57       |

| 4 | Aer | 1                                                       | 59       |

|   | 4-1 |                                                         | 59       |

|   | 4-2 |                                                         | 59<br>60 |

|   |     |                                                         | 60       |

|   |     |                                                         | 65       |

|   |     |                                                         | 67<br>72 |

|   | 4-3 | •                                                       | 73       |

|   | 4-3 |                                                         | 73       |

|   |     |                                                         | 77       |

|   | 4-4 |                                                         | 80       |

|   |     |                                                         | 81       |

|   |     |                                                         | 82       |

|   |     |                                                         | 86       |

|   | 4-5 |                                                         | 88       |

| 5 | Res | ults and discussion                                     | 89       |

|   | 5-1 | Aerospace inverter virtual prototype                    | 89       |

|   |     | 5-1-1 The design variables                              | 90       |

|   |     | 5-1-2 Other design considerations                       | 92       |

|   | 5-2 | Investigation of the domain interdependencies           | 93       |

|   |     | 5-2-1 Thermo - mechanical interdependencies             | 93       |

|   |     | 5-2-2 Electro - thermal interdependencies               | 93       |

|   |     | 5-2-3 Electrical - Package parasitics interdependencies | 95       |

|   |     | 5-2-4 EMI - Electrical interdependencies                | 97       |

|   |     | 5-2-5 EMI - Inverter parasitics interdependencies       | 99       |

|   |     | 5-2-6 EMI - Load parasitics interdependencies           | 99       |

|   | 5-3 | System performance                                      | 00       |

|   | 5-4 | Summary                                                 | 03       |

Table of Contents

| 6            | Conclusions and suggestions for future work  6-1 Conclusions | 105<br>105<br>107 |

|--------------|--------------------------------------------------------------|-------------------|

| $\mathbf{A}$ | Topology comparison analytical models                        | 109               |

| В            | Thermal models                                               | 113               |

| $\mathbf{C}$ | Component characteristics                                    | 121               |

|              | Bibliography                                                 | 123               |

vi Table of Contents

## List of Figures

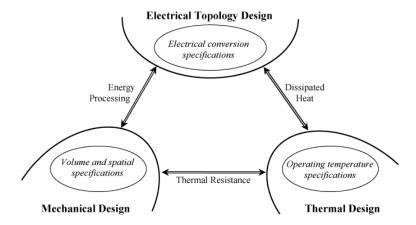

| 2-1  | Electrical, thermal and mechanical interconnections overview by [1]                                            | 7  |

|------|----------------------------------------------------------------------------------------------------------------|----|

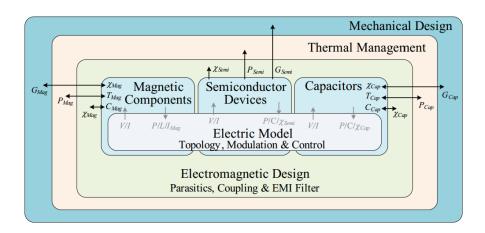

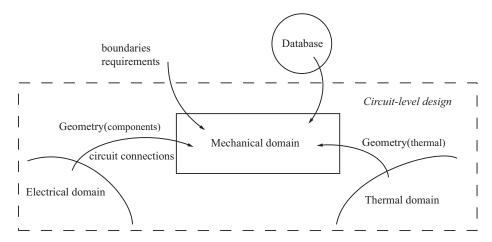

| 2-2  | Multi-domain interdependencies at circuit level design by [2]                                                  | 8  |

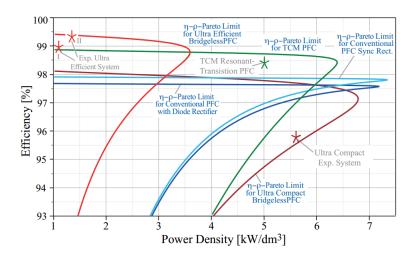

| 2-3  | PFC converters comparison using Pareto frontiers [3]                                                           | 9  |

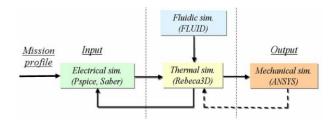

| 2-4  | The IGBT modules design approach using simulations by [4]                                                      | 9  |

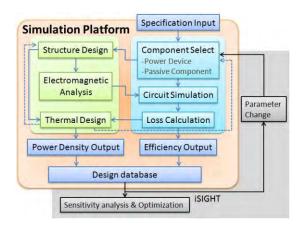

| 2-5  | Simulation based design process of a DC/DC converter by [5]                                                    | 10 |

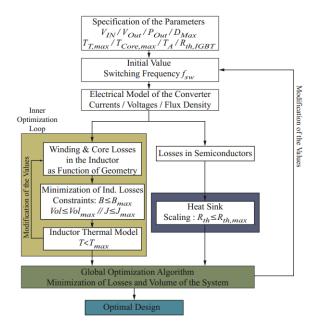

| 2-6  | Electo-thermal domain modeling and optimization process by [6]                                                 | 11 |

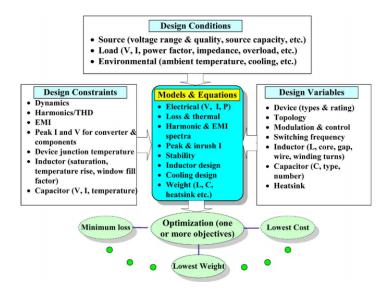

| 2-7  | Multi-domain design approach overview by [7]                                                                   | 11 |

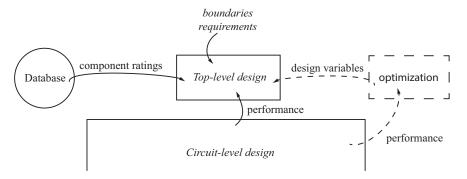

| 2-8  | Multi-domain design overview                                                                                   | 13 |

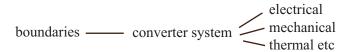

| 2-9  | Converter system boundaries                                                                                    | 14 |

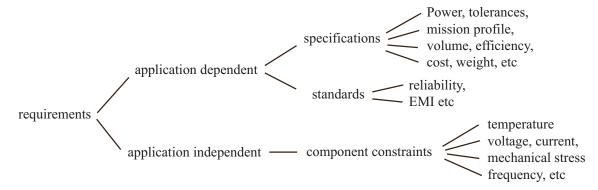

| 2-10 | $\label{lem:power_def} \mbox{Application dependent and independent requirements for power electronics design}$ | 15 |

| 2-11 | Top-level design dependencies                                                                                  | 16 |

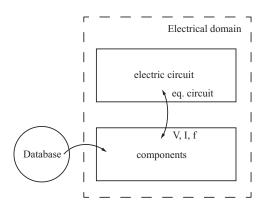

| 2-12 | Electric circuit and component design coupling in the $\it Electrical\ domain.$                                | 17 |

| 2-13 | Electrical domain dependencies                                                                                 | 18 |

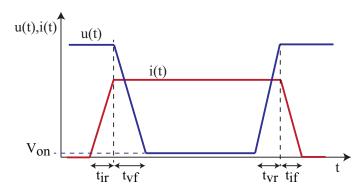

| 2-14 | Piecewise linear approximation of the semiconductor switching waveform for transients and losses calculation   | 19 |

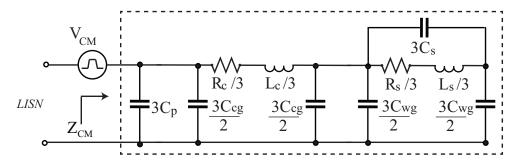

| 2-15 | Common mode and differential mode EMI noise paths                                                              | 21 |

| 2-16 | Switch parasitic capacitance to the ground                                                                     | 21 |

| 2-17 | Capacitor (top) and inductor (bottom) lumped high frequency equivalent circuit.                                | 22 |

| 2-18 | EMI domain dependencies                                                                                        | 22 |

| 2-19 | Conducted EMI standards [8]                                                                                    | 23 |

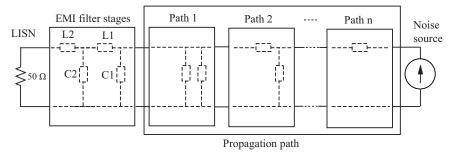

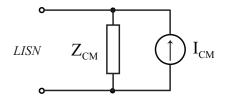

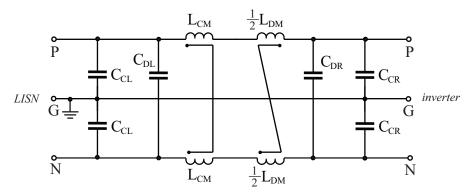

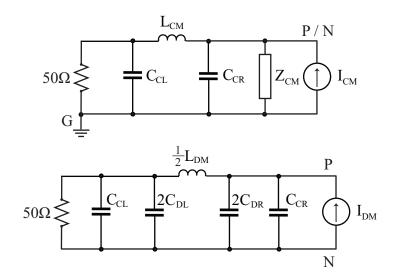

| 2-20 | The LISN connection circuit in a 2-phase system                                                                | 24 |

| 2-21 | Cascaded two-port network conficuration for the CM and DM filter design. $$ .                                  | 24 |

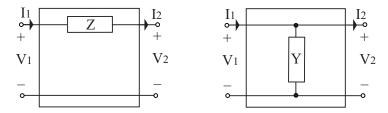

| 2-22 | Two-port networks for equivalent impedance (left) and admittance (right)                                       | 25 |

| 2-23 | Mechanical domain dependencies                                                                                 | 27 |

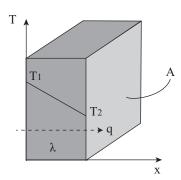

| 2-24 | Conduction heat transfer                                                                                       | 28 |

viii List of Figures

| 2-25 | Thin boundary layer in the convection heat transfer mechanism                                                                                                                                                 | 28 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2-26 | Dependencies of the Thermal domain                                                                                                                                                                            | 30 |

| 2-27 | Electric equivalent model of the convective heat transfer mechanism                                                                                                                                           | 30 |

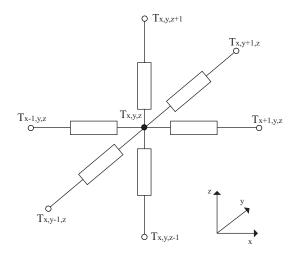

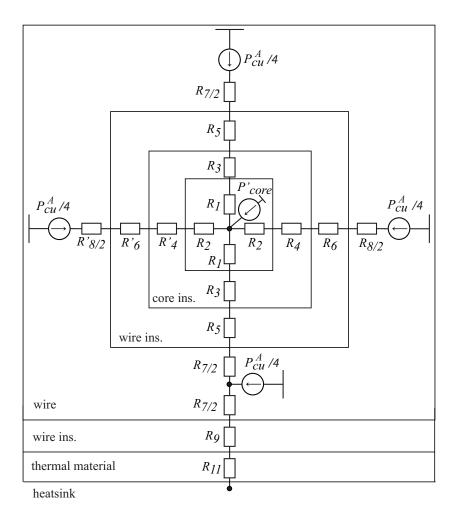

| 2-28 | 3D thermal resistor network                                                                                                                                                                                   | 31 |

| 2-29 | Converter design interdependences                                                                                                                                                                             | 32 |

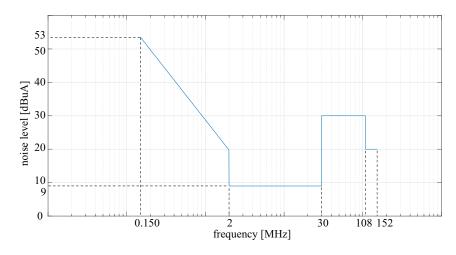

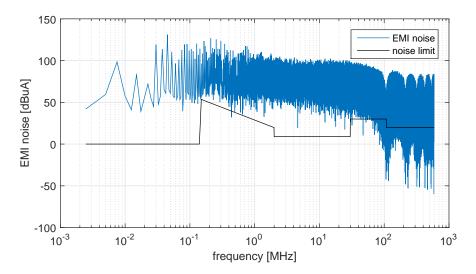

| 3-1  | The RTCA/DO-160 Category P standard for EMI noise in airborne equipment.                                                                                                                                      | 36 |

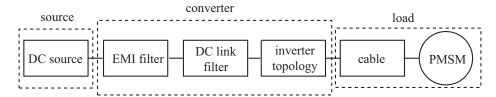

| 3-2  | Block diagram of the inverter system, including source and load connections.                                                                                                                                  | 37 |

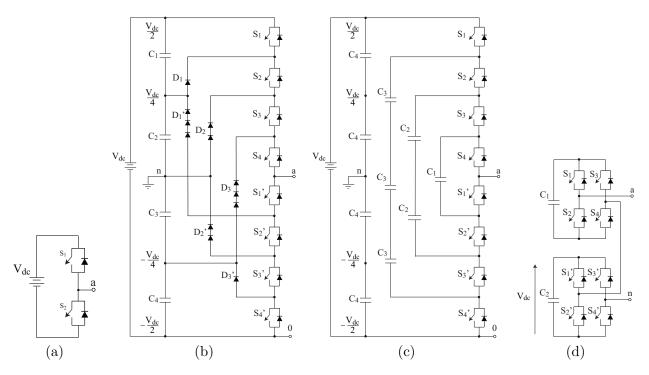

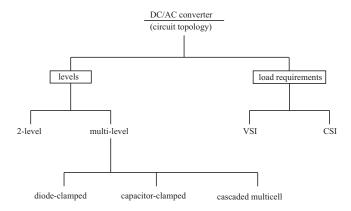

| 3-3  | Phase leg of the 2-level inverter (a) and the multi-level inverter topologies diode-clamped (b) capacitor-clamped and (c) cascaded multicell 5-level (d) inverters [9]                                        | 38 |

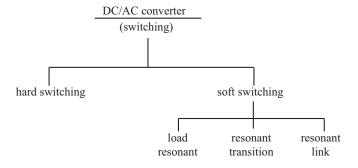

| 3-4  | Inverter topologies classification regarding the circuit topology                                                                                                                                             | 39 |

| 3-5  | Inverter topologies classification regarding switching                                                                                                                                                        | 39 |

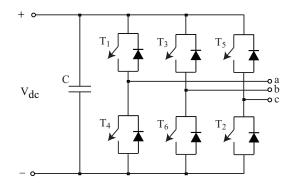

| 3-6  | Topology of the hard switching VSI inverter                                                                                                                                                                   | 41 |

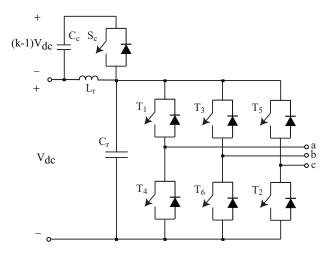

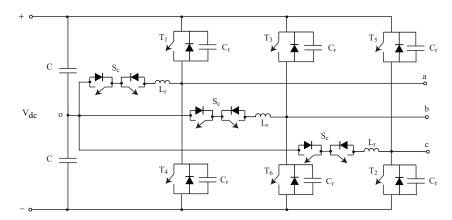

| 3-7  | Topology of the ACRDCL soft switching inverter                                                                                                                                                                | 42 |

| 3-8  | Topology of the CMPRI soft switching inverter                                                                                                                                                                 | 42 |

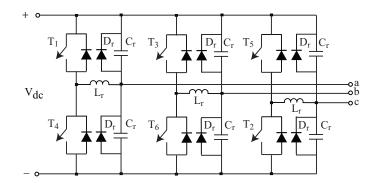

| 3-9  | Topology of the ASCRPI soft switching inverter                                                                                                                                                                | 43 |

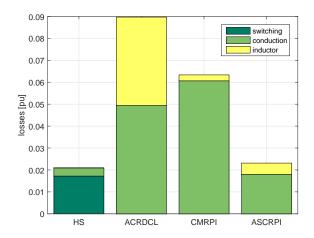

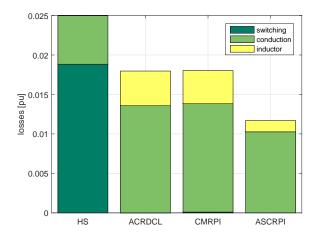

| 3-10 | Comparison of the topologies' losses at rated operating conditions (5 kW)                                                                                                                                     | 45 |

| 3-11 | Comparison of the topologies' losses at 50 kW output power                                                                                                                                                    | 45 |

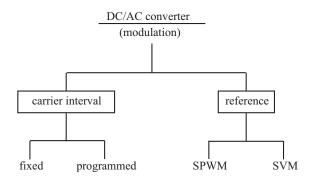

| 3-12 | Modulation schemes classification                                                                                                                                                                             | 48 |

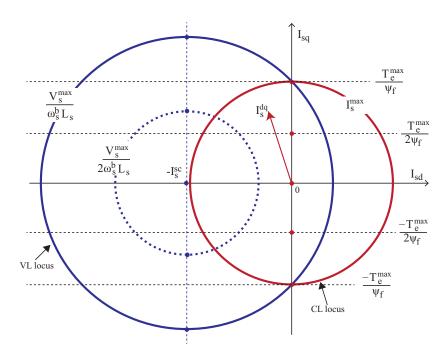

| 3-13 | Machine operation under drive limitations                                                                                                                                                                     | 50 |

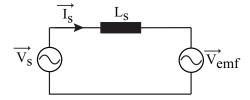

| 3-14 | System model at steady state operation                                                                                                                                                                        | 51 |

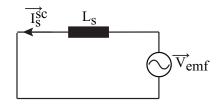

| 3-15 | System model equivalent at short-circuit conditions                                                                                                                                                           | 52 |

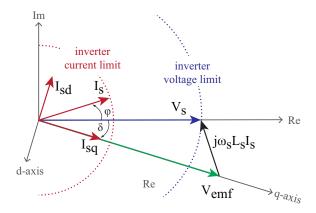

| 3-16 | Vectors diagram for the steady state model equivalent                                                                                                                                                         | 52 |

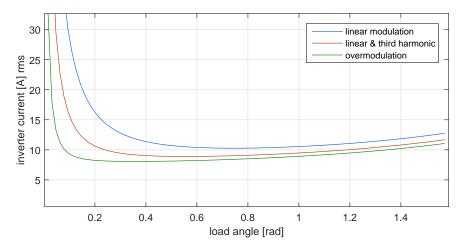

| 3-17 | Inverter current minimization for SPWM with linear modulation, third-harmonic injection and overmodulation                                                                                                    | 53 |

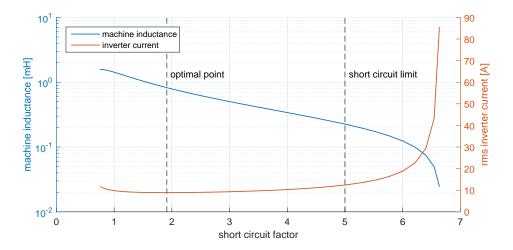

| 3-18 | Machine inductance design space for minimum current rating                                                                                                                                                    | 54 |

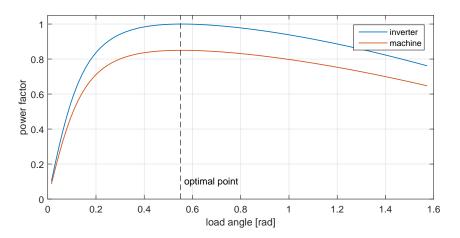

| 3-19 | Inverter and machine power factor                                                                                                                                                                             | 55 |

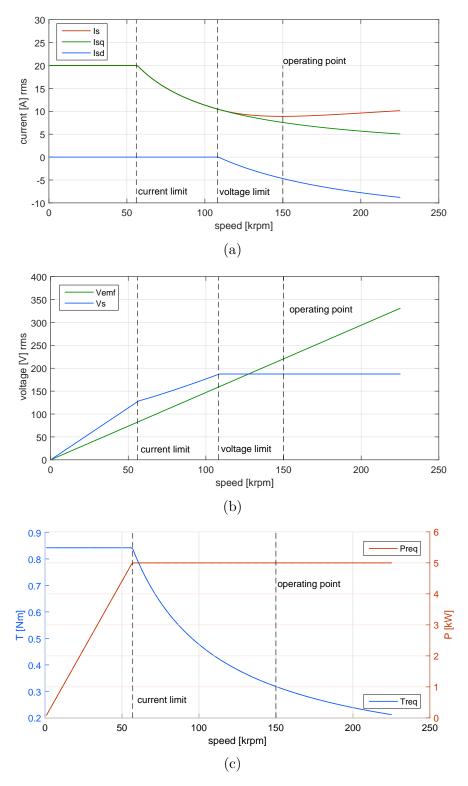

| 3-20 | Operation of the designed system under drive limitations                                                                                                                                                      | 56 |

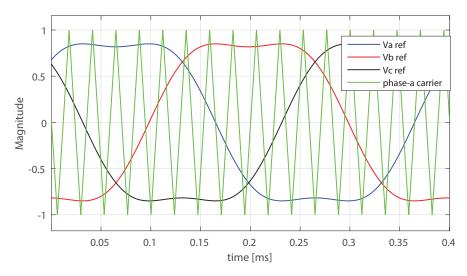

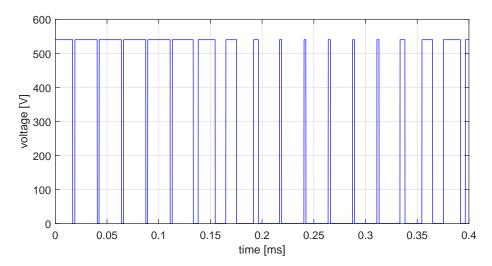

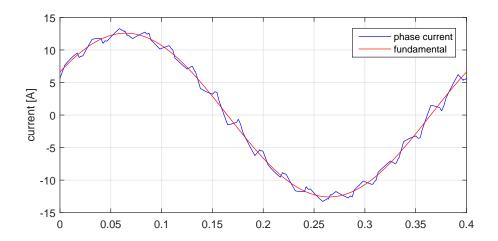

| 4-1  | SPWM with third harmonic injection                                                                                                                                                                            | 60 |

| 4-2  | Switch PWM voltage waveform                                                                                                                                                                                   | 61 |

| 4-3  | Inverter phase output current                                                                                                                                                                                 | 61 |

| 4-4  | Si MOSFET and IGBT hard-switching behavior [10]                                                                                                                                                               | 62 |

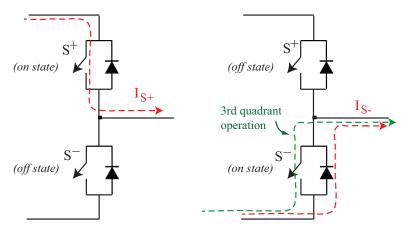

| 4-5  | Load carrying devices during on-state operation                                                                                                                                                               | 63 |

| 4-6  | Current operating points of the phase leg semiconductors. The positive current points correspond to the switch and the negative points correspond to the inverse diode conduction (or 3rd quadrant operation) | 64 |

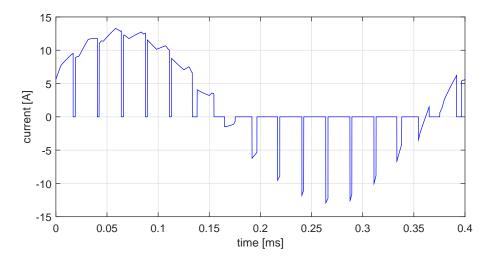

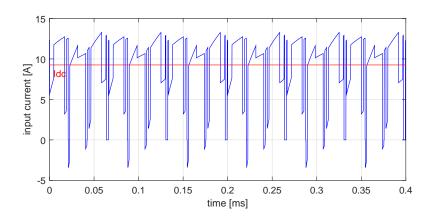

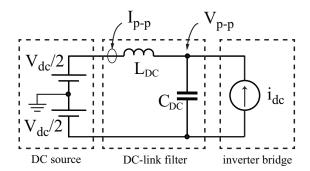

| 4-7  | Inverter input current                                                                                                                                                                                        | 65 |

| 4-8  | DC-link filter model                                                                                                                                                                                          | 65 |

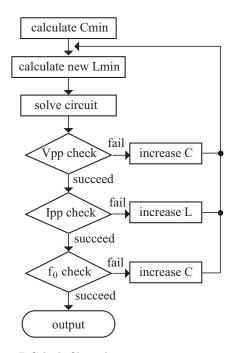

| 4-9  | DC-link filter design process                                                                                                                                                                                 | 67 |

|      |                                                                                                                                                                                                               |    |

List of Figures ix

| 4-10 | Switching losses calculation using the piecewise linear approximation                                                                    | 6 |

|------|------------------------------------------------------------------------------------------------------------------------------------------|---|

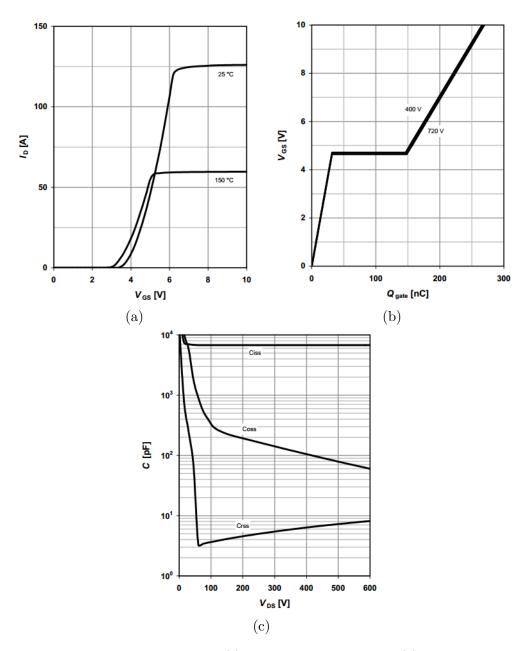

| 4-11 | Transfer characteristic (a), gate-charge characteristic (b) and parasitic capacitances (c) of the IPW90R120C3 MOSFET switch              | 7 |

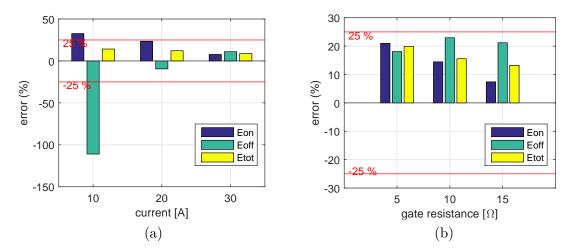

| 4-12 | Accuracy of the MOSFET analytical model for switching energies calculation, using the SiC MOSFET C3M0065090D of CREE as a reference      | 7 |

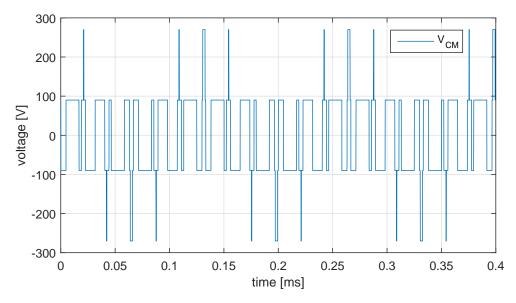

| 4-13 | CM noise source PWM waveform                                                                                                             | 7 |

| 4-14 | CM noise source model where the transient consists of the PWM and $dv/dt$ signals                                                        | 7 |

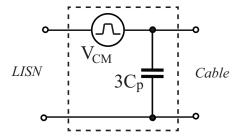

| 4-15 | CM noise phase equivalent circuit of inverter bridge                                                                                     | 7 |

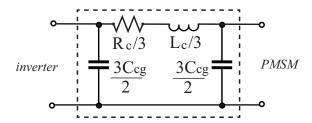

| 4-16 | CM noise phase equivalent circuit of cable connection to the PMSM                                                                        | 7 |

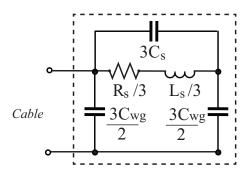

| 4-17 | CM noise phase equivalent circuit of the PMSM                                                                                            | 7 |

| 4-18 | Single phase equivalent circuit of the CM noise source and propagation path.                                                             | 7 |

| 4-19 | Reduced model of the CM noise                                                                                                            | 7 |

| 4-20 | DM noise source and propagation path single-phase equivalent circuit                                                                     | 7 |

| 4-21 | $\Pi$ configuration of the EMI suppression filter                                                                                        | 7 |

| 4-22 | CM (top) and DM (bottom) equivalent circuits for EMI filter design                                                                       | 7 |

| 4-23 | EMI noise measured on the LISN prior to filter design                                                                                    | 7 |

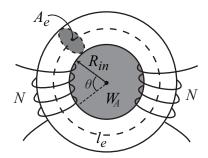

| 4-24 | Coupled inductor for CM choke design                                                                                                     | 7 |

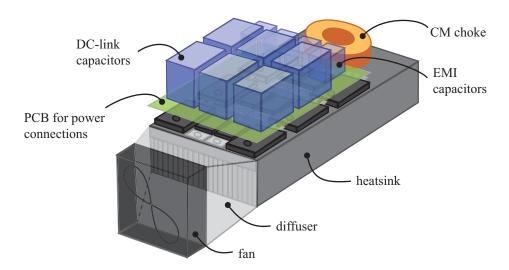

| 4-25 | Spatial design of the inverter circuit, including the cooling mechanism                                                                  | 8 |

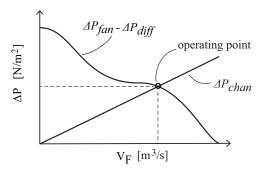

| 4-26 | Heatsink-fan operating point                                                                                                             | 8 |

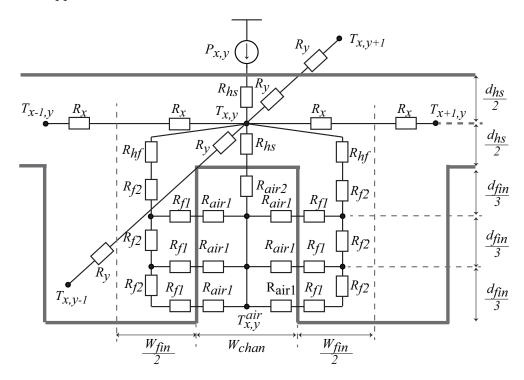

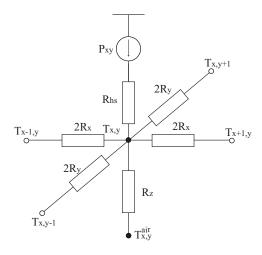

| 4-27 | 3D equivalent resistor model of the heatsink structure                                                                                   | 8 |

| 4-28 | Simplified 3D resistor network of the heatsink elementary segment                                                                        | 8 |

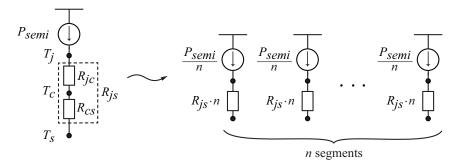

| 4-29 | 3D equivalent resistor model of the semiconductor components                                                                             | 8 |

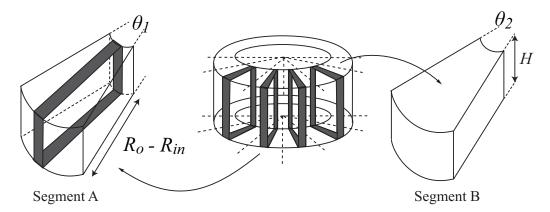

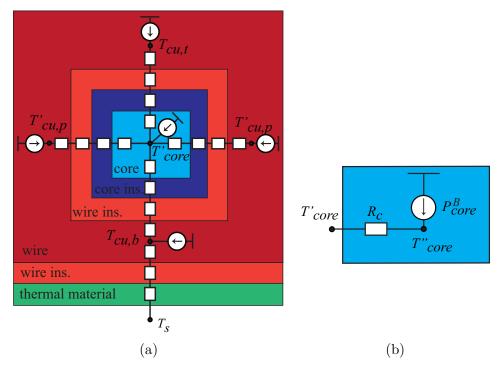

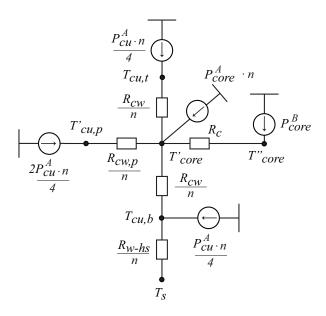

| 4-30 | 3D partitioning of the inductor thermal model                                                                                            | 8 |

| 4-31 | Inductor 3D thermal model: (a) segment A, (b) segment B, (c) simplified model.                                                           | 8 |

| 4-32 | Simplified thermal model of the inductor                                                                                                 | 8 |

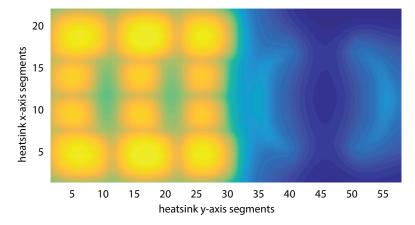

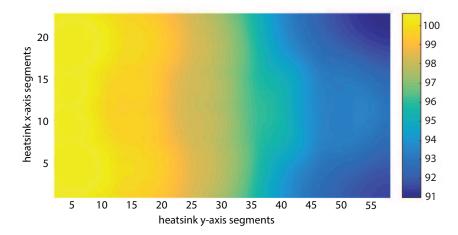

| 4-33 | Spatial arrangement of the heat sources (semiconductors and inductor) mounted onto the heatsink.                                         | 8 |

| 4-34 | Thermal coupling of semiconductors and inductor components through the heatsink body. The fan is cooling the heatsink from the left side | 8 |

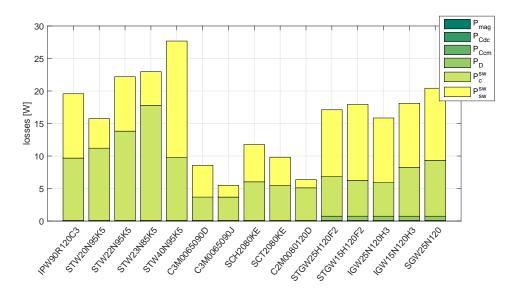

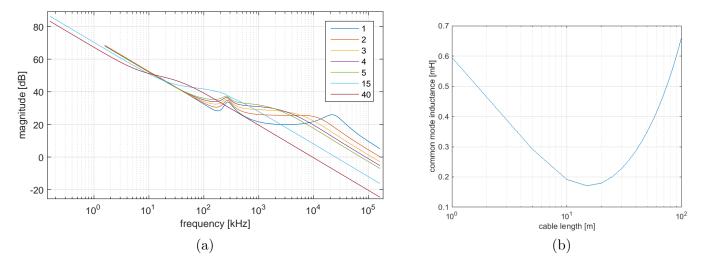

| 5-1  | Losses distribution in the inverter components for $f_s = 27.5$ kHz and minimum gate resistance                                          | 9 |

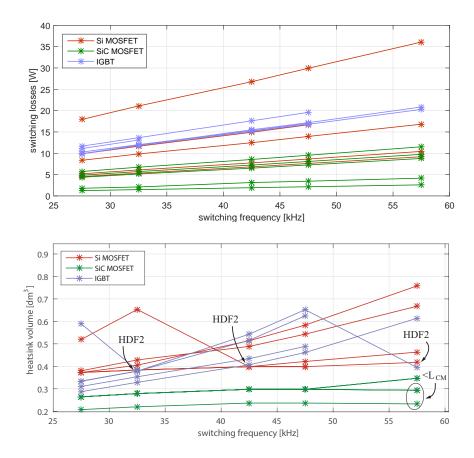

| 5-2  | Switching losses, and heatsink volume dependency on the semiconductors losses as a function of the switching frequency $(R_g = \min)$    | 9 |

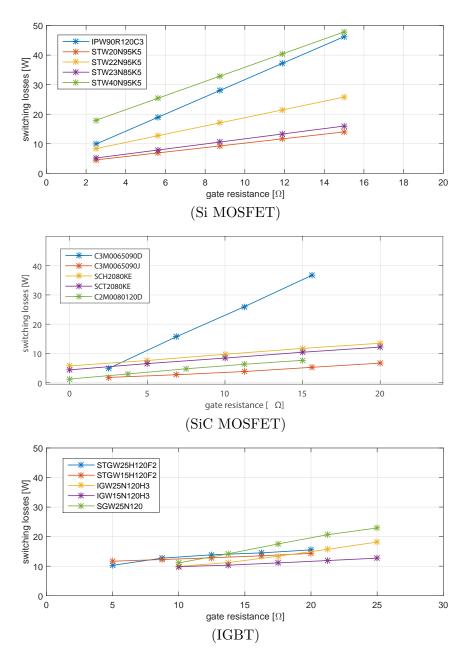

| 5-3  | Switching losses as a function of the gate resistance $R_g$ ( $f_s=27.5~\mathrm{kHz}$ )                                                  | 9 |

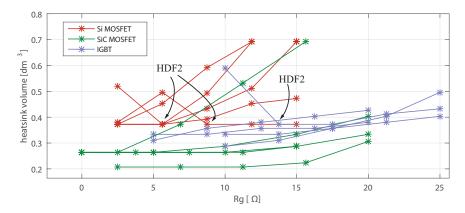

| 5-4  | Heatsink volume dependency on the semiconductors losses as a function of the gate resistance $R_g$ ( $f_s = 27.5 \text{ kHz}$ )          | 9 |

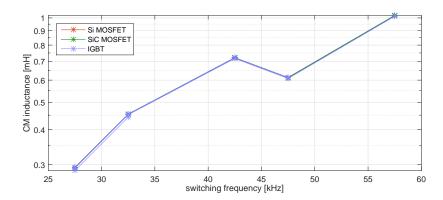

| 5-5  | CM inductance variation with respect to the switching frequency                                                                          | 9 |

| 5-6  | CM inductance as a function of the gate resistance $R_q$ ( $f_s = 27.5$ kHz)                                                             | 9 |

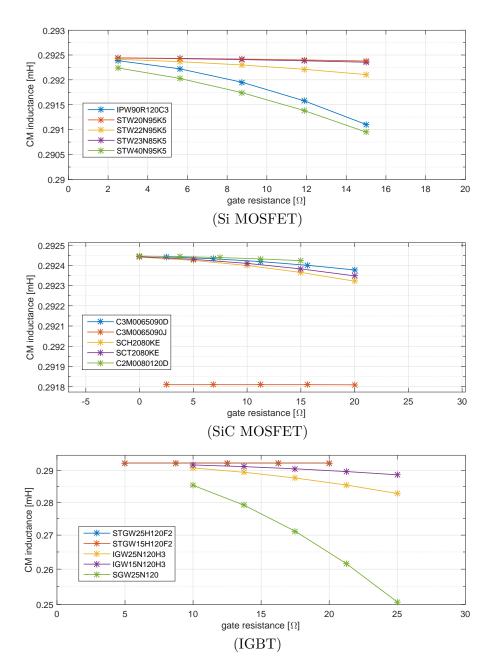

| 5-7  | Capacitance and inductance variation of the DC-link filter with switching fre-                                                           |   |

|      | quency.                                                                                                                                  | 9 |

|      |                                                                                                                                          |   |

Master of Science Thesis

List of Figures

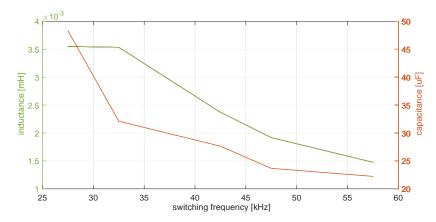

| 5-8  | Cable length effect on EMI filtering: (a) CM propagation path impedance, (b) CM inductance dependence on the cable length | 100 |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

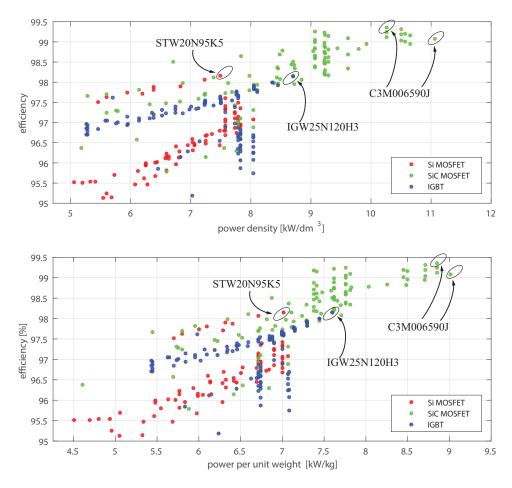

| 5-9  | System performance evaluation with respect to efficiency versus power density and efficiency versus power per weight      | 101 |

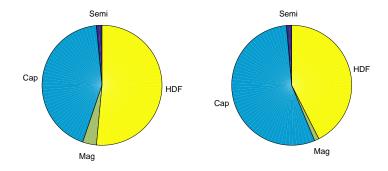

| 5-10 | Overview of the components volume distribution for the C3M006590J switch inverter at 57.5 (left) and 27.5 kHz (right)     | 102 |

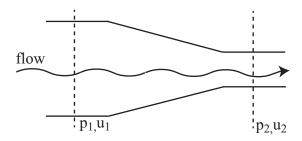

| B-1  | An expanding contracting pipe                                                                                             | 113 |

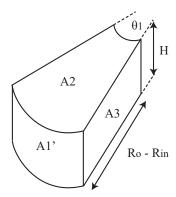

| B-2  | 3D representation of toroid elementary Segment A                                                                          | 116 |

| B-3  | Segment A 2D representation                                                                                               | 117 |

## List of Tables

| 3-1 | Inverter drive specifications        | 36  |

|-----|--------------------------------------|-----|

| 3-2 | Efficiency comparison for 5 kW       | 44  |

| 3-3 | Efficiency comparison for 50 kW      | 45  |

| 3-4 | Complexity comparison                | 46  |

| 3-5 | Cost comparison                      | 46  |

| 3-6 | Inverter operating point             | 54  |

| 3-7 | Machine operating point              | 55  |

| 4-1 | Switches technology comparison       | 63  |

| 5-1 | Switching frequency parameters       | 90  |

| 5-2 | Semiconductors devices               | 91  |

| 5-3 | Semiconductors thermal coupling      | 93  |

| 5-4 | Best designs comparison              | 102 |

| 5-5 | Inverter parameters                  | 103 |

| A-1 | Resonant circuit parameters          | 109 |

| C-1 | Thermal-conducting materials         | 121 |

| C-2 | Ferrite material 'J' core properties | 121 |

xii List of Tables

## Chapter 1

#### Introduction

#### 1-1 Problem statement

The design of high performance power electronic converters is a challenging and complex task. The main reason is that the design considerations are spanning various physical domains, for example electrical, thermal, etc. The complexity results to a high cost and time consuming design process, which often require iterations; design of a first prototype, manufacture it, characterize it and then conclude to a final design. In order to tackle this problem, a virtual prototype by the means of analytical models and/or simulations can help engineers in a pre-design level as well as in the validation steps of the design process. New methodologies employing virtual prototyping in combination with multi-objective optimization are becoming increasingly mature. These methodologies are gradually penetrating the industrial power electronic design process. The application of multi-objective optimization is more powerful with multi-domain modeling, which by means is not always a straightforward task. As a result it is interesting to explore how to research a modular, systematic and scalable methodology.

Moreover, the aerospace industry is placing great emphasis in technologies which can reduce the overall costs and fuel consumption. For this reason, the continuous development of power electronic converters has opened new opportunities to the trend for the More-Electrical Aircraft (MEA), where the conventional power sources (pneumatic, hydraulic, mechanical) are replaced with electric sources to support secondary loads in the aircrafts. The electric systems are expected to lead to more efficient, lighter and lower maintenance solutions by using high power density power electronics and electrical machines. However, the extreme operating conditions and strict reliability regulations in aerospace applications constrain the maximum power density which can be achieved in these applications. In this direction, these challenges need to be met for the electronic devices, in order to obtain optimal designs for power system integration in More-Electrical Aircraft.

Consequently, the problem of optimally designing a motor drive for aerospace applications is gaining more attention. To this regard, applying multi-objective optimization is expected to be crucial towards achieving the stringent requirements that are present. Therefore, a subsequent modeling effort for the inverter and motor is necessary to fully exploit

2 Introduction

the advantages of optimization techniques. This thesis work will focus on the design of an inverter for aerospace applications.

#### 1-2 Thesis objective

This thesis project is conducted in collaboration with Aeronamic B.V. in order to develop a design framework for an inverter which will constitute the basis and support the design for a high-speed PMSM drive system optimization. The primary objective of this thesis is to investigate the interdependencies of the design domains of an inverter for aerospace applications, targeting to design an inverter with minimum volume and weight. In order to achieve the main objective of the thesis, a design method must be developed and the following aspects must be answered:

- Which are the considerations to decouple the design aspects related to power electronics design?

- How are the boundaries of the design aspects defined?

- Which are the interdependencies between the design aspects?

- How can the interdependencies be manipulated to achieve optimal designs?

- Which modeling method is suitable for this study?

- How is the modeling effort determined by the design objectives?

#### 1-3 Thesis contribution

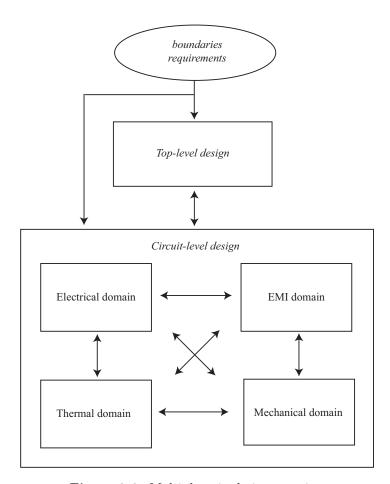

A design methodology is developed in this project thesis, based on multi-domain design. The converter design is decoupled regarding the system and individual component performance and treated in a top-level and circuit-level. In the top-level design, the selection process of a topology, modulation and control strategy takes place. In the circuit-level, the converter is designed regarding the component behavior, with respect to the physical domains that describe the converter operation. The design domains are distinguished in electrical, EMI, thermal and mechanical, and are treated independently. The boundaries of the design levels and domains are determined and the links between the design domains are established though their mutual dependencies.

Based on this methodology, a virtual prototype of an aerospace inverter is realized in software using analytical modeling. In the top level design the inverter is designed for minimum current rating, based on the operation of the inverter-PMSM system under the drive limitations. In the circuit level, the interdependencies of the design domains are manipulated using design variables, similar to an optimization problem, by employing parametric sweep. A high efficiency and high power density aerospace inverter is designed to drive the PMSM load, according to the specifications of Aeronamic B.V. and aerospace regulations.

1-4 Thesis outline 3

#### 1-4 Thesis outline

Apart from the present introductory chapter, the thesis contents are organized as follows.

In Chapter 2, first the background of this work regarding virtual prototyping and multi-domain modeling methods is described. The reasoning for choosing a multi-domain design approach using analytical models is described. Then the methodology developed in this thesis project is described. The converter is considered in a top level and circuit level design domain, which are designed autonomously. Then the design domains of the circuit level design are distinguished, namely electrical, EMI, thermal and mechanical, and their couplings are investigated. In addition, some modeling considerations regarding each domain are briefly addressed.

The design approach is then applied to the design of an aerospace inverter and a design framework in software is developed. First, in Chapter 3, the specifications and application specific constraints of the inverter are addressed. Then the topology selection follows, based on a classification of the available topologies and comparison of the suitable candidates. In addition, a modulation technique is selected for the design based on a classification of the available modulation techniques. Finally, the control strategy is selected and the inverter-PMSM operating points are obtained. The control strategy is selected for a minimum current sizing of the inverter and the operation of the system under drive limitations is investigated.

In Chapter 4, the circuit level design takes place. Here, the objective is to estimate the converter circuit performance and design the main components. The proposed design method is followed for the modeling and linking of the electrical, EMI, thermal and mechanical design domains. Regarding the modeling choices, the reasoning and limitations of the models are addressed and the respective mathematical background is shown.

Chapter 5 presents the results obtained with the design framework which is developed in this thesis. A parametric sweep is used to manipulate the interdependencies of the design domains. First, the results regarding the interdependencies of the design domains are presented and discussed and the trade-offs of the design choices are explained. Finally, a set of inverter designs is presented, from which the best candidate regarding power density and efficiency is be selected.

The conclusions of this thesis project and some recommendations for future research are summarized in Chapter 6.

4 Introduction

## Chapter 2

## Power electronics converter design – a systematic approach

#### 2-1 Introduction

In the first part of this chapter, the concept of virtual prototyping in power electronics and a review of the related work on multi-domain design methods regarding power electronic converters are presented, which constitute the basis for the design method of this work. The second part addresses the design method developed in this thesis, which will be discussed in detail. Specifically, the key aspects of the converter design problem are analyzed, namely design levels and domains, and the interdependencies between them are investigated. Based on this analysis, a design methodology is developed targeting to establish a complete framework for power electronics design. This framework will be later applied to the design of an aerospace inverter, which will be presented in the next chapters.

#### 2-2 Background and motivation

The multi-disciplinary nature of power electronics increases the complexity in the design process, since design in many physical domains is required, regarding the power circuit's operation and environment. These domains are distinguished from each other according to the physical principles that they address, specifically electrical, electromagnetic, thermal and mechanical. Moreover, they are coupled to each other, for example in electro-thermal coupling the links are the component losses and temperature, the mechanical and electrical domain are linked through the component volume and layout (spatial design and parasitics) etc. Thus, a change in a parameter in one domain can affect the converter behavior in other domains and shape the designer's choices in different directions. Furthermore, the impact of the design choices on the converter behavior is not always straightforward and often comes with a price;

for instance, an increase in switching frequency can reduce the volume of the passives but will increase the heatsink volume due to increased losses in the semiconductors [2].

As a result, the development of power electronics poses challenges regarding the design approach. To begin with, even though a comprehensive design requires knowledge on multiple disciplines, the designer's expertise typically does not cover all areas. Also, these areas can be studied as separate domains with respect to the physical principles that define them (eg. electromagnetic, fluid dynamics, mechanical stresses etc.) so that the design process is simplified; however, they are strongly coupled to each other and it is essential that the links are included, to account for the coupled phenomena. Finally, it is often required that competing performance objectives are met simultaneously, for instance maximum efficiency and minimum volume, so the best trade-off between the objectives must be obtained for an optimal performance.

#### 2-2-1 Virtual prototyping in power electronics

There are many ways to design a power electronics system, including empirical equations, analytical models, simulation techniques etc. However, it is important that the design process meets the following general requirements:

- Gives information on the converter behavior regarding the given specifications

- Provides feedback on the design choices

- Reduces the time and effort of the design cycle: predesign, verification and validation

Also, depending on the application or the industry specifications, additional, more specific, requirements are imposed on the design approach, such as to be used for optimization or to be valid for a wide range of operating conditions and so forth. A very useful tool that meets these requirements, is virtual prototyping [2]. A virtual prototype of a converter is a representation of the physical behavior of the converter in a virtual environment, for instance modeling with analytical equations, numerical simulations or a combination of both. In this case, the designer has access to valuable information for the converter performance and reduces the design time process of a prototype as well as the cost; simulations and analytical models are faster to realize with computer-aided design, than to implement and test a prototype in hardware. It also offers flexibility regarding topologies comparison, testing of new concepts and identification of the influence of a parameter in a design.

For these reasons, and more [2], virtual prototyping has been proven beneficial for power electronics design in the literature. To begin with, great level of accuracy is achievable [2] between calculated and experimental results with minimal calculation effort. In this direction, [11] focused on losses calculation to obtain maximum power density for a nine switches matrix converter[12], employing optimization. The design results showed a 2.77% total loss error between calculated and experimental results. In addition, the reliability of power electronics can be estimated. The work in [13] proposed a systematic method for reliability-oriented design of power electronics converter, with emphasis on the reliability of IGBT modules. In the virtual prototype, the lifetime models they presented, revealed the impact of temperature and temperature cycling on 1.6kA/1.7kV/125°C and 2.4kA/1.7kV/150°C IGBT modules based

on the mission profile of a 2.3 MW wind power converter. Since their method is independent from the input, it can be used to test different mission profiles. Furthermore, comparison of different converter topologies is possible. This was the case in [14], where different DC/AC [12] converter topologies were compared with respect to the influence of switching frequency on maximum power per weight value. Finally, the virtual prototype can show the possibility of new R&D opportunities at the device level, to support optimized converters. A characteristic example is the work of [15], where a descriptive language method for renewable system inverters optimization was proposed. In that model, the component parameters were used as design variables for energy loss models of semiconductors, capacitors and inductors; hence, commercial availability was not a limiting factor in this case. To summarize, due to the advantages that virtual prototyping brings in the power electronics design, it is the basis for the methodology in this work as well.

#### 2-2-2 The multi-domain modeling approach

The design methods presented in 2-2-1 are very successful for designs in their area of focus, but none of them includes all aspects involved in a converter design, eg. electromagnetic interference (EMI) and spatial design, or they do not link the electrical and thermal behavior of the converters. To obtain comprehensive insight in the system behavior and achieve better designs, novel approaches using multi-domain modeling([4-7][20][22]) include several physical domains in the design process. This has the advantage of eliminating the risk for multiple iterations in the design or verification stages and avoids unexpected behavior of the prototype converter if the influence between the domains is neglected. As a result, the design process becomes more powerful since the mutual coupling of the domains is accounted for from the beginning of the design. This concept was the focus of [1], where the significance of the electrical-thermal-mechanical domains interdependencies for better designs was shown. Instead of being a limiting factor, the interdependencies were used to an advantage for the design of high-power density high-temperature automotive DC/DC converters, resulting to a 170W/in<sup>3</sup> at 85°C [16] and 120W/in<sup>3</sup> at 110°C [17] prototypes. The interdependencies between the electrical, thermal and mechanical domains of [1] are visualized in Figure 2-1.

Figure 2-1: Electrical, thermal and mechanical interconnections overview by [1].

In addition, the benefits of linking the design domains regarding the future development of

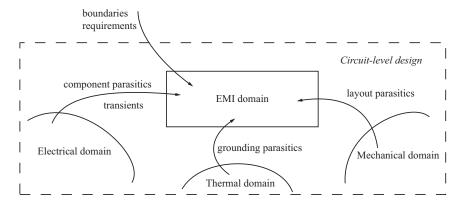

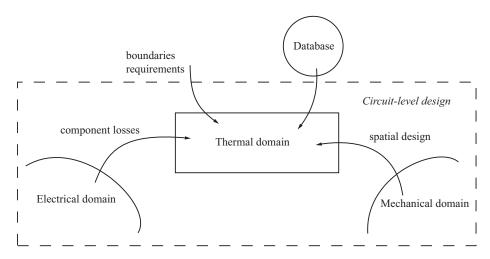

power electronics employing optimization techniques were discussed in [2]. In this work it was shown that the design process effort is expected to be minimized by coupling the engineering tools according to the domains mutual coupling, as illustrated in Figure 2-2. This justifies the fact that multi-domain approaches have become particularly useful in designs employing optimization techniques [18][19].

Figure 2-2: Multi-domain interdependencies at circuit level design by [2].

The need for optimization arises by the market requirements for more efficient, compact, reliable converters and cost-effective solutions, not to mention that such performance objectives is often required to be met simultaneously. As a result, multi-objective optimization is used. Specifically, two techniques can be identified. First, the optimization problem can be transformed into a single objective function with predefined weights for the respective objectives (aggregate technique). Alternatively, Pareto optimization [19] can be used that reveals the best trade-offs between the objectives, where no other optimal solution is obtained without deteriorating a parameter to optimize another. Since the Pareto analysis does not select weights for the optimization targets, it has the advantage of calculating all possible alternatives and is thus often preferred. The outcome of this process is the Pareto frontier of a design, which indicates the optimal solutions and allows comparison of different concepts in terms of multiple performance indexes. An example of this concept is shown in Figure 2-3, for a PFC converter comparison that was performed in [3].

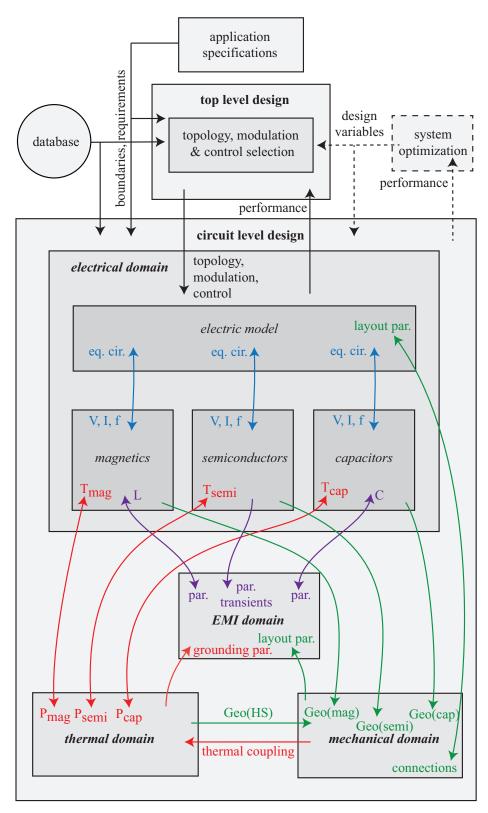

The objective of this thesis project is to arrive at a design method with complete coverage of the physical domains of the converter and their interdependencies. For this reason, this work is based on design methods that employ multi-domain approaches for power electronics, since multi-domain modeling gives insight to the inter-domain dependences and design choices trade-offs. In addition, this work aims to support the integrated design by optimization of an inverter-machine drive system, hence the design approach is based on methods that are suitable for optimization techniques. Two trends of multi-domain design for converters optimization have been identified; simulation-based and analytical equations-based. The suitability of these methods for this work depends on their characteristics, advantages and shortcomings. A short review of these two methods, together with suitability justification for this thesis is following.

Figure 2-3: PFC converters comparison using Pareto frontiers [3].

#### Simulation-based methods

Multi-domain modeling approaches have been used for power electronics design by employing simulations on either specific components or converter system design. A systematic simulation approach was followed in [20] with coupled electrical and thermal models. Their focus was on the calculation of transient temperatures of IGBT modules and short-term overload conditions analysis; this is particularly useful for optimizing module technology and reliability, and their method can be used to create thermal macro-models for system evaluation. The work in [4] also focused on IGBT modules, using multi-domain modeling for electro-thermal simulations with a feedback loop for thermo-mechanical behavior. Their concept is illustrated in Figure 2-4. However, both these methods are limited to the electro-thermal behavior of semiconductor modules. On the other hand, in [5] a simulation platform was presented, which is illustrated in Figure 2-5, for the design of DC/DC converters with focus on power density. The design tool that was developed, except from electrical and thermal domains simulation, estimates the layout parasitics, linking the electrical to the mechanical domain. It does not however include calculations for the EMI noise or filtering.

Figure 2-4: The IGBT modules design approach using simulations by [4].

These approaches require transfer of simulation data between the different physical domains or between the tools that deal with simulations within different domains. This is inherently problematic due to the coupling challenges of design tools [2][21]. Towards solving this issue, in [20] a new circuit simulator was built to solve the problems of a) connecting the

electrical losses to the thermal network and b) poor scaling performance of existing simulators for large impedance matrices for the equivalent thermal networks. Also, in [4] a central program was built to connect the simulation tools, since each physics domain specialist created the simulation models in a tool of their choice. A similar approach was followed in [5]. Since multi-domain modeling requires linking of the different physical domains, if simulation tools are used, either the user has to extend a tool to cover all domains or develop a platform, which translates and transfers the data between the different tools. Due to the limitations of simulation-based methods, combined with the fact that simulations require a substantial calculation effort, simulation-based design is not considered suitable for the work in this thesis project.

Figure 2-5: Simulation based design process of a DC/DC converter by [5].

#### Analytical equations-based methods

Multi-domain analytical models are also used for the design of power electronic converters, often in combination with optimization techniques. In [6] an evaluation of DC-DC multilevel [12] topologies is performed using electro-thermal analytical models. The design process, shown in Figure 2-6, demonstrated the sensitivity of the power density with respect to changes in design variables and proved scalability of the method to other power levels. The conclusions for the best topology were drawn by comparison of Pareto frontiers for each topology. It was proven that the greatest improvement for the system power density can be achieved by investing in better cooling methods and decreasing the semiconductor losses, which were the dominant contributor to the system losses. Also, they used interleaved [6] converters to obtain the required power output, which in turn eliminated the need for an input filter. These results however did not include the derivation of the EMI input noise, and thus the elimination for EMI filtering, or detailed spatial design.

A similar design process was also followed in [22], where analytical modeling with optimization was used for the electrical, thermal and mechanical domains, to compare DC/DC converters for telecom applications. In this study, the trade-offs required for power density over efficiency were shown and the influence of device parameters on the converter power density, considering the net volume of the main components (EMI filter was not considered). Since the volume requirements were the design constraint in this study, special attention was

Figure 2-6: Electo-thermal domain modeling and optimization process by [6].

given to the component volume distribution with respect to the switching frequency. To obtain a continuous relation to power density, their model considered a scaling method to calculate the size of the passives and the type of semiconductor switch, and the losses for the semiconductors were calculated from measurements of specific components.

Meanwhile, [7] followed a systematic approach for evaluation of AC/AC topologies, including electrical, thermal and EMI domains. The main objective was to compare the frontend rectifier topologies of AC/AC converters with respect to minimum converter weight. As a

Figure 2-7: Multi-domain design approach overview by [7].

result, the mechanical domain in their approach considered only the components weight and

spatial design was not included. The impact of the switching frequency regarding the EMI filter design [23] was also studied, which played an important role in selecting the switching frequency of the converter. However, the effect of the circuit and machine parasitics in their design process were neglected. Their design method clearly distinguishes the specifications, boundaries and variables based on which the design process is developed, and is scalable in terms of different topologies design. As a result it can be used for optimization, as noted in Figure 2-7.

With analytical modeling, complex models are required to increase the accuracy of the calculations, which in turn increases the modeling effort. However, the tools linking problem of simulation-based methods does not occur, since the multi-domain aspects were represented with equivalent models and a single modeling tool can be used in this case. Thus, the evaluation of different topologies and concepts is easier to achieve, and optimization can be employed to achieve the best possible performance of the virtual prototype. For these reasons, analytical modeling was decided to be used in the work of this thesis.

From the presented prior art, the following points can be identified. First of all, even though multi-domain modeling is used, not all domains are included in the design, for example EMI. In addition, the modeling does not always include all the contributing parameters, for example the EMI models and spatial design in [7]. Moreover, the mutual coupling is demonstrated with the analytical models, but the interdependencies are not clearly defined. On the other hand, this thesis focuses on the interdependencies of the design domains. For this reason, a complete coverage of the physical domains is needed, which can be effectively decoupled in order to investigate their interdependencies. Thus, a design methodology will be developed in this direction. This methodology is presented in the following section.

#### 2-3 Design methodology

In this section a design approach for power electronic converters based on multi-domain modeling is discussed. The objective is the development of a systematic design method that is expandable in terms of application requirements and modeling accuracy. For this reason, the effective separation of the design problem into independent design tasks and subtasks is investigated. At the same time, the coupling of the respective design aspects is identified, which in combination with the design domains constitutes a complete framework for power electronic converters development.

To meet the objective, the design tasks of the converter system are identified and modeled according to the following characteristics:

- physical behavior

- role in the system

An overview of the concept is shown in Figure 2-8, demonstrating the key design aspects and their links, which will be identified in the following sections. The source of the process is the application *boundaries and requirements*, which refer to the converter specifications, constraints and environment that shape the decision making process and modeling of the converter. Their significance in the design is discussed in section 2-3-1. Then the design

problem is separated into two independent design levels. The objective of this distinction is to decouple design decisions for the performance of the converter as a system and as individual components in the circuit. The first design level is the *Top-level design*. It refers to the converter as a system and involves decisions regarding the selection of appropriate topologies, modulation strategies and control techniques, as well as the converter system operating points. As a result, in this design level only the electrical parameters of the converter as a system are included. The design principles of the *Top-level design* are presented in section 2-3-2. The second design level is the *Circuit-level design*. Here the converter is designed regarding

Figure 2-8: Multi-domain design overview

the component behavior, with respect to the physical domains that describe the converter operation, namely *Electrical*, *EMI*, *Thermal* and *Mechanical domains*. In sections 2-3-3 to 2-3-6 the *Circuit-level design* domains are presented respectively, where the design aspects of each domain and its dependencies to the other domains are investigated. In addition, some design considerations are addressed considering modeling methods of adequate accuracy and high calculating speed for the design process. The methodology is completed in section 2-3-7, where interdependencies between the design levels and domains are established.

#### 2-3-1 Boundaries and requirements

The design requirements and boundaries are defined based on the application specifications and environment. Since power electronics are part of greater systems (motor drives, power amplifiers, power supplies etc), it is important to consider any subsystems that have a strong influence in the operation of the converter.

In [24] the significance of the system boundaries definition was discussed, by comparing the results of a permanent magnet BLDC machine design when the inverter was included or not in the machine design process. The results showed that when the inverter model was ignored then the machine design led to misleading results, whereas when the inverter model was considered, the torque specifications were always met. In the first modeling case, the electrical boundary of the machine included only the machine related parameters. However, in the second modeling case, the electric properties of the converter which affected the machine design were included. Thus, the electrical boundary of the machine was extended to the related electric properties of the converter. In this case, the boundaries refer to properties of the same physical domain between two different systems. As a result, the contributing parameters to the operation of the converter as a system will also be included in this work. This way their effect at the system operating points can be accounted for.

In addition, the physical environment and its properties determine the boundaries between the design domains of the converter (parameters inside the converter system). This can be demonstrated by the following case study. First of all, similar to the previous example, the thermal boundary of the DC/DC converter design in [1] included the high temperature environment of the combustion engine compartment, in which the converter was placed. In this case, the converter thermal boundary included the properties of the same design domain which were external to the converter system. Moreover, in [1] the converter individual design domains also included parameters from different physical domains within the converter system. Specifically, the boundary of the design domains was extended to the others by considering the interdependencies between them. In this thesis work, the boundary between the converter and the external environment parameters is defined in the *Boundaries and requirements* space and is illustrated in Figure 2-9. On the other hand, the interdependencies between the converter design domains which are investigated in this chapter, will define how the design domains' boundaries are extended to each other within the converter system.

Figure 2-9: Converter system boundaries

Considering the converter design requirements, the application specifications determine the output power of the converter, type of the input source and the load, the mission profile, operating frequency, performance regarding efficiency and power density, current and voltage ripple, and other parameters related to the characteristics of the converter that define it as a system. In addition, the application area comes with related reliability standards, EMI noise constraints etc. that further reduce the design space (Figure 2-10). Regardless of the application, it is also required that the performance of the converter must be within the temperature limitations of the components, voltage and current ratings etc. These requirements

are connected to the component level performance criteria. Non compliance with any of the requirements obviously leads to different design decisions.

Figure 2-10: Application dependent and independent requirements for power electronics design

The definition of clear requirements and system boundaries helps the design process, since it gives a comprehensive overview of the system to be designed and allows a better approximation of the real system. Whether they will influence the *Top-level* or *Circuit-level design*, depends on the nature of the boundaries and purpose of the design task, as will be shown in the following sections.

#### 2-3-2 Top level design

At the beginning of the design process, decisions regarding the converter design in the context of a system are the subject of the *Top-level* design. Here, the design considers the electrical parameters of the converter as a system. The objective is to determine the appropriate topologies, modulation and control strategies, which can be employed. In this section, the dependencies of the *Top-level* to other converter aspects are addressed, followed by considerations regarding the design process in this stage.

#### Top level dependencies

The design space regarding converter topologies, modulation and control strategies is very broad, considering their advantages and shortcomings and their suitability for a specific application. The main aspects which influence the selection process are the application specifications and component ratings (Figure 2-11). The application specifications refer to the converter power, source type and load type. These parameters determine the type of converter and suitable topologies, considering the type of the converter elements and their circuit connections. In addition, the voltage and current ratings of the available components from the database affect the selection process of appropriate topologies as well.

The outcome of this process is a number of feasible topologies, modulation and control techniques. From this selection the voltage and current rating of the converter and converter system operating points (input and output current and voltage) are obtained. The suitability of the selected options for the application is fed from the *Circuit-level design* after the

design process is complete. Specifically, the feedback considers the converter performance and determines if the selected design is acceptable according to the specified requirements (Figure 2-11). If optimization is employed, then the feedback loop closes from the outcome of the optimization block.

Figure 2-11: Top-level design dependencies

#### Top level design considerations

Depending on the application, a search in the design space is required so that the appropriate topologies are selected. For this reason, the available topologies are classified regarding the arrangement and number of semiconductors and passive components. Similarly, a classification of the modulation techniques and control strategies can be applied according to the switching characteristics. The criteria for the candidate options selection depend on the requirements of the application, for example constant load, high power, isolation etc. For the final selection of a potentially optimal choice, a comparison based on performance metrics takes place, such as efficiency, volume, cost etc. In some cases the comparison of topologies and switching schemes combination is employed before the *Circuit-level design* to select one option, such as in [25]. In other cases, for example in [7], the candidate topologies are compared from the results of the design process. Choosing whether the topology, modulation and control will be design variables, depends on the application, experience and objectives of the designer.

#### 2-3-3 Electrical domain

In the *Circuit-level design* the electrical performance of the converter is analyzed in the *Electrical domain*. The objective is to determine the electrical characteristics of the elements of the power circuit and use them for the design of the components according to the application specifications. In this section, the parameters which influence the converter electrical behavior are addressed and the dependencies from the other domains are established. Finally, some considerations for the electric circuit design are discussed.

#### Electric circuit and component design coupling

In the design process, the circuit's electrical performance and efficiency are estimated. Regarding the analysis of the electric circuit, the converter input and output voltages and currents

are obtained for the evaluation of the converter power. The current and voltage stresses on each of the converter elements are also calculated for the performance evaluation of each converter element (Figure 2-12). Specifically, regarding the semiconductor elements, the design is based on the operating points at the switching instances and during the on- and off-state periods. Similarly, in the circuit analysis, the value of the passive elements is also calculated with respect to the specified requirements.

Figure 2-12: Electric circuit and component design coupling in the *Electrical domain*.

Furthermore, the operating points and stresses are used for the sizing and design of the respective components. From the component design, the electrical parameters of the components (required values and parasitics) are obtained and the result is an equivalent circuit of each element. The complete electric circuit can be represented more accurately if the equivalent circuits are included, hence the component design and electric circuit coupling is used in the *Electrical domain* (Figure 2-12). It should be noted that the component design in this work is considered as a part of the *Electrical domain*. However, the design of the components also depends on parameters which are obtained form the other domains, as will be discussed in following sections.

#### Circuit operation dependencies

Calculation of the component stresses depends on the operating points of the converter and the component parameters. These values are influenced by the following factors (Figure 2-13):

#### Electric boundaries and requirements

These factors are determined from converter power specifications and the electric boundary is extended to include the source and load connection of the converter. In the design process the voltage and current component constraints are taken into account to form the component design space.

#### Topology, modulation and control

The circuit voltages and currents are shaped by the converter topology (component arrangement) and the switching strategy selected in the *Top level design*. They affect the operating points based on which the circuit characteristics are dependent, for example the parasitic capacitances of the switches depend on the voltage.

#### Temperature

Many electrical circuit level parameters of the components (eg. on-resistance of semiconductors, parasitic capacitance) are temperature dependent. The operating temperature of each component is obtained in the *Thermal domain*.

#### • Layout parasitics

The parasitic inductances and capacitances of the layout interconnections can resonate with the semiconductor device and package parasitics, resulting in voltage and current overshoot and ringing at the switching instances [26]. These parasitics are determined by the spatial design conducted in the *Mechanical domain*.

#### • EMI design

The design process in the *EMI domain* determines the passive components required for the filtering of the EMI noise. These components are part of the electric circuit and hence, their design depends on the V-I characteristics.

Figure 2-13: Electrical domain dependencies

#### Electrical modeling considerations

The purpose of the electric circuit model is to estimate the electrical characteristics of the converter, determine the passive elements and determine the electrical properties used in the design of the appropriate components. From this information, the power density and efficiency can be evaluated.

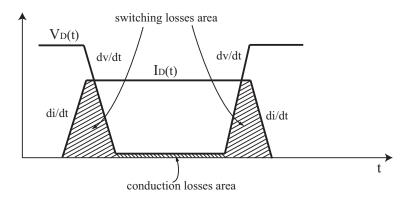

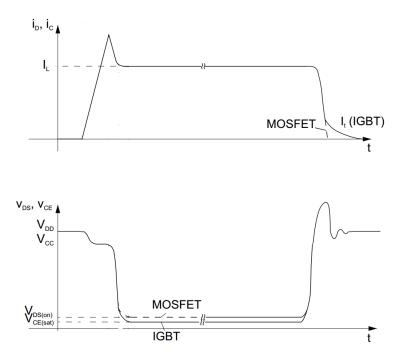

Regarding the modeling of the semiconductor parameters, a time domain representation of the switching behavior will give the current and voltage values at the switching instances and during conduction, in order to obtain the operating points which define the semiconductor parasitics. Assuming the piecewise linear model of the switching waveforms of the active semiconductors [12] (see Figure 2-14), the waveforms over the shaded areas represent the operating points used for the di/dt and dv/dt transients and losses calculations. The model will require the device characteristics and the dependence of the parasitics on voltage and current, which can be obtained from the manufacturer datasheet or measurements.

The semiconductor technology will determine the parasitics of the device and the switching pattern will be shaped by choices regarding the switching frequency, layout parasitics and gate drive circuit parameters, for instance the external resistor connected at the gate of the switch. As a result, the time domain modeling of the switching and losses calculations are driven by the design variables referring to component technology, switching frequency and gate drive. However, the losses and switching times can also be obtained directly from the manufacturer's datasheet, when given. In this case, scaling of the given data is required according to the application operating points. This method gives good accuracy for a first order estimation, since the test circuit of the measured data is different from the circuit in the application. However, the parameter scaling must include the design variables values to achieve more accurate results for the application.

Figure 2-14: Piecewise linear approximation of the semiconductor switching waveform for transients and losses calculation.

On the other hand, higher accuracy is achieved with detailed analytical models, such as in [26], where the parasitics of the circuit and the device packaging are included in the models, to account for the overshoot and ringing phenomena. However, such modeling is powerful only if the parasitic components of the circuit are known, hence it is more useful to be used at a second stage in design, where the converter circuit is fully defined.

Furthermore, the semiconductors switching waveform contains the information needed for the calculation of the currents and voltages for the sizing of the passive components. For the passives calculation, representation of the circuit in the frequency domain is particularly handy. For the frequency domain modeling the fast Fourier transform (FFT) can be used. With computer-aided tools, such as MATLAB [27], both the FFT and the inverse FFT (IFFT) can be calculated, to convert the signals back to the time domain if required. As a result, the capacitor and magnetics values and losses can be calculated in the frequency domain by modeling the excitation and parameter values for every harmonic.

Specifically, the frequency dependence of the capacitors' losses is determined the equivalent series resistance (ESR) of the capacitor, expressed by two general terms: an ohmic term  $(R_{\Omega})$  due to the resistive losses in the metallic parts and dielectric losses represented by the dissipation factor  $\tan \delta$  of the dielectric material divided by a factor of frequency  $\omega C$  [15]. The values of ESR and  $\tan \delta$  are given for a frequency range, which gives very good accuracy for the losses. However, better accuracy can be obtained if the geometry and material characteristics of the capacitor metallic parts are taken into account [15] or from test measurements of the capacitors parameters, as was discussed in [28].

Finally, both winding and core losses of the magnetic components are frequency dependent. The losses in the magnetic core material are derived from empirical equations [29][30] for different material types, which are based on curve fitting of measurements to derive the flux, temperature and frequency dependency of the losses. Considering the winding losses, the dependency on the high-frequency content of the current can be modeled analytically by considering the skin and proximity effect in the conductors [29].

#### 2-3-4 EMI domain

The *EMI domain* deals with the physical phenomena related to the electromagnetic compatibility (EMC) of the converters. The switching operation of power electronics produces EMI noise that is emitted through the free space to other equipment (radiated EMI) and transmitted through the circuit connections (conducted EMI) [31]. As a result, high frequency currents coming from the converter operation interfere with the utility and affect the operation of other equipment connected to the same power bus, or interfere with signaling and communication systems.

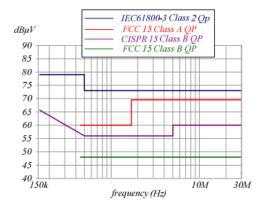

The radiated EMI is difficult and impractical to predict. On the other hand, conducted EMI can be estimated, if the defining aspects of the electromagnetic perturbations are known. The objective of the *EMI domain*, is to identify the sources and propagation paths of conducted EMI, investigate the key parameters that influence the converter behavior in this domain and take the appropriate measures in order to suppress the noise to the levels specified by the conducted emission regulatory limits.

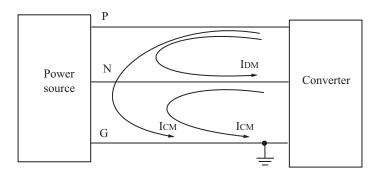

#### EMI noise source and propagation

When the switches are fast switched on and off, PWM voltages appear at the semiconductors as the result of the high dv/dt transitions. In addition, fast di/dts are also created as a result of the switching operation, that imply many high frequency components. The outcome is capacitive coupling between adjacent conductors and inductive coupling through the mutual inductance of the source and victim current loop [32]. As a result, the fast voltage and current transients propagate in the circuit through the coupling of parasitic capacitances and inductances. To simplify the conducted EMI, two mechanisms are considered [33]: the common-mode (CM) noise and differential-mode (DM).

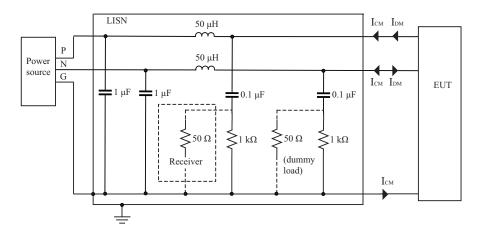

CM is the noise flowing from the power lines to the ground and back to the power lines, and is evenly distributed between the phases, as shown in Figure 2-15. The source of this mechanism is defined as a voltage source, based on the voltage transients waveform of the switches. Depending on the grounding, the propagation path of CM changes and so does the CM noise. The DM noise is circulating through the power leads of the converter, hence is independent of the grounding and does not make any contribution to the noise flowing through the ground. It is considered a current source that consists of the converter input current. In the end, the total EMI noise is a combination of CM and DM components and is unbalanced between the phase lines.

Figure 2-15: Common mode and differential mode EMI noise paths

# EMI noise source dependencies

The CM and DM noise sources are defined by the transients that are shaped by the operation of the converter. The resulting switching operation affects the slope and magnitude of the current and voltage waveform at the switching instances, as well as the switching pattern of the pulses and the harmonic spectrum of the voltage and current. All this information is obtained in the *Electrical domain* and is summarized in the voltage and current transients waveforms which are an input to the *EMI domain*.

#### EMI propagation path dependencies

The generated EMI noise propagates in the circuit through the circuit impedances and parasitic capacitances and inductances which form a low impedance path for the CM or DM current at the coupling points. These parasitics are categorized as follows [34][32]:

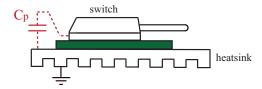

#### • Switch package parasitics

It is common to ground the heatsink and casing of the converter for safety reasons. As a result the die-heatsink-ground connection forms a parasitic capacitance to the ground, noted in Figure 2-16. This parasitic capacitance is considered through the *Thermal domain*. In addition, if discrete semiconductors or modules are used, stray inductances between the semiconductor die and packaging pins are also part of the EMI noise path. These parasitics are an input from the *Electrical domain*.

**Figure 2-16:** Switch parasitic capacitance to the ground.

# • Layout parasitics

These are stray inductances and capacitances depending on the circuit layout conducted in the *Mechanical domain* design.

# • Load parasitics

These parasitics depend on the wiring connection at the converter output and the structure of the load, which form a low impedance path for EMI. Typical cases include the parasitic components of cabling and machine impedances. Here, boundary of the *EMI domain* is extended to the load.

# • High frequency parasitics of passive components

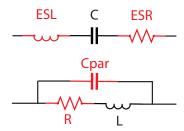

At high frequencies, the inductive and capacitive behavior of the passive components is altered by their parasitics, as shown in Figure 2-17. For this reason, a parallel connection of capacitors is usually employed to obtain a large equivalent capacitance with low parasitic inductance. For magnetics (transformers and inductors), careful design is required to achieve a low parasitic capacitance.

Figure 2-17: Capacitor (top) and inductor (bottom) lumped high frequency equivalent circuit.