## SOME MODELS AND IMPLEMENTATIONS OF DIGITAL LOGIC FUNCTIONS USING JUNCTION CHARGE-COUPLED DEVICES

TR diss 1667 JAAP HOEKSTRA

## SOME MODELS AND IMPLEMENTATIONS OF DIGITAL LOGIC FUNCTIONS USING JUNCTION CHARGE-COUPLED DEVICES

## SOME MODELS AND IMPLEMENTATIONS OF DIGITAL LOGIC FUNCTIONS USING JUNCTION CHARGE-COUPLED DEVICES

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft op gezag van de Rector Magnificus, Prof.drs. P.A. Schenck, in het openbaar te verdedigen ten overstaan van een commissie door het College van Dekanen daartoe aangewezen, op dinsdag 4 oktober 1988 te 14.00 uur

door

#### JAAP HOEKSTRA

geboren te Amsterdam doctorandus in de experimentele natuurkunde

> TR diss 1667

#### Dit proefschrift is goedgekeurd door de promotoren: Prof.dr. M. Kleefstra (promotor) Prof.dr.ir. P.M. Dewilde (co-promotor)

Contents

| 1. IN7 | RODUCTIC                              | DN1                                         |

|--------|---------------------------------------|---------------------------------------------|

| 2. OVE | CRVIEW                                |                                             |

| 2.1    |                                       | cal review                                  |

|        | 2.1.1                                 | Charge-coupled devices5                     |

|        | 2.1.2                                 |                                             |

| 2.2    |                                       | charge-coupled logic9                       |

| 2.3    |                                       | ction to systolic arrays10                  |

| 2.5    | Incroduc                              |                                             |

|        |                                       | OPERATION                                   |

| 3.1    |                                       | ction                                       |

| 3.2    | Equations of the electrical potential |                                             |

| 3.3    |                                       | nodels                                      |

|        | 3.3.1                                 | Charge coupling I, the hydraulic model15    |

|        | 3.3.2                                 | Charge storage I storage in the             |

|        | 3.3.2                                 | potential well                              |

| 3.4    | Derivati                              | ion of charge-potential relationships.26    |

| 3.5    |                                       | L charge transport                          |

| 3.5    | 3.5.1                                 | Vertical charge transport I,                |

|        | J.J.I                                 | principles                                  |

|        | 3.5.2                                 | Charge storage II, storage                  |

|        | 5.5.2                                 | in the pnp-transistor                       |

| 3.6    | More rea                              | alistic models                              |

| 5.0    | 3.6.1                                 | Charge coupling II, more                    |

|        | J.0.1                                 | realistic model                             |

|        | 3.6.2                                 | Vertical charge transport II,               |

|        | 0.012                                 | modeling                                    |

|        | 3.6.3                                 | Backward charge flow41                      |

| 3.7    |                                       | ic wells, and lateral confinement43         |

| 3.8    |                                       | technology of JCCL                          |

| 3.9    |                                       | on of basic JCCL structures                 |

| 5.7    | 3.9.1                                 | Structure of the AND/ $OR_{\odot}$ function |

|        | 3.9.2                                 | Balanced injector structure                 |

| 3.10   |                                       | aracteristics                               |

| 5.10   |                                       |                                             |

|        |                                       | IONS AND IMPLEMENTATIONS                    |

| 4.1    | Introduc                              | ction                                       |

| 4.2    | General                               | description of JCCL61                       |

|        | 4.2.1                                 | Functions in charge domain61                |

|        | 4.2.2                                 | Functions in charge and current             |

|        |                                       | domains                                     |

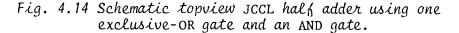

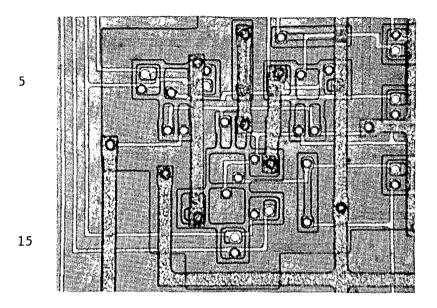

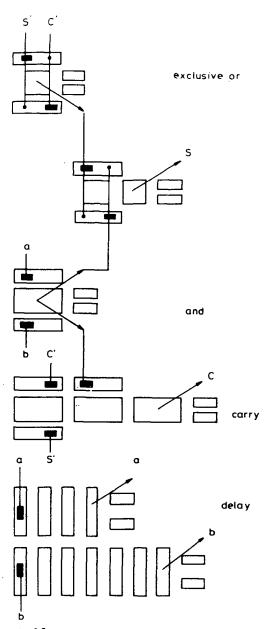

|        | 4.2.3                                 | Functions using exclusive ORs (XORs).68     |

|        | 4.2.4                                 | Threshold logic                             |

|        |                                       |                                             |

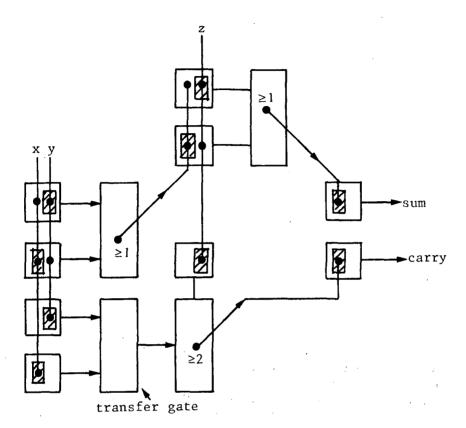

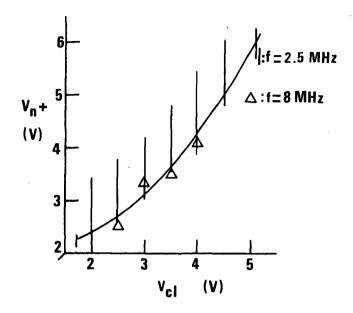

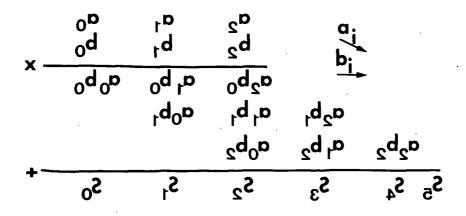

| 4.3<br>4.4<br>4.5<br>4.6<br>4.7 | The transformation of DCCL into JCCL73<br>Full adder using exclusive-OR gates80<br>Full adder/ full subtractor82<br>Threshold logic full adder |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5. EXF                          | PERIMENTAL RESULTS                                                                                                                             |  |  |

| 5.1                             | Introduction                                                                                                                                   |  |  |

| 5.2                             | Results on JCCL, $n \leq 2$                                                                                                                    |  |  |

|                                 | 5.2.1 Simple JCCD logic at 20 MHz90                                                                                                            |  |  |

|                                 | 5.2.2 JCCL operating up to clock                                                                                                               |  |  |

|                                 | frequencies of 40 MHz                                                                                                                          |  |  |

|                                 | 5.2.3 Threshold full adder97                                                                                                                   |  |  |

| 5.3                             | Results on JCCL, $n > 2$                                                                                                                       |  |  |

| 5.4                             | JCCL compatible logic at clock voltages                                                                                                        |  |  |

|                                 | down to 2 V100                                                                                                                                 |  |  |

| 6 CVX                           | THESIS                                                                                                                                         |  |  |

| 6.1                             | Introduction                                                                                                                                   |  |  |

| 6.2                             | Some pipelined multiplier arrays for                                                                                                           |  |  |

| 0.2                             | bit level systolic array architectures108                                                                                                      |  |  |

| 6.3                             | A bit level spiral systolic division array113                                                                                                  |  |  |

| 6.4                             | Junction charge-coupled devices for                                                                                                            |  |  |

| •••                             | bit level systolic arrays                                                                                                                      |  |  |

|                                 |                                                                                                                                                |  |  |

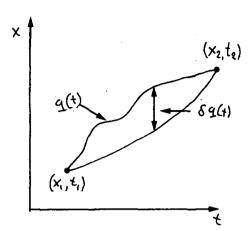

| Append                          | lix A: On the action formulation in semi-                                                                                                      |  |  |

|                                 | conductor physics and modeling129                                                                                                              |  |  |

|                                 |                                                                                                                                                |  |  |

| Refere                          | ences                                                                                                                                          |  |  |

| -                               | 151                                                                                                                                            |  |  |

| Summar                          | ry151                                                                                                                                          |  |  |

| Samenvatting153                 |                                                                                                                                                |  |  |

|                                 |                                                                                                                                                |  |  |

| Acknowledgement155              |                                                                                                                                                |  |  |

|                                 |                                                                                                                                                |  |  |

| List o                          | of symbols156                                                                                                                                  |  |  |

# INTRODUCTION

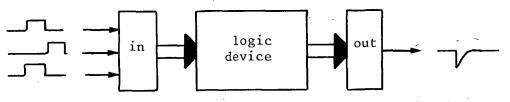

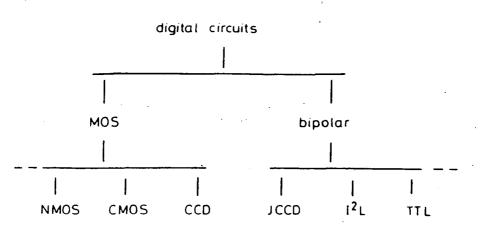

This thesis describes some models and implementations of digital logic functions using junction charge-coupled devices (JCCDs). It is a sequel to the research on junction charge-coupled logic (JCCL), which started some years ago [1.1,1.2]. Operating at driving frequencies below a characteristic value, junction charge-coupled devices have a recognized advantage in low power and high functional density, which justifies research on applications in the field of digital integrated circuits.

Charge-coupled device (CCD) is a generic term which has come to be applied to a family of functional solid-state electronic devices. Under the application of a proper sequence of clock pulses these devices move "potential wells" filled with quantities of electrical charge in a controlled manner across a semiconductor substrate. In digital applications the most common example of the use of CCDs is found in memories. The digital information is represented by the presence or absence of a charge packet. This memory function can be extended with logical functions. However, in charge-coupled devices where charge packets are shifted at each clock pulse, these functions can only be carried out in a pipelined manner. The throughput (= the number of sets of data that can be processed by a functional block or an array in a given amount of time) of pipelined arithmetic calculations is high. The data can enter the logic part of the device at the maximum clock rate. The answer is some time later available but still at the maximum clock rate. In 1982 Nash introduced charge-coupled devices for use in special purpose pipelined arrays of computing elements, such as systolic arrays. He considered the advantages of CCD logic in terms of—gate density X maximum clock frequency / power dissipation—to arrive at an appropriate figure of merit for very large scale integration, VLSI [1.3].

This thesis aims to furnish the reader with a working knowlegde of the physical principles of JCCDs as used in logic applications, and to provide him with tools for the concise and precise description of the basic structures and synthesis of JCCL. The core topic of the first part is the analytical solution of a simplified JCCD. In JCCD literature there are several equations expressing the amount of charge that can be stored in a junction chargecoupled device. Using the simple model a correct expression is derived. Also, a new concept of the charge transport in the junction charge-coupled device is introduced, which is not based on the charge handling capacity (= the maximum amount of charge that can be contained) of the potential well from which charge is leaving, but which is based on the equality of the electrical potential in the driving and receiving well. The description of the basic struc-tures and synthesis of JCCL is a natural extension of the existing theory on junction charge-coupled logic. The basic structures are shown to be elements of both Boolean logic and threshold logic. Bit-level systolic arrays are considered as a main tool for the synthesis.

Briefly, this thesis is organized as follows. Chapter 2 presents an overview of research on charge-coupled devices and an introduction to systolic arrays. In Chapter 3 the basic principles, technology, and limitations of JCCDs as used in logic applications are discussed. The first part of Chapter 4 deals with the general description of JCCL. In the second part of Chapter 4 several JCCL full adders are developed and discussed. Chapter 5 shows experimental results on (i) simple logic devices and (ii) a threshold full adder. Finally, in Chapter 6—the last chapter—the synthesis of JCCL is discussed. Junction charge-coupled logic is a technology for bit-level systolic arrays. From this point of view, the theory of bit-level systolic arrays is part of a synthesis technique. Appendix A discusses a possibility for obtaining the potential relationships in semiconductor devices, here the pnjunction, not from Poisson's equation but from an action integral. Chapter 1

# OVERVIEW

#### 2.1 Historical review

#### 2.1.1 Charge-coupled devices

Charge-coupled devices belong to the class of charge transfer devices. The basic ideas of charge transfer devices have grown out of the development of several concepts.

One of these concepts was that of analogue shift registers. The notion of a shift register involved the passage of charge along a line of capacitors through the sequential switching of transistors. An integrated version of an analogue shift register was proposed by Sangster in 1966, under the name "bucket-brigade device" [2.1]. In 1970 integrated versions of these circuits were shown to be practical for delay and other applications.

Another development came from research on surface charge transistors (Engeler et al.) in 1970 [2.2]. This research involved a concept for controlling the transfer of stored electrical charge along the surface of a semiconductor.

Probably the most important concept originated from the work of Boyle and Smith (1970) on charge-coupled devices [2.3]. In a special issue of IEEE Transactions on Electron Devices (1976) Boyle and Smith recalled that the chargecoupled device concept was a structure that called upon existing technology, and was stimulated by the analogous work that preceded it in magnetic bubbles [2.4]. It was interesting to look for a semiconductor analogy of the magnetic bubble device. First, the charge packet was found as the semiconductor analogy of the magnetic bubble. The next problem was how to store this charge in a confined region. At this point a very important ingredient had been the development of the silicon diode camera tube. As well as the light sensitivity, the diode array had a charge storage capability. The charge could be stored in diodes for periods approaching a hundred seconds [2,5].

In their construction of the electric analogy of the magnetic bubble device Boyle and Smith used the metaloxide-semiconductor (MOS) capacitor in depletion, to store the charge. If a voltage was applied to this MOS structure a potential well was formed at the surface into which one could introduce charge (or not) to represent information. The final problem was to find a way to shift the charge from one side to the other, thereby allowing manipulation of the information. This was solved by placing the MOS capacitors close together to easily pass the charge from one to the next by applying a more attractive voltage to the receiver.

The MOS charge-coupled devices in their different forms are treated in many textbooks, such as those by Sequin and Tompsett [2.6], Beynon and Lamb [2.7], Howes and Morgan [2.8], and Esser and Sangster [2.9].

Boyle and Smith have described the working of a surfacechannel CCD. The following important step was the development of the buried-channel CCD (BCCD) by Esser [2.10] and Walden et al. [2.11]. In buried channel charge-coupled devices majority carriers are transported, that is electrons in an n-type conductivity layer, and individual charge packets are separated by a depleted region. If the MOS capacitors are replaced by reverse-bias pn-junctions we obtain a junction charge-coupled device. If the MOS capacitors are replaced by reverse-biased Schottky barriers, we obtain a Schottky charge-coupled device, both first proposed by Schuermeyer et al. [2.12].

#### 2.1.2 Logic circuits with charge-coupled devices

The idea of using charge-coupled devices for digital circuits and binary logic operations originated in the early 1970's. In 1971 Kosonocky and Carnes [2.13] summarized their work on the digital operation of chargecoupled circuits. Their paper described the operation and application of charge-coupled shift registers and the necessary charge regeneration stages. Thereafter Tompsett (1972) proposed the elementary logic operations NAND and NOR based on charge regenerators [1.14].

These operations did not involve direct interactions of charge packets. The presence or absence of charge packets in a parallel CCD shift register was detected by a floating gate. Mok and Salama (1972) introduced the principle of charge overflow in logic CCDs, which made it possible to have a direct interaction of charge packets in logic devices [2.15]. They used built-in potential barriers for charge packets. In this way the basic logic operation was that of CCD majority logic (= logic that tests whether the sum of a given number of charge packets is greater than a certain amount of charge). The built-in potential barrier could be realized in essentially two ways. First, by placing an ion implantation or a local increase in oxide thickness under the gate. Second, by inserting a separate gate with an offset voltage with respect to the following gate.

The principles of 'floating gate' logic or charge overflow using potential barriers formed the basis of all investigations on logic CCD circuits, such as those by Zimmerman et al. [2.16], Montgomery and Gamble [2.17], and Kerkhoff et al. [2.18].

With the development of JCCDs a new approach, that of charge injection and charge detection with bipolar transistors, was introduced (Wolsheimer [2.19], May et al. [2.20], and van der Klauw [2.21]).

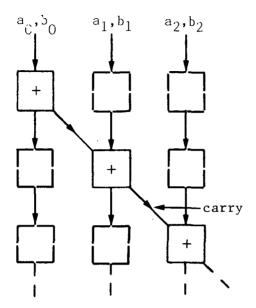

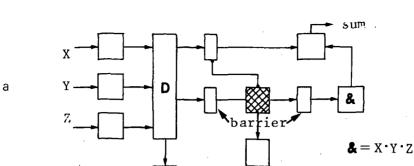

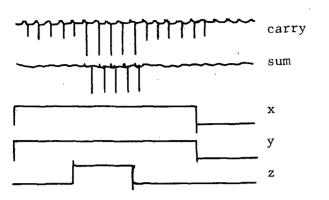

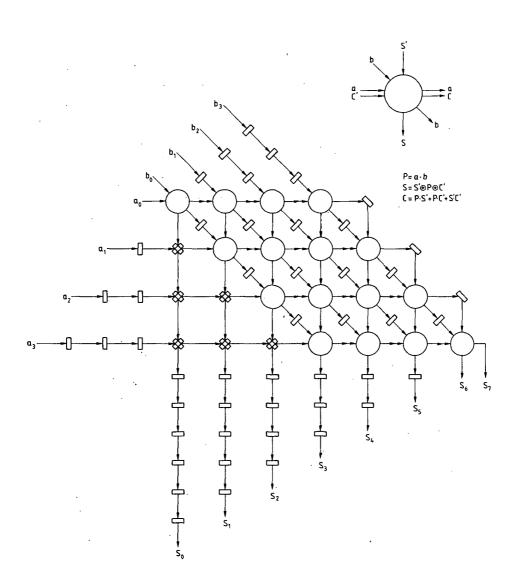

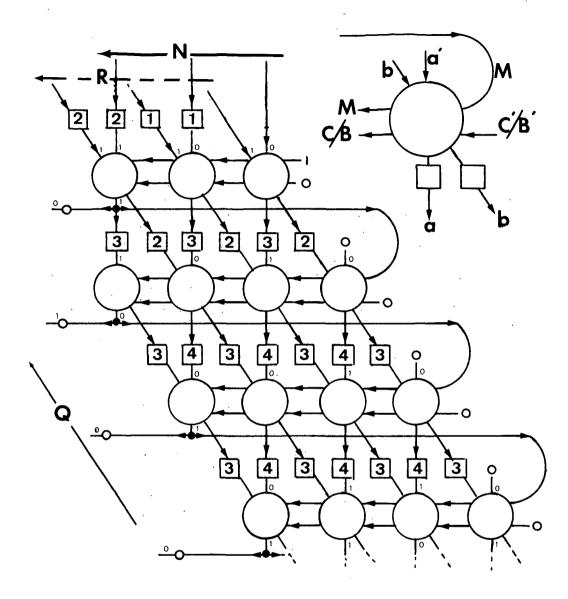

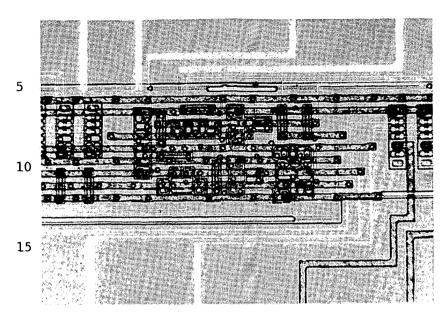

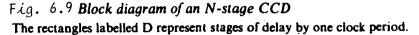

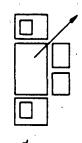

Fig. 2.1 Addition: the carry bits propagate on the diagonal, the set of delays on the input bits is above the diagonal, the set of delays on the output lines is under the diagonal.

In 1977 in an article presenting digital charge coupled logic (DCCL), Zimmerman et al. described a method of implementing digital logic functions based on the use of CCDs in pipelined configurations. The reason that pipelined calculations in arithmetic units are required is associated with the generation of the carry bit at each stage. For example, in the addition of two n-bits words, the two least significant bits can be added immediately and produce their sum and carry outputs. This carry is only then available to be combined with the following significant bits and produce a new sum and carry. Figure 2.1 shows that in this manner the carry is delayed during each operation and so the application of the next significant bits must be delayed by an equal amount. This requires a set of delays on the input lines. An analogous set of delays must be inserted on the output lines if the entire word must be available at one clock pulse sometime in the future. There is another implication of using pipelined arithmetic. As data enter at one clock-phase and exist at one clock-phase in the future it is not efficient

8

to do random calculations with pipelined techniques. This means that digital CCD technologies are best suited for signal processing functions on several blocks of data simultaneously.

Fortunately a large number of algorithms are either already in a pipelined organization or can be cast into one. When a variety of such systems is considered, certain basic functions appear repeatedly. The multiplier, for example, requires adders; the fast Fourrier transformation requires multipliers and adders; serial correlators require shift-registers, multipliers, and accumulators; digital differential analysers use adders and shift registers to perform integration; division and Hadamar transforms require add and subtract functions. The most advanced result, achieved with digital charge-coupled logic was the design of a Hadamar transformer chip of 100 mm<sup>2</sup> in 1979 [2.22].

Another approach was described by Nash in 1982. He combined charge-coupled devices with conventional MOS circuitry in such a way that it combines the low power, high packing density of CCDs with some of the high speed combinatorial (nonclocked) logic capabilities of conventional NMOS circuits [2.23]. This approach possesses a capability that allow information to propagate or ripple through a circuit, and can reduce the number of delays. At the moment the follow-up of this research, the description of a technology which combines charge-coupled devices with CMOS circuitry, is being done in several places throughout the world. Nash introduced systolic arrays as an important candidate for the application of CCD logic circuits. The special features of this kind of array, namely: regular structures, pipelined architecture, special purpose, neighbor communication could be well matched by a charge-coupled device logic.

#### 2.2 Digital charge-coupled logic

The most elaborated research published on charge-coupled logic was that on digital charge-coupled logic [2.22]. For over 6 years many scientists worked on this topic resulting in, among other things, 14 publications and

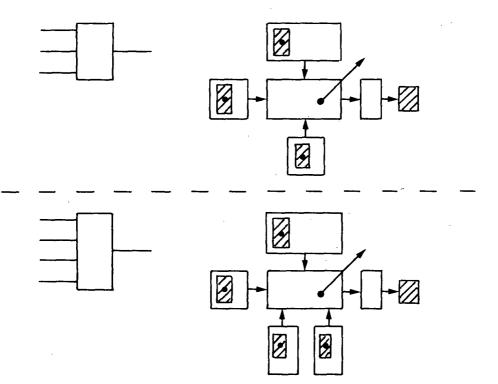

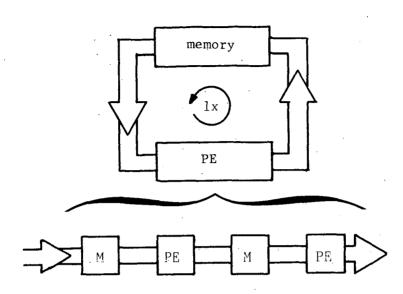

Fig. 2.2 Conventional computer architecture with a single processing element (PE).

6 patents. It is important to recapitulate some of their conclusions. In section 4.3 the basic logic functions in digital charge-coupled logic are considered, and the transformation of logic functions from DCCL into JCCL will be discussed.

The design and realization of DCCL logic and arithmetic circuits presented a number of very difficult concept and modeling problems. The basic adder cells emerged as the most difficult and most essential circuits for performing DCCL logic and arithmetic functions. The half adder had become the basic element, being easily configurable into other essential logic functions, such as charge refresh and logical AND, and having an overall performance better than the full adder. Computer models predicted speeds of 5-10 MHz. Layout problems were caused by the lack of standardized symbolism and the inability to directly interconnect two physically separated signal points with a metal conductor. The final layout obstacle was the lack of computer-aided design rule checking. In a n-channel technology the half adder was successfully demonstrated at 5 MHz. The arithmetic functions obtained in digital charge-coupled logic include 16x16 multipliers and Hadamar transformation.

#### 2.3 Introduction to systolic arrays

In many digital signal processing applications, there are

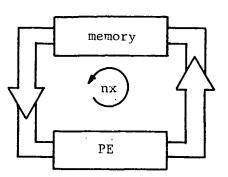

Fig. 2.3 Systolic computer architecture using local data storage.

increasing demands for large-volume or high-speed computations that have to be performed on continuous data streams. The classical Von Neumann circuit architecture fixes a limit to the computing speed. Figure 2.2 shows that in a Von Neumann machine all the processing logic is contained in a processing element (PE) and the memory (M) is located almost entirely in a separate part.

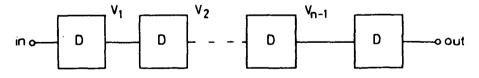

There are two main limitations to this type of circuit organization which must be overcome to obtain maximum benefit from VLSI technology. First, the sequential nature of such machines places a basic limit on their operating capabilities in high-speed processing. Second, a limitation is caused by the long global communication path owing to the separation of the processing element from the memory. Ultimately, the computation speed of such circuitry will be dominated by the time taken to communicate information between the logic elements and the memory, rather than by the intrinsic speed of the logic devices. To overcome these limitations research is stimulated on parallel processing techniques. Systolic arrays, Fig. 2.3, are well suited to implement a major class of signal processing algorithms. According to H.T. Kung and C.E. Leiserson [2.24] 'A systolic array is a network of processors which rhythmically compute and pass system'. data through the

A formal definition is given by S.Y. Kung [2.25]. systolic a computing network possessing the following features: array is

- þ Synchrony: the data are rhythmically computed (timed a global clock) and passed through the network. a)

- and Regularity: (Modularity and Local Interconnections): the array consists of modular elements with regular spatially local interconnections. (q

- delay allotted so that signal transactions from one Temporal locality: there is at least one unit-time to the next can be completed. node ি

- Pipelinability: the throughput is independent of the size of the array. Ŧ

ದ the features a, c, and d can easily been conformed to by charge-coupled logic. In fact, junction charge-coupled logic is a technology for bit-level systolic arrays. If we consider bit-level systems we note that especially

be used as building blocks in a system level design [2.28]. The final step of the trajectory is the selection of concrete algorithms for bit-level computations Some saging this into a more suitable form, mapping it onto an array architecture and converting this to a systolic array approaches can be distin-Some, ad hoc, systolic arrays on the bit-level are described in chapter 6. then the data dependences can often be expressed as matrix-type computations [2.27]. McCanny and McWhirter use this approach to select bit-level solutions which can Anneveling and Dewilde [2.29]. Other techniques are based on the recurrence equations. If algorithms recursive properties are already available architectural design. Different approaches can be dist guished. S.Y. Kung describes a graphical approach which follows the progression of choosing an algorithm, mas-Much of the research on systolic arrays is devoted to for bit-level computations. [2.26]. This approach is also discussed by Kung, on operations on the recurrence equations. algorithms 'strong' with

## THEORY AND

## OPERATION

#### 3.1 Introduction

In this chapter an introduction to the basic principles, technology and limitations of junction charge-coupled devices is given. Using a very simple model, an analytic solution of the equations describing the potential profile in a JCCD with uniform doping concentrations and abrupt junctions, it is possible to explain the essential features of JCCDs. In JCCD literature simple models have been studied. However an analytical solution has not yet been obtained [3.1-3.4].

Unlike other integrated circuits, the charge-coupled device has no discrete equivalent circuit, that is to say, it cannot be made up of discrete devices. The typically dynamic and transient behavior of JCCDs make it apparent that although conventional one-dimensional considerations lead to qualitative and heuristic arguments concerning the device operation, the phenomenon of charge coupling along the transport direction is essentially two-dimensional, the phenomenon of charge transports along the lateral confinements are essentially three-dimensional, and the phenomenon of vertical charge transport is essentially

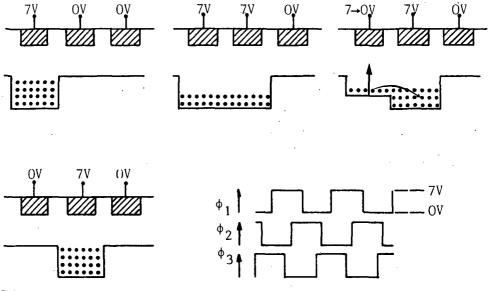

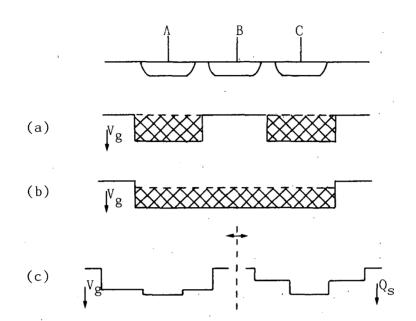

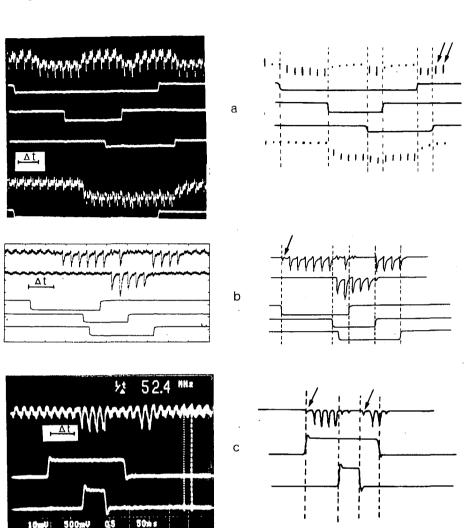

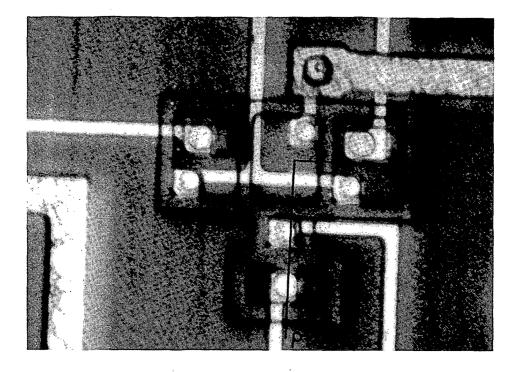

Fig. 3.1 Simple picture of the charge transfer in a CCD. Under influence of clock pulses  $(\phi_1, \phi_2, \phi_3)$  a potential well is transported. The dots represent the signal charge that is transported in the potential well.

An essential feature of JCCDs is to store information in the form of electrical packets in potential wells created in the semiconductor by the influence of separated gates. Under the control of external voltages applied to the gates, the potential wells, and hence the charge packets, can be shifted through the semiconductor. Because of the almost linear relation between the 'depth' of the potential well and the voltage on the gate, a simple hydraulic model for the charge-storage and chargetransport mechanism is generally used to depict the operation of (J)CCD structures.

To understand how a potential well can be removed from one location to another in a JCCD structure, consider the arrangement of three separated gates shown schematically in Fig. 3.1. We assume that some charge is stored initially in the potential well under the first gate which is clocked to 7 V. The other gates are at ground potential. The well underneath the 7 V gate will be much deeper than

16

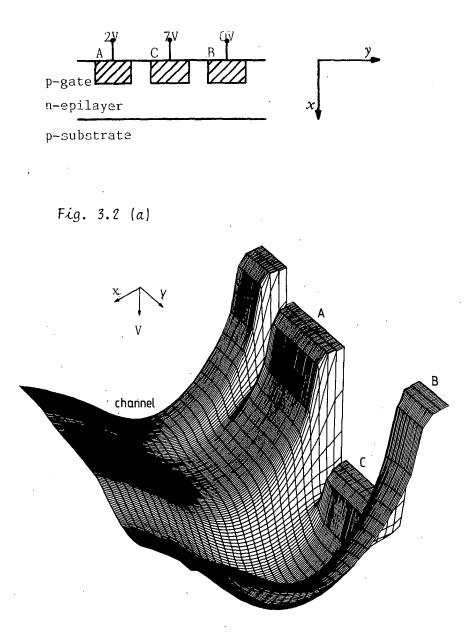

Fig. 3.2 Perspective view of the two dimensional potential distribution. The potential distribution is a result of the sequence of gate voltages as shown in (a). It clearly shows the local potential well underneath gate C.

0f unambiguously in one direction, in this case, is three. Figure 3.2 shows a perspective view of the two-dimensional be 0f those underneath the grounded gates. It is only well that charge will be stored. By applying a potential distribution if one is looking against the transport direction. clock phases needed to propagate the potential well ambiguously in one direction, in this case, is three. varying voltages to the JCCD gates a charge packet can propagated in a controlled manner. The minimum number is only in this succession

# 3.3.2 Charge storage I, storage in the potential well

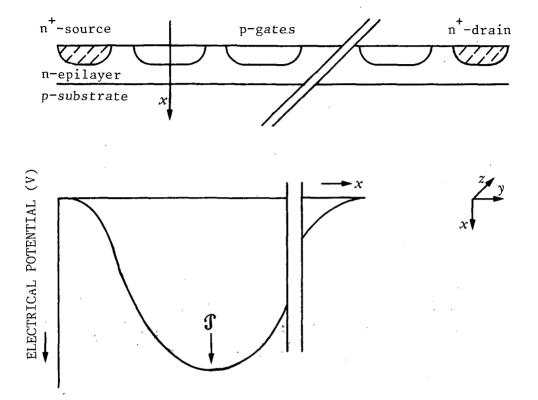

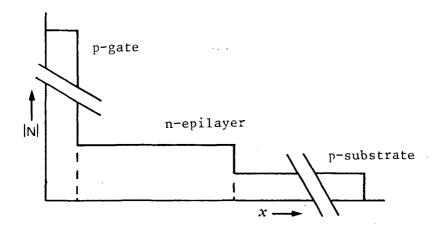

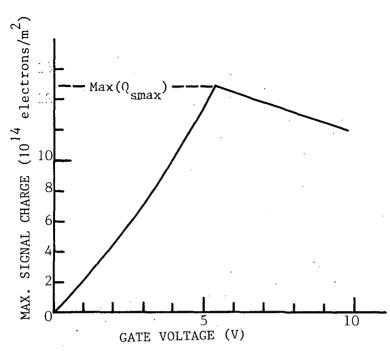

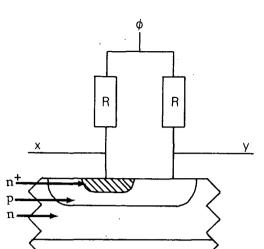

source and drain consist of n+-diffusions. diffused p-gates. lightly doped p-type substrate and an n-type Basically a junction charge-coupled device consists of Figure ω .ω shows an n-type epilayer with a typical JCCD. The ھ

the the voltage to source and drain, while the are kept at ground potential In this the For is layer extending from the gate-epilayer interface and from referred to as channel potential, Vch(Vg=0,Qs=0). electrical substrate-epilayer interface touch. At this point, epilayer by applying a sufficiently large positive a given JCCD structure all electrons potential has reached a maximum. In this case, gate are removed from the depletion and substrate This point

This the the voltage when the entire n-epilayer was depleted by the replace information-carrying electrons are majority carriers which 'n quantities of stored charge, the charge minimum. The structure electrons introduced into the structure will therefore be attracted to a plane parallel to the gate surface and passing through P where the potential energy will be a and can serve as a potential well for electrons. A well-defined local potential maximum can be created produce in the a JCCD resembles that in a buried channel CCD, the vicinity of the epilayer by clocking a gate to a positive voltage, Vg s local potential maximum is referred to as Vch(Vg,0), semiconductor. At low gate voltages, or with small thin 'slab' مf -a thin 'slab' مf applied some of the to the source and electrons that were previously of neutral ís urce and drain. In collecting in through P the electron thus capable of storing charge semiconductor storage mechanism in an Any actually removed nt Vg.

Fig. 3.3 A typical JCCD consists of a p-substrate and an n-epilayer with diffused p-gates. The first and the last gates are the n<sup>+</sup>-source and n<sup>-</sup>drain, respectively. The typical potential distribution along the x-axis has a minimum (the positive V-axis is drawn downwards). The point P indicates the potential maximum.

otherwise totally depleted n-type region.

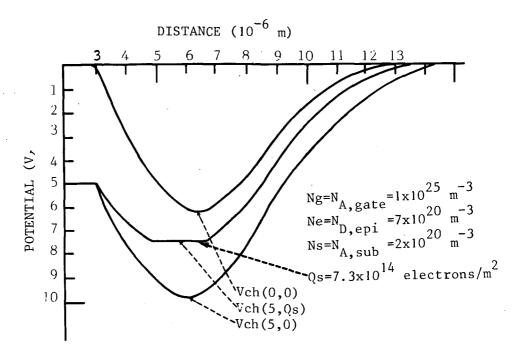

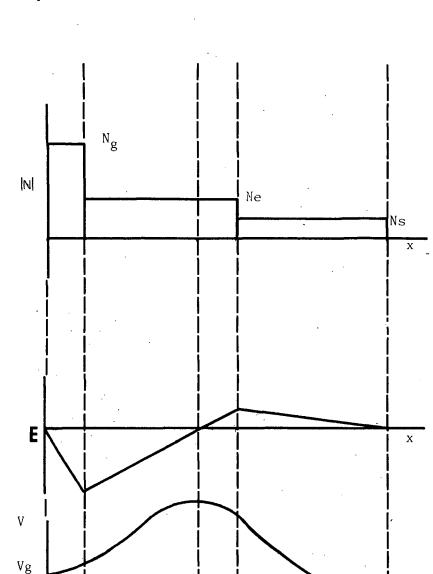

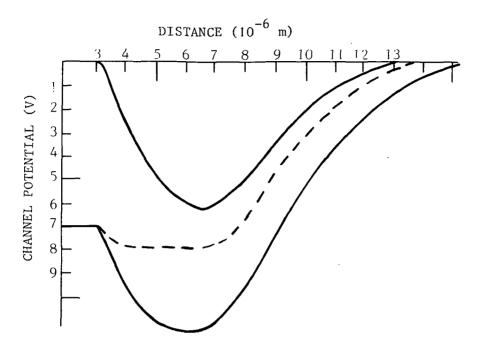

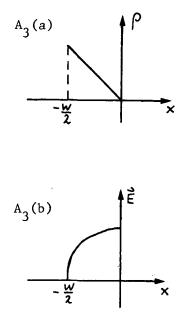

Consider a JCCD built up of uniform doping profiles as shown in Fig. 3.4. From the analysis of section 3.4 we derive the curves of Fig. 3.5 which shows the potential distribution along the axis perpendicular to the center of the gate surface. In this case the acceptor concentration

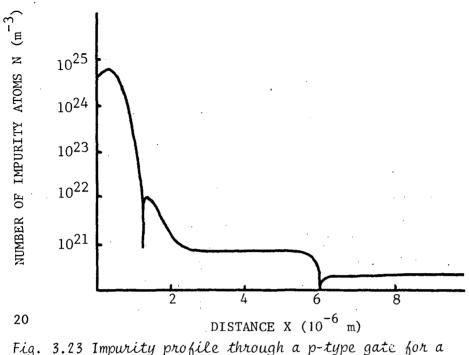

## Fig. 3.4 Impurity profile through a p-gate for an idealized JCCD.

of the gates is  $10^{25}$  acceptor  $atoms/m^3$ , the n-epilayer of doping level  $7.10^{20}$  donor  $atoms/m^3$  is 5  $\mu$ m thick, and the substrate has  $2.10^{20}$  acceptor  $atoms/m^3$ . The upper curve shows the potential profile in the absence of a gate voltage Vg. The lowest curve shows the potential profile when a voltage of 5 Volts is applied to the gate. The curve in the middle shows the potential variation in the same structure, when a signal charge of  $7.3 \times 10^{14}$  electrons/m<sup>2</sup> is introduced. The region of constant potential indicates the physical extent of neutral semiconductor, the width of which is a few microns.

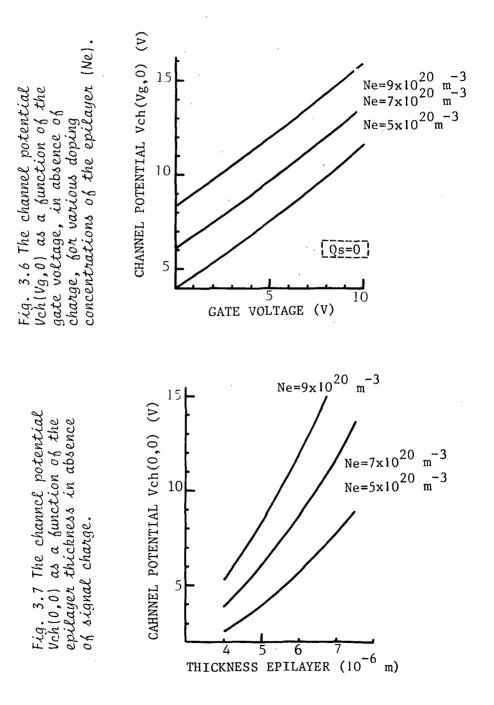

We now consider the effect of varying the voltage on a gate. A detailed analysis is given in the following section but it is intuitively obvious that making the gate more positive must produce a general downward shift (the electron energy is plotted) in the curves of Fig. 3.5. From the analysis of section 3.4 we derive the curves of Fig. 3.6 which shows the relationship between the channel potential Vch(Vg,O), and the gate voltage for various doping concentrations of the epilayer (the signal charge is zero). It clearly shows the almost linear relationship between the gate voltage and the maximum voltage in the epilayer.

Fig. 3.5 Potential distribution along the axis perpendicular to the center of the gate surface. The curve in the middle shows the distribution in the presence of signal charge.

Figure 3.7 shows the channel potential, in the absence of signal charge, Vch(0,0) as a function of the thickness of the epilayer at different epilayer dopings. It indicates the possibilities of scaling down the gate voltages, for the logic devices, under 5 V. The process described in this thesis was obtained after decreasing the epilayer thickness from 7  $\mu$ m to 5  $\mu$ m in a standard process for analogue JCCDs.

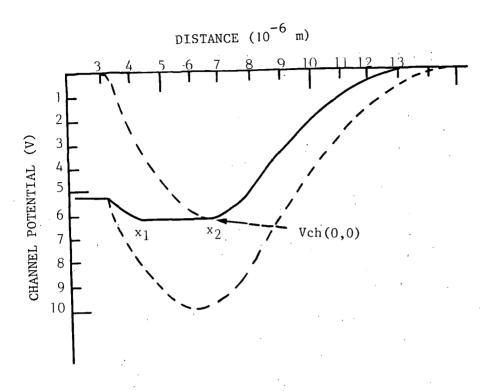

Figure 3.8 shows the situation when at a given gate-voltage the 'well' is filled maximally; if more charge is introduced it will flow underneath adjacent gates, having in common (the potential at) point  $x_2$ . As indicated in the figure this situation can occur if the gate voltage is equal to or less than Vch(0,0)-Vb, where Vb is the builtin voltage of the gate-epilayer junction. If the gate voltage is over Vch(0,0)-Vb, the maximum charge packet in

22

## Fig. 3.8 The potential distribution if the potential well is filled maximally.

the 'potential well' is limited by the requirement that the gate epilayer junction remains reverse-biased. In this case Vch(Vg,Qs) equals Vg+Vb.

Two remarks must now be made about the use of the hydraulic model. First it is necessary to realize that the amount of charge cannot be represented by an area enclosed by the different potential curves, as is the case when we consider a bucket filled with water. The amount of charge is proportional to the length of the straight line between  $x_1$  and  $x_2$ . Second it is useful to notice that the shape of the potential curve is different for different amounts of charge, in this situation it more resembles an elastic film. Consequently it is not possible to obtain a very simple relation that expresses the amount of charge that can be transported in a single clock cycle per unit of gate area, Qs, in terms of the donor concentration, thick

ness of the epilayer, and the applied gate voltage. It can, of course, easily be expressed in terms of  $x_1$  and  $x_2$ :

$$Qs = -q \int_{x_1}^{x_2} Ne \, dx$$

(3.12)

but then we have to realize that  $x_1$  and  $x_2$  are functions of Ne, d(epi), Vg, and Vch(Vg,Qs). In terms of  $x_1$  and  $x_2$ ,  $x_2$  is situated before the point at full depletion, at zero gate voltage, and  $x_1$  is situated after the point where the gate-epilayer junction equilibrium potential difference has been built up. The formula 3.12, which expresses the signal charge in the JCCD, has not appeared in international JCCD literature before. In section 3.4 the formulas for Qs, and its maximal value for a given gate voltage,  $Q_{smax}$ , are derived.

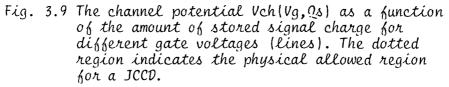

Fig. 3.10 The maximal amount of signal charge that can be handled before charge is spilled into neighboring gates, Osmax, as a function of the gate voltage.

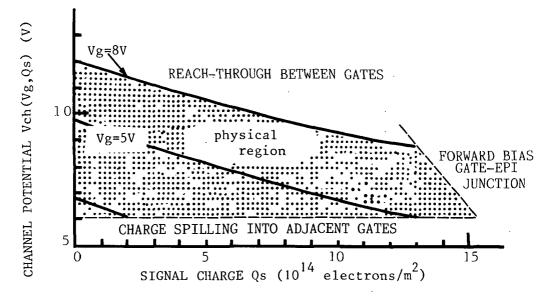

In Fig. 3.9 Vch(Vg,Qs) is shown as a function of the amount of signal charge in the potential well at different gate voltages. It also shows the physically allowed conditions for charge to be stored in the JCCD. The boundaries reflect

- (i) the impossibility of storing charge at a lower potential than that of the adjacent gates,

- (ii) that the gate-epilayer junction has to be reversebiased, and

- (iii) reach-through between the gates will not take place. The potential difference at the junction of a neighboring gate is equal or less than the built-in voltage (reach-through). For higher gate voltages this junction is forward biased and injection of holes is initiated.

The maximal signal charge that can be handled before charge is spilled into neighboring gates,  $Q_{smax}$ , is

shown in Fig. 3.10 as a function of the gate voltage. It shows the maximal amount of charge under the same conditions as above. The maximum amount of charge, Qs,max, is also called the (signal) charge handling capability (CHC). For JCCDs the CHC-curve has a maximum,  $Max(Q_{Smax})$ , if the gate voltage equals Vch(0,0) minus the built-in voltage of the gate-epilayer junction. This maximum in the CHC curve must not be confused with the term used in CCD literature 'Maximal Charge Handling Capability', which stands for another quantity.

#### 3.4 Derivation of charge-potential relationships

Consider that the gate and substrate are kept at ground potential, and the depletion layers extending from the gate-epilayer interface and from the substrate-epilayer interface touch. At this point the electrical potential has reached a maximum and is referred to as Vch(0,0). A well-defined local potential maximum is created by clocking a gate to a positive voltage Vg. This local potential maximum serves as a well for electrons.

In one dimension the distribution of the potential, V, and electric field, E, follow from:

$$\frac{d\mathbf{E}}{d\mathbf{x}} = - \frac{d^2 \mathbf{V}}{d\mathbf{x}^2} = \frac{\rho}{\epsilon} , \qquad \epsilon = \epsilon_{\text{Si}} \epsilon_0 \qquad (3.13)$$

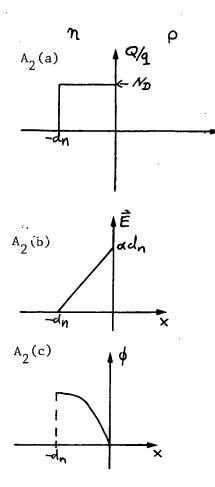

If we use the abrupt approximation and neglect the minority carriers, we obtain (see Fig. 3.11):

Area I: x in interval  $[a_1, a_2]$ We use the boundary conditions  $E(a_1) = 0$ ;  $V(a_1) = Vg$ :

$$^{E}I = \frac{-q Ng}{\epsilon} (x - a_{1})$$

(3.14)

$$V_{I} = \frac{q}{2\epsilon} \left( Ng(x - a_{1})^{2} + \frac{2\epsilon}{q} Vg \right)$$

(3.15)

aı

a<sub>2</sub>

Fig. 3.11 Doping profile, electric field E, and potential V for an idealized and empty JCCD. The figure shows the parameters a...a, which are used in the derivation of the charge-potential relationships.

a4.

a3

х

.a<sub>5</sub>

Chapter 3

Area II: x in interval  $[a_2, a_4]$ With the boundary conditions  $E(a_3) = 0$ ;  $V_T(a_2) = V_{TT}(a_2)$ :

$$E_{II} = \frac{q Ne}{\epsilon} (x-a_3)$$

(3.16)

$$V_{II} = \frac{-q Ne}{2\epsilon} (x - a_3)^2 + K$$

(3.17)

$$K = \frac{q}{2\epsilon} \left[ Ng(a_2 - a_1)^2 + Ne(a_3 - a_2)^2 \right] + \frac{2\epsilon}{q} Vg \quad (3.18)$$

Area III: x in interval  $]a_4, a_5]$ With the boundary conditions  $E(a_5) = 0$  and  $V(a_5) = 0$ :

$$E_{\text{III}} = \frac{-q \text{ Ns}}{\epsilon} (x - a_5) \qquad (3.19)$$

$$V_{\text{III}} = \frac{q \text{ Ns}}{2\epsilon} (x - a_5)^2$$

(3.20)

In these equations  $a_2$  and  $a_4$  are known;  $a_1$ ,  $a_3$ , and  $a_5$  are unknown. The unknown variables can be obtained from the following equations (continuity of the functions E and V):

$$E_{I}(a_{2}) = E_{II}(a_{2})$$

$$E_{II}(a_{4}) = E_{III}(a_{4})$$

$$V_{II}(a_{4}) = V_{III}(a_{4})$$

Which result in:

$$(a_2 - a_1)Ng = (a_3 - a_2)Ne$$

(3.21)

$(a_5 - a_4)Ns = (a_4 - a_3)Ne$  (3.22)

$$Ng(a_2-a_1)^2 + Ne(a_3-a_2)^2 + \frac{2\epsilon}{q}Vg = Ns(a_5-a_4)^2 + Ne(a_4-a_3)^2$$

(3.23)

As we assume Ng>Ne>Ns then the solution of this set of equations can be written using:

$A = \text{NeNg}^{-1} + 1$  $B = \text{NeNs}^{-1} + 1$ as: <u>1</u> if  $A \neq B$

$$a_1 = a_2 - NeNg^{-1}(a_3 - a_2)$$

(3.24)

$a_5 = a_4 + NeNg^{-1}(a_4 - a_3)$  (3.25)

$$a_3 = \frac{-(Ba_4 - Aa_2) - \sqrt{D}}{A - B}$$

with: (3.26)

$$D = AB(a_4 - a_2)^2 + \frac{(Ng - Ns)^2 \epsilon}{NgNs q} Vg$$

(3.27)

$\underline{2}$  if A = B

$$a_3 = \frac{a_2 + a_4}{2} - \frac{\epsilon}{q NeA(a_4 - a_2)} Vg$$

(3.28)

To obtain the equations for the amount of signal charge Qs that can be transported in the JCCD, when the gate-epilayer junction is reverse-biased, we consider two separate diode structures that are coupled by (see Fig. 3.12):

$$V(a_{31}) = Vch(Vg,Qs) = V(a_{3r})$$

(3.29)

Instead of equations (2.21), (2.22), and (2.23) we obtain:

$$(a_2 - a_1)Ng = (a_{31} - a_2)Ne$$

(3.30)

$$(a_5 - a_4)Ns = (a_4 - a_{3r})Ne$$

(3.31)

$$Ng(a_2-a_1)^2 + Ne(a_{31}-a_2)^2 + \frac{2\epsilon}{q}Vg = Vch(Vg,Qs)$$

(3.32)

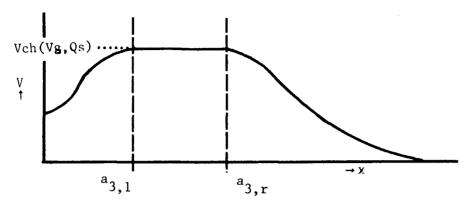

Fig. 3.12 The potential distribution in presence of signal charge. The channel potential equals the maximal potential and depends on Vg and Os.

$$Ns(a_5-a_4)^2 + Ne(a_4-a_{3r})^2 = Vch(Vg,Qs)$$

(3.33)

From these four equations we obtain, under the same conditions as in the previous case:

$$a_{31} = a_2 - \sqrt{\left\{\frac{2\epsilon \left[Vch(Vg,Qs) - Vg\right]}{q \text{ Ne } A}\right\}}$$

(3.34)

$$a_{3r} = a_{4} - \sqrt{\frac{2\epsilon \left[Vch(Vg,Qs) - Vg\right]}{q \text{ Ne } B}}$$

(3.35)

The signal charge Qs is given by:

$$Qs = -qNe \ (a_{3r} - a_{3l}) \tag{3.36}$$

which equals:

$$Qs = qNe (a_4 - a_2) - \left\{ \sqrt{\left\{ \frac{Vch(Vg,Qs)}{p} + \sqrt{\left\{ \frac{Vch(Vg,Qs)}{r} \right\}} \right\}} \right\}$$

(3.37)

with

$$p = \frac{A}{2\epsilon qNe}$$

$r = \frac{B}{2\epsilon qNe}$

If Vb is the built-in voltage of the gate-epilayer junction:

$$Vb = \frac{kT}{q} \left( \ln \frac{NgNe}{ni^2} \right)$$

(3.38)

Than equation (3.37) holds under the following conditions:

- 1) if 0 ≤ Vg ≤ Vch(0,0) -Vb <=> Vch(0,0) ≤ Vch(Vg,Qs) ≤

Vch(Vg,0)

this condition expresses the fact that if charge

'over-fills' the potential well it flows to the

neighboring gates,

- 2) if Vg > Vch(0,0)-Vb <=> Vg+Vb ≤ Vch(Vg,Qs) ≤ Vch(Vg,0) which reflects the fact that the gate-epilayer junction must be reverse-biased.

The maximum signal charge, Qs,max, is obtained in the first case if Vch(Vg,Qs) = Vch(0,0), and in the second case if Vch(Vg,Qs) = Vg+Vb.

3.5 Vertical charge transport

3.5.1 Vertical charge transport I, principles

Junction charge-coupled logic makes use of charge transport through JCCD channels, as well as through junctions induced by surplus charge. Horizontal charge transport, in the JCCD channel, is controlled by the clock voltages through reverse-biased **pn**-junctions.

We consider the combination of two packets of electrons under one gate, when the potential on the receiving gate is raised. In this case the surplus charge, if both wells are filled, is just one packet. This surplus charge can be used for vertical charge transport. Two structures for vertical charge transport are distinguished:

the pnp-transistor, which is formed by the substrate, the epilayer, and the gate, which will become active when the gate voltage is taken above the channel potential and surplus electrons are present

Fig. 3.13 Potential profile, the dashed line representing the curve at maximal filling if the gate potential is above Vch(0,0).

underneath the gate;

ii) the injector structure, which consists of an n diffusion placed in a p-type gate. By forwardbiasing this n p-junction, charge can be injected into the CCD channel, acting as a collector of this vertical npn-transistor. This type of injector has been used successfully in filters and as input structures for multiplexers [3.4],[3.5].

The substrate pnp-transistor opens up the way to vertical charge transport out of the JCCD, charge 'overflow'. We consider the case that the gate voltage is well above Vch(0,0)-Vb, which is the case in logic applications with JCCDs. Figure 3.13 shows the potential profiles, the dashed line representing the curve at maximal 'filling'. If surplus charge is present in this situation it can not spread laterally, but instead it will forward bias the gate epilayer junction. The JCCD structure will act as a pnp-transistor. The gate (emitter) will inject holes into the epilayer. This charge flow will continue until all surplus electrons have been removed.

The behavior of this vertical overflow is strongly related to the JCCD properties, since for vertical charge flow the substrate pnp-transistor is biased by surplus charge transfer through the JCCD. We treat the surplus charge storage first. The processes involved in vertical charge transport and storage of surplus charge is extensively discussed by van der Klauw [3.4].

# 3.5.2 Charge storage II, storage in the pnp-transistor

The amount of signal charge that can be stored in a potential well has been determined in section 3.3.2. All this charge is transportable, if transfer inefficiency is not considered. If we look at charge overflow when one charge packet or several charge packets are transferred into a potential well that can only contain less than the total amount of charge supplied, while the clock voltage is over Vch(0,0)-Vb, two additional charge storage mechanisms can be distinguished.

Under influence of the externally induced field electrons will drift towards the potential well of the receiving gate. After the potential well is filled, surplus electrons will start to decrease the potential barrier at the gate-epilayer junction. In this way putting the junction under forward bias, initiating injection of minority carriers at the junction. Charge flow will continue until all surplus electrons have been removed from the epilayer and the potential difference across the junction is again Vb or untill the surplus charge is 'dumped' in a drain. If a drain is not used, this process will take considerably more time than the common clock periods for JCCDs. We have two additional storage mechanisms:

- i) charge storage associated with the changing depletion layers at the gate and substrate side of the epilayer,

- ii) the storage of electrons to maintain charge neutrality if holes traverse from gate to substrate.

The amount of surplus electrons that can be stored in the changing depletion layers can, for example, easily be estimated using the simple model of section 3.3.2: a forward bias of 300 mV results in a increase in stored charge of 15 %. In real devices the increase in storage capacity is measured to be about 20 % [3.4].

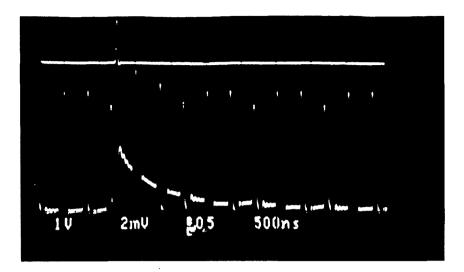

There are two time-constants involved in these storage mechanisms. First, the time-constant  $r_{\rm d}$  indicates the time necessary to decrease the depletion layers until a significant transport current starts. Thereafter, the surplus electron charge that is present in the base region can vanish by injection into the emitter or by recombination with traversing holes. The recombination can be neglected in the present technology [3.4b]. The second time-constant  $\tau_{\rm ct}$  appears in the formula

$$I_{ct} = I_{ct,max} \exp \left(-t/\tau_{ct}\right)$$

(3.39)

in which  $I_{ct}$  is the transport current measured at the collector terminal. This experimental curve expresses the decay of the transport current, and thus of surplus

charge. Figure 3.14 shows a realistic case [3.4c]. It clearly shows that the excess charge may be transferred through the JCCD if a substrate current is tolerated.

The only way to calculate  $\tau_d$  and  $\tau_{ct}$  is by means of a twodimensional and transient program which simultaneously solves Poisson's equation and the Continuity equations for discrete time steps. However for a given device they can be estimated experimentally.

# 3.6 More realistic models

#### 3.6.1 Charge coupling II, more realistic model

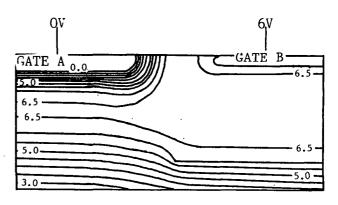

Broadly outlined, the process of charge coupling can be formulated with the JCCD model of section 3.3.2. The physics of the transport of one packet is rather simple: the electrons move towards the point at the highest potential until an equilibrium is established. In equilibrium the channel potential Vch(Vg,Qs) under the transporting gate equals the channel potential under the receiving gate. We consider the case that the clock voltage is 8V.

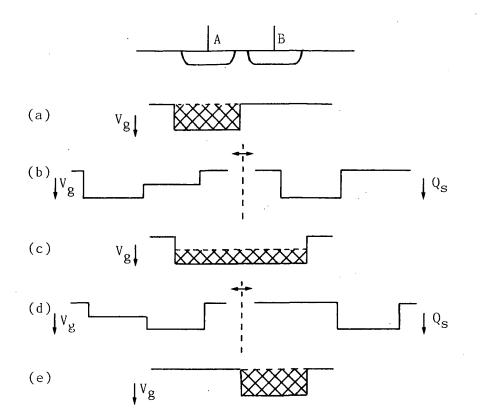

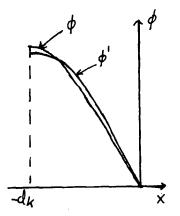

Figure 3.15 shows a schematic representation of the charge transport mechanism. Figure 3.15 a) indicates that the gate voltage on A is maximal, Vg,max(8V), while gate B is grounded. The well under gate A is maximally filled, as suggested by the shaded region. The transport of charge is started as Vch(Vg,max;Qs,max) < Vch(Vg,b;0), where Vg,b indicates a value of the gate voltage on gate B during the rising edge of the clock pulse. The moment that the channel potential under gate A, when filled with Qs, max equals the channel potential Vch(Vg,b;0) under gate B is drawn in Fig 3.15 b). In the model this occurs at Vg,b = 3.8V. In the next step both gates are at 8V. In 3.15 d) we see that if the clock phase on A drops the charge transport is completed if Vch(Vg,a;0) = Vch(Vg,max;Qs,max), thus if Vg,a = 3.8V. In the model used it is assumed that the charge is transported instantaneously.

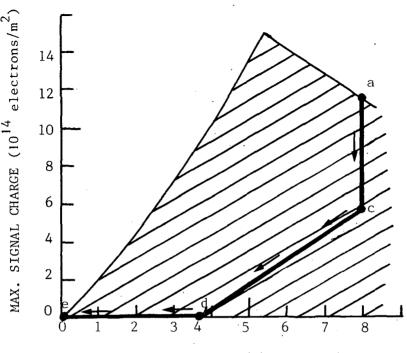

The charge transport can be described by a path in the plane by Qs,max and Vg. The physical region in the  $\rm Q_{smax}$  ,

Fig. 3.15 Schematic representation of the charge transport mechanism. (a) represents a maximally filled potential well at a given voltage on the gate Vg. In (c) the signal charge is spread over the two gates which have the same clock voltage. In the intermediate state (b) it is not possible to indicate the signal charge and the gate voltage together in one picture because the liquid model cannot be used in this case. The left part indicates the distribution of the gate voltages and the right part the distribution of the signal charge. In (e) is the transport of charge completed.

GATE VOLTAGE (V)

Fig. 3.16 The charge transport describes a path in the plane by Osmax and Vg. The physical allowed region in this plane is shaded.

Vg variables is shaded in Fig. 3.16. It is obvious that even in practical devices the charge transport does not follow the charge handling capability curve (Qs,maxcurve), as is suggested by van der Klauw [3.4d].

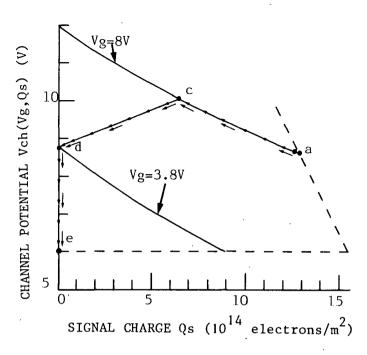

Another way to look at this process is to consider the path that is described in the Vch(Vg,Qs) and Qs variables. Figure 3.17 shows this path. The path from a to e is the "charge line" of the charge under gate A. From a to c Vg is not changed but half the charge has drifted towards gate B. The curve from c to d is obtained using the relations:

37

$$Qs,max(Vg=Vg,max) = Qs_{A} + Qs_{B}$$

(3.40)

and

$$Vch(Qs_A, Vg_A) = Vch(Qs_B, Vg_{max})$$

(3.41)

The "charge line" of the charge under gate B is exactly the reverse path.

We notice that the first half of the charge is transported from the well under A to that under B during the last part of the rising edge of the clock phase on gate B, and that the second half of the charge is transported at the beginning of the voltage drop on gate A.

# 3.6.2 Vertical charge transport II, modeling

As said before, the process of vertical charge transport

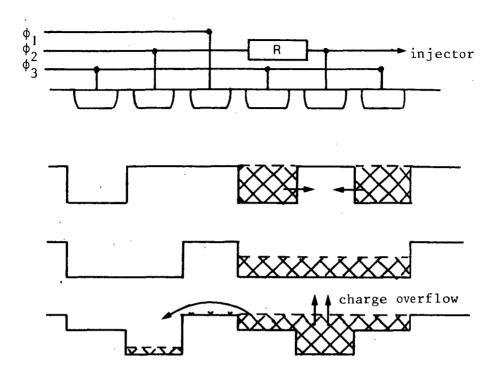

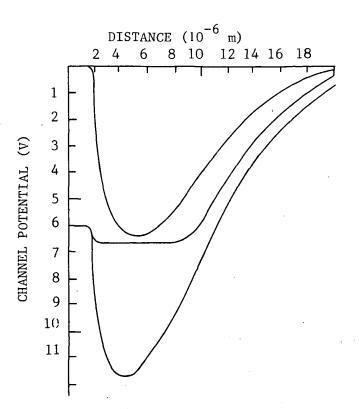

Fig. 3.18 Schematic representation of the combination of two completely filled potential wells. (a) initial situation, (b) charge is divided over the gates at the overlap of the clock pulses. In (c) the situation is drawn in which the well in the middle is filled maximally. The gate voltages in this case is shown in the left part. From this timeslot vertical charge transport through the pnp transistor is initiated.

can only be described by means of a two-dimensional and transient computer program. However, we can formulate qualitatively this transport using the simple model. Figure 3.18 shows the combination of two, completely filled, potential wells. The time slot when all gates are at gate voltage Vg,max is depicted in Fig. 3.18 b). The common well is filled to the 2/3 fraction of Qs,max at the voltage Vg,max. In Fig. 3.19 the "charge line" of gate B is going through the point a' to c'; that of gate A and C from a to c. The transport from the well under A and C to B starts at Vg(B)=3.8V as indicated in Fig. 3.19. The condition that gate B is filled maximally and the channel potential under gate A and C equals the channel potential

Fig. 3.20 Schematic representation of backward charge flow, indicated by the curved arrow.

the value at the beginning of the next puls [3.4e].

The question is, of course, wether backward charge flow rules out the possibility of having logic devices which obtain the function in more than one clock cycle, in other than the present technology. Is backward charge flow an intrinsic mechanism?

Certainly, the possible values for the gate voltage are limited. For example, in the 7  $\mu$ m epi devices the channel potential Vch(0,0) is approximately 9 Volts, while the reach-through between the gates starts at voltages near 10 Volts [3.4f]. And, in the 5  $\mu$ m epi series we have to deal with large parasitic potential wells, that reach potentials of 1-1.5 Volts above Vch(0,0). These conditions probably account for the existence of backward charge flow in the present technology. Unfortunately, these limitations are a consequence of the most favorable technology,

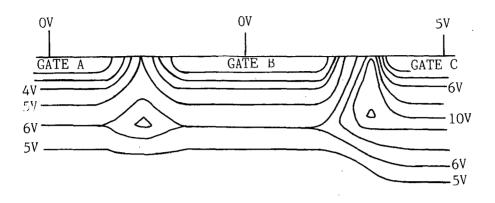

# Fig. 3.21 Schematic representation of the equipotential lines in the simplified JCCD model.

not for digital, but for analogue applications. In principle, the problem should easily be solved, except for very high frequencies.

# 3.7 Parasitic wells, and lateral confinement

To a large extent the quality of a JCCD is determined by the smoothness of the channel potential profile in the transport direction. Distortions in the potential profile act as parasitic wells for electrons.

Figure 3.21 shows a schematic view of the equipotential lines in a JCCD with doping profiles as described in the simple model and with a gate-to-gate distance of 5  $\mu$ m. A large parasitic potential well can be observed between gates A and B. Even, when gate C is clocked to 5 Volts, it will not completely disappear, as can be seen from the equipotential lines around gate C. If we consider another case in which the well underneath gate C is filled with electrons in such a way that Vch(Vg,Qs) equals 10 Volts (of course the gate voltage is in this case above 5 V). then if the clock voltage drops electrons will be trapped in the parasitic well which remains. These trapped electrons will not be transported, thus a large transfer inefficiency can be expected. To eliminate the parasitic potentials between the gates an overall surface implantation--to make it possible to decrease the gate-to-gate distance (increase of reach-through voltage) -- and a phos

Fig. 3.22 The presence of parasitic wells and parasitic channels at the crossings of the lateral gap and the inter-gate gaps.

phorus channel implantation through the mask for the gates—to increase locally the impurity concentration—are performed.

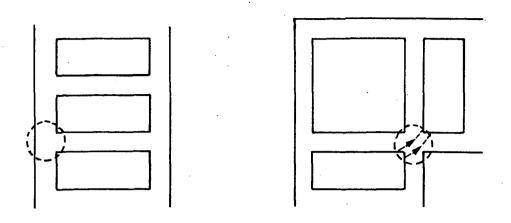

The lateral confinement of JCCD channels, in logic applications, is formed by the same p-type diffusion as used for the gates. The JCCD gates are in this way embedded in a large gate at ground potential. The epilayer underneath will then be fully depleted by the operation of adjacent CCDs.

We consider the situation as depicted schematically in Fig. 3.22. Due to the variation of distance between the ptype gates and the p-type confinement, parasitic potential wells will appear at the crossings of the lateral gap and the the inter-gate gap. If the transport channel makes an angle of 45° a parasitic channel results, which can transport charge during the overlap of the clock phases of the transporting and receiving gate.

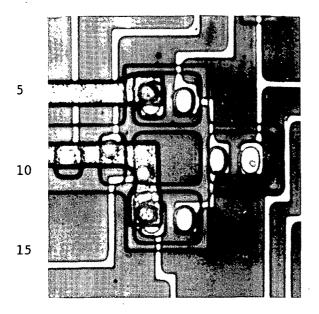

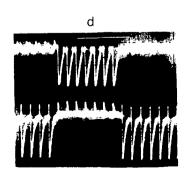

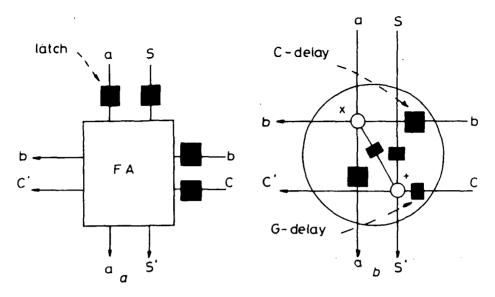

#### 3.9 Current technology of JCCL

The current fabrication process of junction charge-coupled devices, in an adapted standard process for fabricating

44

bipolar circuitry, is outlined.

The ideal JCCD technology meets the following requirements:

- a) Smooth potential distribution: there are no distortions in the potential of the channel when all gates are at ground potential and the epilayer is fully depleted.

- b) No parasitic barriers: the formation of parasitic barriers underneath the gates must be avoided, because they are hardly affected by voltage differences applied between the gates [3.3].

- c) Only small parasitic wells: in a technology using ptype islands for lateral confinement, parasitic wells will be present. Their size should be as small as possible.

- d) High reach-through voltage: the terminal voltage difference between the p-regions at which reach through occurs should be well above Vch(0,0).

- e) Optimal properties of pnp-substrate transistor: the maximum value of the collector transport current of the substrate transistor should be as high as possible, and the decay time as short as possible.

- f) Compatible with good bipolar circuitry: use a technology in which peripheral circuitry, like clock drivers can be integrated.

Of course, if some requirements cannot be simultaneously fulfilled, a compromise must be made. Apart from this, the fabrication process, which has been used, has mainly been developed for analog JCCD applications, and consequently it does not have the best features for digital applications.

The main processing steps in the current fabrication process are listed in table 3.1. The resulting impurity concentration profile through a p-type gate, which was calculated with the technological simulation program SUPREM II [3.8], is shown in Fig. 3.23. -

PROCESS STEP

ł

DETAILS

| p-substrate res          | sistivity                                   | 5080 Ωcm            |

|--------------------------|---------------------------------------------|---------------------|

| n-epitaxial layer res    | sistivity                                   | 8 Ωcm               |

| thi                      | ckness                                      | 5 μm                |

| p-isolatio (DP) she      | et res.                                     | 310,Ω/¤             |

| phosphorus surf. implant | 3x10 cm~2, 30 keV                           |                     |

| annealing                | 1200 °C, 60 min.                            |                     |

| phosphorus channel impla | $8 \times 10^{12} \text{ cm}^{-2}$ , 30 keV |                     |

| annealing                | 1135 °C, 85 min.                            |                     |

| p-base diffusion (SP) sh | neet res.                                   | 195235 Ω/□          |

| gate dep                 | oth                                         | 0.95 µm             |

| emitter p                | 0.4 µm                                      |                     |

| n-emitter diffusion sh   |                                             | 1015 Ω/¤            |

| (source/drain) (S        | 1 μm                                        |                     |

| contact holes mi         | in. dim.                                    | 4x4 μm <sup>2</sup> |

| lst layer (CO)           |                                             |                     |

| interconnection mi       |                                             | 3 µm                |

| lst layer (IN) s         | spacing (min)                               | 3 µm                |

| anodisation              | 2                                           |                     |

| contact holes mi         | n. dim.                                     | 5x5 μm <sup>2</sup> |

| . 2nd layer (CO2)        |                                             |                     |

| interconnect mi          | 12 μm                                       |                     |

| 2nd layer (IN) s         | 8 µm                                        |                     |

| scratch protection (CB)  |                                             |                     |

|                          |                                             |                     |

|                          |                                             |                     |

real JCCD.

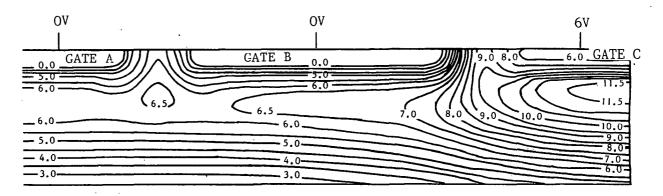

The JCCD structure was analyzed with equipotential plots made with SEMMY2 [3.9]. SEMMY2 is a program for the analysis of two dimensional electrostatic (zero current) semiconductor problems. It solves Poisson's equation using Boltzmann statistics for the charge density. The current densities are assumed to be zero and consequently the quasi-Fermi levels to be constant throughout the device. The terminal voltages are converted into electrical potentials using built-in voltage contributions. The assumption of constant guasi-Fermi levels causes a contradiction if different voltages are applied, like in the JCCD structure in Fig. 3.24. Then in the n-type epilayer different quasi-Fermi levels for the holes, corresponding to the applied voltages on the p-type gates, are defined. This is overcome by assuming that the minority carrier concentration is negligible. The different quasi-Fermi levels for holes in p-gate and p-type substrate are coupled by a curved part in the n-type epilayer. This does not violate the no-current condition because the minority carrier concentration is very small. The potential distribution in

Fig. 3.24 (a) The equipotential lines in the JCCD if no signal charge is present; (b) The equipotential lines in the JCCD if the maximal amount of signal charge is present underneath gate B.

Fig. 3.25 The one-dimensional potential distributions in the JCCD extracted from the figures 3.24 (a),(b).

the presence of charge, Fig. 3.24(b), is obtained using the condition that the voltage over the gate-epilayer junction is just the built-in voltage, and so represents Qs,max.

Figure 3.24(a) shows the three gates of a JCCD cell. Gate A appears partly on the upper left of the plot. Gate C appears partly on the upper right of the plot. Gate A and B, and the substrate are held at ground potential, while the epilayer is fully depleted. The gate voltage on gate C is 6 Volt, which is slightly more than the JCCD channel potential, at Vg=0 and Qs=0, minus the built-in voltage.

A parasitic potential well can be observed between gates A and B. This well does not completely disappear when gate C is clocked to 6 V. Electrons within this well are not transported and thus contribute to the transfer ineffi ciency.

The value of the potential maximum at the silicon-silicon dioxide interface, Vs, between two gates at ground potential is approx. 5.5 V, the value of this potential between gate B and C is approx. 9 V. When a positive voltage is applied to a gate, the potential maximum Vs increases and its position is shifted towards the positive gate. If no avalanche breakdown occurs, the maximum allowable voltage applied to gate C is Vs minus the built-in voltage (reachthrough condition). For higher voltages this junction is forward biased and injection of holes is started. Although experiments show maximum voltages slightly over Vg=Vch(0,0)-Vb, before reach-through between the gates occurs, the plot does not show this effect.

From Fig. 3.24 the potential profile along a line perpendicular to the gate surface through the middle of the gate can be obtained. This is depicted in Fig. 3.25. This figure makes it possible to compare this real JCCD with the simplified model. Clearly, the shape of the curve is qualitatively predicted by the simple model. Because of the phosphorus channel implant the position of the potential maximum is closer to the gate epilayer junction.

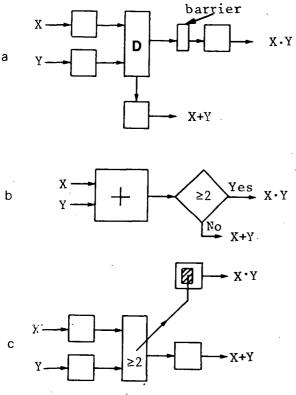

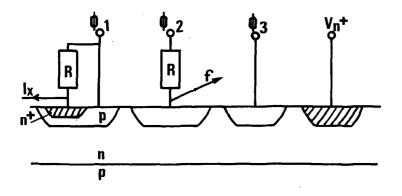

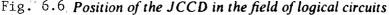

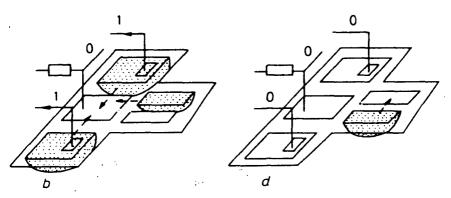

#### 3.9 Operation of basic JCCL structures

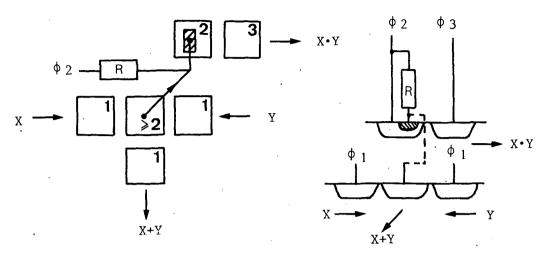

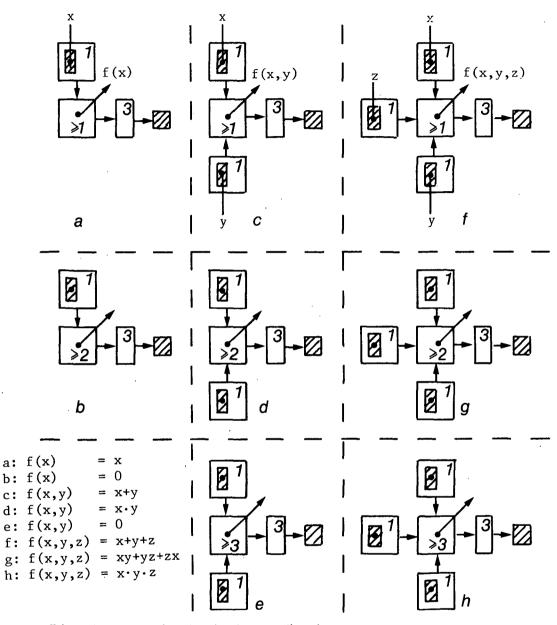

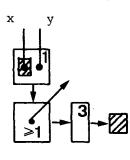

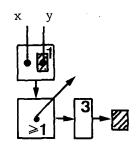

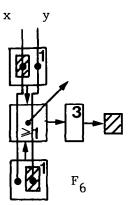

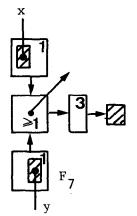

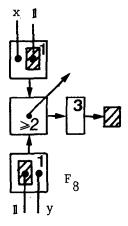

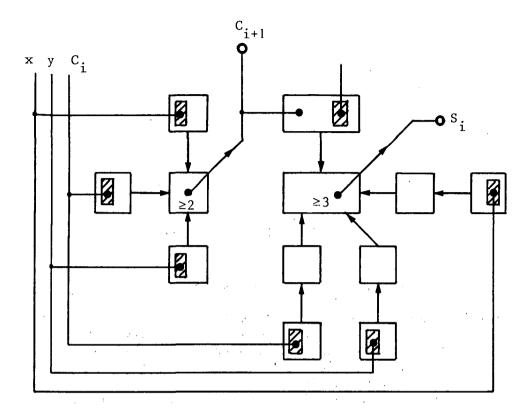

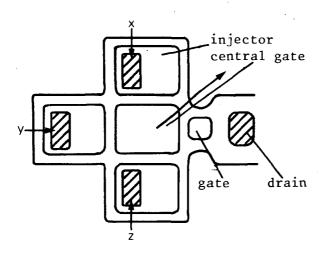

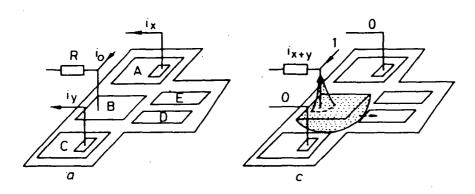

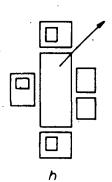

#### 3.9.1 Structure of the AND/OR function

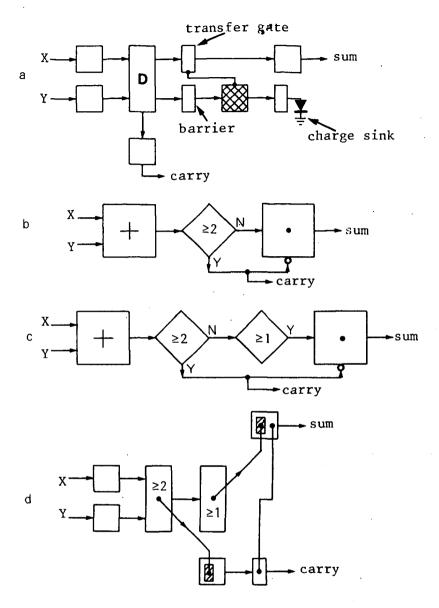

As in all CCD logic, the AND/OR function is the basic configuration. The OR function is the easiest to implement. If two unit charge packets are transferred into an unit area potential well, the resulting charge in this well represents the OR function of the input packets. The normalization of this charge packet can be used to obtain the AND function. In DCCL this normalization is performed laterally by spilling the surplus charge over a potential barrier which is controlled by a DC voltage. In JCCL the normalization is performed vertically through the gate. The AND function explicitly uses the overflow signal that results from bringing together two charge packets in a potential well that can contain only one charge packet. The total overflow current is  $\beta$  times the surplus charge,

Fig. 3.26 (a) Schematic topview of the AND/OR function; (b) Cross-section of the AND/OR function.

$\beta$  is the amplification of the pnp-transistor. The layout and a cross-section of the AND/OR function is given in Figs. 3.26(a) and 3.26(b). The configuration essentially consists of two JCCD channels, one giving the OR of the two inputs and the other giving the AND function. The charge packets X and Y are present in the input/OR channel. The clock phases are indicated in the upper right corners of the gates. The arrow and ' $\geq$ 2' denote an overflow current if two or more charge packets are present. This overflow current is injected in another channel forming the result of the AND function.

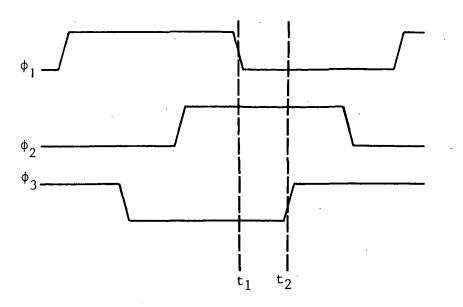

In the logic AND channel, the injector current Iin must result in a full charge packet within the interval bounded by the onset of overflow somewhere during the falling edge of the previous clock phase,  $t_1$ , and its termination somewhere during the rising edge of the following clock phase,  $t_2$ . The clock phase of the injector during this interval is high, Fig. 3.27. illustrates this.

An expression for the value of the resistor R is obtained by van der Klauw [3.4]. The overflow current,  $I_0$ , is taken constant over the interval  $t_2$ - $t_1$ , as can be assumed if  $t_2$  $t_1$  is small compared with the decay time of the pnp-

51

Fig. 3.27 The clock waveforms at charge injection. Charge injection by the injector gate that it driven by  $\phi_2$  is initiated at time  $t_1$  and is terminated at time  $t_2$ .

transport current. The injector structure is seen as a diode parallel to a capacitor C. The diode represents the injector gate in which the base current is negligible, which implies that all the injector current flows into the JCCD channel. The capacitor C represents the injector capacitance including wiring. This capacitor introduces a short delay, typically about 1 ns, in the injection process since it has to be charged to the voltage level at which the diode takes over the current  $I_0$ , if the value of the resistor R is high enough. After the capacitor has been sufficiently charged the current  $I_0$  flows through the injector and the resistor R only. The injector is assumed to follow the ideal relation:

$$I_{in} = I_s \exp(qV_g/kT)$$

(3.46)

in which Is is the saturation current of the injector, and Vg is the applied voltage. The injector current has to create a charge packet Qs,max(Vg) in the remaining time  $\Delta t$ . The required voltage is also the voltage across R and so [3.4]:

$$I_0 = \frac{Q}{\Delta t} + \frac{kT}{qR} \ln \left( \frac{Q}{\Delta t} \cdot \frac{1}{Is} \right)$$

(3.47)

And the minimum value for R equals:

$$R = \frac{kT}{q} \ln \left( \frac{Q}{\Delta t} \cdot \frac{1}{Is} \right) / \left( I_0 - \frac{Q}{\Delta t} \right)$$

(3.48)

At room temperature, the saturation current of an injector gate with a 10x10  $\mu$ m<sup>2</sup> emitter is about 65 fA; using Qmax(7V) = 0.08 pC, I<sub>0</sub> = 0.12 mA (experimental value),  $\Delta$ t = 15 ns (for a device operating at 10 MHz), a minimum resistor value of 4.1 k $\Omega$  is required.

As long as additional capacitive loads from other injectors or wires do not increase the delay too much, it is

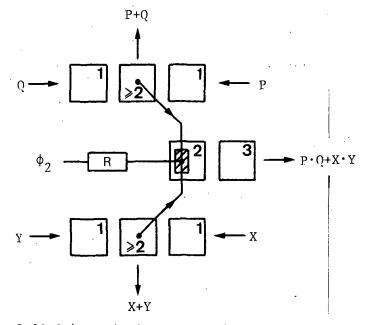

Fig. 3.28 Schematic layout of the function F=P·O+X·Y, using a wired-or operation.

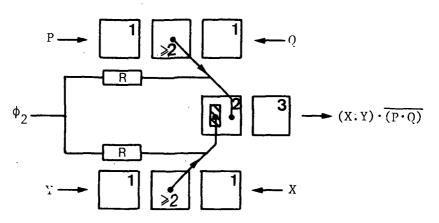

Fig. 3.29 Schematic layout of a complex inverter calculating  $(X \cdot Y) \cdot \overline{(P \cdot Q)}$ .

possible to implement wired-OR functions in JCCL. Figure 3.28 shows an implementation of the function F = PQ + XY using a wired-OR operation [3.4].

# 3.9.2 Balanced injector structure

To obtain a complete description of logic devices we have to define a complementation operator. For this purpose the so-called balanced injector structure is defined.

The balanced injector structure consists of an injector gate to which two overflow structures are connected, one to the emitter of the n+pn-transistor and one to the base of this transistor. If an overflow current is offered to the base, it is converted into a voltage across the resistor and consequently switches off the process of injection if an overflow current is offered to the emitter. The possibility of injecting a charge packet now depends on both overflow currents.

An example of the use of the balanced injector structure is shown in Fig. 3.29. In this case, two identical load resistors R are inserted in the emitter and base connections with the clock. The voltage drops across these resistors, if all inputs are a logical "1". will be identical. The net voltage drop across the injector junction is therefore zero and no charge is injected. The output charge packet represents  $(X.Y).(\overline{P.Q})$ .

#### 3.10 JCCL characteristics

The JCCL characteristics were measured and extensively discussed by van der Klauw [3.4]. In the following these results are summarized.

First the transfer inefficiency is discussed. The physical mechanisms that are responsible for signal charge loss in JCCDs include:

- i) Inadequate time for the carriers to move over the required distance under influence of diffusion or externally induced field,

- ii) potential barrier humps that may exist in the channel potential profile,

- iii) potential wells that are not emptied by the externally induced field,

- iv) the trapping of carriers at bulk states and later release.

If the transfer inefficiency,  $\epsilon$ , is the fraction of the charge that is left behind as a charge packet is transferred from one well to the next, and n is the number of transfers, then for digital applications the transfer inefficiency product, n $\epsilon$ , must be equal to or less than 0.25 if a 50 percent reduction in the noise margin between logic levels is acceptable [3.10]. The transfer inefficiency is different at voltages below and above Vch(0,0)-Vb, because of additional loss of charge due to injection into p-gates, if surplus charge is present. In the present case this loss of charge is less than 0.1%. In a typical JCCL process the  $\epsilon$  is measured to be between  $10^{-2}$

and  $10^{-3}$ . Charge losses that are independent of the amount of charge are usually denoted by  $\delta$ . In the case where no precautions are taken to avoid large parasitic wells at the crossing of the lateral gap and the intergate gap this  $\delta$  can be as large as 15% of the total charge packet if measured after 30 transfers. Power dissipation in dynamic systems increases linearly with the clock frequency as  $P = C V^2 f$ . In JCCL devices, however, the contribution of vertical overflow currents dominates this figure in most cases. A convenient way to characterize power dissipation in JCCL devices is to express the total load of the clock by the equivalent number of unit area gates,  $n_{eq}$ , with equivalent capacitance  $C_{eq}$  which is the average value over the clock voltage swing:

$P = n_{eq} C_{eq} V^2 f = n_{eq} Q_{eq} V f$ (3.49)

$Q_{eq}$  represents the amount of charge that flows through the clock voltage source to the unit area gate, in either direction during a single clock cycle. In C<sub>eo</sub> the capaci--tance to the lateral confinement and to adjacent gates, and the capacitance of an average length of interconnect are included. In the same way the corresponding charges are included in Q<sub>eq</sub>. Although these contributions are constant for a fixed clock voltage swing, the power dissipation is dependent on the presence of a charge packet in the JCCD channel since the charge packet contributes to  $Q_{eq}$ . Values for  $n_{eq}$  and  $Q_{eq}$  are obtained from models of the charge overflow. If we consider a typical logic circuit consisting of 10 gates in which three gates can be used for vertical overflow the n<sub>eq</sub> is estimated to be in the range of 50-100, and the  $Q_{eq}$  in the range of 0.2-0.4 pC.

Two aspects that determine the maximum and minimum operating frequencies of JCCL devices are the typical aspects that are concerned with vertical overflow and some general JCCD characteristics. The minimum operating frequency is determined by the JCCD dark current, which is approximately 12 nA/cm<sup>2</sup> at 300 K. If a filling of 10% of a full packet by this current can be tolerated, then the permissable storage time of a signal is just below one second. This implies a clock frequency of, say, 100 Hz as a hundred JCCD cells are passed from input to output. The use of vertical overflow limits the maximum operating frequency. In the available time for vertical overflow a full charge packet must be created. The limit is at present somewhere between 50 and 100 MHz [3.3,3.4].

đ the performance of logical circuits at clock voltages well The noise margin in JCCL is defined as the maximum amount logic stage while giving the correct output signal. The input-output characteristics for several logic circuits were measured in great detail. Also, the dependences of these characteristics and the clock voltages at several clock frequencies were measured. The conclusion was that the input of of spurious charge that can be tolerated at above the channel potential is acceptable. Chapter 3

÷

# CONFIGURATIONS AND IMPLEMENTATIONS

#### 4.1 Introduction

If a suitable technology is available the possibilities of constructing logic functions with JCCDs are:

- a) Logic functions using only transfers in the charge domain. In this way simple Boolean functions and, say, the carry function can be obtained.

- b) Logic functions using transfers in the charge and current domains. The following classes are distinguished:

i) Boolean logic: in this case the logic functions are based on the conditional operator implication (i.e. if x is true then so is y). The x is said to imply y, written  $x \rightarrow y$ , if the table 4.1 is satisfied (a table of this sort is referred to as a truth table).

ii) Threshold logic: a function  $f(x_1, x_2, ..., xn)$  is a threshold function if a set of numbers  $\{w_1, w_2, ..., wn\}$  (called weights) and a number T (called threshold) exist such that  $f(x_1, x_2, ..., xn) = 1$  if and only if:

ר(x→y) x→y х y 0 0 1 0 0 1 1 0 1 0 0 1 1 1 0 1 The arrow symbol is used in many different contects and so extreme care is needed in deciphering their meaning. So: (4.1)x→y is the same as (-ıx)Vy (4.2)where  $\neg$  is the Boolean complementation operator.

Table 4.1 Truth table of logical implication operator

$$\prod_{i=1}^{n} w_i x_i \ge T$$

$$(4.3)$$

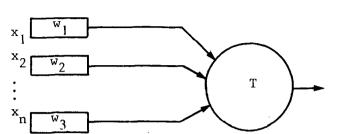

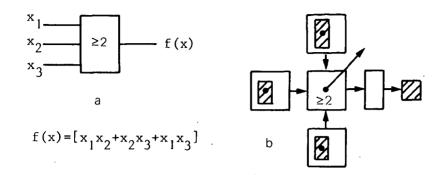

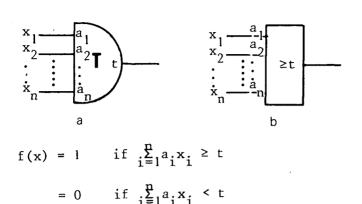

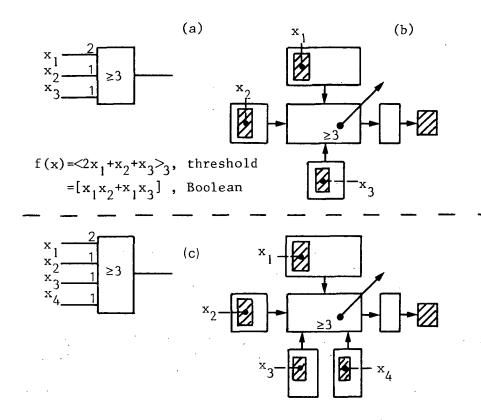

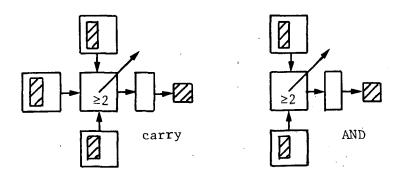

where xi = 0 or 1 and the multiplication and summation are arithmetic (rather than Boolean). In JCCL, a threshold function can be realized using a single device (called a threshold element), as shown in Fig. 4.1.

iii) Other mixtures of horizontal charge transport and overflow currents. The earliest full adders were designed in much of an ad hoc way, using the different possibilities of charge transport. If digital

Fig 4.1 Fepresentation of a threshold element. The numbers w<sub>1</sub>,w<sub>2</sub>...w<sub>n</sub> are weights, T is the threshold.

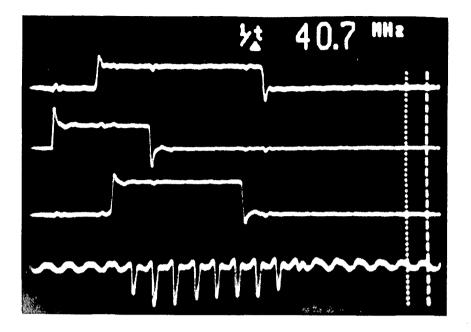

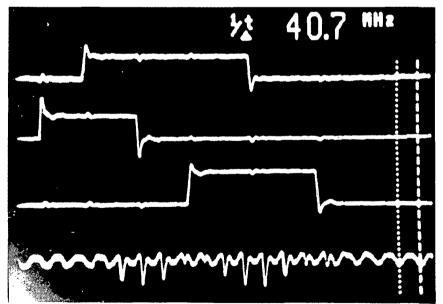

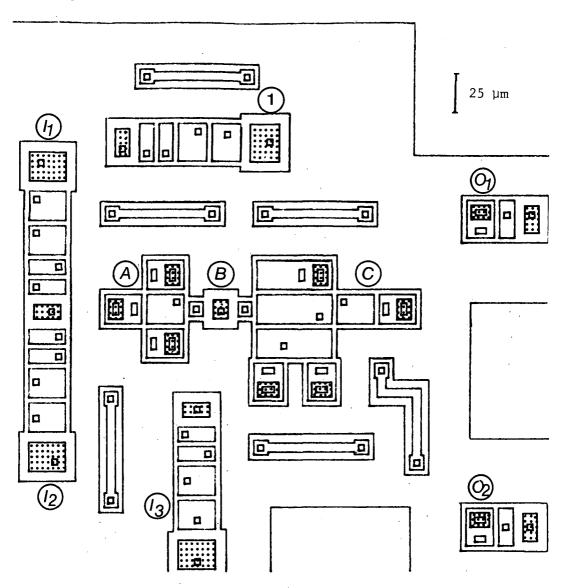

charge-coupled logic (DCCL) is transformed into JCCL the resulting devices belong to this category too.