# A Methodology for Improving gXR5 Speed and Accuracy

Karan Pathak

# A Methodology for Improving gXR5 Speed and Accuracy

**Master Thesis**

by

Karan Pathak

to obtain the degree of Master of Science (MSc) in Embedded Systems (ES) at Delft University of Technology, The Netherlands

Thesis committee:

Chair: Prof. Said Hamdioui, TU Delft

Supervisors: Prof. Georgi Gaydadjiev, TU Delft

Prof. Marina Zapater, HEIG-VD, HES-SO

Dr. Giovanni Ansaloni, EPFL

Prof. David Atienza, EPFL

Prof. Said Hamdioui, TU Delft

External examiner: Prof. Koen Langendoen

Place: Computer Engineering, Faculty of EEMCS, TU Delft.

Project Duration: November, 2022 - August, 2023

Student number: 5479614

An electronic version of this thesis is available at http://repository.tudelft.nl/.

Faculty of Electrical Engineering, Mathematics and Computer Science Engineering

Delft University of Technology, The Netherlands

Dedicated to my parents, Mukesh and Bharti

Copyright © Karan Pathak, 2023 All rights reserved.

#### **Preface**

Computer Architects often walk the tightrope between performance, power and area while designing modern day processors. This daunting task is made even more challenging by short Time-to-Market requirements set by the clients. In light of these challenges, architectural simulators provide a much needed tool for the architects to gauge the impact of their innovations rather quickly. Arguably, use of such simulators is essential in avoiding a product recall due to the processor failing to deliver on performance/power requirements for the intended application. The thesis is in-line with the objective of identifying and addressing the bottlenecks in the RISC-V simulation ecosystem and contribute in the development of RISC-V infrastructure.

The intended objective of an architectural simulator is to capture the trend of the real hardware (i.e., performance improvement due to micro-architectural changes in real hardware should be eloquently captured by the simulator). A good simulator shall have high throughput (less simulation time) and should be easily re-configurable. The re-configurability of the simulator can be as fine as micro-architectural changes or as large as a new ISA being simulated. These attributes of speed and re-configurability come at the cost of accuracy. A high error in performance statistics of the simulator fails to engender confidence among the prospective users. Hence, validating performance of simulators against hardware is essential.

The thesis introduces the need for a full system architectural simulator for RISC-V processors followed by a brief, yet crisp review of the past attempts at making such simulators. The review is from the perspective of existing methodologies for performance validation of the simulators. The work also proposes a new methodology for validating system simulators. Although, the proposed methodology is generic and can be extended to other ISAs (such as ARM, x86, etc.), the target hardware chosen are RISC-V ISA based systems that span both commercially, IP protected processor as well as open-source processors widely adopted by the RISC-V community.

The work concludes by illustrating the future challenges to be addressed to make RISC-V simulation ecosystem vibrant.

### Acknowledgements

"Vasudhaiva Kutumbakam" (The World is one family)

-Maha Upanishad

It's the journey that is worth cherishing and not the end. The experience of carrying out research at a university surrounded by the nature's calmness, the bright sun shining on the lake with blue sky, was surreal. This one-year long journey had ups and downs. The start was not the best, but the end seems to be connecting a lot many dots. The journey was full of excitement, sleep-less nights and happiness (of doing something 'significant'). Looking back, I feel satisfied and proud of what has been achieved.

The work could never have been carried out without the utmost support of my parents, their unconditional love and unfathomable belief in me (more of pride). I would like to thank my supervisors Prof.Georgi Gaydadjiev and Prof.Marina Zapater for showing me the right path. I consider myself lucky that I find the right people at the right moments in life. That also includes Dr.Giovanni Ansaloni for offering advises, providing me an enabling (and positive) environment and always being more than willing to help me. A big thanks to Joshua Klein for getting me started with the project and all off-the record conversations. You have made an impact in my journey for sure!

I would like to offer my sincere thanks to my supervisors **Prof.David Atienza** and **Prof.Said Hamdioui** for giving me the opportunity to work with them. My gratitude towards **Dr.Arjan van Genderen**, for helping me in navigating the treacherous bureaucratic procedures to have this (Inter-University) master thesis. A big thanks to my teacher for Embedded System courses **Prof.Koen Langendoen** and all my teachers who have made an impact in my life. I would also like to thank my cousin **Abhimanyu Kaushal** and his better half **Vaishally Bhardwaj**, for their kind support and bearing with my sense of humor. At last, my friend **Berkin** for all the good moments we had together and the late night "walk the talk" that helped me relieve the stress. My thanks to TU Delft and EPFL for sponsoring my research through **JvE Research Grant** and **SEMP scholarship**.

# Contents

| LI  | st of | Figures | 5          |                        | IX     |

|-----|-------|---------|------------|------------------------|--------|

| Lis | st of | Tables  |            |                        | хi     |

| 1   | Intro | oductio | n          |                        | 1      |

|     | 1.1   | Conte   | xt         |                        | <br>1  |

|     | 1.2   | Motiva  | ation      |                        | <br>3  |

|     | 1.3   | Contri  | butions    |                        | <br>4  |

|     | 1.4   | Thesis  | organis    | ation                  | <br>5  |

| 2   | Lite  | rature  | Review     |                        | 7      |

|     | 2.1   | Archite | ectural Si | mulators               | <br>7  |

|     |       | 2.1.1   | Target n   | netric/Figure of Merit | <br>8  |

|     |       | 2.1.2   | Scope o    | f target               | <br>9  |

|     |       | 2.1.3   | Input to   | Simulators             | <br>9  |

|     |       | 2.1.4   | Driving a  | agent of Simulation    | <br>10 |

|     | 2.2   | Simula  | ation Erro | rs                     | <br>10 |

|     | 2.3   | Valida  | tion Meth  | odologies              | <br>11 |

| 3   | Prel  | iminar  | y Work     |                        | 15     |

|     | 3.1   | gem5    | Extension  | ns for RISC-V: gXR5    | <br>15 |

|     | 3.2   | gXR5    | Models .   |                        | <br>17 |

|     |       | 3.2.1   | CPU Mo     | odel                   | <br>17 |

|     |       |         | 3.2.1.1    | Stage-I: Fetch1        | 17     |

|     |       |         | 3.2.1.2    | Stage-II:Fetch2        | 18     |

|     |       |         | 3.2.1.3    | Stage-III: Decode      | 18     |

|     |       |         | 3.2.1.4    | Stage-IV: Execute      | 19     |

|     |       |         | 3.2.1.5    | Pipeline               | 19     |

|     |       | 3.2.2   | gxR5 - N   | Memory system          | <br>19 |

|     |       |         | 3.2.2.1    | Classical Caches       | 20     |

|     |       |         | 3.2.2.2    | DRAM models            | 22     |

|     |       | 3.2.3   | gXR5-B     | ranch Predictor Models | <br>23 |

|     |       |         | 3.2.3.1    | Local Branch Predictor | 23     |

Contents

|   |     |         | 3.2.3.2     | Tournament Branch Predictor                           | 24   |

|---|-----|---------|-------------|-------------------------------------------------------|------|

|   |     |         | 3.2.3.3     | Bi-Mode Branch Predictor                              | 24   |

|   |     |         | 3.2.3.4     | TAGE Branch Predictor                                 | 24   |

|   |     |         | 3.2.3.5     | Multi-perspective Perceptron Branch Predictor         | 24   |

|   |     |         | 3.2.3.6     | TAGE-Statistical Correlator and Loop Predictor Branch |      |

|   |     |         |             | Predictor                                             | 25   |

|   | 3.3 | Targe   | t Hardwai   | re                                                    | . 25 |

|   |     | 3.3.1   | Sifive Hi   | ighfive Unleashed                                     | . 26 |

|   |     |         | 3.3.1.1     | Micro-architecture                                    | 26   |

|   |     | 3.3.2   | Rocket (    | Chip                                                  | . 28 |

|   |     |         | 3.3.2.1     | Hardware set-up                                       | 29   |

|   |     |         | 3.3.2.2     | Micro-architecture                                    | 31   |

| 4 | Met | hodolo  | gy          |                                                       | 37   |

|   | 4.1 |         |             | tress-ng                                              | . 37 |

|   |     | 4.1.1   |             | stress-ng Benchmarks                                  |      |

|   |     | 4.1.2   |             | cation of Benchmarks                                  |      |

|   | 4.2 | Valida  | iting agair | nst Sifive Unleashed                                  | . 42 |

|   |     | 4.2.1   |             | ٧                                                     |      |

|   |     |         | 4.2.1.1     | Calibrating Arithmetic Functional Units               | 44   |

|   |     |         | 4.2.1.2     | Calibrating Memory Execution Units                    | 45   |

|   |     |         | 4.2.1.3     | Calibrating the Branch Execution Unit                 | 46   |

|   |     |         | 4.2.1.4     | Design Space Exploration of Branch Predictors         | 49   |

|   |     | 4.2.2   | Caches      |                                                       | . 50 |

|   | 4.3 | Valida  | iting agair | nst Rocket System                                     | . 51 |

|   |     | 4.3.1   | MinorCF     | PU:Functional Units Latency                           | . 52 |

|   |     |         | 4.3.1.1     | Estimating Latency of SPFMA unit                      | 54   |

|   |     |         | 4.3.1.2     | Estimating Latency of DPFMA unit                      | 55   |

|   |     |         | 4.3.1.3     | Estimating Latency of FP Division unit                | 57   |

|   |     | 4.3.2   | MinorCF     | PU: Branch Predictor                                  | . 59 |

|   | 4.4 | Concl   | uding rem   | narks                                                 | . 60 |

| 5 | Res | ults an | d Discus    | ssion                                                 | 65   |

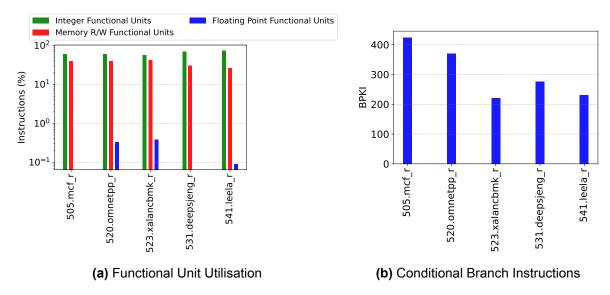

|   | 5.1 | Profili | ng SPEC     | 2017 benchmarks                                       | . 66 |

|   | 5.2 |         |             | lator                                                 |      |

|   |     | 5.2.1   | Target:     | Sifive Unleashed                                      | . 67 |

|   |     |         | 5.2.1.1     | Stress-ng                                             |      |

|   |     |         | 5.2.1.2     | SPEC suite                                            | 69   |

Contents

|    | 5.2.2 Target: Rocket System         5.2.2.1 Stress-ng         5.2.2.2 SPEC suite | 70    |

|----|----------------------------------------------------------------------------------|-------|

| 6  | Conclusion 6.1 Refining the proposed methodology                                 |       |

| Re | eferences                                                                        | 84    |

| Α  | Publications                                                                     | 85    |

| В  | RISC-V ISA selected Instructions                                                 | 95    |

| С  | C Code C.1 ILP Modeling: Parsing and Generating constraint equations             |       |

| D  | Stress-ng Benchmark suite                                                        | 104   |

| Ε  | SPEC2017 Benchmarks                                                              | 106   |

| F  | Full DPS48E1 Slice functionality                                                 | 108   |

| G  | ILP Modeling G.1 Single Precision Fused Multiply and Accumulate                  | . 110 |

| Н  | gXR5 Specifications                                                              | 125   |

#### Nomenclature

**AMAT:** Average Memory Access Time

**BHT:** Branch History Table

**BPKI:** Branch per Kilo Instructions

**BRAM:** Block Random Access Memory

BTB: Branch Target Buffer

CHISEL: Constructing Hardware in a Scala Embedded Language

**DPFMA:** Double Precision Fused Multiply Accumulate

**DSP:** Digital Signal Processing

**FP:** Floating Point

**FPGA:** Field Programmable Gate Array

**FS:** Full System

gXR5: gem5 Extensions for RISC-V

**HBM:** High Bandwidth Memory

**HPC:** Hardware Peformance Counters

**ILP:** Integer Linear Programming

**IMLI:** Inner Most Loop Iterator

IntALU: Integer Arithmetic & Logic Unit

**IPC:** Instruction per cycle

LPDDR: Low Power Double Data Rate

**M-PATH:** Modulo Path history

Nomenclature viii

MAC: Multiply and Add

**MAPE:** Mean Absolute Percentage Error

MBKI: Misses per Kilo Instruction

**MBPKI:** Mispredicted Branches per Kilo Instructions

MIPS/KIPS: Million/Kilo Instructions per second

**MMU:** Memory Management Unit

MP-BP: Multiperspective Perceptron Branch Predictor

**MSHR:** Miss Status Handling Register

**PC:** Program Counter

PPN: Physical Page Number

RAS: Return Address Stack

**RR**: Random Replacement (Cache Policy)

**RTL:** Register-Transfer Level

**SE:** System Emulation

**SPFMA:** Single Precision Fused Multiply Accumulate

TAGE\_SC\_L: TAGE, Statistical Correlator and Loop Predictor

**VPN:** Virtual Page Number

XSDB: Xilinx System Debugger

# List of Figures

| 1.1  | gem5 Simulator Infrastructure                                              | 2  |

|------|----------------------------------------------------------------------------|----|

| 1.2  | Configuring gem5 via python scripts                                        | 4  |

| 1.3  | Comparison of RISC-V architectural simulators                              | 5  |

| 3.1  | High-level view of gXR5 running on host system                             | 16 |

| 3.2  | Simplified model of gXR5 full system simulator [11]                        | 16 |

| 3.3  | Simplified MinorCPU model in gXR5                                          | 18 |

| 3.4  | Comparison of Open-source RISC-V hardware[58]                              | 26 |

| 3.5  | Sifive F5400-C000 Top Level Block Diagram                                  | 27 |

| 3.6  | Chisel to synthesizable verilog translation                                | 29 |

| 3.7  | Rocket system Emulated on FPGA                                             | 30 |

| 3.8  | Booting Linux on rocket system emulated on VC707 FPGA                      | 31 |

| 3.9  | Rocket core: 5 stage pipeline [67]                                         | 32 |

| 3.10 | Rocket Core: Gshare Branch Predictor                                       | 33 |

| 3.11 | Rocket Core: L1-Instruction Cache                                          | 34 |

| 3.12 | Rocket Core: L1-Data Cache                                                 | 35 |

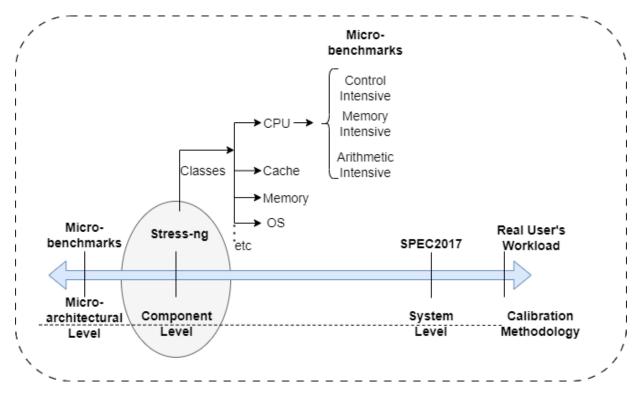

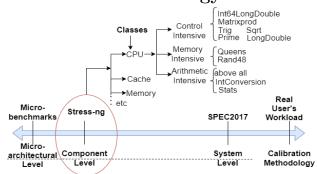

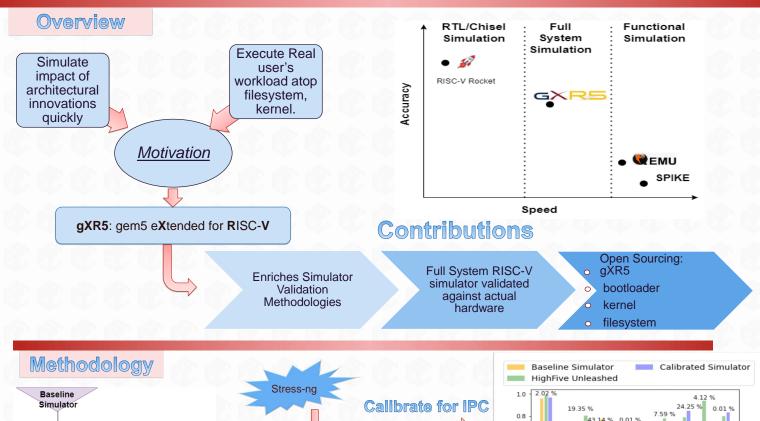

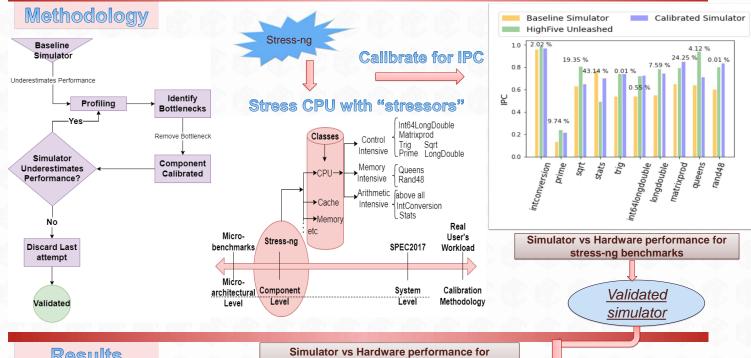

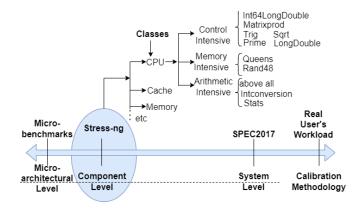

| 4.1  | Methodology: Component Level Calibration                                   | 39 |

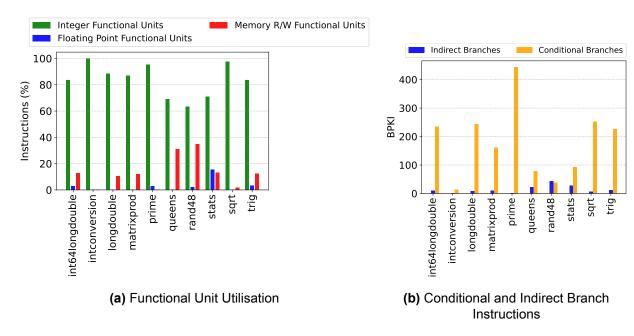

| 4.2  | Profiling stress-ng benchmarks for (a) functional unit utilisation and (b) |    |

|      | branch incidence (using Branches Per Kilo Instruction (BPKI) as the figure |    |

|      | of merit).                                                                 | 40 |

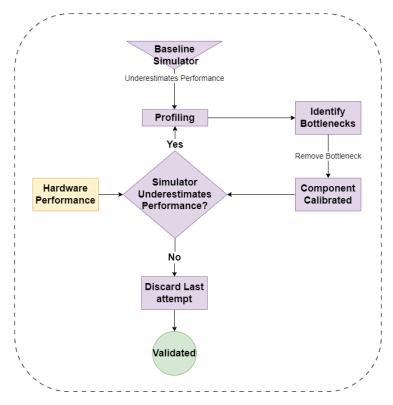

| 4.3  | Calibration strategy                                                       | 43 |

| 4.4  | Comparison of Baseline simulator and hardware running stress-ng bench-     |    |

|      | marks                                                                      | 44 |

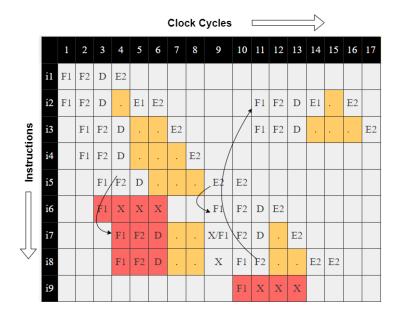

| 4.5  | An example of control related stalls                                       | 47 |

| 4.6  | Sample RISC-V Assembly Code                                                | 48 |

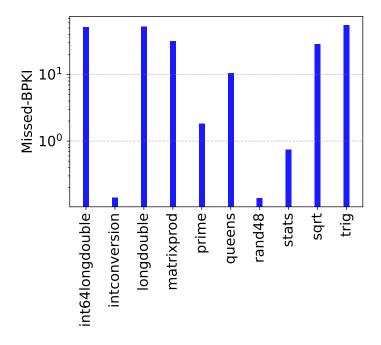

| 4.7  | Missed-BPKI for default tournament branch predictor                        | 48 |

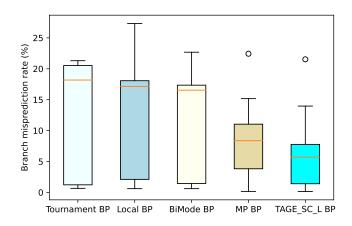

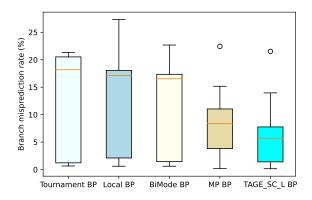

| 4.8  | Misprediction rate for different Branch Predictor                          | 50 |

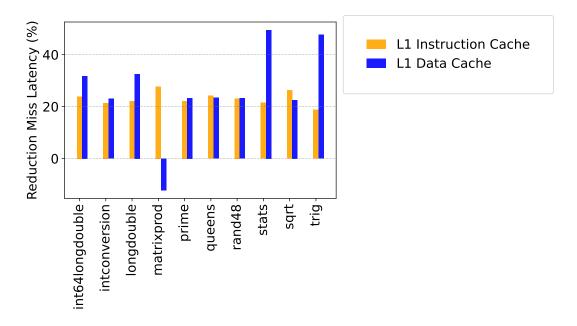

| 4.9  | Reduction in average miss latency for L1 Instruction and Data caches       | 51 |

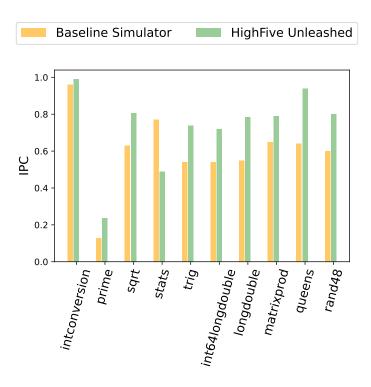

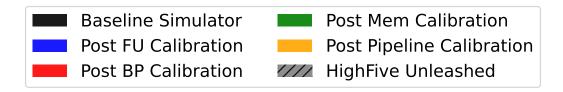

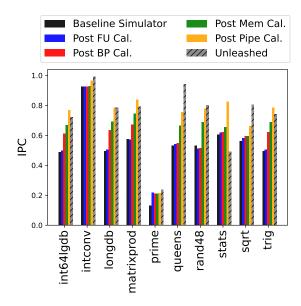

| 4.10 | Simulator Vs. Hardware IPC at different calibration stages                 | 52 |

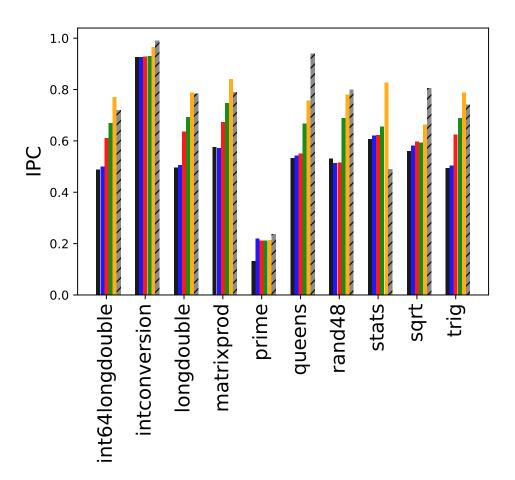

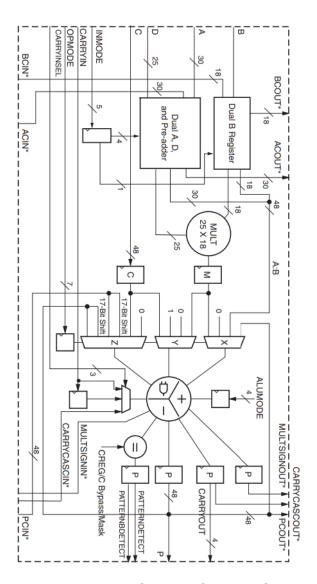

| 4.11 | DSP48E1 slice functionality                                                | 53 |

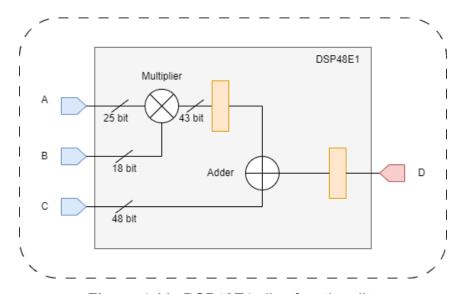

| 4 12 | 3-stage pipeline ports A and B of DPS48E1 slice [68]                       | 54 |

List of Figures x

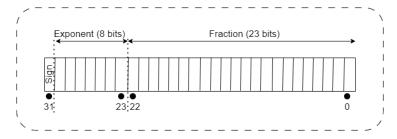

| 4.13 | Single Precision Floating Point Format IEEE- 745                          | 55  |

|------|---------------------------------------------------------------------------|-----|

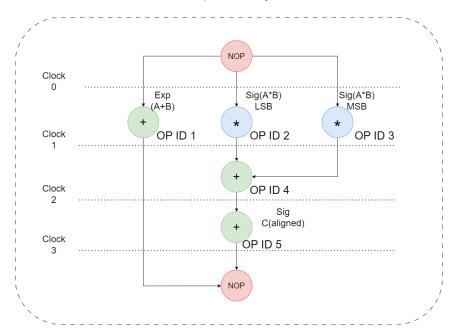

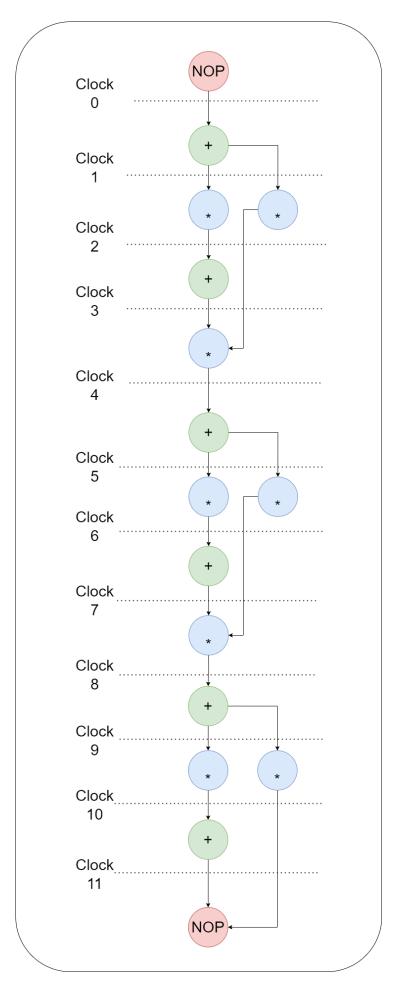

| 4.14 | Sequencing graph for DPFMA Unit                                           | 56  |

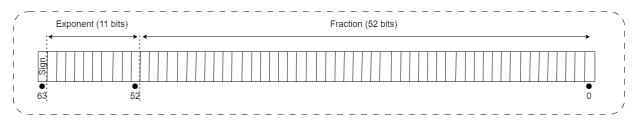

| 4.15 | Double Precision Floating Point Format IEEE- 745                          | 57  |

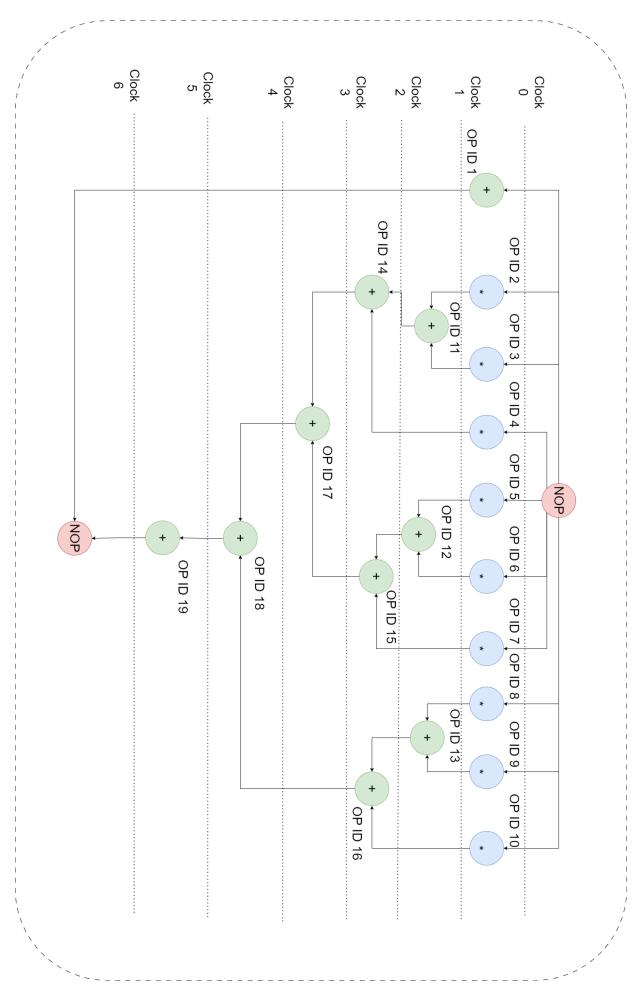

| 4.16 | Sequencing graph for DPFMA Unit                                           | 62  |

| 4.17 | Sequencing graph for FP Division Unit                                     | 63  |

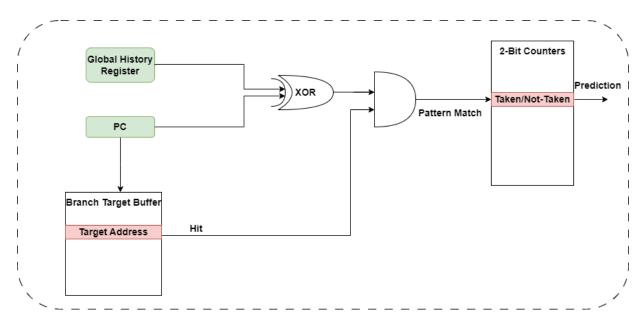

| 4.18 | Gshare Branch Predictor model high level view                             | 64  |

| 5.1  | Profiling SPEC2017 benchmarks for (a) functional unit utilisation and (b) |     |

|      | branch incidence.                                                         | 66  |

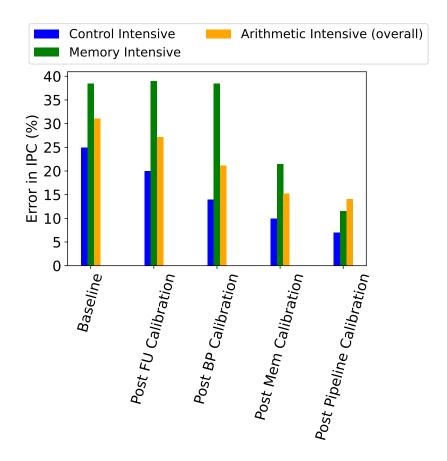

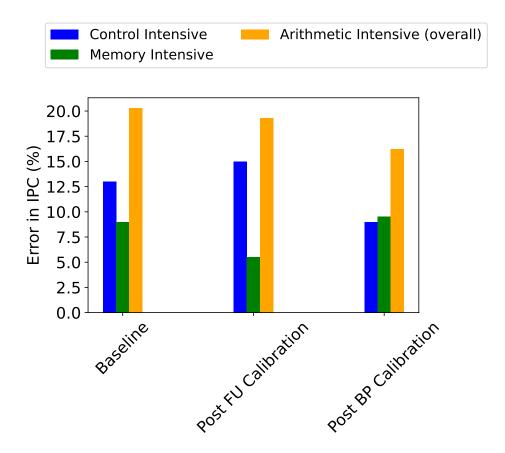

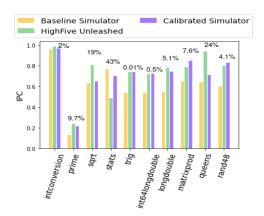

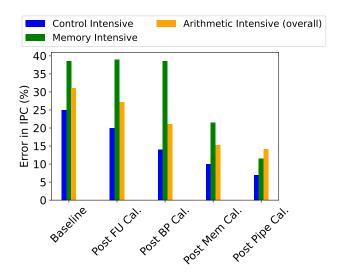

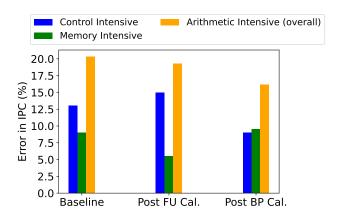

| 5.2  | Error in IPC at different stages of validation against Sifive Unleashed   | 68  |

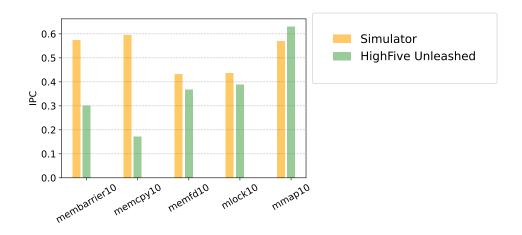

| 5.3  | Sifive Unleashed vs. Simulator IPC for selected memory stressors          | 68  |

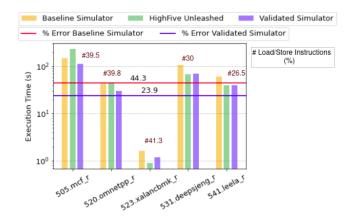

| 5.4  | Sifive Unleashed vs. Simulator IPC for stress-ng benchmarks               | 69  |

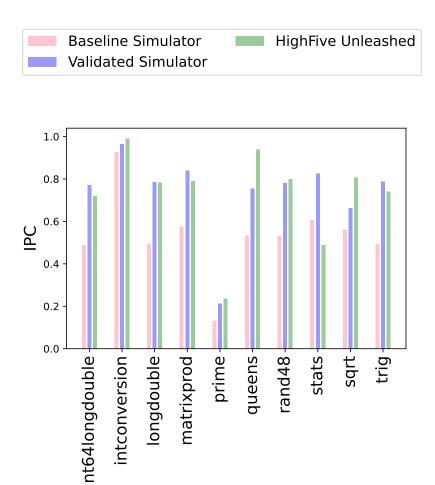

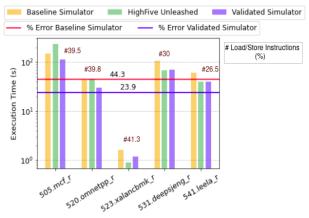

| 5.5  | Sifive Unleashed vs. Simulator IPC for selected SPEC2017 benchmarks       | 70  |

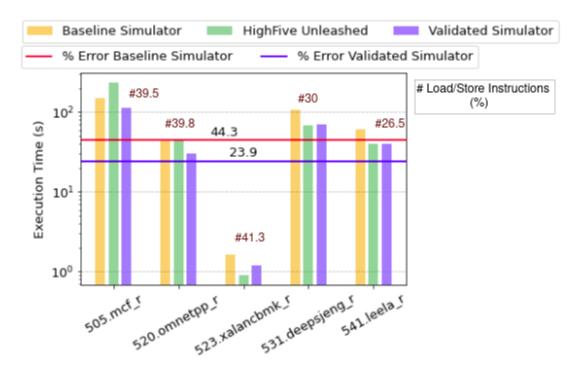

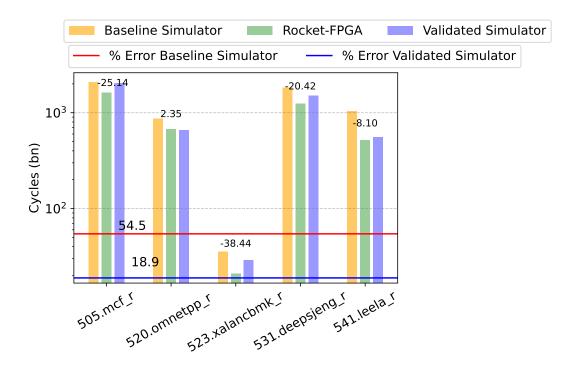

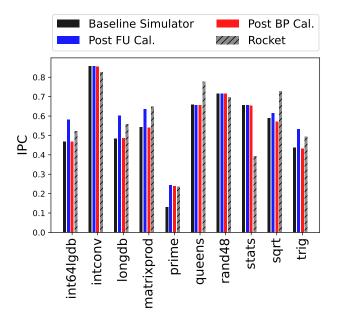

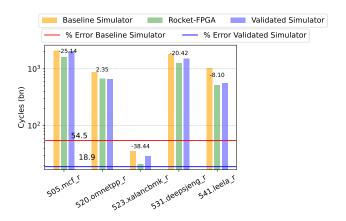

| 5.6  | Rocket System vs. Simulator IPC for stress-ng benchmarks                  | 71  |

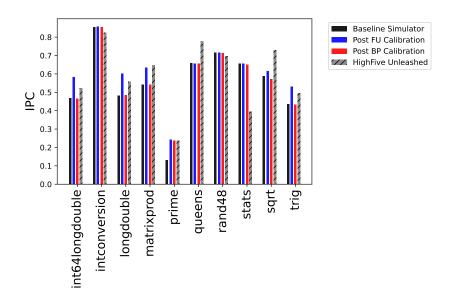

| 5.7  | Error in IPC at different stages of validation against Rocket system      | 72  |

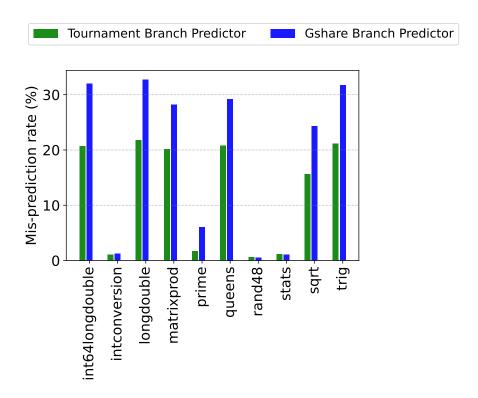

| 5.8  | Branch mis-prediction rates for Tournament and Gshare branch predictor    |     |

|      | for stress-ng benchmarks                                                  | 73  |

| 5.9  | Rocket System vs. Simulator IPC for selected SPEC2017 benchmarks .        | 73  |

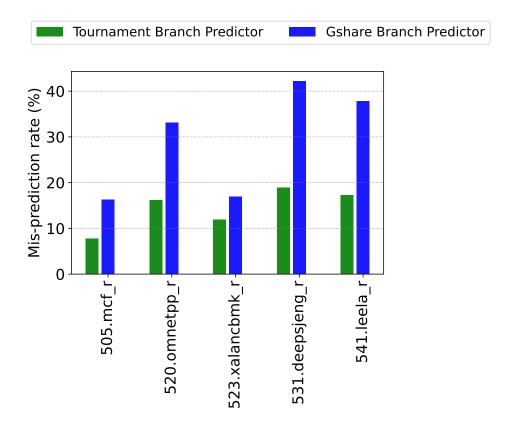

| 5.10 | Branch mis-prediction rates for Tournament and Gshare branch predictor    |     |

|      | models for SPEC2017 applications                                          | 74  |

| F.1  | Xilinx 7 Series DSP48E1 Slice [68]                                        | 108 |

# **List of Tables**

| 2.1 | Past simulator validation efforts with reported errors for benchmarks        | 14  |

|-----|------------------------------------------------------------------------------|-----|

| 3.1 | Technical specifications of simulated models and target hardware             | 36  |

| 4.1 | Instruction Operation Classification by Utilized functional unit             | 39  |

| 4.2 | Instruction Operation Classification by Utilized Memory R/W functional units | 39  |

| 4.3 | Benchmarks Analysis                                                          | 41  |

| 4.4 | Classification of Benchmarks                                                 | 42  |

| 4.5 | Single Precision Fused Multiply and Accumulate (SPFMA) operations'           |     |

|     | dependency                                                                   | 56  |

| 4.6 | Double Precision Fused Multiply and Accumulate (DPFMA) operations'           |     |

|     | dependency                                                                   | 58  |

| 4.7 | Division by Convergence operations and the operation dependency              | 59  |

| B.1 | Selected RISC-V Instructions                                                 | 95  |

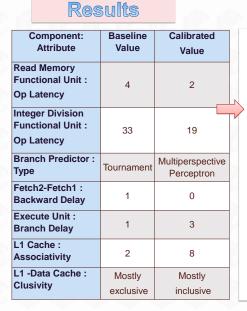

| H.1 | Selected attributes of Baseline and Validated Simulator (against Sifive      |     |

|     | Unleashed                                                                    | 125 |

| H.2 | Selected attributes of Baseline and Validated Simulator (against Rocket      |     |

|     | System)                                                                      | 125 |

1

#### Introduction

#### 1.1. Context

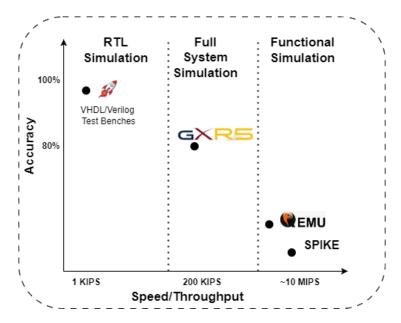

Computer Architects rely on simulators to evaluate the design options before fabricating the real hardware. These simulators can be classified broadly into two categories: Functional and Performance Simulators. The functional simulators (also called ISA-simulators) provide a qualitative test of the simulated hardware. Since these simulators abstract from the micro-architectural details, they have very high simulation speed. Examples of such simulators include Spike [1], QEMU [2], sim-safe model of SimpleScalar [3] etc. On the other hand, the performance simulators (also called Timing-simulators) model the micro-architecture of the hardware, thereby giving cycle-accurate statistics. Often, these simulators are event-driven (as opposed to clock-driven) to make up for the decreased simulation throughput. Examples of such simulators are gem5 [4], GEMS [5], PTLsim [6], etc.

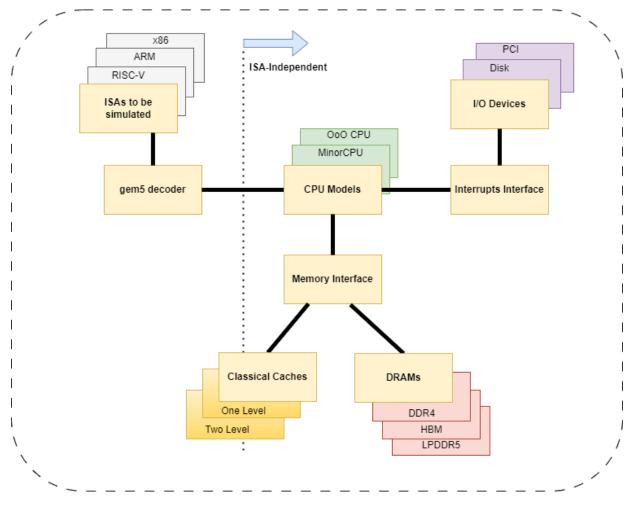

Simulators can also be categorised into Application-specific and Full-system simulators. Application-specific simulators can execute synthetic micro-benchmarks. Poor simulation throughput, usually measured in KIPS/MIPS [7], restricts the use of large applications that require Operating System (and its libraries) to be run on these simulators. RTL simulations fall into this category of simulators. A full system (FS) simulator executes the user space applications atop filesystem and kernel, thereby enabling wider range of applications that can be run on the simulated hardware. gem5 stands as one the strongest open-source simulators that provides full-system capabilities, high reconfigurability as well as compatibility with other modeling tools such as Ramulator (modelling DRAMs) and McPAT (modeling Power). gem5 is a merger of two simulator infrastructures, namely m5[8] and GEMS[5]. It derives the memory system from GEMS and the CPU

1.1. Context 2

models from the m5 network simulator. It supports full system simulation and system emulation by providing tunable system-level architectural models as well as processor micro-architectural models. These models are made ISA-agnostic by remapping ISA specific instructions into "op-classes". The Figure 1.1 depicts the gem5 simulator with gem5 decoder enabling re-use of various models for different ISAs being simulated. The ease of reconfigurability makes gem5 one of the most versatile open source architectural simulator. Moreover, gem5 supports system emulation (SE) mode whereby the system calls are emulated on the host system and the results are delivered to the guest (simulated) system. This guest to host translations improves the simulation throughput but at the same time adversely affects the accuracy (i.e., it increases the disparity between performance statistics compared to the actual hardware) of the simulator.

Figure 1.1: gem5 Simulator Infrastructure

1.2. Motivation 3

#### 1.2. Motivation

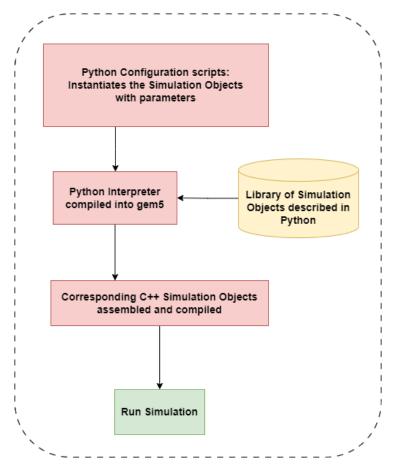

The RISC-V ecosystem has been witnessing tremendous push by the industrial players to accelerate adoption of RISC-V chips in IOT, mobiles, Data centres, automobiles etc [9]. Hardware prototyping is expensive and time taking and so, many industrial players (such as ARM) use full-system simulators to accelerate the chip development process[10]. These simulators have to be representative of the performance of the target hardware. A simulator validated for performance against an actual RISC-V hardware would be a defining contribution towards accelerating RISC-V proliferation. Moreover, the methodology for validating simulators have not been streamlined yet. The "gem5" eXtensions for RISC-V" [11], from now on gXR5, is a full-system simulator built on top of gem5. The objective is to bridge these research/industrial gaps by validating gXR5 against commercially launched Sifive Highfive Unleashed Freedom board [12] as well as RISC-V Rocket core [13] emulated on VC707 FPGA [14]. The Sifive Unleashed is a first Linux capable RISC-V system that is commercially available. The soundness of the proposed methodology to validate is illustrated by validating gXR5 against the IP protected processor, details of whose micro-architecture is not open source. On the other hand, rocket core is one of the most popular open source RISC-V hardware [15]. It has been chosen as a target hardware to prove the fidelity of the proposed methodology. gXR5 builds upon the gem5 simulator and hence, inherits the ISA-agnostic models such as CPUs, Caches, Interconnects, DRAM Controllers etc available in gem5. These behaviour models are written in C++ and made configurable via python bindings (Figure 1.2). Hence, simulation models can be configured via python scripts, facilitating fine changes in micro-architecture rather easily. Moreover, the python configuration scripts accept arguments via the command line to change the attributes of the models.

The conventional RTL test bench simulation of processors has been used in industry given its cycle-accurate performance statistics [16]. Unfortunately, the overhead of RTL design, development, and simulation for architectural exploration is large. In order to see the impact of minor change in the ISA (say adding vector instruction) on user-level benchmarks, extensive changes have to be made in RTL model of the processor core, peripheral systems, test bench, and even the compiler (or cross-compiler). Not to forget, RTL simulation has a very poor simulation throughput compared to This significantly restricts the utility of such RTL simulations for rapid SoC development.

Other simulators such as QEMU [2], SystemC [16], SPIKE [1], and OVPsim [17] have been widely used for simulating systems based on other ISAs (x86 and ARM). The OVPsim does not provide cycle-accurate results unlike gem5. A noteworthy competitor

1.3. Contributions 4

Figure 1.2: Configuring gem5 via python scripts

of gem5 is QEMU, which supports full-system simulation of RISC-V based platforms but only emulates system calls in the host platform, thereby losing greatly on accuracy compared to gem5. On the other hand, SPIKE only simulates the CPU core and caches, thereby offering far inferior functionality compared to gem5. The Figure 1.3 depicts the trade off between accuracy and speed of various simulators. gXR5 brings the best of both worlds, higher speed (compared to RTL Simulations) and higher accuracy (compared to functional simulators).

#### 1.3. Contributions

This work proposes a new methodology that is accurate, fast and generic for validating gXR5. The accuracy is on par with existing full system simulators for x86 and ARM architectures. It is faster in terms of the validation process as it requires far less simulation runs to achieve similar performance accuracy compared to the existing methodologies. Moreover, one does not need to perform extensive hardware characterisation as only

Figure 1.3: Comparison of RISC-V architectural simulators

Instruction and Cycle counts are used. Lastly, the methodology is generic and can be extended to other ISA based processors. The key contributions of the work are as follows:

- a novel "component-level" calibration methodology for fine-tuning and validating full system simulators and demonstrated it's advantages using gXR5 and two real RISC-V implementations;

- 2. the implementation and the validation of the first Gshare branch predictor model compatible with current multi-threaded gem5 CPU models;

- 3. the performance validation of open source gXR5 using selected SPEC CPU2017 benchmarks and real HiFive Unleashed SoC and Rocket Chip emulated on FPGA. We show our simulated results to be within 19-23% as compared to the two hardware targets above.

- 4. removed the need for licensed FPGA emulation to run user's workload on Rocket Chip, making the Rocket Chip ecosystem completely open source.

The thesis makes the system design ecosystem truly open source. It provides validated open source simulator targeting open source hardware based on open source ISA (RISC-V).

#### 1.4. Thesis Organisation

The thesis carries out a brief survey of various architectural simulators and sources of errors in simulators in Chapter 2. It then highlights the existing methodology of

micro-architectural level calibration using Hardware Performance Counters to validate simulators. It gives an estimate of the acceptable error in simulators used in industry/academia. Chapter 3 highlights the background work, including experimental setup, and detailed elaboration of selected gXR5 models. The micro-architecture of the open-source hardware (Rocket chip) is discussed only from the point of view of validation (with the focus on latency of different components). Chapter 4 is the heart of the thesis wherein the methodology is proposed and CPU model of the simulator is calibrated against the two target hardware. Chapter 5 discusses the performance results for selected SPEC2017 benchmark applications.

#### Literature Review

"There are three kinds of lies: lies, damned lies and statistics"

-Mark Twain/Benjamin Disraeli

Architectural simulators provide a platform for the computer architects to evaluate system performance quickly. A good number of these simulators have been built to serve pedagogical needs in universities such as ANT [18], CPU Sim [19], RM [20], etc. The chapter focuses on simulators that find themselves in research and industrial applications. It also provides a concise 'state-of-the-art' in performance validation of simulators. It is expected to give the reader an idea about the standard 'accuracy' of the simulators that are industrially relevant, despite having errors. The sources of errors that are common to all the architectural simulator have also been discussed. Finally, the existing methodologies for carrying out performance validation of simulators (especially full-system gem5 simulations) have been summarised.

#### 2.1. Architectural Simulators

The section restricts itself to simulators capable of simulating the entire computer system. Multicore and multi-processor simulators such as Structural Simulator Toolkit (SST) [21], ZSim [22], Sniper [23] have been kept out of the scope as the focus of the work is on validation of single-core simulation. The objective of the survey is to situate the gem5 full-system simulator among the cohort of the available simulators, highlighting its importance for RISC-V ecosystem.

The various simulators can be classified based on the target metric, the method of

driving the simulation and interaction between simulation models, and complexity of simulation models. The following sections classifies the existing simulators.

#### 2.1.1. Target metric/Figure of Merit

The architectural simulators can fall into following three broader categories depending upon the intended use or target metric.

- Functional Simulators: The Functional Simulators are essential in testing the models to be simulated before timing details are incorporated in the models. These simulators abstract from micro-architectural level details thereby making them computationally lighter. Hence, these are also called ISA-simulators. Examples of functional simulators include SimSafe model of SimpleScalar simulator [3], 'Atomic CPU' model of gem5 simulator [4], etc. Other functional simulators that support RISC-V ISA are Spike [1] and QEMU [2]. Similar functional simulator exist for GPUs, such as Barra [24] which is capable of running CUDA applications on modeled GPGPU.

- Timing/Performance Simulators: The Performance or Timing Simulators model micro-architectural details. Although, the granularity of modeling micro-architectural details vary across these simulators (and even within a simulator, such as different CPU models), the primary objective of these simulators is to serve as a tool to gauge and improve the actual hardware that has been modeled. RTL simulators (with test benches running micro-benchmarks) is one such simulator that models even the gate (or combinational logic) delays, and thus, comes out as the most fine-grained simulator (as far as abstraction in modeling is concerned), gem5 is one of the most prominent performance simulators. gem5 has been the focus of this study and has been described in detail in Section 3.2.3. DRAMSim [25] is a timing simulator for modeline memory system. It models memory controller behaviour for various DRAM protocols such as DDR3, DDR4, LPDDR and HBM. Another memory system simulator, the Ramulator [26] performs similar functionality but it is highly extensible and modular. Both DRAMSim and Ramulator are compatible with gem5 (and can be used with the gem5 CPU models to simulate the entire system). SiNUCA [27] is a simulator developed for modeling non-uniform memory accesses.

- Power/Energy Simulators: The power/energy simulators evaluate energy and power (and area in some cases) of the modeled hardware. McPAT (Multi-core, Power, Area, Timing) simulator [28] can give designers metrics such as energy-delay-area<sup>2</sup> product (EDA<sup>2</sup> P) and energy-delay-area product (EDAP). Though, current versions of McPAT has not been extended for RISC-V ISA. Hence, making

McPAT compatible with gXR5 is a promising research gap to be filled. One of the earliest Architecture-Power simulators include Wattch [29] that provides framework to optimize micro-processors for power consumption. There are a plethora of energy simulators. HotSpot [30] models the die and the package as circuit of resistance/capacitance. These models can then be used at the architectural level for power modeling of SoCs.

#### 2.1.2. Scope of target

The simulators can be classified into Full-system or System Emulation depending upon how the system calls are handled by the simulator.

- 1. Full-System Simulators: A Full-System (fs) simulator is one that is capable of executing user space applications on top of filesystem atop kernel. The kernel resides in the simulated hardware which runs on the host hardware. One of the earliest and arguably most popular of its time was SimOS fs-simulator capable of simulating MIPS CPU with memory virtualisation by MMU [31]. Sunflower [32], PTLsim [6] and MARSS-x86 [33], MARSS-RISCV belong to this category. However, the PTLSim and MARSS-x86 have been designed for simulating 64-bit x86 system.

- 2. System Emulation Simulators: System Emulation simulators are capable of executing applications that require OS services/libraries by bypassing the system calls to the host system. These simulators suffer from high error when system calls make up significant proportion of the workload. QEMU [2] and gem5 system emulation are examples of this type of simulator.

#### 2.1.3. Input to Simulators

The simulators can be classified into trace and executable driven based on the type of application being run.

• Trace driven Simulators: The trace driven simulator uses a pre-compiled set of instructions. The benchmarks are compiled on hardware and the trace of instructions recorded is then fed to the simulator. This leads to the simulator not modeling mis-speculation-logic (eg. branch mis-predictor). Though attempt have been made to incorporate extra logic implementing the mis-speculation path. Since the trace is collected from executing benchmark on another system, the accuracy of the simulator suffers. Shade is one of the earliest trace-driven ISA-simulator. Other such simulator includes MASE [34] which is built on top of Simplescalar toolset [3] and combines timing and performance model for a single core.

2.2. Simulation Errors 10

Executable driven Simulators: Executable driven Simulators simulate the actual

hardware, including the mis-speculations and squashing logic to restore the state

of the system/processor. Hence, they are much more accurate but at the cost of

complex code/logic of models and decreased simulation throughput. Simplescalar

and SESC [35] fall into this category of simulators.

#### 2.1.4. Driving agent of Simulation

Lastly, the simulators can be clock or event driven. These two types have been described below:

- Clock driven Simulators: The clock-driven simulators evaluate the modeled system at every rising/falling edge of the clock. RTL simulation that is highly accurate (and computationally intensive) is an example of clock-driven simulations. The impracticality of such simulators in executing macro benchmarks led to the development of event driven simulators.

- Event driven Simulators: In these type of simulators, the clock runs in background but the simulator evaluates the system only when a event takes place. Often these simulators are modular and hence, the modules interact by way of events. There is an event handler/scheduler that schedules/re-schedules the events sitting in an event queue. Simulating at the events significantly increases the simulation throughput without losing much on accuracy. SESC [35], gem5 [4], SST [21] are examples of event-driven simulator designed for MIPS ISA. The challenge arises in parallelizing the simulations (using OpenMP/MPI) as the events are sequential. However, considerable parallelism can be achieved in (sequential) event-driven simulations by using SimPoint [36] to parallelize the benchmark applications (such as SPEC2017) based on statistical sampling.

#### 2.2. Simulation Errors

The Error in IPC and Execution time of simulator (Vs. target hardware) remains one of the most important metric, apart from the simulation throughput (measured in KIPS/MIPS) [22], [37], [38]. High-level computer architects often rely on execution time of simulators to gauge the run-time of application on real hardware. The hardware designers use IPC to measure improvements in (modeled) hardwares. The simulation throughput reflects the practicality of using simulators and is used to compare simulators. Attempts have been made to streamline the methodologies to reduce this error. Before proceeding to

the following section that describes these methodologies, it is important to discuss and distinguish the source of errors across simulation platforms. The sources of errors in the simulator can be placed into following three categories:

- Abstraction Errors: The developer makes a conscious decision of choosing the level of abstraction while modeling the actual hardware. The higher the abstraction, the less computationally intensive would be the simulations. Abstraction comes at the cost of accuracy. For example, Integer Division (by convergence) Functional unit may be modeled with a fix latency irrespective of the operands being operated upon. The hardware unit will have different latency for division operation depending upon how quickly the denominator converges to value of one.

- Modeling Errors: These errors are due to the designer failing to understand the

functionality of the actual hardware being modeled. For example, the data cache

access may be taking two clock cycles in the actual hardware but has been modeled

with one clock cycle latency.

- Specification Errors: The specification errors are the most challenging of all.

These represent errors due to the lack of knowledge of the architectural details of modeled hardware. A common reason for this is the behind the veil microarchitecture of commercial boards.

Needless to say, all the existing performance validation methodologies target the specification errors while validating for IPC/Execution time. The modeling errors can be resolved by doing the functional validation. The simulators are validated against commercial ARM, x86 ISA compliant boards/processors. The following section discusses these methodologies.

#### 2.3. Validation Methodologies

The earliest methodology for validating architectural simulators can be described as "validation by inspection" [39] wherein multiple simulation runs would lead to enough performance data that could be used to reduce error in the simulator. Gutierrez et al. validate Out-of-order (OoO) CPU model of gem5 against ARM A15 core. They use selected (11 out of 29 applications) SPEC2006 [40] benchmarks with train inputs set to calibrate for gem5 for run time against the actual hardware. Since, they rely on replicating the actual micro-architecture, they reduce the modeling errors significantly. They achieve a mean run time error for selected SPEC applications of 13% and for selected (7 out of 13 applications) PARSEC benchmark, an error of 11% and 12% for single and dual cores respectively. In more recent work Qureshi et al [41] tune and validate performance

of in-order and OoO cores against a real ARM JUNO platform developed by ARM (2015) with a mean absolute error (MAE) below 4 %. The methodology can be at best described as trial and hit method or validation by empirical inspection. Similar work has been done by [42] wherein they modify Out-of-Order (OoO) CPU model of gem5, making the pipeline in-order. This new CPU model is validated against a single and dual core leading to just 8 % run time errors (for single threaded ARM Cortex-A8, single and dual threaded ARM Cortex-A9) for selected (10 out of 13) PARSEC benchmarks [43]. Butko et al [44] calibrated GEMS for the ARM Cortex-A9, bringing the error between 1.39 % and 17.94% for SPLASH-2 [45], ALPBench [46] and STREAM [47] benchmark applications.

Desikan et al. [48] have extended SimpleScalar toolkit for simulating Aplha ISA. They validate this simulator (SimAplha) against alpha 21264 processor of DS-10L Workstation. They propose the methodology of using micro-benchmarks to calibrate individual models of the simulator. These microbenchmarks are divided three categories - "C"(Control), "E" (Execute) and "M" (Memory):

- C micro-benchmarks: These stress the front-end of the processor (Instruction (pre)fetches, line predictors, way predictors, branch predictor, etc.) They are further categorised into control-conditional (C-C), control-recursive(C-R), control-switch (C-S) and complex-control (C-O).

- C-C: Implement simple if-then-else construct.

- C-R: Tests the indirect jumps by having recursive function calls.

- C-S: Implements 10-way switch case statements within a loop.

- C-O: It is a hybrid of C-C and C-S, which loops over if-then-else statements.

- 2. E micro-benchmarks: These test the functional units. They are categorised into:

- Execute-independent: They add the index variable to eight independent, integers stored in registers. They do it 20 times each within a loop.

- Execute-float-independent: They have similar functionality as execute-independent except that they operate on floating point numbers.

- Execute-dependent: They implement (register) dependent chain of operations within a loop.

- 3. M micro-benchmarks: These are categorised into following subcategories:

- Memory-independent: These repeatedly execute the independent loads thereby testing the L1 Data cache bandwidth.

- Memory-dependent: These test the L1 Data cache latency by walking a linked list.

Memory-L2 and memory-memory micro-benchmarks are similar except that the working set size is kept large enough to intentionally cause L1/L2 cache misses.

The IPC error for these benchmarks are brought down from 74% to 2% for the above benchmarks. The validated simulator has less than 20% error for macro-benchmarks derived from SPEC2000 [49] benchmark suite.

Alves et al. [27] follow a similar approach by designing SiNUCA micro-benchmarks [50] for validating the cycle-accurate, trace-driven SiNUCA (Simulator for Non-Uniform Cache Accesses). These micro-benchmarks are classified into four categories, Control benchmarks (comprising of Control Conditional, Control Switch, Control Random and Control Complex), Execute benchmarks, Dependency benchmarks (stressing forward dependency between instructions) and Memory benchmarks. The simulator has been validated against Sandy bridge processor with (geometric) mean error in IPC of 6% for the above micro-benchmarks.

Akram et al.[51] use the SiNUCA micro benchmarks to validate gem5 against Intel (x86) i7-Core (Haswell micro-architecture). Additionally they use Hardware Performance Counters (HPCs) to observe the micro-architectural events in the actual hardware. The Pearson's coefficient [52] is used to find the correlation between error and the micro-architectural event. Pearson's correlation coefficient can capture the strength of correlation as well as the direction of error (positive correlation implies that the simulator is overestimating the performance of micro-benchmarks). They reduce the error in the micro-benchmarks to 6% and also implement a loop predictor in gem5. However, the validated simulator has not been tested by running macro-benchmark suite. Similar work (using HPCs and correlation coefficients) have been carried out for calibrating Out-of-Order (OoO) CPU model in gem5 against ARM Cortex-R8 CPU.

Recently, an attempt has been made to streamline the design of these synthetic benchmarks used to calibrate the simulator models. Huppert et al. [53] have designed micro-benchmarks for calibrating memory hierarchy using simplistic technique of 'Datapinning'. The working set size is made to reside at different memory levels to calibrate access latency using HPCs. Unfortunately, the methodology can not be extended to calibrate other models (especially as complex) as CPU.

Section 4 proposes and implements the new methodology. The methodology reduces the specification errors in simulator by 20% just by calibrating the CPU model. The past attempts for validating simulators have been summarised in the Table 2.1.

| Validated<br>Simulator | Target Hardware                                                                                           | Training Set Error                                   | Test Set Error                                                                                        |

|------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| SimAlpha               | DS-10L worksta-<br>tion (Compaq<br>Alpha 21264 pro-<br>cessor)                                            | Synthetic microbenchmarks IPC Error of less than 2 % | selected mac-<br>robenchmarks<br>derived from<br>SPEC2000 suite<br>IPC Error of 18 [48]<br>%          |

| SiNUCA                 | Sandy bridge processor                                                                                    | Synthetic mi-<br>crobenchmarks<br>IPC Error of 9 %   | SPEC2006 suite<br>having an IPC Error<br>of 19% [27]                                                  |

| gem5                   | ARM Versatile Express TC2 development board                                                               | SPEC and PAR-<br>SEC                                 | SPEC and PAR-<br>SEC Run Time Er-<br>ror of 13 % and 11<br>% [39]                                     |

| gem5                   | Cortex-A53 core of MediaTek Helio X20 SoC                                                                 | Synthetic mi-<br>crobenchmarks                       | SPEC2006 suite<br>IPC Error of 20 %<br>[53]                                                           |

| gem5                   | Arm R8 CPU                                                                                                | Embench workload<br>CPI Error of 13 %                | No macro-<br>benchmarks<br>were run [54]                                                              |

| gem5                   | Intel Core-i7<br>(Haswell Micro-<br>architecture)                                                         | Synthetic micro-<br>benchmarks IPC<br>Error of 6 %   | No macro-<br>benchmarks<br>were run [51]                                                              |

| gem5                   | ARM Cortex-A8<br>(dual core, Snow-<br>ball SDK), ARM<br>Cortex-A9 (single<br>core,BeagleBoard-<br>xM SDK) | PARSEC                                               | Selected PARSEC<br>benchmarks (with<br>simsmall input set),<br>Run time Error of 8<br>% for both [42] |

| GEMS                   | ARM Cortex-A9<br>(Snowball SKY-<br>S9500-ULP-C01)                                                         | SPLASH-2, ALP-<br>Bench, STREAM                      | same as test set,<br>Run time Error of<br>1.39% to 17.94 %<br>[44]                                    |

Table 2.1: Past simulator validation efforts with reported errors for benchmarks.

## **Preliminary Work**

This Chapter delves into the the details of gXR5 models along with the simulation set-up. It gives an overview of the simulator, CPU models, memory system, etc. The micro-architecture of the two target hardware, namely Sifive Highfive Freedom Unleashed board and UC-Berkley's Rocket core has been dealt in detail.

#### 3.1. gem5 Extensions for RISC-V: gXR5

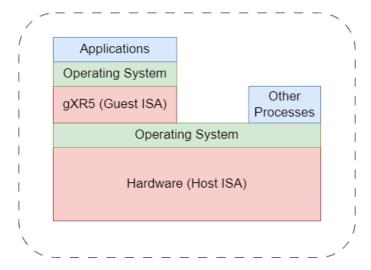

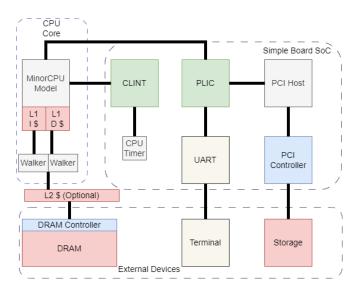

gXR5 is a linux capable full-system simulator for RISC-V ISA based uni-core platforms. It is an event-driven, full-system performance simulator that builds on gem5 and so, it inherits all the models (CPU, caches, DRAM, TLBs, etc.) of gem5. Akin to gem5, it runs on top of the host OS and hardware (usually a different ISA). Figure 3.1 depicts the gXR5 running benchmark applications atop (guest) OS and simulated (guest) hardware, atop (host) OS and (host) hardware.

The simulator comes with a python interpreter that helps configure and instantiate the corresponding C++ models as discussed in Chapter 1. The simulator is run in full system mode by configuring (and connecting) the built-in processor, caches and memory models with the Simple Board components. The built-in UART model is used to interface an external terminal and PCI host model is used to interface the storage to the rest of the system via the the Platform Level Interrupt Controller (PLIC). The PLIC interfaces with the CPU to assign the interrupts to the core whereas the Core Local Interrupt Controller manages the software and timing interrupts of each individual core. Figure 3.2 provides a high level view of the built gXR5-full system simulator. The CPU model used is an in-order MinorCPU model that is interfaced with classical caches and Main memory by buses. Since gXR5 supports SV39 virtualization, the addresses undergo virtual to

Figure 3.1: High-level view of gXR5 running on host system

physical translations via walkers or translation buffers (TLBs) before accessing the L2 cache and main memory. It is important to dive into the implementation details of these C++ models. Hence, the following section describes the micro-architectural details of the CPU,caches and DRAM models.

Figure 3.2: Simplified model of gXR5 full system simulator [11]

#### 3.2. gXR5 Models

The basic building blocks of gXR5 are the Simobjects. A Simobject is a C++ wrapped object that can be configured and interfaced via the python configuration scripts. Almost all objects in gXR5 (such as CPU, caches, TLBs, branch predictor, functional units, etc) inherit from the Simobject. The Simobjects derive from the class Eventmanager which implements functionalities of scheduling/re-scheduling and waking up the events.

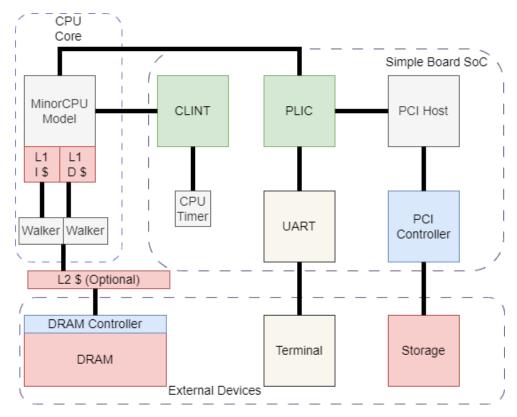

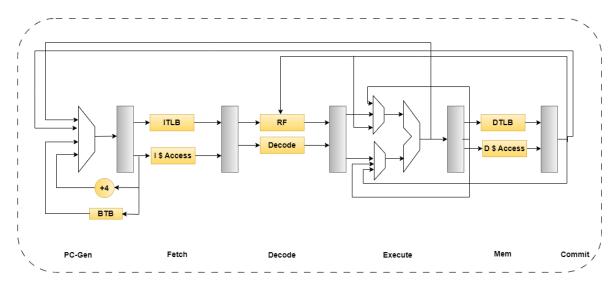

#### 3.2.1. CPU Model

gXR5 comes with four in-built CPU models- Minor (in-order), Out-of-Order (O3), AtomicSimple and TimingSimple CPU models. The AtomicSimple and TimingSimple CPU models are single cycle CPU models (without pipeline). MinorCPU models derive from the BaseCPU model that implements the basic functionalities such as setting up a fetch request, handling pre-execute setup, handling post-execute actions, and advancing the PC to the next instruction. MinorCPU model is an in-order four stage pipelined CPU model with following stages: Fetch1, Fetch2, Decode and Execute. These stages are connected through input buffers that hold the instructions in case of a stall. The instructions traverse through to the next stage of the CPU only when the subsequent stage's input buffer has space to accommodate the instruction. Figure 3.3 depicts Minor CPU model with the four aforementioned stages.

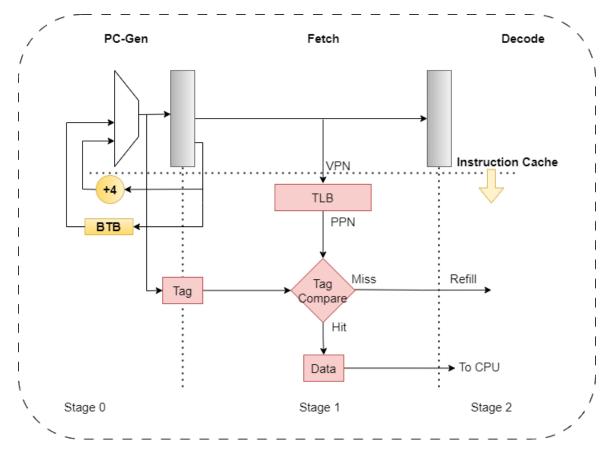

#### Stage-I: Fetch1

The Fetch1 stage fetches the instruction from the L1-instruction cache and passes it onto the Fetch2 stage. Fetch1 unit tags the cache line fetched to enable Fetch2 unit to distinguish between sequential fetches (pc+4) and branched fetches (Target PC). The branched fetches are indicated by "change of stream" signal communicated by Fetch2 (during branch predictions) and Execute stages (during branch mispredictions). Upon receiving the "Change of stream" signal Fetch1 unit starts fetching from the new program counter which is fed by Fetch2 stage (or by Execute stage incase of branch mis-prediction). In case of contention between Fetch2 and Execute stage "change of stream" signal, the Execute stage overrides. The Fetch1 stage comprises of two queues, namely, the Request Queue and the Transfer Queue that keeps track of the requests made to the caches (through the Address Translation Buffer) and responses received, respectively. The instructions are fetched from memory only if it can reserve a space in input buffer to Fetch2 unit, justifying the need to have Request and Transfer Queues.

Figure 3.3: Simplified MinorCPU model in gXR5

#### Stage-II:Fetch2

The Fetch2 stage comprises of a Branch Predictor Unit. There are numerous built-in branch predictor models in gXR5 such as Tournament Bi-mode, Multiperspective Perceptron, TAGE branch predictor, etc. The branch predictor can be chosen and configured into the system via the python configuration script. The Branch predictor either signals "change of stream" (while branch is taken) or feeds the Decode stage with a sequential instructions (while branch is not Taken). Fetch2 stage also performs a sanity check on stream number (tags attached by Fetch1 unit) and discards the instructions having different sequence number from that of predicted sequence number. This way the input buffers are flushed in-case of branch prediction/mis-prediction. The instructions are packed into vectors and sent to the next pipeline stage. The Fetch2 unit updates the Branch Target Buffer (BTB) and Branch History Table (BHT) with the updates received from Decode Unit.

#### Stage-III: Decode

The Decode stage breaks the instructions into micro-ops and packs these into vectors before passing them to the input buffers of the Execute stage.

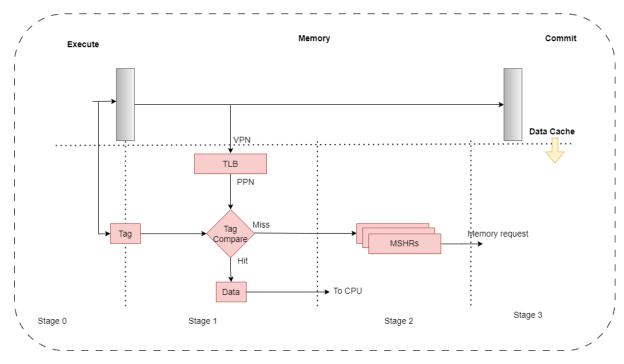

#### Stage-IV: Execute

The input buffer to the Execute stage stores the micro-ops. The Execute stage itself is divided into issue, execute, and commit sub-stages. The micro-ops rest at the issue stage if the corresponding functional unit is pre-occupied. Once the functional unit is available, the micro-op is popped from the issue buffer and executed. The commit stage marks the end of instruction life-cycle. The size of the output vector (number of micro-ops packed) from Decode stage and the size of the input buffer to Execute Unit are intricately related and hence should be tuned simultaneously, otherwise it will lead to stalls. The data fetch requests to memory go through Request and Transfer Queues (similar to Fetch1 Unit). A separate Store buffer ensures that the load and store operations do not hinder each other.

#### **Pipeline**

The pipeline class has an "event" associated with it which is scheduled for every clock tick. The event triggers the method "evaluate()" that calls evaluate method on each stage in reverse order. The order ensures that when the next stage of the cpu stalls, the previous stages too shall stall.

**Listing 3.1:** Pipeline-MinorCPU model

```

void

Pipeline::evaluate()

{

cpu.tick();

execute.evaluate();

decode.evaluate();

fetch2.evaluate();

fetch1.evaluate();

}

```

#### 3.2.2. gxR5 - Memory system

The memory system in gem5 comprises of memory objects (caches, DRAM, etc), ports and packets that are transferred between memory objects. All memory objects inherit from the MemObject class which implements basic functionality such as returning the slave/master port based on name and index. The Memobjects are connected to each other and the CPU via the ports. The ports come in pairs - master and slave. CPU can have more than one master ports interfacing to main memory. Similarly, the DRAM can

have multiple slave ports feeding multiple memory objects (caches) and CPU. The ports have send and receive functions that implement sending and receiving (at the peer side) the packets.

To illustrate the flow of data from CPU to main memory, a request object is created with following attributes :

- 1. Virtual address (in case of virtually addressed caches/memory) or physical address.

- 2. Data size.

- 3. Time stamp of request created.

- 4. Thread ID creating the request.

- 5. The Program Counter creating the request (say, Load/Store instruction)

The request transcends the different memory objects/ports and is broken up in packets. A request travels from sender to the ultimate receiver and back, whereas the packets are exchanged between two objects. The packet encapsulates the following (and not all) important attributes:

- 1. The address: This is derived from the address specified in the request object. Hence, this could be physical or virtual address. In case of a cache miss, this address will be different from the address specified in the request object.

- 2. The Data size: In case of a cache miss, the entire block needs to be fetched from the main memory to the cache. This is the only scenario when the data size of packet would be different from the requester objects data size.

- 3. A pointer to the data being manipulated.

- 4. A flag to indicate success of data transfer and otherwise.

The memory objects and CPU can be connected and configured by python scripts. The following sections give an overview of the built-in memory objects used in gXR5, namely, Classical Caches and DRAM Models.

#### **Classical Caches**

The classical caches are non-blocking caches, i.e., they support hits under a miss by hosting a Miss Status Holding Register (MSHR). The various attributes of caches such as cache and block size, associativity, cache block replacement policy, write back/through policy, etc. are parameterized and can be configured by the corresponding python script for caches. The classical caches come with just MOESI coherence protocol and support snooping for maintaining cache coherency. In gXR5, the snooping requests have been made different from 'normal' memory requests. The snooping requests traverse

horizontally and up the cache-hierarchy whereas the memory requests go down the cache/memory hierarchy. Similarly, the snooping responses travel horizontally and vertically down on the same route as the snooping requests.

The caches are interfaced to the main memory via the coherent bus (cross-bar). The cross-bar has slave ports on the CPU side and master ports on the main memory side. The average memory access time (AMAT) for caches in gXR5 can be mathematically represented by the following equations.

Average Memory Access

$$Time = (Hit\ Time)_{L1} + (Miss\ rate)_{L1} * (Miss\ Penalty)_{L1}$$

(3.1)

where

$$Miss\ penalty_{L1} = (Hit\ Time)_{L2} + (Miss\ rate)_{L2} * (Miss\ Penalty)_{L2}$$

(3.2)

Where, in gXR5

$$Hit\ time = f(response\ latency, data\ latency, tag\ latency)$$

(3.3)

$$Miss\ penalty = f(mshr\ queue\ size, Hit\ time\ of\ lower\ level\ memory)$$

(3.4)

$$Miss\ rate = f(associativity,\ clusivity,\ replacement\ policy)$$

(3.5)

The hit-time, miss penalty and miss rate can be fine-tuned to bring the AMAT (of instruction and data fetches) of simulated memory system closer to the actual memory system.

The miss penalty associated with last level cache (L2) is dependent on the DRAM model (access latency). The precise latency for load/store instruction has been summarised by Wang et al. [54] as follows:

$$Lat_{L1D} = OpLat_{Mem} + Max(TagLat_{L1D}, DataLat_{L1D})$$

(3.6)

The  $OpLat_{Mem}$  represent the latency of the Load/Store Unit (LSU). The tag comparison and the data access happen in parallel and hence, a maximum latency of both is added to the LSU latency to get the hit latency of L1 Data Cache represented as  $Lat_{L1D}$ . Similarly, in case of L1 miss, the total latency comprises of LSU latency, tag look up latency, X-bar latency, access latency of L2 cache and the latency encountered in the return path  $(RespLat_{L1D})$ .

$$Lat_{L2} = OpLat_{Mem} + TagLat_{L1D} + RespLat_{L1D} + MemLat_{L2} + Lat_{Xbar}$$

(3.7)

The following section presents an overview of the DRAM controller models available in

gXR5/gem5.

#### **DRAM** models

gXR5 comes with in-built DDR3, DDR4, Low Power DDR (LPDDR) and High Bandwidth Memory (HBM) models that derive from the class 'DRAMCtrl'. The class 'DRAMCtrl' implements basic functionality associated with DRAMs such as ranks, banks, DRAM packets. It also holds data structures (queues) for tracking read/write requests received by the DRAM. Few of the DDR models available and their peak transfer rates have been summarised below.

- DDR3\_1600\_8x8 with peak transfer rate of 12.8 GBps. The DRAM operates at 1600 MhZ.

- 2. DDR3\_2133\_8x8 with a peak transfer rate of 17.0 GBps. The DRAM operates at 2133 MhZ.

- 3. DDR4\_2400\_16x4 with a peak transfer rate of 19.2 GBps. The DRAM operates at 2400 MhZ.

- 4. DDR4\_2400\_8x8 with a peak transfer rate of 19.2 GBps. The DRAM operates at 2400 MhZ. In comparison to the previous DRAM model, this has 8 banks each 8 bit wide.

- 5. LPDDR2\_S4\_1066\_1x32 with a peak transfer rate of 4.3 GBps.

- 6. HBM\_1000\_4H\_1x64 with a peak transfer rate of 8.0 GBps.

The default scheduling policy implemented by the DRAMCtrl is 'frfcfs' i.e first come first served with row-open hit (first row) being prioritised. The default configuration also uses single bank (group) in a rank with a single channel to the memory.

gXR5 uses the classical caches with one and two level hierarchy along with in-built DDR3 and DDR4 DRAM models. The default configuration of these models are used to replicate the DRAMs used in Sifive Unleashed board and Rocket system emulated on FPGA, leaving calibration of the memory hierarchy as future work.

The focus of work is on calibrating the Minor CPU model. Branch predictors are an indispensable part of modern processor and the biggest source of performance discrepancy for simulators. The following section gives an introduction to the types and micro-architecure of the in-built branch predictor models available in gXR5. The models are described breifly as a design space exploration has to be carried out to choose a model that is closest to the actual branch predictor used in hardware.

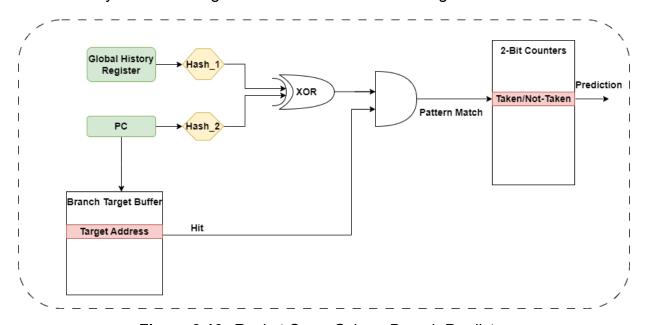

### 3.2.3. gXR5-Branch Predictor Models

The Base class for all branch predictors models in gXR5 is BPredUnit that inherits from the SimObject class. Some of the basic and important public member functions of the 'BPredUnit' class are as follows:

- 1. bool lookup (ThreadID tid, Addr instPC, void \*&bp\_history): The function looks up the branch prediction decision based on PC and branch history. Since the MinorCPU model is multithreaded, each thread (tid) has its own history, PC, prediction, etc. (the 'Context'). The function returns either true or false based on the prediction 'taken' and 'not-taken' respectively.

- 2. void update(ThreadID tid, Addr branchAddr, bool taken, void \*bpHistory, bool squashed, const StaticInstPtr & inst, Addr corrTarget): The function updates the branch history (actual) decision. This could be local or global history depending upon the type of branch predictor implemented. The function also handles 'squashes' incase of branch misprediction.

- 3. *void btbUpdate(ThreadID tid, Addr branchAddr, void \* &bpHistory)*: The function updates the BTB with the target address.

- 4. TheISA::PCState BTBLookup (Addr instPC): The function looks for given PC in the BTB.

- 5. *void uncondBranch(ThreadID tid, Addr pc, void \* &bpHistory)*: The function is called for unconditional branches and updates the bpHistory with (always) 'taken'.

The other member functions implement squashing, logic for valid BTB addresses in case of BTB update, etc. The current gem5 repository (that gXR5 inherits from) has the following MinorCPU compatible branch predictors:

- Local Branch Predictor

- 2. Bi-Mode Branch Predictor

- 3. Tournament Branch Predictor

- 4. TAGE Branch Predictor (with Statistical Correlator and Loop Predictor)

- 5. Multi-perspective Perceptron Branch Predictor

The following section briefly describes these branch predictor models.

#### **Local Branch Predictor**

The Local branch predictor predicts the branch based on local history of each branch. Each branch address is used to index into the local counters which hold the history of a

particular branch. It uses a 2-bit (default) saturating local counter. This is perhaps the most basic branch predictor implemented in gXR5.

#### **Tournament Branch Predictor**

The branch predictor comes with a single global history register that is updated for every take/not taken (actual) outcome of the branch. Along with the global history, the local history is maintained for each branch address (PC) with a configurable saturating counter. There also exists choice counters that decide between global and local history based prediction. The choice counters are indexed by the global history (masked by 'choicehistorymask'). The choice counter is incremented if the outcome matches the global history based prediction and decremented otherwise. A pre-defined threshold is set for choice counters, above which the global history predictor is chosen.

#### **Bi-Mode Branch Predictor**

The Bi-mode predictor comes with two direction predictors and a choice predictor, alike the aforementioned Tournament Predictor. The fundamental differentiating factor being that the direction predictors are indexed by hash of branch address (PC) and global history register.

#### **TAGE Branch Predictor**

The TAGE branch predictor [55] implemented in gXR5/gem5 follows the TAGE branch predictor proposed in Branch Predictor Championship. It comes in two flavors-16KB and 64KB size. The default implementation has 8-component TAGE predictor with seven T-Tables and a basic branch predictor (tag-less, bi-mode indexed by PC). The T-Tables are indexed by hashing the branch address (PC) and the variable (geometric progression series) global history. The prediction by basic predictor is chosen only incase of Tag miss in all the T-Tables. The implementation is based on the predictor proposed at the Branch Predictor Championship.

#### **Multi-perspective Perceptron Branch Predictor**

The Multiperspective Perceptron branch predictor [56] (MP-BP from now on) adds more 'perspectives' beyond the conventional perspectives (discussed above such as local and global history) to make direction predictions. These include the PATH history, Inner-Most Loop Iterator (IMLI), Modulo-PATH history (MPATH), etc. Trained weights are attached to all these perspectives that are used to index the table of counters.

#### TAGE-Statistical Correlator and Loop Predictor Branch Predictor

The TAGE-Statistical Correlator and Loop Predictor branch perdictor (TAGE-SC-L BP [57], from now on) comes with a TAGE branch predictor backed by statistical correlator and loop predictor. The statistical correlator makes up for the poor performance of TAGE predictor in case of branches that have only a small bias towards a direction, but are not strongly correlated with the history path. The TAGE performs poorer than normal PC indexed prediction in such cases. Hence, the statistical correlator decides whether to invert the direction predicted by TAGE predictor or not. The loop predictor simply identifies regular loops with a fixed number of iterations and makes predictions.

The gXR5 ISA-agnostic models discussed above can simulate a wide range of SoCs. The models are aptly abstracted from finer details (like gate and combinational delay) and hence, save a lot of computation power thereby increasing simulation throughput. The functional units too follow the same principle. The functional units are modeled as black boxes with tune-able latency such as 'Issue Latency', 'Operation Latency', etc. The micro-architectural details such as type of adder (say ripple-carry, carry-skip, etc.), multiplier (say higher radix, iterative, etc.) can be implemented by changing the aforementioned latency attributes. Nevertheless, it is important to delve into the micro-architectural details of the target hardware in order to reduce the performance disparity between simulator and actual hardware.

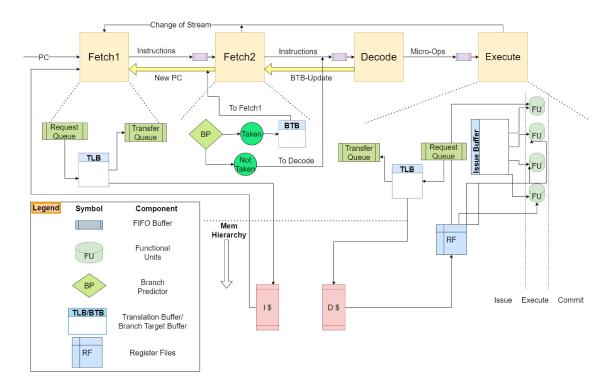

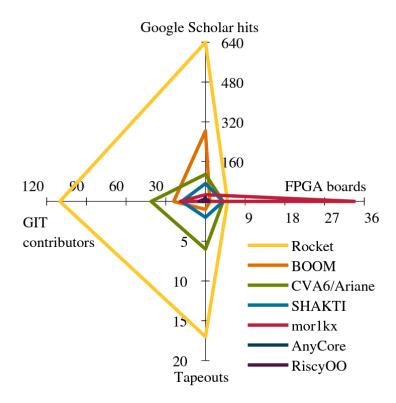

# 3.3. Target Hardware

The following section describes the micro-architecture of the target hardware. gXR5 is being validated against two target hardware, namely, Sifive Highfive Freedom Unleashed[12] and Rocket Chip [13] emulated on VC707 FPGA [14]. The Sifive Unleashed is the first Linux Capable RISC-V board that is commercially available. On the other hand, RISC-V Rocket Chip is one of the most popular open-source processor available. Figure 3.4 uses git activity, citations, tape outs and FPGA emulations of open source hardware including CVA6, BOOM (out-of-order) and Shakti processor. Rocket stands out as the most promising candidate to test the fidelity of the proposed methodolgy.

Figure 3.4: Comparison of Open-source RISC-V hardware[58].

### 3.3.1. Sifive Highfive Unleashed

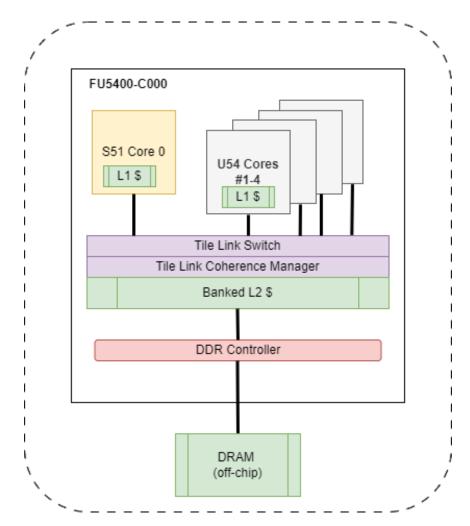

The Sifive Highfive Freedom Unleashed is a quin-core, Linux-capable SoC. It has four FU540-C000 in-order CPU capable of hosting Linux. The other core, the S51, supports Real-Time Operating Systems. The FU540-C000 (also referred to as U54) is a RV64GC core. The figure 3.5 provides a high-level view of the Unleashed board. We base our simulated model and validation effort on single-core workloads executing on the U54 core. The following section divulges the micro-architectural details of U45 core available in the public domain.

#### Micro-architecture

The U54 core has a high performance single-issue 64-bit execution pipeline, sustaining a peak throughput of one instruction per clock cycle. It comes with a dynamic branch prediction scheme and IEEE-754-2008 adherent floating point units, including fused multiply and accumulate units. The core is capable of supporting up to 512 GB of virtual address space using SV39 virtualisation scheme. The core supports the standard RV64GC ISA.

#### Core

Figure 3.5: Sifive F5400-C000 Top Level Block Diagram

The U54 core is a single issue (scalar) 5-stage pipeline in-order core that supports Machine, Supervisor and User privileges modes. The U54 has support for Sv39 virtual memory support with a 39-bit virtual address space, 38-bit physical address space, and a 32-entry Translation Buffer. The U54 cores support data forwarding to overcome data dependencies. The pipeline comprises five stages: instruction fetch, instruction decode and register fetch, execute, data memory access, and register writeback. It has floating point units along with 30-entry branch target buffer (BTB) which caches the target of taken branches, a 256-entry branch history table (BHT), which stores the direction of conditional branches, and a 6-entry return-address stack (RAS). The latency of various functional operations are given below (refer Appendix B for details):

- 1. LW has a two-cycle result latency, assuming a cache hit.

- 2. LH, LHU, LB, and LBU have a three-cycle result latency, assuming a cache hit.

- 3. CSR reads have a three-cycle result latency.

- 4. MUL, MULH, MULHU, and MULHSU have a 5-cycle result latency.

- 5. DIV, DIVU, REM, and REMU have between a 2-cycle and 65-cycle result latency, depending on the operand values.

The limited micro-architectural details of the U54 core poses a challenge for validating gXR5. The actual functional unit type and its latency, branch predictor used and its size, etc. need to modeled or existing models in gXR5 have to be tuned so as to reduce the disparity between simulator and actual hardware.

#### **Memory Hierarchy**

The freedom board comes with 32 KiB 8-way L1 Instruction and Data caches. The shared L2 cache is 2 MiB 16-way associative having coherency fabric. A DDR3/4 controller is used to interface the external DDR3/4/3L DRAM. The maximum data transfer rate from the DRAM used on board is 2400MT/s. The DDR subsystem operates on a separate clock running at 1/4 the DDR data rate.

The IP-protected U54 core with least micro-architectural details made public, provides a perfect avenue to test the soundness of the proposed validation methodology (Chapter 4). To prove the fidelity of the methodology, an open source hardware, namely Rocket core has also been chosen as the target hardware for validation of gXR5. The RISC-V based rocket system enjoys wide popularity among enthusiasts of open source hardware. The following section introduces the rocket system and its emulation on FPGA.

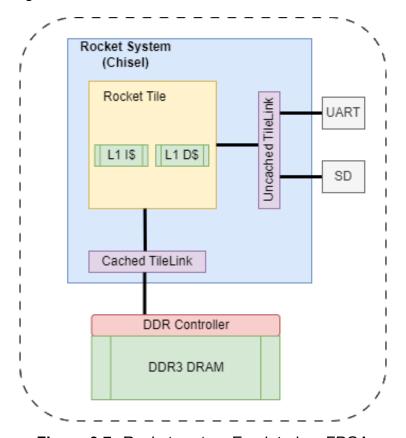

### 3.3.2. Rocket Chip

Rocket core is a 5-stage in-order scalar processor core developed at UC Berkeley and currently supported by SiFive. It implements the RV64G ISA and comes with Memory Management Unit (MMU) that supports page-based virtual memory and non-blocking data cache. Rocket also supports the RISC-V machine, supervisor, and user privilege levels.

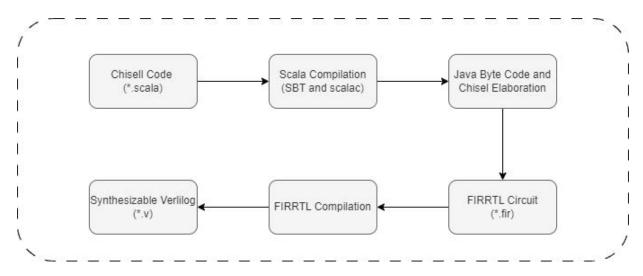

The rocket core [13] along with L1 Cache is called a 'tile'. The source code of the rocket tile is written in chisel (Constructing Hardware in a Scala Embedded Language [59]) that can be translated into verilog. It is high level abstraction language to describe hardware that makes configuring rocket with different components effortless. For example, the chisel libraries come with various types of adders implemented (ripple carrry, carry skip, etc.) that can be included in rocket core. Though this comes at the cost of less control over micro-architecture. Rocket makes use of UC Berkeley's Chisel implementations of floating-point units [60].

The performance validation is done for a single rocket core emulated on Xilinx VC707 Virtex Evaluation Kit. The software stack used is U-boot, OpenSBI and the Linux 5.7 kernel. The following sections describe the hardware set-up and the rocket core architecture in detail. The optimized micro-architecture post synthesis on FPGA is discussed in Chapter 4. The discussion in this chapter has been restricted aspects of core that do not change with synthesis optimisation strategies.

#### Hardware set-up

The Chisel source code for Rocket Tile can be converted to synthesizable verilog targeting FPGA and ASIC [13]. The repository also provides source files to build C++ emulator and verilog files for RTL simulation. The VCS-synopsys tool [61] can be used to carry out RTL simulations with cross-compiled micro-benchmarks (available as part of 'tests' in RISC-V toolchain [62]). Open source Verilator [63] (verilog to C++) can also be used to simulate rocket core. However, the emulator provides insufficient details (such as cycle-accurate) on latency of different functional units. The various steps in translating chisel to synthesize-able verilog is given in Figure 3.6. The Chisel build dependencies include SBT and Mill. The Chisel source code is compiled to give intermediary FIRRTL files. The FIRRTL files are circuit level hardware description code that is compiled to emit verilog files for synthesizing on FPGA.

Figure 3.6: Chisel to synthesizable verilog translation

The rocket core can be configured to use two level cache heirarchy (for multi-core system) with coherency protocols. The emulated system uses one level cache (Instruction and Data) as depicted in figure 3.7. The caches are interfaced to the main memory via Tilelink. The DDR DRAM used is vivado's IP for DDR3 DRAM model. The UART is open source verilog [64] file used to interface with the system terminal. The rocket repository

provides package with definitions for generating JTAG bus interfaces. The repository also provides RTL packages using diplomacy to generate bus implementations of AMBA protocols, including AXI4, AHB-lite, and APB.

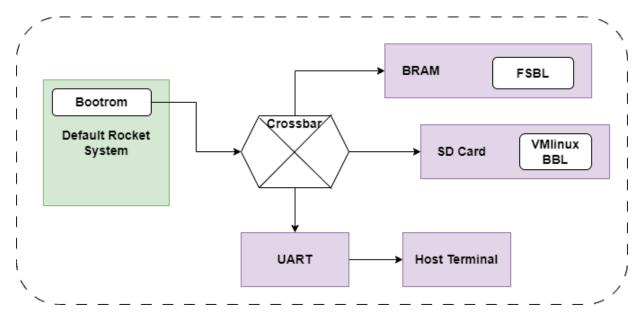

Figure 3.7: Rocket system Emulated on FPGA

Once the system is synthesised (using Vivado HLS [65]) and bitstream (and memory configuration file) uploaded on FPGA, a baremetal program is run on the emulated core using Xilinx System Debugger (XSDB) [66]. The Xilinx System Debugger uses Xilinx hw\_server as the underlying debug engine. It can be used to put the cross-compiled elf file on to the HART (Hardware Thread). It provides the functionality of suspending the HARTs, repointing the Program Counter to the cross-compiled elf and executing the elf file. It also provides a mechanism to observe the contents of the register (including PC, SP, etc) change with the time. The bare metal program (.elf) helps in setting the jumpers, switches and matching the baudrate of terminal receiving the data from UART (FGPA). The bare metal program can be replaced by the actual bootloader, thereby confirming that the system has been successfully emulated. Further, QEMU can be used to debug and check the first stage bootloader by packing the firmware with next stage bootloader.