# ENMOS: Energy Module for Self-Sustainable Wearable Sensors

Ву

# Anirudh Kumar Parag

in partial fulfilment of the requirements for the degree of

Master of Science in Electrical Engineering

at the Delft University of Technology, to be defended publicly on 27th August 2019

Supervisor: Prof. Dr. Ir. Wouter A. Serdijn

Thesis committee: Prof. Dr. Patrick J. French,

Dr. Ir. Qinwen Fan, Ing. Alessandro Urso,

Ing. Alessandro Urso, TU Delft

Dr. André Mansano TU Delft

Nowi Energy B.V.

TU Delft

TU Delft

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

# **Preface**

असंयतात्मना योगो दुष्प्राप इति मे मति: | वश्यात्मना तु यतता शक्योऽवाप्तुमुपायत: ||

asanyatātmanā yogo duṣhprāpa iti me matiḥ vaśhyātmanā tu yatatā śhakyo 'vāptum upāyataḥ

This is the essence of the journey I have been through here at the Bioelectronics group and the TU Delft as well. This Sanskrit shlok (song) from the epic Bhagavad-Gita (an Indian historical sacred scripture), in essence means, in order to achieve perfection in one's trade or practise, one should strive earnestly for an unabridged mind, having a singular focus towards his/her yog or resolve.

Anirudh Kumar Parag Delft, August 2019

# **Contents**

| Α  | bstract                                                           | 8    |

|----|-------------------------------------------------------------------|------|

| A  | cknowledgements                                                   | 9    |

| 1. | Introduction                                                      | .10  |

|    | 1.1. Energy Harvesting: A Walk through the Clock                  | .11  |

|    | 1.2. Case Scenario: Tele-Monitoring                               | .12  |

|    | 1.4. Power Conversion: The Supply Gap                             | .21  |

|    | 1.5. DC-DC Boost Conversion: Fundamentally Speaking               | . 22 |

|    | 1.6. The Research Challenge: 2005-2019?                           | . 25 |

|    | 1.7. Scope: Research Output Expectations                          | . 26 |

| 2  | Architecture                                                      | .27  |

|    | 2.1. Start-up Technique Trends                                    | . 27 |

|    | 2.2. Start-up Architectures                                       | . 28 |

|    | 2.3. Proposal: Decoupling the Problems                            | .31  |

|    | 2.4. Conceiving the Start-Up                                      | . 33 |

|    | 2.5. Architecture Proposal                                        | . 36 |

| 3. | System Level Design                                               | .38  |

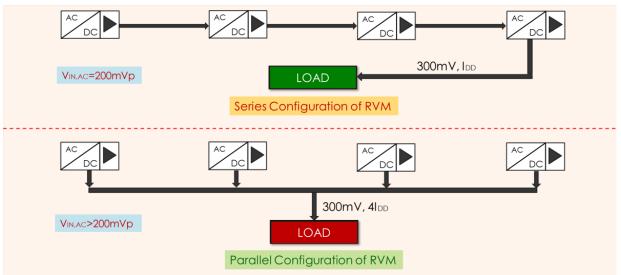

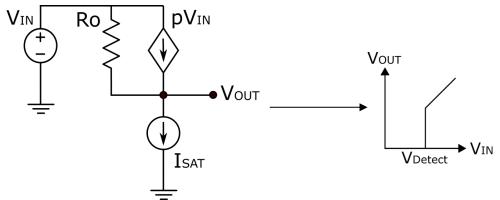

|    | 3.1. RVM: Rectifier-cum-Voltage Multiplier                        | . 38 |

|    | 3.2. Self-Reconfigurable Rectifier-cum-Voltage Multiplier (SRRVM) | . 46 |

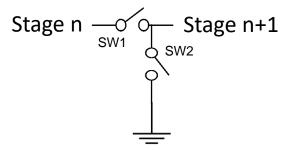

|    | 3.3. Decoupling Stages                                            | . 47 |

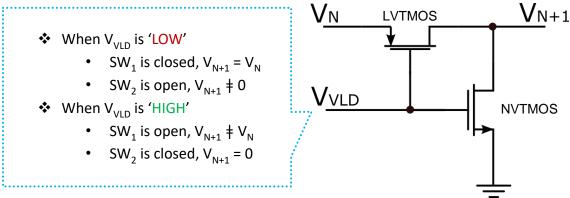

|    | 3.4. Voltage Level Detector (VLD)                                 | . 48 |

|    | 3.5. Timing Generator                                             | . 49 |

|    | 3.6. Bootstrap Feedback                                           | .51  |

|    | 3.7. System Level Design: Proposal                                | . 52 |

| 4. | Circuit Level Synthesis                                           | .54  |

|    | 4.1. Boost Converter: A Non-Ideal Perspective                     | . 55 |

|    | 4.2. RVM (Rectifier-cum-Voltage Multiplier) Design                | .61  |

|    | 4.3. VLD (Voltage Level Detector) Design                          | . 65 |

|    | 4.4. Design for Self-Reconfigurability                            | . 68 |

|    | 4.5. CSRO (Current Starved Ring Oscillator)                       | .77  |

|    | 4.6. Integrated Cold Start-up Architecture                        | . 80 |

|    | 4.7. Cold Start-up Architecture Powered Boost Converter           | . 83 |

|    | 4.8. Bootstrap Feedback Architecture                              | . 85 |

|    | 4.9. Bootstrap VLD                                                | . 86 |

|    | 4.10. Bootstrap CSRO                                              | 87   |

| 4.11. Current Limiter Biasing Circuit                           | 88  |

|-----------------------------------------------------------------|-----|

| 4.12. Entire Bootstrap Feedback: Current-Limited CSRO (CL-CSRO) | 90  |

| 4.13. Power Module Load Connection                              | 92  |

| 4.14. Complete Energy Module                                    | 94  |

| 5. Conclusion                                                   | 105 |

| 6. Research Contributions & Future Work                         | 107 |

| 7. Bibliography                                                 | 110 |

| Appendix A: Energy Harvesters                                   | 114 |

| Appendix B: Cold Start-ups                                      | 117 |

# **Abstract**

Biomedical devices aimed at monitoring a patient's health have been investigated into for quite over a century now, presenting ground-breaking solutions that are now capable of potentially detecting almost all forms of known diseases and their possible symptoms. However, for most of these technological marvels, diagnosis comes at a cost. One of the costs being unavailability of such technologies everywhere a patient can roam around, while another being the bulkiness of such technologies that in turn renders it to be unavailable everywhere. A widely inquired into solution, for about a couple of decades now, focuses on bringing these devices closer to the patient than the other way round. A vision called tele-monitoring, that essentially is observing a patient's health through the employment of unobtrusive body-wearable biomedical devices. However, for such a futuristic vision to be a reality, the electronics aspect of these devices need to be designed quite deftly. For a patient would not want to be disturbed, every now and then, to recharge the device or to buy it all over again whenever its battery runs out. To address these practical issues, researchers have looked into energy sources on or around the body that could potentially power up such devices without the need for any external interferences, rendering it self-sustainable.

To this extent, the difference in temperature a human body has with its ambiance is quite a lucrative source of free and constant energy, which if harvested, could make the entire system self-sustainable. Thermoelectric energy harvesting for body wearable applications, thus, presents a promising prospective for designing battery-less sensors that could, theoretically speaking, facilitate this autonomy of operation for almost forever. Still, one major complication remains. A human body can only provide a temperature difference of about 0.45 K - 2 K with respect to its ambiance, which limits the thermoelectric element's output voltage to 25 mV - 50 mV. How would the sensor, then, be started-up from a completely depleted state, say, when it is used for the very first time or if the energy source intermittently falls short of providing the required energy, and the system shuts down?

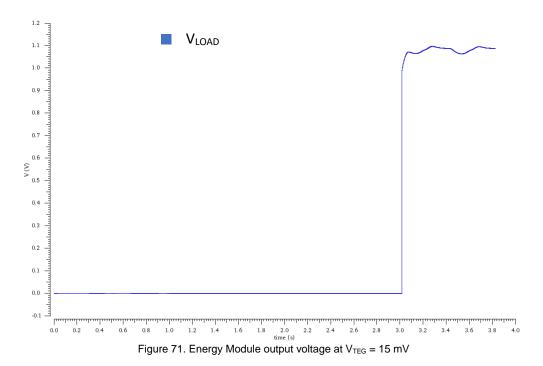

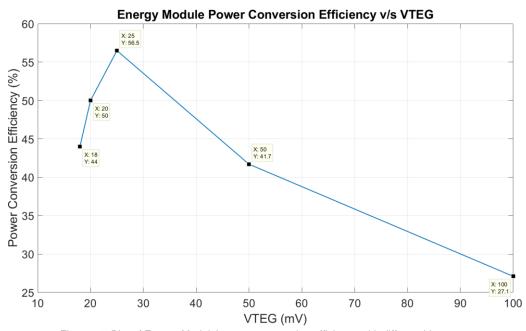

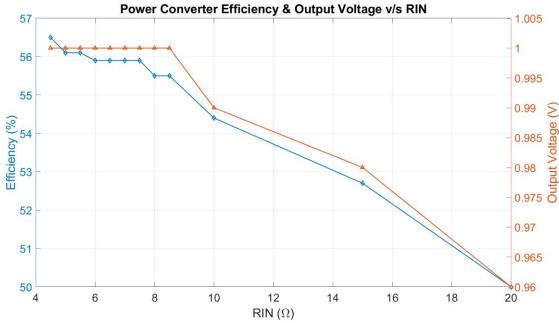

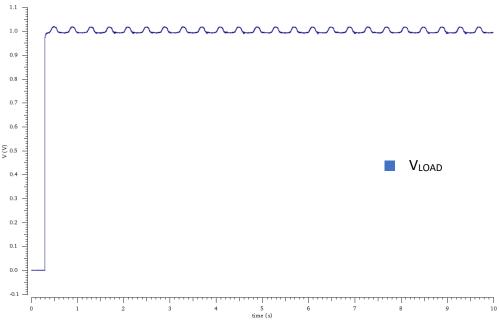

Hence, this work focuses on addressing the fundamental limitation on the minimum cold start-up voltage that could be harvested from a thermoelectric element (TEG). For ultra-low DC voltages, the challenge translates to generating a timed-signal to amplify it up to a value that could be used to drive, say, a boost converter which can then start-up the entire energy module. Contemporary works have, thus, strived to accomplish this using a charge-pump-based or a transformer-based approach, which in turn imposes a limit on the minimum TEG voltage that can be harvested. The solution this work proposes is to decouple the Cold Start-up system from the TEG altogether and instead, use a piezoelectric element (PEH). This element being capable of producing a well-timed (AC) signal for free, based on human body vibrations, can potentially drive a boost converter. To this end, an IC is designed that can utilize the voltage from the PEH, amplifying it up to generate a well-controlled signal that could operate the boost converter. At the heart of this IC, is a self-reconfigurable charge pump that arranges its stages in different boosting ratios (without any complex logic or DSP) based on the input voltage, to allow for a maximum harvested power. The proposed self-reconfigurable architecture can potentially lead the charge pump to be load-variationresistant. It achieves this by providing an almost constant voltage while increasing the power for higher load demands, at the same time maintaining a constant efficiency. Thus, the fully on-chip implementation in TSMC 0.18 um CMOS, can cold start-up the system from 25 mV of thermoelectric voltage to deliver an output voltage of 1 V at 56.5 % converter efficiency, consuming only 240.5 pW of dynamic power (simulation). The minimum Cold Start-up voltage and dynamic power were found to be 18 mV (ΔT = 0.1 K) and 231.6 pW respectively, to supply 1 V at 44 % converter efficiency. Moreover, in order to prove that the fundamental limitation on the Cold Start-up voltage has been addressed successfully, the IC was also simulated to check whether it can further be lowered. In this case, by providing a piezoelectric excitation voltage 73.3 mV<sub>RMS</sub> higher, the Cold Start-up voltage was found to be reduced to 15 mV to supply a constant 1 V at the load. It was also found that increasing the inductor value in this case, can also allow the energy module to support even lower Cold Start-up voltages.

# Acknowledgements

In here, I would like to express my gratitude to all the people who have played an important part in this thesis as well as my life over the course of time this thesis progressed.

First and foremost, I am grateful to my guru, Prof. Wouter A. Serdijn, who accepted my idea with great enthusiasm and have been a constant pillar of motivation to me in all the difficulties I have faced during this work. Scolding me at the right times and steering the course of my endeavour in the right direction each time I faltered, without ever telling me a single straightforward answer, this charismatic guy has inspired me to one day follow in the path he has so guided me upon (and possibly one day surpass him as well). From teaching me how to look at a problem from a more fundamental perspective to literally spoon feeding me with the concepts of designing a circuit from a system-oriented point of view, he has essentially raised me in the past one year on the 18<sup>th</sup> floor to be capable of undertaking any kind of quest in the field of analog IC design. It would not be an overstatement to say whenever I look at him, I learn something new (and that happens every time!). But this also holds in personal life as well, observing him start-up the monthly movie nights, the monthly evening drinks and perform in the BELCA Band, one cannot help but learn how can a person live up to everybody's expectations and yet do well in everything.

My PhD guides, Alessandro Urso and Samprajani Rout, are the backbone for the successful completion of this work. Being a consistent support and an always-available guides, these two people have literally picked me up whenever I fell, and dragged me out whenever I sunk too deep into a problem, where even I thought of myself to be beyond rescue. If this thesis is received well, these are the guys to cheer! From helping me to look at the situation from a system level (Sampi) to a more technical level (Alessandro) to cheering me up every time I discovered something new or concluded that the discovery cannot be proven (happened a lot of times), with equal excitement and willingness to help, I can say I have come a long way into approaching problems and innovating concepts, maturely. Thank you for reviewing my work in all the time-crunch submissions I presented to you and providing me with such insightful feedback.

And now comes the awesome Bioelectronics group. Whatever happens you can always count on these guys for help, be it the presentations, technical details of circuits, intricate details of career or just fun. This is a one big family and these guys have got it all covered. Stimulating discussions about life-&-circuits with Gustavo, Kambiz, Can, Vivo, Ronaldo, Auro, Tim, Koen, Tasos and Marc (forgive me if I forgot someone) have really helped me a lot and cheered me up throughout this journey. Thank you Marion for all the administrative support, specially booking the room for my defense!

I would also like to express my regards to my parents for supporting me all throughout this journey and encouraging me every time I take on a new challenge. Usually for a person from India coming from a completely non-engineering background, it gets a bit difficult to communicate with his family about the unexplored endeavours he wishes to take in life, but not for me and not to these guys. My parents are way too cool for such considerations, exuberantly backing me up in whatever kind of unknowns I plan to explore. Here, I would also like to thank my little brother for taking care of my parents in my absence and assuring me all the time 'All is well!'.

Lastly, I would like to thank the ME House and all the people there for being like brothers to me. Every single person there - Padalia, Rautmare, Kahndelwal, Saparia, Nagarkar, Abhairaj, Khusro, Das, Yadav, Venky, Ramesh, Manchanda and all the other guys – Thanks a ton for being there!

Credits for the picture on the cover page goes to Smit Saparia's photography.

If there is one thing that this journey and TU Delft has taught me here, then that would be humility, something I could have never understood had I not come here. I am heartily grateful that I was selected to do my Master's at TU Delft.

।। हे शिव शम्भो ।।

Let's begin ...

# 1 Introduction

Energy harvesting has evolved into a field where it now finds applicability in driving the world's energy needs from the level of a large-scale community to within an individual person's context, constituting that community. Also referred to as energy scavenging, on a fundamental note, it means extracting energy from the ambient environment, that, along with an untapped potential is virtually inexhaustive. Literature suggests various phenomenon to exercise the transduction of this energy from the form it is available in to the form it can be utilized, to perform specific activities or just stored. While such phenomenon might stir interest and entice a researcher into exploring them, it may be of essence to identify a particular application, before one gets too clogged up in unnecessary nitty-gritty details.

Over the past couple of decades, in the domain of tele-monitoring, researchers have identified a fertile field of energy-autonomous sensors. Such sensors have the capability to derive their energy needs locally from the surroundings, without having to be stuck with a limited-energy supply source such as a precharged battery. Often touted as a rising domain in itself, a major demand towards such investigation arises from the fact that wireless sensor nodes can be used to monitor a variety of conditions, for which the deployment can range from on-the-skin to on-the-organ of a human body. Thus, depending on the specific use-case, it might not be feasible to cater to the needs of battery recharge or replacement every now and then, since it gets depleted. One of the leading research works in this field focuses on utilizing the temperature difference between the human body and the ambiance and as such, is based on thermoelectric energy sources to obtain a reliable, (almost) constant supply of DC voltage, throughout its operation period.

Thermoelectric energy sources are well suited for applications concerning temperature gradients, however small, and can theoretically power a given sensor forever, i.e. if mechanical fatigue and wear-out are omitted. But the caveat in using such energy sources lies in the phrase 'however small'. Smaller the temperature difference, smaller is the output voltage as well as the power that can be harnessed from such a source. An obvious remark could be to use a circuit to boost-up the DC voltage and design the succeeding circuits such that they can be operated on a minimum power budget. While, a remark like that may be welcomed as a suggestion and circuit techniques might be looked into, to implement such a system, a major concern still remains at large.

How to power these circuits such that they could do the magic they have been designed for and the sensor works dutifully, especially in the beginning when the sensor is devoid of any power to even start-up the boosting circuit?

This is a classic problem referred to as the 'Cold Start-up'. Standing up to its name, it has fancied the attention of researchers for quite over a decade now. Here one may be forced to wonder, if such a problem can be solved at all. Well, there are approaches proposed in the literature that are worth appreciating, but when compared to the progression of the state-of-the-art in this area that is long past its scientific curiosity phase, it has been rather slow with not many elegant solutions to report a much awaited significant improvement in the cold start-up voltages.

# 1.1. Energy Harvesting: A Walk through the Clock

It may come as a surprize that mankind has already been up to date with such an eccentric idea since Bronze age. One could argue that it all began with the invention of sails, when wind energy began to be harvested for sailing across the Mediterranean region 5500 years earlier [1]. Moreover, the fact that wind energy was actually harvested in windmill arrangements in India, 2500 years ago [1] also suggests a similar notion, although world-wide commercialization only began during the late 1970s when the wind turbine industry was setup in Denmark. At this point one may argue, that it might appear cheating to allow for such easy credits to the earlier generations when the design and wide-scale employment of such a technological marvel, that converts wind energy to electricity, only started of late. Thus, it would be worthwhile to remember that energy harvesting essentially is allowing the nature to power human invention, that could aid in its propulsion to achieve a desired consequence. Utilization of a transduction mechanism to extract energy from the ambiance in a suitable form so as to power up a given process, is only a finer, aesthetic version of the crude-&-crux definition discussed formerly. History has made it evident, time and again that mankind has always struggled with definitions while exemplifying exceptional grasp of concepts. Take for example the simple invention of small scale water-powered manoeuvring systems such as the waterwheel designed in the early 200 BC by Philon [1]. It was only later in the 19<sup>th</sup> century that the photovoltaic effect (PV) was documented by Bacquerel in 1839, with the successful implementation of PV panels, converting solar energy to electricity, starting in 1954 lead by Bell Laboratories [1], that such fine-tuned definitions of energy harvesting came into picture and intrigued researchers to look for more alternatives to address the growing energy needs of the time. Thus began the ordeal, to discover different transduction mechanisms that could be used to scavenge energy from different environmental phenomenon. Following this up with not a large time lag, came demonstrations of kinetic energy harvesters capable of converting hydro-power to electric power, in 1878 and wind turbines converting wind-power to electrical-power while being stored in a battery, in 1887 [2]. And thus, it may be justified to argue that a field of opportunities, with plenty to cultivate and ample to harvest, opened up.

A careful glance over the many illustrious works and powerful inventions proposed in this field over the last century may easily reveal that most of the efforts from the research community had been towards the large-scale generation and consumption of the harvested energy to satisfy the ever-growing energy needs of the population that proliferates by the minute. It was only during the last few decades that the scientific curiosity shifted towards accommodating an emerging need for energy-autonomous sensor systems in its research prospective. Due to scientific advancements and the recognition conferred upon the growing demand for wireless sensor networks, the field of micro-energy harvesting experienced a major boost-up. A major research question during those times transpired as how would one ensure the availability of energy to drive the wireless sensor nodes in remote areas, and locations abundant with such nodes? One demands strenuous efforts while the other incurs cost.

Consequently, over the last couple of decades this curiosity progressed and developed towards having a more engineering orientation. And eventually, an array of solutions were brought about and presented onto a designers bench [3] to pave way for the development of energy-autonomous sensor systems for micro-scale operations. One of the earliest works on this sprouting topic was reported in 1984 [4]. Researchers from the University of Saarland, Germany identified the breathing movement of thorax as a potential energy source and implanted a PVDF (Polyvinylidene fluoride) based piezoelectric film on the middle ribs at the lateral thorax of a mongrel dog, to obtain a power output of 17uW and proposed to enable an implantable sensor. Following this up in the wearable domain, researchers at the MIT Media Labs in 1998 [5] proposed to generate electrical power by parasitically scavenging the walking movements of a human body. They implemented the idea with a couple different transduction mechanisms including an electromagnetic sensor (magnetic rotor generator) and piezoelectric sensors (PVDF film & PZT unimorph strip) and concluded with a comparison that favoured the latter for shoewearable applications to power an RFID tag. It may be interesting to note that the magnetic rotor sensor extracted a peak power of 1W and the PZT unimorph extracted a peak power 80mW from those movements, that only showcases the potential such energy harvesters propose.

Would you not agree now, if a comment is made to laud the researchers whose life's mission [3] is not only to remove the cords restraining their sensors but also to forsake the need to limit its lifetime that the archaic pre-charged batteries impose?!

At this point it might be wise to ponder, why would the scholarly community want to get rid of such technology that led humanity to embark on a new journey of technological advancements, so impatiently?

A simple answer could be, because now it seems to thwart that very age of opportunities it once flourished, which would become more evident in the next section.

# 1.2. Case Scenario: Tele-Monitoring

Tele-monitoring [6], as literature defines it, is observing a patient's key health parameters like heart-rate, respiratory-rate, temperature, humidity, etc. remotely, without making any physical interactions, through the use of wireless telemetry via internet, Bluetooth etc. Such an approach towards patient monitoring could lead to a reliable and on the go methodology to provide point-of-care diagnostics. Moreover, it also allows the patient to remain in the cosy atmosphere of one's home without having to go through the hassles of finding a hospital room or a home attendant. The reduction in healthcare costs such a methodology enables, also makes it affordable while being convenient at the same time.

So far so good. Now we're ready to consider a case scenario representing the above notion:

Suppose a situation - A young little innocent child had to go through a traumatic accident that caused her to suffer from major injuries inflicted to her thigh bones restricting her upper-leg movements. The doctor has prescribed the child to use a wheelchair till the time her leg recovers, virtually leaving her crippled for the time being. After a couple of weeks of hospitalization the doctors have permitted her parents to take the child home but have warned them to be wary of convulsions, although rare, the kid might have to go through during days.

Owing to the adversity their kid is going through, ideally the parents would want to keep a close eye on their child's health throughout the entire time till she recovers. However, one can't always rely on ideality in the face of hostility. Due to prior engagements and work appointments scheduled prior to the sudden and unfortunate accident, the parents are left with little options but to leave their child during certain office hours.

Worry not, for these were the times a concept as unconventional and as astounding as Tele-monitoring was introduced to humanity and this thesis (above). Thus, under the umbrella of such a vivid notion, a multitude of options [7] have been made available over the years to the humankind, from which a couple of noteworthy ones (broadly speaking) are listed below:

- 1. Attaching health monitoring leads to patient The little kid might have to be hooked up to a large monitoring framework consisting of a swarm of sensors around the house constantly keeping a watch over her along with a bunch of sensors attached to her body through leads and belts worn by her to monitor vitals such as body temperature, heart-rate, respiratory-rate, body posture, humidity, blood pressure, etc [7]. While such a system might be effective in having an all-round, around the clock surveillance of the child, it may not be a convenient idea for the child herself as she might want to get rid of all the wires and the restraining belts wrapped around her, once her parents are gone. A smart and holistic system like that may often be perceived as imprisoning from the patients perspective, if not the observers and in some cases may actually work against the very comfort it's designed to create.

- 2. Patch-Biosensor On a fundamental note, if a patient needs to be monitored, certain key vitals are important to ascertain his/her well-being given the condition, while launching an alert in case of any abnormalities observed, to the nearby hospitals and responsible guardians. In other words, not every nitty-gritty information needs to be recorded to ensure the status of the patient. Such is the innovation proposed by VitalPatch Biosensor [8]. It is available in the form of a compact, lightweight, patch-like disposable package and comes fully equipped with integrated sensors to measure 8 physiological biometrics such as ECG, heart-rate, respiratory-rate, body posture, temperature, activity and fall detection.

In this case, the problem is the disposable zinc-air battery used in the proposed biosensor that could only last for a period of 96 hours or 4 days. What that would mean for the application is that the patient would have to change the patch biosensor every 4 days, considering a prolonged ailment. This could not only be uncomfortable to the patient but would also mean an increased expenditure on healthcare that the stellar concept of Tele-monitoring was catering to solve. Well that wouldn't be so great, isn't it?

Thus, there's an emerging need for engineering solutions that would empower such sensors to operate autonomously on a self-sustainable basis, for longer durations of time, as is required by the patient and the application. 'Self-sustainable' being a fancy term, means the sensor is capable of powering itself on its own and functioning without any external intervention, apparently, via the concept of energy harvesting.

A small detail like powering-up, in a complex and advanced system like the biosensor – designed to accomplish an array of functionalities; can raise doubts on its continuance in the longer run. Such is the significance of the concept we are now going to dive in, next.

# 1.3. Energy Harvesting: Candidates

Energy harvesting, as discussed earlier, in its most aesthetic forms is the transduction of energy available in the environment to the energy it is most suitable in, to power a given application, in this case, electrical energy to drive a sensor. But what is the exact transduction mechanism that should be considered, prior to inquiring further into the design of such a module?

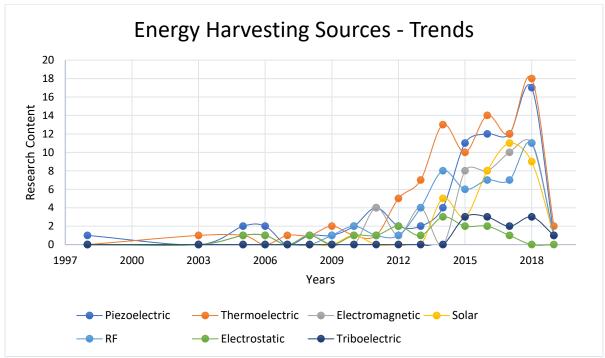

A look into the literature reveals that the research community has been pretty enthusiastic into investigating about the various mechanisms that could advance our goal. This has been summarized in figure 1 below, that has been plotted taking into account a quarter of the works (no. of publications) and ideas propounded by the community over the last two decades, from IEEE Xplore:

Figure 1. Energy harvesting sources – Trends over the years in the wearable domain

From the graph above, it might be worthwhile to note that, as research into the various transduction mechanisms unravelled new techniques of harvesting energy employing the same mechanism over the decades, two particular transduction techniques stand out. One has its root in the annals of human history namely the kinetic energy harvesting and the other being a more recent discovery that has gained widespread adulation as thermoelectric energy harvesting, over the last few years. The technique of

harvesting kinetic energy in this case is the piezoelectric effect that converts mechanical movement of a cantilever beam (in the research papers referred above) to electrical energy.

One may wonder, if it may be rational to follow the current trends and proceed with the flow of research community's fervour. Well, in that case it would be wise to at least discuss the available transduction phenomena briefly and examine their suitability with the application at hand, to guarantee not a single avenue was left unexplored while making an unbiased rationale.

Candidates, under the microscope, are elucidated below:

#### 1.3.1. Kinetic Energy Harvesting

On a general note, any mechanical movement accompanies with itself energy, that allows the subject/object to move from one point to the other. In terms of linear movement characterized by a moving mass 'm' and velocity 'v', this energy called the Kinetic Energy (KE), is given by:

$$KE = \frac{1}{2}mv^2 \tag{1}$$

In theory, if this energy is harvested, the entire *KE* part of the equation should be available to be utilized. In practice, that is not the case, since part of the energy is lost in heat, a part is lost in overcoming the friction imposed by the medium it is in and part of the energy is lost in the actual movement of the mass. Although the last part of the previous argument may sound as a logical consequence of events, a counter argument could be, in an ideal world this energy would get transferred/extracted before the mass has any time to use the energy for itself. However, as real as the world is, practise affirms that the mass moves to cause an impact on its surroundings such that the force produced could transfer this energy from one form to the other, such as raw electric power. This impact and the method with which it is realized or performed gives rise to the various techniques of kinetic energy harvesting, as discussed below:

#### 1.3.1.1. Piezoelectric energy harvesting:

Working on the piezoelectric effect, which broadly speaking, means the formation of an electric dipole when a strain is applied on the lattice of a crystalline material and vice-versa, these energy harvesters are an excellent source for transducing mechanical to electrical domain, without requiring any separate moving parts with respect to a given reference. However, here one needs to be cautious of the word 'broadly speaking', as it often motivates the reader to think there's only one direction the piezoelectric effect can take place. It's true, that for this effect to occur, formation of an electric dipole is a necessity. This is evidenced in the case of materials (GaAs, ZnO) having an asymmetric crystalline lattice whereby due to the shifting centre of gravity of the positive and negative charges acting under a strain, an electric dipole results [9]. Nevertheless, one should be also wary of the fact that there are materials like ceramics (PZT, BaTiO<sub>3</sub>) that already have such dipoles even without the application of stress. For such ceramics, the piezoelectric effect occurs as a result of the rotation of dipoles that creates a potential difference across the lattice [9].

Although different structures, for the piezo-material under consideration, have been studied in the literature to exercise the piezoelectric effect, choice of a specific structure depends, to a great extent, on the application and the environment its being used in. For example, in the application the presented work is designed for, a cantilever beam structure is identified as suitable, by leading researchers as proposed in their respective research [2]. One possible reason could be that such a structure allows for low impact force, low acceleration and low frequency of operation to produce the required energy that could drive such applications [2] as the present one.

Also, the fact that even a small section of a piezoelectric material is capable of generating an alternating voltage when under stress, allows for small-scale miniaturization of such energy harvesting elements (EHE), which in itself is its own substantial proponent towards the cause.

#### 1.3.1.2. Electrostatic energy harvesting:

Often a hotly debated topic on whether or not such a technique can be termed as an energy harvesting methodology, nonetheless, this technique has strived to create its own thriving niche of a research field. The principle of such a transduction technique focuses on the development of electrostatic forces

between the two charged plates of a capacitor under the action of stress. The electrostatic force being responsible for coupling the mechanical and electrical domains [10]. On a more rudimentary level, consider a charged capacitor with capacitance 'C', voltage 'V' and charge 'Q', the relationship among these quantities stands as:

$$Q = C.V \tag{2}$$

Now, if under the application of stress on the plates of this hypothetical capacitor, the plates move apart, the value of the capacitance 'C' would get affected and decrease. Assuming, the charge 'Q 'remains constant with no leakage or mechanical failure (degradation), the voltage 'V' would increase by an amount proportional to the value, capacitance 'C' goes down. This in terms of energy representation would mean:

$$EE = \frac{1}{2}QV \tag{3}$$

Thus, quite a favourable outcome results, since 'Q' remains constant and 'V' increased, the total energy content of the system rises by the same amount. While the outcome favours the mechanism to be called energy harvesting, a counter argument often raised by fellow researchers, questions the initial condition the system must be kept in, that in itself demands some energy to be stored. Well, whichever part of the court the ball may land in, one cannot deny the transduction of energy between the two domains (mechanical to electrical).

With such an EHE one may find it quite natural for it to be fabricated on a micro-scale level and designed into miniature form-factors using various micro-fabrication techniques [2]. However, there are some caveats that are still being tried to be addressed, thus forcing researchers to look for alternative means, such as low charge retention over longer periods of time, low surface charge density, and the fact that it needs to be pre-charged to be useful at all.

#### 1.3.1.3. Electromagnetic energy harvesting:

Often touted as one of the more primordial forms of energy transduction mechanism, that has been, since the discovery of Faraday's Laws in 1831, used to convert energy existing in the forms of hydro, wind, coal or nuclear to electrical energy. However, it all transpired to be known for large-scale electricity generation. Then, what about the poor designers who were in hopes of finding a better solution for micro-energy needs of the society?

A scientific discovery is almost rendered useless if it does not fit in an engineer's little tool-box. How could it make people's life better?

Thus, a newfound interest stirred up the research community and small-scale solutions started to be revealed around the late-20<sup>th</sup> century, with the 1998 demonstration of MIT media lab's wearable shoe-based energy-harvester being one of the prominent proponents of the idea [5].

In layman's terms, this idea corresponds to the generation of electric current (AC in nature) when a magnet moves inside a coil, thus transferring the kinetic energy of the hypothetical magnet into electrical energy for the hypothetical (as well) coil. But the very employment of magnets and coils prevents such EHE from have micro-form factors. Prototypes available in literature suggest volumes from 0.1 cm<sup>3</sup> to 100 cm<sup>3</sup> with output power ranging from 1uW to 100mW respectively [10]. Also, such EHE have been communicated for delivering higher values of currents but lower values of output voltages. Microfabricated forms are not reported to have much larger voltages than 100mV either [10].

Therefore, with respect to the presently considered application, such micro-energy harvesters may not turn out to be a good choice owing to their volume to power/voltage ratio.

#### 1.3.1.4. Triboelectric energy harvesting:

Originally regarded as a wasteful form of electrostatic energy, researchers prior to its discovery, ensured such effects be suppressed. The phenomena was thought for many years to have a negative effect on the performance of a material, due to dissimilar materials charging each other up when in agitative

contact. However, in 2012, the scientific community was taken by a storm when [11] published their work propounding the practicality and feasibility of such an effect to generate and use this electrostatic energy.

In plain text, when two polymer sheets with different triboelectric properties are stacked atop each other, they produce equal and opposite charges that accumulate over the two sides, under the impact of mechanical deformation that causes them to rub against each other, due to nanoscale roughness [11]. The electric dipole formed at the interface, called the triboelectric potential layer [11], also serves as a 'charge pump' to force the flow of charges towards an external load due to the change in capacitance. This variation in capacitance is ensured, by design, to occur due to a mechanical impact. An expression [11] that demonstrates the working principle is:

$$I = C \cdot \frac{\partial V}{\partial t} + V \cdot \frac{\partial C}{\partial t} \tag{4}$$

Where, 'I' is the generated current, 'V' is generated voltage (AC in nature) due to the electrostatically induced charges and 'C' is the capacitance of the triboelectric structure.

Although, high voltages have been reported in literature owing to this phenomena, not very high currents have been observed, thus keeping the output power to be in the lower range [12]. Take for example the case presented in [11] itself, a peak output voltage of 3.3V was harvested with output current of only 0.6uA and a peak power density noted to be at  $10.4 \text{mW/cm}^3$ . Works have been reported to increase the output power to about 1.5W, although the short circuit current was still very low, around 3 mA at  $0.8 \text{M}\Omega$  load, with the open circuit voltage at around 850 V [12].

Materials employed to obtain this effect can be pure-polymer based like Kapton and Polyester (PET) [11] as well as nanocomposite based like BTO (BaTiO3) nanoparticles in a copolymer matrix—poly(vinylidenefluoride-co-trifluoroethylene) (P(VDF-TrFE)) [2], with latter delivering a relatively higher current.

Among the discussed Kinetic energy harvesters, a careful observation into the operation and fabrication of such EHE may reveal that one particularly stands out for the proposed application. The piezoelectric energy harvester fairs well in comparison to its sister EHE techniques due to:

- a. The phenomena that allows for its working, does not demand any mechanically moving parts as in the case of electromagnetic and triboelectric energy harvesters. So wear and tear is fundamentally not an issue.

- b. The phenomena as well allows for the generation of potential due to intrinsic charge arrangements and so does not necessitate any externally applied electric fields as in the case of electrostatic energy harvesters.

- c. Since the phenomena can also occur in a small piece of piezo-material, its micro-fabrication is well supported but only limited by technology or material, as opposed to electrostatic and electromagnetic energy harvesters.

- d. The current output of piezoelectric energy harvesters is reported to be higher than triboelectric energy harvesters [2,12], although this comparison is only based on a more practical ground than a fundamental one.

Now, coming to the point of suitability of such Kinetic EHE towards the application of wearable Telemonitoring, one may note that the critical and elemental requirement for any of the above listed effects is an impact. Such an impact might not always be very practical to expect from a human body specially in cases where a body is in a state of rest and the vibrations are only intermittent not continuous. Also, with regards to the amplitude of vibrations and operating frequencies that can be harnessed, current-state-of-the-art kinetic energy harvesters are not specifically suited for lower amplitude sub-Hz frequency vibrations that are pretty much abundant on a human body. This one might not come as a fundamentally justified comparison but it does hold on a practical level.

#### 1.3.2. Thermal Energy Harvesting

A more popular approach in literature for harvesting energy from the human body, thermoelectric EHE fundamentally drives its principle of operation from the Seebeck effect. Originally discovered by Seebeck

in 1822 [9], the observation related the coupling of thermal to electrical domain. Seebeck effect is the generation of potential along a given material (metal or semiconductor) when one of its ends is heated causing a temperature gradient to form along form that side. This effect is measured when two dissimilar materials (having different Seebeck coefficients) are joined together and the junctions are kept at two different temperatures, say 'T' and 'T+ $\Delta$ T'. Due to the difference in temperature, an electromotive force (Seebeck Voltage) is generated between the two junctions, namely, hot and cold junction. The phrase, Seebeck coefficient, used before, refers to the difference in potential generated between the two junctions per unit difference in temperature applied two the same, for small temperature differences [9]. Thus, the Seebeck voltage can also be expressed as [13]:

$$V_S = S_{AB} \cdot \Delta T = (S_A - S_B) \cdot (T_H - T_C)$$

$$\tag{5}$$

Where, ' $V_S$ ' is Seebeck voltage (DC in nature),  $S_A$  &  $S_B$  are Seebeck coefficients of the two materials and  $T_H$  &  $T_C$  are the temperatures of the hot and the cold junctions.

A close look on the working of such EHE may reveal that better is the conduction of electrical energy, higher will be the electrical power produced, since more conduction electrons between the junctions means more current. On the same note, lower is the thermal conductivity, better is the efficiency of energy transduction, since higher thermal conductivity means sooner neutralization of the temperature difference. The efficiency is thus defined as the ability of the thermoelectric material to conduct electrical energy while impeding thermal conductivity. Another important parameter that measures the performance of a given thermoelectric EHE is called the Figure of Merit (ZT) and is defined as [2]:

$$ZT = \frac{S^2 \lambda}{\kappa} . T \tag{6}$$

Where, 'S' is Seebeck coefficient, ' $\lambda$ ' is electrical conductivity, ' $\kappa$ ' is thermal conductivity and 'T' is temperature.

Therefore, higher is the parameter ZT, better will be the thermoelectric efficiency (of energy conversion). One of the approaches to increase ZT that has gain quite some momentum over the recent years, is to increase the phonon scattering independently to reduce the lattice contributions of thermal conductivity. This has been shown to yield  $ZT \ge 2$ , by using nanostructured bulk thermoelectric materials [2].

Regarding the suitability of such an EHE towards the considered application, it may be worthwhile to note that the human body always maintains an almost constant temperature throughout itself, that, with regards to the ambient room temperature could easily provide a reliable & sufficient temperature difference. By employing a highly efficient (Be<sub>2</sub>Te<sub>3</sub>) EHE to generate energy suitable for a given sensor application, this can be taken advantage of. Moreover, with no moving parts (no maintenance), simple structure and almost 20 years of lifetime [13], these harvesters can emerge being an excellent choice.

#### 1.3.3. Electromagnetic Radiation Energy Harvesting

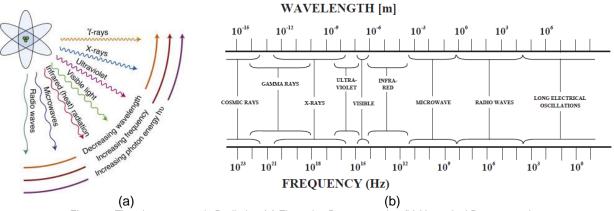

Electromagnetic (EM) radiations are, as the name implies, packets of energy propagating with an alternating electric and magnetic fields. Such radiations consist of a wide range of particle-like waves / wave-like particles distinguished on the basis of frequency and wavelength, that also are responsible for their unique characteristics. Figure 2 gracefully represents this entire electromagnetic spectrum.

Figure 2. The electromagnetic Radiation (a) Figurative Representation (b) Numerical Representation

Humankind since ancient times has always strived to use this abundant energy stored in these radiations. The development of sundial in 3500 BC marked one of the first attempts to use electromagnetic radiations coming from sun, although not to transform energy as such, but to give an idea about time. So, now the question arises, can we benefit from it in our case?

Visible and Infrared light waves being the most abundant forms of energy on this planet, bestowed upon us directly by the sun, proposes an important challenge and a solution for energy harvesting. In the meanwhile, radio-frequency (RF) has also got quite prolific specially in the metropolitan areas with increasing reach towards the countryside across the globe, since the advent of radio-operated cellular phones. Here, one may argue if the artificially available RF waves can be treated as a reliable source to harvest since it's not originally provided by nature. Nonetheless, such an omnipresent EM energy (now-a-days) cannot be left to waste if it has even the slightest potential to be a reliable source of energy. The other forms are not considered as they are not abundant and in some cases even harmful.

#### 1.3.3.1. Solar energy harvesting:

Based on the photovoltaic effect, originally discovered by Becquerel in the 19<sup>th</sup> century, and the successful commercialization by Bell Laboratories (for space explorations, though) in mid-20<sup>th</sup> centuries [1], the field of solar energy harvesting has really taken a deep plunge into effecting the lives of ordinaire, over the years.

The phenomena in itself is quite intriguing (from a microelectronics point-of-view). In a p-n junction, electrons from the n-side diffuse across to the p-side and holes diffuse towards the n-side, due to electrostatic forces of attraction resulting in a free-charge depleted region called the depletion region around this junction. This diffusion and accumulation of opposite charges at the two sides of the depletion region creates a net electric field that cancels the effect of the electrostatic forces of attraction and maintains an equilibrium condition across the junction. Now, when a photon carrying just enough energy to ionize an electron from the valence band, hits the so-formed depletion region, the electron-hole pair thus released are swept towards their respective sides (holes  $\rightarrow$  p-side, electrons  $\rightarrow$  n-side), due to the depletion region's electric field. When such an arrangement is connected to a load, the flow of electrons create a current across it and result in a certain voltage (DC in nature) that is proportional to the photon flux [14]. Thus, the conversion of light energy into electrical energy takes place.

Parameters such as the bandgap and energy conversion efficiency are treated to be a key in determining the capability of a photovoltaic cell [2]. Bandgap being an intrinsic property of a semiconductor material, specifies the Shockley-Queisser (S-Q) limit [2]. This limit decides the maximum (theoretical) energy conversion efficiency a single-junction photo-cell can produce with each bandgap corresponding to an S-Q limit. For a bandgap of 1.34eV, the S-Q limit predicts 33.7% achievable efficiency [2]. Practical implementations have shown GaAs to have the maximum efficiency of >28% while silicon achieves 20-27%, not lagging far behind [2].

While this energy harvesting scheme is known to provide high energy densities than the previously discussed ones, it suffers on accounts that not the entire different wavelength radiation emitted by the sun can be utilized [15] and the fact that such an EHE needs to be lit-up for the energy conversion to take place. Nonetheless, such a scheme provides an interesting energy harvester that does not rely on moving mechanical parts, is reliable, has longer lifetime with low maintenance costs.

Moreover, since our application would require the user to wear the sensor module on the body and under the clothes, at a location ranging from the neck to the knee depending on the use-case, the user would find it difficult to always expose the sensor to light for it to work. Thus, this approach might not present the best suitable EHE.

#### 1.3.3.2. RF energy harvesting:

Another abundantly available energy source due to the presence of WLAN, GSM and Radios around, RF EHE proposes to be a good prospect for wearable applications. The working principle is based on the

ability of the antenna designed for receiving the incoming RF signal to extract energy as well from the available RF waves lying around in its vicinity that it ideally would have rejected. It has been shown that the RF power density that could be harvested from a GSM base station 25m-100m apart ranges from 0.01uW/cm² to 0.1uW/cm² (around -30dBm to -20dBm) [15]. Such harvesters tend to be limited by their rectifiers and the minimum voltage, called the threshold voltage, needed by them to conduct any current [15]. The start-up power i.e., the minimum power needed by the energy harvesting unit to start its operation, thus need is given by [15]:

$$P_{start-up} = \frac{V_{rec,threshold}^2}{2.\eta_A.R_{rec}} \tag{7}$$

Where, ' $V^2_{rec,threshold}$ ' is rectifier threshold voltage, ' $\eta_A$ ' is receiving antenna radiation efficiency, ' $R_{rec}$ ' is rectifier equivalent parallel input resistance and ' $P_{start-up}$ ' is input power needed for the rectification and then harvester to start.

If a practical scenario is considered where  $V_{\text{rec,threshold}} = 0.3V$ ,  $R_{\text{rec}} = 1K\Omega$ ,  $\eta_A = 0.8$ , the  $P_{\text{start-up}} = 56.25uW$  (-12.5dBm), that is quite large as compared to the power that could be extracted from such a technique as of now [15].

Thus, if not on a fundamental basis, then may be on a more practical basis, the RF energy harvesting technique may not propose a very good solution for the presently considered application. Although once such a highly sensitive rectifier is available/designed, such an EHE could be of essence in this field. Also, RF energy cannot be relied to be available wherever a patient can go about that includes remote locations and countryside areas, that poses a major challenge for this EHE scheme.

On a similar note, there are though literature one could find on reputed platforms that talk about design of antennas with sensitivities as high as -30dBm [16], here one should also keep a track of the distance between the receiver antenna and transmitter that generally is around 30cm, which is quite low for practical applications. Such antennas also happen to be quite narrowband, while in practice a range of RF can be discovered in ambiance lying to be harvested which is not quite efficient. Literature has also reported successful design and demonstration of human body based RF EH antenna with a novel voltage-threshold compensated rectifier to achieve -22.5dBm sensitivity & 1V output voltage [17]. However, the applicability was proven for narrowband applications and the distance between transmitting and receiving antenna was only about 30cm with the channel being human body and not air.

After taking in, all the popular energy harvesting techniques, under due consideration, and discussing about their working phenomena, merits and demerits, we have almost reached a conclusion about the perfect EHE that is befitting for the (previously) discussed application that represents the essence of this work. But before the winner is announced let us address some practical nuances regarding power output of state-of-the-art and summarize the results as follows:

1. Comparison of output quantities, under wearable application-specific conditions, of the state-of-the-art EHE in their respective domains is tabulated in Table I as (courtesy of [2]):

TABLE I. Quantitative comparison of state-of-the-art energy harvesting elements (EHE)

| Energy Source                                    | Working<br>Principle        | Material/Configuration                                                                                    | Output<br>Voltage<br>(V) | Output<br>Power<br>(mW) | Output<br>Power<br>Density |

|--------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------|-------------------------|----------------------------|

| Solar                                            | Photovoltaic                | GaAs thin-film, single-<br>junction cell                                                                  | -                        | -                       | 28.8<br>mW/cm <sup>2</sup> |

| Triboelectric<br>(6 kgf pushing<br>force at 5Hz) | Triboelectric               | 5 wt% BTO nanoparticle—<br>P(VDF-TrFE)<br>nanocomposite, poled BTO<br>and P(VDF-TrFE),<br>contacting mode | 1130                     | 6.4                     | 0.71<br>mW/cm <sup>2</sup> |

| Electrostatic<br>(750 rpm rotary)                | Electrostatic<br>(Electret) | Rotor (PMMA+PTFE) + stator (Cu+FR4)                                                                       | 324                      | 10.5                    | 0.42<br>mW/cm <sup>2</sup> |

| Electromagnetic (vibration 2.1Hz) | Electromagnetic          | Magnet suspended by<br>springs on both sides in a<br>vertical tube | 6.5    | 0.432 | 14.16<br>uW/cm <sup>3</sup> |

|-----------------------------------|--------------------------|--------------------------------------------------------------------|--------|-------|-----------------------------|

| Piezoelectric (vibration 1Hz)     | Piezoelectric            | Prestressed multilayer PZT diaphragms                              | -      | 11.3  | 10.55<br>mW/cm <sup>3</sup> |

| Thermoelectric [18]               | Seebeck                  | High density BiTe pellet placement                                 | 0.0501 | 0.176 | -                           |

| RF (GSM) [15]                     | Far-field EM<br>Coupling | Dipole antenna                                                     | -      | -     | 0.1<br>uW//cm <sup>2</sup>  |

2. Summary of comparison based on individual characteristic EHE and application is tabulated in Table II as:

TABLE II. Quantitative comparison of energy harvesting elements (EHE)

| Domain                            | Electromagnetic                                                                                                                                                                    |                                                                                                                                                               | Thermal                                                                                                                                                                                                     | Мес                                                                                                                                                                                    | hanical                                                                                                                                                                                                       |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EH<br>Technique                   | Radio<br>Frequency                                                                                                                                                                 | Solar                                                                                                                                                         | Thermoelectric                                                                                                                                                                                              | Piezoelectric                                                                                                                                                                          | Electromagnetic                                                                                                                                                                                               |

| Energy<br>Harvested               | Electromagnetic radiation                                                                                                                                                          | Electromagnetic radiation                                                                                                                                     | Temperature gradient                                                                                                                                                                                        | Mechanical vibrations                                                                                                                                                                  | Mechanical vibrations                                                                                                                                                                                         |

| Working                           | Dedicated antenna catches RF energy floating around in its vicinity in the ISM band and converts it into electrical energy which is then AC-DC Up converted to power a sensor [15] | Solar cell converts ambient light energy into electrical energy based on the Photovoltaic effect, which may then be DC-DC Up converted to power a sensor [15] | Temperature difference across two dissimilar semiconductor devices (P-N) is exploited to convert the thermal energy to electrical energy based due to Seebeck effect, which then is DC-DC Up converted [19] | Mechanical Vibrations are converted to AC electrical potential exploiting the sensor crystal orientation based on the Piezoelectric effect, which may be AC- DC Up/Down converted [20] | Mechanical Vibrations are converted into electrical domain when a magnet moves inside a coil inducing an AC current into it, exploiting Lorentz force, which may be AC-DC Up converted to power a sensor [21] |

| Availability                      | Mostly where<br>strong WLAN or<br>GSM Network<br>exists [15]                                                                                                                       | Specific to day<br>(outdoors) or<br>good lighting<br>condition inside<br>[15]                                                                                 | ΔT = 0.5K-2K<br>can be found<br>anywhere<br>across the body<br>anytime [19]                                                                                                                                 | Continued supply of power would need persistent vibrations all time                                                                                                                    | Continued supply<br>of power would<br>need persistent<br>vibrations all time                                                                                                                                  |

| Suitability<br>to patient<br>care | NO<br>(Not available<br>everywhere a<br>patient can go)                                                                                                                            | NO<br>(Not available<br>everywhere a<br>patient can go)                                                                                                       | YES (Available all the time everywhere - Reliable)                                                                                                                                                          | NO<br>(Only when<br>body moves<br>can it be<br>used -<br>Erratic)                                                                                                                      | NO<br>(Only when body<br>moves can it be<br>used – Erratic)                                                                                                                                                   |

Hence, a thermoelectric energy harvesting element is reasonably justified to be the most suitable one for the scope of the entire project work.

# 1.4. Power Conversion: The Supply Gap

Triceps

Now that the thermoelectric energy harvesting has been deemed fit for our application, lets have a look at what are the range of temperature differences that can be expected on a human body at room temperature (25°C). This has been aptly tabulated in Table III as (courtesy of [22]):

| Site           | Rested ΔT<br>(speed=0.2 m/s) | Walking ∆T<br>(speed=1.56 m/s) | Running ∆T<br>(speed=4.25 m/s) |

|----------------|------------------------------|--------------------------------|--------------------------------|

| Abdomen        | 1.73 K                       | 3.80 K                         | 4.75 K                         |

| Biceps         | 0.45 K                       | 1.22 K                         | 1.7 K                          |

| Calf-posterior | 0.65 K                       | 1.74 K                         | 2.4 K                          |

| Chest          | 0.94 K                       | 2.37 K                         | 3.18 K                         |

| Forearm        | 0.44 K                       | 1.16 K                         | 1.63 K                         |

| Hamstring      | 0.91 K                       | 2.32 K                         | 3.14 K                         |

| Lumbar         | 0.85 K                       | 2.18 K                         | 2.96 K                         |

| Quadriceps     | 0.82 K                       | 2.12 K                         | 2.89 K                         |

TABLE III. Temperature difference at T<sub>Room</sub> = 25°C for human body in various states of action

As can be observed from the above Table III, not very high temperature gradients can be obtained (or expected) from the human body. The author here finds it important to state about the expectations of rather significantly larger temperature gradients that could also imply that the patient might be in a really unhealthy state, and as such, they are also not being looked forward to.

2.02 K

2.75 K

0.78 K

Hence, with due regards to the above observation, a suitable thermoelectric element needs to be selected that can support the application (sensor) even at  $\Delta T$ =0.45 K. But before one jumps to concluding the search for the perfect thermoelectric energy generator (TEG), there's another key parameter called power output that needs attention along with the form factor of the TEG. The input power needed by different state-of-the-art implementations of sensor modules working for the intended application or in a similar domain (implantable) is tabulated in Table IV as:

| Application                   | Component                                  | Supply<br>Voltage | Power<br>Consumed    | Reference |

|-------------------------------|--------------------------------------------|-------------------|----------------------|-----------|

| Wearable (ECG)                | SiP - EHPPM<br>SoC, NVM, FSK<br>TX         | 1.5 V (max.)      | 5.98 uW<br>(SoC+NVM) | [27]      |

| Wearable (ECG)                | Mixed Signal<br>Monitor System-<br>on-Chip | 1 V               | 82.4 uW              | [23]      |

| Wearable (ECG)                | Analog Front End                           | 1 V               | 8.49 uW              | [25]      |

| Wearable (ECG)                | Analog Front End<br>- ADC                  | 1 V               | 0.30 uW              | [26]      |

| Implantable (Neuromodulation) | Analog Front End                           | 1 V               | 3.20 uW              | [24]      |

TABLE IV. Power consumption of different wearable/implantable sensor modules

<u>Please Note</u>: SiP – System in Package, EHPPM – Energy Harvester Platform Power Manager, NVM – Non Volatile Memory, FSK TX – Frequency Shift Keying Transmitter

From the above Table IV, it can be noted that the minimum power required to drive a system-on-chip (SoC) based sensor module [25] for the intended application should be >82.4 uW. Table IV also gives an idea about the power consumption of the individual components that can be embedded inside the SoC module with state-of-the-art implementations.

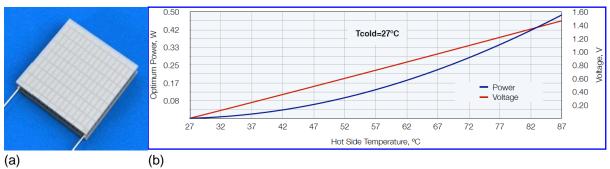

This completes the list of the key issues and specifications that needs to be considered while selecting a suitable TEG. Hence, with due respect to these parameters, the following TEG element – 1MD06-97-05TEG is selected as shown in figure 3 (courtesy of [18]):

Figure 3. (a) TEG element – 1MD06-97-05TEG, (b) Voltage & Power characteristics with respect to temperature difference

The suitability of this TEG element to the proposed application is represented in the following Table V:

TABLE V. Parameters of the TEG element – 1MD06-97-05TEG

| Parameter                                  | Value                      |

|--------------------------------------------|----------------------------|

| Temperature Difference ΔT                  | 0.45 K                     |

| Voltage Output (V <sub>TEG</sub> )         | 25.06 mV DC                |

| Power Extractable (Optimum Load Condition) | 103.76 uW                  |

| Source Resistance (R <sub>TEG</sub> )      | 2.69 Ω                     |

| Volume                                     | 11.4 mm X 11.4 mm X 1.1 mm |

The values of the parameters are interpolated from figure 3.(b) and the datasheet provided by the respective vendor [18].

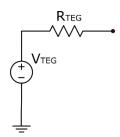

In order to model the TEG voltage source [19], the source resistance, R<sub>TEG</sub>, has to be taken into account and the entire DC voltage source is represented as shown in figure 4:

Figure 4. TEG voltage source representation

At this point, it may be worthwhile to note that although the selected TEG element qualifies to fulfil the minimum specification requirement for power output, while being a compact solution specially fit for wearable monitoring applications, it still is not capable enough to drive a sensor module as discussed in Table IV. The DC voltage output of the TEG is largely insufficient being only 25mV as compared to the mammoth required value of 1V which renders the presented solution for a self-sustainable power module, jeopardized.

One of the most sought after solution proposed by the literature to overcome this practical limitation of such a TEG element is to boost-up this small (apparently insignificant) output voltage, V<sub>TEG</sub>, to the desired value.

The next section explores this very possibility and the potential solutions that could be considered:

# 1.5. DC-DC Boost Conversion: Fundamentally Speaking

There are many prominent approaches described in the literature for boosting a given DC voltage to higher values, while not altering the signal too much. But before we delve into discussing the intricacies

of such converters, it might be worthwhile to start at a more fundamental level and build-up our understanding up to the system level design of the said converter.

Hence, the discussion would start from selecting a primary boosting element first that could either potentially store energy in the electrical or magnetic domain (capacitor & inductor respectively) or directly up-convert the signal without any storage while simultaneously playing at both the electrical and magnetic fronts (transformer). In the below Table VI, a detailed comparison of the above said elements is provided:

TABLE VI. Comparison of potential voltage boosting elements Part I

| Energy Converter | Transformer                                                                                                                                                                                                         | Inductor                                                                                                                                                                                                                              | Capacitor                                                                                                                                                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Topology         | Instantaneous<br>Conversion                                                                                                                                                                                         | Time Dependent<br>Conversion                                                                                                                                                                                                          | Time Dependent<br>Conversion                                                                                                                                                                                                   |

| Nature           | Electrical energy is transferred due to electromagnetic coupling through the core from primary (N1) to secondary (N2) winding as: $\frac{d\emptyset}{dt} = \frac{V1}{N1} \rightarrow V2 = \frac{N2.d\emptyset}{dt}$ | Electrical energy from source creates voltage across coil that forces current through it building up magnetic flux & gets stored as Magnetic energy $I_L = \frac{N.0}{L}$ Source                                                      | Electrical energy from source creates electrical field between plates inducing charge to form a potential across the plates storing energy electrically $ V_C = \frac{Q}{C} $ Source Storage element                           |

| Function         | Voltage applied to primary (N1) winding induces magnetic flux into the core that when coupled to secondary (N2) winding produces a voltage across it as: $\frac{V1}{V2} = \frac{I2}{I1} = \frac{N1}{N2}$            | Voltage across coil builds up current creating magnetic flux. Now, since voltage is constant, flux builds up, increasing current which could transfer this energy $V_L = N \frac{d\emptyset}{dt} \rightarrow V_L = L \frac{dI_L}{dt}$ | Electric field b/w plates moves charges(e-) against it, causing a current, inducing charges on the plates creating voltage that can be used to transfer energy $Q = \int I_C . dt \rightarrow V_C = \frac{1}{C} \int I_C . dt$ |

| Implementation   | Converter design would involve choppers that would convert DC-AC & AC-DC at the interface of transformer since DC could saturate (ideally not) its operation.                                                       | Converter design would involve switches to allow the flow of energy from source to inductor to load in a controlled manner.                                                                                                           | TEG Capacitor Switched Load Capacitor Capacitor Switch Switched Involve switches to allow flow of energy from source to capacitor to load in a controlled manner.                                                              |

Table VII below lists the potential merits and demerits of using the elements described above:

TABLE VII. Comparison of potential voltage boosting elements Part II

| Energy<br>Converter | Transformer                                                                                                                      | Inductor                                                                                                                               | Capacitor                                                                                                                              |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Topology            | Instantaneous<br>Conversion                                                                                                      | Time Dependent Conversion                                                                                                              | Time Dependent Conversion                                                                                                              |

| Advantages          | <ol> <li>Instantaneous processing</li> <li>Voltage matching</li> <li>Impedance matching</li> <li>Electrical isolation</li> </ol> | <ol> <li>Energy Reservoir</li> <li>Smoothens power<br/>flow</li> <li>Protects circuit<br/>against high current<br/>stresses</li> </ol> | <ol> <li>Energy Reservoir</li> <li>Smoothens power<br/>flow</li> <li>Protects circuit<br/>against high voltage<br/>stresses</li> </ol> |

| Comparison          |                                                                                                                                  |                                                                                                                                        |                                                                                                                                        |

| Topology            | Instantaneous                                                                                                                    | Time Consuming Approach                                                                                                                | Time Consuming Approach                                                                                                                |

| Nature              | None                                                                                                                             | None                                                                                                                                   | None                                                                                                                                   |

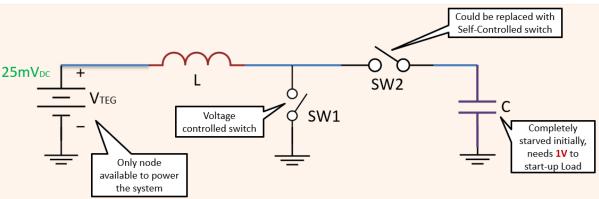

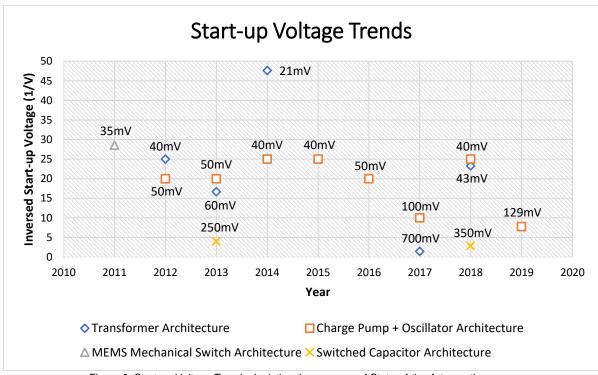

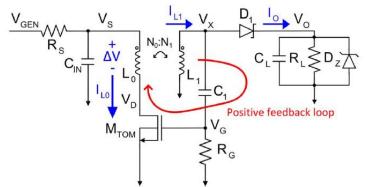

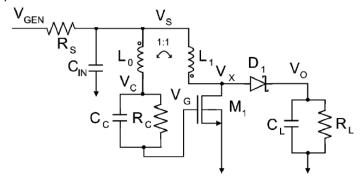

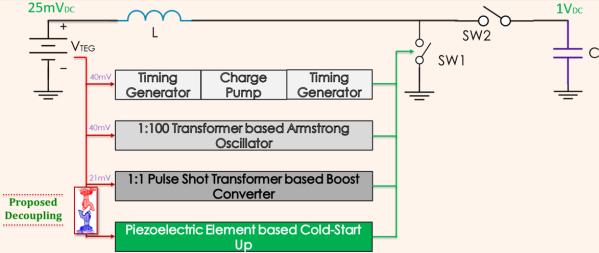

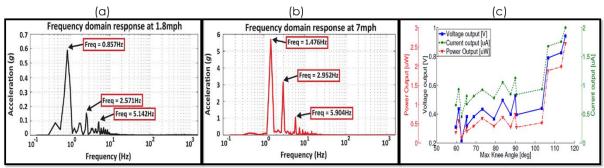

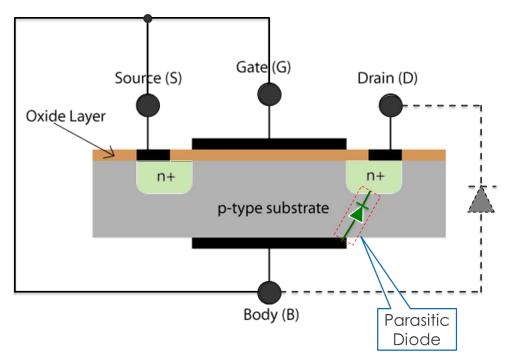

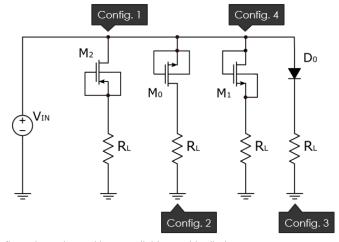

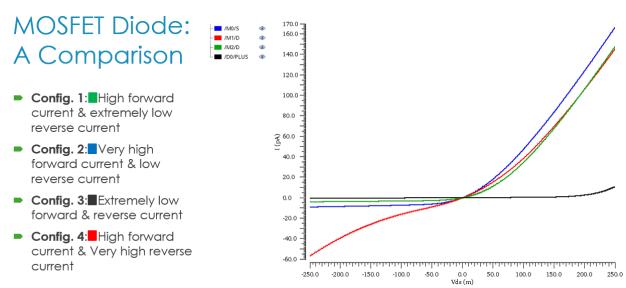

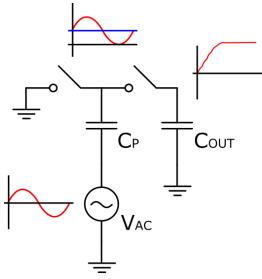

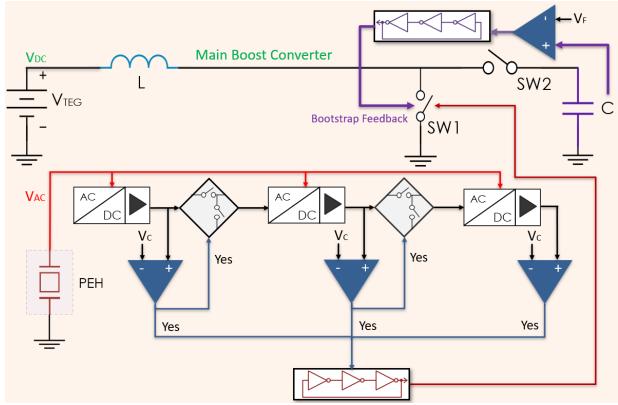

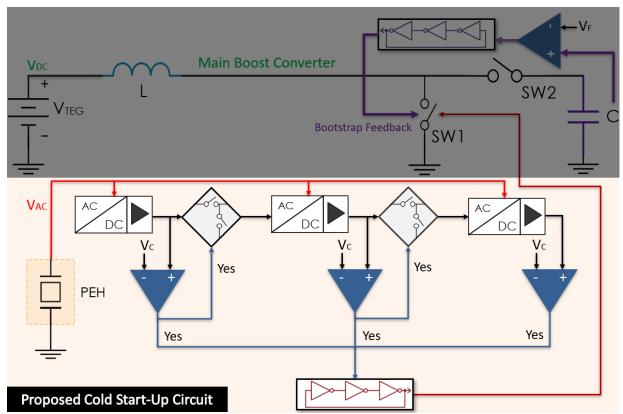

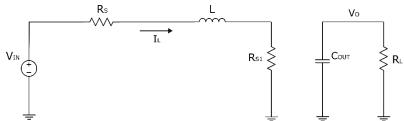

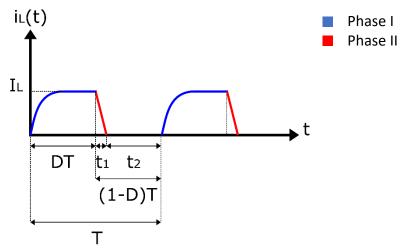

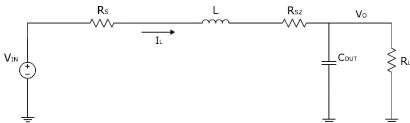

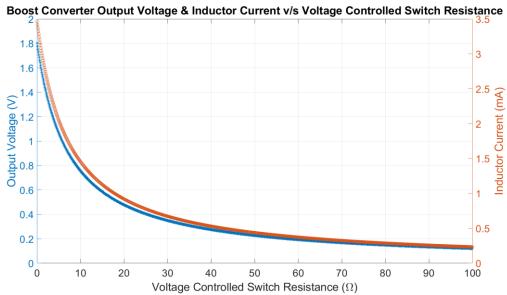

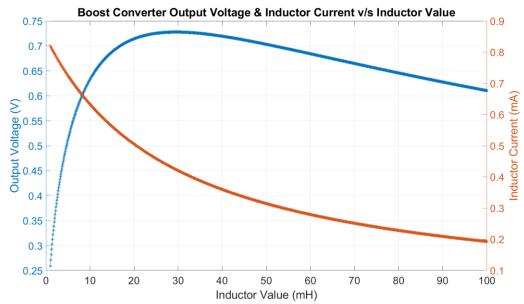

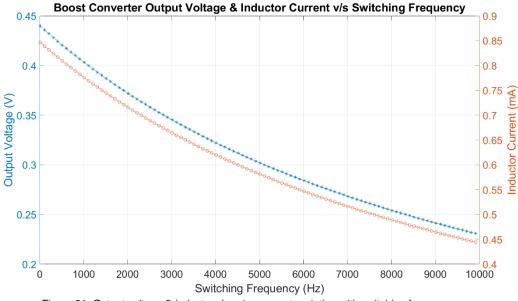

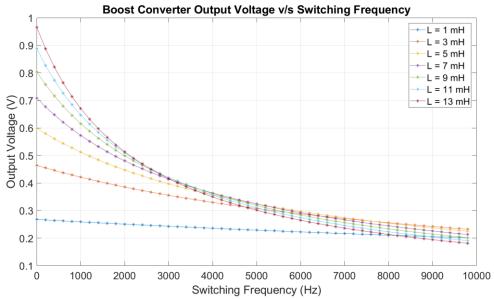

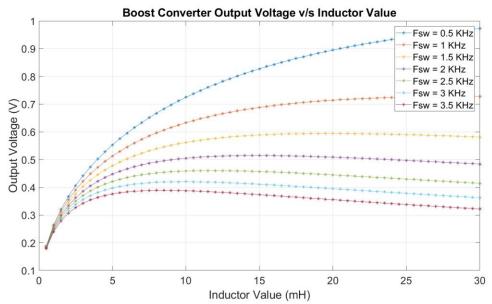

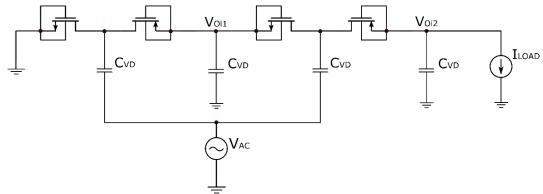

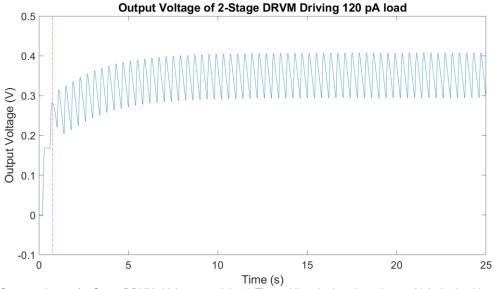

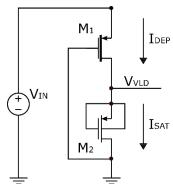

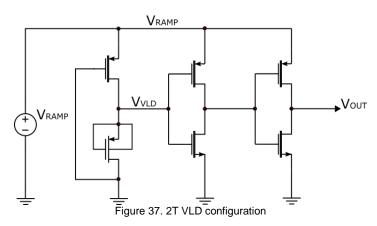

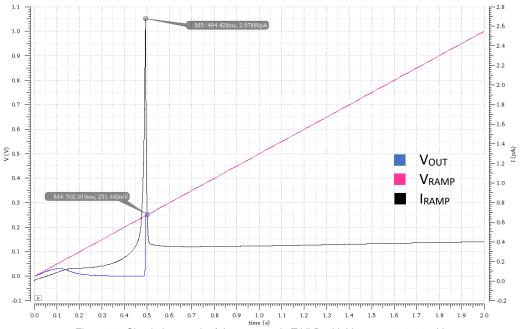

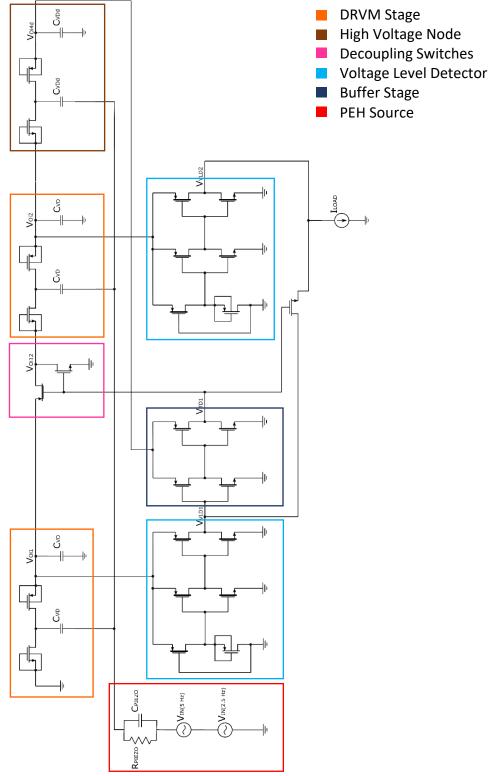

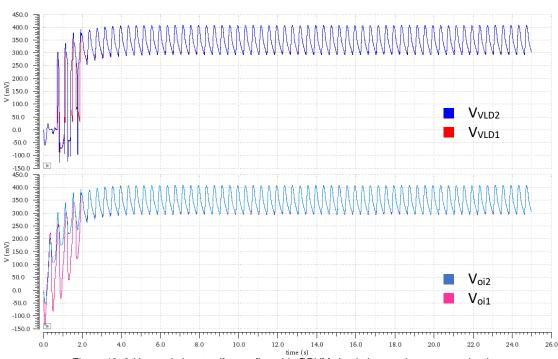

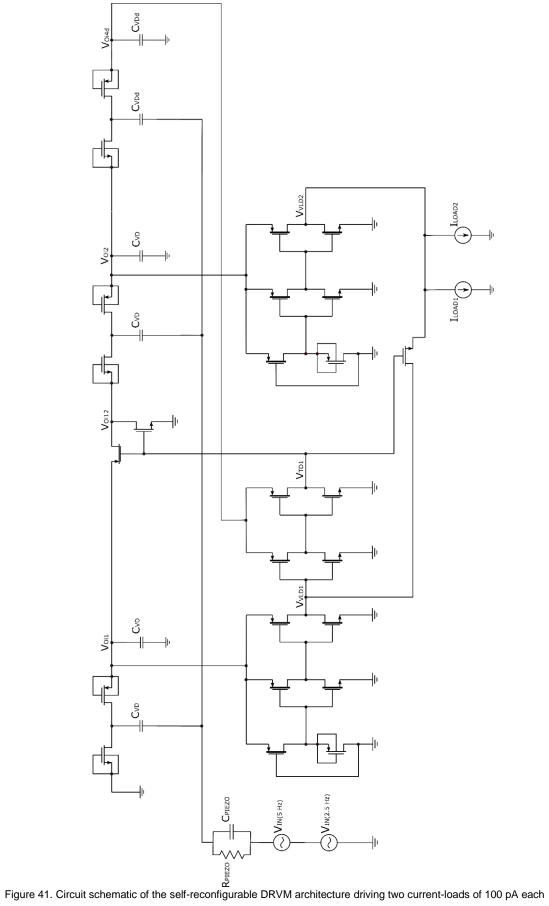

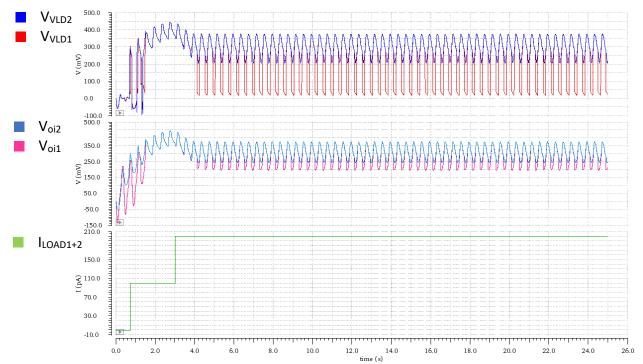

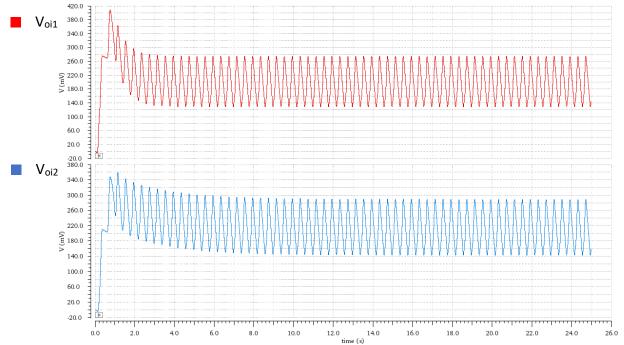

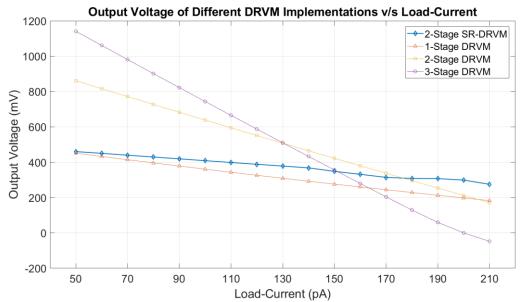

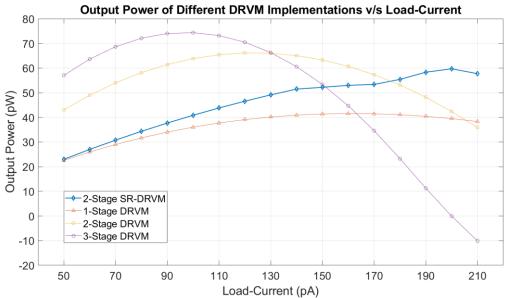

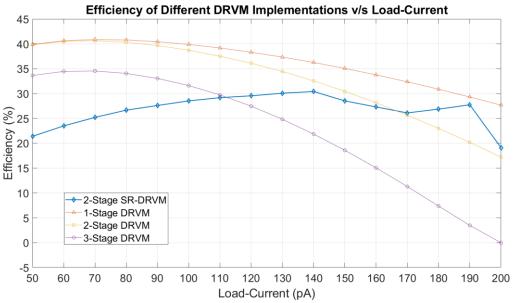

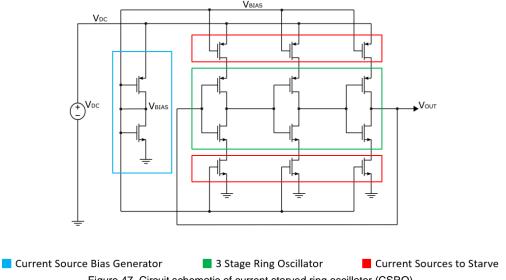

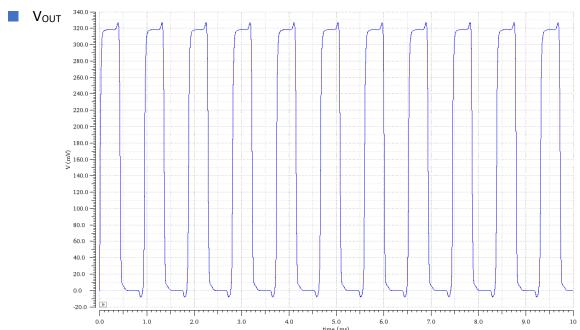

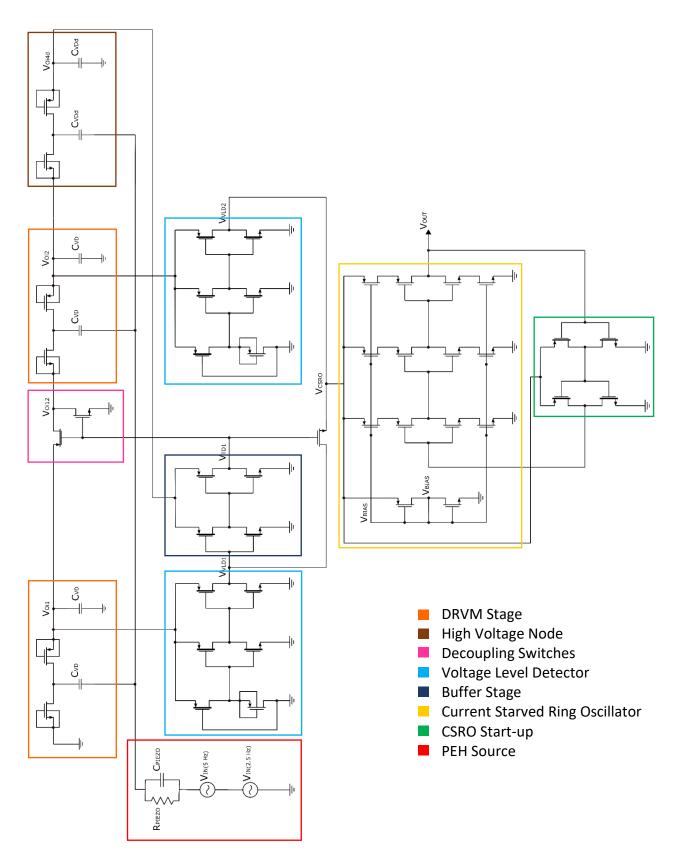

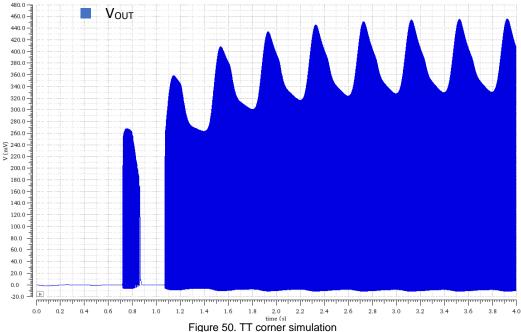

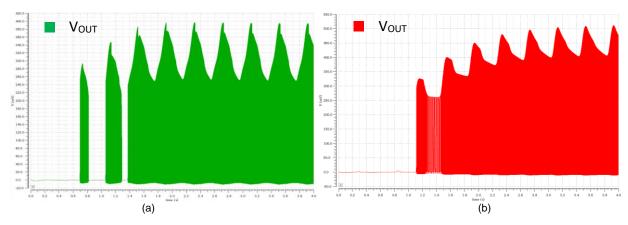

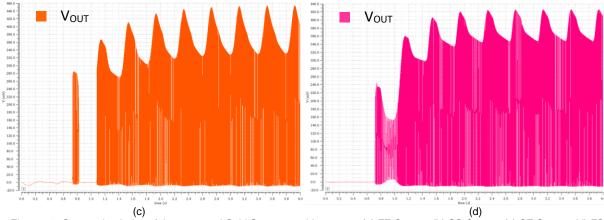

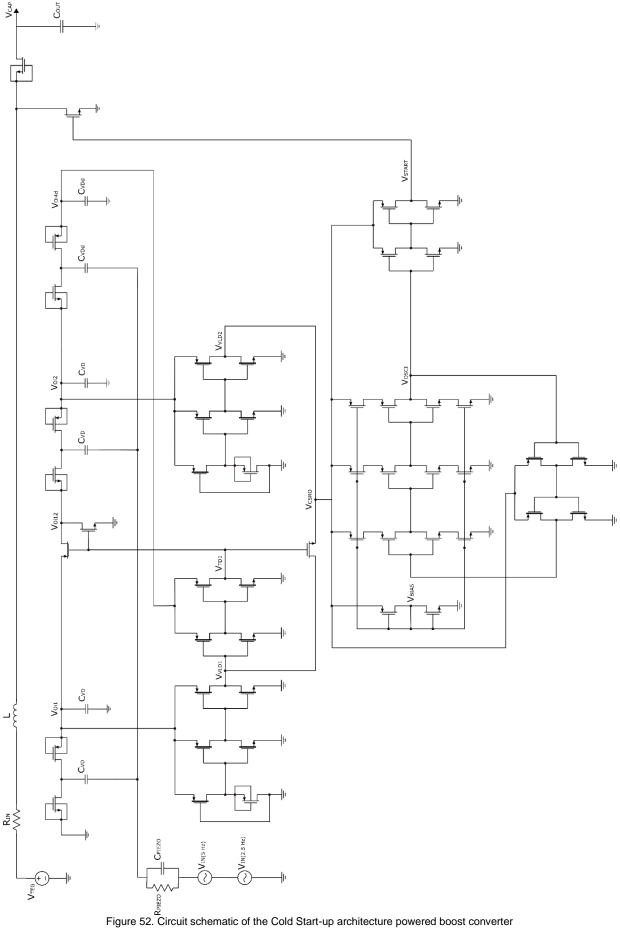

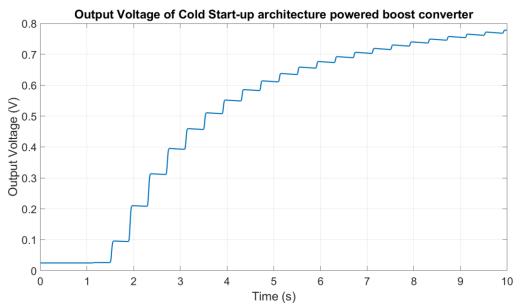

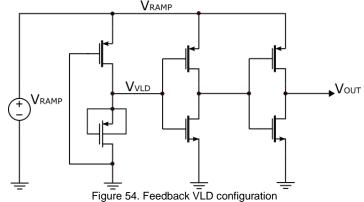

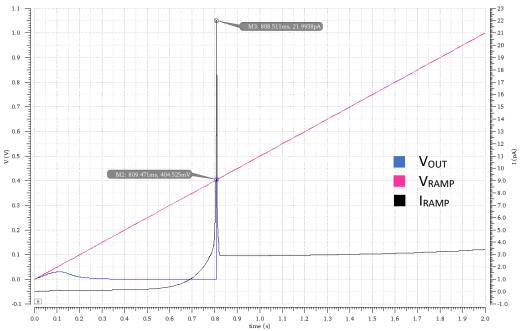

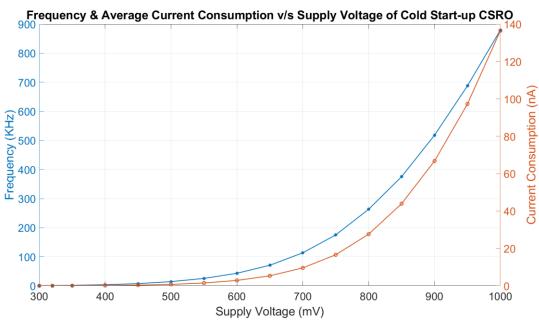

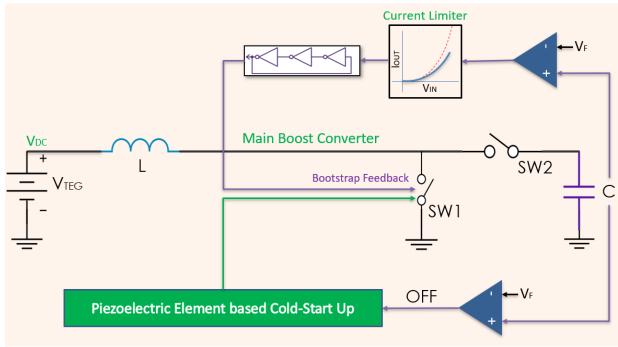

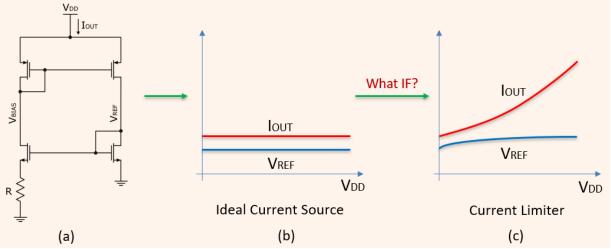

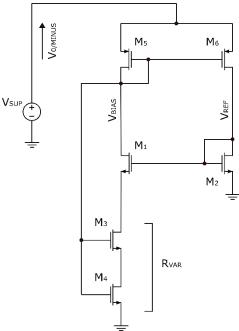

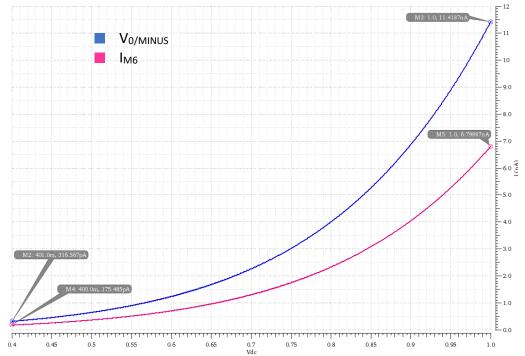

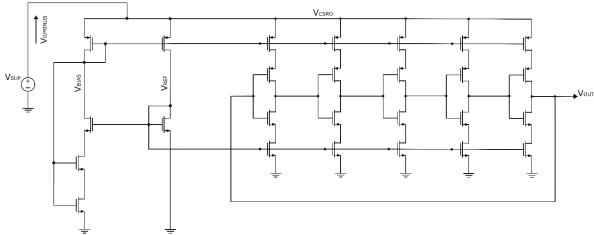

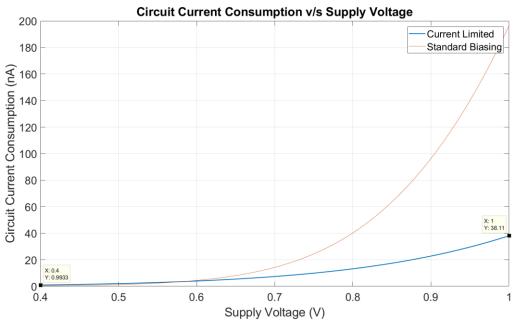

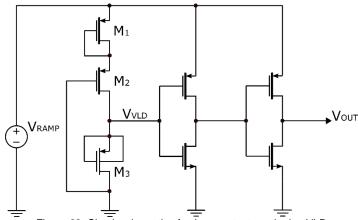

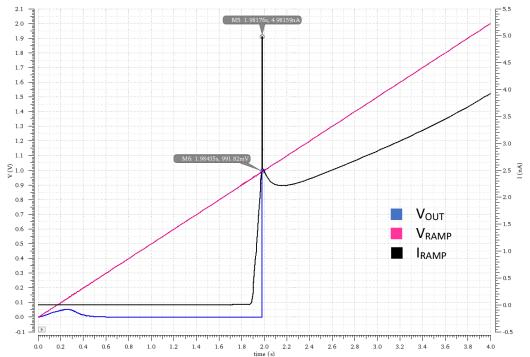

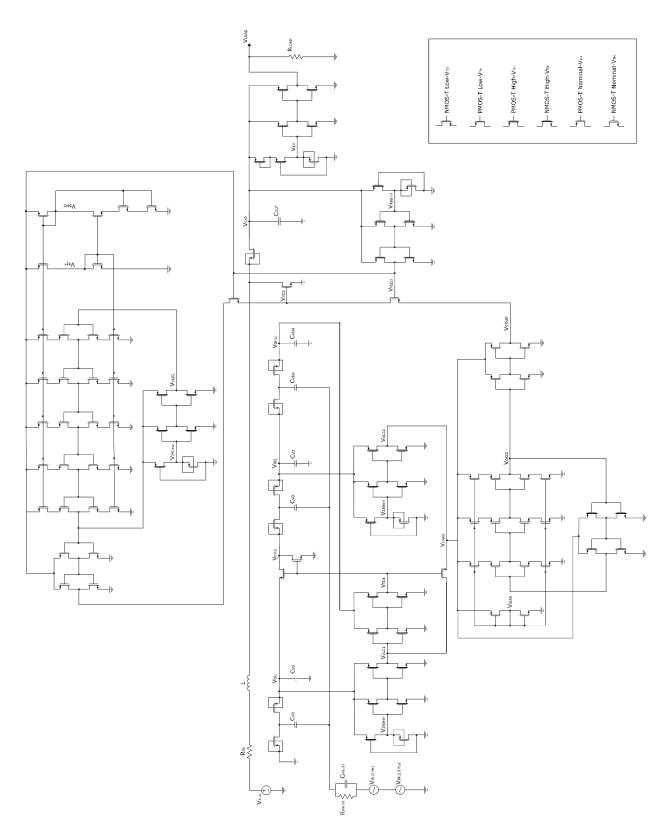

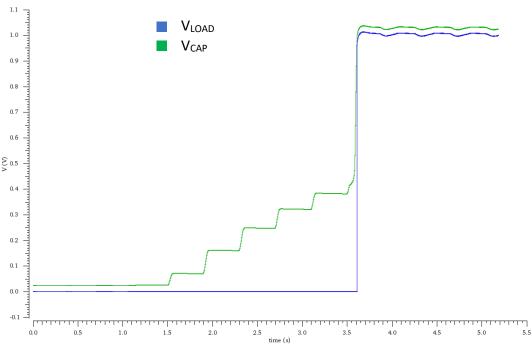

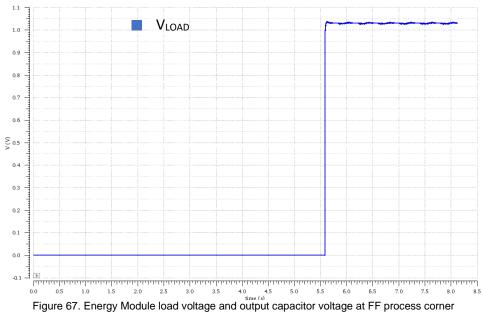

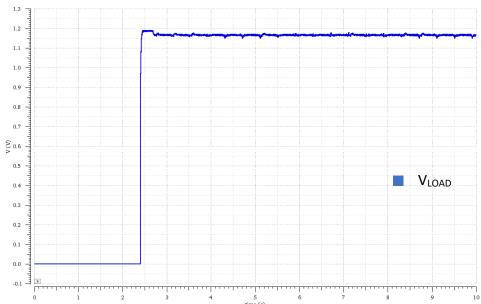

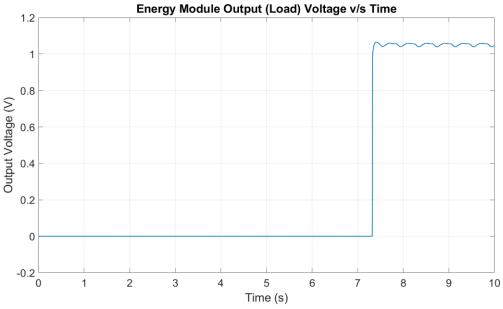

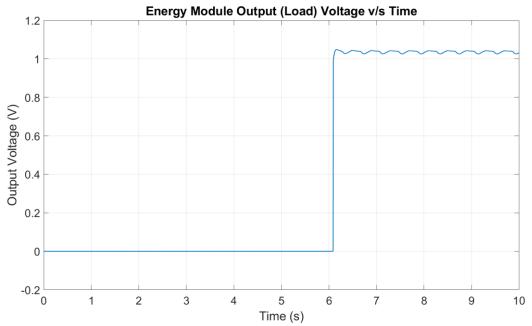

| Function            | Requires time-varying magnetic flux                                                                                              | Requires additional components to deliver power, cannot work independently                                                             | Requires additional components to deliver power, cannot work independently                                                             |