# A Chopper Class-D Amplifier for PSRR Improvement Over the Entire Audio Band

Zhang, Huajun; Rozsa, Nuriel N.M.; Berkhout, Marco; Fan, Qinwen

10.1109/JSSC.2022.3161136

**Publication date**

**Document Version** Final published version

Published in IEEE Journal of Solid-State Circuits

Citation (APA)

Zhang, H., Rozsa, N. N. M., Berkhout, M., & Fan, Q. (2022). A Chopper Class-D Amplifier for PSRR Improvement Over the Entire Audio Band. *IEEE Journal of Solid-State Circuits*, *57*(7), 2035 - 2044. Article 9745547. https://doi.org/10.1109/JSSC.2022.3161136

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A Chopper Class-D Amplifier for PSRR Improvement Over the Entire Audio Band

Huajun Zhang<sup>®</sup>, *Graduate Student Member, IEEE*, Nuriel N. M. Rozsa<sup>®</sup>, Marco Berkhout<sup>®</sup>, *Member, IEEE*, and Qinwen Fan, *Member, IEEE*

Abstract—The power supply rejection ratio (PSRR) of conventional differential closed-loop Class-D amplifiers is limited by the feedback and input resistor mismatch and finite commonmode rejection ratio (CMRR) of the operational transconductance amplifier (OTA) in the first integrator. This article presents a 14.4-V Class-D amplifier employing chopping to tackle the mismatch, thereby improving the PSRR. However, choppinginduced intermodulation (IM) within a pulsewidth modulation (PWM)-based Class-D amplifier can severely degrade PSRR and linearity. Techniques to mitigate such IM are proposed and analyzed. To chop the 14.4-V PWM output signal, a highvoltage (HV) chopper employing double-diffused MOS (DMOS) transistors is developed. Its timing is carefully aligned with that of the low-voltage (LV) choppers to avoid further linearity degradation. The prototype, fabricated in a 180-nm BCD process, achieves a PSRR of >110 dB at low frequencies, which remains above 79 dB up to 20 kHz. It achieves a total harmonic distortion (THD) of -109.1 dB and can deliver a maximum of 14 W into an 8-Ω load with 93% efficiency while occupying a silicon area of 5 mm<sup>2</sup>.

Index Terms—Audio power amplifier, Class-D amplifier, intermodulation (IM), power supply rejection ratio (PSRR), total harmonic distortion (THD).

#### I. INTRODUCTION

CLASS-D amplifiers achieve high power efficiency by switching the output directly to the supply or ground, making them popular in audio applications. However, this inevitably leads to supply sensitivity. To reduce the supply sensitivity, a straightforward solution is to employ a well-regulated supply, but this increases cost. Alternatively, a supply filter can be used. However, for sufficient filtering within the audio band, bulky filter components are required. Hence, most monolithic Class-D amplifiers employ a closed-loop architecture, where the supply-induced error is suppressed by the loop gain [1]–[3], along with the distortion introduced in the output stage.

However, many closed-loop Class-D amplifiers, including [1]–[3], employ the bridge-tied load (BTL) configuration

Manuscript received November 26, 2021; revised February 15, 2022; accepted March 11, 2022. Date of publication March 31, 2022; date of current version June 29, 2022. This article was approved by Associate Editor Rabia Tugce Yazicigil. (Corresponding author: Qinwen Fan.)

Huajun Zhang, Nuriel N. M. Rozsa, and Qinwen Fan are with the Department of Microelectronics, Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS), Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: q.fan@tudelft.nl).

Marco Berkhout is with Goodix Technologies, 6537 TL Nijmegen, The Netherlands.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2022.3161136.

Digital Object Identifier 10.1109/JSSC.2022.3161136

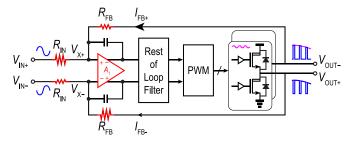

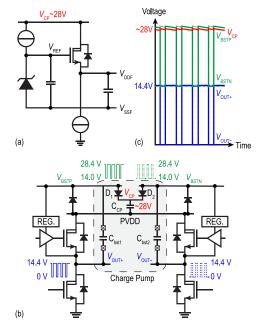

Fig. 1. Conventional closed-loop Class-D amplifier in a BTL configuration and sources of limited PSRR: feedback resistor mismatch, input resistor mismatch, and finite CMRR of the OTA in the first integrator.

(Fig. 1), where the power supply rejection ratio (PSRR) of the Class-D amplifier not only depends on the loop gain but is also limited by the matching between the  $R_{\rm IN}$  and  $R_{\rm FB}$  pairs [4], [5]. Therefore, these components should be laid out carefully to minimize their mismatch [6]. However, as will be explained in Section II, to achieve a PSRR of more than 100 dB, the  $R_{\rm IN}$  and  $R_{\rm FB}$  pairs must match within 10 ppm, requiring excessive area or expensive trimming for high yield. The pseudo-differential structure can alleviate this tradeoff at the expense of increased noise, silicon area, and a loss in the output signal swing due to common-mode offset and its drift [5], which is exacerbated in Class-D amplifiers with a high closed-loop gain.

In [7] and [8], this problem is addressed by closed-loop control of the Class-D amplifier's output common mode, which significantly improves the PSRR at low frequencies. However, the efficacy of this technique diminishes at high frequencies toward 20 kHz as the loop gain rolls off and the effects of mismatch re-emerge. Although chopping is a well-known technique for tackling mismatch [9], it has not been applied to the main signal path in Class-D amplifiers due to the presence of chopping-induced intermodulation (IM), which could demodulate high-frequency pulsewidth modulation (PWM) components at the switching output node into the audio band and degrade linearity [10].

This article improves the PSRR of a closed-loop Class-D amplifier in the BTL configuration by addressing the mismatch through chopping. Analysis shows that by choosing the chopping frequency ( $f_{\rm CH}$ ) to be an odd subharmonic of the PWM switching frequency ( $f_{\rm SW}$ ), even-order nonlinearity and PSRR degradation due to chopping-induced IM can be largely avoided. Furthermore, timing skew between the choppers reduces the linear output swing and thus should be

0018-9200 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

minimized. A 14.4-V Class-D amplifier prototype is designed in a 180-nm BCD process, which achieves a total harmonic distortion (THD) of -109.1 dB. The minimum PSRR across eight samples is >110 dB at low frequencies and remains above 79 dB at 20 kHz, which improves over the previous high-voltage (HV) Class-D amplifiers [8], [11]–[13] by 17 dB.

This article is an extension of [14] and is organized as follows. Section II analyzes the causes of PSRR limitations in conventional Class-D amplifiers. Section III introduces the architecture of the proposed chopper Class-D amplifier, analyzes the effects of chopping-induced IM on PSRR and THD, and presents methods to minimize its impact. Section IV presents the circuit design to implement chopping in the 14.4-V Class-D amplifier. Section V presents the measurement results, followed by a conclusion in Section VI.

#### II. EFFECT OF MISMATCHES ON PSRR

This section discusses how PSRR is limited by various sources of mismatch in conventional Class-D amplifiers employing the BTL configuration switching in AD mode (i.e., fully differential switching [15]).

For the Class-D amplifier shown in Fig. 1, the in-band component of the output common mode equals half the supply, which also modulates the common mode at the virtual ground  $(V_X)$  of  $A_1$

$$\Delta V_{X1,\text{CM}} = \frac{R_{\text{IN}}}{R_{\text{FB}} + R_{\text{IN}}} \Delta V_{\text{OUT,CM}} = \frac{R_{\text{IN}}}{2(R_{\text{FB}} + R_{\text{IN}})} \Delta V_{\text{PVDD}}.$$

(1)

Resistor mismatch and finite common-mode rejection ratio (CMRR) of  $A_1$  will then limit the Class-D amplifier's PSRR.

#### A. Resistor Mismatch

A straightforward analysis of Fig. 1 shows that the PSRR due to  $R_{\rm FB}$  mismatch is given by [5]

$$PSRR_{\Delta R_{FB}} = \frac{R_{FB}}{\Delta R_{FB}} \frac{2A+2}{2A+1}$$

(2)

where  $A = R_{\rm FB}/R_{\rm IN}$  is the closed-loop gain of the Class-D amplifier. For an HV Class-D amplifier,  $A \gg 1$ , thus, the PSRR is approximately  $R_{\rm FB}/\Delta R_{\rm FB}$ .

Similarly, the PSRR limit due to  $\Delta R_{IN}$  is given by

$$PSRR_{\Delta R_{IN}} = \frac{R_{IN}}{\Delta R_{IN}} \frac{2A+2}{A}.$$

(3)

Compared with (2), for HV Class-D amplifiers, PSRR is less sensitive to  $R_{\rm IN}$  mismatch only by about a factor of 2 compared to  $R_{\rm FB}$  mismatch.

#### B. Finite CMRR of $A_1$

Due to  $\Delta V_{X1,CM}$  and the finite CMRR of  $A_1$ , the  $A_1$ 's virtual ground will be offset by

$$\left|\Delta V_{X1,\text{DM}}\right| = \left|\frac{\Delta V_{X1,\text{CM}}}{\text{CMRR}_{A1}}\right|. \tag{4}$$

Following the definition of CMRR [16], therefore, the Class-D amplifier's output will vary by

$$\Delta V_{\text{OUT}} = \frac{R_{\text{IN}} + R_{\text{FB}}}{R_{\text{IN}}} \Delta V_{X1,\text{DM}} = \frac{R_{\text{IN}} + R_{\text{FB}}}{R_{\text{IN}}} \frac{\Delta V_{X1,\text{CM}}}{\text{CMRR}_{A1}}.$$

(5)

Substituting  $\Delta V_{X1,CM}$  with (1), the PSRR due to the finite CMRR of  $A_1$  is given by

$$PSRR_{A1} = \frac{R_{IN}}{R_{IN} + R_{FB}} \frac{2(R_{FB} + R_{IN})}{R_{IN}} CMRR_{A1}$$

= 2CMRR<sub>A1</sub>. (6)

#### III. CHOPPER CLASS-D AMPLIFIER ARCHITECTURE

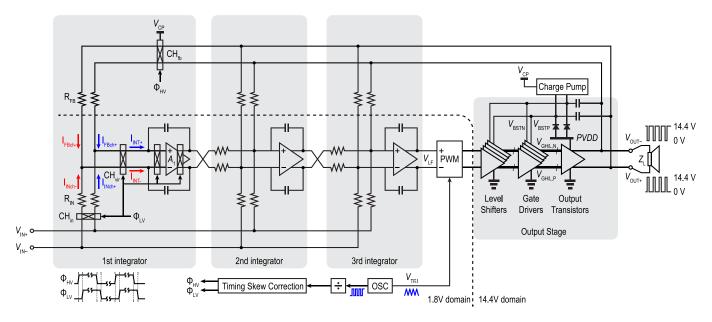

This work aims to improve the PSRR by tackling the mismatch through chopping. Fig. 2 shows the architecture of the proposed Class-D amplifier, which employs AD mode fixed-frequency PWM. The  $R_{\rm IN}$  and  $R_{\rm FB}$  pairs are swapped periodically with choppers  ${\rm CH_{in}}$ ,  ${\rm CH_{fb}}$ , and  ${\rm CH_{vir}}$  such that they contribute equally to the two differential halves over time. The operational transconductance amplifier (OTA)  $A_1$  is also chopped to improve its CMRR. Intuitively, with chopping,  $\Delta R_{\rm FB}$  and  $\Delta R_{\rm IN}$  in (2) and (3) are now set by the ON-resistance mismatch of the chopper switches, which can be made much smaller with reasonable sizing.

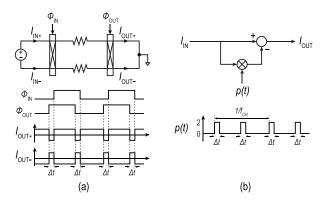

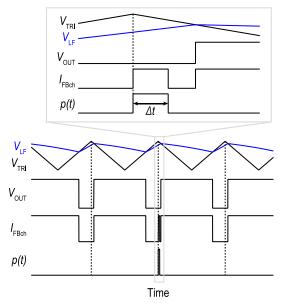

Conventionally, in continuous-time circuitry, chopping has been primarily applied to low-frequency small analog signals. In this work, however, significant HV high-frequency PWM components are present, and thus, the IM products between PWM and chopping should be carefully considered. It should be noted that no IM would occur when any signals pass through only two ideal choppers with perfect timing, if the circuit in between has no delay and infinite bandwidth. In practice, timing skew between the input and output choppers leads to IM. This is shown in Fig. 3, where two resistors are chopped, as is the case for, e.g.,  $R_{\rm FB}$ . When the chopping clocks are skewed by  $\Delta t$ ,  $I_{OUT}(t)$  contains an additional component equal to  $v_{\rm IN}(t)p(t)$ , where p(t) is a pulse train with a period of  $1/(2f_{CH})$ , a width of  $\Delta t$ , and a height of 2. Such a scenario must be considered in HV Class-D amplifiers since the HV and low-voltage (LV) choppers are implemented differently and, therefore, can exhibit significant timing skew.

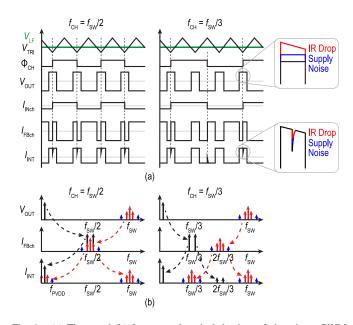

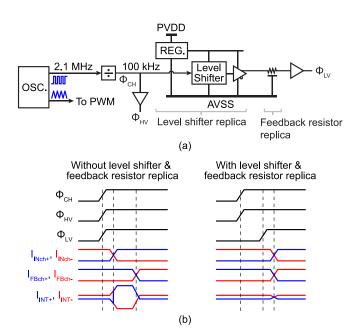

In a PWM-based Class-D amplifier, the output state (high/low) of  $V_{SW}$  is determined by comparing the loop filter output  $V_{LF}$  with a triangle carrier  $V_{TRI}$ . Therefore, by aligning the chopping transitions with the peaks of  $V_{TRI}$ , sampling of the signal-dependent transitions in  $V_{OUT}$  by p(t) can be avoided, which would otherwise lead to signal-dependent IM products. This can be ensured by chopping at the peaks of the triangle wave used for PWM operation, as shown in Fig. 4(a). To the first order, this makes the IM products signalindependent. However, the output waveform of a practical Class-D amplifier includes the supply noise and IR drop components. By choosing  $f_{CH}$  as an even or odd subharmonic of  $f_{SW}$ , p(t) would sample either  $V_{PVDD} - I_{out}(t)R_{on}$  at  $2f_{CH}$ or sample  $V_{\text{PVDD}} - I_{\text{out}}(t)R_{\text{on}}$  and  $-V_{\text{PVDD}} - I_{\text{out}}(t)R_{\text{on}}$  in an alternating fashion at  $2f_{CH}$ , as shown in Fig. 4(a), where  $I_{\text{out}}(t)$  is the audio band signal current plus high-frequency

Fig. 2. Top-level block diagram of the proposed chopper Class-D amplifier.

Fig. 3. Effect of chopper timing skew in the time domain. (a) Circuit model and (b) block diagram, and their respective waveform.

ripple current and  $R_{\rm on}$  is the ON-resistance of the output transistors. Sampling  $V_{\rm PVDD}$  could affect the PSRR, while sampling  $I_{\rm out}(t)R_{\rm on}$  could affect the THD. These will be analyzed in detail in the following.

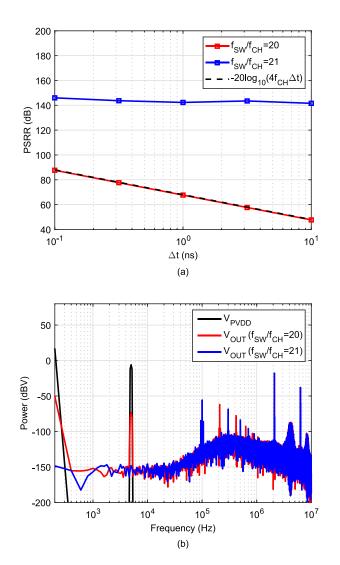

#### A. Impact of IM on PSRR

By definition of the Class-D operation, the PWM output waveform is amplitude-modulated by  $V_{\rm PVDD}$ . Assuming that  $V_{\rm PVDD}$  is modulated by a sinusoid at frequency  $f_{\rm PVDD}$ , in the frequency domain, sidebands appear in the spectrum of  $V_{\rm SW}$  at  $(2n+1)f_{\rm SW} \pm f_{\rm PVDD}$ , where n is an integer, as shown (in blue) in Fig. 4(b).

When  $f_{\text{CH}}$  is an even subharmonic of  $f_{\text{SW}}$ , these sidebands are demodulated to  $f_{\text{PVDD}}$ , which becomes the limiting factor of the PSRR. This effect can be easily quantified in the time domain since p(t) effectively samples  $V_{\text{PVDD}}$  with the same polarity at each chopping transition, as shown in Fig. 4(a). Therefore, the IM product is given in the time domain by  $V_{\text{PVDD}}(t)p(t)$ . In the frequency domain, the component at  $f_{\text{PVDD}}$  is proportional to the dc component of p(t),

Fig. 4. (a) Time- and (b) frequency-domain behaviors of chopping a PWM signal.

which equals  $4f_{CH}\Delta t$  (Fig. 3). Hence, the PSRR due to the chopping-induced IM is given by

$$PSRR_{IM,even} = 20 \log_{10} \left( \frac{1}{4 f_{CH} \Delta t} \right). \tag{7}$$

On the other hand, when  $f_{\rm CH}$  is an odd subharmonic of  $f_{\rm SW}$ , the IM product's polarity alternates for each chopping transition and, in the spectrum, appears at  $f_{\rm CH} \pm f_{\rm PVDD}$ . Therefore, by choosing  $f_{\rm CH}$  sufficiently higher than 20 kHz, the IM products can be kept out of the audio band, as shown in Fig. 4(b).

Fig. 5 shows the simulated PSRR of the system shown in Fig. 2. The PWM switching frequency  $f_{SW} = 2.1$  MHz. Except for a timing skew  $\Delta t$  introduced in CH<sub>fb</sub> with respect

Fig. 5. (a) PSRR due to timing skew of  $CH_{fb}$  for  $f_{CH}=100$  kHz and  $f_{CH}=105$  kHz, from system-level simulations. (b) Spectra of the Class-D amplifier output  $V_{OUT}$  and supply voltage  $V_{PVDD}$  when  $\Delta t=1$  ns.

to all other choppers, all blocks are ideal. The PSRR is plotted versus  $\Delta t$  for  $f_{\rm CH}=100$  kHz and  $f_{\rm CH}=105$  kHz. When  $f_{\rm CH}=105$  kHz, the PSRR suffers as predicted by (7), whereas when  $f_{\rm CH}=100$  kHz, the PSRR remains high regardless of  $\Delta t$ .

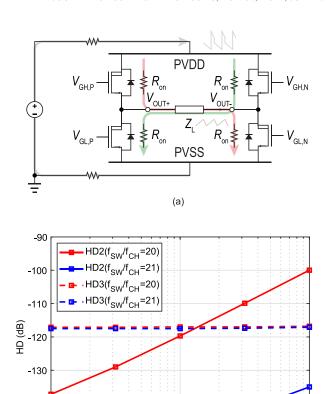

#### B. Impact of IM on Linearity

Aside from supply voltage variations,  $V_{\rm SW}$  also deviates from the ideal levels due to the IR drop in the output transistors and supply routing, as shown in Fig. 6(a). The load current consists of both audio band signal current and high-frequency PWM ripple current. For a sinusoidal input, it contains sidebands around multiples of  $f_{\rm SW}$  besides the audio signal. The sideband spacing around odd multiples of  $f_{\rm SW}$  is  $2Nf_{\rm IN}$ , whereas the sideband spacing around even multiples of  $f_{\rm SW}$  is  $(2N-1)f_{\rm IN}$  [17], [18], where N is a positive integer. The strongest sidebands are located around  $f_{\rm SW}$ .

If  $f_{CH}$  is chosen as an even subharmonic of  $f_{SW}$ , the strongest sideband components are demodulated to base-

Fig. 6. (a) IR drop due to the parasitic resistance in the supply routing and ON-resistance of the output transistors. (b) HD due to timing skew of  $CH_{fb}$  for  $f_{CH}=100$  kHz and  $f_{CH}=105$  kHz, from system-level simulations.

10<sup>0</sup>

$\Delta t$  (ns)

(b)

10<sup>1</sup>

-140

-150

10<sup>-1</sup>

band and contribute to even-order harmonic distortion (HD) [Fig. 4(b) red]. This is avoided if  $f_{CH}$  is chosen as an odd subharmonic of  $f_{SW}$ . Nevertheless, in both cases, the sidebands around even multiples of  $f_{SW}$  are demodulated into odd-order HD. Fortunately, these sidebands located at higher frequencies are lower in amplitude than those around  $f_{SW}$ . The IR drop induced by these sidebands components is further reduced by the increasing inductive impedance of the speaker [19], leading to less IM distortion.

An analytical derivation for the HD involving the Fourier series expansion of the PWM waveform of  $V_{\rm OUT}$  [17] would be lengthy. For brevity, Fig. 6(b) shows the simulated HD due to chopping-induced IM for  $f_{\rm CH}=100$  kHz and  $f_{\rm CH}=105$  kHz. All circuit blocks are ideal except for a timing skew  $\Delta t$  that is introduced in CH<sub>fb</sub> with respect to other choppers. The load impedance  $Z_L$  is 8  $\Omega$  in series with 44  $\mu$ H to represent a realistic speaker model. The supply routing resistance adds additional IR drop and therefore is modeled and assumed to be 50 m $\Omega$  and  $R_{\rm on}=150$  m $\Omega$  [Fig. 6(a)] is assumed, to balance gate charging loss and conduction loss in the output stage. As discussed above, choosing  $f_{\rm CH}=100$  kHz avoids evenorder HD even with excessive  $\Delta t$ . Moreover, since the IR drop induced by the PWM components is attributed to the ripple current, the relatively large inductance exhibited in a

Fig. 7. Transient waveform in the closed-loop chopper Class-D amplifier ( $f_{\rm SW}/f_{\rm CH}>1$ ).

loudspeaker helps keep this distortion below -100 dB. The constant HD3, on the other hand, is attributed to the inherent PWM residual aliasing distortion and therefore is independent of  $\Delta t$  [20].

Although minimizing  $\Delta t$  does not seem to improve HD once  $f_{\rm CH}$  is chosen to be the odd subharmonic of  $f_{\rm SW}$ , it is only true when p(t) does not sample the transitions of  $V_{\rm SW}$ . Minimizing  $\Delta t$  is still essential for maximizing the linear output swing of the chopper Class-D amplifier. This is because in a closed-loop Class-D amplifier, the output of the loop filter  $V_{\rm LF}$  (Fig. 2) contains residual PWM ripple, which skews the center of the PWM pulses away from the triangle wave peaks [20], as shown in Fig. 7. As the Class-D feedback loop's unity-gain frequency ( $f_U$ ) is increased toward the maximum of  $f_{\rm PWM}/\pi$  for maximal loop gain [21], the interval between a triangle wave peak and the next PWM transition is further reduced. Once this interval reduces below  $\Delta t$ , which is likely to happen under a large input, distortion due to IM drastically increases.

#### C. Other Sources of IM

So far, only IM due to the timing skew between choppers is analyzed. In addition, two other circuit nonidealities can contribute to IM. First, when the circuit between the two choppers delays or filters the signal, glitches appear in the output waveform. This is the case when a pair of chopped resistors (e.g.,  $R_{\rm FB}$ ) exhibit nonnegligible parasitic capacitance or when a chopped transconductor (e.g., in the OTA of the first integrator) has finite bandwidth. The resulting IM can be described by a model similar to Fig. 3(b), where the pulse shape of p(t) is modified to capture the settling transient [22]. Second, when the OTA in the first integrator is chopped, the parasitic capacitors at the input and internal nodes inject charge packets into the integrator at each chopping transition. Effectively, chopping samples the voltage on these parasitic capacitors at  $2f_{\rm CH}$  [23].

Since both abovementioned IM mechanisms occur between the PWM signal and even harmonics of  $f_{\rm CH}$ , they can be largely mitigated by choosing  $f_{\rm CH}$  to be an odd subharmonic of  $f_{\rm SW}$ . Extra measures, such as compensating the resistor delay in the chopper clock generator and increasing the bandwidth and gain of the OTA [24], can further help minimize the residual IM effect, which will be explained in detail in Section IV.

### IV. CIRCUIT IMPLEMENTATION

#### A. Overview

The Class-D amplifier in this work uses a 14.4-V supply for the output stage and switches at  $f_{SW} = 2.1$  MHz to avoid interfering with the AM band and achieve high loop gain [11], [13]. A fully differential third-order loop filter based on active RC integrators is employed (Fig. 2) for high loop gain [13], [25], with  $f_U = 570$  kHz. The first stage of  $A_1$  is chopped to boost its CMRR and eliminate its 1/f noise. In a 200-run Monte Carlo simulation, chopping improves the worst case CMRR of  $A_1$  from 87 to 108 dB. The OTAs in the loop filter are designed in a two-stage feedforward compensated topology for high gain-bandwidth product (GBW), which helps to suppress IM at the virtual ground of the first integrator OTA due to chopping, as mentioned in Section III-C. To perform PWM, a differential triangle wave produced by an RC oscillator is compared with the loop filter output [25]. The input chopper employs conventional bootstrapping for high linearity.

Based on the analysis in Section II,  $f_{\rm CH}$  is chosen to be  $f_{\rm SW}/21 = 100$  kHz to avoid PSRR degradation and evenorder HD, while it is high enough to avoid IM around  $f_{\rm CH}$  from folding back into the audio band. If a higher  $f_{\rm CH}$  is used, more nonlinear glitches will be introduced by CH<sub>in</sub>, which must process an audio waveform, unlike the mostly two-level waveform in CH<sub>fb</sub>.

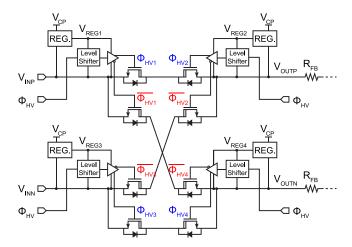

#### B. HV Chopper

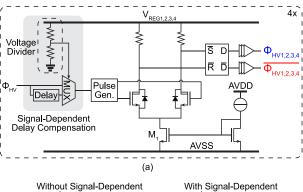

$CH_{fb}$  must handle the 14.4-V PWM output. As shown in Fig. 8, each switch consists of two back-to-back n-channel lateral DMOS (LDMOS) devices so that they can be completely turned off despite the presence of their body diodes. Level shifters are employed to translate the chopping clock to the floating gate drivers powered from floating regulators bootstrapped to the source nodes of each LDMOS switch. They are supplied by a charge pump that provides a dc voltage  $V_{CP}$  near 28 V.

Fig. 9(a) shows the regulator, in which a source follower buffers a Zener-based reference. The charge pump is shown in Fig. 9(b), which reuses the circuitry and takes advantage of the switching operation in the Class-D amplifier's output stage. Two off-chip bootstrap capacitors are employed to supply the high-side gate driver of the output stage [13]. They are charged to  $V_{\rm PVDD}$  due to the switching operation. Through Schottky diodes  $D_1$  and  $D_2$ , they charge  $V_{\rm CP}$  to  $\sim 2V_{\rm PVDD}$  [Fig. 9(c)], which is buffered by a small output capacitor  $C_{\rm CP}$  on-chip. Fig. 10(a) shows the level shifter, which is based on [25]. During each chopping transition, a current pulse pulls down one of the set-reset (SR)-latch inputs through

Fig. 8. Schematic of the HV chopper.

Fig. 9. (a) Floating regulator. (b) Charge pump. (c) Its timing diagram.

the corresponding pull-up resistors, thereby updating the level shifter's output.

#### C. Timing Skew Correction

As mentioned in Section III, the timing skew between  $\mathrm{CH_{fb}}$  and the other choppers reduces the linear output swing. The main source of timing skew comes from the level shifter, whose delay is the sum of a fixed and a signal-dependent component. The latter is due to the  $V_{\mathrm{DS}}$  modulation of the current source  $M_1$  by the signal level at the corresponding terminal of  $\mathrm{CH_{fb}}$ . To compensate for the signal-dependent delay, the voltage level (high/low) at each input and output terminal of  $\mathrm{CH_{fb}}$  (i.e.,  $V_{\mathrm{INN}}$ ,  $V_{\mathrm{INP}}$ ,  $V_{\mathrm{OUTN}}$ , and  $V_{\mathrm{OUTP}}$  in Fig. 8) is detected using a resistive voltage divider from  $V_{\mathrm{REG}}$ , and a compensation delay is switched in/out. Fig. 10(b) shows the effect of the signal-dependent delay. Without compensation, the resulting timing skew leads to asymmetry in the output

Fig. 10. (a) Level shifter with added signal-dependent delay compensation circuit. (b) Input–output and switch control signals in the HV chopper with and without compensation for the signal-dependent delay.

waveform, whose differential component can also be modeled using Fig. 3(b) with the pulse height modified to 1 for p(t). The compensation delay minimizes the asymmetry and the pulsewidth of the resulting p(t).

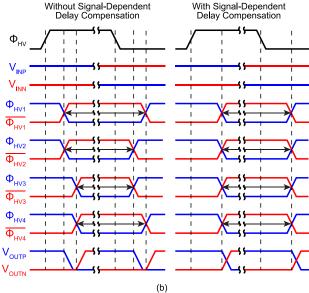

The fixed component of the level-shifter delay and the delay due to the parasitic capacitance of  $R_{\rm FB}$  is compensated by a replica-based delay line to ensure good tracking over process, voltage, and temperature (PVT) variations. Fig. 11(a) shows the clock paths for all the choppers. The 2.1-MHz oscillator produces a triangle wave and a digital clock signal that toggles whenever the triangle wave changes its ramp direction [25]. The latter is divided by 21, to 100 kHz to drive the choppers. The chopping clock's duty cycle error compromises the efficacy of chopping. The design of the oscillator and divider ensures an accurate duty cycle for the chopping clock. Fig. 11(b) shows the current waveform with and without the replica. The mismatch between the level shifters and the replica results in a residual timing skew. Nevertheless, Monte Carlo simulation shows that the replicabased timing skew correction reduces  $\Delta t$  from about 3.2 ns to

<sup>&</sup>lt;sup>1</sup>The process design kit (PDK) does not include a mismatch model for the two LDMOS devices in the level shifter, so their mismatch contribution is not included.

Fig. 11. (a) Replica delay circuit to align chopping transitions of HV and LV choppers. (b) HV and LV chopper clock signals and resulting input, feedback, and integrator current (annotated in Fig. 2) with and without the replica delay circuit

Fig. 12. Die micrograph.

within 200 ps. The input signal range with p(t) and transitions of  $V_{\rm SW}$  colliding is reduced from 12% to well below 1% of the full scale.

## V. MEASUREMENT RESULTS

A prototype of the proposed chopper Class-D amplifier is fabricated in a 180-nm BCD process, and the die occupies 5 mm². Fig. 12 shows the die micrograph. The HV chopper and timing skew correction circuitry occupy 0.37 mm². For testability, the divide ratio between  $f_{\rm SW}$  and  $f_{\rm CH}$  is made programmable. The amplifier is loaded with 8  $\Omega$  in series with 44  $\mu$ H, and its output is measured by an Audio Precision APx555 audio signal analyzer. The output stage supply is generated using a Keysight N6705C and also monitored by the APx555.

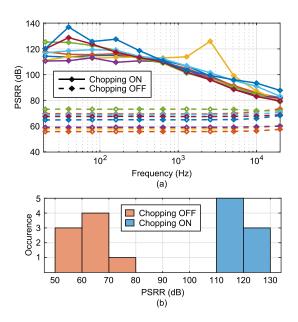

Fig. 13 shows the measured PSRR across the entire audio band, where  $V_{\text{PVDD}}$  is modulated by a  $2V_{\text{PP}}$  sinusoid.

Fig. 13. (a) Measured PSRR versus  $f_{PVDD}$  of eight samples with chopping ON (solid) and OFF (dashed). (b) Histogram at 20 Hz.

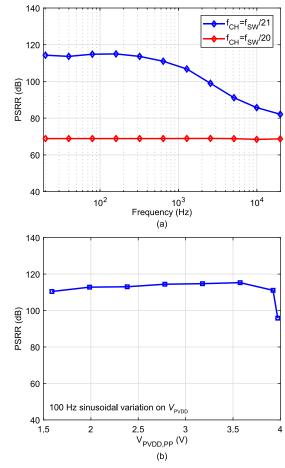

Fig. 14. (a) PSRR comparison between odd ( $f_{\rm CH}=100~{\rm kHz}$ ) and even ( $f_{\rm CH}=105~{\rm kHz}$ ) ratios between  $f_{\rm CH}$  and  $f_{\rm SW}$ . (b) Measured PSRR as the magnitude of the sinusoidal supply variation is increased.

The PSRR when chopping is turned off is shown in the dashed lines, showing a spread due to random mismatch of the resistors in the feedback network, with an average of

<sup>&</sup>lt;sup>2</sup>The results reported here are obtained from a silicon revision of [14], which fixes a bond pad issue in [14] that caused the THD to degrade at large-signal levels.

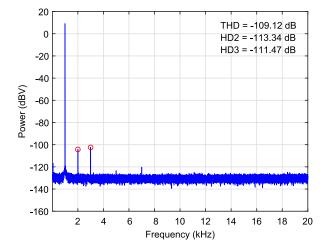

Fig. 15. Measured output spectrum at an output power of 1 W.

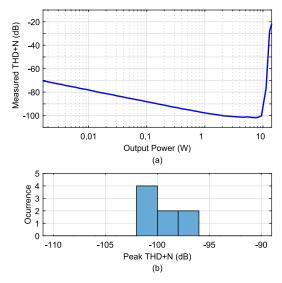

Fig. 16. (a) Measured THD+N across output power. (b) Peak THD+N for eight samples.

about 65 dB. When chopping is enabled, the worst case PSRR is improved by over 20 dB over the entire audio band, reaching a minimum of 110 dB at 20 Hz and 79 dB at 20 kHz. The worst case PSRR without chopping is below 60 dB. Achieving a PSRR of more than 100 dB through brute-force sizing would thus require the feedback resistors' width and length to be increased by more than 100 times [26], and their area would increase from 0.00016 mm<sup>2</sup> of this work to above 1.6 mm<sup>2</sup>, which is more than four times larger than the area of the HV chopper and timing skew correction circuitry. Fig. 14(a) compares the PSRR performance when  $f_{CH}$  is programmed to  $f_{SW}/21$  and  $f_{SW}/20$  for the same sample. The PSRR is severely degraded when  $f_{\rm CH} = f_{\rm SW}/20$ , as mentioned in Section III. Fig. 14(b) shows the measured PSRR when the magnitude of the sinusoidal variation on  $V_{PVDD}$  is increased. The PSRR stays consistently high until the magnitude reaches about  $4V_{PP}$ , at which point the virtual ground of  $A_1$  goes beyond 1.8 V, causing its input pair to operate in triode.

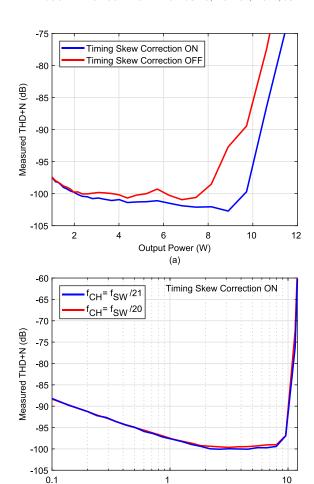

Fig. 17. THD+N comparison (a) with and without timing skew correction and (b) for  $f_{\rm CH}=f_{\rm SW}/21$  and  $f_{\rm CH}=f_{\rm SW}/20$ .

Output Power (W)

(b)

Fig. 15 shows the measured output spectrum when the amplifier delivers 1 W into the load, in which a THD of -109.1 dB is achieved. Fig. 16 shows the measured THD plus noise (THD+N). The prototype reaches a typical peak THD+N of -100 dB, and it can deliver a maximum of 13 W into an 8- $\Omega$  load at 10% THD. Fig. 17(a) plots the THD+N of a sample when the timing skew correction circuitry is intentionally bypassed and compares it with that during normal operation. As expected, timing skew correction significantly improves the linearity above 8 W. Fig. 17(b) compares the THD+N for  $f_{\rm CH} = f_{\rm SW}/21$  and  $f_{\rm CH} = f_{\rm SW}/20$ , which is similar and agrees with the prediction of Fig. 6(b) for a small  $\Delta t$ .

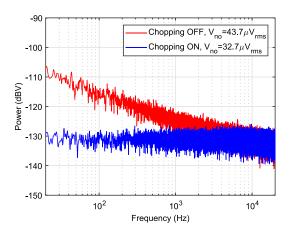

Fig. 18 compares the output spectrum with the input shorted when chopping is turned on and off. Flicker noise is clearly suppressed by chopping, and the A-weighted integrated output noise is reduced from 43.7 to 32.7  $\mu$ V.

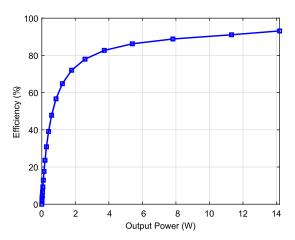

Fig. 19 shows the measured power efficiency across output power. The prototype achieves a peak efficiency of 93%. The slight improvement from that reported in [14] is likely due to the improved thermal conductivity of the test assembly.

Table I summarizes the performance of this work and compares it with other state-of-the-art Class-D amplifiers with output power above 10 W. This work achieves > 17 dB higher

|                        | This Work      | D. Schinkel [8]<br>JSSC 2017 | TAS6424 [11]   | E. Cope [12]<br>ISSCC 2018 | S. Karmakar [13]<br>ISSCC 2020     |

|------------------------|----------------|------------------------------|----------------|----------------------------|------------------------------------|

| Input                  | Analog         | Digital                      | Digital        | Digital                    | Analog                             |

| Area (mm²)             | 5              | -                            | -              | 4.3                        | 4.8                                |

| Supply (V)             | 14.4           | 25                           | 14.4           | 8~20                       | 14.4                               |

| f <sub>sw</sub> (kHz)  | 2100           | 500                          | 2100           | 400                        | 2000                               |

| Quiescent Current (mA) | 21             | =                            | 180            | 20.5                       | 17                                 |

| Idle Power (mW)        | 300            | -                            | -              | -                          | 245                                |

| Output Power (W)       | 14             | 80                           | 75             | 20                         | 28                                 |

| Efficiency             | 93%            | >90%                         | 86%            | 90%                        | 91%                                |

| Peak THD+N @ 1kHz      | 0.001%         | 0.004%                       | 0.02%          | 0.0013%                    | 0.0008%                            |

| SNR (A-weighted)       | 108.7 dB       | -                            | -              | 116 dB                     | -                                  |

| DR (A-weighted)        | 110.2 dB       | 115 dB                       | -              | 115.5 dB                   | 109 dB                             |

| PSRR                   | 110 dB~79 dB   | 88 dB~60 dB                  | 75 dB~57 dB    | 80 dB~50 dB                | $70 \text{ dB} \sim 62 \text{ dB}$ |

| (Frequency Range)      | (20 Hz~20 kHz) | (100Hz~20kHz)                | (20 Hz~20 kHz) | (20 Hz~20 kHz)             | (20 Hz~20 kHz)                     |

| # Samples              | 8              | -                            | -              | -                          | -                                  |

$\label{eq:table_interpolation} \mbox{TABLE I}$  Performance Summary and Comparison

Fig. 18. Measured output spectrum with chopping ON and OFF when the input is shorted.

Fig. 19. Power efficiency across output power.

PSRR at both the low end and the high end of the audio band, due to the chopping technique. In the meantime, it achieves a competitive THD+N compared to [8], [11], [12]. Compared to [13], which is also an analog-input design with similar supply voltage and switching frequency, this works significantly improves the PSRR while achieving similar THD+N and dynamic range, at the expense of a slight increase in the idle power, consumed in the HV chopper.

#### VI. CONCLUSION

A 14.4-V Class-D amplifier using chopping to improve PSRR is presented. The timing of chopping and PWM is co-designed to avoid degrading PSRR and THD due to chopping-induced IM. An HV chopper design and timing skew correction circuits are applied to enable chopping in a 14.4-V amplifier. Measurement results of a 180-nm prototype show >17 dB of PSRR improvement across the entire audio band compared to prior works while achieving a competitive THD+N.

#### REFERENCES

- [1] L. Guo, T. Ge, and J. S. Chang, "A 101 dB PSRR, 0.0027% THD+N and 94% power-efficiency filterless class D amplifier," *IEEE J. Solid-State Circuits*, vol. 49, no. 11, pp. 2608–2617, Nov. 2014.

- [2] Y. Choi, W. Tak, Y. Yoon, J. Roh, S. Kwon, and J. Koh, "A 0.018% THD+N, 88-dB PSRR PWM class-D amplifier for direct battery hookup," *IEEE J. Solid-State Circuits*, vol. 47, no. 2, pp. 454–463, Feb. 2012.

- [3] M. Kinyua, R. Wang, and E. Soenen, "Integrated 105 dB SNR, 0.0031% THD+N class-D audio amplifier with global feedback and digital control in 55 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 8, pp. 1764–1771, Aug. 2015.

- [4] T. Ge, J. S. Chang, and W. Shu, "PSRR of bridge-tied load PWM Class D Amps," in *Proc. ISCAS*, May 2008, pp. 284–287.

- [5] K.-H. Chen and Y.-S. Hsu, "A high-PSRR reconfigurable class-AB/D audio amplifier driving a hands-free/receiver 2-in-1 loudspeaker," *IEEE J. Solid-State Circuits*, vol. 47, no. 11, pp. 2586–2603, Nov. 2012.

- [6] M. A. Teplechuk, A. Gribben, and C. Amadi, "True filterless class-D audio amplifier," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2784–2793, Dec. 2011.

- [7] W.-C. Wang and Y.-H. Lin, "A 118 dB PSRR, 0.00067% (-103.5 dB) THD+N and 3.1 w fully differential Class-D audio amplifier with PWM common mode control," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2808–2818, Dec. 2016.

- [8] D. Schinkel et al., "A multiphase class-D automotive audio amplifier with integrated low-latency ADCs for digitized feedback after the output filter," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3181–3193, Dec. 2017.

- [9] C. C. Enz and G. C. Temes, "Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization," *Proc. IEEE*, vol. 84, no. 11, pp. 1584–1614, Nov. 1996.

- [10] W.-C. Wang and Y.-H. Lin, "A 0.0004%(-108dB) THD+N, 112dB-SNR, 3.15 W fully differential Class-D audio amplifier with Gm noise cancellation and negative output-common-mode injection techniques," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 58–60.

- [11] Texas Instruments. 2-MHz Digital Input 4-Channel Automotive Class-D Audio Amplifier With Load-Dump Protection and I2C Diagnostics. Accessed: Jul. 15, 2020. [Online]. Available: https://www.ti. com/lit/gpn/tas6424-q1

- [12] E. Cope et al., "A 2–20W 0.0013% THD+N class-D audio amplifier with consistent performance up to maximum power level," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 56–58.

- [13] S. Karmakar *et al.*, "A 28-W, -102.2-dB THD+N class-D amplifier using a hybrid ΔΣM-PWM scheme," *IEEE J. Solid-State Circuits*, vol. 55, no. 12, pp. 3146–3156, Dec. 2020.

- [14] H. Zhang, N. Rozsa, M. Berkhout, and Q. Fan, "A -109.1 dB/-98 dB THD/THD+N chopper class-D amplifier with >83.7 dB PSRR over the entire audio band," in *Proc. ESSCIRC*, Sep. 2021, pp. 395–398.

- [15] X. Jiang, "Fundamentals of audio class D amplifier design: A review of schemes and architectures," *IEEE Solid-State Circuits Mag.*, vol. 9, no. 3, pp. 14–25, Aug. 2017.

- [16] B. Razavi, "Differential amplifiers," in *Design of Analog CMOS Integrated Circuits*. New York, NY, USA: McGraw-Hill, 2001, p. 123.

- [17] N. Anderskouv, K. Nielsen, and M. A. Andersen, "High-fidelity pulse-width modulation amplifiers based on novel double-loop feedback techniques," in *Proc. 100th AES Conv.*, May 1996, pp. 1–17.

- [18] W. Shu and J. S. Chang, "Power supply noise in analog audio class D amplifiers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 1, pp. 84–96, Jan. 2009.

- [19] R. Bortoni and H. Sette, "Loudspeakers' electric models for study of the efforts in audio power amplifiers," in *Proc. 115th AES Convention*, Oct. 2003, pp. 1–9.

- [20] S.-H. Chien, Y.-W. Chen, and T.-H. Kuo, "A low quiescent current, low THD+N class-D audio amplifier with area-efficient PWM-residualaliasing reduction," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3377–3385, Dec. 2018.

- [21] M. Berkhout, L. Breems, and E. van Tuijl, "Audio at low and high power," in *Proc. ESSCIRC*, Sep. 2008, pp. 40–49.

- [22] T. Rooijers, S. Karmakar, Y. Kusuda, J. H. Huijsing, and K. A. A. Makinwa, "A fill-in technique for robust IMD suppression in chopper amplifiers," *IEEE J. Solid-State Circuits*, vol. 56, no. 12, pp. 3583–3592, Dec. 2021.

- [23] S. Billa, A. Sukumaran, and S. Pavan, "Analysis and design of continuous-time delta-sigma converters incorporating chopping," *IEEE J. Solid-State Circuits*, vol. 52, no. 9, pp. 2350–2361, Sep. 2017.

- [24] R. Theertham and S. Pavan, "Unified analysis, modeling, and simulation of chopping artifacts in continuous-time delta-sigma modulators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 8, pp. 2831–2842, Aug. 2019.

- [25] H. Zhang et al., "A high-linearity and low-EMI multilevel class-D amplifier," *IEEE J. Solid-State Circuits*, vol. 56, no. 4, pp. 1176–1185, Apr. 2021.

- [26] A. Hastings, "Matching of resistors and capacitors," in *The Art Analog Layout*. Upper Saddle River, NJ, USA: Prentice-Hall, 2006, p. 259.

Huajun Zhang (Graduate Student Member, IEEE) received the B.E. degree in electrical and computer engineering from Shanghai Jiao Tong University, Shanghai, China, in 2015, and the B.S.E. and M.S. degrees in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2015 and 2017, respectively. He is currently pursuing the Ph.D. degree with the Delft University of Technology, Delft, The Netherlands.

In summer 2016, he was an Analog/Mixed-Signal Design Intern with Analog Devices, Inc., Wilming-

ton, MA, USA. From May 2017 to February 2019, he was a Mixed Signal Design Engineer with Analog Devices, Inc., Norwood, MA, USA. He joined the Electronic Instrumentation Laboratory, Delft University of Technology, in March 2019. He holds one U.S. patent. His technical research interests include precision analog circuits, Class-D audio amplifiers, and ultralow-power data converters.

Mr. Zhang has served as a Reviewer for the IEEE OPEN JOURNAL OF THE SOLID-STATE CIRCUITS SOCIETY, the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS, the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II: EXPRESS BRIEFS, and the IEEE SENSORS JOURNAL.

**Nuriel N. M. Rozsa** received the B.Sc. degree (*cum laude*) in electrical engineering through the Honors Program and the M.Sc. degree in microelectronics from the Delft University of Technology, Delft, The Netherlands, in 2018 and 2021, respectively.

Since May 2021, he has been employed with the Electronic Instrumentation Laboratory, Delft University of Technology, as an Analog/Mixed-Signal Designer for the Ultra-X-Treme Research Program. His current research interests include analog/mixed-signal circuits, 3-D ultrasound probes, sensor interfaces, and Class-D audio amplifiers.

Marco Berkhout (Member, IEEE) received the M.Sc. degree in electrical engineering and the Ph.D. degree from the University of Twente, Enschede, The Netherlands, in 1992 and 1996, respectively.

From 1996 to 2019, he was with Philips/NXP Semiconductors, Nijmegen, The Netherlands. He is currently a Fellow with Goodix Technologies, Nijmegen. His main research interests are Class-D amplifiers and integrated power electronics.

Dr. Berkhout was a member of the Technical Program Committee of the European Solid-

State Circuits Conference (ESSCIRC) from 2008 to 2018 and the ISSCC from 2013 to 2016. He serves as a member of the Technical Program Committee of the International Solid-State Circuits Conference (ISSCC). He was a recipient of the 2002 ESSCIRC Best Paper Award and was a plenary invited speaker on audio at low and high powers at the 2008 ESSCIRC.

Qinwen Fan (Member, IEEE) received the B.Sc. degree in electronic science and technology from Nankai University, Tianjin, China, in 2006, and the M.Sc. degree (*cum laude*) in microelectronics and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2008 and 2013, respectively.

From August 2007 to August 2008, she was an Intern with NXP Research Laboratories, Eindhoven, The Netherlands, where she designed a precision instrumentation amplifier for biomedical purposes.

From October 2012 to May 2015, she worked with Maxim Integrated Products, Delft. From June 2015 to January 2017, she worked with Mellanox, Delft. Since 2017, she has been with the Delft University of Technology, where she is currently an Assistant Professor with the Electronics and Instrumentation Laboratory. Her current research interests include precision analog, class D audio amplifiers, dc–dc converters for energy harvesters, and current-sensing amplifiers.

Dr. Fan currently serves as a TPC member of the International Solid-State Circuits Conference (ISSCC), Very Large Scale Integration (VLSI) Symposium on Technology and Circuits, and European Solid-State Circuits Conference (ESSCIRC). She is also an Associate Editor of the IEEE OPEN JOURNAL OF THE SOLID-STATE CIRCUITS SOCIETY (OJ-SSCS).