# Analysis and Design of a Multi-Core Oscillator for Ultra-Low Phase Noise

Ahmadi-Mehr, S. A. R.; Tohidian, M.; Staszewski, R. B.

10.1109/TCSI.2016.2529218

**Publication date**

**Document Version** Final published version

Published in

IEEE Transactions on Circuits and Systems Part 1: Regular Papers

**Citation (APA)**Ahmadi-Mehr, S. A. R., Tohidian, M., & Staszewski, R. B. (2016). Analysis and Design of a Multi-Core Oscillator for Ultra-Low Phase Noise. *IEEE Transactions on Circuits and Systems Part 1: Regular Papers*, *63*(4), 529-539. https://doi.org/10.1109/TCSI.2016.2529218

# Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Analysis and Design of a Multi-Core Oscillator for Ultra-Low Phase Noise

Seyed Amir-Reza Ahmadi-Mehr, *Member, IEEE*, Massoud Tohidian, *Member, IEEE*, and Robert Bogdan Staszewski, *Fellow, IEEE*

Abstract—In this paper, we exploit an idea of coupling multiple oscillators to reduce phase noise (PN) to beyond the limit of what has been practically achievable so far in a bulk CMOS technology. We then apply it to demonstrate for the first time an RF oscillator that meets the most stringent PN requirements of cellular basestation receivers while abiding by the process technology reliability rules. The oscillator is realized in digital 65-nm CMOS as a dualcore LC-tank oscillator based on a high-swing class-C topology. It is tunable within 4.07-4.91 GHz, while drawing 39-59 mA from a 2.15 V power supply. The measured PN is -146.7 dBc/Hz and -163.1 dBc/Hz at 3 MHz and 20 MHz offset, respectively, from a 4.07 GHz carrier, which makes it the lowest reported normalized PN of an integrated CMOS oscillator. Straightforward expressions for PN and interconnect resistance between the cores are derived and verified against circuit simulations and measurements. Analysis and simulations show that the interconnect resistance is not critical even with a 1% mismatch between the cores. This approach can be extended to a higher number of cores and achieve an arbitrary reduction in PN at the cost of the power and area.

*Index Terms*—Basestation (BTS), class-C oscillator, coupled oscillators, figure of merit (FoM), LC-tank, phase noise.

# I. Introduction

RECEIVERS in cellular basestations (BTS) work in the presence of powerful unwanted blockers while being required to sense weak desired signals. To avoid distortion through reciprocal mixing, phase noise (PN) of BTS oscillators must satisfy extremely stringent performance requirements. Monolithic SiGe/Bi-CMOS technology, together with discrete external components, are used nowadays for such RF frontends. However, due to power consumption and cost reasons, together with an increasing deployment, there is a strong motivation for their full monolithic integration in CMOS.

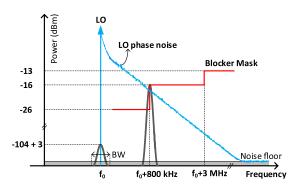

The stringent PN requirements originate from the in-band blocking characteristics imposed by the Global System for Mobile Communications "GSM900 normal basestation" [1]. Fig. 1 illustrates the worst case scenario when a blocker is present at 800 kHz away from the desired signal. The oscillator PN  $(\mathcal{L})$  is integrated over the channel bandwidth, BW (here,

Manuscript received November 2, 2015; revised January 6, 2016; accepted January 20, 2016. Date of publication March 11, 2016; date of current version April 15, 2016. This work was supported in part by EU ERC Starting Grant 307624. This paper was recommended by Associate Editor P.-I. Mak.

S. A.-R. Ahmadi-Mehr and M. Tohidian are with the Qualinx B. V., Delft University of Technology, Delft, The Netherlands (e-mail: s.a.r.ahmadimehr@tudelft.nl).

R. B. Staszewski is with the University College Dublin, Dublin, Ireland. He is also with Delft University of Technology, Delft, The Netherlands.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2016.2529218

Fig. 1. Blocker levels in a GSM900 system as a function of offset frequency.

200 kHz), and mixed with the blocker of power  $P_b$  at 800 kHz away and then down-converted on top of the desired signal,  $P_s$ . In order to maintain the minimum carrier-to-interference ratio (C/I) of 9 dB set by the GSM standard [1], an oscillator must satisfy the strict PN according to

$$P_b + \left[\mathcal{L}(\Delta f) + 10\log(BW)\right] < P_s - \left(\frac{C}{I}\right). \tag{1}$$

Per Fig. 1,  $P_b = -16$  dBm and  $P_s = -101$  dBm. Therefore, the PN at 800 kHz should satisfy -147 dBc/Hz, which is 20 dB lower than that required in mobile stations (MS) [1].

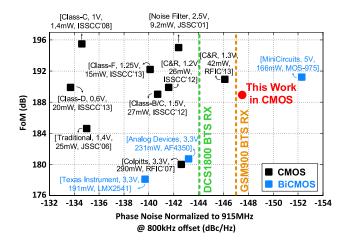

Extensive efforts [2]–[14] have been made to improve PN in CMOS oscillators while maintaining good figure-of-merit (FoM), i.e., normalized PN per 1 mW of power consumption

$$FoM = |PN| + 20\log_{10}\left(\frac{f_0}{\Delta f}\right) - 10\log_{10}\left(\frac{P_{DC}}{1 \text{ mW}}\right) \quad (2)$$

where  $f_0$  is the oscillating frequency,  $\Delta f$  is the frequency offset from  $f_0$ , and  $P_{\rm DC}$  is the power consumption. However, none of the prior works has managed to satisfy the toughest BTS phase noise specifications even given ample margin to the reasonably expected limit on power consumption (see the "current" and "FoM" entries in Table I). Furthermore, a recent work in [15] has established fundamental limits on the FoM performance of oscillators and has re-introduced a metric termed excess noise factor (ENF), something akin to a noise figure (NF) of an LNA. As it turns out, state-of-the-art oscillators are just a few dB away from that fundamental limit. Hence, the only realistic avenue for substantial PN performance improvements is to increase the power consumption  $P_{\rm DC}$  while maintaining a good FoM. This appears to invariably lead to an increase in the oscillation amplitude  $V_{\rm osc}$  of the resonating LC-tank according to (based on (2) in [4])

$$V_{\rm osc} = \sqrt{P_{\rm DC} \cdot \alpha_I \cdot \alpha_V \cdot Q \cdot \omega_0 L} \tag{3}$$

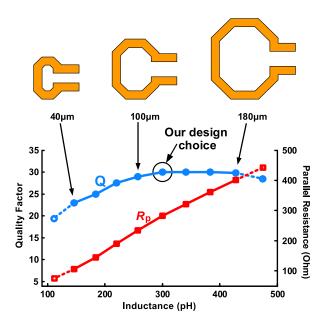

Fig. 2. By continually reducing the inductor size (value), at some point Q-factor starts degrading.

where  $\alpha_I$  and  $\alpha_V$  are the current and voltage conversion efficiencies, Q is the tank's quality factor,  $\omega_0=2\pi f_0$ , and L is the tank inductance.  $\alpha_I$  and  $\alpha_V$  are largely fixed by the chosen oscillator topology.

For an optimal power consumption efficiency (i.e., FoM), Q should be kept as high as possible. Attempting to further improve the PN by increasing  $P_{\rm DC}$  will result in large  $V_{\rm osc}$ , which will eventually lead to serious device reliability concerns [4]. Hence, based on (3), a reasonable strategy in delivering more effective  $P_{\rm DC}$  would be decreasing L while keeping  $V_{\rm osc}$  at its maximum tolerated level. As pointed out later in Section II, there is a technological limitation on how low L can go. To conclude, each CMOS process seems to have a technological limitation on phase noise of a given oscillator topology (i.e.,  $\alpha_I$  and  $\alpha_V$ ).

In this paper, we propose to break that limit by a dual-core oscillator topology [16] and then demonstrate it in bulk CMOS. The rest of the paper is organized as follows. Section II presents a background discussion on various techniques to improve PN. Section III elaborates more on the multi-core oscillators. Section IV discusses the effect of different practical impairments in multi-core oscillator design and is followed by measurement results in Section V.

# II. PHASE NOISE REDUCTION TECHNIQUES

# A. Parameter Optimization

In 1966, Leeson presented an empirically derived PN  $(\mathcal{L})$  model of oscillators [17]

$$\mathcal{L}(\Delta\omega) = 10 \cdot \log \left( F \frac{4kTR_p}{V_{\text{osc}}^2} \left( \frac{\omega_0}{2Q\Delta\omega} \right)^2 \right) \tag{4}$$

where k is Boltzmann's constant, T is the absolute temperature,  $R_p$  is an equivalent parallel tank resistance, and F is a noise factor of the active device.

Leeson's equation shows the dependency of PN on Q. The inductor's Q-factor in bulk CMOS is limited in best case to 30, even with an ultra thick metal option. Furthermore, oscillators need to cover a certain tuning range (> 15%) to account for variations in process, voltage and temperature (PVT). Such tuning is typically done with switched capacitors, which also have a limited Q-factor. In addition, there is a trade-off between the tuning range and Q of these switches. Consequently, the tank's Q does not have much margin left for further improving the PN in scaled CMOS.

Furthermore, advances in the CMOS technology lead to systematic reductions in the supply voltage,  $V_{\rm DD}$ . Maximum practical voltage swing  $V_{\rm osc}$  in the oscillator gets saturated to less than twice  $V_{\rm DD}$ . Hence, the voltage scaling will directly lead to the PN degradation, as per (4). Moreover, FoM of the oscillator is also dependent on the voltage efficiency,  $\alpha_V = V_{\rm osc}/V_{\rm DD}$ , which tends to be degraded with supply scaling. It has been shown that [16]

$$FoM = \frac{4Q^2 \cdot \alpha_I}{F \cdot 4kT} \times \frac{V_{\text{osc}}}{V_{\text{DD}}} \times 10^{-3}$$

(5)

where  $\alpha_I$  is the current efficiency (conversion factor of the bias current into the fundamental current harmonic).

An important parameter is an inductance value, L, of the LC-tank. Equation (5) is written such that FoM does not depend directly on L. However, L affects the equivalent parallel resistance of the tank as  $R_p = L\omega Q$ . By decreasing L and, consequently,  $R_p$  (while managing to keep Q constant), PN can be reduced, as per (4). However, the bias current should be increased to keep the maximum oscillation amplitude with, hopefully, a constant FoM.

To maximally reduce the PN, one might pick a high-Q inductor at first and then try to lower the inductance by shrinking its radius or reducing its number of turns. Although a multi-turn inductor might have a slightly higher quality factor, by choosing a 1-turn inductor, a much lower inductance value can be obtained. Reducing the radius of an inductor results in a lower inductance (see Fig. 2). However, after a certain point, the quality factor starts dropping dramatically as series resistance losses (e.g., due to vias, interconnecting metal) start to dominate. By trading off between a low L and high Q, we can find the optimum point from which further increasing the inductance would worsen the PN, but lowering the inductance would drop Q and thus worsen FoM and perhaps even PN. At that point, the oscillator could have the lowest possible PN in a given process technology with a good FoM. In other words, to improve the PN of the oscillator, the term  $R_p/Q^2 = L\omega/Q$  from (4) needs to be reduced. From Fig. 2, this ratio cannot keep on decreasing indefinitely since at certain point Q drops more than L. Moreover, there is a limit on how small the inductor can become before it gets limited by vias and other fixed routing parasitics.

# B. High-Swing Class-C Topology

Based on Leeson's equation, another parameter that can be exploited to improve PN is F (i.e., amplifier's noise factor).

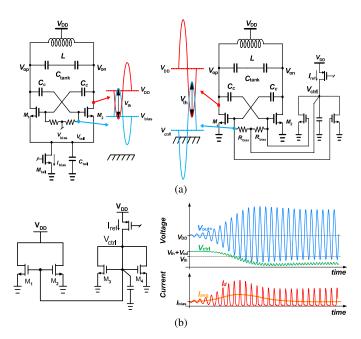

Fig. 3. Schematic of the original class-C oscillator (left), and high-swing class-C (HSCC) oscillator used in this work (right); (b) conceptual diagram of DC biasing and related start-up waveforms.

There are a number of efforts to reduce F by shaping the tank voltage and reducing the effective noise of active devices [2]-[4], [11].

A class-C oscillator was first introduced in [11] and, according to [15], its ENF is very competitive. Its schematic is shown in Fig. 3(a) (left). As noted above, the PN improves with increasing the oscillation amplitude, which here would mean lowering the gate bias voltage  $V_{\rm bias}$ . Unfortunately, the original class-C oscillator restricts the fixed  $V_{\rm bias}$  from being set low enough, otherwise the oscillator might not start up.

In [18], a high-swing class-C (HSCC) oscillator was introduced, which removed the tail current transistor of the original class-C oscillator [11]. Instead, an automatic amplitude control was introduced to stabilize the oscillation amplitude. In this work, instead of the transformer used in [18], a simple RC bias is chosen. The oscillator schematic is shown in Fig. 3(a) (right) while Fig. 3(b) focuses on the concept of adaptive DC bias of the oscillator, where, for the ease of explanation, the inductors and resistors are shorted and the capacitors are open. The currents of the core transistors are mirrored and, after a comparison against the reference bias current  $I_{\rm ref}$  and then integration, the resulting control voltage  $V_{\rm ctrl}$  is applied to the cross-coupled  $M_{1,2}$  transistor gates. At start-up, since there is no current through the oscillator,  $V_{\text{ctrl}}$  node rises to  $V_{\text{th}} + V_{\text{od}}$ . As the waveforms demonstrate, the amplitude feedback scheme produces the maximum  $V_{

m ctrl}$  to ensure the reliable start-up and adaptively reduces at steady-state for class-C operation with high output voltage swing.

The value of  $R_{\rm bias}$  should not be too small as it could load the tank's Q and not too large as to avoid amplitude instability (squegging) due to the RC network delay in the feedback loop of amplitude control. The noise contribution from  $R_{\rm bias}$  has no negative impact since it will be filtered out by the low-pass combination of  $R_{\rm bias}$  and  $C_c$ . The alternative method of using

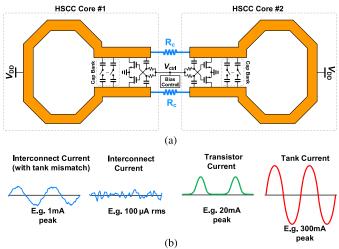

Fig. 4. (a) Dual-core high-swing class-C (HSCC) oscillator, and (b) related current waveforms. Note the internal LC-tank current is Q times larger than the oscillator drain current,  $I_{\rm DC}$ .

the transformer coupling could also be beneficial with regard to amplitude stability.

To summarize our approach so far: After choosing the class-C oscillator topology to obtain the FoM performance close to the theoretical limit, then maximizing the output swing to minimize PN, while optimizing the inductor and the capacitor bank, the final oscillator should reasonably have the lowest possible PN. In the next section we demonstrate how to further improve PN by coupling multitude of such oscillators.

# III. MULTI-CORE OSCILLATOR

To address the aforementioned limitations on the PN performance of a CMOS oscillator, we exploit an old idea of coupling multiple oscillators [19]–[21] and propose that such coupling can be resistive using, e.g., long and thin traces, which is often convenient in practical realizations. Fig. 4(a) depicts this idea for N=2, i.e., a dual-core oscillator. Two identical oscillator cores [generally of any topology, but here the core is the high-swing class-C from Fig. 3(a) (right)] are "coupled" in parallel thus they are locked and oscillating in-phase. Each of the inductors has its own local capacitor bank. Hence, high resonant current of each LC-tank gets circulated only locally.

According to Leeson's formula (4), by doubling the capacitance and halving L (assuming  $R_c$  is low), the oscillation frequency remains the same but  $R_p$  becomes half, which reduces PN by 3 dB. Intuitively: equivalent current noise of core #1 experiences twice the capacitance and therefore its PN contribution is reduced by 6 dB. Similarly, PN contribution of core #2 is reduced by 6 dB. These two contributions originated from core #1 and #2 are uncorrelated, thus their powers are summed up. Therefore the total PN is reduced by 3 dB.

To get a deeper insight, let us consider the following: If we would apply this technique (i.e., doubling the capacitance) to a single core, the inductor needs to be scaled down also by a factor-of-two in order to maintain the frequency. Then, PN would improve because of the  $R_p$  reduction (as discussed in Section II). However, continual reduction of L at some point

hits the physical limitations of the technology where Q-factor starts dropping precipitously. This is exactly where we back off a bit and pick our inductor value, as indicated in Fig. 2. As a result, to move forward with the PN reduction, we then proceed to the multi-core approach. Note that each LC-tank in Fig. 4(a) needs a dedicated active device  $(M_{1,2})$  in order to perpetuate its oscillation, and to constraint the large resonating current  $Q \cdot I_{\rm DC}$  between L and C [see Fig. 4(b)] from going to the other core. In other words, the active devices serve an additional purpose of allowing a weak coupling between oscillators in the multi-core arrangement.

In general, the presence of N tanks reduces the PN due to a single noise source by a factor  $N^2$ . There are now N current noise sources instead of just one. As the noise sources are all uncorrelated and equal in power, the total PN is N times contribution of one of them. So, the overall PN is N times better than with a single core

$$\mathcal{L}_N(\Delta\omega) = \mathcal{L}_1(\Delta\omega) - 10\log(N). \tag{6}$$

Obviously, the total power consumption grows N times. This keeps FoM unchanged [16]. Hence, the lower PN would come at a cost of proportionately higher power consumption and area.

For a *weakly* coupled multi-oscillator system, the oscillators inject small currents into each other and hence require some time to correct for any resulting perturbations. These perturbations will affect the coupled system differently according to their frequency content. Low frequency noise perturbations will afford enough time for the system to respond and hence achieve the expected PN improvement while fast perturbations or high frequency noise will experience less such rejection. This will be demonstrated mathematically in Section IV and then supported through measurements in Section V. The conclusion is that the coupling factor mainly affects the bandwidth of the PN improvement; i.e., the larger the coupling factor, the wider the bandwidth of the PN improvement.

It should be clarified that coupled oscillators have been historically used to provide multiple phases (with the *quadrature* being the most prominent example [22]) for integrated transceivers. To construct a 2N-phase LC oscillator, at least N (differential) oscillator cores are needed. In theory, they have the advantage of reduced phase noise: N-coupled oscillators have N times less phase noise than a single oscillator [20]. However, such coupling for the multi-phase generation might lead to a PN degradation in two ways: first, due to a reduction of effective Q caused by the shift from the tank's resonance and, second, due to additional noise from the coupling devices [10], [23], [24].

In [25], the cores are coupled *in-phase* through  $g_m$  transistor stages in a ring arrangement, so the flicker up-conversion is avoided from the coupling devices. However, that approach is limited to class-B oscillators and does not appear applicable to other topologies. Multi-core transformer coupling through differential coplanar transmission lines for a mm-wave oscillator is presented in [26]. However, that technique seems applicable only at mm-wave due to otherwise large transformer sizes. In addition, recent works on mode-switching oscillators aim to

significantly improve the trade-off between frequency tuning range and phase noise [27]–[29]. Low/high oscillation frequency can be selected there by switching a coupling capacitor between odd/even modes of two coupled LC oscillators. Hence, in one mode the phase noise was observed to improve due to the parallel arrangement.

In our approach, the multiple oscillators are simply coupled electrically through a finite (preferably, but not necessarily, small) resistance  $R_c$  of the interconnecting wire. As stated above, the general oscillator coupling technique has been known in the past (e.g., see [19]) and has been used in microwave circuits [20] and discrete-component circuits [21], but it has not yet been sufficiently exploited in monolithic oscillators to reduce phase noise to the point of reaching the cellular basestation performance. Similar on our approach originally disclosed in [16], authors in [30] paralleled 2/4 inductors in low-/high-band modes to reduce PN while widening the total tuning range. These PN advantages of coupled oscillators (N=1,2,3) have also been recently verified for inverter-based ring oscillators in 16-nm FinFET CMOS technology [31].

# IV. ANALYSIS OF IMPERFECTIONS IN MULTI-CORE OSCILLATOR

A major concern that comes along with practical implementations of multi-core oscillators is how to connect all of them in parallel. Since the footprint of inductors is bulky, interconnections between them are expected long. Hence, the resistance of these interconnects would play a role in the PN performance. In addition, the interconnection between the oscillator cores could be switchable, in which case channel resistance of NMOS/PMOS switches could be on the order of hundreds of  $\Omega$  to a few  $k\Omega$ . An example of such a reconfigurable three-core oscillator was presented in [31], in which transmission gates are engaged to couple two or three inverter-ring oscillators in order to improve phase noise at the cost of power consumption.

Another imperfection is a mismatch between free-running frequencies of the cores. In presence of a high interconnect impedance, mismatch increases the chance that the cores would oscillate at separated frequencies thus producing injection pulling spurs. Therefore, the coupling should be tight enough to achieve the desired PN performance.

As depicted in Fig. 4(b), in an ideal case (completely matched cores) no static or cyclic current is passing through the wires inter-connecting the two cores. Nonetheless, a very small noise current (with an average of zero) is going back and forth. The current inside the tank is Q times larger than the fundamental current component that injects into it. Thus, in a presence of a small mismatch between the cores, if interconnection resistance is small enough, a small cyclic current at the fundamental frequency would go through the inter-connection wires to balance the cores and force them to oscillate at the same frequency.

# A. Interconnect Resistance

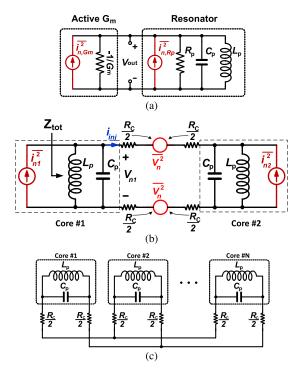

In order to investigate the effect of interconnect resistance, we start with a simple linear time-invariant model of an oscillator shown in Fig. 5(a). It includes noise of the active device

Fig. 5. Oscillator model for calculating PN: (a) simple linear model of an LC-tank oscillator; (b) dual-core oscillator model; (c) model of N star-connected oscillators.

$\overline{i_{n,Gm}^2}$  and the tank  $\overline{i_{n,Rp}^2}$ . Fig. 5(b) extends this model to the dual-core oscillator considering the interconnect resistance  $R_c$  between them. In this figure, the total current noise of each core,  $\overline{i_{n,Gm}^2} + \overline{i_{n,Rp}^2}$ , is represented as  $\overline{i_n^2}$ . In addition, the parallel resistance of the tank is canceled out in steady-state with a negative resistance of the active part. Although majority of oscillators operate in a strongly nonlinear region, linear analysis is still useful in gaining further insight.

Using a superposition of each core's noise, the total noise on each node can be calculated. Since all the noise sources are considered uncorrelated, their powers add up. The impedance of a single tank,  $Z_{\rm tank}$ , oscillating at  $\omega_0$ , can be approximated at a frequency offset  $\Delta\omega$  as [19]

$$|Z_{\text{tank}}(\Delta\omega)| = \left| \frac{1}{2} \frac{R_p \omega_0}{Q \Delta\omega} \right|. \tag{7}$$

The noise power at the differential node  $V_{n1}$  can thus be calculated from the superposition as follows:

$$\overline{V_{n1}^2} = \overline{i_{n1}^2} \cdot |Z_{\text{tot}}|^2 + \overline{i_{n2}^2} \cdot |Z_{\text{tot}}|^2 \cdot \left| \frac{Z_{\text{tank}}}{2 R_C + Z_{\text{tank}}} \right|^2$$

(8)

where  $Z_{\rm tot}$  is the total impedance seen from one side, defined in Fig. 5(b). Since the two cores are identical, we assume  $\overline{i_n^2} = \overline{i_{n1}^2} = \overline{i_{n2}^2}$ . Then, (8) is simplified to

$$\overline{V_{n1}^{2}} = \overline{i_{n}^{2}} \times \frac{1}{2} \times |Z_{\text{tank}}|^{2} \times \frac{2 R_{c}^{2} + |Z_{\text{tank}}|^{2}}{R_{c}^{2} + |Z_{\text{tank}}|^{2}}$$

$$= \overline{i_{n}^{2}} |Z_{\text{eq}}|^{2}. \tag{9}$$

As defined in (4),  $F = 1 + \overline{i_{n,gm}^2}/\overline{i_{n,R_p}^2}$ , so the total noise of each core can be written as

$$\overline{i_n}^2 = F \cdot \overline{i_{R_p}}^2 = F \frac{4kT}{R_p}.$$

(10)

The PN is calculated by dividing the noise power over the signal power. The noise calculated in (9) equally includes amplitude and PN contributions [32]. The amplitude noise is suppressed by the oscillator's nonlinearity due to its positive feedback, so only half of the power in (9) remains as noise in phase. Therefore, the PN of the dual-core oscillator is

$$\mathcal{L}(\Delta\omega) = 10 \log \left(\frac{\frac{V_1^2}{2}}{\frac{V_{\text{osc}}^2}{2}}\right)$$

$$= 10 \log \left(F \frac{4kTR_p}{V_{\text{osc}}^2} \left(\frac{|Z_{\text{eq}}|}{R_p}\right)^2\right). \tag{11}$$

Applying the same method for an N-core oscillator coupled in a star connection [Fig. 5(c)], results in a general equivalent impedance

$$|Z_{\rm eq}|^2 = \frac{1}{N} \times |Z_{\rm tank}|^2 \times \frac{NR_c^2 + |Z_{\rm tank}|^2}{R_c^2 + |Z_{\rm tank}|^2}.$$

(12)

For  $R_c \ll |Z_{\rm tank}(\Delta\omega)|$ , the third factor  $(N{R_c}^2 + |Z_{\rm tank}|^2)/(R_c^2 + |Z_{\rm tank}|^2)$  is close to unity, such that  $|Z_{\rm eq}|^2 \approx |Z_{\rm tank}|^2/N$ . However, it increases with increasing  $R_c$  and the offset frequency  $\Delta\omega$ . Its maximum value can reach N such that  $|Z_{\rm eq}|^2 \approx |Z_{\rm tank}|^2$ . In terms of PN, the former case (i.e., tight coupling,  $R_c \ll |Z_{\rm tank}(\Delta\omega)|$ ) reduces the PN power N times with respect to the single-core oscillator. In the latter case, there is no benefit since the cores are completely decoupled. Summarizing

$$\overline{V_{n1}^{2}} = \begin{cases} \overline{i_{n}^{2}} \times \frac{|Z_{\text{tank}}|^{2}}{N} & R_{c} \to 0\\ \overline{i_{n}^{2}} \times |Z_{\text{tank}}|^{2} & R_{c} \to \infty. \end{cases}$$

(13)

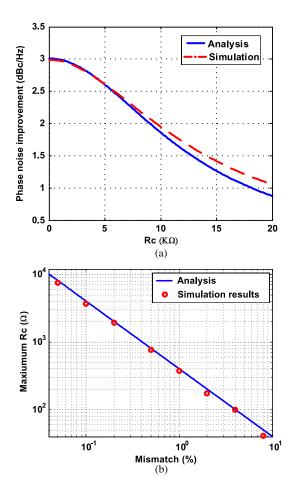

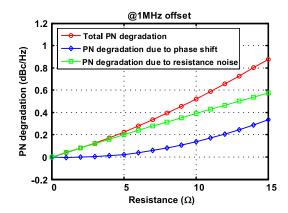

Fig. 6(a) plots an example of the maximum (i.e.,  $\Delta\omega \to 0$ ) PN improvement in the dual-core (N=2) versus  $R_c$ . In our implementation, even with  $R_c$  as high as 5 k $\Omega$ , an improvement of 2.6 dB can still be obtained. Considering the PN versus  $\Delta\omega$  with a certain  $R_c$ , at very low frequencies where  $Z_{\rm tank}\gg R_c$ , the improvement is 3 dB. However, for very high offset frequencies where  $Z_{\rm tank}(\omega)\ll R_c$  the cores become decoupled and no improvement is achieved. Generalizing for N cores we have

$$\overline{V_{n1}^2} = \begin{cases} \overline{i_n^2} \times \frac{|Z_{\text{tank}}|^2}{N} & \Delta\omega \to 0\\ \overline{i_n^2} \times |Z_{\text{tank}}|^2 & \Delta\omega \to \infty. \end{cases}$$

(14)

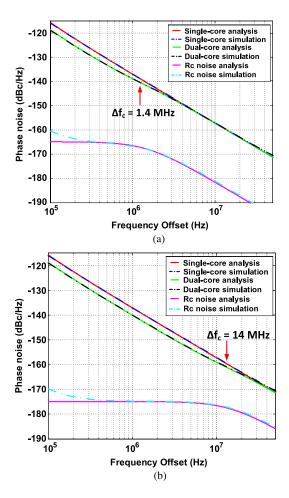

The above PN model is verified against Spectre-RF simulations in Fig. 7 for N=1 and 2, and with  $R_c$  of 10 k $\Omega$  and 1 k $\Omega$ . F is estimated 2. Based on the results, the analysis is in a good agreement with simulations.

Next, we calculate the noise voltage at  $R_c$  [Fig. 4(b)]. By using superposition at  $V_{n1}$  from two uncorrelated noise sources, PN can be derived as

$$\mathcal{L}(\Delta\omega) = 10\log\left(2 \times \frac{4kTR_c}{V_{\rm osc}^2} \left| \frac{Z_{\rm tank}}{2R_c + 2Z_{\rm tank}} \right|^2\right). \quad (15)$$

Fig. 6. (a) Effect of interconnect resistance on close-in PN improvement in a dual-core oscillator. (b) Maximum interconnect resistance to maintain a lock condition with resonant frequency mismatches between the cores.

This PN contributed by  $R_c$  is also plotted in Fig. 7. There is a small disagreement with the simulations due to disregarding the dynamic amplitude control in each oscillator, although the noise power level is insignificant for the realistic  $R_c$  values.

It is also insightful to calculate a corner frequency where the PN improvement starts degrading by half, from (15) and (12) as follows:

$$\Delta\omega_c = \frac{R_p \,\omega_0}{2R_c \,Q}.\tag{16}$$

This is also in agreement with the fact the PN improvement is within the lock range of the two oscillators, defined later in (17).

#### B. Mismatch Between the Oscillator Cores

In a realistic situation, there will certainly be resonant frequency mismatches between the oscillator cores. If, in addition, the interconnections between them are very weak, they could all be oscillating independently at their natural frequencies and so no PN improvement would be achieved.

To quantify the effect of mismatches, we start with the concept of injection locking. We consider one of the oscillators to be an aggressor, injecting current  $I_{\mathrm{inj}}$  at an angular frequency  $\omega_{\rm inj}$  into a "victim" oscillator resonating at  $\omega_0$  with an internal

Fig. 7. Simulation and analytical plots of the phase noise with F=2 in (10) including noise from  $R_c$  for two cases: (a)  $R_c=10~{\rm k}\Omega$ , and (b)  $R_c=1~{\rm k}\Omega$ .

tank current  $I_{\rm osc}$ , and whose quality factor is Q. As defined in [33], lock range  $\omega_L$  and pulling strength  $\eta$  are re-stated in (17) and (18)

$$\omega_L \approx \frac{\omega_0}{2Q} \cdot \frac{I_{\rm inj}}{I_{\rm osc}}$$

$$\eta = \frac{\omega_0}{|\omega_0 - \omega_{\rm inj}|}.$$

(17)

$$\eta = \frac{\omega_L}{|\omega_0 - \omega_{\rm ini}|}.$$

(18)

The injection current  $(I_{inj})$  in Fig. 5(b) can be evaluated as

$$I_{\rm inj} = \frac{|V_{\rm osc}|}{|2 Rc + Z_{\rm tank}(\Delta \omega_n)|}$$

(19)

where  $\Delta\omega_n$  is the frequency shift from  $\omega_0$  after two oscillators are locked (for simplicity, let us assume  $\Delta\omega_n = ((\omega_{osc1} (\omega_{osc2})/2)$ ). In order for both oscillators to maintain the lock condition,  $\eta$  should be larger than one. Applying this condition, together with (18) and (19), the maximum allowable  $R_c$  is calculated from

$$R_c < \frac{\omega_0 R_p}{4Q} \sqrt{1 - \frac{1}{\Delta \omega_n}}.$$

(20)

This expression is validated against Spectre-RF simulations at different mismatches and the comparison is shown in Fig. 6(b). For instance, for a typical mismatch of 1%, the upper limit on the interconnect resistance  $R_c$  is 400  $\Omega$ .

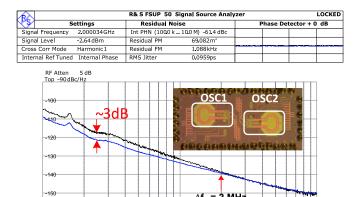

Fig. 8. Phase noise improvement through the parasitic coupling of two separate oscillators.

through the subs

In fully monolithic implementations, the natural coupling between various oscillators through substrate is mostly considered undesired as it could produce injection pulling spurs and lead to modulation distortion [34], [35]. Here, it is advantageous as it improves tolerance to mismatches in the oscillators' natural frequencies. In order to show that the natural substrate coupling can relax specification on the interconnection strength, the chip in [34] (shown in Fig. 8) is re-measured for our purposes. The chip contains two separate oscillators and the only interaction between them is parasitic substrate and magnetic coupling. In order to measure the amount of injection, two oscillators are forced to resonate 10 MHz away from each other, which leads to injection pulling spurs. Based on calculations according to [33], the power of the biggest injection pulling spur under a weak injection is

$$P(\omega_{\rm spur}) \approx \left(\frac{\omega_0}{4Q} \cdot \frac{I_{\rm inj}}{I_{\rm osc}} \cdot \frac{1}{\omega_m}\right)^2$$

(21)

where  $\omega_m$  is the offset frequency of the generated spur. By measuring the spurious tone power, the injection current is calculated around 70  $\mu$ A. By extracting  $V_{\rm osc}$  from post-layout simulations, it turns out that the equivalent coupling resistance  $R_c$  is about 25 k $\Omega$ . Using (16), the calculated lock range is about 2 MHz. As shown in Fig. 8, at low frequencies, the PN improves 3 dB but degrades rapidly around 2 MHz (lock range) and reaching the PN level of a single core oscillator. These measurement results confirm the formulas derived above. To summarize: The natural parasitic substrate coupling between oscillators provides a certain level of injection locking that results in PN improvements, but a deliberate electrical connection would further push the region of the PN improvements to much higher frequency offsets.

# V. DESIGN CONSIDERATIONS AND MEASUREMENT RESULTS

Since the ultimate goal in this work is to achieve the ultralow PN, careful attention should be paid to the ohmic resistance  $R_{\rm par}$  of the cross-coupled connection (in series with  $C_c$ ). As

Fig. 9. Phase noise degradation due to ohmic resistance in  $g_m$  cross-coupled connection

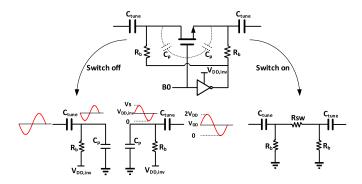

Fig. 10. Switched-capacitor for coarse tuning of the oscillator frequency.  $V_{\rm DD,inv}=0.8\,\mathrm{V}$  ensures a long-term reliability for thin-oxide devices.

shown in Fig. 9, the delay is introduced  $(R_{\rm par}C_c\approx 5~{\rm ps})$  in the oscillator loop, which degrades the effective quality factor and reduces the center frequency. Moreover, the noise from  $R_{\rm par}$  can degrade PN with total degradation as high as 0.5 dB when  $R_{\rm par}=10~\Omega$ , which could happen in case the layout is not carefully done.

To avoid AM-to-PM noise conversion, MOM capacitors are used here, instead of linear varactors, as they are less sensitive to the supply noise. A switched capacitor structure, shown in Fig. 10, is used to coarsely tune the resonant frequency. Here, a conventional topology is used but with a single modification, which will be explained shortly. The size of the switches is set as a compromise between their parasitic capacitance (too large switches would reduce the tuning range) and the PN degradation (too small switches would introduce a resistive loss,  $R_{\rm sw}$ , in on-state, thus reducing the Q-factor of the switched capacitors,  $Q_{\rm on} = 2/(\omega C_{\rm tune} \cdot R_{\rm sw})$ ). The switch pull-up/down resistor,  $R_b$  (here, 20 k $\Omega$ ), needs to be chosen large enough to avoid the tank Q-factor degradation during the off-state,  $Q_{\rm off} = 1/(R_b C_p \omega)$ . However, floating the source/drain of the switch must be avoided, otherwise the transistor would enter undesirable regions. Since the stated objective is the ultra-low PN, large transistor sizes are used in the switched-capacitor bank. The bank contains 5-bit switchable capacitance, in which both the capacitors and switches are sized together in a binary fashion. The unit capacitance is 170 fF and its switch has a total width of 270  $\mu$ m. Such a large unit size ensures excellent

|                                                      |       | This<br>Work         | JSSC'13<br>[2]      | JSSC'13<br>[3] | JSSC'15<br>[4]     | ISSCC'12<br>[5]       | ISSCC'12<br>[6]       | RFIC'07<br>[7]     | JSSC'06<br>[8]      | JSSC'15<br>[9]     | Mini Circuits<br>MOS-975 | Analog<br>Devices<br>ADF4350 |

|------------------------------------------------------|-------|----------------------|---------------------|----------------|--------------------|-----------------------|-----------------------|--------------------|---------------------|--------------------|--------------------------|------------------------------|

| Description                                          |       | Dual-Core<br>Class-C | Class-F             | Class-D        | Class-F2           | Clip &<br>Restore     | Class-B/C             | Colpitts           | Class-B             | Class-B            | -                        | -                            |

| Technology                                           |       | 65nm                 | 65nm                | 65nm           | 65nm               | 65nm                  | 55nm                  | 130nm              | 90nm                | 55nm               | BiCMOS                   | BiCMOS                       |

| Tuning Range (GHz)                                   |       | 4.07-4.91<br>(18.6%) | 2.94-3.78<br>(25%)* | 3-4.8<br>(48%) | 7.2-8.7<br>(18.8%) | 3.64-4.03<br>(10.2%)* | 3.35-4.6<br>(31.44%)* | 1.5-1.65<br>(9.6%) | 3.21-4.1<br>(24.3%) | 7.4-8.4<br>(12.6%) | -                        | 0.88-0.99<br>(11.8%)         |

| Frequency (GHz)                                      |       | 4.07                 | 3.7                 | 4.8            | 4.2                | 3.92                  | 3.35                  | 1.56               | 0.915               | 4                  | 3.3                      | 0.915                        |

| Phase Noise (dBc/Hz)                                 | 3MHz  | -146.7               | -133                | -136           | -141.71            | -142.2                | -142                  | -150.38            | -149                | -141               | -143.5                   | -163.4                       |

|                                                      | 20MHz | -163.1               | -149.5              | -152.5         | -158.18            | -158.6                | -158.48               | -166.85            | -167                | -157.5             | -160                     | -179.9                       |

| Phase Noise<br>norm. to a 915MHz carrier<br>(dBc/Hz) | 3MHz  | -159.7               | -147.4              | -150.5         | -154.35            | -154.3                | -153.3                | -155.02            | -149                | -153.8             | -154.7                   | -163.4                       |

|                                                      | 20MHz | -176.14              | -163.9              | -167           | -170.8             | -170.7                | -169.75               | -171.49            | -167                | 170.3              | -171.2                   | -179.9                       |

| Supply Voltage (V)                                   |       | 2.15                 | 1.25                | 0.5            | 1.3                | 1.2                   | 1.5                   | 3.3                | 1.4                 | 1.5                | 3.3                      | 5                            |

| Current (mA)                                         |       | 59                   | 12                  | 14             | 32                 | 21.5                  | 18                    | 88                 | 18                  | 4                  | 70                       | 33                           |

| FoM @ 3MHz (dB)                                      |       | 189                  | 192.2               | 191            | 191                | 189.9                 | 189                   | 180                | 184.6               | 195                | 180.7                    | 191                          |

| Area (mm²)                                           |       | 0.37 <sup>1</sup>    | 0.157               | 0.116          | 0.26               | 0.19                  | 0.49                  | 0.322              | 0.52 <sup>1</sup>   | 0.19               | -                        | -                            |

| Including decoupling capacitor                       |       |                      |                     |                |                    |                       |                       |                    |                     |                    |                          |                              |

TABLE I

PERFORMANCE SUMMARY AND COMPARISON WITH STATE-OF-THE-ART

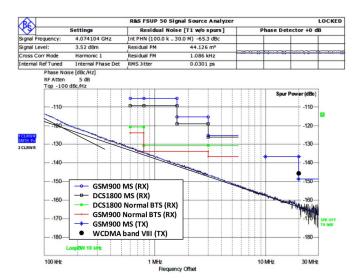

Fig. 11. Phase noise plot of the oscillator.

Q-factor in the switched-capacitor's on-state but it increases oscillator's parasitics thus limiting its tuning range.

In the off-state, the voltage swing at the drain of the switch driver is very high  $(V_{\rm osc} \cdot C_{\rm tune}/(C_{\rm tune}+C_p))$ , with the capacitance ratio here 0.55–0.6) which is usually beyond the reliability limit of thin-oxide devices. To solve this, one could use larger thick oxide devices whose parasitic capacitances are higher in order to have the same Q. However, doing so would degrade the tuning range  $(C_{\rm on}/C_{\rm off})$  becomes smaller). Here, to tackle this problem, we propose to use a different supply voltage for the driver,  $V_{\rm DD,inv}=0.8~\rm V$ . This way, the thin oxide devices can still be used while ensuring reliability and avoiding the tuning range degradation.

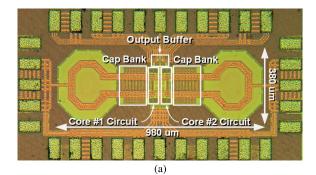

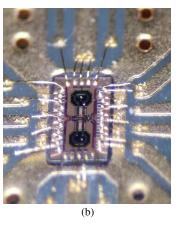

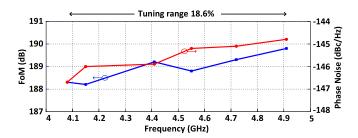

The dual-core HSCC oscillator is implemented in TSMC 65 nm LP CMOS. Its chip micrograph is shown in Fig. 12(a). The measured output frequency range is from 4.07 GHz to

Fig. 12. (a) Chip micrograph; (b) related FR4 PCB board with wire bond length reduction.

4.91 GHz, yielding 18.6% tuning range. Measured phase noise (PN) is plotted in Fig. 11 together with normalized PN specifications of some of the toughest cellular basestation (BTS) and mobile (MS) communication standards [1]. The normalized measured PN is well below the receiver LO purity specifications of "GSM900 MS," "DCS1800 MS," and "normal BTS." The PN is also 0.6 dB below the toughest "GSM900 normal BTS"

Fig. 13. Comparison with state-of-the-art low phase noise oscillators.

Fig. 14. Measured phase noise and FoM at 3 MHz offset over the tuning range.

at 800 kHz offset although this could degrade by up to 1.5 dB over the entire tuning range, which is mostly due to flicker noise upconversion. It also meets MS transmitter standards of GSM900 and WCDMA band-VIII with 14 dB and 17 dB margins, respectively. To the best of our knowledge, this is the first-ever reported oscillator in CMOS IC that reaches all these requirements. This PN could be further lowered by 3 dB by adding two more oscillator cores.

The implemented differential inductor is 300 pH, but its effective value will be a bit increased due to the routing of the capacitor bank. The total estimated Q from a post-layout simulations is around 20. The cross-coupled thick-oxide transistors are sized at (112  $\mu$ m/280 nm), in order to ensure safe start-up with a reasonable margin for worst case conditions and proper class-C operation. The mirror ratio should also be chosen carefully (in this design, 5) in accordance with its bias capacitance to avoid potential squegging. The oscillator drains 39 mA to 59 mA from a 2.15 V power supply, which is much higher than the nominal 1.2 V supply of core transistors. Thick oxide devices are used instead to insure reliability. Each oscillator core has an independently controlled 5-bit binaryweighted coarse MoM capacitor bank. This chip was directly wire bonded on a PCB board. In order to reduce the effects of high current spikes in the supply voltage due to the wire-bond inductance, 250 pF decoupling capacitance is added on-chip. To further improve performance, the fabricated chip was placed in a hole in the PCB board to shorten the wire-bond length, as shown in Fig. 12(b).

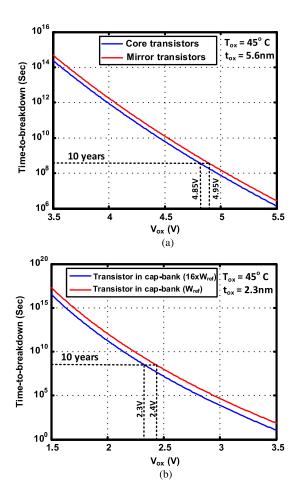

Fig. 15. (a) Estimated time-to-breakdown of this dual-core oscillator based on the measured parameter of 65 nm CMOS in [4]. (a) Thick oxide core transistors. (b) Thin oxide switched-capacitor transistors ( $W_{\rm ref}$  is the smallest transistor width in the switched-capacitor bank).

Flicker noise corner frequency is 130 kHz at the lower end of the tuning range and it increases to 300 kHz at 4.91 GHz because of the switching off all the MoM capacitors. Fig. 13 compares PN and FOM of the dual-core oscillator versus state-of-the-art low-phase-noise CMOS oscillators and some commercial basestation oscillators made of discrete components. Table I compares it with other recently published state-of-the-art CMOS oscillators (and commercial BiCMOS oscillators). This oscillator has the lowest PN of -159.7 dBc/Hz and -176.1 dBc/Hz normalized to the 915 MHz carrier at 3 MHz and 20 MHz offsets, respectively. The measurements of the PN and FoM over the tuning range are depicted in Fig. 14. The average FoM over the tuning range is about 189 dB.

Based on (22), (23), and measurement data in [4] for exactly the same 65-nm CMOS technology, the lifetime estimation of this oscillator is plotted in Fig. 15(a) for both the core and mirror transistors. The plot indicates that the maximum voltage across the oxide for transistors should be less than 4.85 V to ensure 0.01% failure during 10 years of operation at 45 °C. The worst case maximum  $V_{\rm ox}$  in this case is around 4.6 V, which demonstrates no reliability concerns.

As mentioned above, the switched-capacitor transistors used in this design are thin-oxide devices. In order to check their reliability, the same figure (Fig. 15(b)) is plotted for this binary weighted bank. The maximum  $V_{\rm ox}$  in this case is around 1.7 V, which is clearly well below the value for the 10-year operational guaranty.

### VI. CONCLUSION

To further extend the phase noise (PN) performance barrier of CMOS oscillators, a dual-core LC-tank oscillator based on a high-swing class-C (HSCC) topology is introduced in this paper. Simple expressions for PN and interconnect resistance  $R_c$  are derived and verified against circuit-level simulations. Simulations and analysis show that  $R_c$  is not of a high importance up to a certain reasonably large value and that  $R_c$  should be limited due to mismatches between the two cores. This approach can be extended to a higher number of cores and to allow reaching far beyond the state-of-the-art PN levels at the expense of power consumption and area. The proposed oscillator was implement in 65 nm CMOS. Measurement shows that this oscillator can meet even the toughest PN specification of cellular basestations while ensuring long-term reliability.

#### ACKNOWLEDGMENT

The authors would like to express their gratitude to Wireless Infrastructure Group of NXP Semiconductors in Eindhoven, The Netherlands, and RF Department of HiSilicon/Huawei in Shanghai, China, for support. Further thanks to Reza Lotfi, Iman Madadi, Morteza Alavi, and Masoud Babaie at Delft University of Technology for fruitful technical discussions. The authors also gratefully thank Atef Akhnoukh and Wil Straver for measurement support.

### REFERENCES

- [1] 3GPP Specification. [Online]. Available: http://www.etsi.org/deliver/etsi\_ts/145000\_145099/145005/12.03.00\_60/ts\_145005v120300p.pdf.

- [2] M. Babaie and R. Staszewski, "A class-F CMOS oscillator," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3120–3133, Dec. 2013.

- [3] L. Fanori and P. Andreani, "Class-D CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3105–3119, Dec. 2013.

- [4] M. Babaie and R. Staszewski, "An ultra-low phase noise class-F2 CMOS oscillator with 191 dBc/Hz FoM and long-term reliability," *IEEE J. Solid-State Circuits*, vol. 50, no. 3, pp. 679–692, Mar. 2015.

- [5] A. Visweswaran, R. Staszewski, and J. Long, "A clip-and-restore technique for phase desensitization in a 1.2 V 65 nm CMOS oscillator for cellular mobile and base stations," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2012, pp. 350–352.

- [6] L. Fanori, A. Liscidini, and P. Andreani, "A 6.7-to-9.2 GHz 55 nm CMOS hybrid class-B/class-C cellular TX VCO," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2013, pp. 354–356.

- [7] J. Steinkamp and F. A. Henkel, "A colpitts oscillator design for a GSM base station synthesizer," in *Proc. IEEE Radio Freq. Integr. Circuits* (RFIC) Symp., Jun. 2007, pp. 405–408.

- [8] C.-M. Hung, R. Staszewski, N. Barton, M.-C. Lee, and D. Leipold, "A digitally controlled oscillator system for SAW-less transmitters in cellular handsets," *IEEE J. Solid-State Circuits*, vol. 41, no. 5, pp. 1160–1170, May 2006.

- [9] M. Garampazzi, P. Mendes, N. Codega, D. Manstretta, and R. Castello, "Analysis and design of a 195.6 dBc/Hz Peak FoM P-N Class-B oscillator with transformer-based tail filtering," *IEEE J. Solid-State Circuits*, vol. 50, no. 7, pp. 1657–1668, Jul. 2015.

- [10] P. Andreani and X. Wang, "On the phase-noise and phase-error performances of multiphase LC CMOS VCOs," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 1883–1893, Nov. 2004.

- [11] A. Mazzanti and P. Andreani, "Class-C harmonic CMOS VCOs, with a general result on phase noise," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2716–2729, Dec. 2008.

- [12] S. Rong and H. Luong, "Analysis and design of transformer-based dual-band vco for software-defined radios," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 3, pp. 449–462, Mar. 2012.

- [13] A. Mazzanti and A. Bevilacqua, "On the phase noise performance of transformer-based cmos differential-pair harmonic oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 9, pp. 2334–2341, Sep. 2015.

- [14] Z. Wang, S. Diao, L. He, X. Jiang, and F. Lin, "Analysis of current efficiency for cmos class-b lc oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 5, pp. 1345–1352, May 2015.

- [15] M. Garampazi, S. Dal Toso, A. Liscindini, D. Manstretta, P. Mendez, L. Romano, and R. Castello, "An intuitive analysis of phase noise fundamental limits suitable for benchmarking LC oscillators," *IEEE J. Solid-State Circuits*, vol. 49, no. 3, pp. 635–645, Mar. 2014.

- [16] M. Tohidian, S. Ahmadi-Mehr, and R. Staszewski, "Dual-core high-swing class-C oscillator with ultra-low phase noise," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2013, pp. 243–246.

- [17] D. Leeson, "A simple model of feedback oscillator noise spectrum," *Proc. IEEE*, vol. 54, no. 2, pp. 329–330, Feb. 1966.

- [18] M. Tohidian, A. Fotowat-Ahmadi, M. Kamarei, and F. Ndagijimana, "High-swing class-C VCO," in *Proc. ESSCIRC*, Sep. 2011, pp. 495–498.

- [19] B. Razavi, RF Microelectronics (2nd Edition). Upper Saddle River, NJ, USA: Prentice-Hall, 2011.

- [20] H.-C. Chang, X. Cao, U. K. Mishra, and R. York, "Phase noise in coupled oscillators: Theory and experiment," *IEEE Trans. Microwave Theory Tech.*, vol. 45, no. 5, pp. 604–615, May 1997.

- [21] X. Cao and R. York, "Phase noise reduction in scanning oscillator arrays," in *IEEE MTT-S Int. Microw. Symp. Dig.*, May 1995, vol. 2, pp. 769–772.

- [22] A. Rofougaran, J. Rael, M. Rofougaran, and A. Abidi, "A 900 MHz CMOS LC-oscillator with quadrature outputs," in *IEEE Int. 42nd Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 1996, pp. 392–393.

- [23] L. Romano, S. Levantino, C. Samori, and A. Lacaita, "Multiphase LC oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 53, no. 7, pp. 1579–1588, Jul. 2006.

- [24] A. Mirzaei, M. Heidari, R. Bagheri, S. Chehrazi, and A. Abidi, "The quadrature LC oscillator: A complete portrait based on injection locking," *IEEE J. Solid-State Circuits*, vol. 42, no. 9, pp. 1916–1932, Sep. 2007.

- [25] L. Romano, A. Bonfanti, S. Levantino, C. Samori, and A. Lacaita, "5-GHz oscillator array with reduced flicker up-conversion in 0.13-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 41, no. 11, pp. 2457–2467, Nov. 2006.

- [26] F. Shirinfar, M. Nariman, T. Sowlati, M. Rofougaran, R. Rofougaran, and S. Pamarti, "A multichannel, multicore mm-wave clustered VCO with phase noise, tuning range, and lifetime reliability enhancements," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2013, pp. 235–238.

- [27] G. Li, L. Liu, Y. Tang, and E. Afshari, "A low-phase-noise wide-tuning-range oscillator based on resonant mode switching," *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp. 1295–1308, Jun. 2012.

- [28] G. Li and E. Afshari, "A distributed dual-band LC oscillator based on mode switching," *IEEE Trans. Microw. Theory Tech.*, vol. 59, no. 1, pp. 99–107, Jan. 2011.

- [29] Q. Zou, K. Ma, and K. S. Yeo, "A low phase noise and wide tuning range millimeter-wave vco using switchable coupled vco-cores," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 2, pp. 554–563, Feb. 2015.

- [30] M. Taghivand, K. Aggarwal, and A. Poon, "A 3.24-to-8.45 GHz low-phase-noise mode-switching oscillator," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2014, pp. 368–369.

- [31] T.-H. Tsai, M.-S. Yuan, C.-H. Chang, C.-C. Liao, C.-C. Li, and R. Staszewski, "A 1.22 ps integrated-jitter 0.25-to-4 GHz fractional-N ADPLL in 16 nm FinFET CM0S," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2015, pp. 1–3.

- [32] T. H. Lee, *The Design of CMOS Radio-Frequency Integrated Circuits*. Cambridge, MA, USA: Cambridge Univ. Press, 2004.

- [33] A. Mirzaei and A. Abidi, "The spectrum of a noisy free-running oscillator explained by random frequency pulling," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 3, pp. 642–653, 2010.

- [34] S. A. R. Ahmadi Mehr, M. Tohidian, and R. Staszewski, "Frequency translation through fractional division for a two-channel pulling mitigation," in *Proc. ESSCIRC*, pp. 241–244.

- [35] S. Ahmadi Mehr, M. Tohidian, and R. Staszewski, "Toward solving multichannel RF-SoC integration issues through digital fractional division," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 24, no. 3, pp. 1071–1082, Mar. 2016.

Seyed Amir-Reza Ahmadi-Mehr (S'08–M'15) received the B.S.E.E. degree from Isfahan University of Technology, Isfahan, Iran, in 2007 and the M.S. degree (with honors) from University of Tehran, Tehran, Iran, in 2009, both in electrical engineering. In 2015, he received the Ph.D. degree from Delft University of Technology, The Netherlands. He is now Principal Circuit and System Designer and Co-founder of Qualinx B.V. since February 2015. His research interests includes RF-CMOS integrated circuit design for wireless communications, high performance, low

power frequency synthesizer, and transmitter for Internet-of-Things (IoT).

Massoud Tohidian (S'08–M'15) received the B.Sc. degree (with honors) from Ferdowsi University of Mashhad, Iran, in 2007 and the M.Sc. degree in electrical engineering (with honors) from the University of Tehran, Iran, in 2010. In 2015, he received the Ph.D. degree (cum laude) from Delft University of Technology (TU Delft), The Netherlands. He was a researcher in IMEP-LAHC laboratory, Grenoble, France, in 2009–2010. He was a consultant at M4S/Hisilicon, Leuven, Belgium, in 2013–2014, designing a 28 nm SAW-less receiver chip for

mobile phones. Since February 2015, he is co-founder and CEO of Qualinx B.V., The Netherlands, developing low-power CMOS wireless chips. His research interest includes RF transceivers, discrete-time/digital signal processing, PLL, and oscillators. He holds 7 patents and patent applications in the field of RF-CMOS design.

Robert Bogdan Staszewski (M'97–SM'05–F'09) was born in Bialystok, Poland. He received the B.S. degree (*summa cum laude*) in electrical engineering, the M.S. degree in electrical engineering, and the Ph.D. degree in electrical engineering from the University of Texas at Dallas, Dallas, TX, USA, in 1991, 1992, and 2002, respectively. From 1991 to 1995, he was with Alcatel Network Systems, Richardson, TX, USA, working on SONET cross-connect systems for fiber optics communications. He joined Texas Instruments, Dallas, TX, USA, in 1995, where he was

elected Distinguished Member of Technical Staff (limited to 2% of technical staff). Between 1995 and 1999, he was engaged in advanced CMOS read channel development for hard disk drives. In 1999, he co-started a Digital RF Processor (DRP) Group within Texas Instruments with a mission to invent new digitally intensive approaches to traditional RF functions for integrated radios in deeply-scaled CMOS processes. He was appointed a CTO of the DRP Group between 2007 and 2009. In July 2009, he joined Delft University of Technology, Delft, The Netherlands, where he is currently a part-time Full Professor. Since September 2014, he has been a Professor with the University College Dublin (UCD), Dublin, Ireland. He has authored and coauthored three books, five book chapters, 190 journal and conference publications, and holds 140 issued U.S. patents. His research interests include nanoscale CMOS architectures and circuits for frequency synthesizers, transmitters, and receivers.

Prof. Staszewski has been a TPC Member of ISSCC, RFIC, ESSCIRC, ISCAS, and RFIT. He is a recipient of the IEEE Circuits and Systems Industrial Pioneer Award.