# CMOS Bandgap References and Temperature Sensors and Their Applications

# CMOS Bandgap References and Temperature Sensors and Their Applications

---

## PROEFSCHRIFT

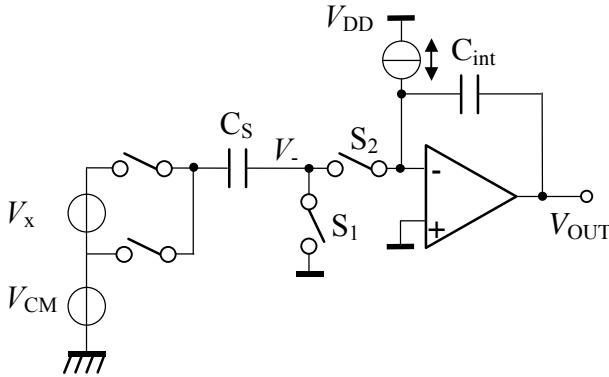

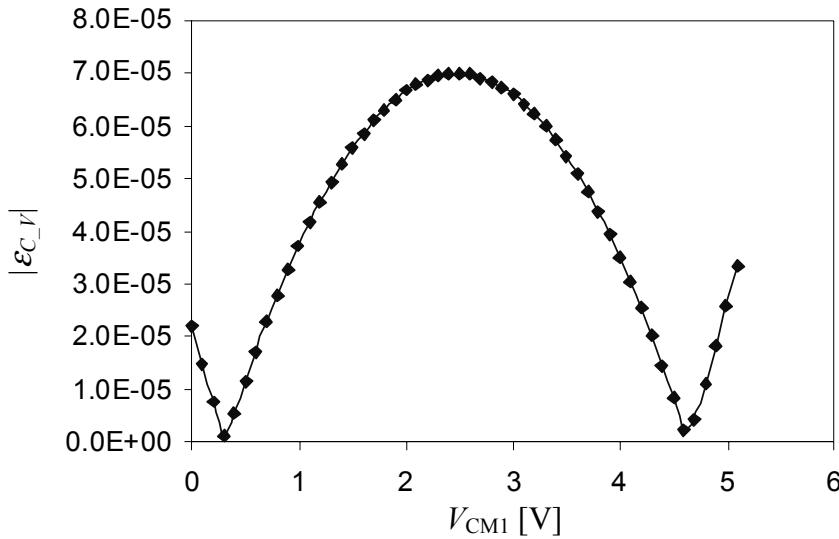

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

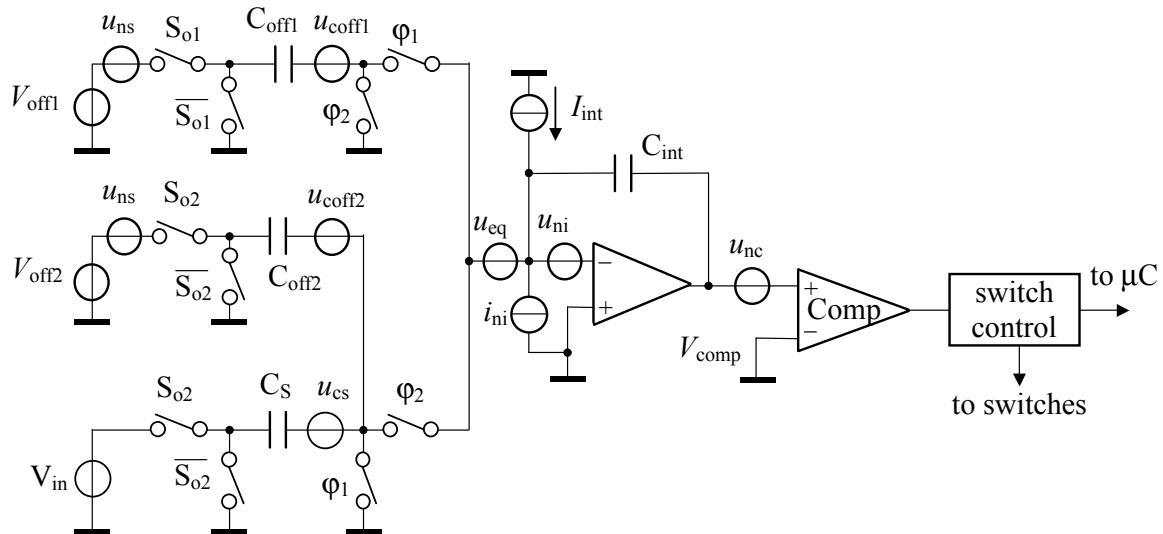

op gezag van de Rector Magnificus Prof. dr. ir. J. T. Fokkema,

voorzitter van het College voor Promoties,

in het openbaar te verdedigen

op dinsdag 11 januari 2005 om 10:30 uur

door

Guijie WANG

Master of Science in Electronics, Nankai University, China,

geboren te Henan, China

Dit proefschrift is goedgekeurd door de promotores:

Prof. dr. ir. G.C.M. Meijer

Prof. dr. ir. A.H.M. van Roermund

Samenstelling promotiecommissie:

|                                    |                                             |

|------------------------------------|---------------------------------------------|

| Rector Magnificus,                 | voorzitter                                  |

| Prof. dr. ir. G.C.M. Meijer        | Technische Universiteit Delft, promotor     |

| Prof. dr. ir. A.H.M. van Roermund, | Technische Universiteit Eindhoven, promotor |

| Prof. dr. ir. J.R. Long,           | Technische Universiteit Delft               |

| Prof. dr. ir. J.H. Huijsing,       | Technische Universiteit Delft               |

| Prof. dr. ir. J.W. Slotboom,       | Technische Universiteit Delft               |

| Prof. ir. A.J.M. van Tuijl,        | Philips Research Laboratory                 |

| Dr. ir. H. Casier,                 | AMI Semiconductor Belgium                   |

| Prof. dr. P.J. French,             | Technische Universiteit Delft, reservelid   |

*Published and distributed by:* Optima Grafische Communicatie

Pearl Buckplaats 37

Postbus 84115, 3009 CC, Rotterdam

Phone: +31 10 220 11 49

Fax: +31 10 456 63 54

ISBN: 90-9018727-8

Keywords: CMOS technology, substrate bipolar transistors, temperature sensor, bandgap reference, voltage-to-period converter, three signal auto-calibration, dynamic element matching.

Copyright © 2004 by Guijie Wang

All right reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by means, electronic or mechanical, including photocopying, recording, or by any information storage and retrieval system, without written permission from the publisher: Optima Grafische Communicatie.

Printed in The Netherlands

*For Xiujun*

*For my children*

*For my parents*

# Contents

|          |                                                                                |           |

|----------|--------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introductions</b>                                                           | <b>1</b>  |

| 1.1      | Silicon temperature sensors and bandgap references                             | 1         |

| 1.2      | Why CMOS technology                                                            | 1         |

| 1.3      | Statement of the problems                                                      | 2         |

| 1.4      | The objectives of the project                                                  | 3         |

| 1.5      | The outline of the thesis                                                      | 3         |

|          | References                                                                     | 5         |

| <b>2</b> | <b>Bipolar components in CMOS technology</b>                                   | <b>7</b>  |

| 2.1      | Introduction                                                                   | 7         |

| 2.2      | Basic theory of bipolar transistors                                            | 7         |

| 2.2.1    | Ideal case                                                                     | 7         |

| 2.2.2    | Low-level injection                                                            | 10        |

| 2.2.3    | High-level injection                                                           | 11        |

| 2.2.4    | The temperature-sensor signals and the bandgap-reference signals               | 11        |

| 2.2.5    | Calibration of bandgap-references and temperature sensors                      | 13        |

| 2.3      | Bipolar transistors in CMOS technology                                         | 15        |

| 2.3.1    | Lateral transistor                                                             | 15        |

| 2.3.2    | Vertical substrate transistor                                                  | 16        |

| 2.3.3    | Comparison of two types of the bipolar transistors                             | 17        |

| 2.4      | Conclusions                                                                    | 18        |

|          | References                                                                     | 19        |

| <b>3</b> | <b>Temperature characterization</b>                                            | <b>21</b> |

| 3.1      | Introduction                                                                   | 21        |

| 3.2      | Measurement set-ups                                                            | 21        |

| 3.3      | Parameter characterizations                                                    | 23        |

| 3.3.1    | The saturation current $I_S$                                                   | 24        |

| 3.3.2    | The knee current $I_{KF}$                                                      | 24        |

| 3.3.3    | Parameters $V_{go}$ and $\eta$                                                 | 25        |

| 3.3.4    | Effective emission coefficient $m$                                             | 28        |

| 3.3.5    | Forward current gain $B_F$                                                     | 30        |

| 3.3.6    | Base resistances $R_B$                                                         | 32        |

| 3.4      | Effects affecting the accuracy of $V_{BE}(I_C, T)$ and $\Delta V_{BE}(I_C, T)$ | 35        |

| 3.4.1    | Base resistances $R_B$                                                         | 35        |

| 3.4.2    | Forward current gain $B_F$                                                     | 36        |

| 3.4.3    | Effective emission coefficient $m$                                             | 38        |

| 3.4.4    | High-level injection effect                                                    | 39        |

| 3.4.5    | Low-level injection effect                                                     | 39        |

| 3.4.6    | Thermal effects                                                                | 40        |

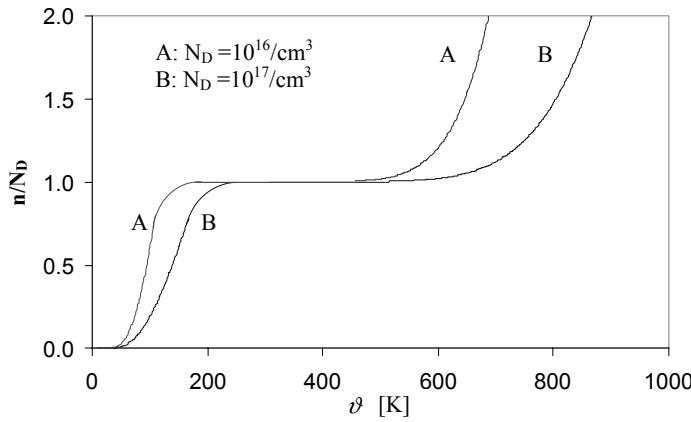

| 3.4.7    | Freeze-out effect                                                              | 42        |

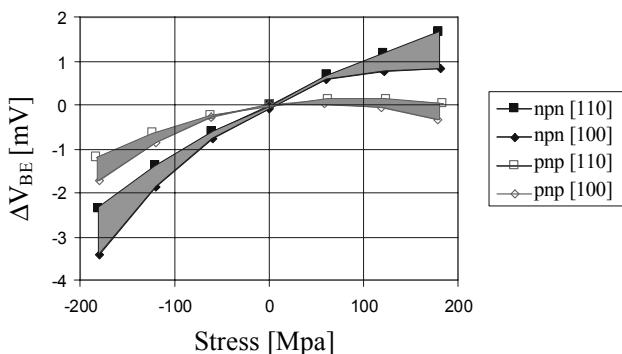

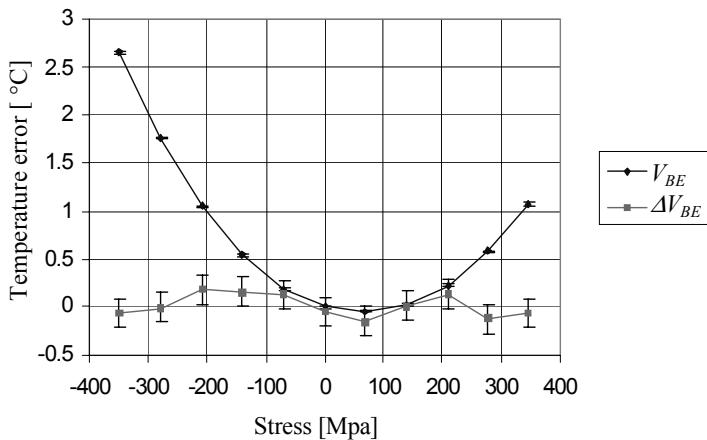

| 3.4.8    | Piezo-junction effect                                                          | 43        |

|                                                                         |            |

|-------------------------------------------------------------------------|------------|

| 3.5 Conclusions                                                         | 45         |

| References                                                              | 48         |

| <b>4 Advanced techniques in circuit design</b>                          | <b>49</b>  |

| 4.1 Introduction                                                        | 49         |

| 4.2 Three-signal technique                                              | 51         |

| 4.3 Modulators                                                          | 51         |

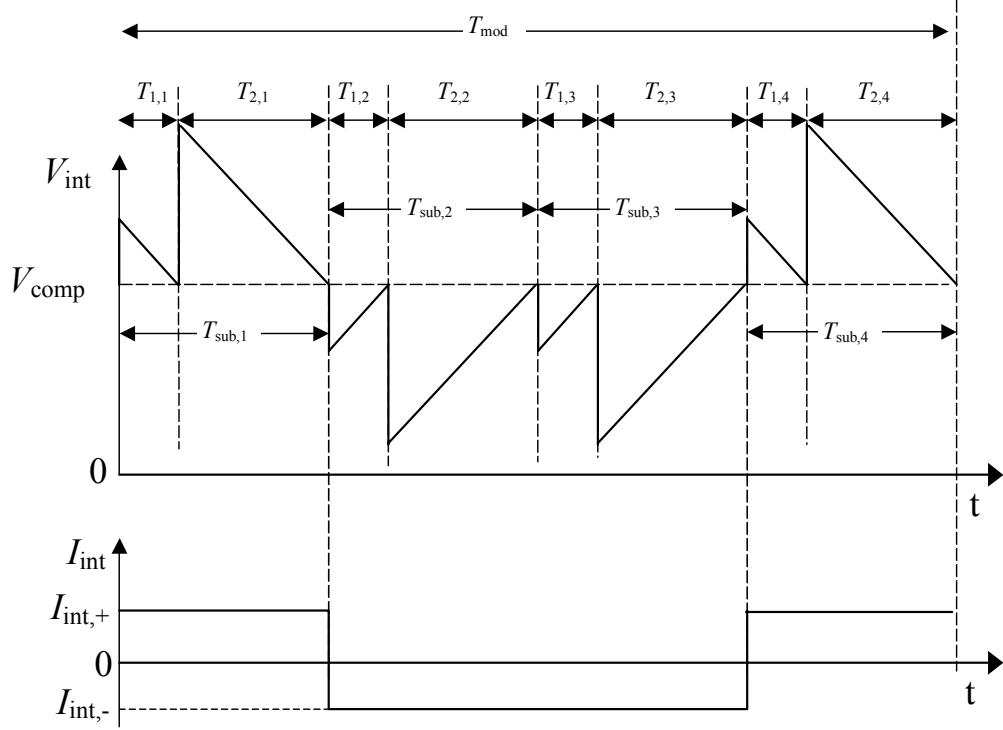

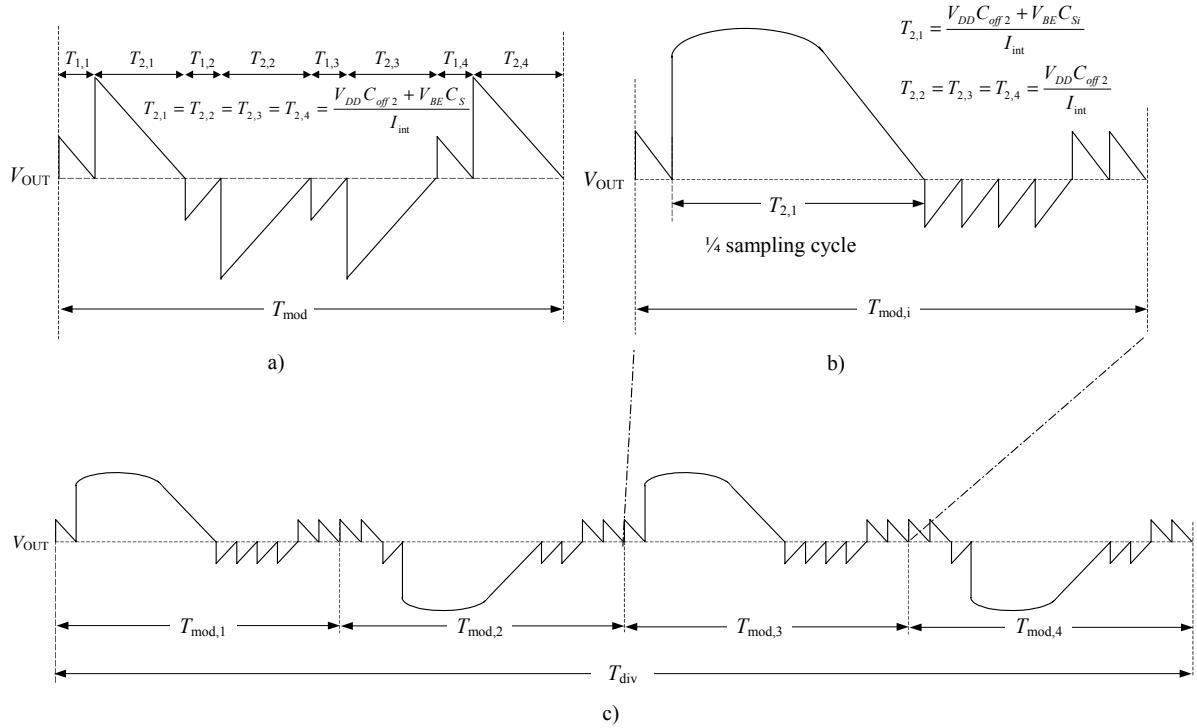

| 4.3.1 Selection of modulator                                            | 52         |

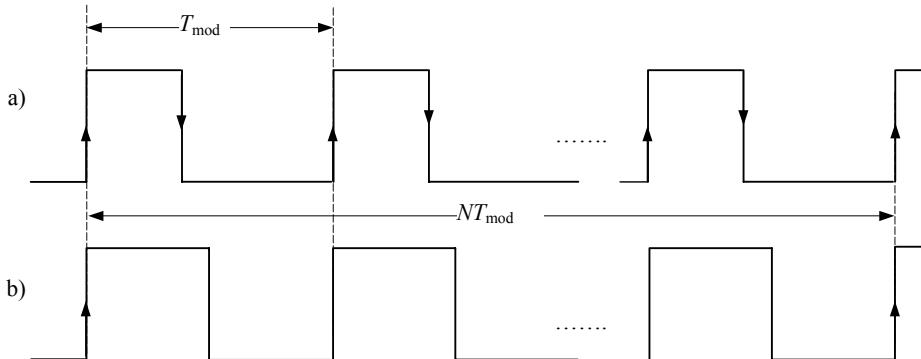

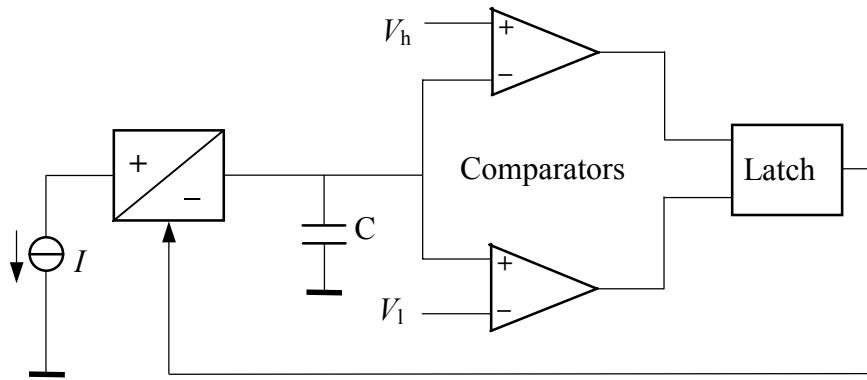

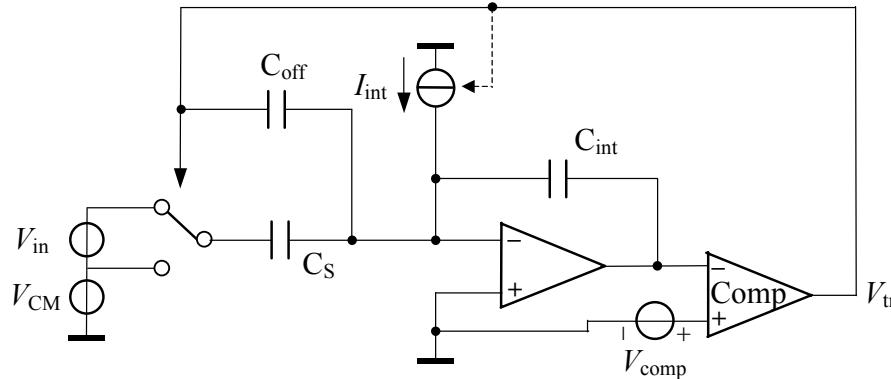

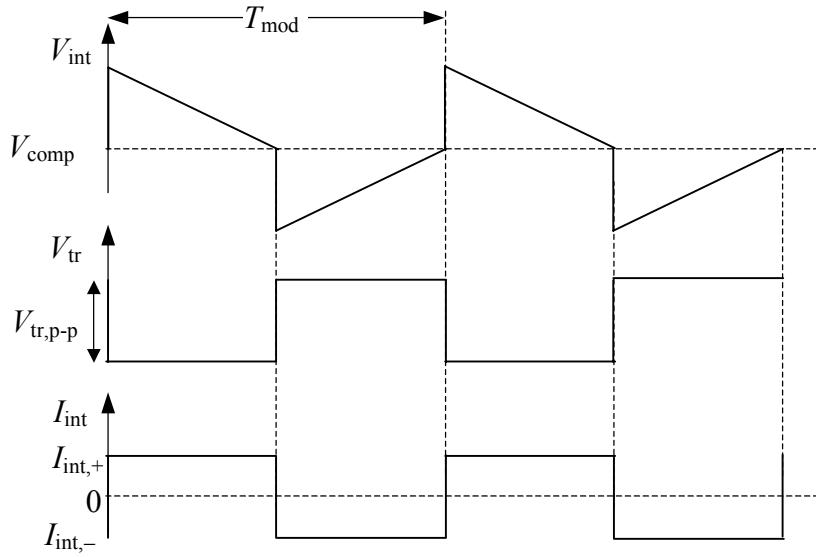

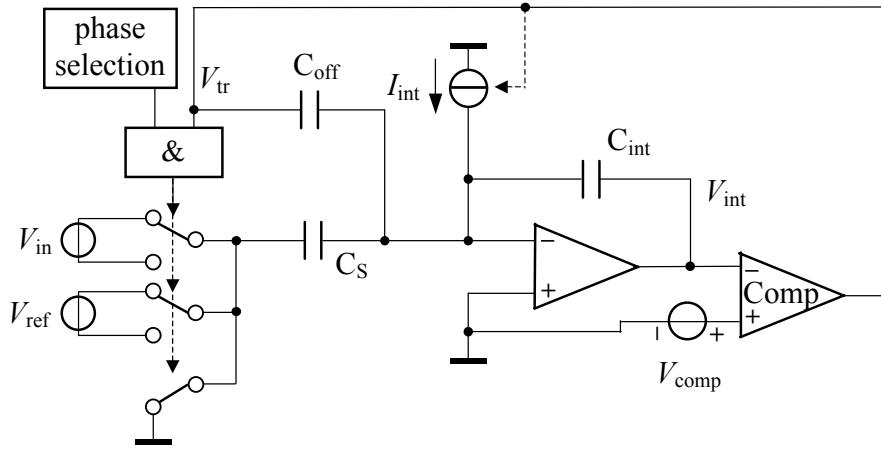

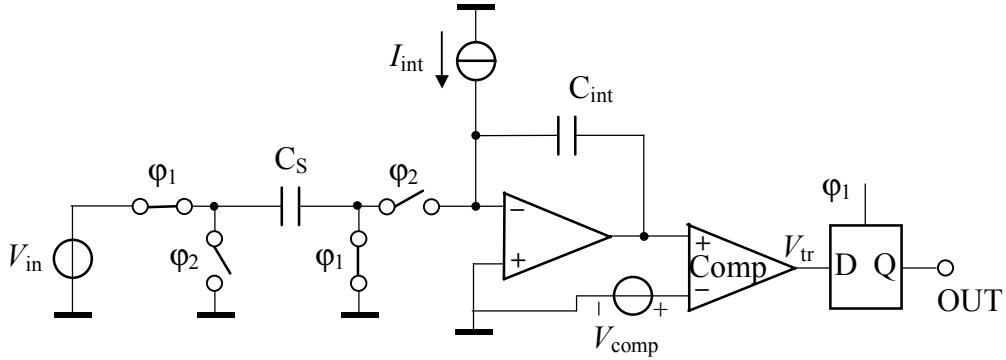

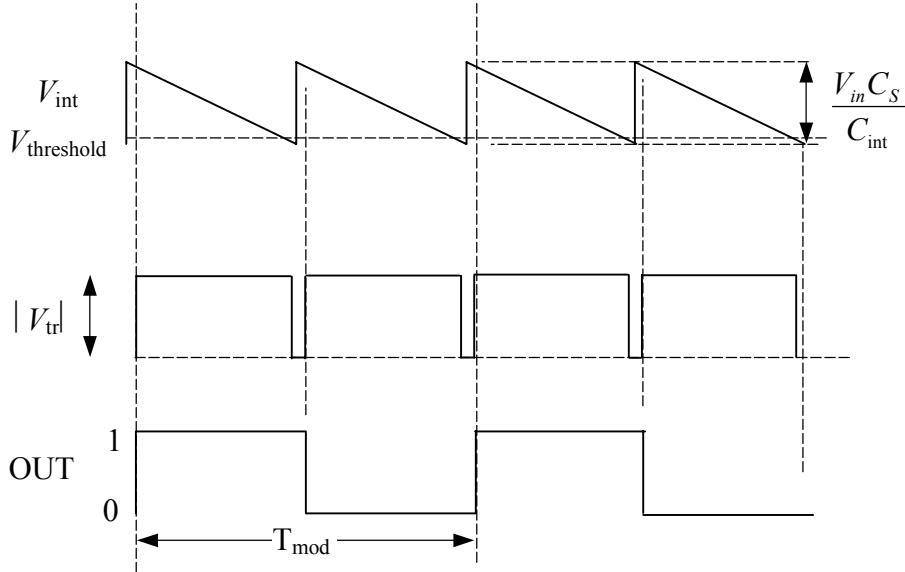

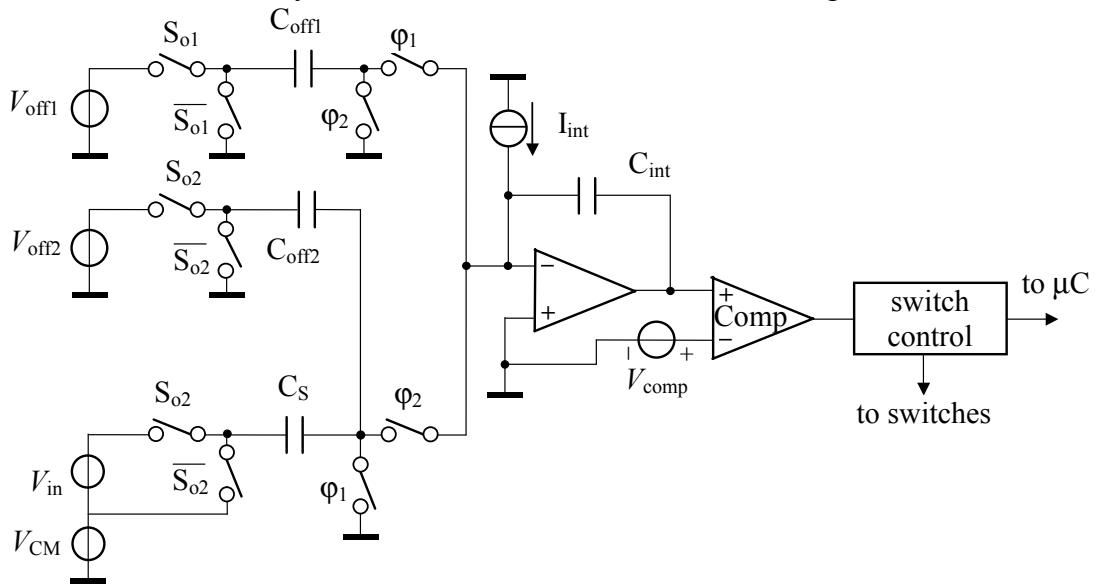

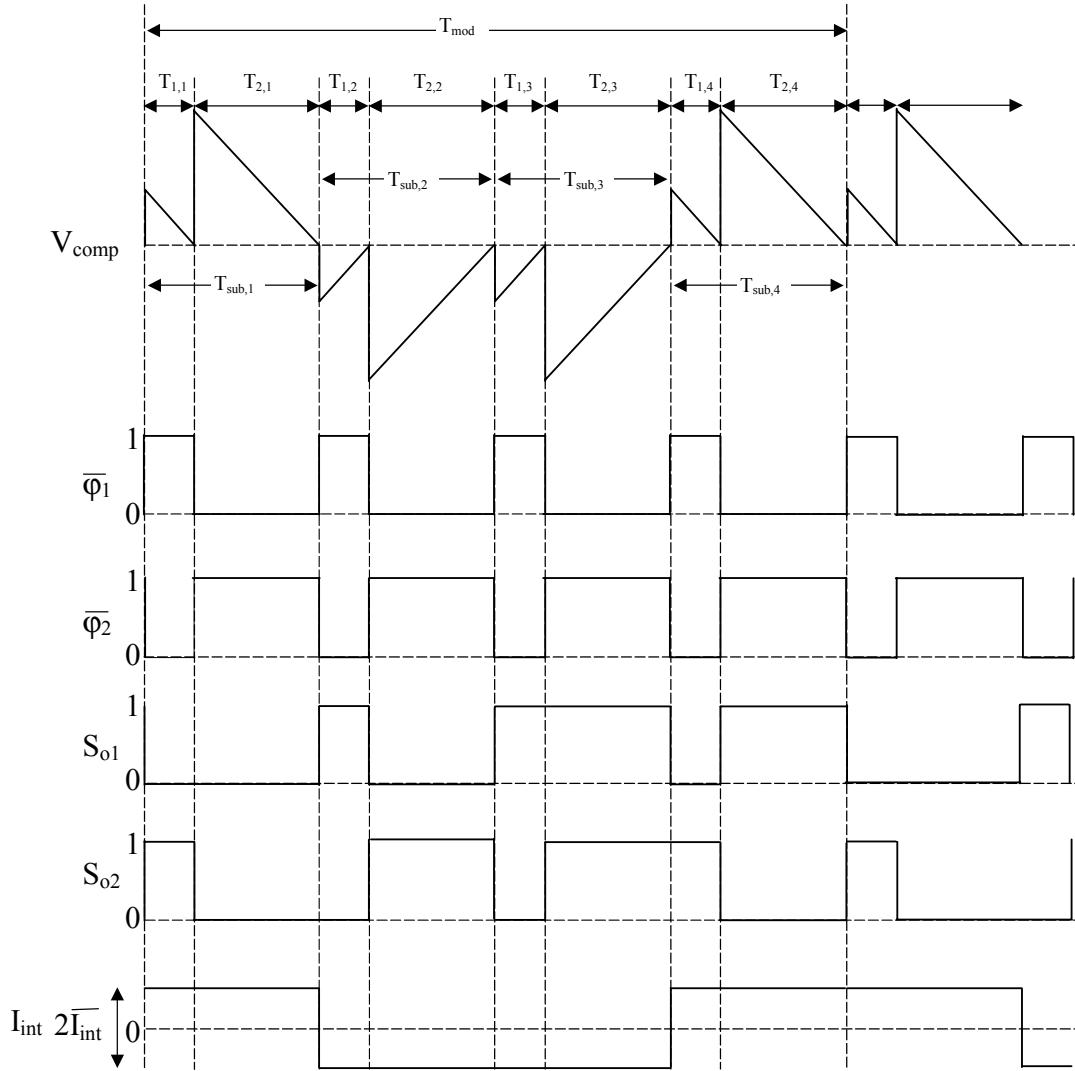

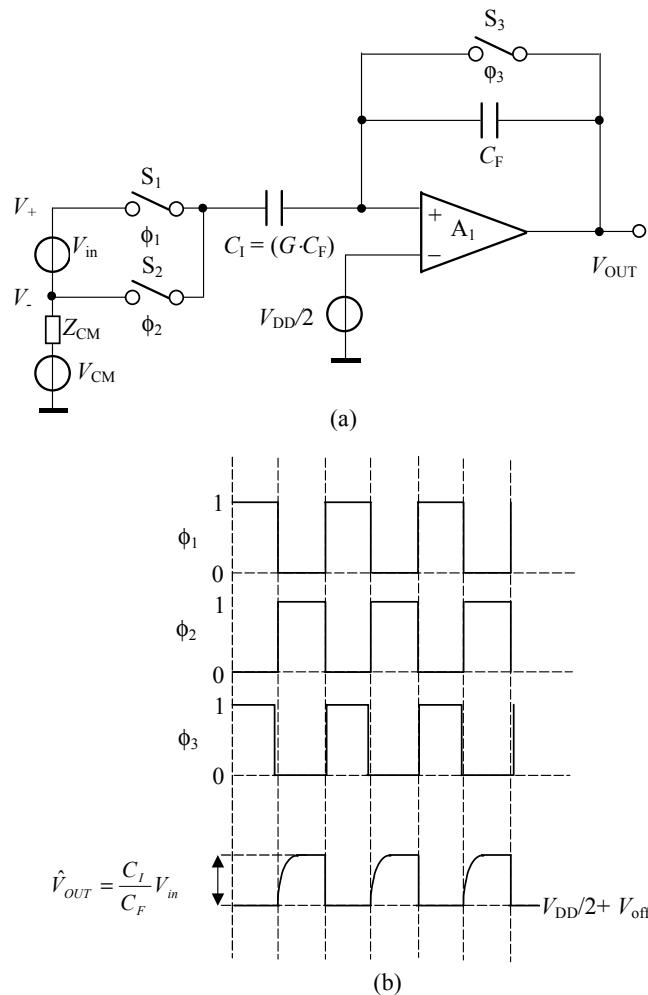

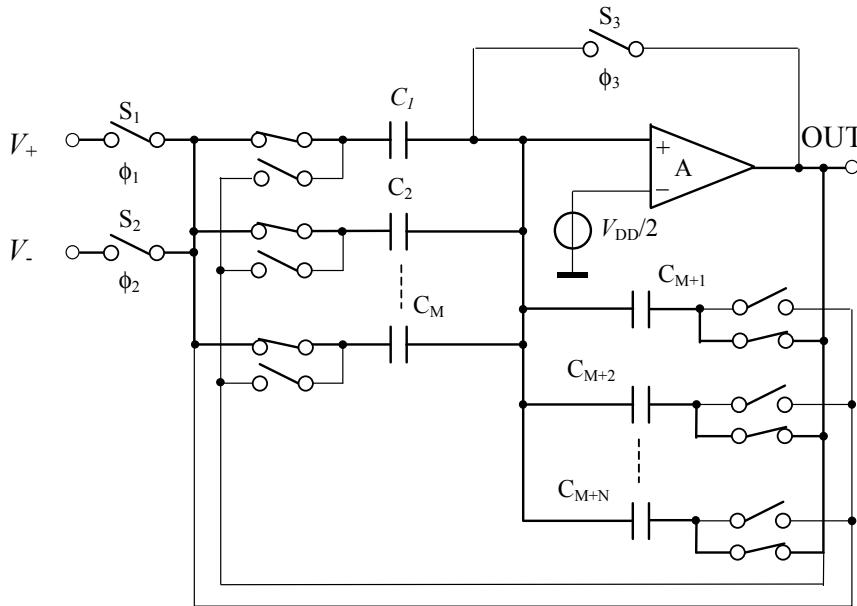

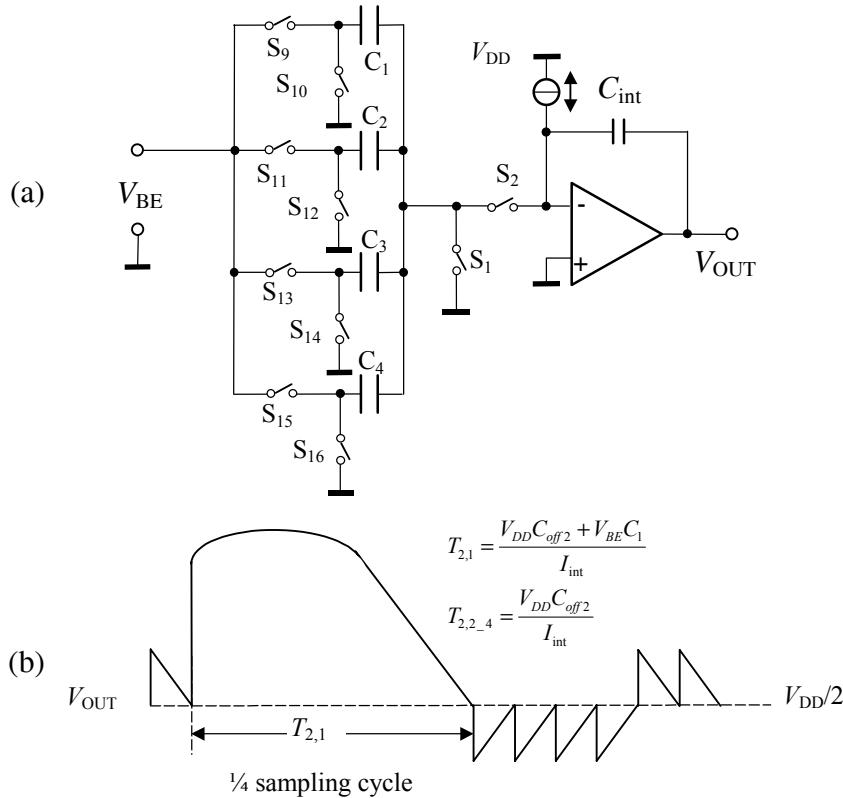

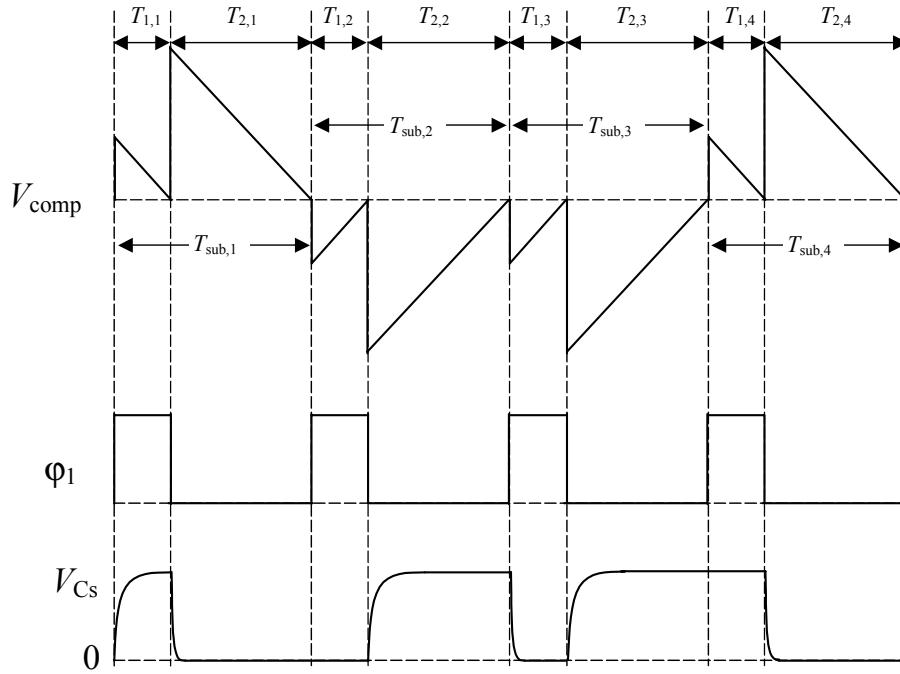

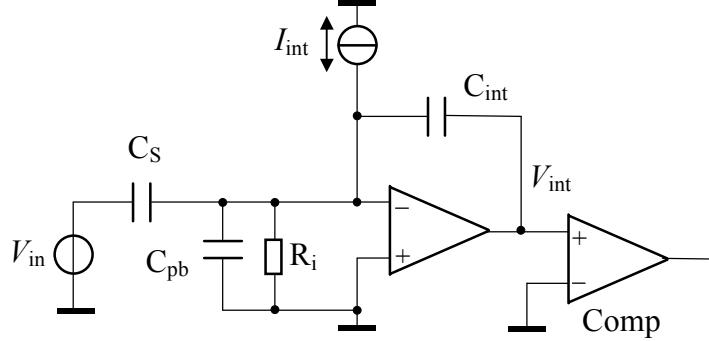

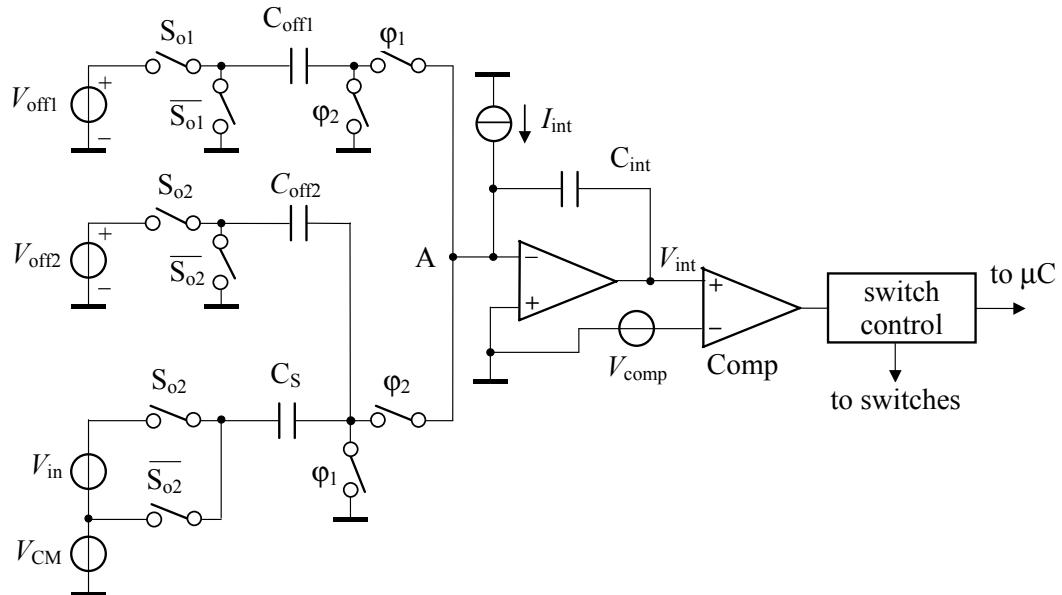

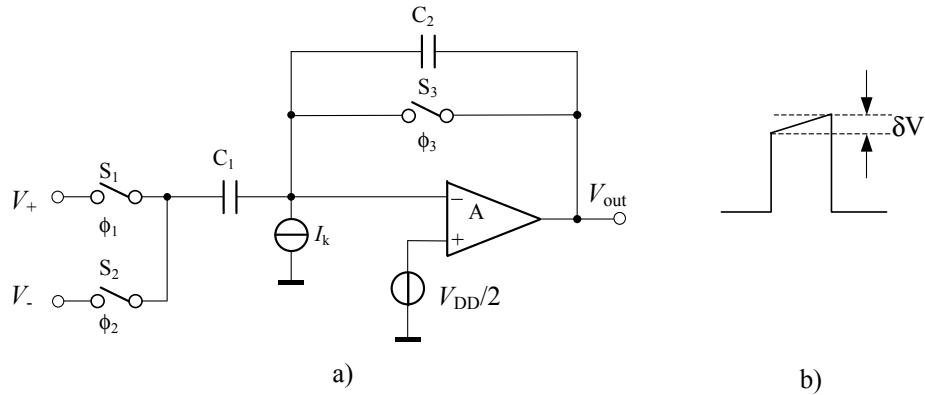

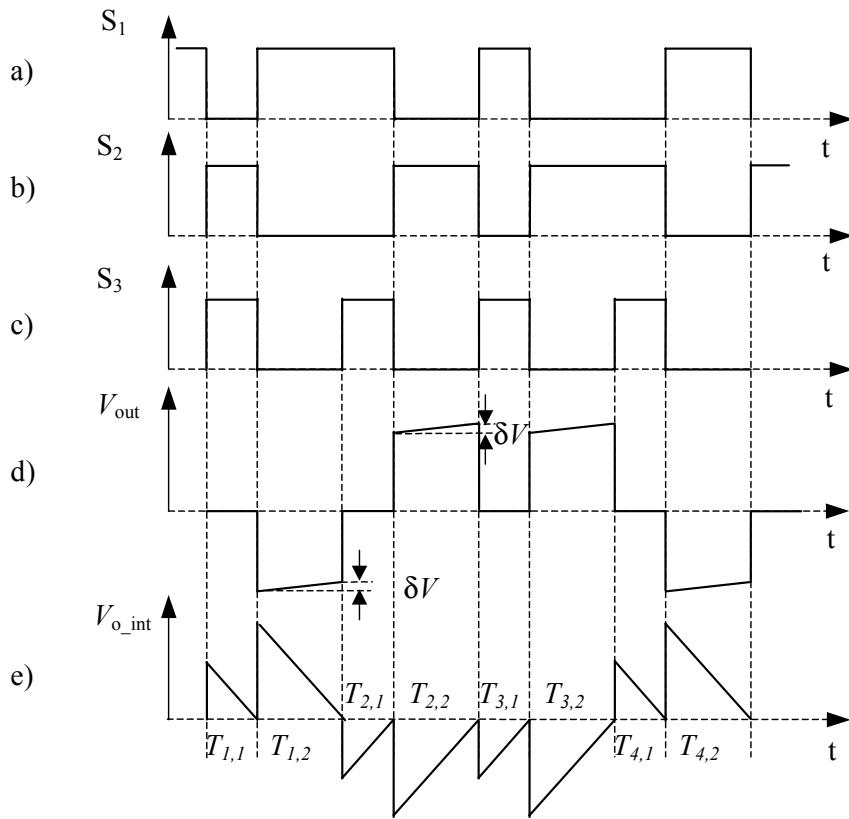

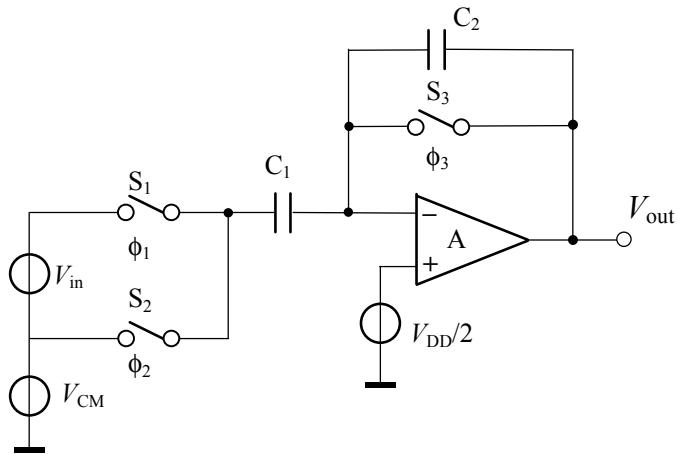

| 4.3.2 Voltage-to-period converter                                       | 54         |

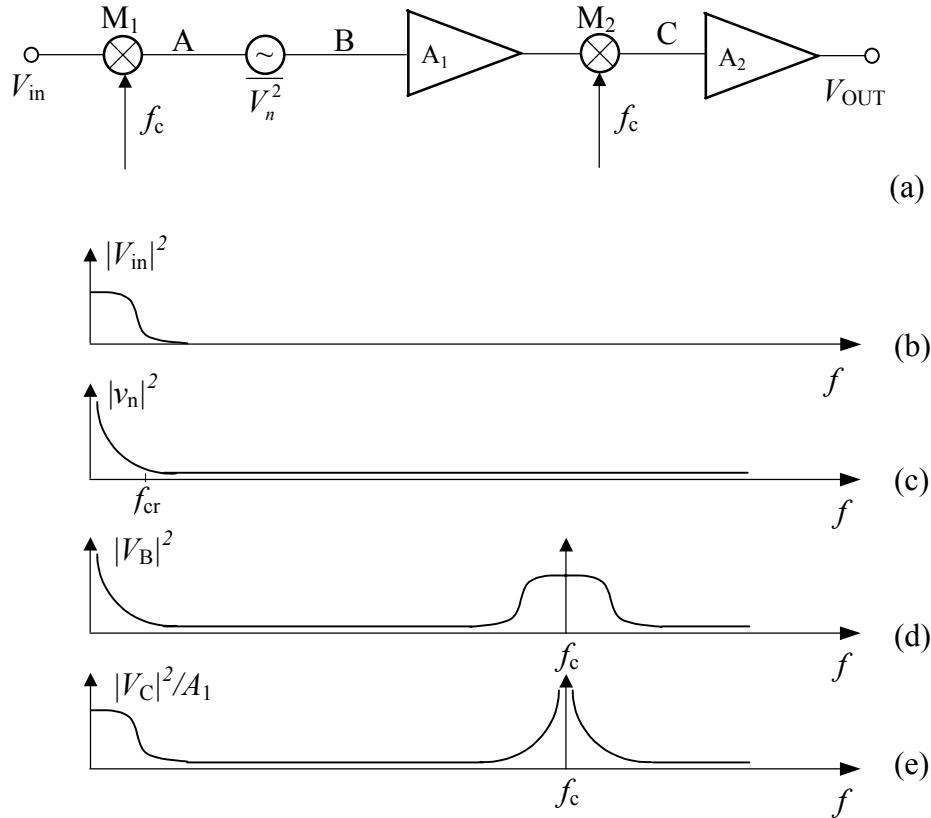

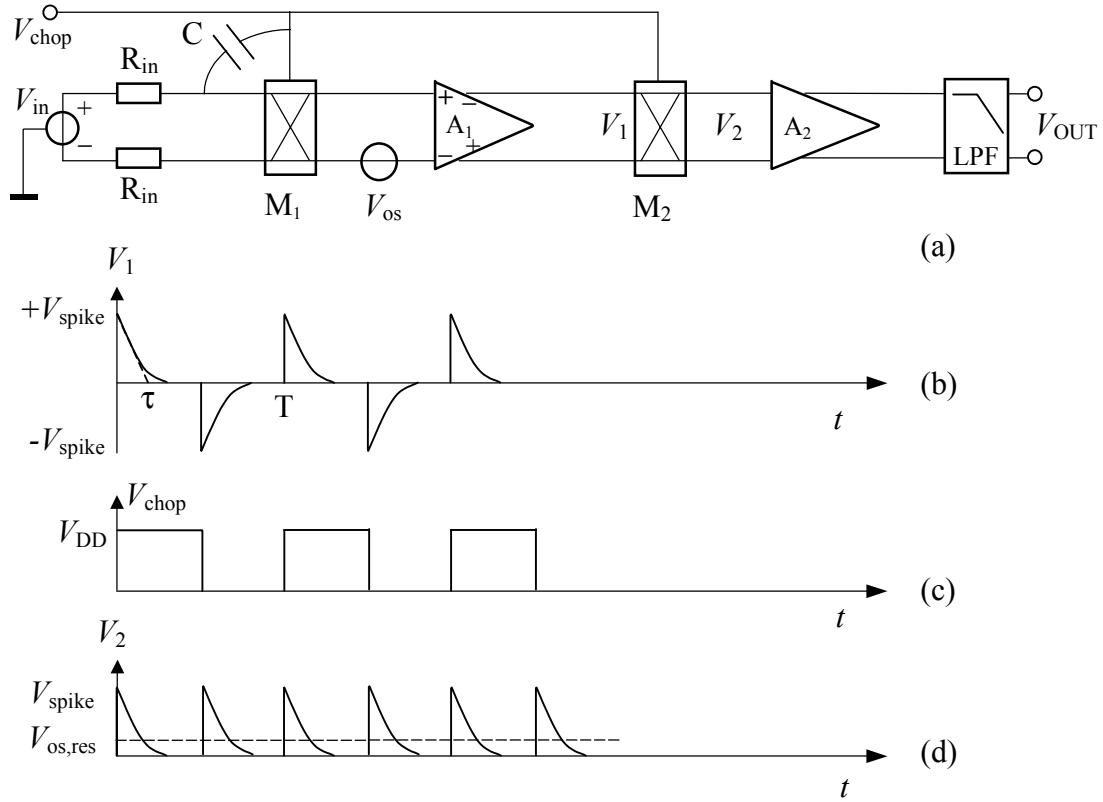

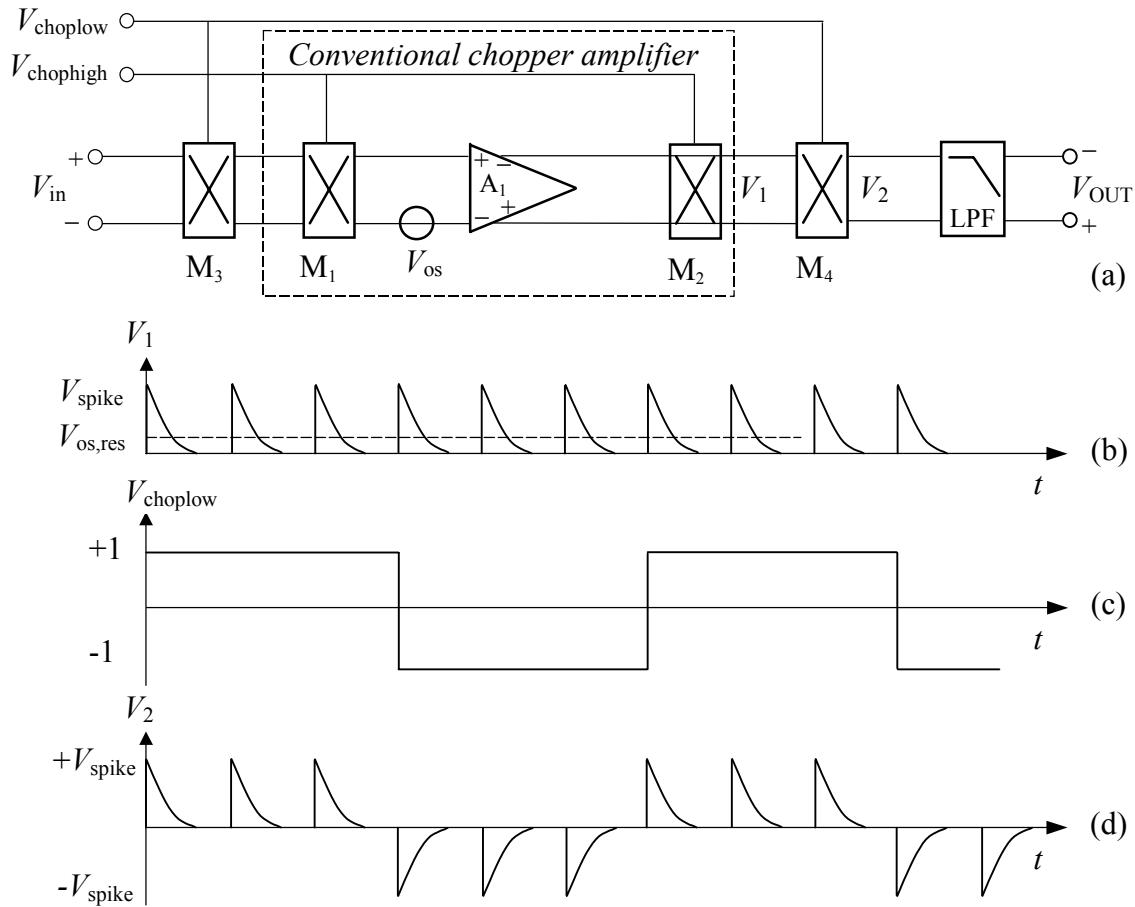

| 4.4 Chopping technique                                                  | 59         |

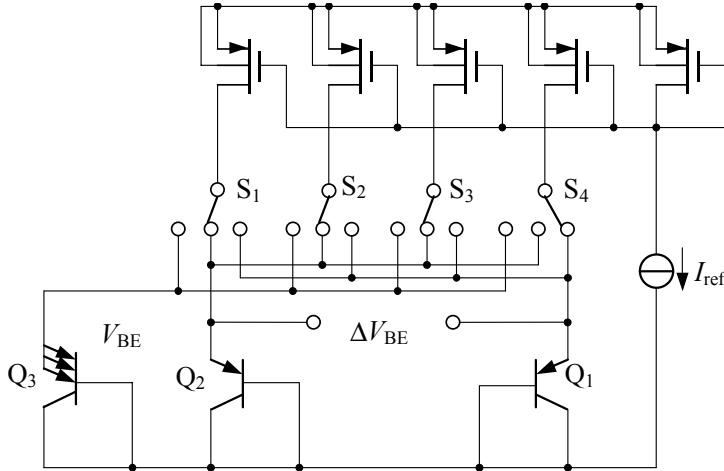

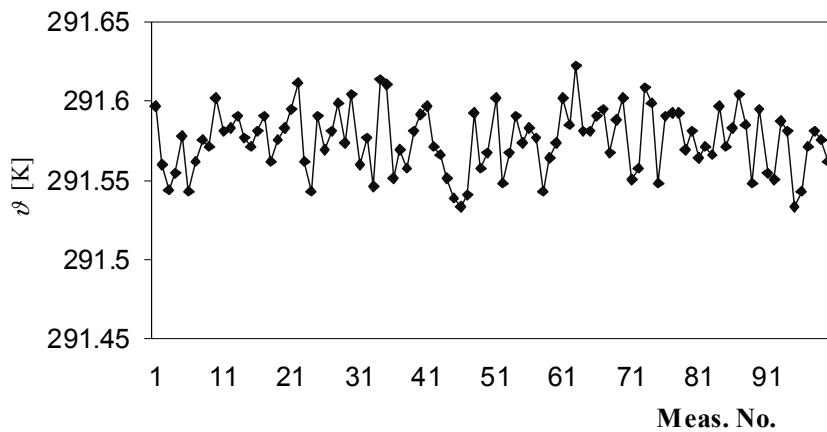

| 4.5 DEM techniques                                                      | 63         |

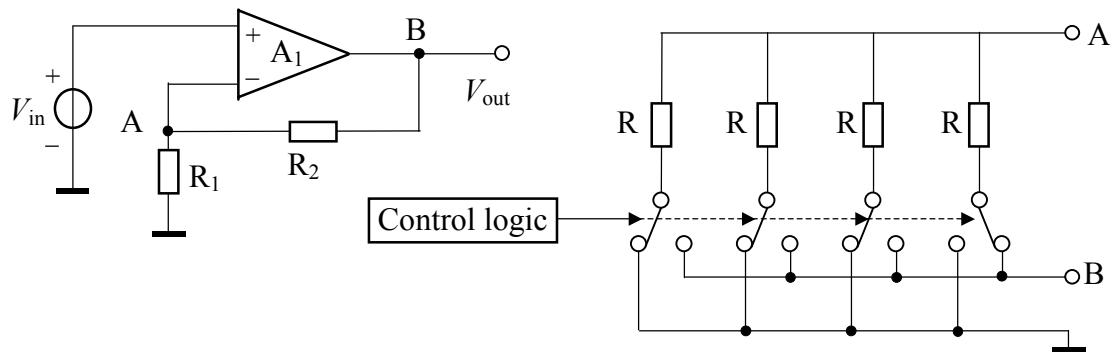

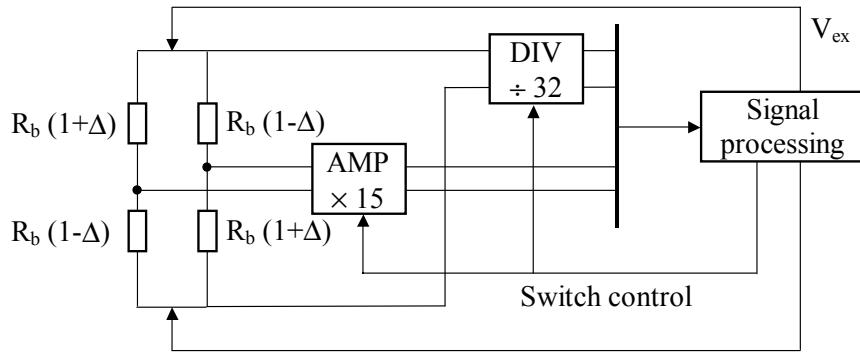

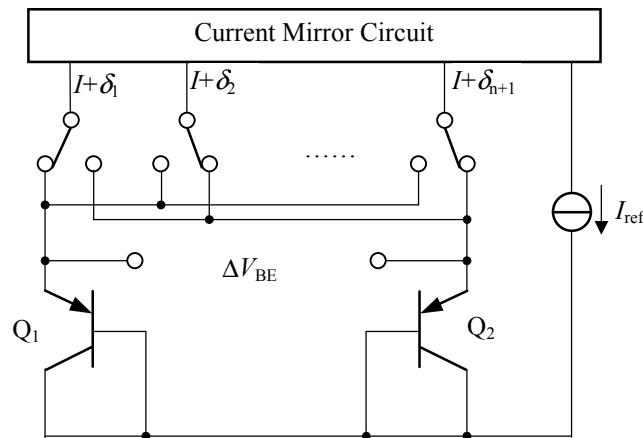

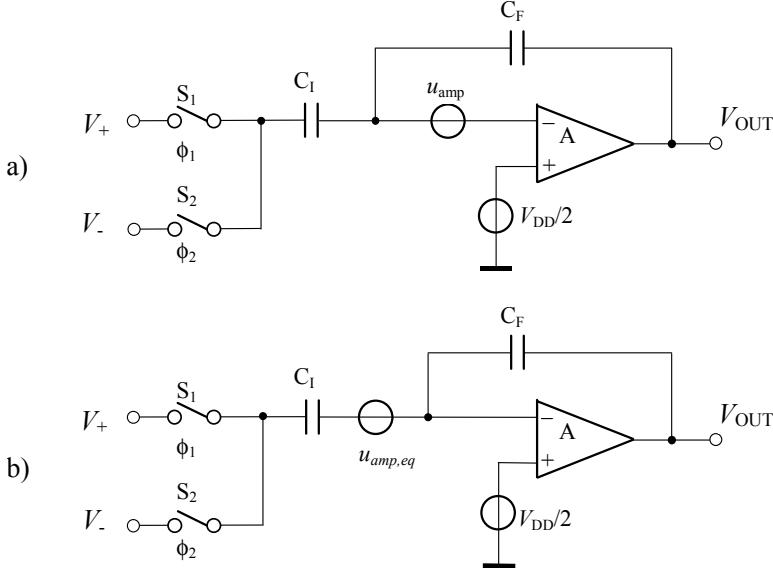

| 4.5.1 DEM amplification of small voltage signals                        | 63         |

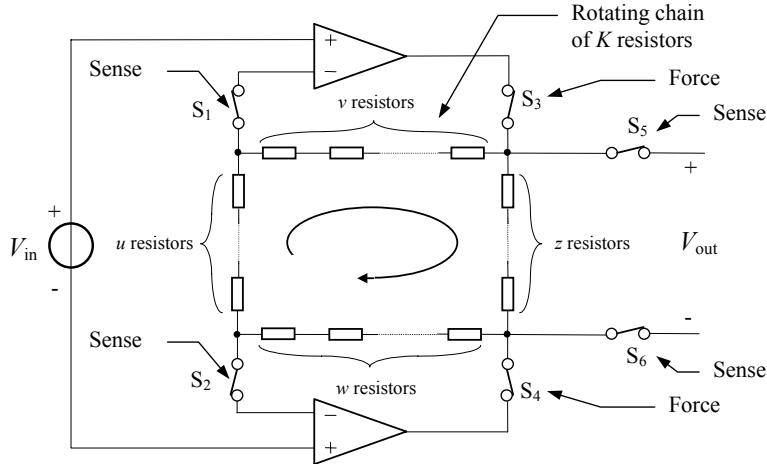

| 4.5.2 DEM division of large voltage signals                             | 67         |

| 4.5.3 DEM biasing for PTAT circuit                                      | 70         |

| 4.6 Remaining problems                                                  | 72         |

| 4.6.1 Non-linearity                                                     | 72         |

| 4.6.2 Noise                                                             | 81         |

| 4.7 Conclusion                                                          | 84         |

| References                                                              | 85         |

| <b>5 Architecture considerations</b>                                    | <b>87</b>  |

| 5.1 Introduction                                                        | 87         |

| 5.2 Thermal design considerations                                       | 87         |

| 5.3 Considerations for the electrical system design                     | 89         |

| 5.4 The measurement requirements                                        | 92         |

| 5.4.1 Accuracy of bandgap-reference voltage                             | 92         |

| 5.4.2 Accuracy of the measurement of the reference-junction temperature | 93         |

| 5.4.3 Linearity and the noise of the voltage-to-period converter        | 93         |

| 5.5 The input configuration                                             | 93         |

| 5.6 Configurations considering the bipolar transistors                  | 96         |

| 5.6.1 Configuration using multi-bipolar transistors                     | 96         |

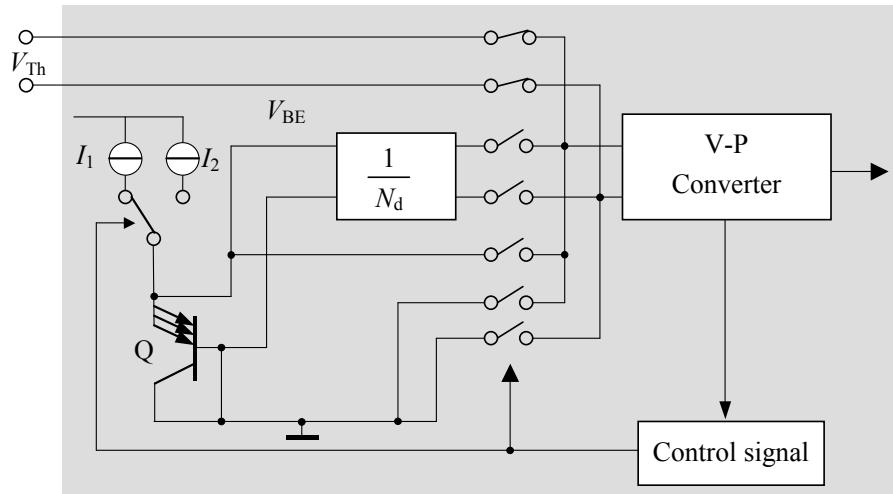

| 5.6.2 Configuration using a single bipolar transistor                   | 97         |

| 5.6.3 Comparison of the two configurations                              | 98         |

| 5.7 Conclusions                                                         | 98         |

| References                                                              | 100        |

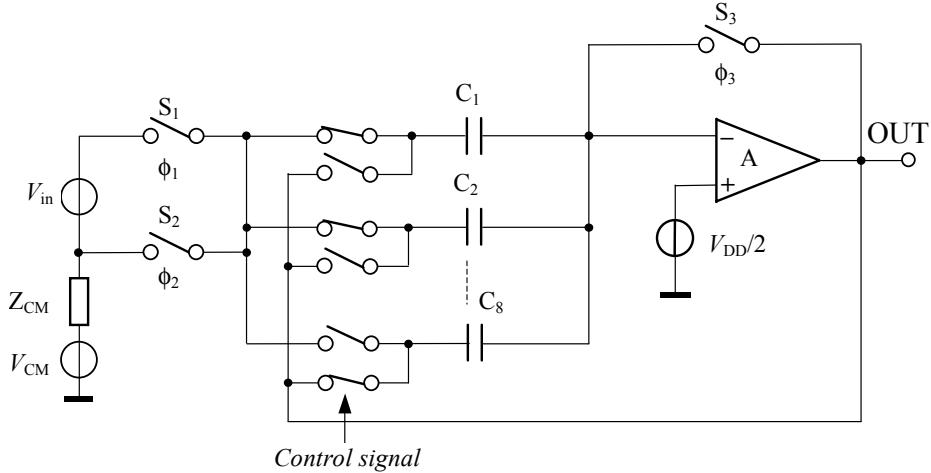

| <b>6 Smart thermocouple interface</b>                                   | <b>101</b> |

| 6.1 Introduction                                                        | 101        |

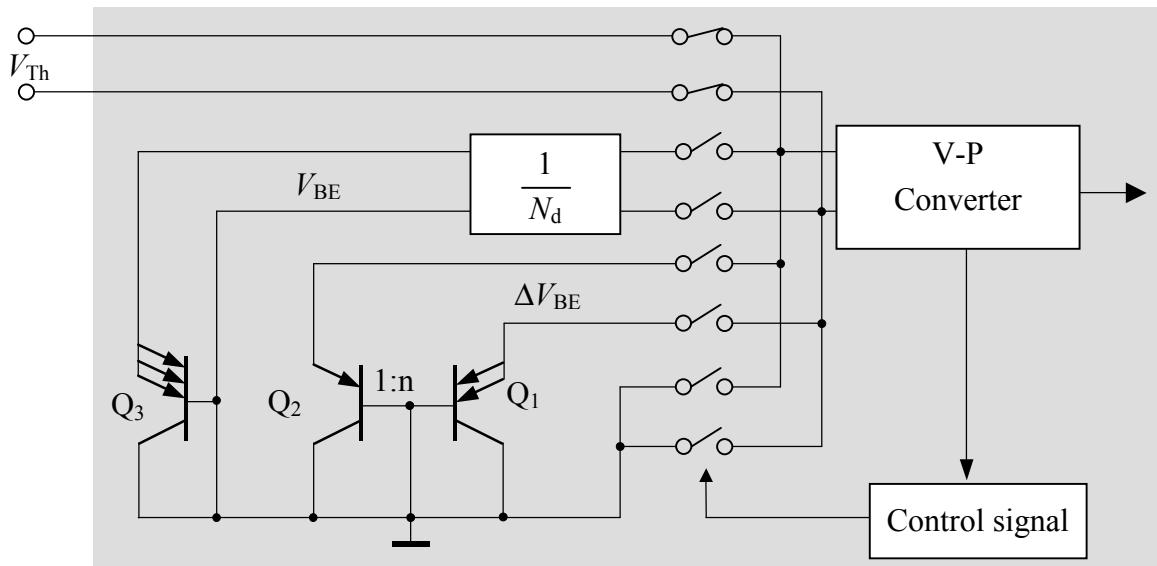

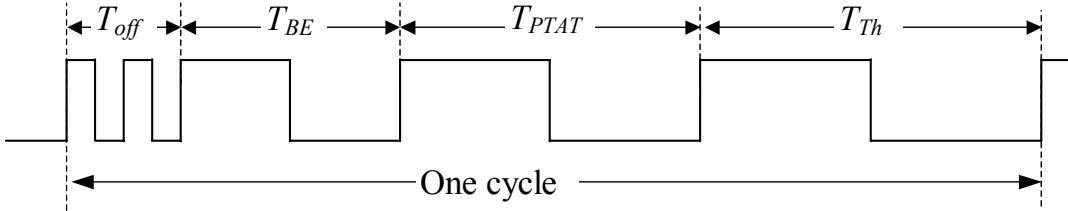

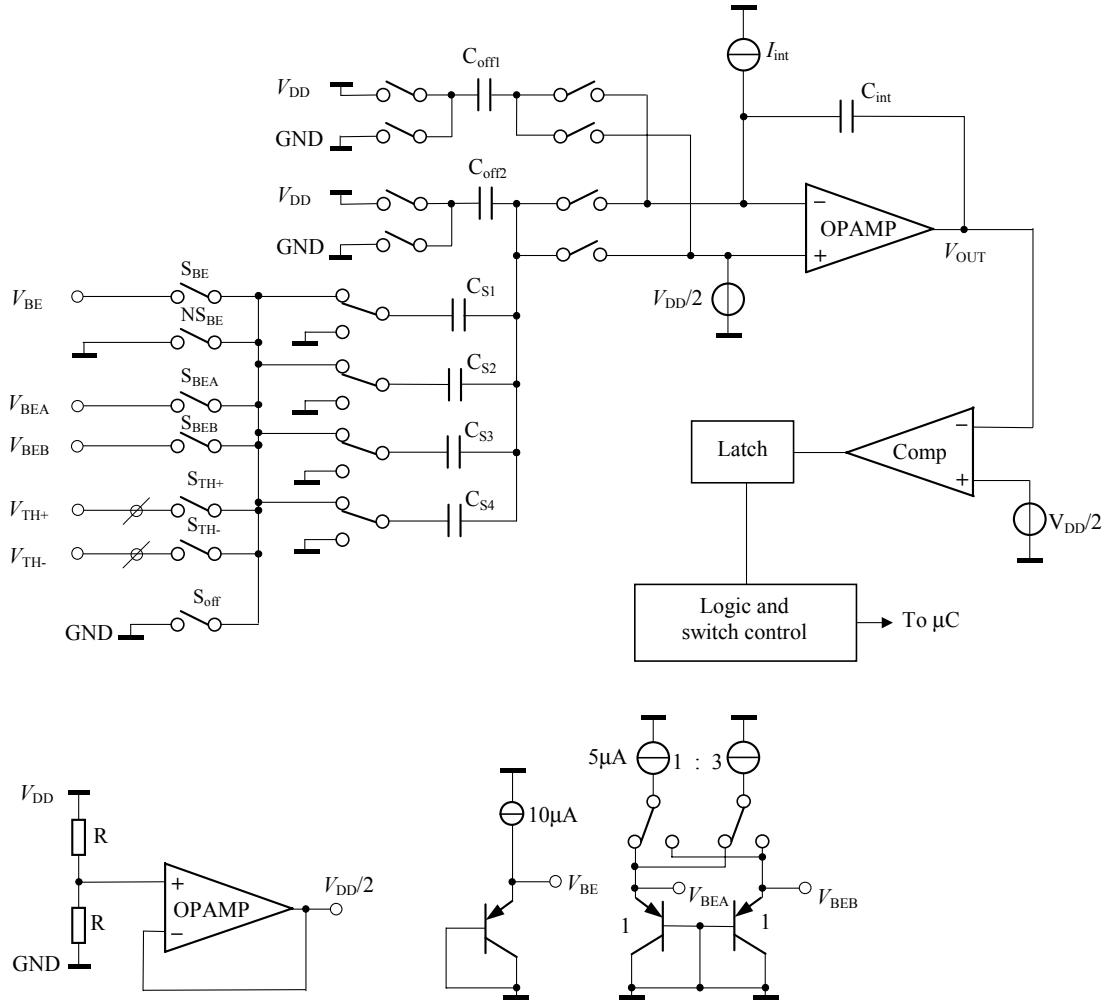

| 6.2 Circuit design                                                      | 101        |

| 6.2.1 The generation of the basic signals                               | 101        |

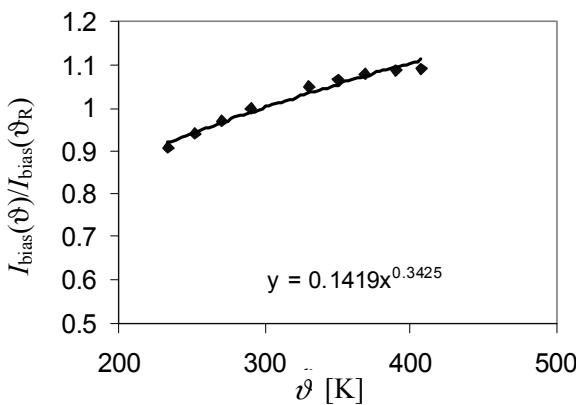

| 6.2.2 Bias current for the bipolar transistors                          | 103        |

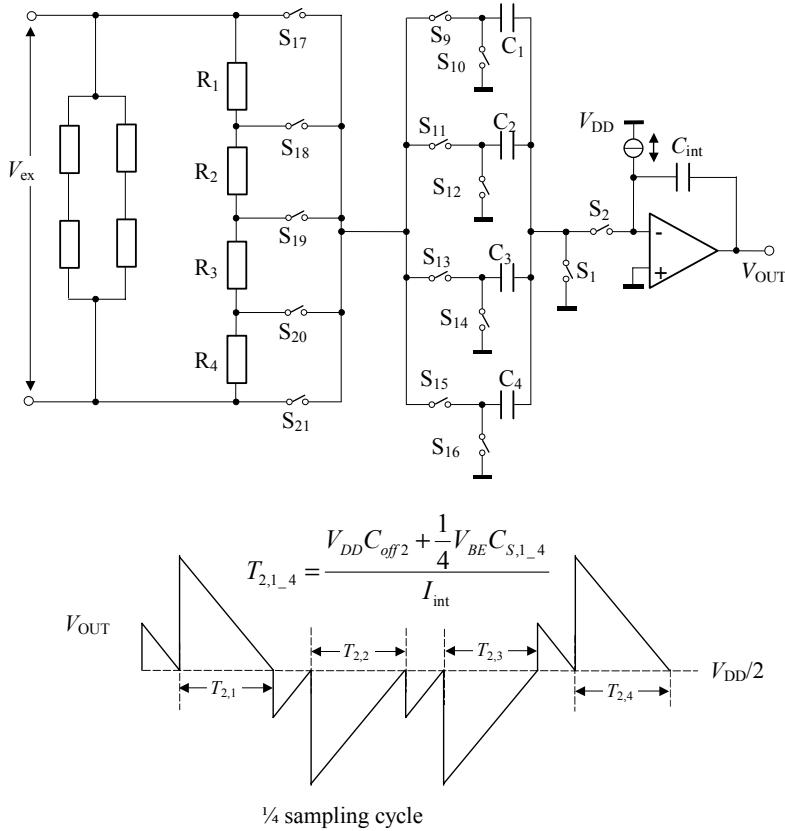

| 6.2.3 Voltage-to-period converter                                       | 104        |

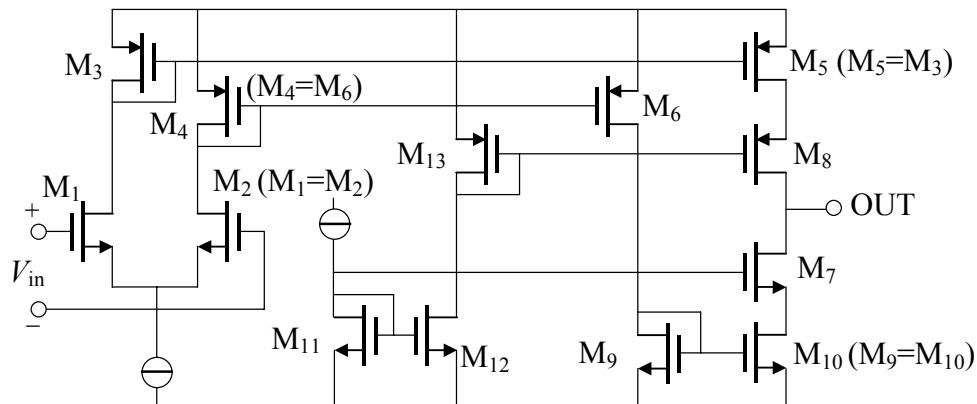

| 6.2.4 Design of the integrator op-amp                                   | 107        |

| 6.2.5 Integration current source                                        | 108        |

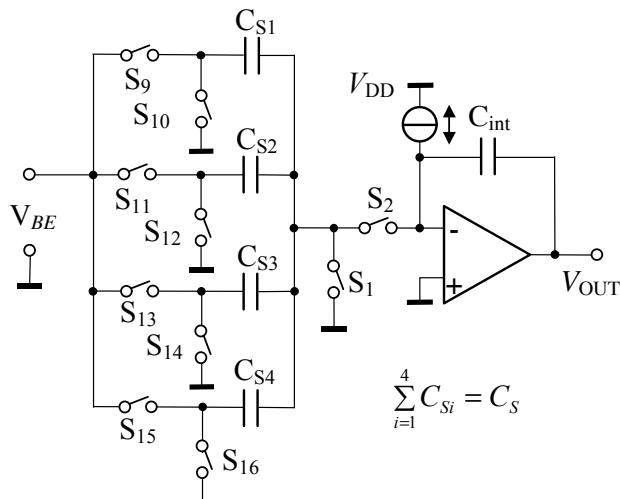

| 6.2.6 Division of base-emitter voltage                                  | 110        |

| 6.2.7 The complete circuit                                              | 112        |

|                                                                                              |     |

|----------------------------------------------------------------------------------------------|-----|

| 6.3 Non-linearity                                                                            | 112 |

| 6.4 Noise analysis                                                                           | 113 |

| 6.4.1 Noise of the voltage-to-period converter                                               | 113 |

| 6.4.2 Noise of the bipolar transistors                                                       | 115 |

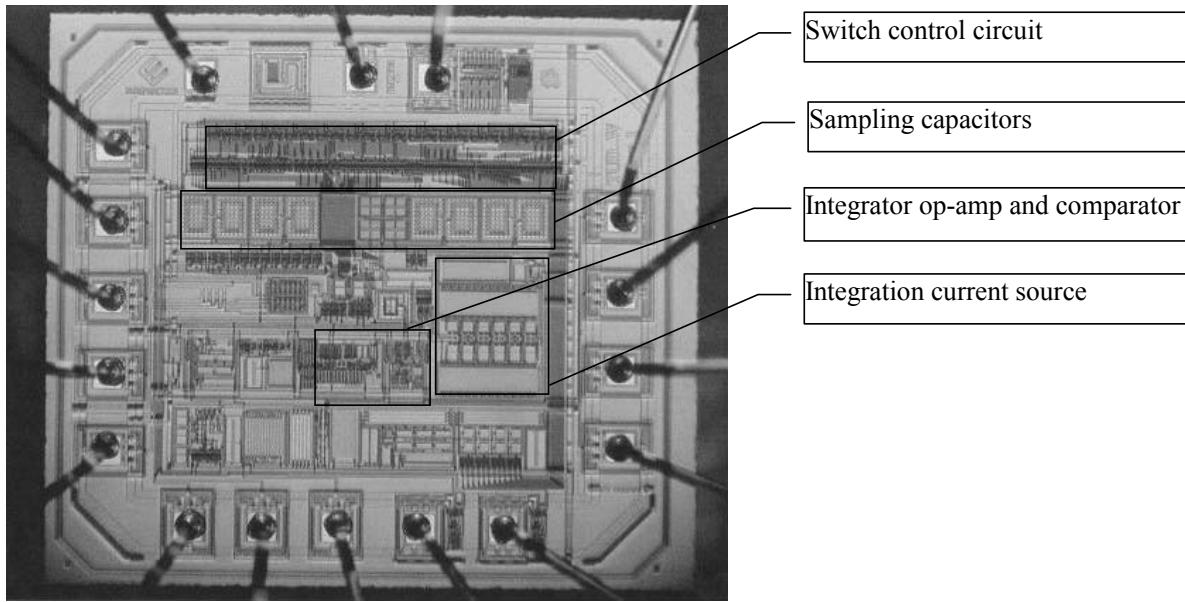

| 6.5 Measurement results                                                                      | 116 |

| 6.5.1 The whole chip design                                                                  | 116 |

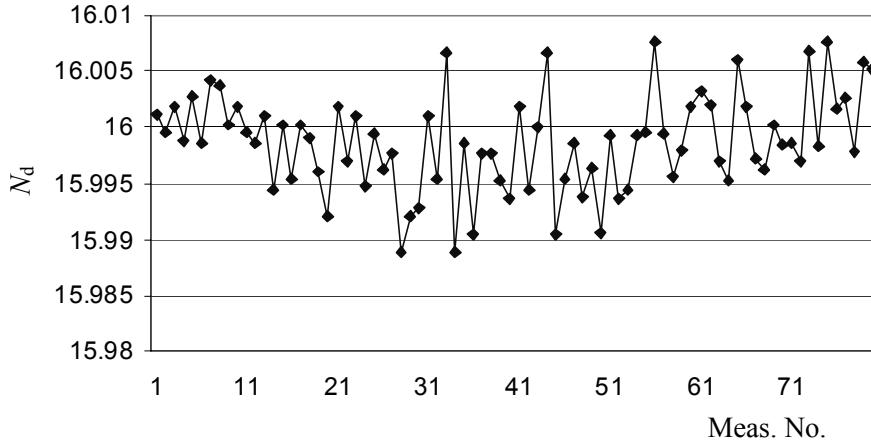

| 6.5.2 Accuracy of the voltage divider                                                        | 117 |

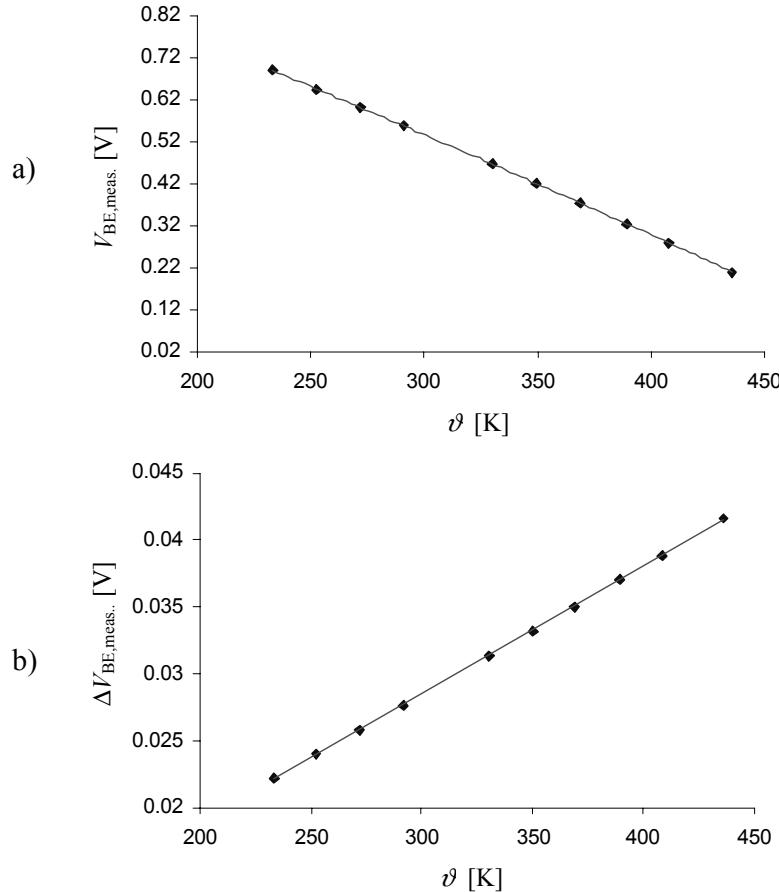

| 6.5.3 Base-emitter voltage and $\Delta V_{BE}$                                               | 118 |

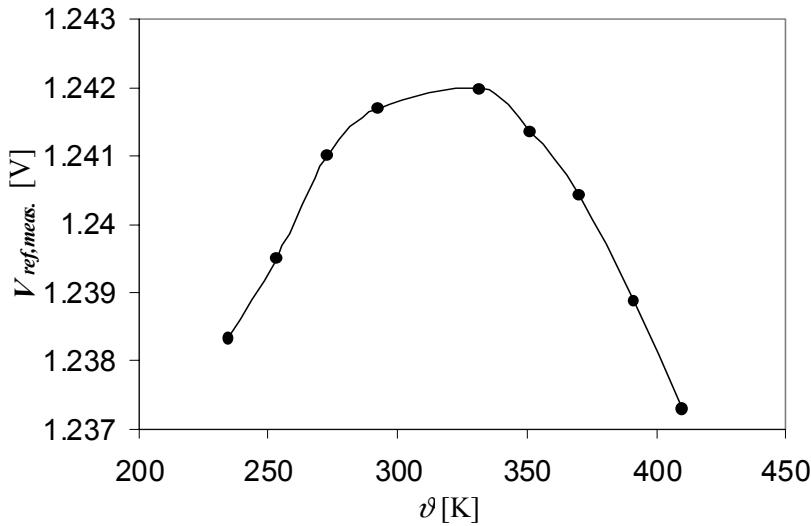

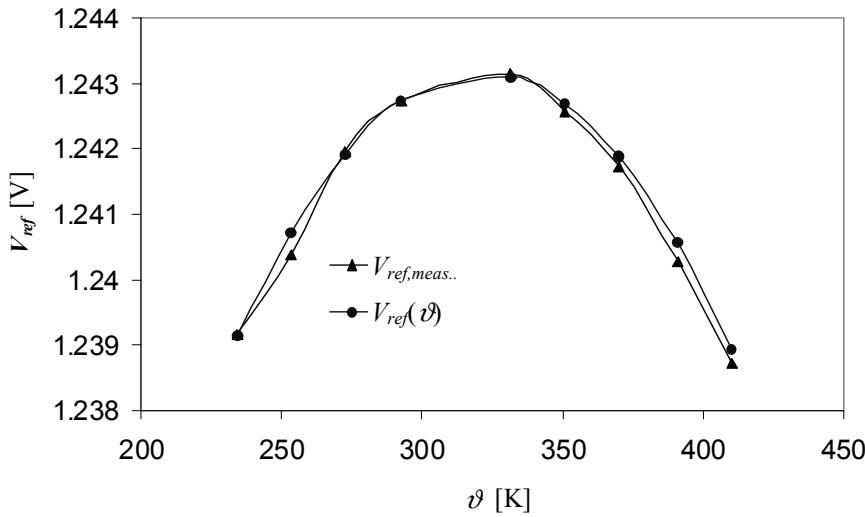

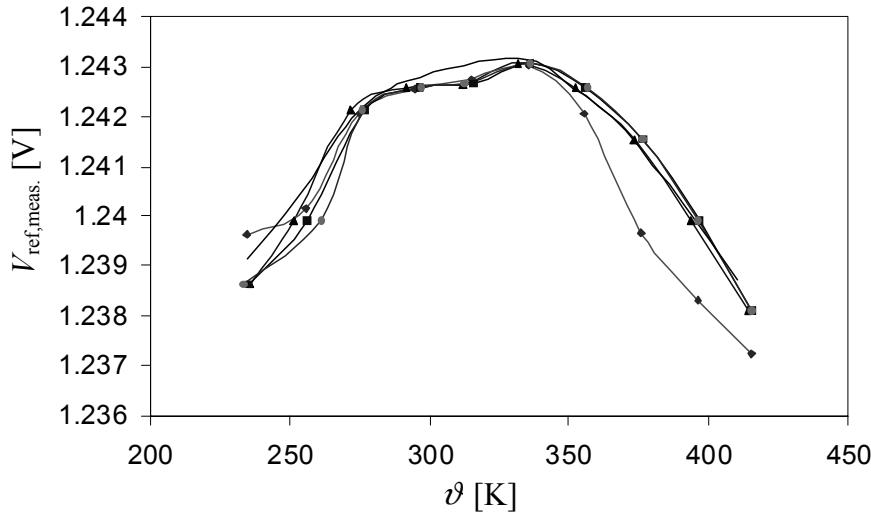

| 6.5.4 On-chip bandgap-reference voltage                                                      | 120 |

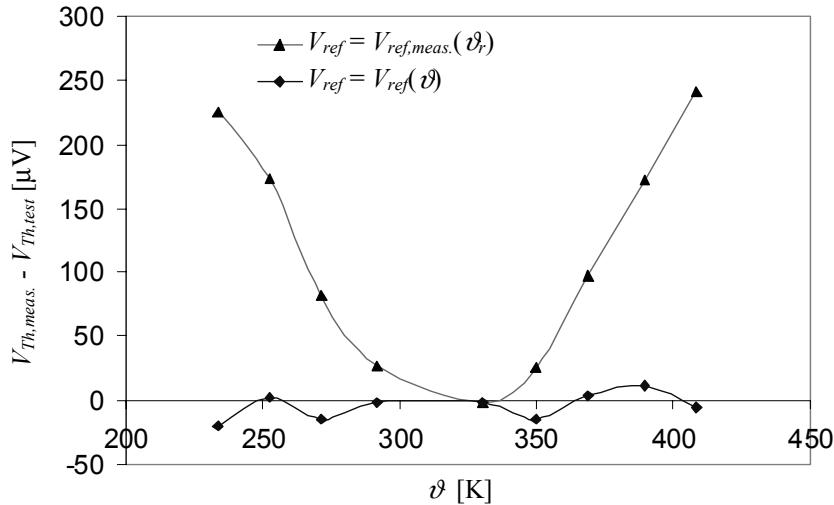

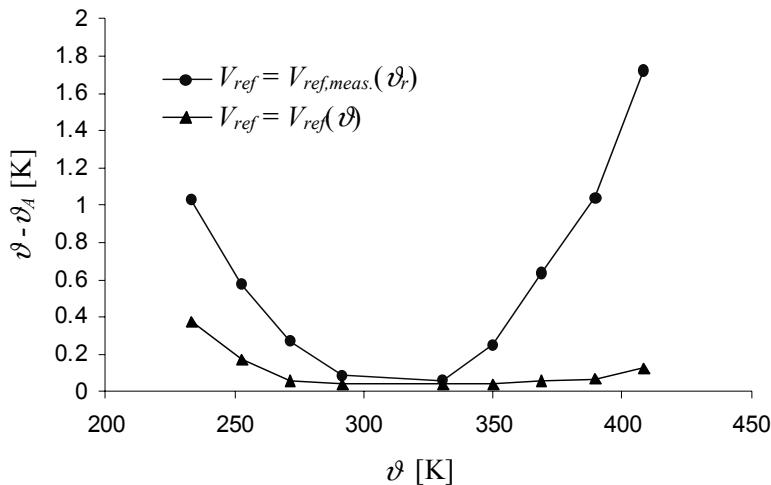

| 6.5.5 High-order correction for the bandgap-reference voltage                                | 122 |

| 6.5.6 The complete system                                                                    | 123 |

| 6.5.7 On-chip temperature sensor                                                             | 124 |

| 6.5.8 The noise performance                                                                  | 125 |

| 6.5.9 The residual offset                                                                    | 126 |

| 6.5.10 Summary of the performances of the interface                                          | 127 |

| 6.6 Conclusions                                                                              | 127 |

| References                                                                                   | 129 |

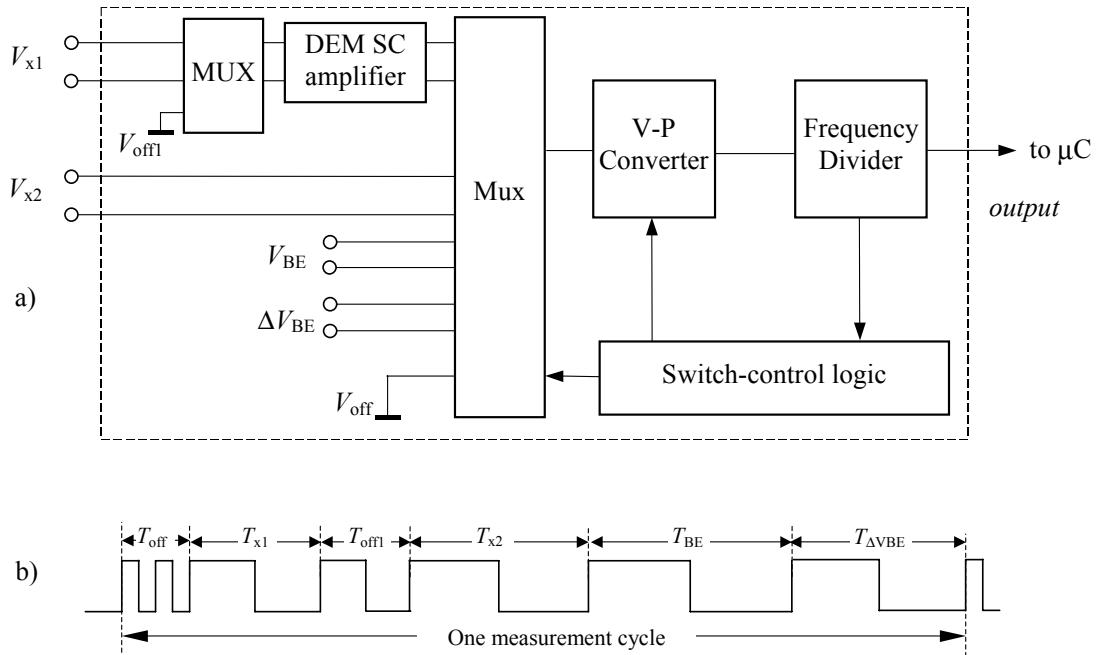

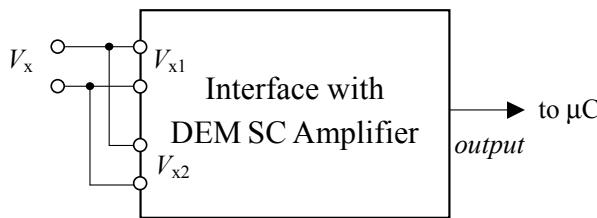

| <b>7 Switched-capacitor instrumentation amplifier with dynamic-element-matching feedback</b> | 131 |

| 7.1 Introduction                                                                             | 131 |

| 7.2 Circuit design                                                                           | 131 |

| 7.2.1 The DEM SC instrumentation amplifier                                                   | 131 |

| 7.2.2 The complete circuit                                                                   | 132 |

| 7.3 Non-idealities of the DEM SC amplifier                                                   | 133 |

| 7.3.1 Finite open-loop gain                                                                  | 133 |

| 7.3.2 Leakage current at the inverting input of the op-amp                                   | 134 |

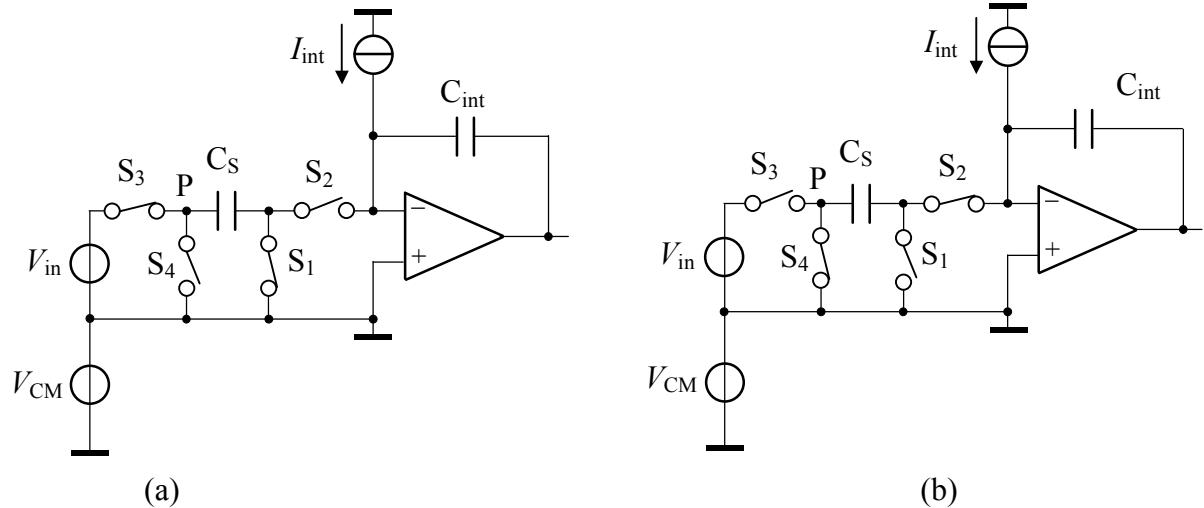

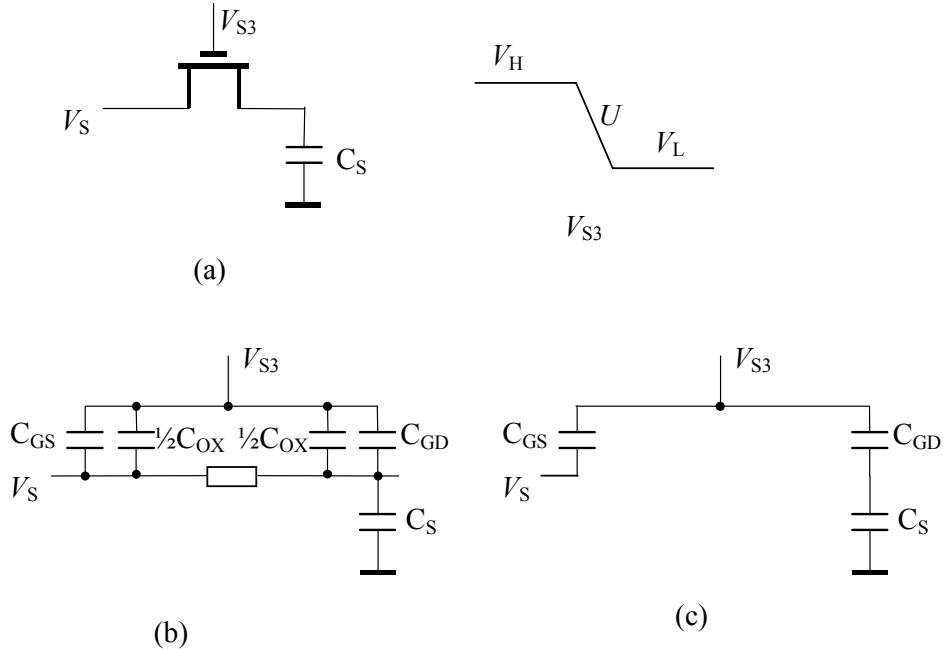

| 7.3.3 Switch-charge injection                                                                | 135 |

| 7.3.4 Noise of the DEM SC amplifier                                                          | 136 |

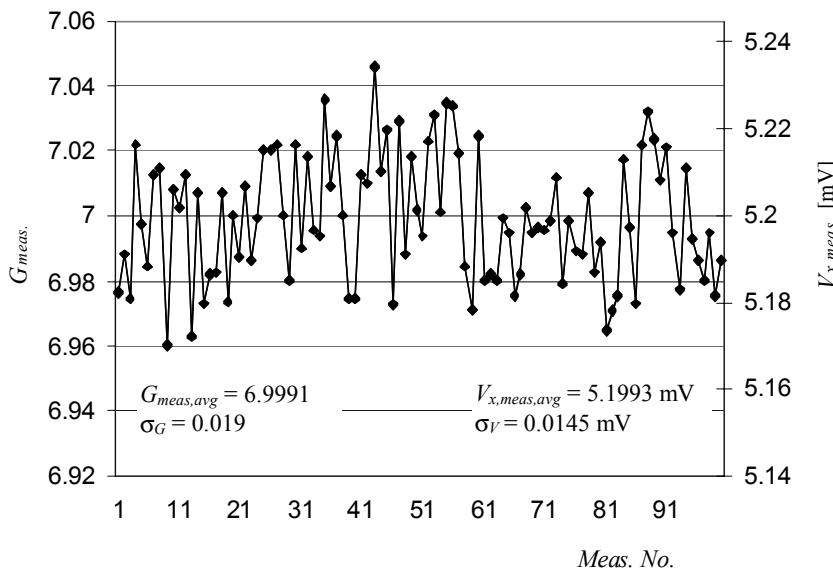

| 7.4 Experimental results                                                                     | 138 |

| 7.5 Conclusions                                                                              | 140 |

| References                                                                                   | 141 |

| <b>8 Conclusions</b>                                                                         | 143 |

| <b>9 Summary</b>                                                                             | 147 |

| <b>Samenvatting</b>                                                                          | 153 |

| <b>Acknowledgement</b>                                                                       | 159 |

| <b>List of publications</b>                                                                  | 161 |

| <b>Biography</b>                                                                             | 163 |

# Chapter 1    Introduction

## 1.1    Silicon Temperature Sensors and Bandgap References

Silicon temperature sensors and bandgap references have been developed for a long time, together with the development of semiconductor industry. The semiconductor temperature sensors take a large part of the temperature-sensors market. There are several types of semiconductor temperature sensors: thermistors, which use the resistive properties of a semiconductor composite (consisting of different types of metal) to measure temperature; semiconductor thermocouples, which use a very large Seebeck effect to measure temperature differences; and temperature sensors based on diodes or transistors, which use the temperature characteristics of junctions. Thermistors need specific fabrication processes. As single sensing elements, thermistors and silicon thermocouples are widely used in the industry for measuring temperature and temperature difference, but they need extra interface circuitry for signal processing and data display. For users, it is much easier to have temperature sensors employing the temperature characteristics of junctions integrated with the interface circuit on the same chip. Because the junctions are part of the basic components of the integrated circuit, no effort is needed for process compatibility. In such smart temperature sensors, the temperature behaviour of the junction characteristics is applied to generate the basic sensor signal.

Presently, the most frequently used semiconductor materials are silicon (Si), germanium (Ge) and gallium arsenide (GaAs). Compared to Ge and GaAs, silicon has many advantages. Firstly, silicon is one of the most abundant elements on earth. Secondly, as a good isolator,  $\text{SiO}_2$  is used as carrier for the interconnecting metallization and ensures excellent passivation of the surface. Thirdly, the band gap of silicon is 1.12 eV, higher than that of germanium (~0.72 eV), so the maximum operation temperature of silicon is 200 °C, while that of germanium is only about 85 °C. For these reasons, most semiconductors are produced in silicon.

For the design of bandgap references, the temperature behaviour of junctions is also applied, but in a different way. For temperature sensors, the temperature dependence of the output signal must be maximized, in order to get larger temperature sensitivities. For bandgap references, on the other hand, the temperature dependence of the output signal must be minimized, in order to get a temperature-independent output whose value is related to the bandgap energy of the semiconductor material. The temperature behaviour of the junctions determines the performance of the temperature sensors and bandgap references.

## 1.2 Why CMOS Technology?

Bipolar technology was originally developed for commercial IC products. Many types of integrated temperature sensors and bandgap references have been on the market, for instance, the temperature-sensor series LM135 [1.3], the AD590 series [1.4], etc, and the bandgap-reference series ADR390 [1.5], the LM113 [1.6] series and REF1004 series [1.7] etc.

The development of IC technology has been driven by the ever smaller size and higher performance required of IC products. The technologies used are the bipolar technology, MOS technology, CMOS technology, and BiCMOS technology.

Nowadays, the CMOS technology is becoming more and more important in the IC market. Compared to those fabricated using a bipolar technology, the ICs fabricated in CMOS have some advantages. Firstly, CMOS is a cheap technology, because of the higher integration grades. With the same amount of components, the chip size of IC fabricated in CMOS technology is much smaller than that fabricated in a bipolar technology. Secondly, some options in circuit design, such as using analog switches, and switched capacitors, are only offered by CMOS [1.8], which allows for a more flexible circuit design. This makes it easier to design CMOS temperature sensors that do not only have a continuous analog output, but also a modulated output in the time domain. Thirdly, in CMOS technology, temperature sensors and bandgap references can be integrated with digital ICs, such as a microcontroller and a CPU; no external components are required for temperature detection and/or a reference signal.

For these reasons, temperature sensors and bandgap references fabricated in CMOS technology are preferred.

## 1.3 Problem Statement

Both bipolar transistors and MOS transistors can be used for temperature sensors and bandgap references. The temperature characteristics of the transistors are applied in the circuit design. Since it is easier to model and control the temperature characteristics of bipolar transistors, these transistors have been used as the basic components of integrated temperature sensors and bandgap references.

Much research work has been done on characterizing the temperature dependence of the properties of bipolar transistor [1.1, 1.2]. These dependencies can be used to design temperature sensors and bandgap references. They can also be used in other IC designs to reduce temperature effects. As we have seen in section 1.2, many types of integrated temperature sensors and bandgap references have been on the market for a relatively long time, for instance, the temperature-sensor series LM135 [1.3], the AD590 series [1.4], SMT160 [1.9], etc, and the bandgap-reference series ADR390 [1.5], the LM113 [1.6] series and REF1004 series [1.7] etc.

There are some problems specific to realizing temperature sensors and bandgap references in CMOS technology, which can be classified in two groups: device and circuit level problems.

The performance of temperature sensors and bandgap references strongly depends on the kind of bipolar transistors implemented in CMOS technology. To design temperature sensors or bandgap references, we have to know the temperature characteristics of these bipolar

transistors. Although many interesting designs of CMOS temperature sensors and bandgap-reference circuits have been presented in the literature [1.10, 1.11], very little is known about the basic limitation of the accuracy of these circuits and their long-term stability.

Also problems in circuit design have to be solved in CMOS technology. The poor matching of MOSFETs causes op-amps and comparators to have large offsets. This results in systematic errors in temperature sensors and bandgap references. Moreover, because MOSFETs are surface-channel devices, they have much higher  $1/f$  noise (flicker noise) than transistors fabricated in bipolar technology. This causes larger random errors.

Through the application of advanced techniques in circuit design, these non-idealities can be minimized. For instance, by applying chopping techniques, one can significantly reduce the offset and  $1/f$  noise of the op-amps [1.12]. By applying Dynamic Element Matching (DEM) techniques, one can eliminate the errors caused by the mismatch between components to the second order [1.3, 1.4]. Thus we can obtain accurate voltage amplification and division without trimming with good long-term stability. An auto-calibration technique can be applied to reduce the inaccuracy of the systematic parameters of the circuits significantly, so that high accuracy and good long-term stability can be guaranteed.

## 1.4 The Objectives of the Project

The accuracy of CMOS temperature sensors and bandgap references is limited by two things: by the accuracy of the bipolar components, which generate the basic signals, and by the accuracy of the processing circuit. Thus, the objectives are to characterize the behaviour of the bipolar device and to design a high-performance CMOS circuit.

In temperature sensors and bandgap references, the basic signals are the base-emitter voltage  $V_{BE}$  and the difference between two base-emitter voltages under different bias-current densities  $\Delta V_{BE}$ . The performance of a well-designed temperature sensor or bandgap-reference circuit depends on the accuracy of these two basic signals.

Here, the device characterization is used to investigate the temperature dependencies of the base-emitter voltage  $V_{BE}$  and the voltage difference  $\Delta V_{BE}$ . Effects affecting the ideal values of these voltages  $V_{BE}$  and  $\Delta V_{BE}$  are studied.

Care must be taken in circuit design to maintain the accuracy of the basic signals  $V_{BE}$  and  $\Delta V_{BE}$  based on the characterization results. For instance, the accuracy of  $\Delta V_{BE}$  depends on the matching of two bipolar transistors, as well as the accuracy of the bias-current ratio. The circuit should be carefully designed to eliminate errors due to mismatching of the bipolar transistors and device mismatch in the current-ratio-generating circuit.

The process tolerance results in a certain spread in the value of the saturation current, thus results in the spread in the value of base-emitter voltage under a determined temperature. Thus an appropriate trimming technique is necessary to reduce this error. Single-point trims are discussed later.

## 1.5 The Outline of the Thesis

Chapter 2 gives a brief theoretical description of bipolar transistors. In this chapter, the properties of the base-emitter voltage versus temperature and bias current are described. Also,

two types of bipolar transistors available in CMOS technology are presented. It is shown that the vertical substrate transistors are preferable for temperature sensors and bandgap references.

Chapter 3 characterizes vertical substrate transistors fabricated in CMOS technology. A measurement set-up has been built to measure the base-emitter voltage and the  $\Delta V_{BE}$  voltage difference over the temperature range from  $-40^{\circ}\text{C}$  to  $160^{\circ}\text{C}$ , with biasing currents from 5 nA to 1 mA. The characterization results show that the base-emitter voltage of a vertical substrate transistor fits the well-known Gummel-Poon model quite well. This means that the base-emitter voltage of the substrate transistors can be well predicted by applying the extracted model parameters  $V_{g0}$  and  $\eta$ . The measurements show that the  $\Delta V_{BE}$  voltage can be generated with an inaccuracy of less than 0.1%, by optimisation of the bias current and the emitter size of the transistors.

Chapter 4 describes some advanced technologies in circuit design. The main focus is on the circuit design technologies, such as DEM techniques, the chopping technique and auto-calibration techniques. The architecture considerations in circuit design are also discussed in this chapter.

Chapter 5 discusses some architecture considerations. It is possible to obtain the temperature-sensing signal and bandgap-reference signal sequentially from a single bipolar transistor under different bias currents or from multiple transistors. Features of the different architectures such as circuit complexity, noise performance, power consumption, etc. have been investigated.

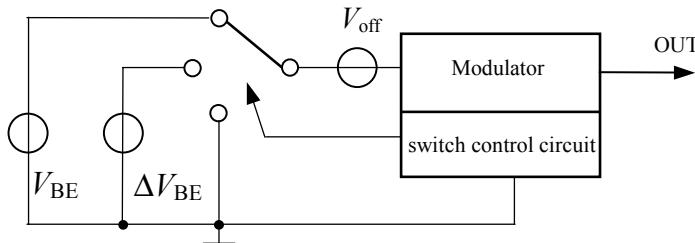

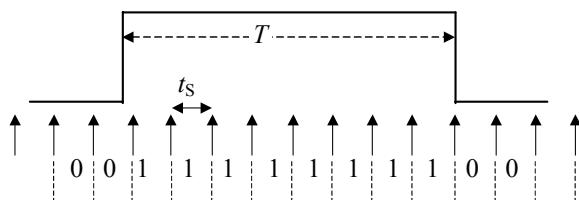

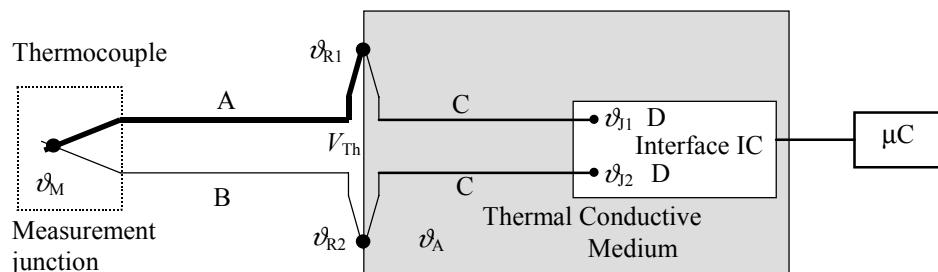

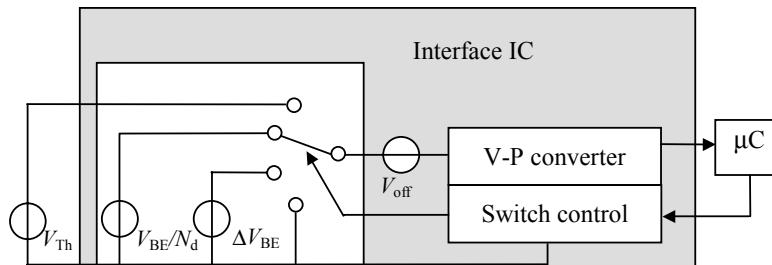

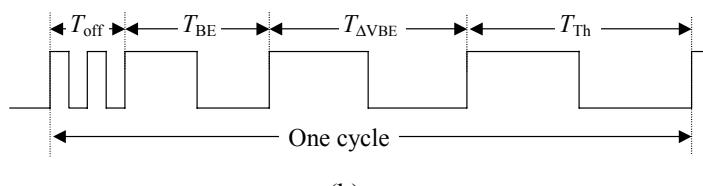

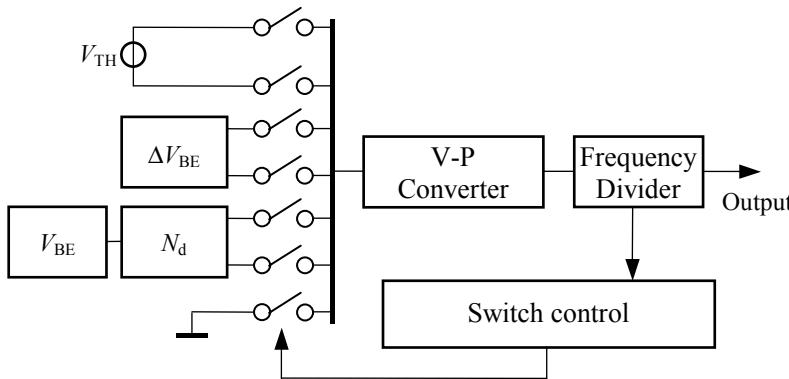

Chapter 6 presents the application of the device characteristics in an advanced circuit design. A CMOS integrated interface circuit for thermocouples has been designed. In this circuit, the basic voltage signal  $V_{BE}$ ,  $\Delta V_{BE}$ , the offset voltage  $V_{off}$  and the unknown thermocouple voltage  $V_x$  are converted into the time domain, using a voltage-to-time converter. The combinations of  $V_{BE}$  and  $\Delta V_{BE}$  form a bandgap-reference voltage and a temperature-sensing voltage. The bandgap-reference voltage and the offset voltage are used for auto-calibration. Auto-calibration is applied to eliminate the additive and multiplicative errors of the voltage-to-time converter. The temperature-sensing voltage represents the chip temperature, enabling cold-junction compensation for thermocouples. The measurement results are also presented here.

Chapter 7 presents a switched-capacitor (SC) instrumentation amplifier with Dynamic-Element-Matching (DEM) feedback. This instrumentation amplifier can be applied in combination with the thermocouple interface to pre-amplify accurately the extreme small thermocouple voltage before this signal is converted to the time domain.

Chapter 8 gives the main conclusions of the thesis.

Chapter 9 gives the summary of the thesis

**References:**

- [1.1] G.C.M. Meijer, “An IC Temperature Transducer with an Intrinsic Reference”, IEEE Journal of Solid-state Circuits, Vol. SC-15, No. 3, pp. 370-373, June 1980.

- [1.2] S.L. Lin and C.A.T. Salama, “A  $V_{BE}(T)$  Model with Application to Bandgap-Reference Design”, IEEE Journal of Solid-state Circuits, Vol. SC-20, No. 6, pp. 83-85, Dec. 1985.

- [1.3] National Semiconductor, “LM135 - Precision Temperature-Sensor”, <http://www.national.com> 2004.

- [1.4] Analog Devices, “AD590 is a two-terminal integrated circuit temperature transducer”, <http://www.Analogdevice.com>, 2004.

- [1.5] Analog Devices, “ADR589 a two-terminal IC 1.2 V reference”, <http://www.analogdevice.com>, 2004.

- [1.6] National Semiconductor, “LM113 Precision Reference”, <http://www.national.com>, 2004.

- [1.7] Burr-Brown, “REF1004 1.2 V and 2.5 V Micro Power Voltage Reference”, <http://www.burr-brown.com>, 2004.

- [1.8] M. Tuthill, “A Switched-Current, Switched-Capacitor Temperature-Sensor in 0.6- $\mu$ m CMOS”, IEEE Journal of Solid-state Circuits, Vol. 33, No. 7, pp. 1117-1122, July 1998.

- [1.9] Smartec B.V., “Specification Sheet SMT160-30”, <http://www.smartec.nl>, 1996.

- [1.10] Y.P. Tsividis and R.W. Ulmer, “A CMOS Voltage Reference”, IEEE Journal of Solid-state Circuits, Vol. SC-13, No. 6, pp. 774-778, Dec. 1978.

- [1.11] G. Tzanateas, C.A. Salama and Y.P. Tsividis, “A CMOS Bandgap-Reference”, IEEE Journal of Solid-state Circuits, Vol. SC-14, No. 3, pp. 655-657, June 1979.

- [1.12] A. Bakker, “High-Accuracy CMOS Temperature-Sensors”, Ph.D. thesis, 1999. Delft University of Technology, The Netherlands.

# Chapter 2 Bipolar Components in CMOS Technology

## 2.1 Introduction

This chapter mainly focuses on the basic characteristics of bipolar transistors and the bipolar transistors available in CMOS technology.

The basic characteristic of bipolar transistors is the base-emitter voltage versus the bias current and the temperature  $V_{BE}(I_C, \vartheta)$ . The properties of  $V_{BE}(I_C, \vartheta)$  are applied to generate the temperature-sensor signal and the bandgap-reference signal.

The chapter describes two types of bipolar transistors available in CMOS technology: lateral and vertical substrate transistors. A comparison of these two types of structures shows that vertical substrate transistors are more suitable for designing high-performance temperature sensors and bandgap references.

## 2.2 Basic Theory of Bipolar Transistors

### 2.2.1 Ideal Case

Under forward biasing, the collector current depends exponentially on the base-emitter voltage:

$$I_C = I_S \left( \exp \frac{qV_{BE}}{k\vartheta} - 1 \right), \quad (2.1)$$

where  $I_C$  = the collector current of the bipolar transistor,

$I_S$  = the saturation current of the bipolar transistor,

$V_{BE}$  = the forward-biased base-emitter voltage,

$k$  = the Boltzmann's constant,

$q$  = the electron charge, and

$\vartheta$  = the absolute temperature.

If the base-emitter voltage  $V_{BE} > 3k\vartheta/q$ , equation (2.1) can be simplified, yielding:

$$I_C \approx I_S \exp \frac{qV_{BE}}{k\vartheta}. \quad (2.2)$$

The saturation current  $I_S$  amounts to:

$$I_S = \frac{q^2 n_i^2 A_E D_B}{Q_B}, \quad (2.3)$$

where  $A_E$  = the emitter-junction area,

$n_i$  = the intrinsic carrier concentration in the base,

$D_B$  = the effective minority-carrier diffusion constant in the base, and

$Q_B$  = the charge represented by the net number of doping atoms in the neutral base per unit area.

The charge  $Q_B$  is obtained by using the integration equation:

$$Q_B = q \int_{x_E}^{x_C} N_B^+ dx, \quad (2.4)$$

where  $N_B^+$  represents the majority density,  $x_E$  and  $x_C$  represent the boundaries of the neutral base region on the emitter side and the collector side, respectively.

At moderate temperatures, the dopant is fully ionised, and the intrinsic carrier concentration is much less than the doping concentration. In this case, it holds that:

$$Q_B \approx q \int_{x_E}^{x_C} N_B dx, \quad (2.5)$$

where  $N_B$  represents the base-doping density.

The temperature dependency of  $I_S$  is based on the temperature dependency of the parameters  $n_i$  and  $D_B$  [2.1], according to:

$$n_i^2 \propto \vartheta^3 \exp^{-\frac{qV_g}{k\vartheta}} \quad (2.6)$$

$$D_B = \frac{k\vartheta}{q} \bar{\mu}_B, \quad (2.7)$$

where  $\bar{\mu}_B$  = the effective value of the mobility of the minority carriers in the base,

$V_g$  = the bandgap voltage of the base material.

The net base charge  $Q_B$  also changes with temperature, because the boundaries  $x_E$  and  $x_C$  depend on temperature, and  $N_B^+$  also changes with temperature at very low and high temperatures. At very low temperatures, the dopant is not fully ionised due to the freeze-out effect. And at very high temperatures, the intrinsic carriers become dominant. However, in the moderate temperature range, we can neglect the temperature dependence of  $Q_B$ .

The mobility  $\bar{\mu}_B$  and the bandgap voltage  $V_g$  are related to the temperature in a non-linear way. By approximation, they can be expressed as:

$$\bar{\mu}_B \propto \vartheta^{-n}, \quad (2.8)$$

$$V_g = V_{g0} - \alpha \vartheta, \quad (2.9)$$

where  $n$  and  $\alpha$  are constants.  $n$  depends on the doping concentration and profile in the base, and thus  $n$  is a process-dependent constant.  $V_{g0}$  is the extrapolated value of the bandgap voltage  $V_g(\vartheta)$  at 0 K.

Taking together all the temperature dependencies of equation (2.2) yields the equation:

$$I_C = C\vartheta^\eta \exp\left[\frac{q(V_{BE} - V_{g0})}{k\vartheta}\right], \quad (2.10)$$

where  $C$  is a constant, and  $\eta = 4 - n$ .

According to measurement results of Meijer [2.2], the values of the parameters  $V_{g0}$  and  $\eta$  differ from those one would expect on the basis of physical considerations. This is due to the poor approximation in equation (2.9) for  $V_g(\vartheta)$  [2.3]. With empirical values for  $V_{g0}$  and  $\eta$ , equation (2.10) can perform rather accurately.

To find out the equation for  $V_{BE}(\vartheta)$ , we consider two temperatures: an arbitrary temperature  $\vartheta$  and a reference temperature  $\vartheta_r$ . Applying equation (2.10) for both temperatures, we can derive the temperature dependence of base-emitter voltage  $V_{BE}(\vartheta)$  from the expression of  $I_C(\vartheta)/I_C(\vartheta_r)$

$$V_{BE}(\vartheta) = V_{g0} \left(1 - \frac{\vartheta}{\vartheta_r}\right) + \frac{\vartheta}{\vartheta_r} V_{BE}(\vartheta_r) - \eta \frac{k\vartheta}{q} \ln\left(\frac{\vartheta}{\vartheta_r}\right) + \frac{k\vartheta}{q} \ln\left(\frac{I_C(\vartheta)}{I_C(\vartheta_r)}\right). \quad (2.11)$$

When, for practical reasons, the collector current is made proportional to some power of the temperature  $\vartheta$ :

$$I_C \propto \vartheta^m, \quad (2.12)$$

equations (2.11) and (2.12) give:

$$V_{BE}(\vartheta) = V_{g0} \left(1 - \frac{\vartheta}{\vartheta_r}\right) + \frac{\vartheta}{\vartheta_r} V_{BE}(\vartheta_r) - (\eta - m) \frac{k\vartheta}{q} \ln\left(\frac{\vartheta}{\vartheta_r}\right). \quad (2.13)$$

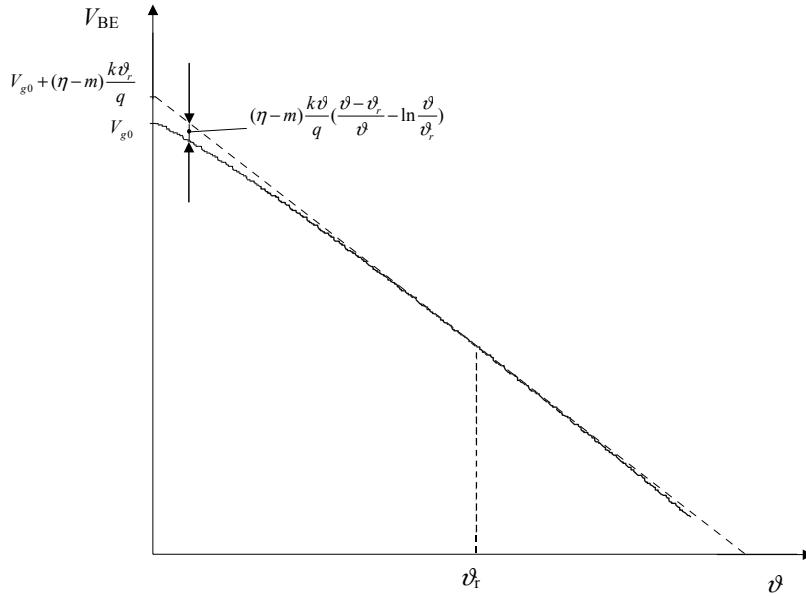

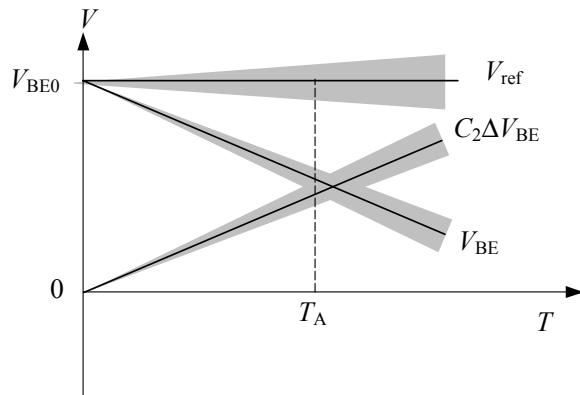

For convenience, in circuit designs, it is better to express  $V_{BE}(\vartheta)$  as the sum of a constant term, a term proportional to  $\vartheta$ , and a higher-order term. In such way, the linear terms represent the tangent to the  $V_{BE}(\vartheta)$  curve at the reference temperature  $\vartheta_r$ , as shown in Figure 2.1.

The new expression is:

$$V_{BE}(\vartheta) = \underbrace{V_{g0} + (\eta - m) \frac{k\vartheta_r}{q}}_{\text{constant}} - \underbrace{\lambda \vartheta + (\eta - m) \frac{k}{q} \left(\vartheta - \vartheta_r - \vartheta \ln \frac{\vartheta}{\vartheta_r}\right)}_{\text{linear}}. \quad (2.14)$$

where

$$\lambda = \frac{\left\{V_{g0} + (\eta - m) \frac{k\vartheta_r}{q}\right\} - V_{BE}(\vartheta_r)}{\vartheta_r}. \quad (2.15)$$

The first term in (2.14) is defined as  $V_{BE0}$ , which is an important parameter in bandgap references.

Figure 2.1 The base-emitter voltage versus temperature.

Under the condition of a small temperature change,  $(\vartheta - \vartheta_r) \ll \vartheta$ , taking the first three terms of the Taylor expansion of the last term in (2.14) results in

$$V_{BE}(\vartheta) = \left\{ V_{g0} + (\eta - m) \frac{k\vartheta_r}{q} \right\} - \lambda\vartheta - \frac{1}{2}(\eta - m) \frac{k\vartheta_r}{q} \left( \frac{\vartheta - \vartheta_r}{\vartheta_r} \right)^2, \quad (2.16)$$

which is widely used to design circuits for temperature sensors and bandgap references.

### 2.2.2 Low-Level Injection

Equation (2.1) is the approximation of a complex expression for the collector current, where the other terms are neglected. When the collector current is small (under a low bias base-emitter voltage or at high temperatures), other effects cannot be neglected. If they are all considered, the collector current amounts to

$$I_C = I_S \left( e^{\frac{qV_{BE}}{k\vartheta}} - 1 \right) + I_S \left( e^{\frac{qV_{BC}}{k\vartheta}} - 1 \right) + \frac{I_S}{B_R} \left( e^{\frac{qV_{BC}}{k\vartheta}} - 1 \right) + I_{gen} - I_{rec}, \quad (2.17)$$

where  $V_{BC}$  = the voltage across the base-collector junction, which is always reverse biased,

$B_R$  = the reverse current gain,

$I_{gen}$  = the generation current in the base-collector junction, and

$I_{rec}$  = the recombination current in the base-collector junction.

In CMOS technology, the voltage across the base-collector junction  $V_{BC}$  is set to be zero. As a result the generation current  $I_{gen}$  is balanced by the recombination current  $I_{rec}$ , and only the first term in equation (2.17) remains. So one can counteract the effect of low-level injection by keeping  $V_{BC}$  equal to zero.

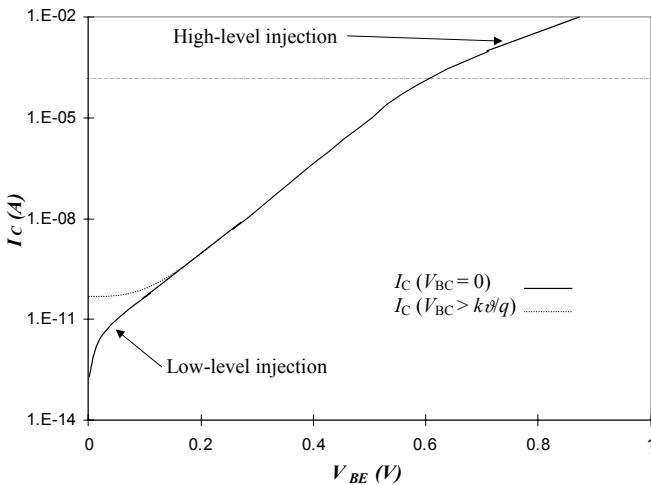

### 2.2.3 High-Level Injection

If the injected minority carrier concentration is in the order of the base-doping concentration, the collector current deviates from (2.1). If the injected carrier concentration is above the base-doping concentration, (2.1) becomes:

$$I_C = I'_S \left( e^{\frac{qV_{BE}}{2k\vartheta}} - 1 \right), \quad (2.18)$$

where  $I'_S = \frac{q^2 n_i N_B A_E D_B}{Q_B}$ .

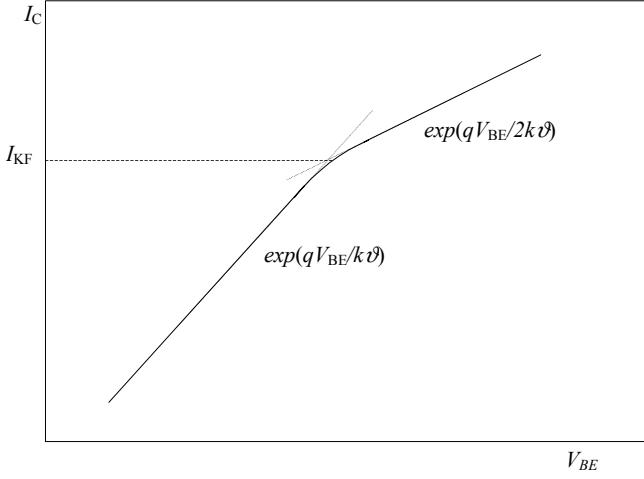

Figure 2.2 shows the  $I_C$  -  $V_{BE}$  curve for two base-collector voltages.

Figure 2.2 The  $I_C$  versus  $V_{BE}$  for two values of  $V_{BC}$ .

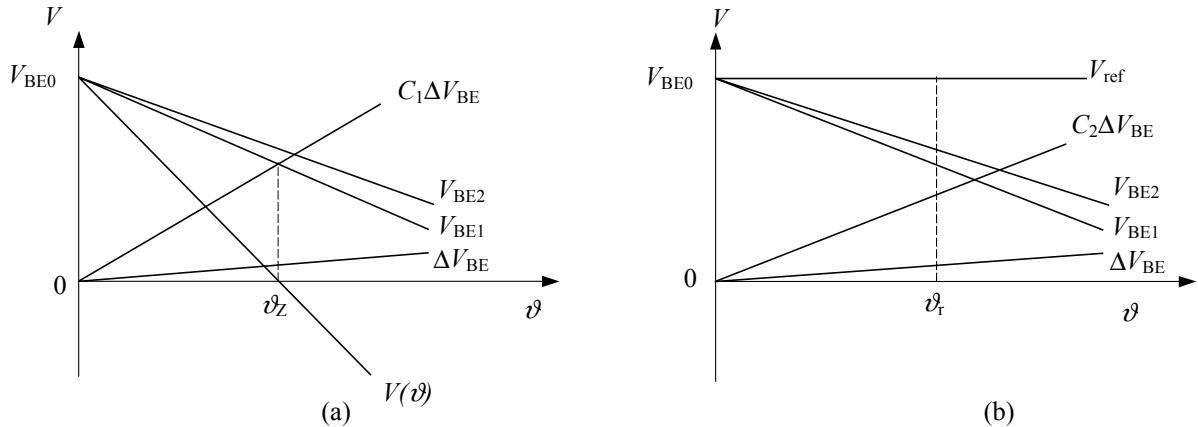

### 2.2.4 The Temperature-Sensor Signal and the Bandgap-Reference Signal

The temperature-sensor signal and the bandgap-reference signal are realized by the linear combinations of the base-emitter  $V_{BE}$  voltage and a voltage  $\Delta V_{BE}$ , which is proportional to the absolute temperature

$$V(\vartheta) = \pm(V_{BE}(\vartheta) - C_1 \Delta V_{BE}), \quad (2.19)$$

$$V_{ref} = V_{BE}(\vartheta) + C_2 \Delta V_{BE}, \quad (2.20)$$

where  $\Delta V_{BE}$  is generated from two base-emitter voltages under different bias current densities. According to (2.2),  $\Delta V_{BE}$  can be expressed as:

$$\Delta V_{BE} = \frac{k\vartheta}{q} \ln \left( \frac{I_{C2}}{I_{C1}} \frac{I_{S1}}{I_{S2}} \right) = \frac{k\vartheta}{q} \ln \gamma, \quad (2.21)$$

The symbol  $\pm$  in (2.19) represents the negative and the positive temperature coefficient, respectively. We call the voltages  $C_1\Delta V_{BE}$  or  $C_2\Delta V_{BE}$  PTAT (Proportional to the Absolute Temperature) voltages.

The value of the bandgap-reference voltage at a reference temperature  $\vartheta_r$  is equal to

$$V_{ref} = V_{g0} + (\eta - n) \frac{k\vartheta_r}{q}. \quad (2.22)$$

The parameters  $C_1$  and  $C_2$  are determined by

$$C_1 = \frac{V_{BE}(\vartheta_Z)}{\Delta V_{BE}(\vartheta_Z)} = \frac{V_{BE}(\vartheta_Z)}{\frac{k\vartheta_Z}{q} \ln \gamma}, \quad (2.23)$$

$$C_2 = \frac{V_{ref} - V_{BE}(\vartheta_r)}{\frac{k\vartheta_r}{q} \ln \gamma}. \quad (2.24)$$

Figure 2.3 shows how the signals are combined for the temperature sensor and the bandgap reference.

Figure 2.3 The linear combinations of  $V_{BE}$  and  $\Delta V_{BE}$  for (a) temperature sensors, (b) bandgap references.

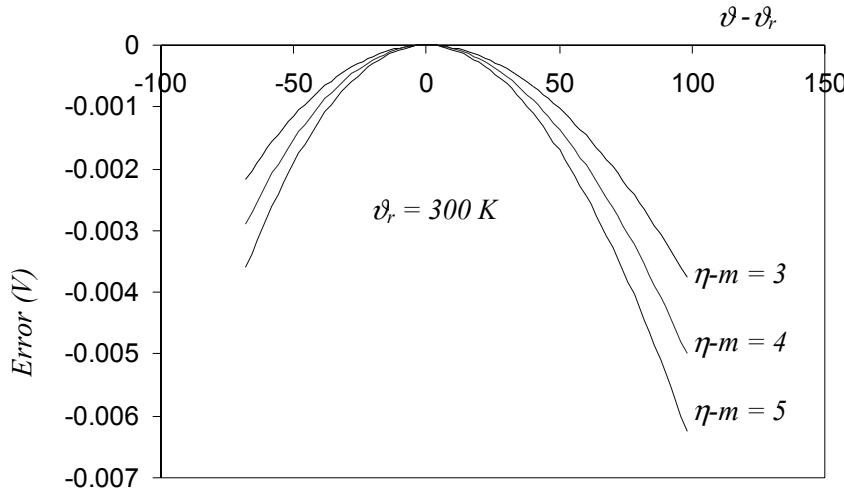

The higher-order term in equation (2.14) is not considered in the linear combinations (2.19) and (2.20). It causes a non-linear error in temperature sensors and bandgap references, as shown in Figure 2.4. The circuit design technique used to compensate for this error is called curvature correction.

Figure 2.4 The non-linearity  $\frac{k}{q}(\eta - m)(\vartheta - \vartheta_r - \vartheta \ln(\frac{\vartheta}{\vartheta_r}))$  versus temperature.

## 2.2.5 Calibration of Bandgap-References and Temperature Sensors

There are two reasons to calibrate bandgap references and temperature sensors: Firstly, at the ambient temperature the base-emitter voltage may deviate from the nominal value  $V_{BE}(\vartheta_A)$ ; this is due to process spread. Secondly, the amplification factor  $C_1$  or  $C_2$  may deviate from the design values due to a mismatch. Figure 2.5 shows the deviation of a bandgap reference due to deviations in the base-emitter voltage  $V_{BE}(\vartheta)$  and in the voltage  $C_2\Delta V_{BE}$ .

Figure 2.5 The spreading in the base-emitter voltage and in the PTAT voltage results in spreading in the bandgap reference.

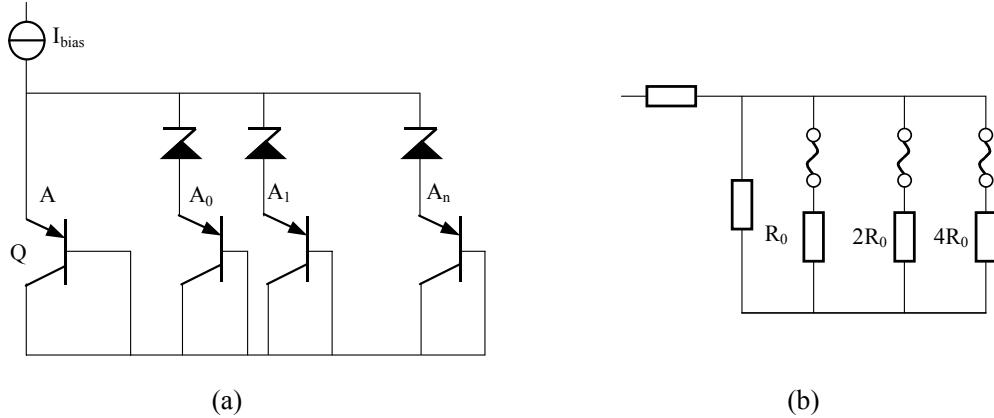

Trimming can be performed to adjust the base-emitter voltage or to adjust the resistors as shown in Figure 2.6. In Figure 2.6(a) the base-emitter voltage is adjusted by trimming the emitter area of the transistor. In Figure 2.6(b) the resistance is adjusted using fusible links.

Figure 2.6 (a) Adjusted emitter area, (b) adjusted resistor.

Several trimming techniques can be applied. The most commonly used are:

- Zener zapping (Figure 2.6(a)), to short-circuit connection,

- Fusible links (Figure 2.6(b)), to blow up connections, and

- Laser trimming, to adjust resistors.

The advantage of using fusible links is that for trimming a rather low voltage (5 V) can be used. For zener zapping, voltages up to 100 V are required. Therefore, special precautions have to be taken to protect the circuit during trimming. On the other hand, the zener-zapped components are usually highly reliable and show good long-term stability. With fusible links, special precautions have to be taken to avoid deterioration of the wafer-test probes. Furthermore, care has to be taken to avoid metal regrowth due to on-chip electro migration [2.4] during the whole lifetime of the chip.

The spreading in the base-emitter voltage  $\Delta_{VBE}$  and the adjustment tolerance of the base-emitter voltage  $\delta_{VBE}$  determine how many bit of trimming should be designed and the minimum area of the emitter, according to the following equations

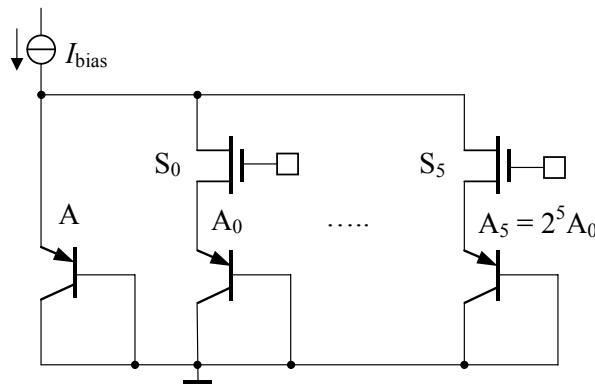

$$\begin{aligned} \frac{k\vartheta_r}{q} \ln \left( \frac{A + (2^n - 1)A_0}{A} \right) &\geq \Delta_{VBE}, \\ \frac{k\vartheta_r}{q} \ln \left( \frac{A + A_0}{A} \right) &\leq \delta_{VBE} \end{aligned} \quad (2.25)$$

where  $A$  represents the minimum area of the emitter,  $A_0$  represents minimum area of the emitter that can be adjusted and  $n$  represents the bit number of the trimming system. The emitter area can be adjusted from the minimum value  $A$  to the maximum value  $(A + (2^n - 1)A_0)$ . For instance, with  $\vartheta_r = 300$  K,  $\Delta_{VBE} = 20$  mV, and  $\delta_{VBE} = 0.5$  mV. Substituting the value into equation (2.25) yields

$$\begin{aligned} (2^n - 1)A_0 &\geq 1.158A \\ A_0 &\leq 0.0194A \end{aligned}$$

where  $n = 6$  and  $A = 52A_0$  can meet the above requirements. In this case, a 6-bit trimming structure is required. The area  $A$  is determined by the value of the base-emitter voltage at the reference temperature  $V_{BE}(\vartheta_r)$ .

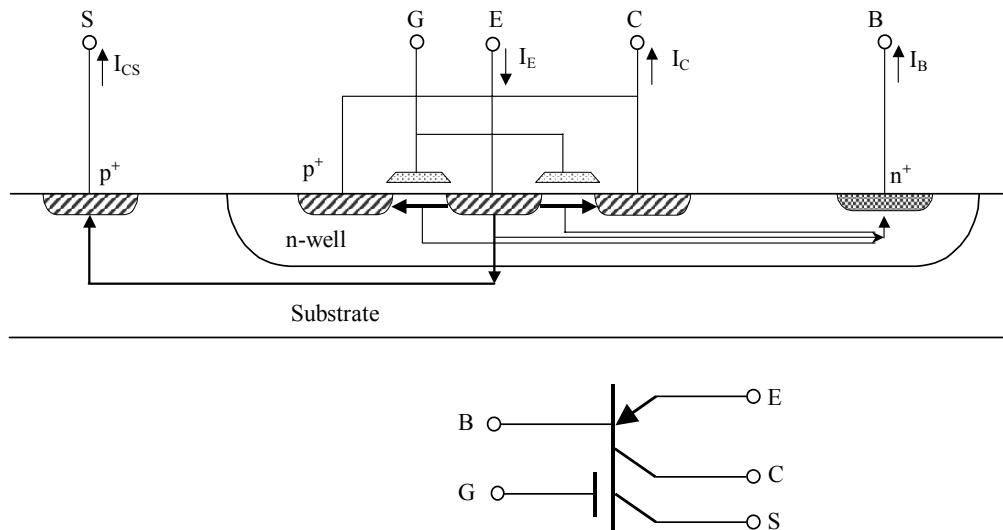

## 2.3 Bipolar Transistors in CMOS Technology

There are two types of CMOS processes: the n-well CMOS and the p-well CMOS process. The two types of bipolar transistors available thus differ for these two processes. For an n-well CMOS process, lateral pnp and vertical substrate pnp transistors are available. In addition, for a p-well CMOS process, lateral npn and vertical substrate npn transistors are available. In this thesis, bipolar transistors in an n-well CMOS process are described.

### 2.3.1 Lateral Transistor

Figure 2.7 shows a cross section of a lateral bipolar transistor implemented in a standard n-well CMOS process [2.4]. Two implanted p+ regions in the same n-well are used as the emitter and collector, while the n-well is used as the base. A gate is used to obtain a thin oxide layer, which makes it easier to etch the holes for the emitter and collector diffusions. Compared to lateral pnp transistors fabricated in a bipolar process, those fabricated in CMOS have the following special properties:

- There is no buried layer, and as a result quite a lot of the injected holes are collected by the substrate, which gives rise to a relatively high substrate current  $I_{\text{sub}}$ .

- They do not show one-dimensional behaviour, and as a result, the  $I_C(V_{\text{BE}})$  characteristic deviates from the ideal exponential relation.

- Even at rather low current level, high-level effects occur because especially transistors made using an n-well CMOS process have a low surface doping concentration.

Figure 2.7 The cross section of a lateral PNP-transistor in an n-well CMOS process.

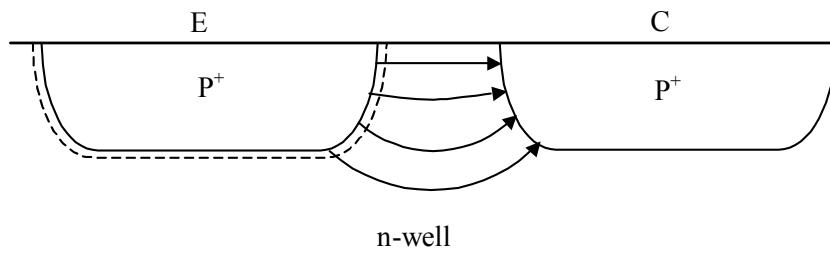

The effective emitter area in the expression of the saturation current  $I_S$  for the lateral transistor depends on the length along the emitter and the collector and on the depth of the p-diffused emitter, as shown in Figure 2.8. The change in the depletion layer between the emitter-base junctions that is caused by the change in the base-emitter voltage will change the effective emitter area. It causes  $I_C(V_{\text{BE}}, \vartheta)$  to deviate from the ideal exponential relation. Since the depletion layer also changes with temperature,  $V_{\text{BE}}(\vartheta)$  deviates from (2.11) as well.

Figure 2.8 The cross section of a lateral PNP-transistor in an n-well CMOS process.

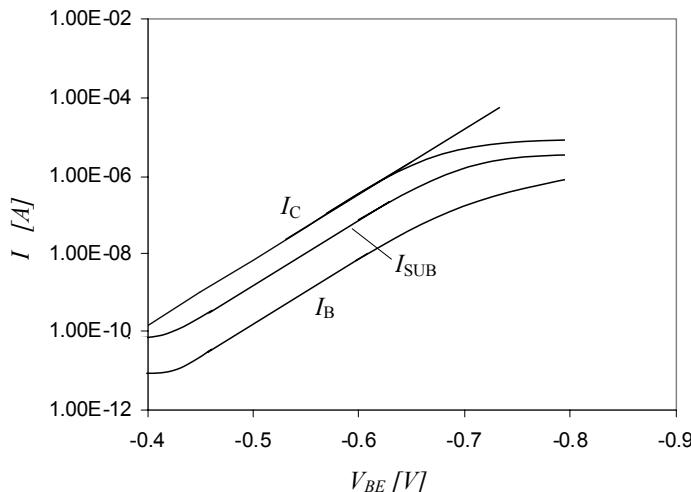

Figure 2.9 shows the  $I_C(V_{BE})$  characteristic of a lateral pnp transistor fabricated in the  $1.2\text{ }\mu\text{m}$  n-well CMOS process of Alcatel Microelectronics [2.5]. With the decrease in device size to submicron level, the depths of the  $n^+$ ,  $p^+$  and n-well become smaller, and the  $I_C(V_{BE}, \vartheta)$  characteristics becomes worse.

Figure 2.9 The  $I(V_{BE})$  characteristics of a lateral pnp transistor fabricated in an n-well CMOS process (courtesy of Alcatel Microelectronics).

The gate G in the 5-terminal structure can be used to improve the performance of the lateral bipolar transistors. By biasing the gate G properly, one can push the injected emitter current below the surface; thus:

- Noise due to surface effects is reduced.

- Current flow is repelled under the surface of the n-well, where the doping concentration is lower than that at the surface, which results in a larger forward current gain.

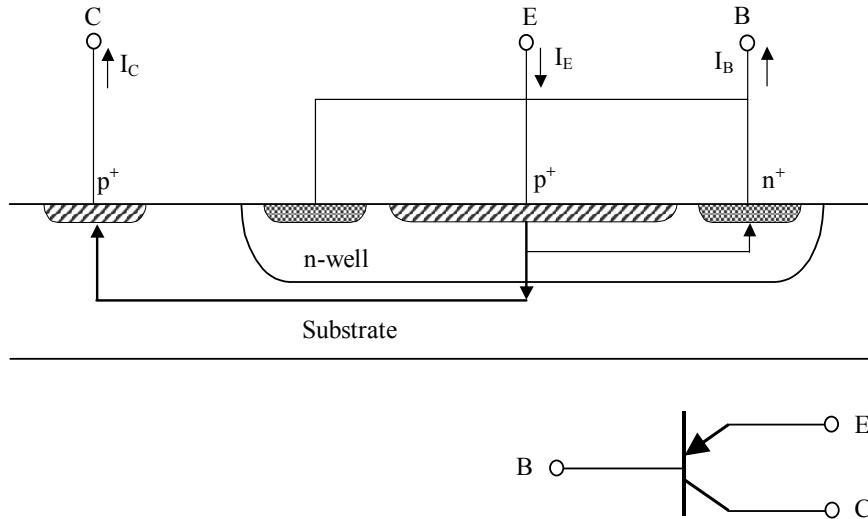

### 2.3.2 Vertical Substrate Transistor

Figure 2.10 shows a cross section of a vertical pnp transistor implemented in a standard n-well CMOS process. Some special properties of the vertical bipolar transistors are:

- The base width, typically a few microns, is determined by the distance between the bottom of the p+ regions and that of the n-well.

- The base-width modulation effect is relatively weak due to the larger base width, resulting in a large early voltage. The base resistance is also relatively high.

- The collector (substrate) is lightly doped, and therefore the series collector resistance is high.

Figure 2.10 The cross section of a vertical PNP-transistor in an n-well CMOS process.

Although its junction depths and doping are not optimized for bipolar operation, the vertical bipolar transistor exhibits good performance with respect to the ideality of the  $I_C(V_{BE})$  characteristic, because it shows better one-dimensional behaviour than the lateral transistor. However, the substrate collector limits the circuit design to only common-collector configurations.

### 2.3.3 Comparison of Two Types of the Bipolar Transistors

Lateral [2.5] [2.6] and vertical [2.7]-[2.11] bipolar transistors have been applied in the designs of temperature sensors and bandgap references.

With respect to the  $I_C(V_{BE})$  characteristic, vertical substrate transistors are superior, because they perform much better than lateral transistors.

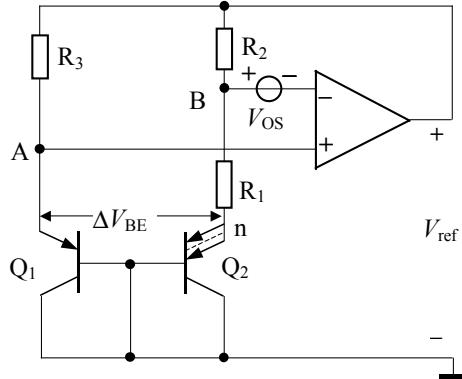

With respect to the circuit design, circuits based on lateral transistors are more flexible, because they allow the use of configurations from bipolar technology in CMOS technology. Designing circuits based on vertical transistors in CMOS poses a problem however, as there the common-emitter structure, which is the conventional circuit used in bipolar technology to generate and amplify the signal  $\Delta V_{BE}$ , cannot be applied. Therefore, special amplifier configurations are required to amplify the voltage  $\Delta V_{BE}$ . Figure 2.11 shows two basic circuits for a CMOS bandgap reference using lateral and vertical transistors.

Figure 2.11 Two simple schematics of bandgap references in CMOS technology using (a) lateral, and (b) vertical transistors.

In Figure 2.11(b), the offset voltage of the operational amplifier must be taken into account in the expression of the output voltage:

$$V_{ref} = V_{BE1} + \frac{R_3}{R_1} V_{R1} \approx V_{BE1} + A_2 \left( \frac{k\vartheta}{q} \ln \frac{I_{S2}}{I_{S1}} + V_{OS} \right), \quad (2.26)$$

where  $V_{R1}$  represents the voltage across the resistor  $R_1$ . The non-zero offset voltage  $V_{OS}$  and its temperature dependence deteriorate the performance of the bandgap voltage output. For this reason, circuits using vertical transistors show worse results than those using lateral transistors [2.5] –[2.11].

In order to design high-performance bandgap references and temperature sensors, one must first develop advanced circuit design techniques that overcome the disadvantages of circuits employing vertical transistors, as the performance of temperature sensors and bandgap references is mainly limited by imperfection of the device characteristics.

In this thesis, it is shown that by the use of advanced circuit design techniques, one can obtain circuits generating a highly accurate  $\Delta V_{BE}$  signal. In these high-performance temperature sensors and bandgap references, vertical bipolar transistors are used, which perform much better than lateral ones.

## 2.4 Conclusions

This chapter described the basic theory of bipolar transistors, especially the  $I_C(V_{BE}, \vartheta)$  for the purpose of circuit design for temperature sensors and bandgap references. Two types of bipolar transistors, lateral and vertical substrate transistors, fabricated in CMOS technology were discussed. With respect to the  $I_C(V_{BE})$  characteristic, vertical substrate transistors are preferred for generating the signals  $V_{BE}$  and  $\Delta V_{BE}$  in our high-precision temperature sensors and bandgap references. However, advanced circuit design techniques should be developed to overcome the disadvantages of circuits employing vertical transistors.

## References

- [2.1] J.W. Slotboom and H.C. De Graaf, "Measurements of Bandgap Narrowing in Si Bipolar Transistors", Solid-State Electronics, Vol. 19, pp. 857-862, Oct. 1976.

- [2.2] G.C.M. Meijer and K. Vingerling, "Measurement of the Temperature Dependence of the  $I_C(V_{BE})$  Characteristics of Integrated Bipolar Transistors", IEEE Journal of Solid-state Circuits, Vol. SC-15, No. 2, pp. 1151-1157, April 1980.

- [2.3] Y.P. Tsividis, "Accurate Analysis of Temperature Effects in  $I_C-V_{BE}$  Characteristics with Application to Bandgap Reference Sources", IEEE Journal of Solid-state Circuits, Vol. SC-15, No. 6, pp. 1076-1084, Dec. 1980.

- [2.4] G.C.M. Meijer, "Concepts for Bandgap-references and Voltage Measurement Systems", in Analog Circuit Design edited by J.H. Huijsing, R.J. van de Plassche and W.M.C. Sansen, Kluwer Ac. Publ., Dordrecht, pp. 243-268, 1996.

- [2.5] M.G.R. Degrauwe, O.N. Leuthold, E.A. Vittoz, H.J. Oguey and A. Descombes, "CMOS Voltage References Using Lateral Bipolar Transistors", IEEE Journal of Solid-state Circuits, Vol. SC-20, No. 6, pp. 1151-1157, Dec. 1985.

- [2.6] R.A. Bianchi, F. Vinci Dos Santos, J.M. Karam, B. Courtois, F. Pressecq and S. Sifflet, "CMOS compatible temperature sensor based on the lateral bipolar transistor for very wide temperature range application", Sensors and Actuators, A71, pp. 3-9, 1998.

- [2.7] Ganesan et al., "CMOS Voltage Reference with Stacked Base-Emitter Voltages", US. Patent, 5.126.653, June 30, 1992.

- [2.8] M. Tuthill, "A Switched-Current, Switched-Capacitor Temperature Sensor in 0.6- $\mu\text{m}$  CMOS", IEEE Journal of Solid-State Circuits, Vol. 33, No. 7, pp. 1117-1122, July 1998.

- [2.9] G. Tzanateas, C.A. Salama and Y.P. Tsividis, "A CMOS Bandgap Reference", IEEE Journal of Solid-State Circuits, Vol. SC-14, No. 3, pp. 655-657, June 1979.

- [2.10] Eric A. Vittoz and O. Neyroud, "A Low-Voltage CMOS Bandgap Reference", IEEE Journal of Solid-state Circuits, Vol. SC-14, No. 3, pp. 573-577, June 1979.

- [2.11] Y.P. Tsividis and R. W. Ulmer, "A CMOS Voltage Reference", IEEE Journal of Solid-state Circuits, Vol. SC-13, No. 6, pp. 774-778, Dec. 1978.

# Chapter 3 Characterization of the Temperature Behavior

## 3.1 Introduction

This chapter deals with the device characterization of vertical substrate bipolar transistors. To investigate the characteristics of vertical bipolar transistors, and to identify the non-ideal effects that limit the accuracy of the voltages  $V_{BE}$  and  $\Delta V_{BE}$ , we measured the voltages  $V_{BE}$  and  $\Delta V_{BE}$  versus the temperature and the collector current  $I_C$ . We derived the parameters  $V_{g0}$  and  $\eta$ , the effective emission coefficient  $m$ , the forward current gain  $B_F$ , and the base resistances  $R_B$ . Non-ideal effects were analysed too.

For vertical substrate bipolar transistors, it is easier to control the emitter current  $I_E$  than the collector current  $I_C$ . Therefore, not only the  $V_{BE}(I_C, \vartheta)$  characteristics must be characterized, but also the base-current effect: due to the low current gain of the vertical substrate bipolar transistors, the base current has a significant effect on the voltages  $V_{BE}$  and  $\Delta V_{BE}$ . The non-idealities that affect the accuracy of  $\Delta V_{BE}$ , such as the base resistance, the effective emission coefficient and the low injection effect were investigated by measuring  $\Delta V_{BE}$ . We investigated how the geometry and biasing current of the transistors can be optimized.

Devices fabricated in two CMOS processes, 0.7- $\mu\text{m}$  and 0.5- $\mu\text{m}$ , were characterized.

## 3.2 Measurement Set-ups.

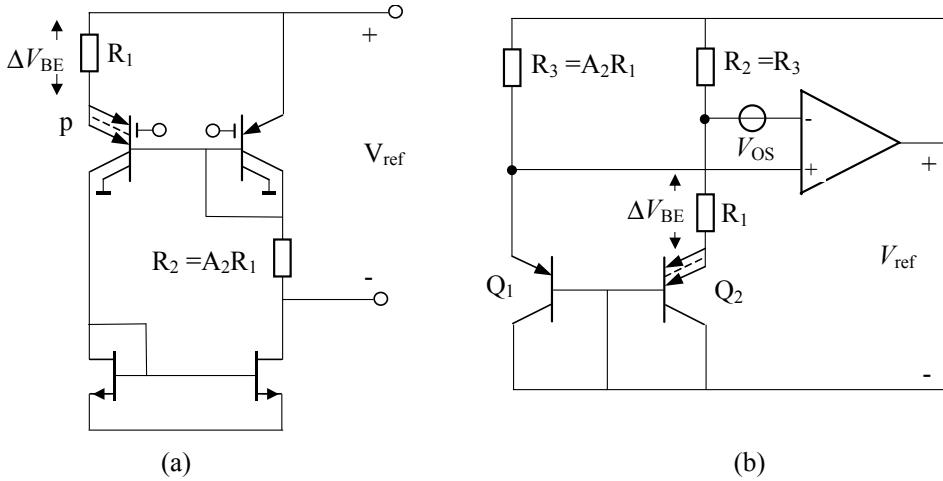

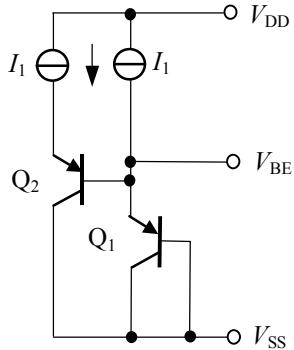

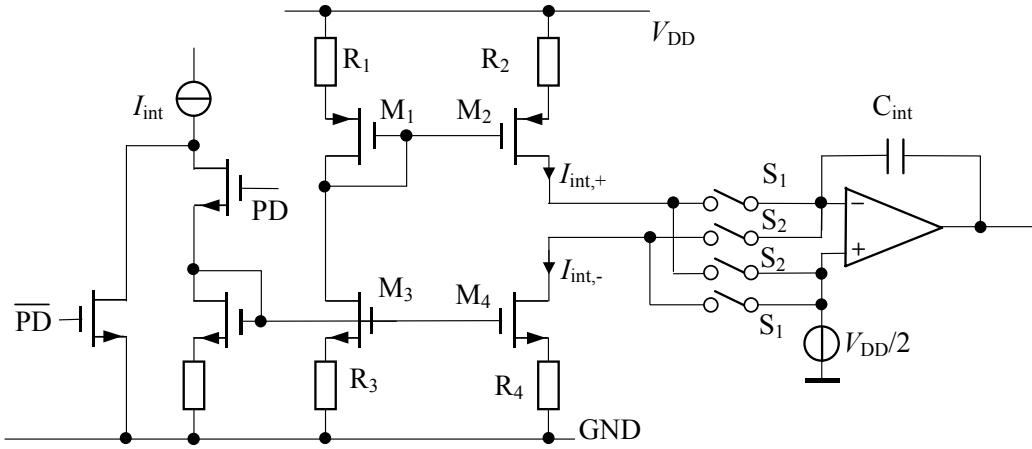

Figure 3.1 shows the schematics of the measurement set-ups for the  $V_{BE}(I_C, \vartheta)$  and  $\Delta V_{BE}(I_C, \vartheta)$  characterizations. The emitter currents  $I_E$ , the base currents  $I_B$  and the voltages  $V_{BE}$  and  $\Delta V_{BE}$  are measured for different temperatures.

For our investigations and experiments, we selected a temperature range of  $-40$  °C to  $160$  °C. For the biasing current range, we chose the range of 5 nA to 1 mA for the base-emitter voltage measurement and that of 5 nA to 100  $\mu\text{A}$  for the  $\Delta V_{BE}$  measurement, respectively. The current range was chosen based on practical constraints. These are due to the low-current effects, interference, and  $1/f$  noise at the low end of the range, and to the high-current effects and power dissipation at the high end. The target for the desired accuracy of all measurements corresponds to a temperature error of less than 0.1 K.

To realize accurate voltage and current measurements, we applied an auto-calibration technique to eliminate the additive and multiplicative effects of the measurement set-ups [3.1].

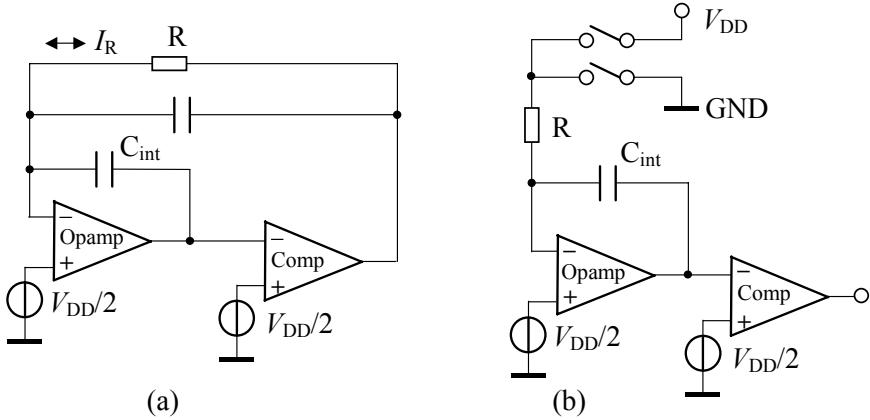

Figure 3.1 The measurement set-ups for the (a)  $V_{BE}(I_C, \theta)$ , and (b)  $\Delta V_{BE}(I_C, \theta)$  characterisation.

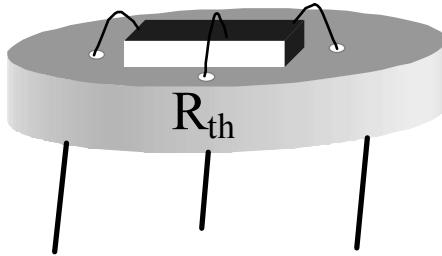

By using an appropriate thermal design, we could control and measure the temperature accurately. In this design, particular care has been taken to minimize the self-heating, the temperature gradients and drift during the measurement.

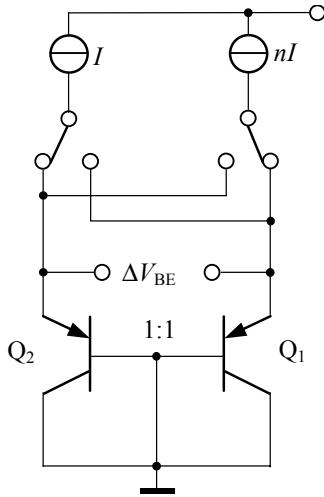

The test device for the  $\Delta V_{BE}$  characterization consists of a pair of transistors of identical emitter size. Mismatching of the transistors will introduce an error in the  $\Delta V_{BE}$  measurement. This error has been eliminated by employing the dynamic element matching technique. This was realized by interchanging the two transistors and taking the average of the measured  $\Delta V_{BE}$  voltages under the same biasing condition [3.2].

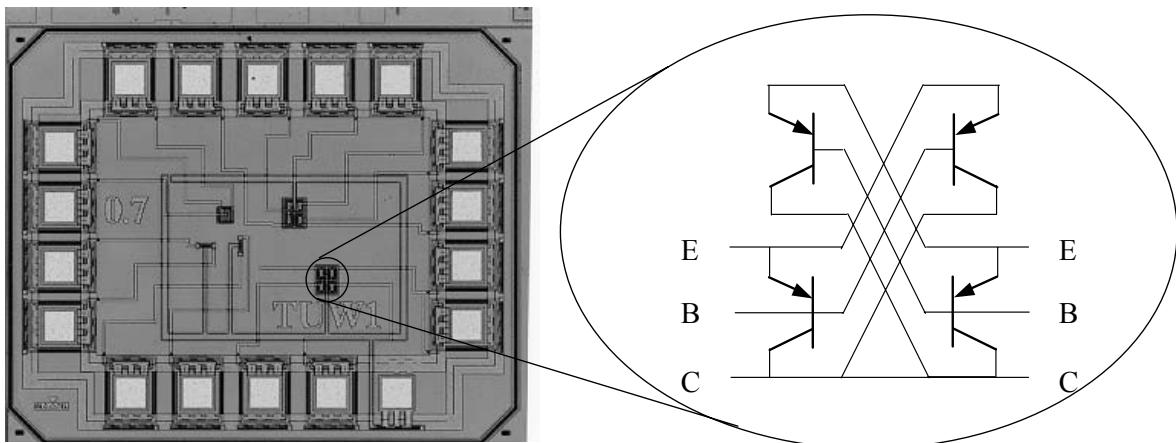

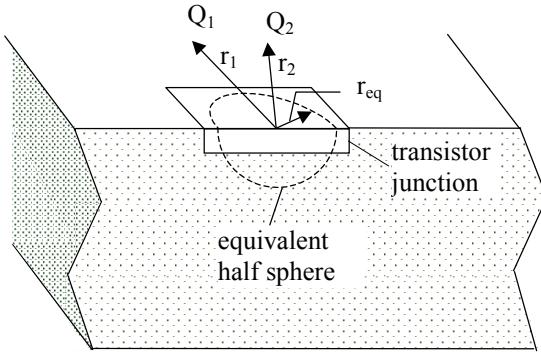

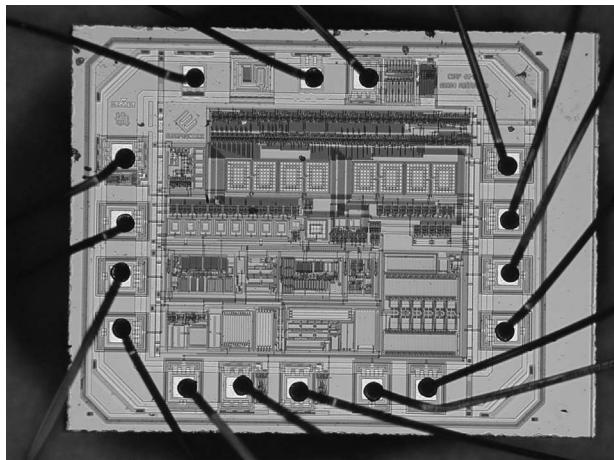

Figure 3.2 shows a photograph of the test chip. On this chip, a single bipolar substrate transistor and a pair of transistors in a quad configuration are used to characterize the  $V_{BE}(I_C, \theta)$  and  $\Delta V_{BE}(I_C, \theta)$  behaviour. The emitter size of all transistors is  $10 \mu\text{m} \times 20 \mu\text{m}$ .

Figure 3.2 (a) A photograph of the test chip; (b) The transistor pairs under tested are configured in a quad configuration.

### 3.3 Parameter Characterizations

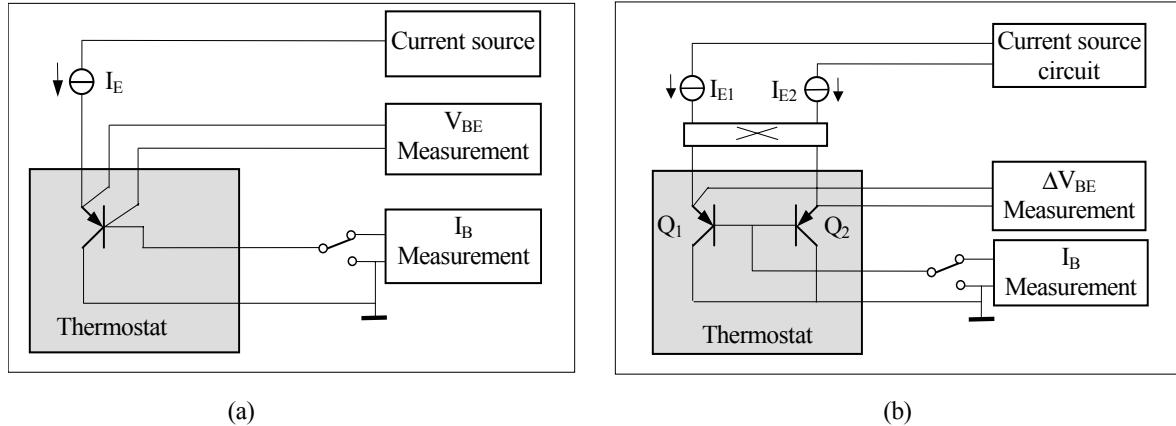

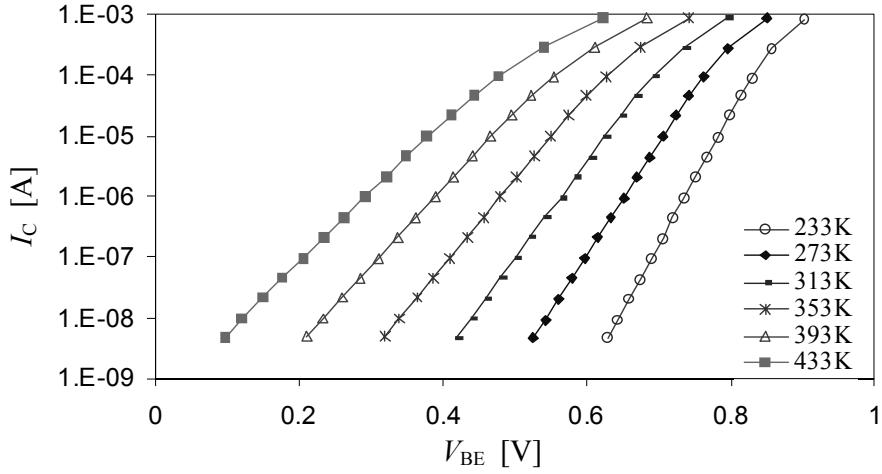

For the temperature range from  $-40$  °C to  $160$  °C, we measured the base-emitter voltage  $V_{BE}$  under a emitter current  $I_E$  varying from  $5$  nA to  $1$  mA. The corresponding base current  $I_B$  was measured as well. The collector current  $I_C$  was derived by subtracting the measured base current from the measured emitter current. The measured  $V_{BE}(I_C, \vartheta)$  is plotted in Figure 3.3.

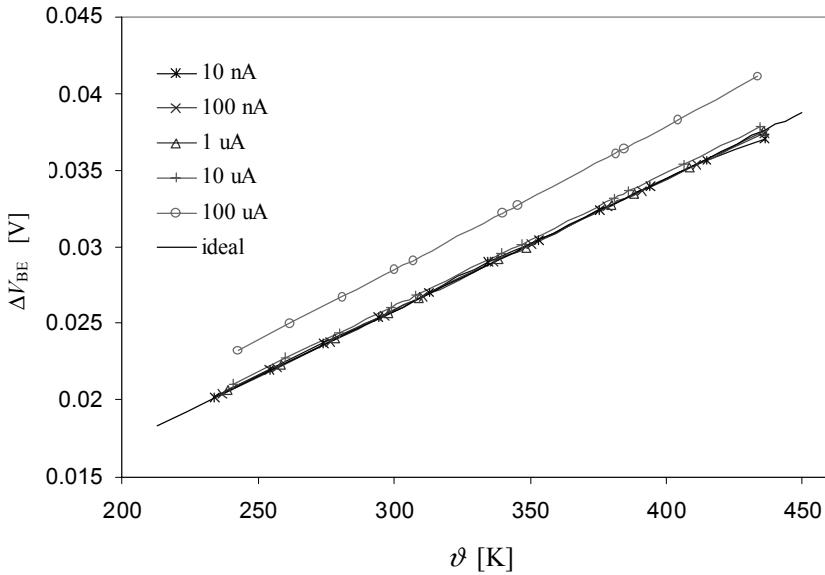

For the same temperature range, we measured the voltage  $\Delta V_{BE}$ , under a emitter current ( $I_{E1}$ ) varying from  $10$  nA to  $100$   $\mu$ A, with the emitter current ratio ( $I_{E2}/I_{E1}$ ) of 3. The measured  $\Delta V_{BE}(I_C, \vartheta)$  is plotted in Figure 3.4. The emitter currents and the corresponding base currents were measured as well.

These measurement results were used to derive the transistor parameters, as described in the next paragraphs.

Figure 3.3 The measured results for  $V_{BE}(I_C, \vartheta)$  for  $0.7$ - $\mu$ m CMOS.

Figure 3.4 The measured  $\Delta V_{BE}(\vartheta)$  for different emitter currents ( $I_E$ ).

### 3.3.1 The Saturation Current $I_S$

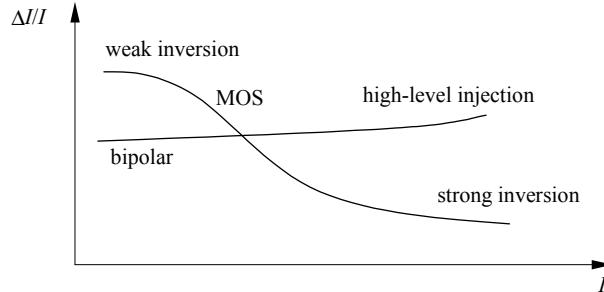

Figure 3.3 shows the measured results for the  $V_{BE}(I_C, \vartheta)$  of a substrate bipolar transistor. A good exponential relation was found between  $V_{BE}$  and  $I_C$  over several decades of collector current. The deviation at high current levels is due to the contributions of the base resistance and the high injection effect.

The saturation current  $I_S$  was derived by curve fitting of the measured  $I_C$ - $V_{BE}$  characteristic over the current range of 10 nA to 4  $\mu$ A. Table 3.1 lists the extracted saturation current  $I_S$  of the devices fabricated in 0.7- $\mu$ m and 0.5- $\mu$ m CMOS with an emitter area of 10  $\mu$ m  $\times$  20  $\mu$ m.

|                     | $I_S$ (A) (0.7- $\mu$ m CMOS) | $I_S$ (A) (0.5- $\mu$ m CMOS) |

|---------------------|-------------------------------|-------------------------------|

| $\vartheta = 233$ K | $1.26 \times 10^{-22}$        | $3.04 \times 10^{-23}$        |

| $\vartheta = 293$ K | $3.49 \times 10^{-17}$        | $9.13 \times 10^{-18}$        |

| $\vartheta = 433$ K | $3.98 \times 10^{-10}$        | $1.08 \times 10^{-10}$        |

Table 3.1 The extracted saturation currents for three temperatures (emitter size: 10  $\mu$ m  $\times$  20  $\mu$ m).

Note that the saturation currents of a substrate bipolar transistor fabricated in 0.7- $\mu$ m CMOS technology were roughly 3.8 times of those of a transistor fabricated in 0.5- $\mu$ m CMOS technology. According to equations (2.3), (2.5) and (2.7), the saturation current depends on the mobility of the minority in the base and the doping concentration in the base. We can conclude that the heavier doping concentrations and mobility of the minority in the base result in the lower saturation current in 0.5- $\mu$ m CMOS.

### 3.3.2 The Knee Current $I_{KF}$

The parameter  $I_{KF}$  represents the behaviour of the transistor at high injection, when the injected minority carrier concentration is in the order of the base doping concentration. In this case,  $I_C(V_{BE})$  deviates from the exponential relation  $I_C = I_S e^{(qV_{BE}/k\vartheta)}$ :

$$I_C = -\frac{I_{hl}}{2} + \frac{I_{hl}}{2} \sqrt{1 + \frac{4I_S}{I_{hl}} e^{\frac{qV_{BE}}{k\vartheta}}}, \quad (3.1)$$

where the current  $I_{hl}$  is defined as the current when the injected minority concentration equals the base doping concentration:

$$I_{hl} = qD_B F_{geo} N_B \quad (3.2)$$

which also equals the value of the knee current  $I_{KF}$ . When

$$I_S e^{\frac{qV_{BE}}{k\vartheta}} \gg I_{hl}, \quad (3.3)$$

equation (3.1) becomes:

$$I_C = \sqrt{I_{hl} I_S} e^{\frac{qV_{BE}}{2k\vartheta}}, \quad (3.4)$$

Figure 3.5 The  $I_C$ - $V_{BE}$  including high injection effect.

In the area where the curve starts to bend from  $\exp(qV_{BE}/k\vartheta)$  to  $\exp(qV_{BE}/2k\vartheta)$ , the knee current  $I_{KF}$  can be approximately calculated by

$$I_{KF} = I_{hl} = \frac{I_{C,m}^2}{I_S e^{\frac{qV_{BE}}{k\vartheta}} - I_{C,m}}, \quad (3.5)$$

where  $I_{C,m}$  is the measured collector current and  $I_S$  is derived from the measured  $I_C$ - $V_{BE}$  at lower current range. The calculated  $I_{KF}$  at room temperature is listed in Table 3.2, where the effect of the base resistance is neglected. It is shown that with the same emitter area, the high injection occurs earlier in devices fabricated in 0.7- $\mu\text{m}$  CMOS than in the devices fabricated in 0.5- $\mu\text{m}$  CMOS.

|                     | $I_{KF}$ (A)<br>(0.7- $\mu\text{m}$ CMOS) | $I_{KF}$ (A)<br>(0.5- $\mu\text{m}$ CMOS) |

|---------------------|-------------------------------------------|-------------------------------------------|

| $\vartheta = 293$ K | ~1.5 mA                                   | ~4.3 mA                                   |

Table 3.2 The calculated knee current  $I_{KF}$  at room temperature (emitter size: 10  $\mu\text{m} \times$  20  $\mu\text{m}$ ).

### 3.3.3 Parameters $V_{g0}$ and $\eta$

As described in chapter 2, the temperature dependence of the base emitter voltage  $V_{BE}(\vartheta)$  can be expressed as:

$$V_{BE}(\vartheta) = V_{g0} \left( 1 - \frac{\vartheta}{\vartheta_r} \right) + \frac{\vartheta}{\vartheta_r} V_{BE}(\vartheta_r) - \eta \frac{k\vartheta}{q} \ln \left( \frac{\vartheta}{\vartheta_r} \right) + \frac{k\vartheta}{q} \ln \left( \frac{I_C(\vartheta)}{I_C(\vartheta_r)} \right), \quad (3.6)$$

where  $V_{g0}$  is the extrapolated bandgap voltage at 0 K,  $\eta$  is a material-dependent and process-dependent parameter, and  $\vartheta_r$  is the reference temperature.

The parameters  $V_{g0}$  and  $\eta$  can be derived from the measured results of  $V_{BE}$  at three temperatures  $\vartheta_1$ ,  $\vartheta_r$  and  $\vartheta_2$  ( $\vartheta_1 < \vartheta_r < \vartheta_2$ ) [3.3], by solving the equation:

$$\begin{cases} V_{BE}(\vartheta_1) = V_{g0} \left( 1 - \frac{\vartheta_1}{\vartheta_r} \right) + \frac{\vartheta_1}{\vartheta_r} V_{BE}(\vartheta_r) - \eta \frac{k\vartheta_1}{q} \ln \left( \frac{\vartheta_1}{\vartheta_r} \right) + \frac{k\vartheta_1}{q} \ln \left( \frac{I_C(\vartheta_1)}{I_C(\vartheta_r)} \right) \\ V_{BE}(\vartheta_2) = V_{g0} \left( 1 - \frac{\vartheta_2}{\vartheta_r} \right) + \frac{\vartheta_2}{\vartheta_r} V_{BE}(\vartheta_r) - \eta \frac{k\vartheta_2}{q} \ln \left( \frac{\vartheta_2}{\vartheta_r} \right) + \frac{k\vartheta_2}{q} \ln \left( \frac{I_C(\vartheta_2)}{I_C(\vartheta_r)} \right) \end{cases} \quad (3.7)$$

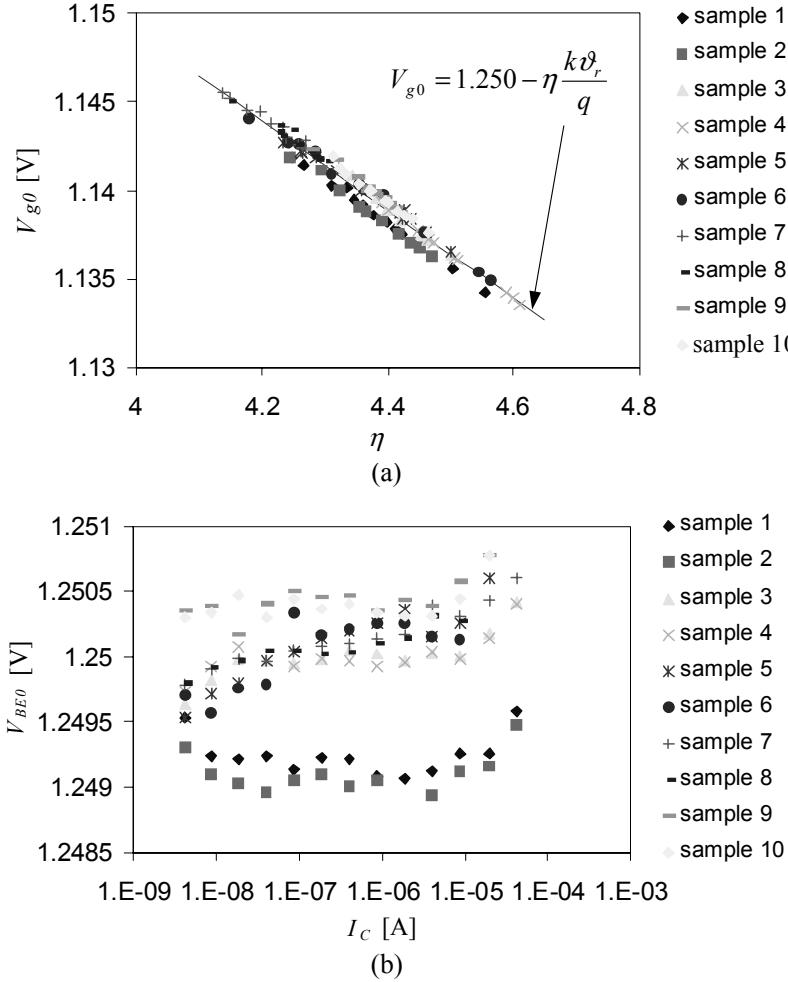

The parameters  $V_{g0}$  and  $\eta$  have been calculated based on the measured base-emitter voltages for  $-40$  °C ( $\vartheta_1$ ),  $20$  °C ( $\vartheta_r$ ), and  $80$  °C ( $\vartheta_2$ ). The results are shown in Figure 3.6(a). There is a strong negative correlation between  $V_{g0}$  and  $\eta$ , which is similar to that found by Meijer and Vingerling, and by Ohte and Yamahata, for transistors fabricated in bipolar technology [3.3], [3.4].

An important parameter in designing a bandgap reference is  $V_{BE0}(\vartheta_r)$ , which is the intersection of the tangent of the curve  $V_{BE}(\vartheta)$  at the point  $\vartheta_r$  with the vertical axis ( $\vartheta = 0$  K). The parameter  $V_{BE0}(\vartheta_r)$  is calculated as:

$$V_{BE0}(\vartheta_r) = V_{g0} + \eta \frac{k\vartheta_r}{q}. \quad (3.8)$$

It was found that at  $293$  K,  $V_{BE0} \approx 1.252$  V for transistors fabricated in  $0.7$ -μm CMOS technology, and  $V_{BE0} \approx 1.250$  V for transistors fabricated in  $0.5$ -μm CMOS technology. The value of  $V_{BE0}$  versus the collector current is plotted in Figure 3.6(b). At high current levels, due to the effects of the base resistance and the high injection,  $I_C$ - $V_{BE}$  deviates from the exponential relationship, resulting in a large deviation in the parameter extraction.

Figure 3.6 (a) The calculated parameter  $V_{go}$  and  $\eta$  based on the measurement results for -40 °C, 20 °C, and 80 °C for 10 samples, and (b) the parameter  $V_{BE0}$  at room temperature (300K) for 0.5- $\mu$ m CMOS.

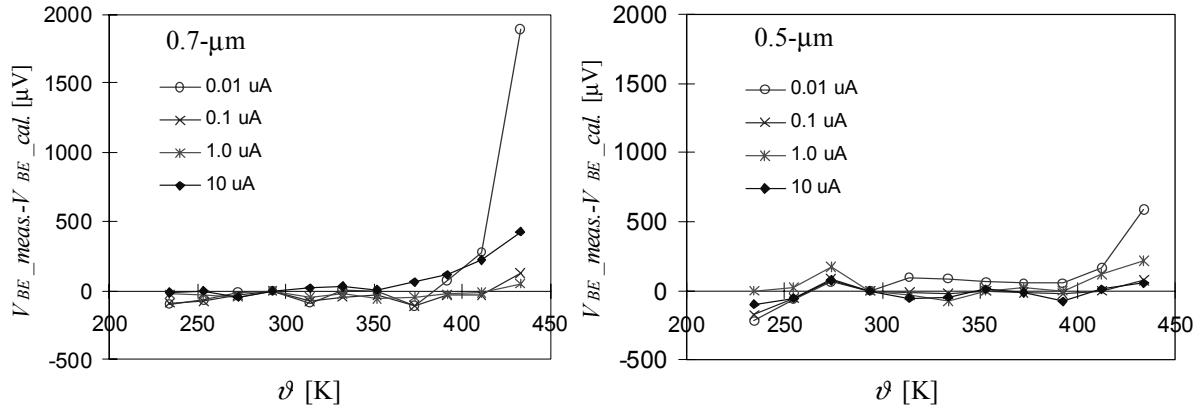

Figure 3.7 shows the difference between the measured base-emitter voltage  $V_{BE\text{meas.}}$  and the calculated base-emitter voltage  $V_{BE\text{cal.}}$ , based on the Gummel-Poon model, for which the extracted model parameters were used, which fits the  $V_{BE}(\vartheta)$  best ( $V_{go} = 1.147$  V,  $\eta = 4.15$ ). The inaccuracy is less than  $\pm 0.1$  mV (see Figure 3.7), which corresponds to a temperature error of less than  $\pm 0.05$  K for the temperature range of -20°C to 100°C. Comparing this result with those presented in [3.3] and [3.4], we can conclude that the temperature behavior of  $V_{BE}$  of CMOS bipolar substrate transistors fits the Gummel-Poon model as well as the behavior of the transistors fabricated in bipolar technology. This indicates why the curve with emitter current of 0.01  $\mu$ A shows a large deviation at high temperatures. At these temperatures, the low injection effect occurs, so that the simplified exponential relation  $I_C = I_{S\text{exp}}(qV_{BE}/k\vartheta)$  no longer accurately express the  $I_C-V_{BE}$ . For instance, the extracted saturation current at 160 °C is  $3.9 \times 10^{-10}$ , under the biasing current of 0.01  $\mu$ A, the simplified exponential relation  $I_C = I_{S\text{exp}}(qV_{BE}/k\vartheta)$  causes an error of 1.6 mV. The large deviation of the curve for the emitter current of 10  $\mu$ A at high temperatures is due to the base resistance and the high injection effect.

Figure 3.7 The deviation of the measured  $V_{BE}$  from the calculated value based on the Gummel-Poon model with the fitted result  $V_{go} = 1.147$  V,  $\eta = 4.15$ , for 0.7- $\mu$ m CMOS and  $V_{go} = 1.141$  V,  $\eta = 4.3$ , for 0.5- $\mu$ m CMOS.

Table 3.3 lists the parameters derived from measurements for the current range from 0.01  $\mu$ A to 10  $\mu$ A. It is clear that there are only minor differences for the parameters  $V_{go}$ ,  $\eta$ , and  $V_{BE0}$  between the devices fabricated in 0.7- $\mu$ m CMOS technology and the devices fabricated in 0.5- $\mu$ m CMOS technology.

|                   | $V_{go}$ (V)        | $\eta$          | $V_{BE0}$ (V) (300K) | $V_{BE\text{meas.}} - V_{BE\text{cal.}}$ ( $\mu$ V) |

|-------------------|---------------------|-----------------|----------------------|-----------------------------------------------------|

| 0.7- $\mu$ m CMOS | $1.1456 \pm 0.0030$ | $4.23 \pm 0.10$ | $1.255 \pm 0.001$    | < 100                                               |

| 0.5- $\mu$ m CMOS | $1.1390 \pm 0.0050$ | $4.33 \pm 0.20$ | $1.252 \pm 0.001$    | < 100                                               |

Table 3.3 The parameter values for bipolar substrate transistors fabricated in 0.7- $\mu$ m and 0.5- $\mu$ m CMOS technology, respectively.

### 3.3.4 Effective Emission Coefficient $m$

The effective emission coefficient  $m$  is defined as [3.5]:

$$\frac{1}{m} = \frac{k\vartheta}{qI_C} \cdot \left. \frac{\partial I_C}{\partial V_{BE}} \right|_{V_{CB}=\text{const.}} \quad (3.9)$$

$m$  varies from approximately unity at low collector current to approximately two at high collector currents. If we take the effective emission coefficient into account, the  $I_C$ - $V_{BE}$  dependency is:

$$I_C = I_S \exp^{\frac{qV_{BE}}{mk\vartheta}} \quad (3.10)$$

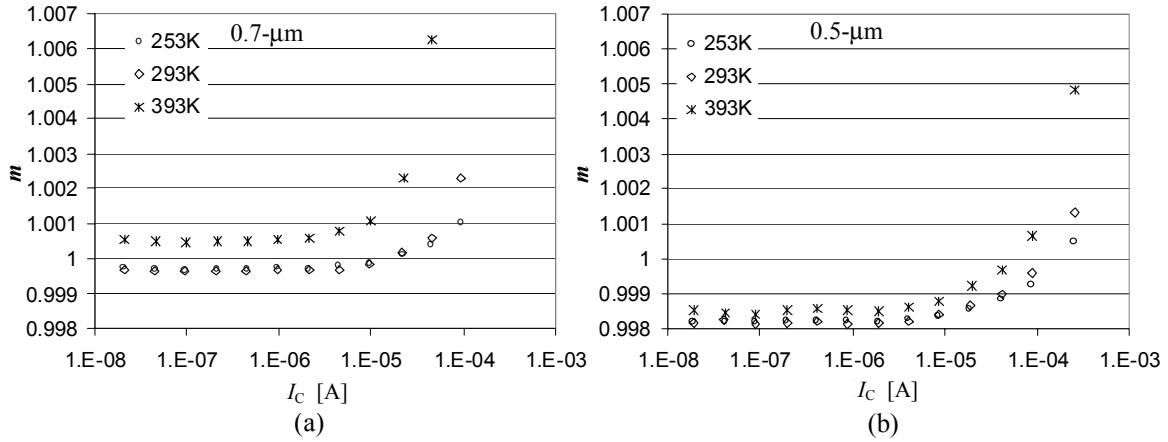

From the measurement results shown in Figure 3.3, the parameter  $m$  is derived and depicted in Figure 3.8.

Figure 3.8 The effective emission coefficient at three temperatures.

The calculation according to equation (3.2) shows that at higher temperatures, the  $I_C$ - $V_{BE}$  starts to deviate from the ideal exponential relation earlier, and as a result, the effective emission coefficient  $m$  deviates from unity earlier. Figure 3.8 supports this conclusion.

The effective emission coefficient  $m$  can also be derived from the  $\Delta V_{BE}(I_C, \vartheta)$  measurement. In the moderate current range, the low injection effect and high injection effect can be neglected. In this current range, the effective emission coefficient  $m$  can be derived from:

$$m = \frac{\Delta V_{BE\_Meas.} - R_B \Delta I_B}{\Delta V_{BE\_i.}}, \quad (3.11)$$

where  $\Delta V_{BE\_Meas.}$  is the measured voltage  $\Delta V_{BE}$  and  $\Delta V_{BE\_i.}$  is the voltage  $\Delta V_{BE}$  calculated by substituting the measurement data for the current ratio and the temperature in equation (2.21). The result  $m$  versus temperature is shown in Figure 3.9. The drop of  $m$  at high temperatures

and low currents is caused by the fact that the approximation of  $I_C = I_S \exp^{\frac{qV_{BE}}{mk\vartheta}}$  is not valid any more. According to equation (2.1),  $\Delta V_{BE\_i.}$  is calculated by:

$$\Delta V_{BE\_i.} = \frac{k\vartheta}{q} \cdot \ln \left( \frac{I_{C2} + I_{S2}}{I_{C1} + I_{S1}} \cdot \frac{I_{S1}}{I_{S2}} \right), \quad (3.12)$$

which results in a lower value than when it is calculated using equation (2.21).

Figure 3.9 The effective emission coefficient  $m$  at  $I_{E1} = 0.1 \mu\text{A}$  and  $I_{E1} = 1 \mu\text{A}$  for the same emitter area of  $10 \mu\text{m} \times 20 \mu\text{m}$ .

The parameter  $m$  derived from the  $\Delta V_{BE}$  measurement (Figure 3.9) is in good agreement with that derived from the  $V_{BE}$  measurement, except for the point at a temperature of 233 K.

It is concluded that in the moderate current range, the effective emission coefficient in CMOS technology is very close to the ideal value of unity.

### 3.3.5 Forward Current Gain $B_F$

We determined the static forward common-emitter current gain  $B_F$  by measuring the emitter current  $I_E$  and the base current  $I_B$ , respectively.

$$B_F = \frac{I_E}{I_B} - 1 \quad (3.13)$$

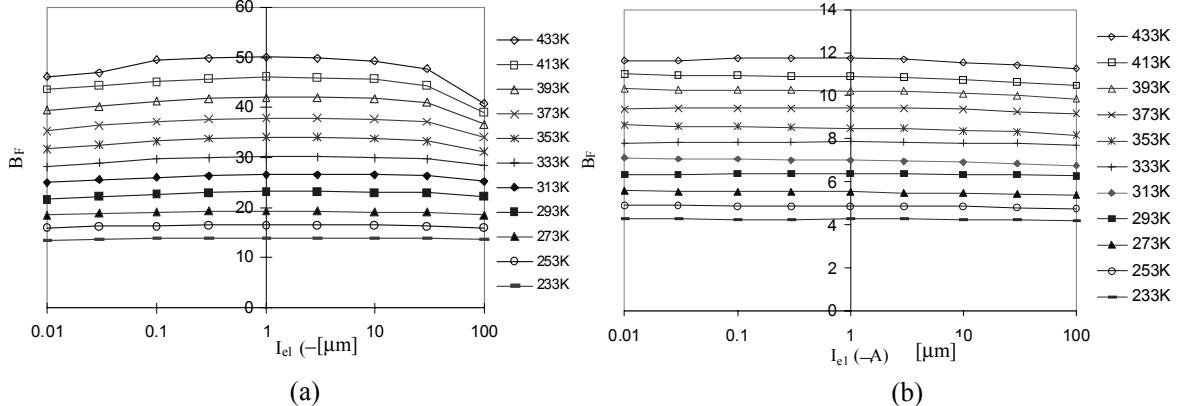

The measured forward current gain  $B_F$  versus emitter current and temperature are depicted in Figure 3.10 and Figure 3.11, respectively.

Figure 3.10 The current dependencies of the current gain for (a) 0.7-μm, and (b) 0.5-μm CMOS.

Figure 3.10 shows that in the intermediate current range,  $B_F$  hardly depends on the emitter current for the temperature range of  $-40$  °C to  $160$  °C, for both  $0.7$ -μm CMOS and  $0.5$ -μm CMOS. Figure 3.10 shows that: a) the common-emitter current gain of the vertical bipolar transistors fabricated in CMOS technology is much lower than that of those fabricated in bipolar technology; b) the common-emitter current gain of the transistors fabricated in  $0.5$ -μm CMOS technology is much lower than that of those fabricated in  $0.7$ -μm CMOS technology.

In the moderate current range, the forward common-emitter current gain  $B_F$  is determined with the emitter efficiency  $\gamma$  and the transfer factor  $\alpha_T$ , which are determined by [3.6]:

$$\gamma \approx \frac{1}{1 + \frac{D_E}{D_B} \cdot \frac{n_{eo}}{p_{no}} \cdot \frac{W_B}{L_E}} = \frac{1}{1 + \frac{D_E}{D_B} \cdot \frac{n_{ie}^2}{n_{ib}^2} \cdot \frac{N_B}{N_E} \cdot \frac{W_B}{L_E}}, \quad (3.14)$$

$$\alpha_T \approx 1 - \frac{W_B^2}{2L_p^2}, \quad (3.15)$$

where  $D_E$  = the diffusion coefficient at the emitter,

$D_B$  = the diffusion coefficient at the base,

$N_E$  = the impurity concentration at the emitter,

$N_B$  = the impurity concentration at the base,

$W_B$  = the base thickness,

$L_E$  = the diffusion length at the emitter, and

$L_p$  = the diffusion length at the base.

The forward common-emitter current gain can be approximated by the equation:

$$B_F = \frac{\alpha_T \gamma}{1 - \alpha_T \gamma} \approx \frac{1 - \frac{W_B^2}{2L_p^2}}{\frac{W_B^2}{2L_p^2} + \frac{D_E}{D_B} \cdot \frac{n_{ie}^2}{n_{ib}^2} \cdot \frac{N_B}{N_E} \cdot \frac{W_B}{L_E}}. \quad (3.16)$$

A possible reason to explain the low value of  $B_F$  is the big value of  $W_B$  in CMOS technology. As a parasitic device, the base thickness of a pnp vertical bipolar transistor is the space between the bottom of a p+ region and the bottom of the n-well. This space is much larger than that of bipolar transistors fabricated in bipolar technology, where the process is designed to optimize the parameters of the bipolar transistors. This fact explains why the forward common-emitter current gain  $B_F$  of the vertical bipolar transistors fabricated in CMOS technology is much lower than that of transistors in bipolar technology. This also explains why the vertical bipolar transistors fabricated in CMOS technology have much larger forward early voltages ( $V_{ar} = 170$  V for  $0.7$ -μm CMOS and  $V_{ar} = 95$  V for  $0.5$ -μm CMOS).

For smaller size of CMOS process, it requires heavier doping or implant concentrations and thus the thinner well and smaller depletion thickness. The heavier doping concentrations result in smaller diffusion lengths. The combination of all these effects results in a lower common-emitter current gain in  $0.5$ -μm CMOS than in  $0.7$ -μm CMOS.

As shown in Figure 3.10, the forward common-emitter current gain  $B_F$  decreases at low current levels and at high current levels. At low current levels, this is due to the generation-recombination current in the emitter-base depletion region, which is added to the base current,

resulting in the decrease of  $B_F$ . At high current levels, the decrease of  $B_F$  is caused by the high injection effect, where the injected minority-carrier density in the base tends to approach the impurity concentration  $N_B$ . In other words: the injected carriers effectively increase the base doping, which in turn cause the emitter efficiency to decrease.

Figure 3.11 The temperature dependency of the current gain for (a) 0.7- $\mu\text{m}$  CMOS, and (b) 0.5- $\mu\text{m}$  CMOS.

The temperature dependence of  $B_F$  is plotted in Figure 3.11. Both items in equation (3.16) are temperature dependent. If the contribution of the term  $W^2/(2L_P^2)$  is neglected, the current gain can be simplified to:

$$B_F = \frac{D_B}{D_E} \cdot \frac{n_{iB}^2}{n_{iE}^2} \cdot \frac{N_E}{N_B} \cdot \frac{L_E}{W_B} = \frac{D_B}{D_E} \cdot \frac{N_E}{N_B} \cdot \frac{L_E}{W_B} \cdot \exp \frac{q(V_{gE} - V_{gB})}{k\vartheta} = \frac{D_B}{D_E} \cdot \frac{N_E}{N_B} \cdot \frac{L_E}{W_B} \cdot \exp \frac{q\Delta V_g}{k\vartheta} \quad (3.17)$$

where  $V_{gE}$  = bandgap voltage of the emitter,

$V_{gB}$  = bandgap voltage of the base.

The bandgap narrowing of the emitter due to the heavy doping concentration has been derived from the measured temperature dependence of the forward common-emitter current gain, while the temperature dependencies of the diffusion coefficients were neglected. It was found that  $\Delta V_g \approx -55$  mV for 0.7- $\mu\text{m}$  CMOS and  $\Delta V_g \approx -45$  mV for 0.5- $\mu\text{m}$  CMOS.

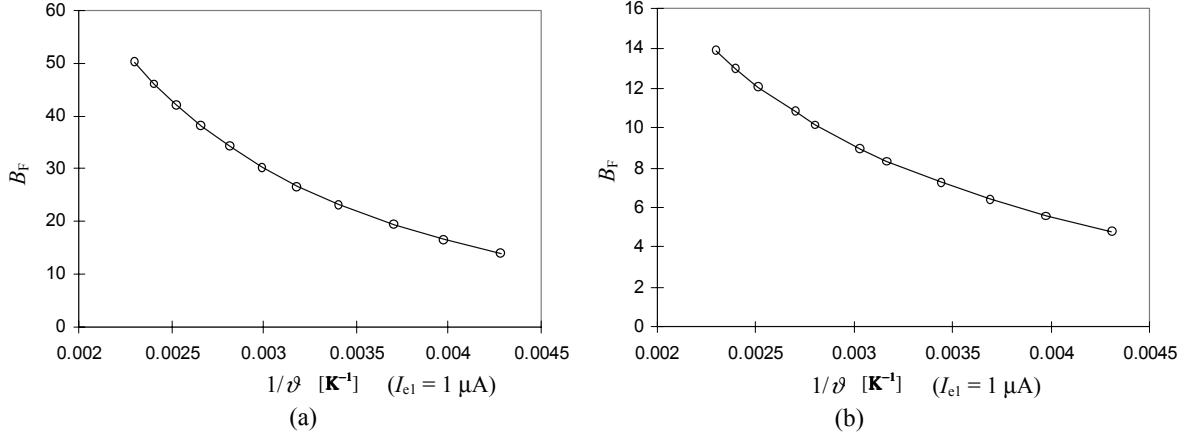

### 3.3.6 Base Resistances $R_B$

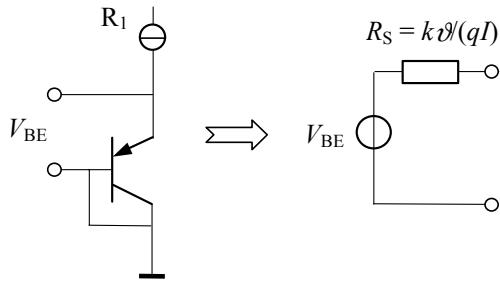

The series base resistances and the emitter resistances also contribute to the base-emitter voltage, as seen in Figure 3.12. Thus the base-emitter voltage becomes

$$V_{BE} = \frac{mk\vartheta}{q} \cdot \ln \frac{I_C}{I_S} + I_B R_B + I_E R_E, \quad (3.18)$$

Figure 3.12 The base and the emitter resistances contribute to the base-emitter voltage  $V_{BE}$ .

If the effects caused by the base resistance and the emitter resistance are taken into account, the voltage  $\Delta V_{BE}$  becomes:

$$\Delta V_{BE} = \frac{mk\vartheta}{q} \cdot \ln r + \Delta I_B [R_B + (B_F + 1)R_E]. \quad (3.19)$$

Due to the fact that the emitter resistance is much lower than the base resistance, and to the fact that the common-emitter current gain is also low, the contribution of the emitter resistance to the voltage  $\Delta V_{BE}$  can be neglected, thus:

$$\Delta V_{BE} \cong \frac{mk\vartheta}{q} \cdot \ln r + \Delta I_B \cdot R_B = \frac{k\vartheta}{q} \cdot \left[ m + \frac{(r-1)}{(B_F + 1) \frac{k\vartheta}{q} \ln r} I_{E1} R_B \right] \ln r, \quad (3.20)$$

where  $m$  is the effective emission coefficient,  $r$  the emitter current ratio  $I_{E2}/I_{E1}$ ,  $B_F$  the forward current gain and  $R_B$  the base resistance.

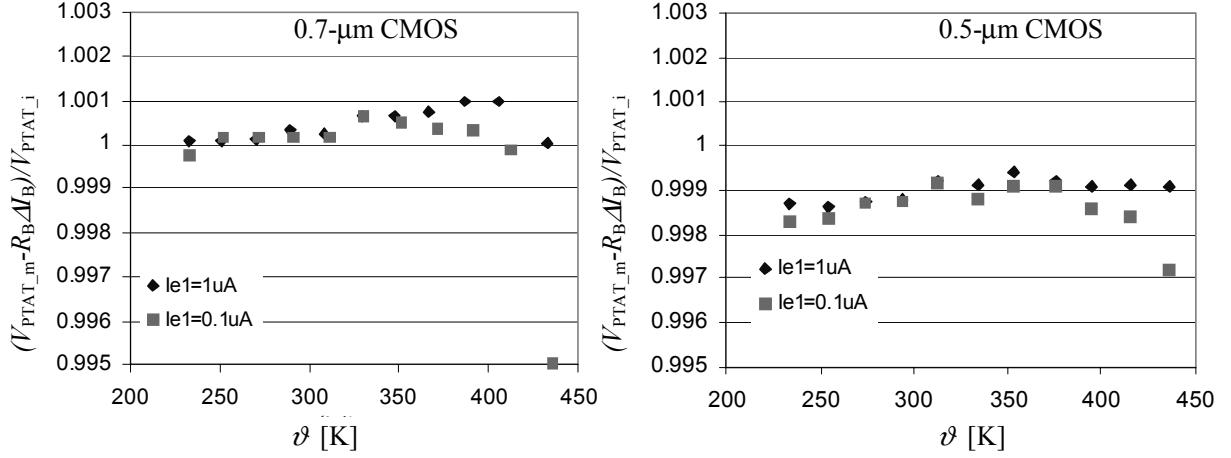

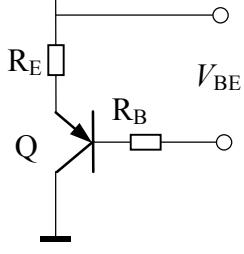

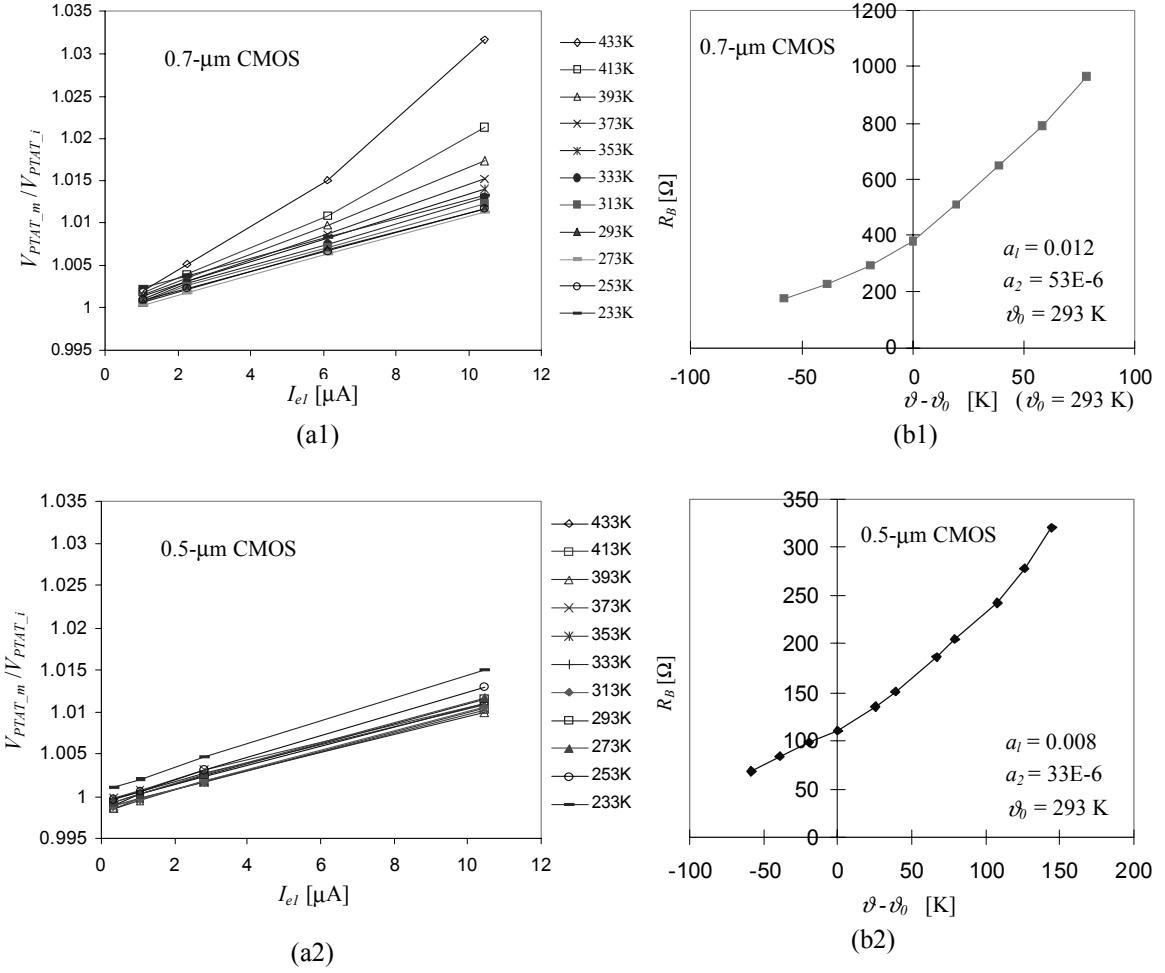

Figure 3.13(a) shows the normalized measured  $\Delta V_{BE}$  versus  $I_{E1}$ . The slope  $\theta$  of the curves is

$$\theta = \frac{r-1}{(B_F + 1) \frac{k\vartheta}{q} \ln r} [R_B + (B_F + 1)R_E]. \quad (3.21)$$

Neglecting the effect of emitter resistance, equation (3.21) can be rewritten as

$$R_B = \frac{\theta (B_F + 1) \frac{k\vartheta}{q} \ln r}{(r-1)}. \quad (3.22)$$

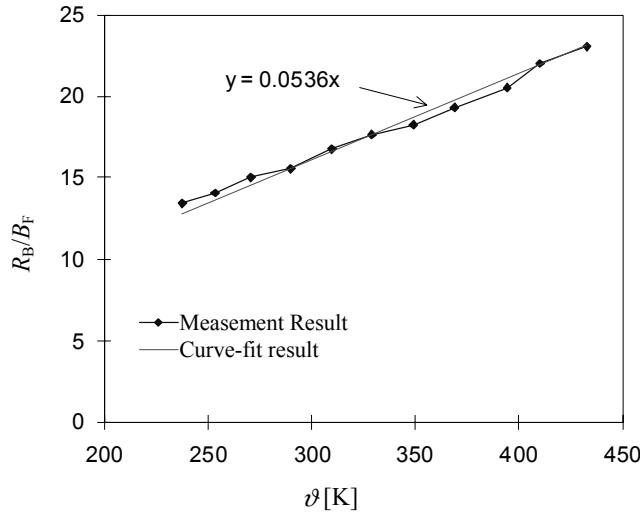

From the measurement results of  $\vartheta$ ,  $B_F$  and  $r$ , we can derive the base resistance  $R_B$  for different temperatures. The results are shown in Figure 3.13(b). At higher temperatures ( $\vartheta > 373$  K), for 0.7- $\mu\text{m}$  CMOS, the high injection effect already occurs at relatively low currents, so that the correct base resistance cannot be extracted (see Figure 3.13(a1)).

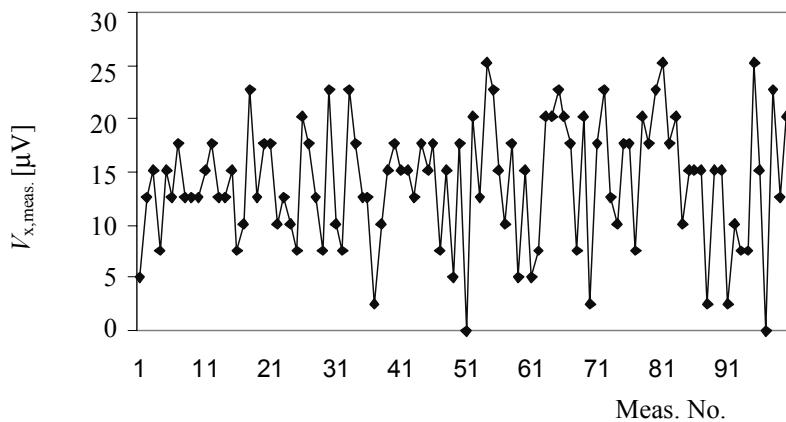

Figure 3.13 (a) the measured normalized  $\Delta V_{BE}$  voltage, and (b) the extracted  $R_B$  versus temperature for devices with an emitter area of  $10\mu\text{m} \times 20\mu\text{m}$ .