# **The Optimum Driving Method of Super E-paper**

The technical research complementing R:eFlex's businessplan

Amit Gupta Miki Trifunovic

# The Optimum Driving Method of Super E-paper

The technical research complementing R:eFlex's businessplan

### **Bachelor of Science Thesis**

In

**Electrical Engineering**

**Delft 2010**

Authors:

Amit Gupta - 1384201 Miki Trifunovic - 1354787

Professor:

Dr. R. Ishihara

Tutor:

Dr. J. Derakhshandeh

Electrical Engineering

Faculty of Electrical Engineering, Mathematics, and Computer Science

Delft University of Technology

The Netherlands

Photo on the cover by M. Trifunovic

#### **Preface**

This thesis is written with regards to the bachelor graduation project on the optimization of the Super E-paper, conducted in the 3<sup>rd</sup> and final year of Bachelor in Electrical Engineering at Delft University of Technology. During the research the optimum characteristics for the Super E-paper had to be found, by testing the Super E-paper under various conditions. To achieve this, various steps have been taken from study in theory to designing the supplying voltage circuit for the measurements.

For our research we made a schedule of requirements that are reflected on in every chapter. During our research, some difficulty has occurred which will be described in this thesis. Most of them are avoided, some were inevitable.

With the continuous environmental awareness rising globally, researchers from all over the world are looking for alternatives in order to do one's bit to contribute to a better environment. As result of this, researchers from the TU Delft are currently developing a technology that can replace all ordinary papers by one single device: Super E-paper.

Those who are interested in reading about the market analysis of our product are advised to read the first part of this report (chapters 2 and 3). The ones interested in the technology behind the Super E-paper and technical research conducted on this Super E-paper, are advised to start reading from part 2 onwards (chapters 4 to 9).

We would like convey our special gratitude to the following persons for their useful contributions.

- Dr. R. Ishihara (TU Delft), for his overall support and guidance throughout the project

- J. Derakhshandeh Kheljani (TU Delft), for his support and guidance with respect to all the measurements conducted in DIMES

- Wei Man Chim (Master graduate from TU Delft), for his master thesis on flexible E-paper and his support

- P. J. F. Swart (Electronic components, technology and materials), for the tutorial of how to use the different measurement machines.

- N. Saputra, (TU Delft), for his support with regards to the level shifter

- A. Baiano, (TU Delft), for his PhD thesis on Single Grain TFTs

- D. Tajari Mofrad (TU Delft), for his explanation of the Excimer Laser process and support

- J. Hoekstra, T. Slats, M. Schumacher for their support by providing the equipment and materials for the circuits we've built.

Amit Gupta & Miki Trifunovic Delft, 28 May 2010

# **CONTENTS**

| Pre | eface                                                 | ii                         |

|-----|-------------------------------------------------------|----------------------------|

| Lis | t of Figures                                          | .v                         |

| Αb  | Introductions                                         |                            |

| Su  | mmary                                                 | ix                         |

| 1.  | Introduction                                          | 1                          |

| РΑ  | RT I: Market Research                                 |                            |

| 2.  | •                                                     |                            |

|     | ·                                                     |                            |

|     |                                                       |                            |

|     | · ·                                                   |                            |

|     | • •                                                   | V   Viii   ix   ix   1   1 |

| 3.  | Schedule of requirements                              | 4                          |

| •   |                                                       | -                          |

| PA  | RT II: Technical research                             |                            |

| 4.  |                                                       |                            |

|     |                                                       |                            |

|     | •••                                                   |                            |

|     | · · · · · · · · · · · · · · · · · · ·                 |                            |

|     |                                                       |                            |

|     | · · · · · · · · · · · · · · · · · · ·                 |                            |

|     | ·                                                     |                            |

|     |                                                       |                            |

|     |                                                       |                            |

|     | 4.3. Summary                                          | . 12                       |

| 5.  | Measurements on the Single Grain Thin-Film Transistor | .13                        |

|     | 5.1. Measurement parameter descriptions               | .13                        |

|     | 5.2. Measurement 1: SG-TFT characteristics            | . 15                       |

|     | ·                                                     |                            |

|     | 5.4. Measurement 3: SOI characteristics               | 19                         |

|     | 5.5. Conclusion                                       | .21                        |

| 6.  | Level shifter: Supply for the E-paper                 | 22                         |

|     |                                                       |                            |

|     | 6.1.1. Circuit Analysis                               |                            |

|     | 6.1.2. Problem encountered: overloading               |                            |

|     | 6.2. Level shifter 2: Protective resistors added                             | 24 |

|-----|------------------------------------------------------------------------------|----|

|     | 6.2.1. Circuit Design                                                        | 24 |

|     | 6.2.2. Problem encountered: maximum PMOS gate-source voltage                 | 25 |

|     | 6.3. Level shifter 3: Breakdown Vgs avoided                                  | 26 |

|     | 6.3.1. Circuit Analysis                                                      | 26 |

|     | 6.4. Conclusion                                                              | 27 |

| 7.  | Active Matrix Measurements with Bridgestone's E-paper                        | 28 |

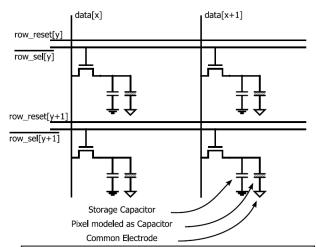

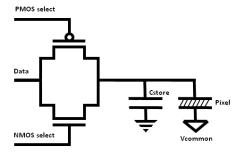

|     | 7.1. Active Matrix addressing                                                | 28 |

|     | 7.2. Layout of the wafer                                                     | 28 |

|     | 7.3. Measurement analysis and discussion                                     | 31 |

|     | 7.3.1. Measurements 1: Finding the matrix of pixels that are driven          | 32 |

|     | 7.3.2. Measurements 2: Activating a vertical array of pixels with data lines | 33 |

|     | 7.3.3. Measurements 3: Use microscopic changes for research                  | 33 |

|     | 7.4. Conclusion                                                              | 37 |

| 8.  | Passive Matrix Measurement with Bridgestone's E-paper                        | 39 |

|     | 8.1. Passive Matrix addressing                                               | 39 |

|     | 8.2. Printing an image on flexible E-paper                                   | 39 |

|     | 8.3. Conclusion                                                              | 42 |

| 9.  | Conclusions and recommendations                                              | 43 |

| Bik | oliography                                                                   | 45 |

| Аp  | pendices                                                                     | 46 |

| •   | Appendix 1: Id-Vd Measurement results of SG-TFT                              |    |

|     | Appendix 2: Id-Vd Measurement results of p-TFT                               |    |

|     | Appendix 3: Id-Vd Measurement results of SOI transistors                     |    |

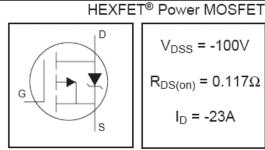

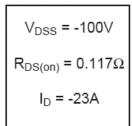

|     | Appendix 4: IRF540 Datasheet                                                 |    |

|     | Appendix 5: IRF9540 Datasheet                                                |    |

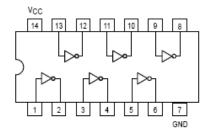

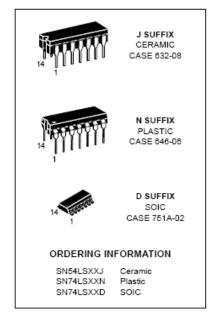

|     | Appendix 6: 74LS04 HEX inverter Datasheet                                    | 51 |

|     | Appendix 7:Measuring Devices                                                 |    |

|     | Appendix 8: More images of changes in particles                              | 55 |

# List of Figures

| 4.1  | Different types of solids: amorphous silicon(a), polycrystalline           | _   |

|------|----------------------------------------------------------------------------|-----|

|      | silicon(b), and single crystalline silicon(c)[9]                           | 6   |

| 4.2  | μ-Czochralski process for the manufacturing of a single SG-TFT [6]         | 7   |

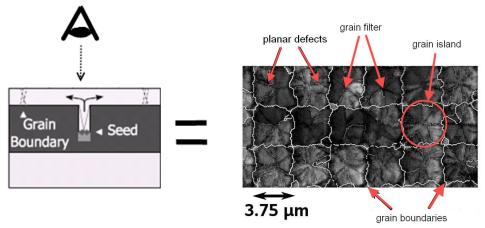

| 4.3  | Microscopic view of the grid of grains, showing the planar defects,        |     |

|      | grain filter holes, grain islands and grain boundaries[8]                  | 8   |

| 4.4  | 3D inverter made from SG-TFT's, picture from transmission electrode        |     |

|      | microscope (TEM)[12]                                                       | 8   |

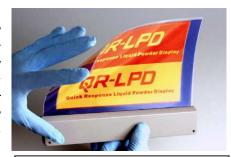

| 4.5  | QR-LPD developed by Bridgestone[13]                                        | 9   |

| 4.6  | The electric field causing movement in the Liquid-Powder particles [6]     | 9   |

| 4.7  | Hysteresis plot, reflectivity (pixel colour) versus applied voltage on     |     |

|      | the electrode. (HV stands for High Voltage and Vth for the Threshold       |     |

|      | Voltage)[6]                                                                | 10  |

| 4.8  | Display structure of the QR-LPD[6]                                         | 11  |

| 4.9  | E-ink technology displaying 3 pixels as capsules                           | 11  |

| 4.10 | A drop of oil positioned on the surface of water, in (a) no voltage is     |     |

|      | applied in the oil through the electrode, in (b) voltage is applied an     |     |

|      | oil becomes gradually hydrophilic.[16]                                     | 11  |

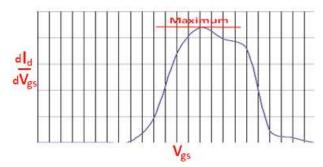

| 5.1  | Computing mobility from the $dI_D$ - $dV_{GS}$ graph of an NMOS transistor | 14  |

| 5.2  | Sample NMOS transistor IDVG curve for subtheshold voltage swing            |     |

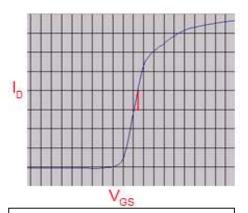

|      | computation, ID is logarithmically scaled                                  | 14  |

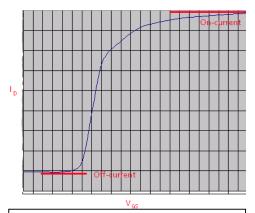

| 5.3  | Sample NMOS transistor IDVG curve for off- and on-current                  |     |

|      | computation, ID is logarithmically scaled                                  | 14  |

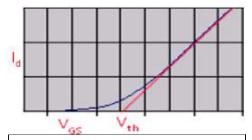

| 5.4  | Sample IDVG curve for NMOS threshold voltage computation, both             |     |

|      | ID and VG are linearly scaled                                              | 15  |

| 5.5  | sample NMOS $I_D$ - $V_{DS}$ curve with different gate-source voltages     | 15  |

| 5.6  | PMOS SG-TFT on the wafer under the microscope                              | 15  |

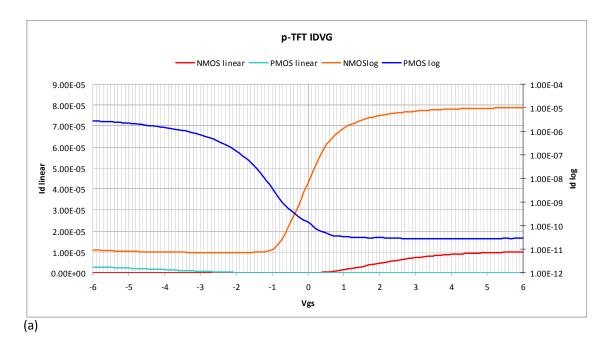

| 5.7  | Linear and logarithmic scaled IDVG graphs for both NMOS and PMOS           |     |

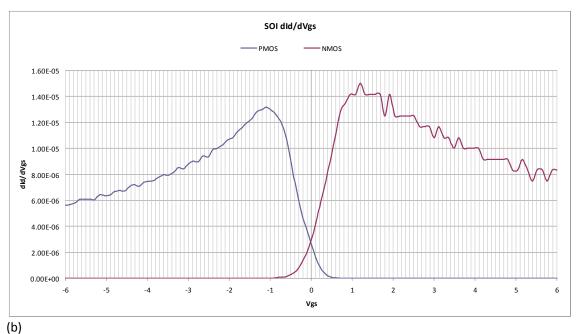

|      | SG-TFT's in (a). SG-TFT dId/dVgs curves for PMOS and NMOS in (b)           | 16  |

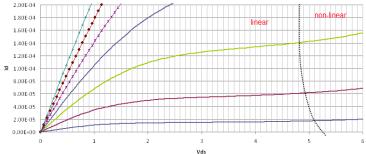

| 5.8  | NMOS SG-TFT IDVD curve showing non-linear region for high Vds              | 17  |

| 5.9  | Linear and logarithmic scaled IDVG graphs for both NMOS and PMOS           | 1,  |

| 3.3  | p-TFT's in (a). p-TFT dld/dVgs curves for PMOS and NMOS in (b)             | 18  |

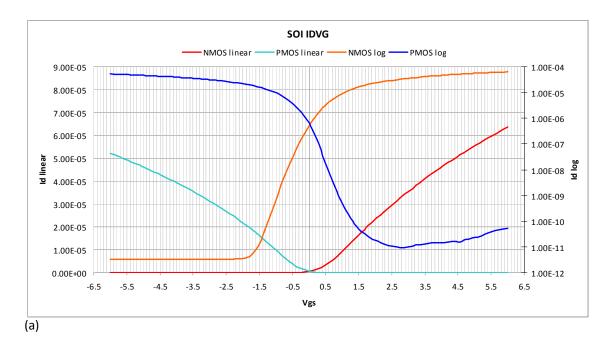

| 5.10 | Linear and logarithmic scaled IDVG graphs for both NMOS and PMOS           | 10  |

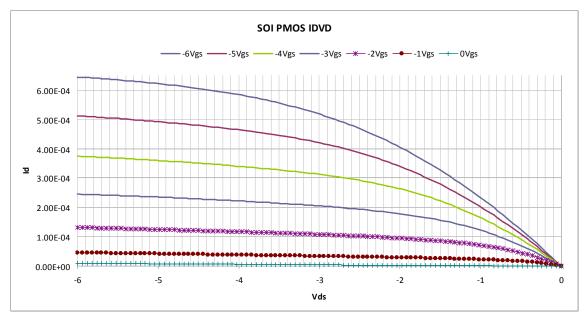

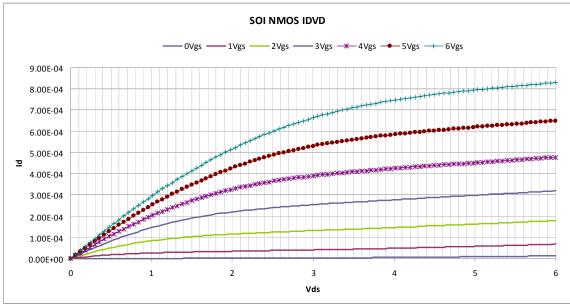

| 3.10 | SOI transistors in (a). SOI dld/dVgs curves for PMOS and NMOS in (b)       | 20  |

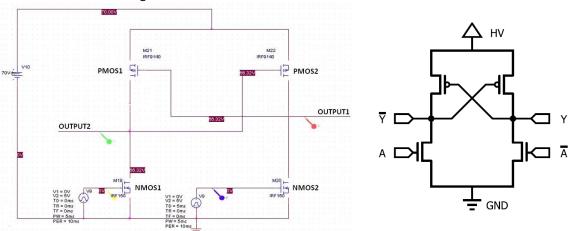

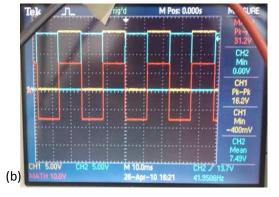

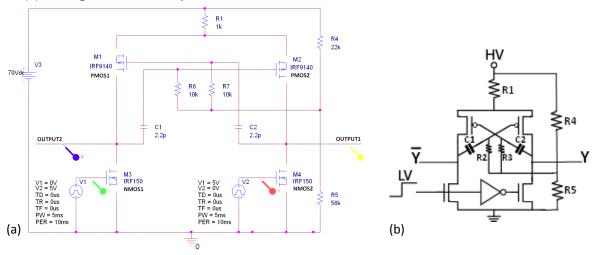

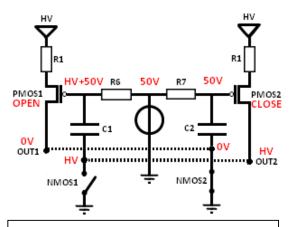

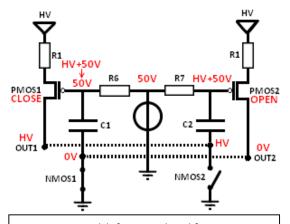

| 6.1  | Level shifter design number 1: basic level shifter circuit designed in     | 20  |

| 0.1  |                                                                            | 22  |

| 6.3  | PSpice in (a) and the basic modelling scheme in (b) [6]                    | 22  |

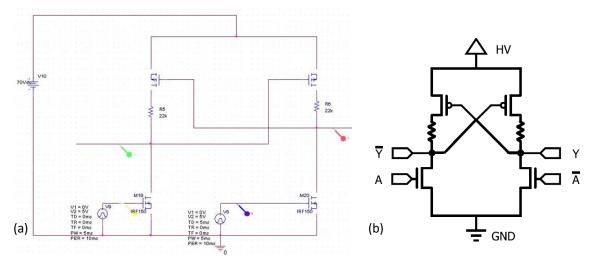

| 6.2  | Level shifter design number 2: resistors placed to prevent                 | 2.4 |

| c 2  | overloading, in PSpice in (a) and the basic modelling scheme in (b)        | 24  |

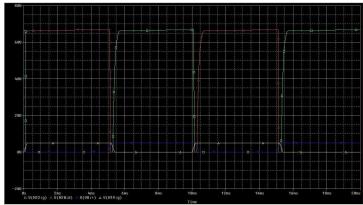

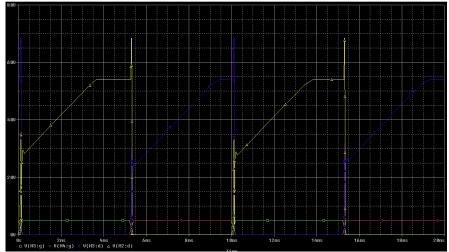

| 6.3  | Simulation result of level shifter design number 2                         | 25  |

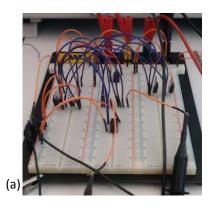

| 6.4  | Realization of our second level shifter circuit, showing the circuit       |     |

|      | built in (a), and the outputs on the oscilloscope screen in (b)            | 25  |

| 6.5  | Level shifter design circuit 3: avoiding high PMOS Vgs in PSpice in (a),   |     |

|      | and the original modelling scheme in of N. Saputra (b)                     | 26  |

| 6.6  | Simulation result of level shifter design number 3                         | 26  |

| 6.7  | Level shifter 3 analyzed from a different perspective, situation1:         |     |

|      | pulse1 = 0V, pulse2 = 5V, corresponding to NMOS switching                  | 27  |

| 6.8  | Level shifter 3 analyzed from a different perspective, situation2:         |     |

|      | pulse1 = 5V, pulse2 = 0V, corresponding to NMOS switching                  | 27  |

| 7.1  | Example of an active matrix addressing scheme with 4 pixels                | 28  |

| 7.2  | Circuit for driving a single pixel                                            | 28 |

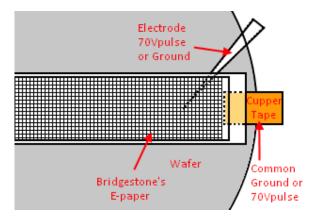

|------|-------------------------------------------------------------------------------|----|

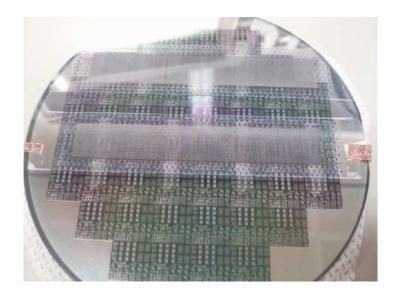

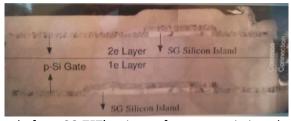

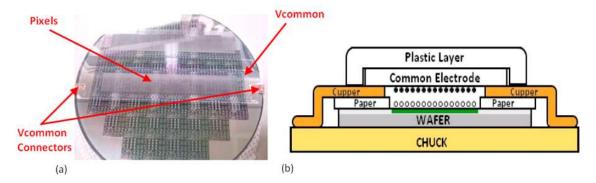

| 7.3  | Picture of the Super E-paper used for our research in (a) and a               |    |

|      | schematic cross-section sketch of the wafer with the different layers         |    |

|      | of material place on a chuck in (b)                                           | 29 |

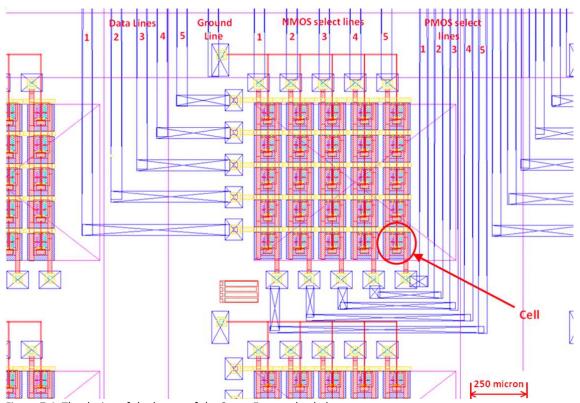

| 7.4  | The design of the layout of the Super E-paper backplane                       | 30 |

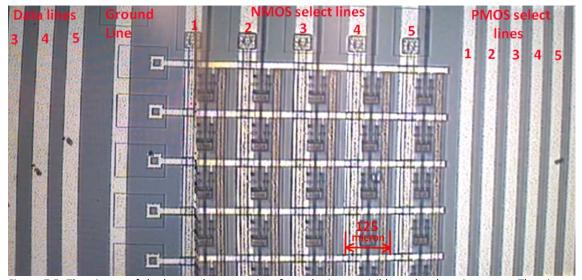

| 7.5  | The picture of the layout that was taken from the image visible               |    |

|      | under the microscope. The picture was taken on a matrix of cells              |    |

|      | that was situated above the pixel area                                        | 30 |

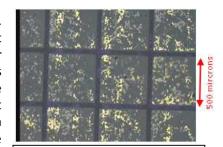

| 7.6  | Microscopic picture of the pixels of the Super E-paper                        | 31 |

| 7.7  | The measurement model of the connections between the machines                 |    |

|      | used                                                                          | 32 |

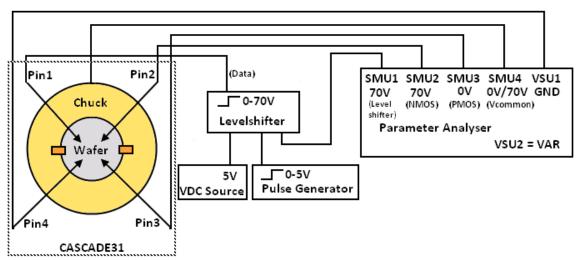

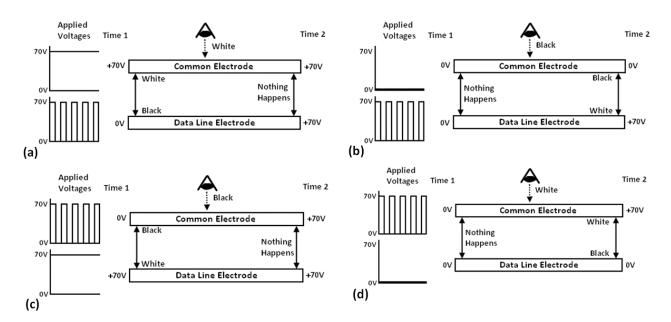

| 7.8  | Four different connection arrangements                                        | 34 |

| 7.9  | Example of typical transient                                                  | 34 |

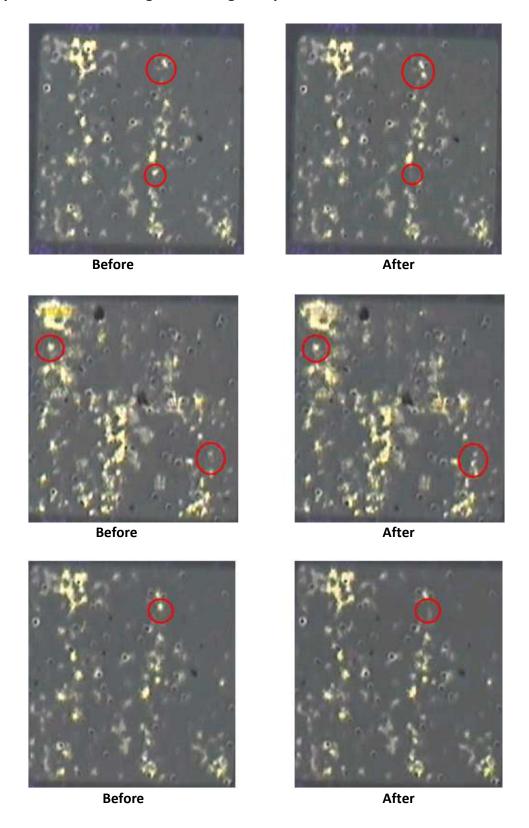

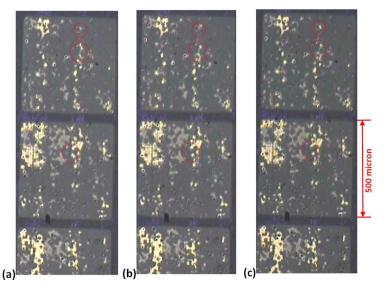

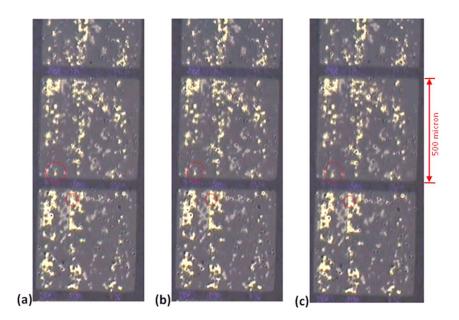

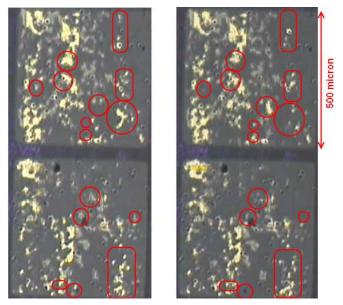

| 7.10 | changes observed in array of pixels during the multiple attempt test;         |    |

|      | from (a) to (b) the first attempt is observed, and from (b) to (c) the        |    |

|      | second                                                                        | 35 |

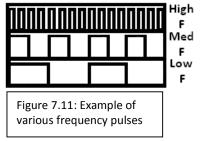

| 7.11 | Example of various frequency pulses                                           | 35 |

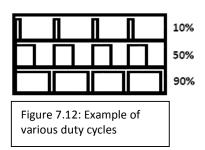

| 7.12 | Example of various duty cycles                                                | 35 |

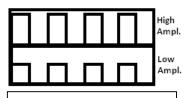

| 7.13 | Example of high and low amplitude pulses                                      | 36 |

| 7.14 | Array of pixels changing when voltage is applied from (a) to (b), and         |    |

|      | when voltage is switched off from (b) to (c)                                  | 37 |

| 7.15 | Change in pixels under the microscope, increased particle movement            |    |

|      | due to switching of the sources to the electrodes                             | 37 |

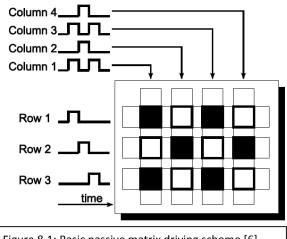

| 8.1  | Basic passive matrix driving scheme [6]                                       | 39 |

| 8.2  | Images in form of bears in (a) and swans and reindeers in (b) are cut         |    |

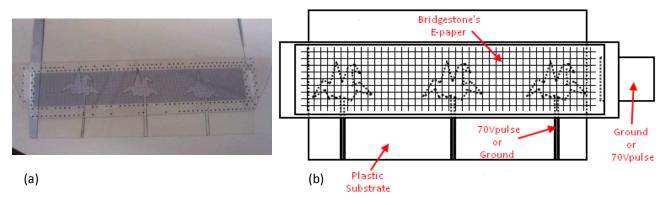

|      | on a thick aluminium foil                                                     | 40 |

| 8.3  | The plastic substrate with a layer of 300 nm aluminium shapes                 |    |

|      | deposited on top by electron beam evaporation                                 | 40 |

| 8.4  | Bridgestone's E-paper taken from the wafer and placed on top of the           |    |

|      | substrate                                                                     | 40 |

| 8.5  | The schematic for the 2 <sup>nd</sup> E-paper on the wafer with the aluminium |    |

|      | strip pushed inside                                                           | 42 |

#### **Abbreviations**

a-Si = Amorphous Silicon AC = Alternating Current c-Si = Single-Crystalline Silicon

DC = Direct Current

dld/dVgs = Derivative of the ld function to the gate-source voltage

E-paper = Electronic paper

Fa = Attraction Force

Fe = Electric field Force

Fq = Coulomb Force

Fv = Van der Waals Force

GND = Ground voltage or zero volts

HV = High Voltage

HV SG-TFT = High Voltage Single Grain Thin-Film Transistor

Ids or Id = Drain-Source Current

IDVD = Drain Current versus Drain Voltage IDVG = Drain Current versus Gate Voltage

ITO = Indium-Tin-Oxide LV = Low Voltage

MOSFET = Metal-Oxide-Semiconductor Field-Effect Transistor

NMOS = N-type Metal-Oxide-Semiconductor Field-Effect Transistor

p-Si = Poly-crystalline Silicon

p-TFT = Poly-crystalline Silicon Thin-Film Transistor

PMOS = P-type Metal-Oxide-Semiconductor Field-Effect Transistor

QR-LPD = Quick-Response Liquid-Powder Display

SG-TFT = Single-Grain Thin-Film Transistor

SMU = Source Monitoring Unit SOI = Silicon-On-Insulator TFT = Thin-Film Transistor

TU Delft = Delft University of Technology

U = Voltage

Vcommon = Voltage supplied to the common electrode

Vds or Vd = Drain-source Voltage

Vgs or Vg = Gate-source Voltage

Vstep = Voltage step size

VSU = Voltage Source Unit

Vth = Threshold Voltage

### Summary

#### Introduction

With the so many available sorts of E-paper, the optimal performing and consumer friendly E-paper needs to be found in order to win the E-paper market. As result of this, researchers from the TU Delft are currently developing a technology that can replace all ordinary papers by one single device, which has outperforming characteristics compared to the current E-papers: Super E-paper. In order to launch this superior product, a research needs to be conducted with regards to the optimum driving method of the Super E-paper. This thesis shall not only investigate what the optimum driving method of the Super E-paper is, by applying different types of power to the product. But also describe our steps towards this measurement by sharing background knowledge, linking theory to practice, designing the source that will be used for our Super E-paper measurements. For the measurements, several variables are analysed:

- · Voltage amplitude

- Frequency of the source (number of electric pulses sent to the Super E-paper)

- Duty cycle of the source (the percentage of high voltage within a period of an electric pulse)

#### Core

Through our market analysis a schedule of requirements of our product has been developed. These requirements are met through our technical research in every chapter. The most important requirements prove to be the flexibility of the Super E-paper and the wirelessly refreshable feature.

The Super E-paper is made up of two main technologies. The first technology is the Single Grain Thin-Film Transistor (SG-TFT) that is used for the back plane of our product. This transistor compared to other types of transistors is manufactured at low temperatures so that flexible plastics can be used to build the transistors on. This makes flexible electronics possible. The technology also makes it possible to stack transistors so that in the final product all electronics are integrated behind the display, for wireless interaction and an edgeless product.

The second technology is the Quick-Response Liquid-Powder Display (QR-LPD) technology that uses oppositely charged and coloured particles that are attracted and repulsed through appliance of voltage on the screen. This second technology is also flexible and faster than other front plane technologies and is therefore beneficial for the full flexibility of our final product and displaying motion pictures.

SG-TFT proved to be better than poly crystalline TFT's which has worse electrical properties due to the type of silicon used. The Silicon-on-insulator (SOI) transistors that we measured had worse characteristics than the SG-TFT transistors we measured, however theoretically the range of the SOI transistor's mobility should be higher than those of SG-TFT's. The performance of the SG-TFT and the low temperature process of manufacturing such a transistor make it ideal for the flexible Super E-paper.

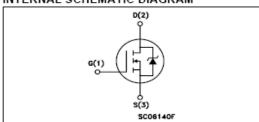

The prototype Super E-paper requires to be driven by a voltage of at least 35V. We made a level shifter that can send pulses of 70V for a better result. Three level shifters have been designed: the first and basic design had an overloading issue, so that in the second design we have placed a resistor to avoid this problem. This second design has been used for short periods of time for our measurements with the prototype when another error has been discovered. The third design avoids the problem of breakdown voltage on the PMOS transistors, and outputs gradual increasing pulses of higher than the threshold voltage.

Active Matrix addressing of our Super E-paper prototype proved to be difficult due to the bad visibility of the under laying design behind the pixels. Data lines that were available on the back plane

that were running under the pixels were used to activate the pixels which showed more movement within the pixels compared to previous research by A. Baiano and W. M. Chim. A remarkable condition has been discovered when applying voltages to both electrodes for the movement of the pixels, the pixels changed when both voltages were switched off.

During our Passive Matrix research, we used a flexible plastic substrate with metal shapes, made by electron beam evaporation, on which the QR-LPD has been pasted to model a flexible display. Effects of various types of voltages applied through the metallic shape have been analyzed.

#### Conclusion

The 70V pulse proved to have a better effect on the Super E-paper Display than the 70Vdc voltage. We also discovered the issue when applying a pulse to one electrode, and high voltage at the other. When switching off both voltages, the screen shows change because of the slight delay of shutting down of the pulse voltage.

It was clear that higher amplitude caused a bigger electric field which caused more movement in particles. Also when duty cycle was equal to 100% we may assume the source to be supplying a DC voltage and so we could say that the pulse voltage compared to the DC voltage had more effect on the particles in the pixels. We faced however some difficulties during our research so that a specific optimum frequency, amplitude, and duty cycle were hard to define. A list of difficulties in the order of importance follows:

- 1. lack of change in pixels when voltage applied;

- 2. no common reference point to be able to compare different situations;

- 3. no visibility of the colour of the grains under the microscope;

- 4. circuitry underneath the pixels was invisible and of incorrect size;

- 5. no plastic layer keeping the Liquid Powder at its place.

#### Recommendations

For future research we have a number of recommendations:

- 1. Use a new front plane that makes the underlying circuitry visible so that active matrix addressing can be checked accordingly.

- 2. This new front plane should have equal active matrix addressing cell size as pixel size.

- 3. Ask from Bridgestone a separate piece of E-paper front plane that can be used for passive matrix addressing.

- 4. Use a magnifying glass in stead of a microscope to see the movement of different coloured particles.

#### 1. Introduction

Electronic paper or E-paper is a display technology that mimics the appearance of ordinary ink on paper. While a conventional flat panel display, like LCD displays for example, uses a backlight to display its pixels, E-paper reflects light like any ordinary paper. The reading comfort of such E-paper therefore is exactly the same as ordinary paper making it possible for one to enjoy hours of reading on such a device without getting their eyes strained, like when looking at a conventional flat panel device. One single device can replace all the papers needed for books, newspapers, flyers etc. Besides a better space utilization and lighter transportation, the biggest advantage of this device is the fact that it contributes significantly to a better environment. Due to the utilised technology, the power consumption of the E-paper is also very low. With the rapidly advancing technology, researchers from the TU Delft now have managed to make a new type of E-paper also known as the Super E-paper. The Super E-paper has compared to the current E-paper: Full flexibility, a higher refresh rate so that animations can be played, full colour, and integrated drivers within the display that minimizes the edges around the display.

Super E-paper however, needs to be further developed before it can enter the display market. One of the researches required on the product is the optimum driving method. At this point the exact specifications on the best functioning conditions of the device are still unknown.

Research on these conditions is absolutely essential for the development of the product. Not only is this necessary for bringing the product to the market, but when further experiments and research need to be done with the product, one can greatly benefit from the information on the optimum driving methods.

The goal of our project is to investigate what the optimum driving method of the Super E-paper is by applying different types of power to the product.

We followed the following steps for our research on the Super E-paper. We have analyzed TU Delft's driving backplane, combined with the E-paper front plane from Bridgestone; together they form the Super E-paper. We will design a level shifter for supplying the product. In order to discover the optimum driving method, several conditions are analyzed:

- Voltage amplitude

- Frequency of the source (number of electric pulses sent to the Super E-paper)

- Duty cycle of the source (the percentage of high voltage within a period of an electric pulse)

Naturally, each phase of our research had some restrictions and requirements, these requirements will be first analysed and later met in every chapter. Changes in pixels are analyzed under the microscope and for a better analysis, these changes are filmed. The pixels are monitored carefully while triggering the pixels on the Super E-paper with different variables. However, noted changes are subjectively measured, since individual particle changes are impossible to be quantified. The rates at which pixels change rely therefore on the individual analyzing.

This report is divided into two parts. The first part provides intrinsic information about the market analysis and the second part gives the outcomes of our technical research. The market analysis starts in chapter 2. This chapter describes all the market participants for the applications of our product. The other chapter in this section (chapter 3), will provide a schedule of requirements.

Chapters 4-9 give outcomes of our technical research. Chapter 4 reveals in-depth information about the various technologies used in the Super E-paper based on our literature research. In the 5<sup>th</sup> chapter the results from the measurements on SG-TFT's are analysed. Chapter 6 provides information about the level shifter, which is designed to supply the E-paper with high voltage pulses. Bridgestone's E-paper measurements can be found in the 7<sup>th</sup> and 8<sup>th</sup> chapter, starting with Active Matrix addressing and afterwards Passive Matrix addressing. The conclusions and recommendations about the technical research can be found in the last chapter, chapter 9.

# PART I Market Research

## 2. Market analysis

The product that we are researching is new and is not yet introduced to the market. Expectations of how well the Super E-paper will do in the market can be analysed through its external environment [1]. This analysis gives an overview of all the players in the market in which the product is active. Through this analysis we can obtain the requirements and restrictions of our product. Our research however is searching for the optimum way to drive the product. In the next chapter we will give a schedule of the requirements of our technical research.

This chapter is divided into three sections, each explaining a different type of player in the market. Section 2.1 gives an overview of the customers and their requirements. Section 2.2 explains who the suppliers for the Super E-paper will be. Finally, the third section will give an overview of the competition in the Super E-paper market

#### 2.1 Customer requirements

The following section shall elaborate on the requirements of the main customers of our E-paper technology. These customers can be divided in three sectors; advertisement, newspaper and others. Subsection 2.1.1 shall be devoted for the advertisement branch. Subsection 2.1.2 shall provide information regarding the newspaper branch.

#### 2.1.1 Customer 1: Advertisement

In the Netherlands there are two main companies active with regards to advertising. The biggest of them is JCDecaux and the second largest is CBS Outdoor. Both of them are interviewed, to get a feeling on their view of the application of E-paper in this market sector. Here follows a brief summary about the requirements of the Super E-paper for these two players.

#### **JCDecaux**

From the interview with JCDecaux it became clear that replacing all the 2m<sup>2</sup> (bus stop size) spaces won't be cost effective, as the cost of paper posters is significantly lower than the costs of E-paper. However about 1,500 of the 2m<sup>2</sup> posters and all the larger posters of 8 m<sup>2</sup>, use a rotating system that allows JCDecaux to display multiple posters at an interval without manually having to change them. These systems are relatively expensive and replacing these with the E-paper can be a very lucrative investment. More detailed information about the interview can be read in the [2]

#### **CBS Outdoor**

CBS Outdoor (previously called Viacom Outdoor) a sub-division of the CBS Corporation is also one of the leading outdoor media companies globally. From the interview with CBS Outdoor, it became quite clear that CBS Outdoor sees the implementation of the E-paper in their advertisement business as an opportunity to set a stronger hold in this market section. The reason why CBS believes so is E-paper's ability to refresh advertisements using wireless transmission. This way the advertisements don't need to be manually changed, which in its way contributes to CBS Outdoors cost saving procedures. Therefore, they would like Super E-paper to have a lifecycle of at least 4 years after calculating the possible price of the product. The full interview can be read in [3]

#### 2.1.2 Customer 2: Newspaper

In the Netherlands, about 3.5 million people have a subscribed to a newspaper<sup>1</sup>. With such a large number of subscribers, successfully penetrating this market shall definitely give a boost to us. During the interviews with relatively large market players in this field, HDC Media and Het Financieel Dagblad, their interest in an e-newspaper as a substitute for the conventional paper version became clear. Here follows a brief summary about the requirements from the newspaper branch.

#### **HDC Media**

HDC Media was certainly interested in the Super E-paper, however was waiting for it to develop further. HDC Media is looking for a version of E-paper which has a price from approximately 150 euro's, flexibility of the display for the newspaper feeling, and they were looking for the possibility of displaying multiple pictures. Once the technology is this advanced, HDC Media hopes to deliver the news quickly and efficiently per region (city or neighbourhood). An option of bonus editions or updates, in case the customer pays extra, should also be integrated. They also hope that the option of viewing high resolute videos on the Super E-paper, should also be possible in the next version. The biggest advantage HDC Media sees from this product, apart from the cost cutting factors, is quickly updating its customers. They therefore hope to attract customers as they shall be providing a service keeping all its customers fully updated at all times and therefore making the midnight deadline obsolete. More detailed information about this all can be read in the [4]

#### **Het Financieel Dagblad**

Het Financieel Dagblad (FD) is a Dutch newspaper. As the internet is rapidly taking over the news-supplying-market, FD is having troubles keeping up with this digital world. In order to safeguard itself, the company therefore wants an innovative tool/idea to attract new customers. They said that they would like the Super E-paper to have a function of being a personalized product, which could adjust the news to the taste of the subscriber. By implementing this new technology, the company hopes to save costs, provide better service to the customers and hopes to attract new customers. The price of our product should range from 100 to 200 euro's. According to FD the two most important requirements for this product are: remaining up-to-date and adjusting to personal interests/requirements. The full interview can be read in [5]

#### 2.2 Suppliers

Super E-paper uses two main technologies that are supplied by Bridgestone and JSR. These technologies make it possible for the product to be flexible, however certain conditions naturally have to be met. Bridgestone supplies us with the Quick-Response Liquid Powder Display (QR-LPD) that can only be driven with at least 35 volts. JSR supplies us with liquid silicon that forms the basis of the driving circuit for Bridgestone's display. More information on the suppliers of our product can be found in [1]

#### 2.3 Competitors

Products competing with Super E-paper have an influence on product requirements, if our product would be much more expensive than the products of our competitors, the Super E-paper would be pushed out of the market. Besides the type of competitor that produces a similar product as ours, a different type would be is the substitute. Products such as plain paper, non E-paper displays or E-readers can be used for the same purpose as the Super E-paper. The extra features that we offer such as flexibility, motion on display, full colour, energy efficiency, should outperform the competing products. More information on the competitors of our product can be found in. [1]

# 3. Schedule of requirements

Product requirements can be derived from our market research, however in our technical research we will be focussing on the optimization of driving the product. Our product is relatively new and specific customer orientated requirement implementation is still difficult. Our thesis will however meet some of these requirements and at the end of chapter an evaluation, of the requirement that has been met through the corresponding research, shall be provided

#### **Super E-paper features**

Super E-paper has a number of features that it aims to achieve:

- 1. fully flexible display;

- 2. all drivers and electronics integrated in the display so that the final product will have minimum edges, together with feature 1, this would mean that the electronics are flexible as well;

- 3. full colour and animations possible;

- 4. wireless communication possible;

- 5. energy efficient.

These features make the product besides a useful replacement for current billboards and newspapers, possible to replace current price tags, E-readers, make clothing with animated pictures possible, and even flexible medical sensors are some of the many potential applications of the Super E-paper.

#### Requirements based on market research

The market stakeholders have a couple of requirements regarding what the product needs to be. These requirements are ordered, starting with the most important requirement first.

- [1.1] Super E-paper needs to be able to display multiple images with minimum effort (all customers indicated in section 2.1).

- [1.2] The product needs to be fully flexible since no other non E-paper displays or current E-readers have this ability (suppliers and competitors from chapter 2).

- [1.3] The same product should be wirelessly refreshable (all customers indicated in section 2.1).

- [1.4] Super E-paper must be cheaper than current LCD screens (advertising companies).

- [1.5] The newspaper variant of Super E-paper needs to be flexible to maintain a similar feeling to the current paper newspaper (newspaper customers from section 2.1).

- [1.6] The newspaper variant of the product needs to have a price of approximately 150 euro's (HDC Media and Het Financieel Dagblad).

- [1.7] The billboard variant of the product should have a lifecycle of at least 4 years (CBS Outdoor).

#### Requirements concerning the ecological and social situation

Here follows a list of requirements seen from the environmental, safety and social perspectives.

- [2.1] Product should meet internationally set product safety standards with regards to EM-radiation.

- [2.2] Product should meet internationally set product safety standards with regards to the health and safety of consumers using our product.

- [2.3] Product should meet internationally set product safety standards with regards to the hazardous materials that may spread when the product is damaged.

#### Requirements concerning the design of the product

Here follows a list of requirements with regards to the design of the product. This is categorized in three subsections: User interface requirements, Production requirements and Usage requirements and Recycling requirements.

#### User interface requirements

- [3.1.1] The Super E-paper should be easy to use through its interface.

- [3.1.2] The Super E-paper should be able to adapt to the user's personal preferences (text size, etc).

#### *Production and usage requirements*

- [3.2.1] With regards to the production of the Super E-paper, both the technologies  $\mu$ -Czochralski and QR-LPD shall be applied.

- [3.2.2] The production process of the Super E-paper shall be led by certified members only.

- [3.2.3] The production process should produce minimum harm to the environment

- [3.2.4] The display resolution should have a similar appearance as print on paper.

- [3.2.5] The product should be able to play animations.

#### Recycling requirements

- [3.3.1] Product should meet internationally set product recycling standards with regards to the materials used, which could be harmful for the environment once disposing or recycling.

- [3.3.2] Upon breaking the display, it should be able to be replaced by a new screen

#### Schedule of product requirements based on our technical research

For our research we analysed a prototype Super E-paper under the microscope and applied different types of voltages to drive the pixels. By varying a single parameter from the 70V pulse, for example, the frequency, the duty cycle or the amplitude, we can see at which values of these parameters the change in pixel colour is the greatest. Therefore our primary requirement is:

The pixel has to change more heavily for a value of the variable closer to the optimum parameter setting.

#### Related sub requirements would be:

- The difference in change of pixel between two different valued parameters should be great

enough to be able to assign the change of pixel to the change of value in the corresponding

parameter.

- A common reference situation should be realized to compare the change in value of the parameters under equal conditions.

When these requirements are met, the optimum driving method can be derived. Once the optimum driving method is concluded, research for meeting the other requirements in this chapter can be focussed on.

In this thesis we have divided our approach of testing the prototype into several sections that meet the requirements announced in this chapter. The requirements that need to be met are briefly explained in the introduction of every chapter, and evaluated at the end of every chapter.

Chapter 4: Technological background of Super E-paper

Requirement: The capabilities of the technologies used

Chapter 5: Measurements on the Single Grain Thin-Film Transistor

Requirement: The choice of SG-TFT over other transistors

Chapter 6: Level shifter: supply for the Super E-paper

Requirement: The required supply for driving the E-paper front plane

Chapter 7: Active Matrix Measurements on Bridgestone's E-paper

Requirement: Identifying the optimum parameters through the Active Matrix approach

Chapter 8: Passive Matrix Measurements on Bridgestone's E-paper

Requirement: Identifying the optimum parameters through the Passive Matrix approach

# PART II Technical Research

## 4. Technological background of Super E-paper

The Super E-paper uses two main technologies [6]. The first one is the Single Grain Thin-Film Transistor (SG-TFT) which is developed by TU Delft. The other one is the Quick Response Liquid Powder Display technology (QR-LPD) that is developed by the company Bridgestone. The two technologies are needed for the construction of Super E-paper: the SG-TFT is used for the integrated circuit backplane of the device and the QR-LPD is required for the E-paper front plane of the device.

In this chapter these technologies are explained. Section 4.1 describes the different types of transistors, the manufacturing process of a SG-TFT, and finally the resulting product. Section 4.2 explains the physics behind QR-LPD, and the structure that is used in the front plane of the Super E-paper. Section 4.3 is a summary of the discussed technologies with reflection on the schedule of requirements

#### 4.1 The Single Grain Thin-Film Transistor

This section will start with a brief background explanation of different materials used for transistors, and how this is important for the SG-TFT. The process and technique of manufacturing such a transistor is explained afterwards, and finally the advantages of such a transistor are discussed. The theory can be found in [6][7][8].

#### 4.1.1 Types of Transistors

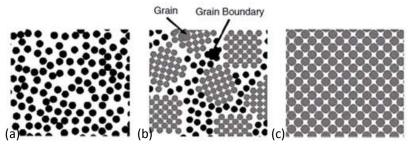

Transistors are made of different types of semi-conductor material. Amorphous silicon (a-Si), polycrystalline silicon (p-Si) and single crystalline silicon (c-Si) are some of the different types of silicon used to make a transistor. The types are characterized by the size of an ordered region within the material. Ordered regions in this sense are spatial volumes in which atoms or molecules have regular geometric periodicity. These ordered regions are also known as grains and are separated by grain boundaries when more grains are present in the material. A-Si has almost no order or ordered regions, p-Si does have ordered regions, but these vary in size and orientation with respect to each other, and c-Si has a high degree of order or regular geometric periodicity throughout the entire volume of the material as shown in Figure 4.1. Ordered materials have superior electrical characteristics to non-ordered materials and are therefore preferred [7].

Figure 4.1: Different types of solids: amorphous silicon (a), polycrystalline silicon (b), and single crystalline silicon(c). [9]

Thin-Film Transistors (TFT) are special types of MOS transistors, where a thin film of semiconducting material is deposited on a substrate like glass for example. However, since the silicon must be deposited, only a-Si or p-Si materials can be used, which ultimately results in a lower electrical performance than single crystalline versions of MOS transistors. The c-Si transistors are made from c-Si wafers that are grown from a single seed so that the wafer as a whole consists of a single grain.

There is however a way to greatly improve an a-Si TFT so that the electrical properties will become comparable to the c-Si transistor. This process is also known as the  $\mu$ -Czochralski process and uses a special way to fabricate high performance TFT's at a relatively low temperature of 100°C [10]

#### 4.1.2 The Manufacturing Process of a SG-TFT

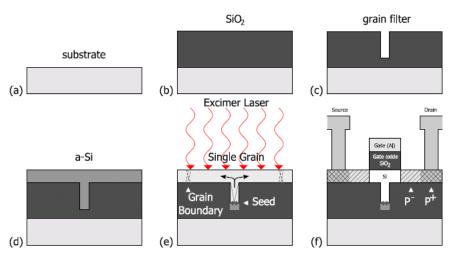

The  $\mu$ -Czochralski process is used to locate single grains from amorphous silicon and let it grow as a seed to single grain islands so that TFT's can be built within this single grain island. This greatly improves the electrical performance TFT since there are no grain boundaries within the TFT that degrades its performance. The process of making one single grain is illustrated in Figure 4.2. and explained in the following steps:

<u>Step 1</u>: A substrate is chosen, since the  $\mu$ -Czochralski process works with relatively low temperatures (350°C compared to over a thousand degrees Celsius for a regular transistor), we can use plastic as a substrate as well. (Figure 4.2(a))

<u>Step 2</u>: A layer of the insulating material silicon dioxide ( $SiO_2$ ) is deposited on top of the substrate. (Figure 4.2(b))

Step 3: Holes are made in the  $SiO_2$  by using a grain filter. This grain filter patterns a grid of cavities over the whole layer of  $SiO_2$ . (Figure 4.2(c))

<u>Step 4</u>: A layer of a-Si is deposited on top. This layer covers the whole area and fills up all the holes made by the grain filter. (Figure 4.2(d))

<u>Step 5</u>: Excimer Laser is used to melt the top part of the a-Si layer, leaving a non-molten a-Si crystal at the bottom of the hole. This crystal will serve as the seed that grows into a single grain island on top of the SiO<sub>2</sub> layer. Excimer Laser is used because this laser type can remove very thin layers of surface material with almost no effect to the rest of the material. (Figure 4.2(e))

<u>Step 6</u>: Within every grain phosphorus or boron is implanted to form NMOS SG-TFT and PMOS SG-TFT respectively. (Figure 4.2(f))

Figure 4.2:  $\mu$ -Czochralski process for the manufacturing of a single SG-TFT: starting with a substrate (a), with a layer of SiO<sub>2</sub> deposited on top (b). Then by using a grain filter, a hole in the SiO<sub>2</sub> is made(c) which gets filled by the deposition of a-Si (d). Excimer Laser melts the top layer leaving a seed at the bottom of the hole (e). Finally we have a transistor (f). [6]

Since TFT's are made within a single grain island, the grain boundary limitations are not an issue anymore and the electrical properties are greatly improved. However, the TFT's do have minor planar defects as shown in Figure 4.3. These planar defects have a far less negative effect on the electrical properties compared to the effects of grain boundaries.

Figure 4.3: Microscopic view of the grid of grains, showing the planar defects, grain filter holes, grain islands and grain boundaries. [8]

As we will discuss in section 5.2, Bridgestone's E-paper front plane requires a supply voltage of 70V. An SG-TFT that we described in the previous section would break down at these voltages; breakdown voltage is about 6V. Therefore, an extra processing step is needed. A thicker gate oxide and a change in doping profile are needed. This High Voltage SG-TFT (HV SG-TFT) can handle the 70V supply voltage but is slower in return. A combination of both the fast but fragile SG-TFT and the strong but slow HV SG-TFT is needed for driving at high speeds and low voltages, and change pixels on the screen respectively.

#### 4.1.3 The SG-TFT features

The SG-TFT technology offers the possibility of 3D-integrated circuits and flexible electronics[11]. 3D-Integration of integrated circuits (IC's) is now possible because the transistors can be stacked. The stacking is made possible by the use of Excimer Laser technology, which doesn't penetrate through multiple layers of transistors, but only a very thin layer as shown in Figure 4.2(e). This stacking of electronics would mean for the Super E-paper that all of its electronics can be integrated behind the display. In Figure 4.4 this feature is used with an inverter.

The development of flexible electronics is also a positive feature for the Super E-paper. This flexibility is made possible due to the relatively low temperature manufacturing process (100°C). Due to this low temperature, every type of flexible plastic can be used as a substrate for flexible electronics.

Figure 4.4: 3D inverter made from SG-TFT's, picture from transmission electrode microscope (TEM) [12]

#### 4.2 The Quick-Response Liquid Powder Display

While Bridgestone's core business is tire production, they have managed to be the first to develop a new Electronic Liquid Powder suitable for making E-paper Displays. They managed to achieve this by using the high-level materials design and processing technology cultivated through their tire business. The E-paper Displays using this highly advanced technology are also known as QR-LPD (Quick-Response Liquid Powder Display).

A paper like appearance, low power consumption, high resolution, an excellent image stability, quick response, and clear threshold characteristics are the ideal

Figure 4.5: QR-LPD developed by Bridgestone [13]

characteristics which make the QR-LPD the ideal technology for the E-paper displays. The theory discussed in this section can be found in [6] [11]

Subsection 4.2.1 will describe the properties of Bridgestone's newly made Liquid-Powder and shall also describe the forces which are acted on the particles and in subsection 4.2.2 the structure of the QR-LPD is explained. Finally, in section 4.2.3 other types of E-paper are discussed briefly.

#### 4.2.1 Properties of the QR-LPD

E-paper is a type of display technology that has similar characteristics to paper. It doesn't require backlight since it simply reflects light as plain paper does. It is also very thin, light and doesn't consume energy while displaying a static image. Through electronics the display can be updated.

The Electric Liquid Powder developed by Bridgestone for the QR-LPD, is an electrical sensitive powder which combines the properties of a liquid and powder. Because of this combination, the material despite having a powder form, still behaves like a liquid; making the material highly fluid and easily suspended, where every single particle reacts to the electric field.

Bridgestone has developed two types of powders: a negatively charged white coloured powder and a positively charged blacked coloured powder that are placed between two electrodes. One of the electrodes is made of Indium-Tin-Oxide (ITO) which is both conductive as well as optically transparent. Once a negative voltage is applied over an electrode, the black particles get attracted to this electrode and once a positive voltage is applied the white particles will. More detailed explanation can be found in section 4.2.2. Observing this, we can conclude that the Liquid-Powder moves when subjected to an electric field. Figure 4.5 shows the forces implied on the powder particles.

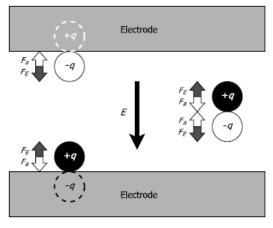

Figure 4.6: The electric field causing movement in the Liquid-Powder particles [6]

#### Forces applied in the QR-LPD

The particles in the figure are given two sorts of colours; the positively charged black particle and the negatively charged white particle. As the charges of the particles are intrinsic to themselves, external frictions to obtain those charges are not required. Basically, there are three forces applied on the particles; the attraction force Fa, the image charge force and the electric field force Fe. The attraction force Fa is the force which attracts the positive and negative particles to each other. This attractive force consists of two forces; the Coulomb force Fq and the Van der Waals force Fv. Everywhere in the cell this attractive force is of the same magnitude, but only at the surface of the electrode an additional force acts upon the particles. This force is called the image charge force and arises due to the polarization of the electrode by the charged particles. Due to this polarization the charged particle is kept at its position on the electrode even when the electric field is removed. In other words, these attractive and repulsive forces between the particles and the electrodes make it possible to retain an image on the display without any power consumption; a black image when the electric field is removed after applying negative voltage to the electrode, and a white image when the electric field is removed after positive voltage. This feature makes the QR-LPD bistable.

Once voltage is applied on the electrodes, the electric field that arises acts as a repulsive force to the pair of oppositely charged particles. This electrical field shall therefore separate the oppositely charged particles from each other, once the electric field force Fe is larger than the attractive force Fa. If so, the particles move to the electrode of the opposite charge with respect to their own charge. A similar principle holds for separating the particles from the electrode.

#### **Gradual change of colours**

While the particles travel from one electrode to the other, the particles reach high speeds. It has been reported that the particle transfer speed was over 11.11m/sec (about 40 km/hour), the pixel response time will result in 0.2ms from black to white and the other way around which gives the display the capability of showing animations [8][11].

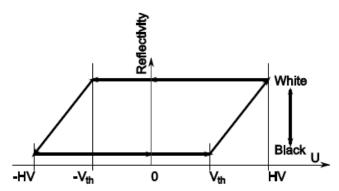

Below in Figure 4.7 the hysteresis plot can be found. This hysteresis plot explains the reflectivity of the particles when different voltages are applied. As can be seen from the plot, once the pixel has a colour, for example black, when a voltage higher than the threshold voltage Vth is applied, the electrode will gradually turn white as more and more white particles are attracted, and black particles are repulsed. Once polarization of the electrode occurs, the pixel will remain in that colour even when the electric field is switched off so the applied voltage is 0V. The pixel will change to the opposite colour again once the negative threshold is reached (-Vth). The QR-LPD requires relatively high driving voltage of 70V and the voltage required to overcome the attractive force is the threshold voltage which is about 35V. The voltage potentials between 35V and 70V are interesting for grey-scale levels. The higher the voltage above the threshold, the more the particles get attracted by the electrode. This causes different grey scale levels for different voltages between 35V and 70V.

Figure 4.7: Hysteresis plot, reflectivity (pixel colour) versus applied voltage on the electrode. (HV stands for High Voltage and Vth for the Threshold Voltage)[6]

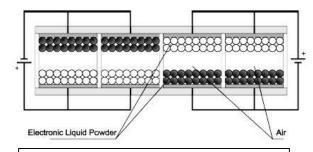

#### 4.2.2 Structure of a QR-LPD

In Figure 4.8 the structure of the QR-LPD is shown. This figure shows four cells only. As we have stated before: each cell contains two types of powder; a white coloured negatively charged powder and a black coloured positively charged powder. As both powders are of opposite charge, the two are attracted to each other forming a grey mass. As soon as the top electrode has a different voltage with respect to the bottom electrode, the particles will arrange at

Figure 4.8: Display structure of the QR-LPD [6]

the oppositely charged electrode. When looking at the top electrode, the arrangement of a single particle type is visible, while the other type of particles is attracted by the other electrode and therefore can not be seen. However these particles attracted by the lower electrode, can be seen again once the opposite voltage is applied.

In the cell, the remaining space is filled by plain air, which is also the transport medium and free space for the moving powder particles. The speed of the particles through the air is high enough to give a response time of 0.2ms.[6]

#### 4.2.3 Other types of E-paper

Besides Bridgestone's E-paper that uses charged particles and cells filled with air and driven by electrodes, there are various other technologies that are also recognized as E-paper. Since they also have a paper like appearance, we will discuss two important types briefly.

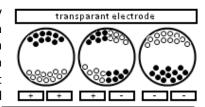

#### E-ink

E-Ink is a spin-off from the American MIT Media Lab. The technology uses microcapsules with charged particles and a transparent fluid in them [15]. These particles are attracted and repulsed by applying a voltage between two electrodes that keep the microcapsules in between them. In this sense, this technology is similar to the one that Bridgestone uses, however, Bridgestone uses air in stead of the liquid that make the movement of the particles faster, and also uses cells in stead of capsules, so that no space in between the capsules is wasted.

Figure 4.9: E-ink technology displaying 3 pixels as capsules

#### Electrowetting

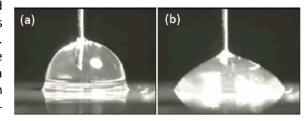

Electrowetting is a technology that uses dark oil and water. By applying a voltage, the oil becomes increasingly hydrophilic rather than hydrophobic. Figure 4.10 shows two images of an applied voltage on oil, on a surface of water. When the oil covers a larger surface area, the screen turns black. When otherwise, the light gets reflected through the oilless area, and white can be observed. The display will consist of cells with water and oil trapped within each cell. An electrode is used to shape the oil so that either the screen absorbs light or reflects light, causing the black and white colours.

Figure 4.10: A drop of oil positioned on the surface of water, in (a) no voltage is applied in the oil through the electrode, in (b) voltage is applied an oil becomes gradually hydrophilic. [16]

#### 4.3 Summary

In this section, the two main technologies used for making the Super E-paper are analysed. The first technology forms the driving back plane of the Super E-paper which is Single Grain Thin-Film Transistor (SG-TFT) technology. The second technology discussed, forms the Super E-paper front plane that is produced by Bridgestone: the Quick-Response Liquid-Powder Display (QR-LPD) technology.

#### SG-TFT

There are three basic types of silicon used for making a transistor: Amorphous Silicon (a-Si), Polycrystalline Silicon (p-Si), and Single Crystalline Silicon (c-Si). The types are ordered in size of regular geometric periodicity within the material, where a-Si has least geometric periodicity throughout the material, and c-Si the most. The more geometric periodicity, the less the material has grain boundaries which results in better the electric performance.

Thin-Film Transistors (TFT) are made from a-Si, p-Si and c-Si. The c-Si transistors are manufactured at high temperatures, therefore a-Si or p-Si transistors have to be used. However the  $\mu$ -Czochralski process makes it possible to make high quality TFT's at low temperatures (<100°C), which makes it suitable to use plastic substrates, from a-Si or p-Si transistors. The process builds TFT's onto single grain islands that are grown, which avoids the grain boundary influence and results in a TFT quality close to c-Si. The SG-TFT's can be used for flexible electronics, and stacking of the electronics.

#### QR-LPD

The QR-LPD developed by Bridgestone essentially uses two types of particles: white negatively charged particles and black positively charged particles. These particles are placed between two electrodes which attract or repulse the types of particles. One of the electrodes is made of Indium-Tin-Oxide (ITO) that is both conductive and optically transparent. Within the QR-LPD, various forces are applied. The particles attract each other through Coulomb force and Van der Waals force. Once an electric field is applied between the electrodes, the particles will be pulled apart. As soon as the particle touches the electrode, the electrode gets polarized and keeps attracting the particle even after switching off the electric field. This results in no energy consumption when holding a certain image on the display. The screen therefore has a hysteresis effect that changes the colour of the image after crossing opposing threshold voltages. The particles are contained in cells with air as a medium that can individually be addressed as pixels.

Besides QR-LPD, there are two other commonly used E-paper front plane techniques. The first technique is E-ink, which uses microcapsules that contain the same charged particles with a fluid medium; the idea is similar to the QR-LPD. The second technique is Electrowetting which uses the hydrophilic and hydrophobic characteristics of oil when voltage is applied to an electrode. The oil absorbs the light and changes shape within a cell to let light reflect from the other electrode.

#### Schedule of requirements

Both technologies give an answer to some of the product requirements. SG-TFT makes it possible to use a flexible substrate for achieving flexible electronics. It also has the feature of the possibility of stacking transistors, which is beneficial for the requirement of having an edgeless final product, since all electronics can be integrated behind the display of the Super E-paper.

The QR-LPD is also flexible, so the combination of this technology with SG-TFT makes a fully flexible product possible. The technology also serves the requirement of minimum energy consumption since it doesn't use power when holding a certain image on the display. QR-LPD uses air as a medium in stead of a fluid in E-ink, which results in higher speeds and therefore higher refresh rates. This property of reaching higher speeds, makes animations on the display possible.

# 5. Measurements on the Single Grain Thin-Film Transistor

In chapter 4 we have discussed about using the Single Grain TFT technology in Super E-paper. In this chapter we will analyze the quality of this type of transistor by measuring the  $I_D$ - $V_{GS}$  curve. This curve can provide information of the transistors such as the sub threshold voltage swing, the leak current, the on-current, the threshold voltage, the mobility of the transistor, and the current and voltage characteristics of the transistor when different gate voltages are applied. Ultimately we want to compare the SG-TFT with different transistors to obtain a better knowledge of the quality of such a transistor.

In section 5.1 we will define the different parameters that we will analyze by means of a sample NMOS curve and explain their meaning. Following this section, first the SG-TFT parameters are identified in section 5.2, after which it is compared to the p-TFT. These transistors being both TFT's, can prove to us the higher quality of the SG-TFT. Section 5.3 and 5.4 will compare the SG-TFT characteristics to silicon-on-insulator (SOI). Finally, in section 5.5, a conclusion will be given on the quality of the SG-TFT.

#### 5.1 Measurement parameter descriptions

Comparing transistors is done by analyzing the  $I_D$ - $V_{GS}$  curve. From this curve important parameters can be obtained which can be used to compare different transistors. The examples in the following descriptions are used with regards to NMOS transistors. PMOS transistors have a similar but mirrored image in the y-axis. Formula's and ways of finding the various parameters were provided by J. Derakhshandeh and [17]

#### Mobility

The mobility of a transistor, describes the average drift velocity of a carrier due to an electric field, which is expressed as cm²/Vs and has the symbol  $\mu$ . When one transistor has a higher mobility than the other, this transistor will usually be of higher quality since the mobility determines the speed of the transistor. This parameter can be calculated from the formula for the drain current, when the transistor is in the linear region. We will use for every measurement minimum  $V_{ds}$  which is low enough for the transistor to be in the linear region.

$$I_{d} = \mu \cdot C_{OX} \cdot \frac{W}{L} \left( V_{GS} - V_{th} - \frac{V_{ds}}{2} \right) V_{ds}$$

(5.1)

$$C_{OX} = \frac{\varepsilon_{OX}}{t_{OY}} \tag{5.2}$$

Where  $I_d$  is the drain current,  $C_{O\!X}$  is the oxide capacitance which is inversely proportional to the thickness of the gate oxide  $t_{O\!X}$ . The oxide permittivity ( $\varepsilon_{O\!X}$ ) is equal to 3.5e-11 F/m [17]. W and L are the width and length of the depletion region of the transistor respectively.  $V_{G\!S}$  is the gate voltage with respect to the source, and  $V_{th}$  is the threshold voltage. Finally,  $V_{d\!S}$  is the drain voltage with respect to the source. We take the differential of  $I_d$  with respect to  $V_{G\!S}$  to obtain the function:

$$\frac{dI_d}{dV_{GS}} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot V_{ds}$$

(5.3)

This function shows that from the  $I_D$ - $V_{GS}$ , graph, we need to differentiate it to  $V_{GS}$ , and obtain its maximum to get the maximum mobility of the transistor. Figure 5.1 shows the differential graph of  $I_D$ - $V_{GS}$  of a sample NMOS transistor.

Figure 5.1: Computing mobility from the  $dI_D$ - $dV_{GS}$  graph of an NMOS transistor.

By using formula 5.3, the mobility can be computed by filling in the maximum value obtained from the derivative graph: dld/dVgs. The mobility can then be obtained by:

$$\mu = \frac{dI_d}{dV_{GS}} \cdot \frac{1}{C_{OX} \cdot V_{dS}} \cdot \frac{L}{W}$$

(5.4)

#### Subthreshold voltage swing

Figure 5.2 shows an example of deriving the subthreshold voltage swing S from the  $I_D$ - $V_{GS}$  curve. When a transistor is switched on, a voltage at the gate is applied crossing the threshold voltage. The speed at which it turns on when crossing this threshold voltage is important to the quality of a transistor. A low subthreshold swing accounts for a fast transition from the off-current to the on-current. Optimally the transistor is off when voltage is applied at the gate that is under the threshold voltage, and on when the voltage goes above the threshold voltage. Notice that we use the logarithmic y-axis for easier computation. From the  $I_D$ - $V_{GS}$  curve we can easily compute the S in terms of mV/dec. So the voltage needed to increase the current by a factor 10. An ideal transistor has a swing of 60mV/dec [6].

Figure 5.2: Sample NMOS IDVG curve for subthreshold voltage swing computation, Id is logarithmically scaled

#### **Off-Current**

It is important to know how much current is "leaking" when the gate-source voltage is under the threshold voltage. A transistor is better if it has a low leak current/off-current. This current is defined as the minimum current in the  $I_D$ - $V_{GS}$  curve, as you can see in Figure 5.3. Again the y-axis is logarithmically scaled.

#### **On-Current**

How much current is running through the transistor when it is switched on? There has to be a significant difference between on-current and off-current. This ratio would also describe in a lesser sense the speed of the transistor. To obtain this current we take the current level of the transistor that is switched on and saturated when taking the logarithmically scaled y-axis. In Figure 5.3 we also show the on-current of the sample transistor.

Figure 5.3: Sample NMOS transistor IDVG curve for off- and on-current computation, ID is logarithmically scaled

#### **Threshold Voltage**

This parameter defines at what gate voltage the transistor is switched on and off. Preferably this voltage would be between 0V and 1V for an NMOS and between -1V and 0V for a PMOS, so that low gate to source voltages can drive the transistor. To compute this parameter, we need again the  $I_D$ - $V_{GS}$  curve, but this time the  $I_D$ -axis needs to be in a linear scale. We use the extension of the increasing line through the x-axis to compute the threshold voltage, as shown in Figure 5.4 for a sample NMOS transistor.

#### I<sub>D</sub>-V<sub>DS</sub> Curves

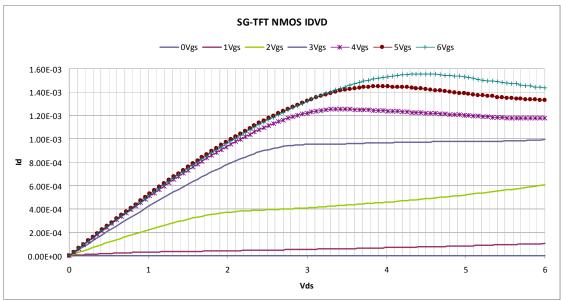

Different gate voltages cause different  $I_D$ - $V_{DS}$  characteristics. It is important to know how the  $I_D$ - $V_{DS}$  curve changes for different gate voltages. Increased gate voltages usually cause an increased saturation linear region. One would have to take care which formula to use for the drain current for a particular gate voltage. Figure 5.5 shows an example of such a curve for an NMOS transistor. For PMOS transistors the curves are in the fourth quadrant with similar shapes but mirrored in the vertical and horizontal axis. For our measurements regarding the IDVG curve, we take a Vds of 0.02V to stay in the linear region of the transistor for every Vgs.

These curves have been appended for every type of transistor for our measurements. The curves are obtained

Figure 5.4: Sample IDVG curve for NMOS threshold voltage computation, both ID and VG are linearly scaled

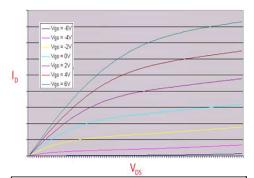

Figure 5.5: sample NMOS  $I_D$ - $V_{DS}$  curve with different gate-source voltages

from transistors with short channel lengths which explains why they don't saturate to a constant Id value for high Vds [17].

#### 5.2 Measurement 1: SG-TFT characteristics

In this section we will take a close look at the results of our SG-TFT measurements. The measurements we did with other transistors will come in sections 5.3 and 5.4, since we first need to know what to take as a reference. The SG-TFT is also used in Super E-paper and it is therefore very important to gain a better knowledge of the product. We used a Vds of 0.02V

The particular group of SG-TFT's that we used for our measurements has the following characteristics:

- a gate oxide thickness ( $t_{OX}$ ) of 27nm,

- made with tetra-ethyl-ortho-silicate (TEOS);

- has 250 nm of silicon thickness.

- channel width is 4μm, and length is 2μm.

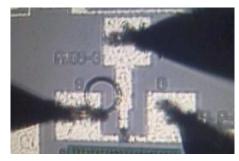

Figure 5.6: layout of the PMOS SG-TFT on the wafer under the microscope

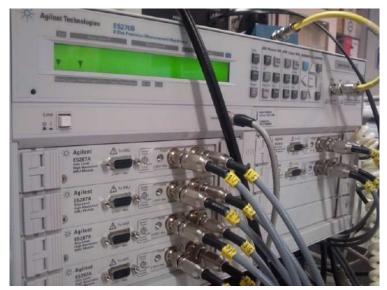

For our measurements we used CAS34 with an 8-slot precision measurement mainframe. These machines can be viewed in Appendix 7. The layout of the transistor under the microscope is observed in Figure 5.6. The source and drains are symmetrical and can be used one way or the other during our measurements. The black areas in the figure are the Source Monitoring Unit (SMU) pins, which are used for measurement purposes. The top pin touches the gate of the transistor, whereas the other two are touching the source and drain. We expect the mobility of this transistor to be around 600 cm²/Vs [10]

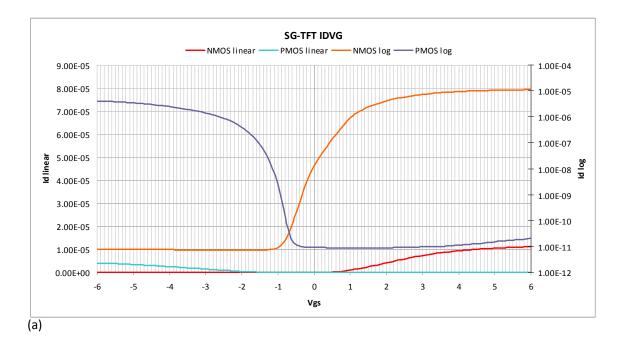

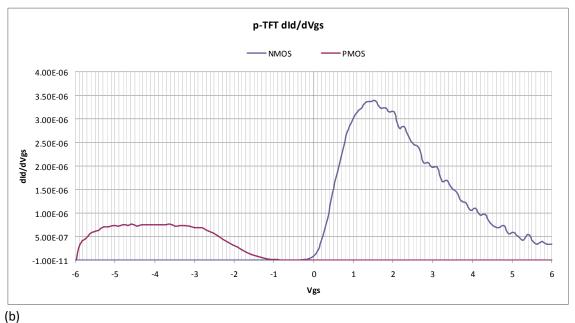

Figure 5.7: Linear and logarithmic scaled IDVG graphs for both NMOS and PMOS SG-TFT's in (a). SG-TFT dId/dVgs curves for PMOS and NMOS in (b).

Table 5.1: SG-TFT NMOS and PMOS characteristics.

| Transistor type | Mobility (μ)            | Subtheshold | Off-current | On-current | Threshold |

|-----------------|-------------------------|-------------|-------------|------------|-----------|

|                 |                         | Swing (S)   |             |            | Voltage   |

| NMOS            | 694 cm <sup>2</sup> /Vs | 360 mV/dec  | 7.3e-12 A   | 1.1e-05 A  | 0.8V      |

| PMOS            | 216 cm <sup>2</sup> /Vs | 480 mV/dec  | 9.0e-12 A   | 4.0e-6 A   | -1.7V     |

#### Id-Vas

Figure 5.7(a) shows the results of our Id-Vgs measurements on the SG-TFT's. We introduced a Vds of 0.02V to measure the transistor in the linear region. 101 Voltage steps have been taken between -6V and 6V equally separated by 0.12V each. The red and orange lines from Figure 5.7(a) are both the results of the NMOS Id-Vgs measurement. The orange line is scaled logarithmically on the y axis positioned on the right side of the graph. The red line is scaled linearly on the y-axis positioned on the left side of the graph. The dark blue line and light blue line are both the measurement results of the PMOS Id-Vgs measurement and are logarithmically and linearly scaled respectively. From this graph the subthreshold voltage swing, the off- and on-current and threshold voltage can be derived in the ways described in section 5.1. The results are shown in table 5.1.

#### dld/dVgs

For the mobility, a separate graph has to be made. As function 5.4 describes, the derivative function of the Id-Vgs graph with respect to Vgs has to be made. This derivative graph is shown in Figure 5.7(b). From this graph the maximum values of dId/dVgs for the NMOS SG-TFT (3.6e-6) and PMOS SG-TFT (1.12e-6) can be obtained. These maximums are used in function 5.4 to finally obtain the mobility of the SG-TFT transistors.

#### Discussion on the obtained parameters

Remarkably the PMOS threshold voltage is less than -1V, which means that this particular SG-TFT needed more doping to shift this level to between -1V and 0V. Also, it is clear that the NMOS transistor is of a higher quality than the PMOS transistor. This can be seen from the much higher mobility, and the higher ratio of on- versus off-current.

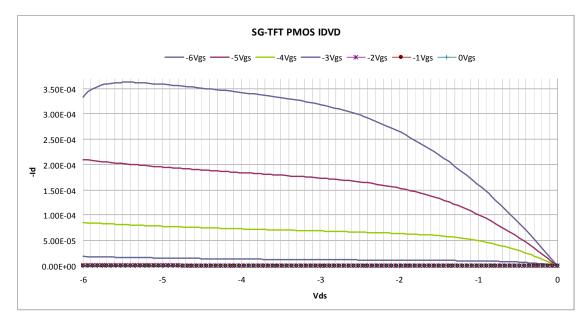

During our Id-Vg measurements, Id-Vd measurements have been done as well, and these can be seen in Appendices 1 to 3. For the parameters that we are focusing on, these graphs aren't very important. Both Id-Vd curves however, show in the higher Vds voltages a non linear behaviour; as can be seen in Figure 5.8 for the lower Vgs voltages. This behaviour is due to the thickness of the silicon layer which is 250nm.

Figure 5.8: NMOS SG-TFT IDVD curve showing non-linear region for high Vds.

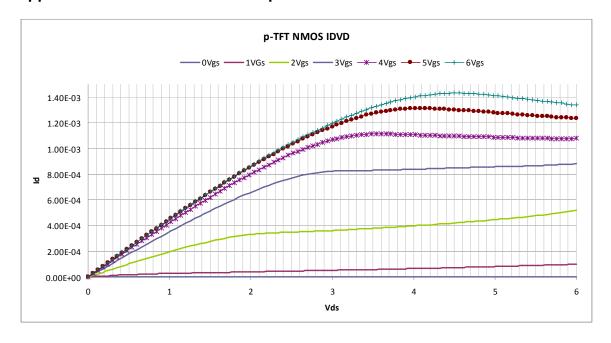

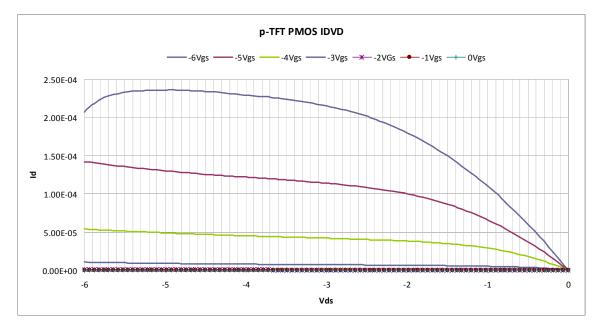

#### 5.3 Measurement 2: p-Si TFT characteristics

In chapter 4 we have already explained that traditional TFT's are from a-Si or p-Si because the silicon has to be deposited. We used a Vds of 0.2V. Since these transistors have negative influence by the grain boundaries, we should see worse transistor characteristics than the SG-TFT's. The layout of the device on the wafer we used is the same as the SG-TFT layout. We expect the p-TFT to have a mobility up to 100 cm²/Vs [10]. The particular p-TFT we used for these measurements had the following characteristics:

- a gate oxide thickness (t<sub>OX</sub>) of 27nm;

- manufactured with TEOS;

- has 250 nm of silicon thickness;

- channel width is 4μm, and length is 2μm.

Figure 5.9: Linear and logarithmic scaled IDVG graphs for both NMOS and PMOS p-TFT's in (a). p-TFT dId/dVgs curves for PMOS and NMOS in (b).

Table 5.2: p-TFT NMOS and PMOS characteristics.

| Transistor type | Mobility (μ)             | Subtheshold | Off-current | On-current | Threshold |

|-----------------|--------------------------|-------------|-------------|------------|-----------|

|                 |                          | Swing (S)   |             |            | Voltage   |

| NMOS            | 65.6 cm <sup>2</sup> /Vs | 300 mV/dec  | 7.3e-12     | 1.0e-5 A   | 0.6V      |

| PMOS            | 14.8 cm <sup>2</sup> /Vs | 600 mV/dec  | 2.7e-11     | 2.7e-6 A   | -2V       |

#### Id-Vas

The Id-Vgs graph looks similar to the SG-TFT Id-Vgs. This can be observed from Figure 5.9(a). Especially the NMOS curves look alike, however, the PMOS curves of the p-TFT looks wider than the SG-TFT PMOS which could mean that the mobility and swing are worse than the SG-TFT PMOS. Again the same colours have been used for the types of transistor graphs: orange and red describe the NMOS transistor on logarithmic and linear scale respectively, and the dark blue and light blue curves describe the PMOS transistor also on logarithmic and linear scale respectively. The linear curves are kept on the same scale to compare the Id-Vgs graphs of the transistors on the same scale.

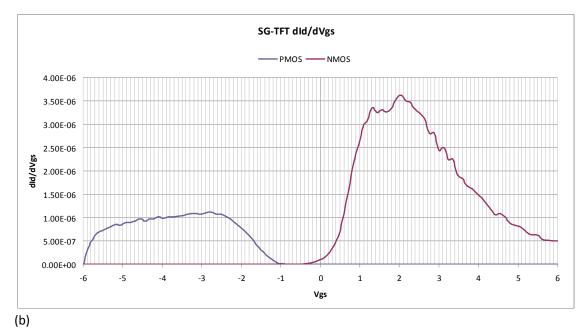

#### dId/dVqs

The dId/dVgs curves, shown in Figure 5.9(b), compared to the SG-TFT version of the curves look also very similar. Both of them however have a bit lower maximum than the SG-TFT transistors. The maximum value for the NMOS transistor is 3.4e-6, and for the PMOS transistor it's 7.7e-7.

#### Discussion on the obtained parameters

Table 5.2 represent the parameter values of the p-TFT transistors obtained from the Id-Vgs graph. These parameters are compared to the SG-TFT parameters from table 5.1. In the sense of speed of the transistors, the SG-TFT's are much faster and therefore of higher quality than the p-TFT's when focused only on the NMOS transistors. This is due to the lower Vds which will alter the function value. The on- off-current ratios of the NMOS transistors from both types are very similar.

The PMOS transistors of the p-TFT are of much poorer quality compared to the SG-TFT PMOS. The mobility is again much higher in the SG-TFT PMOS. The subthreshold voltage swing is much higher for the p-TFT PMOS which means that the transition from off to on-current and vice versa is much slower than the SG-TFT. The on- off-current ratio for the PMOS is much higher for the SG-TFT type than the p-TFT type. Threshold voltages are similar to the SG-TFT's where the PMOS transistors of both types of transistors are just outside the -1V to -V range.

#### 5.4 Measurement 3: SOI characteristics

Silicon-on-insulator (SOI) transistors are high quality single grain transistors. This can therefore be noted as the optimum version of SG-TFT's.

#### Difference in manufacturing process