# Computer Engineering Mekelweg 4, 2628 CD Delft The Netherlands

The Netherlands http://ce.et.tudelft.nl/

# MSc THESIS

# Hardware Support for Dynamic Partial Reconfiguration

Venkatasubramanian Viswanathan

#### Abstract

CE-MS-2011-23

Dynamically reconfigurable architectures have demonstrated superior performance in comparison to the general-purpose processors. This thesis describes a generic approach for Dynamic Partial Reconfiguration (DPR) of a reconfigurable platform, connected to a general purpose system through a high-speed interconnect. Thus, the system can dynamically install and execute hardware instances of software functions (bitstreams) on-demand. Furthermore, the thesis also serves as a starting point for accelerating multiple software functions concurrently on the hardware. To achieve DPR, system calls are inserted into the original program. The host processor of the system, thus manages the hardware reconfiguration and execution through a Linux device driver. Accelerating multiple software functions is achieved by implementing multiple accelerators on the hardware, managing their interfaces for communication, and providing memory consistency for read and write requests. To do so, the driver provides support for non-blocking execution of multiple software functions. The above system is implemented on a general purpose machine providing a Hyper Transport bus to connect a Xilinx Virtex4-100 FPGA, an AMD Opteron-244, and 1 GB of DDR main memory. The efficiency of the system is evaluated using audio

processing and encryption workloads. The proposed system achieves a 12x speedup over software with audio processing workload and 13x speedup when the workloads were accelerated concurrently.

# Hardware Support for Dynamic Partial Reconfiguration

# Accelerating multiple functions

# THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

COMPUTER ENGINEERING

by

Venkatasubramanian Viswanathan born in Chennai, India

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

# Hardware Support for Dynamic Partial Reconfiguration

by Venkatasubramanian Viswanathan

#### Abstract

ynamically reconfigurable architectures have demonstrated superior performance in comparison to the general-purpose processors. This thesis describes a generic approach for Dynamic Partial Reconfiguration (DPR) of a reconfigurable platform, connected to a general purpose system through a high-speed interconnect. Thus, the system can dynamically install and execute hardware instances of software functions (bitstreams) on-demand. Furthermore, the thesis also serves as a starting point for accelerating multiple software functions concurrently on the hardware. To achieve DPR, system calls are inserted into the original program. The host processor of the system, thus manages the hardware reconfiguration and execution through a Linux device driver. Accelerating multiple software functions is achieved by implementing multiple accelerators on the hardware, managing their interfaces for communication, and providing memory consistency for read and write requests. To do so, the driver provides support for non-blocking execution of multiple software functions. The above system is implemented on a general purpose machine providing a Hyper Transport bus to connect a Xilinx Virtex4-100 FPGA, an AMD Opteron-244, and 1 GB of DDR main memory. The efficiency of the system is evaluated using audio processing and encryption workloads. The proposed system achieves a 12x speedup over software with audio processing workload and 13x speedup when the workloads were accelerated concurrently.

**Laboratory** : Computer Engineering

Codenumber : CE-MS-2011-23

Committee Members :

Advisor: Ioannis Sourdis, CSE, Chalmers University

Advisor: Georgi Gaydadjiev, CE, TU Delft

Chairperson: Koen Bertels, CE, TU Delft

Member: Koen Langendoen, ES, TU Delft

Dedicated to my family and friends. Especially my parents and brother for always supporting and encouraging me in all my endeavors.

# Contents

| Li | st of | Figures                                                    | Ĺ |

|----|-------|------------------------------------------------------------|---|

| Li | st of | Tables                                                     | Ξ |

| A  | ckno  | wledgements                                                | i |

| A  | chiev | rements                                                    | i |

| 1  | Inti  | roduction 1                                                | L |

|    | 1.1   | Motivation                                                 | 2 |

|    | 1.2   | Problem Statement                                          | 3 |

|    | 1.3   | Objectives and Goals                                       | í |

|    | 1.4   | Overview                                                   | 7 |

| 2  | Bac   | kground                                                    | ) |

|    | 2.1   | Memory Hierarchy                                           | ) |

|    | 2.2   | Reconfigurable General Purpose Computing                   | - |

|    |       | 2.2.1 DRC Computers                                        | L |

|    |       | 2.2.2 SRC Computers                                        |   |

|    |       | 2.2.3 Xtreme Data                                          |   |

|    | 2.3   | Reconfigurable High Performance Computing                  |   |

|    |       | 2.3.1 Altix                                                |   |

|    | 2.4   | 2.3.2 Convey                                               |   |

|    | 2.4   | HTX System Architecture                                    |   |

|    |       | 2.4.1 Communication                                        |   |

|    |       | 2.4.2 Integration and Control of the Reconfigurable device |   |

|    | 2.5   | 2.4.3 Implementation Platform                              |   |

|    | 2.0   | Xilinx Partial Reconfiguration                             |   |

|    | 2.6   | Conclusion                                                 |   |

| 3  | Har   | edware Support 27                                          | 7 |

| •  | 3.1   | Dynamic Partial Self-Reconfiguration                       |   |

|    | 3.1   | 3.1.1 ICAP Controller                                      |   |

|    |       | 3.1.2 Device Driver Support                                |   |

|    |       | 3.1.3 Partition Pins                                       |   |

|    |       | 3.1.4 Configuration memory read back                       |   |

|    | 3.2   | Multiple Accelerators                                      |   |

|    |       | 3.2.1 Wrapper Support                                      |   |

|    |       | 3 2 2 Compiler Support 40                                  |   |

|              | 3.2.3 Driver Support                                                                    | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 3.2.4 Memory Consistency                                                                | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | 3.2.5 Partial Reconfiguration                                                           | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

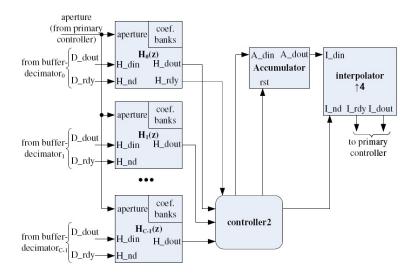

| 3.3          | Beamforming Audio Processor                                                             | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | 3.3.1 The Design                                                                        | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | 3.3.2 Buffers Decimator (BD)                                                            | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

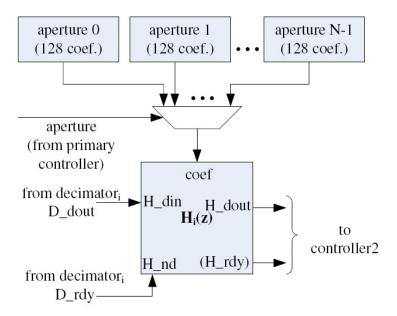

|              | 3.3.3 H(z) beemsteering FIR filter                                                      | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | 3.3.4 Beamforming Interpolator (BI)                                                     | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.4          | Conclusion                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Eva          | luation                                                                                 | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.1          | Area Utilization                                                                        | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

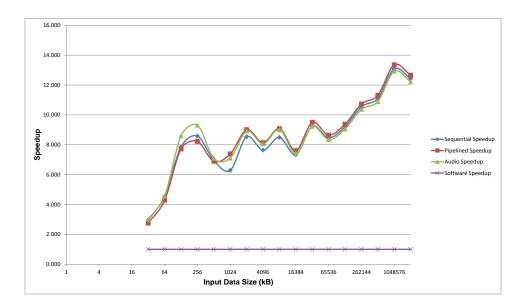

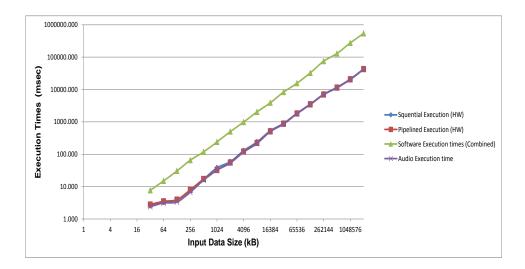

| 4.2          | Speedup and execution times                                                             | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.3          |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.4          |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.5          | • •                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.6          | · · · · · · · · · · · · · · · · · · ·                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.7          | Conclusion                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Con          | nclusion                                                                                | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.1          | Summary                                                                                 | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.2          | · · · · · · · · · · · · · · · · · · ·                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.3          | Future Work                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Bibliography |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SVI          | F file to read back configuration memory                                                | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              | 3.4<br>Eva<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>Cor<br>5.1<br>5.2<br>5.3 | 3.2.4 Memory Consistency 3.2.5 Partial Reconfiguration 3.3 Beamforming Audio Processor 3.3.1 The Design 3.3.2 Buffers Decimator (BD) 3.3.3 H(z) beemsteering FIR filter 3.3.4 Beamforming Interpolator (BI) 3.4 Conclusion  Evaluation 4.1 Area Utilization 4.2 Speedup and execution times 4.3 Bitstream size vs Reconfiguration Latency 4.4 Floorplaning 4.5 Bandwidth of HTX and Queue size 4.6 Power Consumption 4.7 Conclusion  Conclusion  Conclusion  5.1 Summary 5.2 Contributions 5.3 Future Work |

# List of Figures

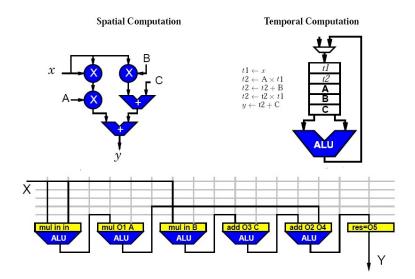

| 1.1  | Spatial versus Temporal Computation for the expression $Ax^2 + Bx + C$                                                                           | 1   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

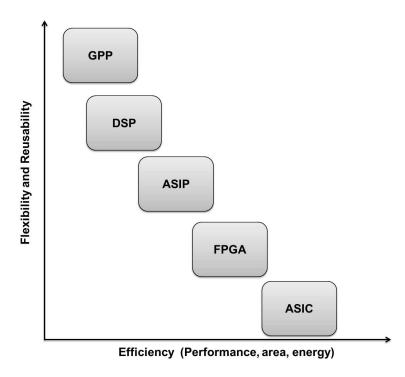

| 1.2  | Trade off between flexibility and efficiency                                                                                                     | 3   |

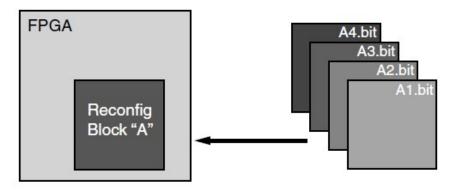

| 1.3  | Basic Premise of Partial Reconfiguration                                                                                                         | 6   |

| 2.1  | Possible locations for the RPF in the memory hierarchy. Source from Reconfigurable Computing: The Theory and Practice [1]                        | 10  |

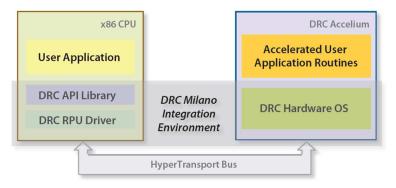

| 2.2  | DRC Accelium architecture                                                                                                                        | 11  |

| 2.3  | SRC IMPLICIT+EXPLICIT architecture                                                                                                               | 12  |

| 2.4  | Xtreme Data XD2000i architecture                                                                                                                 | 13  |

| 2.5  | Block diagram showing how the FPGA is connected to the NUMA link interconnect and several banks of SRAMs. Source: Reconfigurable                 |     |

| 2.0  | Application-Specific Computing User's Guide [2]                                                                                                  | 14  |

| 2.6  | The Convey Architecture with Intel host processor, co-processor and                                                                              | - 4 |

| 2.7  | shared virtual memory. Source: Convey HC-1 Architecture White Paper[3]. The coprocessor is divided into the Application Hub, Memory Controllers, | 14  |

|      | and Application Engines. Source: Convey HC-1 Architecture White                                                                                  |     |

|      | Paper[3]                                                                                                                                         | 15  |

| 2.8  | Top-level block diagram of the proposed system                                                                                                   | 16  |

| 2.9  | Detailed diagram of the modules located in the wrapper                                                                                           | 17  |

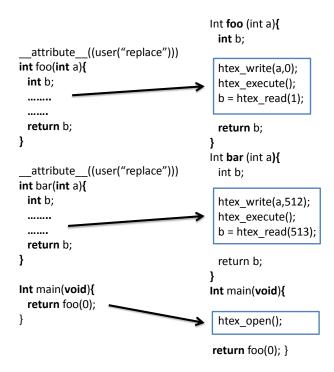

| 2.10 | Code modification by the extended compiler                                                                                                       | 19  |

| 2.11 | Diagram showing how the TLB is used to translate a virtual address to a                                                                          |     |

|      | physical address                                                                                                                                 | 20  |

|      | The three IO regions and how they are mapped to hardware Implementation platform connecting a reconfigurable device to the host                  | 23  |

|      | and the main memory through a HyperTransport bus                                                                                                 | 24  |

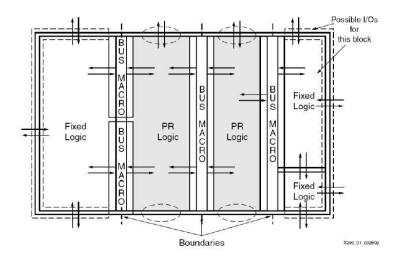

| 2.14 | Bus Macros                                                                                                                                       | 25  |

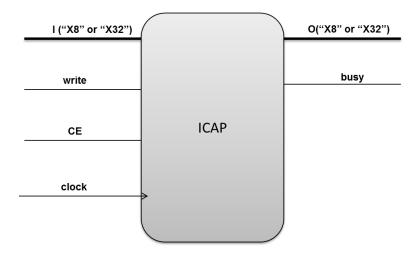

| 3.1  | Xilinx ICAP primitive                                                                                                                            | 29  |

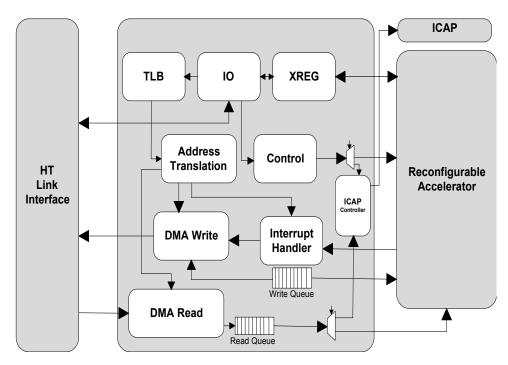

| 3.2  | Architecture with ICAP controller                                                                                                                | 30  |

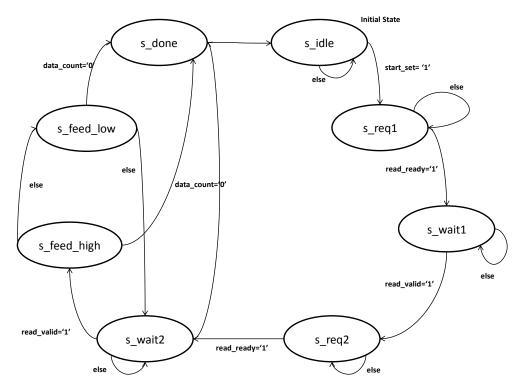

| 3.3  | ICAP Controller FSM                                                                                                                              | 31  |

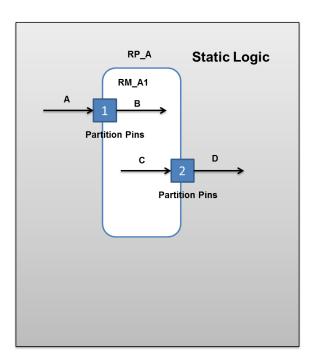

| 3.4  | Static and Reconfigurable logics with Partition Pins inserted                                                                                    | 32  |

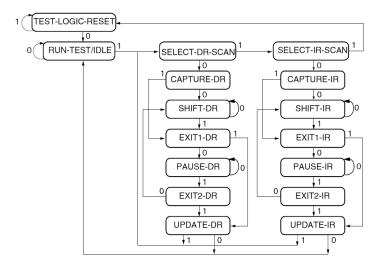

| 3.5  | JTAG TAP Controller State Diagram. Source Xilinx configuration guide [4]                                                                         | 33  |

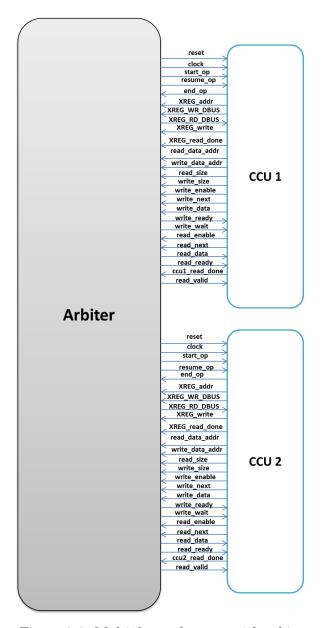

| 3.6  | Multiple accelerators with arbiter                                                                                                               | 35  |

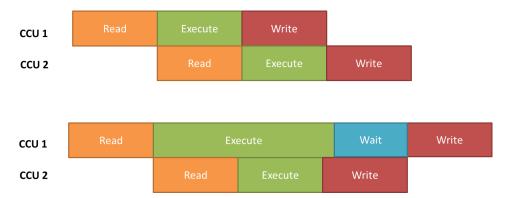

| 3.7  | Execution phases of CCUs without data dependencies                                                                                               | 36  |

| 3.8  | Execution phases of CCUs with data dependencies                                                                                                  | 37  |

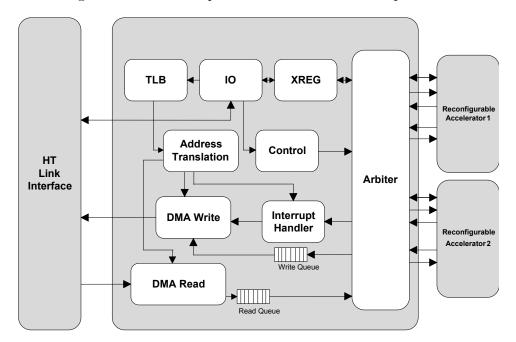

| 3.9  | Wrapper with multiple accelerators                                                                                                               | 37  |

| 3.10 | Pipelined sequential execution with TLB Support                                                                                                  | 39  |

| 3.11 | Proper arguments inserted to htex_write() wrapper function                                                                                       | 40  |

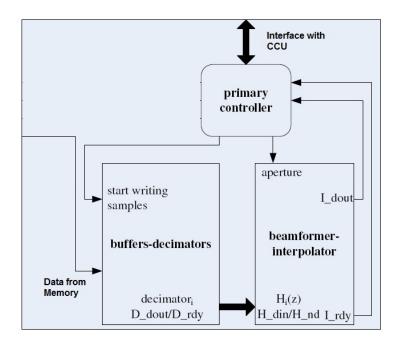

|      | Beamforming Fabric Co-processor (BF_FCP) Organization                                                                                            | 44  |

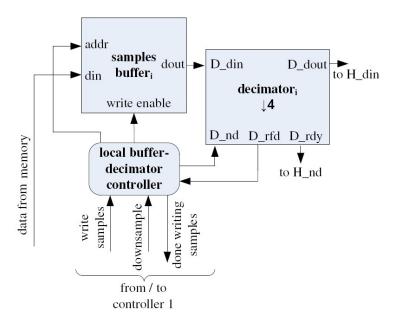

|      | Buffer-decimator module                                                                                                                          | 45  |

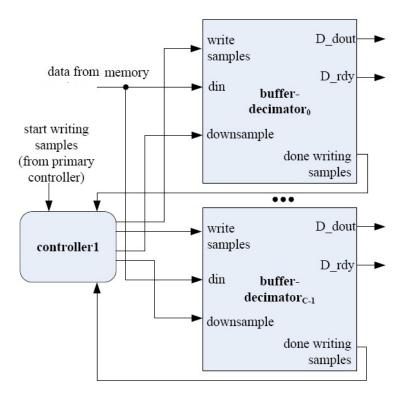

|      | Controller1 and buffer-decimator (BD) modules                                                                                                    | 46  |

| 3.15 | A beamsteering FIR filter                                                                                                                        | 46  |

| 3.16 | Controller2 and the accumulator               | 47 |

|------|-----------------------------------------------|----|

| 4.1  | Input size versus speedup                     | 53 |

| 4.2  | Input size versus execution times             | 54 |

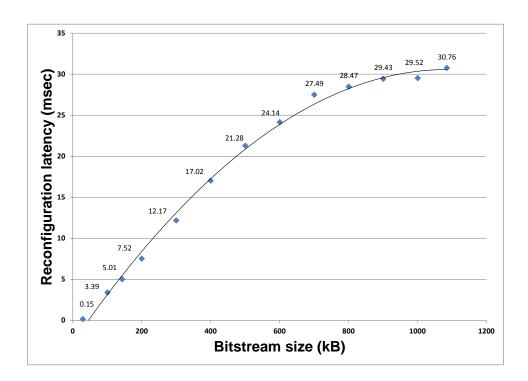

| 4.3  | Reconfiguration latency versus bitstream size | 56 |

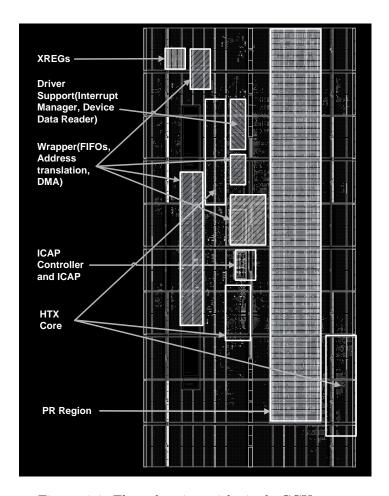

| 4.4  | Floorplanning with single CCU                 | 57 |

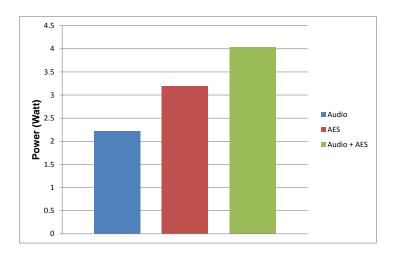

| 4.5  | Design and power consumption                  | 59 |

# List of Tables

| 2.1 | Overview of General Purpose Reconfigurable Platforms                | 23 |

|-----|---------------------------------------------------------------------|----|

| 3.1 | Memory Consistency for request/response from different CCUs         | 43 |

| 4.1 | Area Utilization of the FPGA Design Blocks with single CCU          | 50 |

| 4.2 | Area Utilization of the FPGA Design Blocks with multiple CCUs       | 50 |

| 4.3 | Execution times and speedup for different input sizes for Audio CCU | 51 |

| 4.4 | Execution time and speedup for multiple concurrent CCUs             | 52 |

| 4.5 | Bitstream size versus reconfiguration latency                       | 55 |

| 4.6 | Design and power utilization                                        | 58 |

# Acknowledgements

I would like to thank Georgi Gaydadjiev for having given me the opportunity to work on this master thesis topic, taking his time to read and correct my thesis and providing me financial support throughout the second year. I am very grateful to Ioannis Sourdis for providing me his guidance throughout my thesis and spending time to read and correct my thesis work. It would not have been possible to publish my work in FPT'11 if not for his valuable inputs and suggestions. I would like to extend my gratitude to Anthony Brandon for helping me understand the HTX platform during the initial stages in my work. I would also like to thank Google for supporting this work in the context of their Faculty Research Awards program.

Words certainly can not describe how grateful I am to my parents and my brother for all their motivation and encouragement. My parents have always been a constant source of support; emotional, moral and of course financial, and this thesis would certainly not have existed without them. My family and my cousins have been, always, my pillar, my joy and my guiding light, and I would like to thank them all. Finally, I am indebted to my friends Srini, Ram, Abhijit, Venkatraman, Shreyas Bhargav, Ajith, Ganesh, Chokka and many others who have made my stay very enjoyable and memorable through these years. Their support and care has made these years of my graduate study priceless. I greatly value their friendship and hope to stay in touch with them throughout the rest of my life.

Venkatasubramanian Viswanathan Delft, The Netherlands October 1, 2011

# Achievements

# $Conference\ Publications$

• Ioannis Sourdis, Venkatasubramanian Viswanathan, Abhijit Nandy, Anthony Brandon, Dimitris Theodoropoulos, Georgi N. Gaydadjiev, **Reconfigurable Acceleration and Dynamic Partial Self-Reconfiguration in General Purpose Computing**, International Conference on Field-Programmable Technology (FPT), New Delhi, India, December 2011.

Introduction

Traditional computation involves either implementing the application in hardware (e.g., ASICs) or implementing them in software running on processors (e.g., DSPs, micro controllers, embedded or general-purpose microprocessors). More recently, Field-Programmable Gate Arrays (FPGAs) have emerged as a platform for implementing compute intensive applications. Such devices combine the post-fabrication programmability of processors with the spatial computational style most commonly employed in hardware designs. Using FPGAs for computing led the way to a new class of computer organizations which we now call reconfigurable computing architectures. Reconfigurable computing bridges the gap between traditional hardware/ software approach by giving the programmer/systems designer the flexibility of hardware implementation. By combining reconfigurable computing with general purpose computing we can accelerate critical time consuming parts of the program on the FPGA while still allowing other non-critical parts of the program to be run on the general purpose processor. This eliminates the need to implement the complete design as a hardware structure.

Integrating Reconfigurable computing into traditional Computing systems has been a challenge since the early days of FPGAs; several machines have been designed towards this direction, such as PAM [5], Splash [6], and DISC [7]. The primary drawback of all these attempts was the limited bandwidth and high communication latency between the general purpose host-processor and the reconfigurable device. In order to overcome this

Figure 1.1: Spatial versus Temporal Computation for the expression Ax<sup>2</sup> +Bx+C

bottleneck, other solutions proposed a more tightly coupled reconfigurable-unit which is at the cost of significant changes in the host-processor architecture, e.g., Garp[8], Chimaera[9], PRISC [10], and OneChip [11]. Recently, however, components such as motherboards, have been released which support standard high-speed communication between general purpose processor(s), memory, peripheral and other input/ouput devices. These components use high-speed on-board links such as the Intel QuickPath (QP) [12] and the AMD HyperTransport bus (HTX) [13] and provide multi-GByte/sec bandwidth, low-latency communication. The above mentioned developments offer a new opportunity for integrating reconfigurable computing into general purpose computing systems. Several commercial systems have been released offering reconfigurable acceleration combined with traditional computers, but they all are in general hard to program. Examples of such machines are the Altix SGI[14], ClearSpeed[15], and Convey[16], which mostly target High-Performance scientific computing rather than the General Purpose domain. Another interesting approach, recently announced by Intel, is the new Atom embedded processor with an Altera Arria FPGA built into the same package connected to the Atom via two PCIe buses[17]; however, even on the same die the PCIe bandwidth is about an order of magnitude lower than an HTX or a QP.

Rather than building a machine from scratch or suggesting fundamental architectural changes, it is more performance and cost-efficient to propose a generic solution that uses existing off-the-shelf components with only software (and configuration) modifications. Existing platforms such as HTX[18] describe a generic solution that requires only an FPGA device driver, few compiler extensions and a reconfigurable wrapper inside the FPGA to provide reconfigurable acceleration for General Purpose Computing. However, this approach also has few shortcomings as described in the following sections. Thus according to Moore's law, the saturating computational power of processors calls not only for a whole new era of custom computing, but also techniques to exploit the available resources and computational power of FPGAs.

The remainder of this chapter is organized in four sections. Section 1.1 states the motivation for work. Section 1.2 describes the problems with current platforms for combining general purpose computing with reconfigurable computing. In Section 1.3 states the main objectives and goals of the thesis and gives an outline of the main contributions. Finally, Section 1.4 gives an overview of the remaining chapters of the thesis.

# 1.1 Motivation

Some decades ago a circuit designer had little choices when implementing a new system. If flexibility was needed, it was built using general purpose processors (GPPs). Demand for more speed meant building custom solutions in hardware, so application specific integrated circuits (ASICs) were chosen. Over the years, more and more alternatives appeared on the market. Digital signal processors (DSPs) were designed for data-flow intensive computation. Glue logic grew to programmable logic arrays (PLAs) and

Figure 1.2: Trade off between flexibility and efficiency

complex programmable logic devices (CPLDs). Along with them, Field Programmable Gate Arrays (FPGAs) were introduced. Like all the other techniques, FPGAs fill a gap. From a system designer's point of view, they can be seen as programmable ASICs offering less speed, less power efficiency but more flexibility. Since FPGAs offer spatial computing capabilities just as ASICs do, FPGAs offer the same concurrency in calculation as the ASICs. Figure 1.2 shows the flexibility/efficiency trade-off provided by different devices.

On the other side, the computational power of GPPs were reaching a saturation due to the decrease in the size of the transistors which demands an ever increasing power utilization. Therefore, to overcome this limitation of GPPs, by exploiting the computational power and flexibility of FPGAs, there came a need for custom computing which combined the flexibility of GPPs with the efficiency of FPGAs. This gave rise to a whole new field of opportunity as well as challenges which are described in the following sections.

## 1.2 Problem Statement

The above mentioned platforms for custom computing have various drawbacks which has been explained in the following paragraphs. The first drawback being the memory access latency and the data bandwidth between the reconfigurable accelerator and the main memory. Since most of the applications that are chosen for reconfigurable acceleration are compute intensive, they require the access of huge amount of input data. This is an important point of concern because, having memory access latency comparable to that of compute time will almost halve the speedup and thereby reducing the efficiency of accelerating the application on the hardware. Therefore, the accelerators should have low memory access latency. Some architectures such as GARP [8], Chameleon[15], Chimaera[9], OneChip[11] and PRISC[10] attempt to solve this by integrating the reconfigurable accelerator in the same chip as the general purpose processor. However, this requires redesign of the entire chip and it has to undergo a separate fabrication process. Thus making the process more time consuming and expensive. As mentioned above, standard high-speed buses such as QuickPath and HyperTransport, which are specifically developed for high-speed connections between processors, main memory and peripherals with latencies of less than 200ns [19], help reducing the bottleneck presented by data access.

The second drawback is that, most of the architectures that has been developed are very much platform specific and depend on specific compilation process and tool chain. This makes the task of programming the device dependent on the knowledge of a particular platform and tool chain. This also means that significant work is needed to port either the application or accelerator (or both) to a different implementation of the same platform. Maxeler Technologies MAX3 acceleration card uses a platform specific bus connection to connect to the processor, memory and other peripheral devices [20]. It also uses platform specific tools for compiling the code for the platform. Several other systems with RPUs as co-processors are being developed such as DRC Accelium Coprocessors [21], SRC Computers [22] have been developed commercially. But all these systems also use specific compilers, APIs and tool chains. Some platforms such as Molen[23], Convey[16], and Altix[14] address this by specifying a specific interface to the accelerator and software.

The next drawback is that most of these systems are not suitable for general purpose computing. Convey and Altix are aimed at high performance computing intended for scientific research instead of general purpose computing. Molen, which is not aimed at high performance computing, nor uses any custom hardware, is not ideal for general purpose computing. This is because, Molen is implemented entirely on an FPGA board. Further, there is no readily available operating system that will run on it while giving the same performance and features as an operating on a general purpose machine. The final drawback of reconfigurable computing systems in general is the programmability. The common solutions for programming these systems are as follows. First, either some new or extended programming languages are used, which is then transformed by a compiler into intermediate form which uses hardware. Or, they use system specific function calls to manage the reconfigurable device.

HTX [18] is a general purpose platform with a reconfigurable device integrated into the system, using a high-speed interconnect. Architecture and details of the HTX has been explained in Chapter 2.4. Significant work has been done on the HTX reconfigurable platform, to address the above mentioned problems and create to a

generic platform for accelerating applications. The platform uses a general purpose machine, with a reconfigurable accelerator, a Linux device driver and a GCC compiler plug-in to identify parts of source program and accelerate parts of it on the hardware. However, the platform still has the following drawbacks. First, it does not provide support for dynamic partial reconfiguration. This means that significant amount of time has to be spent on reprogramming the FPGA device every time a different software function has to be accelerated. Moreover, the platform does not provide non-blocking execution of the function. Whenever a software function is accelerated on the hardware, the Linux device driver puts the calling software function to sleep, thereby preventing any further execution of the program until the device returns the results. Finally the device does not provide hardware support to accelerate multiple software functions of a process, simultaneously on the hardware.

All these existing problems with integrating a reconfigurable platform and programming it can be summarized as follows:

- The reconfigurable accelerator should be connected to the host system using an existing low latency/high bandwidth link;

- The architecture should be easily implementable and portable on different platforms with slight modifications of the existing one;

- Platform should provide runtime partial reconfiguration support to support the acceleration of any software function on the fly;

- Platform should provide non blocking execution to accelerate multiple software functions simultaneously whenever possible.

# 1.3 Objectives and Goals

The previous section described the various problems that exists in the field of reconfigurable computing and also explains the various challenges involved in integrating a reconfigurable platform into a general purpose system. Although HTX [24] addresses most of the issues, there are still a few drawbacks on the existing system as mentioned in the previous section. The goal of this thesis is to address those issues by improving the architecture of the existing system by providing the following functionalities:

• Dynamic Partial Reconfiguration: Xilinx FPGA technology provides the flexibility of modifying an operating FPGA design by performing partial reconfiguration, using a partial bit file as shown in Figure 1.3. Dynamic Partial Reconfiguration, also known as an active partial reconfiguration permits to change the part of the device while the rest of the FPGA is still running. Having DPR allows us to dynamically install and execute hardware instances of software functions (bitstreams) on-demand. It thus gives the ability to accelerate any application on the fly, without having to spend much time on reprogramming the entire FPGA. The

Figure 1.3: Basic Premise of Partial Reconfiguration

Dynamic Reconfiguration is initiated by the program, which has locked the device. In the hardware an ICAP controller reads the bitstreams from the memory and feeds it to the Internal Configuration Access Port (ICAP) thus initiating Dynamic Partial Self-Reconfiguration (DPSR);

- Multiple accelerators: The existing architecture supports the acceleration of a single software function at a time. However, advanced architectures and compute intensive applications demand the acceleration of multiple software functions simultaneously, so as to minimize the execution time. Having such an architecture not only allows us to accelerate two functions at the same time whenever possible, but also minimizes partial reconfiguration overhead time. This can be achieved by having multiple accelerators on the hardware, managing their interfaces with the hardware wrapper for read/write requests, and providing memory consistency for requests from different accelerators;

- Hardware support for multiple accelerators: When having two accelerators on the hardware, the FPGA Wrapper has to be extensively modified to provide proper management of resources and provide memory consistency for requests from different accelerators. First, the arbiter manages the parallel resource access requests from multiple accelerators. Furthermore, it also provides memory consistency for read and write requests from individual accelerators by identifying the request/response packets, and pushing them into corresponding read/write queues. Finally there has to be a synchronization mechanism between the reads and writes of different accelerators:

- TLB support for streaming applications: When executing two streaming applications on the hardware concurrently, the arbiter detects the address dependencies for read and write requests from the accelerators. When it does so, the accelerators are scheduled to execute sequentially one after the other. However, this results in the consumer accelerator waiting for a longer period, until the producer writes back all its results to the memory. In order to avoid this, the data

1.4. OVERVIEW 7

produced by the first accelerator should be immediately available to the second, their execution has to be pipelined and synchronized. In order to do so, memory access and address lookup mechanisms are modified by providing additional support for locking and unlocking the TLB entries;

- Compiler support for multiple accelerators: The system calls will be inserted in the original code using a modified GCC compiler plug-in after annotating the function to be accelerated. However, additional support has to be provided to the compiler to identify multiple annotated functions and insert system calls accordingly;

- Device Driver support for non-blocking execution: The existing Linux device driver has been modified to provide non-blocking execution support. It allows a single process to accelerate multiple independent functions concurrently.

### 1.4 Overview

This chapter has described the main motivations for the work, provided an overview of the problems in the existing platforms and has stated the main objectives of the work. This thesis has further been divided of four chapters organized as follows.

Chapter 2 discusses some of the background on reconfigurable computing. We explain the difference between course grained and fine grained reconfigurable fabrics, and their influences in architectural choices. It then explains the different memory hierarchies in which an FPGA can be integrated in a General Purpose processing system. It further discusses some of the commercially available reconfigurable General purpose systems and their features. Finally we also look at how the HTX architecture solves the problems by providing solutions such as easy of programmability, virtual memory, memory protection and paging, interrupt support, compiler and driver support.

Chapter 3 explains the architectural changes required for Dynamic Partial Reconfiguration support. Furthermore, it also describes accelerating multiple software functions on hardware. Several modifications have been made to the existing FPGA Wrapper modules to provide hardware support. Compiler and driver support have been provided for non-blocking execution. Finally, it provides an overview of the architecture of the audio beamforming processor used to evaluate the proposed system.

Chapter 4 evaluates the system using different performance metrics. Two different applications are accelerated in hardware and the execution time and speedup achieved are compared with that of a pure software implementation of the same. This is followed by an evaluation of the latency for performing a Dynamic Partial Self-Reconfiguration. Other parameters such as, area, power are measured. Finally, Chapter 5 draws some conclusions on the architecture and the results. It also describes some future works to enhance the features of the platform.

Background

Chapter 1 discussed about the various problems that we face in integrating reconfigurable and general purpose computing, and gave an introduction to the thesis work highlighting its main goals and objectives. This chapter explains the architecture, working and the implementation of the HTX platform [18] in detail, which forms the basis of this work. Furthermore it discusses some commercially available reconfigurable general purpose systems and also gives a short introduction to the Xilinx partition-based partial reconfiguration flow and terminology.

One of the main considerations when integrating reconfigurable systems with general purpose systems is the question of how to integrate the Reconfigurable Processing Fabric (RPF) into the system as explained in section 2.1. This plays an important role because, when accelerating compute intensive data processing applications, the memory access latency and bandwidth are critical factors. Examples include data-streaming applications with significant digital signal processing, such as multimedia applications like image compression and decompression, and encryption. Many architectures have been designed in this direction. Most of these are aimed at high performance computing such as XD1 [25], Altix [14], Convey [16] and SRC [22]. These systems are sold as supercomputers with added support for reconfigurable computing. Other platforms used for general purpose computing such as MAX3 Acceleration card [20] has the RPF in the same package and use specific tool chain for compilation.

For the above mentioned reasons, we have chosen HTX[18] as a starting platform because of the number of advantages it provides. First the RPF runs on a general purpose platform with a Linux kernel. It uses the existing off the shelf high bandwidth low latency components for communication, and it is easy to port to different platforms with slight modifications. It provides compiler and driver support for accelerating software programs in hardware in a generic way. Therefore the architectural features can be improved to provide dynamic runtime partial reconfiguration support. Moreover, it uses open-source tools and OS, and hence it can be customized at any point according to the needs.

The chapter is further organized as follows. Section 2.1 gives an overview of the different ways in which a reconfigurable platform can be integrated into the memory hierarchy a general purpose system. Section 2.2 discusses some commercially available general purpose reconfigurable systems. Section 2.4 describes in detail about the HTX architecture. Section 2.5 explains the basic terminology of Xilinx Partial Reconfiguration and finally section 2.6 summarizes the chapter.

Figure 2.1: Possible locations for the RPF in the memory hierarchy. Source from Reconfigurable Computing: The Theory and Practice [1]

# 2.1 Memory Hierarchy

There are different ways to integrate the Reconfigurable Processing Fabric(RPF) in the memory hierarchy of a general purpose system as shown in Figure 2.1. In a tightly and loosely coupled hierarchy, the RPF is a part of the processor chip. However in the former, the reconfigurable fabric is used as a functional unit of a processor. In case of the latter, the RPF is connected to processor and the memory through a data bus. However in case of co-processor, the RPF is in a separate chip connected to a peripheral bus, allowing it to communicate with main memory.

Tightly couple hierarchy has the same memory access latency as that of any other functional unit. Whereas, loosely coupled hierarchy will have more latency. Since independent co-processor RPFs are are on separate chips, the integration of the RPF into existing computer systems is simplified through the available PCI slots on the system. Unfortunately, this limits the bandwidth and increases the latency between the RPF and memory in traditional processing systems depending on the peripheral bus interface used. For this reason, independent co-processor RPFs are well suited only to systems with high bandwidth, low latency communication links.

Figure 2.2: DRC Accelium architecture

# 2.2 Reconfigurable General Purpose Computing

This section explains the use of reconfigurable computing in general purpose systems that are commercially available. Several research organizations have made efforts to integrate FPGAs into a general purpose systems and make it commercially available. The following subsections explains a few commercially available systems and the features they provide.

## 2.2.1 DRC Computers

The architecture of DRC Accelium is shown in Figure 2.2. DRC computers provides the support for reconfigurable accelerator in the form of coprocessor [21]. The DRC Accelium Coprocessor is integrated with the GPP through a HyperTransport expansion slot. Accelium fits into a standard AMD Opteron PCIe expansion slot and provides very low latency transfers directly to motherboard memory uninterrupted by intermediate memory controllers. It uses a Xilinx Virtex-5 FPGA as its accelerator. In order to provide software support it uses a DRC Milano operating system to integrate the coprocessor into the system. It also provides API, driver and management interface on the CPU, and a hardware operating system on the DRC RPU. Further, it also provides run-time reconfiguration.

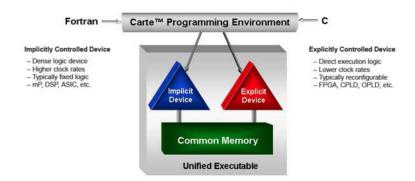

### 2.2.2 SRC Computers

The SRC IMPLICIT+EXPLICIT architecture allows the user to execute existing code, or recompile and develop code for the reconfigurable processor. In order to provide software support for such an architecture, Carte programming environment is used. The seamless integration of a general purpose processor and a reconfiguration processor into a system is called as Direct Execution Logic(DEL). The SRC Carte Programming Environment is an FPGA C and Fortran programming environment, taking applications written in Fortran and/or C and integrates the computational capability of MAP processors and microprocessors into a single application executable code. The main components of the Carte programming environment are MAP Compiler, Libraries, and debugger.

Figure 2.3: SRC IMPLICIT+EXPLICIT architecture

The main element of the architecture is a MAP reconfigurable processor. The MAP processor uses reconfigurable components to accomplish both control and user-defined computation, data prefetch and data access functions. This compute capability is teamed with very high on and off-board interconnect bandwidth. The MAP processor has multiple banks of SRAM memory. MAP modules are also equipped with separate input and output ports. However, it does not provide runtime reconfiguration.

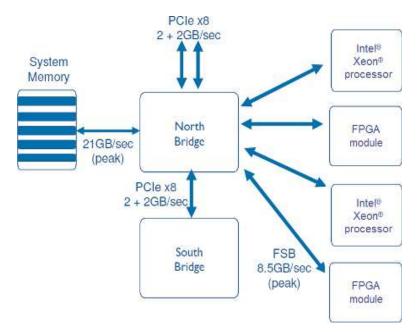

#### 2.2.3 Xtreme Data

XtremeData's XD2000i development system is a complete platform which has an FPGA coprocessor within an x86 COTS computing environment as shown in Figure 2.4. The system has complete hardware, software, and FPGA IP so users can immediately begin developing their FPGA-accelerated applications. The GPP used is an Intel Xeon processor with an XD2000i FPGA coprocessor bases on Altera technology. The coprocessor interfaces with the memory via the FSB available on the motherboard. Application software running on the Xeon can store and load FPGA configuration images that are located on the hard disk. XtremeData provides an open source Linux device driver which allows user space applications to directly access memory mapped FPGA resources, service FPGA interrupt requests, lock physical memory, and perform FPGA controlled DMAs. It also provides support for C to VHDL conversion.

# 2.3 Reconfigurable High Performance Computing

High-Performance Computing (HPC) refers to the use of supercomputers and computer clusters to perform scientific and financial computations where complex calculations are made in a limited time frame. Examples of such applications are: simulation of weather models, protein folding, DNA matching, and constructing three dimensional models in searching for oil and gas reserves. High-Performance computers deliver the required performance by exploiting parallelism in the applications, and by using the most powerful processors available. Because FPGAs use spatial computation models to exploit parallelism, they are increasingly being used in the field of HPC. Two currently available HPC systems with reconfigurable computing are SGI Altix [14] and Convey Computer's HC-1

Figure 2.4: Xtreme Data XD2000i architecture

[16]. These systems use RPF with GPPs to allow acceleration. In Altix the programmer must know more about the platform, and must explicitly use the reconfigurable accelerator through a library. In the Convey, the compiler does automatically detects when the accelerator can be used, allowing the programmer to program without learning any details about the system.

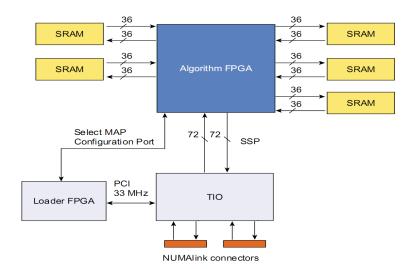

### 2.3.1 Altix

SGI Altix provides support for reconfigurable computing in the form of their reconfigurable Application Specific Computing (RASC) program[2]. As shown in Figure 2.5, in RASC, an FPGA is connected to the SGI NUMA link[2] interconnect as a co-processor. NUMA link is a high bandwidth and low latency interconnect which is used to connect processors, memory, and other components in Altix machines. The FPGA is also connected to several banks of SRAMs, which it uses to store data locally. The FPGA is divided into the Core Services block and the re-programmable Algorithmic block. The Algorithmic block implements in hardware an application specific algorithm which is used to speed up the execution of an application. The Core service block provides interface between the Algorithmic block and the host system. The FPGA can be accessed through a library called RASC Abstraction Layer (RASCAL) which abstracts the system calls and device management. The programmer uses library calls to reserve and use devices; the programmer must also explicitly transfer data to and from the SRAMs using library calls.

Figure 2.5: Block diagram showing how the FPGA is connected to the NUMA link interconnect and several banks of SRAMs. Source: Reconfigurable Application-Specific Computing User's Guide [2]

Figure 2.6: The Convey Architecture with Intel host processor, co-processor and shared virtual memory. Source: Convey HC-1 Architecture White Paper[3].

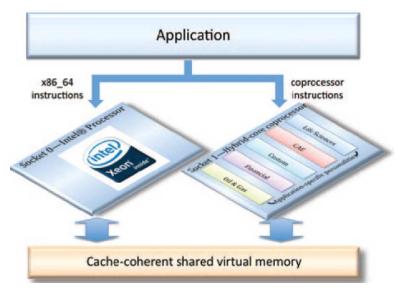

### **2.3.2** Convey

The Convey architecture (Figure 2.6) consists of off-the-shelf Intel processors in combination with a reconfigurable coprocessor. The Convey Instruction Set Architecture [3] extends the x86-64 instruction set with instructions executed by the co-processor. The co-processor can be reconfigured at run-time to execute different instructions, depending on the application. The instruction executed by the co-processor are grouped into "personalities" which can be programmed into the co-processor at run-time. A

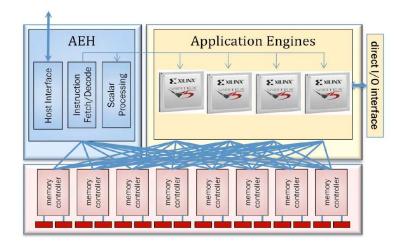

Figure 2.7: The coprocessor is divided into the Application Hub, Memory Controllers, and Application Engines. Source: Convey HC-1 Architecture White Paper[3].

personality is essentially an instruction set tailored to a specific application, and defines all instructions that can be executed by the co-processor. Each personality has a minimal set of instructions which are implemented in all personalities. While the system can have multiple personalities, only a single personality can be loaded into the co-processor at any time. Furthermore the co-processor shares a cache-coherent view of the global virtual memory with the host processor.

The co-processor consists of three components (Figure 2.7): the Application Engine Hub (AEH), Memory Controllers (MCs), and the Application Engines (AEs). The AEH is responsible for the interface to the host processor and I/O chipset, and fetching instructions. The Memory Controllers perform address translation for the AEs and perform the DMA requests to deliver data to the AEs. This allows the co-processor to work on the same virtual address space as the host processor. The AEH and MCs implement the instructions which are shared among all personalities to ensure that basic functionality such as memory protection, access to co-processor memory and communication with the host processor is always possible. The AEs are the units that execute the remainder of the instructions in the personality. Programming for the Convey architecture is done in standard C/C++ or FORTRAN. The compiler then emits code for both the Intel host processor and the co-processor, in the same executable. During compilation, the compiler uses a state description of the instructions in a personality to determine what code can be executed on the co-processor. The compiler also emits instructions which start the co-processor by writing to a memory location. This approach allows existing software to be recompiled without changes in order to make use of the advantages of the architecture.

Figure 2.8: Top-level block diagram of the proposed system

# 2.4 HTX System Architecture

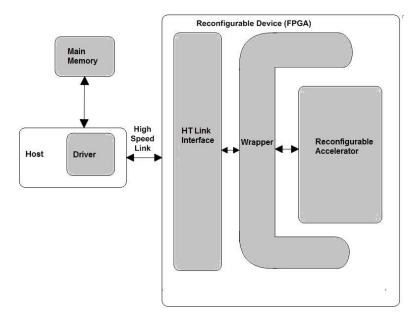

The HTX [24] is a general purpose platform with a reconfigurable device used for accelerating computationally intensive functions in hardware. Such functions are annotated in the code to indicate that they will be executed in hardware. Figure 2.8 illustrates the overview of the proposed system. The Reconfigurable device (FPGA card) is connected to the main memory through a high-speed link. On the host side, a Linux device driver has been developed for the communication of the FPGA device with the host GPP via system calls and interrupts. On the reconfigurable device, a HyperTransport link core is present for the device to communicate with memory. A wrapper is present to support the integration of FPGA device into the system. Finally, a reconfigurable accelerator is present to accelerate software functions on the hardware. It can be customized depending on the function to be accelerated.

#### 2.4.1 Communication

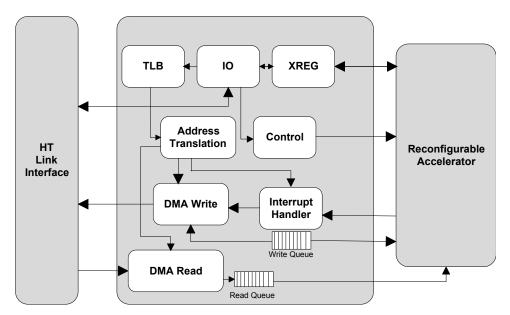

Figure 2.9 offers a more detailed view of the internal modules of the hardware wrapper. The IO module controls all the memory mapped IO of the device. DMA reads and writes are handled by the DMA Manager and DMA Read/Write unit with the support of the Address translation module. Address translation uses a TLB copy of the host to translate virtual addresses to physical before each DMA request. Finally, the Interrupt Handler (IH) manages the interrupts raised by the device. In general, the wrapper is responsible for the following:

• Communication with the memory mapped IO regions; exchange registers (XREGs), a TLB copy, as well as control and status registers;

Figure 2.9: Detailed diagram of the modules located in the wrapper

- The control registers are used by the host to pass commands to the FPGA device, while the status registers hold information regarding the status of the device;

- The exchange registers (XREGs) are used for passing function-arguments from the host to the accelerator and return execution results to the host;

- Has an interrupt handler (IH) for the interrupts generated by the FPGA device;

- Performs Direct Memory Access (DMA) operations between the FPGA device and the main shared (virtual) memory;

- Translates virtual addresses to physical using a local TLB copy and handles TLB misses (by raising an interrupt).

The system mainly supports three types of communication between the host, reconfigurable device and the main memory:

- Host to/from reconfigurable device: The host can write the arguments of a function call to the FPGA through Linux system calls. The FPGA uses these arguments to read/write from/to the main memory. The host can also send control signals to to start the execution or reset the device. Finally it can write the physical address entries into the device in case of any address translation interrupts and can read back any return results of the device;

- Reconfigurable device to host: The device in turn will notify the host by means of interrupt, in case of execution done or address translation by setting a value for the status register which in turn will be be read by the host;

• Reconfigurable device to main memory: The FPGA can communicate with the main memory by means of a HyperTransport link interface. It can perform DMA reads and writes to read the input data and write back the output data.

## 2.4.2 Integration and Control of the Reconfigurable device

In order to integrate the reconfigurable device into the system we use several modules. As mentioned before, the Wrapper module in the FPGA plays an important role for communication from the hardware. There is a Linux device driver which provides the API for various system calls for reading from and writing to the device. Finally, there is also a GCC compiler plug-in that has been developed to identify parts of the program (annotated functions) that has to be accelerated on the hardware and insert corresponding system calls. All these components and their functionalities are explained in the following sections.

## 2.4.2.1 Driver Support

The Driver is responsible for providing the APIs to control the FPGA device. These APIs internally corresponds to a Linux system call. The following system calls are used to control the functionality of the FPGA device: open(), close(), read(), write(), ioctl(). The open() system call is used by a program, running on the host processor, to get a lock on the device, while the close() system call releases the lock. The write() and read() system calls are used to write the arguments of function calls to the (memory-mapped) exchange registers (XREGs) of the FPGA device and to read the return values, respectively. Furthermore, the ioctl() call can be programmed to pass commands to the device by writing into the control registers using memory mapped IO. It is used to initiate the execution of the reconfigurable accelerator ioctl(EXECUTE). Using system calls rather than for instance extending the ISA of the host processor, like in [23], provides a more generic approach applicable to any system that supports a connection to an FPGA device.

#### 2.4.2.2 Compiler Support

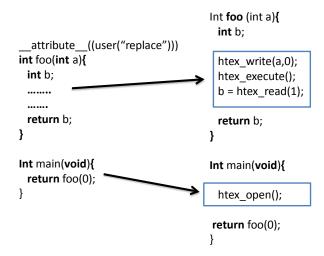

The programmer indicates the functions to be executed in hardware, by annotating them with GCC attributes: \_\_attribute\_\_((user("replace"))). The compiler will then automatically insert the appropriate APIs provided by the driver. To do so, the GCC 4.5 compiler has been extended with a plug-in which scans the source code for such annotated functions. The body of such a function is then replaced with the required system calls. The plug-in is executed by GCC as follows:

• When the compiler plug-in is loaded an entry function is called which registers a new attribute with the compiler. It also registers a new pass called replace pass;

Figure 2.10: Code modification by the extended compiler

- The replace pass is run by the GCC after the code has been transformed into the internal representation. During the compilation of source file, the function registered along with the attribute is called every time the attribute occurs;

- The actual replacement pass is called once for every function in the source file after the code has been translated into the internal representation.

Figure 2.10 illustrates an example of the system calls automatically inserted by the compiler to the original code in order to allow the execution of a function in the FPGA: first, the device is initialized (dev =open(DEVICE)), then the function parameter is passed to the FPGA (write(dev, a, 0)), subsequently, the function is executed in hardware (ioctl(dev, EXECUTE)), and finally the result is returned to the host (b=read(dev, 1)).

#### 2.4.2.3 Address Translation

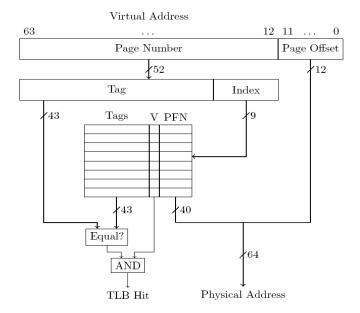

The FPGA device works on the virtual address space. Consequently, in order to access the memory, the device needs to have address translation support. To do so, the virtual addresses are translated into physical addresses using a local TLB copy in the FPGA. TLB misses are handled by interrupts raised by the device. In such cases, the driver will write the missing entry to the FPGA TLB which then will be able to proceed with the respective translation. All pages stored in the FPGA TLB copy are locked in memory by the driver, while pages which are replaced in the TLB copy are unlocked. Address translation is handled by the Address Translation unit. Whenever an address must be translated, the address translation unit takes the following steps: First the input address. Next, bits 20 to 12 (the page index) of the virtual address are used as an index into the TLB, to find the entry corresponding to the virtual address. The remaining most significant bits (63 to 21) are then compared to the tag stored in the TLB at the given index. If these bits match, and the valid bit is set to true, otherwise the TLB entry is invalid and an interrupt is generated to indicate to the driver that address translation

Figure 2.11: Diagram showing how the TLB is used to translate a virtual address to a physical address

is required. Once the correct entry is written to the TLB the address translation unit will append the lowest 12 bits of the virtual address (the page offset) to the physical address stored in the TLB. The TLB is implemented as a BRAM with 512 entries of 96 bits. Of these 96 bits 40 are used to store the page number for the hardware address, 43 are used to store the tag for the virtual address. The remaining bits are used to store the valid tags, and any future tags such as read and write protection. Figure 2.11 shows how the address translation unit uses the TLB to translate a virtual address to a physical address. The TLB works as follows: The 52 bit virtual page number is split into a 9 bit index and a 43 bit tag. The TLB also has a valid bit which indicates whether the entry at the given index has been set or not. When an address is translated the index is used to index the TLB array, and the tag stored in the TLB is compared to the one from the address being translated. If they are the same and the valid bit is set there is a hit in the TLB and the page number from the TLB is combined with the page offset to form the physical address used by the DMA units.

## 2.4.2.4 DMA Read and Write

When the accelerator wants to read or write data, it first sets the address and size signals to the starting address and the total number of 64 bit values being written or read, and asserts the read enable or write enable signal respectively. The corresponding manager unit then translates the starting address to the physical address through the address translation unit. Once the address is translated, the manager sends the request on to the either the DMA read or write unit. If the request crosses a page boundary, the manager reduces the size of the request to the DMA unit to assure that no page boundary is crossed. This is done because consecutive pages in virtual memory do

not necessarily map to consecutive pages in physical memory. Likewise, the manager translates the addresses for all the pages. Since a TLB miss takes a very large number of cycles (thousands of cycles) this hides some of the latency of the miss.

When the DMA read unit receives a request from its manager it checks if there are available tags, and if so it sends a read request using the next available tag and increments the tag counter, and decrements the total number of free tags. Because individual memory accesses cannot cross the 512 bit boundary (HTX supports a maximum of 32 outstanding requests), the DMA unit also checks if the request crosses this boundary and if so reduces the size of the data requested. Otherwise it requests the maximum number of data elements (8 64 bit data elements) or the total number of requested elements, whichever is smaller. When the DMA read unit receives a response command packet it stores the count field in that packet, and decrements it as the data packets arrive until all the data has arrived. Each data packet is pushed into the read FIFO, from which it will be read by the accelerator. Once all the data packets belonging to a single response command packet have arrived, the response packet is discarded and the number of free tags is incremented.

In the case of the DMA write unit, things work very similarly except there is no need for tags, and for receiving data. When the DMA write unit receives a request, it waits until the write queue is filled with the number of data elements needed to fulfill the next write command. This number is determined in the same manner as in the DMA read unit. It depends on the total number of data elements, and whether or not request cross the 512 bit boundary. The write command packet is only sent once all the data is in the write FIFO, since otherwise, if there is an error in the accelerator and not enough data is written to the FIFO, while the write request is already sent, the PC will hang while waiting for all the data to arrive.

## 2.4.2.5 Interrupt Handler

Interrupt Handle in the wrapper supports the interrupts caused by the device in case of address translation or execution completion. The interrupt manager is responsible for prioritizing multiple simultaneous interrupts, and indicating which of these caused an interrupt. Whenever one of these conditions occurs, the interrupt manager sets a flip-flop corresponding to the cause of the interrupt to one. This ensures that in the case of multiple simultaneous interrupts all interrupts are handled.

Next if there are multiple interrupts the interrupt manager selects the one with the highest priority. Execution completion has the highest priority, while address translation has the lowest. The IH then sets a status register which can be read by the host to a value indicating the cause of the interrupt. The manager also signals the DMA write unit that there is an interrupt request, and waits until the DMA write manager has sent the interrupt to the host. At this point the flip-flop corresponding to the interrupt being handled is reset.

Next the interrupt manager waits until the host signals that the interrupt has been handled, before sending the next interrupt, if any. This ensures that a second interrupt will not automatically overwrite the value in the status register, which indicates the cause of an interrupt. The host signals that the interrupt is handled by writing a specific value to the command register, explained in Section 2.4.2.6. Interrupts are sent over HyperTransport by writing to a memory address. This address is specified by the driver during the initialization of the device. This means that the DMA write unit is also responsible for sending interrupts.

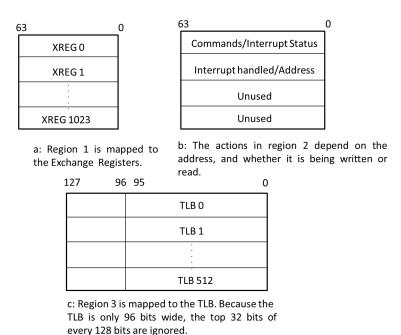

## 2.4.2.6 Memory Mapped IO

The host processor controls the FPGA device through the driver using three regions of memory mapped IO explained in Figure 2.12. The host uses these regions by mapping them into the kernel address space and accessing them as arrays of data. The FPGA device uses the IO regions as follows: The first region is mapped to the exchange registers (XREGs). The second region is used to send commands, such as EXECUTE, to the device and to get information about the status of the device such as the cause of an interrupt or the address to be translated. The third region is used for the driver to read and write directly to/from the TLB. When the host processor writes to one of these regions, a command and data packet arrive on the posted input queue. Whenever the driver writes into the memory mapped IO region, a command and data packet arrives on the input queue of the HTX bus.

A hardware component called the read-write unit handles these requests. It consists of a state machine which detects a command packet in the input queue. It checks what memory region the request belongs to and writes the data either to the XREGs or TLB in case of the first or third region, or in the case of the second region, it signals the control unit that there is a command. The control unit is also a state-machine which waits until it receives a command from the host processor. When it does, it checks what address the command was written to. If the value is written to address 0, then the accompanying data packet is interpreted as one of three commands: EXECUTE, RESET, or HANDLED. In case of EXECUTE, the control unit asserts a start signal to the accelerator for one cycle. In the case of a RESET command, the control unit asserts the reset signal for the reconfigurable accelerator, and the address translation unit. This is done to ensure that the device returns to a known state in case there was a mistake in the accelerator. The HANDLED command is sent by the driver to indicate that an interrupt has been handled. The control unit then signals the IH, which can then send the next interrupt, or wait until the next interrupt event occurs.

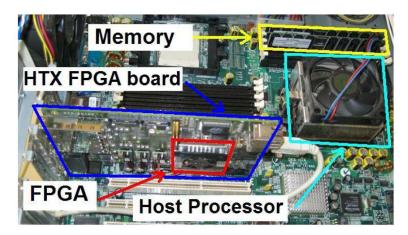

## 2.4.3 Implementation Platform

The implementation platform, used to realize the proposed system, is shown in Figure 2.13. It consists of an AMD Opteron-244 1.8GHz 64-bit host processor and a 1-GByte DDR memory at an IWILL DK8-HTX motherboard. The motherboard provides a

Figure 2.12: The three IO regions and how they are mapped to hardware

|               | High Speed | Partial         | Multiple     | Open-source |

|---------------|------------|-----------------|--------------|-------------|

| Machine       | Link       | Reconfiguration | Accelerators | Platform    |

| SRC Computers | X          |                 |              |             |