# Integrating a MOSFET into a c-Si IBC Solar Cell

Tristan Stevens

# Integrating a MOSFET into a c-Si IBC Solar Cell

by

## Tristan Stevens

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Friday July 14, 2023 at 10:30 AM.

Student number: 5628660

Project duration: October 14, 2022 – July 14, 2023

Thesis committee: Dr. René van Swaaij, Associate Professor, PVMD, TU Delft

Dr. Ir. Massimo Mastrangeli, Assistant Professor, ECTM, TU Delft

Dr. Patrizio Manganiello, Ir. David van Nijen,

Assistant Professor, PVMD, TU Delft, supervisor PhD candidate, PVMD, TU Delft, daily supervisor

This thesis is confidential and cannot be made public until July 14, 2023.

Style: TU Delft Report Style, with modifications by Daan Zwaneveld

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## Preface

This report marks the achievement of an eight-month-long thesis project and by the same time the end of my two years of SET Master at TU Delft. Studying there has been a unique experience for me. Above the scientific knowledge I acquired, traveling outside France and meeting fellow students from all places of the world was an amazing opportunity for personal enrichment. Working on that thesis was for me an unforgettably challenging and passionate experience. Integrating a MOSFET into an IBC solar cell required me to go deeper in my knowledge of PV technology but especially to learn from the beginning about the MOSFET design and operation. Furthermore, I had the opportunity to work in cleanroom laboratories, which was a total discovery.

Although it might sound like it, a thesis is nothing but an individual project. I would thus like to thank the numerous persons without whom I would not have achieved the end of the project. The first person I want to thank is my daily supervisor, David van Nijen. The work presented in this report is a direct part of his Ph.D. project, aiming to integrate power converter components into solar cells. David has continuously supported me, showing, explaining, and commenting on every step of the project. I hope that my contribution will help him toward his Ph.D. goals. Then, my gratitude comes to my supervisor, Patrizio Manganiello. The clarifying, inspiring, and supportive meetings we had helped me define my framework and progress in my work. Both David and Patrizio demonstrated investment and availability that were crucial to me. Furthermore, I would like to thank the numerous persons who assisted me during my work in the cleanroom laboratory. Paolo Sberna, Mehmet Karaman, Hugo Schellevis, Katerina Kovačević, and Daniel van der Plaats have especially helped me several times during the project.

A special thank comes to my fellow Master's students who also had graduation projects at the PVMD. They are the reason why it was a pleasure to come every morning to the university. First, to my office mates: Maria, Rahul, Mohua, and Shloka. Shloka is one of the most hardworking people I know who managed to keep me motivated by coming early in the morning and sometimes leaving late at night. A special thank you to her and Maria who generously provided free coffee all throughout the year. Moreover, along with Shriram, Mehdi, Mathijs, Mathias, Devansh, Alex, and Anson, we all formed a special lunch team that gave super fun times. I shall not forget the support provided by my friends and housemates as well. Finally, I would like to thank my family and my girlfriend for everything they did for me before and during this Master's.

Tristan Stevens Delft, July 2023

# Summary

Several promising photovoltaic (PV) concepts are supported by transistors. Along with the growth of PV capacity in the urban environment, issues related to partial shading highlight the interest in more shade-tolerant PV systems. An example of technologies improving a PV module's energy yield under partial shading is the submodule power optimizer, including a power converter that operates sub-module maximum power point tracking (MPPT). Alternately, reconfigurable PV modules enable dynamic reconfiguration of the solar cells' interconnections to optimize the energy yield depending on the irradiance distribution. Both technologies make use of transistors as fundamental components. Integrating the latter into the solar cell wafer might be a solution for cost reduction and reliability improvement and thus support such concepts. Moreover, that kind of transistor integration can have applications in solar cell-embedded electronic and digital devices.

In this thesis, a lateral metal-oxide-semiconductor field-effect transistor (MOSFET) and an interdigitated back-contacted (IBC) solar cell are integrated into the same crystalline silicon (c-Si) wafer. A combined process flow is developed to manufacture both components with a minimum number of additional steps compared to single-component manufacturing processes. One criterion for this is a high similarity in the design of the device. Therefore, a tunneling oxide passivated contact (TOPCon) solar cell structure is used, involving polycrystalline silicon (poly-Si) at the device's backside. Similarly, the MOSFET's gate is made of a highly doped poy-Si film. Ion implantation is used as a common doping process.

Both solar cells and transistors that were manufactured with the combined process flow are first characterized separately. The highest efficiencies obtained for n-type and p-type solar cells are 20.29% and 20.66%, respectively. This is achieved thanks to multiple combined passivation approaches including TOPCon, wet poly-Si etching, a front-side hydrogenated amorphous silicon (a-Si:H) film, and hydrogenated silicon nitride on both sides of the device. Different MOSFET layouts are explored to make the device able to handle relatively large currents. It is found that introducing several drain-source pairs in parallel is more efficient than increasing the channel width to reduce the on-resistance. The on-resistance is further minimized with a gate length reduction and wet chemical poly-Si etching. As expected, the comparison of PMOS and NMOS (MOSFETs built on n-type and p-type wafers, respectively) shows better on-performance for the latter. A minimum on-resistance value of 1  $\Omega$  is then obtained. However, a higher leakage current consistently seems to come along with reduced on-resistance; i.e., higher on-performance is coupled with lower off-performance. Finally, experiments are performed combining both components. Under illumination, the MOSFET exhibits lower off-performance due to the photovoltaic effect. However, this effect does not affect the on-performance of the component. The monolithically connected components exhibit I-V characteristics that depend on the applied MOSFET's gate potential. In the on-mode, the solar cell maintains more than 95% of the conversion efficiency compared to the efficiency measured with the same solar cell without the transistor. However, a non-zero current is obtained in the off-mode, exhibiting low transistor blocking capability. Nevertheless, the large difference in characteristics obtained between the on- and off-modes proves the feasibility of integrating a solar cell and a transistor on the same substrate with a minimum number of additional processing steps.

# Contents

| Pr | етасе                           | <del>)</del>                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ш                                                                     |

|----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Su | mma                             | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                     |

| No | men                             | clature                                                                                                                                                                                                                                                                                                                                                                                                                                            | xiii                                                                  |

| 1  | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | An Energy-Dependant Society Solar Energy Potential Power Electronics in Solar Systems Integration of a Transistor Research Questions and Report Outline                                                                                                                                                                                                                                                                                            | 1<br>1<br>2<br>2<br>5<br>6                                            |

| 2  | Sola                            | ar Cell and MOSFET Theory                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                                                                     |

|    | 2.2                             | Semiconductors  2.1.1 Definition  2.1.2 The P-N Junction  2.1.3 Charge Carrier Generation and Recombination Photovoltaic Technology  2.2.1 Solar Radiation  2.2.2 Working Principle of a Solar Cell  2.2.3 Solar Cell External Parameters  2.2.4 Crystalline Silicon Solar Cell  2.2.5 Interdigitated Back-Contacted Solar Cell  MOSFET  2.3.1 Structure  2.3.2 Operation  2.3.3 Static Electrical Parameters  2.3.4 Dynamic Electrical Parameters | 7<br>7<br>8<br>9<br>9<br>10<br>11<br>11<br>12<br>12<br>13<br>14<br>16 |

| 3  | Dev                             | rice Fabrication and Characterization Methods                                                                                                                                                                                                                                                                                                                                                                                                      | 19                                                                    |

|    | 3.1                             | Microfabrication Processes  3.1.1 Thermal Oxidation  3.1.2 Plasma-Enhanced Chemical Vapor Deposition  3.1.3 Low-Pressure Chemical Vapor Deposition  3.1.4 Evaporation  3.1.5 Photolithography  3.1.6 Etching  3.1.7 Lift-Off  3.1.8 Ion Implantation                                                                                                                                                                                               | 19<br>19<br>20<br>20<br>21<br>21<br>21<br>22<br>22                    |

|    | 3.2                             | Measurement Tools  3.2.1 Lifetime Measurement  3.2.2 Spectroscopic Ellipsometry  3.2.3 Microelectronics Components Measurement  3.2.4 Solar Simulation                                                                                                                                                                                                                                                                                             | 22<br>22<br>23<br>24<br>24                                            |

|    | 3.3                             | Combined Manufacturing Process Flow  3.3.1 Zero-Layer  3.3.2 MOSFET gate oxide  3.3.3 Passivated poly-Si Contact and Texture  3.3.4 Back Contacts and Gate Patterning  3.3.5 Backside Implantation                                                                                                                                                                                                                                                 | 24<br>25<br>25<br>25<br>25<br>25<br>27                                |

viii Contents

|    | 3.4                         | 3.3.8 Process flow summary                                                                                                                                                                                                                                                                                                                                             | 27<br>28<br>29<br>29                         |

|----|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 4  | <b>Sola</b> 4.1 4.2 4.3 4.4 | Kinks in the J-V Characteristics       3         Effect of Post-Metallization Thermal Annealing       3         Effect of the Manufacturing Method       3                                                                                                                                                                                                             | 33<br>34<br>35<br>37                         |

| 5  | 5.1<br>5.2<br>5.3<br>5.4    | Parameters Derivation Methods       3         Effect of Thermal Annealing       4         Effect of the Design       4         5.3.1 On-Resistance       4         5.3.2 Leakage Current       4         Effect of the Manufacturing Methods       4         5.4.1 Threshold Voltage       4         5.4.2 On-Resistance       4         5.4.3 Leakage Current       4 | 39<br>10<br>11<br>12<br>13<br>14<br>15<br>15 |

| 6  | 6.1<br>6.2                  | Effect of Light on the MOSFET                                                                                                                                                                                                                                                                                                                                          | 19<br>19<br>50<br>56                         |

| 7  | 7.1                         | Conclusion                                                                                                                                                                                                                                                                                                                                                             | 5 <b>7</b><br>57                             |

| Re | fere                        | nces 5                                                                                                                                                                                                                                                                                                                                                                 | 59                                           |

# List of Figures

| 1.1<br>1.2 | Simplified global energy production per energy resource from 1971 to 2019 [2] Comparing finite and renewable planetary energy reserves (Terawattyears). Total recoverable reserves are shown for finite resources. Yearly potential is shown for the | 1      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.3        | renewables [5]                                                                                                                                                                                                                                       | 2      |

|            | Germany in 2021 [8]                                                                                                                                                                                                                                  | 3      |

| 1.4        | An example of a transformer-less inverter unit as could be used for residential PV systems [11]                                                                                                                                                      | 3      |

| 2.1        | Energy band diagram for: (a) intrinsic semiconductor; (b) n-type doped semiconductor;                                                                                                                                                                | 0      |

| 2.2        | (c) p-type doped semiconductor [11]                                                                                                                                                                                                                  | 8<br>8 |

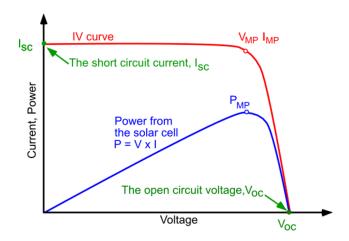

| 2.2<br>2.3 |                                                                                                                                                                                                                                                      | 10     |

| 2.3        | Solar spectrum [11]                                                                                                                                                                                                                                  | 11     |

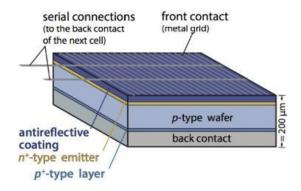

| 2.5        | Scheme of an FTC crystalline silicon cell, with a p-type wafer [11].                                                                                                                                                                                 | 12     |

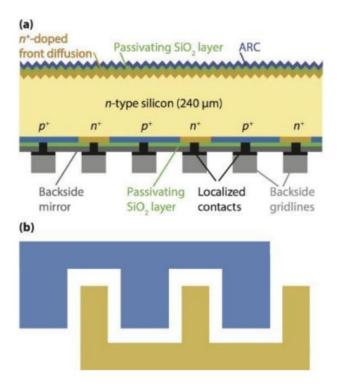

| 2.6        | (a) Side view of the structure of an n-type IBC solar cell; (b) backside contact [11]                                                                                                                                                                | 13     |

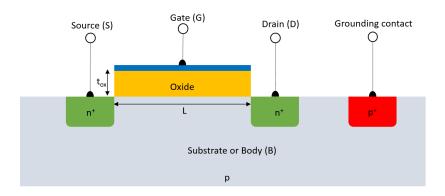

| 2.7        | Architecture of an N-channel enhancement mode MOSFET                                                                                                                                                                                                 | 14     |

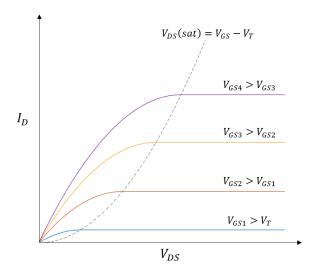

| 2.8        | Abacus of $I_D - V_{DS}$ curves for an n-channel enhancement mode MOSFET                                                                                                                                                                             | 14     |

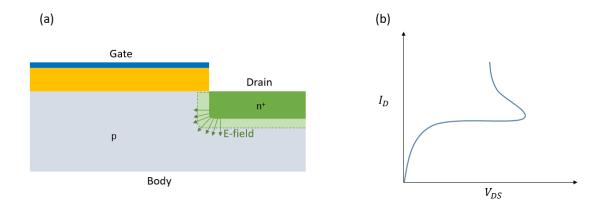

| 2.9        | (a) curvature effect on the electric field in the drain junction; (b) current-voltage charac-                                                                                                                                                        | '-     |

| 2.5        | teristic showing the snapback breakdown effect                                                                                                                                                                                                       | 16     |

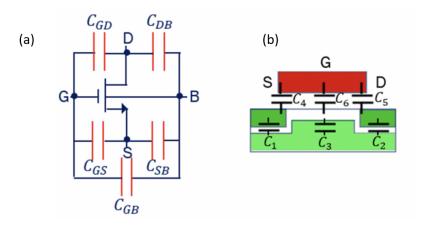

| 2 10       | (a): symbolic equivalent circuit of a MOSFET in high-frequency regime; (b): Represen-                                                                                                                                                                | 10     |

| 2.10       | tation of capacitances in a MOS device [53]                                                                                                                                                                                                          | 17     |

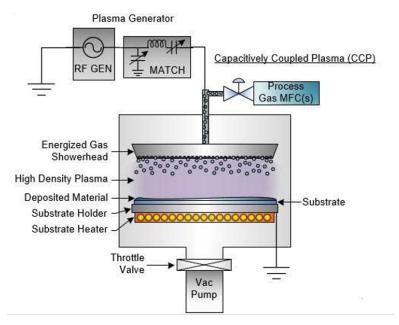

| 3.1        | Diagram of direct PECVD processor reactor [57]                                                                                                                                                                                                       | 20     |

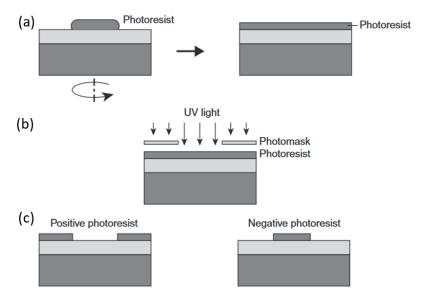

| 3.2        | Photolithography process: (a) photoresist coating; (b) exposure; (c) development [55].                                                                                                                                                               | 21     |

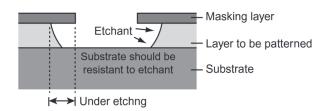

| 3.3        | Wet etching (side view) [55]                                                                                                                                                                                                                         | 22     |

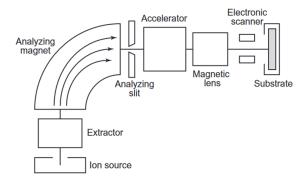

| 3.4        | Ion implantation setup [55].                                                                                                                                                                                                                         | 23     |

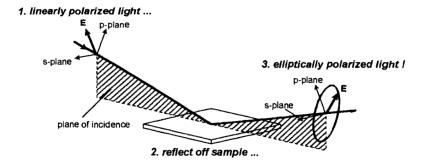

| 3.5        | Interaction of polarized light with a sample [63]                                                                                                                                                                                                    | 24     |

| 3.6        | Gate oxide layer creation: (a) dry thermal oxidation; (b) photolithography; (c) oxide etch-                                                                                                                                                          |        |

| 27         | ing and photoresist stripping                                                                                                                                                                                                                        | 25     |

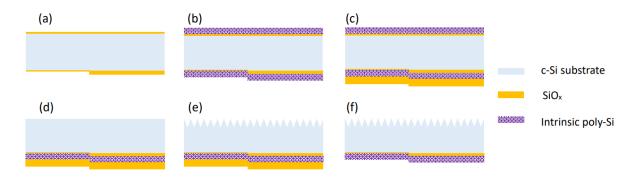

| 3.7        |                                                                                                                                                                                                                                                      |        |

|            | SiO <sub>x</sub> PECVD; (d) Front-side poly-Si stripping; (e) Front-side texturing; (f) Back-side SiO <sub>x</sub> stripping.                                                                                                                        | 26     |

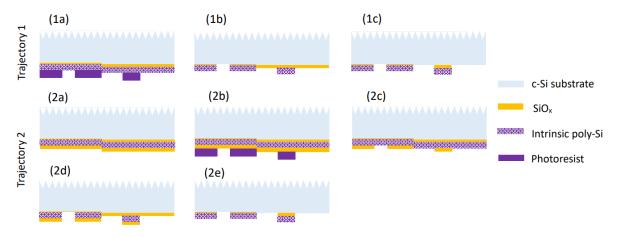

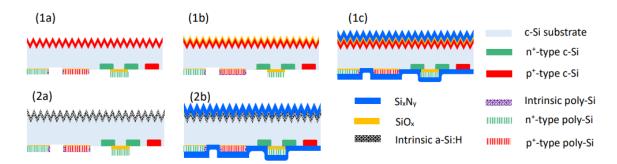

| 20         | Back-contacts and gate patterning: (1a) - (1c) dry poly-Si etching trajectory; (2a) - (2e)                                                                                                                                                           | 20     |

| 3.8        | wet poly-Si etching trajectory                                                                                                                                                                                                                       | 26     |

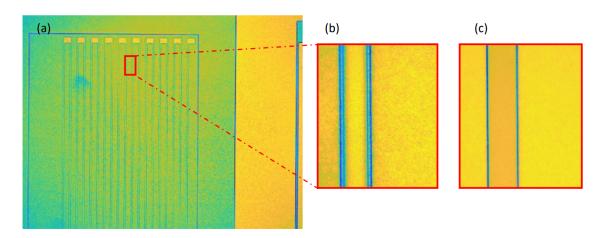

| 3.9        | poly-Si pattern. (a) part of one MOS gate (left) and part of one solar cell (right); (b) wafer                                                                                                                                                       | 20     |

| 3.9        | N6 wet poly-Si etched MOS gate; (c) wafer N1 dry poly-Si etched MOS gate                                                                                                                                                                             | 27     |

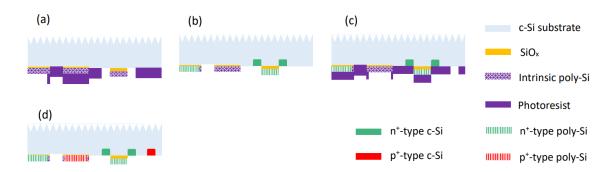

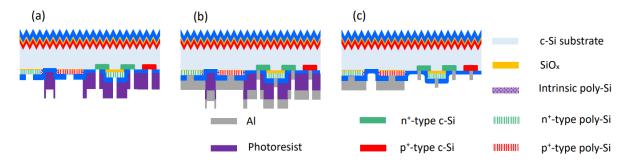

| 3 10       | Back-side doping process. (a) photolithography before Ph implantation; (b) Ph implanta-                                                                                                                                                              | 21     |

| 3.10       | tion and PR stripping; (c) photolithography before B implantation; (d) B implantation and                                                                                                                                                            |        |

|            |                                                                                                                                                                                                                                                      | 28     |

| 2 11       | Surface passivation: (1a) ion implantation; (1b) NAOS; (1c) double-side Si <sub>x</sub> N <sub>y</sub> PECVD;                                                                                                                                        | 20     |

| 5.11       | (2a) (i)a-Si:H PECVD; (2b) double-side $Si_xN_y$ PECVD                                                                                                                                                                                               | 28     |

| 3 12       | Metallization: (a) Photolithography; (b) Al evaporation; (c) Lift-off                                                                                                                                                                                | 29     |

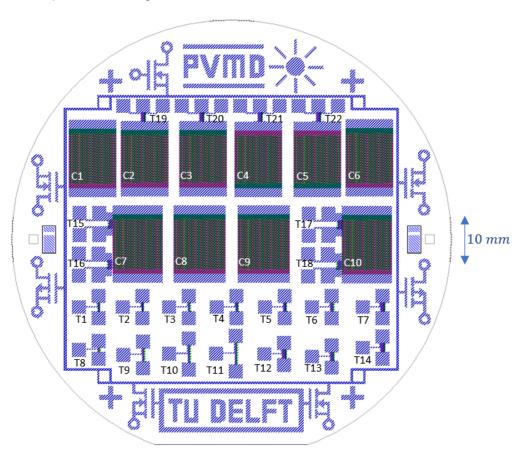

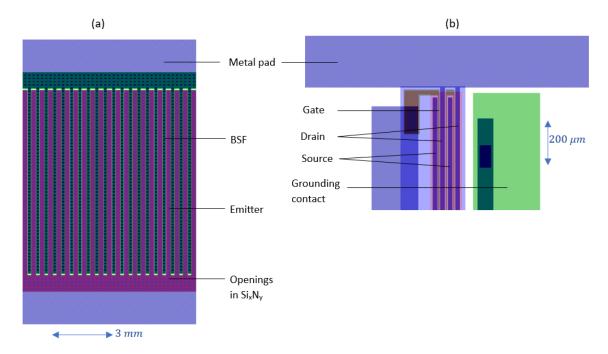

|            | Full view of the device backside, from L-Edit software.                                                                                                                                                                                              | 30     |

|            | Layouts from L-Edit software: (a) solar cell C1; (b) top of transistor T2                                                                                                                                                                            | 31     |

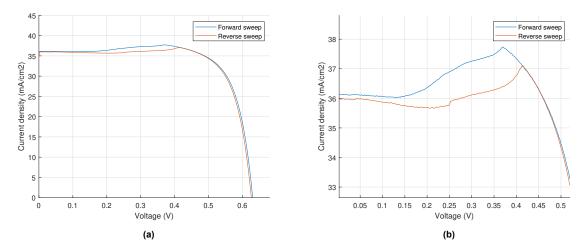

| 4.1        | Kinks in the J-V characteristic obtained from forward and reverse voltage sweeps: (a)                                                                                                                                                                |        |

|            | full characteristic; (b) zoom in the kink region                                                                                                                                                                                                     | 34     |

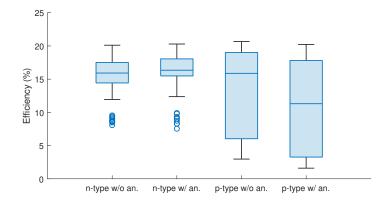

| 42         | Impact of post-metallization annealing on n-type and p-type solar cells                                                                                                                                                                              | 34     |

X List of Figures

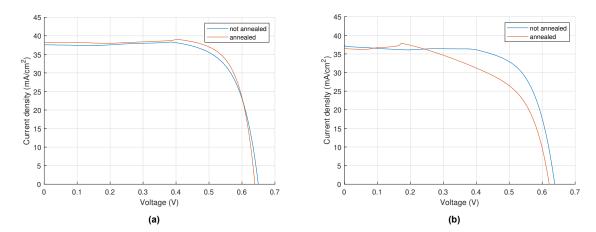

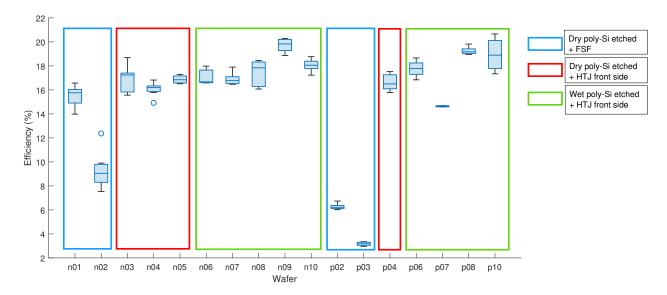

| 4.3<br>4.4 | J-V curves before and after annealing: (a) n-type substrate; (b) p-type substrate Comparison of solar cell power conversion efficiencies issued from different processes.                                                                                                                                                                                                  | 35<br>36   |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

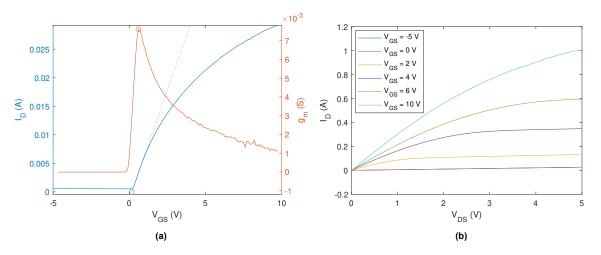

| 5.1        | Characteristics of NMOS T2 from wafer N8: (a) $I_D$ - $V_{GS}$ characteristic in solid blue; $g_m$ - $V_{GS}$ in red; tangent at the maximum slope in dotted blue. (b) $I_D$ - $V_{DS}$ characteristics for                                                                                                                                                                |            |

| 5.2        | increasing gate voltage                                                                                                                                                                                                                                                                                                                                                    | 39         |

|            | annealing. (a) NMOS from wafer P8; (b) PMOS from wafer N2                                                                                                                                                                                                                                                                                                                  | 40         |

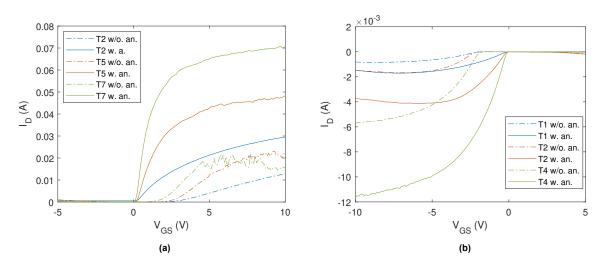

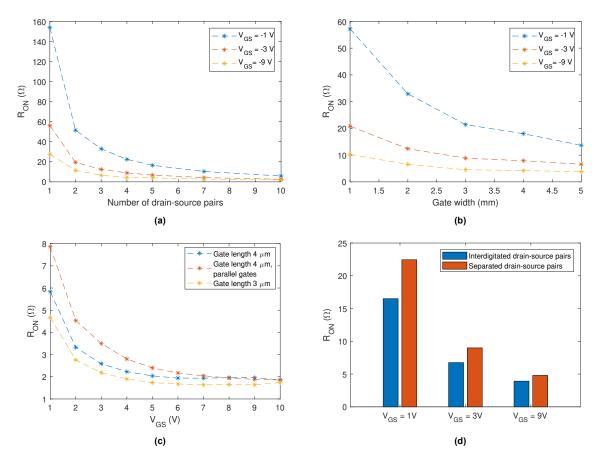

| 5.3        | MOSFET design patterns: (a) interdigitated drain-source pairs with an S-shape gate; (b) several gates in parallel (T12); (c) separated drain-source pairs.                                                                                                                                                                                                                 | 42         |

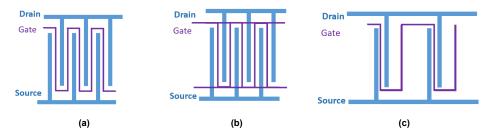

| 5.4        | On-resistances of PMOSs from wafer N6 at several gate-source voltages for (a) variable drain-source voltage pairs, $L=4~\mu\text{m}$ , $W=2~\text{mm}$ ; (b) variable gate widths, $L=4~\mu\text{m}$ ;                                                                                                                                                                     | 42         |

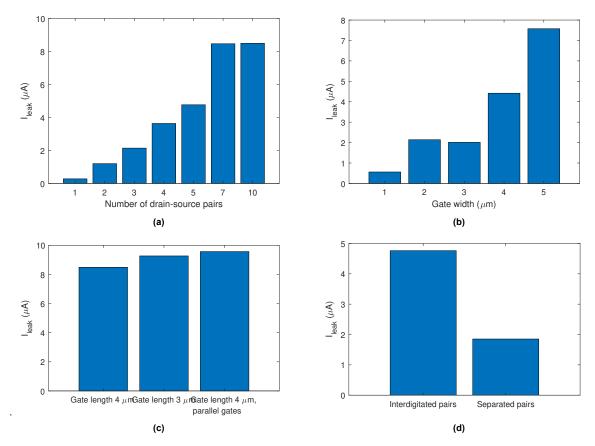

| 5.5        | 3 drain-source pairs; (c) several gate lengths and designs, $W=2$ mm; 10 drain-source pairs; (d) Interdigitated and separated drain-source pairs, $L=4~\mu\text{m},W=2$ mm; 5 pairs. Leakage current of PMOS's from wafer N5 for: (a) variable drain-source voltage pairs, $L=4~\mu\text{m},W=2$ mm; (b) variable gate widths, $L=4~\mu\text{m},3$ drain-source pairs; (c) | 43         |

|            | several gate lengths and designs, $W=2$ mm, 10 drain-source pairs; (d) Intricated and separated drain-source pairs, $L=4$ $\mu$ m, $W=2$ mm, 5 pairs                                                                                                                                                                                                                       | 44         |

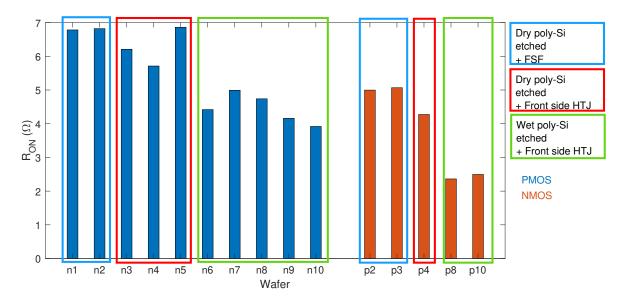

| 5.6        | On-resistance of PMOS at $V_{GS}$ = -8V and NMOS at $V_{GS}$ = 8V                                                                                                                                                                                                                                                                                                          | 46         |

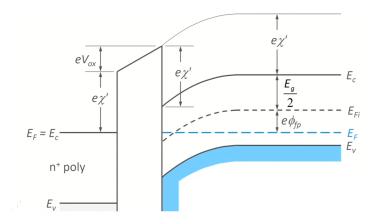

| 5.7        | Energy band diagrams of MOS junctions involving highly doped n <sup>+</sup> poly-Si as the gate                                                                                                                                                                                                                                                                            |            |

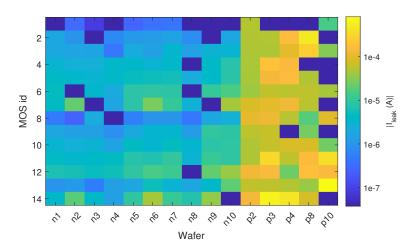

| 5.8        | and p-type body [70]                                                                                                                                                                                                                                                                                                                                                       | 46         |

| 0.0        | blue pixels are related to dysfunctional devices                                                                                                                                                                                                                                                                                                                           | 47         |

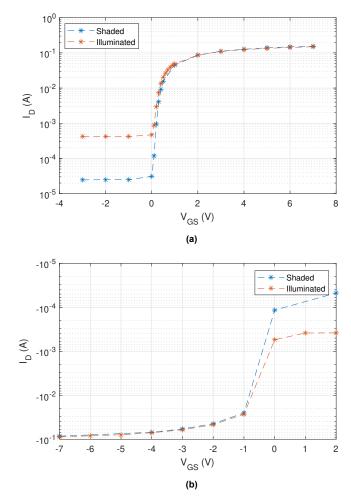

| 6.1        | I <sub>D</sub> -V <sub>GS</sub> characteristics for dark and illuminated: (a) NMOS T22 from wafer p8; (b) PMOS                                                                                                                                                                                                                                                             | <b>5</b> 0 |

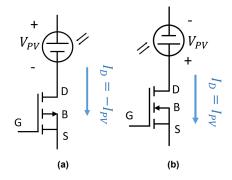

| 6.2        | T21 from wafer n9                                                                                                                                                                                                                                                                                                                                                          | 50         |

|            | n6; (b) C2 and NMOS T19 of wafer p6                                                                                                                                                                                                                                                                                                                                        | 51         |

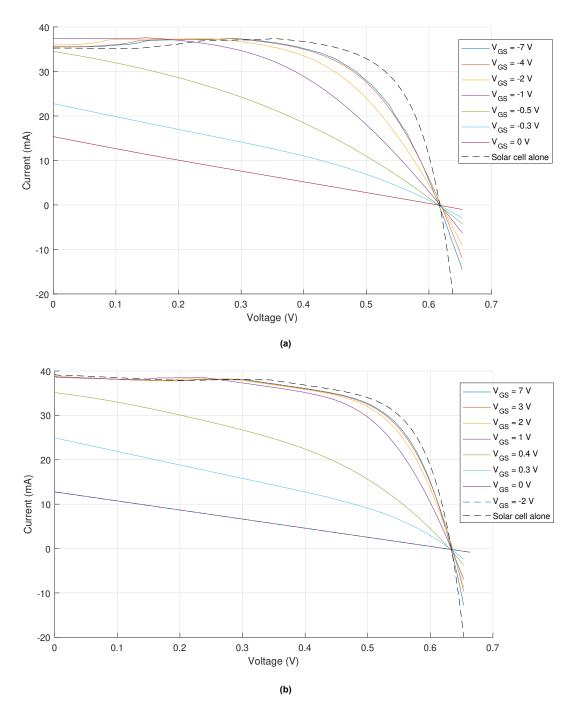

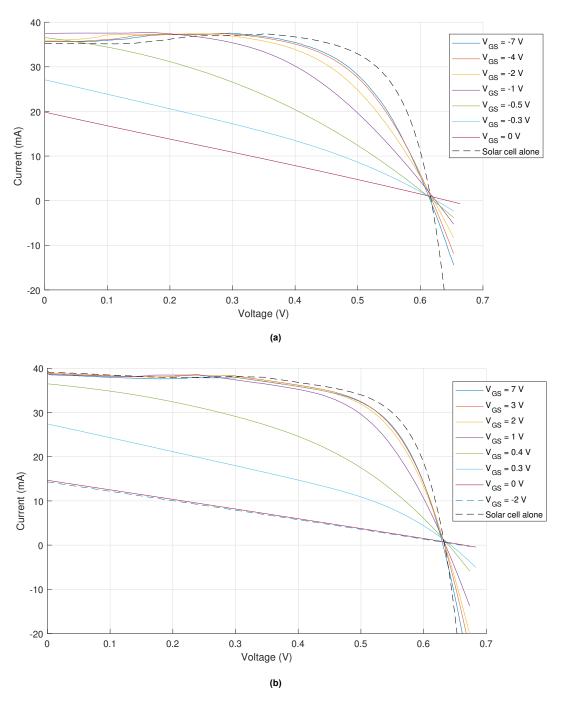

| 6.3        | I-V characteristics of monolithically connected solar cell and transistor: (a) n-type solar                                                                                                                                                                                                                                                                                |            |

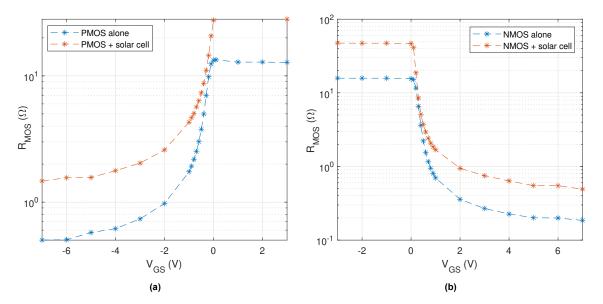

| 6.4        | cell and PMOS; (b) p-type solar cell and NMOS. The transistor is in the dark Comparison of the MOS equivalent resistance (off- and on-resistance) with and without                                                                                                                                                                                                         | 52         |

|            | including the solar cell in the measurement: (a) PMOS case; (b) NMOS case                                                                                                                                                                                                                                                                                                  | 53         |

| 6.5        | I-V characteristics of monolithically connected solar cell and transistor: (a) n-type solar                                                                                                                                                                                                                                                                                | 54         |

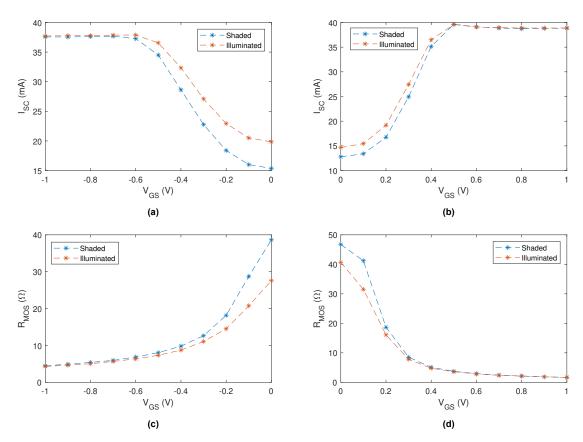

| 6.6        | cell and PMOS; (b) p-type solar cell and NMOS. The transistor is illuminated Evolution of the short-circuit current and MOS equivalent resistance with the gate potential in the dark and under illumination: (a) short-circuit current with the n-type solar cell and PMOS; (b) short-circuit current with the p-type solar cell and NMOS; (c) PMOS                       | 54         |

| 6.7        | resistance; (d) NMOS resistance                                                                                                                                                                                                                                                                                                                                            | 55<br>55   |

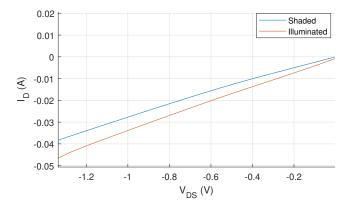

| 6.7        | Illuminated and dark MOS $I_D$ - $V_{DS}$ characteristic at $V_{GS}$ = 0 V                                                                                                                                                                                                                                                                                                 | 55         |

# List of Tables

| 3.1 | Wet poly-Si etching time.                                                                                                                                                             | 26 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | Implantation atoms, doses, and energies for the wafers including an FSF                                                                                                               |    |

|     | Process flows comparison                                                                                                                                                              |    |

|     | Parallel MOS number for transistors T1-7 and T12-14. Common gate width: 2mm                                                                                                           |    |

| 3.5 | Gate width for transistors T8-11. 3 parallel MOS                                                                                                                                      | 31 |

| 4.1 | Best-performing n-type and p-type solar cells per manufacturing process                                                                                                               | 36 |

| 5.1 | Comparison of the threshold voltage, leakage current, and maximum transconductance of annealed and not annealed MOSs. The NMOSs and the PMOSs are from wafers P8 and N2, respectively | 41 |

| 5.2 | Average and standard deviation of PMOS and NMOS threshold voltages per manufacturing process.                                                                                         |    |

| 5.3 | • ,                                                                                                                                                                                   |    |

|     |                                                                                                                                                                                       |    |

| 6.1 | Performance of the n- and p-type solar cells with or without the MOSFET. Comparison of the fill factor, short-circuit current, and efficiency.                                        | 51 |

# Nomenclature

## Abbreviations

| Abbreviation                   | Definition                                        |

|--------------------------------|---------------------------------------------------|

| :H                             | Hydrogenated                                      |

| a-Si                           | Amorphous Silicon                                 |

| AC                             | Alternative Current                               |

| ARC                            | Anti-Reflective Coating                           |

| AM                             | Air Mass                                          |

| В                              | Boron                                             |

| BHF                            | Buffered Hydrogen Fluoride                        |

| BJT                            | Bipolar Junction Transistor                       |

| BSF                            | Back-Surface Field                                |

| c-Si                           | Crystalline Silicon                               |

| CMOS<br>CVD                    | Complementary Metal-Oxide-Semiconductor           |

| DC                             | Chemical Vapor Deposition Direct Current          |

| EKL                            | Else Kooi Laboratory                              |

| ESP                            | Electrical Sustainable Power                      |

| FBC                            | Front-Back Contacted                              |

| FSF                            | Front-Surface Field                               |

| HTJ                            | HeTeroJunction                                    |

| IBC                            | Interdigitated Back-Contacted                     |

| IC                             | Integrated Circuit                                |

| IEA                            | International Energy Agency                       |

| LCOE                           | Levelized Cost Of Electricity                     |

| LPCVD                          | Low-Pressure Chemical Vapor Deposition            |

| MEMS                           | MicroElectroMechanical Systems                    |

| MOS                            | Metal-Oxide-Semiconductor                         |

| MOSFET                         | Metal-Oxide-Semiconductor Field-Effect Transistor |

| MPP                            | Maximum Power Point                               |

| MPPT                           | Maximum Power Point Tracking                      |

| MSE                            | Mean Square Error                                 |

| NAOS                           | Nitric Acid Oxidation of Silicon                  |

| NMOS                           | p-type MOS                                        |

| OSC                            | Organic Solar Cell                                |

| PE PEON P                      | Power Electronics                                 |

| PECVD                          | Plasma-Enhanced Chemical Vapor Deposition         |

| Ph                             | Phosphorus  The MOS                               |

| PMOS                           | n-type MOS                                        |

| poly-Si<br>PV                  | Poly-crystalline Silicon Photovoltaic             |

| QSSPC                          | Quasi-Steady State PhotoConduction                |

| SE                             | Spectroscopic Ellipsometry                        |

| Si                             | Silicon                                           |

| SiO <sub>x</sub>               | Silicon Oxide                                     |

| Si <sub>x</sub> N <sub>v</sub> | Silicon Nitride                                   |

| SRH                            | Shockley-Read-Hall                                |

| STC                            | Standard Test Conditions                          |

| 510                            | Otalida d 163t Odifutions                         |

xiv List of Tables

| Abbreviation | Definition                      |

|--------------|---------------------------------|

| TMAH         | TetraMethylAmmonium Hydroxide   |

| TOPCon       | Tunnel Oxide Passivated Contact |

| UV           | Ultraviolet                     |

## Symbols

| Symbol                   | Definition                                   | Unit/Value                       |

|--------------------------|----------------------------------------------|----------------------------------|

| $\overline{A}$           | Area                                         | $[m^2]$                          |

| C                        | Capacitance                                  | [F]                              |

| $E_C$                    | Conduction energy                            | [eV]                             |

| $E_V$                    | Valence energy                               | [eV]                             |

| $E_F$                    | Fermi energy                                 | [eV]                             |

| $E_g$                    | Bandgap energy                               | [eV]                             |

| $E_{ph}$                 | Photon energy                                | [J]                              |

| FF                       | Fill factor                                  | [-]                              |

| G                        | Irradiance                                   | $[W/m^2]$                        |

| $g_m$                    | Transistor gain                              | $[\Omega^{-1}]$                  |

| $I_D$                    | Drain current                                | [A]                              |

| $I_{MP}$                 | Maximum power current                        | [A]                              |

| $I_{SC}$                 | Short-circuit current                        | [A]                              |

| L                        | Gate length                                  | $[\mu m]$                        |

| $P_{in}$                 | Input power                                  | [W]                              |

| $P_{MP}$                 | Maximum power                                | [W]                              |

| $Q_{SD}^{\prime}$        | Inversion layer charge surface density       | [C/m <sup>2</sup> ]              |

| $Q_{SD}^{	ilde{\prime}}$ | Equivalent oxide charge surface density      | [C/m <sup>2</sup> ]              |

| $R_{ON}^{-}$             | ON-resistance                                | $[\Omega]$                       |

| t                        | Time                                         | [s]                              |

| $t_{\sf ox}$             | Oxide thickness                              | [nm]                             |

| $V_{bi}$                 | Built-in voltage                             | [V]                              |

| $V_{DS}$                 | Drain-source voltage                         | [V]                              |

| $V_{GS}$                 | Gate-source voltage                          | [V]                              |

| $V_{MP}$                 | Maximum power voltage                        | [V]                              |

| $V_{OC}$                 | Open-circuit voltage                         | [V]                              |

| $V_T$                    | Threshold voltage                            | [V]                              |

| $V_{T(N/P)}$             | (N/P)MOS threshold voltage                   | [V]                              |

| W                        | Gate width                                   | [ $\mu$ m]                       |

| $\theta$                 | Angle                                        | [°]                              |

| $\lambda$                | Wavelength                                   | [nm]                             |

| $\eta$                   | Efficiency                                   | [%]                              |

| $\mu_{n/p}$              | Electron/hole mobility                       | [cm <sup>2</sup> /(V.s)]         |

| $\epsilon_{OX}$          | Oxide permittivity                           | [F/m]                            |

| $\phi_{f(p/n)}$          | Intrinsic-(p/n)type Fermi level difference   | [V]                              |

| $\phi_{ms}$              | Metal-semiconductor work function difference | [V]                              |

| $\tau$                   | Lifetime or duration                         | [s]                              |

| $\overline{c}$           | Light celerity                               | 3.10 <sup>8</sup> m/s            |

| h                        | Planck's constant                            | $6.626.10^{-34} \; \mathrm{J.s}$ |

## Introduction

#### 1.1. An Energy-Dependant Society

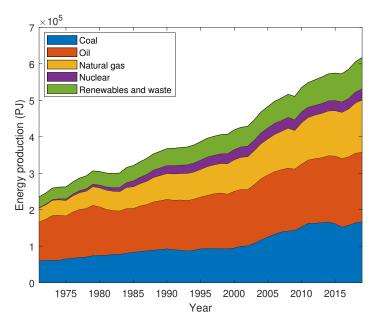

Our modern industrialized society experiences exponential global growth. In 1972, Meadows et al. analyzed trends in major categories, namely the world population, food, industry, capital, and non-renewable resources consumption, and concluded that their growth would eventually hit the physical world limits, leading to a collapse of society before 2100 [1]. These five sectors have in common a direct or indirect need for energy to develop. Hence, one observes an increase in energy production, regardless of the resource, as shown in Figure 1.1. The latter displays the global energy production evolution, from 1971 to 2019, according to the International Energy Agency (IEA) [2]. Despite the growth of nuclear and renewable energies, fossil fuel-based energies (coal, oil, and natural gas) have always dominated more than 80% the global energy production. However, it causes important emissions of greenhouse gases, altering the climate and thus threatening the conditions that make human life possible in many areas on Earth [3].

Figure 1.1: Simplified global energy production per energy resource from 1971 to 2019 [2].

The need to tightly reduce fossil fuel consumption is thus motivated by both the finite amount of such non-renewable natural resources and limiting climate change. To that end, the United Nations has defined a set of 17 goals for sustainability, among which the one for affordable and clean energy. That goal includes the target of increasing substantially the share of renewable energy in the global energy

mix by 2030 [4].

#### 1.2. Solar Energy Potential

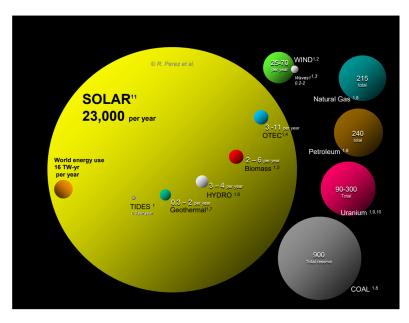

Solar energy is one form of renewable energy, consisting of converting the Sun's radiation into electricity or heat. According to Perez et al., that source has, by far, the highest energy yield potential among all forms of energy sources [5]. Figure 1.2 shows that solar energy received by emerged continents only has an energy production potential of 23000 TW-yr/year, much higher than the World energy use, which is 16 TW-yr/year.

**Figure 1.2:** Comparing finite and renewable planetary energy reserves (Terawattyears). Total recoverable reserves are shown for finite resources. Yearly potential is shown for the renewables [5].

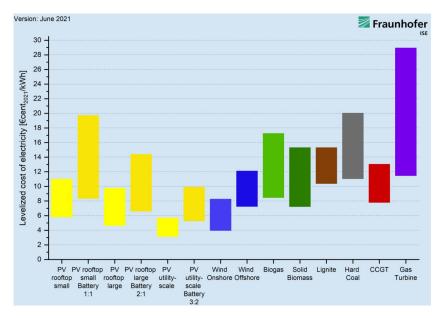

Another advantage of solar energy over the other forms of energy is the low cost. According to the Fraunhofer Institute, the levelized cost of electricity (LCOE) of photovoltaics (PV) was among the lowest LCOEs in Germany in 2021. As depicted in Figure 1.3, large PV systems (at utility-scale) produce the cheapest electricity among all the different types of renewable energy and conventional power plants. Including batteries and reducing the PV system size increase the LCOE; however, even in the most expensive case (small PV system on rooftops with a battery), it competes with most of the electricity generated from fossil fuels. Worldly, the global weighted average LCOE was 0.041 €/kWh. That value has decreased by about 17% on a year-to-year basis in the last 11 years [6]. Along with the LCOE decrease, global PV installation increases at an accelerating pace. Hence, according to the International Renewable Energy Agency (IRENA), the World PV generation was 1,047 GW in 2013, against 137 GW in 2022 [7].

## 1.3. Power Electronics in Solar Systems

Power electronics (PE) plays a major role in the operation of photovoltaic (PV) systems. One of the main applications of PE is maximum power point tracking (MPPT), using a DC-DC converter. Since the PV current-voltage characteristic depends on variable parameters such as solar irradiance and temperature, the voltage for which the output power is maximum needs to be adjusted constantly. MPPT optimizes the power output of the PV system. To do so, the DC-DC converter regulates the input and output voltage ratio via a high-frequency switch that operates according to a duty cycle controlled by an algorithm [9]. Another fundamental application of PE is converting the direct current (DC) produced by the solar panels into an alternating current (AC) through DC-AC converters, also called inverters. This is necessary for grid-connected PV systems, which represent more than 99% of the overall worldwide PV installations [10]. Along with the recent rapid growth of the PV capacity through several sizes of PV systems [7], a large variety of PE architectures in PV systems have been developed. The inverter topol-

Figure 1.3: LCOE of renewable energy technologies and conventional power plants at locations in Germany in 2021 [8].

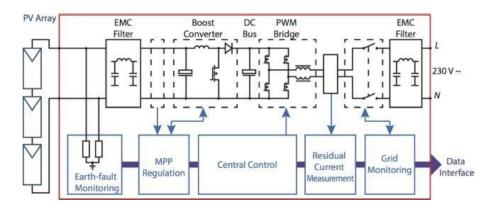

ogy is classified following the scale of the PV system to which it is connected. String and multi-string inverters are connected to one and several strings of PV modules (series connected PV modules), respectively; central inverters work with PV arrays (parallel connected strings); module inverters or micro-inverters are adapted to one or a few PV modules [10]. Figure 1.4 illustrates an example of inverter unit for residential use [11]. It includes for MPPT a type of DC-DC converter, called boost converter, and a PWM bridge for DC to AC conversion. A data interface monitors the whole conversion process.

Figure 1.4: An example of a transformer-less inverter unit as could be used for residential PV systems [11].

Several criteria must be taken into account to correctly choose the topology and size of the PV system inverter, usually requiring a cost-benefit analysis [12]. Generally, one seeks consequent energy harvesting and minimum cost. Location-related irradiance non-uniformity and partial shading scenarios affect the former point. If modules of one string are unequally irradiated, the string current is typically limited by the one from the least irradiated module. The power output of the modules with higher irradiation is thus lower than at their maximum power point. Consequently, while central inverters are preferable for PV arrays subjected to a uniform irradiance thanks to their higher efficiency and low cost, smaller-scale inverters can be preferable for systems that suffer from non-uniform irradiance or partial shading and hence need to be more resilient [10]. For small PV systems surrounded by an urban environment, MPPT with higher granularity is necessary. This can be done by either implementing more DC-DC converters or smaller inverters such as module inverters, forming so-called AC modules [13].

However, partial shading can also occur at a module scale. Since PV modules generally include single strings of series-connected solar cells, non-uniform irradiance or minor partial shading on one cell reduces the string current, hence a reduced global output power. If the cell is more severely shaded, the string current mismatch results in that cell consuming the energy produced by the unshaded other cells. The problematic cell thus achieves a high reverse voltage that can cause a breakdown, which in turn causes local overheating that can imply irreversible damage. Besides, the whole string does not produce any output power [11, 14]. Partial shading effects are generally limited by separating solar cell strings into several substrings, each containing one bypass diode [10, 15]. Consequently, if a substring is shaded, the current flows through the related bypass diode to not perturb the unshaded substrings. However, the three-bypass-diodes architecture results in the power loss of one-third of a module in the case of only one partially shaded cell. Another drawback is that modules containing many high-efficiency solar cells still can reach very high temperatures if only three bypass diodes are used [15]. Several alternative approaches aim to increase the partial shading tolerance of PV modules. The first idea is introducing more bypass diodes, shortcutting either a smaller group of cells or even one single cell [16]. A second possible solution is to introduce submodule power converters. In [17], Leuenberger et al. propose AC modules integrating three parallel substrings DC-DC converters to proceed in submodule MPPT. The investigated topology reveals an achievable efficiency of 94.5% using high-performance electronic devices. Besides improving the partial shading resilience of PV modules in an urban environment, module-embedded PE can boost a solar farm's energy production per land area. [18] introduces submodule MPPT to allow resilience to PV array interrow shading. Consequently, the distance between rows can decrease, hence a better ground-cover ratio. Finally, a third approach is a reconfigurable series-parallel PV module architecture. The idea is to keep the cells fully connected in series for current minimization when the module is unshaded and switch to a parallel connection of solar cell strings when shading occurs. Calcabrini et al. have investigated and module topology of 6 reconfigurable blocks of solar cells and found that it can increase the energy yield by 12.7% compared to a module with 6 bypass diodes, for a module shaded 32% of the time [19].

However, all these latter approaches need the integration of PE components that is not yet optimal. They are usually included in the junction box, or laminated or mounted to the module frame. One drawback is then an increased wiring complexity [20]. Solar cell-embedded electronic components appear to be a promising solution that can facilitate further implementation of PE in PV. Above the less bulky integration and simpler wiring that help the device be more portable, the reliability can be improved. Although integrated components are less accessible and thus less replaceable, integrated components into the cell can allow monolithic electrical connections instead of solder joints. The latter is one main cause of failure in transistors [21, 22], which have today the most critical reliability of the power converter [23]. In turn, the latter has the lowest lifetime of the PV system [24]. Another argument is the potential cost reduction. Integrating a power converter into cells avoids the installation cost of such a device in the PV system, usually separated from the modules. In proportion, the fraction of a PV system cost related to this cost has recently increased due to the important cost decline in PV panels [10]. Manufacturing electrical components and a solar cell on the same substrate could also reduce production costs. However, for this, the manufacturing processes of the solar cells and the electrical components must be similar to minimize the number of necessary additional processes to build such a device. Solar cell-embedded PE components can support the integration of power converters that work for a small number of cells, hence increasing the MPPT granularity and making PV systems more shade resilient. Finally, besides PE, integrating electronic components such as diodes and transistors can have applications for modern cell-level bypass circuits, which aim to replace simple diodes to reduce power losses [16, 25].

To the best of the author's knowledge, solar cell-integrated components of power converters have been little explored. Shawly et al. have developed a complete on-chip cell-level MPPT system, including a DC-DC converter and a Ripple Correlation Control circuit that controls the converter [26]. However, this integrated circuit (IC) is not built on the same substrate as the solar cell. Imtiaz et al. have made efforts towards integrating power transistors, inductors, capacitors, and diodes on solar cells [27]. Nevertheless, this thesis is based on the work of van Nijen et al., who explored the integration of power converter components into c-Si solar cells and considered ease of integration as an essential criterion [28]. That work explores solar cell native capacitance and inductance as potential components for a

power converter. Diodes can easily be integrated thanks to their very similar structure to solar cells and mature research on that subject [29]. Finally, the transistor may be the least similar component to solar cells, and one must closely investigate its integration.

## 1.4. Integration of a Transistor

This thesis specifically focuses on integrating a transistor into a solar cell. Combining both components on a single c-Si-based device has recently been explored, especially from integrating a solar cell into ICs perspective, giving the name of on-chip solar cells [30–34]. Most of these works are based on the structure of complementary metal oxide semiconductor (CMOS) technologies, being similar to one of the solar cells, both involving PN junctions. This similarity was already exploited decades ago, as Mouthan fabricated integrated cascade micro-solar cells on ICs in 1984 [30]. More recently, concrete applications of on-chip solar cells emerged with the growing interest in the Internet of Things, which connects real and virtual objects which perform machine-to-machine communication [35]. Micro-solar cells are thus on-chip integrated to harvest energy for digital devices, as done by Ghosh et al. [31], Steffan et al. [32], and Zenibayashi et al. [33], who also use the solar cell as a light signal sensor for communication. These solar cells have the structure of CMOS chips. Hence, despite the advantage of not adding and processing steps in chip IC manufacturing, they are not optimized for energy harvesting. Besides, it is worth noting that these structures are adapted to very low energy production levels since these digital devices consume little power.

Organic materials can also be adequate solutions for combining both components. Organic semiconductors having a delocalized  $\pi$  electron system are known to support organic solar cells (OSCs) [36] and organic transistors [37]. Multiple semiconducting polymer materials have been synthesized, resulting in electronic properties allowing to have applications in both organic field-effect transistors and OSC [38, 39]. It is thus possible to imagine a device based on such material and receiving different local treatments to create solar cells and transistors on the same organic wafer. The advantages of using organic materials are the low-cost synthesis and easy manufacturing processes. The very large flexibility in shape, orbitals, energy levels, and electron densities offered by polymers make this material very promising for OSCs. However, they are still an immature technology facing several issues, such as still low power conversion efficiency, non-adapted absorption spectra, short exciton diffusion distance, and short lifespan [40]. Likewise, despite rapid development in the past decades, organic transistors still face challenges to achieving realistic applications in daily life [37]. In this thesis, the maturity of existing technologies is essential to focus on their combination. Therefore, organic materials are not further explored here.

For this reason of necessary maturity, we aim to integrate the transistor into a c-Si solar cell. The arguments supporting the choice of the transistor and solar cell provided in this paragraph are raised in more detail by van Nijen et al. [28]. One must here distinguish the two main architectures of c-Si solar cells. First, the front-back contacted (FBC) solar cells, which are the most usual ones, include metal contacts at both the top and bottom sides of the device. Second, the interdigitated back-contacted (IBC) solar cells carry positive and negative metal contacts on the backside of the cell only. Depending on these architectures, different transistor types are best suited for integration into the same c-Si wafer. For FBC cells, since the positive and negative metal contacts have opposite sides, vertical transistors, which also contain terminals at both sides of the wafer, are more easily integrable. IBC cells can more easily integrate lateral transistors, which hold all their terminals on the same side. Most transistors adopted for power converters are power transistors, which are vertical components. However, their architectures have many differences from FBC solar cells, and embedding them would thus require a significant number of additional processing steps. On the contrary, lateral transistors such as the metal-oxide-semiconductor field-effect transistor (MOSFET) and the bipolar junction transistor (BJT) would require few additional processing steps as compared with the manufacturing method of an IBC solar cell. MOSFETs have the advantage over BJTs to perform correctly until a higher limiting switching frequency, the latter being an important criterion for power converter applications. Another advantage is the nature of transistor control: while the BJT is a current-controlled device, the MOSFET is voltagecontrolled, allowing for lower losses.

Consequently, it is chosen for this thesis to integrate a MOSFET on an IBC solar cell. More specifically, the solar cell involves a tunnel oxide passivated contact (TOPCon) structure, which is chosen for its proven high efficiency and close structural similarity with the MOSFET design [41]. Before this work, Yavuzhan Mercimek optimized the MOSFET size for solar cell integration and manufactured the component with processes used for TOPCon IBC solar cell manufacturing [42]. The challenge is now to manufacture these two components with a minimum number of processing steps while still having satisfying solar cell and transistor performances.

#### 1.5. Research Questions and Report Outline

The objective of this Master's thesis is to carry out a combined fabrication of both an IBC solar cell and a MOSFET on one substrate and to characterize them. To explore different possibilities and hence allow a better understanding of their behavior, we use both n-type and p-type substrates, and both components can be either connected or characterized separately. The project aims to answer the following research questions:

- 1. How does integrating both components on the same substrate simultaneously affect their performance?

- 2. How does the doping nature (n- or p-type) of the substrate affect the performance of both components?

- 3. How does illumination affect the MOSFET performance?

- 4. How do the monolithically interconnected components perform, compared to separated ones?

The following outline is used in this report to address these questions. Firstly, this chapter provided context and motivation for the research. Secondly, chapter 2 provides the necessary theoretical knowledge to understand the physics and technologies involved. Then, fabrication and measurement methods are described in chapter 3. Measurement results are provided as follows: chapter 4 refers to the characterization of the solar cell; chapter 5 provides an analysis of the MOSFETs; chapter 6 presents the behavior of the MOSFET in illuminated condition and related to solar cell and MOSFET characterization, respectively. Finally, chapter 7 concludes the work and discusses the potentials, challenges, and limitations of the investigated combined fabrication for further applications.

# Solar Cell and MOSFET Theory

This chapter aims to provide theoretical insight into the technologies studied in the thesis, namely the IBC solar cell and the MOSFET. Fundamental physical mechanisms, design, and parameters are described for both components. First, section 2.1 provides a basis for both technologies by introducing the semiconductor. Next, sections 2.2 and 2.3 describe the solar cell and the MOSFET, respectively.

#### 2.1. Semiconductors

The semiconductor is a material from which many technologies emerged in the 20<sup>th</sup> century, including solar cells and transistors. It is introduced in this section, first in subsection 2.1.1 by defining essential concepts, then in subsection 2.1.2 by introducing the p-n junction, and in subsection 2.1.3 describing charge carriers' generation and recombination. Unless otherwise stated, all the content given in this section derives from the book *Semiconductor Physics and Devices: basic principles*, by Neamen [43].

#### 2.1.1. Definition

Semiconductors are solid-state materials having an electrical conductivity higher than insulators and lower than metals. In both PV and IC industries, silicon (Si) is by far the most used semiconductor material for reasons including its high abundance [44]. In this thesis, the study focuses on Si material. Crystalline and poly-crystalline semiconductors have ordered atomic structures with a lattice having the dimensions of the whole solid and many atoms, respectively. On the contrary, amorphous semi-conductors do not have an atom structure.

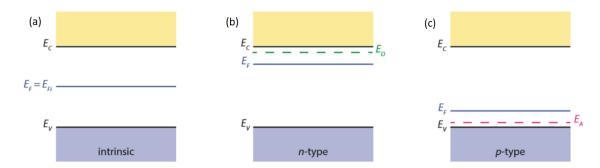

Atoms of Si have 4 valence electrons, orbiting around the nucleus and creating covalent bonds with neighboring atoms. If they have enough energy, valence electrons can move from one atom to another, thus breaking the covalent bond. This process would create a lack of electrons, called "holes", around the first atom and electron excess around the second atom. This free electron with such high energy is able to conduct electricity; hence, it is called a "conduction electron". Both holes and conduction electrons are charge carriers. Their energies belong to specific ranges: while holes belong to the valence band, conduction electrons belong to the conduction band. These bands are sketched in Figure 2.1(a). The figure also includes the conduction energy  $E_C$  and the valence energy  $E_V$ , which are the lowest energy of the conduction band and the highest energy of the valence band, respectively. Between these two energy levels, is located the bandgap, which is a forbidden band for charge carriers. The range of this bandgap is:

$$E_q = E_C - E_V \tag{2.1}$$

The Fermi energy  $E_F$  is the energy below which all states are filled with electrons and above which all states are empty at T = 0 K.

Figure 2.1: Energy band diagram for: (a) intrinsic semiconductor; (b) n-type doped semiconductor; (c) p-type doped semiconductor [11].

Figure 2.1(a) shows the case of an intrinsic semiconductor, i.e., a semiconductor without doping. Contrarily, a doped semiconductor has a fraction of the native atoms replaced by atoms (dopants) possessing another number of valence electrons. It creates a lack or surplus of electrons. Consequently, the Fermi level value changes, so there are more conduction electrons and fewer holes, or vice versa. In n-type semiconductors, the dopant has 5 valence electrons, such as phosphorus (Ph), so conduction electrons are more numerous, and the Fermi level is higher. Inversely, in p-type semiconductors, the dopant has 3 valence electrons, such as boron (B), so holes are more numerous, and the Fermi level is lower. Figure 2.1(b) and (c) sketch n-type and p-type energy band diagrams, respectively. In the following, conduction electrons will be simply called electrons.

#### 2.1.2. The P-N Junction

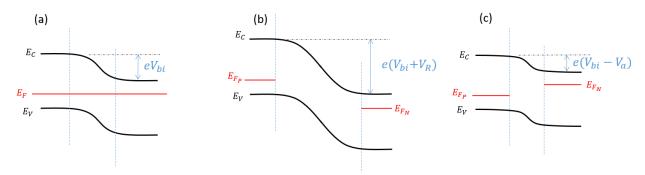

A p-n junction is the metallurgical junction of p-type and n-type semiconductors. Figure 2.2(a) displays the energy diagram of such a junction without applied bias. Three regions are distinguished: the p-type and the n-type semiconductors, respectively on the left and the right, and a depletion region in the middle. Since no bias is applied, the Fermi level is constant; hence, the conduction and valence levels are higher in the p-type than in the n-type material. The energy difference is proportional to the built-in voltage  $V_{bi}$ . A depletion region, free of charge carriers, is formed at the interface between the p- and n-type materials. Consequently, an electric field is created, justifying the slope of  $E_C$  and  $E_V$  in the figure. In Figure 2.2(b), a negative voltage is applied to the p-type region, corresponding to a reverse bias voltage at the junction. It results in a difference between the Fermi levels, an increased conduction and valence levels variation, and an increased depletion region width. In Figure 2.2(c), a positive voltage is applied to the p-type region, corresponding to a forward bias voltage, hence a reduction of the energy level variation, and a decreased depletion region width.

Figure 2.2: Energy band diagrams of a p-n junction for (a) zero bias; (b) reverse bias; (c) forward bias.

Charge carriers displace from one side of the junction to another according to two antagonistic mechanisms. Firstly, drift is the transport of charge carriers subjected to an electric field. It implies electrons and holes present in the depletion region move from the p- to the n-side and from the n- to the p-side, respectively. Secondly, diffusion is the transport of charges due to a concentration gradient. It implies the electrons and holes move from the n- to the p-side and from the p- to the n-side respectively. When

no bias is applied, the thermal equilibrium is achieved, and both mechanisms compensate for each other. Consequently, no current is globally observed. If a positive voltage is applied to the p-type region, diffusion dominates; hence, a current flows through the junction.

#### 2.1.3. Charge Carrier Generation and Recombination

Generation and recombination are defined by the creation and the annihilation of an electron-hole pair, respectively. At the thermal equilibrium, generation is only due to thermal effects and is compensated by recombination. Outside thermal equilibrium conditions, excess carriers are generated, by external forces such as illumination. These carriers then recombine after a random time, the average of which, called the minority carrier lifetime, is a parameter of the recombination rate. The lifetime also affects the diffusion length, defined by the mean free path the charge carriers browse before recombining. Recombination can be due to different mechanisms [11]:

- Radiative and direct recombination mechanisms are prominent for direct semiconductors but negligible for semiconductors with an indirect band gap. A semiconductor is indirect if a hole at the valence energy does not have the same crystal momentum as an electron at the conduction energy. Silicon is an indirect semiconductor; hence, these mechanisms are not significant.

- Shockley-Read-Hall (SRH) recombination is a process in which the electron-hole pair recombines at an energy level, called 'trap state', belonging to the bandgap. Such trap states are present due to impurity atoms in the crystal.

- Auger recombination is a mechanism involving 3 carriers. As an electron recombines with a hole, the energy and momentum transfer to a third particle, which can either be a hole or an electron. Depending on the semiconductor quality, SRH or Auger recombinations can be dominant for indirect semiconductors such as c-Si.

- Surface recombination occurs at the surface of the material. If the crystal abruptly ends, the atoms at the surface cannot create 4 covalent bonds; hence, dangling bonds appear instead. These dangling bonds are defects and cause the creation of trap states. As well as for SRH recombination, these trap states cause recombination.

## 2.2. Photovoltaic Technology

This section introduces PV technology, from fundamental concepts to the technology used in this thesis. First, subsection 2.2.1 introduces the sun's radiation. The solar cell is then introduced, first with subsection 2.2.2, explaining its fundamental physical mechanisms, then with subsection 2.2.3, presenting the external parameters, and with subsection 2.2.4, introducing crystalline silicon (c-Si) solar cell. Finally, subsection 2.2.5 focuses on the interdigitated back-contacted solar cell, which is the technology used in this thesis. Unless otherwise specified, all the content of this section is available in *Solar energy: the physics and engineering of photovoltaic conversion, technologies, and systems*, by Smets et al. [11].

#### 2.2.1. Solar Radiation

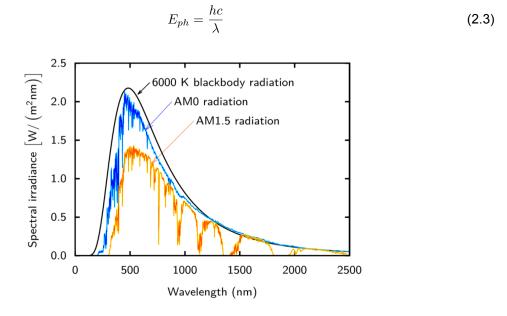

The Sun can be approximated by a blackbody model, with a surface temperature of roughly 6000 K. In Figure 2.3, the back curve shows the spectral irradiance of such a perfect blackbody, while the blue curve shows the "AM0 radiation", meaning the measured Sun radiation received at the top of the Earth's atmosphere. Finally, the orange curve shows the "AM1.5 radiation", considered as the standard reference for solar cell efficiency measurement. The differences between the blue and the orange curves result from some parts of the spectrum absorbed by the atmosphere and the orientation of the surface of the Earth. AM1.5 is verified when:

$$\frac{1}{\cos \theta} = 1.5 \tag{2.2}$$

With  $\theta$  the angle between the Zenith and the direction of the Sun. If the Sun is at the Zenith, i.e.,  $\theta=0$ , AM1 is verified, and the amplitude of the spectral irradiance is larger. The quantum theory considers that elementary particles of light, called photons, behave as both a wave and particles. Each photon carries energy, which is inversely proportional to the wavelength, as written in Equation 2.3, with  $\lambda$  the wavelength, h the Planck's constant, and c the light celerity.

Figure 2.3: Solar spectrum [11].

#### 2.2.2. Working Principle of a Solar Cell

A solar cell, also called a PV cell, is an electronic device that converts the energy of the light directly into electricity by the photovoltaic effect [45]. To do so, 4 fundamental mechanisms successively occur:

- Absorption of a photon by the semiconductor. Competing mechanisms can also occur, such as reflection and transmission, limiting absorption. To restrain reflection, solar cell top surfaces are usually textured and coated by a layer with a specific thickness and refraction index such that the reflection coefficient is minimum. To decrease transmission, the semiconductor substrate thickness can be increased.

- 2. Creation of an electron-hole pair from the absorbed photon. It can only happen if the energy of the photon is higher than the semiconductor bandgap:

$$E_{ph} \ge E_q \tag{2.4}$$