Monolithic Integration of Rectifiers and Drivers for low power SSL applications on a Rigid to Flex Substrate

# Monolithic Integration of Rectifiers and Drivers for low power SSL applications on a Rigid to flex substrate

By

#### Manjunath Ramachandrappa Venkatesh

#### **MASTER THESIS**

#### **ELECTRICAL ENGINEERING**

Delft University of Technology

Faculty of Electrical Engineering, Mathematics and Computer science

Delft institute of Microsystems and Nano-electronics

Laboratory of Electronic Components, Technology and Materials

Supervisor: Prof. dr. ir.G.Q. Zhang TU Delft Thesis committee: Dr.H.W. van Zeijl, TU Delft Ir.P.Liu, TU Delft

Yi Wang, Philips

#### **Abstract**

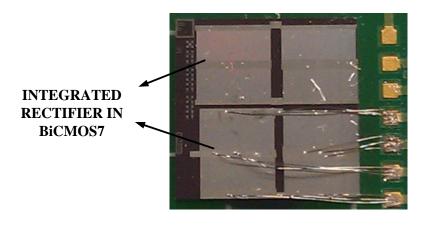

Solid State Lighting (SSL) is one of the prominent light sources for future lighting applications with benefits such as high energy savings, long lifetimes and high efficiency. The main drawback in solid state lighting system is that the total initial cost of the system is high for large scale production. Packaging and electronics components in the system account to about 60% of the total cost. Silicon based wafer level packaging offers great advantages for large scale cheap production. Furthermore it also helps to create to create miniaturized and multifunctional system with integrated electronics with LEDs. In this thesis, a novel schottky diode in BiCMOS having high current conduction and high breakdown is designed and fabricated. A monolithically integrated rectifiers composed with four schottky diodes is presented. The rectifiers designed using schottky diodes are fabricated in a simple and low cost DIMES BiCMOS7 process. A detailed modeling and simulation of schottky diodes in a standard BiCMOS process is done to derive design parameters to achieve high current and high breakdown voltage. It has been found that with guard rings and a n well doping concentration determined by a phosphor dose of 6e12, schottky diodes with a breakdown voltage of 27V and forward current of 1A at 0.68V are fabricated in this process. A complete design, fabrication, characterization and spice modeling of the schottky diodes are presented. NMOS and NPN bipolar transistor fabricated in the BiCMOS process are characterized and modeled. A basic linear and switch mode driver using the devices fabricated in the BiCMOS process is analyzed. A design proposal for integrating the rectifiers and drivers on a Rigid to flex substrate is presented. The developed concept offers great advantage for wafer level integration of SSL system to reduce cost and create smart multifunctional miniaturized products.

## **Table of Contents**

| Chapter 1 | Introduction                                                              | 13 |

|-----------|---------------------------------------------------------------------------|----|

| 1.1 S     | olid State Lighting System                                                | 14 |

| 1.2 W     | Vafer Level Integration for SSL system                                    | 16 |

| 1.3 D     | esign and Thesis focus                                                    | 19 |

| 1.3.1     | Electrical specifications for G4 retrofit LED capsule                     | 19 |

| 1.3.2     | Design proposal                                                           | 23 |

| 1.4 Т     | hesis Outline                                                             | 26 |

| Chapter 2 | Process and Device Modelling                                              | 28 |

| 2.1 Se    | chottky diodes                                                            | 28 |

| 2.1.1     | Forward I-V Characteristics of Schottky Diodes                            | 31 |

| 2.1.2     | Analysis of Breakdown Voltage in Schottky Diodes                          | 34 |

| 2.1.3     | Junction Barrier Schottky Diodes                                          | 36 |

| 2.2 Se    | chottky diodes in BiCMOS process                                          | 37 |

| 2.2.1     | Forward characteristics of Schottky diodes in BiCMOS process              | 37 |

| 2.2.2     | Breakdown voltage analysis of Schottky diodes in BiCMOS process           | 43 |

| 2.2.3     | Design parameters for schottky diodes in BiCMOS process                   | 47 |

| 2.3 P     | rocess and Device simulation of Schottky diodes in DIMES BiCMOS7 process  | 48 |

| 2.3.1     | Modeling and simulation of N-Well Doping profile                          | 49 |

| 2.3.2     | Modeling and simulation of Schottky Diodes                                | 52 |

| 2.3.3     | Modeling and simulation of high current Schottky Diodes in BiCMOS process | 55 |

| 2.4       | Chapter Summary                                                           | 59 |

| Chapter 3 | Fabrication and Characterisation                                          | 60 |

| 3.1 F     | abrication of Schottky diodes in DIMES BiCMOS7 process                    | 60 |

| 3.1.1     | Design rules for mask layout                                              | 60 |

| 3.1.2     | DIMES BiCMOS7 fabrication process                                         | 65 |

| 3.2 M     | leasurement and Characterization of Schottky diodes                       | 73 |

| 3.2.1     | Measurements of low current Schottky diodes in BiCMOS7 process            | 73 |

| 3.2.2        | Measurements of high current Schottky diodes in BiCMOS7 process      | 82  |

|--------------|----------------------------------------------------------------------|-----|

| 3.2.3        | Temperature measurements of high current Schottky diodes             | 88  |

| 3.2.4        | Spice Model of Schottky diodes                                       | 90  |

| 3.3 Me       | asurement and characterization of NPN BJT and NMOS in BiCMOS process | 94  |

| 3.3.1        | Modeling and characterization of NPN Bipolar Transistors             | 94  |

| 3.3.2        | Modeling and characterization of NMOS Transistors                    | 98  |

| 3.4 Ch       | apter Summary                                                        | 102 |

| Chapter 4 Ir | ntegrated Rectifiers and Drivers on a Rigd to Flex substrate         | 103 |

| 4.1 Inte     | egrated rectifiers in BiCMOS7 process                                | 103 |

| 4.1.1        | Simulation of Rectifiers using DIMES BiCMOS7 schottky diode model    | 103 |

| 4.1.2        | Characterization of Rectifiers fabricated in DIMES BiCMOS7 process   | 107 |

| 4.2 Inte     | egrated drivers in BiCMOS7 process                                   | 109 |

| 4.3 Des      | sign of Integrated rectifiers and drivers on Rigid to flex substrate | 112 |

| 4.4 Ch       | apter Summary                                                        | 115 |

| Chapter 5 C  | onclusions and Future Recommendations                                | 116 |

| 5.1 Conclu   | usions                                                               | 116 |

| 5.2 Future   | Recommendations                                                      | 118 |

## **Table of Figures**

| Figure 1.1 Cost breakdown of SSL System                                                         | 16   |

|-------------------------------------------------------------------------------------------------|------|

| Figure 1.2 3D LED and IC integration                                                            | 17   |

| Figure 1.3 LED packaging on Silicon platform                                                    | 17   |

| Figure 1.4 Rigid to Flex interconnect technology                                                | 18   |

| Figure 1.5 G4 LED Capsule                                                                       | 19   |

| Figure 1.6 Schematic of a low power 12V LED system                                              | 19   |

| Figure 1.7 Vertical power schottky diode                                                        | 20   |

| Figure 1.8 Schottky diode structure in Standard CMOS process                                    | 21   |

| Figure 1.9 Linear driver circuit example                                                        | 21   |

| Figure 1.10 Current mirror linear driver                                                        | 21   |

| Figure 1.11 Schematic of Buck driver topology                                                   | 22   |

| Figure 1.12 Schematic of average current control buck driver                                    | 23   |

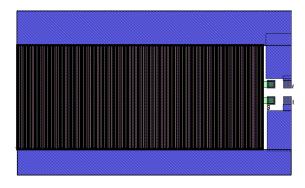

| Figure 1.13 Fabricated Integrated rectifiers chip in BiCMOS7                                    | 23   |

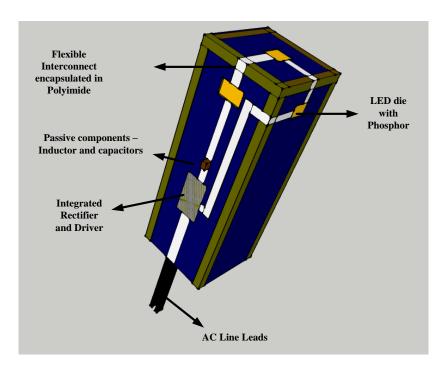

| Figure 1.14 3D model of monolithically integrated rectifiers and drivers on to Flex-to-rigid    |      |

| substrate                                                                                       | 24   |

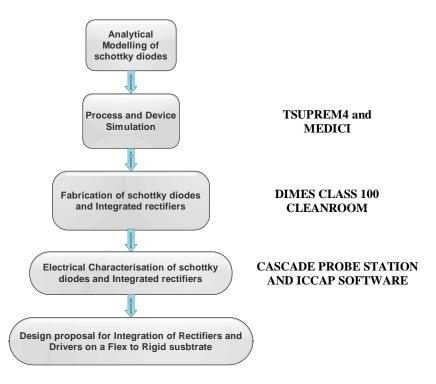

| Figure 1.15 Design Flow                                                                         | 25   |

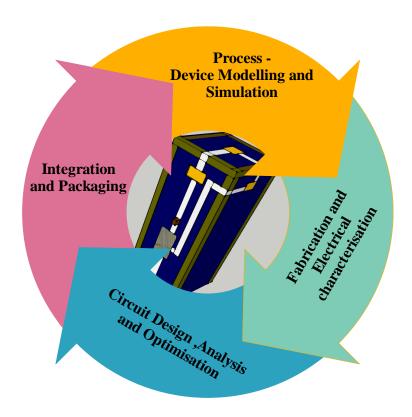

| Figure 1.16 Design cycle for Wafer level integration of G4 module                               | 26   |

| Figure 2.1 Energy Band Diagram before metal contact                                             | 29   |

| Figure 2.2 Energy Band Diagram after metal contact                                              | 29   |

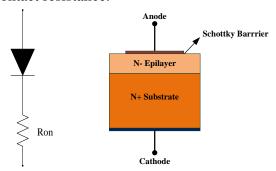

| Figure 2.3 Cross section of Power Schottky Diode                                                | 30   |

| Figure 2.4 Schottky diode current transport mechanism in Forward Bias                           | 31   |

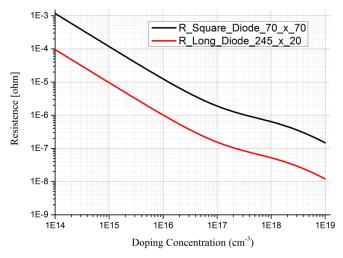

| Figure 2.5 RON v/s Doping concentrations for different epitaxial layer thickness                | 32   |

| Figure 2.6 Forward Voltage $V_F$ for various barrier height and area at $J_F = 1 \text{A/cm}^2$ | 34   |

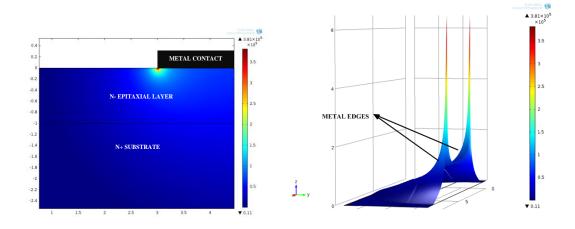

| Figure 2.7 Electric Field at reverse bias voltage of 100V                                       | 35   |

| Figure 2.8 Cross section of Junction Barrier Schottky diode                                     | 36   |

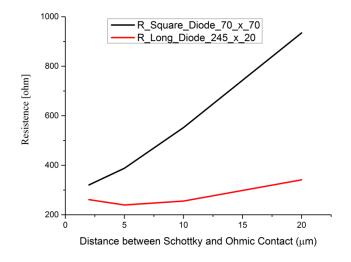

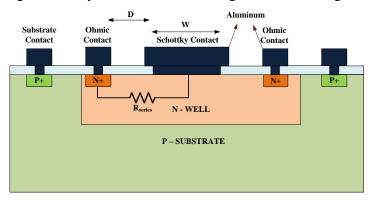

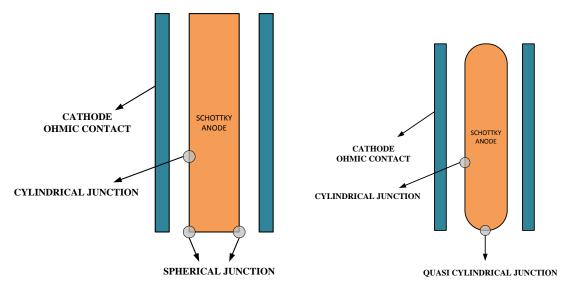

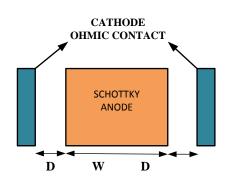

| Figure 2.9 Cross section of Planar Schottky Diode device                                        | 38   |

| Figure 2.10 Components of series resistance in Planar Schottky Diode                            | 39   |

| Figure 2.11 Spread Resistance RSPREAD vs. Doping concentration                                  | 41   |

| Figure 2.12 Resistance RN+ vs. distance between schottky and ohmic contact                      | 41   |

| Figure 2.13 Planar Square Schottky diode device cross section                                   |      |

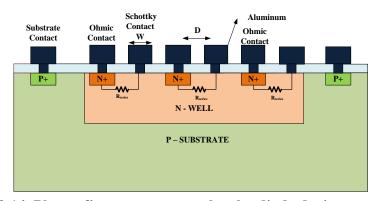

| Figure 2.14 Planar finger structure schottky diode device cross section                         | 42   |

| Figure 2.15 Critical Electric Field v/s Doping concentrations for Si Schottky diode             | 43   |

| Figure 2.16 Field of Planar Schottky Diode at Reverse Bias of -10V                              | . 44 |

| Figure 2.17 Electric Field of Planar Schottky Diode at Reverse Bias of -50V                     | . 44 |

| Figure 2.18 Breakdown voltage v/s Doping concentrations for Si Schottky diode                   | 45   |

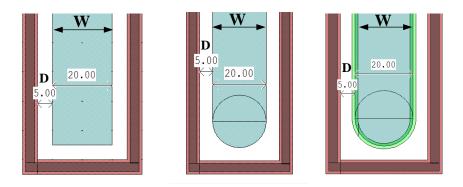

| Figure 2.19 Layout rectangular masks                                                            |      |

| Figure 2.20 Layout cylindrical masks                                                            | 46   |

| Figure 2.21 Schottky diode layout with P+ guard rings                                           |      |

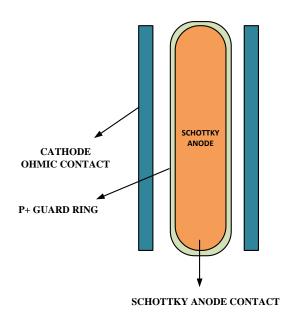

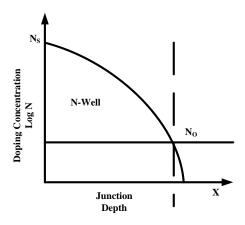

| Figure 2.22 N-Well Doping profile                                                               | 49   |

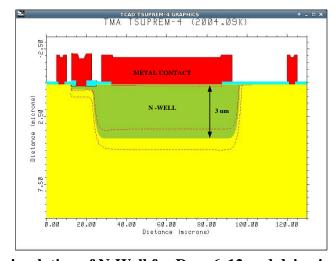

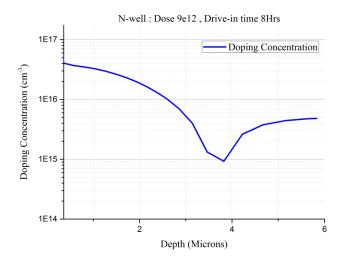

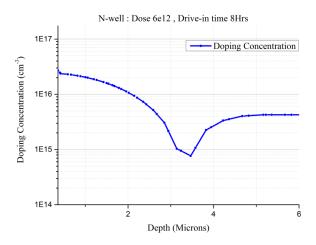

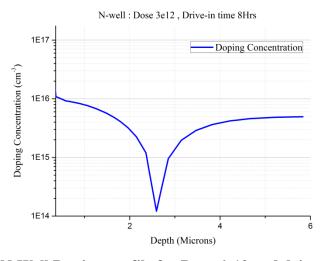

| Figure 2.23 2-D simulation of N-Well for Dose 6e12 and drive-in time 8Hrs                        | 50     |

|--------------------------------------------------------------------------------------------------|--------|

| Figure 2.24 N-Well Doping profile for Dose 9e12 and drive-in time 8Hrs                           | 51     |

| Figure 2.25 N-Well Doping profile for Dose 6e12 and drive-in time 6Hrs                           | 51     |

| Figure 2.26 N-Well Doping profile for Dose 6e12 and drive-in time 6Hrs                           | 51     |

| Figure 2.27 Layout of Long diode                                                                 | 52     |

| Figure 2.28 Layout of square diode                                                               | 52     |

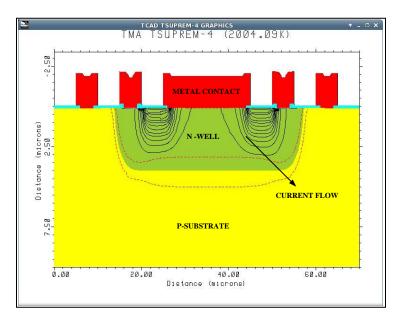

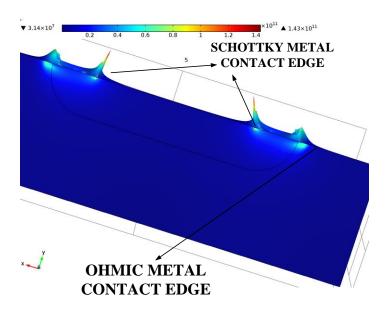

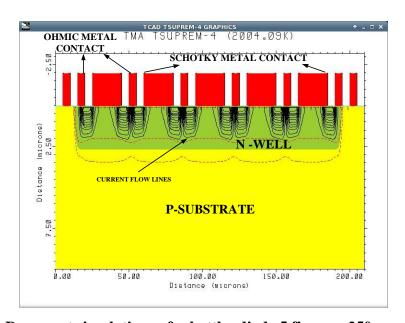

| Figure 2.29 2-D current simulations of schottky diode - 245μm x 20μm                             | 53     |

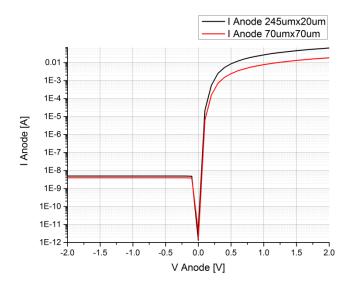

| Figure 2.30 Forward IV characteristics of Long and Square Schottky diode                         | 54     |

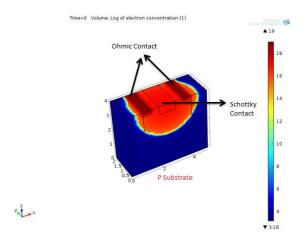

| Figure 2.31 Electron concentration profile in Schottky diode 3D Model                            | 54     |

| Figure 2.32 Current Density profile for Schottky diode in forward bias                           | 55     |

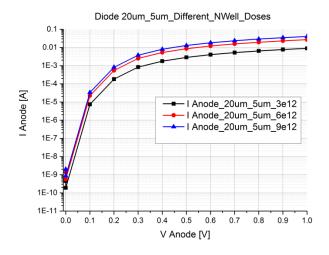

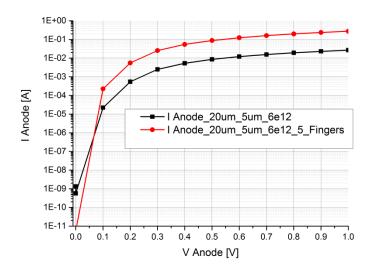

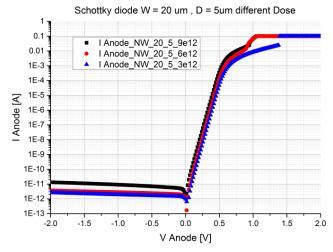

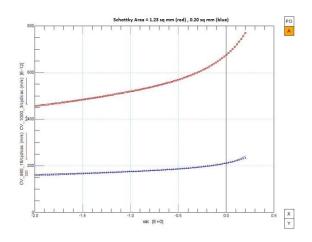

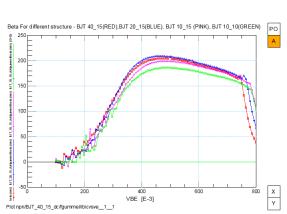

| Figure 2.33 Schottky diode W=20um D = 5um for different n-well dose                              | 57     |

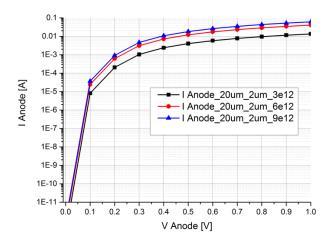

| Figure 2.34 Schottky diode W=20um D = 2um for different n-well dose                              | 57     |

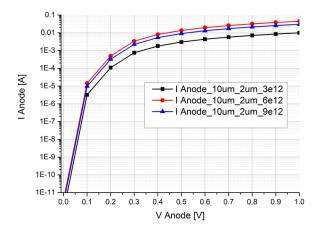

| Figure 2.35 Schottky diode W=10um D = 2um for different n-well dose                              | 57     |

| Figure 2.36 2-D current simulations of schottky diode 5 fingers- 250μm x 20μm                    | 58     |

| Figure 2.37 Schottky diode finger design vs. single schottky diode $W = 20$ , $D = 5$            | 58     |

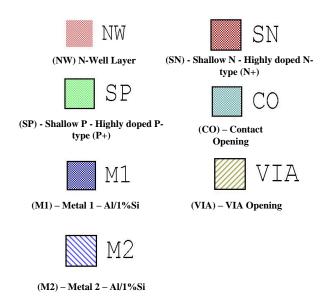

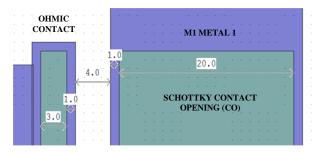

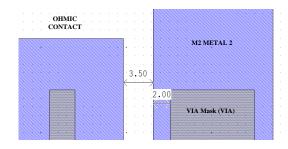

| Figure 3.1 Layers for BiCMOS mask design                                                         | 61     |

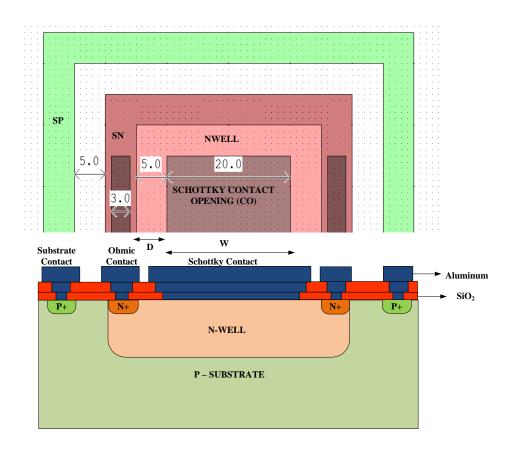

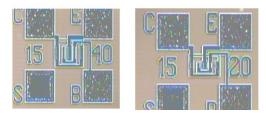

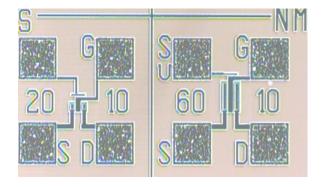

| Figure 3.2 Mask Layout and device cross section – scale in µm                                    | 62     |

| Figure 3.3 Example layout design for spacing between metal 1 (M1)                                | 63     |

| Figure 3.4 Example layout design for spacing between metal 2 (M2)                                | 63     |

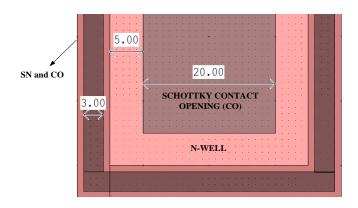

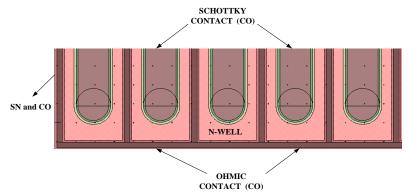

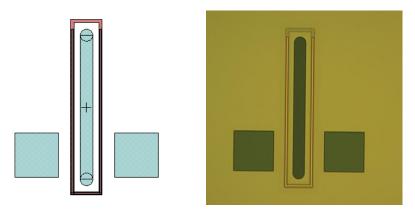

| Figure 3.5 Rectangular schottky diode layout designs                                             | 63     |

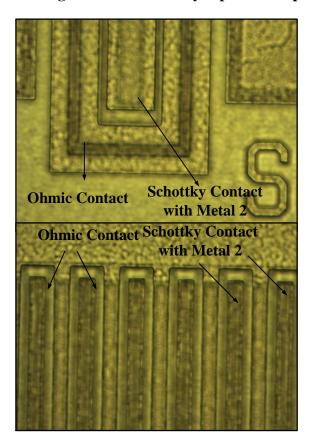

| Figure 3.6 Cylindrical schottky diode finger designs for schottky and ohmic contacts             | 64     |

| Figure 3.7 Test structures of low current schottky diode $W = (20\mu m, 10\mu m), L = 250\mu m$  | 64     |

| Figure 3.8 Test structures of high current schottky diode $W=20\mu m$ , $L=1000\mu m$ 70 fingers | s with |

| schottky contact area = 1.4 mm2                                                                  | 64     |

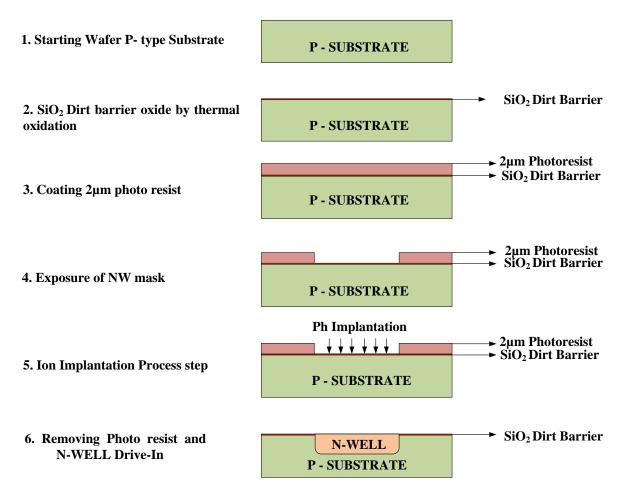

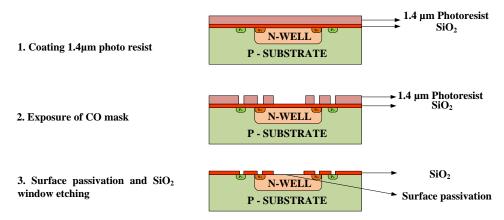

| Figure 3.9 N well formation process steps                                                        | 65     |

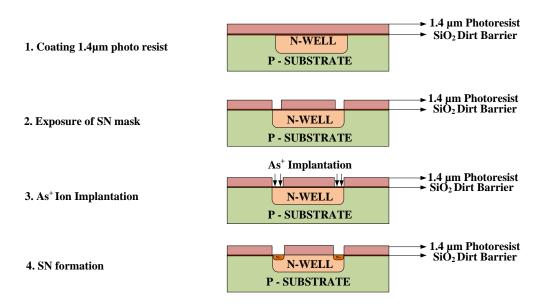

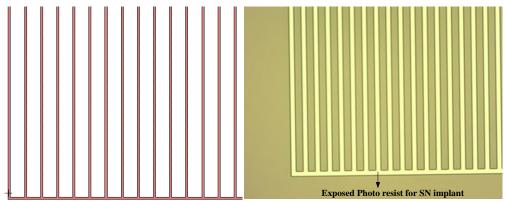

| Figure 3.10 Shallow N process steps                                                              | 66     |

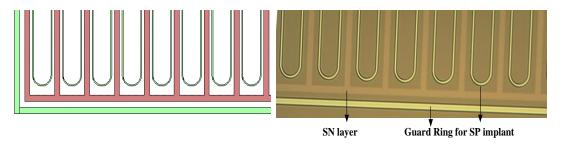

| Figure 3.11 Shallow N patterns on wafer after development compared with SN mask                  | 67     |

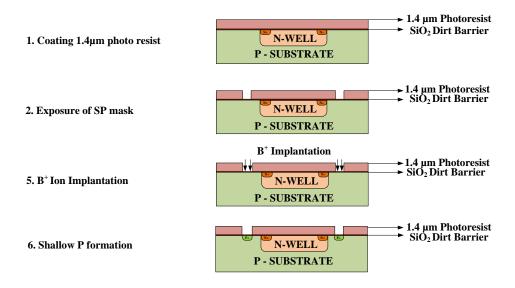

| Figure 3.12 Shallow P process steps                                                              |        |

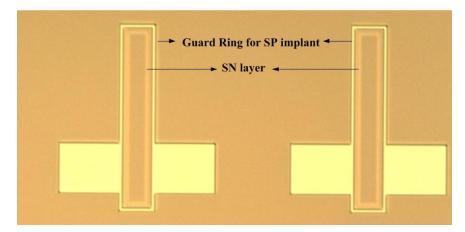

| Figure 3.13 Shallow P pattern on wafer after development and SN Layer                            | 68     |

| Figure 3.14 Shallow P pattern on wafer after development and SN Layer                            | 68     |

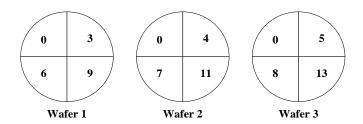

| Figure 3.15 VT adjust B+ implant (in 1012 cm-2) for 3 wafers of same N-Well dose                 |        |

| Figure 3.16 Contact opening (CO) process steps                                                   | 69     |

| Figure 3.17 Contact opening (CO) pattern on wafer after development – rectangular and            |        |

| cylindrical schottky contacts – single and finger structures                                     |        |

| Figure 3.18 Contact opening (CO) pattern on wafer after development with CO mask                 |        |

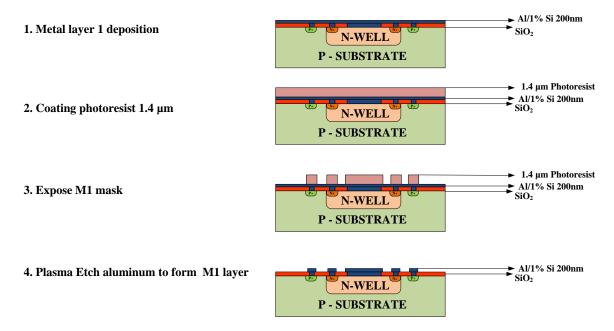

| Figure 3.19 Metal 1 layer process steps                                                          |        |

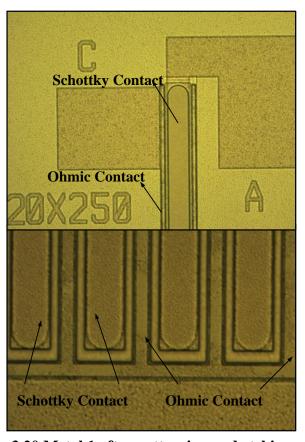

| Figure 3.20 Metal 1 after patterning and etching                                                 |        |

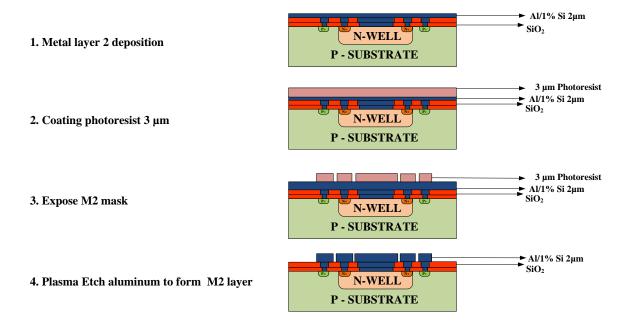

| Figure 3.21 Metal 2 layer process steps                                                          |        |

| Figure 3.22 Metal 2 after patterning and etching                                                 |        |

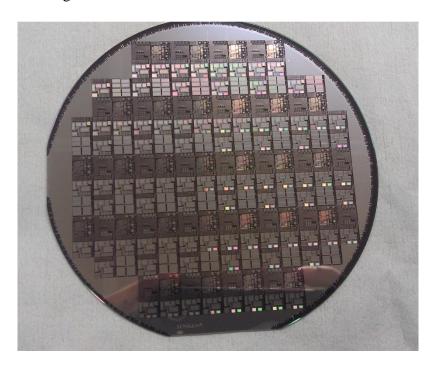

| Figure 3.23 Wafer after metallization and alloying step                                          | 73     |

| Figure 3.24 Schottky diode structures for measurements rectangular, cylindrical and cylindr      | ical |

|--------------------------------------------------------------------------------------------------|------|

| with guard rings (from left to right)                                                            | 74   |

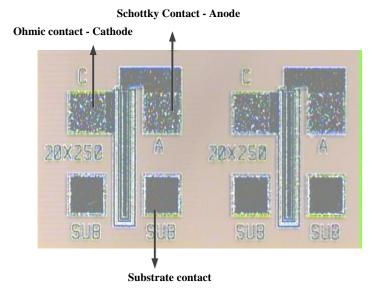

| Figure 3.25 Test structure for measurement of schottky diode W=20µm D=5µm                        | 74   |

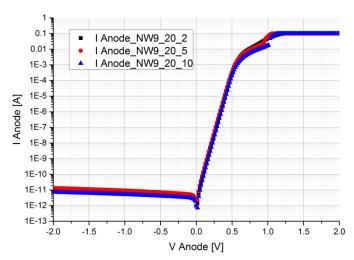

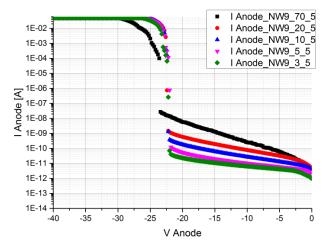

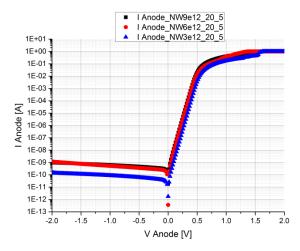

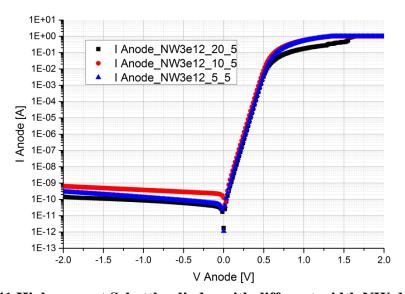

| Figure 3.26 Schottky diodes $W = 20\mu m$ , $D = 5\mu m$ for different NW dose                   | 76   |

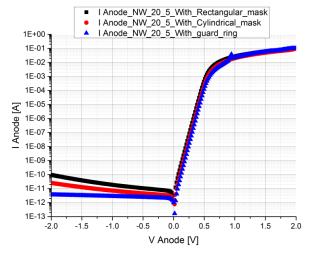

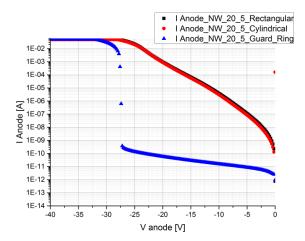

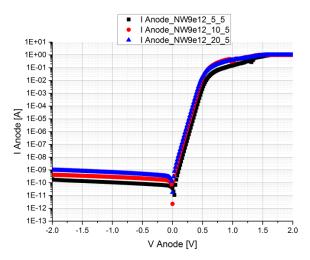

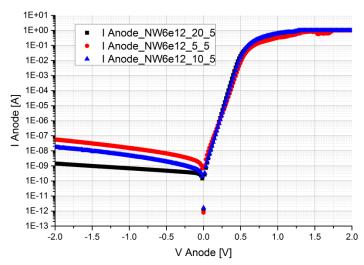

| Figure 3.27 Schottky diodes $W = 20\mu m$ , $D = 5\mu m$ for different layout design             | 77   |

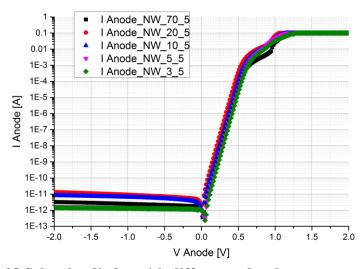

| Figure 3.28 Schottky diodes with different schottky contact width W                              | 77   |

| Figure 3.29 Schottky diodes with different distance D                                            | 78   |

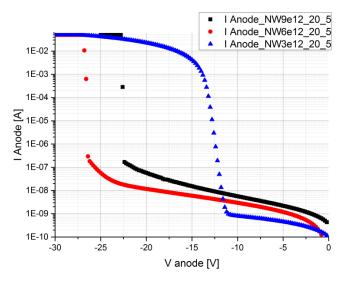

| Figure 3.30 Breakdown Voltage for $W = 20\mu m$ , $D = 5\mu m$ for different NW dose – Rectangu  | ılar |

| schottky contact mask                                                                            | 79   |

| Figure 3.31 Breakdown Voltage for $W = 20\mu m$ , $D = 5\mu m$ for different NW dose – Cylindric | cal  |

| schottky contact mask                                                                            | 79   |

| Figure 3.32 Breakdown Voltage for $W = 20\mu m$ , $D = 5\mu m$ for different NW dose – Cylindric | cal  |

| schottky contact mask with guard ring                                                            | 80   |

| Figure 3.33 Breakdown Voltage for $W = 20\mu m$ , $D = 5\mu m$ for different layouts             | 80   |

| Figure 3.34 Breakdown Voltage for different schottky contact width W - NW9e12                    | 81   |

| Figure 3.35 Breakdown Voltage for different schottky contact width W - NW6e12                    | 81   |

| Figure 3.36 Breakdown Voltage for different distance D - NW6e12                                  | 81   |

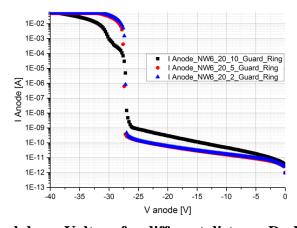

| Figure 3.37 Test structure of high current schottky diode W=20µm D=5µm 50 fingers                | 83   |

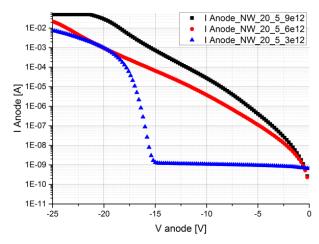

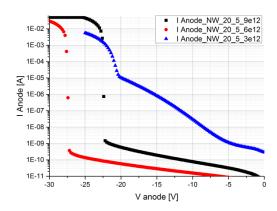

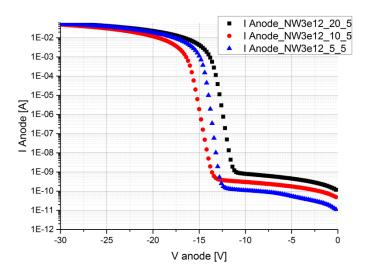

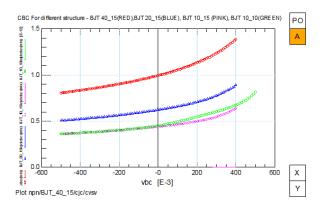

| Figure 3.38 Schottky diodes $W = 20\mu m$ , $D = 5\mu m$ , 50 fingers for different NW dose      | 84   |

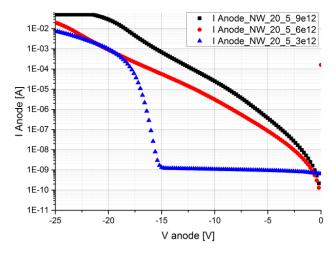

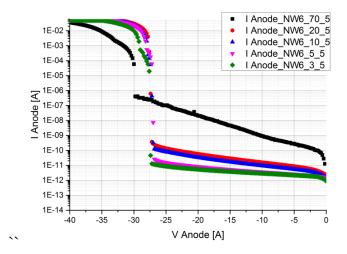

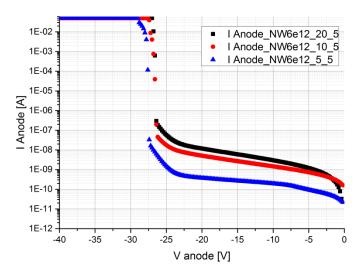

| Figure 3.39 High current Schottky diodes with different width W for NW = 9e12                    | 84   |

| Figure 3.40 High current Schottky diodes with different width NW dose = 6e12                     | 85   |

| Figure 3.41 High current Schottky diodes with different width NW dose = 3e12                     | 85   |

| Figure 3.42 Schottky diodes $W = 20\mu m$ , $D = 5\mu m$ , 50 fingers for different NW dose      | 86   |

| Figure 3.43 High current Schottky diodes with different width NW dose = 9e12                     | 86   |

| Figure 3.44 High current Schottky diodes with different width NW dose = 6e12                     | 87   |

| Figure 3.45 High current Schottky diodes with different width NW dose = 3e12                     | 87   |

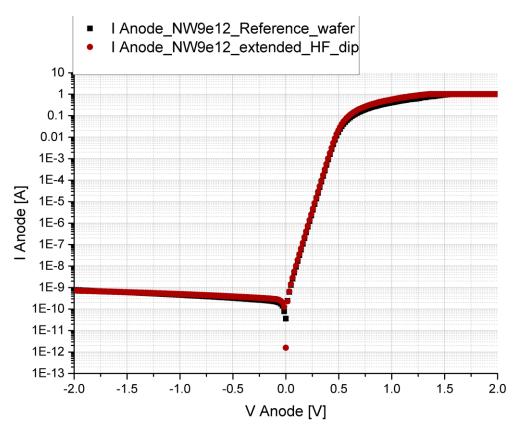

| Figure 3.46 High current Schottky diodes comparison with extended HF dip                         | 88   |

| Figure 3.47 High current Schottky diodes temperature characteristics forward IV                  | 89   |

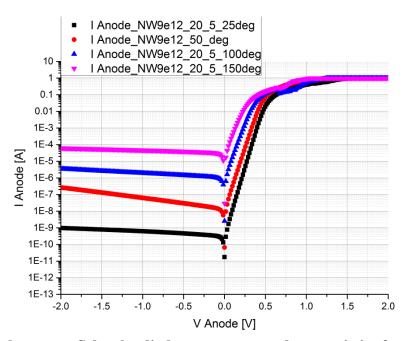

| Figure 3.48 High current Schottky diodes temperature characteristics reverse IV                  | 89   |

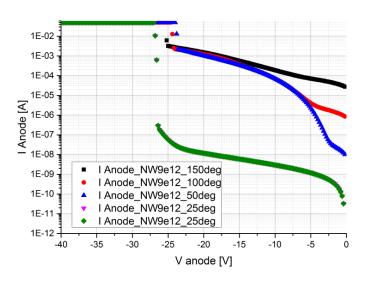

| Figure 3.49 Large signal equivalent circuit of Schottky diode                                    | 90   |

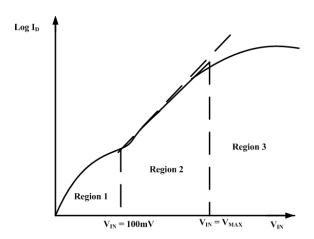

| Figure 3.50 Regions in forward IV characteristics                                                | 90   |

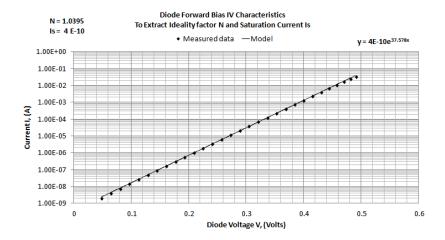

| Figure 3.51 Extracting Ideality factor N for N-well dose = 9e12                                  | 91   |

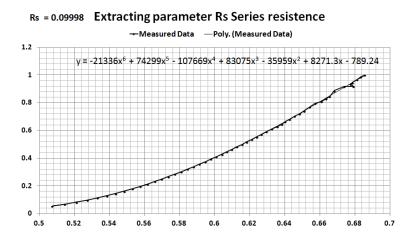

| Figure 3.52 Extracting factor Rs for N-well dose = 9e12                                          | 92   |

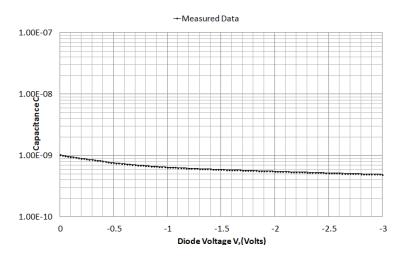

| Figure 3.53 Capacitance – Voltage characteristics of schottky diode                              | 92   |

| Figure 3.54 Capacitance – Voltage characteristics different area                                 | 93   |

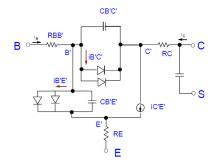

| Figure 3.55 Large signal Gummel Poon model of BJT                                                | 95   |

| Figure 3.56 Test structure for BJT modeling                                                      | 95   |

| Figure 3.57 CV measurement (CBE) for different BJT structure                                     | 96   |

| Figure 3.58 Large signal Gummel Poon model of BJT                                                | 97   |

| Figure 3.59 Large signal Gummel Poon model of BJT                                                | 97   |

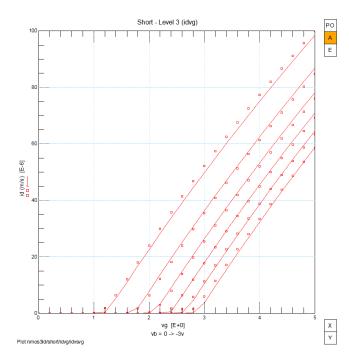

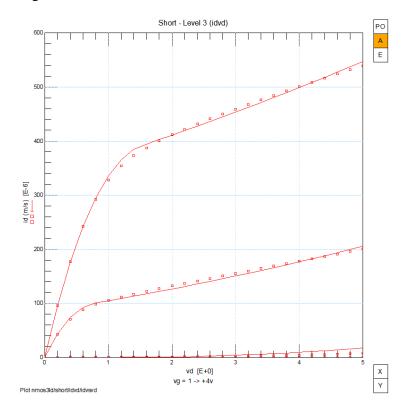

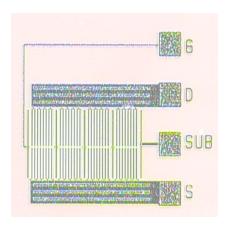

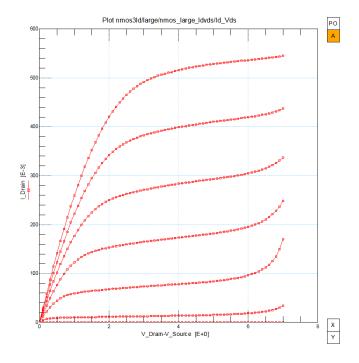

| Figure 3.60 Test structure for NMOS modeling                                                     | 98    |

|--------------------------------------------------------------------------------------------------|-------|

| Figure 3.61 ID versus VGS to extract threshold voltage                                           | 99    |

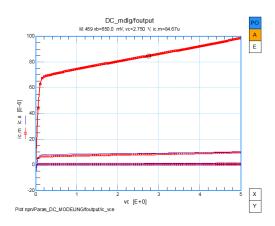

| Figure 3.62 ID versus VDS                                                                        | 100   |

| Figure 3.63 Power MOSFET Test structure                                                          | 100   |

| Figure 3.64 ID versus VDS for Power Mosfet                                                       | 101   |

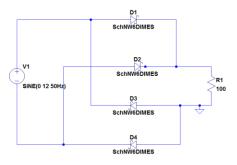

| Figure 4.1 Schematic of Rectifier circuit with schottky diodes                                   | 104   |

| Figure 4.2 Schematic of Rectifier circuit with schottky diodes                                   | 104   |

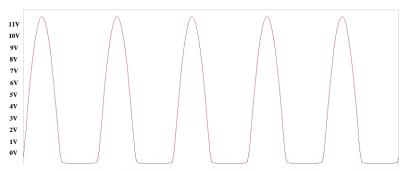

| Figure 4.3 Output voltage at diode D1                                                            | 104   |

| Figure 4.4 Output voltage at diode D4                                                            | 105   |

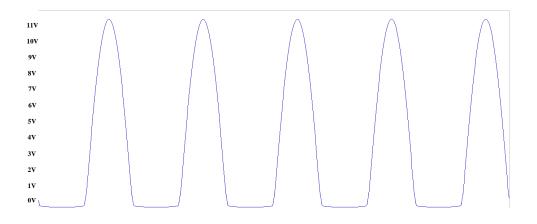

| Figure 4.5 Output voltage at resistor                                                            | 105   |

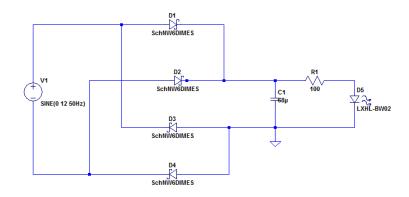

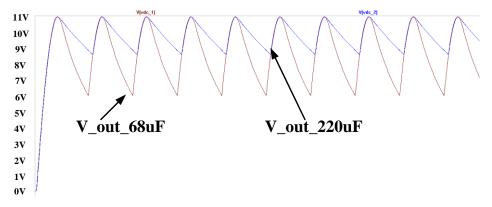

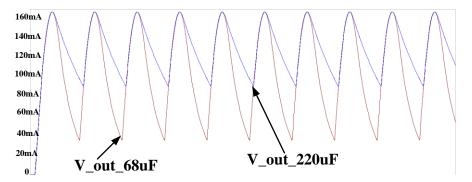

| Figure 4.6 LTspice schematic of Rectifier circuit with resistor as linear driver                 | 106   |

| Figure 4.7 Output voltage simulation of the integrated rectifier circuit with schottky diodes    |       |

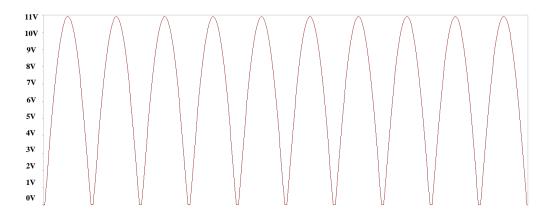

| fabricated in DIMES BiCMOS7 process                                                              | 106   |

| Figure 4.8 Output current simulation of the integrated rectifier circuit with schottky diodes    |       |

| fabricated in DIMES BiCMOS7 process                                                              | 106   |

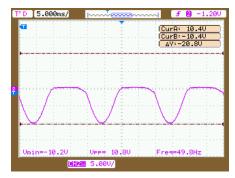

| Figure 4.9 On wafer testing of the rectifiers using cascade probe station                        | 107   |

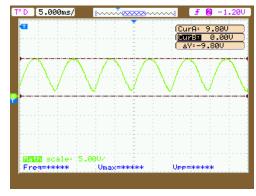

| Figure 4.10 Output voltage at diode D1 of the integrated rectifier                               | 107   |

| Figure 4.11 Output voltage at diode D4 of the integrated rectifier                               | 107   |

| Figure 4.12 Output voltage at the load of the integrated rectifier                               | 108   |

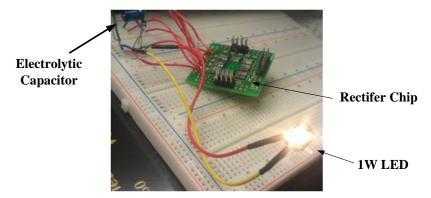

| Figure 4.13 Integrated rectifier wirebonded to PCB                                               | 108   |

| Figure 4.14 Integrated rectifiers and linear driver for the G4 LED                               | 108   |

| Figure 4.15 Linear driver circuit example                                                        | 109   |

| Figure 4.16 Current Mirror driver circuit example                                                | 110   |

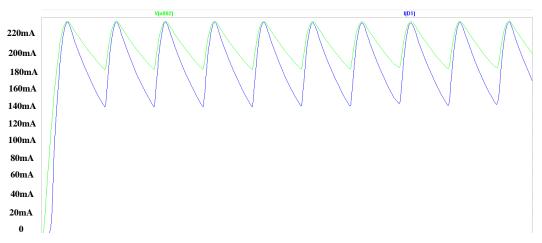

| Figure 4.17 Current mirror output                                                                | 110   |

| Figure 4.18 Current mirror with rectifiers using schottky diodes                                 | 110   |

| Figure 4.19 Output of Current mirror with rectifier                                              | 111   |

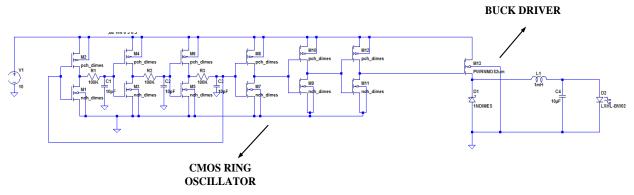

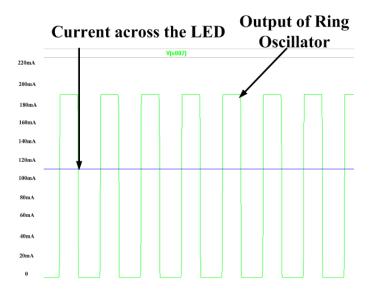

| Figure 4.20 Buck driver with ring oscillator used for switching the mosfet                       | 111   |

| Figure 4.21 Output of Buck driver with ring oscillator                                           | 112   |

| Figure 4.22 3D illustrations of proposed integrated rectifier and driver in a Rigid to Flex subs |       |

|                                                                                                  | 113   |

| Figure 4.23 Process step of Rigid to flex substrate                                              | 113   |

| Figure 4.24 Proposed Mask design for integrated rectifier and driver usin Rigid to Flex subs     | trate |

|                                                                                                  | 114   |

## **List of Tables**

| Table 1.1 Levels of SSL System                                                                       | . 15 |

|------------------------------------------------------------------------------------------------------|------|

| Table 2.1 On-state forward voltage drop V <sub>F</sub> for different metal contact and schottky area | . 33 |

| Table 2.2 Implantation Dose and drive-in time for different surface concentration                    | . 50 |

| Table 2.3 Surface concentration theoretical and practical comparison                                 | . 52 |

| Table 2.4 Schottky diode with different W and distance D                                             | . 56 |

| Table 3.1 Measurements of Schottky diodes ( $L = 250\mu m$ ) with different W and distance D to      |      |

| determine $V_F$ for $I_F = 100$ mA and breakdown voltage                                             | . 75 |

| Table 3.2 Measurements of Schottky diodes with guard ring - $V_F$ for $I_F = 1A$                     | . 83 |

| Table 3.3 Measurements of Schottky diodes and extracted model parameter                              | . 91 |

| Table 3.4 Spice model extracted parameters of high current schottky diode                            | . 93 |

| Table 3.5 CV measuremet procedure and extracted parameter                                            | . 95 |

| Table 3.6 DC Measurements                                                                            | . 96 |

| Table 3.7 NPN SPICE MODEL Parameters                                                                 | . 97 |

| Table 3.8 DC measuremet procedure and extracted parameter                                            | . 99 |

| Table 3.9 NMOS SPICE Parameter extracted                                                             | 101  |

# Chapter 1

## Introduction

With the invention of semiconductor devices and integrated circuit, this era has been defined as the electronics era. The semiconductor industry is a key driver for the development of many industries such as education, transportation, biomedical, communication and entertainment to name a few. Electronics systems have influenced every aspect of our lives and play a vital role in day to day activities. The next big development in the semiconductor industry over the last decade has been with the advent of Solid State Lighting (SSL) for general lighting application.

Technology for the lighting industry began with the invention of the incandescent bulb by Thomas Alva Edison in 1879. Later in the year 1906, General Electric patented the first tungsten light bulb. Though incandescent lamps are very cheap to manufacture, they were inefficient as they convert only about 1% to 5% of the consumed electricity into usable light. The next generation of lighting technology followed with the introduction of fluorescent lamp in 1930's. These lamps have improved efficiency than incandescent bulbs but contain small amount toxic gases like mercury which is harmful for the atmosphere. Due to the above drawbacks of incandescent and fluorescent lamps, there is a need for the lighting industry to create lighting systems that are efficient, have lower manufacturing cost and reduced atmospheric pollution [1].For this development, there here has been a lot of interest in the field of Solid State Lighting as it provides good potential for energy efficient, safe and affordable lighting solutions. In the recent survey, the lighting market, including light sources(LED's), electronics and luminaries is estimated to increase from €50 billion in 2010 to €70 billion by the year 2020 [2].

Solid State Lighting refers to light obtained from semiconductor devices. The first report on electroluminescence was published by Henry J Round in 1907 when he found that current passed through carborundum diode emitted light. But the invention of Light Emitting Diode is credited to Russian scientist Losev who correctly explained the phenomena of light emission in

silicon carbide diodes used in his work on radio receivers [3]. LED's mainly red, blue, green was used as indicators, displays in electronic systems due to their low lumen/watt till the early 90's. The development of white LED's in mid-90's provided interest to use LED's as an alternative to general lighting and it has accelerated the growth of LED's. The design of LED lighting system is complex and different from conventional lighting. It provides a lot of design and reliability challenges in the area of electrical, packaging, optical and luminaries.

LED's are constant voltage load with a low equivalent series resistance. Most of the LED's are powered by DC source. For general lighting it becomes essential to convert AC main supply voltage to regulated DC voltage using rectifiers and filters. Based on the topology of the connected LED's i.e. series or parallel, a constant voltage regulated driver or current regulated driver is used [4]. The electronics components in the SSL system that account to cost and PCB space include rectifying diodes, driver IC and passive components. The process integration of the electronics and passive components by monolithically or wafer level integration can significantly bring down the initial cost of the SSL system. Since SSL is based on semiconductor technology, it can be integrated with standard CMOS process to create a complete multifunctional miniaturized module.

In the introductory chapter, the design of an SSL system is first discussed. Then the concepts of wafer level integration for SSL are presented. Finally, the research focus and a systematic approach followed in the thesis for monolithic integration of rectifiers and driver for low power solid state lighting system on rigid to flexible platform is presented.

## 1.1 Solid State Lighting System

The design of SSL system is similar to a microelectronics system design. It is different from the conventional lighting system design. The fundamental part of the SSL system is the LED (Light emitting diode). Light Emitting Diodes are p-n junction diodes when forward biased emit light by spontaneous recombination of electron-hole pairs and simultaneous emission of photons. The energy of the photons emitted determines the wavelength of light emitted. LED's are made from silicon carbide material or III–IV semiconductor like gallium arsenide, gallium nitride. The light emitted from LED occupies a narrow spectrum and the specific wavelength or color depends on the band gap of the material. Most white light LED's use an LED emitting at shorter wavelength (e.g. blue) and a wavelength converter (e.g. phosphor). The light emitted by the blue LED is absorbed by the phosphor material and converted as white light with longer wavelength [5]. The quality measurement of LED's are defined using the table of white light from blue LED is achieved by wavelength converters. The LED die is mounted in a on a silicon carrier and installed in a package for electrical connection. This LED module is the fundamental component of the solid state lighting system.

A brief summary of SSL system components and its functions is presented in Table 1.1[6]

**Table 1.1 Levels of SSL System**

| Level | System Component              | Example                                 | Function                                                                   |

|-------|-------------------------------|-----------------------------------------|----------------------------------------------------------------------------|

| 0     | LED Die                       | F. A.                                   | To achieve high luminous efficiency                                        |

| 1     | LED Package                   |                                         | For electrical connection, heat dissipation and mechanical stability.      |

| 2     | Multi LED Board               |                                         | Increasing the number of LED's for higher lumen output.                    |

| 3     | LED Power Control and Drivers | T A A A A A A A A A A A A A A A A A A A | To convert AC to DC and provide constant current and control of the LED.   |

| 4     | Luminaire Designs             | PHILIPS                                 | To enable usage of LED bulb as conventional bulb by using retrofit design. |

| 5     | Lighting System<br>Designs    |                                         | Multiple interconnected luminaries for lighting system on large scale.     |

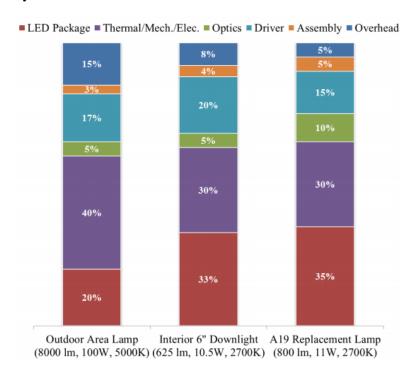

As described in Table 1.1, it can be seen that the electronics components comprise more than 50% of a complete SSL system. The main semiconductor IC components of this system are power converters and driver circuitry. A composition of the cost analysis of driver for SSL

system for a LED lighting system is shown in Figure 1.1[2]. The major cost component of the LED system is due to the LED package which contributes to about 30% of the total LED bulb. The other component that drives the cost is the thermal/ mechanical housing and electrical components in the system.

Figure 1.1 Cost breakdown of SSL System

Since LED packaging and electronics are the critical components that drive the total system cost, the integration of both packaging and electronics for the SSL system can result in the reduction of total system cost. Some of the concepts of wafer level integration are discussed in the next section.

## 1.2 Wafer Level Integration for SSL system

Heterogeneous wafer level system integration and packaging is a key driving technology for multifunctional system in a package (SiP) microelectronic systems for reducing cost, size and improving performance. The main aspect of system in a package technology is to combine semiconductor technology with other technologies in an electronic packaging dimension. This includes integration of heterogeneous functions like electrical, optical, mechanical to create high value single miniaturized system package at low cost [7].

For a SSL system in a package, the main challenges include integration of power converters, drivers and passives along with LED module. Since LED's are manufactured on

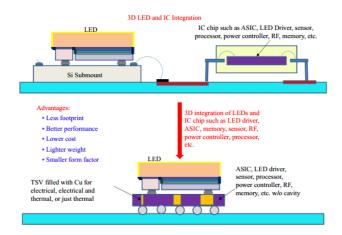

silicon carbide or gallium nitride substrate and semiconductor IC technology is on silicon substrate, it is not possible to integrate both lighting functions and IC functionalities on a single substrate. One of the methods for integrating LED module with integrated circuits is shown in Figure 1.2 [6]. In the first design the LED is mounted on a silicon sub mount and wire bonded to the PCB for electrical connection. The IC chip for LED driver and power controller are packaged components connected to the LED through PCB interconnections.

Figure 1.2 3D LED and IC integration

With 3D integration the passive Si sub mount in the LED module will be replaced by the ASIC, LED drivers, power controller and processors in a 3D method. The electrical connection for this module is achieved by through silicon vias (TSV) of copper. The main advantages of this system in a package is less footprint, low cost and small form factor [6] [8].

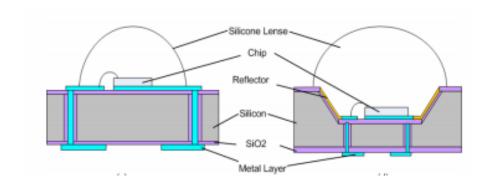

Conventional LED packaging consists of LED module with interconnect leads housed in a ceramic packaging. A better LED packaging technology that is suitable for wafer level integration is using silicon based packaging. Silicon is used as carrier wafer and interconnection with LED is made using through silicon vias (TSV). The LED chips are then encapsulated in a silicone lens. An example of silicon based packaging is shown in Figure 1.3 [9].

Figure 1.3 LED packaging on Silicon platform

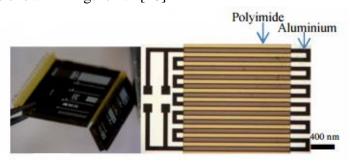

Since, SSL system is essentially a microelectronic system with semiconductor components like diodes, driver IC's required of powering the LED chip; a silicon platform for LED chip packaging allows a great possibility of integration of semiconductor devices along with the LED chip for a complete wafer level integration of SSL system. The wafer level packaging on silicon discussed in Fig 1.2 is rigid and two-dimensional. A 3D form factor for wafer level packaging of LED can be achieved by using flexible interconnect technology as discussed in [10] .The flexible interconnect technology consists of aluminum layer sandwiched between two spin layers of polyimide material. An example of aluminum interconnect embedded in polyimide substrate is shown in Figure 1.4 [10]

Figure 1.4 Rigid to Flex interconnect technology

A combination of silicon wafer level packaging using flexible interconnect and integration of power converters ,drivers and sensors on chip to form a single system in a package offers great potential for smart miniaturized SSL system.

The main challenge using silicon as the substrate material for integration is that the breakdown voltage for silicon is less than 100V [11]. Hence, silicon as substrate material cannot be used for high power lighting application. The power converters and driver electrical circuit for the LED require large storage capacitors. These are used as discrete components on PCB. The electrolytic capacitors are mainly used as the storage capacitors. They are bulky and occupy a lot of space. Another challenge with silicon as the substrate is the integration of capacitors in silicon to match the storage capacity of electrolytic capacitor.

By considering the above drawbacks of silicon, the design considerations have to be made to know about the components that can be integrated on chip and off chip. For low voltage applications, silicon as substrate material offers a great potential for monolithic integration of rectifiers and drivers. But passive components such as capacitors, inductors and high watt resistors provide huge challenges to be integrated on-chip. These components have to be off chip components.

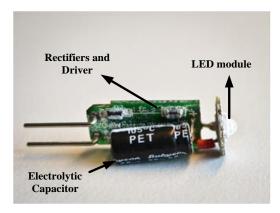

In order to study the feasibility of integration of power converters and drivers using silicon as the substrate material, we consider a low power LED module – for example a G4 retrofit LED capsule. A breakout of the G4 capsule is shown in Figure 1.5 [12]. The PCB consists of discrete components such as diodes, electrolytic capacitor and driver IC. The research

focus of the thesis project is to build a integrated rectifier and driver on chip to reduce system cost and PCB space.

Figure 1.5 G4 LED Capsule

## 1.3 Design and Thesis focus

In this thesis, a proof of concept for monolithic integration of rectifiers and drivers in a standard BiCMOS7 for low power LED system is investigated. In this section, the electrical requirements of G4 retrofit LED capsule and design proposal for integration of the rectifiers and drivers on a rigid to flex substrate is presented.

#### 1.3.1 Electrical specifications for G4 retrofit LED capsule

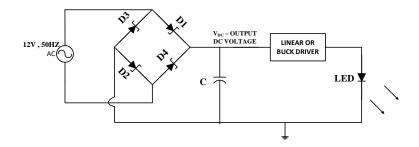

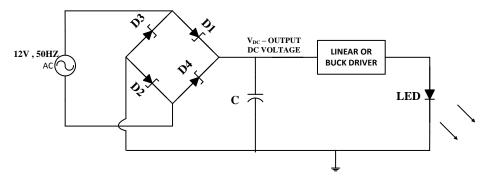

The G4 LED capsule is a 2.5W that can provide a lumen output of 100lumen. The input voltage requirement of G4 LED capsule is 12V AC. The G4 module uses a single LED for light output. Considering these specification for a low power LED system, the basic block diagram of this system is shown in Figure 1.6. The input 12V AC is first converted into DC by a bridge rectifier. The bridge rectifier uses schottky diodes due to their low forward voltage drop and high current conduction.

Figure 1.6 Schematic of a low power 12V LED system

During the positive half cycle of ac input voltage diodes D1 and D2 are forward biased. The current flows from diode D1, the capacitor C and LED load. During the negative half cycle the diodes D3 and D4 are forward biased and current flows through D3, D4, capacitor C and the LED load. Since two diodes are in series when forward biased, the output voltage  $V_{dc}$  will be lower than the input voltage by two voltage drops of the diode. If we consider ideal schottky diodes with forward voltage drop of 0.4V, then for a 12V input ac voltage the output dc voltage will have a maximum voltage of 11.2V. The important parameter for the bridge rectifier is the peak inverse voltage (PIV) rating. The peak inverse voltage is the maximum voltage across the diode during the reverse bias condition. It is given by [13],

$$PIV = V_m \tag{1.1}$$

Where,

V<sub>m</sub> – Peak AC input voltage

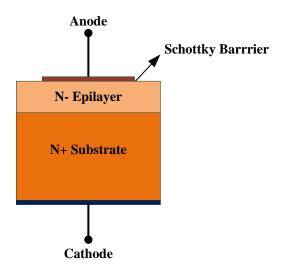

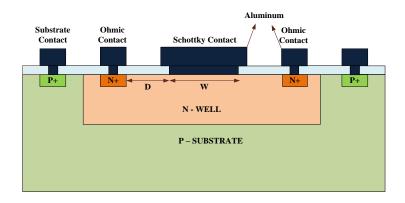

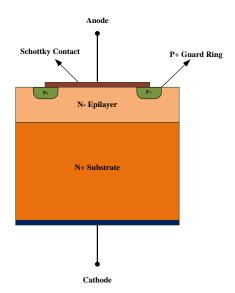

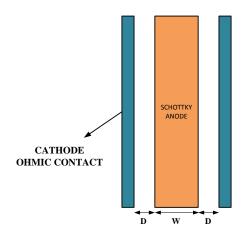

For an AC input voltage of 12V, Vm = 16.97 volts. Hence the peak inverse voltage of the bridge rectifier in Fig 1.6 is PIV = 16.97V. The schottky diodes must have a breakdown voltage that is greater than 16.97V to block the AC voltage during negative half cycle. A breakdown voltage of 40V is desired for schottky diodes in this configuration. The commercial available schottky diodes used for rectifier circuit have vertical device structure with a top anode contact and bottom cathode contact as shown in Figure 1.7[11]. With the vertical structure it is difficult to integrate in a planar standard BiCMOS process. An example of planar structure of schottky diodes is shown in Figure 1.8[14]. The current flow laterally in this device is from schottky contact to the ohmic contact. This structure provides a great potential for integrating the rectifiers using schottky diodes in a planar standard BiCMOS. In this thesis, a detailed study on the design and fabrication of high current and high breakdown schottky diodes in standard BiCMOS process suitable for low voltage integrated rectifiers is presented.

Figure 1.7 Vertical power schottky diode

Figure 1.8 Schottky diode structure in Standard CMOS process

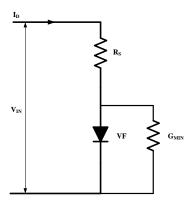

The two methods to maintain constant current in a LED are by using a linear driver or a switch mode driver. The linear current driver is cost effective but it has poor efficiency. A basic circuit for linear constant current driver for LED is shown in Figure 1.9 and Figure 1.10[15].

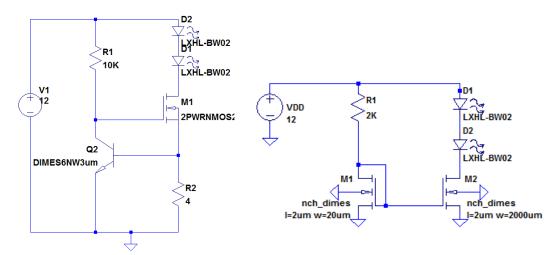

Figure 1.9 Linear driver circuit example Figure 1.10 Current mirror linear driver

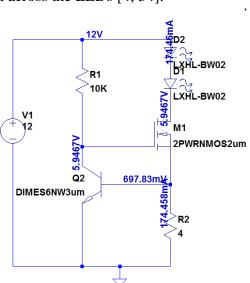

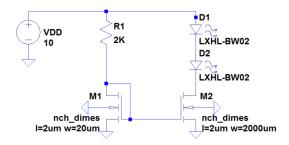

The current in the circuit in Figure 1.9 is set by the resistor R2. The NMOS is on when the voltage at R1 is greater than the threshold voltage of the NMOS. The transistor Q2 turns on with base emitter voltage Vbe of the transistor set by voltage drop across R2 that should be less than 600mV. The transistor Q2 turns on it pulls down the voltage at the gate of the NMOS causing the MOSFET to go into linear region and limits the current in the circuit. In the Figure 1.10 ,the circuit for the linear driver is a constant current mirror of nmos devices. The current through the LED's is set by the resistor R1. The current in the LED branch is set by the ratios of the width of the NMOS M1 and M2.

In a switch mode regulator configuration, the switch basically mosfets takes a small portion of energy for a given time from the input voltage source and transfers it to the driven load [16].

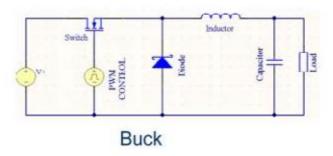

Figure 1.11 Schematic of Buck driver topology

The switch mode driver is more efficient in power conversion than linear drivers. A simple circuit of a buck driver is shown in Figure 1.11.In the switch mode driver the main components that controls the switching function is the PWM controller. When the switch is closed the mosfets is on and the current flows through the inductor and the load while the diode is reverse biased. When the switch is open, the energy stored in the inductor provides the current path through the diode which is forward biased. At the output of the load instead of square voltage only a ripple voltage will be seen[16]. The integration of switch mode driver on chip is difficult due to the presence of inductor and capacitor components in the circuit. A basic explanation of the rectifiers and drivers are discussed in this section. The on chip components that can be integrated will include power mosfets, schottky diodes and PWM control IC. The output voltage of a buck driver is given by,

$$V_{out} = V_{in} \frac{T_{ON}}{T} \tag{1.2}$$

where,

$V_{in}$  – input DC voltage  $T_{on}$  – Duty cycle of the PWM control

One of the basic topology of the PWM control for the buck driver is discussed in paper [17]. The circuit is shown in Figure 1.12. This circuit consists of an error amplifier and a PWM generator for controlling the power mosfets. This circuit uses the sense resistor to apply feedback for the PWM control. If the value of the sense resistor voltage is greater than the reference voltage, the output of the error amplifier is negative and the PWM control is adjusted so that the voltage across the sense resistor increases and the error amplifier output attains a positive value. The PWM amplifier uses a saw tooth waveform to generate a pulse output based on the output of the error amplifier and the compensation network of R and C.

Figure 1.12 Schematic of average current control buck driver

This thesis does not focus on the implementation of PWM control but provides a basic design of buck driver circuit in which a ring oscillator controller is used for switching the power mosfets.. The ring oscillator has a duty cycle of 50% which provides an output voltage which is equal to half the input DC voltage.

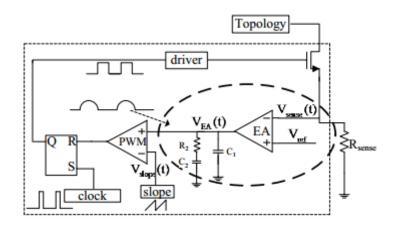

#### 1.3.2 Design proposal

In this thesis, monolithic integrated of bridge rectifiers using schottky diodes are designed, fabricated in BiCMOS7 process. BiCMOS7 is a semiconductor fabrication process in which diodes, transistors and mosfets are fabricated in a planar process on a single substrate. The DIMES BiCMOS7 process is simple, low cost 7 mask process to fabricate the devices. The schottky diodes fabricated in standard planar process have a breakdown of about 27V. The fabricated chip in this process with rectifiers using schottky diode are shown in Figure 1.13.

Figure 1.13 Fabricated Integrated rectifiers chip in BiCMOS7

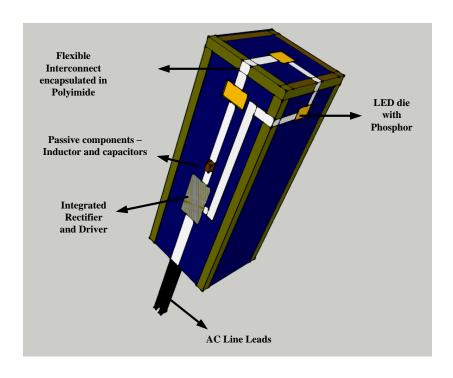

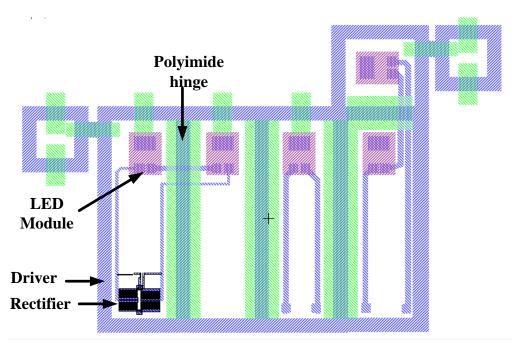

The integrated rectifier has a dimension of 3mm by 3mm. The schottky diodes are optimized for high breakdown and high current conduction as discussed in detail in chapter 2 of the thesis. Using the same BiCMOS7 process in which the schottky diodes and rectifiers are fabricated, a design proposal for integrating both rectifiers and driver on a rigid to flex substrate is proposed. A 3D illustration of retrofit G4 module is shown in Figure 1.14. In this module, the on chip components include monolithic integrated rectifiers and drivers and the off-chip components include capacitors and inductors. The flexible interconnect allows a 3D form factor design and integration of more than one LED chip. This offers advantage of both monolithic integration of devices and 3D wafer level packaging of LED module using silicon as the substrate.

Figure 1.14 3D model of monolithically integrated rectifiers and drivers on to Flex-to-rigid substrate.

For the integration of schottky diodes, rectifiers a systematic design flow is followed in the thesis. The design flow and the related tools used in the process is shown in Figure 1.15. An analytical model of schottky diode in standard BiCMOS process is done and compared with the model of a conventional schottky diode in this step. This study gives us an understanding of the process and layout design required for achieving the specification of high current conduction and high breakdown voltage schottky diode. In the next step this analytical model is verified by simulations using TCAD software TSUPREM4 and MEDICI. This provides guidance for simulating the process and device models that allow us to predict the process parameters that would be required during fabrication of the devices. The next step is the electrical characterization of the schottky diodes. The measurements are done using cascade probe station with ICCAP software. A spice model is extracted from the measurement data for circuit analysis.

In the same measurement procedure, characterization of BJT and NMOS devices of the various wafers are done to extract the spice parameters.

Figure 1.15 Design Flow

Using the spice models extracted from the software, electrical circuit analysis is done for the basic linear and buck driver circuits. A design proposal is presented for integration of rectifiers and drivers on a Flex to Rigid substrate. This design steps allows us to check and iterate at each step to optimize the design for future process.

The key research goals of this thesis topic are,

- Develop an analytical model for designing schottky diodes in standard BiCMOS process for achieving high current conduction and high breakdown

- Process and Device Modeling of schottky diode in BiCMOS process to deduce a set of design parameters.

- To provide a complete methodology for electrical characterization and modeling of schottky diodes, NPN bipolar transistors and MOS devices.

- Analyze the driver circuits that can be integrated in this process.

- To provide a design proposal for integrating rectifiers and drivers on rigid to flex substrate

Since designing an SSL system is similar to designing a microelectronic system, for an in-depth design analysis it becomes essential to know the concepts from device processing to circuit analysis and packaging and integration for the system development. A design cycle for building a wafer level integrated SSL system with G4 capsule as an example is illustrated shown in Figure 1.16.

Figure 1.16 Design cycle for Wafer level integration of G4 module

A robust process and device modeling of the devices intended for integration on chip must be done. The devices are then fabricated and characterized. With the device models extracted from the measurement data, circuit analysis is done for integrating higher level circuits. Silicon wafer level packaging for LED dies and flexible interconnects for electrical connection is designed. The design concepts are tested for reliability and optimized in the next development cycle.

#### 1.4 Thesis Outline

In this thesis, monolithically integrated rectifiers is designed, fabricated in BiCMOS7 process and characterized. The thesis organization is discussed below,

In Chapter 2 a detailed analytical modeling for schottky diode in standard BiCMOS process is presented. Process and device modeling is done using TCAD simulation software like TSUPREM4 and MEDICI.

In Chapter 3 the fabrication process steps of schottky diodes and rectifiers in BiCMOS is presented. The schottky diodes are characterized and a spice model is extracted from the measurement data. A spice model is also extracted for NPN Bipolar transistor and NMOS devices fabricated in the same process.

In Chapter 4 the characterization of integrated rectifiers is discussed. A circuit analysis basic linear and buck driver from the spice model extracted is analyzed. A design proposal for integration of rectifiers and drivers on flex to rigid substrate is presented.

In Chapter 5, the conclusions of the thesis and future work recommendations are provided.

# Chapter 2

## **Process and Device Modeling**

This chapter deals with process and device modeling of schottky diodes used in the design of integrated full wave bridge rectifiers. First conventional schottky diode characteristics and working is discussed. The factors affecting forward current conduction and breakdown of the schottky diodes are explained. The working principle of vertical and planar schottky diode structure is discussed. The process and device simulation for schottky diode in BiCMOS7 process is done in Tsuprem4 and device simulation in Medici. Finally, the design parameters for schottky diodes in DIMES standard BiCMOS7 are derived based on these modeling results.

### 2.1 Schottky diodes

The current transfer to external components from a semiconductor device can be achieved by two ways namely ohmic contact and schottky contact. Ohmic contacts are non-rectifying metal semiconductor junction with low-resistance providing current conduction in both directions. Ohmic contacts are made by sputtering or evaporating metal on highly doped p+ or n+ region. Schottky junction or schottky barrier diode contain a metal semiconductor junction with rectifying characteristics i.e. they allow current to flow only in forward biasing condition [18]. Schottky contacts are mostly made by sputtering or evaporating metal directly on low doped n– type semiconductor. Schottky diodes are unipolar semiconductor devices.

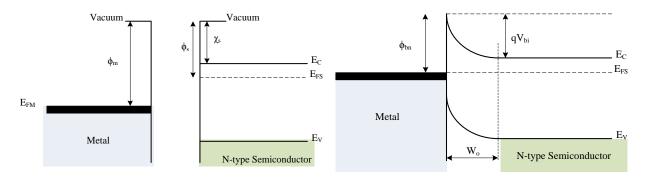

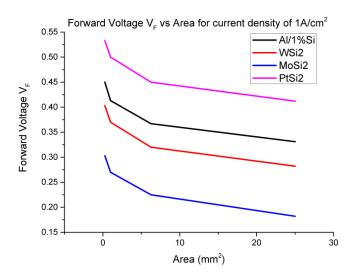

In order to understand the working principle of schottky barrier diode, let us consider the band diagram of metal and the semiconductor before and after contact. The energy band diagram of the metal and semiconductor before contact as discussed in [18] is shown in Figure 2.1. The vacuum energy level given by  $E_v$  is the energy level where the electron is essentially free from the metal.  $\phi_m$  is the metal work function defined as energy required in removing an electron from metal to vacuum level and  $\phi_n$  is the n-type semiconductor work function defined as the

energy required in removing an electron from semiconductor to the vacuum level. In the Figure 2.1, the situation of  $\phi_n > \phi_s$  is considered and Fermi level of semiconductor is above the Fermi level of the metal. When metal is brought in contact with semiconductor electrons will flow from semiconductor to lower energy states in the metal. At the interface of the metal-semiconductor the positively charged donor atoms create a space charge region and Fermi level become constant through the system as shown in Figure 2.2

Figure 2.1 Energy Band Diagram before metal contact

Figure 2.2 Energy Band Diagram after metal contact

At the interface, the electrons moving from the metal to the semiconductor see a potential barrier of  $\phi_{bn}$ . This barrier is called the schottky barrier [18] and it is given by,

$$\phi_{bn} = (\phi_m - \chi) \tag{1}$$

where:

$\phi_m$  = metal work function of the metal,

$\chi$  = electron affinity of the semiconductor

Next the electrons from the conduction band of the semiconductor moving into the metal see a barrier given as built-in potential barrier  $V_{bi}$ . This is given by,

$$V_{bi} = (\phi_{bn} - \phi_n) \tag{2}$$

where:

$\phi_n$  = work function of n-type semiconductor

$\phi_n$  is given as,

$$\phi_n = \frac{kT}{q} \ln \left( \frac{N_c}{N_d} \right) \tag{3}$$

where:

$N_c$  = effective density of states in conduction band,

$N_d$  = donor impurity concentration

From Eq (1), it can be seen that the schottky barrier height  $\phi_{bn}$  is dominantly dependent on the metal work function and the semiconductor in contact.

The current mechanism in schottky diodes is different from that of p-n junction diodes. The current in p-n junction diodes is mostly determined by the diffusion of majority and minority carriers across the depletion region in forward bias. In schottky diodes the current mechanism is by thermionic emission of the majority carriers over the potential barrier. In p-n junction diode the turn on voltage is dependent on the doping concentrations. In comparison, turn-on voltage of schottky diode is a function of barrier height of the metal semiconductor contacts. It is always less than the turn on voltage of p-n junction diode [18]. Since schottky diode is a majority carrier device, there is no minority stored carrier charge in the reverse bias condition. Schottky diodes are used in high frequency applications as it is able to switch between the on and off states very fast. They are used in rectifiers in low power systems due to their low forward voltage drop and high forward currents. The disadvantage of schottky diodes is that they have lower breakdown and higher reverse leakage current than p-n junction diode.

A cross section of vertical power schottky diode is shown in Figure 2.3. The main difference between conventional schottky diode and power schottky diode is the presence of a thick layer of lightly doped N-type drift region. This drift region supports the reverse blocking voltage of schottky diode. The wafers used for fabricating are heavily doped N+ substrate. The lightly doped N-type drift region is grown on top of the N+ substrate handle by epitaxial process [11]. The doping concentration of this drift region determines the blocking voltage of the schottky diode which is discussed later. A layer of silicon-di-oxide with thickness of about 300nm is thermally grown on the semiconductor. The contact openings are patterned and the silicon surface is cleaned to remove the native SiO<sub>2</sub> on the surface. Al /1% Si or other contact metal like tungsten, platinum is sputtered and patterned. This forms the schottky contact to the semiconductor and it is the anode terminal of the schottky diode. The bottom of the semiconductor is highly doped with n+ to obtain ohmic contact. This is the cathode terminal of the diode. The equivalent circuit of the device can be represented as diode and series resistance or on-resistance (Ron). This resistance is the sum contribution of the drift region resistance, substrate resistance and ohmic contact resistance.

Figure 2.3 Cross section of Power Schottky Diode

#### 2.1.1 Forward I-V Characteristics of Schottky Diodes

In this section the factors the forward voltage drop and current conduction is discussed. Under forward bias condition for schottky junctions on n-type semiconductor, the basic conduction mechanism as discussed in [18] is shown in Figure 2.4. They are described below,

- 1. Thermionic emission (A): Transport of electrons from the conduction band over the schottky barrier into the metal.

- 2. Electrons close to the barrier tunnel through the barrier (B).

- 3. Generation and Recombination of electrons and holes in the depletion region (C).

- 4. Hole injection into the neutral region of the semiconductor (D).

Figure 2.4 Schottky diode current transport mechanism in Forward Bias

The schottky diode forward I-V characteristics are mostly determined by thermionic emission (A) described in Figure 2.4. The forward current equation for schottky diode is given by [18],

$$I = AJ_F$$

$$= AJ_S[e^{(qV_a/kT)} - 1]$$

$$= AA^*T^2e^{-(q\phi_{bn}/kT)}[e^{(qV_a/kT)} - 1]$$

(4)

where:

A = active area of schottky contact,

$J_F$  = forward current density [ A/cm<sup>2</sup>],

$J_S = A^*T^2e^{-(q\phi_{bm}/kT)}$  = reverse saturation current density [ A/cm<sup>2</sup>],

$A^*$  = effective Richardson constant for thermionic emission,

$V_a$  = forward voltage drop across schottky contact.

The on-state voltage drop  $V_F$  of the power schottky diode depends on voltage drop across the schottky junction, ohmic voltage drop in the drift region, substrate and ohmic contact. For a given forward current density  $J_F$  it is given by [11],

$$V_F = V_{SCHOTTKY} + V_R = \frac{kT}{q} \ln \left( \frac{J_F}{A * T^2} \right) + \phi_{bn} + R_{ON} J_F$$

(5)

where:

RoN = total series-specific on resistance

From Eq (5), the main components that affect on-state voltage drop of the schottky diode are the schottky barrier height  $\phi_{bn}$  and specific on-resistance.

The total series specific on resistance *Ron* of the schottky diode is the resistance of the schottky diode under saturated forward bias condition. It is the sum of epitaxial drift layer, the substrate resistance and the contact resistance of anode and cathode. It is given by [11],

$$Ron = R_{DRIFT} + R_{SUB} + R_{CNT} \tag{6}$$

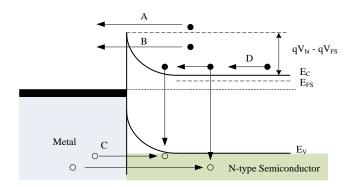

Since the drift region is lightly doped N-type semiconductor, it is the dominant factor of the total specific on resistance when compared to the highly doped N+ substrate and contact resistance. The resistance of the drift region is determined by epitaxial layer thickness ( $t_{epi}$ ), doping concentration ( $N_d$ ) and electron mobility ( $\mu_n$ ) [19] given by,

$$Ron \cong R_{DRIFT} = \frac{t_{epi}}{q\mu_n N_d}$$

[  $\Omega \text{cm}^2$  ] (7)

From Eq (7), the total on-resistance approximated to drift region resistance is inversely proportional to the doping concentration in the drift region for a given epitaxial layer thickness. The dependency of doping concentration and the drift resistance is shown below in Figure 2.5.

Figure 2.5 RON v/s Doping concentrations for different epitaxial layer thickness

The thickness of the epitaxial layer and the doping concentration is an important design parameter for the forward voltage drop. As seen from Figure 2.5 a higher doping concentration reduces the on resistance of the drift region and thus the on-state voltage drop of the diode.

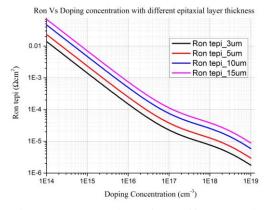

The next significant design parameter as per Eq (5) affecting the forward voltage drop is schottky barrier height. The schottky barrier height is a function of the metal work function as seen in Eq(1) earlier. A lower barrier height is needed to reduce the on-state voltage drop across the diode. The experimental determined value of schottky barrier height of various metals [11] is shown in Table 2.1 the effective Richardson's constant  $A^*$  for schottky contact with n-type semiconductor is given as 110 Acm<sup>-2</sup>K<sup>-2</sup>[20]. Using Eq (4) and Eq (5), the forward voltage drop  $V_F$  for forward current  $I_F = 1$ A is determined for different areas and schottky barrier heights in and illustrated in Figure 2.6. For lower on-resistance RoN, consider a doping density of  $10^{18}$  with epitaxial layer thickness of 3um which is calculated as  $7.65 \times 10^{-6} \Omega \text{cm}^2$ .

Table 2.1 On-state forward voltage drop V<sub>F</sub> for different metal contact and schottky area

| Metal             | Barrier<br>Height (eV) | Schottky Contact<br>Area (cm <sup>2</sup> ) | Current Density $J_F$<br>at $I_F = 1A (A/cm^2)$ | On state forward voltage drop $V_F(V)$ |

|-------------------|------------------------|---------------------------------------------|-------------------------------------------------|----------------------------------------|

|                   |                        | 0.05 x 0.05                                 | 400                                             | 0.450                                  |

| Al/1%Si           | 0.7                    | 0.1 x 0.1                                   | 100                                             | 0.413                                  |

|                   |                        | 0.25 x 0.25                                 | 16                                              | 0.367                                  |

|                   |                        | 0.5 x 0.5                                   | 4                                               | 0.331                                  |

|                   |                        | 0.05 x 0.05                                 | 400                                             | 0.403                                  |

|                   | 0.65                   | 0.1 x 0.1                                   | 100                                             | 0.370                                  |

| $WSi_2$           |                        | 0.25 x 0.25                                 | 16                                              | 0.320                                  |

|                   |                        | 0.5 x 0.5                                   | 4                                               | 0.282                                  |

|                   |                        | 0.05 x 0.05                                 | 400                                             | 0.303                                  |

|                   | 0.55                   | $0.1 \times 0.1$                            | 100                                             | 0.270                                  |

| $MoSi_2$          |                        | 0.25 x 0.25                                 | 16                                              | 0.225                                  |

|                   |                        | 0.5 x 0.5                                   | 4                                               | 0.182                                  |

|                   |                        | 0.05 x 0.05                                 | 400                                             | 0.533                                  |

| PtSi <sub>2</sub> | 0.78                   | $0.1 \times 0.1$                            | 100                                             | 0.500                                  |

|                   |                        | 0.25 x 0.25                                 | 16                                              | 0.450                                  |

|                   |                        | 0.5 x 0.5                                   | 4                                               | 0.412                                  |

Figure 2.6 Forward Voltage  $V_F$  for various barrier height and area at  $J_F = 1A/cm^2$

From the above analysis, the schottky metal contact with lower barrier provides a lower on state voltage drop. Increasing the area of the diode has a significant impact on the current conduction and the on state voltage drop. With large the area, the forward current density decreases and the on-state voltage drop decreases significantly. Considering a standard packaged schottky device dimension taken as  $A = 2.5 \text{mm} \times 2.5 \text{mm} = 6.25 \text{mm}^2$ , schottky contacts using MoSi<sub>2</sub> or WSi<sub>2</sub> provides higher current conduction at lower on-state voltage drop.

In this section, the factors affecting the on-state voltage drop and current conduction was discussed. It can be seen that a higher doping of the drift region and lower schottky barrier metal provides a good design choice for the fabrication of low voltage high current schottky diodes. But using a highly doped drift region affects the breakdown performance of the schottky diode. This is discussed in the next section.

#### 2.1.2 Analysis of Breakdown Voltage in Schottky Diodes

In schottky diodes, under reverse bias condition there is high electric field created in the interface of the metal contact and at the edges of the semiconductor metal contact. The large current flow with increasing reverse voltage is caused due to avalanche breakdown phenomena. In reverse bias, the electrons or holes that enter the depletion region due to diffusion or recombination are swept out by the electric field. With increasing reverse voltage, the depletion region electric field increases and the mobility of carriers is increased. These carriers collide with the lattice atoms and generate electron-hole pairs. This is referred as impact ionization which is a multiplicative process that generates more electron-hole pairs with increasing reverse voltage. The reverse current increases rapidly and the device breakdown at this condition. The critical electric field is dependent on the material and the doping concentration of the drift region. For

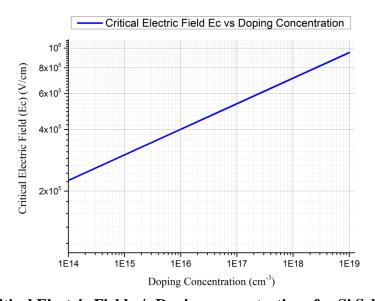

silicon the maximum critical electric field before breakdown is calculated to be  $2.5 \times 10^5 \text{ V/cm}$  [11]. The dependency of critical electric field with doping concentration is it is given by,

$$E_{C, Si} = 4010 N_D^{1/8} \tag{8}$$

where

$N_D$  = drift region doping concentration

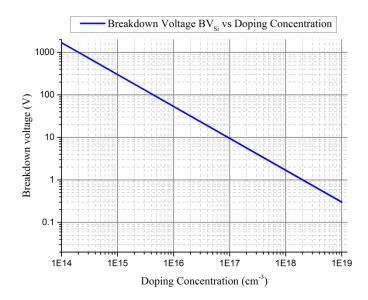

The relation of breakdown voltage with doping concentration in the drift region is given by Eq (9). The breakdown voltage at the schottky junction is inversely proportional to the doping concentration of the drift region [11]  $N_D$ .

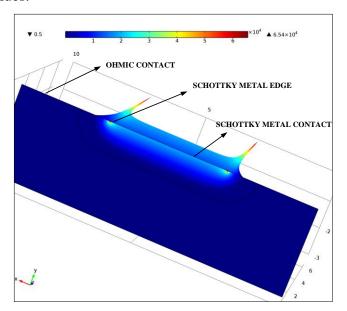

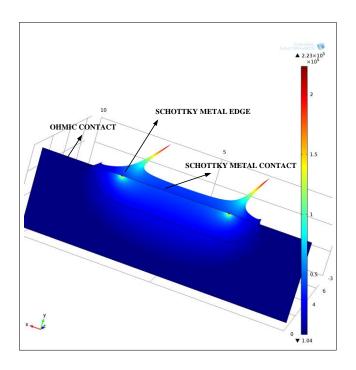

$$BV_{Si} = 5.34 \times 10^{12} N_D^{-3/4} \tag{9}$$

In the conventional schottky diode with increased reverse bias the depletion region at the schottky metal contact will expand both vertically and along the lateral direction. The electric field converges at the edge of the contact and it is maximum at the edge. The breakdown is mostly due to edge effect [21]. The high concentration of the electric field will give rise to increased reverse leakage current. This causes premature breakdown of the schottky diodes. The electric field distribution under large reverse bias modeled in COMSOL is shown in Figure 2.7 (Electric field range  $0.5 \times 10^5$  V/cm [blue] to  $3.8 \times 10^5$  V/cm [red]). The substrate is highly doped N+ layer with a doping concentration of  $10^{19}$ cm<sup>-3</sup>. The epitaxial drift layer has a doping concentration of  $10^{16}$ cm<sup>-3</sup>. At the edges the electric field is about  $3.8 \times 10^5$  V/cm whereas at the metal interface it is around  $0.5 \times 10^5$  V/cm. The electric field at the metal interface is still less than critical breakdown for Si  $(2.5 \times 10^5$  V/cm) but at the metal edges it has crossed this critical field value. This causes soft breakdown at the edges of the schottky diodes.

Figure 2.7 Electric Field at reverse bias voltage of 100V

From the analysis of forward conduction and breakdown voltage in schottky diodes it can be seen that for design the schottky diode the following cases is considered,

- 1. A lower doping concentration and thicker epitaxial drift layer is important for high breakdown voltage.

- 2. A higher doping concentration, thinner epitaxial drift layer, schottky metal with lower barrier height and large area device is important for lower on resistance, lower turn-on voltage and higher current conduction.

The above choice of design parameters of doping concentration, breakdown voltage and thickness of epitaxial layer is dependent on the application of the schottky diodes.

To improve the reverse breakdown voltage of the schottky diode many edge termination techniques are used. These are employed in Junction Barrier Schottky (JBS) diode which is explained in the next section.

#### 2.1.3 Junction Barrier Schottky Diodes

One of the main disadvantages of Schottky diodes are high reverse leakage current and lower breakdown. From the analysis of electric field and breakdown voltage in the previous section it can be seen that the breakdown voltage is predominantly determined by high electric field at the edges of the schottky metal contact. There are many methods employed to reduce the electric field at the edges of the schottky contact. In Junction barrier Schottky diode, a p+ guard ring is incorporated at the edges of the schottky metal contact junction in the n-type epitaxial drift layer [22, 23]. The cross-section of a Junction barrier schottky diode is shown in Figure 2.8. The equivalent circuit of this structure has schottky diode in parallel with a p-n junction. In forward bias, the forward voltage drop is defined by the voltage drop of the schottky diode.

Figure 2.8 Cross section of Junction Barrier Schottky diode

In reverse bias condition, the p+ junction depletion layer expands and a potential barrier is created at the schottky metal edge. This prevents the schottky barrier lowering and increase of reverse saturation current. The reverse blocking voltage of the schottky diode can be increased by this method. The p+ guarding is fabricated by argon or boron implantation

The forward conduction of the JBS diode is modified by the addition of the p+ guard ring. The series resistance is affected by the presence of the junction grid. The JBS show higher on state forward voltage drop when compared to conventional schottky diodes. But the reverse blocking voltage is increased by this structure.

The concepts of forward conduction and reverse conduction of conventional schottky diodes are discussed in this section. In the next section we discuss implementing the schottky diode in DIMES BiCMOS process.

### 2.2 Schottky diodes in BiCMOS process

Conventional schottky diodes and junction barrier power schottky diode are fabricated as vertical structure with top anode contact and bottom cathode contact. These are the general packaged diodes available as commercial off the shelf components. The disadvantage of these power schottky diodes having vertical structure is that it cannot be integrated monolithically with other integrated circuit components in a standard BiCMOS process. In this thesis project the requirement of a schottky diode with a breakdown voltage of 40V is desired. The schottky diodes fabricated in standard CMOS process forms the basic component of integrated low voltage full wave bridge rectifier circuit for powering the driver and LED. In this section we discuss the factors affecting the current conduction and breakdown voltage of schottky diodes in standard BiCMOS process. The current and breakdown mechanism in the planar schottky diode follow similar behavior as the vertical structure of the schottky diode discussed in the previous section.

### 2.2.1 Forward characteristics of Schottky diodes in BiCMOS process

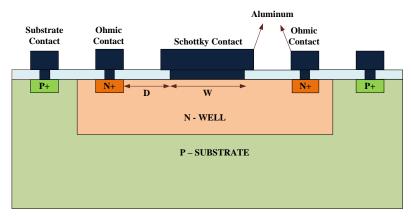

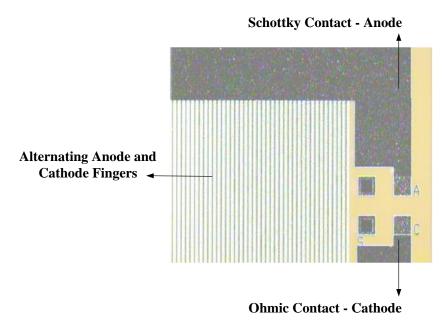

In the vertical structure of power schottky diodes there is a wide choice of metal like aluminum, platinum, tungsten that can be used in the fabrication process. But in the fabrication of planar schottky diodes in a standard BiCMOS process, the choice of metal for the schottky contact is limited. In this process, aluminum is the metal used for the schottky contact. The next difference between the vertical schottky diode and the planar schottky diode is the n-type region of schottky contact. In vertical schottky diode the schottky metal is in contact with a lightly doped n-type drift layer. In the planar process, the schottky metal is in contact with moderately doped n-type layer obtained by N-Well diffusion process. The anode contact of the schottky diode is made with the n-well region and the cathode ohmic contact is with a heavily doped n-layer [14, 24]. A cross-section of planar schottky diode is shown in Figure 2.9.

Figure 2.9 Cross section of Planar Schottky Diode device

The schottky contact area shown in Figure 2.10 is given as (W x L) where width W is the width of the schottky diode and L is the length of the schottky diode. The distance between the schottky contact and ohmic contact is defined with D. The drift region in this case is the lightly doped N-Well region. The current conduction in planar schottky diode is in the lateral direction from anode schottky contact to the cathode ohmic contact .When the anode terminal of the schottky diode is forward biased by applying a negative bias voltage, the electrons cross over the schottky barrier by thermionic emission move towards the cathode ohmic contact though the n-well region .The current under forward bias is given by the general schottky diode current equation as [24],

$$I = AA^*T^2e^{-(q\phi_{bn}/kT)}[e^{(qV_a/kT)} - 1]$$

(10)

where:

$A = \text{schottky contact area defined by } (W \times L)$

The current conduction of schottky diode described in Eq (10) follows similar mechanism of vertical schottky diode as explained before in section 2.1 of this chapter. The main factors for the consideration of current conduction are discussed below,

- 1. Schottky barrier height  $\phi_{bn}$  In this process the schottky barrier height is defined by the aluminum metal in contact and hence it is a constrained value.

- 2. Area of the schottky diode A The area parameter of the schottky diode is directly proportional to the current as seen in Eq (10).

- 3. Specific series on resistance  $R_{ON}$  This is the sum of resistance in the current path from schottky contact to ohmic contact. This component plays a significant role to determine the on-state voltage drop of the schottky diode.

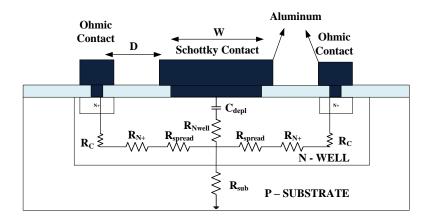

The total specific series on-resistance  $R_{ON}$  modeled by resistor components for the planar schottky diode is shown in Figure 2.10[25]. It is given as,

Figure 2.10 Components of series resistance in Planar Schottky Diode

$$Ron = R_{nwell} + R_{Spread} + R_{N+} + R_{C}$$

(11)

The resistance components in Eq (11) is discussed and analyzed. The first component  $R_{nwell}$  is the n-well resistance. This resistance is taken at 0V bias since the n-well will be undepleted and the resistance at this bias maximum. It is given as [25],

$$R_{\text{nwell}} = \frac{1}{WL} \rho_{\text{nwell}} T_{\text{nwell}}$$

(12)

where:

W =Width of the schottky contact,

L =Length of the schottky contact,

$\rho_{nwell}$  = resistivity of n-well layer,

$T_{nwell}$  = Thickness of un-depleted N-well layer,

The second component R<sub>Spread</sub> is the spreading resistance defined as the resistance due to the current spreading under and around the anode metal contact of the schottky diode. It is given as [25],

$$R_{\text{Spread}} = \frac{1}{3} \frac{W}{4} \frac{1}{L} \rho_{nwell} T_{nwell}$$

(13)

where:

W =Width of the schottky contact,

L =Length of the schottky contact,

$\rho_{nwell}$  = resistivity of n-well layer,

$T_{nwell}$  = Thickness of un-depleted N-well layer,

From Eq (12) and Eq (13), the n-well resistance and the spreading resistance is inversely proportional to length L of the schottky diode. These resistances can be minimized by increasing the length L of the schottky diode and keeping the width W as small as possible. The resistivity of n-well is inversely proportional to doping concentration. A higher doping concentration and a thinner n-well layer defined in the process can also contribute to reduce these resistances.

The third component is  $R_{N+}$  which is defined as the resistance in the current path due to the distance between the ohmic contact and the schottky contact. This distance is defined as D in the .Figure 2.10  $R_{N+}$  is given by,

$$R_{N+} = \frac{1}{2} \frac{D}{L} \frac{\rho_{n+}}{T_{n+}} \tag{14}$$

where:

D = Separation between schottky contact and ohmic contact,

L = Length of the schottky contact,

$\rho_{n+}$  = resistivity of n+ layer,

$T_{n+}$  = Thickness of n+ layer

The reduction of  $R_{N+}$  can be achieved by decreasing the separation between the schottky contact D to as minimum as possible. This is layout dependent parameter limited by the lithography limit of the process. The last component  $R_{C}$  is the contact resistance due to the ohmic contact. It is given by,