# **Characterization of pure boron depositions integrated in silicon diodes for nanometer-deep junction applications**

Francesco Sarubbi

**Characterization of pure boron depositions

integrated in silicon diodes

for nanometer-deep junction applications**

**PROEFSCHRIFT**

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus Prof. ir. K. C. A. M. Luyben,

voorzitter van het College voor Promoties,

in het openbaar te verdedigen

op maandag 18 januari 2010 om 15:00 uur

door

**Francesco SARUBBI**

Dottore in Ingegneria Elettronica

van Università degli Studi di Napoli 'Federico II', Italië,

geboren te Rome, Italië

Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. L. K. Nanver

Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. dr. L. K. Nanver, Technische Universiteit Delft, promotor

Prof. dr. ir. P. Kruit, Technische Universiteit Delft

Prof. dr. ir. J. W. Slotboom, Technische Universiteit Delft

Prof. dr. F. Roozeboom, Technische Universiteit Eindhoven

Dr. S. N. Nihtianov, Technische Universiteit Delft

Dr. G. N. A. van Veen, FEI Company, Eindhoven

Dr. T. Suligoj, Sveučilište u Zagrebu, Croatia

Prof. dr. E. Charbon, Technische Universiteit Delft, reserve lid

Francesco Sarubbi,

Characterization of pure boron depositions integrated in silicon diodes

for nanometer-deep junction applications,

Ph.D. Thesis, Delft University of Technology,

with summary in Dutch.

Keywords: boron (B), chemical vapor deposition (CVD), deep-/extreme-ultraviolet (DUV/EUV) radiation, diborane (B<sub>2</sub>H<sub>6</sub>), diode saturation current, doping, Gummel number, photodiode, *p*<sup>+</sup>*n* diode, *pnp* bipolar junction transistor (BJT), radiation hardness, responsivity, silicon, silicon-on-glass technology, solid-phase diffusion, ultra-shallow junction, varactor.

ISBN: 978-90-8570-436-2

Copyright © 2010 by Francesco Sarubbi

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written permission of the copyright owner.

Printed by CPI, Wöhrmann Print Service, Zutphen, The Netherlands.

# Contents

|          |                                                                              |           |

|----------|------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                          | <b>1</b>  |

| 1.1      | Boron doping by chemical vapor deposition . . . . .                          | 2         |

| 1.2      | Innovative nanometer-deep <i>pn</i> -junction applications . . . . .         | 4         |

| 1.2.1    | Silicon-on-glass varactors for RF applications . . . . .                     | 6         |

| 1.2.2    | Photodiodes for detection of ultraviolet (UV) radiation . . . . .            | 8         |

| 1.3      | Outline of the thesis . . . . .                                              | 11        |

| <b>2</b> | <b>Chemical vapor deposition of boron layers</b>                             | <b>13</b> |

| 2.1      | Processing conditions . . . . .                                              | 13        |

| 2.2      | Transmission electron microscopy analysis . . . . .                          | 14        |

| 2.2.1    | B-layer morphology and growth rate . . . . .                                 | 14        |

| 2.2.2    | Topography dependence: selectivity, uniformity, and isotropy .               | 15        |

| 2.2.3    | Low-temperature deposition . . . . .                                         | 16        |

| 2.3      | Secondary ion mass spectrometry analysis . . . . .                           | 18        |

| 2.3.1    | Boron content in as-deposited layers . . . . .                               | 18        |

| 2.3.2    | B-layer removal . . . . .                                                    | 19        |

| 2.3.3    | Boron diffusion during the deposition . . . . .                              | 20        |

| 2.4      | Electrical characterization of surface boron doping . . . . .                | 23        |

| 2.4.1    | Sheet-resistance measurements . . . . .                                      | 23        |

| 2.4.2    | Depletion-type MOS-capacitors . . . . .                                      | 24        |

| 2.4.3    | Capacitance-voltage profiling . . . . .                                      | 27        |

| 2.5      | Conclusions . . . . .                                                        | 30        |

| <b>3</b> | <b>B-layers studied in <i>p</i><sup>+</sup><i>n</i> diode configurations</b> | <b>31</b> |

| 3.1      | Device fabrication . . . . .                                                 | 31        |

| 3.2      | Ohmic contacts . . . . .                                                     | 32        |

| 3.3      | <i>p</i> <sup>+</sup> <i>n</i> junction diodes . . . . .                     | 34        |

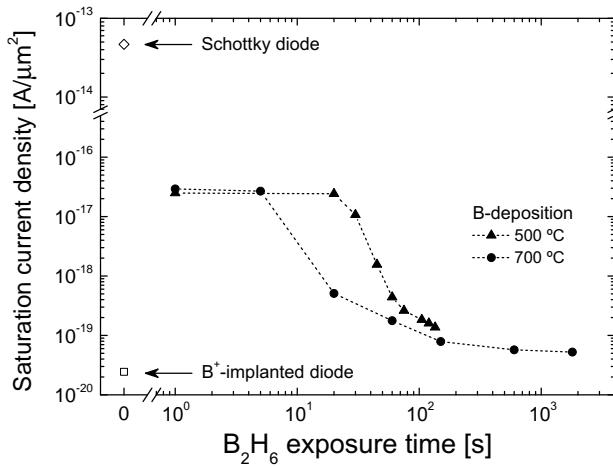

| 3.3.1    | Exposure time dependence . . . . .                                           | 34        |

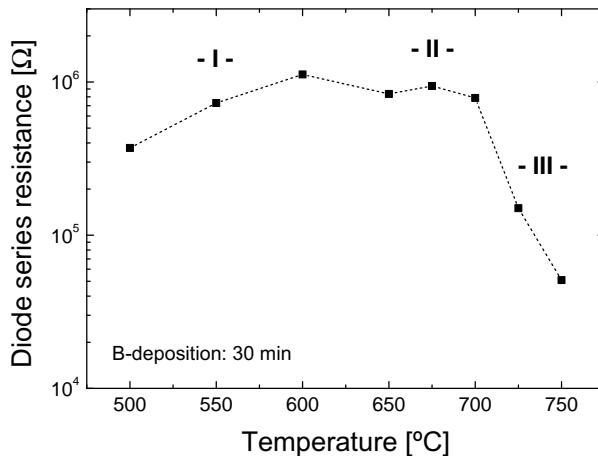

| 3.3.2    | Temperature dependence . . . . .                                             | 36        |

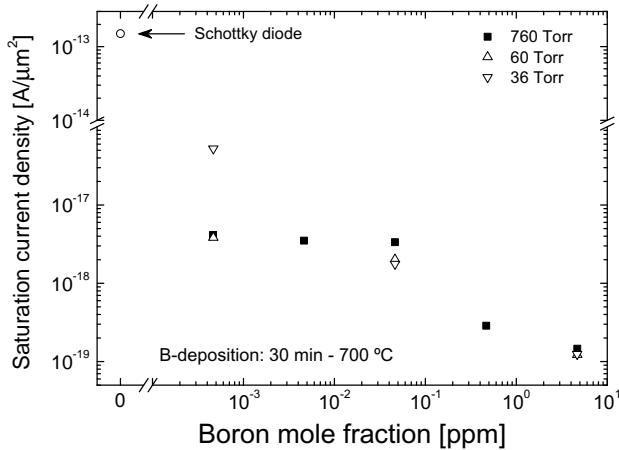

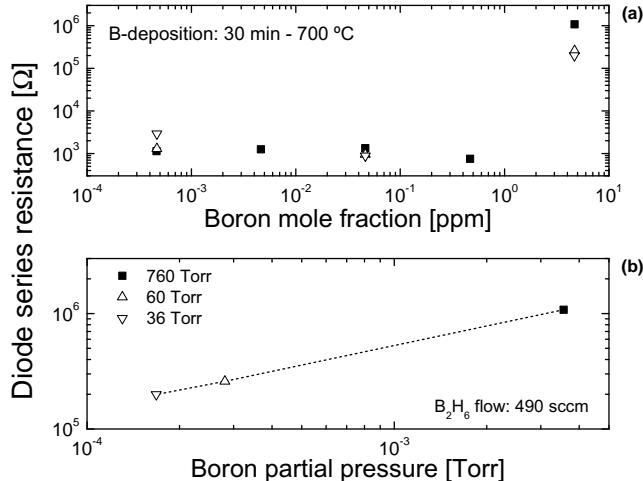

| 3.3.3    | Flow rate and pressure dependence . . . . .                                  | 37        |

| 3.3.4    | Masking . . . . .                                                            | 39        |

| 3.3.5    | Non-planar Si surfaces . . . . .                                             | 40        |

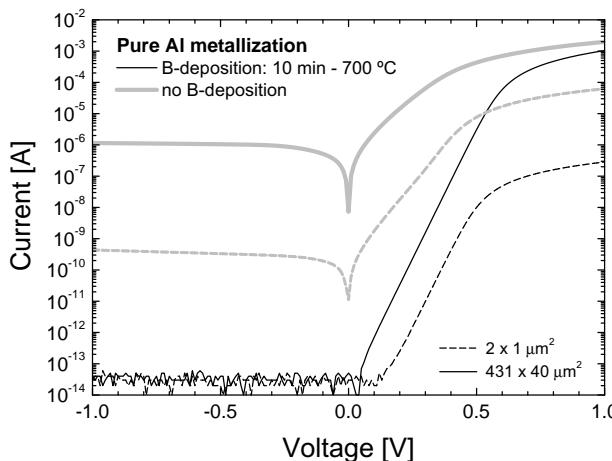

| 3.3.6    | Pure aluminum metallization . . . . .                                        | 40        |

|                                          |                                                                 |           |

|------------------------------------------|-----------------------------------------------------------------|-----------|

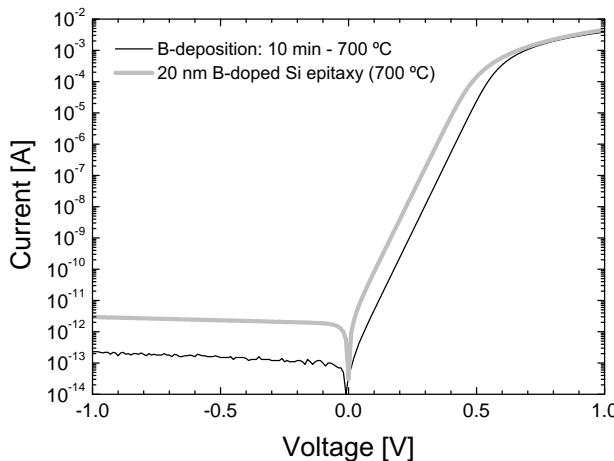

| 3.3.7                                    | Comparison of B-deposition and B-doped Si epitaxy . . . . .     | 42        |

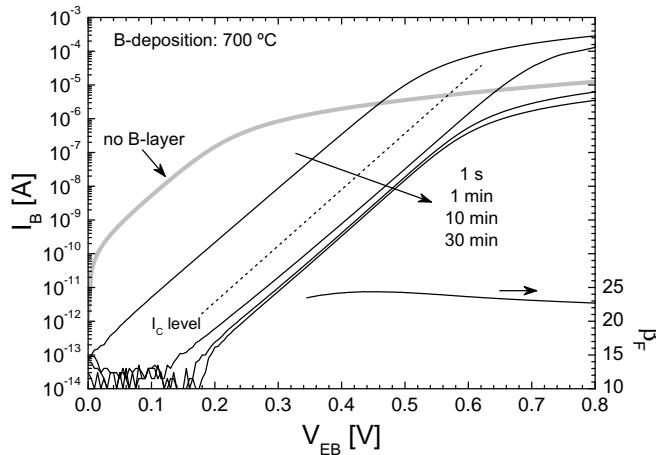

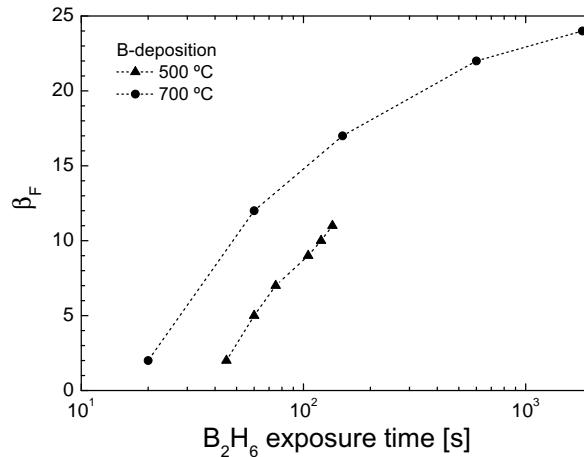

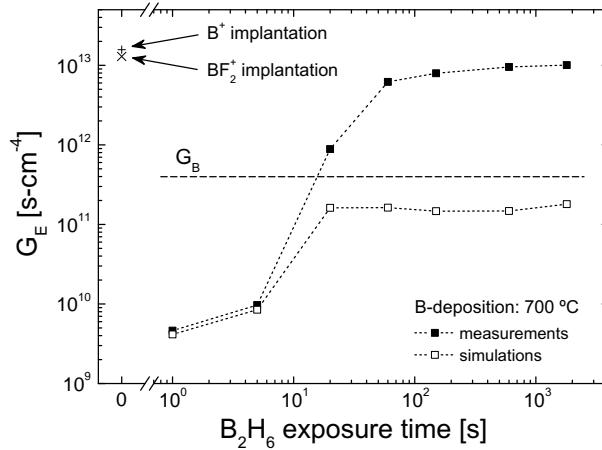

| 3.4                                      | Emitters in <i>pnp</i> bipolar transistors . . . . .            | 42        |

| 3.5                                      | Conclusions . . . . .                                           | 45        |

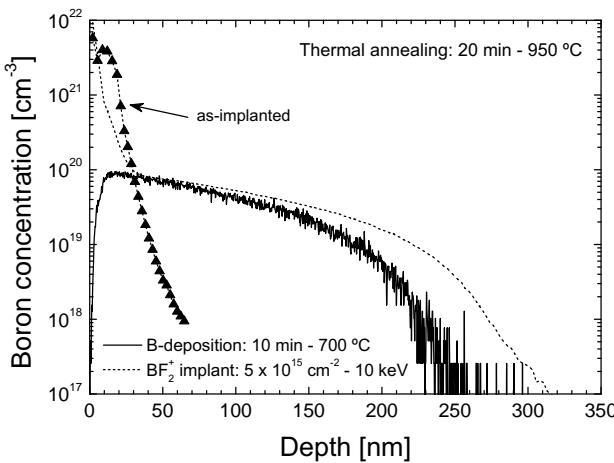

| <b>4</b>                                 | <b>B-layers as source for dopant diffusion</b>                  | <b>47</b> |

| 4.1                                      | Thermal annealing . . . . .                                     | 47        |

| 4.1.1                                    | Thermal annealing of $\leq 1$ ML boron coverage . . . . .       | 48        |

| 4.1.2                                    | Thermal annealing of B-layers . . . . .                         | 49        |

| 4.2                                      | Thermally annealed B-layers in <i>pnp</i> transistors . . . . . | 53        |

| 4.3                                      | Conclusions . . . . .                                           | 56        |

| <b>5</b>                                 | <b>B-layers applied to silicon-on-glass varactor technology</b> | <b>57</b> |

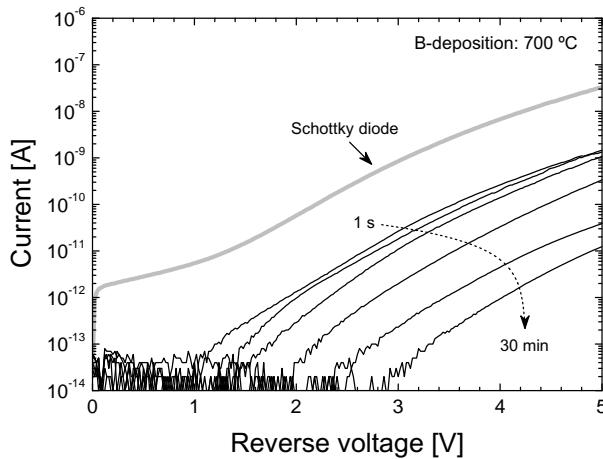

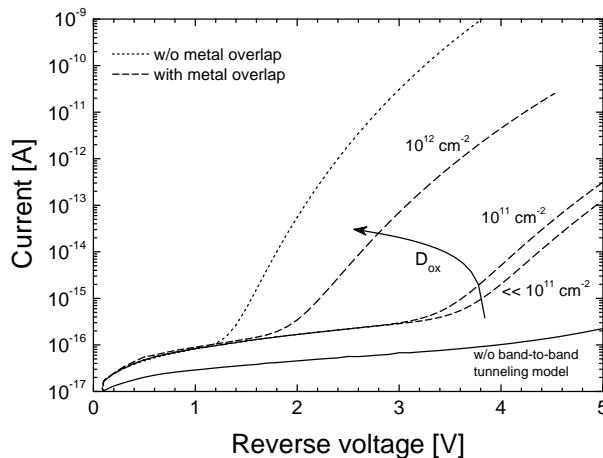

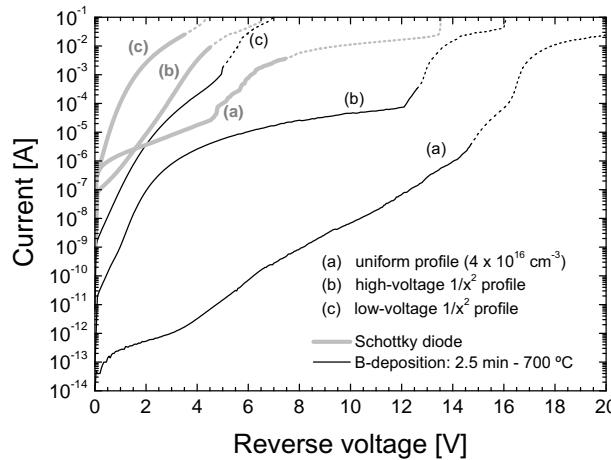

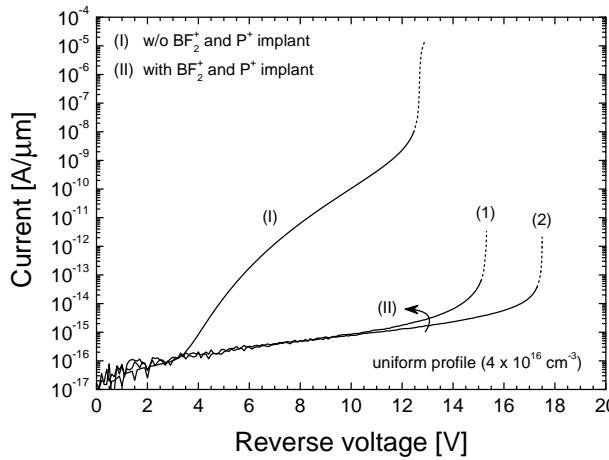

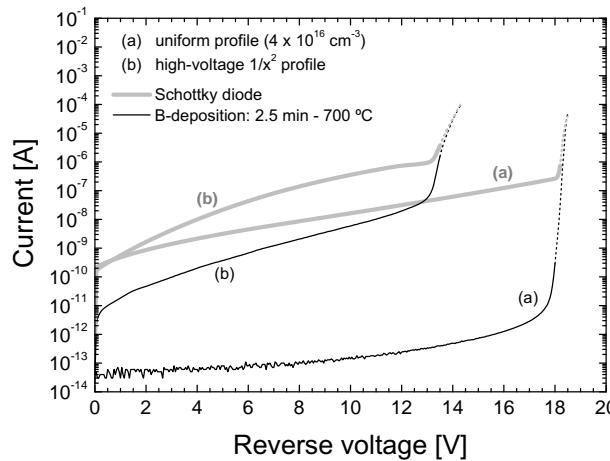

| 5.1                                      | Reverse I-V characteristics of as-deposited B-diodes . . . . .  | 57        |

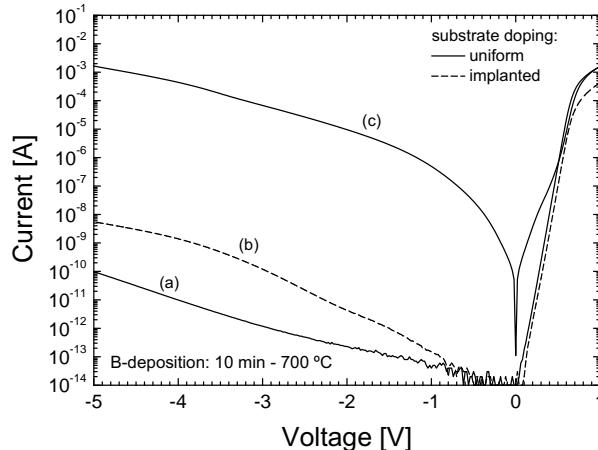

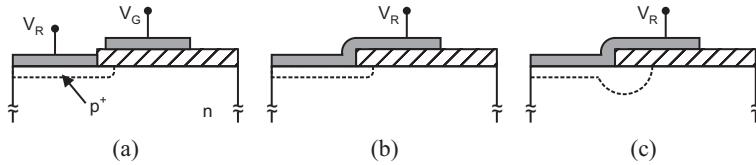

| 5.2                                      | Strategies for improving reverse I-V characteristics . . . . .  | 60        |

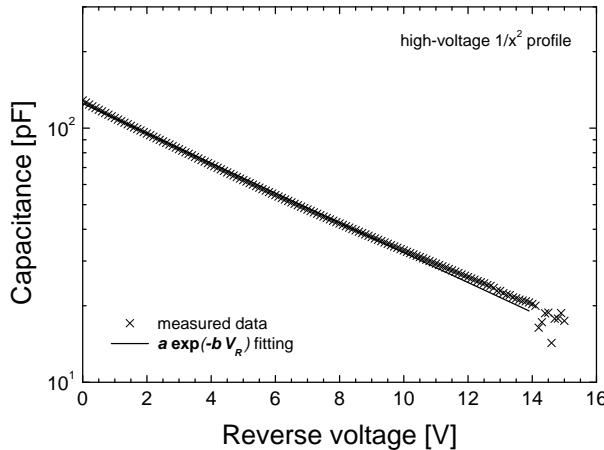

| 5.3                                      | Silicon-on-glass varactor technology . . . . .                  | 62        |

| 5.3.1                                    | Device fabrication . . . . .                                    | 64        |

| 5.3.2                                    | Electrical characterization . . . . .                           | 65        |

| 5.4                                      | Conclusions . . . . .                                           | 68        |

| <b>6</b>                                 | <b>Deep-/extreme-ultraviolet radiation photodiodes</b>          | <b>69</b> |

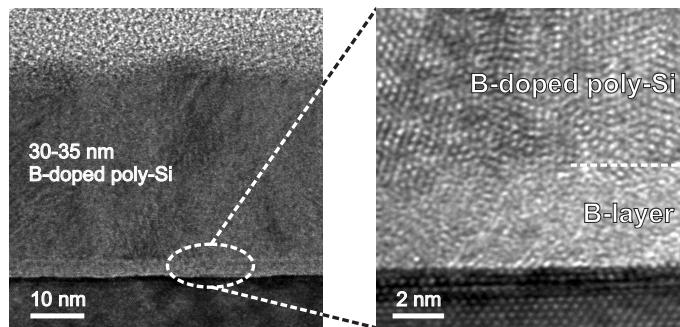

| 6.1                                      | Formation of photodiode $p^+$ front-area . . . . .              | 69        |

| 6.1.1                                    | B-deposition . . . . .                                          | 70        |

| 6.1.2                                    | <i>In-situ</i> thermal annealing . . . . .                      | 70        |

| 6.1.3                                    | Selective B-doped silicon epitaxial growth . . . . .            | 72        |

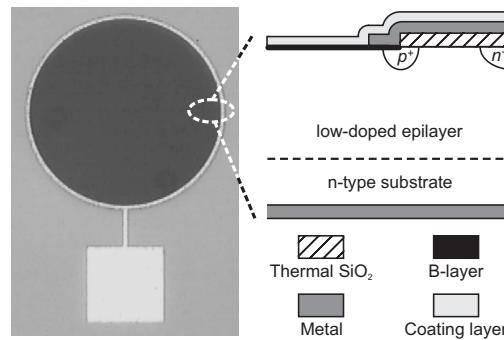

| 6.2                                      | Device fabrication . . . . .                                    | 73        |

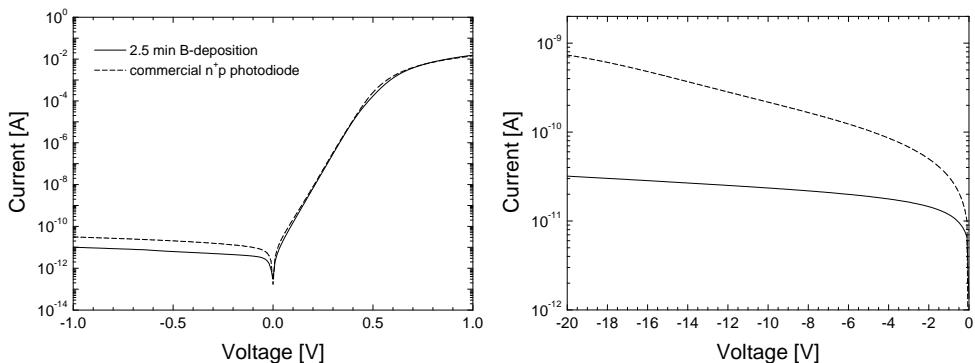

| 6.3                                      | Electrical characterization . . . . .                           | 74        |

| 6.3.1                                    | Dark current . . . . .                                          | 74        |

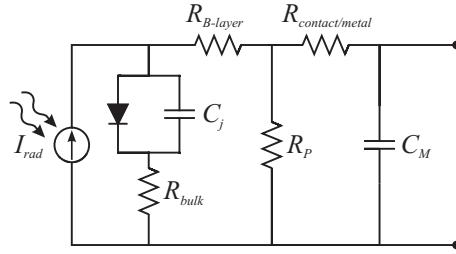

| 6.3.2                                    | Series resistance and response time . . . . .                   | 75        |

| 6.4                                      | Optical characterization . . . . .                              | 77        |

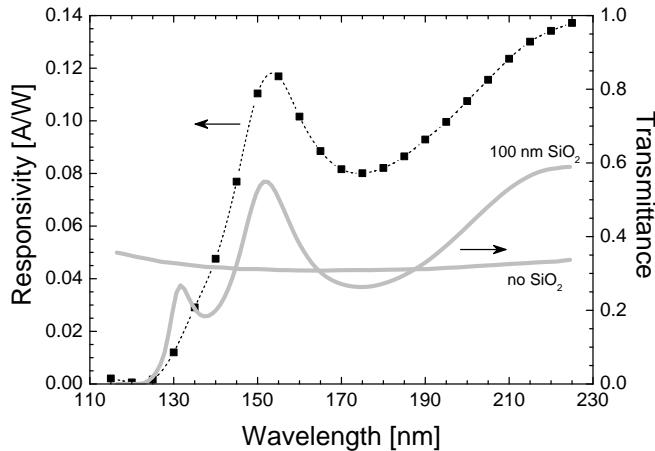

| 6.4.1                                    | Responsivity in DUV spectral range . . . . .                    | 77        |

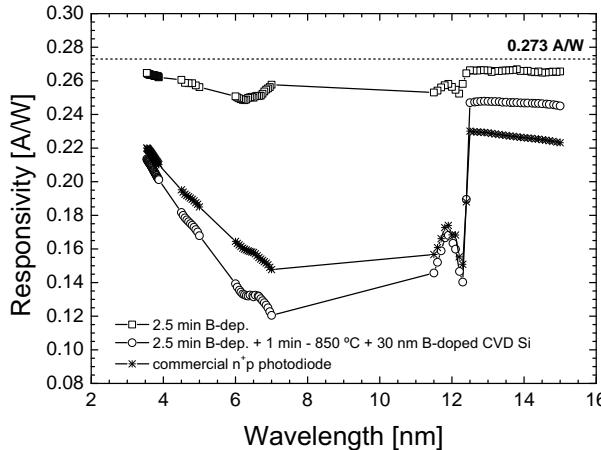

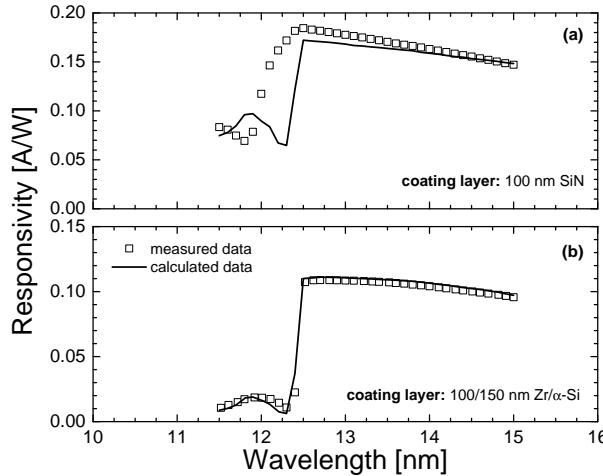

| 6.4.2                                    | Responsivity in EUV spectral range . . . . .                    | 78        |

| 6.5                                      | Performance stability . . . . .                                 | 80        |

| 6.5.1                                    | Dark current degradation . . . . .                              | 80        |

| 6.5.2                                    | Responsivity degradation . . . . .                              | 82        |

| 6.6                                      | Conclusions . . . . .                                           | 82        |

| <b>7</b>                                 | <b>Conclusions and recommendations</b>                          | <b>85</b> |

| 7.1                                      | Conclusions . . . . .                                           | 85        |

| 7.2                                      | Recommendations . . . . .                                       | 86        |

| <b>Bibliography</b>                      |                                                                 | <b>89</b> |

| <b>List of symbols and abbreviations</b> |                                                                 | <b>95</b> |

| <b>Summary</b>                           |                                                                 | <b>99</b> |

---

|                             |            |

|-----------------------------|------------|

| <b>Samenvatting</b>         | <b>103</b> |

| <b>List of publications</b> | <b>107</b> |

| <b>Acknowledgments</b>      | <b>111</b> |

| <b>About the author</b>     | <b>113</b> |

# Chapter 1

## Introduction

This thesis presents the formation of nanometer-thick boron (B) layers on (100)-oriented Si surfaces during exposure to diborane ( $B_2H_6$ ) in a chemical vapor deposition (CVD) system either at atmospheric or reduced pressures. At the applied temperatures from 500 °C to 700 °C, the deposition forms a layer stack of amorphous boron ( $\alpha$ -B) and boron-silicon compound ( $B_xSi_y$ ) from which the crystalline Si substrate (c-Si) is *p*-doped to depths below 10 nm up to the solid solubility by thermal diffusion. This process exhibits high selectivity to Si, isotropy, spatial homogeneity, and compatibility with standard semiconductor device fabrication. The dependence of the growth mechanism and boron doping on processing parameters is investigated by analytical techniques in conjunction with an extensive electrical characterization. The B-layer is also demonstrated to be a stable and controllable supply of B for the formation of deep  $p^+$ -regions by using thermal drive-in.

The pure B CVD process is applied to fabricate high-quality, extremely ultra-shallow  $p^+n$ -junction diodes, where the saturation current can be tuned from high Schottky-like values to low deep-*pn*-junction-like values by increasing the deposited B-layer thickness. In particular, the study of *pnp* structures with  $p^+$  B-deposited emitters shows that the presence of an  $\alpha$ -B layer significantly increases the effective Gummel number of the as-diffused emitter. Such unique properties are exploited with great advantages in  $p^+n$  diodes fabricated at 700 °C for the integration of two distinct device technologies: varactor diodes for adaptive functions in radio frequency (RF) applications and photodiodes for detection of ultraviolet (UV) radiation.

In the former case, B-deposition offers a low-temperature process module within the silicon-on-glass (SOG) substrate-transfer technology to secure hyper-abrupt arsenic (As) profiles needed for highly-linear tunable varactors. Similarly, outstanding electrical and optical performance is achieved for  $p^+n$  photodiodes implemented by forming the radiation-exposed  $p^+$  area with B-layers. In particular, this technology enables the maximum silicon spectral responsivity over the complete UV photon spectral range.

The following two sections of this introductory chapter illustrate the motivation of the research activity, which was focused on two areas: process/characterization of

a new material and integration in Si-based devices. First, on the materials level, the B-deposition is set within the general context of novel CVD doping technologies proposed to face the difficult challenges in the front-end processing that have emerged due to the aggressive downscaling of vertical dimensions for future semiconductor devices. However, the process substantially differs from other techniques that use  $\text{B}_2\text{H}_6$  exposure for surface doping, both with respect reaction kinetics and the low temperatures used. The latter is generally very attractive for versatile use of a doping technology. Thus, the deposition of a B-layer on Si is demonstrated to offer unprecedented advantages that have not been explored so far for formation of ultrashallow and more efficient *pn*-junctions in the nanometer-regime. On the device level, the integration of B-layers mainly aims to boost the performance of dedicated device technologies that are developed at DIMES of the Delft University of Technology.

## 1.1 Boron doping by chemical vapor deposition

Low-energy  $\text{B}^+$  and  $\text{BF}_2^+$  ion implantations conventionally combined with high-temperature, very short-time thermal anneals are the main techniques used by the semiconductor device industry to form  $p^+$  ultrashallow contacts and junctions. However, a drawback of this method is the undesirable broadening of the associated doping profiles due to implantation damage induced transient-enhanced diffusion (TED) effects that are particularly severe for B dopants. In addition, the presence of any lattice damage can be detrimental when the doping profiles in the vicinity of the junction are decisive for the device operation.

As an alternative to implantations, *in-situ* doping during Si or SiGe chemical vapor deposition (CVD) has been increasingly used, for instance in raised or re-filled source/drain CMOS regions or intrinsic bases of HBT devices. TED effects are effectively avoided since no lattice defects are created during the process. The advantages of CVD methods for device manufacturing reside also in low cost, high throughput, compatibility with standard semiconductor processing, and capability of well-controlled epitaxial growth even at low temperatures. In particular, diborane ( $\text{B}_2\text{H}_6$ ) gas is widely used as *p*-type dopant gas, while arsine ( $\text{AsH}_3$ ) and phosphine ( $\text{PH}_3$ ) are added for *n*-type doping.

However, a few studies have demonstrated *p*-like doping behavior of *n*-type (100) Si surfaces after exposure solely to  $\text{B}_2\text{H}_6$  in an oxygen-free atmosphere without any extra addition of silane-based sources, either using ultrahigh vacuum and low-pressure apparatus [1–5] or CVD systems operating at atmospheric pressure [6, 7]. This technique differs from other conventionally used *p*-type doping methods based on dopant diffusion from a gas source, where B drive-in is implemented in an oxidizing ambient. Moreover, in the latter case the doping efficiency, i.e. the maximum doping concentration, is governed by the solid solubility at the processing temperature. On the other hand, pure  $\text{B}_2\text{H}_6$  gas injection in the reactor chamber can lead the boron density at the Si surface to significantly increase beyond the solid solubility by appropriately varying the source gas parameters and the exposure time.

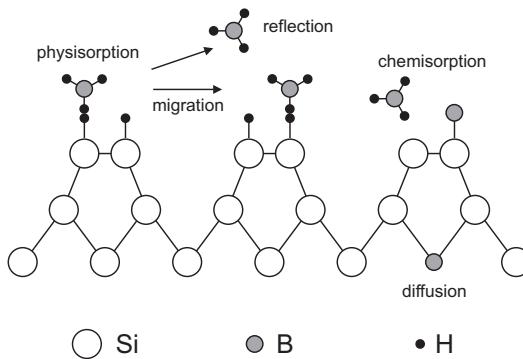

A model of the surface reaction doping for boron atoms on silicon during exposure

**Figure 1.1:** Doping reaction model for Si surface exposure to  $\text{B}_2\text{H}_6$  dopant gas (after [8]).

to diborane in a CVD reactor was proposed by [8], as schematically shown in Fig. 1.1. Assuming that  $\text{BH}_3$  is the dopant species generated by thermal dissociation of  $\text{B}_2\text{H}_6$  gas,  $\text{Si}-\text{H}$  are silicon atoms at the surface whose dangling bonds are terminated by hydrogen, and  $\text{Si}^\circ$  are silicon atoms with dangling bonds, the sequence of the mechanisms is:

1. Physisorption:  $\text{Si}-\text{H} + \text{BH}_3 \rightarrow \text{Si}-\text{HBH}_3$

2. Reflection:  $\text{Si}-\text{HBH}_3 \rightarrow \text{Si}-\text{H} + \text{BH}_3$

3. Migration:  $\text{Si}-\text{HBH}_3 + \text{Si}-\text{H} \rightarrow \text{Si}-\text{H} + \text{Si}-\text{HBH}_3$

4. Recombination:  $\text{Si}-\text{HBH}_3 + \text{Si}-\text{HBH}_3 \rightarrow 2\text{Si}-\text{H} + \text{B}_2\text{H}_6$

5. Chemisorption:  $\text{Si}^\circ + \text{BH}_3 \rightarrow \text{SiB} + 3\text{H}$

6. Diffusion:  $\text{SiB} \rightarrow \text{Si}^\circ + \text{B}(\text{diffused})$

Therefore, the  $\text{B}_2\text{H}_6$  surface reaction doping relies on the thermal decomposition of the source gas, so that the available boron atoms may stick to the surface, chemically react with silicon atoms, and diffuse into the substrate. However, the reactivity with the silicon surface is reduced by the presence of hydrogen-terminated silicon dangling bonds, since the physisorption and migration of  $\text{BH}_3$  precursor is enhanced. In fact, chemisorption and  $\text{Si}-\text{B}$  bonds formation, which is a prior step for the in-diffusion, can only occur when  $\text{Si}^\circ$  are available.

However, when all Si surface sites are occupied by B, the model should also take into account a chemisorption mechanism at B-occupied surface sites to describe the well-known non-self-limiting adsorption. Thus, the boron coverage can exceed one monolayer (1 ML), which is equivalent to the surface density of  $6.78 \times 10^{14} \text{ cm}^{-2}$  for (100)-oriented Si, and lead to the formation of a distinct boron layer [9, 10]. This behavior differentiates boron from other doping impurities, such as phosphorus and arsenic, [1, 4, 11, 12].

In this respect, the exposure conditions in terms of dopant gas flow rate and carrier gas play the most significant role. Indeed, termination of Si dangling bonds is maintained during dopant injection when hydrogen is used as carrier gas and the

diborane concentration is low ( $\leq 4$  ppm). This is valid even at high deposition temperatures, where hydrogen thermal desorption might be a dominant mechanism [11]. Thus boron segregation is suppressed, but actual doping of the substrate can be still achieved. On the other hand, either different inert ambient, such as in nitrogen gas, or high flow rate of diborane ( $\geq 6$  ppm) can significantly reduce the probability of hydrogen-terminated Si dangling bonds, and large amount of boron atoms can be deposited on the silicon surface proportionally to the exposure duration [8, 11]. At the same time, the growing B-layer will act as a source for boron diffusion into the silicon substrate during the CVD process itself [13].

While gas parameters can determine the transition from surface Si doping to B-deposition, the temperature mainly influences the actual boron doping of the silicon substrate and the final composition of the deposited film. In fact, high temperatures certainly increase boron diffusion at any gas flow conditions. On the other hand, boron-silicon compounds can be formed when B segregation occurs at high temperatures. In fact, as reported in [9, 10], boron silicide is the predominant phase in deposited film prepared at temperatures  $\geq 800$  °C. On the other hand, amorphous boron will be formed on the silicon surface if the deposition temperature is lower.

For device applications, the bulk of these earlier works focused on deposition temperatures around 800–900 °C, where substantial B-doping of the Si substrate is expected. Even though few experiments were performed at lower temperatures, such as 400–600 °C [5, 7], the exposure conditions were mainly chosen to prevent boron adsorption to less than a monolayer. In fact, either pure boron segregation or formation of boron-silicon compounds were often addressed as drawbacks of the  $\text{B}_2\text{H}_6$  reaction kinetics. In contrast to such propositions, in this work excessive B adsorption is intentionally promoted during  $\text{B}_2\text{H}_6$  exposure at temperatures down to 500 °C. The material and electrical properties of the deposited layer are studied as function of processing parameters and subsequently exploited in the formation of extremely ultrashallow junctions for silicon-based  $p^+n$  diodes.

## 1.2 Innovative nanometer-deep *pn*-junction applications

For several years now source/drain formation for CMOS devices has been the main driving force behind the development of novel doping technologies targeting nm-shallow, ultra-abrupt, and highly-doped junctions with damage-free properties. Likewise, for advancing the speed of SiGe heterojunction bipolar transistors (HBTs), downscaling and precise engineering of doping profiles has also become a crucial line of development.

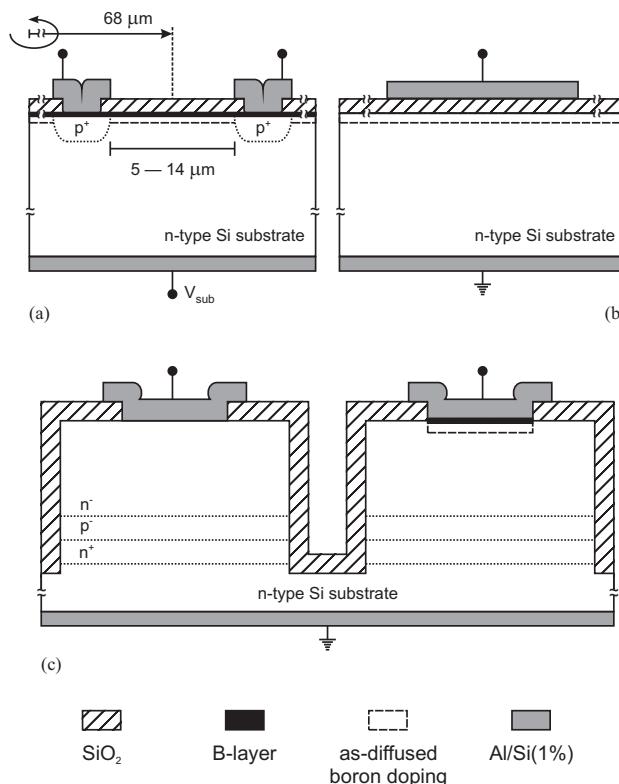

There are also many other *pn*-junction-based devices beyond the Bipolar/CMOS scenario that also can profit from advances in doping technology. Here the focus has been on two Si devices that have become the first, very successful, applications of the B-deposition:

1. varactor diodes for tunable circuits in RF applications,

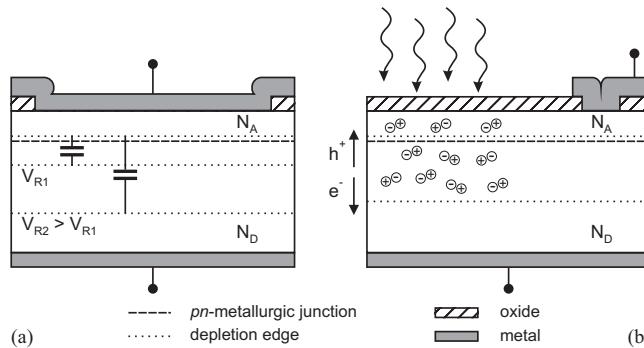

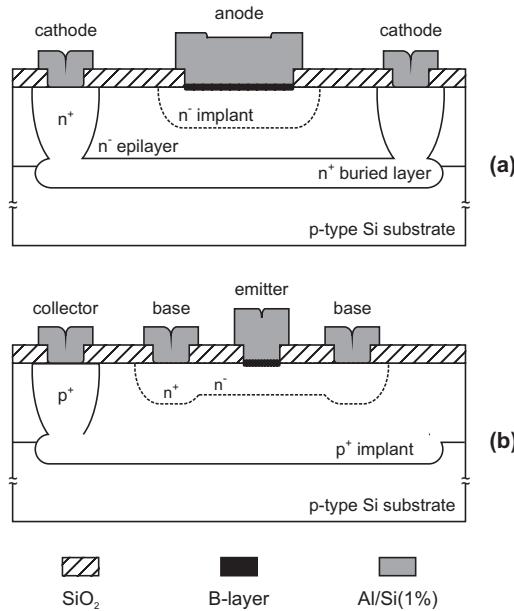

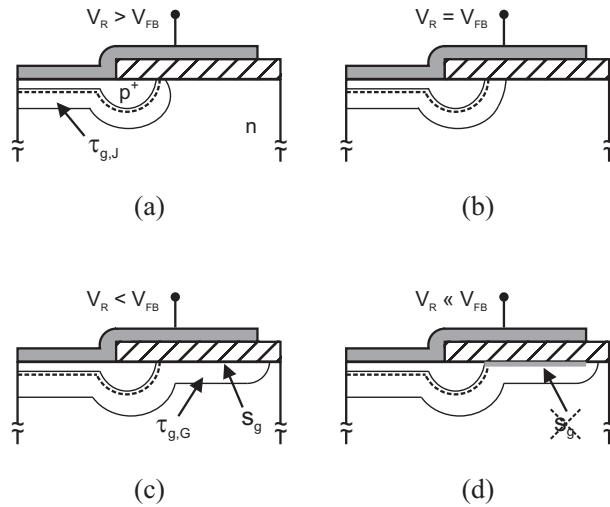

**Figure 1.2:** Schematic cross-section of: (a) a varactor diode and (b) a photodiode.

## 2. photodiodes for radiation detection in UV/soft X-ray spectral range.

Although both device concepts are well-known [14], their performance has been so far limited by manufacturability and design trade-offs. Schematic cross-sections of the devices are shown in Fig. 1.2 for a  $p^+n$  diode implementation, but similar conclusions can be drawn for  $n^+p$  structures. More details will be given in the following paragraphs, while here the general operating principles are briefly considered. This discussion, in fact, will essentially highlight the benefits on the device design and performance resulting from a doping technology that can provide ultrashallow junctions and high doping efficiency. The latter feature, rather than being associated with a low sheet-resistance of the doped region, is here mainly of importance due to the fact that an ‘effective’ one-sided abrupt junction can be formed ( $N_A \gg N_D$ ) in a manner that the diode current is only determined by the minority carrier injection into the substrate.

A varactor is a device whose reactance can be varied in a controlled manner with a bias voltage. In particular, the capacitance per unit area associated with the depletion region can be expressed as

$$C = \frac{\epsilon_0 \epsilon_{Si}}{W(N_D(x), V_R)} \quad (1.1)$$

where  $\epsilon_0$  is the permittivity in vacuum,  $\epsilon_{Si}$  the Si permittivity,  $W$  the depletion width,  $N_D(x)$  the n-type doping profile, and  $V_R$  the reverse bias voltage. Therefore, by properly varying the distribution of the bulk doping profile, many capacitance-voltage relationships can be achieved and thus different tunable capabilities. However, all the physics-based designs of  $N_D(x)$  are derived under the assumption of a one-sided abrupt junction, i.e. the depletion does not extend into the  $p^+$ -doped region due to the high dopant concentration and abruptness.

Photodiodes also count on the depletion region of a *pn*-junction and on the resulting electric field in order to separate electron-hole pairs generated by the incident radiation and to collect holes and electrons at the anode and cathode, respectively.

Nevertheless, photogenerated carriers are also formed in the quasi-neutral top diffused junction. In fact, the intensity of the radiation and thus the carrier generation rate inside the device decreases exponentially from the surface with a characteristic length, i.e. the penetration depth, defined as the reciprocal of the absorption coefficient at the incident radiation wavelength. Therefore, an extremely ultrashallow junction will be instrumental for minimizing the carrier loss in the quasi-neutral region, since electron-hole pairs can recombine before being collected at the electrodes, while most of the photogeneration could occur in the space-charge-region.

Based on these considerations, a Schottky diode would appear the most efficient solution for both devices, since it gives an ideal abrupt junction and the depletion starts already from the surface. On the other hand, since such devices generally operate in reverse bias conditions, *pn*-junction configurations are preferred to Schottky contacts because the I-V characteristics of the former have lower current levels. Therefore, the choice of a *pn*-based device structure will translate for the varactors into a more ideal capacitive behavior, since the equivalent parallel resistance would be higher. On the other hand, photodiodes with low ‘dark’ current, i.e. the current without irradiation, can have a greater signal-to-noise ratio and be more sensitive to weak radiation intensities. The influence on optical performance will be discussed below.

Although ultrashallow and abrupt  $p^+$  doping profiles became available, the reduction of the junction depth should be also supplemented with higher doping efficiency, otherwise the I-V characteristics would be influenced in a less favorable way. In fact, the resulting junction will not suppress the injection of minority carriers from the substrate, and the diode current will be high. Doping techniques, such as implantation or CVD epitaxial growth, are not suitable. In the former case, in fact, beside the unavoidably broadening of either the  $p^+$  profile or the background *n*-type doping distribution, the depletion region might be affected by reduced carrier lifetime due to lattice damage. This will generally increase the generation-recombination leakage current and, in particular, the loss of photogenerated carriers in devices for radiation detection. CVD depositions can provide nm-thick Si layers with abrupt doping transitions, but low-temperature processing, which are required for instance in varactor implementations, cannot provide high efficiency for boron doping due to limited solid solubility.

In this thesis, the boron CVD deposition is demonstrated to be a reliable solution for the formation of the  $p^+$ -junction needed in these devices. Outstanding performance has been achieved and the fabricated devices represent to our knowledge the state-of-the-art among academic and industrial communities both for varactor-based and UV detector technologies.

### 1.2.1 Silicon-on-glass varactors for RF applications

Future wireless systems increasingly demand circuit techniques that facilitate RF adaptivity. Some examples of adaptive circuits include tunable filters, tunable matching networks for low-noise and power amplifiers, and multiband voltage controlled oscillators. However, these applications rely on a tunable capacitive element that

should particularly ensure high linearity, wide tuning range, extremely low loss, i.e. high quality-factor (Q), and ruggedness to high voltage and high current.

Such requirements have generally disqualified the use of varactor diodes for RF tuning techniques due to the inherently non-linear behavior at the microwave frequency of interest for use with modern communication standards. In addition, conventional bulk-silicon device implementations suffered from high losses in terms of parasitic resistive and capacitive components, which strongly inhibit high frequency performance, due to the need for buried layers or finger structures for contacting the device regions.

Nevertheless, in the last years a number of record-breaking circuits with excellent linearity and high Q-factors were fabricated with varactor-based circuit topologies in the DIMES silicon-on-glass (SOG) substrate-transfer technology [15–19]. This excellent performance has been possible as a result of two design/process strategies:

- a) *Tuning range and linearity constraints are concomitantly fulfilled by proper choice of the varactor doping profile and circuit topology.*

Assuming that the *pn*-junction is one-sided and the doping distribution  $N_D$  of the substrate is  $N_D = Kx^m$ , the C-V relationship of Eq. 1.1 can be expressed as  $\propto (V_R + V_{bi})^{-s}$ , where  $V_{bi}$  is the built-in potential of the *pn*-junction and  $s = \frac{1}{m+2}$  is the varactor sensitivity, which thus strictly depends on the doping profile. The larger the  $s$ , the larger the capacitance variation will be, i.e. the tuning range, with the biasing voltage. For  $m = 0$  the profile corresponds to a uniformly doped one-sided abrupt junction. For  $m \leq -1$  the so-called hyper-abrupt junctions are formed, and they have higher sensitivity [14, 20].

A theoretical analysis has demonstrated that cancellation of distortion arising from the non-linear C-V varactor characteristics can occur for circuit topologies when the doping is such that  $s$  is  $\geq 0.5$  [21]. For instance, a theoretical ‘Distortion-Free Varactor Stack’ (DFVS) configuration can be achieved with an anti-series connection of two identical uniformly doped varactors ( $s = 0.5$ ), while a ‘High Tuning Range Varactor Stack’ (HTRVS) topology based on an anti-series/anti-parallel configuration of four hyper-abrupt varactor diodes ( $s > 0.5$ ) can facilitate linear operation with higher  $C_{max}/C_{min}$  ratio [22]. In particular, novel configurations have been recently presented, namely the ‘Narrow/Wide Tone-Spacing Varactor Stack’ (NTSVS-WTSVS) to solve even further linearity constraints with narrow and wide tone-spacing in a single technology [17, 19], while also providing an increased tuning range. These circuit topologies are based on varactors with an exponential C-V relationship. The required *n*-doping profile is composed of a lightly-doped top layer, which is fully depleted at zero bias voltage, with an abrupt transition to a  $1/x^2$ -like profile. From a technological point of view, fabrication of these hyper-abrupt  $p^+n$  junction profiles is now possible owing to the recent developments of As-doped epitaxial growth techniques [23]. Moreover, the optimized circuit topologies are also less sensitive to process deviations [15, 17].

- b) *High Q-factors translate into efficient elimination of losses from parasitic resistances and capacitances.*

While the silicon-on-insulator (SOI) technology has the merit of having enhanced significantly the RF circuit characteristics due to substrate-loss reduction, the back-wafer contacted silicon-on-glass technology developed at DIMES has ultimately pushed even further the capability to enable the fabrication of high performance low-power RF integrated circuits with on-chip integration of active devices and high quality passive components [24]. First, the high-precision lithography for patterning of the back-wafer-aligned contacts in the substrate-transfer technology improves the access to the active device areas for the electrical terminals. This unique property is particularly attractive from the device design point of view, since very compact layouts are possible and device structures approach theoretical one-dimensional behavior. The process has been further enhanced with low-ohmic and low-defect contacts, which are formed by excimer laser annealing of implanted arsenic, and low metal-track resistance by using thick copper electroplating.

Based on these two approaches, implemented varactor configurations have shown output third-order intercept point ( $OIP_3$ ) of  $\sim 60$  dBm and average Q-factor of 80–100 at 2 GHz [19]. These excellent results, however, strongly rely on the technique used for formation of the front  $p^+$  anode region. For linearity requirements, the challenges are to guarantee one-sided junctions and, at the same time, that the  $p^+$  process should not involve temperatures or defect creation that cause any significant arsenic diffusion by thermal or transient-enhanced effects. Moreover, an ultra-low-loss tunable element can be targeted if the  $pn$ -junction is not affected by excessive diode leakage current at reverse biasing. Finally, theoretical breakdown voltages should be achieved in order to effectively profit from the wider tuning range. Therefore, in this thesis the B-deposition is also considered as a solution to such specific technology demands.

### 1.2.2 Photodiodes for detection of ultraviolet (UV) radiation

Recent years have witnessed a significant growing interest for development and fabrication of highly sensitive and stable detectors for radiation in the ultraviolet (UV) spectral range ( $\lambda = 400\text{--}10$  nm), particularly at vacuum UV (VUV) wavelengths ( $\lambda = 200\text{--}10$  nm), down to soft X-rays ( $\lambda = 10\text{--}0.1$  nm). This has been mainly driven by advances in lithography equipment, since several sensors are used to evaluate and optimize the imaging performance as position sensing and beam intensity monitoring. In fact, for future high-volume nanoelectronics manufacturing, after ArF ( $\lambda = 193$  nm) and F<sub>2</sub> ( $\lambda = 157$  nm) excimer-laser lithography systems, the semiconductor industry has chosen to develop extreme-ultraviolet (EUV) lithography tools with 13.5 nm radiation wavelength, and commercialization is planned for application at the 22 nm device node by 2014 [25]. Furthermore, remote sensing instrumentation needed for next solar metrology missions have also triggered an intense research of high-performance devices for radiation detection at visible, EUV, and X-ray wavelengths [26].

For many such applications, the radiation-sensitive area is exposed to high photon

flux doses and is generally affected by either surface or bulk contamination. These harsh conditions readily deteriorate the optical performance and limit the lifetime of the device itself. Therefore, ruggedness and long-term stability to high radiant exposure and aggressive environments is one of the key features demanded for detector applications in the VUV spectral range, along side extreme requirements for excellent reliability, high and spatially uniform sensitivity, wide dynamic range, high linearity, and low noise, i.e. low dark current.

Solutions for UV radiation detection are generally offered by silicon-based devices, which are inherently responsive to a broadband radiation extending from the near infrared region wavelengths ( $\leq 1 \mu\text{m}$ ) down to soft X-rays ( $\lambda \sim 1 \text{ nm}$ ). Moreover, they have attractive characteristics in terms of accuracy and prediction of optical efficiency [27]. Although III-N wide-bandgap semiconductors, like gallium nitride (GaN), aluminum nitride (AlN), aluminum-gallium nitride (AlGaN), have been recently considered as promising candidates mainly due to their radiation hardness [28–30], they still face lower sensitivity and many processing issues compared to more mature and cost-effective Si technologies. Even their intrinsic solar-blindness, i.e. a good UV/visible response ratio, can be feasibly achieved for silicon devices. In fact, it has been demonstrated that integration of a thin film of a suitable filtering material directly on the exposed surface is fully compatible and makes possible selective response to a much narrower band [31].

Regarding the device structure, documented methods of producing reliable UV detectors involve mainly planar diffused silicon *pn*-junctions, either  $p^+n$  [32] or  $n^+p$  [33], and Schottky diodes [34]. Instead, natural-inversion-layer photodiodes result in low yield due to poor process control of the indirect method of forming the surface depletion and conductive top-layer. As stated above, diffusion-type photodiodes have lower dark current. In addition, they are much more sensitive than Schottky-type photodiodes either on Si or III-N compounds, especially at deep-ultraviolet (DUV) wavelengths (120–200 nm). The limited radiation sensitivity for Schottky diodes might be due to a combination of several factors, mainly dependent on the specific photodiode technology, such as high reflection and absorption losses in the front metal contact, lower surface electric field, and higher surface recombination. On the other hand, the presence of a metallic front-layer has been demonstrated to provide more stable performance under heavy radiation exposure [35]. Similar ruggedness has been reported for metal-silicide windows on  $n^+p$  junction diodes [36, 37].

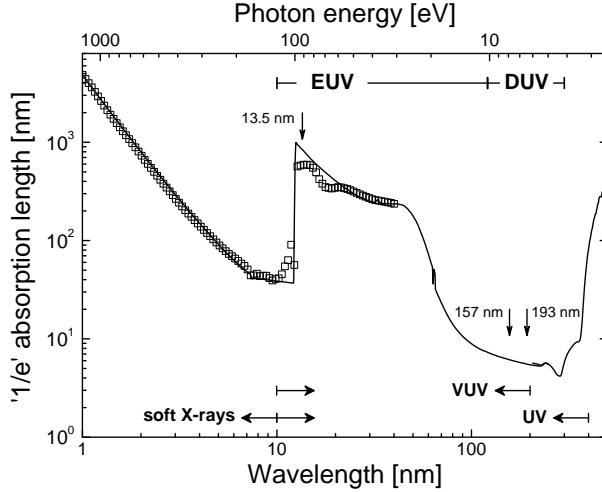

Moreover, for planar diffused diodes, the spectral sensitivity to UV radiation is also dependent on the Si absorption coefficient, since the ‘ $1/e$ ’ penetration depth of UV photons into silicon approaches values lower than 10 nm in the wavelength range of 100–350 nm, as shown in Fig. 1.3. In particular, a minimum of  $\sim 5 \text{ nm}$  is reached at the DUV wavelengths of applicative interest, such as  $\lambda = 157 \text{ nm}$  and  $\lambda = 193 \text{ nm}$ . Therefore, to optimize the optical conversion efficiency the uppermost edge of the depletion region should be within this distance. However, commercial *np*-junction diodes more simply rely on both the built-in electric field induced by the gradient of the  $n^+$  diffused doping profile and the formation of junctions shallower than the diffusion length of the minority carriers. The latter requirement is quite straightforward to realize, since the diffusion length of holes is about  $0.4 \mu\text{m}$  or higher for

**Figure 1.3:** ‘1/e’ absorption length in Si as a function of the radiation wavelength in the UV/soft X-rays spectral range: — after Ref. [38], □ after Ref. [39].

the reported  $n^+$  doping levels of about  $10^{18}$ – $10^{19}$  cm $^{-3}$ . Most of the built-in electric field is also induced by steep dopant pile-ups that are intentionally formed during thermal growth of SiO<sub>2</sub> coating layers. In fact,  $n$ -type species, such as arsenic and phosphorus, segregate at the Si/SiO<sub>2</sub> interface [33]. In contrast, for boron profiles an opposite segregation mechanism does not allow to tailor the electric field in this manner, and thus the carrier collection efficiency is poorer than the  $n^+p$  implementation. Furthermore, the presence of positive charges in the anti-reflection oxide coating can induce further carrier losses in the  $p^+$  front region, since the resulting electric field will hinder the carrier collection. For these reasons,  $n^+p$  photodiodes have been generally preferred over  $p^+n$  junctions and claimed to be inherently more stable than boron-diffused devices in UV spectral range [40]. However, one could easily argue that the  $n^+$  surface peak would be too strictly dependent on the presence of the SiO<sub>2</sub> front-layer, which can be either a cause of radiation absorption at short wavelengths or radiation-induced degradation.

On the other hand, the ability to form extremely ultrashallow and highly-doped junctions can maximize the optical performance up to the theoretical limits even for  $p^+n$  photodiodes, as in the case of B-deposition. In fact, the reduced junction depth would significantly increase the percentage of carriers generated in the depletion region. At the same time, the electric field induced by the high-concentration doping profile would efficiently separate any further electron-hole pairs created in the shallow diffused area, since it will not be confined within the space-charge region, but it would extend until the surface [14]. The high doping concentration can have the additional advantage of being able to screen any influence of oxide charges when anti-reflection coating layers are needed. Moreover, the enhancement of carrier collection by such doping-induced electric fields strongly prevents any recombination of photogenerated

carriers at the Si surface or Si/SiO<sub>2</sub> interface, since minority carriers will be in the presence of recombination traps for a negligible time.

### 1.3 Outline of the thesis

The thesis is organized as follows. The following Chapter illustrates the experimental procedures for the formation of CVD boron layers on Si surfaces. Transmission electron microscopy (TEM) and secondary ion mass spectrometry (SIMS) are used to study the morphology and the boron content in the deposited layers, respectively. The analytical characterization is then coupled to electrical measurements of test structures incorporating the layers in order to study the boron surface doping and junction depth. In Chapter 3, the previous results are assessed with respect to reliable implementation of B-deposition in Si devices. The electrical properties of the B-layers are extensively investigated as a function of the processing conditions by fabricating contacts, diodes, and *pnp* bipolar structures. The thermal stability and doping efficiency of B-layers during the subsequent drive-in process are examined in Chapter 4. Both *in-situ* and *ex-situ* thermal anneals are considered. Chapter 5 reports on the B-deposition applied to the silicon-on-glass varactor technology. Particular accent is set on the reverse-biased I-V characteristics of as-deposited B-diodes. Processing and design solutions are also discussed which aim to increase the maximum operating voltage up to theoretical breakdown limits. Fabrication of planar *p<sup>+</sup>n* photodiodes for UV radiation detection is illustrated in Chapter 6, where B<sub>2</sub>H<sub>6</sub> exposure conditions are properly tuned to optimize the optical conversion efficiency. In addition, the technology is demonstrated to be tailored for further improvement of photodiodes parameters, such as series resistance, by also combining the pure B-deposition with optional extra-processing steps. The electrical and optical performance of the fabricated photodiodes are shown, also with respect to their stability after high dose irradiation. Finally, Chapter 7 gives the main conclusions and provides recommendations for the future work.

## Chapter 2

# Chemical vapor deposition of boron layers

The experimental conditions for the deposition of boron layers on Si surfaces are described here. Analytical characterization techniques have been applied to investigate the film morphology and the boron content as function of processing parameters. The Chapter also reports on the study of the surface boron doping to determine the diffused active boron doses and the resulting  $p^+$ -junction depths by means of electrical test structures. The experimental results have been also validated by process and device simulations, which have been carried out with the Taurus TSUPREM-4<sup>TM</sup> and MEDICI<sup>TM</sup> softwares, respectively, [41, 42].

### 2.1 Processing conditions

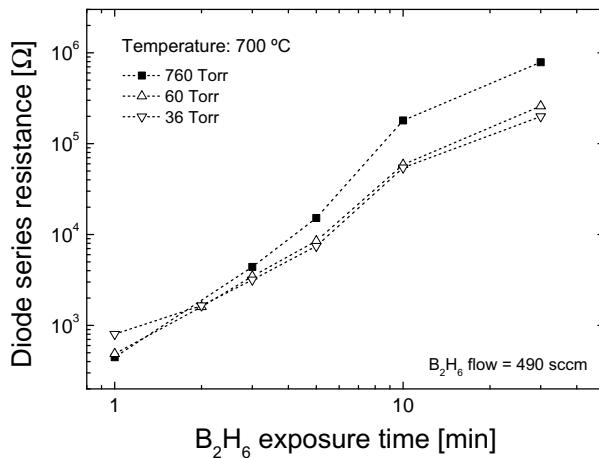

The B-layer formation is performed in an ASM Epsilon One reactor by chemical vapor deposition (CVD) at either atmospheric pressure (AP), i.e. 760 Torr, or reduced pressures (RP), such as 60 Torr or 36 Torr. The depositions themselves have been monitored for processing temperatures ranging from 500 °C to 800 °C. Diborane (B<sub>2</sub>H<sub>6</sub>) is injected into the reactor chamber as the dopant gas with a typical flow rate of 490 sccm, while hydrogen (H<sub>2</sub>) is used as the carrier gas and for dilution of the doping source. Rotation of the sample can provide homogeneous exposure preventing gas depletion phenomena. Nevertheless, the influence of the doping gas flow on the deposition process has been also investigated for various diborane partial pressures (10<sup>-8</sup>–10<sup>-3</sup> Torr). For a given temperature, ambient pressure and diborane concentration, the boron coverage of the Si surface and the doping of the crystalline silicon substrate can be controlled by varying the deposition time. The results presented here correspond to exposures in the range of 1 s to 30 min.

It is known that the boron atoms will not be adsorbed as a distinct layer on SiO<sub>2</sub> [2, 9, 10], so it is crucial to provide an oxide-free Si surface for the deposition. This is achieved by first treating the substrates by conventional wet cleaning and HF dipping.

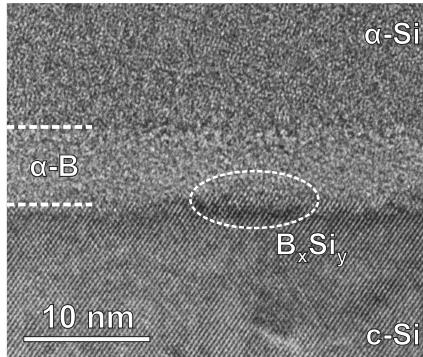

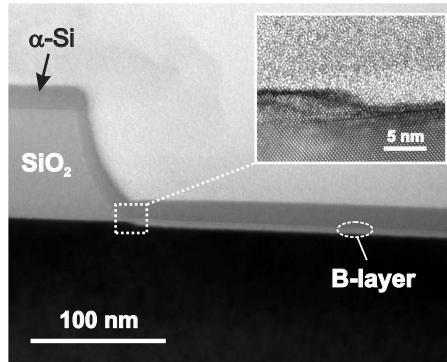

**Figure 2.1:** High-resolution TEM image of a B-layer formed after 10 min  $\text{B}_2\text{H}_6$  exposure at 700 °C. The sample has been covered with PVD  $\alpha$ -Si as contrasting layer.

In the reactor itself, any remaining native  $\text{SiO}_2$  is removed before  $\text{B}_2\text{H}_6$  exposure by an *in-situ* thermal cleaning step in  $\text{H}_2$  ambient at 900 °C for 30 min. In the case of a patterned  $\text{SiO}_2$  layer being used as hard-mask for selective B-deposition, the pre-bake step should be carried out at atmospheric pressure to avoid high-temperature silicon-dioxide decomposition [43, 44]. However, lower temperatures, such as 700 °C, have also been demonstrated to be appropriate for *in-situ* surface cleaning.

Finally, in our experiments only (100) Si wafers have been exposed to the gas mixture, due to their wide use in device fabrication. However, while the deposition rate of pure boron layers is independent of the crystallographic orientation [9], Saitoh's work demonstrated (100) silicon surfaces to induce faster growth for boron-silicide films as compared to (111) substrates.

## 2.2 Transmission electron microscopy analysis

### 2.2.1 B-layer morphology and growth rate

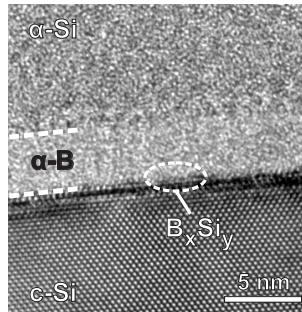

A high-resolution TEM image of a B-layer formed after 10 min  $\text{B}_2\text{H}_6$  exposure at 700 °C in a 760 Torr ambient is shown in Fig. 2.1. During the thermal decomposition of diborane, the high gas-source injection (490 sccm) causes boron atoms to readily segregate on the bare silicon surface in amorphous phase, thus forming an  $\alpha$ -B layer. In addition, at such temperature the very high and uniform B content at the Si interface induces boron atoms to initiate a reaction with the silicon in a boron-silicon phase [9]. Thus a boron silicide  $\text{B}_x\text{Si}_y$  layer is also formed, which is here seen as a roughening of the c-Si surface.

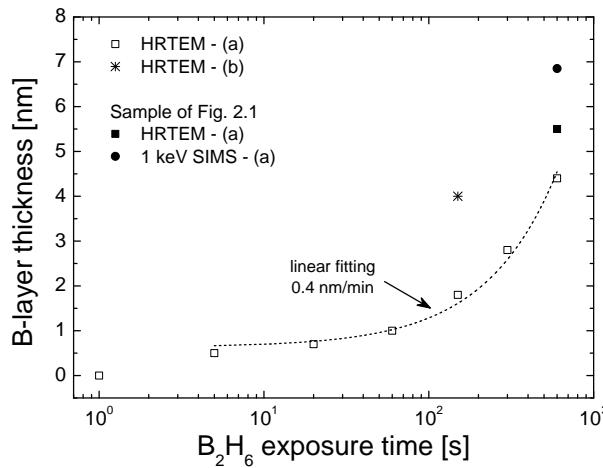

The film is uniform, and the corresponding average thickness determined from HRTEM images is shown in Fig. 2.2 as a function of the  $\text{B}_2\text{H}_6$  exposure time at 700 °C. Apart from the 5 s exposure point, the time dependence of the B-layer thickness for the CVD on blanket Si surfaces is quite linear with a calculated growth rate of 0.4 nm/min. At the early stage of the deposition, such as at 5 s, HRTEM

**Figure 2.2:** The average B-layer thickness as a function of  $B_2H_6$  exposure time at 700 °C determined from HRTEM images. For the 10 min as-deposited sample shown in Fig. 2.1, the physical thickness is also compared to the full-width-at-half-maximum (FWHM) of the corresponding SIMS (1-keV- $O_2^+$ ) boron profile. The analytical characterization was performed on samples where B-layers were deposited either (a) on blanket (100) Si surfaces or (b) in contact windows.

images revealed adsorbed boron to either approximately form an atomic plane on silicon or interact non-homogeneously with the first atomic Si plane, the distance between {100} Si planes being equal to the lattice constant of 5.4 Å. Finally, the deviation between the 10 min B-doped samples is probably due to the temperature calibration of the reactor chamber, which has been performed in different time frames.

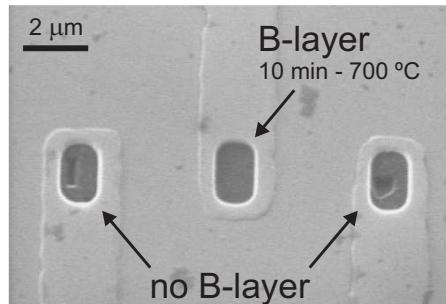

### 2.2.2 Topography dependence: selectivity, uniformity, and isotropy

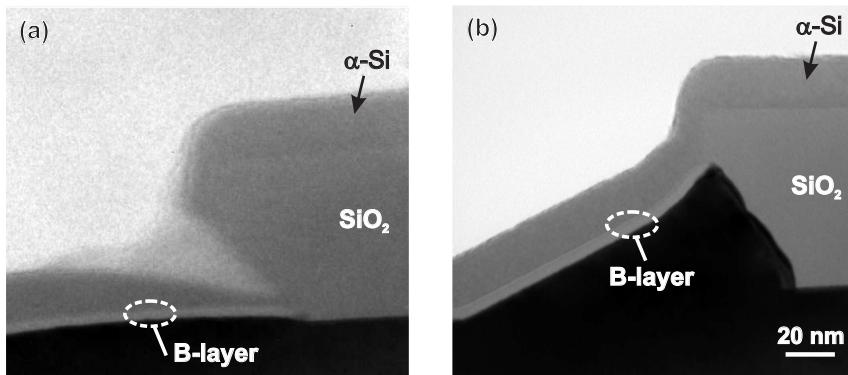

TEM imaging has been used to investigate the growth of B-layers performed directly into contact windows of various sizes ranging from  $1 \times 1 \mu\text{m}^2$  to  $450 \times 450 \mu\text{m}^2$ . The windows have been wet-etched into a 100 nm thermal silicon oxide. The pattern dependence has been studied for samples with 4 min *in-situ* pre-bake step at 700 °C followed by a 2.5 min  $B_2H_6$  exposure at the same temperature.

The TEM image of Fig. 2.3 shows that the pure diborane exposure provides selective deposition on Si: no boron can be observed on the flat or beveled  $\text{SiO}_2$  surfaces. In the window, the boron layer is seen to be continuous and uniform across the Si with an average thickness of 4 nm independent of the window sizes investigated. The film is, however, thicker than the layers deposited on the bare Si surface, as shown in Fig. 2.2. An inspection of the window periphery reveals a  $\sim 3$  nm recession of the Si with respect to the Si/ $\text{SiO}_2$  interface, which, at least in part, is due to the cleaning steps performed before and after loading the sample into the reactor. Some

**Figure 2.3:** TEM image of a B-layer directly formed in a contact window during a 2.5 min  $\text{B}_2\text{H}_6$  exposure at  $700^\circ\text{C}$ . The inset shows an enlarged view of the edge periphery that reveals a  $\sim 3$  nm recession of the Si with respect to the  $\text{Si}/\text{SiO}_2$  interface.

Si consumption may also be due to the reaction with B atoms during formation of the boron-silicide layer [9].

Figs. 2.3 and 2.4 can be used to compare three different types of contact window perimeters after 2.5 min B-deposition. The non-conventional topographies of the window edges seen in Fig. 2.4 have been formed after *in-situ* thermal cleaning at low pressure and at a temperature of  $900^\circ\text{C}$ . Under these conditions, the oxide sidewalls are steadily undercut as a result of  $\text{SiO}_2$  decomposition at the perimeter of the contact opening. This is due to the reaction  $\text{Si} + \text{SiO}_2 \longrightarrow 2\text{SiO}$ , where the SiO is a volatile product [43, 44]. In addition to this, on a clean Si surface, as obtained here by *in-situ* H-baking, the Si atoms will be mobile and can accumulate at the perimeter of patterned areas. In all cases, the CVD process ensures excellent boron coverage of the silicon surface up to the oxide edge, whether a cavity, e.g. Fig. 2.4(a), or a Si mount, e.g. Fig. 2.4(b), was formed. The latter case evidences that the growth mechanism is isotropic, since the B-layer thickness appears to be independent of the c-Si surface orientation, as expected for temperatures  $\leq 700^\circ\text{C}$  [9].

### 2.2.3 Low-temperature deposition

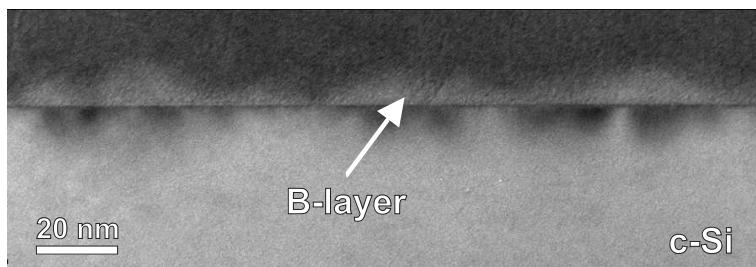

The growth rate of the B-layers, as well as the resulting layer-stack composition, is dependent on the deposition temperature [9]. At temperatures below  $600^\circ\text{C}$ , the decomposition of diborane, although not completely dissociative, has been found to result in the formation of pure boron layers, while at  $700^\circ\text{C}$  some reactivity with the silicon atoms is initiated, and the consequent silicidation of the B-layer increases with temperature.

In Fig. 2.5, a TEM image is shown for a substrate treated with 10 min  $\text{B}_2\text{H}_6$  exposure at  $500^\circ\text{C}$ . A B-layer was formed with an average thickness of  $\sim 6$  nm, although the uniformity along the Si surface is poor in comparison to deposition at  $700^\circ\text{C}$ . In fact, at low temperatures, boron forms preferably B-rich grains separated by regions

**Figure 2.4:** TEM images of contact windows after 2.5 min B-deposition at 700 °C. The SiO<sub>2</sub> etch geometry was generated by low pressure *in-situ* thermal cleaning at 900 °C before diborane exposure.

of clean silicon, while larger and rough islands are formed by coalescence of several grains after longer exposures [10, 45]. On the other hand, depositions performed at higher temperatures, even for shorter times, exhibited better spatial homogeneity. Therefore, it is probable that high temperatures enhance the migration of species along the Si surface, besides promoting the reactivity of boron with Si atoms.

Furthermore, the bending contours of the TEM diffraction contrast image reveal the presence of local stress between the B-layer and the c-Si substrate. The stress might be induced by an altered lattice parameter at the Si surface due to the deposited B atoms. Variation in lattice plane distances could not really be discerned, although a tendency towards a lower {110} lattice plane distance, i.e. horizontal compression, was observed. As reported in [3], such structural effect would be in agreement with the fact that boron substitution at the (100) Si surface will distort the Si lattice to achieve a Si—B bond length of 2.0–2.1 Å, substantially shorter than the 2.35 Å bond length in bulk silicon.

**Figure 2.5:** TEM image of a B-layer formed after a 10 min B<sub>2</sub>H<sub>6</sub> exposure at 500 °C. The analysis has been performed with the electron beam direction a few degrees away from [110] so that the 220 reflection is in the Bragg's condition.

## 2.3 Secondary ion mass spectrometry analysis

### 2.3.1 Boron content in as-deposited layers

The number of boron atoms in as-deposited layers has been monitored by using secondary ion mass spectrometry (SIMS) with  $O_2^+$  primary ion beam either at 2 keV or 1 keV. On the other hand, oxygen levels were monitored by using  $Cs^+$  primary ions at 3 keV. In order to get an accurate SIMS signal from the surface, a layer of 100 nm amorphous silicon ( $\alpha$ -Si) has been sputtered on the samples at room temperature after the boron deposition.

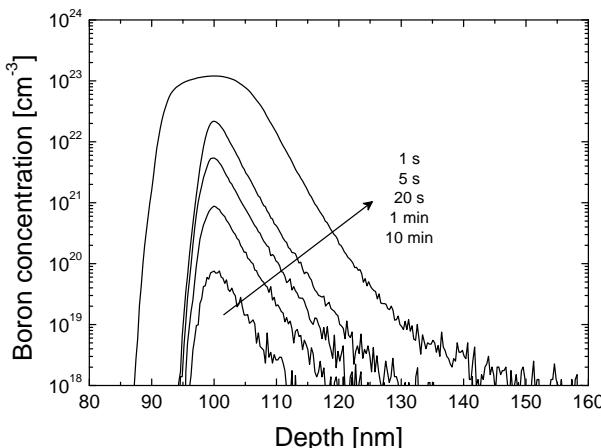

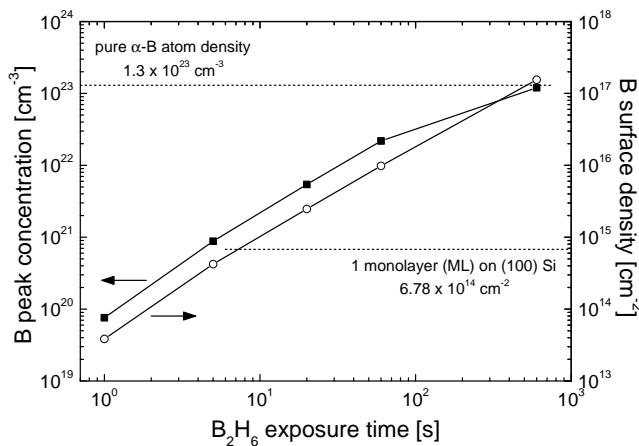

In Fig. 2.6 SIMS profiles are shown of B-layers formed at 700 °C for various deposition times. The  $B_2H_6$  exposure was performed at atmospheric pressure with a flow rate of 490 sccm. Both the B peak concentrations and the integrated surface densities have been extracted, and the corresponding values are presented in Fig. 2.7 as a function of the deposition time.

The SIMS analysis of these ultrashallow and highly-doped layers will be influenced by the knock-on effect, which gives errors in determining the absolute value of boron concentration and limits the depth resolution. Nevertheless, the B-content increase seen in these measurements is similar for both surface density and peak concentration, and the time dependence has a grading coefficient of 1.2. The concentration peak of the SIMS profiles seems to saturate at the equivalent atom density of amorphous B for very long exposures, the latter being determined by the atomic weight (10.81 g/mole) and density (2.34 g/cm<sup>3</sup>) of boron [46]. On the other hand, the time dependence of the surface density has shown that the saturation coverage occurs within the first 20 s followed by a transition to the non-self-limiting segregation of boron. As is also visible from TEM images and indicated in Fig. 2.2, after 5 s the boron coverage starts

**Figure 2.6:** SIMS profiles (2-keV- $O_2^+$ ) of B-layers formed for 1 s to 10 min deposition at 700 °C. For comparison, the point of boron peak concentration has been moved to 100 nm in all cases.

**Figure 2.7:**  $\text{B}_2\text{H}_6$  exposure time dependence at  $700\text{ }^\circ\text{C}$  of boron peak concentration (left y-axis) and surface density (right y-axis) as determined from SIMS profiles shown in Fig. 2.6.

to exceed the surface atomic density of one monolayer (ML), which corresponds to  $6.78 \times 10^{14} \text{ cm}^{-2}$  on (100) Si. High-resolution SIMS profiling was performed on the sample with a 10 min B-deposition and the full-width-at-half-maximum (FWHM) value, also included in Fig. 2.2, is in good agreement with the other data.

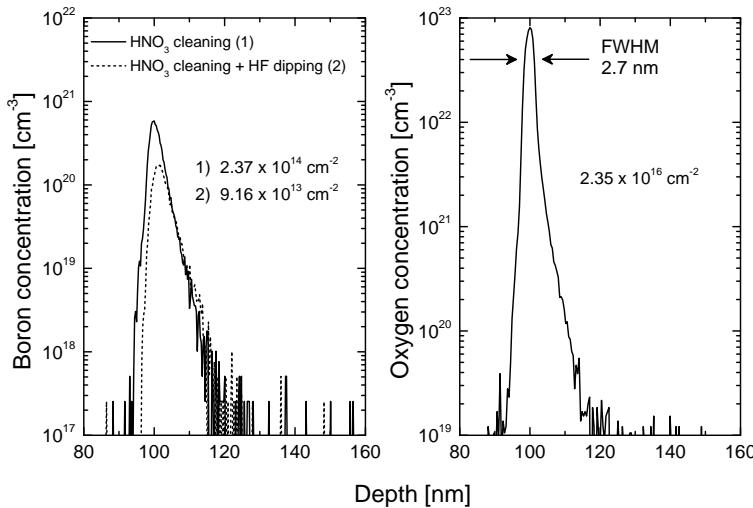

### 2.3.2 B-layer removal

The chemical reactivity of boron with  $\text{HNO}_3$ -based acid solutions [9, 46] can facilitate the removal of the  $\alpha$ -B layer in a standard cleaning process. After a 10 min B-deposition at  $700\text{ }^\circ\text{C}$ , a substrate has been soaked for 10 minutes in a boiling concentrated nitric acid solution (65%) at  $110\text{ }^\circ\text{C}$ . The resulting boron and oxygen profiles are shown in Fig. 2.8. The cleaning step completely dissolves the high-boron peak region ( $> 10^{23} \text{ cm}^{-3}$ ), which supports the assumption that it is a metal-like boron layer. The oxygen delta-profile, which has a FWHM of only  $\sim 3$  nm, is most likely due to cleaning-induced oxidation of about 1.3 nm of silicon, assuming that the Si thickness is 0.455 times the oxide thickness. A 4 min dipetch in an HF solution (0.55%) removes the oxide.

After the  $\text{HNO}_3$  treatment, the boron SIMS profile reveals a concentration peak of  $6 \times 10^{20} \text{ cm}^{-3}$  that is slightly reduced upon HF dipping, showing that some boron atoms are also incorporated in the cleaning-induced oxide. A similar high boron concentration ( $8 \times 10^{20} \text{ cm}^{-3}$ ) was also obtained by using a 750-eV-SIMS analysis, as shown in the following section. Since these levels considerably exceed the B solid solubility of  $1.7 \times 10^{19} \text{ cm}^{-3}$  at  $700\text{ }^\circ\text{C}$  in bulk Si [47], the surface peak is attributed to the high boron content in the  $\text{B}_x\text{Si}_y$  layer, which is only partly oxidized and removed during the  $\text{HNO}_3 + \text{HF}$  cleaning sequence [13].

**Figure 2.8:** Boron and oxygen SIMS profiles of an as-deposited 10 min B-doped layer formed at 700 °C after standard cleaning in boiling  $\text{HNO}_3$ . The boron profile resulting from the removal of the cleaning-induced oxide with an HF dip is also shown.

### 2.3.3 Boron diffusion during the deposition

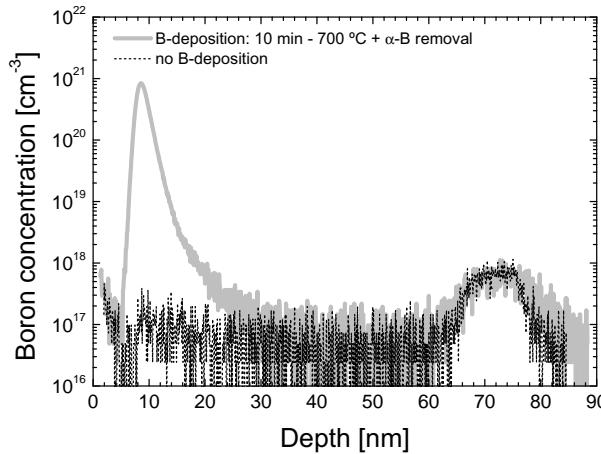

Along with the surface reactions that induce formation of a B-layer, diffusion of boron atoms into the Si substrate is also accomplished during the  $\text{B}_2\text{H}_6$  exposure [8,13]. However, the doping of the c-Si is too light to be distinguished in the HRTEM or in the corresponding B-profile determined by SIMS. For the application in devices it is important to know if this doping and the background doping are affected by any deposition-associated defect formation that causes transient-enhanced (TED) or boron-enhanced diffusion (BED). In particular, the latter effect has been observed during annealing at 950 °C either for B-implanted samples when the dopant dose exceeds  $1 \times 10^{15} \text{ cm}^{-2}$  or for an evaporated B-layer containing  $3.2 \times 10^{16} \text{ cm}^{-2}$  boron atoms on the Si surface [48]. The influence is, however, more pronounced in the former case. In both situations, the formation of a silicon-boride phase due to the high B content is assumed to be a source of excess interstitials.

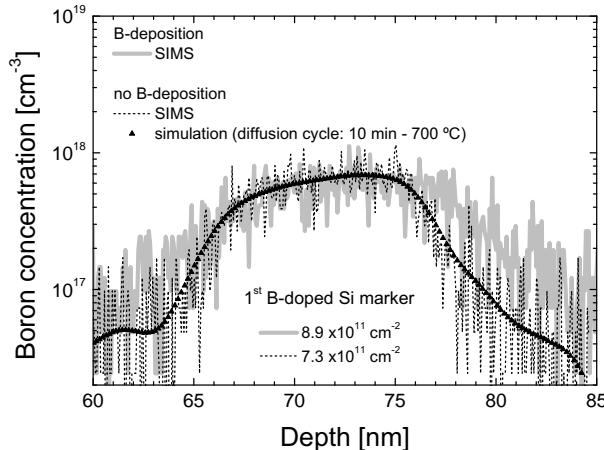

Enhanced diffusion effects have been evaluated, here, by examining the out-diffusion of epitaxially grown B-doped Si markers after a 10 min B-deposition at 700 °C. This layer contains  $1.55 \times 10^{17} \text{ cm}^{-2}$  boron atoms, which is much higher than in the above mentioned evaporated layer, but the process/anneal temperature is much lower, i.e. 700 °C, instead of 950 °C. Two samples were fabricated with 20-nm-wide B-markers located approximately at a depth of 70 nm, 350 nm, and 700 nm. The resulting B-layer has been removed to minimize the SIMS knock-on effect, and then a capping layer of 10 nm amorphous silicon has been deposited at room temperature on both samples. A SIMS with primary  $\text{O}_2^+$  beam energy of either 2 keV or 750 eV was used to study the diffusion in respectively all the markers or, with improved

**Figure 2.9:** SIMS profiles ( $\text{O}_2^+$  primary ion beam at 750 eV) of samples with and without a 10 min B-deposition at 700 °C on a Si wafer containing epitaxially-grown B-doped Si markers. The  $\alpha$ -B layer was removed with  $\text{HNO}_3$  cleaning and HF dip etching before covering the sample with 10 nm PVD  $\alpha$ -Si.

resolution, the region within 100 nm of the surface. The boron profiles obtained from the latter analysis condition are shown in Figs. 2.9–2.10.

Firstly, although the doping profile might still be influenced by the SIMS energy and the high B concentration peak at the surface, the junction depth for an *n*-type background doping level of  $10^{17} \text{ cm}^{-3}$  is expected to be within 20 nm of the sur-

**Figure 2.10:** Enlarged view of the SIMS profiles shown in Fig. 2.9 for the first B-marker. The result of a simulation of a 10 min thermal anneal at 700 °C of the original B-marker is also included.

face. Thus the drive-in of boron atoms during the CVD process itself is very limited. However, more accurate profiling has been achieved with capacitance-voltage measurement technique, as described in Section 2.4.3 on page 27.

Secondly, within the resolution of the high-energy SIMS, no broadening of the B-markers could be discerned. However, the B-profiles obtained with a 750-eV-analysis did show very slight deviations at the first marker of the different samples, as can be seen in Fig. 2.10. To evaluate the possible effect of the 10 min thermal processing cycle at 700 °C in itself, a diffusion simulation was performed on the as-grown B-doped Si marker. This did not reveal any diffusion effects. This result along with the spread in the calculated B-doses is a clear indication that the differences should be accorded to variations in the original B-doped epitaxial growth rather than enhanced-diffusion effects. Thus, the high B-concentration and gradient at the surface is only instrumental in doping of the c-Si up to the solid solubility by thermal diffusion.

**Figure 2.11:** Schematic cross-sections of the fabricated test structures used to determine: (a) sheet-resistance, (b) as-diffused boron doping density, and (c) junction depth.

## 2.4 Electrical characterization of surface boron doping

This section illustrates the electrical measurements of sheet-resistances and depletion-type MOS-capacitors that have been used to determine the active boron concentration in the silicon substrate. In addition, the corresponding junction depth has been extracted from capacitance-voltage profiling.

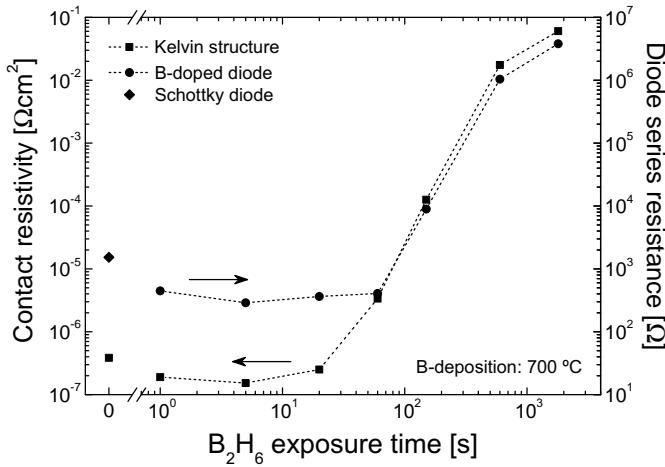

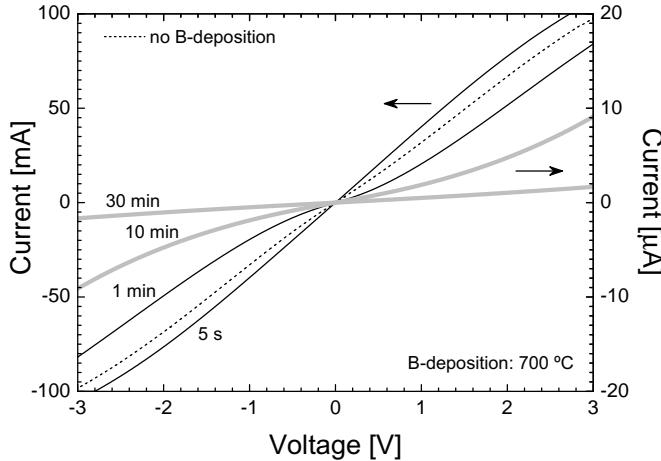

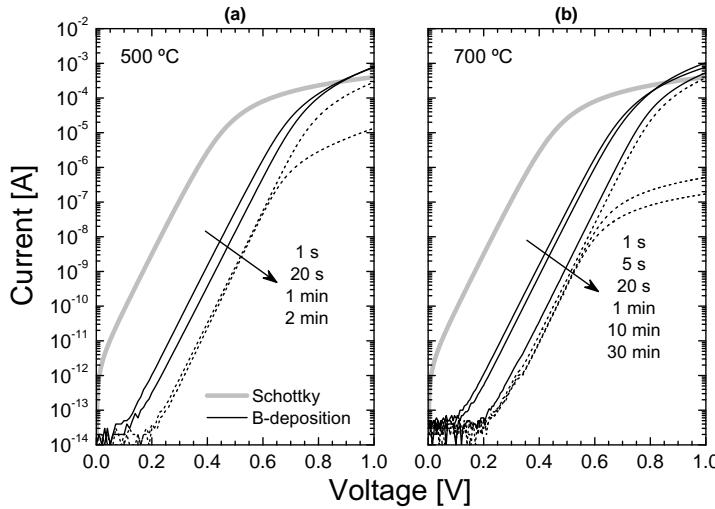

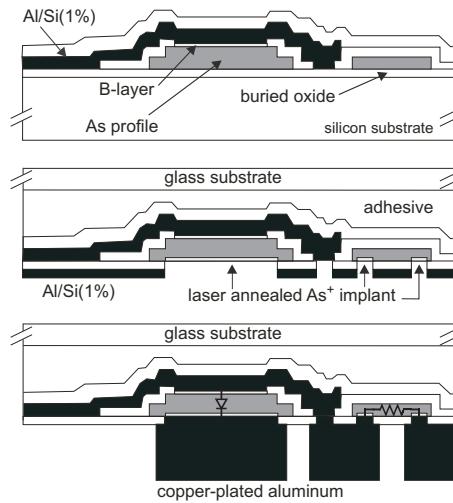

Schematic cross-sections of fabricated test structures are shown in Fig. 2.11. The devices were fabricated on  $n$ -type 2–5  $\Omega\text{cm}$  substrates. For the sheet-resistance and MOS capacitance-voltage measurements, the B-layer was prepared uniformly over the wafer and covered with 300 nm PECVD TEOS oxide. The B-layer itself was contacted via contact windows to pre-fabricated implanted  $p^+$  plugs, and PVD Al/Si(1%) metallization of both the front and backside of the wafer provided electrodes to the  $n$ -wafer as well as the  $p$ -type regions and gates on the front side. For the C-V profiling technique, an epitaxial  $n^-$ - $p^-$ - $n^+$  layer stack was grown on  $n$ -type substrates. Shallow trenches were made to isolate the devices. Then LPCVD TEOS oxide was deposited in which contact windows were etched for B-deposition and subsequently metalized. Schottky diodes were also formed on the same sample by contact opening to the neighboring structure and Al/Si(1%) deposition. For all devices, the boron layer was formed at atmospheric pressure with a  $\text{B}_2\text{H}_6$  flow rate of 490 sccm.

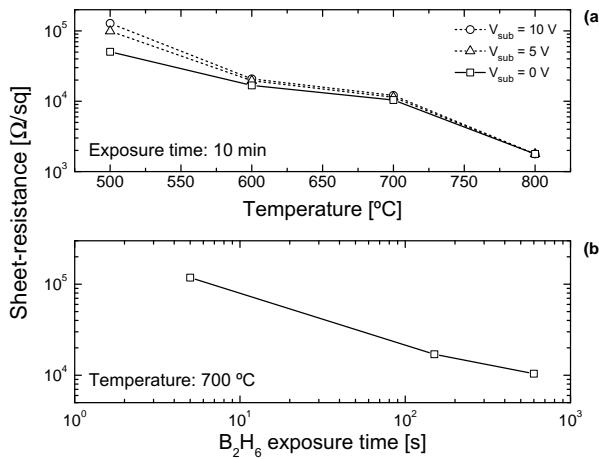

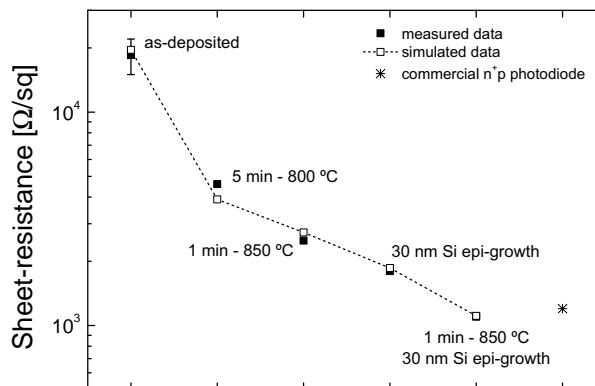

### 2.4.1 Sheet-resistance measurements

The sheet-resistance of as-deposited B-layers has been determined by using differential electrical measurements on ring-shaped structures similar to those described in [49]. In Fig. 2.12(a) the extracted sheet-resistance  $\rho_s$  is shown for samples with 10 min deposition at temperatures ranging from 500 °C to 800 °C. In addition, the time dependence of  $\rho_s$  is reported in Fig. 2.12(b) for  $\text{B}_2\text{H}_6$  exposures performed at 700 °C. The reduction of the sheet-resistance with either the deposition temperature or time is reasonably consistent with the expected diffusion rate of boron into the silicon, where the B concentration peak is limited by the solid solubility. Therefore, higher dopant activation is obtained with increasing temperatures and this in turn reduces the influence of the substrate bias voltage on  $\rho_s$ , as also seen in Fig. 2.12(a).

Above 700 °C a boron-silicide film is formed [9,10], but of relatively thin layers of a few nm. Thus, the lateral conductivity should still be dominated by impurity diffusion, if the reported resistivity values for B-Si phases of 0.2–20  $\Omega\text{cm}$  apply [50]. On the other hand, based on experimental results reported by [51], formation of  $\text{B}_{12}$  icosahedron could influence the electrical properties of the B-layer, and the corresponding sheet-resistance would be comparable to that of the boron-doped c-Si region. Such boron phase was demonstrated to be induced by heavy doping implantations ( $\geq 3 \times 10^{16} \text{ cm}^{-2}$ ) into silicon substrates, and concomitantly a high hole concentration (about  $10^{21} \text{ cm}^{-3}$ ) was generated without any post-annealing. Thus,  $\text{B}_{12}$  was proposed to be responsible for the measured low resistivity (2  $\text{m}\Omega\text{cm}$ ) by acting as a double acceptor.

Sheet-resistance measurements of B-exposed areas have been also performed after  $\text{HNO}_3$  cleaning and HF dipping until a hydrophobic surface was achieved. This

**Figure 2.12:** Sheet-resistance of B-layers as a function of (a) deposition temperature, and (b) B<sub>2</sub>H<sub>6</sub> exposure time.

removal of the B-layer significantly increases the sheet-resistance. In particular, for exposure times shorter than 5 min, the *p*<sup>+</sup> boron-doped region is either largely removed or depleted by charges in the field isolation oxide. The latter observation is confirmed by capacitance-voltage measurements described in the following section. A summary of sheet-resistance for B-layers formed at 700 °C without and with the HNO<sub>3</sub> + HF cleaning process is given in Table 2.1.

#### 2.4.2 Depletion-type MOS-capacitors

A quantitative analysis of the active boron dose diffused in the c-Si substrate during the deposition process is enabled by capacitance-voltage measurements of depletion-type *p*-channel MOS devices, since variation of the doping underneath the gate oxide can readily affect the C-V characteristics in terms of either threshold or

**Table 2.1:** Sheet-resistance of B-layers deposited at 700 °C before and after the HNO<sub>3</sub> cleaning + HF dipping sequence.

| Sample description                          |             | Sheet-resistance      |  |

|---------------------------------------------|-------------|-----------------------|--|

| B <sub>2</sub> H <sub>6</sub> exposure time | α-B removal | [Ω/sq]                |  |

| 2.5 min                                     | no          | 1.8 × 10 <sup>4</sup> |  |

| 10 min                                      | no          | 1.0 × 10 <sup>4</sup> |  |

| ≤ 5 min                                     | yes         | -                     |  |

| 10 min                                      | yes         | 2.5 × 10 <sup>5</sup> |  |

| 30 min                                      | yes         | 5.9 × 10 <sup>4</sup> |  |

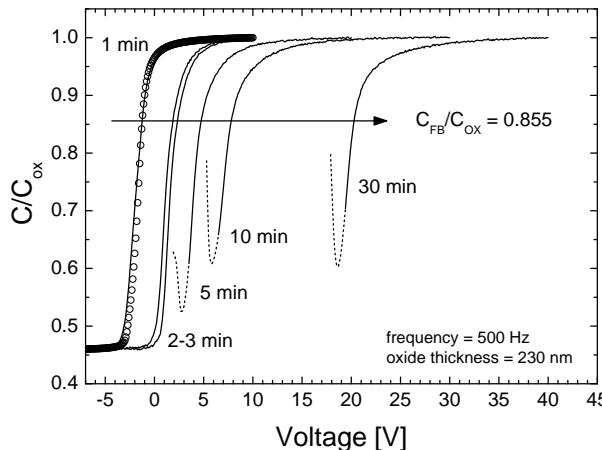

**Figure 2.13:** Normalized C-V characteristics of depletion-type *p*-MOS structures fabricated for various min-long  $\text{B}_2\text{H}_6$  exposures at  $700^\circ\text{C}$  followed by an  $\text{HNO}_3 + \text{HF}$  cleaning sequence. The shift of the flatband voltage due to boron doping of the c-Si substrate is also indicated. The 1 min B-doped sample has been assumed as reference. The simulated  $C/C_{\text{OX}}$  curve (open-circles) is of an equivalent enhancement-type MOS structure with  $D_B = 0$  and  $D_{\text{OX}} = 9.25 \times 10^{10} \text{ cm}^{-2}$ .

flatband voltages [14].

However, since the presence of the B-layer has been found to screen any influence of the metal/ $\text{SiO}_2/\text{Si}$  system up to  $\pm 100$  V, the  $\alpha$ -B layer was removed before performing gate oxide deposition. For the latter, the actual thickness was 230 nm. Normalized C-V characteristics are shown in Fig. 2.13 at a measurement frequency of 500 Hz. Similar results have also been achieved at higher frequencies, such as 1 MHz, and during quasi-static measurements. Nevertheless, in all cases a shift of the C-V curve is constantly observed for increasing deposition times.

This result indicates the presence of higher boron content at the surface of the *n*-type c-Si substrate. Therefore, the boron doping density  $D_B$  [ $\text{cm}^{-2}$ ] can be derived from the flatband voltage  $V_{FB}$  shift according to the following expression:

$$\Delta V_{FB} = V_{FB}(D_B) - V_{FB}(D_B = 0) = \frac{qD_B}{C_{\text{OX}}} \quad (2.1)$$

where  $C_{\text{OX}}$  is the oxide capacitance per unit area. However, the presence of a positive oxide charge density  $D_{\text{OX}}$  can shift the  $V_{FB}$  in the opposite direction. This effect is particularly visible in the C-V curve of a 1 min B-doped sample where the flatband voltage has been found to be  $-1.2$  V. In fact, by neglecting the influence on  $V_{FB}$  of the boron doping, the measured curve could be interpreted as an enhancement-type *p*-MOS structure ( $D_B = 0$ ) with  $D_{\text{OX}} = 9.25 \times 10^{10} \text{ cm}^{-2}$ , as shown in Fig. 2.13. Therefore, this device has been used as flatband voltage reference, i.e.  $V_{FB}(D_B = 0)$ . Under the assumption of similar  $D_{\text{OX}}$  in all other samples, the relative boron doping densities have been calculated as a function of the exposure time according to Eq. 2.1,

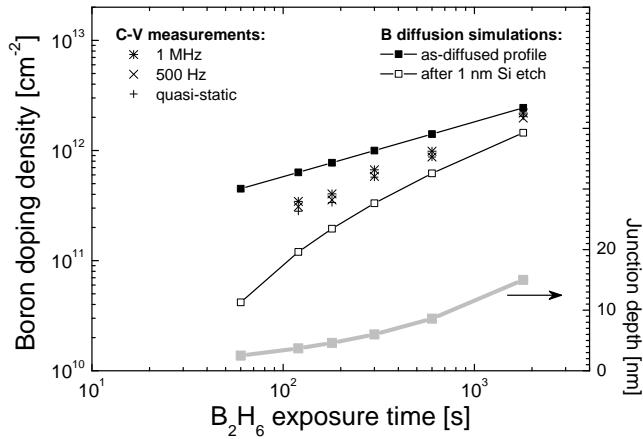

**Figure 2.14:** (Left y-axis) Boron doping density as a function of  $\text{B}_2\text{H}_6$  exposure time at  $700^\circ\text{C}$  determined from the flatband voltage shift at  $C_{FB}/C_{OX} = 0.855$  of the C-V characteristics for three different measurement frequency conditions. For comparison, the simulation results of boron diffusion at  $700^\circ\text{C}$  with a surface source are also displayed for either as-diffused profiles or after removal of a 1 nm surface Si layer. (Right y-axis) The simulated time dependence of the as-diffused B-doped junction depths for an  $n$ -type substrate doping level of  $10^{15} \text{ cm}^{-3}$ .

and they are plotted in Fig. 2.14 for various measurement frequencies. In comparison, simulation results of boron diffusion at  $700^\circ\text{C}$  are also reported for either as-diffused profiles or after removal of a 1 nm Si surface layer, which would be a plausible effect of the cleaning sequence.

Both diffusion and Si etching simulations were performed with Taurus TSUPREM-4<sup>TM</sup> [41]. In particular, a diffusion process can be modeled when the concentration of one or more impurities in the ambient gas is specified at the surface of the structure. In our case, the growing B-layer acts as the source of boron for the adjacent bulk silicon [13]. Therefore, the dopant surface concentration was varied during the simulated diffusion cycle according to the time dependence of the B-layer peak concentration as determined by the SIMS results shown in Fig. 2.7. Diffusion temperature and time were then defined as the experimental  $\text{B}_2\text{H}_6$  exposure conditions. The diffusion equations and the activation of boron impurities were solved by using the most comprehensive models available with the default material parameters. Besides information on the diffused profile, such as boron dose and junction depth (see Fig. 2.14), the software is also able to extract electrical characteristics, as demonstrated by the simulated high-frequency capacitance-voltage curve in Fig. 2.13 for the enhancement-type MOS structure.

The time dependence of the measured boron densities is in good agreement with the 0.5 grading coefficient of the simulated doping process, although for short exposures the B-layer removal might also slightly reduce the amount of active boron atoms incorporated at the c-Si surface. The C-V method thus overcomes the limitation of

**Figure 2.15:** Relative increase of the sheet-resistance with respect to the sheet-resistance at 0 V reverse biasing as a function of the substrate bias for either a 10 min as-deposited B-layer or a 30 min B-doped sample after standard cleaning and HF dipping. Simulation results are also reported for a boron doping profile formed during boron diffusion at 700 °C for equivalent exposure times. The influence of oxide charges has been taken into account for the latter sample.

sheet-resistance measurements, since boron doping is also revealed to be present for deposition times less than 5 min. In fact, oxide charges in combination with interface trapped charges can readily deplete or even invert such ultrashallow  $p^+$ -doped region.

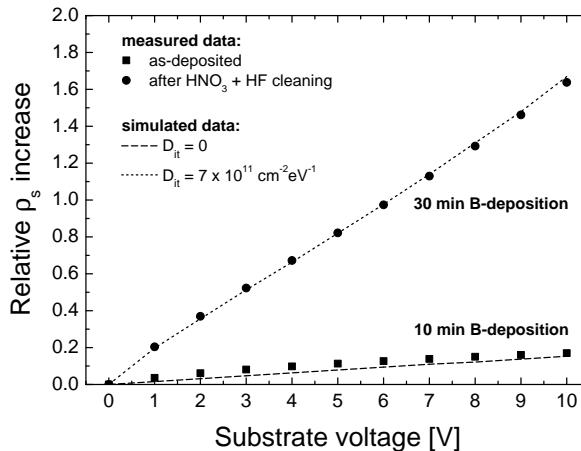

An attempt to extract the interface trapped charge density  $D_{it}$  has also been made by using a conventional method proposed in [52] based on the comparison of C-V measurements at 1 MHz and in quasi-static conditions. The calculated  $D_{it}$  show a similar 0.5 grading coefficient in the  $B_2H_6$  exposure dependence. In particular, an interface trapped charge density of  $7 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$  has been determined for a 30 min B-doped sample. Although the  $D_{it}$  level would also introduce a slight correction in the B doses, as seen for oxide charges, their effect is more evident on the sheet-resistance measurements shown in Fig. 2.15 as a function of the substrate voltage. In fact, the presence of the  $\alpha$ -B layer formed after 10 min deposition can screen any influence of the oxide charge, and thus the relative increase is in agreement with simulated  $p^+n$  junction depletion spreading in an equivalent boron-diffused region. On the other hand, after the removal of the  $\alpha$ -B film, the sheet-resistance of a 30 min B-doped sample will experience a more rapid increase due to charge-induced depletion at the Si surface. The latter effect is even more severe for samples with shorter exposures treated with the cleaning sequence.

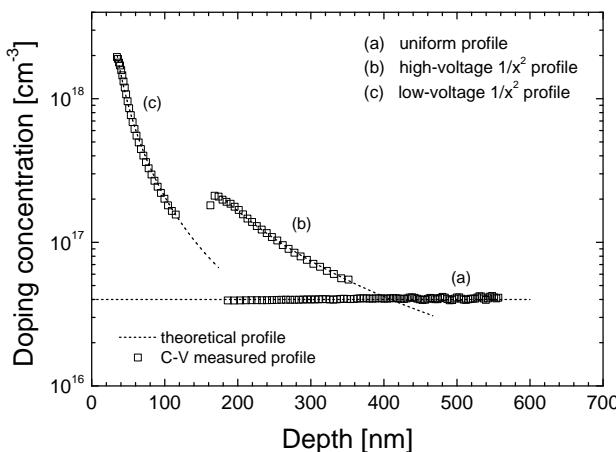

### 2.4.3 Capacitance-voltage profiling

In order to confirm that the B-deposition process is suitable for fabrication of nm-deep junctions, the diffusion of boron atoms into the c-Si substrate has been deter-

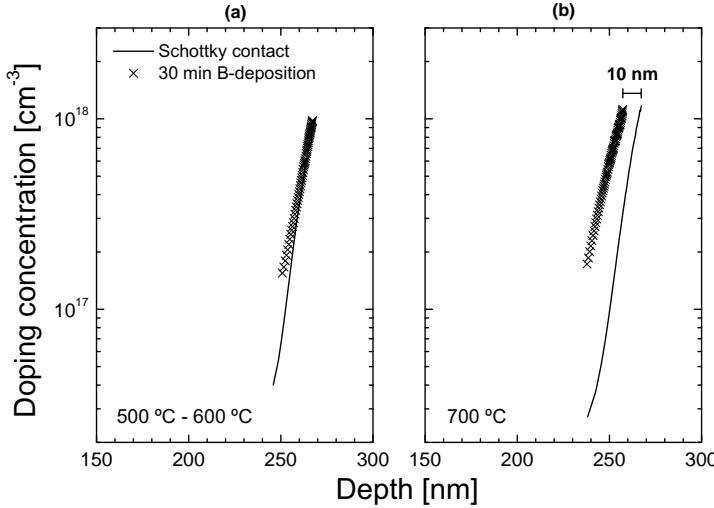

**Figure 2.16:** C-V doping profiles of the abrupt  $n^+$  buried layer measured by using at the surface either a Schottky contact or a B-layer. The boron deposition has been performed for 30 min at temperatures of (a) 500 °C and 600 °C, (b) 700 °C.

mined with an in-house capacitance-voltage profiling technique that uses the abrupt  $n^+$  buried layer of the  $n^-$ - $p^-$ - $n^+$  epi-stack to profile the tail of B-doped junctions at the wafer surface [53]. The  $B_2H_6$  exposure has been carried out at temperatures ranging from 500 °C to 700 °C. In Fig. 2.16 the profile of the  $n^+$  buried layer obtained from a Schottky contact is compared to that of the  $p^+$ - $n^-$ - $p^-$ - $n^+$  structure with a 30 min B-deposition at the surface. For both 500 °C and 600 °C exposures, the two curves essentially coincide, which suggests that a  $p^+$ -like layer is formed without any significant diffusion of dopant atoms. For the 700 °C deposition, the 10 nm difference in the position of the two curves verifies that the junction depth remains limited even after prolonged deposition times. In comparison, a similar 700 °C thermal treatment for a 5 keV  $BF_2^+$  implantation of  $1 \times 10^{15} \text{ cm}^{-2}$  will result in a diffused junction profile approximately six times deeper and much less steep [53, 54].

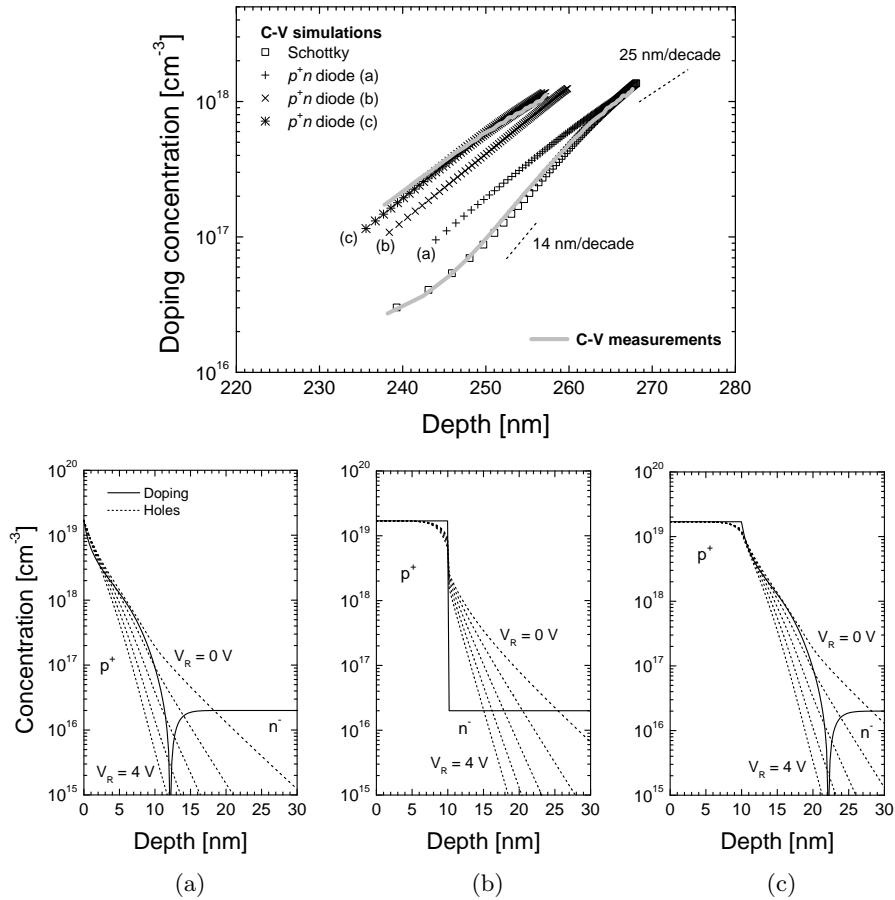

Device simulations of the C-V profiling technique have been also performed, and the results are shown in Fig. 2.17. The profile of the  $n^+$  buried layer from the  $n^-$ - $p^-$ - $n^+$  structure with a Schottky contact is coincident with the experimental curve. On the other hand, for the  $p^+$ - $n^-$ - $p^-$ - $n^+$  device, the influence of the boron deposition has been first investigated by assuming the  $p^+$ -doped junction to be formed only from a 30 min boron diffusion at 700 °C. The B surface source has been varied accordingly with the SIMS data. The resulting B profile is shown in Fig. 2.17(a) along with the majority carrier distribution for different reverse biasing voltages. Thus, the hole distribution rather than the actual doping affects the extraction of the  $n^+$ -profile mainly for impurity concentrations as low as  $10^{17} \text{ cm}^{-3}$ , where the characteristic length of the majority carriers (6–9 nm/decade) is comparable to the slope of the buried layer

**Figure 2.17:** (Top) Simulation and measurement results of the C-V profiling technique. (Bottom) The influence of a 30 min  $\text{B}_2\text{H}_6$  CVD process at  $700^\circ\text{C}$  has been simulated by assuming the  $p^+$ -doped region to be formed by: (a) thermal diffusion of boron with surface source in accordance with SIMS data, (b) 10 nm deep uniform B-doped layer, and (c) combination of profile (a) and (b).

(14 nm/decade). Instead, at higher reverse biasing voltages the abruptness of the hole profile will be determined by the Debye length of 1 nm corresponding to the boron peak concentration of  $1.7 \times 10^{19} \text{ cm}^{-3}$ , i.e. the solid solubility limit, and thus the C-V technique will reconstruct the less steep buried layer gradient ( $\sim 25 \text{ nm/decade}$ ). On the other hand, the experimental profile can be reconstructed by combining the effect of the as-diffused B profile with a 10 nm-deep uniform B-doped region (see Fig. 2.17(c)). The latter could be attributed to both silicon consumption during *in-situ* pre-bake cleaning and growth of a boron-silicide layer, since only use of the profile in Fig. 2.17(b) would still not completely describe the measured curve.

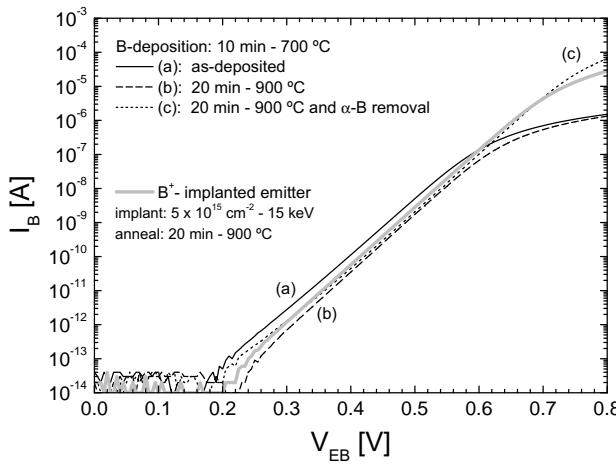

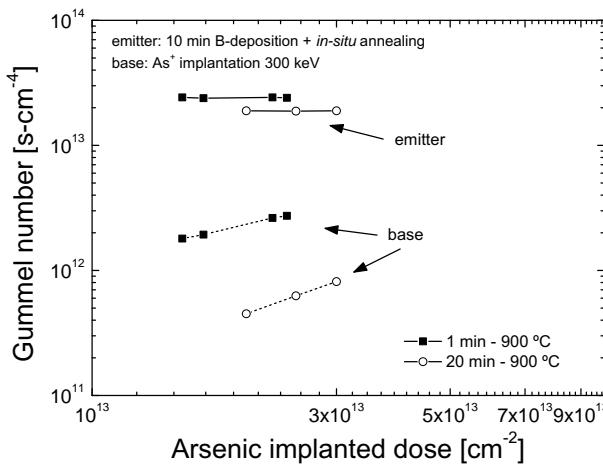

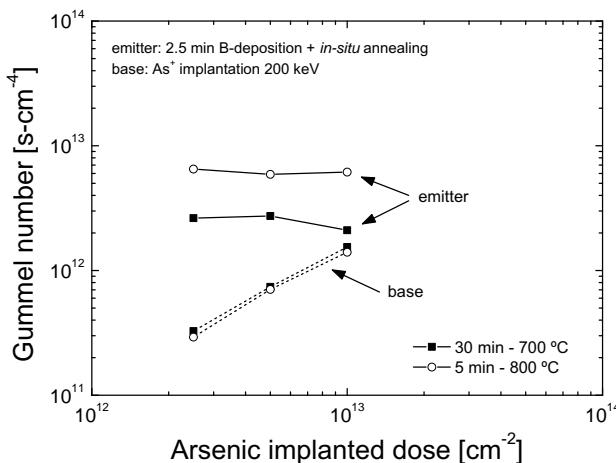

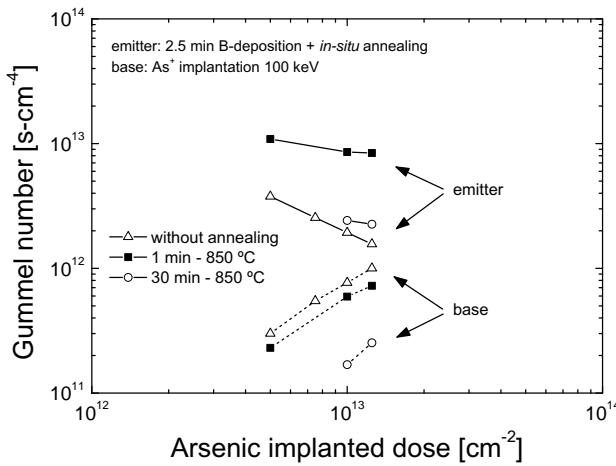

## 2.5 Conclusions