# Stellingen behorende bij het proefschrift INTO DEEP SUBMICRON: a simulation perspective door Serban Bruma

- 1. De "event-driven" aanpak hoort tot de essentie van de natuur, terwijl "global equations" alleen in onze geest bestaan.

- Naarmate de afmetingen van transistors verder in het submicron gebied doordringen, stagneert de performance verbetering als gevolg van de verzadiging van de carrier velocity.

- 3. "Level transparency" is de sleutel tot system-on-chip simulatie.

- "Het ikoon van de dode ster Komt langzaam aan de hemel op. Zij was, en was toch niet te zien, Nu we haar zien, is ze verdwenen."

<<M. Eminescu, Aan de ster>>

- 5. In dichtbevolkte systemen tellen de interacties tussen de individuen veel zwaarder als de individuele deugden.

- 6. Als we ideeën konden communiceren in plaats van woorden, zou elk cultureel onderscheid verdwijnen.

- 7. Software is voor computers wat onderwijs is voor mensen. Wat een netwerk is voor computers is de omgeving voor mensen.

- 8. Het grootste probleem dat het informatietijdperk met zich brengt, is het filteren van de ruis.

- 9. Het belangrijkste gevolg van het bestuderen van razend ingewikkelde zaken is dat we inzicht verwerven in eenvoudige, fundamentele problemen.

- 10. Het laten maken van "stellingen" is een onderzoek naar de geestesgesteldheid van de promovendus na voltooiing van het promotiewerk.

#### **Propositions**

#### accompanying the thesis

#### INTO DEEP SUBMICRON:

#### a simulation perspective

by

#### Serban Bruma

- 1. The "event-driven" approach is in the very essence of nature, while "global equations" exist only in our minds.

- 2. When down-scaling into the deep submicron regime, the saturation of carrier velocity brings performance improvement to a halt.

- 3. "Level transparency" is the key to system-on-a-chip simulation.

- 4. "The icon of the now dead star

Slow in the sky it rises;

She was, while we could not see her,

Now that we see, she's vanished."

<<M. Eminescu, To the star>>

- 5. In densely populated systems what matters are the interactions between individuals rather than the particular virtues of each individual.

- 6. If we could communicate through ideas instead of words, cultural borders would disappear.

- 7. Software is for computers like education for human beings. What a network is for computers, is the society for the people.

- The main problem brought by the information age is filtering the informational noise.

- 9. The main consequence of studying intricate matters is that we will be able to handle simple, fundamental matters.

- 10. The "propositions" are a sanity check of what is left of the spirituality of the Ph.D. candidate after years of research.

7567 7057 TR 3567

## INTO DEEP SUBMICRON: a simulation perspective

Serban BRUMA

## INTO DEEP SUBMICRON: a simulation perspective

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.F. Wakker, voorzitter van het College voor Promoties, in het openbaar te verdedigen op maandag 25 september 2000 om 16:00 uur

door

Serban BRUMA

inginer - Universitatea Tehnică din Iași, Roemenië geboren te Iași, Roemenië

Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. R.H.J.M. Otten

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. dr. ir. R.H.J.M. Otten, promotor

Prof. dr. ir. A.H.M. van Roermund

Prof. dr. H. Wallinga

Prof. dr. ir. W.M.G. van Bokhoven

Dr. ir. R. Nouta

Dr. ir. N.P. van der Meijs

Technische Universiteit Delft Technische Universiteit Delft

Universiteit Twente

Technische Universiteit Eindhoven

Technische Universiteit Delft

Technische Universiteit Delft

This book was set using the TEX typesetting system (and related packages) and the dvips DVI to PostScript translator. The fonts used were 10 points Times Roman. Part of the illustrations were created by using XFIG, XMGR, xdvi and ghostview. All these programs were made freely available to the public by their authors.

Copyright © 2000 by Serban Bruma. All rights reserved. No part of this book may be reproduced in any form or by any electronic or mechanical means (including photocopying, recording, or information storage and retrieval) without prior permission in writing from the author. Correspondence about this thesis and related subjects can be directed via email to: serban@cas.et.tudelft.nl.

"E pur si muove."

Galileo Galilei

$To\ my\ parents\ and\ my\ brother.$

## Contents

| A١ | Abstract |                                    |     |  |

|----|----------|------------------------------------|-----|--|

| A  | cknov    | wledgments                         | vii |  |

| 1  | Dee      | p submicron                        | 1   |  |

|    | 1.1      | Evolution of technology            | 1   |  |

|    | 1.2      | Devices                            | 3   |  |

|    | 1.3      |                                    | 5   |  |

|    | 1.4      | Complexity                         | 7   |  |

|    | 1.5      | This thesis                        | 8   |  |

| 2  | Lev      | el transparency                    | 11  |  |

|    | 2.1      | System description                 | 12  |  |

|    | 2.2      | Direct methods                     | 14  |  |

|    | 2.3      | Local linearization                | 15  |  |

|    | 2.4      | Locally linear systems             | 17  |  |

|    | 2.5      | A piecewise linear approach        | 18  |  |

|    | 2.6      | One algorithm                      | 23  |  |

| 3  | Tra      | insistors in the limit             | 25  |  |

|    | 3.1      | Impact of velocity saturation      | 27  |  |

|    | 3.2      | Model equations                    | 29  |  |

|    | 3.3      | Scaling down                       | 34  |  |

|    | 3.4      | Saturated velocity                 | 38  |  |

|    | 3.5      | Piecewise linear transistor models | 40  |  |

ii CONTENTS

| 4 | Col | llapsible current sources                  | 43  |

|---|-----|--------------------------------------------|-----|

|   | 4.1 | Definition                                 | 44  |

|   | 4.2 | Algorithmic requirements                   | 49  |

|   | 4.3 | Transistors as collapsible current sources | 52  |

|   | 4.4 | Modified collapsible current sources       | 52  |

|   | 4.5 | Choosing a simulator                       | 56  |

| 5 | Int | roducing time                              | 59  |

|   | 5.1 | Time discretization                        | 61  |

|   | 5.2 | Multirate integration                      | 63  |

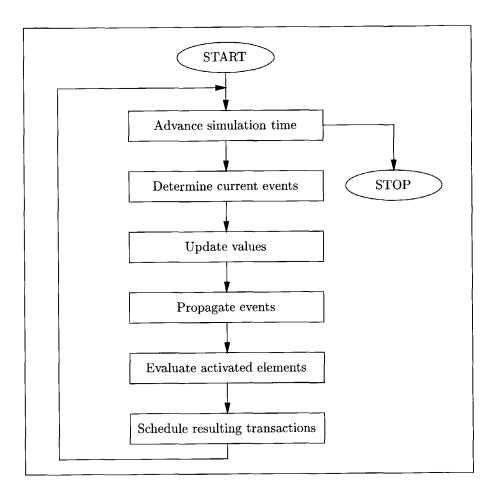

|   | 5.3 | Event-driven simulation                    | 64  |

|   | 5.4 | Multi-level simulation capabilities        | 66  |

| 6 | Tra | nsistor inertia                            | 71  |

|   | 6.1 | Quasi-static approximations                | 72  |

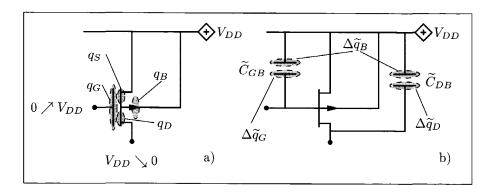

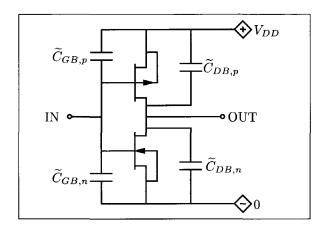

|   | 6.2 | Modeling large-signal charge variations    | 76  |

|   | 6.3 | Evaluating large-signal charge variations  | 81  |

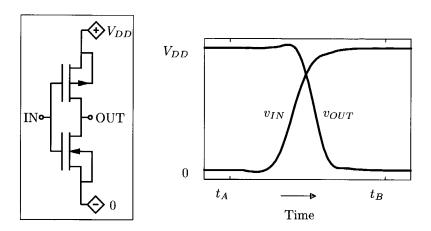

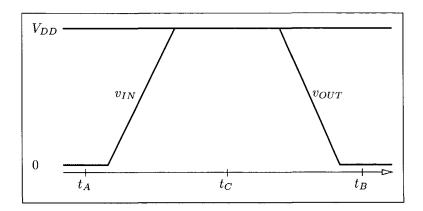

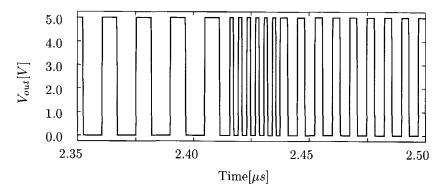

|   | 6.4 | Dynamic characterization of an inverter    | 84  |

|   | 6.5 | Average capacitors                         | 86  |

| 7 | One | e language, one algorithm                  | 89  |

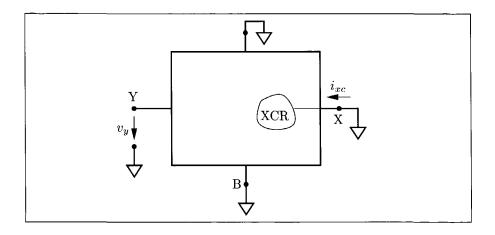

|   | 7.1 | Voltage and current events                 | 90  |

|   | 7.2 | Constitutive processes                     | 92  |

|   | 7.3 | Topological processes                      | 93  |

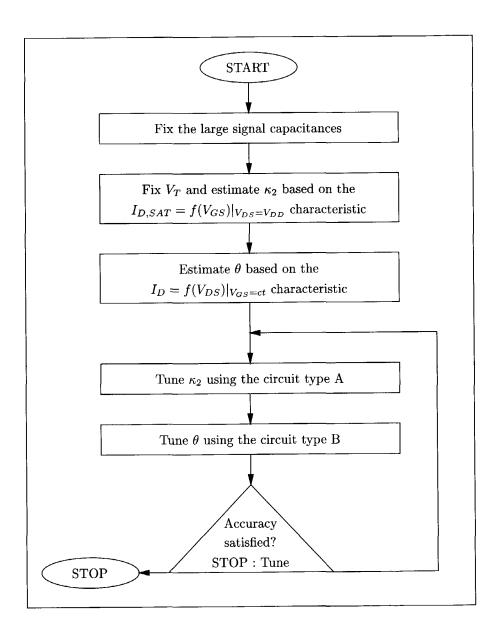

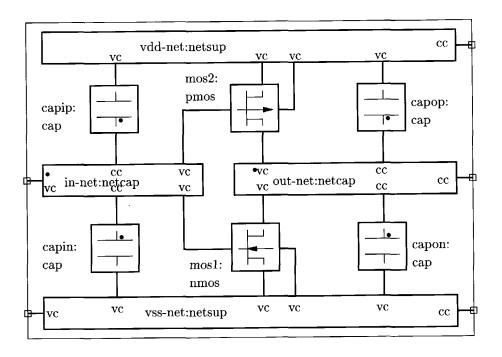

|   | 7.4 | Model calibration                          | 95  |

|   | 7.5 | Using the VHDL-MOS package                 | 98  |

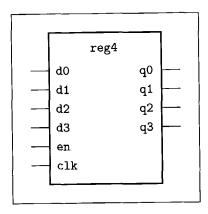

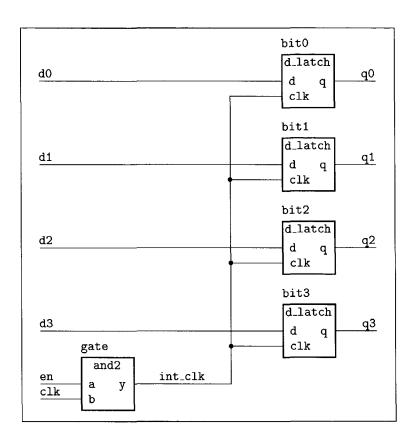

| 8 | Per | spectives                                  | 101 |

|   | 8.1 | Libraries                                  | 102 |

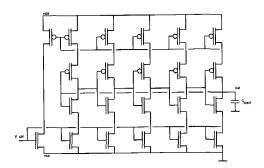

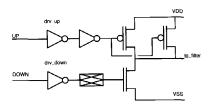

|   | 8.2 | Complex digital circuits                   | 103 |

|   | 8.3 | Mixed analog/digital circuits              | 106 |

|   | 8.4 | Conclusions                                | 108 |

| 9 | A d | eep submicron vanishing point              | 113 |

#### CONTENTS

| A            | The   | linear complementarity problem         | 119 |

|--------------|-------|----------------------------------------|-----|

|              | A.1   | Path followers                         | 120 |

|              | A.2   | Complementary pivoting                 | 122 |

|              | A.3   | PLATO                                  | 124 |

| В            | Lon   | g channel static operation             | 125 |

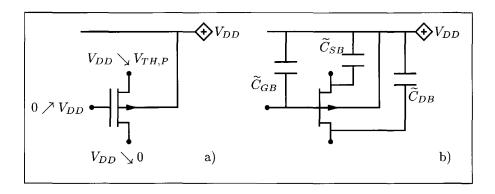

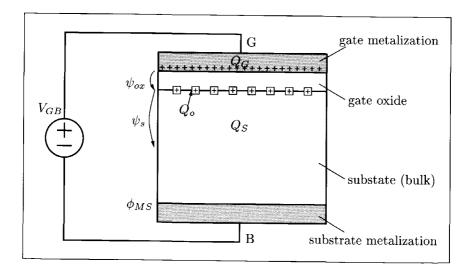

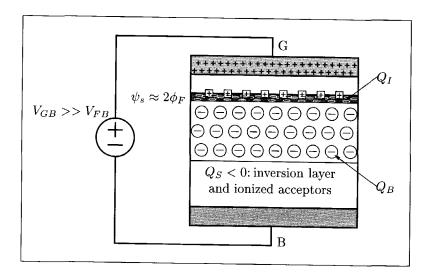

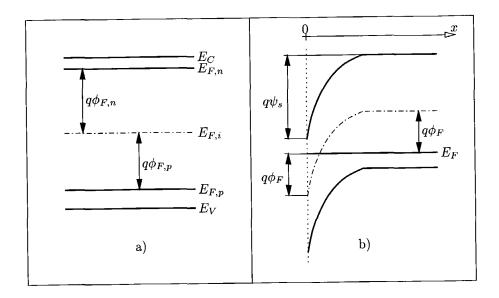

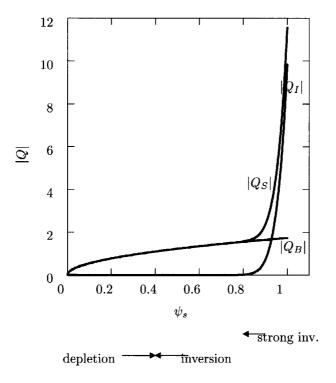

|              | B.1   | Transistor structure                   | 125 |

|              | B.2   | Capacitors                             | 127 |

|              | B.3   | Diodes                                 | 134 |

|              | B.4   | Transistors                            | 135 |

|              | B.5   | Remarks                                | 143 |

| $\mathbf{C}$ | VH    | DL summary                             | 145 |

|              | C.1   | Elements of behavior                   | 145 |

|              | C.2   | Elements of structure                  | 148 |

|              | C.3   | Mixed structural and behavioral models | 149 |

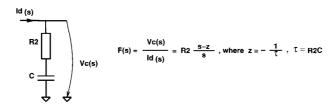

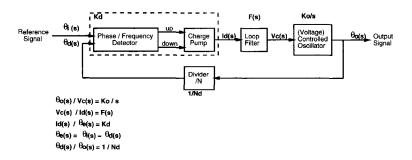

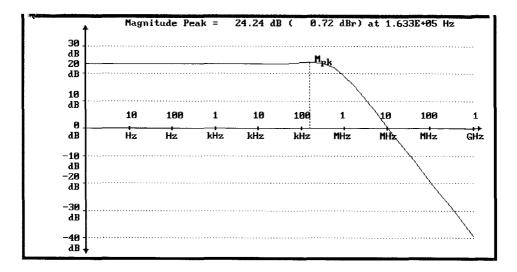

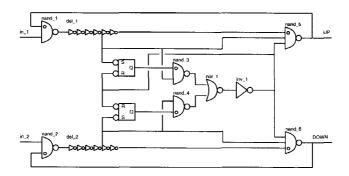

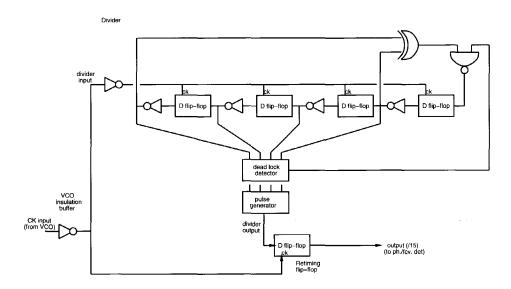

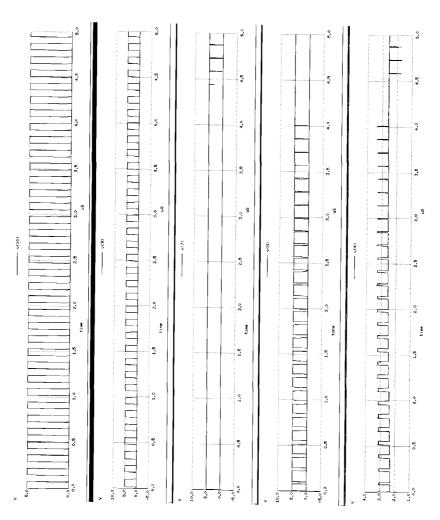

| D            | Cha   | arge pump PLL                          | 153 |

| В            | iblio | graphy                                 | 161 |

| G            | lossa | ary                                    | 167 |

| A            | bout  | the author                             | 173 |

| S            | amer  | nvatting                               | 175 |

iv CONTENTS

### Abstract

The increasing demand for more processing capability has brought the CMOS technology into the deep submicron era. To integrate complex systems on the same chip designers have to manage the diversity and the complexity of the deep submicron circuits during the design process.

This thesis describes research on efficient analysis of complex, large-size deep submicron CMOS circuits. The *diversity* aspect of the problem calls for the usage of one single simulation algorithm for the multiple abstraction levels involved in system description. The *complexity* aspect of the problem calls for a minimal, compact model for the components.

We show that the event-driven approach, based on local modeling and global signaling, is a better alternative for efficient multi-level simulation than an equation-based approach. The piecewise linear approach, which is based on diode states and thus satisfies the one-algorithm demand for multi-level simulation, falls short in what concerns the computational efficiency.

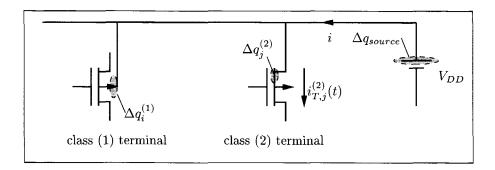

We use a compact, piecewise linear model for the static behavior of the deep submicron MOS transistor. This collapsible current source model, is minimal to explain the transistor level operation of the CMOS circuits. Beside this, we use a compact model based on average capacitors to capture the terminal charge variations in the MOS structure for large-signal dynamic operation.

We prove that this compact way of modeling the static and dynamic operation of a deep submicron MOS transistor is an analytically sound method as far as the waveform estimations and power consumption for a digital CMOS circuit are concerned.

vi ABSTRACT

We achieve efficient analysis of complex, large-size deep submicron CMOS circuits by using this compact model of the MOS transistor in the framework of an event-driven simulator. We present a special VHDL package which we developed to capture continuous aspects of CMOS circuit operation in an event-driven simulator.

We practically use this approach to verify large circuits. We obtain a high level of accuracy, comparable with the one achieved in the classical transistor level modeling, however at considerably lower price in terms of computation. Our approach opens the way to multi-level simulation, i.e., digital gate-level descriptions can coexist with analog-like transistor-level descriptions inside the same event-driven simulation kernel.

**Keywords:** deep submicron, multi-level simulation, level transparency, event-driven, piecewise linear, collapsible current source model, average capacitors model, CMOS

## Acknowledgments

The research presented in this thesis was carried out in the Circuits and Systems group at the Delft University of Technology.

At this occasion I would like to express my gratitude to a number of people that were of great help during my research. First of all, my supervisor Ralph Otten, for support and guidance towards the completion of this thesis. I do appreciate the freedom and trust that I was granted, as indispensable ingredients for my accomplishments. Reinder Nouta encouraged me with the VHDL-MOS approach. Nick van der Meijs and Arjan van Genderen gave their advice on various aspects of the CAD tools. Patrick Groeneveld and Viorica Simion generously offered their support in the early stages of my research. Jack Glas, with his rigorous time planning, acted as an efficiency example. Jan Nieuwstad helped me to set-up a Linux machine for typesetting this thesis. Aard Wiersma, as student, thoroughly exercised with the final approach. My gratitude goes also to Marion de Vlieger for ensuring the smooth functioning and the good spirit of the group.

I would also like to thank all my colleagues from Philips Research for support and help towards finishing this thesis.

Finally, I would like to thank my parents for continuous encouragement and Cezar Bruma for fraternal support. This book is dedicated to them.

Serban Bruma Netherlands, September 2000

## Chapter 1

## Deep submicron

#### Contents

| 1.1 | Evolution of technology |  |

|-----|-------------------------|--|

| 1.2 | Devices                 |  |

| 1.3 | Interconnect 5          |  |

| 1.4 | Complexity              |  |

| 1.5 | This thesis             |  |

Three decades ago the digital CMOS emerged as a robust technology. At that time the theoretical framework was ripened: boolean algebra and sequential processing of digital data were matured concepts. The CMOS technology offered fertile ground for the implementation of the digital abstraction. It was a robust technology due to the large built-in noise margin.

The design effort was considerably lower because designers could much easier manipulate the digital abstraction than operate with a concept that would take into account the analog operation of the circuits.

#### 1.1 Evolution of technology

During the last three decades these technological and economical advantages of the CMOS technology had a major contribution to the boost of the semiconductor industry, making it following the predictions of the Moore's [1] law.

In the last few years the pressure put by the demands of the new information age made people doubt of the capacity of the once so-good CMOS technology. The ever increasing demand for more processing power translated into two issues: (1) higher processing rates, and (2) more processing capability per silicon unit area.

Engineers believed that by down-scaling the dimensions of the MOS transistor they would reach both goals, therefore it would be possible to integrate more functionality on a given silicon area and at the same time improve the performance<sup>1</sup>.

This can be seen from the following line of reasoning. By scaling-down the MOS transistor length, the current capability per unit width improves with some factor. The gate area reduces and as a consequence the capacitive load of the driver may decrease. Moreover, by scaling-down to a certain extent the transistor width the performance improves still considerably. Therefore, with the length and the width scaled-down, one can obtain both a more efficient utilization of the silicon area and a better performance.

The delay of the gate is roughly defined by:

$$t_d \approx \frac{(C_{GATE}/W) \cdot V_{DD}}{I_{D,SAT}/W} \tag{1.1}$$

where  $C_{GATE}$  is the switched capacitive load, W is the MOS transistor width,  $I_{D,SAT}$  is the saturation current of the transistor, and  $V_{DD}$  is the supply voltage. By scaling down the transistor length, an improvement in the current capability  $I_{D,SAT}/W$  can be obtained. In the overall scaling effort, the specific gate capacitance  $C_{GATE}/W = C_{ox}L$  turns out to a first approximation to be constant, as  $C_{ox}$ , the gate oxide capacitance per unit area, increases by reducing the thickness of the gate oxide and L, the effective channel length, decreases. The supply voltage  $V_{DD}$  must decrease with the down scaling, based on power considerations. Concluding, the gate delay diminishes, i.e., improves, by shrinking the technology.

One might believe that down sizing can infinitely go on, however, as explained in the next sections, there are essential limiting factors.

In the situation of ideal down scaling, the same area of silicon would sell at a higher price due to more added value, which stems from: (1) the possibility to physically integrate more processing capability, which actually was the initial aim, and (2) the increased complexity of the systems that could be integrated on one

<sup>&</sup>lt;sup>1</sup>In this context performance is equivalent to speed.

1.2. DEVICES 3

chip. The latter was the direct consequence of the possibility to have hundreds of millions of transistors on a deep submicron chip. Therefore the deep submicron technology marks the dawning of the system-on-a-chip era.

However, nothing comes from free. To extend the validity of the Moore's law further into future engineers have to solve a lot of problems. What could be considered just side-effects in the beginning proved to be the limiting factors in deploying new technologies.

The challenges that have to be dealt with in the deep submicron technology can be classified in three categories:

- effects on devices,

- effects on interconnect,

- induced consequences at system design level.

The first category directly relates to the shrinking of the dimensions of the active devices. The second category includes effects which are indirect consequences of shrinking the feature size all over the chip, including the interconnect. The last category came into reality when designers later realized that in their methodology for system-on-a-chip design they will have to deal with the increased system complexity, as well.

#### 1.2 Devices

The deep submicron effects at device level arise from the fact that all the three dimensions of the transistor have been shrunk-down.

1. In our view the most important limiting factor<sup>2</sup> in the down-scaling is the saturation of the **drive current** as a consequence of the saturation of the carrier velocity [2]. The immediate implication is that the device performance, measured as delay time, does not improve anymore with the down-scaling.

At very short channel length, most carriers travel at a maximum saturated velocity,  $v_{sat}$ , through the channel, which nearly eliminates the influence of the

<sup>&</sup>lt;sup>2</sup>We do not deny another important limiting factor, namely the poor scaling of the interconnect performance. While the down-scaling of the active device dimensions is the originally desired action, the down-scaling of the interconnect appeared as a consequence of the former.

channel length on the saturation current. A more suitable expression of the drain saturation current for this limiting case is:

$$I_{D,SAT} = W v_{sat} C_{ox} (V_{GS} - V_{th})$$

$$\tag{1.2}$$

This expression makes clear that the drain saturation current is independent of the channel length. Moreover it shows a linear dependence on the gate voltage drive. These characteristics contrast with the behavior of the classical long channel MOS, where the drain saturation current does depend on the channel length and the dependence is proportional to the square of the gate voltage drive. Apart from showing the forthcoming limitation of the deep submicron technology, equation (1.2) hints at how to build a compact static model for the deep submicron device.

We present the theoretical background and the derivation of the equation (1.2) in Chapter 3 and the implication on the limitation of the performance increase of the deep submicron devices in Chapter 9. We explain how we exploited the linear dependency to obtain computationally efficient model implementations for the deep submicron transistor in Chapter 4 and in Chapter 7.

2. Another issue that requires special attention in deep submicron circuits is the power dissipation [3]. Even if the total active capacitance to be switched per unit of area stays constant with the down-scaling, it turns out that the power dissipation of the chip increases because of the increased operating frequency. The most efficient method to reduce the power consumption is to reduce the supply voltage, as

$$P = \alpha C V_{DD}^2 f \tag{1.3}$$

where  $\alpha$  is the switching activity factor, C is the switched capacitance, and f is the operating frequency.  $V_{DD}$  cannot be reduced anymore as to preserve the already fragile noise margin.

One can find an accurate estimator for the switching activity factor, provided that he has an efficient model and an efficient method to simulate the power consumption. We present such a model incorporating the static as well as the dynamic behavior of the deep submicron transistor in Chapter 3 and in Chapter 6. We state the need for level transparency when simulating complex circuits and consider one such simulation method in Chapter 2.

3. At short channel length another phenomenon looms large in the deep submicron technology. Its effect is the decrease of the MOS transistor threshold voltage as the distance between source and drain becomes shorter. This effect requires special consideration during device design, because it makes visible the subthreshold current contribution to the total power consumption. Process tolerances cause statistical deviations of the channel length across different dies, therefore the designer must ensure that the threshold voltage does not become too low for the device with the shortest channel length on the chip.

To keep this short-channel effect under control, gate **oxide thickness** is reduced nearly in proportion to channel length. This reduction is necessary for the gate to retain more control over the channel than the drain does. Thin oxide raises then serious concerns about leakage due to direct tunneling of the current through such an extremely thin layer [4, 5].

#### 1.3 Interconnect

Interconnect wires are responsible for the communication on the chip. To take advantage of the scaled-down dimensions of the active devices, wiring pitches are dropping rapidly and at about the same rate as the gate length. This means that both the wire width and the wire spacing are scaled down. Deep submicron interconnect effects, among which the most important are the RC delay, the cross-coupling noise, and the electromigration, rise a variety of problems to process engineers, circuit designers, and CAD tool developers.

1. The most commonly cited deep submicron interconnect problem is the rising **RC delay** [6], or the long-wire delay problem [7]. The increased line resistance is the main reason behind the increased wire delay in deep submicron.

Wiring resistance scales inversely with the wire's cross sectional area. To keep resistance from increasing too quickly, two approaches can be taken: (1) scale the line height at a slower rate than the wire width, and (2) use better conductors for the on-chip interconnect.

Wiring capacitance is also increasing in scaled down processes due to the higher interconnect densities in modern chips. As a reduced packing density is not an option in deep submicron, the only method to reduce the wiring capacitance is to use a material with a lower dielectric constant than the silicon dioxide, material

commonly known as a low-k material.

Apart from the technological solutions, i.e., an increased interconnect aspect ratio and materials with higher conductivity, also circuit level solutions are possible. Various techniques have been developed to improve the communication on the chip, such as buffer insertion, shielding, differential signalling. Yet the interconnect tends to dominate the speed performance on a deep submicron chip.

2. As mentioned earlier, one way to reduce the resistance has been to slowly scale line thickness, resulting in taller, thinner wires. These high aspect ratio interconnect tracks have a detrimental side effect in that they result in a large amount of coupling capacitance. With an aspect ratio greater than one, lines tend to have more coupling capacitance to neighboring wires in the same layer than to upper and lower wiring layers, which effectively serve as ground planes.

This increased coupling capacitance is what makes the **cross-coupling noise** an issue for deep submicron interconnects. It comes in two distinct forms: cross-coupling delay and crosstalk. The cross-coupling delay means a delay deterioration, as the total load capacitance of a gate is no longer a constant value, due to the Miller effect [6].

For the deep submicron technology, the increased coupling capacitance between adjacent wires and the reduced supply voltage are erosion factors for the fragile noise margin. They enable the undesired analog aspects to permeate the digital circuitry operation, endangering the originally robust digital abstraction.

Simulating deep submicron circuits such that to capture this effect, calls for a transparent way to model both digital and analog behavior and also compact way so that devices and interconnect can be included in the same analysis. We believe that the modeling and simulation approach presented in this thesis is very suitable for this purpose.

3. Beside the beneficial effect on the wire resistance, better conductors also have the advantage of increased resistance to **electromigration** effects. Electromigration is a reliability problem associated with large current densities. The large current physically moves metal ions down the wire, resulting in opens in the line or shorts to adjacent wires. By using copper in place of the traditional aluminum, the electromigration lifetime until failure can be increased up to two orders of magnitude [8].

#### 1.4 Complexity

An inherent implication of the reduced feature size in the deep submicron technologies is the availability of hundreds of millions transistors on one chip. This opens the possibility to integrate very complex systems on the same die, but also rises the challenge of managing the complexity of such systems during the design process. In the last years engineers realized that the growth enabled by the deep submicron technology is slowed down by the design productivity gap. This means that the pace at which systems-on-a-chip (SOC) can be designed is not quick enough to exploit all the integration capabilities of the new technologies.

Lately engineers talk about system-on-a-chip design methodologies as being the only way to develop huge systems on a single silicon substrate in a short design cycle. Nowadays, such a methodology begins at system level through planned **reuse** [9] of functional components including programmable processors, mixed signal functions, and software. In long term designers will continue to move their design efforts to higher levels of abstraction. Designing better architectures is what will generate the next large advance in systems-on-a-chip design [10].

Designers must make architectural decisions at system level: IP<sup>3</sup> selection, hardware/software partitioning, performance analysis, and functional verification. At the moment there are several EDA tools dealing with these issues. The evaluation of power and timing at system level is preferred to transistor level. The current transistor level tools are indeed more accurate, but not fast enough to handle large designs.

Managing the complexity in an efficient way calls for (1) compact models, and (2) one single algorithm for multi-level simulation.

Our approach to compact modeling for the deep submicron device allows us to verify large circuits at a high level of accuracy, comparable with the one achieved in the classical transistor level modeling, but at considerably lower price in terms of computation. Yet, the most important contribution that our work brings to system design is the possibility to co-simulate, co-verify mixed circuits. The key is the level transparency in modeling and simulation of complex systems-on-a-chip, notion which we introduce in Chapter 2, we reconsider in Chapter 5, and then extend in an original manner in Chapter 7.

$<sup>^3</sup>$ Intellectual Property

#### 1.5 This thesis

This thesis describes our research work on modeling and analysis of large size deep submicron CMOS circuits. From all the challenges that have been mentioned towards the end of Section 1.1 we give an answer only to those which can be approached from circuit level.

Such an approach would incorporate the most important limiting factor in the down-scaling – the saturation of the drive current. It would allow us to accurately estimate the power dissipation of the deep submicron circuits. It would provide a way to include both digital and analog behavior under the same paradigm, so that devices and interconnect can be included in the same analysis; this might be used in dealing with cross-coupling noise. It would certainly provide the means to deal with part of the problems raised by the increased complexity of the systems-on-a-chip, i.e., the efficient verification of large circuits at high level of accuracy and the co-simulation/co-verification of mixed digital/analog circuits.

In Chapter 2 we state the need for level transparency for the efficient simulation of systems-on-a-chip, i.e., circuits with large size and with descriptions across different abstraction levels, as digital and analog. We introduce a candidate modeling and simulation framework based on a classical simulation approach.

In Chapter 3 we analyze the fundamental implications of reducing the MOS transistor length into the deep submicron regime. We contrast the static behavior of the short channel transistor to the one of the long channel transistor, presented for reference in Appendix B. We propose a compact static model for the deep submicron transistor, model which is minimal for the explanation of the transistor level operation of the CMOS circuits.

We realize that this MOS transistor model, as implied by the deep submicron reality, is well fitted with the simulation framework introduced in Chapter 2. We show how the model is implemented in this simulation framework in Chapter 4.

In Chapter 5 we address modalities for dynamic simulation. Reconsidering the need for efficient simulation we point out another modeling and simulation framework, which comes out to be best fitted with our need.

We complete the modeling of the deep submicron MOS transistor in Chapter 6 where we discuss the dynamic operation and we derive an analytically sound model for the large-signal terminal charge variations.

In Chapter 7 we discuss the implementation of the compact models, static

1.5. THIS THESIS 9

and dynamic, in the simulation framework from Chapter 5. Here we propose a simulation package with a larger applicability area than for CMOS. We devise a methodology to calibrate the models for accurate power and waveform estimation.

In Chapter 8 we indicate from a pragmatic perspective how our modeling and simulation approach would have to be used for the efficient analysis of large, complex systems. On a couple of test designs, we assess the accuracy and the efficiency of our approach. In this chapter we also summarize our findings and final thoughts regarding efficient modeling and analysis of large deep submicron circuits.

In Chapter 9 we comment on the future trend of down-scaling, from the point of view of the achievable performance increase.

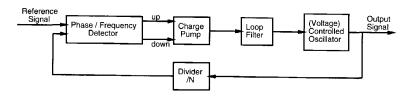

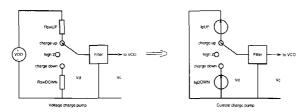

In Appendix A we present some methods used for solving the linear complementarity problem that we mentioned in Chapter 2. In Appendix B we shortly present the classical concept of the long-channel MOS transistor operation. Here the reader can find some prerequisites for Chapter 3. In Appendix C we recall some basic VHDL language concepts that we use for the presentation in Chapter 7. In Appendix D we recall the main design and implementation issues of the phase-lock loop, used as a demonstration vehicle in Chapter 8.

The book also contains a list of bibliographic references regarding the physics and operating principles of the deep submicron MOS transistor, piecewise linear and event-driven simulation paradigms, modeling languages, and related subjects in the Bibliography chapter. Further, the Glossary explains the abbreviations, acronyms, symbols and a couple of terms frequently used throughout this book.

## Chapter 2

## Level transparency

#### Contents

| 2.1        | System description          |

|------------|-----------------------------|

| <b>2.2</b> | Direct methods              |

| 2.3        | Local linearization         |

| 2.4        | Locally linear systems      |

| 2.5        | A piecewise linear approach |

| 2.6        | One algorithm               |

Deep submicron technologies promise the possibility to integrate very complex systems on a single chip. The equivalent transistor count for such systems-on-a-chip is huge, in the order of one hundred million. The manipulation of a system of such size during various design phases, such as simulation or verification, cannot always be performed at transistor level as a whole, because of the overwhelming complexity. Moreover, the amount of detail produced by simulations at that level is rarely manageable, and therefore hardly useful.

As a result, large parts of the system have to be represented at several levels of abstraction, i.e., gate level, register level, behavioral or higher. However, some smaller parts of the system, where continuous aspects of the operation cannot be abstracted into a logic description, remain to be represented at transistor level only.

Consequently, a system-on-a-chip simulation approach has to accommodate multiple levels of abstraction. In this way:

- the simulation becomes feasible, as the more abstract representations are more compact, demanding less computational resources;

- the degree of detail of a transistor level representation is provided at the places where needed;

- the simulation is precise enough, as the more abstract levels ensure a realistic signal environment for the transistor level.

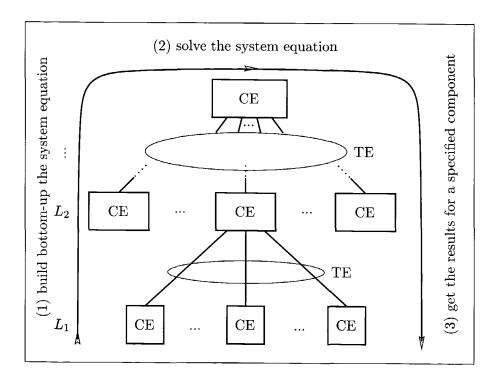

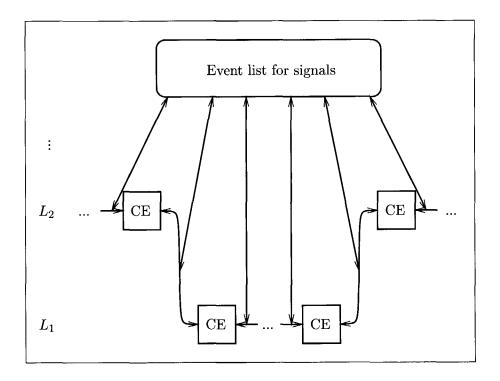

A straight solution would be to use separate level-specific simulation engines, and to have these engines communicate with each other. The computational efficiency of such a solution depends heavily on the communication speed between processes at different levels. Hence, it would be best if we could have a common modeling language for all descriptions and a single algorithm to manipulate these descriptions. In this way, one engine would be sufficient for the system-on-a-chip simulation, provided that acceptable efficiency can be achieved. The capability of a simulation engine to use one single algorithm for manipulating multiple levels of description is called level transparency.

#### 2.1 System description

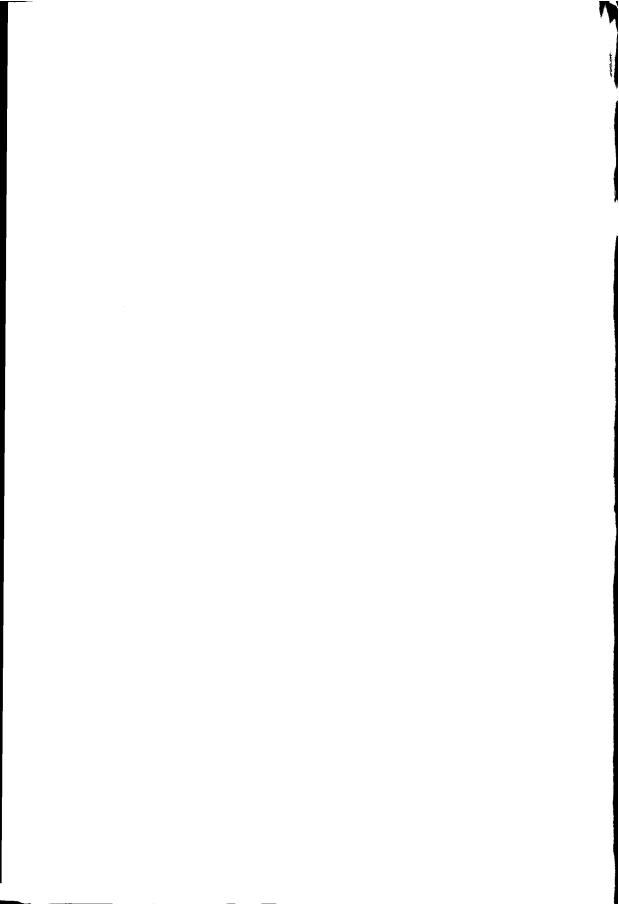

At a specified hierarchical level a system is defined as a union of components which interact according to some topological and numerical rules. The system communicates with the environment through stimuli and responses. Each component has an intrinsic operation, reflected in a set of constitutive relations. In general, each component "inherits" the structure of the system it is part of, in the sense that each component may be regarded as a union of subcomponents which are interacting according to a set of topological rules, and that for each component one may define an environment to communicate with (see Figure 2.1). At the lowest level of hierarchy the system consists of atomic components that are no further decomposed. Atomic components are primitive systems which are described completely by constitutive relations.

The rules of interaction between components together with the individual behavior of each component give the functionality of the system. In the general case of a non-linear system both the components and the interactions between them are described by non-linear relations.

Figure 2.1: Component interaction inside a system. Each component  $C_i$  is a union of subcomponents  $C_{ij}$ . The arrows indicate interactions.

When the lumped circuit approximation is valid¹ the topology of an electrical system is well described by Kirchhoff's voltage and current laws. The branch voltages are related with the node voltages via the Kirchhoff voltage law. The Kirchhoff current law is an electric charge conservation law: the exchange of charge between the components connected to a node is done in a conservative way, i.e., the amount of charge which enters a node is the same as that which leaves it. Associating the flow of charge with the electric current, Kirchhoff current law states that the sum of currents which enter a node must be equal to the sum of currents leaving that node. Both, Kirchhoff current law and Kirchhoff voltage law, are of a linear nature and thus the topological equations for an electrical system are linear. In the case of a lumped electric circuit each atomic component is described by a dependency, the constitutive equation, between its terminal currents and voltages. This dependency is often of a non-linear nature.

<sup>&</sup>lt;sup>1</sup>This depends on the size of the atomic components, their physical distance and the transients (frequencies) in the circuit.

#### 2.2 Direct methods

It appears that a lumped electric circuit is completely specified if we know the constitutive equations of each component and the topology of the system (how the components interact). In order to simulate such a circuit, *direct methods* seek to solve two problems:

- 1. aggregate the constitutive equations according to the topology into some sort of global description, and

- 2. find a way to manipulate this global description, as for any input stimuli one should be able to compute the system response.

The latter task is performed by solving for a sequence of time points a set of equations that represent the behavior of a non-linear resistive network. This set has the form

$$\mathbf{f}(\mathbf{x}, \mathbf{y}) = \mathbf{0} \quad \equiv \begin{cases} f_1(\mathbf{x}, y_1, y_2, \dots, y_n) = 0 \\ f_2(\mathbf{x}, y_1, y_2, \dots, y_n) = 0 \\ \vdots \\ f_n(\mathbf{x}, y_1, y_2, \dots, y_n) = 0 \end{cases}$$

(2.1)

where  $\mathbf{f}$  is a vector of functions,  $\mathbf{x}$  is the stimuli vector, and  $\mathbf{y}$  is the response vector. The contents of the system response,  $\mathbf{y}$ , is dependent on the particular method (nodal, tableau, modified nodal) used to build (2.1). Each function  $f_i(\mathbf{x}, \mathbf{y})$  is a linear combination (topological equations) of possibly non-linear functions (constitutive equations), thus  $f_i$  is in general non-linear in  $\mathbf{x}$  and  $\mathbf{y}$ . The set (2.1) describes a non-linear algebraic set of equations. Apart from special cases, usually of small size, the solution of this set cannot be obtained in a closed form and computer techniques are used to solve for  $\mathbf{y}$ .

This poses two problems, namely how to represent the non-linearities in a computer, and how to solve the set of equations. The two are of course not unrelated. Methods using the analytic properties of the non-linear functions need access to the Jacobian matrix or have the capability of approximating all partial derivatives. An elementary method for multidimensional problems that works well for finding a root is the *Newton-Raphson method* provided a sufficiently close guess of the solution is available. Otherwise one has to resort to globally more convergent methods,

which are without exception much more complicated. Fortunately, the way time-continuous circuit simulation is organized, that is from time point to sufficiently close time points, makes it easy to satisfy that condition, and therefore Newton-Raphson procedures are in the core of the most popular transistor level circuit simulators since the seventies.

#### 2.3 Local linearization

For a given stimuli vector  $\mathbf{x}$  the Newton-Raphson method produces in an iterative way a sequence of vector values  $\mathbf{y^0}$ ,  $\mathbf{y^1}$ , ...,  $\mathbf{y^k}$ ,  $\mathbf{y^{k+1}}$ , ... which converges to the exact solution  $\mathbf{y^*}$ .  $\mathbf{y^0}$  is the initial guess and is usually taken to be the solution of the previous stimuli set. As the computing resources are limited, infinite sequences cannot be afforded; a certain  $\mathbf{y^a}$  will be declared the approximate solution if it satisfies given accuracy requirements (absolute and/or relative error less than some imposed values).

We will describe briefly the k-th iteration step: build  $\mathbf{y}^{k+1}$  starting from  $\mathbf{y}^k$ , for fixed input stimuli  $\mathbf{x}$ . For the duration of the current iteration process the contribution of the fixed  $\mathbf{x}$  can easily be absorbed in the constant part of  $\mathbf{f}$ . Consider the Taylor expansion of  $\mathbf{f}(\mathbf{y})$  around  $\mathbf{y}^k$ :

$$f_{1}(\mathbf{y}) = f_{1}(\mathbf{y}^{k}) + \frac{\partial f_{1}}{\partial y_{1}}\Big|_{\mathbf{y}^{k}}(y_{1} - y_{1}^{k}) + \dots + \frac{\partial f_{1}}{\partial y_{n}}\Big|_{\mathbf{y}^{k}}(y_{n} - y_{n}^{k}) + \dots$$

$$f_{2}(\mathbf{y}) = f_{2}(\mathbf{y}^{k}) + \frac{\partial f_{2}}{\partial y_{1}}\Big|_{\mathbf{y}^{k}}(y_{1} - y_{1}^{k}) + \dots + \frac{\partial f_{2}}{\partial y_{n}}\Big|_{\mathbf{y}^{k}}(y_{n} - y_{n}^{k}) + \dots$$

$$\vdots$$

$$(2.2)$$

$$f_n(\mathbf{y}) = f_n(\mathbf{y}^k) + \frac{\partial f_n}{\partial y_1}\Big|_{\mathbf{y}^k} (y_1 - y_1^k) + \dots + \frac{\partial f_n}{\partial y_n}\Big|_{\mathbf{y}^k} (y_n - y_n^k) + \dots$$

With the assumption that the terms which contain higher order partial derivatives can be neglected, the Taylor expansion (2.2) can be written in terms of only the first order differences:

$$\mathbf{f}_{\mathbf{L}|\mathbf{y}^{\mathbf{k}}}(\mathbf{y}) = \mathbf{f}(\mathbf{y}^{\mathbf{k}}) + \mathbf{M}|_{\mathbf{y}^{\mathbf{k}}}(\mathbf{y} - \mathbf{y}^{\mathbf{k}})$$

(2.3)

The function  $\mathbf{f}_{L|\mathbf{y}^k}$  represents the local linearization of  $\mathbf{f}$  in the vicinity of  $\mathbf{y}^k$ . The matrix  $\mathbf{M}$  contains the first order partial derivatives of each component of the vector function  $\mathbf{f}$  and is called the *Jacobian* matrix of the system.

$$\mathbf{M}\big|_{\mathbf{y}} = \begin{bmatrix} \frac{\partial f_{1}}{\partial y_{1}} \big|_{\mathbf{y}} & \frac{\partial f_{1}}{\partial y_{2}} \big|_{\mathbf{y}} & \dots & \frac{\partial f_{1}}{\partial y_{n}} \big|_{\mathbf{y}} \\ \frac{\partial f_{1}}{\partial y_{1}} \big|_{\mathbf{y}} & \frac{\partial f_{1}}{\partial y_{2}} \big|_{\mathbf{y}} & \dots & \frac{\partial f_{1}}{\partial y_{n}} \big|_{\mathbf{y}} \\ \vdots & \vdots & & \vdots \\ \frac{\partial f_{n}}{\partial y_{1}} \big|_{\mathbf{y}} & \frac{\partial f_{n}}{\partial y_{2}} \big|_{\mathbf{y}} & \dots & \frac{\partial f_{n}}{\partial y_{n}} \big|_{\mathbf{y}} \end{bmatrix}$$

$$(2.4)$$

$\mathbf{y}^{\mathbf{k}+\mathbf{1}}$  is found as the formal solution of  $\mathbf{f}_{\mathbf{L}|\mathbf{y}^{\mathbf{k}}}(\mathbf{y}) = 0$ :

$$\mathbf{y}^{\mathbf{k}+\mathbf{1}} = \mathbf{y}^{\mathbf{k}} - \mathbf{M}^{-1}|_{\mathbf{y}^{\mathbf{k}}} \mathbf{f}(\mathbf{y}^{\mathbf{k}})$$

(2.5)

The solution (2.5) is not practical for computer manipulation because it involves the inversion of the Jacobian. A better way to find  $y^{k+1}$  is to consider the Newton-Raphson equation:

$$\mathbf{M}|_{\mathbf{y}^{\mathbf{k}}} \cdot \Delta \mathbf{y}^{\mathbf{k}} = -\mathbf{f}(\mathbf{y}^{\mathbf{k}}) \tag{2.6}$$

Using the LU-factorization method one solves (2.6) for the correction  $\Delta \mathbf{y}^{\mathbf{k}}$ . The result of the k-th iteration step becomes:

$$\mathbf{y}^{\mathbf{k}+\mathbf{1}} = \mathbf{y}^{\mathbf{k}} + \Delta \mathbf{y}^{\mathbf{k}} \tag{2.7}$$

Thus, one Newton-Raphson iteration step consists essentially of two actions:

- 1. solve the Newton-Raphson equation (2.6) using linear algebra methods, and

- 2. update the approximate solution according to (2.7).

The calculation of  $\mathbf{f}(\mathbf{y^k})$  requires virtually no effort once the constitutive equations and topological equations are known. By contrast, the calculation of the Jacobian matrix  $\mathbf{M}|_{\mathbf{y^k}}$  requires the existence of the partial derivatives  $\frac{\partial f_i}{\partial y_j}|_{\mathbf{y^k}}$  and then the capability of manipulating and calculating them. The Newton-Raphson procedure involves at each iteration step the *local linearization* of the function  $\mathbf{f}$  in the vicinity of  $\mathbf{y_k}$ .

#### 2.4 Locally linear systems

One important limitation of the classical Newton-Raphson algorithm as recognized above is that information about the system's Jacobian M is not directly embedded in the system function f. Overhead is added during the simulation process in order to make this information available.

A substantial simplification of the Newton-Raphson algorithm becomes possible if the constitutive equations of the system components are locally linear, i.e., inside each operating region the relation between stimuli and response is linear, where an operating region is defined by certain ranges for the terminal currents and branch voltages. The union of the operating regions has to cover the whole operating range of the component. When gathering the linear topological equations with the locally linear constitutive equations one obtains a piecewise linear system function  $\mathbf{f}_{PL}(\mathbf{x}, \mathbf{y})$ . For a specific global operating region l the system function is given by:

$$\mathbf{f}_{\mathbf{PL}}^{\mathbf{l}}(\mathbf{y}) = \mathbf{M}_{\mathbf{l}} \cdot \mathbf{y} - \mathbf{w}_{\mathbf{l}} - \mathbf{w}$$

(2.8)

The system matrix  $\mathbf{M}_l$  and the source vector  $\mathbf{w}_l$  are constant throughout a linear operating region l, but change with the operating region;  $\mathbf{w}$  is the independent source vector (here enters  $\mathbf{x}$ ).  $\mathbf{M}_l$  and  $\mathbf{w}_l$  are assembled from the system Kirchhoff current law and Kirchhoff voltage law and from the component piecewise linear constitutive equations.

The application of the Newton-Raphson algorithm to find the solution of  $\mathbf{f}_{PL}(\mathbf{y}) = 0$  follows the same main steps as before, but now with the additional advantage that during the iteration step k the Jacobian of the system is identical with the system matrix:

$$\mathbf{M}^{\mathbf{k}} = \frac{\partial \mathbf{f}_{\mathbf{PL}}}{\partial \mathbf{y}} = \mathbf{M}_{\mathbf{l}} \tag{2.9}$$

For a piecewise linear system the Jacobian is implicitly stored with the topological equations and the piecewise linear constitutive equations, and is updated at each iteration step together with the system matrix.

Let us consider in some detail iteration step k: starting from  $\mathbf{y}^{\mathbf{k}}$  with the representative point situated in a piecewise linear region l, solve the Newton-Raphson

equation which now reads

$$\mathbf{M}_{\mathbf{l}} \cdot \Delta \mathbf{y}^{\mathbf{k}} = -\mathbf{f}_{\mathbf{PL}}^{\mathbf{k}} \quad \text{with} \quad \mathbf{f}_{\mathbf{PL}}^{\mathbf{k}} = \mathbf{M}_{\mathbf{l}} \cdot \mathbf{y}^{\mathbf{k}} - \mathbf{w}_{\mathbf{l}}^{\mathbf{k}} - \mathbf{w}$$

(2.10)

and find out the correction  $\Delta y^k$ .

If the calculated next iteration point  $\hat{\mathbf{y}}^{k+1} = \mathbf{y}^k + \Delta \mathbf{y}^k$  stays within the same linear region l, then we are done:  $\hat{\mathbf{y}}^{k+1}$  is the exact solution of the piecewise linear equation system.

If  $\hat{\mathbf{y}}^{k+1}$  exceeds the limits of the current linear region, then the step has to be reduced by weighting  $\Delta \mathbf{y}^k$  with  $t^k < 1$ , such that the point

$$\mathbf{y}^{\mathbf{k}+\mathbf{1}} = \mathbf{y}^{\mathbf{k}} + t^k \cdot \Delta \mathbf{y}^{\mathbf{k}} \tag{2.11}$$

is on the border between the region l and a neighbor region l'. This is the result of the k-th iteration step.

The next iteration step starts from the neighboring linear region l' with  $\mathbf{y^{k+1}}$  as the starting point and is concerned with the solution of the updated Newton-Raphson equation:  $\mathbf{M_{l'}} \cdot \Delta \mathbf{y^{k+1}} = -\mathbf{f_{PL}^{k+1}}$ .  $\mathbf{M_{l'}}$  is the updated system matrix in the new linear region and  $\mathbf{f_{PL}^{k+1}}$  is the updated system function in the new linear region.

Where the general Newton-Raphson algorithm performs a local linearization on the system equation at each iteration step, the piecewise linear variant of the Newton-Raphson algorithm runs on an already locally linear equation. This means that for the piecewise linear case no extra information about the system Jacobian is needed, as the Jacobian is implicitly stored with the topological equations and the constitutive equations. The Newton-Raphson algorithm finds in the general form an approximate solution, while in the piecewise linear form it finds the exact solution of the equations; there is however the error due to the linearization during modeling.

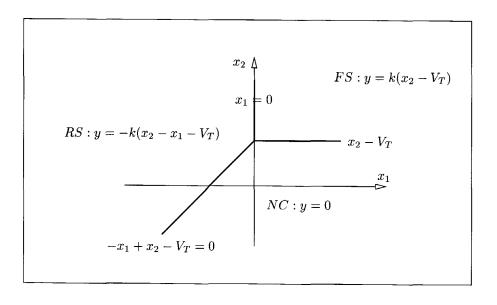

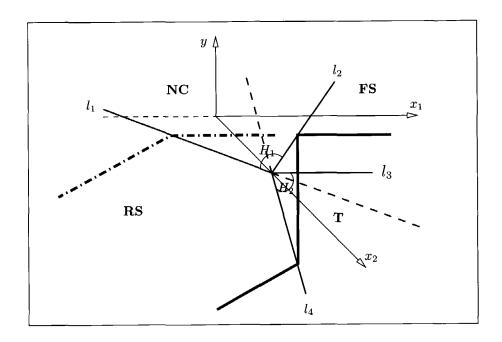

#### 2.5 A piecewise linear approach

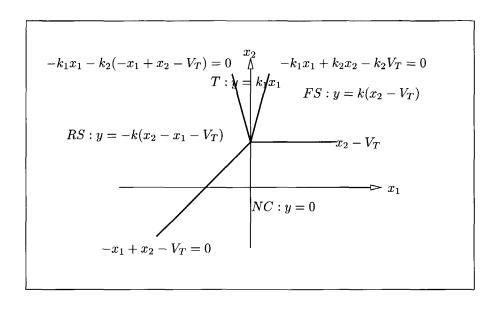

As in the general case (see Section 2.1) each circuit entity is described by a mapping from the space of input variables (stimuli) to the space of output variables (responses). The core idea of the PL concept is to approximate this application by a concatenation of linear segments. The input space is divided into a number

of regions: inside each region the output variables depend linearly on the input variables. Changing of region is reflected in changing coefficients in the linear dependency. The *linear* topological equations and the *linear* constitutive equations inside each region are combined with a *linear* description of the regions. Hyperplanes are used as boundaries for regions. In this way we obtain what is called *polytopes* - regions expressed in terms of linear equations. This technique based on a linear dependency inside each linearly characterized region is called the *piecewise linear technique*.

The piecewise linear modeling problem for a generic entity can be formulated in the following manner. Given:

- 1. a partition of the input space X into a set of adjacent convex polytopes  $P_i$ ,

- 2. a mapping  $\mathcal{F}$  from the input space  $\mathbf{X}$  to the output space  $\mathbf{Y}$  continuous along every boundary which separates the polytopes, and

- 3. a linear dependence of the output vector  ${\bf y}$  on the input vector  ${\bf x}$  inside each polytope  ${\bf P_i}$

find a global analytical representation for  $\mathcal{F}$  suitable for computer manipulation.

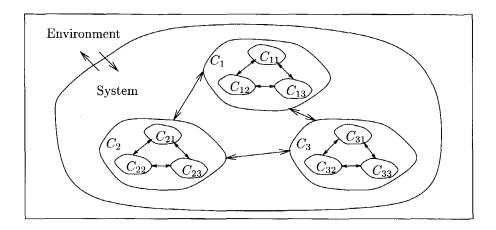

An elegant solution to this problem is the implicit global piecewise linear technique based on diode states [11], that we adopt in the remainder of this section. It is a mechanism to keep track of the operating region for the piecewise linear Newton-Raphson approach, with the aid of the so-called diode variables. The approach based on diode states emerged from a network perspective, with the ideal diode as representation for the basic nonlinearity. An ideal diode (see Figure 2.2a for notations and characteristic) operates in one of two states:

- conducting (any positive current implies a zero bias voltage), when it represents a closed connection between its terminals, or

- blocking (a zero current is prescribed for any reverse voltage), when it represents an open circuit between its terminals.

A circuit composed of linear components (sources and resistors) and ideal diodes, is suggested in Figure 2.2b. When the input is changed the *diodes* might switch *state* and the topology of the circuit changes accordingly. For each possible combination of diode states the circuit has a certain topology with linear components, and therefore a linear transfer function.

Figure 2.2: Ideal diode a) current-voltage convention and characteristic b) relation to a PL circuit

More precisely, each polytope  $P_i$  is associated with a diode state  $S_i$ . The state of the diodes depends (not necessarily uniquely) on the input. The output is a function of the input and the diode state:  $y = \mathcal{F}(x, S(x))$ . When x crosses the boundary from  $P_i$  to  $P_j$  the diode state changes from  $S_i$  to  $S_j$  and the coefficients of the linear mapping should change as well.

The problem can thus be decomposed into:

- 1. find a state S(x) of the diodes corresponding to the input vector, and

- 2. find the output vector  $\mathbf{y}$  by using the linear output mapping corresponding with the solution of  $\mathbf{S}(\mathbf{x})$ .

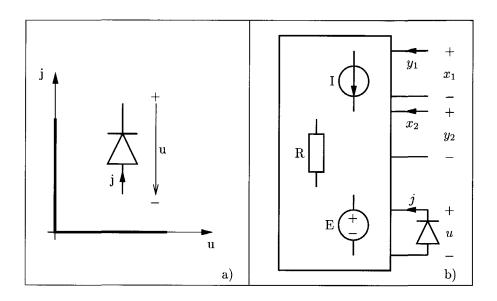

This formulation is called the **diode state model** of the piecewise linear system [12] and is represented in Figure 2.3. The diode state  $\bf S$  may be encoded with the diode vectors  $\bf u$  and  $\bf j$ . Diode vectors are orthogonal and nonnegative. The diode state  $\bf S$  becomes a function of diode variables  $\bf u$  and  $\bf j$ , and remains an implicit

Figure 2.3: Diode state model for a piecewise linear system

function of the input vector  $\mathbf{x}$ .

$$\begin{cases} \mathbf{S} = \mathbf{S}(\mathbf{u}, \mathbf{j}) & \text{with} \quad \mathbf{u} = \mathbf{u}(\mathbf{x}), \quad \mathbf{j} = \mathbf{j}(\mathbf{x}) \\ \mathbf{u}^{\mathbf{T}} \cdot \mathbf{j} = \mathbf{0}, \mathbf{u} \ge \mathbf{0}, \mathbf{j} \ge \mathbf{0} \end{cases}$$

(2.12)

The introduction of the additional variables  ${\bf u}$  and  ${\bf j}$  enables the compact analytical representation:

$$\mathbf{y} = \mathbf{A} \cdot \mathbf{x} + \mathbf{B} \cdot \mathbf{u} + \mathbf{f} \tag{2.13a}$$

$$\mathbf{j} = \mathbf{C} \cdot \mathbf{x} + \mathbf{D} \cdot \mathbf{u} + \mathbf{g} \tag{2.13b}$$

$$\mathbf{u}^{\mathbf{T}} \cdot \mathbf{j} = \mathbf{0}, \mathbf{u} \ge \mathbf{0}, \mathbf{j} \ge \mathbf{0} \tag{2.13c}$$

where **A**, **B**, **C**, and **D** are matrices and **f** and **g** are column vectors. This is the most general piecewise linear description and was proposed by Van Bokhoven [13].

Relation (2.13a) is called the *linear input-output mapping*, equation (2.13b) is the *diode state equation*, and the set (2.13c) represents the *complementary constraints*. Relations (2.13b) and (2.13c) form together the so called *linear complementarity problem*. This problem [14] has been identified in a broader context: for a given source vector  $\mathbf{q}$  find the orthogonal nonnegative vectors  $\mathbf{w}$  and  $\mathbf{z}$  that satisfy:

$\mathbf{w} = \mathbf{M} \cdot \mathbf{z} + \mathbf{q}.$

With  $\mathbf{x}$  in the polytope  $\mathbf{P}^*$ , for which  $\mathbf{u} = \mathbf{0}$ , the input-output relation reads simply:

$$\mathbf{y} = \mathbf{A} \cdot \mathbf{x} + \mathbf{f} \tag{2.14}$$

The description (2.13) is then called the *natural representation* for the specific polytope  $\mathbf{P}^*$ . When the input vector leaves that specific polytope  $\mathbf{P}^*$  at least one component of vector  $\mathbf{u}$ , say  $u_k$ , becomes positive and relation (2.14) is not valid anymore. However, the piecewise linear mapping (2.13a) is valid across the entire input space. If we now interchange  $j_k$  and  $u_k$  in relation (2.13b) - an operation called *pivoting* – and we transform (2.13a) to reflect this change, we obtain another natural representation valid in the newly entered polytope. This is the core idea of the so-called "path-following algorithms" for solving the linear complementarity problem. Various algorithms have been developed to solve the linear complementarity problem (see Appendix A).

In the representation (2.13) the diode state equation reflects the geometry of the input space. The hyperplanes are defined only in terms of the input variables. Such a hyperplane equation reads as  $C_{k*} \cdot x + g_k = 0$ . This description is suited when the input space is divided into polytopes by full hyperplanes only and the mapping is continuous over changing the polytope. In those cases the diode state equation (2.13b) is easily obtained by inclusion of hyperplane equations.

From a modeling point of view it may be more convenient to consider the input-output space for the boundary equations. In terms of input space variable we may end up with half-hyperplanes or piecewise hyperplanes. If the result is a full hyperplane in terms of input and output variables, then we can use a slightly modified version of (2.13):

$$\mathbf{0} = \mathbf{I} \cdot \mathbf{y} + \mathbf{A} \cdot \mathbf{x} + \mathbf{B} \cdot \mathbf{u} + \mathbf{f} \tag{2.15a}$$

$$\mathbf{j} = \mathbf{D} \cdot \mathbf{y} + \mathbf{C} \cdot \mathbf{x} + \mathbf{I} \cdot \mathbf{u} + \mathbf{g} \tag{2.15b}$$

$$\mathbf{u^T} \cdot \mathbf{j} = 0, \mathbf{u} \ge 0, \mathbf{j} \ge 0 \tag{2.15c}$$

In (2.15b) the diode state equation is written in the input-output space, or

in other words the boundary hyperplanes are defined in terms of both  $\mathbf{x}$  and  $\mathbf{y}$ . The equation of such a hyperplane is  $\mathbf{D}_{\mathbf{k}*} \cdot \mathbf{y} + \mathbf{C}_{\mathbf{k}*} \cdot \mathbf{x} + \mathbf{g}_{\mathbf{k}} = \mathbf{0}$ .  $j_k$  and  $u_k$  are the complementary variables supposed to change when the representative point in the  $\mathbf{x}$ - $\mathbf{y}$  space crosses this boundary.

### 2.6 One algorithm

Any network that can be modeled by linear components and ideal diodes, can be handled by simulators that can solve the ensuing linear complementarity problem. Once inside the polytope the problem is reduced to solving a set of linear equations. It is not important what level of abstraction has been modeled: the components can be switches, transistors, gates, etc. As long as they conceptually fit in the framework of (2.13), the same algorithm can be used to find an operating point that satisfies the constraints and the input-output mapping.

In that sense piecewise linear simulators can be considered level transparent, although the requirement to obtain suitable piecewise linear models for every non-linear component at every level should not be deemed simple and facile. Also, automatically "zooming" in and out by changing local levels is far from simple. But, once every component is represented in the framework at the adequate level of detail, the same simulation engine can do the job. Unlike methods with Newton-Raphson iterations in the kernel storage or calculating the Jacobian matrix is not necessary, and global convergence to an existing operating point is much better.

# Chapter 3

# Transistors in the limit

#### Contents

| 3.1 | Impact of velocity saturation      | 27 |

|-----|------------------------------------|----|

| 3.2 | Model equations                    | 29 |

| 3.3 | Scaling down                       | 34 |

| 3.4 | Saturated velocity                 | 38 |

| 3.5 | Piecewise linear transistor models | 40 |

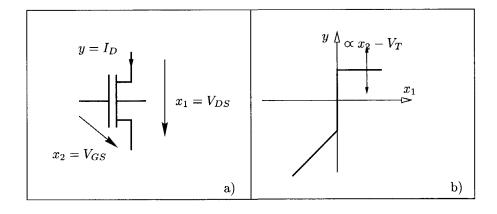

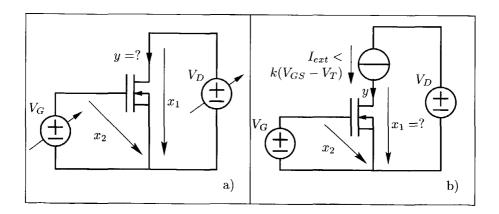

Any simulator for electronic circuits should be capable of including and handling amplifying devices, i.e., a signal imposed at the input of that device should appear amplified (or restored) at the output. This is the so-called *triode operation*, invented at the beginning of last century and catalyzing the creation of the largest industry ever during that century.

A triode has at least three terminals: an input terminal, the *gate*, an output terminal, the *drain*, and a common terminal, the *source*<sup>1</sup>. They come in two types, *n*-type and *p*-type triodes. The operational principle is to create and sustain mobile charge carriers in the current path between drain and source by bringing an opposite charge on the gate, close to that path. The number of carriers can be controlled by the amount of charge. Under the influence of an electric field created

<sup>&</sup>lt;sup>1</sup>The naming conventions depend on the triode realization: vacuum tubes have *grid*, *anode* and *cathode*, while bipolar junction transistors have *base*, *collector* and *emitter*.

by potential difference between drain and source, carriers can form a current between those terminals. In n-type triodes the carriers are predominantly negatively charged (electrons), while in p-type triodes they are positively charged. Triodes can be classified according by the way they prevent carriers from flowing into the gate [15].

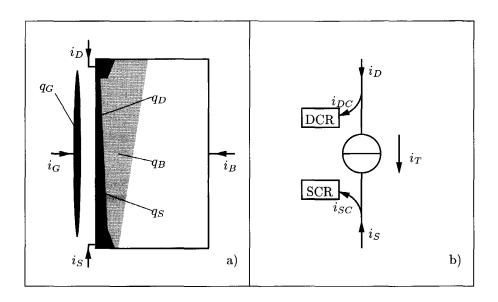

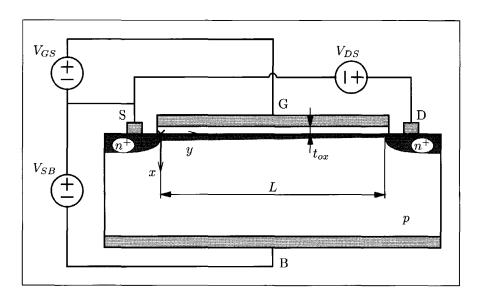

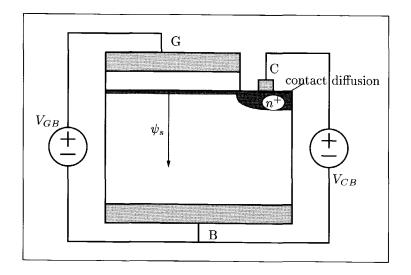

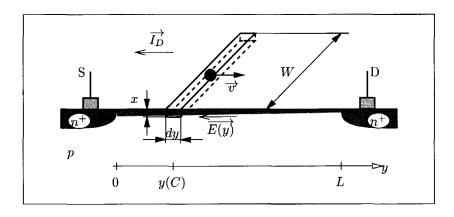

The discussion in this thesis is limited to triodes that are built by a three layer structure: a conducting gate, separated from an extrinsic semiconductor channel by a thin isolator. The well-established theory of these so-called *MOS-transistors* for relatively long distance between drain and source is summarized in Appendix B. Here we are interested in the behavior for relatively short distances between those terminals, but still long enough to maintain the same operational principles.

In the *n*-type MOS transistor positive charge should be moved to the gate electrode to attract negative mobile electrons in the channel. This requires a minimum amount of charge on the gate, but from then on, the more charge is on the gate, the more mobile electrons are available for the device current. Under ideal operating conditions the gate is perfectly isolated from the conducting channel and the positive charge moves in and out of the gate without losing any charge to elsewhere in the device. The gate charge attracts an equal amount of mobile charge of opposite sign, that can be used for current under the influence of the drain-source field, which cycles through the closed loop of load circuitry and power supply. The device current flows in a thin surface *sheet* of the silicon.

In a scaled-down technology the MOS transistor suffers from both short-channel and narrow-channel effects [16, 17]. Complex models, exhaustive in capturing the MOS transistor operation, are presented elsewhere in the literature [18]. Here we will focus on a modeling approach which is compact and still reflects the essential physical operation.

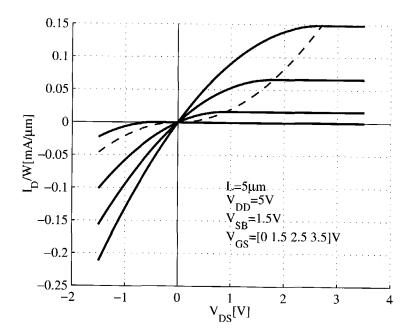

The channel length scales-down at a faster rate than the supply voltage. As a consequence, the longitudinal electric field in the channel increases with the technology generation and the charge carriers travel at a velocity closer to the saturation velocity. It is an hypothesis of this thesis that velocity saturation is the overwhelming effect on the current drive of transistor, an hypothesis that has to be tested.

If not further specified: "transistor" means n-type MOS-transistor. The names of the channel contacts, drain and source, is with reference to the circuit configuration, and not as usual, with reference to the flow direction of the carriers.

They are denoted D and S respectively. G denotes the gate. B stands for the bulk, the fourth terminal of the real device.

#### 3.1 Impact of velocity saturation

To study the relative impact of the drift velocity saturation effect [19] on transistor behavior we consider two modeling experiments.

1. Suppose that the charge carriers in the transistor channel are allowed to approach a higher saturation velocity than imposed by the actual material of the channel.

Figure 3.1: Current drive vs. saturation velocity  $(v_{sat} \approx 100000[m/s])$ .

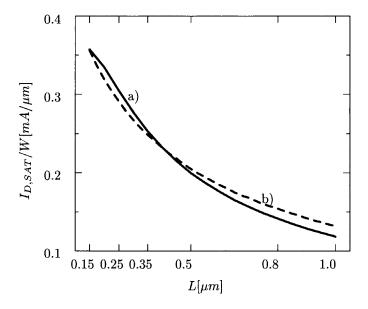

We would obtain this situation by increasing the saturation velocity parameter  $v_{sat}$  in the detailed deep submicron transistor model from [18]. The simulation results in Figure 3.1 show that the current drive  $I_{D,SAT}/W$  is affected by velocity saturation, and in such a way the smaller  $v_{sat}$  the smaller the current drive.

#### 2. We take two transistor models:

- the same detailed deep submicron transistor model, complete with all the effects which may have an influence on the current drive, including the velocity saturation effect, and

- the first-order charge sheet model enhanced with only the velocity saturation as short-channel effect.

Comparing the current drive  $I_{D,SAT}/W$  at various channel lengths L for both models (Figure 3.2) shows that the velocity saturation effect is dominant over other short-channel effects, in what concerns the current drive of a deep submicron transistor.

Figure 3.2: Current drive vs. channel length a) detailed model b) compact model

These two experiments show not only that velocity saturation has a significant effect on the transistor current drive, but that it is the dominant factor affecting the transistor current drive when the channel length gets shorter. We therefore

re-derive the model equations of the transistor, but not with constant mobility as in Appendix B, but with the commonly used dependency on the electrical field.

## 3.2 Model equations

In a channel with high longitudinal electric field the drift velocity  $(v_d)$  of the carriers no longer obeys the simple linear dependency expressed by:

$$|v_d| = \mu |E_y| = \mu \frac{d\psi_s}{dy} \cong \mu \frac{dV_{CS}}{dy}$$

for  $V_{DS} \ge 0$  (B.20a)

$$= -\mu \frac{d\psi_s}{dy} \cong -\mu \frac{dV_{CS}}{dy} \qquad \text{for } V_{DS} \leq 0$$

(B.20b)

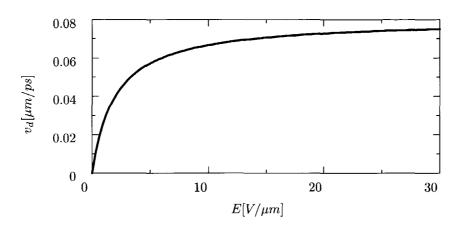

where C is an arbitrary point with strong inversion in the channel. As the electric field is increased,  $|v_d|$  exhibits a saturation tendency, i.e., there is a  $|v_d|_{max}$  barrier which cannot be passed regardless how strong the electric field. A commonly used empirical approximation [20] for the drift velocity is:

$$|v_d| = |v_d|_{max} \frac{|E|/|E_c|}{1 + |E|/|E_c|} = \mu \frac{|E|}{1 + |E|/|E_c|}$$

(3.1)

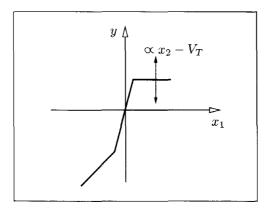

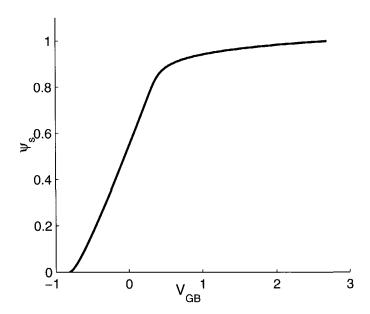

where  $\mu$  is the low field surface mobility of the carriers, |E| is the magnitude of the longitudinal electric field, and  $E_c = \frac{|v_d|_{max}}{\mu}$  is the critical field. The saturation of the drift velocity with the electric field as predicted by (3.1) is presented in Figure 3.3. The saturated drift velocity is given by:

$$v_{sat} = |v_d|_{max} = \mu |E_c| \tag{3.2}$$

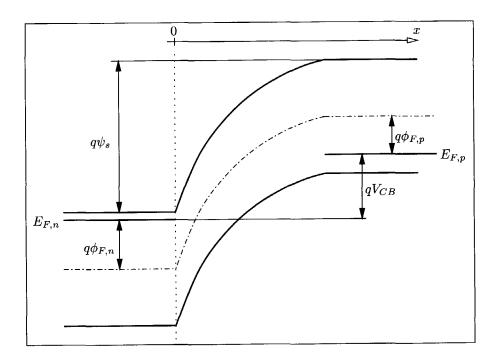

As in the long-channel case we state that the current conduction through the channel is possible if at least one end of the channel is in strong inversion.

The transistor is said to be in forward conduction when the drain is biased to a higher potential than the source, i.e.,  $V_{DS} \geq 0$ . Normal operation requires that both contact-to-substrate  $n^+p$  junctions to be reverse biased:  $V_{SB} \geq 0$  and  $V_{DB} \geq 0$ .

When both ends of the channel are in strong inversion (B.19) for forward

Figure 3.3: Drift velocity vs. longitudinal electric field

conduction with velocity saturation effects becomes:

$$I_D = W|Q_I|\mu \frac{|E|}{1 + |E|/|E_c|}, \text{ with } |E| \cong \frac{dV_{CS}}{dy} \text{ for } V_{DS} \ge 0$$

(3.3)

After some manipulations we find:

$$I_D dy = \left(\mu W|Q_I| - \frac{I_D}{E_c}\right) dV_{CS}(y) \tag{3.4}$$

With the inversion layer charge given by:

$$Q_I(y) = -C_{ox}(V_{GS} - V_T(V_{SB}) - (1 + \delta)V_{CS}(y))$$

(B.22)

the drain current in forward triode operation for a short-channel transistor becomes:

$$I_{D} = \mu \frac{W}{L} C_{ox} \frac{(V_{GS} - V_{T})V_{DS} - (1 + \delta)\frac{V_{DS}^{2}}{2}}{1 + \frac{V_{DS}}{V_{0}}} \quad \text{for } V_{DS} \ge 0 \text{ and } V_{DS} \le V_{DS, SAT}$$

$$(3.5)$$

where  $V_0 = \frac{Lv_{sat}}{\mu}$  is a parameter which accounts for velocity saturation effects. Expression (3.5) is valid as long as  $I_D$  keeps increasing with  $V_{DS}$ , i.e., for  $V_{DS}$  below a certain value  $V_{DS, SAT}$ . The validity limit of (3.5) is found by setting the first derivative of the drain current with respect to  $V_{GS}$  equal to zero:

$$V_{GS} = V_T + (1+\delta)V_{DS} + \frac{1+\delta V_{DS}^2}{V_0}$$

or (3.6a)

$$V_{DS, SAT} = V_0 \left( \sqrt{1 + \frac{2}{1 + \delta} \frac{V_{GS} - V_T}{V_0}} - 1 \right)$$

(3.6b)

The value of the saturation current is found to be:

$$I_{D, SAT} = \mu \frac{W}{L} C_{ox} \frac{1+\delta}{2} V_{DS, SAT}^2$$

(3.7)

Equation (3.6a) can be seen as the separation between the forward saturation and the forward triode regions of a short-channel transistor. The  $V_{DS}$  value at which the current saturation occurs for a given  $V_{GS}$  is lower than the value in the long channel situation.

Reverse conduction is possible when  $V_{SB}$  is assigned a positive value. Similar to forward conduction, reverse conduction of a short channel transistor shows triode and saturation operating regions when  $V_{DS}$  is decreased from zero down to a sufficiently large negative value, with  $V_{GS}$  fixed above the threshold voltage. The triode covers a part of the situation with strong inversion at both ends of the channel, namely the part with small  $V_{DS}$  magnitudes. The saturation covers the part with higher  $V_{DS}$ . For  $V_{GS} > V_T$  the source end of the channel is in strong inversion, as appears from the discussion preceding (B.16) about the threshold voltage. Expression (B.22) for the inversion layer charge at the strong inverted points C in the channel is also valid for  $V_{CS} < 0$ . For reverse drain-to-source bias  $V_{DS} < 0$  the drain end of the channel will be in deeper strong inversion than the source end. For reverse triode conduction with velocity saturation effects expression (B.19) becomes:

$$I_D = -W|Q_I|\mu \frac{|E|}{1 + |E|/|E_c|}$$

with  $|E| \cong -\frac{dV_{CS}}{dy}$  for  $V_{DS} \le 0$  (3.8)

Integrating over the channel length one may find the drain current in reverse triode

operation for a short-channel transistor:

$$I_D = \mu \frac{W}{L} C_{ox} \frac{\left( (V_{GS} - V_T) V_{DS} - (1 + \delta) \frac{V_{DS}^2}{2} \right)}{1 - \frac{V_{DS}}{V_0}}$$

(3.9)

The validity of (3.9) extends up to the separation between reverse triode and reverse saturation ( $V_{DS} \leq 0$  and  $V_{DS} \geq -V_{SD, SAT}$ ). In the ( $V_{SD}, V_{GD}$ ) plane the separation equation is:

$$V_{GD} = V_T(V_{DB}) + (1+\delta)V_{SD} + \frac{1+\delta V_{SD}^2}{V_0}$$

(3.10)

$V_{SD, SAT}$  is found as the solution of (3.10).  $V_T(V_{DB})$  defines the onset of the strong inversion at the drain end relative to  $V_{GD}$ . According to (B.16),  $V_T(V_{DB})$  relates to  $V_T(V_{SB})$  by

$$V_T(V_{DB}) = V_T(V_{SB}) + \delta V_{DS} \tag{3.11}$$

and the expression for  $V_{SD, SAT}$  becomes:

$$V_{SD, SAT} = V_0 \left( \sqrt{1 + \frac{2}{1+\delta} \frac{V_{GS} - V_T - (1+\delta)V_{DS}}{V_0}} - 1 \right)$$

(3.12)

The separation equation (3.10) between reverse triode and reverse saturation may be rewritten in the  $(V_{DS}, V_{GS})$  plane as:

$$V_{GS} = V_T + \frac{1 + \delta V_{DS}^2}{V_0}$$

(3.13)

For  $V_{DS} < -V_{SD,\;SAT}$  the transistor is in reverse saturation and the drain current is given by:

$$I_{D, SAT}^{REV} = -\mu \frac{W}{L} C_{ox} \frac{1+\delta}{2} V_{SD, SAT}^2$$

(3.14)

For a short channel transistor there are two flavors of reverse conduction, depending on the  $V_{GS}$  magnitude: (1) if  $V_{GS} > V_T$  first reverse triode and then

| Operating region   | Operating region   Delimitation in the $(V_{DS}, V_{GS})$ plane                                                                   | Drain current expression                                                                                                   |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                    | 1 (2)                                                                                                                             | 1                                                                                                                          |

| Forward saturation | $V_{DS} \ge 0$ and $V_{GS} \ge V_T$ and $V_{GS} \le V_T + (1+\delta)V_{DS} + \frac{1+\delta V_{DS}^2}{2V_0}$                      | $I_D = \mu \frac{W}{L} C_{ox} \frac{1+\delta}{2} V_{DS, SAT}^2$                                                            |

| Forward triode     | $V_{DS} \ge 0$ and $V_{GS} \ge V_T$ and $V_{GS} \ge V_T + (1+\delta)V_{DS} + \frac{1+\delta V_{DS}^2}{2V_0}$                      | $I_{D} = \mu \frac{W}{L} C_{ox} \frac{(V_{GS} - V_{T})V_{DS} - \frac{1 + \delta}{2} V_{DS}^{2}}{1 + \frac{V_{DS}}{V_{0}}}$ |

| Reverse triode     | $V_{DS} \le 0 \text{ and } V_{GS} \ge V_T + (1+\delta)V_{DS} \text{ and } V_{GS} \ge V_T + \frac{1+\delta}{2} \frac{V_D^2}{V_0}$  | $I_{D} = \mu \frac{W}{L} C_{ox} \frac{(V_{GS} - V_{T})V_{DS} - \frac{1 + \delta}{2} V_{DS}^{2}}{1 - \frac{V_{DS}}{V_{o}}}$ |

| Reverse saturation | $V_{DS} \le 0 \text{ and } V_{GS} \ge V_T + (1+\delta)V_{DS} \text{ and}$ $V_{GS} \le V_T + \frac{1+\delta}{2} \frac{V_D^2}{V_0}$ | $I_D = -\mu \frac{W}{L} C_{ox} \frac{1+\delta}{2} V_{SD, SAT}^2$                                                           |

| Nonconducting      | $V_{GS} \le V_T$ and $V_{GS} \le V_T + (1+\delta)V_{DS}$                                                                          | $I_D = 0$                                                                                                                  |

$$V_{DS,\,SAT} = V_0 \bigg( \sqrt{1 + \frac{2}{1 + \delta} \frac{V_{GS} - V_T}{V_0}} - 1 \bigg), \ V_{SD,\,SAT} = V_0 \bigg( \sqrt{1 + \frac{2}{1 + \delta} \frac{V_{GS} - V_T - (1 + \delta)V_{DS}}{V_0}} - 1 \bigg), \ \text{and} \ V_T = V_T (V_{SB}).$$

Table 3.1: Velocity saturation effect on the large signal operation of a short channel transistor. Operating region delimitations in the  $(V_{DS}, V_{GS})$  plane and expressions for the drain current.

reverse saturation is encountered when decreasing  $V_{DS}$  from zero down to negative values, and (2) if  $V_{GS} < V_T$  first non-conduction and than reverse saturation is encountered for a similar excursion of  $V_{DS}$ .

Table 3.1 presents a summary of the equations derived in this section.

### 3.3 Scaling down

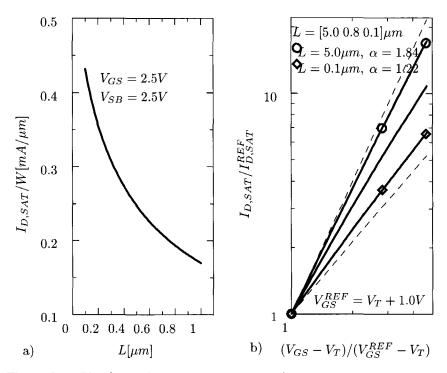

In Section 3.1 we showed the dramatic impact of velocity saturation on the saturation current when devices get very short, and consequently  $V_0$  very small. Figure 3.2 showed the increase in current drive capability with shorter channel length, which is repeated in Figure 3.4a. Other effects can, of course, be read from the relations (3.6b) and (3.7), but one aspect becomes very explicit if we look at the mathematical limit of the latter equation:

$$\lim_{V_0 \to 0} I_{D, SAT} = W v_{sat} C_{ox} (V_{GS} - V_T). \tag{3.15}$$

The quadratic dependence of the saturation current on  $V_{GS} - V_T$  observed (and derived) for long-channel transistors, supposedly changes into a linear dependence when the channel is short. This can already be observed with devices for  $V_{GS} > 2V_T$  that are still  $1\mu m$ .

A semi-empirical expression has been proposed in [21] to capture that phenomenon. It is the so-called  $\alpha$ -power law for the drain saturation current:

$$I_{D, SAT} \propto (V_{GS} - V_T)^{\alpha}. \tag{3.16}$$

The drain saturation current is considered proportional to the  $\alpha$ -power of the gate drive  $V_{GS} - V_T$ , where both,  $\alpha$  and the proportionality constant, depend on L. This implies for a given length a linear relation between the logarithm of the relative saturation current and the logarithm of the relative gate voltage above the threshold:

$$log \frac{I_{D, SAT}}{I_{D, SAT}^{REF}} = \alpha log \frac{V_{GS} - V_T}{V_{GS}^{REF} - V_T}.$$

(3.17)

This makes it easy to obtain evidence for the validity of the formula (3.16), and to establish the value of  $\alpha$  graphically, and observe how it evolves with decreasing channel length. The latter is presented in Figure 3.4b where the slope of the charac-

teristic on a log-log plot equals  $\alpha$ : when scaling a long channel down to a very-short one, the  $\alpha$  coefficient moves from two towards one.

Figure 3.4: The forward saturation current: a) current drive improvement with down-scaling b) variation of the  $\alpha$  coefficient with the channel length. The extreme cases of a long ( $\alpha = 2.0$ ) and short ( $\alpha = 1.0$ ) channel are given with thin dashed lines.

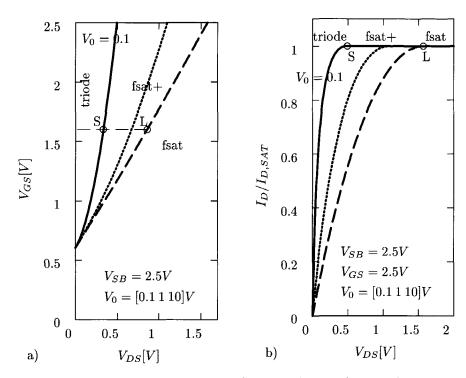

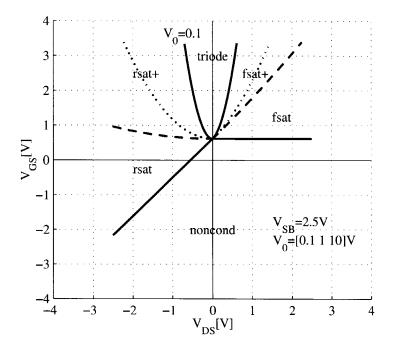

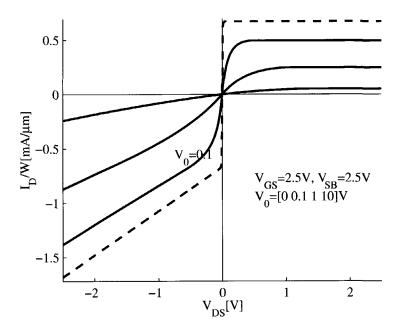

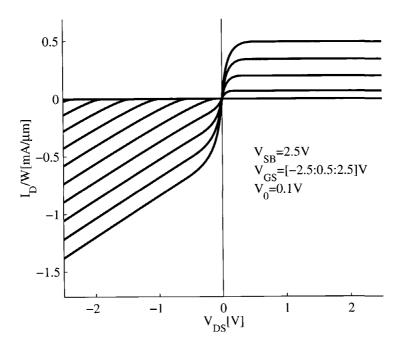

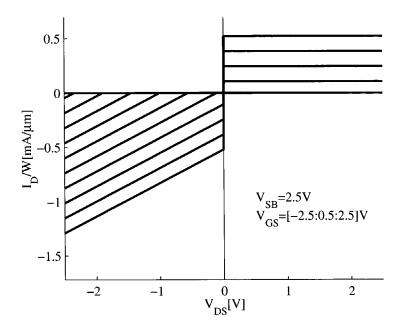

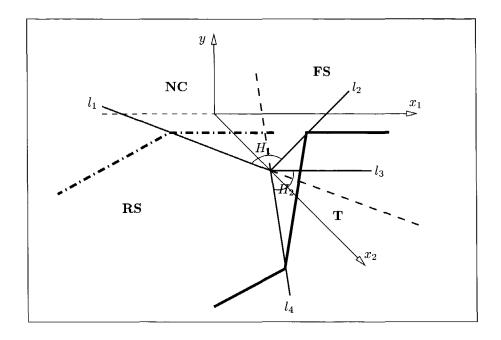

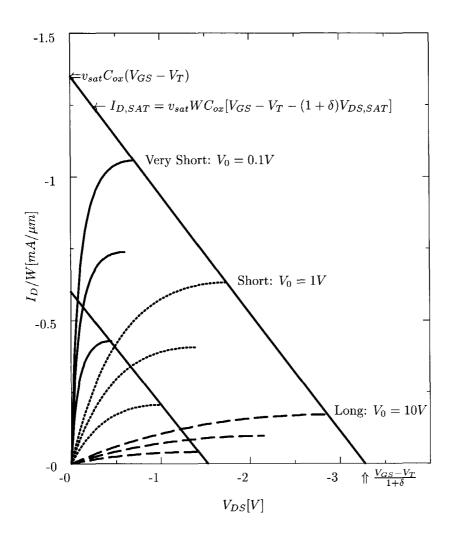

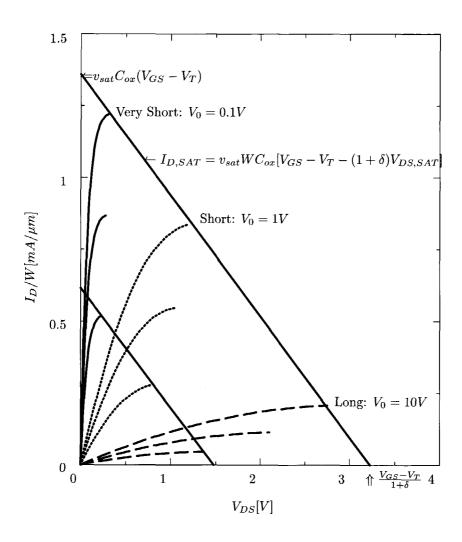

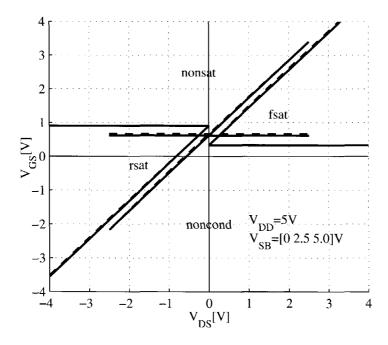

Yet another aspect can be uncovered by the study of Figure 3.5 where the operating regions of forward conduction are given in the  $(V_{DS}, V_{GS})$  plane next to  $I_D$  vs.  $V_{DS}$  characteristic. In the  $(V_{DS}, V_{GS})$  plane we show the separation line between the forward saturation and triode operating regions for three values of the  $V_0$  parameter, 0.1V, 1V, and 10V, values which correspond to a very-short, short, and long channel, respectively. Note the relative positions of point S and of point L, to see that in the case of shorter channels the current saturates at smaller  $V_{DS, SAT}$ . fsat+ denotes the region with the additional pairs  $(V_{GS}, V_{DS})$  for short-channel devices as compared with the long-channel device. In the  $I_D$  vs.  $V_{DS}$  plane we see that the onset of saturation occurs the earlier the shorter the channel length.

All operating regions are considered in Figure 3.6, including reverse conduc-

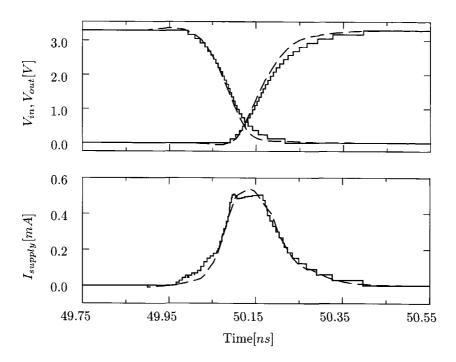

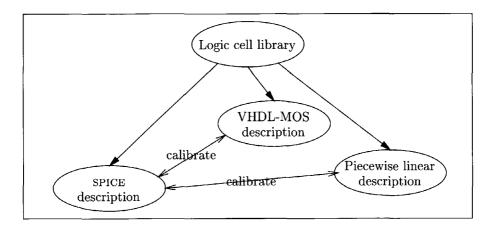

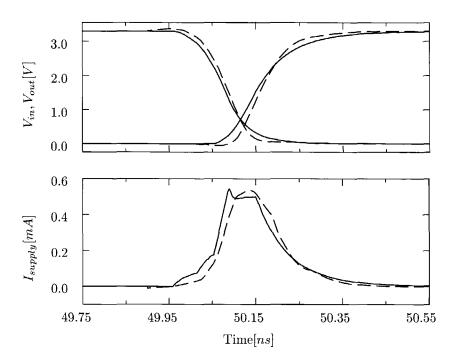

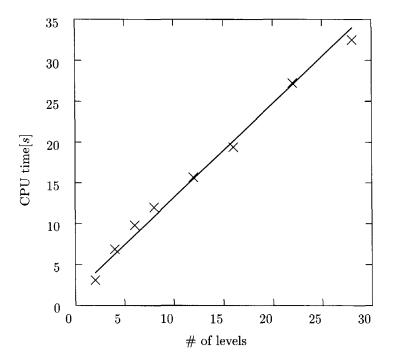

Figure 3.5: Forward conduction for long  $(V_0 = 10V)$ , short  $(V_0 = 1V)$  and very short  $(V_0 = 0.1V)$  devices with dashed, dotted and full lines respectively: a) boundary between triode and saturation b)  $I_D$  vs.  $V_{DS}$  characteristic