A 16-Channel CMOS Reconfigurable Recording Unit for Simultaneous In-Vitro Microelectrode Array (MEA) and Current-Clamp (CC) Measurements

## Asli Yelkenci

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Tuesday October 27, 2020 at 14:00.

Student number: 4749618

Project duration: Summer, 2018 – October 27, 2020 Thesis committee: Prof. Wouter Serdijn, TU Delft

Dr. Marco Spirito TU Delft

Dr. Virgilio Valente, TU Delft and Ryerson University, ON, CA

This thesis is confidential and cannot be made public until 31 December 2022.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## **Preface**

It was one of the happiest days of my life when I had been accepted by TU Delft as a master student, and now, I can literally see the reason of feeling such a happiness. It has been a long, yet enriching road for me, and I have met a lot of inspiring people along the way. First of all, I would like to thank Virgilio Valente not only for his continuous guidance on the project, but also for his kind and supportive approach all the time. Without his continuous help, this thesis would not have happened. I cannot express my gratitude enough to him for the last 2 years.

I also would like to express my sincere appreciation to Prof. Wouter Serdijn for participating in the committee, and being such a great head of Section: Bioelectronics. I believe that all of us feels like belonging to our section, and you make this happen.

I would like to thank all members of Bioelectronics section for their kind personalities, and joyful conversations during coffee breaks. I cannot name all of them here, since we are very big group fortunately, but I have to express my appreciation from bottom of my heart to Ronaldo Ponte for his great support in the project, and his open-mind and kind personality. And, thank you very much to Brian and Shengjie to make our office fun and comfortable place.

Last but not least for sure, I would like to express my deepest gratitude to my dear friends. Thank you very much, Andrea, Ata, Chris, Erdi, Hazal, Oguz and Sevilay. Even in the toughest days, I did not feel like I am doing this alone. You know that it means world to me.

I want to finish my acknowledgement with the life-altering quote for me:

The credit belongs to the woman who is actually in the arena, whose face is marred by dust and sweat and blood.

If she fails, at least fails while daring greatly, so that her place shall never be with those cold and timid souls who neither know victory nor defeat.

Asli Yelkenci Delft, October 2020

### **Abstract**

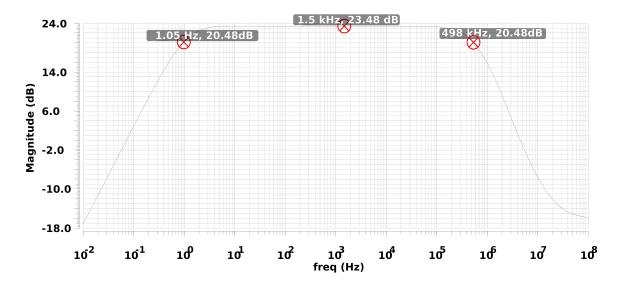

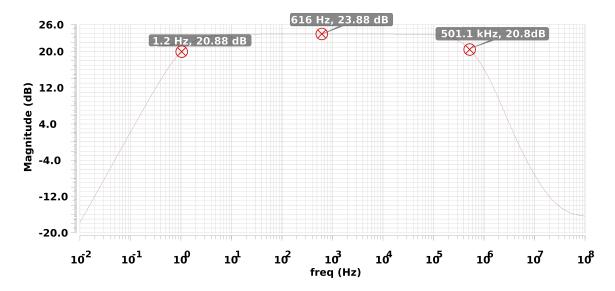

In-vitro cell culturing technique is widely used in many branches of science such as in neuroscience and cardiology to investigate the dynamics of large population of cells. Cultured cells can be studied by means of two fundamental recording techniques that are intracellular and extracellular recordings. Patch-clamp technique is the gold standard of high-fidelity action potentials (APs) and synaptic potentials of an individual cell. However, patch-clamp method suffers from very poor scalability. Approximately only 10 cells can be studied per day by experienced personnel working on a bulky and expensive setup. Microelectrode arrays (MEAs) have been proposed to perform multi-site and high-throughput extracellular recordings. Although MEA technology is utilized to understand network dynamics of large population of cells, MEA electrodes lack intracellular access to cell membrane which results in highly-attenuated potentials. Thus, MEA electrodes are only capable of recording action potentials (APs), and they are completely blind to synaptic events. Recent studies report that APs and synaptic potentials of an individual cell play a role in an increase in network activities as well as extracellular field potentials can induce a single-cell activity. Concurrent high throughput patch-clamp and MEA measurements are needed to gain insight into correlation between single-cell and network dynamics. The thesis project presents the design of 16-channel dual-mode recording unit for simultaneous measurements of intracellular and extracellular activities. The recording channel consists of capacitively-coupled instrumentation amplifier (CCIA) to reject DC offset of electrodes and unary-weighted current-steering DAC for stimulation of cells. The ratio of CCIA capacitors defines the gain of the amplifier, and the capacitors with MOS-based pseudo-resistors determine the low-frequency cut-off frequency. Single-stage single-ended 5T operational transconductance amplifier (OTA) is implemented in the core of CCIA. The unit current source of 4-bit thermometer-coded DAC copies 100 pA current from the reference and is localized in each channel. The injected current is increased by activating the adjacent unit current sources, and total current can reach to 1.6 nA. The reconfigurable recording channel has been designed in standard 0.18  $\mu$ m CMOS technology. By post-layout simulations, the gain of the amplifier equals to 23.5 dB. The input-referred noise of the channel is 8.1  $\mu V_{rms}$  in the frequency band ranging from 1.05 Hz to 10 kHz with NEF of 6.2. The power consumption of each individual recording unit is 7.18  $\mu$ W. Each reconfigurable channel occupies 0.021 mm<sup>2</sup> area on a die. This thesis projects integrates dual-mode functionality which opens a door to high-throughput multi-site intracellular and extracellular recordings for further understanding of correlation between single-cell activity and network dynamics of cells.

# Contents

| ostract                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction  1.1 State-of-the-Art in Patch Clamp and MEA Technologies               | 1<br>6<br>8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2 Digital Control Unit                                                             | 13<br>13<br>15<br>16<br>25<br>30<br>34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.2 AC Simulations          3.3 Noise Simulations          3.4 Transient Simulations | 37<br>39<br>41<br>43<br>46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Discussion                                                                           | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Conclusion 5.1 Future Work and Recommendations                                       | 57<br>58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Appendix                                                                             | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bliography                                                                           | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                      | 1.1 State-of-the-Art in Patch Clamp and MEA Technologies. 1.2 Problem Statement.  Proposed Architecture and Circuit Design 2.1 System Level Architecture 2.2 Digital Control Unit 2.3 Recording Channel. 2.3.1 5T Operational Transconductance Amplifier (5T-OTA) Design 2.3.2 Unary-Weighted Current-Steering DAC Design 2.3.3 Pseudo-Resistor Elements 2.3.4 CCIA Capacitors  Results 3.1 DC Simulations 3.2 AC Simulations 3.3 Noise Simulations 3.4 Transient Simulations 3.5 Statistical Results  Discussion  Conclusion 5.1 Future Work and Recommendations  Appendix |

1

## Introduction

In-vitro cell culturing is an essential method to study large populations of cells [1]. In-vitro cell modelling systems are widely used in neuroscience to understand dynamics of neural networks [2]. For example, the morphology of the cells and different aspects of brain-functioning are enabled to be studied with in-vitro cell cultures [1]. Also, impact of added chemicals such as drugs or toxicants to cells can be investigated by means of in-vitro cell culturing technique [1]-[3]. The investigation of cultured cells can be done by 2 fundamentally different techniques: 1) intracellular recordings, and 2) extracellular recordings [4].

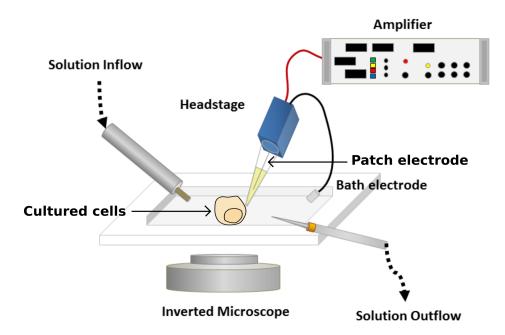

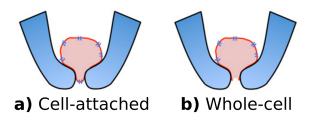

Intracellular recordings of electrogenic cells such as heart cells and neurons, carry tremendous importance to understand how a human body functions. The patch clamp technique is widely used in order to perform measurements of intracellular electrical activity of electrogenic cells. Fig. 1.1 shows the representation of how patch clamp technique is applied on cultured cells. The patch clamp method was first introduced by Neher and Sakmann in 1970s [5], and it is still considered the gold standard to perform intracellular recordings [6],[7],[8] [9]. The patch electrode is brought in close contact with the cell membrane, and a tight seal is formed between electrode and cell. The resistance between electrode and cell must be in the range of gigaohms to guarantee high-fidelity recording [10]. The resistance in gigaohms range provides good isolation of cell membrane. Also, leakage current is highly reduced by means of good coupling between cell and electrode. Thus, the resulting intracellular recording provides single-channel activities such as action potentials (APs), subhthreshold post-synaptic potentials (PSPs), and membrane oscillations [11] in real-time and with ultra-high resolution (in the order of 1 pA)[12].

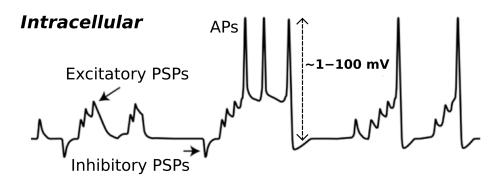

An AP is a rapid voltage change in cell membrane from -70 mV to 30 mV because of changes of ion concentrations (Na<sup>+</sup>, K<sup>+</sup>) causing depolarization and hyperpolarization across the membrane. This 100 mV change in cell membrane because of an AP can be recorded with by patch-clamping (see Fig. 1.2). Moreover, subthreshold events such as excitatory and inhibitory PSPs are only accessible when cells are examined intracellularly. Excitatory and inhibitory PSPs play an important role in cell electrophysiology. For example, a neuron only fires when its membrane exceeds a certain threshold voltage (around -50 mV). Excitatory PSPs increase the likelihood of a neuron to generate APs since excitatory PSPs contribute depolarizing of the cells, i.e. increasing the cell membrane voltage (making it less negative voltage).

1. Introduction

**Figure 1.1:** Representation of how patch clamp experiment is implemented (Adapted from [13].

On the contrary, inhibitory PSPs cause hyperpolarization that results in more negative membrane voltages. As a consequence of a decrease in membrane voltage, the neuron becomes less likely to fire an AP [14]. Excitatory and inhibitory PSPs with APs are highlighted in Fig. 1.2 [15].

**Figure 1.2:** Intracellular recordings obtained by patch clamping (Adapted from [15])

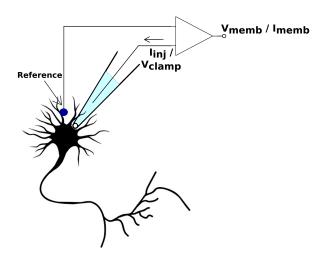

In addition, the patch clamp method enables simultaneous voltage- or current-clamp stimulation of the cells. In current-clamp experiment, a known current  $(I_{inj})$  is applied to the cell through the patch pipette inside electrolyte solution (see Fig 1.3). The resulting membrane voltage  $(V_{memb})$  is measured by means of an amplifier which is connected to the pipette. The current-clamp technique is used to understand how the cell responds in voltages (such as APs) to a current stimuli. The voltage-clamp experiment is performed by applying a known voltage  $(V_{clamp})$  to the membrane, and the current flowing through the membrane  $(I_{memb})$  is measured. By means of voltage-clamp experiment, concentration of the voltage-sensitive

ion channels can be determined. These results are very useful for pharmaceutical applications such as drug discovery [16].

**Figure 1.3:** A neuron and patch pipette filled with electrolyte solution and an electrode connected to an amplifier. (Picture of neuron is taken from [17])

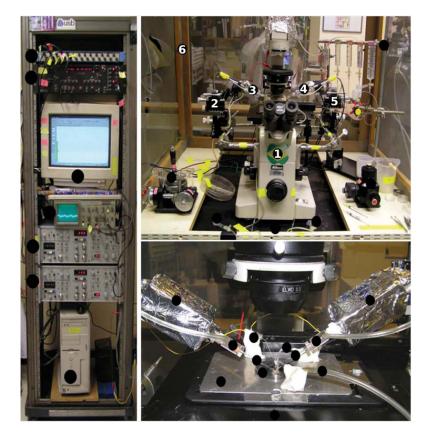

Although patch clamp technique offers nonesuch information about excitable cells and how they function, it suffers from considerably poor scalability. It has been reported that only 12 patch neuron recordings have been executed in parallel so far [18]. In addition, skilful personnel have to be trained to perform patch clamp experiments on a bothersome work station which mainly contains micromanipulators, optical microscope on a vibration-free table and a Faraday cage [6]. Fig. 1.4 shows a patch clamp work station which contains aforementioned tools [19].

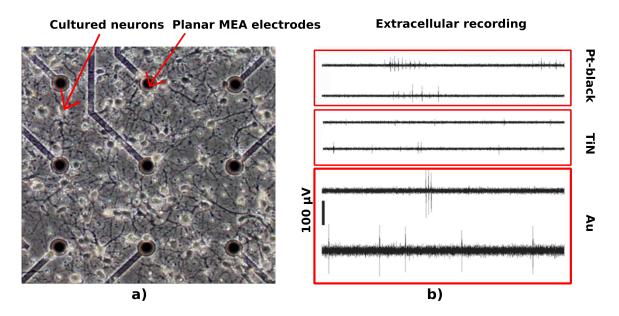

Microelectrode array (MEA) technology has been proposed as an alternative cell study technique in 1972 [20] for the first time as passive planar-type electrodes. Since then, the technology is being used for in-vitro extracellular recordings of electrical activities of cultured excitable cells [21–27]. Planar MEA electrodes are usually fabricated on a glass wafer, and they are usually made of nontoxic metals such as gold (Au), iridium (Ir), platinum (Pt) or titanium nitride (TiN)[28]. They are relatively easy-to-fabricate because they use conventional photolithography techniques to pattern the electrodes on a silicon wafer [15]. An example of planar-MEA electrodes, and recorded signals from cultured neurons by means of metal electrodes are given in Fig. 1.5.

The extracellular recording by means of planar MEA electrodes are done in a non-invasive manner in contrast to patch-clamping. Therefore, long-term measurements are enabled with MEA technology. Moreover, multi-site recording is possible when MEA electrodes are used for recording which opens a door to have better understanding on network dynamics [4]. Also, MEA technology provides higher throughput than patch-clamping technique, since 60 electrodes can be easily fabricated on silicon wafer. However, because of a need to interconnect each passive electrode to the pads of a wafer, there is a certain limit of number of electrodes that can be integrated on silicon [29]. Also, MEA electrodes are completely blind to synaptic events shown in Fig. 1.2 [15]. Planar-MEA electrodes are only capable of recording APs as spikes (see Fig. 1.5). As it can be seen from Fig. 1.5, the recorded AP signals are in around

4 1. Introduction

**Figure 1.4:** A patch clamp work station. (1) Inverted microscope. 2-5) Micromanipulators. (6) Faraday cage. Adapted from [19]

100  $\mu$ V range in amplitude. Table 1.1 summarizes the amplitude and frequency ranges of extracellular and intracellular activities occurring within a neuron [14, 30].

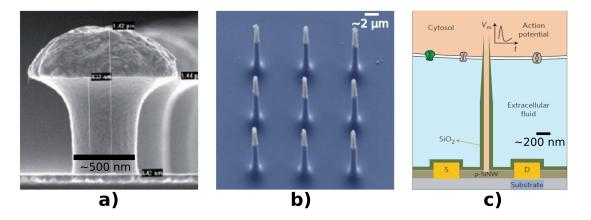

3D micro- or nano-electrode arrays were introduced for intracellular recordings with high-spatial resolution [11, 31–34]. Some of them, e.g. gold mushroom-shaped microelectrodes provides in-cell recordings of subthreshold and APs from single-neuron (see Fig. 1.6a.) However, an external circuitry was used to record the signals [11]. This makes the 3D-MEA system dependant on the performance of external components that are not designated and optimized for the electrodes. Vertical nanowire electrode arrays (VNEAs) were proposed as a scalable platform for intracellular recording (see Fig. 1.6b.)[34]. However, subthreshold events could not be recorded by VNEAs until the recording electronics with current- and voltage-clamp capability are integrated on the same platform with the electrodes [35]. The reason can be

**Table 1.1**

| Amplitude and Frequency Summary Table of Electrical Activities of Cells |                                      |                 |                 |  |  |  |  |

|-------------------------------------------------------------------------|--------------------------------------|-----------------|-----------------|--|--|--|--|

| Features                                                                | tures Extracellular Subthreshold APs |                 |                 |  |  |  |  |

| Amplitude                                                               | 10-1000 μV                           | 1-4 mV          | 1-100 mV        |  |  |  |  |

| Frequency                                                               | 0.1 Hz- 10 kHz                       | 300 Hz - 10 kHz | 300 Hz - 10 kHz |  |  |  |  |

**Figure 1.5:** An example of planar MEA electrodes and extracellular recordings. a) Planar-type MEA electrodes. b) Extracellular recordings of cultured neurons from Pt-black, TiN, and Au electrodes. (Taken from [2])

explained by the intrinsic high impedance of such small electrodes lowers the signal-to-noise ratio (SNR). Nanotube field-effect transistors (nano-FETs) are also offered to provide intracellular access to cells ((see Fig. 1.6c.)[31]. A considerably high force (> 1 nN) had to be applied to nano-FETs to penetrate cell membrane. However, this force caused cell membrane to be compressed, and only APs were recorded by means of nano-FETs. In addition to not achieving high-resolution in recording, some of 3D-MEAs also suffer from complex microfabrication steps such as focused ion beam (FIB) deposition or electron beam lithography which make them hard-to-scale [15].

**Figure 1.6:** 3D-MEA electrode examples a) Gold mushroom-shaped MEAs [11] b) Vertical nanowire arrays (VNEAs) [34]. c) Intracellular nanotube field-effect transistor (FET) (Taken from [31])

6 1. Introduction

Table of Performance Comparison State-of-the-Art in Patch-Clamp Units Multiclamp 700B [38] MWSCAS, 2011 [16] JNP, 2014 [36] Nature El., 2019 [37] **Parameters** Technology N/A  $0.5 \mu m$  $0.35 \mu m$  $0.18 \mu m$ V N/A 3.3 V N/A 3.3 Supply Die size N/A  $4 \times 8$  $4.7 \times 3$  $3.23 \times 2.73$ mm × mm 4 No. of channel N/A 1 1 CC Gain V/V  $50 \text{ M}\Omega - 5 \text{ G}\Omega$ 4 1  $100~\mathrm{p}_{pp}$ -5 p - 128 n Injected current range Α a few p - 200 n less than 1 n 50 M - 50 G 49 k - 100 M 0 - 225 M VC (TIA) Gain Ω Nonlinear  $\mu V_{rms}$ Input-referred voltage noise N/A 150 8.2 20 mW 30000 30 N/A 7 Power

Table 1.2

### 1.1. State-of-the-Art in Patch Clamp and MEA Technologies

The state-of-the-art in patch clamp technology offers integrated circuit patch amplifier with both current- and voltage-clamp capability [16, 36, 37] to mitigate the problems in conventional bulky, expensive and non-scalable bench-top systems [38].

The first fully-integrated patch clamp amplifier with current-clamp capability was introduced by Goldstein et.al. [16]. The operation mode of the channel can be changed via digital control logic. The recording channel is in transimpedance amplifier (TIA) configuration when voltage-clamp modality is chosen. The channel is configured to a unity gain buffer when current-clamp mode is active. Although the channel is shared and uniquely configured for two different modalities, the channel occupies large areas on silicon with only 4 channels integrated on 4 mm × 8 mm die area. One of the reasons of large area occupation can be explained as using large resistances in the design. Besides the TIA and large resistances, there are compensation circuits to eliminate the non-linearities rising from the electrodes.

The second study example of a CMOS amplifier with both clamp capabilities is offered by Harrison et.al.[36]. Particularly in this study, nonlinear feedback elements (diodes) are used to avoid from the need of using large value resistances. However, since the nonlinear circuit elements are prone to process and temperature variations in manufacturing, additional calibration circuits had to be used.

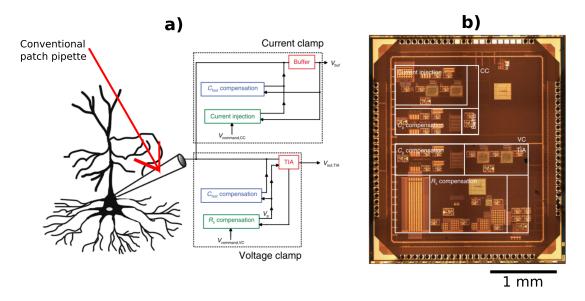

Another example of CMOS amplifier for both patch clamping method was introduced by Shekar et. al.[37]. For current-clamp measurements, a unity gain buffer is used, whereas a TIA with resistive feedback is implemented as a separate block in the design. Since the IC still needs to be used with conventional patch pipettes, it can only be used for single-channel measurements. Fig. 1.7 shows the neural recording setup and the micrograph of offered amplifier. The die size is 3.23 mm  $\times$  2.73 mm. The resistance in the feedback of TIA ranges from 0-225M $\Omega$ . The summary comparison table of CMOS amplifier in patch-clamping and one of the bench-top system is given in Table 1.2.

Complementary-Metal-Oxide-Semiconductor (CMOS)-based MEAs are offered to overcome the issue of poor scalability of passive MEA electrodes and millimetre-sized CMOS patch-clamp amplifiers. Integrating 10000's of electrodes and recording electronics together

**Figure 1.7:** a) The setup for neural recording either in voltage- or current-clamp mode b) Micrograph of the amplifier (Taken from [37])

| Table of Performance Comparison State-of-the-Art in MEA Technologies |       |                          |                 |                 |                   |  |  |

|----------------------------------------------------------------------|-------|--------------------------|-----------------|-----------------|-------------------|--|--|

| Parameters                                                           | Units | Lab on a Chip, 2009 [26] | JSSC, 2017 [41] | JSSC, 2018 [27] | Nature, 2020 [35] |  |  |

| Supply                                                               | V     | 5/3.3                    | 3.3 V           | N/A             | N/A               |  |  |

| Technology                                                           | _     | 0.5 μm                   | 0.18 μm         | 0.13 μm         | 0.18 μm           |  |  |

| No. of. Electrodes                                                   | _     | 4096                     | 59760           | 16384           | 4096              |  |  |

| No. of channels                                                      | _     | N/A                      | 2048            | 1024            | 4096              |  |  |

| Gain                                                                 | dB    | 29.5-30.8                | 29.5-79.9       | 6-69.5          | 29.5-48.8         |  |  |

| Bandwith                                                             | Hz    | 10 k                     | 1 - 10 k        | 0.5 - 10 k      | <1 - 30 k         |  |  |

| Injected current range                                               | N/A   | N/A                      | N/A             | N/A             | ±15 p             |  |  |

5.4

86

12

95

23

1250

13.3

132

Input-referred voltage noise

Power

$\mu V_{rms}$

mW

**Table 1.3**

has been made possible on CMOS-Based MEAs [27, 39–41]. Therefore, CMOS-MEAs offer better performance than passive MEA electrodes on multi-site extracellular recordings from large populations of cells. This feature enables studying the network activities to understand synchronized activity and properties of very large number of cells. However, since CMOS MEAs record the signals in extracellular manner as it has done in passive MEAs, the signals that they can only capture are APs, they are highly attenuated (to around  $100~\mu Vs$ ) [42]. The illustration of multi-functional CMOS-MEA with 59760 electrodes is given in Fig. 1.8a [41]. The recorded signals from rat cortical neurons are shown as averaged negative peak amplitudes and as APs around  $100~\mu Vs$  in Fig. 1.8b-c, respectively. It can be also seen that CMOS-MEAs cannot detect critical excitatory/inhibitory PSPs as it has been mentioned in Chapter 1.

1. Introduction

**Figure 1.8:** a) Illustration of Multi-functional MEA with 59760 electrodes b) Averaged negative peak amplitudes recorded from rat cortical neurons c) APs recorded by means of CMOS-MEAs. (Taken from [41])

#### 1.2. Problem Statement

The extracellular field potentials are a combination of all ionic changes ranging from the slowest oscillations to APs. All ionic currents in cell membrane yields a contribution as intracellular and as extracellular activity. The amplitude and frequency of extracellular field potentials are dependant on multiple variations of multiple single current sources. For example, the distance from a current source play a role in magnitude of an extracellular potential. If the distance from a current source increases, extracellular potential amplitude decreases. Another important aspect of single current sources contributing extracellular potentials is the synchronicity of the sources. Overlapped synaptic potentials are the main contributors of extracellular current flow [43].

**Table 1.4**

| Qualitative Comparison of Patch-Clamp, MEA, 3D MEAs, CMOS-MEA, and Proposed Platform |                                                         |     |     |     |     |  |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------|-----|-----|-----|-----|--|--|

| Features                                                                             | res Patch-Clamp MEAs 3D MEAs CMOS-MEAs Proposed Platfor |     |     |     |     |  |  |

| Intracellular access                                                                 | Yes                                                     | No  | Yes | No  | Yes |  |  |

| Network activity                                                                     | No                                                      | Yes | Yes | Yes | Yes |  |  |

| High throughput                                                                      | No                                                      | Yes | Yes | Yes | Yes |  |  |

| Scalability                                                                          | No                                                      | Yes | No  | Yes | Yes |  |  |

| Cost-effective                                                                       | No                                                      | Yes | No  | Yes | Yes |  |  |

1.2. Problem Statement 9

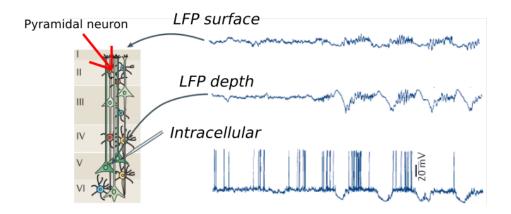

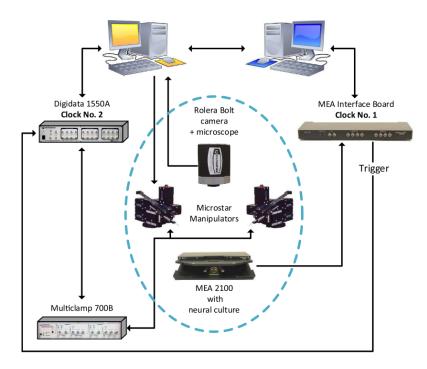

A simultaneous recording example of local field potentials (LFPs) from surface and deep regions of pyramidal neuron, and intracellular recordings is given in Fig. 1.9. In Fig. 1.9, intracellular activity in the deep regions of pyramidal neuron also reflects as synchronous activity in LFPs. In addition to that, Fig. 1.10 shows the contribution of a single AP on extracellular field potentials. Therefore, overlapped APs can have huge impact on extracellular field potentials. For instane, the study by Vardi et. al. reported that firing activity of a single neuron shows high-correlation or high anti-correlation with the network activity [44]. The research study used bench-top patch-clamp system (Multiclamp 700B) with bench-top MEA system (MEA2100) to record intracellular and extracellular activities simultaneously. The measurement setup is depicted in Fig. 1.11. It was also stated that multi-clamp system was required to shed the light especially on anti-correlation between intracellular and extracellular recordings [44]. Moreover, collective activity of large population of a cell can cause hyperpolarization in a single-neuron [43]. Therefore, multi-patch-clamp recordings combined with the multi-electrode-array recordings of a very large population of cells can be a key feature to understand the connectivity between cells and their organizational scheme [43, 44].

**Figure 1.9:** Simultaneous recordings of LFPs from surface and deep regions of neurons, and intracellular recordings (Adapted from [43]).

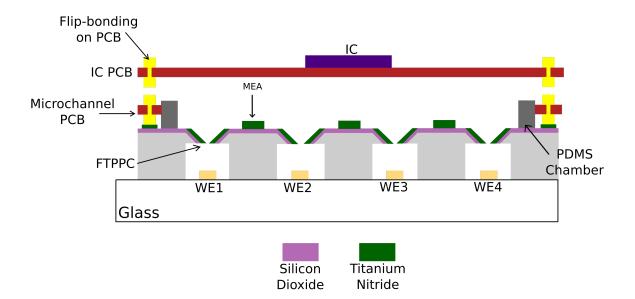

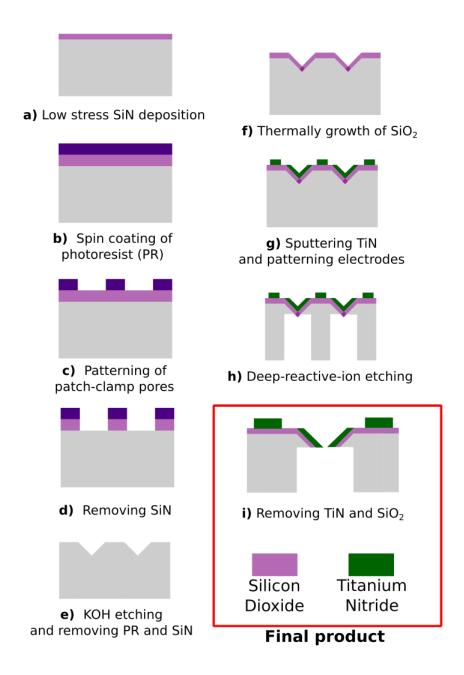

In order to offer a platform that can realize both extracellular and intracellular recordings simultaneously, firstly, a novel envisioned micro total analysis system ( $\mu$ TAS) that integrates flip-tip planar patch-clamp (FTPPC) electrodes and MEAs on the same wafer is proposed. MEA electrodes with 50  $\mu$ m diameter with 400  $\mu$ m distance between each other can be implemented on the front-side of the wafer. Funnel-shape planar patch clamps can offer a good coupling between cultured cells and electrodes on the tip. 2  $\mu$ m tip diameter can be achieved by FTPPCs which mimics conventional patch pipettes. The microfabrication of this  $\mu$ TAS is a cost-effective process because it only uses 2-masks. In fact, it offers a scalable microfabrication process because it uses conventional photolithography. The proposed system is compared to patch-clamp, MEAs, 3D-MEAs, and CMOS-MEAs qualitatively in Table 1.4. The details of the microfabrication steps can be found in Appendix.

1. Introduction

**Figure 1.10:** The contribution of a single AP on extracellular field potentials (Taken from [43]).

**Figure 1.12:** Stand-alone  $\mu$ TAS and CMOS IC.

**Figure 1.11:** The setup used in simultaneous patch-clamp and MEA recordings (Taken from [44])

**Table 1.5**

| Table of Targeted Specifications of Proposed Recording Unit |               |                                |  |  |  |

|-------------------------------------------------------------|---------------|--------------------------------|--|--|--|

| Parameters                                                  | Units         | <b>Targeted Specifications</b> |  |  |  |

| Supply                                                      | V             | 1.8                            |  |  |  |

| Technology                                                  | _             | 0.18 μm                        |  |  |  |

| No. of channels                                             | _             | 16                             |  |  |  |

| Gain                                                        | dB            | 29.5                           |  |  |  |

| Bandwith                                                    | Hz            | 10 k                           |  |  |  |

| Injected current range                                      | A             | 100 p to a few n               |  |  |  |

| Input-referred voltage noise                                | $\mu V_{rms}$ | Less than 10                   |  |  |  |

| Power                                                       | W             | a few $\mu$ / channel          |  |  |  |

1. Introduction

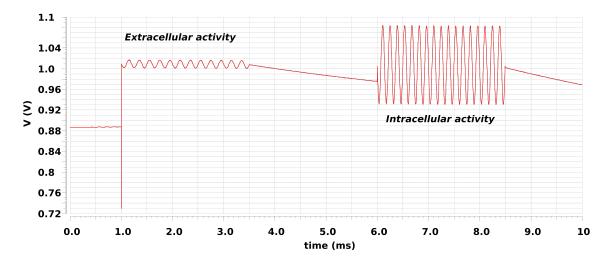

The proposed stand-alone  $\mu$ TAS must be combined and operated together with an integrated circuit (IC) designed for simultaneous extracellular recordings from MEA electrodes, and intracellular recordings from FTPPCs. The pads of both MEA and FTPPCs electrodes can be soldered to a printed-circuit-board (PCB) designed for  $\mu$ TAS. Another PCB that contains proposed IC can be connected by means of flip-bondings as it is shown in Fig. 1.12. By this project, we propose a dual-mode reconfigurable recording unit for both in-vitro measurements of MEA and current-clamp in channel-array operation. In doing so, each channel can be configured independently which enables simultaneous extra- and intra-cellular recordings. The envisioned  $\mu$ TAS consists of 16 of MEA electrodes and 16 of FTPPCs. Therefore, 16-channel operation is proceeded to have access to all electrodes. The gain of the recording channel must be high enough to amplify the extracellular potentials. At the same time, recordings of intracellular activities should not exceed the supply voltage 1.8 V. The seal resistance of envisioned patch electrodes cannot be known before fabricating. 3D-MEAs have provided intracellular potentials around 20 mVs. If the same value for intracellular activity is taken into account for proposed system, gain 30 V/V (or 29.5 dB) is chosen for both modalities to avoid clipping issues. As it is shown in Table 1.1, electrophysiological activities of cells occurs at frequencies ranging from 0.1 Hz to 10 kHz. Therefore, bandwidth of the recording channel must be at least 10 kHz. Also, the smallest possible signal in amplitude is around 10  $\mu$ V (see Table 1.1). Therefore, input-referred noise level must be kept below 10  $\mu$ V to record small extracellular signals. The current-clamp injection current mimics the currents generated by synaptic activities. The current value ranging from 100 pA to 1.6 nA to be able to measure subthreshold PSPs and APs. The proposed platform is designed for in-vitro measurements that mimic the body temperature of animal or human bodies. Therefore, low power consumption must be targeted to avoid heating issues which might result in killing cells [45]. Table of targeted specifications is given in Table 1.5.

## Proposed Architecture and Circuit Design

### 2.1. System Level Architecture

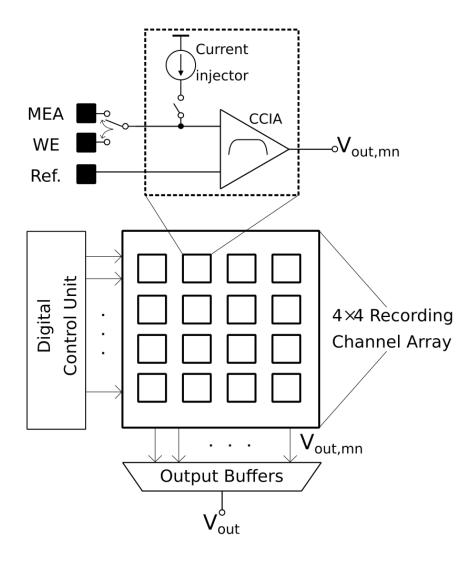

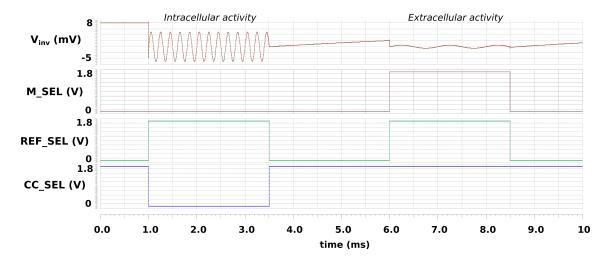

Fig. 2.1 presents the top-level system architecture with a simplified representation of the dual-mode channel. The proposed architecture contains 16 recording channels (4×4) which form the channel array, Digital Control Unit, and Output Buffers. Fig. 2.1, MEA represents the MEA electrode assigned for the particular channel, whereas WE corresponds to each independent working electrode in the pore.

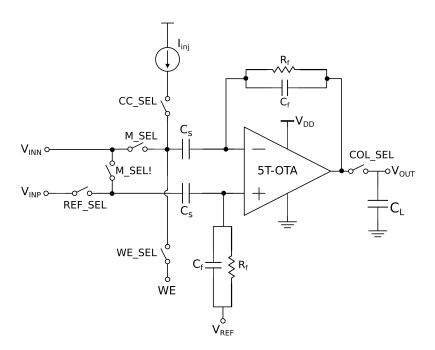

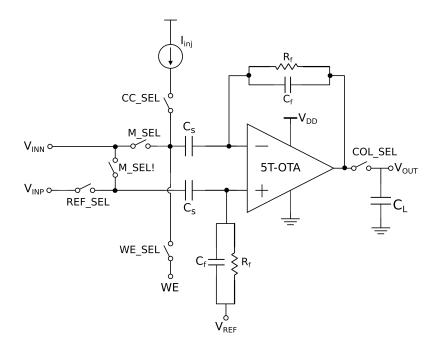

Each channel can be independently configured for 2 different modalities: 1) MEA-modality; 2) CC-modality. The (in total 8) switches (see Fig. 2.3)<sup>1</sup> select the operation modes of the channel out of these 2 possible options. Digital Control Unit programs and controls the switches. Each channel consists of a capacitively coupled instrumentation amplifier (CCIA) and current injector circuit. The output of the channel-under-duty is directed to output buffers to be post-processed. The detailed explanation regarding the each main block of the top-level system architecture is given in the following sections (Section 2.2-2.3).

### 2.2. Digital Control Unit

Digital Control Unit is the logic circuit in charge of controlling the switches. Each channel is controlled by 7 switches which form the Digital Control Logic. The list below describes the duties of each individual switch.

- MEA\_SEL: This switch is dedicated to connect the particular MEA electrode to the channel.

- MEA\_SEL!: The all MEA electrodes except the one being investigated by the channel in MEA-modality is connected to the non-inverting node of the channel through MEA\_SEL! to act as the reference electrode.

- **REF\_SEL**: This switch connects reference electrode to the non-inverting node of the channel.

<sup>&</sup>lt;sup>1</sup>Current injector switches are not shown here for simplicity. These switches will be explained in Section 2.3.2.

**Figure 2.1:** Top-level system architecture. (Figure inspired from [46])

- COL\_SEL: After activating this switch, the output voltage of the channel is being directed to the output buffers.

- WE\_SEL: There is WE\_SEL to connect each working electrode to the inverting node of the channel.

- CC\_SEL: This switch let current flowing from current injector DAC reach to the working electrode through the inverting node of the channel.

- $\mathbf{B}_n$ ,  $\mathbf{B}_n$ !: These switches are put in the circuit as complementary switches of the current injector DAC.

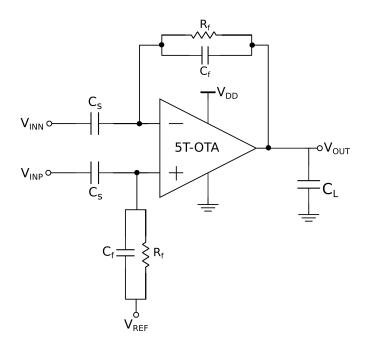

### 2.3. Recording Channel

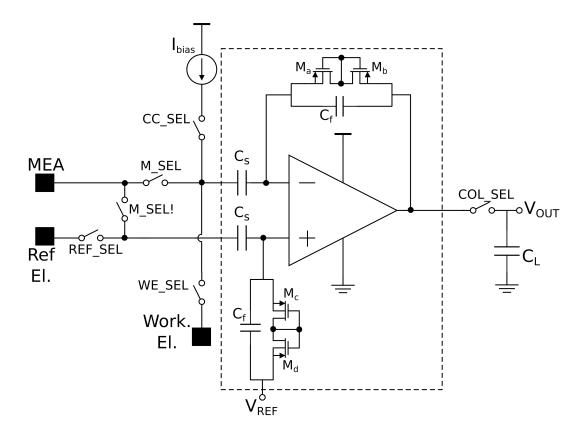

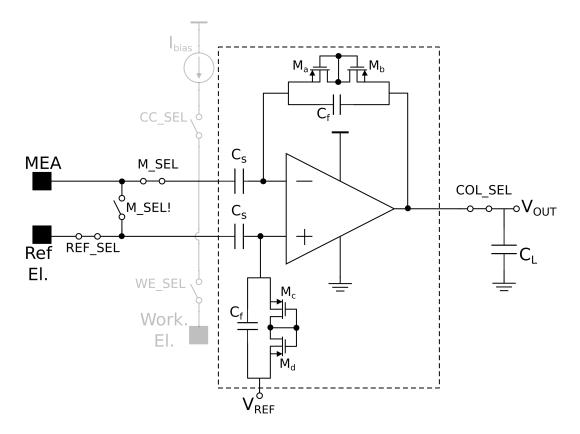

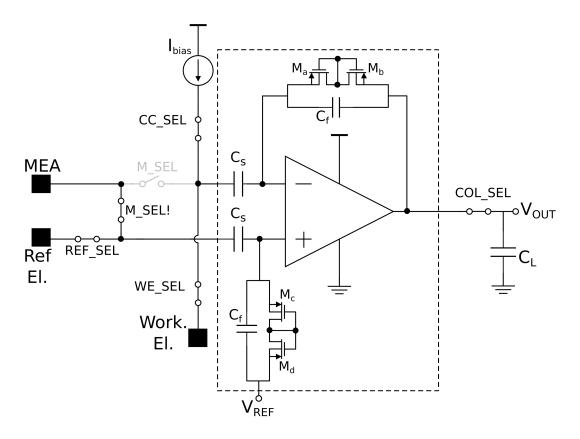

Fig. 2.3 shows the schematic of dual-mode reconfigurable channel. The AC-coupled front-end amplifier (shown in dashed line in Fig. 2.3) is shared between MEA- and CC-modality. There are two main reasons to choose capacitively-coupled configuration for the channel: 1) The DC offset voltage rising from the electrode-electrolyte interface can reach up to 1 V [47]. This voltage level is considerably higher than the signal amplitudes generated from the cells. By means of this architecture, the DC offset voltage is removed. 2) the DC current that generated from the current injector circuit can flow through the working electrode (WE) to apply current-clamp technique on cells.

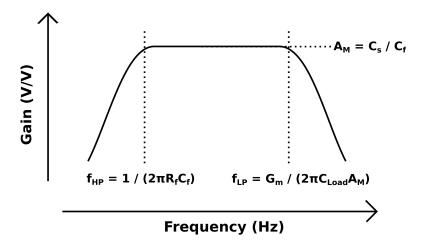

The transfer function of the AC-coupled front-end amplifier is given in Eq. 2.1. The midgain  $A_M$  is defined by the ratio of the capacitors  $C_s$  and  $C_f$ . The high-pass cut-off frequency  $(f_{HP})$  corner sits at  $\frac{1}{2\pi R_f C_f}$ , and the low-pass cut-off frequency  $(f_{LP})$  corner happens at  $\frac{f_{unity}}{A_M}$  which is equal to  $\frac{G_m}{2\pi C_{Load}A_M}$ . Note that  $G_M$  is the transconductance of the front-end amplifier, whereas  $R_f$  represents the resistance in the feedback path which has done by the diodeconnected PMOS transistors.

$$\frac{V_{out}}{V_{in}} = -\frac{sR_f \cdot C_s}{1 + sC_f \cdot R_f} \tag{2.1}$$

**Figure 2.2:** The closed-loop characterization of AC-coupled front-end amplifier shown in Fig. 2.3.

**Figure 2.3:** The circuit schematic of the dual-mode reconfigurable channel.

The channel configuration for the MEA-operation is depicted in Fig. 2.4. When the channel operates in MEA-modality, the switches CC\_SEL and WE\_SEL are inactive, while M\_SEL, M\_SEL!, REF\_SEL are turned on. If the voltage is wanted to be read out, then the switch COL\_SEL of this particular channel is being activated.

When current-clamp cell study technique is required to be applied, then the channel is configured as it is shown in Fig. 2.5. All the MEA electrodes are connected to the reference electrode node by means of M\_SEL! as being on. Therefore, working electrode dedicated for the channel is connected to the inverting node of the AC-coupled amplifier. In addition, the switches REF\_SEL, WE\_SEL, CC\_SEL are turned on. The switch COL\_SEL is active, when the output voltage is asked to be read out. The position of the all switches for each modality is given in Table 2.1.

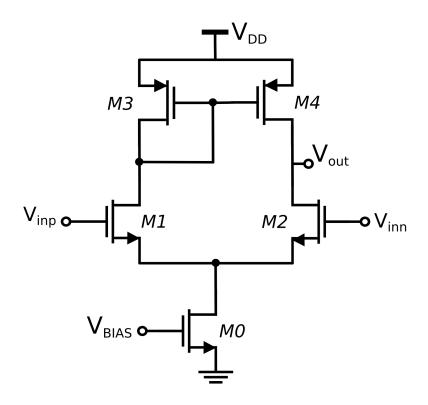

#### 2.3.1. 5T Operational Transconductance Amplifier (5T-OTA) Design

Fig. 2.6 presents the schematic of single-ended 5T-OTA used in AC-coupled instrumentation amplifier. Transistors M1 and M2 consist of the input pair of the OTA. The active load is realized by means of transistors M3 and M4. The tail current of the circuit is supplied through transistor M0 which is connected to its current mirror pair biased with reference current. The figure does not show the biasing circuit.

5T-OTA, in other words, differential pair with an active load is a standard circuit topology. Yet, the circuit requires proper sizing of transistors to meet certain noise, power, and area

**Figure 2.4:** The dual-mode channel configured for MEA operation.

specifications. The tail current is specified as 2  $\mu$ As. Therefore, the current flows through left-branch (M1 and M3), and right-branch (M2 and M4) is equal and 1  $\mu$ A.

The inversion coefficient (*IC*) defines how the channel of a MOS transistor is inverted. Depending on the bias voltage, the free carriers in the inversion channel differ in quantity. By changing *IC*, the operation region of the transistor can be set as weak, moderate or strong inversion [48].

Firstly, the device parameters of the transistors in TSMC 0.18  $\mu$ m technology are determined to be able to move forward with design choices. Table 2.2 shows simulated and calculated process parameters of NMOS and PMOS transistors used in this technology. In Table 2.2, I<sub>0</sub> represents the technology current, whereas n<sub>0</sub> is the slope factor of devices. The term  $\mu_0$  corresponds to the low-field mobility, while  $C_{ox}$  defines the gate-oxide capacitance. The relation between IC and drain current is given in Eqn. 2.2 below, where S defines the aspect ratio (W/L) of the device [49].

$$IC = \frac{I_D}{I_0.S} \tag{2.2}$$

As it has mentioned before, IC is a numerical measure of the inversion level of the channel. For IC < 0.1, the channel is weakly inverted which means the device is in weak inversion. When 0.1 < IC < 10, the device is now moved to moderate inversion. Strong inversion occurs when IC > 10 [48, 49].

**Figure 2.5:** The dual-mode channel configured for CC operation.

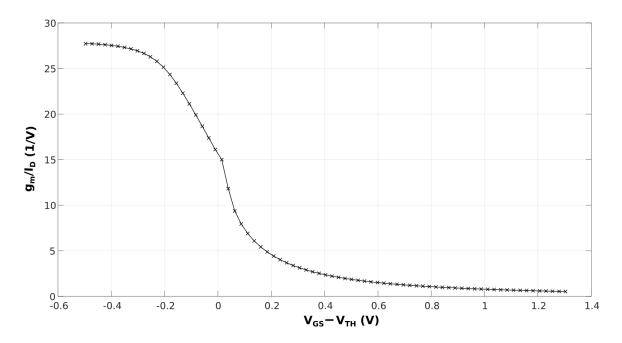

As it can be seen from Table 2.3, the transconductance efficiency  $(g_m/I_D)$  reaches its highest when the device operates in weak inversion. The transconductance efficiency can be described as a quality factor of a transistor. It basically shows how much transconductance can be provided for a given current value [48]. Fig. 2.7 shows the relation between  $V_{EFF}$  and  $g_m/I_D$ . It is clearly observable that pushing the device into deeper weak inversion results in higher transconductance efficiency. Therefore, choosing lower IC must cause higher  $g_m/I_D$ . For a MOS transistor, transconductance efficiency in weak inversion is given as [49]:

$$g_m/I_D = \frac{1}{n \cdot U_T} \tag{2.3}$$

where transconductance equals to:

$$g_m = \frac{I_D}{n \cdot U_T} \tag{2.4}$$

Table 2.4 presents the sizes and operating points of 5T-OTA. It is challenging that to design a low-noise amplifier by not exceeding a certain power consumption. The input-referred thermal noise power of the OTA can be calculated as:

$$\overline{v_{thermal}^2} = \left[ \frac{16kT}{3g_{m1}} \left( 1 + \frac{g_{m3}}{g_{m1}} \right) \right]$$

(2.5)

where  $g_{m1}$  corresponds to the transconductances of M1 and M2 (identical pair), and the transconductance of M3 and M4 (identical load) is represented as  $g_{m3}$ . In order to minimize

| Table of Positions of the Switches in CC- and MEA-modality |                     |     |  |  |  |  |

|------------------------------------------------------------|---------------------|-----|--|--|--|--|

| Switches                                                   | CC-Modality MEA-Mod |     |  |  |  |  |

| MEA_SEL                                                    | OFF                 | ON  |  |  |  |  |

| MEA_SEL!                                                   | ON                  | OFF |  |  |  |  |

| CC_SEL                                                     | ON                  | OFF |  |  |  |  |

| REF_SEL                                                    | ON                  | ON  |  |  |  |  |

| WE_SEL                                                     | ON                  | OFF |  |  |  |  |

| COL_SEL                                                    | ON                  | ON  |  |  |  |  |

| В                                                          | ON                  | OFF |  |  |  |  |

| R!                                                         | OFF                 | ON  |  |  |  |  |

Table 2.1

Table 2.2

| Device parameters at 300 K for TSMC 0.18 $\mu$ m Technology |                          |       |                        |  |  |  |

|-------------------------------------------------------------|--------------------------|-------|------------------------|--|--|--|

| Parameters                                                  | rameters NMOS PMOS Units |       |                        |  |  |  |

| $I_0$                                                       | 0.561                    | 0.169 | $\mu A$                |  |  |  |

| $n_0$                                                       | 1.4                      | 1.4   | N/A                    |  |  |  |

| $\mu_0$                                                     | 30                       | 9.5   | $\mu$ A/V <sup>2</sup> |  |  |  |

| $C_{ox}$                                                    | 10                       | 9.5   | fF/ $\mu m^2$          |  |  |  |

the input-referred thermal noise,  $g_{m1}$  must be higher than  $g_{m3}$ , so that the term  $g_{m3}/g_{m1}$  can be very small. This aim can be achieved by using wider devices for input pair M1 and M2 such that W/L ratio is high. At the same time, aspect ratio of current mirror load devices must be decreased to decrease their transconductances. In other words, current mirror load must operate in strong inversion, whereas input pair operates in deep weak inversion. It can be seen in Table 2.4, transconductance of input pair reaches 28.9  $\mu$ A/V with IC 0.01. To be able to push current mirror load devices into strong inversion, IC has been chosen as 50. Although increasing the aspect ratio of input pair results in higher transconductance, it also increases the input capacitance of the amplifier. The contribution of the OTA to the input-referred noise of the channel is given as follows:

$$\overline{v_{ni,ch}^2} = \left(\frac{C_s + C_f + C_{in}}{C_s}\right) \cdot \overline{v_{OTA}^2}$$

(2.6)

Therefore, an increase in the width of input pair causes higher input capacitances which results in higher input-referred noise. The reason of that is that the input capacitances play a role in signal division. In other words, it decreases the overall gain of the amplifier, so that increases the input-referred noise. On the other hand, it is advantageous to use wider devices to reduce the flicker noise contribution of the transistors. The flicker noise of the OTA is given in the equation below [50]. The optimization study have not been implemented to find the best ratio of W/L, preliminary schematic simulations show that increasing the width and the length with the same factor did not result in very lowered input-referred noise. For example,  $360 \mu m$  /  $2 \mu$  m aspect ratio resulted in  $11.2 \mu V_{rms}$ , where it is found as  $11.4 \mu V_{rms}$  when aspect ratio is  $180 \mu m$  /  $1 \mu m$ . Considering also the area concerns, the latter W/L option is applied to the

Figure 2.6: Schematic of 5T-OTA.

input transistors.

$$\overline{V_{1/f}^2} = 2\frac{K}{C_{ox} \cdot (WL)_3} \cdot \frac{1}{f} \cdot \left(\frac{g_{m3}}{g_{m1}}\right)^2 + 2\frac{K}{C_{ox} \cdot (WL)_1} \cdot \frac{1}{f}$$

(2.7)

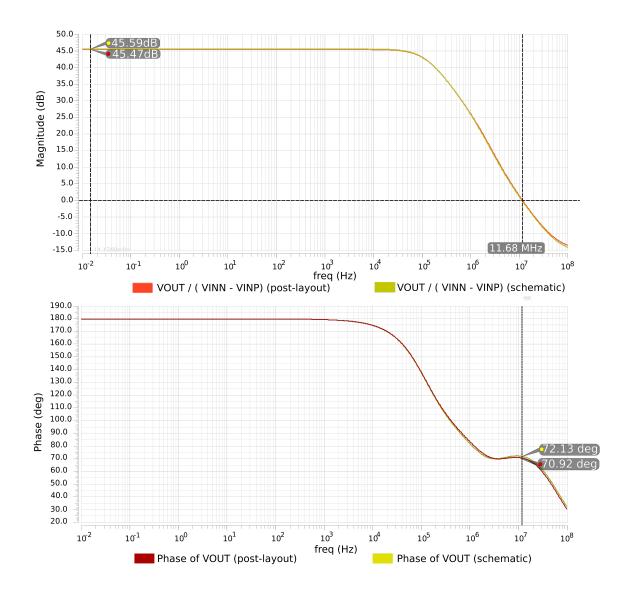

Fig. 2.8 shows the gain and phase of 5T-OTA in AC analysis. The differential gain of the transconductance amplifier can be given as:

$$A_d = g_m \cdot r_{out} \tag{2.8}$$

where  $g_m$  is the transconductance value of one of the input pair devices, and  $r_{out}$  is the parallel combination of the  $r_{o1}$  and  $r_{o3}$  [51]. The transconductance  $(g_m)$  of 5T-OTA is 28.9  $\mu$ A/V and the output impedance  $(r_{out})$  is found and simulated as 6.72 M $\Omega$ . Therefore, the

**Table 2.3**

| <b>Expressions for W, <math>g_m/I_D</math>, <math>V_{DSAT}</math> and <math>V_{EFF}</math></b> [48] |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| $W = (L/IC) \cdot (I_D/I_0)$                                                                        |  |  |  |  |  |  |

| $g_m/I_D = 1/\left(n \cdot U_T \cdot \left(\sqrt{IC + 0.5\sqrt{IC} + 1}\right)\right)$              |  |  |  |  |  |  |

| $V_{DSAT} = 2U_T \cdot \sqrt{IC + 0.25} + 3U_T)$                                                    |  |  |  |  |  |  |

| $V_{EFF} = n \cdot U_T \cdot ln(IC)$                                                                |  |  |  |  |  |  |

**Figure 2.7:** Simulated  $g_m/I_D$  of an NMOS as  $V_{GS}$  swept from 0 to 1.8 V.

| OTA Transistor Sizes and Operating Points |                          |                                 |                                   |                                                 |                          |  |

|-------------------------------------------|--------------------------|---------------------------------|-----------------------------------|-------------------------------------------------|--------------------------|--|

| Transistor                                | <b>W/L</b> (μ <b>m</b> ) | $\mathbf{I}_{D}(\mu\mathbf{A})$ | $\mathbf{g}_m (\mu \mathbf{A/V})$ | $\mathbf{g}_m/\mathbf{I}_D$ $(\mathbf{V}^{-1})$ | Inversion<br>Coefficient |  |

| M0                                        | 1/14                     | 2                               | 7.2                               | 3.9                                             | 50                       |  |

| M1                                        | 180/1                    | 1                               | 28.92                             | 29.1                                            | 0.01                     |  |

| M2                                        | 180/1                    | 1                               | 28.92                             | 29.1                                            | 0.01                     |  |

| M3                                        | 1/8                      | 1                               | 3.57                              | 3.59                                            | 50                       |  |

| M4                                        | 1/8                      | 1                               | 3.57                              | 3.59                                            | 50                       |  |

**Table 2.4**

differential open-loop gain  $A_d$  is calculated as 45.8 dB. The calculated results can be confirmed by the both schematic and post-layout simulation results with a small deviation 0.18 dB and 0.29 dB where  $A_d$  is simulated as 45.59 dB and 45.47 dB with schematic and post-layout views, respectively. The phase margin of the OTA is 72.13 degree for schematic views, whereas 70,92 degree is simulated for phase margin of the amplifier. Since the amplifier is in a single-stage configuration, there is no stability issues existing.

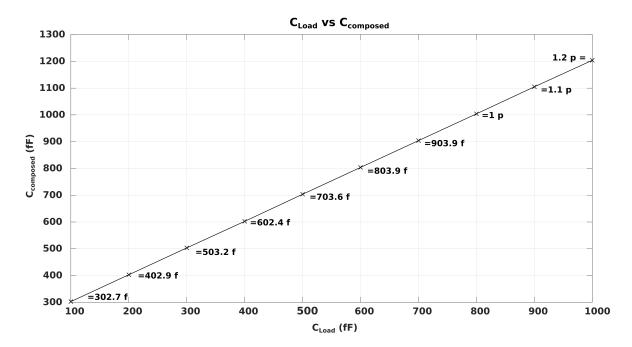

Although gain-bandwidth product (GBW) is expected to be at  $GBW = g_m/C_{out}$  where  $C_{Load}$  is the main contributor of  $C_{out}$ , the simulation results show that roll-off curve passes 0 dB earlier than expected. The calculations based on simulation results reflects that there is another parasitic capacitance which plays a role on GBW. Fig 2.9 shows the relation between  $C_{Load}$  and found  $C_{composed}$  which is composition of  $C_{Load}$  and  $C_{parasitics}$  in the circuit.  $C_{parasitics}$  is found as 204 fF where  $C_{gd}$  is 69 fF. The junction-drain capacitance  $C_{jd}$  is simulated as 174 fF which might be playing a role on overall parasitics.

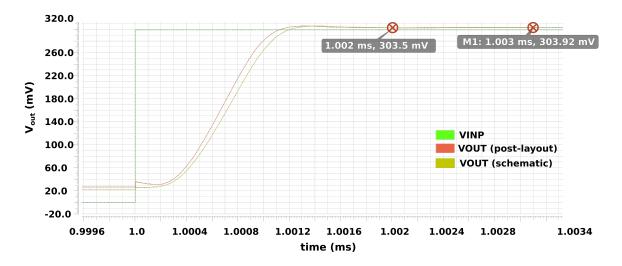

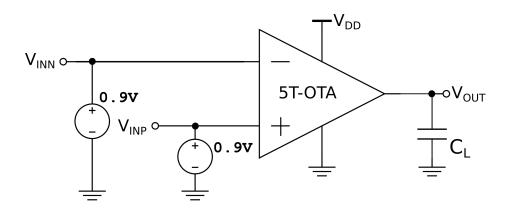

Transient analysis is run to simulate the settling time of the OTA. The OTA was used in

**Figure 2.8:** Gain and phase of 5T-OTA.

unity gain configuration where its inverting input is connected to the output node. For input signal at  $V_{INP}$  node, the extreme case scenario was thought which assumes presence of 10 mV of extracellular activity at a MEA electrode. A 10 mV input signal is amplified by the gain of the channel (23.5 dB in post-layout simulations). This will result in 150 mV at the output, and for the settling time analysis, this value is multiplied by 2 to enclose range of all possible input signals. A 300 mV with 1 ns of rising time input signal is applied to the non-inverting node of the OTA, and resulting step response simulation is given in Fig. 2.10. The output voltage reaches steady-state position (303.5 mV) with 0.4 mV tolerance in around 2  $\mu$ s for both schematic and post-layout simulations.

**Figure 2.9:** The relation between  $C_{Load}$  and  $C_{composed}$  which is equal to  $C_{Load} + C_{parasitics}$ .

**Figure 2.10:** Settling time needed of 5T-OTA when 0.3 V input voltage applied with 1 ns rising time.

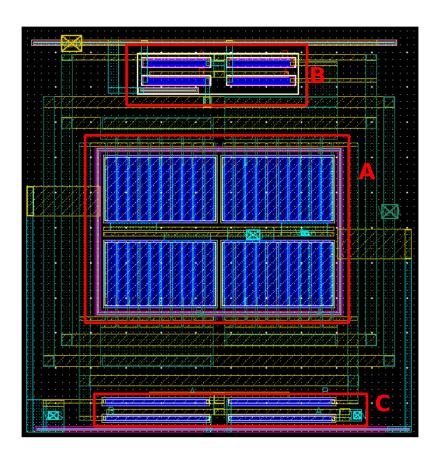

Fig 2.11 presents the layout of 5T-OTA. The input pair is the critical block to have good matching between two transistors. Parameter variations, e.g. oxide thickness, can occur across the wafer. These variations are most likely to happen linearly when devices are in short distance from each other. Common-centroid patterns are used to average out these variations, so that minimize the effect of errors happening during the fabrication processes. In our OTA design, therefore, common centroid patterns are applied to all sub-blocks which are input, current mirror load-, and current mirror bias-pairs. The input pair is notated with "A" in Fig 2.11. Both M1 and M2 are divided into 2 pieces by using "multiplier=2" in Cadence Spectre to apply ABBA common-centroid pattern. Then, in the layout view, 10 fingers are used

for each input pair devices. The input nodes are connected in between with the same width and length of interconnections. The input pair sub-block is guarded with PSUB guarding to connect the bulks of devices to ground node. The letter "B" highlights the current mirror load devices, and ABBA common-centroid is also followed for these devices. In addition, NWELL taps are used in shared NWELL to be able to connect the bulks of PMOS transistors to VDD node. The third sub-block is presented with letter "C" in Fig 2.11. As in the other sub-blocks, the pattern ABBA is applied to current mirror bias devices. 5T-OTA consumes 55  $\mu$ m × 55  $\mu$ m of area on silicon wafer.

**Figure 2.11:** The layout view of 5T-OTA which covers 55  $\mu$ m × 55  $\mu$ m.

#### 2.3.2. Unary-Weighted Current-Steering DAC Design

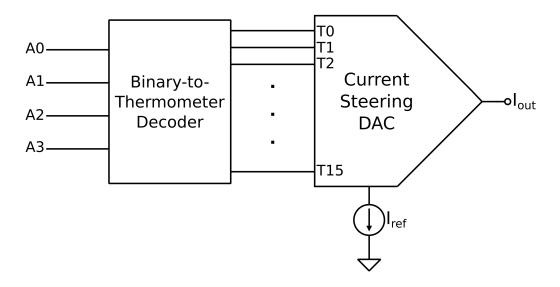

Figure 2.12: Block diagram of unary-weighted current-steering DAC.

In order to understand the operation principle of unary-weighted current-steering DAC, the conventional binary-to-thermometer-coded DAC must be introduced. The block diagram of unary-weighted current-steering digital-to-analog converter (DAC) is given in Fig. 2.12. The converter depicted is an example of 4-bit thermometer-coded DAC. The relation between input and output digital code of the converter is given in Table 2.5. As it can be seen in Table 2.5, In the case of conventional method, current-steering DAC contains  $2^N$  digits consisting of thermometer code. Since the binary code is 4-bit, then there is  $2^N = 16$  bits, and 16 current sources that are controlled by the thermometer code. For example, to replicate the  $I_{ref}$  of the DAC, the first current source must be turned on. Therefore, the binary code (A0, A1, A2, and A3) must be "0001", respectively. If the  $I_{ref}$  is wanted to be made tripled, then the binary code becomes "0011". In other words, the decimal representation of the binary code decides that how many of the unit current sources contribute to  $I_{out}$ .

There are several advantages of thermometer-coded DACs compared to binary-weighted DACs. The first advantage of thermometer-coded current DAC is guaranteed monotonicity. The current output of a monotonic current DAC always increases (decreases) as the digital input code increases (decreases). In the thermometer-coded current DAC, to increase (decrease) the output current ( $I_{out}$ ), the digital code increases (decreases) by 1 Least Significant Bit (LSB). In other words, the output current always increases with the increasing digital input code which meets the definition of monotonicity [52].

The other advantage of unary-weighted thermometer-coded DAC is the relaxed matching requirements. To achieve differential nonlineartiy (DNL) <0.5 LSB, 50% matching of two unit current sources is good enough [52].

One of the advantages of thermometer-coded DAC is reduced glitch problem. In a 3-bit DAC, in order to turn on 3 unit current sources, the binary code must be "011". In order to have 4 unit current sources operating, the binary codes changes from "011" to "100". It means that

| Thermometer code representations for 4-bit binary values |                                            |

|----------------------------------------------------------|--------------------------------------------|

| Binary code                                              | Thermometer code                           |

| A0 A1 A2 A3                                              | T0 T1 T2 T3 T4 T5 T6 T7 T15                |

| 0 0 0 0                                                  | $0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \$  |

| 0 0 0 1                                                  | $0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 1$ |

| 0 0 1 0                                                  | $0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 1\ 1$    |

| 0 0 1 1                                                  | 0000000000000111                           |

| 0100                                                     | $0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 1\ 1\ 1\ 1$ |

| 0 1 0 1                                                  | 000000000011111                            |

| 0110                                                     | 000000000111111                            |

|                                                          |                                            |

| 1111                                                     | 1111111111111111                           |

**Table 2.5**

all binary bits change their current situation to the opposite one. However, this transition only means that one more additional current source is activated to contribute to  $I_{out}$ . Therefore, glitching is considerably decreased by this type of DAC architecture [52].

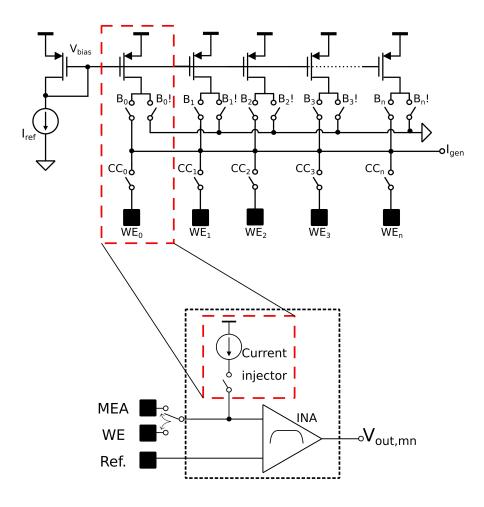

The proposed design of DAC for the dual-mode reconfigurable channel mainly uses the same operation principle of unary-weighted thermometer-coded DACs. As it is shown in Fig. 2.13, each channel contains unit current source as the current injector. The current injector is combination of a PMOS transistor which copies  $I_{ref}$ , and the control switches  $B_n$ ,  $B_n$ !, and  $CC_n$ . All the unit current sources (PMOS transistors) are connected on their gates which guarantees the (almost) same  $V_{bias}$  for all of them. Also, the nodes after each  $B_n$  are shorted together as node  $I_{gen}$  as it has done in thermometer-coded DACs. Therefore, for example, to double  $I_{gen}$ , two of unit current sources are activated. To obtain  $10 \times I_{ref}$ , 10 of the switches  $B_n$  are switched ON. The switch represented in each individual channel to control current injector is called as  $CC_n$  in the unit current injector. In the case of  $CC_n$  is in active mode, then it means that the channel is connected to the  $WE_n$  through switch  $WE_{SEL}$ .

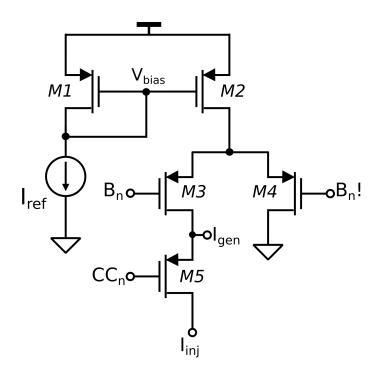

The schematic of each unit of unary-weighted DAC is depicted in Fig. 2.14. Since the minimum current used to stimulate the cells is determined as 100 pA,  $I_{ref}$  is set to 100 pA. To determine the sizes of PMOS current mirror devices, the equation below followed:

$$I_{Dp} = I_{0p} \cdot \frac{W}{L} \cdot exp((V_{GS} - V_T)/nU_T)$$

(2.9)

$I_{0p}$  corresponds to technology current for PMOS, n is the slope factor in weak inversion (see Table 2.2),  $V_T$  is the threshold voltage of the PMOS device, and  $U_T$  represents thermal voltage. When the suitable values are substituted into the equation above, the aspect ratio of the PMOS current mirror device is found as 6. Note that to calculate W/L, the equation for drain current in weak inversion is used, since the current value dealt with is extremely small. In fact,  $I_{ref}$  is more than 1500 times less than the technology current. Since the aspect ratio is decided on, the next step is choosing the length of the device. The simulation results show that if the length of the device keep increasing, the leakage current rising from the current-mirror

Figure 2.13: Current injector DAC.

devices is decreased. To be more specific, if the transistor has sizes as 6  $\mu$ m/ 1 $\mu$ m, then, the resulting current at the drain of M5 is 115.5 pA. This means that only 1-bit of DAC gives 15.5% current error which can reflect around 250 pA error for a 16-channel array. At the same time, the area occupation of the unit current source in a channel must be taken into account. In this case, W/L ratio of PMOS current mirror transistor is chosen as 60  $\mu$ m/ 10 $\mu$ m. The complementary (B<sub>n</sub> and B<sub>n</sub>!) and current-clamp selection switches (CC<sub>n</sub>) are implemented by PMOS transistors in minimum size. The complementary switches are implemented to direct the current to the ground through B<sub>0</sub>!, when B<sub>0</sub> is inactive. In doing so, the leakage currents at drain node of M3 and M5 are tried to be reduced.

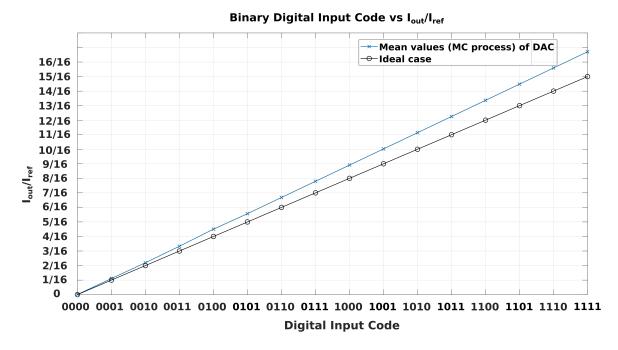

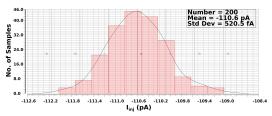

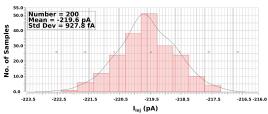

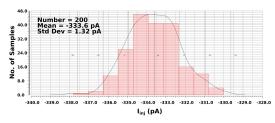

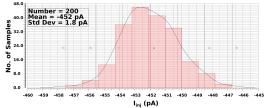

The relation between digital input code and  $I_{out}/I_{ref}$  can be observed in Fig. 2.15. In order to characterize the DAC properly, firstly, one unit current injector has undergone Monte Carlo process and mismatch simulations. The number of samples is chosen as 200. The mean value for a single current injector is found as 107.7 pA when  $I_{ref}$  is 100 pA. Note that  $I_{ref}$  is always kept at 100 pA throughout all MC simulations mentioned here. The same analysis has done for the 4 unit current injectors shorted at  $I_{gen}$  node. When the simulations are applied, the mean current value is found as 110.6 pA. In the light of these simulations, we can assume that one unit current injector contributes around 1 pA as the leakage current. After that, to increase the

Figure 2.14: Schematic of unary-weighted DAC unit.

current in the first unit current source, the other current injectors were activated one by one. In that way, the current in the first current injector must be around 100 pA, 200 pA, 300 pA, and 400 pA by activating the adjacent current sources. The mean current values after the Monte Carlo (process and mismatch together) simulations are found as 219.6 pA, 333.6 pA, and 452 pA, respectively, when the ideal cases assume 200, 300 and 400 pA. By these simulations, the leakage current from an active unit injector is calculated as 11.38 pA which is the average value of 4 current injectors. The rest of the values are extrapolated according to these results.

In the light of MC simulations, Fig. 2.15 is generated to show the nonlinearities of the proposed DAC, and how it deviates from the ideal case. In ideal case, each output increment from one digital input code to the adjacent code. However, in proposed DAC, the increment does not happen ideally, but it increases with slightly higher values than 1 LSB (100 pA). The difference between the actual increment and ideal increment is defined as differential

**Unary-Weighted DAC Transistor Sizes Transistor**  $W/L (\mu m)$  $\mathbf{I}_{D}\left(\mathbf{A}\right)$ M160/10 100*p* M260/10 100*p* M3 0.22/0.18100*p* M40.22/0.18 N/A M5 0.22/0.18 100*p*

**Table 2.6**

Figure 2.15: The relation between digital input code and  $I_{out}/I_{ref}$ .

nonlinearity (DNL), and it can be formulated as follows [53]:

$$DNL_n = \frac{I_{inc,n} - I_{inc,ideal}}{I_{inc,ideal}}$$

(2.10)

where  $I_{inc,n}$  represents the actual increment at  $n^{th}$  digital input code, and  $I_{inc,ideal}$  is equal to the ideal increment and 1 LSB which is 100 pA in this case. For instance, DNL<sub>2</sub> is the difference between actual increment (333.6p-219.6p=114pA) 114 pA and ideal increment 100 pA which results in as 0.14 LSB.

Another fundamental characteristic of DACs is the integral nonlinearity (INL) which can be defined as the difference between actual output values at an input code and the expected value at the same value according to the reference line drawn from the first point to the last point. INL can be formulated as follows [53]:

$$INL_n = \frac{I_{out,n} - I_{out,ref}}{I_{ref}}$$

(2.11)

where  $I_{out,n}$  defines the actual output value at  $n^{th}$  digital input code, and  $I_{out,ref}$  is the expected value at  $n^{th}$  code when a straight reference line is drawn between the first and the last points.  $I_{ref}$  represents the reference current (100 pA). When the reference line is drawn between the zero input code (0000) and "1111", the resulting line shows a trend according to the equation y = 110.97n - 1.24p, where n represents the  $n^{th}$  digital input code. For example, when the digital input code "0100" ( $4^{th}$  input code), then the expected output current of the DAC is 442.6 pA. However, the actual simulations reflects that the output current at the same input code is 452 pA. Therefore, INL<sub>4</sub> is 0.09 LSB for  $4^{th}$  input code "0100".

Ideally, a current DAC gives 0 A output current when the digital input code is 0. Any difference from 0 A current at "0000" shows the offset error of the DAC [53]. Ten, the offset

| Summary of characteristics of |             |  |  |  |

|-------------------------------|-------------|--|--|--|

| proposed                      | current DAC |  |  |  |

| Characteristics Value (LSBs)  |             |  |  |  |

| DNL                           | 0.18        |  |  |  |

| INL                           | 0.08        |  |  |  |

| Offset error                  | 0.013       |  |  |  |

| Gain error                    | 0.11        |  |  |  |

**Table 2.7**

error is given as 1.25 pA or 0.013 LSB in proposed design since the current at  $I_{inj}$  node is found as 1.25 pA.

As the last but not least characteristic of the DAC given is the gain error. The gain error shows the deviation of the slope of transfer curve of output current from the ideal slope [53]. Therefore, it can be formulated as in Eq. 2.12. The slope of the actual transfer curve is 110.97 as it is mentioned above in Eq. 2.3.2. Therefore, the gain error is 0.11 LSB where ideal slope is 100 pA.

$$Gain\ error = Ideal\ slope - Actual\ slope$$

(2.12)

The characteristics of the proposed DAC is summarized in Table 2.7 by giving the worst-case results. These results are obtained by connecting 4 unit current sources, and then running MC process and mismatch simulations together as it is mentioned above. The output currents are extrapolated after digital input code "0101" based on the MC simulations. In order to fully characterize the proposed DAC, further simulations are needed where all unit current sources are connected.

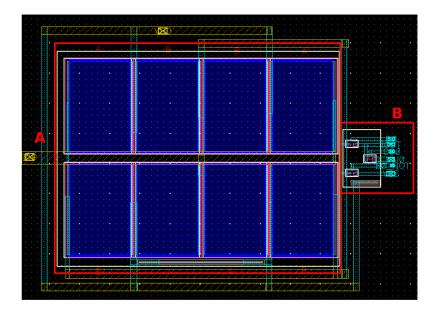

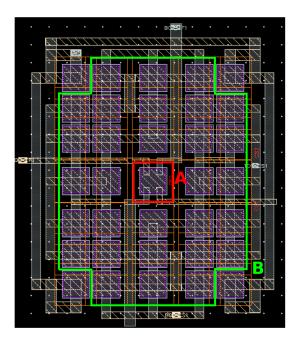

Fig. 2.16 shows the layout of the unit current injector of each individual channel. Copying the reference current to the channel in a correct and reliable way is an important aspect in current mirror. Because of the fact that this importance should be considered carefully, common-centroid pattern is also applied to the unit current injector. Preliminary schematic results show that using 4 multipliers rather than 2 multipliers for each current mirror PMOS transistor will give more accurate copied current values. Therefore, "ABBABAAB" common-centroid pattern is used for the current injector. This is highlighted in Fig. 2.16 with a big red box and letter "A'. The minimum size switches are placed on the right-hand side of the current mirror transistors in an NWELL. Also, switches  $B_0$  and  $B_0$ ! are in the same distance to the drain of M2. Switches  $B_0$ ,  $B_0$ !, and  $CC_0$  are shown in the smaller red box with letter "B". The unit current injector covers  $56.5\mu m \times 44\mu m$  of area on a die in total.

#### 2.3.3. Pseudo-Resistor Elements

In order to achieve high value resistors in standard CMOS technology, large areas must be consumed on silicon. The doping levels of silicon and poly-silicon allows us to have a sheet resistance ranging from a few  $\Omega \Box^{-1}$ s to a few  $k\Omega \Box^{-1}$ s. For this reason, long resistors must be used in folded manner which increases the parasitic capacitances of the structure. The resulted parasitic capacitance might degrade the frequency response [54].

**Figure 2.16:** The layout of unit current injector which occupies  $56.5\mu m \times 44\mu m$  of area.

Pseudo-resistors based on MOS devices, therefore, are proposed as an alternative way of realizing high value resistors. In our design, we use pseudo-resistor elements to set the cut-off frequency of high-pass filter. The relation between the cut-off frequency and  $R_{pseudo}$  is given as:

$$f_{HP,cut-off} = \frac{1}{2\pi \cdot C_f \cdot R_{pseudo}}$$

(2.13)

As it can be seen from Eq. 2.13, the cut-off frequency and the resistance of pseudo-resistor element is inversely proportional to each other. The extracellular action potential can vary in frequency ranging from 0.1 Hz to 10 kHz. For example, in the presence of 100 fF capacitance in the feedback path, the resulting  $R_{pseduo}$  value is found as around 16 T $\Omega$ s to achieve 0.1 Hz as cut-off frequency.

**Figure 2.17:** The schematic of single PMOS transistor as a non-tunable pseudoresistor element.

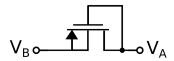

There are mainly two types of pseudo-resistors which are non-tunable and tunable structures. In non-tunable structures, one or even number of transistors in series are used in diode-connected configuration [54]. An example of single non-tunable PMOS device is presented in Fig. 2.17. The bulk and source of the device is connected together. This PMOS devices acts as a MOS transistor when  $V_A < V_B$ , and it has diode-like behaviour when  $V_B < V_A$ .

The device is operated in deep subthreshold regime to achieve very low current (in a few fAs range) flowing through the devices. In the case of fAs, the resistance can reach to  $T\Omega$ s

resistance values. In order to do that, the voltage difference between  $V_A$  and  $V_B$  must be close to 0 V. When the device acts as MOSFET in subthreshold operation region, then the current of the device can be calculated as follows [54]:

$$I_{SD} = I_{SD0} \cdot exp\left(\frac{V_{SG}}{n \cdot U_T}\right) \cdot \left[1 - exp\left(\frac{V_{SD}}{n \cdot U_T}\right)\right]$$

(2.14)

where [54]

$$I_{SD0} = 2n_{ox} \left(\frac{W}{L}\right) U_T^2 \cdot exp\left(\frac{|V_{th}|}{n \cdot U_T}\right)$$

(2.15)

Therefore, the resistance of the pseudo-resistors can be described as [55]

$$R \simeq 2 \frac{L}{n\mu C_{ox}WU_T} exp\left(-\frac{(V_{GS} - V_{th} - nU_T)}{U_T}\right)$$

(2.16)

In the equations above, n is the slope factor,  $C_{ox}$  is the gate-oxide capacitance,  $\mu$  presents the mobility of free carriers,  $U_T$  is the thermal voltage. W/L represents the aspect ratio of the transistors, and the threshold voltage of the device is given as  $V_{th}$ . As it can be interpreted from the equations, the longer devices give smaller current flowing through the channel which results in higher resistance values.

Although the single device pseudo-resistors are easy-to-implement in layout, they show asymmetric behaviour by their nature. To overcome this issue, tunable pseudo-resistors are proposed. Instead of connecting the gate to the drain, a voltage source is used to control the gate voltage of the device [54], [56]. This makes the device controllable, yet the resistance values that can be achieved by this kind of structures is reduced to  $M\Omega$ -G $\Omega$  range [54]. That is a clear disadvantage for our design, where the cut-off frequency is wanted to be ideally at 0.1 Hz. Even with 100 G $\Omega$  feedback resistance, the cut-off frequency becomes around 16 Hz which might result in loss of valuable information about the cell activity.

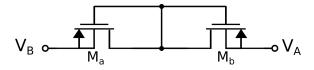

Therefore, to be able to achieve at least hundreds of  $100~\text{G}\Omega\text{s}$  with pseudo-resistors, nontunable structure is chosen. The impedance can be further increased by using 2 PMOS transistors in series [54], [56]. Another advantage of using 2 PMOS transistors in series is that improved linearity can be achieved by means of this structure. The aspect ratio is decided as  $250\text{nm}/18\mu\text{m}$  which gives the (almost) smallest value for W/L for each device. As a result of this small aspect ratio, the highest possible resistance value is expected. This expectation is confirmed by the simulation results. The schematic view is given Fig. 2.18, and Fig. 2.19 shows the layout of the pseudo-resistor elements. In Fig. 2.19, the letter "A" represents the transistor  $M_a$ , whereas  $M_b$  is highlighted with letter "B".

**Figure 2.18:** The schematic of pseudo-resistor designed in the system.

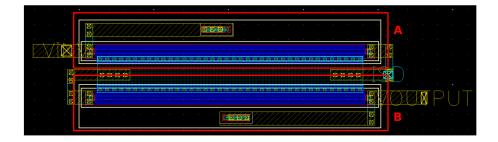

Figure 2.19: The layout view of pseudo-resistor elements designed in the system.

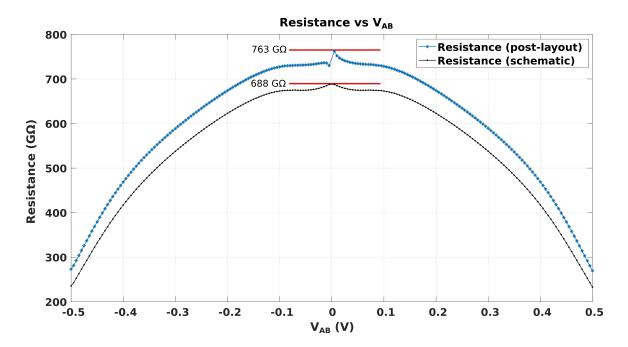

The schematic and post-layout simulation results of the resistance of pseudo-resistor elements are shown in Fig. 2.20. The resistance value is calculated as 688 G $\Omega$ s with nominal transistors in schematic view. After laying out the devices, the resistance value is found as 763 G $\Omega$ s. The reason of increased resistance value might be because of that the current that must flow through the channel may be directed to other nodes due to the parasitics. This might cause a decrease in current value which results in higher resistance values.

**Figure 2.20:** The comparison of schematic and post-layout simulation results of pseudoresistor elements.

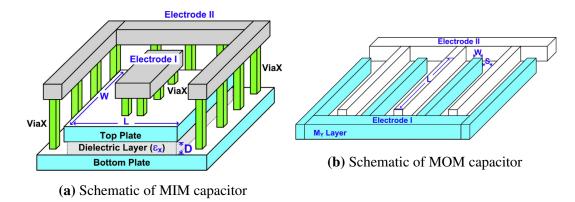

Figure 2.21: The illustrations show MIM and MOM capacitor structures (Taken from [57]).

#### 2.3.4. CCIA Capacitors

Capacitive feedback elements are the another critical sub-block in recording channel to be designed. In IC technology, three kinds of capacitance structures are widely used which are MOS capacitor, metal-oxide-metal (MOM) capacitor, and metal-insulator-metal (MIM) capacitor. MIM capacitors have a structure such that two parallel metal plates are insulated from each other with a dielectric material. MOM capacitor structures form the capacitance in metal interconnections in an interdigitated manner. The illustrations of these two kinds of capacitor are depicted in Fig 2.21 [57]. Due to the thin oxide layers in the gate, MOS capacitors provide the highest capacitance density among three structures. However, MOS capacitors show highly non-linear characteristics by their nature. Changes in gate voltage alter the gate capacitance. Also, they are very sensitive to process variations. As a result of that, MOS capacitors cannot be suitable for defining the ratio of  $C_s/C_f$ , so that the gain of the recording channel. This reduces the capacitance options from 3 to 2 as MOM and MIM capacitors.

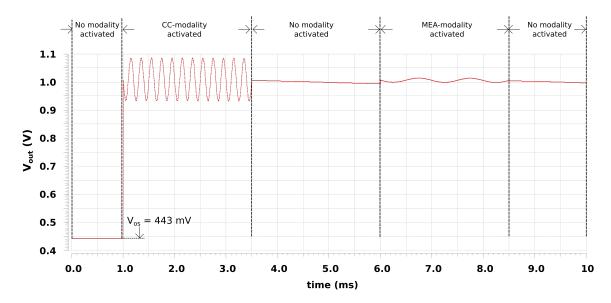

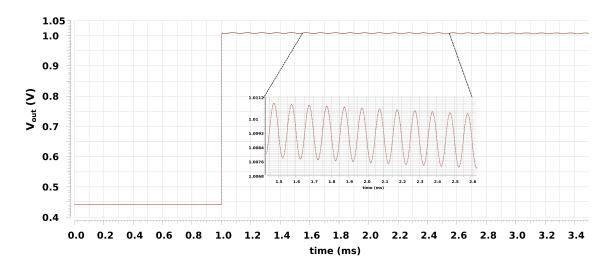

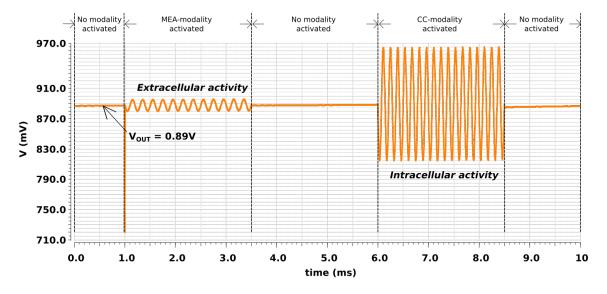

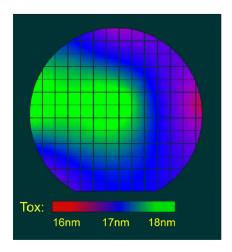

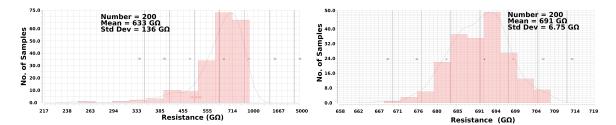

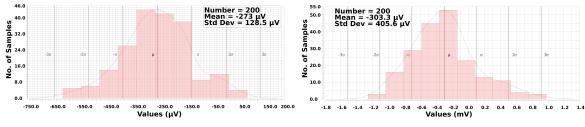

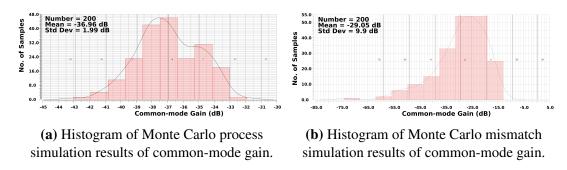

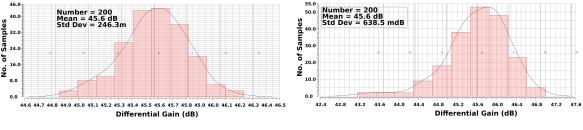

There are two main important aspects of choosing the feedback capacitor value and type. The first aspect is that the cut-off frequency of the high-pass filter configuration. The cut-off frequency and the capacitor value is inversely proportional to each other. In other words, to increase the recording capability in a few Hz range, the capacitance value must be increased. However, this brings up one issue in terms of an increase in area occupation on silicon. Therefore, 100 fF is chosen as the feedback capacitance to achieve  $f_{HP}$  around a few Hzs in the presence of hundreds of  $G\Omega$  of feedback resistance. Also, this makes the  $C_S$  3 pF to maintain 30 V/V closed-loop gain in the recording channel. Among MOM and MIM capacitors, MIM capacitors provide the higher capacitance density per unit area which results in smaller area consumption. MIM capacitor models gives  $1 fF/1 \mu m^2$  capacitance density. 3 pF of  $C_S$  covers around 60  $\mu m \times 70 \mu m$ , when MIM capacitor (model: mimcap-2p0-sin) is used. The same capacitance value occupies around 80  $\mu m \times 80 \mu m$  area, when MOM capacitor (model: crtmom) is implemented. As a result of this analysis, MIM capacitor is chosen to implement the capacitors with 100 fF and 3 pF.