# A Programmable-Gain Floating Inverter Low-Noise Amplifier for Ultrasound Imaging Analog Frontends

Dias, D.A.; Costa, Tiago; Goes, João

DOI

10.1109/ISCAS56072.2025.11043193

**Publication date**

2025

**Document Version**

Final published version

Published in

Proceedings of the 2025 IEEE International Symposium on Circuits and Systems (ISCAS)

Citation (APA)

Dias, D. A., Costa, T., & Goes, J. (2025). A Programmable-Gain Floating Inverter Low-Noise Amplifier for Ultrasound Imaging Analog Frontends. In *Proceedings of the 2025 IEEE International Symposium on Circuits and Systems (ISCAS)* (Proceedings - IEEE International Symposium on Circuits and Systems). IEEE. https://doi.org/10.1109/ISCAS56072.2025.11043193

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights.

We will remove access to the work immediately and investigate your claim.

# Green Open Access added to <u>TU Delft Institutional Repository</u> as part of the Taverne amendment.

More information about this copyright law amendment can be found at <a href="https://www.openaccess.nl">https://www.openaccess.nl</a>.

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A Programmable-Gain Floating Inverter Low-Noise Amplifier for Ultrasound Imaging Analog Frontends

$^{1,2} \mathrm{Diogo~Dias}^*, \, ^2 \mathrm{Tiago~Costa}, \, ^1 \mathrm{João~Goes}$

<sup>1</sup>DEEC, CTS-UNINOVA and LASI, School of Science and Technology, NOVA University of Lisbon, Caparica, Portugal <sup>2</sup>Bio-electronics Department, EEMCS, Delft University of Technology, Delft, The Netherlands \*das.dias@campus.fct.unl.pt/ddias@tudelft.nl

Abstract—Wearable ultrasound devices for imaging and therapeutic applications demand low-power and lowarea integrated circuits to interface with ultrasound transducers. In the case of ultrasound imaging frontends, discrete time-gain compensation (TGC) simplifies gain control in ultrasound imaging (USI) ASICs, but higher gain-step resolution increases area and power dissipation, while high PSRR is needed to suppress switching noise from co-integrated HV digital circuits. This work presents a programmable-gain floating inverter low-noise amplifier (FIALNA) architecture in 28nm CMOS for low-power, wide-bandwidth USI. A thermometer-encoded variable reservoir capacitance enables fine TGC with five PVT-robust gain steps, achieving 53.6dB PSRR and an area of 0.0023mm<sup>2</sup>, an order of magnitude smaller than current PGA designs. The FIALNA dissipates 116µW and achieves 59µVrms input-referred noise, making it suitable for low-power wearable ultrasound devices.

Index Terms—Discrete TGC, PGA, LNA, Floating Inverter Amplifier, Ultrasound Imaging, PMUT Matrix

#### I. Introduction

Vagus nerve stimulation (VNS) is a clinically approved therapy for epilepsy and treatment-resistant depression. Of the several methods to perform VNS, image-guided ultrasound neuromodulation (IGUN) offers the optimal compromise between non-invasiveness and precision [1, 2]. However, IGUN still relies on bulky equipment with form-factors [2] incompatible with wearable technologies, which hamper existing treatments. Recent advances in 2D US transducer arrays with integrated stimulation [3, 4] and imaging ASICs [5] allow for the miniaturization of IGUN systems and reduce reliance on expensive imaging techniques like MRI and CT, though integration and portability challenges remain for truly wearable US systems [1]. In VNS applications, one of such challenges is obtaining accurate ultrasound images of the vagus nerve such that its coordinates can be transferred to the neuromodulation sub-system. This, in turn, demands compact and powerefficient ultrasound receiver integrated circuit front-ends [2].

This work has been supported by Portuguese National Science and Technology Foundation (FCT) under the PhD grant UI/BD/153604/2022, and CTS multiannual funding program CTS/00066.

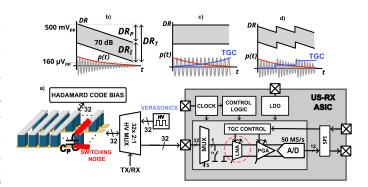

Fig. 1. a) USI system overview. b) Vagus nerve imaging application dynamic range breakdown, c) Continuous TGC readout US signal, d) Discrete TGC readout US signal.

Considering an average attenuation coefficient  $\alpha_T$  for soft tissue of approximately  $0.55 \text{ dB} \cdot (\text{MHz cm})^{-1}$  [6], imaging the vagus nerve (VN) imposes a propagation dynamic range  $(DR_P)$  up to 30dB at a typical center frequency  $f_0$  of 4MHz, given the average human neck radius (D = 7.6cm) [7, 8], which in turn require higher resolution analog-todigital converters and higher power consumption and area. Considering an instantaneous DR  $(DR_I)$  of 40dB for US signals, the total input DR can achieve 70dB (Fig. 1c) [5, 9]. Linear-in-dB time-gain compensation (TGC) enables the compression of the US signal's DR (Fig. 1b), and hence a relaxed DR of the analog frontend (AFE) [9]. Continuous TGC implementations (Fig. 1c) improve image quality but often rely on static current-mode variable-gain amplifiers (VGAs), which are prone to PVT variations without feedback and add complexity to gain control [10]. Programmable-gain amplifiers (PGAs) using discrete-gain steps (Fig. 1d) implemented through variable capacitance feedback networks greatly simplify gain control, while leading to significant power-dissipation overhead in widebandwidth USI ASICs [5, 9, 11]. Moreover, discrepancies between gain steps and US signal attenuation rates can cause imaging artifacts [10, 11]. Increased discrete TGC resolution greatly increases area in PGAs[10]. In-band supply noise from co-integrated circuits can degrade LNA performance, and although inverter OTAs reduce power dissipation, their poor PSRR requires regulated supply nodes, further increasing area and power dissipation[5, 9].

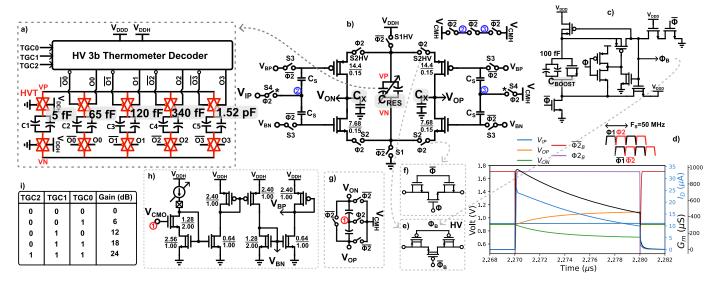

Fig. 2. a) Thermometer-encoding scheme for  $C_{RES}$  control, b) FIALNA topology, c) dynamic clock-boosting circuit, d) simulated transient waveforms, e) high-VT S2/S1 P-switches, f) standard-VT S2/S1 N-switches, g) output CM detector, h) output CM-controlled gate-biasing circuit, i) 3-bit discrete TGC function.

This work presents an open-loop LNA architecture using a programmable-gain floating inverter amplifier (FIALNA) in standard-bulk 28nm CMOS technology for low-power, wide-bandwidth USI. A variable-capacitance reservoir capacitor  $(C_{RES})$  enables discrete TGC via programmable capacitive source degeneration[11–13]. Fully-differential operation enhances PSRR, while thermometer encoding for  $C_{RES}$  ensures fine linear-in-dB gain steps without significant area overhead.

#### II. US IMAGING SYSTEM

The USI RX ASIC (Fig. 1a) integrates a 2D PMN-PT matrix using a row-column indexing scheme. Due to the 28nm standard bulk technology lacking high-voltage devices, integration with the 2D matrix is done at the PCB level. Each column is multiplexed into a single US RX channel in the ASIC. A coherent planar wave compounding (CPWC) imaging scheme performs RX beamforming in the digital backend [14], while a Fresnel lens modulates the RX sensitivity transfer function in the elevational (row) direction, performing row-level beamforming [15], with HV pulses and plane-wave angle-dependant 32b Hadamard code top-plate biasing (for Fresnel lens control) generated off-chip using a Verasonics machine.

#### III. PROPOSED PROGRAMMABLE GAIN LNA

The proposed LNA is based on a floating-inverter amplifier (FIA) (Fig. 2b) with thermometer-decoded programmable-capacitance  $C_{RES}$  (Fig. 2a) for linear-in-dB gain steps of 6dB (Fig. 2i). An analog voltage supply  $(V_{DDH})$  of 1.8V is used to facilitate the FIA's linearity when targetting the large input/output DR. HV device logic (Fig. 2a,e,f) enabled by a dynamic clock-boosting circuit (Fig. 2c) was used to allow proper switch-on/off near the HV supply and ensure circuit reliability. Dedicated gate-biasing

(Fig. 2h) is required to maintain the devices in weak inversion during the amplification phase ( $\Phi$ 2) due to the increased voltage headroom, reducing gain error [16]. The common-mode rejection ratio (CMRR), defined as CMRR(T<sub>S</sub>) =  $-2C_P/C_{RES}$  [17], is enhanced through parasitic capacitance equalization using anti-parallel MoM capacitors, with a complementary feedback circuit mitigating differential CM offset increase as  $C_{RES}$  decreases (Fig. 2g), thereby preserving the amplifier's linearity.

### A. Gain of the FIALNA

It has been shown that  $I_D(t)$  $I_{D,0^+}/\left(1+(t-T_S/2)/\tau_{w,i}\right)$  accurately represents the FIA's dynamic biasing current during  $\Phi$ 2 (Fig. 2d) [17, 18]. The parameter  $\tau_{w,i} = 2 \cdot C_{RES}/G_m(0^+)$ , where  $G_m(0^+)$  is the initial channel transconductance, us used to represent the time required for the inverter's devices to reach weak inversion, with its value dependent on the size of the reservoir capacitor and biasing current [17]. Due to the approximate relationship  $G_m \propto I_D$ , the average  $G_m/I_D$ value of the inverter's devices throughout the  $\Phi 2$  is used to approximate the inversion level during amplification as a constant value  $(G_m/I_D)_{avg} = \frac{1}{T_S} \int_0^{T_S} \frac{G_m}{I_D}(\tau) d\tau$ , simplifying the remaining steps of the analysis (1). Despising the finite output resistance of the FIA and noting that  $\Delta V_{OD}(t) \approx \frac{\Delta V_{ID}}{C_X} (G_m/I_D)_{avg} \int_0^t I_D(\tau) d\tau$ , we finally arrive at the gain expression for the FIA (2).

$$\int_{0}^{t} G_{m}(\tau)d\tau \approx \frac{G_{m}}{I_{D}} \left(I_{D}(t)T_{S} - I_{D,0^{+}}T_{S}\right) \approx (1)$$

$$\approx \frac{G_{m}}{I_{D}} \int_{avg}^{T_{S}} I_{D}(\tau)d\tau$$

$$A_v(T_S) \approx -\frac{2C_{RES1}}{C_X} \frac{(G_m/I_D)_{avg}}{(G_m/I_D)_{0+}} \cdot \ln\left(1 + \frac{T_S}{2\tau_{w,i}}\right) \quad (2)$$

## B. Noise Analyis

The FIA's total output-referred noise comprises sampled thermal noise,  $v_{tn,o}^2 = kT/C_X$  [ $V^2$ ], and sampled shot noise,  $i_{sn,o}^2 = 2qI_D(t)$  [ $A^2H_z^{-1}$ ]. The kT/C noise is reduced by a sufficiently large output capacitor ( $C_X = 100$  fF), while shot noise dominates as devices enter weak inversion, scaling with the dynamic bias current, aggravated to  $i_{sn,o}^2 = 4qI_{D,sat}(t)$  [ $A^2H_z^{-1}$ ] upon  $V_{DS} < 5kT/q$  [17, 19–21]. The input-referred noise is derived as in [16, 17], resulting in (3). As shown in (3), increasing  $C_{RES}$  reduces input-referred noise but raises power dissipation and area. Larger  $C_{RES}$  also increases  $\tau_{w,i}$ , which lowers  $(G_m/I_D)_{avg}$  during  $\Phi 2$ , counteracting noise reduction—an effect not well captured in previous analyses [16, 17]. Optimal noise suppression is achieved by biasing the inverter's devices into weak inversion since the start of  $\Phi 2$ .

$$\sigma_{i,d}^{2}(T_{S}) = \frac{\sigma_{o}^{2}(T_{S})}{(A_{V}(T_{S}))^{2}}$$

$$\approx \frac{4q (G_{m}/I_{D})_{0^{+}}}{C_{RES} \cdot \ln\left(1 + \frac{T_{S}}{2 \tau_{w,i}}\right) (G_{m}/I_{D})_{avg}^{2}} \frac{V^{2}}{Hz}$$

(3)

## C. Power-Supply Rejection Ratio of the FIALNA

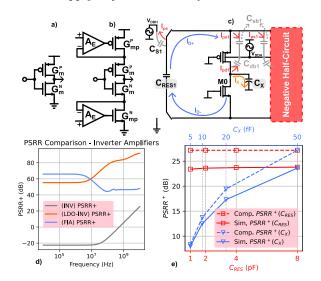

Fig. 3. a) Single-ended inverter amplifier, b) LDO-regulated single-ended inverter amplifier, c) FIA positive half-circuit used for PSRR analysis, d) single-ended inverter amplifiers PSRR comparison simulation, e) Comparison between simulated and computed single-ended FIA PSRR.

A comparison of the single-ended PSRR for a standard inverter, LDO-regulated inverter, and FIA (Fig. 3a,b,c, respectively) was performed using a dedicated simulaion testbench. Simulation parameters used were  $C_{RES} = 2 \text{pF}$ ,  $C_X = 50 \text{fF}$ , error amplifier gain of  $A_E = 80 \text{dB}$ , transistor finger widths  $F_{W,n}/F_{W,p} = 220/440 \text{nm}$ , channel length  $L_{ch} = 120 \text{nm}$ , number of fingers NF = 4, input frequency  $F_{in} = 100 \text{kHz}$ , and clock frequency  $F_S = 100 \text{MHz}$ . The error amplifier and switches were implemented using nonideal linear models. A 20 mV sinusoidal signal was applied to the positive rail, and output voltage was measured to

assess PSRR. The unregulated inverter acts as a commongate (CG) amplifier with PSRR inversely proportional to the gain (PSRR<sup>+</sup><sub>INV</sub> =  $|G_{ds}/(G_m + G_{ds})|$ ), while an LDO-regulated inverter shows improved PSRR directly proportional to the LDO open-loop gain (PSRR $^+_{LDO-INV} \approx$  $|G_{ds}(1+A_{E0})/(G_{m,p}+G_{ds,p})|$ ). For the FIA, a timedomain approach was used to obtain (4), where supply ripple affects output through sampled ripple  $(\Delta V_{ripple}(T_S/2) = \Delta V_{DD}(1 - e\{-T_S/(2 C_{RES} 2R_{ON,S1})\}))$ during reset phase  $(\overline{\Phi 2})$  and parasitic coupling during  $\Phi 2$ . The sampled ripple from the  $\overline{\Phi 2}$  features strong non-linear attenuation at high  $F_S$  and due to source-nodes discharging during  $\Phi$ 2, being despised in the analysis. From the KCL applied to the FIA's current-reuse loop (Fig. 3c), and computing the total charge redistributed during  $\Phi 2$ , we arrive at the single-ended PSRR of the FIA in (4), where the voltage transfer function is modeled as a CG amplifier, expressed as  $\Delta V_S(T_S) = \Delta V_X(T_S)/A_{V,CG}(T_S)$ , with  $A_{V,CG}(t) \approx -A_V(t)$ . Small device widths and ideal reset switches enable the PSRR of the FIA to acheive a similar performance to the LDO-regulated inverter (Fig. 3d), with the FIA's PSRR degrading as the supply ripple's frequency achieves similar orders of magnitude to  $F_S$ . Computed FIA PSRR features good agreement with simulated values (Fig. 3e). The 3dB error of (4) is associated with 1)the despise of the finite output impedance, 2) ideal resistive switches usage,3) CG amplifier A<sub>V,CG</sub>(T<sub>S</sub>) approximation, and 4) parasitic capacitance coupling due to S2 HVT switches (possible to be accounted for in  $C_{S1}$ ), further degradading (4). Finally, supply ripple sampled during  $\overline{\Phi 2}$  affects both FIA differential branches with the same magnitude and phase, enabling the achievement of differential PSRR values in the range of 50dB for this inverter-based topology, being mainly dependant on device mismatch  $(C_{db,sb} \pm \Delta C, \text{ and }$  $A_{V,CG} \pm \Delta A_{V,CG}$ ).

$$PSRR_{FIA}^{+}(T_S) \approx \left| \frac{C_X + C_{db,1} + \frac{C_{S1}/2 + 2C_{sb,1}}{A_{V,CG}(T_S)}}{C_{db,1} + C_{S1}/2 + 2C_{sb,1}} \right|$$

(4)

### D. Design and Trade-offs

DC decoupling anti-parallel MoM capacitors ( $C_S = 500 \mathrm{fF}$ , total 1pF) are employed to independently establish the common-mode of the PMUT array sensors while allowing the multiplexed RX channel to be grounded during the US TX phase [17].  $C_{RES}$  is set to approximately 2pF, enabling a maximum gain setting of 21dB, while device widths are optimized for minimum bandwidth ( $\omega_{p1}(t) = 1/(R_{out}(t)C_X) = G_m(t)/(A_V(t)C_X)$ ), designed at half the sampling rate ( $F_S/2$ ) to facilitate wide-band USI. A dedicated gate-biasing circuit stabilizes the FIA's devices ( $|V_{GS}| - |V_T|$ ) at approximately 50mV, thereby minimizing sensitivity to PVT variations and input-referred noise due to the increased logarithmic gain compression [16].

# IV. SIMULATION RESULTS

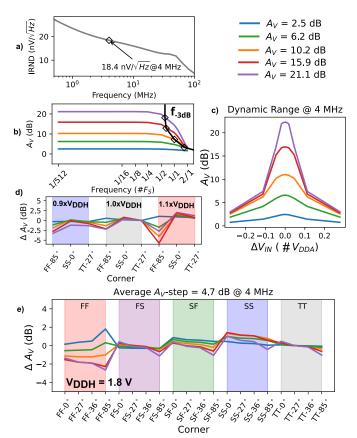

Schematic simulations were obtained with 2048 points transient at conservative settings (Fig. 4). A differential

PSRR of 53.6dB is achieved, efficiently decoupling supply noise from the output differential signal (Tab. I). Noise simulations show an input-referred noise density (IRND) of  $18.4 \text{nV}/\sqrt{\text{Hz}}$  at a center frequency of  $f_0 = 4 \text{MHz}$  (Fig. 4a), leading to 59μVrms single-ended (118μVrms differential) input-referred noise  $(v_{n,rms})$ , allowing the detection of a 70dB DR, 80µV single-ended US signal. The differential LNA topology doubles the input-referred noise, aggravated by the lack of negative feedback and a reduced  $C_{RES}$ for area optimization, explaining the increased noise floor. Enhancing the open-loop gain of the base FIA design [16] and employing noise-cancelling techniques using the DC-decoupled AFE's cascaded gain stages [22] leads to a reduction the impact of input-referred noise in the AFE at the cost of a reduced output-swing. Increasing TX pulse voltage amplitude to raise TX power, thereby offsetting the total 70dB DR to higher voltage levels (Fig. 1b), can also mitigate the impact of noise. The use of HVT transmission gates slightly increases gain at low settings due to the increased parasitic capacitance at VP and VN nodes, but ultimately reduces overall gain across all settings due to the additional resistive source degeneration (Fig. 2a). Increased output capacitance due to the CM detector circuit (Fig. 2g), further reduces each gain-step, resulting in a discrete TGC function with five PVT-robust gain steps averaging 4.7dB (Fig. 4b,c,d). The -3dB bandwidth  $f_{-3dB}$ , inversely proportional to  $C_{RES}$  (Fig. 4b), is established at  $F_S/2$  in the maximum gain setting  $(f_{-3dB} = 26.5 \text{MHz})$  for  $F_S = 50 \text{MHz} - 2 \times \text{higher than the reported SOTA (Tab.)}$ I). Cascaded low-pass filtering stages can enforce  $f_{-3dB}$  at  $F_S/2$  for lower gain settings of the FIALNA. At a maximum gain of 21.1dB, the measured total harmonic distortion (THD) at the 1dB gain-compression point was -46.4dB for a 35mV single-ended input amplitude, a value within state-of-the-art (SOTA) results (Fig. 4c). The extreme FF process corner at  $85^{\circ}$ C and a +10% supply voltage variation ( $V_{DDH} = 1.98V$ ) collapses FIALNA gain due to significantly decreased  $G_m/I_D$  during  $\Phi 2$  (Fig. 4d), compensated through the external current source (Fig. 2h). A  $|\Delta A_V|$  < 3dB across all gain settings (Fig. 4d,e) is achievable in the remaining PVT corners.

#### V. Conclusions

An open-loop FIALNA in 28nm standard-bulk CMOS for a wide-bandwidth USI ASIC employing a programmable reservoir capacitor was proposed, achieving 53.6dB differential PSRR while eliminating LDO-regulator area and power-dissipation overhead. The variable capacitive source degeneration was implemented using a thermometer encoding scheme for the control of  $C_{RES}$ , leading to an estimated area of  $0.0023 \mathrm{mm}^2$ , representing an improvement by an order of magnitude comparing to the reported PGA SOTA for USI applications (Tab. I). A total dissipated power of  $116\mu\mathrm{W}$  at a  $1.8\mathrm{V}$  supply was achieved, leading to a nominal noise efficiency factor (NEF) of 4.7 (5) - considering the  $26.8\mu\mathrm{Arms}$  current biasing the FIALNA devices in the

Fig. 4. a) Simulated input-referred noise-density (IRND), b) gain transfer function at -3dB BW, c) input DR and gain compression, d) gain variation  $\Delta A_V$  vs. supply voltage variations, e)  $\Delta A_V$  vs. process-and-temperature corners (at nominal supply: 1.8V).

maximum gain setting. The presented FIALNA enables area and energy-efficient readout of 70dB DR input single-ended signals, converting them to differential (maximizing the SNDR of the AFE) while allowing for a enhanced-resolution, linear-in-dB, discrete TGC function - easing the DR specification of the subsequent interface circuits and minimizing the impact on 2D and 3D USI quality.

TABLE I STATE-OF-THE-ART COMPARISON

| Work                                            | [23]         | [9]            | [24](SCMF)   | This Work*   |

|-------------------------------------------------|--------------|----------------|--------------|--------------|

| Tech. (nm)                                      | 350          | 180            | 180          | 28           |

| TGC                                             | Discrete     | Discrete       | Discrete     | Discrete     |

| Closed-Loop                                     | Yes          | Yes            | Yes          | No           |

| Differential                                    | Yes          | No             | Yes          | Yes          |

| Supply (V)                                      | 3.3          | 1.8            | 1.8          | 1.8          |

| Dynamic                                         | No           | No             | No           | Yes          |

| $A_V$ (dB)                                      | 31.0/16.0    | 22.5/4.7/-13.2 | 26.6         | 21.1/15.9/   |

|                                                 |              |                |              | 10.2/6.2/2.5 |

| $f_{-3\ dB}@A_{V,max}(MHz)$                     | 6.6          | 9.8            | 7.0          | 26.5         |

| $f_0(MHz)$                                      | 2.5          | 4.0            | 3.0          | 4            |

| $THD_{1 \ dB \ Comp.}$ (dB)                     | -40@34.5mVin | -40@273mVin    | -51.5@35mVin | -46.4@35mVin |

| $@A_{V,max}$                                    |              | $(@A_{V,min})$ |              |              |

| $PSRR@f_0$ (dB)                                 | NA           | 45.8           | NA           | 53.6         |

| IRND@ $f_0$ (nV/ $\sqrt{\text{Hz}}$ )           | 5.42         | 5.9            | 5.3          | 18.4         |

| $P_D \text{ (mW)}$                              | 0.900        | 0.135          | 0.270        | 0.116        |

| NEF                                             | 6.8          | 3.0            | 4.3          | 4.7          |

| Area/                                           | 0.0340       | 0.0100         | NA           | 0.0023**     |

| US RX Channel(mm <sup>2</sup> )                 | 0.0340       | 0.0100         | IVA          | 0.0023       |

| *Simulation Results, **Estimated from schematic |              |                |              |              |

$NEF = v_{n,rms} \sqrt{\frac{2I_{TOTAL}}{4\pi k T U_T B W}}$  (5)

### References

- [1] A. Fomenko *et al.*, "Low-intensity ultrasound neuromodulation: An overview of mechanisms and emerging human applications," *Brain Stimul.*, vol. 11, no. 6, pp. 1209–1217, Nov. 2018.

- [2] S. A. Lee et al., "Displacement imaging during focused ultrasound median nerve modulation: A preliminary study in human pain sensation mitigation," *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 68, no. 3, pp. 526–537, 2021.

- [3] T. Costa *et al.*, "An integrated 2d ultrasound phased array transmitter in cmos with pixel pitch-matched beamforming," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 15, no. 4, pp. 731–742, 2021.

- [4] H. Rivandi et al., "A 2d ultrasound phased-array transmitter asic for high-frequency us stimulation and powering," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 17, no. 4, pp. 701–712, 2023.

- [5] C. Chen et al., "A front-end asic with receive sub-array beamforming integrated with a  $32 \times 32$  pzt matrix transducer for 3-d transesophageal echocardiography," *IEEE JSSC*, vol. 52, no. 4, pp. 994–1006, 2017.

- [6] C. M. I. Quarato et al., "A review on biological effects of ultrasounds: Key messages for clinicians," *Diagnostics*, vol. 13, no. 5, p. 855, Feb. 2023. http: //dx.doi.org/10.3390/diagnostics13050855

- [7] L. L. Ben-Noun et al., "Neck circumference as a simple screening measure for identifying overweight and obese patients," Obesity Research, vol. 9, no. 8, pp. 470–477, 2001. https://onlinelibrary.wiley.com/doi/abs/10.1038/ob y.2001.61

- [8] B. Moura et al., "Neck and waist circumference values according to sex, age, and body-mass index: Brazilian longitudinal study of adult health (elsa-brasil)," Brazilian Journal of Medical and Biological Research, vol. 53, no. 10, 2020. http://dx.doi.org/10.1590/1414-431X20209815

- [9] C. Chen et al., "A compact 0.135-mw/channel lna array for piezoelectric ultrasound transducers," in 2015 IEEE 41st ESSCIRC Conf., 2015, pp. 404–407.

- [10] P. Guo et al., "A pitch-matched low-noise analog front-end with accurate continuous time-gain compensation for highdensity ultrasound transducer arrays," *IEEE JSSC*, vol. 58, no. 6, pp. 1693–1705, 2023.

- [11] Z. Yu et al., "Front-end receiver electronics for a matrix transducer for 3-d transesophageal echocardiography," IEEE TUFFC, vol. 59, no. 7, pp. 1500-1512, 2012.

- [12] I. Choi et al., "Accurate db-linear variable gain amplifier with gain error compensation," *IEEE JSSC*, vol. 48, no. 2, pp. 456–464, 2013.

- [13] M. S. Akter et al., "A capacitively degenerated 100-db linear 20–150 ms/s dynamic amplifier," *IEEE JSSC*, vol. 53, no. 4, pp. 1115–1126, 2018.

- [14] G. Montaldo et al., "Coherent plane-wave compounding for very high frame rate ultrasonography and transient elastography," *IEEE TUFFC*, vol. 56, no. 3, pp. 489–506, 2009.

- [15] K. Latham *et al.*, "Simultaneous azimuth and fresnel elevation compounding: A fast 3-d imaging technique for

- crossed-electrode arrays,"  $IEEE\ TUFFC,$  vol. 65, no. 9, pp.  $1657-1668,\ 2018.$

- [16] R. S. A. Kumar et al., "Analysis and design of a discrete-time delta-sigma modulator using a cascoded floating-inverter-based dynamic amplifier," *IEEE JSSC*, vol. 57, no. 11, pp. 3384–3395, 2022.

- [17] X. Tang et al., "An energy-efficient comparator with dynamic floating inverter amplifier," *IEEE JSSC*, vol. 55, no. 4, pp. 1011–1022, 2020.

- [18] R. S. Ashwin Kumar, "Analysis of stability, noise, and design guidelines for a cascaded floating-inverter amplifier," *IEEE TCAS-II*, vol. 71, no. 9, pp. 4126–4130, 2024.

- [19] K. H. Lundberg, "Noise sources in bulk cmos," 2002. https://api.semanticscholar.org/CorpusID:18751943

- [20] P. Nuzzo et al., "Noise analysis of regenerative comparators for reconfigurable adc architectures," IEEE TCAS-I: Regular Papers, vol. 55, no. 6, pp. 1441–1454, 2008.

- [21] H. S. Bindra et al., "A 1.2-v dynamic bias latch-type comparator in 65-nm cmos with 0.4-mv input noise," *IEEE JSSC*, vol. 53, no. 7, pp. 1902–1912, 2018.

- [22] J. Liu et al., "A 13-bit 0.005-mm2 40-ms/s sar adc with kt/c noise cancellation," *IEEE JSSC*, vol. 55, no. 12, pp. 3260-3270, 2020.

- [23] G. Peyton et al., "Quadrature synthetic aperture beamforming front-end for miniaturized ultrasound imaging," IEEE TBioCAS, vol. 12, no. 4, pp. 871–883, 2018.

- [24] Z. Cao et al., "Design of fully differential energy-efficient inverter-based low-noise amplifier for ultrasound imaging," in 2021 IFIP/IEEE 29th VLSI-SoC, 2021, pp. 1–6.