### Computer Engineering

Mekelweg 4, 2628 CD Delft The Netherlands http://ce.et.tudelft.nl/

### MSc THESIS

### Hardware Design and Implementation of a Network-on-Chip Based High Performance Crossbar Switch Fabric

Turhan Karadeniz

#### Abstract

High-performance routers have the task of transmitting traffic in between the nodes of the Internet, the network of networks that carries the vast amount of information among billions of users. The switch fabric is the key building block of every router, and various switch fabric architectures are used in the market products. The crossbarbased switch fabric architectures (both buffered and unbuffered) offer very high performances and are widely used for high-performance routers. However their cost grows quadratically with the input/output port count, since they require internal crosspoints (and buffers) for every input/output port pair.

Recently, a functional-level design of two novel Network-on-Chip based switch fabric architectures was proposed, Unidirectional NoC (UDN) and Multidirectional NoC (MDN), as a replacement of the buffered crossbar switch fabric architecture. In this thesis, we propose the hardware design and implementation of the aforementioned architectures for the FPGA platform. We further improve the routing and scheduling algorithms of these architectures for feasible hardware design. The synthesis and simulations are carried out over a wide range of switch sizes and traffic scenarios. The simulation results are also validated on the FPGA platform, by generating pseudo-

random destination addresses for the packets on LFSR based test modules. The results show that UDN outperforms MDN in terms of throughput, whereas MDN offers greater performance-cost ratio. Both architectures offer scalability, flexibility and high performance, confirming the ideas in the original proposal.

CE-MS-2010-9

### Hardware Design and Implementation of a Network-on-Chip Based High Performance Crossbar Switch Fabric

### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

COMPUTER ENGINEERING

by

Turhan Karadeniz born in Kastamonu, Turkey

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

### Hardware Design and Implementation of a Network-on-Chip Based High Performance Crossbar Switch Fabric

#### by Turhan Karadeniz

#### Abstract

High-performance routers have the task of transmitting traffic in between the nodes of the Internet, the network of networks that carries the vast amount of information among billions of users. The switch fabric is the key building block of every router, and various switch fabric architectures are used in the market products. The crossbar-based switch fabric architectures (both buffered and unbuffered) offer very high performances and are widely used for high-performance routers. However their cost grows quadratically with the input/output port count, since they require internal crosspoints (and buffers) for every input/output port pair.

Recently, a functional-level design of two novel Network-on-Chip based switch fabric architectures was proposed, Unidirectional NoC (UDN) and Multidirectional NoC (MDN), as a replacement of the buffered crossbar switch fabric architecture. In this thesis, we propose the hardware design and implementation of the aforementioned architectures for the FPGA platform. We further improve the routing and scheduling algorithms of these architectures for feasible hardware design. The synthesis and simulations are carried out over a wide range of switch sizes and traffic scenarios. The simulation results are also validated on the FPGA platform, by generating pseudo-random destination addresses for the packets on LFSR based test modules. The results show that UDN outperforms MDN in terms of throughput, whereas MDN offers greater performance-cost ratio. Both architectures offer scalability, flexibility and high performance, confirming the ideas in the original proposal.

**Laboratory** : Computer Engineering

Codenumber : CE-MS-2010-9

Committee Members :

Advisor: Kees Goossens, ES, TU/e

Advisor: Lotfi Mhamdi, CE, TU Delft

Chairperson: Koen Bertels, CE, TU Delft

Member: Rene van Leuken, CAS, TU Delft

Member: Said Hamdioui, CE, TU Delft

## Contents

| Li            | st of                  | Figures                                         | vii                    |

|---------------|------------------------|-------------------------------------------------|------------------------|

| $\mathbf{Li}$ | $\operatorname{st}$ of | Tables                                          | x                      |

| N             | omer                   | nclature                                        | xi                     |

| A             | ckno                   | wledgements                                     | xiii                   |

| D             | edica                  | tion                                            | $\mathbf{x}\mathbf{v}$ |

| 1             | Intr                   | $\mathbf{r}$ oduction                           | 1                      |

|               | 1.1                    | Thesis Overview                                 | 1                      |

|               | 1.2                    | Motivation                                      | 3                      |

|               |                        | 1.2.1 Problem Statement                         | 3                      |

|               |                        | 1.2.2 The Thesis Contributions                  | 4                      |

|               | 1.3                    | Thesis Outline                                  | 5                      |

| <b>2</b>      | Bac                    | kground Information & Related Work              | 7                      |

|               | 2.1                    | Introduction                                    | 7                      |

|               | 2.2                    | Switch Fabric Architectures                     | 8                      |

|               | 2.3                    | Emergence of Network on Chip (NoC)              | 10                     |

|               | 2.4                    | Network on Chip                                 | 11                     |

|               | 2.5                    | Communication Technologies, Protocols & Packets | 15                     |

| 3             | $\mathbf{U}\mathbf{D}$ | N/MDN Hardware Design                           | 17                     |

|               | 3.1                    | UDN/MDN Overview                                | 17                     |

|               | 3.2                    | U(M)DN Packet Organization                      | 19                     |

|               | 3.3                    | Input Buffers (FIFOs)                           | 20                     |

|               | 3.4                    | Network Interface (NI)                          | 21                     |

|               |                        | 3.4.1 Input Network Interface                   | 21                     |

|               |                        | 3.4.2 Output Network Interface                  | 22                     |

|               | 3.5                    | UDN Router Design                               | 24                     |

|               |                        | 3.5.1 Router Types                              | 25                     |

|               |                        | 3.5.2 UDN Router Architecture                   | 30                     |

|               | 3.6                    | Instantiating Routers and NIs in the UDN Switch | 31                     |

|               | 3.7                    | MDN Router Design                               | 34                     |

|               | 3.8                    | MDN Virtual Channels                            | 34                     |

|               | 3.9                    | Instantiating Routers and NIs in the MDN Switch | 36                     |

| 4  | UD    | N/MDN Routing & Scheduling                            | 41        |

|----|-------|-------------------------------------------------------|-----------|

|    | 4.1   | Routing in UDN and MDN Switches                       | 41        |

|    |       | 4.1.1 UDN Routing Algorithm: UDN XY Modulo            | 43        |

|    |       | 4.1.2 MDN Routing Algorithm: MDN XY Modulo            | 44        |

|    | 4.2   | Scheduling in UDN and MDN Switches                    | 46        |

|    |       | 4.2.1 UDN Scheduling                                  | 47        |

|    |       | 4.2.2 MDN Scheduling                                  | 50        |

| 5  | UD    | N/MDN Synthesis                                       | <b>51</b> |

|    | 5.1   | UDN Synthesis Results                                 | 52        |

|    | 5.2   | MDN Synthesis Results                                 | 54        |

|    | 5.3   | UDN/MDN Comparison                                    | 59        |

| 6  | UD    | N/MDN Simulations                                     | 61        |

|    | 6.1   | Simulation Environment                                | 61        |

|    |       | 6.1.1 Traffic Types                                   | 61        |

|    | 6.2   | UDN Simulations                                       | 62        |

|    |       | 6.2.1 Simulations under Bernoulli Uniform Traffic     | 63        |

|    |       | 6.2.2 Simulations under Unbalanced (Weighted) Traffic | 67        |

|    | 6.3   | MDN Simulations                                       | 70        |

|    |       | 6.3.1 Simulations under Bernoulli Uniform Traffic     | 71        |

|    |       | 6.3.2 Simulations under Unbalanced (Weighted) Traffic | 74        |

|    | 6.4   | Comparison of Arbiter Schemes                         | 76        |

|    | 6.5   | Increasing Throughput with T-Value                    | 79        |

| 7  | UD    | N/MDN Performance & Cost Analysis                     | 87        |

|    | 7.1   | Defining the Performance & Cost Functions             | 87        |

|    |       | 7.1.1 Performance                                     | 87        |

|    |       | 7.1.2 Cost                                            | 87        |

|    |       | 7.1.3 Performance / Cost                              | 87        |

|    | 7.2   | UDN Performance & Cost Analysis                       | 88        |

|    | 7.3   | MDN Performance & Cost Analysis                       | 91        |

|    | 7.4   | UDN/MDN Comparison                                    | 94        |

| 8  | In-C  | Circuit Verification                                  | 97        |

|    | 8.1   | LFSR (Linear Feedback Shift Registers) for Testing    | 97        |

|    | 8.2   | FPGA Validation                                       | 98        |

| 9  | Con   | nclusion                                              | 101       |

| Bi | bliog | graphy                                                | 106       |

# List of Figures

| <ul> <li>the Internet, a Network of Networks</li> <li>the Router Block Diagram</li> <li>Switch Architectures</li> <li>Buffered Crossbar and NoC Based Crossbar Switch Architectures</li> <li>Shared-Bus Switch Architecture</li> <li>Shared-Memory Switch Architecture</li> <li>Crossbar Switch Architecture</li> <li>Network-on-Chip Switch Fabric</li> <li>Example of a Deadlock, on a Mesh Topology [1]</li> <li>Packetization on the Network Interface</li> <li>ISO/OSI 7 Layer Model, the Abstraction Layers</li> <li>Diagram of the UNI ATM Packet, where the top row denotes the rof bits. [2]</li> <li>Unidirectional NoC</li> <li>Multidirectional NoC</li> <li>U(M)DN Packet Structure, where the top row denotes the number</li> </ul> |                                                      | 2<br>3<br>4<br>9<br>9<br>10<br>12<br>13<br>14<br>15<br>16 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|

| 1.3 Switch Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      | 9<br>9<br>10<br>12<br>13<br>14<br>15                      |

| 1.4 Buffered Crossbar and NoC Based Crossbar Switch Architectures 2.1 Shared-Bus Switch Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      | 9<br>10<br>12<br>13<br>14<br>15                           |

| <ul> <li>2.2 Shared-Memory Switch Architecture</li> <li>2.3 Crossbar Switch Architecture</li> <li>2.4 Network-on-Chip Switch Fabric</li> <li>2.5 Example of a Deadlock, on a Mesh Topology [1]</li> <li>2.6 Packetization on the Network Interface</li> <li>2.7 ISO/OSI 7 Layer Model, the Abstraction Layers</li> <li>2.8 Diagram of the UNI ATM Packet, where the top row denotes the of bits. [2]</li> <li>3.1 Unidirectional NoC</li> <li>3.2 Multidirectional NoC</li> </ul>                                                                                                                                                                                                                                                                 |                                                      | 9<br>10<br>12<br>13<br>14<br>15                           |

| <ul> <li>2.3 Crossbar Switch Architecture</li> <li>2.4 Network-on-Chip Switch Fabric</li> <li>2.5 Example of a Deadlock, on a Mesh Topology [1]</li> <li>2.6 Packetization on the Network Interface</li> <li>2.7 ISO/OSI 7 Layer Model, the Abstraction Layers</li> <li>2.8 Diagram of the UNI ATM Packet, where the top row denotes the of bits. [2]</li> <li>3.1 Unidirectional NoC</li> <li>3.2 Multidirectional NoC</li> </ul>                                                                                                                                                                                                                                                                                                                |                                                      | 10<br>12<br>13<br>14<br>15                                |

| <ul> <li>2.4 Network-on-Chip Switch Fabric</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      | 12<br>13<br>14<br>15                                      |

| <ul> <li>2.5 Example of a Deadlock, on a Mesh Topology [1]</li> <li>2.6 Packetization on the Network Interface</li> <li>2.7 ISO/OSI 7 Layer Model, the Abstraction Layers</li> <li>2.8 Diagram of the UNI ATM Packet, where the top row denotes the of bits. [2]</li> <li>3.1 Unidirectional NoC</li> <li>3.2 Multidirectional NoC</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      | 13<br>14<br>15<br>16                                      |

| <ul> <li>2.6 Packetization on the Network Interface</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                      | 14<br>15<br>16                                            |

| <ul> <li>2.7 ISO/OSI 7 Layer Model, the Abstraction Layers</li> <li>2.8 Diagram of the UNI ATM Packet, where the top row denotes the of bits. [2]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | number                                               | 15<br>16                                                  |

| <ul> <li>2.8 Diagram of the UNI ATM Packet, where the top row denotes the rof bits. [2]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 16                                                        |

| of bits. [2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      |                                                           |

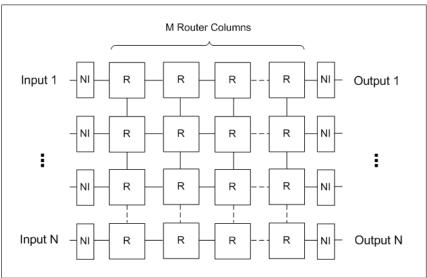

| 3.1 Unidirectional NoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      |                                                           |

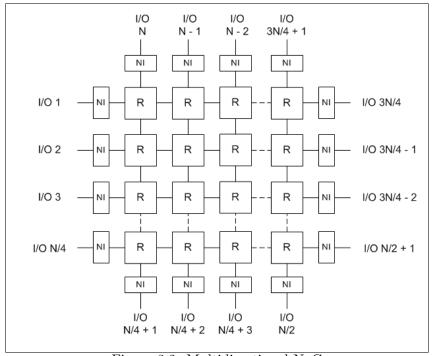

| 3.2 Multidirectional NoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      | 18                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                      |                                                           |

| 2 2 II(M)DN Dealest Structure whom the ter new deserted the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      | 18                                                        |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      | 20                                                        |

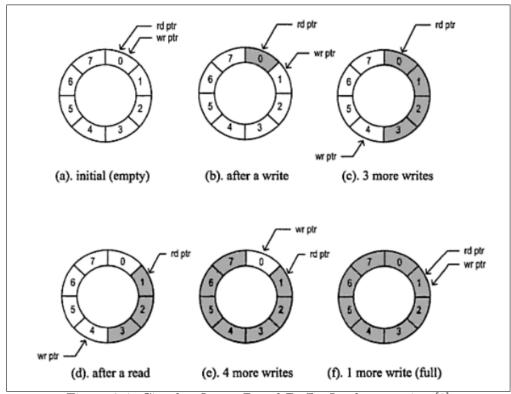

| 3.4 Circular Queue Based Buffer Implementation [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      | 21                                                        |

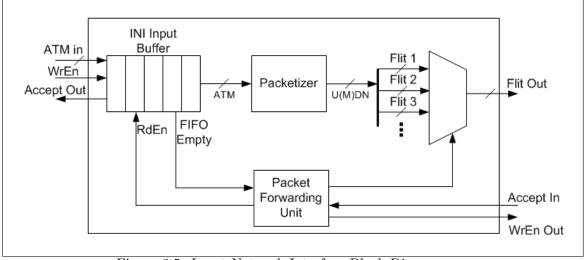

| 3.5 Input Network Interface Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      | 22                                                        |

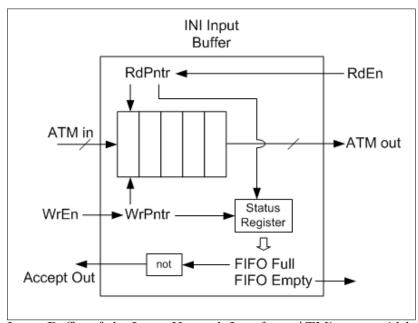

| 3.6 Input Buffer of the Input Network Interface: ATMin port width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                           |

| bytes, and FlitOut port width 9-bytes. PFU selects individual fli                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                           |

| the U(M)DN packet and serializes the transfer to the next routers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | 23                                                        |

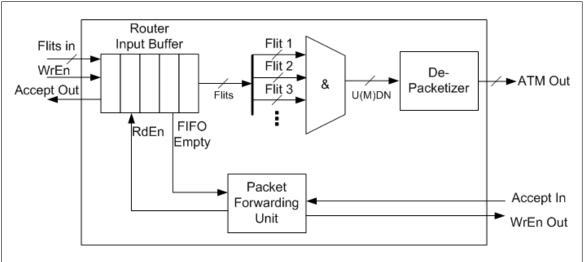

| 3.7 Output Network Interface Block Diagram: ATMout port width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                      |                                                           |

| bytes, and FlitIn port width 9-bytes. The ATM packet is stripped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                      | 2.4                                                       |

| the U(M)DN Wrapper and ejected to the output line card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      | 24                                                        |

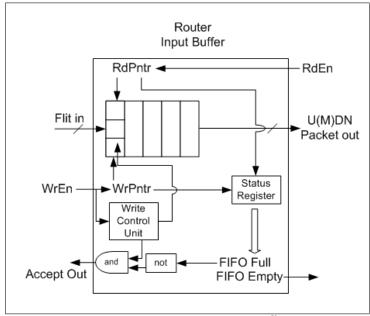

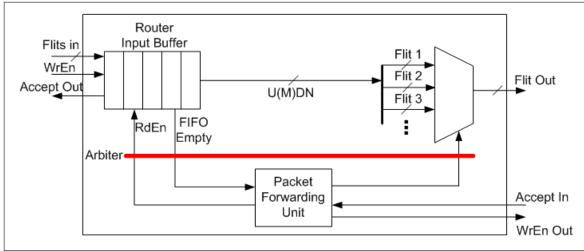

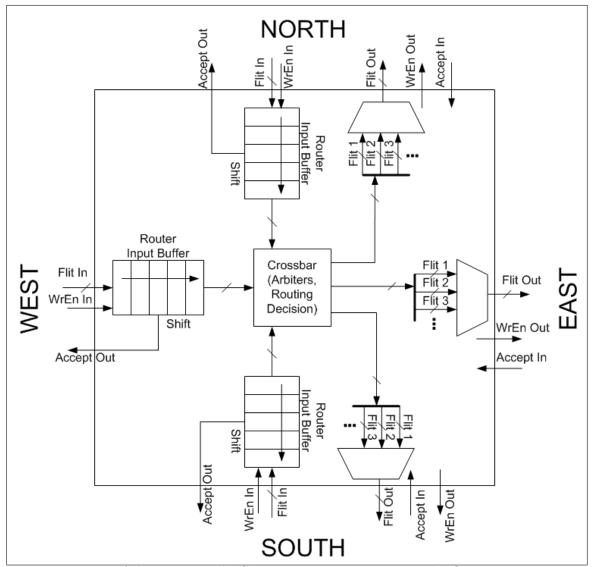

| 3.8 Router Input Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      | 25                                                        |

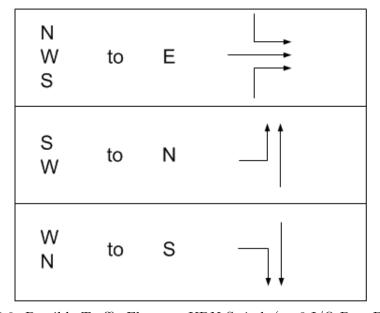

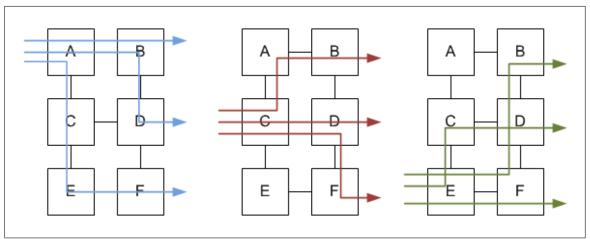

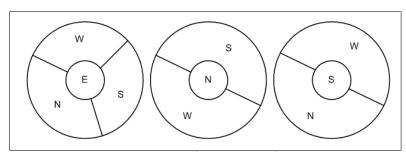

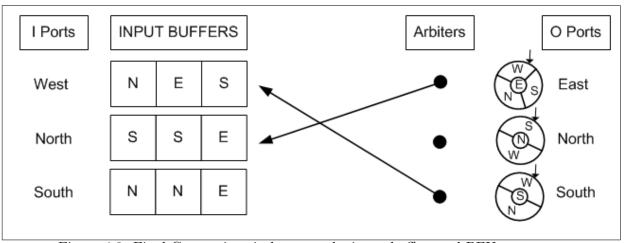

| 3.9 Possible Traffic Flows on UDN Switch (on 3 I/O Port Routers) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      | 25                                                        |

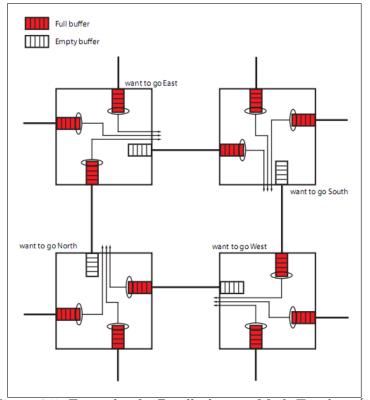

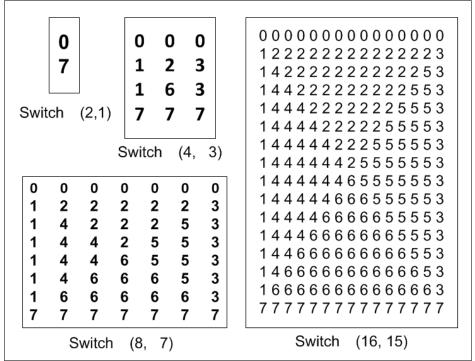

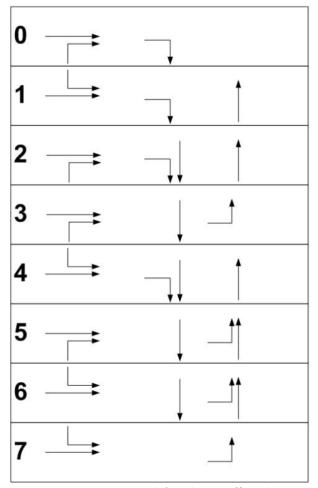

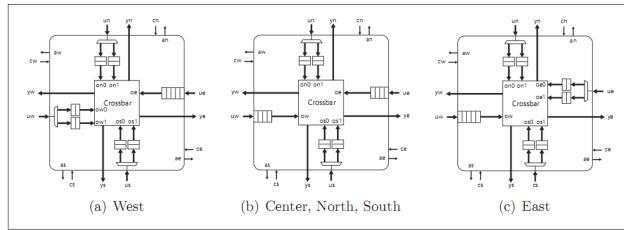

| 3.10 Routers with Different Traffic Flows over Various Switch Sizes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      | 26                                                        |

| 3.11 Legend for the Traffic Flows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | 27                                                        |

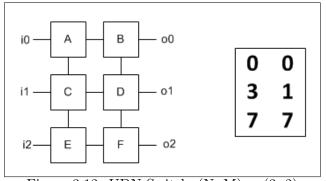

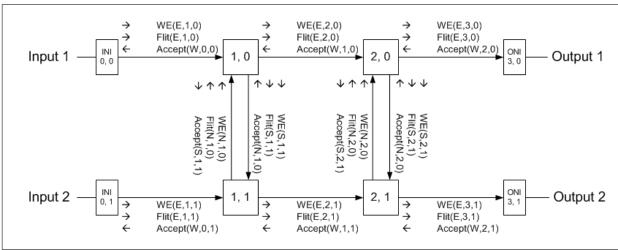

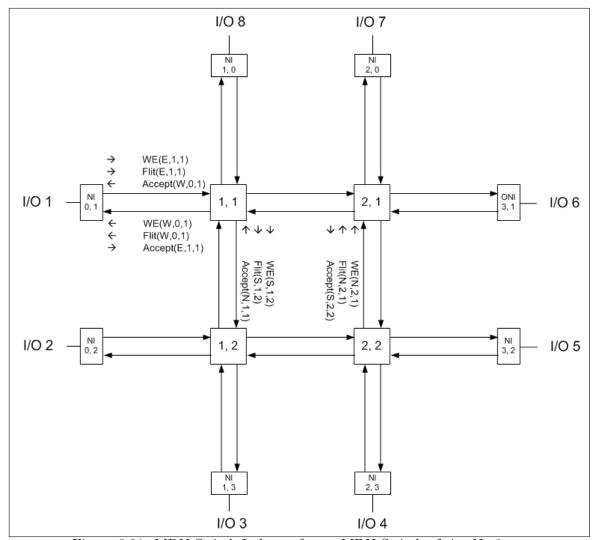

| 3.12 UDN Switch, $(N, M) = (3, 2) \dots $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                      | 27                                                        |

| 3.13 Routing Paths in a UDN Switch, over UDN XY Modulo Routing A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                    |                                                           |

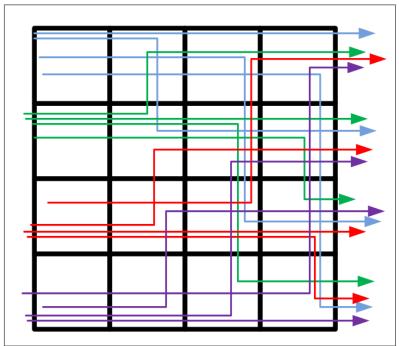

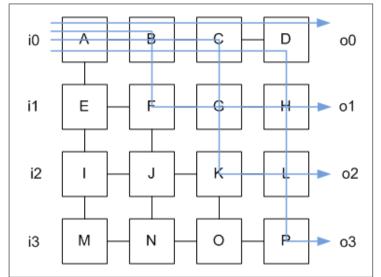

| 3.14 All routing paths on the switch, N=M=4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      | 30                                                        |

| 3.15 3 I/O Port UDN Router, Top-Level Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      | 31                                                        |

| 3.16 Arbiter, Virtually Connecting an Input Port to the Output Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      | 32                                                        |

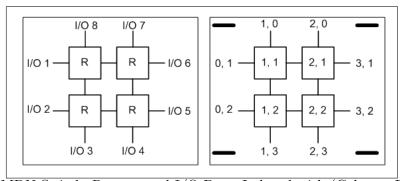

| 3.17 UDN Switch Indexes, for a UDN Switch of Size (2, 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      | 33                                                        |

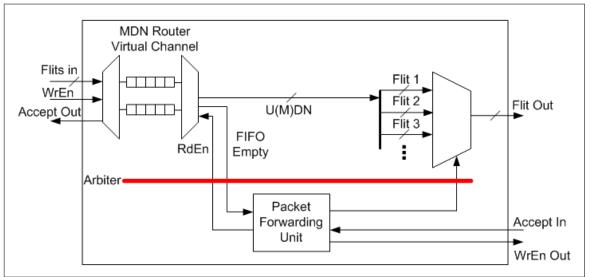

| 3.18 Virtual Channels in the MDN Routers [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      | 35                                                        |

| 3.19 Virtual Channel for an Input Ports of MDN Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      | 35<br>36                                                  |

| 3.20 Multidirectional NoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      | 36<br>37                                                  |

| 4.1 XY Modulo Routing on UDN and MDN Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                      | 42                                                        |

| 4.2  | MDN Switch, Routers and I/O Ports Indexed with (Column, Row) Indices   | 44  |

|------|------------------------------------------------------------------------|-----|

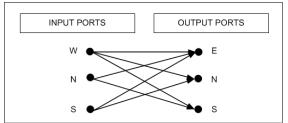

| 4.3  | Bipartite Graph Matching Problem in UDN                                | 47  |

| 4.4  | RRRs for All Output Ports (Inner Circle), and the Input Ports that can |     |

|      | access the respective output ports (Outer Circle)                      | 47  |

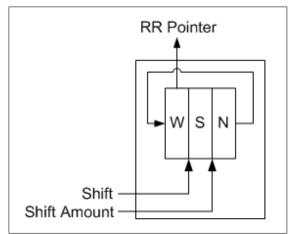

| 4.5  | Implementation of the East RRR for 3 I/O Port UDN Router               | 48  |

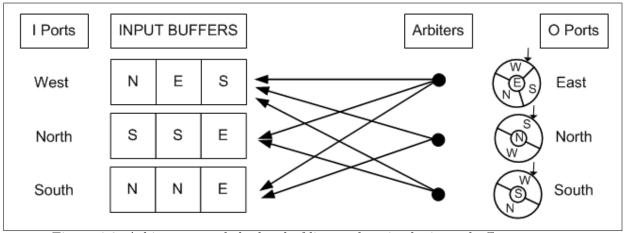

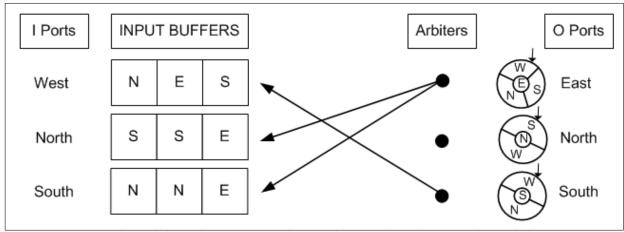

| 4.6  | Arbiters control the head-of-line packets in the input buffers         | 48  |

| 4.7  | The valid combinations are kept, whereas the others are discarded      | 49  |

| 4.8  | Final Connections in between the input buffers and PFUs                | 49  |

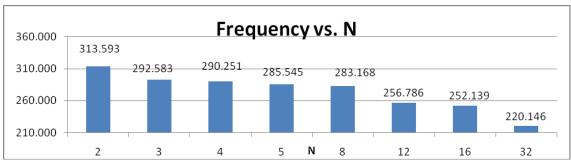

| 5.1  | Frequency Results for various $(N, 1)$ Switches                        | 53  |

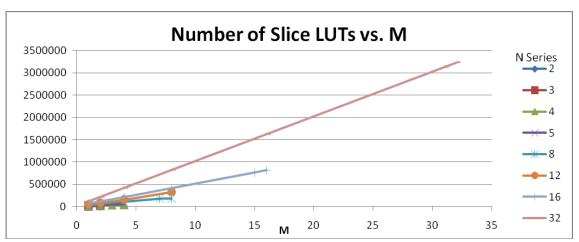

| 5.2  | Number of Slice LUTs vs. M                                             | 54  |

| 5.3  |                                                                        | 55  |

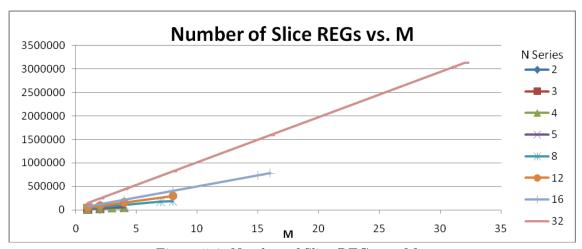

| 5.4  | Number of Slice REGs vs. M                                             | 56  |

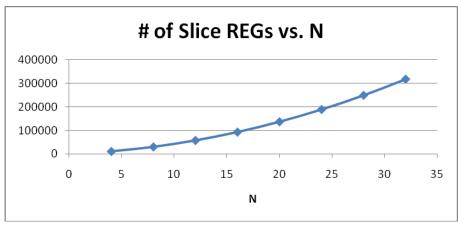

| 5.5  | Number of Slice REGs vs. N                                             | 56  |

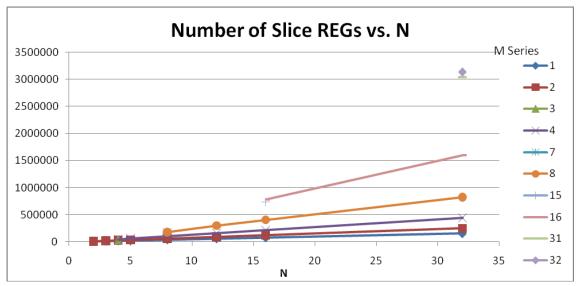

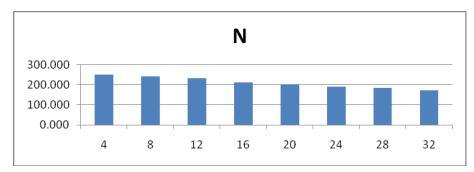

| 5.6  | Frequency vs. N, in MDN                                                | 57  |

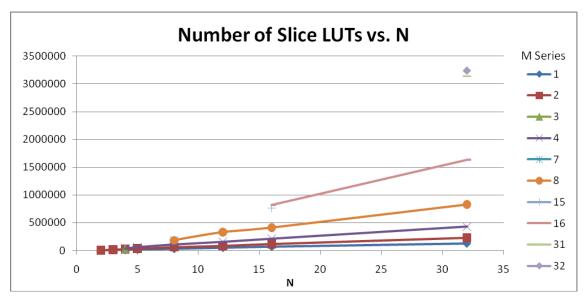

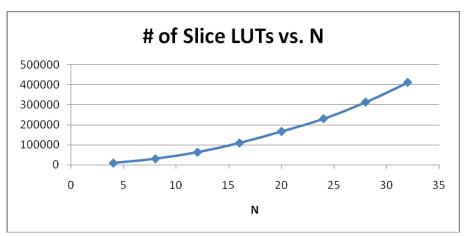

| 5.7  | Number of Slice LUTs vs. N, in MDN                                     | 58  |

| 5.8  | Number of Slice Registers vs. N, in MDN                                | 58  |

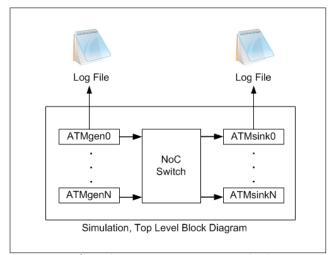

| 6.1  | Simulation Environment Block Diagram                                   | 62  |

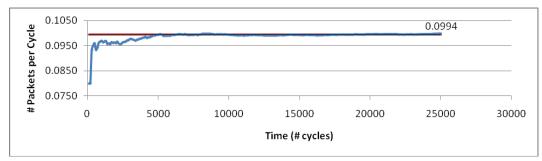

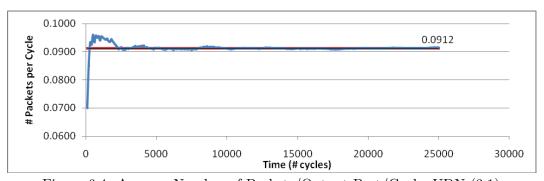

| 6.2  | Average Number of Packets/Output Port/Cycle, UDN (2,1)                 | 63  |

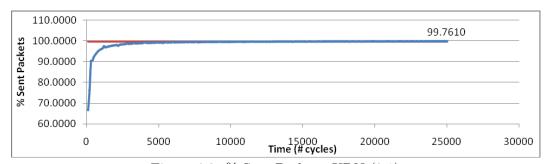

| 6.3  | % Sent Packets, UDN (2,1)                                              | 63  |

| 6.4  | Average Number of Packets/Output Port/Cycle, UDN (3,1)                 | 63  |

| 6.5  | % Sent Packets, UDN (2,1)                                              | 64  |

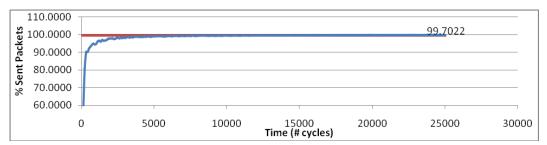

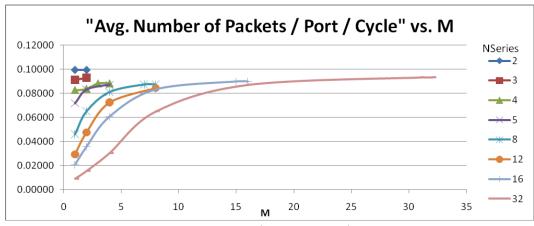

| 6.6  | , , , , , , , , , , , , , , , , , , , ,                                | 65  |

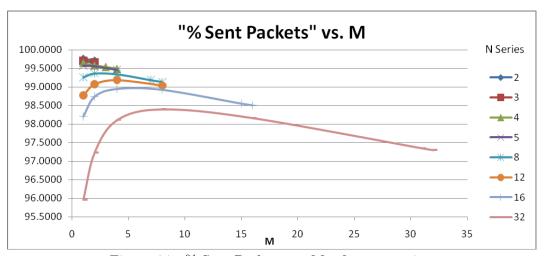

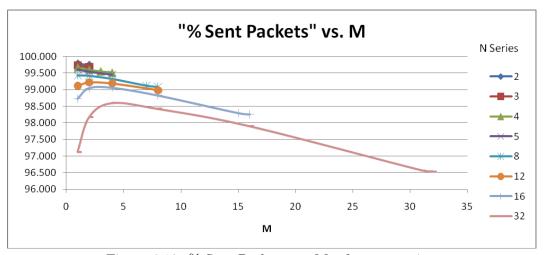

| 6.7  | % Sent Packets vs. M, after saturation                                 | 65  |

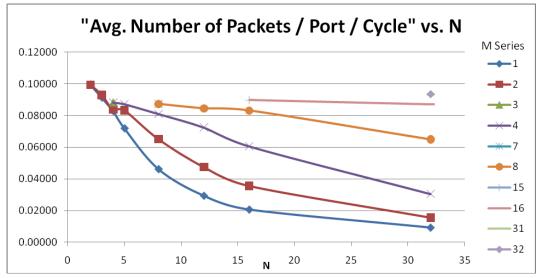

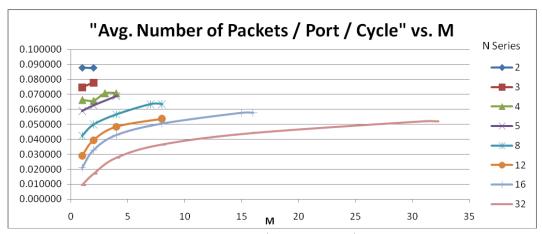

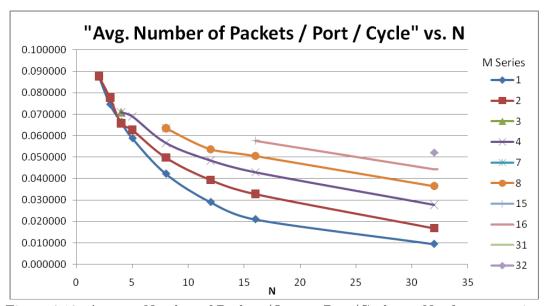

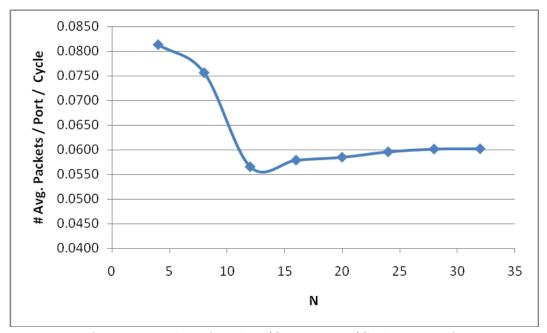

| 6.8  | Average Number of Packets/Output Port/Cycle vs. N, after saturation .  | 66  |

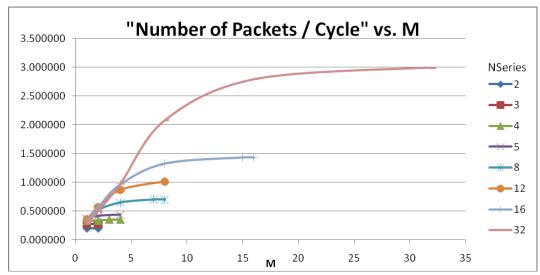

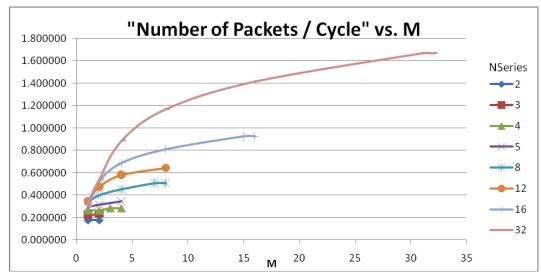

| 6.9  | Number of Packets/Cycle vs. M, after saturation                        | 67  |

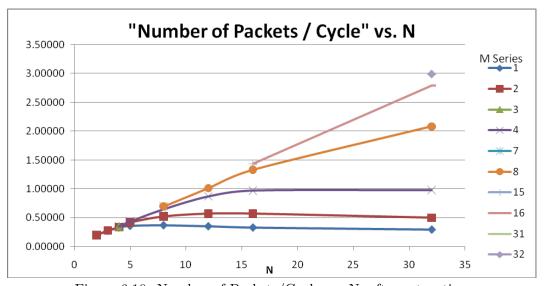

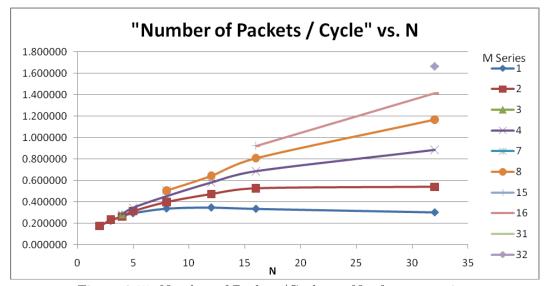

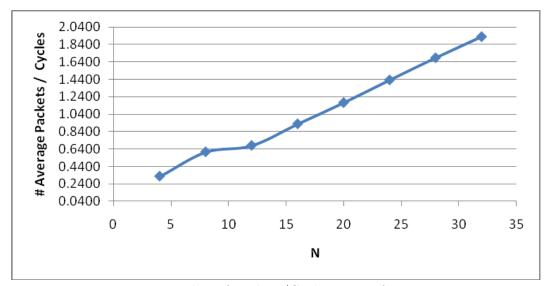

| 6.10 | Number of Packets/Cycle vs. N, after saturation                        | 67  |

| 6.11 | Average Number of Packets/Output Port/Cycle vs. M, after saturation .  | 68  |

| 6.12 | % Sent Packets vs. M, after saturation                                 | 69  |

| 6.13 | Average Number of Packets/Output Port/Cycle vs. N, after saturation .  | 70  |

| 6.14 | Number of Packets/Cycle vs. M, after saturation                        | 71  |

|      |                                                                        | 71  |

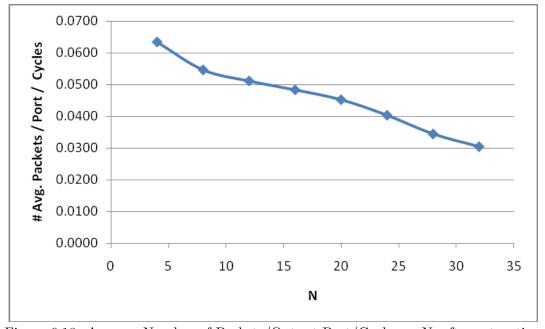

| 6.16 | Average Number of Packets/Output Port/Cycle vs. N, after saturation .  | 72  |

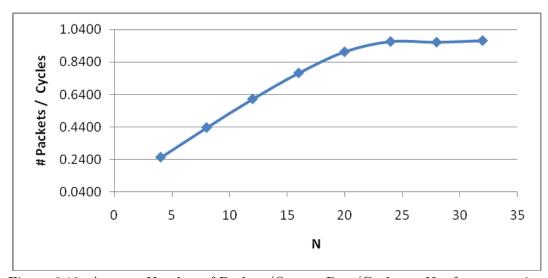

| 6.17 | Number of Packets/Cycle vs. N, after saturation                        | 73  |

| 6.18 | Average Number of Packets/Output Port/Cycle vs. N, after saturation .  | 74  |

| 6.19 | Average Number of Packets/Output Port/Cycle vs. N, after saturation .  | 75  |

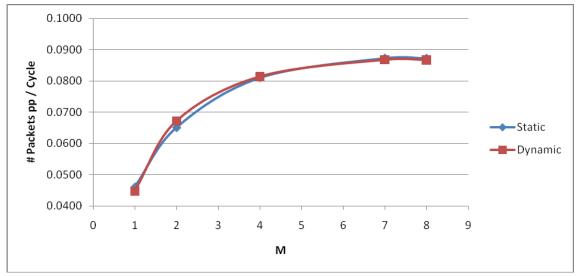

| 6.20 | Performance Comparison of Static and Dynamic Arbitration               | 76  |

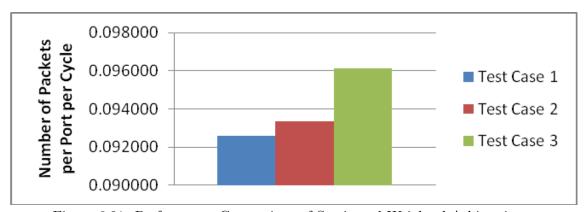

| 6.21 | Performance Comparison of Static and Weighted Arbitration              | 79  |

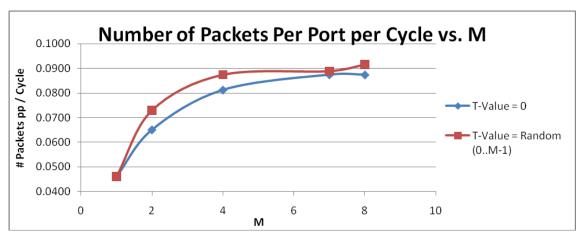

| 6.22 | Evaluation and comparison of two cases: T-Values=0 and T-              | 0.0 |

| 0.00 |                                                                        | 80  |

|      |                                                                        | 81  |

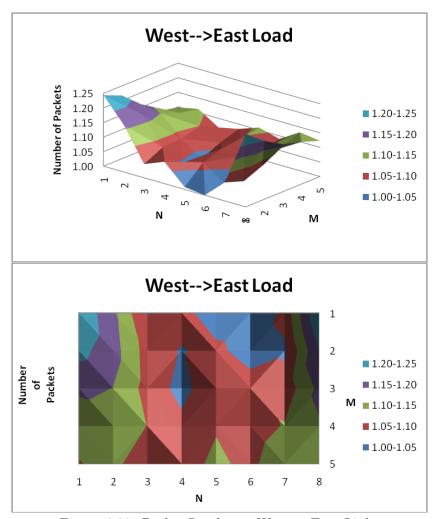

|      |                                                                        | 82  |

|      |                                                                        | 83  |

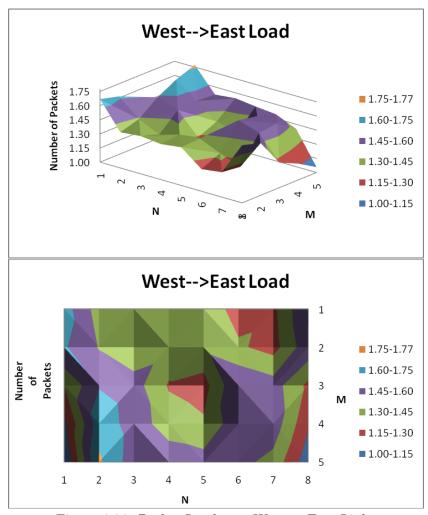

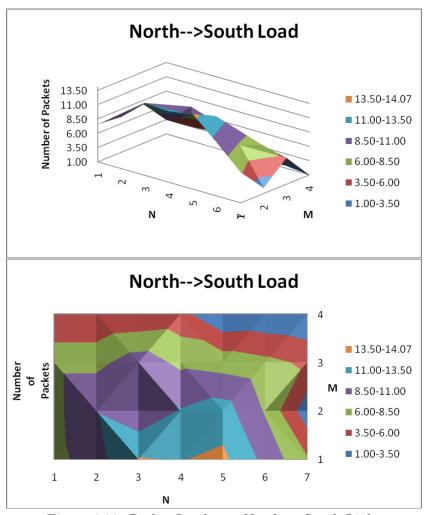

| 6.26 | Packet Load over West to East Links                                    | 84  |

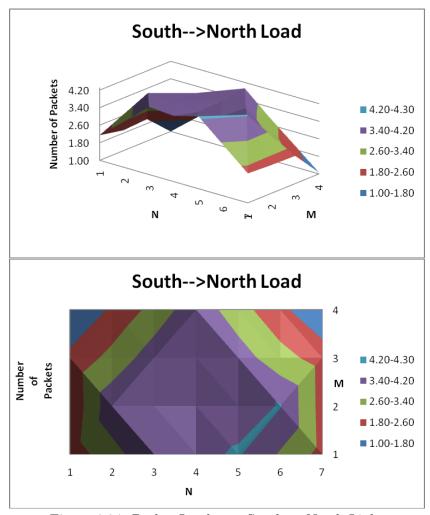

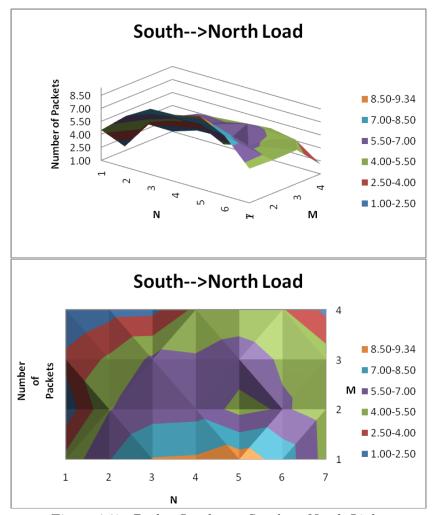

| 6.27 | Packet Load over South to North Links              | 85 |

|------|----------------------------------------------------|----|

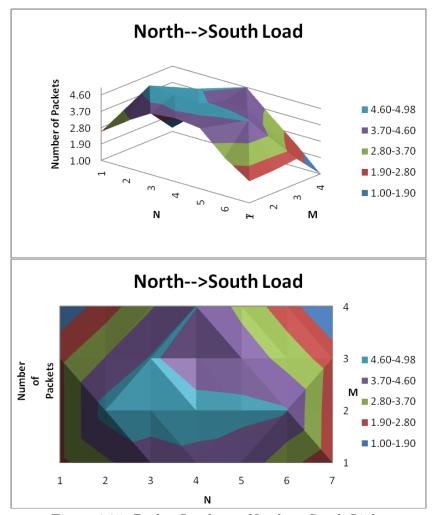

| 6.28 | Packet Load over North to South Links              | 86 |

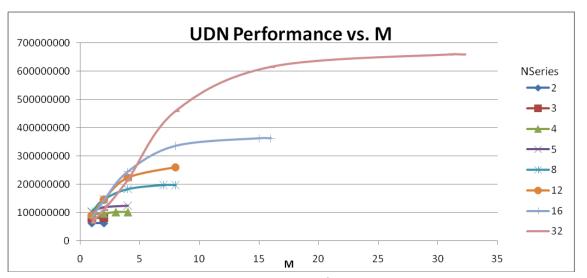

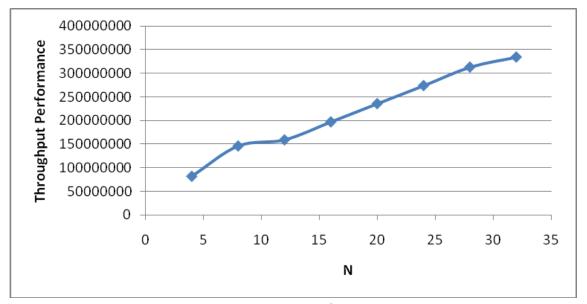

| 7.1  | UDN Performance                                    | 88 |

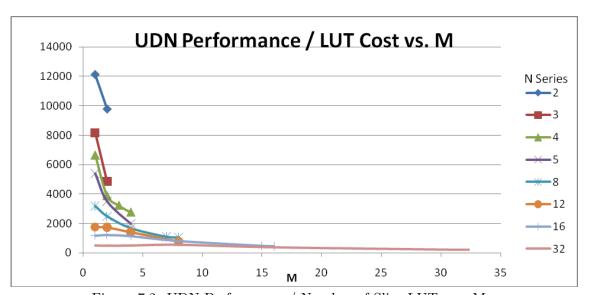

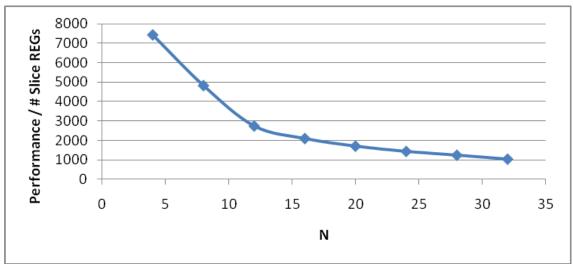

| 7.2  | UDN Performance / Number of Slice LUTs vs. M       | 90 |

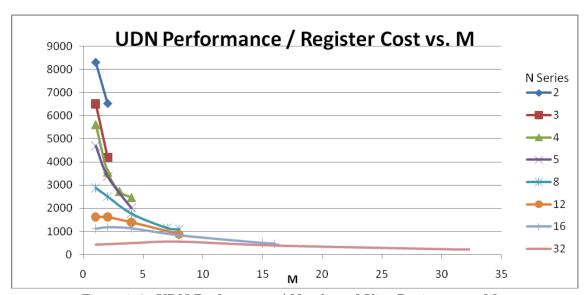

| 7.3  | UDN Performance / Number of Slice Registers vs. M  | 91 |

| 7.4  | MDN Performance                                    | 92 |

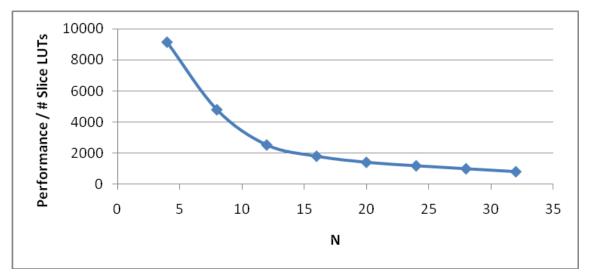

| 7.5  | MDN Performance / Number of Slice LUTs vs. N       | 94 |

| 7.6  | MDN Performance / Number of Slice Registers vs. N  | 95 |

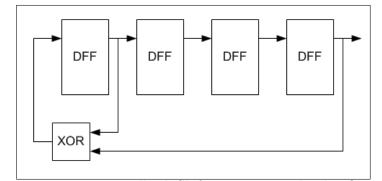

| 8.1  | Linear Feedback Shift Registers, with 1-bit Output | 97 |

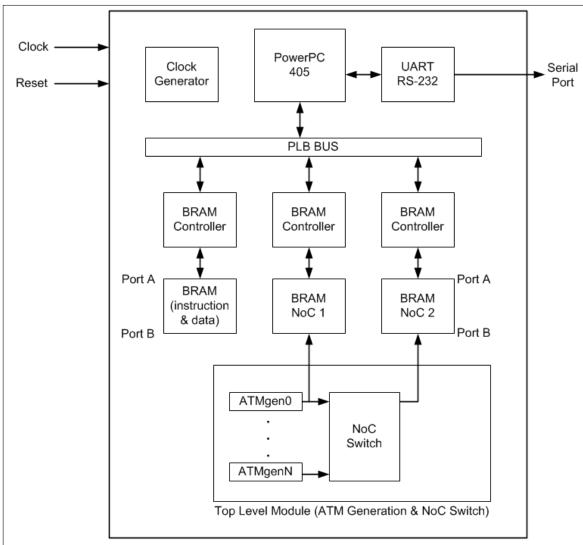

| 8.2  | Block Diagram for FPGA Validation System           | 99 |

# List of Tables

| 3.1  | List of Routers in the Routing Path of the I/O Port Pairs                          | 28 |

|------|------------------------------------------------------------------------------------|----|

| 3.2  | List of Port Pairs on the path in between the Switch's I/O Pairs                   | 28 |

| 3.3  | Traffic Flows on Individual Routers                                                | 29 |

| 3.4  | Frequency of Traffic Flows on Router Types                                         | 29 |

| 5.1  | Synthesis Results for individual UDN Modules                                       | 52 |

| 5.2  | Frequency Results for various (N, M) Switches in MHz                               | 53 |

| 5.3  | Number of Slice LUTs for various (N, M) Switches                                   | 54 |

| 5.4  | Number of Slice REGs for various (N, M) Switches                                   | 55 |

| 5.5  | Synthesis Results for individual MDN Modules                                       | 55 |

| 5.6  | Frequency Results for various MDN Switches                                         | 57 |

| 5.7  | Number of Slice LUTs for various MDN Switches                                      | 57 |

| 5.8  | Number of Slice Registers for various MDN Switches                                 | 58 |

| 5.9  | UDN and MDN Switch Comparison                                                      | 59 |

| 6.1  | Average Number of Packets/Output Port/Cycle, after saturation                      | 64 |

| 6.2  | % Sent Packets, after saturation                                                   | 64 |

| 6.3  | Number of Packets/Cycle                                                            | 66 |

| 6.4  | Average Number of Packets/Output Port/Cycle, after saturation                      | 68 |

| 6.5  | % Sent Packets, after saturation                                                   | 68 |

| 6.6  | Number of Packets/Cycle                                                            | 70 |

| 6.7  | Average Number of Packets/Output Port/Cycle, after saturation                      | 72 |

| 6.8  | Number of Packets/Cycle, after saturation                                          | 73 |

| 6.9  | Average Number of Packets/Output Port/Cycle, after saturation                      | 74 |

| 6.10 | Average Number of Packets/Output Port/Cycle, after saturation                      | 75 |

|      | Performance Comparison of Static and Dynamic Arbitration                           | 76 |

|      | Performance Comparison of Static and Weighted Arbitration                          | 79 |

| 6.13 | Evaluation and comparison of two cases: T-Values= $0$ and T-Values=Random $(0M-1)$ | 80 |

|      |                                                                                    |    |

| 7.1  | UDN Performance                                                                    | 88 |

| 7.2  | Number of Slice LUTs for various (N, M) Switches                                   | 89 |

| 7.3  | Number of Slice REGs for various (N, M) Switches                                   | 89 |

| 7.4  | UDN Performance / Number of Slice LUTs Cost                                        | 90 |

| 7.5  | UDN Performance / Number of Slice REGs Cost                                        | 91 |

| 7.6  | MDN Performance                                                                    | 92 |

| 7.7  | Number of Slice LUTs for various MDN Switches                                      | 93 |

| 7.8  | Number of Slice Registers for various MDN Switches                                 | 93 |

| 7.9  | MDN Performance / Number of Slice LUTs Cost                                        | 93 |

| 7.10 | MDN Performance / Number of Slice REGs Cost                                        | 94 |

|      | Comparison of Synthesis Results                                                    | 95 |

| 7 12 | Comparison of Simulation Results                                                   | 96 |

|      | Comparison of Performance and Performance/Cost                      |    |

|------|---------------------------------------------------------------------|----|

| 7.14 | Throughput Performance in Gbytes / sec                              | 96 |

| 8.1  | List of Generated Random Values on a 4-Bit LFSR, with Seed = $1101$ | 98 |

### Nomenclature

CICQ Combined Input-Crosspoint Queueing

**FIFO** First In First Out

FPGA Field Programmable Gate Array

FSM Finite State Machine

HOL Head-of-Line Blocking

IC Integrated Circuit

INI Input Network Interface

LAN Local Area Network

**LUT** Lookup Table

MDN Multidirectional Network-on-Chip

NINetwork InterfaceNoCNetwork-on-Chip

ONI Output Network Interface PFU Packet Forwarding Unit RAM Random Access Memory

RR Round Robin

RRR Round Robin Register

**UDN** Unidirectional Network-on-Chip

VC Virtual Channel

# Acknowledgements

First of all, I would like to thank my supervisors, Kees Goossens and Lotfi Mhamdi, for their guidance all through the MSc project.

It was very helpful of Vlad-Mihai Sima, Yi Lu, and Dimitris Theodoropoulos to help me with the problems I have experienced with the design tools.

I would also like to thank Iria Varela Senin, for her work "Design of a High-Performance Buffered Crossbar Switch Fabric Using Network on Chip", which formed the basis for my thesis.

Last, but not least, I would like to thank Koen Bertels, Said Hamdioui and Rene Van Leuken for taking part in my graduation committee.

Turhan Karadeniz Delft, The Netherlands June 25, 2010

### Dedication

#### I dedicate this thesis to

my mother, who showed me the simple ways to find joy in life, my father, who got me interested in wondering about the ways of life, my grandmother Tulay, who grew me up, in my beloved city of Istanbul, my grandfather Rafet, who taught me the real meaning of affection and sentimentality, my drop of life Damla, with whom I will make the best of life, as well as the best wine,

and my lifelong colleagues, Onur Can Ulusel, Stavros Tzilis,

and my lifelong mentors,

Nurdan Ugural,

Nino Carella,

Lou Ungemach,

Cengiz Agalar,

Erkay Savas,

Ilker Hamzaoglu,

Georgi Gaydadjiev,

and last, but not least, Serkan Sahin.

Turhan Karadeniz Delft, The Netherlands June 25, 2010

Introduction

This chapter describes the motivation and objectives of this thesis. First, it gives an overview of the background information that forms the basis for this research. Then, it describes the problem statement and the thesis contributions. Finally, it presents the outline for the following chapters.

### 1.1 Thesis Overview

The Internet has become the backbone of communication among the billions of users all over the world, connecting networks of different sizes, purposes and scopes. The Internet is defined as the network of networks (Figure 1.1), and it carries information and services among the vast number of nodes. The communication among these networks and nodes is realized by a broad and diverse body of electronic and optical technology. The routers have the task of transmitting the traffic to the destination nodes, through the best possible route. The links in between the routers and the nodes has to transmit the data as fast as possible, while the routers provide the bandwidth to ensure that they are not a bottleneck in the network communication.

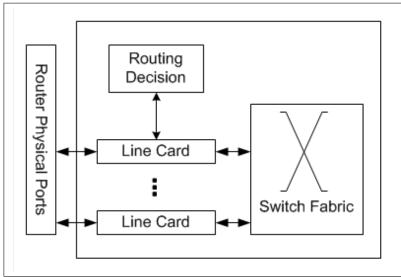

The Internet is based on **packet mode communication**. All the information to be communicated is divided into suitably sized blocks, called **packets**. The routers connect two or more networks, decide the **routing path** of a packet that has been injected in the router and finally transmit the packet to the destination address (**packet forwarding**). These two essential tasks of the router are implemented by four basic modules, which are the **line cards**, **packet processing unit**, **routing unit**, and **the switch fabric** (Figure 1.2). The switch fabric, moreover, requires the implementation of a **scheduling unit**, which regulates and grants permission for the pairing of input/output ports.

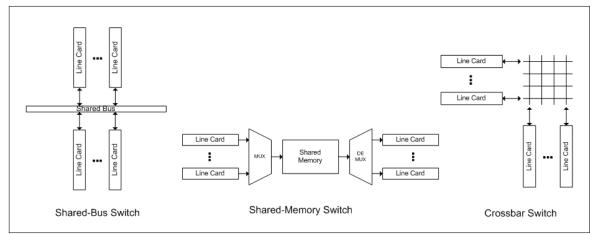

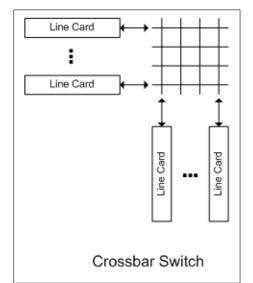

The main design challenges for implementing switch fabrics include bandwidth, latency, scheduling algorithms, interfacing, and routing algorithms. Several switch fabric architectures have been proposed, including the **crossbar** [4], **shared-bus** [5] and **shared-memory** [6] switches, which deal with these design challenges in various ways (Figure 1.3). Crossbar switch is the dominant architecture in today's high-performance switches, due to a number of reasons. Crossbar switch is more scalable than the shared-bus and shared-memory; this is due to the limitations in bus transfer bandwidth and memory access bandwidth, respectively. Crossbar switch provides **point-to-point connections** and **non-blocking** properties, as well as supporting **multiple simultaneous transactions**, increasing the bandwidth and speed of the router.

Figure 1.1: the Internet, a Network of Networks

Figure 1.2: the Router Block Diagram

The crossbar switches are further divided into **unbuffered** [7] and **buffered** or **combined input-crosspoint queueing (CICQ)** [8][9] crossbar switches. The unbuffered crossbar switches have the advantage of low cost, because of using no internal buffers;

1.2. MOTIVATION 3

Figure 1.3: Switch Architectures

however the scheduling unit gets very complex and needs to be centralized. On the other hand, the buffered crossbar switch architectures require **dedicated internal buffers**, which are instantiated per all input/output combinations, resulting in the area cost to grow quadratically with the port count; however the scheduling unit is distributed and simpler.

### 1.2 Motivation

#### 1.2.1 Problem Statement

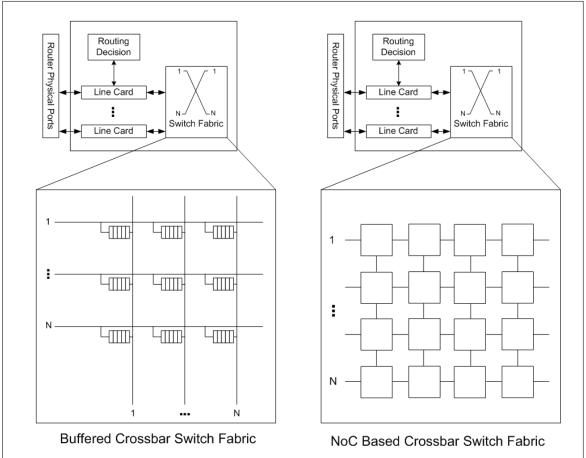

The proposal in [1], [10], and [11] studies the performance of Network-on-Chip based crossbar switch fabric, targeting greater scalability and flexibility, as well as greater performance per hardware cost, compared to buffered crossbar switch fabric (Figure 1.4). [1] proposes functional-level design of two NoC based switch fabric, Unidirectional NoC (UDN) and Multidirectional NoC (MDN).

In this thesis, we address to the problem of hardware design and implementation of the NoC based switch fabric architectures, and try to validate and prove the claims of the original proposal in hardware. The hardware implementation mandates the altering of some design parameters, constraints and algorithms, during the transition from functional-level to register-transfer level design. In particular, we wish to investigate the performance and cost of the NoC based switch fabrics over a wide range of switch sizes, to explore the hardware implementation feasibility.

Figure 1.4: Buffered Crossbar and NoC Based Crossbar Switch Architectures

#### 1.2.2 The Thesis Contributions

In this thesis, we carry out the hardware design and implementation of NoC based crossbar switch fabric proposed in [1], and investigate the performance and cost through synthesis and simulations over a wide range of switch sizes. The hardware design is implemented in RTL, using VHDL. The simulation results are also validated on the FPGA platform, by generating pseudo-random destination addresses for the packets on LFSR based test modules.

In the thesis, we have explored the scalability of the UDN and MDN switches, over uniform and non-uniform (unbalanced) traffic scenarios. We have altered the MDN routing algorithm in the original proposal, for better performance and simpler implementation. We have further proposed a method to improve load balancing by randomly assigning the T-Value parameter of the routing algorithm of UDN and MDN. Finally, we have proposed various arbitration schemes based on Round Robin scheduling, and explored their performances.

### 1.3 Thesis Outline

The remainder of this thesis is organized as follows:

In Chapter 2, we present the background information and the related literature. This chapter includes the detailed explanation of the terminology used throughout the thesis, various architectures that historically have been the milestones in the network switch design, Network-on-Chip related information, and discussions why a certain design decision has been preferred over the others.

In Chapter 3, we present the hardware design of the Unidirectional NoC (UDN) and Multidirectional NoC (MDN), including the Input Buffers, Network Interface and Routers. The routing and scheduling algorithms and their hardware implementations are discussed in Chapter 4.

In Chapter 5, the synthesis results are presented for the individual modules that constitute the UDN and MDN switches, as well as different sized UDN and MDN switches. The synthesis results include the operational frequency and the 2-tuple resource cost (Number of Slice LUTs, Number of Slice Registers) of the modules.

Simulation results of UDN and MDN switches are presented in Chapter 6. The switches are tested under two different traffic types: the Bernoulli Uniform and Unbalanced (Weighted) Traffic. In addition, our proposals for improving the scheduling and load balancing are simulated in order to explore their positive and negative aspects.

In Chapter 7, we define the performance and cost functions for the UDN and MDN architectures, and present the performance / cost analysis for both architectures, over a wide range of sizes and various traffic loads. We conclude this chapter with a comparison of the architectures.

In Chapter 8, we present the in-circuit verification, which is an important step of reconfigurable hardware design; it involves mapping the final design on the reconfigurable platform (FPGA) and carrying out the verification/validation of the results and the timing analysis.

Finally, we conclude the thesis in Chapter 9, giving a detailed observation on the results we have obtained and point out the possible future work.

# Background Information & Related Work

This chapter includes the detailed explanation of the terminology used all through the thesis, various architectures that historically has been the milestones in the network switch design, the emergence of network-on-chip evolving from computer networks as a new paradigm for on-chip communication, and some communicational protocols.

### 2.1 Introduction

The Internet is a network of networks, carrying vast quantity of information and services among the billions of users all over the world. Internet services such as WWW, email, VOIP, IPTV, e-commerce, e-banking, FTP etc. are increasingly used on daily basis [12], and therefore require increasing **network bandwidth**, such that the great quantities of data can be communicated in between the servers and users. **High-performance routers** have the task of transmitting traffic in between the nodes of the Internet. The routers need to support high bandwidths, in order not to become the bottleneck in the network communication.

The Internet is based on **packet mode communication**. All the information to be communicated is divided into suitably sized blocks, called **packets**. The routers connect two or more networks, and perform two important functions: **routing path determination**, computing the route of a packet that has been injected in the router, and **packet forwarding**, transmitting the packet to the destination address. **The line cards**, **routing unit**, and **the switch fabric** are the key building blocks of a router, which implement the two essential functions of the router. When a packet is injected into the router, it is first accepted by the inbound network interface (input line card). Once the routing path is computed on the routing unit, it is forwarded via the switch fabric to the outbound interface (output line card) and finally ejected from the router, to its final destination [13].

The design of the switch fabric, the module responsible of packet forwarding, constitutes an important part of the network router design, and therefore it remains to be an open research problem. Various switch fabric architectures are used in the market products, like Vitesse's GigaStream and IBM's Power Packet Routing Switch [14].

### 2.2 Switch Fabric Architectures

The development of switch fabric architectures has shown a trend from the **shared** resources towards dedicated resources. Some of the reasons for this trend include:

- The need for higher bandwidths. We live in a web-dependent world, where the

use of Internet services, such as email, VoIP, streaming audio and video, search

engines and online encyclopedias, become a must even in our daily lives. All these

services require high data rates, and therefore higher bandwidth in the routers

become crucial for data transfers.

- Developments in the integrated circuits (IC) technology, which have led to the point where very complex systems could be implemented on a single chip, resulting in low cost routing solutions that incorporate hardware-software co-design to yield high performance routers [13].

The important parameters in designing a switch fabric are **throughput**, **packet delays**, **amount of buffering**, **scalability**, **complexity of the implementation** and **packet loss**. The shared-bus, shared-memory, crossbar architectures are the basic approaches that shape the switch fabric design; the proposed solutions are either a variation or combination of these architectures. As a result, it is important to describe the characteristics of these approaches [13].

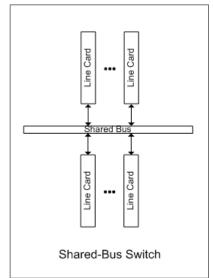

The shared-bus switch fabric (Figure 2.1) is the simplest among the router architectures. It is implemented by a shared single medium over which all data is transmitted. Statistical multiplexing is used to allocate the bus for an input/output port pairing, since the Internet is based on packet mode communication. **Statistical multiplexing** might either serve the packets in the first-come-first-serve fashion, or might deliver the packets according to a scheduling discipline (such as **Round Robin**) for fair queuing. The bus is the bottleneck of the communication, since all the traffic flows over it. It is reliable and simple to implement. As the number of input/output ports increase, scalability becomes an important issue, as it gets more difficult for the bus to support the total bandwidth.

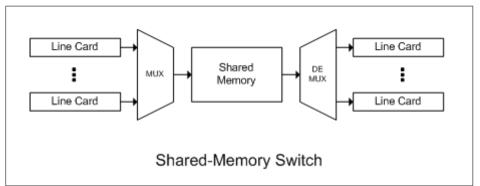

The shared-memory switch fabric's typical architecture is shown in Figure 2.2. The shared-memory architecture is implemented by a dual-port, shared and centralized memory which is used as an output buffer. The inbound packets are multiplexed into the centralized buffer, and the outbound packets are demultiplexed into the output line cards. The advantage of the approach is that the buffer can be statistically shared, according to the buffering needs. The disadvantage is that the memory access speed becomes the bottleneck, resulting in scalability and bandwidth issues.

The third approach, crossbar switch fabric (Figure 2.3), relies on dedicated resources, as opposed to the shared resources of the first two architectures. In a crossbar, there exists a crosspoint for any input/output port combination. The crossbar switches are very good for their scalability and non-blocking properties. Since there is a crosspoint for

Figure 2.1: Shared-Bus Switch Architecture

Figure 2.2: Shared-Memory Switch Architecture

every input/output port pair, it also supports multiple simultaneous transactions. The crossbar switches are further divided into **unbuffered**, and **fully-buffered switches**.

Some variations and combinations of the above approaches, such as partially-buffered crossbar switch fabric [15] and Bufferless Clos-Network Switches [16], are also available. [15] proposes a partially-buffered architecture that is comparable to the cost of unbuffered switch, and to the performance of fully-buffered switch. [16] proposes a Memory-Space-Memory architecture which is a combination of shared-memory and bufferless crossbar architectures.

Recently, a functional-level design of two novel Network-on-Chip based switch fabric architectures were proposed, Unidirectional NoC (UDN) and Multidirectional NoC (MDN), as a replacement of the buffered crossbar switch fabric architecture proposed in [1]. With this novel architecture, the trend goes back towards shared resources, in exchange of scalability.

Figure 2.3: Crossbar Switch Architecture

In the next section we explain the emergence of Network-on-Chip as an on-chip communication paradigm.

### 2.3 Emergence of Network on Chip (NoC)

On-chip communication has evolved, in accordance to the increase in number of elements that are present in a certain system-on-chip. As the number of modules increased, the difficulty of implementing the communication has increased as well. The scalability of the communication circuitry became an important part in the design effort. With these aspects, the evolution of on-chip communication resembles of the switch fabric; the main difference being that the communication on-chip is in **circuit mode**, as opposed to **packet mode**. This means that a dedicated circuit (or channel) has to be established in between the nodes, as if they were physically connected via an electrical circuit [17].

The simplest methodology, involves the communication of two IPs, via a dedicated **point-to-point connection**. This communication involves a hand-shake protocol; a valid signal indicating that the initiator has set the data for the target, and an accept signal, indicating that the target has used the data. In this methodology, the modules need to have a connection to each module they need to communicate with, exponentially increasing the implementation cost. The scalability and re-use of these types of communicational circuits are very low.

A remedy to the high costs and re-use issues of point-to-point communication is to communicate over a shared single communication channel, a **bus** [18], which all modules are connected to. In this case only one of the modules can access this channel at a given time, resulting in a system bottleneck. The modules that are in communication

at a given time seem as if they are hard-wired to the bus that they are communicating through, while the rest of the modules are not. To realize this, there is the need of an arbitration (scheduling) system, to grant the communication rights to the nodes over the bus. On the other hand, the bus communication lacks scalability, like the point-to-point communication.

Verifying the communication circuit repeatedly even for minor changes in the system quickly become a major burden in the design effort, and therefore designing for scalability becomes crucial [19]. **Network-on-Chip (NoC)** is a solution to the scalability issue in on-chip communication. NoC communication has a different structure from the other on-chip communication architectures, because it is based on packet mode communication, like a network router. The communication in NoC is realized on a router matrix, where the nodes are connected to each other with point-to-point connections [20]. This kind of a structure makes it possible for new routers to be added in the matrix very easily.

In on-chip communication, point-to-point is one end, representing singularity in connections, whereas NoC is the current other end, emphasizing scalability and abstraction among many others. **Abstraction** is another important aspect of NoC [21]; because the router communication is based on packets, the computational part is completely separated from the communicational part. Abstraction implies **composability**, which means changing only some parts of NoC without changing and re-verifying rest of the system. Abstraction layers are implemented to provide services for the higher abstraction levels to use, hiding the details of implementation, yielding composability [21].

### 2.4 Network on Chip

Network on chips, a relatively new concept in system-on-chip communication, borrows many ideas from the computer networks, the domain in which the research on routers and packet switching has matured. However, these ideas need to be adapted in NoC as well, since there is no direct translation of these methodologies [22].

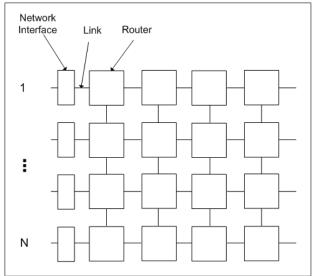

Figure 2.4 shows a network-on-chip, in the form of an N-by-N router matrix. Computational cores are connected to **network interfaces**, which are in turn connected to the routers. Different network topologies such as **mesh**, **torus**, **express cubes**, etc. can be used to enhance the connections in between the routers, such that the **diameter of the network** (largest minimal hop count) can be decreased [23]. Some other important concepts in NoC are **routing**, flow control, buffer management, quality of **service** and **network** interfaces.

The **router** is the most important building block of a network-on-chip. **Routing** decision is about finding the path in between a start and ending point in NoC, which can be in a deterministic, oblivious or adaptive fashion [17]. In deterministic routing, the path in between the source and destination are always the same. In oblivious routing, any of the possible routes is chosen, regardless of the network state. In adaptive routing, the network state is taken into consideration while computing the **routing path**. The

Figure 2.4: Network-on-Chip Switch Fabric

routing path can be computed **all-at-once** in the NI, or **incrementally** (step by step) on the routers. As the packets are transmitted over the routers, **contention** (more than one packets competing over a certain route) and **congestion** (decrease in throughput due to contention) become the main routing problems that need to be avoided. As a solution, **flow control** needs to be applied in either a **bufferless** or **buffered** fashion. Bufferless flow control deals with the routing problems by either dropping both of the packets; dropping one of the packets; or misrouting one of the packets. Buffered flow control involves use of large buffers in the routers to store one of the packets, which increases the size and cost of the circuit, as well as adding **buffer management** overhead [17], in return of **lossless** routing.

The packets' data structure is organized in two sections, the **header** and the **payload**. The header carries the routing related information and instructions, whereas the payload carries the actual data packet is delivering to the destination. Large network packets are broken into smaller pieces called **flow control digits** (flits), for serializing the packet transmission in between the routers.

In buffered flow control scheme, the **switching mode** determines when a packet is forwarded in between two routers. In **Store and Forward** mode [24], a packet is forwarded when the current router has received the whole packet, and the next router has the space for the whole packet. In **Virtual Cut Through** mode [25], a packet is forwarded when the current router has received the flit, and the next router has the space for the whole packet. In **Worm Hole** mode [26], a packet is forwarded when the current router has received the flit, and the next router has the space for the flit.

Buffered flow control solves the contention by forwarding one of the packets and storing the other, which requires the routers to have buffers in various schemes. **Input Buffering** is the simplest and cheapest scheme, with the worst performance among

others; it is implemented either by first-in-first-out (FIFO) buffers per input port or a shared-memory [27]. Output Buffering is an efficient scheme, however it is the most expensive since it is implemented by FIFO buffers per input/output port pair. Virtual Output Buffering [28] is logically the same as Output Buffering, however implementation-wise it uses dual port rams per input port, virtualizing the buffers per input/output port on a single ram. Input and (Virtual) Output Buffering schemes suffer from head-of-line blocking (HOL), in case of contention. Some architectures consist of combinations of the above schemes [29].

If a packet is waiting for an event to occur, but the event will never occur due to some blocking in the switch, this is called a **deadlock**. In Figure 2.5, we exemplify this problem, on a mesh based topology, with buffered flow control. When HOL occurs in a circular loop, the packets cannot be forwarded to the next routers, because all of the input buffers are already full and are blocking each other. A proposal to avoid deadlocks suggests the use of virtual channels, implemented as parallel buffers, to yield deadlock-free network [30][31].

Figure 2.5: Example of a Deadlock, on a Mesh Topology [1]

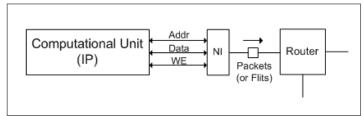

The **network interface** acts as an **abstraction layer** between the computational unit's interface and NoC interface (Figure 2.6). Since on-chip communication is based on circuit mode, the data has to be packetized in the **packetization** unit of the network interface. Once the packets are generated, they are transmitted to the next router, in

equally sized flits.

Figure 2.6: Packetization on the Network Interface