**Delft University of Technology**

#### Integrated RC Frequency References in Standard CMOS

Gürleyük, C.

DOI 10.4233/uuid:140a9735-4956-4875-a334-ea80cd49f29f

Publication date 2024 **Document Version**

Final published version

Citation (APA) Gürleyük, C. (2024). Integrated RC Frequency References in Standard CMOS. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:140a9735-4956-4875-a334-ea80cd49f29f

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Integrated RC Frequency References in Standard CMOS

## Integrated RC Frequency References in Standard CMOS

#### Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology, by the authority of the Rector Magnificus Prof. dr. ir. T.H.J.J. van der Hagen, chair of the Board for Doctorates, to be defended publicly on Tuesday 22, October 2023 at 15:00 o'clock

by

## Çağrı GÜRLEYÜK

Master of Science in Electronics Engineering, İstanbul Technical University, İstanbul, Türkiye, born in İstanbul, Türkiye. This dissertation has been approved by the promotor.

Composition of the doctoral committee:

Rector Magnificus, Prof. dr. K.A.A. Makinwa, Dr. Fabio Sebastiano, voorzitter Delft University of Technology, promotor Delft University of Technology, promotor

*Independent members:* Prof. dr. Ian Galton, Prof. dr. ing. L.C.N. de Vreede Prof. dr. ir. Klaas Bult, Prof. dr. Yuongcheol Chae, Dr. ir. A.J. Annema,

UC San Diego, US Delft University of Technology Delft University of Technology Yonsei University, Korea University of Twente

Copyright  $\ensuremath{\mathbb{C}}$  2024 by Çağrı Gürleyük

ISBN 978-94-93391-62-8

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

# Contents

| Su | Summary is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                |  |  |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|

| Sa | menvatting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xi                                                             |  |  |  |

| 1  | Introduction1.1History of Timekeeping.1.2Electronic Timekeeping1.3The Quartz Crystal1.4Integrated Frequency References1.5Motivation and Challenges1.6Organization of the ThesisReferences                                                                                                                                                                                                                                                                                                                                                    | 4<br>5<br>7<br>9<br>10                                         |  |  |  |

| 2  | Integrated Frequency References         2.1 Introduction.         2.2 Integrated Time Constants         2.2.1 RC - Resistor & Capacitor         2.2.2 LC - Inductor & Capacitor         2.2.3 Thermal Diffusivity.         2.3 Oscillator Architectures         2.3.1 Harmonic Oscillators         2.3.2 Relaxation Oscillators         2.3.3 Frequency Locked Loops         2.4 Temperature Compensation         2.4.1 Digital Nonlinear Temperature Compensation         2.5 Integrated Frequency Reference Survey.         2.6 Conclusion | 16<br>22<br>23<br>25<br>25<br>34<br>35<br>41<br>43<br>45<br>46 |  |  |  |

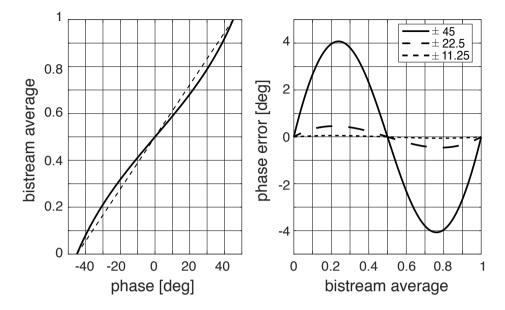

| 3  | RC References Based on Phase-to-Digital Converters         3.1 Introduction.         3.2 The RC Filter         3.3 Synchronous Demodulator as a Phase Detector         3.4 Phase-Domain Delta-Sigma Modulator         3.4.1 Cosine Nonlinearity                                                                                                                                                                                                                                                                                              | 54<br>57<br>58                                                 |  |  |  |

|   |                                         | 3.4.2  | Effect of Higher-Order Harmonics              |         | 60  |  |

|---|-----------------------------------------|--------|-----------------------------------------------|---------|-----|--|

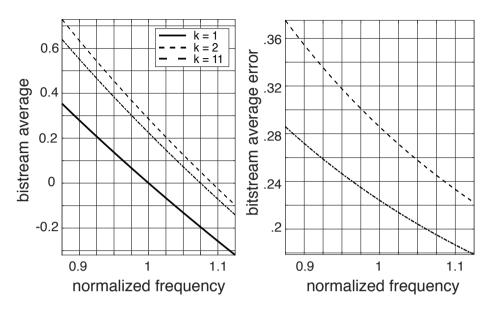

|   | 3.5                                     | Frequ  | ency-Locked Loops                             |         | 62  |  |

|   |                                         | _      | Voltage Controlled Oscillator Dynamics        |         |     |  |

|   |                                         |        | Analog FLL Dynamics                           |         |     |  |

|   |                                         |        | Digital FLL Dynamics                          |         |     |  |

|   | 3.6                                     |        | usion                                         |         |     |  |

|   |                                         |        |                                               |         |     |  |

| 4 | A ±2                                    | 200 pp | m CMOS Dual-RC Frequency Reference            |         | 73  |  |

|   |                                         |        | ecture Proposal                               |         | 73  |  |

|   |                                         |        | Wien Bridge                                   |         |     |  |

|   |                                         |        | Dual-RC Temperature Compensation              |         |     |  |

|   |                                         |        | Linear Model                                  |         |     |  |

|   |                                         | 4.1.4  | Inaccuracy Analysis                           |         | 80  |  |

|   |                                         | 4.1.5  | Dynamic Analysis                              |         | 82  |  |

|   | 4.2                                     | Circui | t Design                                      |         | 84  |  |

|   |                                         | 4.2.1  | Wien Bridge Readout: Phase-Domain DSM .       |         | 84  |  |

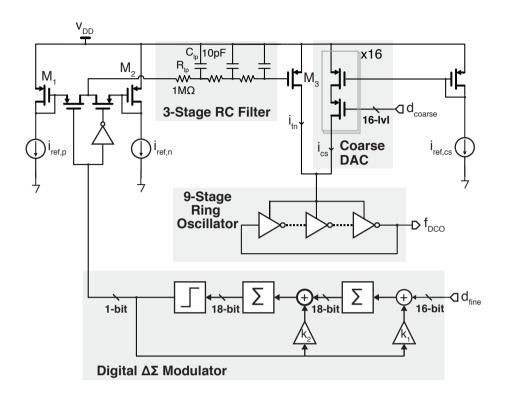

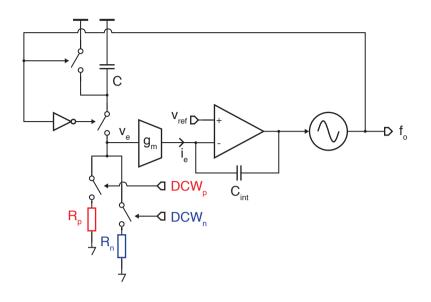

|   |                                         | 4.2.2  | Digitally Controlled Oscillator               |         | 85  |  |

|   | 4.3                                     | Digita | 1 Temperature Compensation & Loop Filter .    |         | 88  |  |

|   | 4.4                                     | Exper  | imental Results                               | ••••    | 90  |  |

|   |                                         | 4.4.1  | Open-Loop Block Characterization              | ••••    | 90  |  |

|   |                                         | 4.4.2  | Derivation of the Trimming Polynomials        | • • •   | 94  |  |

|   |                                         | 4.4.3  | Final Inaccuracy Characterization             | • • •   | 94  |  |

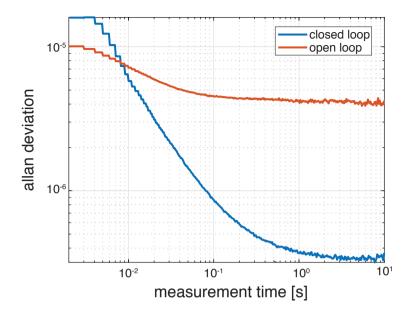

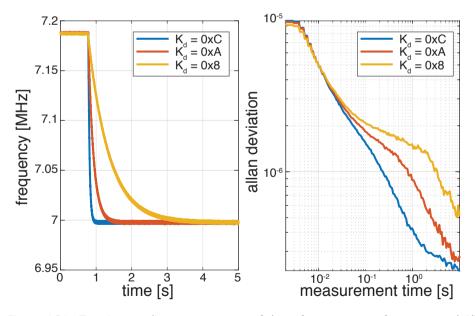

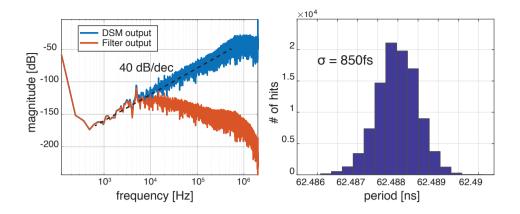

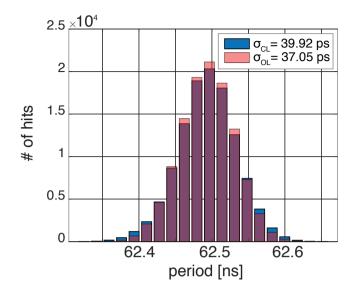

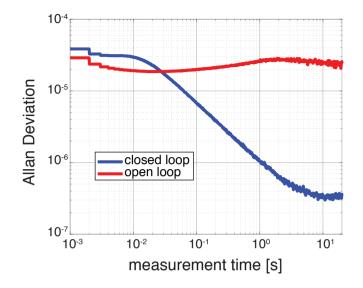

|   |                                         |        | Noise & Long-Term Stability                   |         |     |  |

|   | 4.5                                     | Concl  | usion                                         | • • • • | 101 |  |

|   | References                              |        |                                               |         |     |  |

| 5 | 5 A ±90 ppm CMOS RC Frequency Reference |        |                                               |         |     |  |

|   | 5.1                                     | Introd | luction                                       | • • •   | 105 |  |

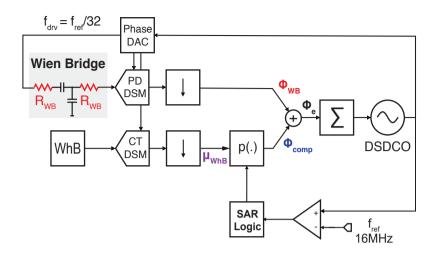

|   | 5.2                                     | Archit | ecture Proposal                               | • • • • | 106 |  |

|   |                                         |        | Temperature Compensation Principle            |         |     |  |

|   |                                         |        | Linear Model                                  |         |     |  |

|   |                                         |        | Inaccuracy Analysis                           |         |     |  |

|   |                                         |        | Second-order Nonlinearity Compensation        |         |     |  |

|   |                                         |        | Dynamic Analysis                              |         |     |  |

|   | 5.3                                     |        | t Design                                      |         |     |  |

|   |                                         |        | Bridge Design                                 |         |     |  |

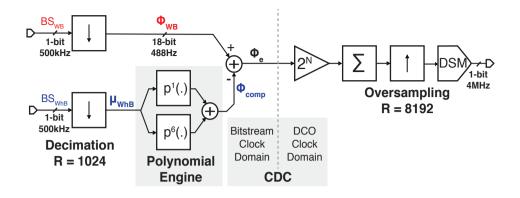

|   |                                         |        | Wien Bridge Readout: Improved PDDSM           |         |     |  |

|   |                                         |        | Wheatstone Bridge Readout: CTDSM              |         |     |  |

|   |                                         | 5.3.4  | Delta-Sigma Digitally Controlled Oscillator . | • • •   | 120 |  |

|                      | 5.4              | Digital Loop Filter and Temperature Compensation | 122 |  |  |  |

|----------------------|------------------|--------------------------------------------------|-----|--|--|--|

|                      | 5.5              | Experimental Results                             | 123 |  |  |  |

|                      |                  | 5.5.1 Closed-loop Trimming Methodology           | 124 |  |  |  |

|                      |                  | 5.5.2 Derivation of the Trimming Polynomials     | 127 |  |  |  |

|                      |                  | 5.5.3 Final Inaccuracy Characterization          |     |  |  |  |

|                      |                  | 5.5.4 Noise & Long-Term Stability                |     |  |  |  |

|                      | 5.6              | Conclusion                                       | 134 |  |  |  |

|                      | Refe             | erences                                          | 136 |  |  |  |

| 6                    | Con              | clusion                                          | 137 |  |  |  |

|                      | 6.1              | Main Findings                                    | 137 |  |  |  |

|                      | 6.2              | Contemporary Work                                |     |  |  |  |

|                      |                  | Future Work                                      |     |  |  |  |

|                      |                  | 6.3.1 Stress and Aging                           | 141 |  |  |  |

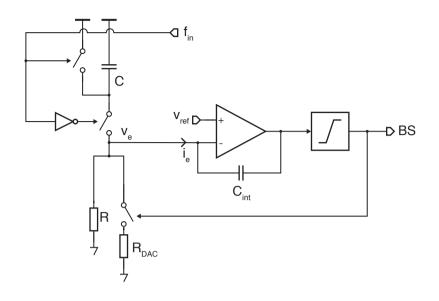

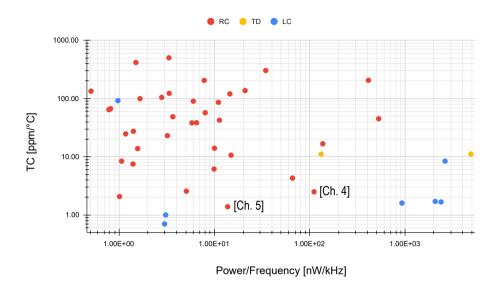

|                      |                  | 6.3.2 Switched-Capacitor FDCs                    | 142 |  |  |  |

|                      |                  | 6.3.3 LC Frequency References                    | 143 |  |  |  |

|                      | Refe             | erences                                          | 145 |  |  |  |

| A                    | Inte             | grated Frequency Reference Survey                | 147 |  |  |  |

| List of Publications |                  |                                                  |     |  |  |  |

| Ac                   | Acknowledgements |                                                  |     |  |  |  |

| Ab                   | About the Author |                                                  |     |  |  |  |

# Summary

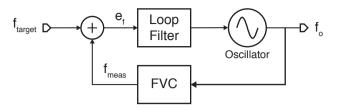

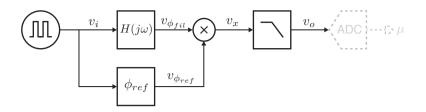

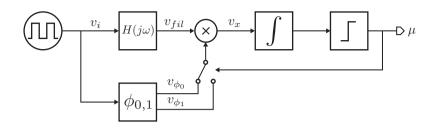

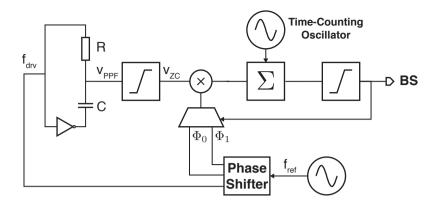

This thesis describes the design, implementation, and characterization of integrated RC frequency references. The primary focus of the work is a frequency-locked loop (FLL) architecture, realized in standard CMOS, that digitizes the phase shift of an integrated RC filter, processes the results in the digital domain, and uses it to control an output frequency to maintain its accuracy over temperature variations.

Chapter 1 introduces the thesis by discussing the progress of accuracy in frequency measurements and its impact on human development throughout history. Quartz crystals are presented as the primary frequency reference of the electronic era. While cheap to produce and widely available, quartz crystals pose a serious shortcoming: they are only available as discrete components. The economic trend of the past few decades is to integrate more functional components on a single monolithic die to achieve systems-on-chip (SoC). MEMS (microelectromechanical systems) and BAW (bulk acoustic wave) in the form of multi-chip modules present possible alternatives, even though they do not achieve full integration. This work's motivation is to realize a frequency reference compatible with a standard CMOS process and with accurate enough to enable wireline communication apllications without a quartz crystal.

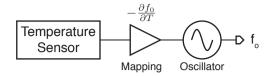

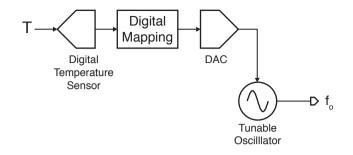

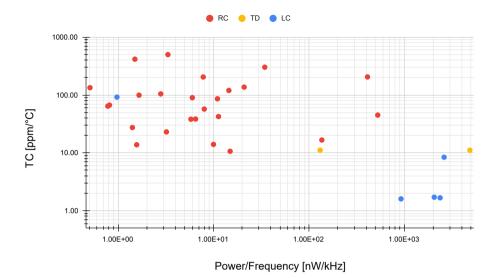

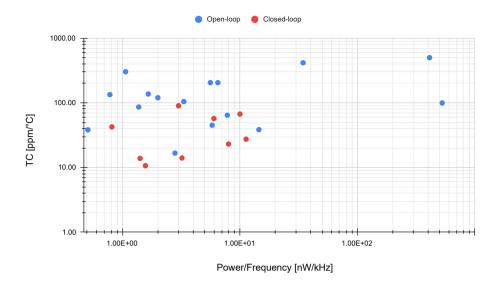

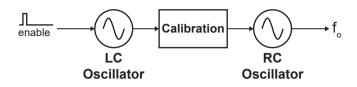

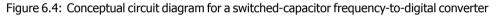

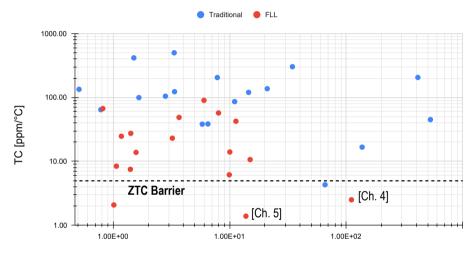

Chapter 2 presents a literature survey of the state-of-the-art integrated frequency references. Integrated frequency references are studied in three categories: their on-chip time constant, oscillator architecture, and the type of temperature compensation. Time constants available in a CMOS process are limited to the few common choices of RC, LC, and thermal diffusivity (TD) and determine performance parameters such as accuracy and power consumption. Oscillator architectures such as harmonic, relaxation oscillators, and frequency-locked loops are discussed, as they generally degrade the accuracy of their time constant. Finally, the temperature sensitivity of both the time constant and the oscillator must be addressed through analog or digital temperature compensation. A survey of integrated frequency references published in the last two decades determines a research direction towards the motivation of the thesis: an FLL-based RC reference with digital temperature compensation.

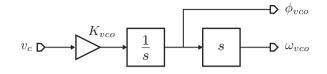

Chapter 3 discusses the digital FLL-based RC frequency reference solu-

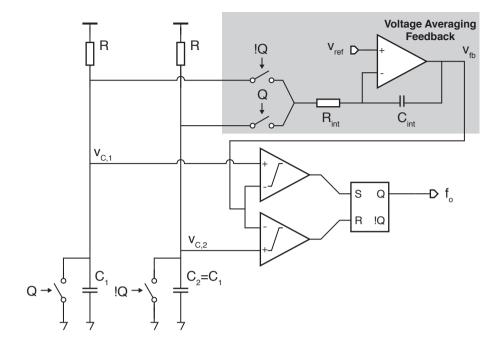

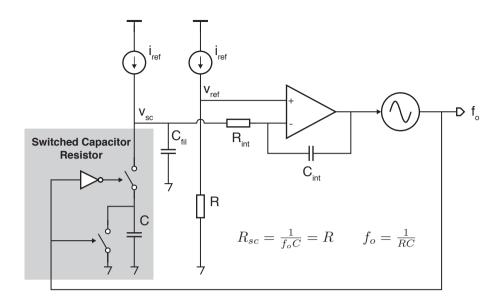

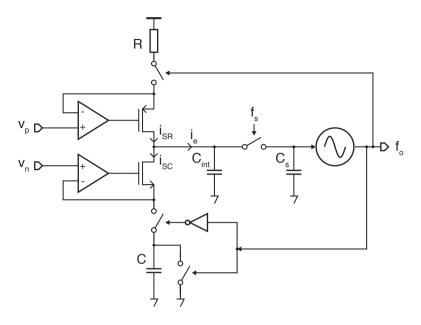

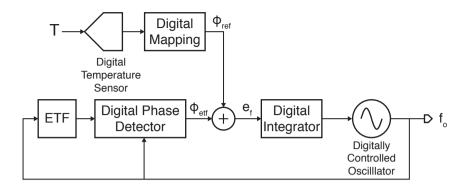

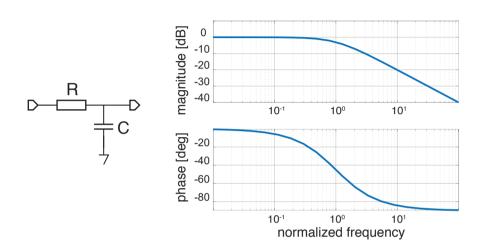

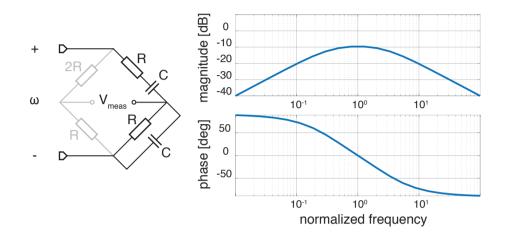

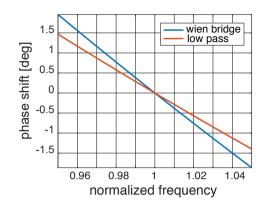

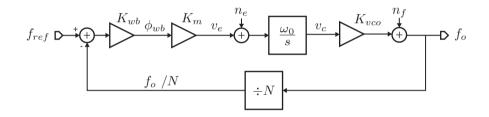

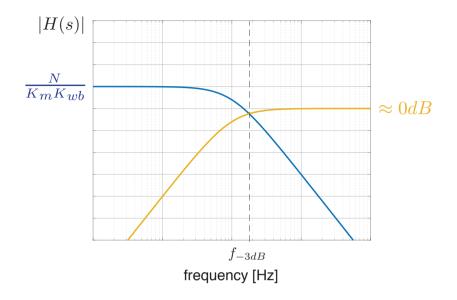

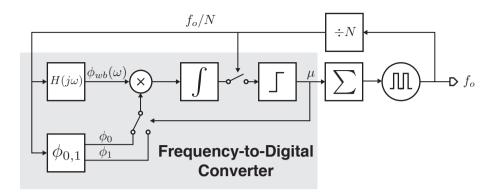

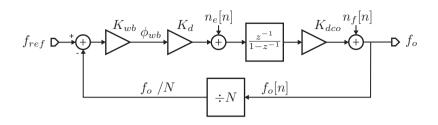

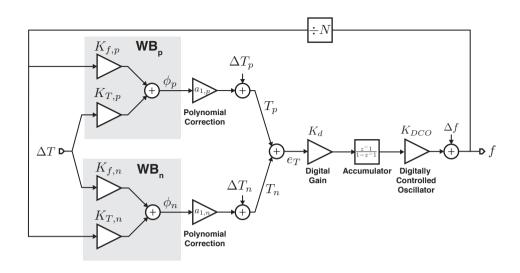

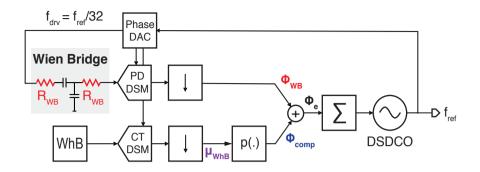

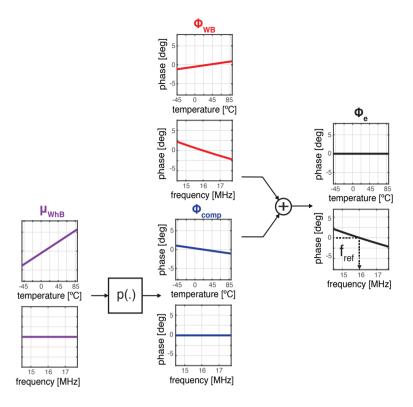

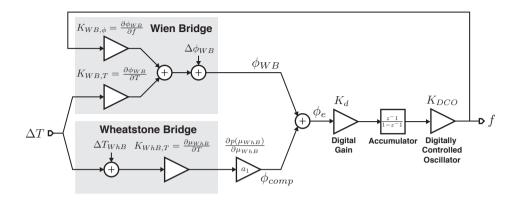

tion through analysis of its components. The Wien Bridge, an RC band-pass filter, is proposed as the time constant due to its high sensitivity and simple architecture. Synchronous demodulation, integrated into a phase-domain delta-sigma modulator (PDDSM), is proposed to digitize the phase shift of this RC filter. This digitized word is then used to control a digitally controlled oscillator (DCO) after being processed by a digital loop filter (DLF). The dynamics of this digital frequency control loop are studied, laying the groundwork for the following experimental work.

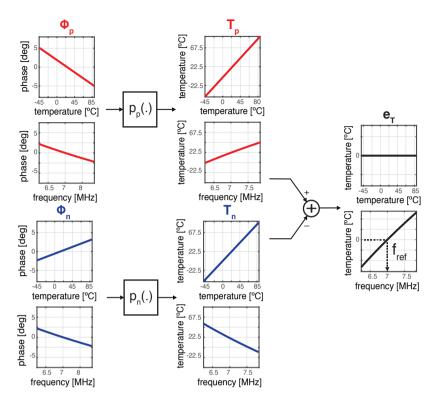

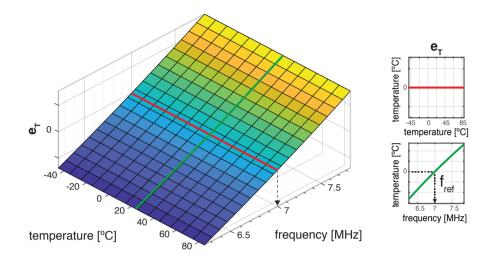

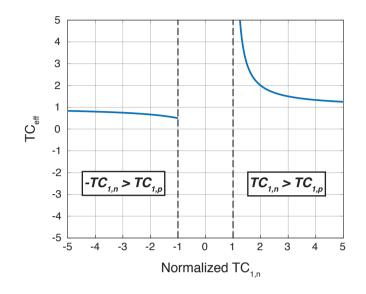

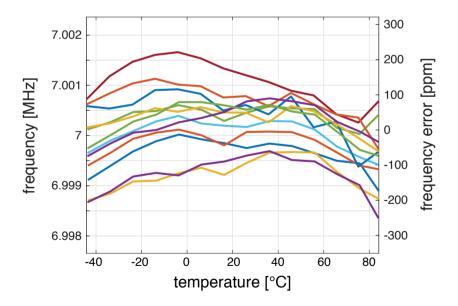

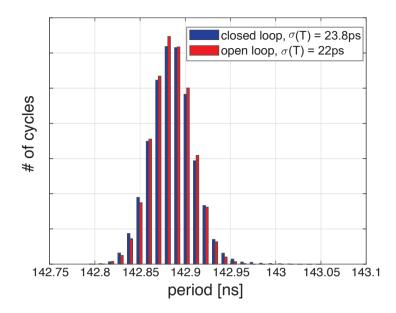

Chapter 4 introduces the Dual-RC frequency reference. Instead of a traditional digital temperature compensation loop, the Dual-RC reference combines the phase shift of two WBs made with different resistors with TCs of opposite signs to achieve a temperature-independent frequency. It features PDDSMs to digitize the phase shift of the two WBs accurately and features digital domain polynomial processing to linearize and combine the two channels. The prototype 7 MHz reference is implemented in a standard CMOS process and achieves  $\pm 162.5$  ppm inaccuracy from -45 °C to 85 °C, showing a 5.5x improvement to the state of the art. It boasts a 330 ppb Allan Deviation floor in a 3s measurement time, displaying a 12x improvement over the state-of-the-art.

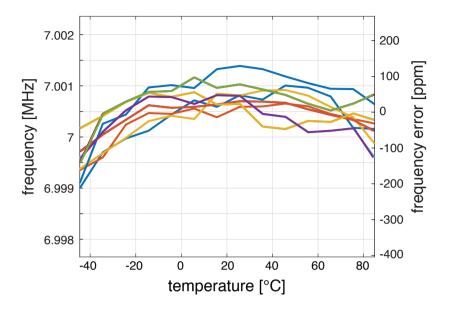

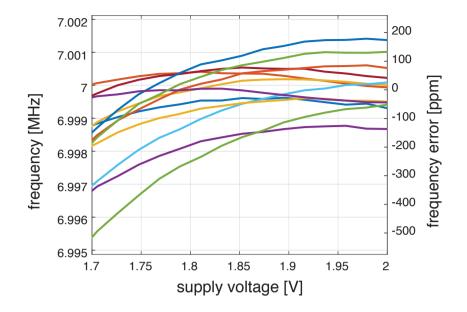

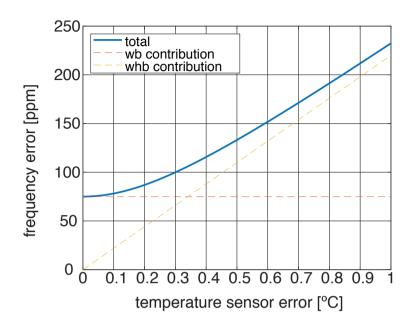

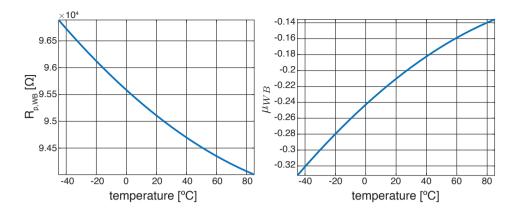

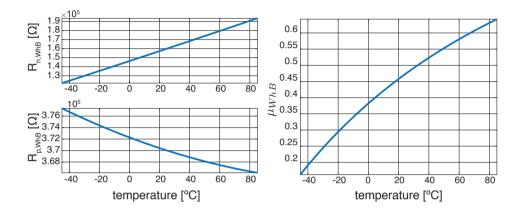

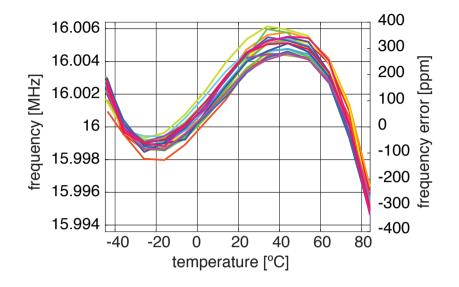

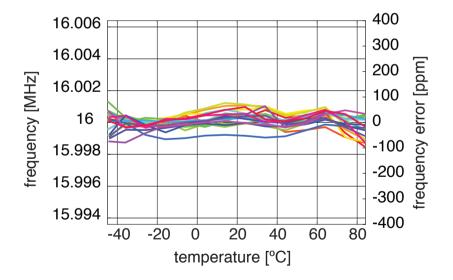

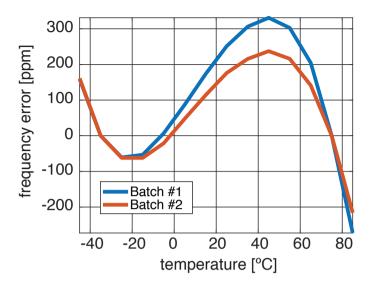

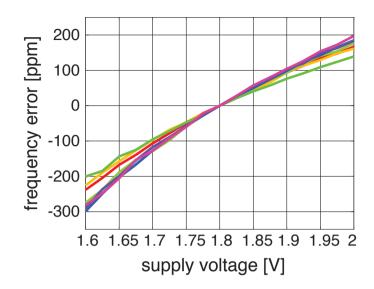

Chapter 5 builds on the experimental results of the Dual-RC reference to improve accuracy and increase the industrial applicability of the design. Utilizing a low-TC WB for the frequency-sensitive channel and a resistorbased temperature sensor, its structure resembles a traditional temperaturecompensated digital FLL with simplified digital domain polynomial processing. A closed-loop trimming methodology is proposed to determine the coefficients of the polynomials very accurately. In addition to maintaining the noise performance of the previous design, the prototype 16 MHz reference implemented in a standard CMOS process achieves  $\pm$ 90 ppm inaccuracy -45 °C to 85 °C for 20 samples, a 2.5x improvement to the state-of-the-art Dual-RC design.

Chapter 6 summarizes the main findings of the thesis. RC-based FLLs with digital temperature compensation can achieve below  $\pm 300$  ppm inaccuracy, enabling wireline communication applications in systems-on-chip. Additionally, this chapter features contemporary work that has been published during the work in this thesis. Finally, the future direction for the research is proposed. While this thesis primarily focused on temperature compensation, mechanical stress and aging still pose limitiations on the accuracy of integrated frequency references, and work on addressing these issues is already ongoing.

# Samenvatting

Deze proefschrift beschrijft het ontwerp, de implementatie en de karakterisering van geïntegreerde RC-frequentiereferenties. De primaire focus van dit werk ligt op een frequentievergrendelingslus (FLL)-architectuur, gerealiseerd in standaard CMOS, die de faseverschuiving van een geïntegreerd RC-filter digitaliseert. De resultaten hiervan worden digitaal verwerkt en deze worden gebruikt om een uitgangsfrequentie te controleren om de nauwkeurigheid te behouden bij temperatuurschommelingen.

Hoofdstuk 1 geeft een introductie van de vooruitgang in frequentiemetingen en de impact ervan op de menselijke ontwikkeling door de geschiedenis heen. Quartz-kristallen worden gepresenteerd als de primaire frequentiereferentie van het elektronische tijdperk. Hoewel goedkoop te produceren en breed beschikbaar, hebben quartz-kristallen een belangrijk nadeel: ze zijn alleen beschikbaar als discrete componenten. De economische trend van de afgelopen decennia is om meer functionele componenten op een enkele monolithische chip te integreren om zo system-on-chip (SoC) te realiseren. MEMS (micro-elektromechanische systemen) en BAW (bulk akoestische golven) in de vorm van multi-chip modules bieden mogelijke alternatieven, hoewel ze geen volledige integratie bereiken. De motivatie van dit werk is het realiseren van een frequentiereferentie die compatibel is met een standaard CMOS-proces en nauwkeurig genoeg is om communicatie via vaste lijnen mogelijk te maken zonder een quartz-kristal.

Hoofdstuk 2 biedt een literatuuronderzoek naar de huidige stand van geïntegreerde frequentiereferenties. Deze worden bestudeerd in drie opzichten: hun on-chip tijdconstante, de oscillatorarchitectuur en het type temperatuurcompensatie. Tijdconstanten die beschikbaar zijn in een CMOS-proces zijn beperkt tot enkele gemeenschappelijke keuzes zoals RC, LC en thermische diffusiviteit (TD) en bepalen prestatieparameters zoals nauwkeurigheid en energieverbruik. Oscillatorarchitecturen zoals harmonische, relaxatieoscillatoren en frequentievergrendelingslussen worden besproken, aangezien ze over het algemeen de nauwkeurigheid van hun tijdconstante verminderen. Ten slotte moet de temperatuurgevoeligheid van zowel de tijdconstante als de oscillator worden aangepakt via analoge of digitale temperatuurcompensatie. Een overzicht van geïntegreerde frequentiereferenties gepubliceerd in de afgelopen twee decennia bepaalt de onderzoeksrichting naar de motivatie van de scriptie: een op FLL gebaseerde RC-referentie met digitale temperatuurcompensatie.

Hoofdstuk 3 bespreekt de digitale FLL-gebaseerde RC-frequentiereferentieoplossing door analyse van zijn componenten. De Wien Bridge (WB), een RC-banddoorlaatfilter, wordt voorgesteld als de tijdconstante vanwege zijn hoge gevoeligheid en eenvoudige architectuur. Synchrone demodulatie, geïntegreerd in een fase-domein delta-sigma modulator (PDDSM), wordt voorgesteld om de faseverschuiving van dit RC-filter te digitaliseren. Dit gedigitaliseerde woord wordt vervolgens gebruikt om een digitaal gestuurde oscillator (DCO) te controleren, nadat het is verwerkt door een digitaal lusfilter (DLF). De dynamiek van deze digitale frequentiebesturingslus wordt bestudeerd, waarmee de basis wordt gelegd voor het volgende experimentele werk.

Hoofdstuk 4 introduceert de Dual-RC frequentiereferentie. In plaats van een traditionele digitale temperatuurcompensatielus, combineert de Dual-RC referentie de faseverschuiving van twee WBs gemaakt met verschillende weerstanden, met TC's van tegengestelde tekens, om een temperatuuronafhankelijke frequentie te bereiken. Het bevat PDDSM's om de faseverschuiving van de twee WBs nauwkeurig te digitaliseren en bevat digitale polynomiale verwerking om de twee kanalen te lineariseren en te combineren. Het prototype van de 7 MHz-referentie is geïmplementeerd in een standaard CMOS-proces en bereikt een onnauwkeurigheid van  $\pm 162,5$  ppm van -45 °C tot 85 °C, wat een verbetering van 5,5x ten opzichte van de huidige stand van de techniek laat zien. Het prototype vertoont een Allan-deviatie van 330 ppb in een meettijd van 3 seconden, wat een verbetering van 12x is ten opzichte van de huidige stand van de techniek.

Hoofdstuk 5 bouwt voort op de experimentele resultaten van de Dual-RC referentie om de nauwkeurigheid te verbeteren en de industriële toepasbaarheid van het ontwerp te vergroten. Door gebruik te maken van een lage-TC WB voor het frequentiegevoelige kanaal en een op weerstanden gebaseerde temperatuursensor, lijkt de structuur op een traditionele temperatuur gecompenseerde digitale FLL met vereenvoudigde digitale polynomiale verwerking. Een gesloten-lus afstemmethodologie wordt voorgesteld om de coëfficiënten van de polynomen zeer nauwkeurig te bepalen. Naast het behouden van de ruisprestaties van het vorige ontwerp, bereikt het prototype van de 16 MHz-referentie, geïmplementeerd in een standaard CMOS-proces, een onnauwkeurigheid van  $\pm$ 90 ppm van -45 °C tot 85 °C voor 20 samples, wat een verbetering van 2,5x is ten opzichte van het Dual-RC ontwerp.

Hoofdstuk 6 vat de belangrijkste bevindingen van het proefschrift samen. RC-gebaseerde FLL's met digitale temperatuurcompensatie kunnen een onnauwkeurigheid van minder dan ±300 ppm bereiken, waardoor ze geschikt zijn voor toepassingen in draad gebonden communicatie in system-on-chip. Daarnaast wordt in dit hoofdstuk werk besproken dat tijdens dit onderzoek is gepubliceerd. Tot slot wordt de toekomstige richting van het onderzoek voorgesteld. Hoewel deze scriptie zich voornamelijk richtte op temperatuurcompensatie, vormen mechanische spanningen en veroudering nog steeds beperkingen voor de nauwkeurigheid van geïntegreerde frequentiereferenties, en er wordt al gewerkt aan het aanpakken van deze problemen.

# 1

# Introduction

Time is a fundamental aspect of existence. Every event happens at a specific point in the time dimension. From our perspective, these events form a unidirectional flow of moments, from the past to the present, extending into the future. A ball allowed to fall freely from the top of a building might now be in the air but will undoubtedly hit the floor in the future. Such observations of ordered sequences of events and the causal relationships between them inspired efforts to quantitatively define these moments of interest and measure the intervals between them.

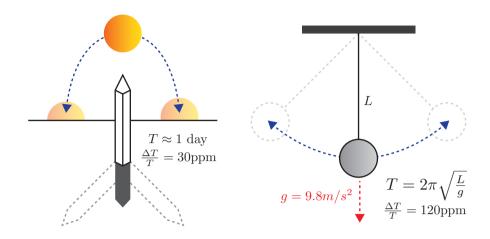

The primary method of measuring time intervals is by counting reliably repetitive events. The sun rises and sets once a *day*, a weight suspended by a one-meter wire swings about 30 times a *minute*, and the Cs-133 atom transitions between its two hyperfine ground states about nine billion times a *second*. These repeated events all define specific intervals or *periods*. Multiples or fractions of these periods can be used as references to quantify any arbitrary time difference. It is thus possible to quantify the time it takes for a ball to fall: dropped from the top of a 90-meter-high building 2 seconds (or 0.0033 days) ago, it will hit the ground precisely 2.284 seconds (or 0.0038 days) later.

However, all naturally periodic events suffer from variation. Time measurements from perfect observations of the sun's position in the sky can vary by up to 16 minutes in a year (or  $\pm 30$  parts-per-million, ppm) just due to the eccentricity of the Earth's orbit [1]. A pendulum's rate of oscillation varies not only because of the nonidealities of its mechanism but also because of ambient temperature or humidity variations. These cause the period of even the best-constructed pendulums to vary by a few seconds in a day, or about  $\pm 120$  ppm [2]. These variations add *inaccuracy* to the said time measurement.

The widely accepted International System of Units defines the standard period chosen for time measurements as the second, *s*. The second is a base unit: one of seven such units based on constants and used to define all other units encountered in nature. Unlike the other base units, its definition depends on the measurement of a natural phenomenon. In the SI system, a second is defined as the time it takes for 9 192 631 770 ground-state hyperfine transitions of the Cs-133 atom at rest. Many other units are derived from this definition, including the unit for frequency, the number of occurrences of a repeating event per second. The derived unit for frequency is Hertz, Hz, in the units of  $s^{-1}$ , the reciprocal of one second.

When the current definition of a second was accepted in 1967 [3], it represented the highest accuracy and stability of any measurement. The transition rate of Cs-133 is based on its fundamental physics: excited Cs-133 atoms will transition back to their base state at this rate at any location, unaffected by external factors such as gravity or temperature. A typical Caesium frequency standard has a relative accuracy of  $5 \times 10^{-13}$  [4]: two measurements taken from different units will thus vary by one second in approximately 63 thousand years. This represents a nine-orders-of-magnitude improvement in accuracy compared to time measurements made with a pendulum clock.

More accurate time measurements enable tighter scheduling of events and activities and increase the accuracy of any other measurement that involves temporal events. Consequently, accuracy in time measurements correlates well with humankind's technological and societal advancement. As human civilization advanced, systems required tighter synchronization between more and more users. These requirements resulted in an exponential increase in the accuracy of time measurements within a few millennia.

### 1.1. History of Timekeeping

Time measurements in ancient times required little accuracy. Hunter-gatherers only needed to know when the seasons would change to coordinate their movement from pastures to valleys. They could rely on inaccurate observations of the rhythmic patterns of stars in the night sky to deduce and predict the passing of seasons. The agriculturalists that followed a few thousand years later would need to know more precisely when to sow, how long to keep their crops in the soil, and when to reap. Inaccuracies in timekeeping could mean a loss of crop yield and an understocked winter.

Figure 1.1: Two common ancient timing devices: a sundial and a pendulum, and their relative inaccuracy.

Consequently, it was the agriculturalists who developed the first primitive timing devices and methods for organizing days and seasons into calendars. The time of the day based on the sun's position in the sky, or the *apparent solar time*, would be the general basis of timekeeping. For a few thousand years, such devices remained the primary forms of time measurements.

The next significant improvement in timing accuracy occurred in the 16<sup>th</sup> century when Galileo Galilei observed that the rate of a pendulum's swing depends only on its length. Based on this principle, the Dutch scientist Christiaan Huygens developed the first pendulum clock in 1656. With the increased accuracy that this provided, he was able to calculate the error in the apparent solar time due to the eccentricity of the Earth's orbit [1]. Since then, the use of harmonic oscillators for conducting time measurements has been the norm.

The next advances in timing accuracy emerged from navigational requirements. The Sicily naval disaster of 1707 involved the loss of four English Royal Navy fleet ships, causing the death of 2,000 sailors. It occurred because the ships' navigators could not correctly estimate their longitude because they lacked accurate clocks. The pendulum clocks available at the time were affected by variations in the Earth's gravity, making them too inaccurate for use aboard ships. The British government offered a prize for a clock that could work on a ship with better than 3 seconds per day, or  $\pm 30$  ppm, accuracy. In 1773, the prize was won by John Harrison, whose

H series of chronometers were able to keep time to about 5 seconds in a 10-day trip or to about 6ppm accuracy [5].

The advent of the industrial age required even more cooperation between people. Factories needed to operate on tight schedules to be profitable, and trains needed to run on time to carry workers to these factories. People became more aware of the current time as the rhythm of life started to run on a fixed reference to enable mass cooperation [6]. As a result, in 1880, the British established the Greenwich Mean Time to ensure that their vast empire had a reference time across the globe.

The most significant increase in timekeeping accuracy has occurred in the last century. The development of atomic clocks enabled the most accurate time measurements ever conducted and, in turn, has enabled previously undreamt applications. A great example is GPS, which is composed of satellites housing very accurate atomic clocks that broadcast their current time reading to the entire world [7]. Since they are in known orbits, a person receiving broadcasts from three GPS satellites can triangulate their position anywhere on Earth to an accuracy of about 5 meters, a 10 ppm measurement considering the Earth's circumference. This level of positional accuracy is now available to virtually anyone on Earth who can afford a smartphone. This widespread availability is the result of great strides in electronic engineering, allowing a vast amount of computation to be housed in a portable form factor. The mass-production economics of integrated circuit technology has given everyone easy access to this newfound power.

#### **1.2.** Electronic Timekeeping

Electronic systems require accurate timing devices for timing, communication, and synchronization. Synchronous digital circuits are designed with timing constraints: data transfer between a series of flip-flops via asynchronous logic elements has to occur in a specified time to ensure that the input of the receiving flip-flop is ready before the next cycle. Such constraints warrant the need for a stable frequency: if the frequency is too high, it could result in metastability and data corruption.

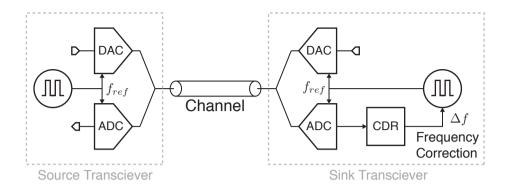

Frequency accuracy is of particular importance for the synchronization of electronic communication systems. As shown in Figure 1.2, these systems consist of a transmitter that sends data through a channel and a receiver that resamples the data stream. Each side of such a system has a local oscillator that establishes the local timing. Frequency errors between the transmitting and receiving sides result in loss of synchronization and corrupt data transmission. Generally, receivers rely on clock-data-recovery meth-

Figure 1.2: Block diagram of an electronic communication system where a sink transceiver uses a CDR algorithm to lock its local frequency to the source frequency

ods that lock their local oscillator to the transmission frequency; however, these algorithms can correct for only a limited range of frequency errors: the capture range. This defines a communication standard's tolerable frequency error. For example, WiFi can only tolerate a  $\pm 20$  ppm error between transceivers [8].

Another application for accurate frequency references was created by the emergence of the Internet of Things (IoT), which consists of multiple sensor nodes that acquire and exchange data. These generally have very tight power consumption constraints, as they are supplied by battery or harvested power. A traditional solution to reduce the power consumption is to operate them in sleep-wake cycles, during which the device briefly senses and transmits data before going to sleep for a set amount of time [9]. The only block that must run constantly in such a system is the timing unit, bringing additional power consumption constraints. Its frequency inaccuracy, or a lack of long-term frequency stability, then causes increased power consumption and a shorter lifetime.

Fortunately, most electronic systems have access to an accurate frequency reference in a small form factor: the quartz crystal. Virtually all electronic systems today integrate one or more quartz crystals.

## 1.3. The Quartz Crystal

A quartz crystal consists of silicon and oxygen atoms arranged in a lattice structure. Quartz crystals possess piezoelectric properties: they produce an electric potential when subjected to mechanical forces and produce mechanical stress on the crystal when subjected to an electric potential. This energy

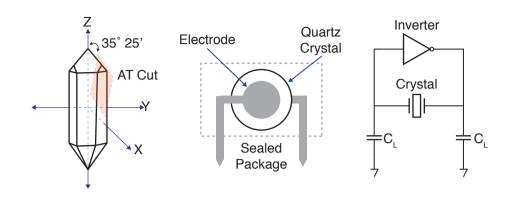

Figure 1.3: Quartz crystal and an AT cut profile, contacted with electrodes and mounted in a hermetically sealed package, finally used in a crystal oscillator circuit using an inverter.

transformation from the electrical to the mechanical domain can be used to excite a crystal into electromechanical resonance. The oscillation between the electrical and mechanical potentials happens at a specific frequency, also called the resonance frequency of the crystal. It is possible to build an oscillator with a quartz crystal by combining this frequency-selective property with an electrical circuit that compensates for the losses of the crystal, as in Figure 1.3.

Because the crystal lattice structure of quartz is very regular and consistent, the resonant frequency of a quartz crystal is very accurately determined by its size and shape. Specific crystal orientations can be adopted to lower the temperature or stress sensitivity of the resonance frequency. Quartz crystals can be mass-produced using methods of synthetic growth, resulting in a very low impurity density and a very accurate geometry, leading to time constants that are accurate to better than ±100 ppm.

However, quartz crystals suffer from nonidealities, which limit their accuracy and stability. They exhibit temperature dependency, which their cut can reduce to about  $\pm 10$  ppm, but they require compensation to achieve better accuracy and stability levels. Temperature-compensated (TCXO) or oven-controlled (OCXO) oscillators use a temperature sensor or active temperature control of the crystal to increase temperature stability, but this comes at the expense of increased power consumption and production costs. Quartz crystals are also sensitive to mechanical stress. External forces, such as shocks and vibrations, can result in frequency shifts. Stress-compensated (SC) cuts can be adopted to reduce the sensitivity to mechanical stresses,

but this comes at the expense of lower temperature stability [10]. Finally, quartz crystals are prone to aging due to chemical processes that occur with time. Contaminants from the atmosphere can penetrate the crystal and behave like impurities. Similarly, their metal electrodes can react with the quartz, creating interface oxides [11]. Quartz crystals and oscillators need to be housed in hermetically sealed packages to avoid damping and slow down such aging processes.

The requirements for processing, mounting, contacting, and housing quartz crystals make them discrete components. Being only available in such a form is the main disadvantage of quartz crystals. Processes developed to build high-stability quartz oscillators are incompatible with modern integrated circuit processes, and the two cannot be produced on the same die. Electronic systems incorporating an external quartz crystal must sacrifice precious board space. Moreover, having to source an extra component incurs additional costs. These factors have driven the search for an integrated frequency reference to replace quartz crystals.

#### **1.4.** Integrated Frequency References

Integrated circuit technology enables the realization of numerous electronic devices on a single monolithic silicon wafer. These devices can be combined to build functional blocks, such as amplifiers, data converters, and central processing units, allowing for better performance, miniaturization, and economical fabrication of systems of immense scale. The lack of an integrated frequency reference as a functional circuit block motivates the search for quartz alternatives.

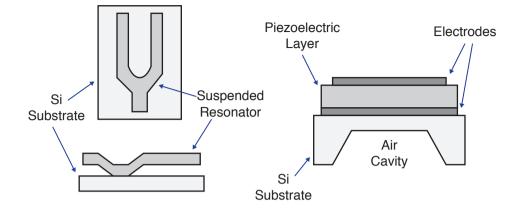

Two such alternatives that have achieved commercial success are BAW (bulk acoustic wave) resonators and MEMS (micro-electromechanical systems) (Figure 1.4). BAW resonators [12] are constructed by depositing thin piezoelectric materials on the surface of a silicon substrate and rely on the same piezoelectric properties that crystal oscillators possess to build frequency references. They are generally constructed as separate chips that can be stacked on top of a traditional integrated circuit. In contrast, MEMS [13] resonators are miniaturized mechanical tuning forks, generally constructed by etching silicon dies to build a physical structure that shows mechanical resonance. However, their manufacturing process is also not compatible directly with standardized IC processes. BAW and MEMS oscillators generally feature a two-chip system, one for the resonator and the other for the electronic circuits that sustain oscillation and provide temperature compensation [12, 13]. These systems can achieve a higher level of

Figure 1.4: MEMS and BAW resonators, crystal replacements used for frequency references that enable multi-die integration.

integration than hermetically-sealed quartz crystal oscillators and so have been commercially successful, which is an affirmation of the market desire for further integration of frequency references. Despite their performance and commercial success, multi-die-based systems still need to achieve full integration. A fully integrated frequency reference must be compatible with a standard CMOS process, using only the limited devices available. Only then can the frequency reference block be co-integrated to realize a complete system-on-chip.

Unfortunately, integrated circuit processes have yet to yield a set of devices that match the stability and accuracy of MEMS or BAW resonators. Frequency references based on LC oscillators [14] made a short-lived commercial appearance for low-accuracy applications in the early 2010s. While they were the only example of fully integrated frequency references at the time, they displayed electromagnetic susceptibility, which caused them to be taken off the market. The accuracy of RC oscillators has generally been limited to about  $\pm 1000$  ppm, which ruled them out as viable contenders for many applications as the integrated frequency references is still unsolved, and taking a step towards a solution forms the primary motivation of this thesis.

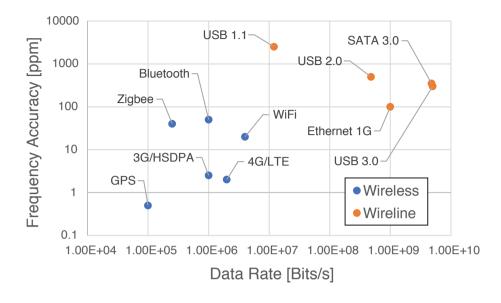

Figure 1.5: Frequency accuracy (absolute, DC) requirements of wireless and wired communication standards vs. their maximum bitrate

#### **1.5.** Motivation and Challenges

Frequency references that utilize multi-chip solutions have already achieved the goal of combining package-level integration with accuracy comparable to that of a crystal oscillator. These devices achieve better than  $\pm 100$  ppm inaccuracy and are economically viable quartz replacements. However, they still require extra production steps, so the challenge of building low-cost, fully integrated frequency references remains.

It should be noted that many important applications do not require crystallevel performance. For instance, the frequency accuracy required by modern communication standards depends on the data rate and the losses of the communication medium. As shown in Figure 1.5, wireless communication standards, such as WiFi[8] or Bluetooth[15], generally require inaccuracies below  $\pm 10$  ppm, which is readily attainable by relatively inexpensive crystals but cannot be matched by on-chip components. Wireline communication standards that operate in cabled environments, such as USB[16] and SATA[17], can tolerate more frequency inaccuracy, up to  $\pm 350$  ppm.

The primary goal of this work is to design a frequency reference in standard CMOS that achieves better than  $\pm 300$  ppm inaccuracy. This is quite challenging because on-chip elements suffer from fabrication tolerances and

environmental variations. Due to fabrication tolerances, multiple samples of the same frequency reference will have different output frequencies while environmental factors, such as temperature, will cause the frequency to drift over its lifetime.

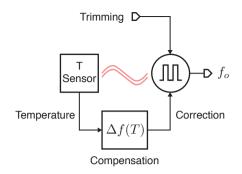

As shown in Figure 1.6, these issues can, in principle, be addressed by the use of trimming and temperature compensation. However, implementing these techniques comes with new challenges. The effectiveness of trimming is limited by the presence of system noise (frequency jitter), while the effectiveness of temperature compensation schemes is limited by the non-linearity and spread in the temperature dependency of on-chip elements. Furthermore, such schemes also need to be fast enough to track thermal transients.

## 1.6. Organization of the Thesis

This chapter briefly introduces time measurements, their place in history, and the challenges associated with designing (integrated) electronic frequency references. The rest of this thesis describes the implementation of accurate frequency references in a standard CMOS process using trimming and digital temperature compensation. The goal is to achieve better than  $\pm 300$  ppm inaccuracy over a wide temperature range, thus enabling the implementation of wireline telecommunication protocols without the need for external components.

Chapter 2 presents a literature survey of the state-of-the-art in integrated frequency references at the conception of this work. Building an on-chip frequency reference is divided into three distinct steps: choosing an on-chip time constant, an oscillator architecture, and finally, implementing temper-

ature compensation. Various choices for each step are discussed, together with their advantages and limitations. A survey of the state-of-the-art motivates the exploration of frequency references in which the frequency of an oscillator is locked to an RC time constant and the use of digital techniques to compensate for their nonlinear temperature dependence.

Chapter 3 discusses such frequency-locked loops in more detail. Synchronous demodulation and delta-sigma conversion are proposed to digitize the phase shift of an RC filter. This information can then be used to set the frequency of a digitally controlled oscillator. The operation of such phasedomain digitizers is analyzed, and their main error sources are discussed. Then, the dynamics of the resulting frequency-locked loops are studied. This chapter lays the foundations for the architecture used in the experimental work of chapters 4 and 5.

Chapter 4 proposes the Dual-RC frequency reference. Instead of using a traditional temperature compensation loop, which typically requires a separate temperature sensor, the phase shift of two RC filters with different temperature dependencies is digitized. This information is then combined in the digital domain to achieve a low-TC frequency error signal in a digital frequency-locked loop. The Dual-RC reference implemented in a standard CMOS process achieves ±250 ppm inaccuracy from -45 °C to 85 °C for 12 samples with a two-point trim and higher-order digital polynomial correction. The work in this chapter represents the first step in reducing the inaccuracy of RC frequency references to significantly below 1000 ppm, showing a 5x improvement to the state-of-the-art.

Chapter 5 describes the implementation of RC frequency reference with improved inaccuracy. An architecture based on a single low-TC Wien Bridge compensated with a complementary temperature sensor is proposed. This architecture aims to address the shortcomings of the Dual-RC implementation to reduce inaccuracy and lower power consumption and area. Moreover, an industrially feasible method for temperature compensation is presented. The architecture is implemented in a standard CMOS process, and a new method for trimming the reference is proposed. The work achieves ±400 ppm inaccuracy from -45°C to 85 °C with a simple, industrially feasible, two-point trim over 20 samples. Moreover, adding a higher-order digital polynomial correction in the loop improves the inaccuracy to ±90 ppm. The work in this chapter represents the second step, showing a 2x improvement in residual inaccuracy compared to the Dual-RC.

Chapter 6 summarizes the main findings of the thesis. The unexplored aspects of RC frequency references are discussed, and a direction for future work on integrated RC frequency references is proposed.

#### References

- [1] C. Huygens, Kort Onderwys aengaende het gebruyck der Horologien tot het vinden der Lenghten van Oost en West, (1665).

- [2] Proceedings of the Royal Society of London. Series A, Containing Papers of a Mathematical and Physical Character **85**, 505–526 (1911).

- [3] M. A. Lombardi, T. P. Heavner, and S. R. Jefferts, *NIST primary frequency standards and the realization of the si second*, NCSLI Measure 2, 74–89 (2007).

- [4] 5071A Primary Frequency Standard Datasheet, Microsemi (2019).

- [5] E. Bruton, *The History of Clocks and Watches* (London: Little, Brown, 2000).

- [6] Y. N. Harari, D. Vandermeulen, and D. Casanave, *Sapiens* (Albin Michel, 2020).

- [7] D. W. A. N. A. C. C. Hodge, *The Science of Timekeeping*, Hewlett Packard (1997).

- [8] A. Behzad, Z. M. Shi, S. Anand, L. Lin, K. Carter, M. Kappes, T.-H. Lin, T. Nguyen, D. Yuan, S. Wu, Y. Wong, V. Fong, and A. Rofougaran, A 5-GHz direct-conversion CMOS transceiver utilizing automatic frequency control for the IEEE 802.11a wireless LAN standard, IEEE Journal of Solid-State Circuits 38, 2209 (2003).

- [9] F. Sebastiano, L. Breems, and M. K. A. A., *Mobility-based time references for Wireless Sensor Networks* (Springer, 2013).

- [10] J. R. Vig and A. Ballato, *Method of Making Miniature High Frequency SC-cut Quartz Crystal Resonators*, (1985).

- [11] F. Iwasaki, A. H. Shinohara, H. Iwasaki, and C. K. Suzuki, *Effect of impurity segregation on crystal morphology of Y-bar synthetic quartz, Japanese Journal of Applied Physics* **29**, 1139 (1990).

- [12] D. Griffith, P. T. Roine, T. Kallerud, B. Goodlin, Z. Hughes, and E. T.-T. Yen, A ±10ppm -40 to 125°C BAW-based Frequency Reference System for Crystal-less Wireless Sensor Nodes, in 2017 IEEE International Symposium on Circuits and Systems (ISCAS) (2017) pp. 1–4.

- [13] M. H. Perrott, J. C. Salvia, F. S. Lee, A. Partridge, S. Mukherjee, C. Arft, J. Kim, N. Arumugam, P. Gupta, S. Tabatabaei, S. Pamarti, H. Lee, and F. Assaderaghi, *A Temperature-to-Digital Converter for a MEMS-Based Programmable Oscillator With*  $< \pm 0.5$ -ppm Frequency Stability and < 1-ps Integrated Jitter, IEEE Journal of Solid-State Circuits **48**, 276 (2013).

- [14] M. S. McCorquodale, G. A. Carichner, J. D. O'Day, S. M. Pernia, S. Kubba, E. D. Marsman, J. J. Kuhn, and R. B. Brown, A 25-MHz Self-Referenced Solid-State Frequency Source Suitable for XO-Replacement, IEEE Transactions on Circuits and Systems I: Regular Papers 56, 943 (2009).

- [15] IEEE Standard for Information technology– Local and metropolitan area networks– Specific requirements– Part 15.1a: Wireless Medium Access Control (MAC) and Physical Layer (PHY) specifications for Wireless Personal Area Networks (WPAN), IEEE Std 802.15.1-2005 (Revision of IEEE Std 802.15.1-2002), 1 (2005).

- [16] Universal Serial Bus 3.2 Specification, USB Implementers Forum, Inc. (2022), rev. 1.1.

- [17] Long Term Frequency Accuracy and SSC Profile Tests for Transmitters, Serial ATA International Organization (2007), rev. 1.0.

2

# Integrated Frequency References

Economic motivations often drive innovation in circuit design. In the case of frequency references, the incentive results from increased system costs associated with quartz crystals. The recent success of MEMS-based frequency references confirms the economic value of increased integration.

The main goal of this thesis is to realize fully integrated, CMOS-compatible frequency references with reasonable accuracy. This goal has yet to be fully achieved due to the spread and temperature dependence of the components available in CMOS processes. This chapter will present a systematic study of these sources of inaccuracy in typical CMOS frequency references.

## **2.1.** Introduction

Building a frequency reference involves three distinct steps. Firstly, a stable physical quantity defining the oscillation frequency must be selected. Then, a mechanism must be designed to maintain a stable oscillation at this frequency. Finally, the effect of external sources of frequency variation, such as temperature, humidity, and physical stress, must be corrected.

Building an *integrated* frequency reference means that these steps must be carried out within the confines of integrated circuit technology. Unfortunately, this limits the variety of physical mechanisms that can be used to define the oscillation frequency. On the flip side, integrated circuit technologies exhibit some of the tightest tolerances known to humanity. The accuracy of photolithography allows the definition of geometric structures with very high repeatability, resulting in components with low mismatch. Also, the materials used in these processes are generally highly pure. The mono-crystalline silicon used in the substrate of integrated circuits has impurity densities of a few parts part-per-billion. So, it should be possible to exploit the strengths of integrated circuit technologies to realize very accurate frequency references.

Another advantage of integrated circuit technology is the availability of significant computational resources, especially in advanced CMOS technologies. The possibility of *going digital* enables complex solutions that are not feasible with analog techniques alone.

This chapter reviews the state-of-the-art in integrated frequency reference design at the conception of this work. First, integrated time constants commonly available in standard CMOS processes and the circuit elements used to build them will be discussed, focusing on their accuracy. Next, circuit architectures to realize oscillators will be presented. The primary error sources in these circuit architectures will be identified. Then, methods used to compensate for these error sources will be studied. Finally, a survey of state-of-the-art integrated frequency references in 2018 will be presented to discern a promising direction for the work conducted in this thesis.

#### **2.2.** Integrated Time Constants

The first step in building an integrated frequency reference is the choice of an integrated time constant, i.e., a physical quantity with units of seconds that defines the oscillation frequency. A fully integrated frequency reference should derive its time constant using only the available integrated circuit components. References based on MEMS, BAW, or SAW resonators do not comply with this requirement as they require additional processing steps or package-level integration of multiple chips.

Unfortunately, searching for a standard CMOS-compatible time constant yields only a few options. Combinations of various circuit elements, resistors, capacitors, and inductors are the most common, resulting in resistor-capacitor (RC) and inductor-capacitor (LC) time constants. In addition, thermal time constants can be used to build frequency references [1, 2]. In the rest of this section, these time constants and the circuit elements that make them will be discussed.

#### 2.2.1. RC - Resistor & Capacitor

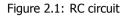

A resistor and a capacitor can be combined to realize an RC time constant. The capacitor stores energy as an accumulated charge over a potential difference, and the resistor then dissipates this energy by discharging the ca-

Figure 2.2: A typical resistor in a planar IC process

pacitor with a current proportional to the voltage across the capacitor and its resistance.

In Figure 2.1, the voltage across the simple RC network decays exponentially from its initial value by:

$$V(t) = V_0 e^{\frac{-t}{\tau_{RC}}} \quad \rightarrow \quad \tau_{RC} = RC \quad [s]$$

(2.1)

The time constant  $\tau_{RC}$  is the characteristic property of this first-order, linear time-invariant system. As expected, the unit of RC is in seconds; thus, an RC network can define the frequency of an oscillator.

#### **Integrated Resistors**

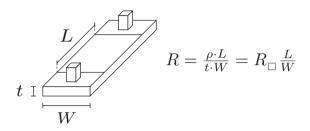

Resistors in integrated circuit technologies generally consist of thin planar strips of doped material sandwiched between two insulating layers. The well-known expression in Figure 2.2 gives the resistance R of such a planar structure, with width W, length L, thickness t, and resistivity  $\rho$ . Since the thickness of the layer is not a variable parameter in a planar IC process, the parameter R<sub> $\Box$ </sub> defines the resistivity of a square of material with constant thickness.

Nonidealities in the production process limit the accuracy of an integrated resistor. Variations in its dimensions or resistivity will cause its resistance to spread. Relative variations in the lateral dimensions can be mitigated by increasing the size of the resistor. However, the thickness of the layer is less well controlled, showing significant variation. Moreover, resistivity is a function of the doping level and spreads significantly between wafers.

The accuracy of integrated resistors is also limited by their temperature and voltage dependence. A large voltage across a resistor causes charge carrier velocity to approach the maximum drift velocity, causing an increase in resistivity. Similarly, temperature variation can cause changes in charge carrier concentration and mobility. The modulation of resistance due to these external factors can be modeled by the temperature and voltage coefficients  $TC_{1...N}$  and  $VC_{1...N}$  as in:

$$R(T,V) = \left(R_{\Box,0}\frac{L}{W}\right) \left(1 + TC_1(T - T_0) + TC_2(T - T_0)^2 + \dots\right)$$

$$\left(1 + VC_1(V - V_0) + VC_2(V - V_0)^2 + \dots\right)$$

(2.2)

#### Types of Integrated Resistors

Various integrated resistors can be fabricated in a typical planar CMOS process. The most commonly used layers are diffusion, polysilicon, and metal (Figure 2.3). These have different trade-offs between resistivity, absolute and relative accuracy, and voltage and temperature coefficients. The properties and trade-offs of these commonly used integrated resistors are discussed below.

**Diffusion Resistors** Diffusion resistors consist of bulk silicon doped with positive or negative charge donors. The doping modulates the charge concentration of the material, modulating its resistivity. Highly doped diffusion layers (P<sup>+</sup> and N<sup>+</sup>) are used to form the source/drain terminals of MOS transistors. They have relatively low resistivity ( $R_{\Box}$ =10-100 $\Omega$ ) but have high absolute variation (±25%) due to their dependence on dopant concentration. Their temperature dependence is due to the reduced mobility of charge carriers with increasing temperature, resulting in positive TCs of about 1500 ppm/°C. Lightly doped diffusion layers (P<sup>-</sup> and N<sup>-</sup>) are used to form the bulk region of MOS transistors. Due to their low impurity count, they provide high resistivity ( $R_{\Box}$ =1000-5000  $\Omega$ ) but also have higher absolute variation (±40%). Moreover, they have a much higher voltage coefficient of 8000 ppm/V and a temperature coefficient of 4000 ppm/°C. Diffusion resistors have additional nonidealities, such as the voltage dependence

Figure 2.3: Different types of resistors in a standard CMOS process

of their parasitic capacitance, leakage effects, and high mechanical stress sensitivity. Due to these reasons, they are usually not preferred for highaccuracy applications.

**Polysilicon Resistors** Polysilicon (polycrystalline silicon) is often used as the gate material of short-channel (< 1µm) planar MOS devices. Depending on its doping levels, polysilicon can provide a relatively high resistivity ( $R_{\Box}$ =100-1000  $\Omega$ ) but with a high absolute resistivity variation (±25%).

Additionally, it is possible to modulate the TCs of polysilicon resistors by modulating their doping concentration [3]. Their TCs can be tuned to cover a broad range, from -1500 ppm/°C to 1500 ppm/°C, including values as low as 100 ppm/°C. Polysilicon resistors are also quite linear, with voltage coefficients of about 100 ppm/V. Being sandwiched between oxide layers, they display relatively low parasitic capacitance, which is desirable in high-speed applications. For these reasons, polysilicon resistors are the preferred choice for building frequency references, as evidenced by their widespread use [4–7]. Polysilicon resistors are used in the RC frequency references in chapters 4 and 5.

**Silicided Resistors** Doped silicon or polysilicon can be combined with a metal such as nickel, cobalt, titanium, or tungsten to form a silicide, which reduces their resistivity further. These metallic silicon compounds retain the properties of both their constituents. They have low resistivity ( $R_{\Box}$ =5-10  $\Omega$ ) compared to unsilicided polysilicon, but still much higher than that of

metals. They inherit the temperature sensitivity of the metal, resulting in significant positive temperature coefficients on the order of 3000 ppm/°C [8]. They also exhibit relatively low absolute variation since their resistivity is not dependent on dopant concentration. Their high TCs and low resistivity variation make them especially attractive for high-resolution temperature sensors [9]. Silicided polysilicon resistors are used in the Dual-RC frequency reference presented in chapter 4.

**Metal Resistors** Metal interconnects, generally used as electrical connections between circuit elements, can also be used to build integrated resistors. They have very low resistivity ( $R_{\Box}$ =50-70 m $\Omega$  for thin metal layers,  $R_{\Box}$ =10-40 m $\Omega$  for thick metal layers), which makes them suitable for use as interconnects. Their absolute accuracy is high, primarily limited by geometry effects. Metal resistors are also highly linear. However, they have high TCs of 3000 ppm/°C due to the reduction of electron mobility at high temperatures. Metal resistors are not commonly used in circuit design due to the difficulty of achieving high resistances in a feasible circuit area.

**Thin Film Resistors** Thin films of conductive material deposited onto insulators may be used as integrated resistors. Compounds such as nickelchromium (NiCr) or silicon-chromium (SiCr) can be deposited with thicknesses ranging from 3-200 nm by sputtering them on an insulating silicon oxide layer. This allows for precise film thickness control, enabling resistors with a wide range of resistivity ( $R_{\Box}$ =30-2000  $\Omega$ ) [10] with very low absolute resistivity variation. Also, their temperature sensitivities can be finely tuned to near zero by controlling their annealing properties [11]. These properties make thin-film resistors attractive in high-accuracy circuit design, including frequency references [12]. However, their integration requires additional process steps, which makes them a non-standard option in planar CMOS processes. Polysilicon and diffusion resistors are impossible to realize in FinFET processes due to the quantized nature of the transistors. In such processes, thin-film resistors have become the sole option [13].

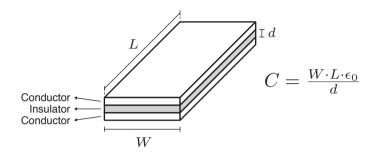

#### **Integrated Capacitors**

Capacitors implemented in integrated circuit technologies generally belong to one of two categories. A parallel plate capacitor can be built using two conducting layers separated by an insulator. The parasitics of active devices, such as diodes formed by PN junctions or MOS gates, can also be used as capacitors.

Figure 2.4: A typical parallel plate capacitor in a planar IC process

Capacitors based on the parasitics of active devices are available in all CMOS processes. Usually, these capacitors show good capacitance density (5 fF/ $\mu$ m<sup>2</sup>). However, their values depend heavily on doping concentration and so spread significantly. Similarly, their capacitance is generally a function of the depletion region width, which, in turn, is a strong function of voltage and temperature. Their voltage dependence limits their use when large voltage swings occur, as may be expected from oscillators. Their temperature dependence and its variation represent another source of error. Additionally, reverse-biased PN junctions are prone to leakage. The leakage current is a highly temperature-dependent parasitic parameter and behaves like a parallel, nonlinear resistor across the capacitor.

Capacitors that consist of two conducting layers separated by an insulator do not suffer from most of the parasitic effects of device capacitors, making them the preferred choice for applications that require accuracy. They are traditionally constructed as parallel plate structures, as in Figure 2.4, but can be implemented as fingered wires or the more exotic woven or guasi-fractal structures [14]. The primary limit to the accuracy of such capacitors is the thickness variation of their insulating layers, which is usually around 10%. Typically, only metal-oxide-metal (MOM) capacitors are available, where interconnect metals are used as the conducting layers. MOM capacitors have generally high voltage ratings due to the thick oxide layer separating them but consequently have low capacitance density (> 1 fF/ $\mu$ m<sup>2</sup>). For frequency reference applications, the capacitor's absolute value (thus the density) is also essential. Metal-insulator-metal (MIM) capacitors, where a thin layer of an insulator is deposited between an intermediate metal layer, are the preferred choice for this application. These capacitors benefit from the high capacitance density granted by the low-thickness insulator but come at the cost of an additional mask and are generally available only as an extra option.

2.2.2. LC - Inductor & Capacitor

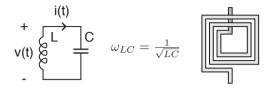

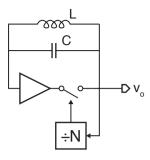

Figure 2.5: LC circuit and a planar inductor

Another commonly used electrical on-chip time constant is the LC tank. Like the capacitor, the inductor is a circuit element that stores energy. As the current flow through the inductor changes, a magnetic field is induced, which creates a potential difference across the inductor that opposes the current flow. The energy required to overcome this potential is stored in the magnetic field. Contrary to an RC circuit, in an LC tank, energy is not dissipated but transferred between the capacitor and the inductor.

The time constant for the LC tank in Figure 2.5 can be derived from its natural frequency: the frequency at which the energy transfer between the two components occurs.

$$i(t) = Ae^{j\frac{-t}{\sqrt{LC}} + j\phi_0} \quad \to \quad \tau_{LC} = \frac{1}{\omega_n} = \sqrt{LC} \qquad [s]$$

(2.3)

The LC time constant is again in the unit of seconds, implying that an LC tank can be used to define the frequency of an oscillator.

Integrated inductors can be realized as planar coils in metal interconnect layers of a circuit process. Generally, higher metal layers with low resistivity are preferred to build inductors, resulting in lower losses and higher quality factors. As the coil geometry defines the inductive properties of these coils, layer thickness variations that reduce the accuracy of integrated capacitors are not of great concern for inductors. Moreover, their temperature coefficients are low and related to the parasitic resistance of the coil and their quality factors [15]. These stable and well-defined properties of inductors make them attractive candidates for building frequency references.

Unfortunately, practical size limitations limit the viable inductance values achievable on-chip. A  $200x200 \ \mu m$  multiple-turn coil inductor will generally

have 100s of pH inductance [16]. This limitation and practical area requirements for integrated capacitors result in resonance frequencies in the GHz range for integrated LC tanks. These GHz frequency outputs and the frequency dividers following them generally result in high power dissipation for LC frequency references [17, 18].

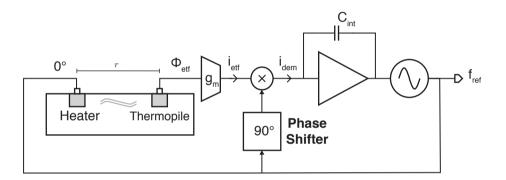

#### 2.2.3. Thermal Diffusivity

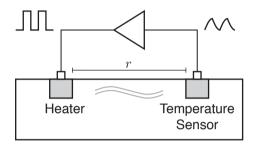

Figure 2.6: The thermal oscillator

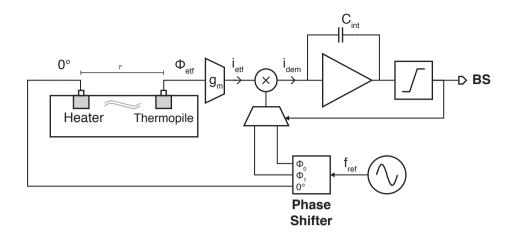

On-chip time constants can also be created in the thermal domain. For example, a thermal oscillator can be made [19], which consists of a thermal delay line in an electrical feedback loop. As shown in Figure 2.6, a thermal delay line can be made by implementing a heater and a temperature sensor in close proximity on a silicon chip. Driving the heater generates heat waves that diffuse through the silicon substrate and cause temperature fluctuations. A temperature sensor placed a distance r away senses the temperature in its vicinity and drives the amplifier, closing the feedback loop. The power dissipated at the resistor will cause temperature fluctuations in the substrate that decrease as the distance from the resistor increases. Additionally, due to the thermal inertia of the substrate, it will take a specific time before the temperature change reaches the sensor. The oscillation frequency will be defined by the dynamics of this electrothermal system, known as an electrothermal filter (ETF).

The heat equation that describes the dynamic behavior of an ETF is a partial differential equation that relates the rate of temperature change to the temperature gradient:

$$\frac{\partial T}{\partial t} = \frac{k}{c\rho} \nabla^2 T \tag{2.4}$$

where

2

$$D = \frac{k}{c\rho} \qquad \left[\frac{m^2}{s}\right] \tag{2.5}$$

where k is thermal conductivity, c is the specific heat capacity, and  $\rho$  is density.

Electrothermal filters can be analyzed with an electrical analogy between the electrical and thermal domains [20]. The temperature T [K] can be regarded as an electrical potential, and heat flow [W/s] can be regarded as an electrical current. It is then possible to define a thermal impedance  $Z_{TH}$  as the ratio of the temperature fluctuations at the temperature sensor,  $\Delta T$ , to the heat flow, P. For a simplified electrothermal filter with a point heat source and a point temperature sensor, the frequency-dependent thermal impedance is given by [21]:

$$Z_{TH}(\omega) = \frac{1}{2\pi k r} e^{-r\sqrt{\frac{\omega}{2D}}} e^{-jr\sqrt{\frac{\omega}{2D}}}$$

(2.6)

Assuming an amplitude control mechanism ensures unity loop gain, the oscillation frequency  $\omega_{TH}$  for the thermal oscillator of Figure 2.6 is when the phase shift across the filter is  $2\pi$ .

$$\angle Z_{TH} = -r \sqrt{\frac{\omega_{TH}}{2D}} = 2\pi \tag{2.7}$$

The thermal time constant of the electrothermal filter in seconds can then be derived as:

$$\tau_{TH} = \frac{r^2}{4\pi D} \qquad [s] \tag{2.8}$$

The electrothermal time constant depends on two parameters: the distance between the heater and the sensor and the thermal diffusivity of silicon. Both of these parameters are highly controlled in integrated circuit processes. The bulk material is a single silicon crystal (mono-crystalline silicon) and is one of the purest manufactured materials. Similarly, the parameter r, the distance between the heater and the sensor, is dependent on the accuracy of the photolithographic process and is controlled to a sub-nm level in modern CMOS processes. Relatively small electrothermal filters that promise high accuracy can be built by taking advantage of the high level of control [2].

The primary disadvantage of electrothermal filters is the high power consumption of the heater. The only way to increase the temperature signal

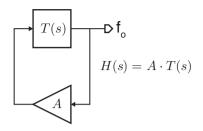

Figure 2.7: A feedback network representation of an oscillator with the frequency selective linear T(s) and the amplifier A

at the thermal sensor is to dissipate more power in the heating element, implying a low quality-factor for electrothermal filters. The implementation in [1] dissipates 2.1 mW of power to achieve a 48 ps jitter.

# **2.3.** Oscillator Architectures

A stable oscillator needs to maintain its output frequency *and* amplitude over time. Losses in practical time constants will dampen oscillations and need to be compensated via an active circuit. In a practical oscillator, an active circuit injects energy into the system from a DC power source to ensure that the oscillation amplitude does not decay over time.

The architecture of such an active circuit may dramatically affect the oscillator's performance. Oscillators can be categorized into two groups depending on the linearity of their active element: harmonic and relaxation oscillators. The rest of this section discusses these categories of oscillators.

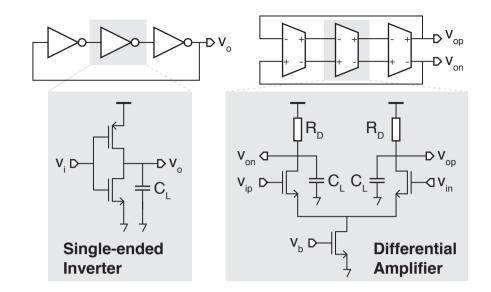

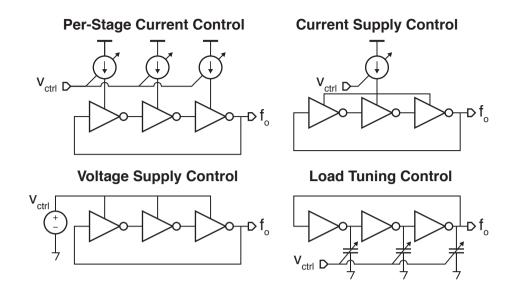

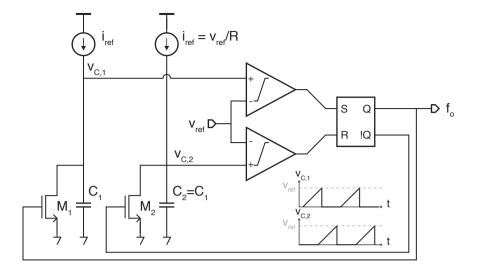

#### 2.3.1. Harmonic Oscillators

Oscillators that output a spectrally pure sine wave are called harmonic oscillators. They generally consist of linear components whose dynamics can be readily analyzed with feedback theory.

An essential foundational theory for electrical oscillators is the Barkhausen stability criterion, which describes a mathematical condition for a feedback circuit to maintain a stable oscillation. A stable oscillation is defined as having a constant frequency and amplitude. Given a feedback network, as shown in Figure 2.7, where an amplifier A closes the loop around a linear network with the transfer function T(s), the criterion states that a stable oscillation will occur when:

Figure 2.8: The Wien Bridge oscillator

$$|H(s)| = 1$$

$$\angle H(s) = N \cdot 2\pi$$

$$N \in \mathbb{Z}$$

For stable oscillation, the phase shift around the loop must be an integer multiple of  $2\pi$ . Additionally, the loop gain at the oscillation frequency must be unity. If the gain exceeds unity, the oscillation amplitude will grow, bounded by the range of the amplifier. If the gain is smaller than unity, the oscillation will decay, or the oscillator will not start. In reality, the amplifier needs to provide a gain greater than unity to ensure a fast start-up, and the gain needs to reduce to unity after the required amplitude level has been reached.

In the following, the characteristics of some common harmonic oscillators used in the literature are described.

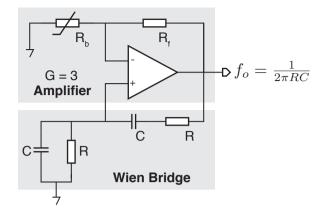

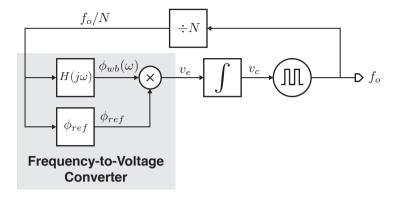

#### Wien Bridge Oscillator

The Wien Bridge oscillator is a well-known harmonic oscillator circuit. Its simplified schematic is shown in Figure 2.8. The Wien Bridge is a passive network of two resistors and capacitors with a band-pass response. At its center frequency, defined by  $1/2\pi$ RC, the Wien Bridge has 0° phase shift and a gain of 1/3. The amplifier is configured to have a gain of R<sub>f</sub>/R<sub>b</sub> = 3 to compensate for the loss in the Wien Bridge. Although this gain is not enough to guarantee start-up, making the gain larger causes the oscillation amplitude to grow, saturating the amplifier and degrading the spectral purity of the output.

Figure 2.9: Integrated Wien Bridge oscillator implemented in [4]

In his 1939 patent, the problem of stabilizing the feedback gain was solved by Bill Hewlett (of Hewlett-Packard fame) using a positive TC thermistor for  $R_b$ [22]. Before the oscillator starts,  $R_f/R_b$  is greater than 3. As the oscillation builds up, the current flowing through  $R_b$  increases its resistance and reduces the amplifier gain. This mildly nonlinear effect stabilizes the gain, resulting in a high linearity sine wave at the output. It was this spectral purity that ensured the success of the very first product of Hewlett-Packard, the low-distortion audio oscillator, HP200A [23].

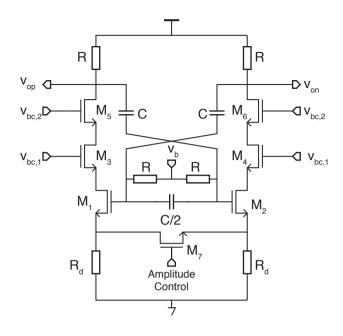

Recently, integrated frequency references based on Wien Bridge oscillators have been presented [4, 5]. Figure 2.9 shows the circuit diagram of the 6 MHz Wien Bridge oscillator in [4]. Its fully differential Wien Bridges incorporates complementary TC polysilicon resistors combined to lower their temperature coefficient and MIM capacitors for high accuracy. Degenerating  $M_{1,2}$  by  $R_d$  provides the gain  $R/R_d = 3$  needed to achieve unity loop gain. A separate amplitude control loop (not shown) detects the output amplitude and tunes the degeneration resistors via  $M_7$  to regulate the gain. This design's primary challenge is to achieve an high output-impedance amplifier as it alters the Wien Bridge transfer function and causes a shift in the output frequency. Moreover, the output impedance is a function of MOS device pa-

Figure 2.10: LC harmonic oscillator schematic in two-stage, cross-coupled pair, and negative resistance forms

rameters, which are less accurate than the Wien Bridge elements. In [4], the output impedance is increased by the double gain-boosted cascode transistors  $M_{3-6}$ . This design achieves a ±26400 ppm absolute inaccuracy for seven measured samples ( $3\sigma$ ), with a temperature dependency of 86 ppm/°C.

#### LC Oscillators

LC circuits derive their time constant from the energy exchange between two storage elements at their resonance frequency. The resonant elements with a high quality-factor result in LC networks with excellent frequency selectivity that can be used to realize harmonic oscillators.

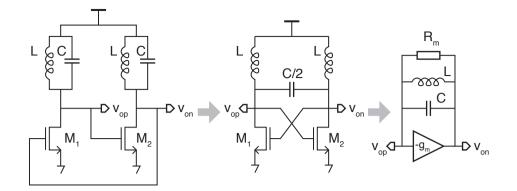

Figure 2.10 shows a typical integrated LC oscillator circuit in its three common forms: two cascaded stages, a cross-coupled pair, and simplified negative resistance [16]. The operation of the cross-coupled pair in a harmonic oscillator is easier to understand when seen as a derivative of the two-stage oscillator. In each stage, an inverting common-source transistor drives an LC load that exhibits high impedance and 0° phase shift at its resonance frequency. Due to the two cascaded inverting stages, the loop gain has a 360° phase shift. As long as the transistors have the transconductance needed to achieve larger than unity gain at the resonance frequency, oscillation will start.

The two stages must provide unity gain at the resonance frequency to maintain a stable oscillation amplitude. The loss the LC tank exhibits at its resonance frequency can be represented by the parallel resistor,  $R_m$ . The cross-coupled pair behaves as a *negative* transconductance: a positive voltage across the oscillator outputs results in a negative current to be drawn from the tank. The transistors  $M_{1,2}$  can be sized or biased to provide

Figure 2.11: Temperature-independent LC oscillator used in [18]

a transconductance with a magnitude equal to  $1/R_m$  at the oscillation frequency, which achieves unity gain and a stable oscillation frequency. The oscillator also provides some in-built amplitude control, as increasing oscillation amplitude reduces the headroom of  $M_{1,2}$ , pushing them out of saturation and reducing their excess gain.

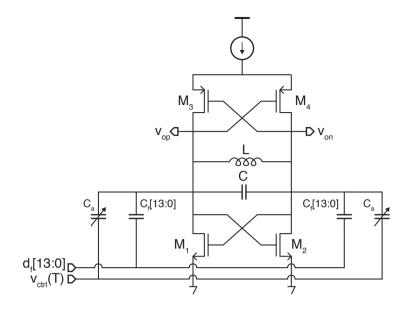

Integrated frequency references based on LC oscillators were used in the early 2000s as crystal replacements [18]. Initially supporting better than  $\pm 500$  ppm inaccuracy over PVT, they were targeted to replace external crystals used for wireline communication protocols such as USB 2.0 [17]. The design in [18], shown in Figure 2.11, uses complementary cross-coupled NMOS and PMOS pairs, biased with a temperature-independent constant current. The LC oscillator is designed to oscillate at 800 MHz, which is divided by 16 to provide a 25 MHz reference output. Two capacitor banks allow the tank frequency to be tuned to reduce the spread. The digitally programmable bank (C<sub>f</sub>) consists of switched MOS capacitors and allows post-production trim of the tank frequency, covering  $\pm 10\%$  with 20 ppm steps. The programmable analog bank (C<sub>a</sub>) consists of accumulation-mode PMOS varactors controlled by a temperature-dependent bias voltage v<sub>c</sub>(T). This voltage is generated via a programmable resistor network that features selectable p-poly, n-poly, p-diffusion, and n-well resistors to fine-tune its TC

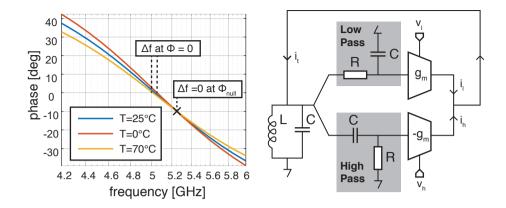

Figure 2.12: The LC oscillator in [25] based on achieving oscillation at  $\Phi_{\mbox{null}},$  where the TC of the tank is the lowest

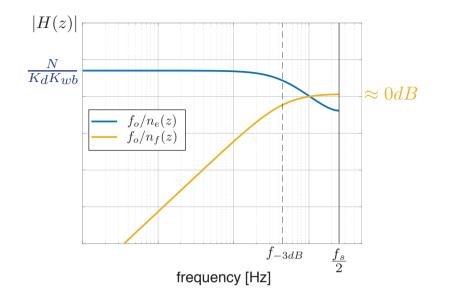

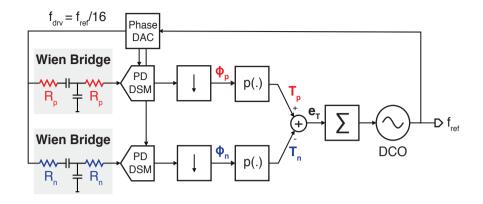

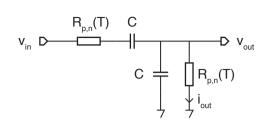

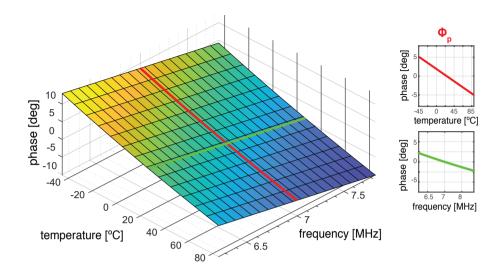

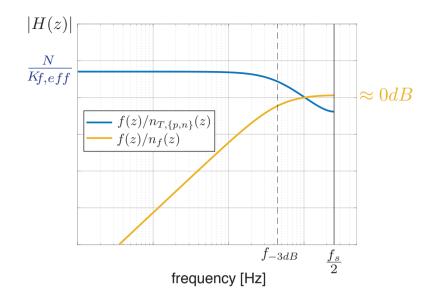

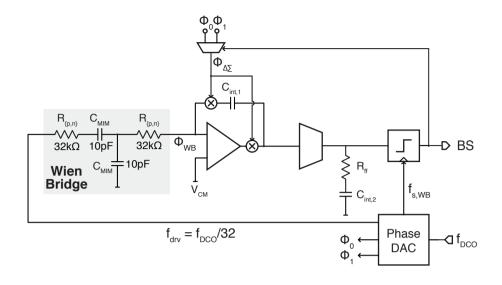

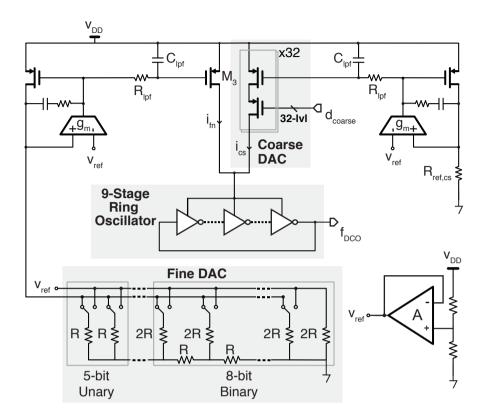

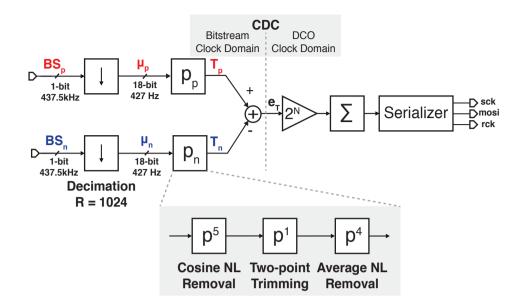

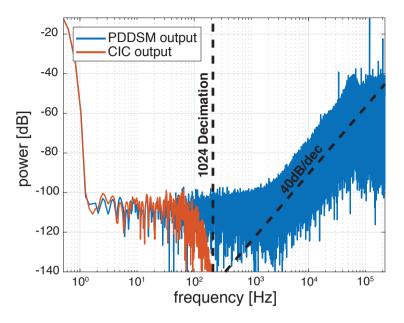

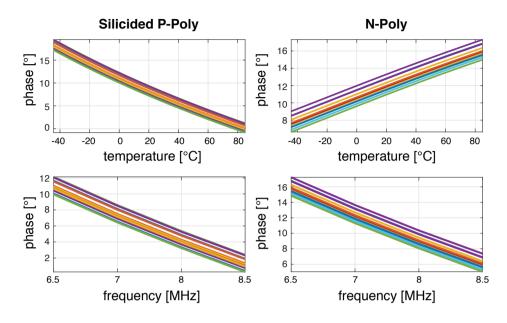

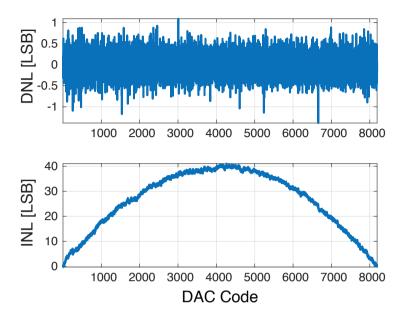

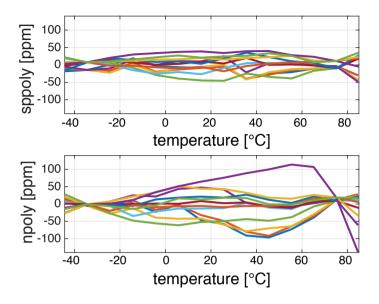

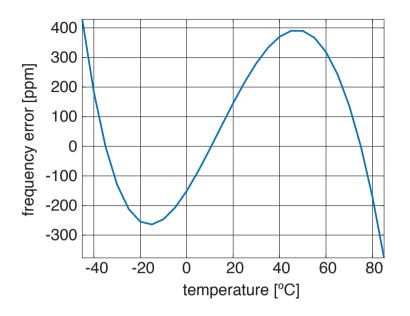

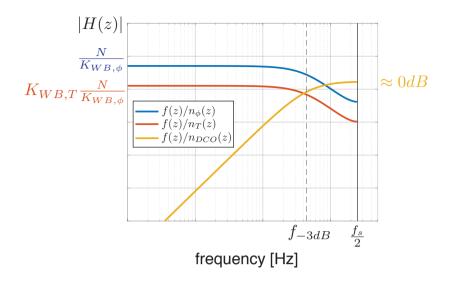

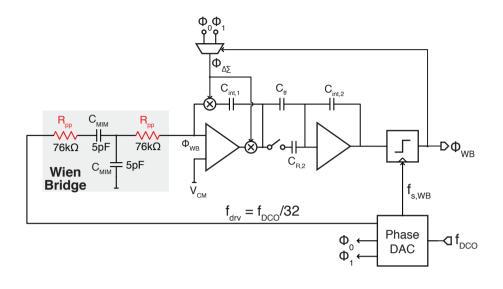

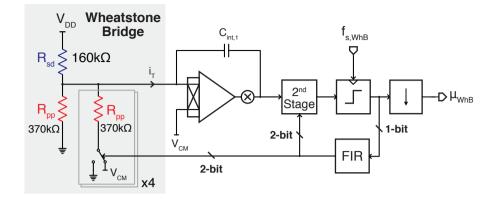

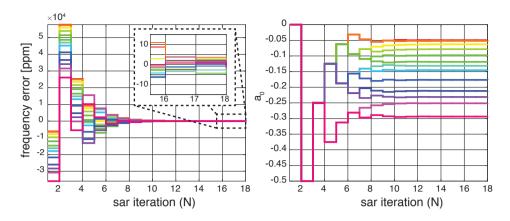

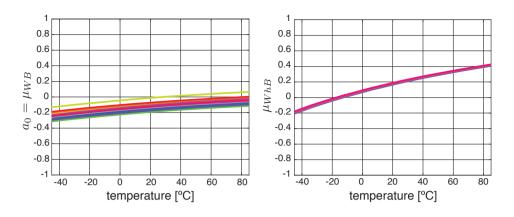

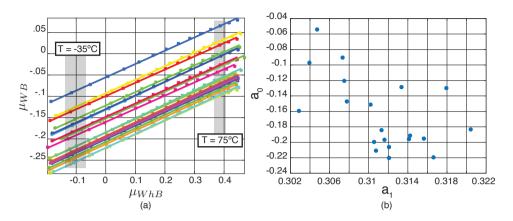

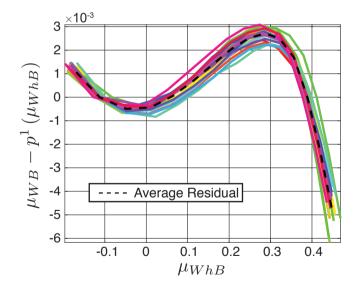

to compensate for that of the oscillator itself and achieve frequency trimming in production [17]. The design achieves  $\pm 152$  ppm absolute accuracy from -10 °C to 80 °C for ten compensated devices while dissipating 60 mW. The excellent inaccuracy achieved demonstrated, for the first time, that fully integrated frequency references could challenge the accuracy of crystal oscillators.