# MMIC RF Power Amplifier Design

At 10 GHz in 0.12  $\mu$ m GaN Technology

# MMIC RF Power Amplifier Design

At 10 GHz in 0.12  $\mu m$  GaN Technology

by

# Laura M. van Vliet

Student Name Student Number

Laura M. van Vliet 5767776

Supervisor MAD Lab: Simon J. Mahon

Supervisor TU Delft: İlke Ercan

Additional Support: David J. Niven (MAD Lab)

Project Duration: July, 2024 - August, 2025

Faculty: Electrical Engineering, Mathematics & Computer Science, Delft Thesis committee: İlke Ercan, Simon J. Mahon, Dennis van der Born and Ioan Lager

# Preface and Acknowledgements

This work documents my activities in the final project in the bachelor programme Electrical Engineering at the Delft University of Technology, The Netherlands. The work was performed during two internships at the MAD Lab of the Macquarie University in Sydney, Australia: I am very grateful to the Delft University of Technology and Macquarie University for facilitating this international collaboration.

I am very grateful to the entire staff of the MAD Lab in Sydney. Their openness to receive a bachelor student, deal with all my questions and tirelessly explain and help me on my way was superb. It taught me a lot about Australian hospitality and brought my microwave knowlegde from very elementary up to a level that I could successfully design a 10 GHz MMIC. I cannot name all the individual contributions, there were so many and in so diverse way, but I want extent my special thanks to Simon Mahon and David Niven for their exceptional support. To Melissa, Evan, Andrew, Imelda, Mohammed, Jakov, Anthony, Jeremy, Benny, to the entire MAD Lab staff: Thank you!

I am grateful to the Delft University of Technology for allowing me to do this final project in Australia, it has very much contributed to my personal growth. Many people played a role, but I would particularly like to thank İlke Ercan who was involved most closely.

We acknowledge WIN Semiconductors Corp. for providing access to their NP12 GaN HEMT process and supporting the design. Evidently, this work could not have been performed without their support.

Laura M. van Vliet Sydney, September 2025

# **Abstract**

This work investigates whether a power amplifier (PA) designed for a lower operating frequency (10 GHz) can be effectively implemented using a process that has a  $f_{max}$  of well above 100 GHz. Operating a process far below its maximum frequency offers potential benefits in gain and efficiency, but also presents challenges. Particularly for the stability of the amplifier, which becomes increasingly critical at high gain levels.

To investegate the potential for such an RF power amplifier, Gallium Nitride (GaN) High Electron Mobility Transistors (HEMTs) are used. This is a technology that forms the current State-of-Art for microwave high-power high-efficiency MMICs. The circuit is fabricated using WIN Semiconductors NP12-01 GaN-on-SiC technology with 0.12  $\mu$ m gates. They offer a technology with one of the shortest gatelengths that are around in the industry.

First a Programme of Requirements was established, before starting the design and four Key Performance Indicators (power, efficiency, stability and size) were defined. A design process was followed that started with transistor measurements, after which an architectural design was made, followed by schematic implementation, electromagnetic (EM) modelling and final layout creation. Continuous refinement between schematic, EM and layout stages where necessary to avoid excessive simulation times. After design rule verification and stability checks, the circuit was submitted for fabrication, with MMIC samples received back approximately four months later, after which, an extensive characterization of MMICs was performed, through both small-signal as well as non-linear measurements.

All this work resulted in the following KPI's:

- For the power, a peak power of over 38 dBm was realized under dedicated measurement conditions and over 35 dBm for nominal measurement conditions (20 V  $V_{DS}$ ) and a bandwidth of more than 2 GHz (-1 dB bandwidth) or 3 GHz (3-dB bandwidth) was obtained.

- For the PAE, 35% was nominally achieved over various bias points and frequencies.

- Unconditional stability was achieved.

- The size of the amplifier was 2x1.75 mm<sup>2</sup>, resulting in slightly below 2 W/mm.

While amplifiers with higher absolute power at X-band exist, the NP12 process is unlikely to surpass the state-of-the-art in this regard due to its limited maximum drain voltage, which constrains the achievable output power. However, the measured efficiency and gain are promising for a first design iteration. Notably, the implementation of the stability analysis for this power amplifier took a significant effort, but was proved highly effective as no instability was observed at all during the measurements. Two variations of the amplifier were implemented to investigate the possibility of reusing the source via-hole for two adjacent output stage transistors. This variation, with re-used via-holes, worked similar to the baseline design, but exhibited a lower PAE.

In conclusion, the expectation is strengthened that the advantages of a mm-wave process used at X-band frequencies can pay off in a modest increase of the efficiency and a significantly increased gain. Finally, the work resulted in one conference publication, and two tutorial documents for future students (an AWR student guide and MMIC mounting tutorial).

# Contents

| Pro | etace               |                                                    | 1           |

|-----|---------------------|----------------------------------------------------|-------------|

| No  | men                 | clature                                            | ix          |

| 1   | Intro<br>1.1<br>1.2 | oduction General Introduction                      | 1<br>1<br>2 |

|     | 1.3                 | Problem Statement                                  | 2           |

|     | 1.4                 | Approach                                           | 2           |

|     | 1.5                 | Collaboration with Macquarie University            | 3           |

|     | 1.6                 | Thesis outline                                     | 3           |

| 2   |                     | gramme of Requirements                             | 5           |

|     | 2.1                 | Introduction                                       | 5           |

|     | 2.2                 | Mandatory Requirements                             | 5           |

|     | 2.3                 | Objectives                                         | 5<br>6      |

|     |                     | 2.3.1 Functional Requirements                      | 6           |

|     |                     | <ul><li>2.3.2 Manufacturing Requirements</li></ul> | 6           |

|     | 2.4                 | Key Performance Indicators                         | 6           |

|     |                     |                                                    |             |

| 3   |                     | ign Methodology                                    | 7           |

|     | 3.1                 | MMIC Semiconductor Technologies                    | 7           |

|     | 3.2                 | High Electron Mobility Transistors (HEMTs)         | 8           |

|     | 3.3                 | Linear Transistor Behaviour                        | 10          |

|     |                     | 3.3.1 Linear Transistor Modeling                   | 10          |

|     |                     | 3.3.2 S-Parameters                                 | 11<br>12    |

|     | 2.4                 | 3.3.3 Gain                                         | 12          |

|     | 3.4                 | Non-linear Transistor Behaviour                    | 12          |

|     |                     | 3.4.2 Large-Signal Metrics                         | 14          |

|     |                     | 3.4.3 AWR Microwave Office <sup>TM</sup>           | 18          |

|     | 3.5                 | Load-pull                                          | 18          |

|     | 3.6                 | Impedance Matching Networks                        | 18          |

|     | 3.7                 | Chip layout                                        | 19          |

|     | 3.8                 | Electromagnetic Simulation                         | 19          |

|     | 3.9                 | Stability Checks                                   | 20          |

|     | 0.7                 | 3.9.1 K-factor                                     | 20          |

|     |                     | 3.9.2 Ohtomo Stability Analysis                    | 21          |

|     | 3.10                | Design Rule Check                                  | 22          |

|     | 3.11                | Connectivity Check                                 | 22          |

| 1   |                     | ign Implementation                                 | 24          |

| 4   | 4.1                 | NP12-01 Technology                                 | 24          |

|     | 4.2                 | E0300: X-band Power Amplifier                      | 24          |

|     | T.4                 | 4.2.1 Architecture                                 | 25          |

|     |                     | 4.2.2 Implementation                               | 28          |

|     | 4.3                 | Simulation Results                                 | 41          |

|     | 1.0                 | 4.3.1 S-Parameters                                 | 41          |

|     |                     | 4.3.2 Power                                        | 42          |

Contents

| 5  | Fabrication         44           5.1 Probe Pad Layout         44           5.2 Manufacturing         44                                                                                                                                                                                                                                                                 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6  | Measurement Setup         47           6.1 Mounting MMICs         47           6.2 S-Parameters measurement setup         47           6.3 Power measurement setup         48           6.4 Calibration         49                                                                                                                                                      |

| 7  | Measurement Results       50         7.1       S-Parameters       50         7.1.1       E0300: X-band Power Amplifier       50         7.1.2       E0302: E0300 with Alternative Transistor       53         7.2       Power       55         7.2.1       E0300: X-band Power Amplifier       55         7.2.2       E0302: E0300 with Alternative Transistor       57 |

| 8  | Discussion         8.1       S-Parameters       59         8.1.1       E0300: X-band Power Amplifier       59         8.1.2       E0302: E0300 with Alternative Transistor       60                                                                                                                                                                                     |

|    | 8.2 Power       61         8.2.1 E0300: X-band Power Amplifier       61         8.2.2 E0302: E0300 with Alternative Transistor       63         8.3 General Discussion       64                                                                                                                                                                                         |

| 9  | Conclusion and Future Work         9.1 Conclusion       66         9.1.1 Overview       66         9.1.2 Key Performance Indicators       66         9.1.3 Evaluation       66         9.2 Future Work       67         9.2.1 Design Optimization       67         9.2.2 Design Application       67                                                                    |

| Re | eferences 69                                                                                                                                                                                                                                                                                                                                                            |

| A  | Requirements Implementation       71         A.1 Mandatory Requirements       71         A.2 Objectives       71         A.2.1 Functional Requirements       71         A.2.2 Manufacturing Requirements       72         A.2.3 System Requirements       72                                                                                                            |

# List of Figures

| 1.1  | Example amplifier topology                                                                                                           | 3          |

|------|--------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.1  | Cross-sectional view showing material layers of a GaN HEMT structure                                                                 | 8          |

| 3.2  | Overview of EBL gate fabrication and GaN HEMT structure used in the RF power                                                         |            |

|      | amplifier design                                                                                                                     | 9          |

| 3.3  | Energy band diagram of a HEMT structure [3]                                                                                          | 9          |

| 3.4  | FET structure with equivalent circuit elements [5]                                                                                   | 10         |

| 3.5  | Two-port network                                                                                                                     | 11         |

| 3.6  | Linear Transistor Model                                                                                                              | 13         |

| 3.7  | Non-linear Intrinsic Circuit Model                                                                                                   | 13         |

| 3.8  | 1dB compression gain                                                                                                                 | 14         |

| 3.9  | Typical output power versus input power characteristic of a GaN power amplifier showing                                              |            |

|      | the linear region, 1-dB compression point, and saturation region                                                                     | 16         |

| 3.10 | Illustration of a distorted waveform decomposed into its fundamental and harmonic                                                    |            |

|      | frequency components [16]                                                                                                            | 17         |

| 3.11 | Schematic diagram of a load-pull measurement setup                                                                                   | 18         |

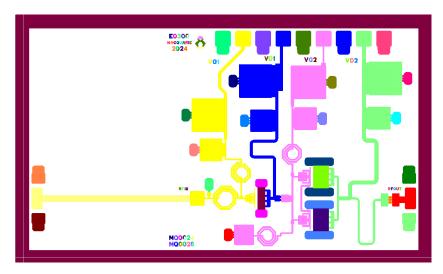

|      | Reticle Layout with Section Labels                                                                                                   | 19         |

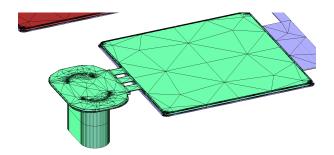

|      | Via structure in mesh layout using Axiem EM solver                                                                                   | 20         |

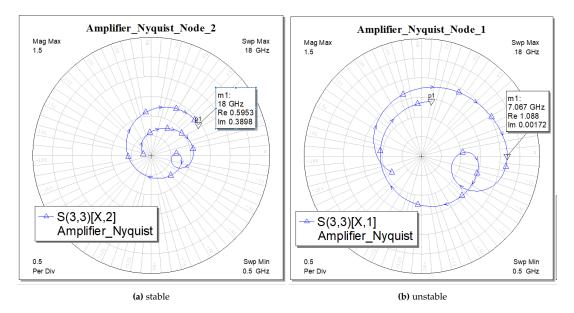

|      | Nyquist stability analysis of amplifier showing (a) stable and (b) unstable cases                                                    | 22         |

|      | Connectivity check                                                                                                                   | 23         |

| 11   | Planta di anno a Colla trans et a consultifica di ancien di alcunet del transactività con di actuari                                 |            |

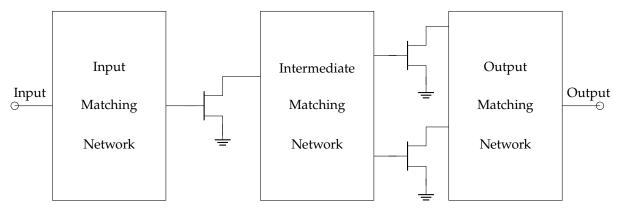

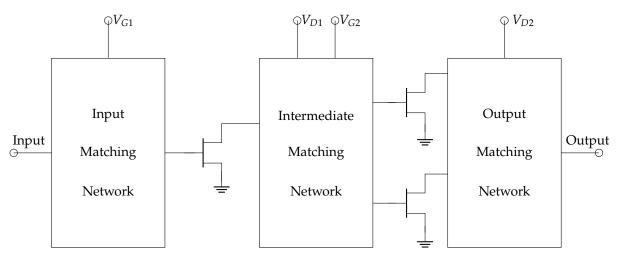

| 4.1  | Block diagram of the two-stage amplifier showing the input, intermediate and output                                                  | 25         |

| 4.2  | matching networks, along with the associated gate and drain bias connections                                                         | 25         |

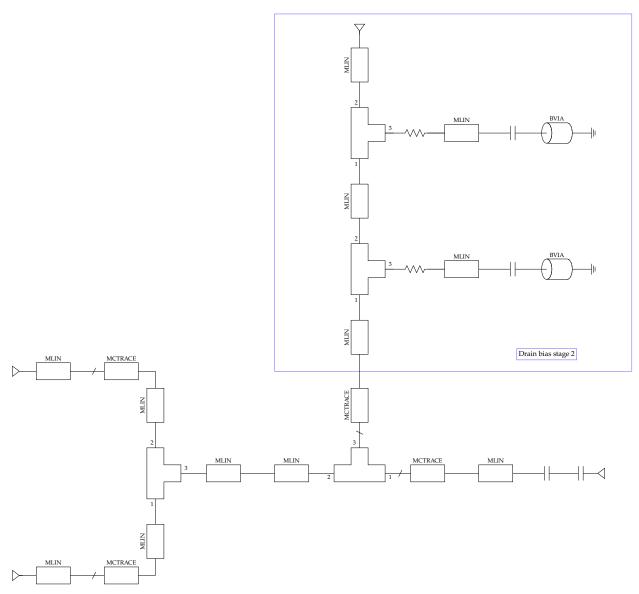

| 4.2  | Detailed schematic of the output matching network, including bias circuitry for the                                                  | 20         |

| 1.0  | second-stage drain $(V_{D2})$                                                                                                        | 26         |

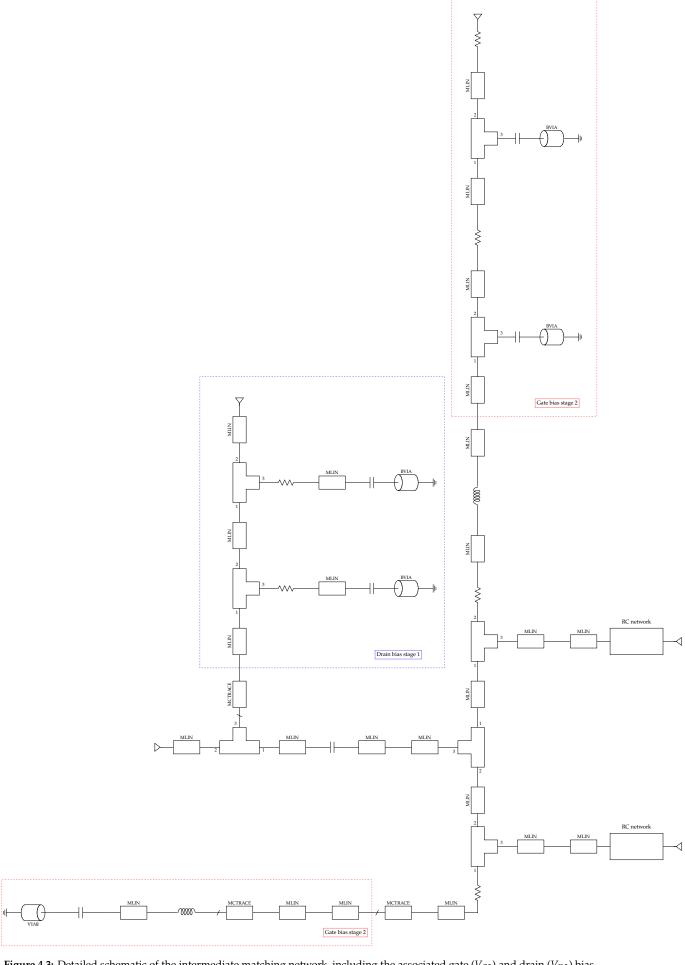

| 4.3  | Detailed schematic of the intermediate matching network, including the associated gate $(V_{G2})$ and drain $(V_{D2})$ bias networks | 27         |

| 4.4  | Detailed schematic of the input matching network, including bias circuitry for the                                                   |            |

|      | first-stage gate $(V_{G1})$                                                                                                          | 28         |

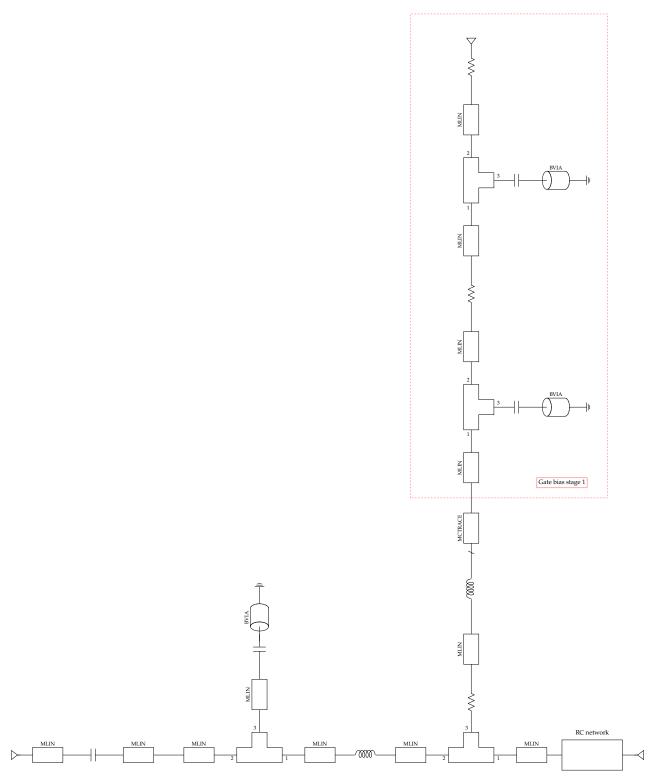

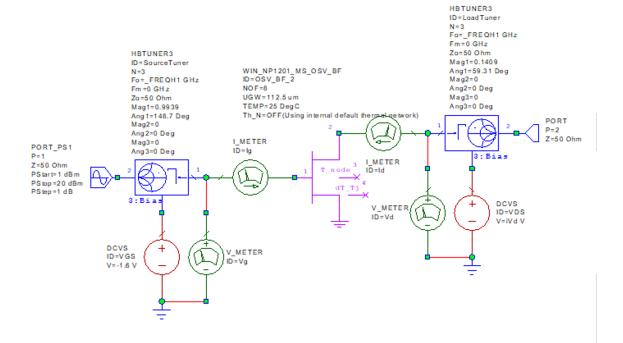

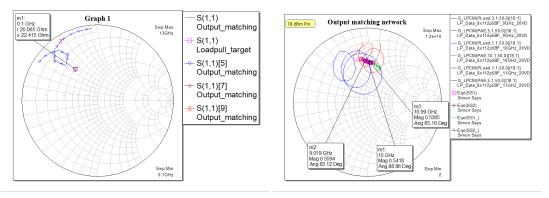

| 4.5  | Load-pull simulation schematic showing the structure and tuning elements                                                             | 29         |

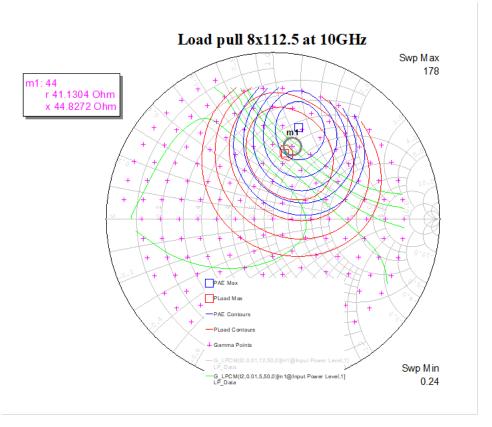

| 4.6  | Load-pull simulation results of a transistor with 8 fingers with a width of 122.5 $\mu$ m on a                                       |            |

| 1.0  | Smith chart showing contours of the output power ( $P_{out}$ ), power-added efficiency (PAE)                                         |            |

|      |                                                                                                                                      | 30         |

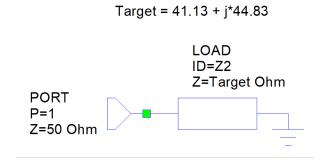

| 4.7  | Circuit representation fo the target impedance ( $Z = 41.13 + j44.83 \Omega$ ) at 10 GHz                                             | 31         |

| 4.8  | Smith chart output impedance transformation before and after application of the output                                               | 01         |

| 1.0  |                                                                                                                                      | 31         |

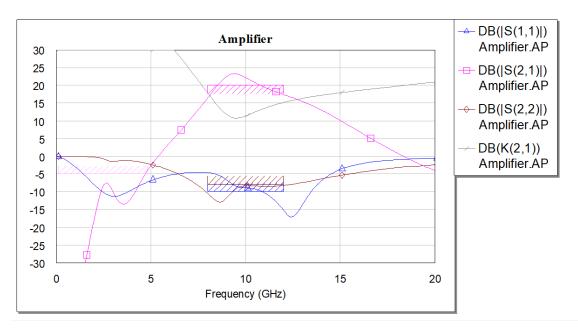

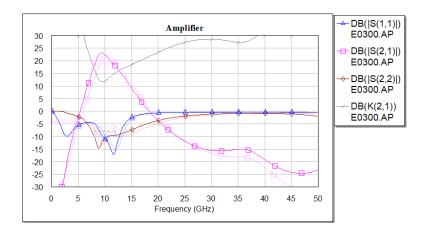

| 4.9  | Simulated S-parameters ( $S_{11}$ , $S_{21}$ , $S_{22}$ ) and stability factor (K-factor) of the designed                            | 51         |

| 4.7  | amplifier                                                                                                                            | 32         |

| 1 10 | amplifier                                                                                                                            | 32         |

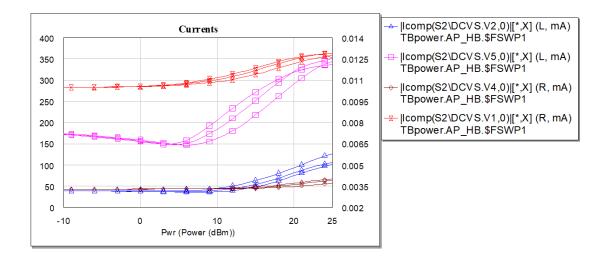

| 4.10 | Simulated bias currents as function of output power ( $P_{out}$ ). Drain currents, pink and                                          |            |

|      | blue, are plotted on the left y-axis, while gate currents, orange and brown, are plotted on                                          | 22         |

|      | the right y-axis.                                                                                                                    | 33         |

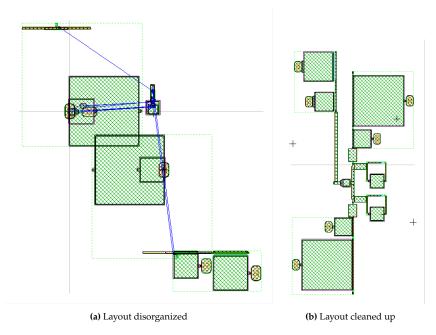

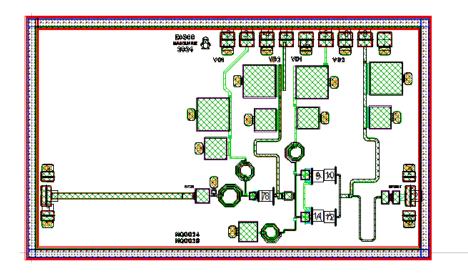

|      | Example layout                                                                                                                       | 34         |

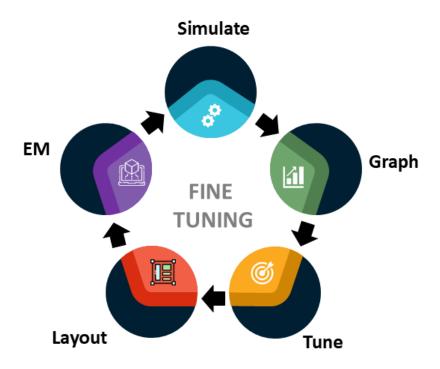

| 4.12 | Iterative fine-tuning cycle of the power amplifier design process, consisting of simulation,                                         | - <b>-</b> |

|      | result analysis, tuning, layout adjustments and EM simulations                                                                       | 35         |

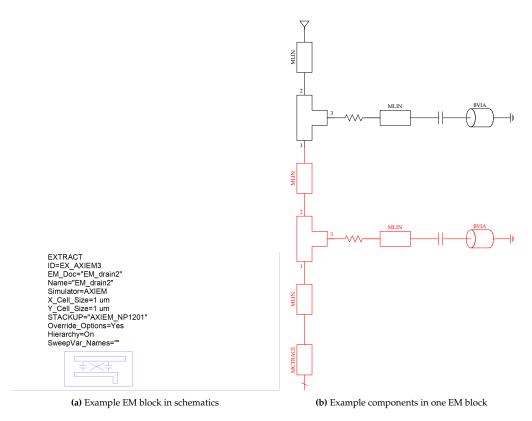

|      | EM where the schematics are directly connected to EM                                                                                 | 36         |

|      | Example of S-parameter variation before and after electromagnetic (EM) simulation                                                    | 36         |

|      |                                                                                                                                      | 37         |

|      | Comparison of port definition strategies in EM simulations                                                                           | 38         |

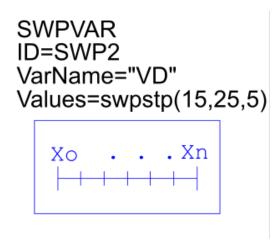

| 117  | Schamatic cotup for gate and drain voltage extrem                                                                                    | 20         |

List of Figures vi

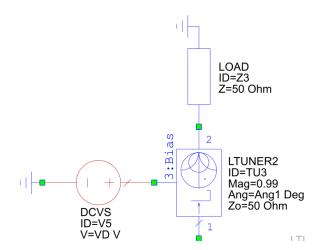

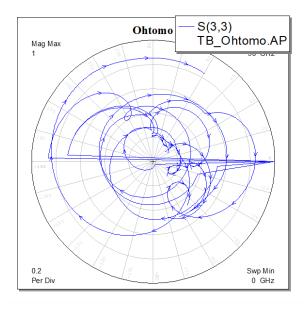

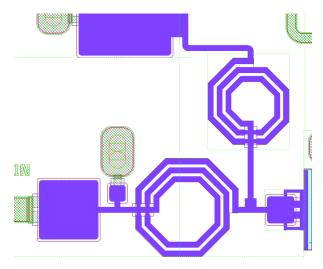

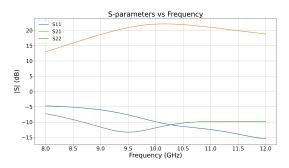

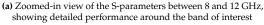

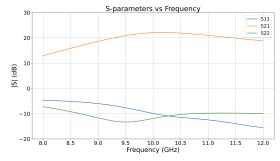

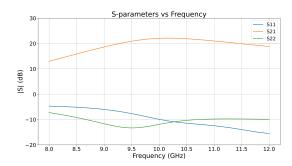

| 4.19<br>4.20<br>4.21              | Schematic setup for impedance sweep  Ohtomo stability analysis  Connectivity check in parts  Simulated S-parameters (S11, S21, S22) of one instance of the E0300 chip measured under nominal bias conditions | 39<br>40<br>41<br>41 |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                   | Simulated S-parameters (S11, S21, S22) and K-factor of one instance of the E0302 chip measured under nominal bias conditions                                                                                 | 42<br>42             |

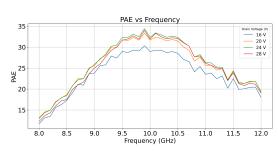

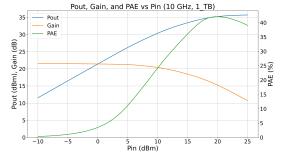

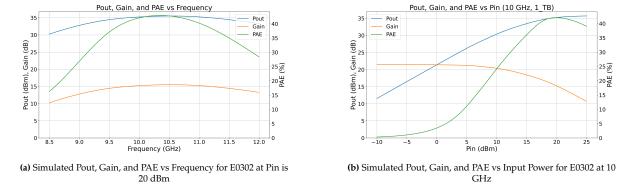

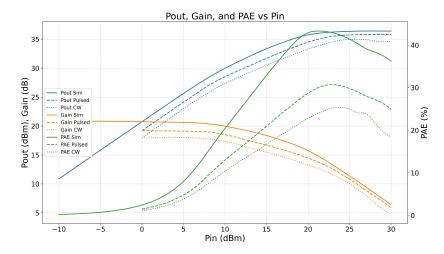

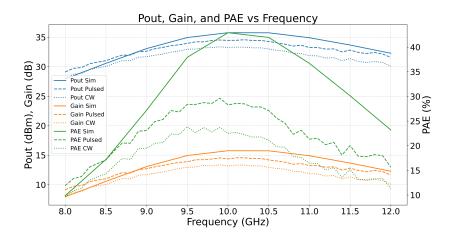

|                                   | Simulated RF Performance of E0302: Pout, Gain, and PAE vs Frequency and Input Power                                                                                                                          | 43                   |

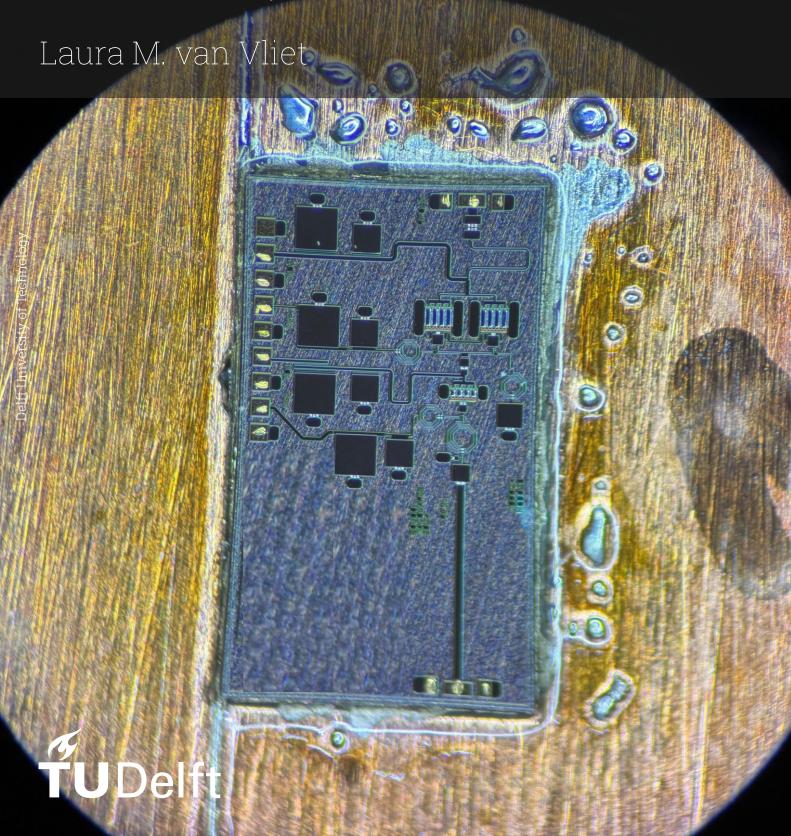

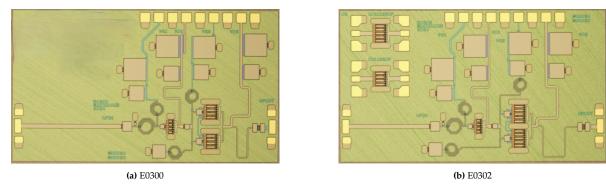

| 5.1                               | High-magnification microscope images of the fabricated MMICs after delivery from the foundry                                                                                                                 | 45                   |

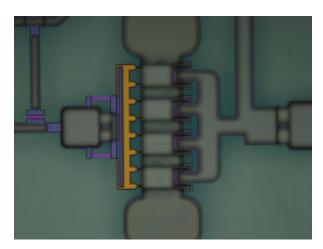

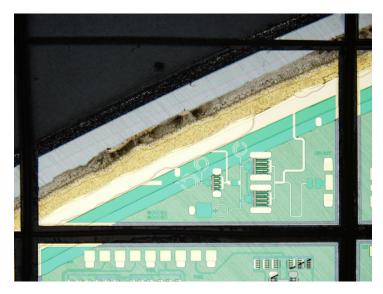

| <ul><li>5.2</li><li>5.3</li></ul> | Microscope image of a single transistor, showing the gate metallization (yellow), resistors (purple), and thick gold interconnects (green-grey)                                                              | 45<br>46             |

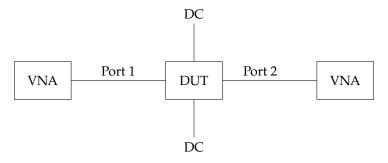

| 6.1<br>6.2<br>6.3                 | Mounting chips on copper block                                                                                                                                                                               | 47<br>48<br>48       |

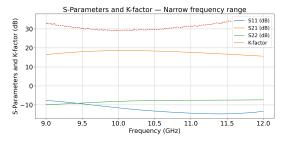

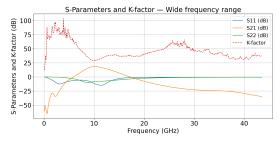

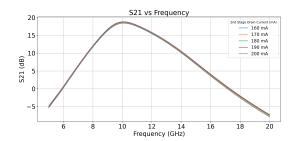

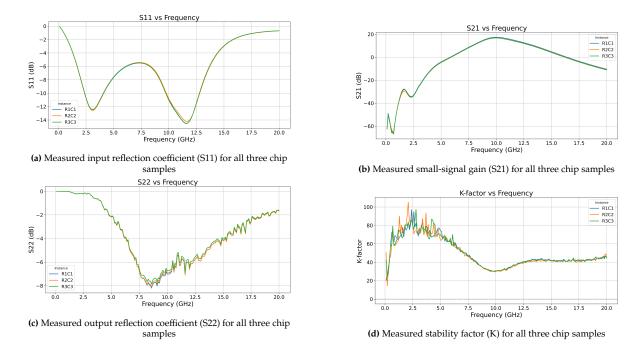

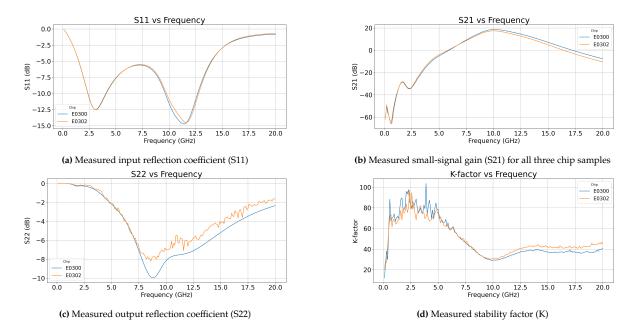

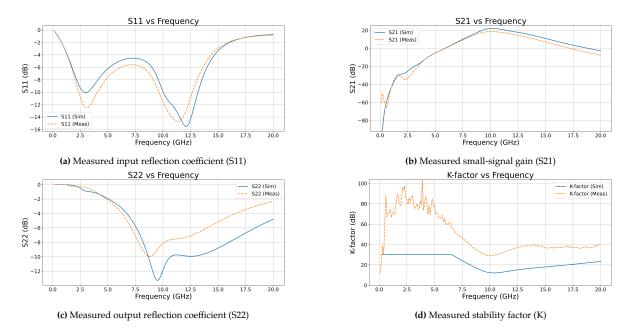

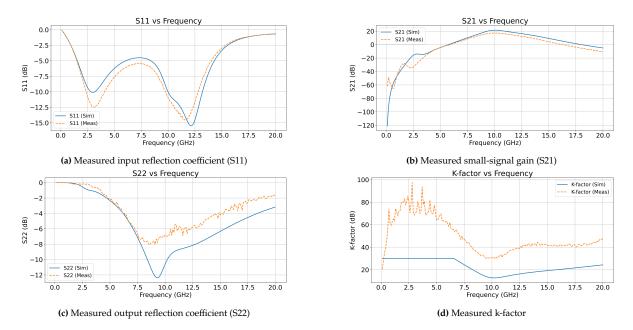

| 7.1                               | Measured S-parameters (S11, S21, S22) and K-factor of one instance of the E0300 chip measured under nominal bias conditions                                                                                  | 50                   |

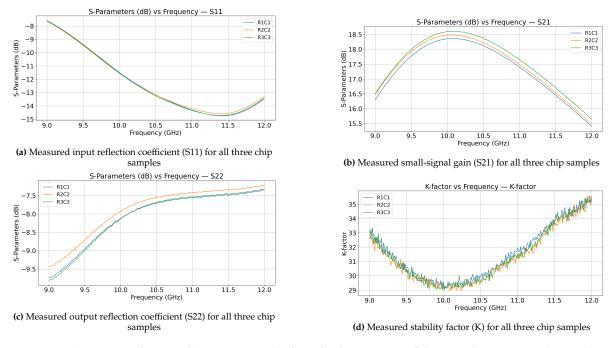

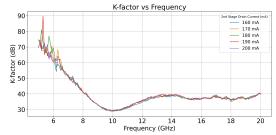

| 7.2                               | Comparison of measured S-parameters and K-factor for three instances of the E0300 chip across 9-12 GHz under nominal bias conditions                                                                         | 51                   |

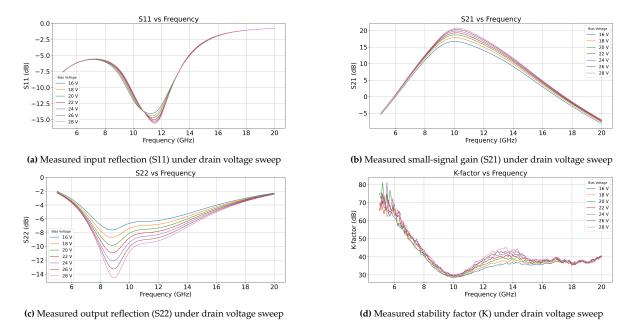

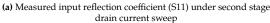

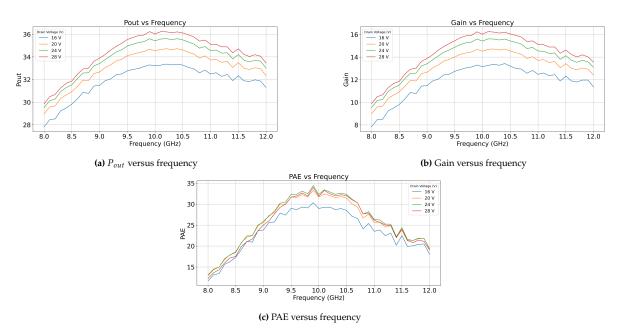

| 7.3                               | Measured S-parameters and K-factor of the E0300 chip under drain voltage sweep of the two stages tied together from 16 <i>V</i> to 28 <i>V</i> in 4 <i>V</i> steps                                           | 51                   |

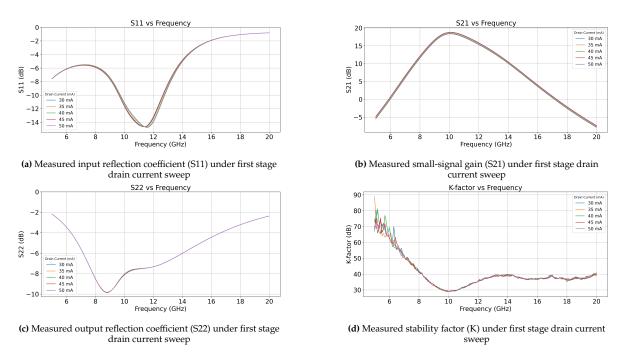

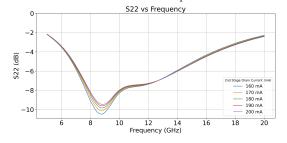

| 7.4                               | Measured S-parameters and K-factor of the E0300 chip under drain current sweep of the first stage transistor from 30 mA to 50 mA in 5 mA steps                                                               | 52                   |

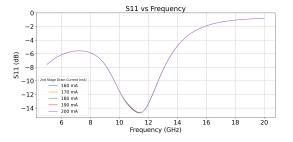

| 7.5                               | Measured S-parameters and K-factor of the E0300 chip under drain voltage sweep and                                                                                                                           |                      |

| 7.6                               | drain current sweep of the second stage transistors from 160 m <i>A</i> to 200 m <i>A</i> in 10 m <i>A</i> steps Comparison of measured S-parameters and K-factor for three instances of the E0302 chip      |                      |

| 7.7                               | across 0-20 GHz under nominal bias conditions                                                                                                                                                                | 54                   |

| 7.8                               | 0-20 GHz under nominal bias conditions                                                                                                                                                                       | 55                   |

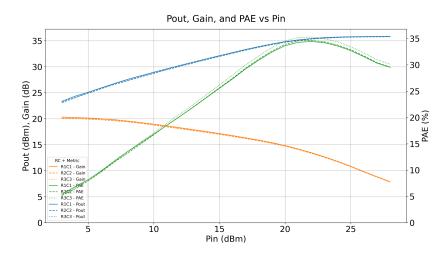

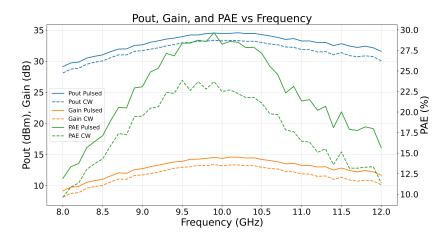

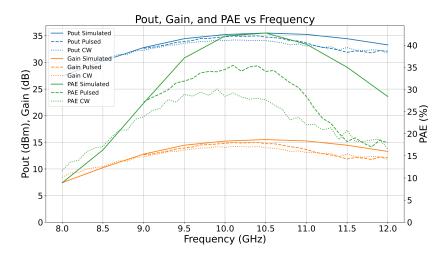

| 7.9                               | under nominal conditions                                                                                                                                                                                     | 55                   |

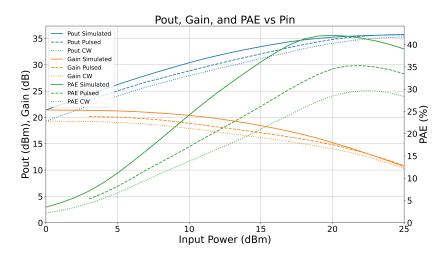

| 7.11                              | input power                                                                                                                                                                                                  | 56<br>56<br>57       |

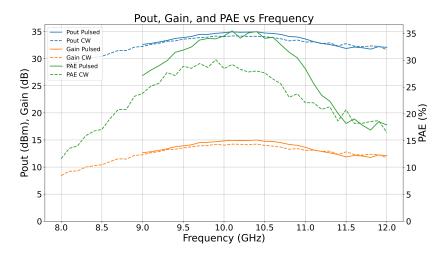

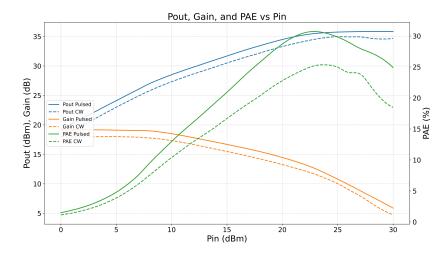

|                                   | Measured output power, power gain, and PAE of the E0302 MMIC as a function of frequency at 20 dBm input power under CW and pulsed conditions                                                                 | 57                   |

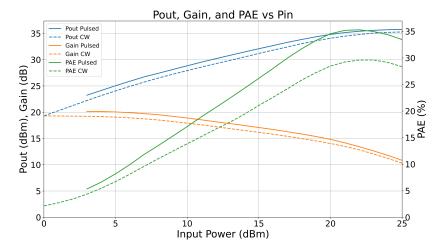

| 7.13                              | Measured output power, power gain, and PAE of the E0302 MMIC as a function of input power at 10 GHz under CW and pulsed conditions                                                                           | 58                   |

| 8.1                               | Comparison of simulated and measured S-parameters and K-factor for the E0300 chip under nominal bias conditions                                                                                              | 60                   |

| 8.2                               | Comparison of simulated and measured S-parameters and K-factor for the E0302 chip                                                                                                                            |                      |

| 8.3                               | under nominal bias conditions                                                                                                                                                                                | 61                   |

| 8.4                               | MMIC as a function of frequency at 20 dBm input power under CW and pulsed conditions Comparison of simulated and measured output power, power gain, and PAE of the E0300                                     |                      |

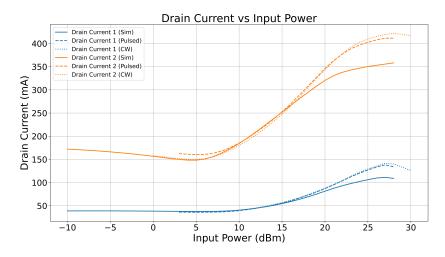

| 8.5                               | MMIC as a function of input power at 10 GHz under CW and pulsed conditions Comparison of simulated and measured drain currents of the E0300 MMIC versus input                                                | 62                   |

| 8.6                               | power at 10 GHz for the first and second amplifier stages, under CW and pulsed operation Measured and simulated output power, gain and PAE versus input power at 10 GHz                                      | 63                   |

|                                   | input power for the E0302 design, under CW and pulsed conditions                                                                                                                                             | 63                   |

| - 1              | ••   |

|------------------|------|

| List of Figures  | 1711 |

| 1.151 OF ETUTIES | VII  |

|                  |      |

| 8.7 | Measured and simulated output power, gain and PAE versus frequency at 20 dBm input |    |

|-----|------------------------------------------------------------------------------------|----|

|     | power for the E0302 design, under CW and pulsed conditions                         | 64 |

# List of Tables

| 3.1 | Material properties of MMIC Semiconductor Materials at 300 K [2]           | 8  |

|-----|----------------------------------------------------------------------------|----|

| 3.2 | Overview of gain definitions                                               | 12 |

| 3.3 | Difference between non- and linear transistor model                        | 14 |

| 3.4 | Causes of Power-added Efficiency degration in GaN PAs [11, 12, 13, 14, 15] | 16 |

| 4.1 | Current density limits for metal layers [22]                               | 24 |

| 4.2 | Examples Layout Design Rules NP12-01 WIN Semiconductors [22]               | 40 |

| 6.1 | Performance Limits of Measurement Setup Components                         | 49 |

|     | Bias supplies                                                              |    |

# Nomenclature

# **Abbreviations**

| Abbreviation D |                                                                                  |  |  |

|----------------|----------------------------------------------------------------------------------|--|--|

| ADS A          | dvanced Design System                                                            |  |  |

|                | ontinuous Wave                                                                   |  |  |

|                | irect Current                                                                    |  |  |

|                | esign Rule Check                                                                 |  |  |

|                | evice Under Test                                                                 |  |  |

|                | -beam lithography                                                                |  |  |

|                | lectromagnetic                                                                   |  |  |

|                | eld Effect Transistor                                                            |  |  |

|                | allium Arsenide, semiconductor material                                          |  |  |

|                | allium Nitride, semiconductor material                                           |  |  |

|                | raphic Design System 2                                                           |  |  |

|                | eterojunction Bipolar Transistor                                                 |  |  |

|                | igh Electron Mobility Transistor                                                 |  |  |

|                | ategrated Circuit                                                                |  |  |

|                |                                                                                  |  |  |

|                | adium Phosphide, semiconductor material                                          |  |  |

|                | Key Performance Indicator  Macquaria Apalag Davises Laboratory                   |  |  |

|                | Macquarie Analog Devices Laboratory  Metal Semiconductor Field Effect Transistor |  |  |

|                |                                                                                  |  |  |

|                | letal Insulator Metal, capacitor type                                            |  |  |

|                | Ionolithic Microwave Integrated Circuit                                          |  |  |

|                | ower Amplifier                                                                   |  |  |

|                | ower Added Efficiency                                                            |  |  |

|                | rinted Circuit Board                                                             |  |  |

|                | rocess Development Kit                                                           |  |  |

|                | adio Frequency                                                                   |  |  |

|                | cattering parameter                                                              |  |  |

|                | canning Electron Microscope                                                      |  |  |

|                | licon, here used as substrate material                                           |  |  |

|                | emi-Insulating                                                                   |  |  |

|                | licon Carbide, substrate material                                                |  |  |

|                | licon Germanium, semiconductor material                                          |  |  |

| SOLT SI        | nort, Open, Load, Through, calibration standard                                  |  |  |

List of Tables x

| Abbreviation                                      | Definition                                   |

|---------------------------------------------------|----------------------------------------------|

| TaN Tantalum Nitride, integrated resistor materia |                                              |

| TRL                                               | Through, Reflect, Line, calibration standard |

| VNA                                               | Vector Network Analyzer                      |

| X-Band                                            | 8–12 GHz                                     |

# **Symbols**

| Symbol | Definition  | Unit  |

|--------|-------------|-------|

| f      | Frequency   | [GHz] |

| R      | Resistor    | [Ω]   |

| Z      | Impedance   | [Ω]   |

| С      | Capacitance | [pF]  |

| L      | Inductance  | [nH]  |

| V      | Voltage     | [V]   |

| I      | Current     | [mA]  |

| 1      | Length      | [µm]  |

| W      | Width       | [μm]  |

| P      | Power       | [dBm] |

$\int$

# Introduction

This chapter introduces the application and realization of microwave power amplifiers. The problem that is investigated in this thesis is formulated and the approach that was followed is introduced. Finally, the co-operation with Macquarie University in the frame of this Bachelor Project is described, as it forms the context of this work, and the structure of the thesis is described.

#### 1.1. General Introduction

Microwave power amplifiers are all around us. Every cell phone has a small microwave power amplifier that allows the cell phone to connect to the local wifi router and provide connectivity to its user. Every microwave oven has a large microwave power amplifier, a magnetron, that provides the power to heat up our food is a short time. But there are many more microwave power amplifiers that are not so visible to the general public. They fly in space to make radar pictures of the earth, they are in basestations in the top of telecom towers to serve a large amount of users for cell phone coverage, they are in level gauge sensors that determine how full silos are filled with liquids (such as oil) or food (such as grain).

Those microwave power amplifiers essentially convert power from a power source into microwave power. They do so with a finite efficiency, which is never 100%, and the remainder of the energy is wasted in heat. This is problematic in different ways: it is not environmentally friendly to waste energy resources to create heat, the finite efficiency leads to shorter phone use-time (so you have to charge your phone more often), they lead to problems in cooling (how do you get rid of the heat in a satellite?) and many related problems. The problem is even more profound for power amplifiers than for other parts in the system, as usually the power involved is the largest for the power amplifier, so losses are significant at the system level.

By convention the term microwave refers to the frequency range from approximately 1 GHz to 30 GHz, while "millimetre wave" (mm-wave) refers to the 30 GHz to 300 GHz range. Despite this, the terminology is not always used in the most precise sense, as 80 GHz is still often called microwave.

Microwave power amplifiers, in the broadest sense, can be realized with vacuum devices or with semiconductor devices. In the past, vacuum devices were the only available option. They can still be found, for example in microwave ovens, but they are much less used than in the past. They still find use for extremely high power levels (with exotic devices such as klystrons) and in space applications (often using travelling wave tubes). They are increasingly replaced by semiconductor, or solid-state, power amplifiers. This thesis is concerned with solid-state power amplifiers.

## 1.2. Solid-State Microwave Power Amplifiers

A solid-state microwave power amplifier consists of a semiconductor die, the 'chip' that performs the actual amplification. On or around the chip is a matching network that establishes the right performance in view of the source and load impedances. For its actual application, the chip is packaged in for example a plastic or ceramic package. Plastic packages are cheaper, and often found in commercial applications, ceramic packages are more expensive but can provide hermetic properties, amongst others, and are for example found in satellite systems. When the matching network is integrated on the same chip, we speak of a 'Monolithic Microwave Integrated Circuit' (MMIC), as all elements are monolithically (on the same substrate) integrated.

For the semiconductor technology, we distinguish between the material system and the device type. The material system determines the elementary characteristics of the transistor (such as the maximum frequency of operation and the maximum current density). Materials of choice for microwave power ampliers can be SiGe, GaAs, InP and GaN. In this work, GaN (Gallium Nitride) is used for reasons discussed later in this thesis. With that material system, different transistor devices can be made. Choices include MESFET, HEMT, HBT and several other transistor devices. We have been using a GaN HEMT device design as this currently offers the best performance in terms of power density and microwave gain. The GaN HEMT technology used is finally classified by the length of the gate: a short gate leads to a high frequency at which the transistor can operate.

Finally, also the substrate material is of importance. For GaN devices, two substrates are commonly found: Si or SiC. A silicon substrate is more compatible with the large volume IC manufacturing, which is almost always on Si. That can lead to a lower manufacturing cost. For microwave power amplifiers, however, the heat transport is crucial and there is a better choice available: SiC. This diamond-like material (transparent and very strong) outperforms almost all other materials including metals in its heat conductivity performance.

#### 1.3. Problem Statement

The research question that was posed at the start of the work is whether we can design a lower frequency (10GHz) power amplifier in a power amplifier process that has an extremely high maximum frequency (well over 100 GHz). Actually, this 10 GHz is not really a low frequency as it is higher than for example wifi frequencies (usually 2.4 or 5 GHz), but it is low in the sense that it is not so close to the frequencies at which the technology is capable of.

Using a process well below its maximum operating frequency offers potential advantages in gain and efficiency, but also poses challenges, in particular for the stability of the amplifier. For power amplifiers, stability is always a critical factor, and is even more an issue at frequencies where there is so much gain. This advantage and the demonstration thereof has been performed at lower frequencies, but was not demonstrated for the class of (state-of-art) technologies (0.12  $\mu$ m) that we are using. More common is to use a 0.25  $\mu$ m GaN HEMT technology, that has a much lower maximum frequency of operation.

To investigate the potential for such an RF power amplifier, we use Gallium Nitride (GaN) High Electron Mobility Transistors (HEMTs) with Electron Beam Lithography (EBL) gates. This is a technology that forms the current State-of-Art for microwave high-power high-efficiency MMICs: The circuit is fabricated using the WIN Semiconductors NP12-01 GaN-on-SiC technology with 0.12  $\mu$ m gates (that is one of the shortest gatelengths that is around in industry.) and source-coupled field plates for high breakdown and 28 V operation. The process offers two interconnect metals, MIM capacitors, TaN resistors and through wafer vias. Process details can be found in [1].

# 1.4. Approach

The method to investigate the research question is through the design of a power amplifier IC and characterize its performance.

As the models available for specific power transistors is always problematic, the work started with

characterizing dedicated power transistors. This is important for two reasons:

- We need to choose the right size of transistor, that is big enough to support the output power that we want to realize, but not too big (because that sacrifices amplifier efficiency).

- For the right size of the transistor, we need to determine the load impedance at which optimum power and efficiency are available, these measurements are called load-pull measurements. This data is almost never available with the right accuracy.

In that process, test transistors were mounted on a carrier, which is a very delicate activity. Based on transistor data, we then created the amplifier topology (consisting of device sizes and their interconnection). An example is shown in Figure 1.1 below.

Figure 1.1: Example amplifier topology

In this, the transistor sizes need to be chosen such that the required power and gain can be accommodated. The matching networks are now the essential elements that need to be designed in detail and that will define the amplifier performance.

The topology for these three matching networks will then be designed, first with lumped elements to get the right topology and later with electromagnetic analysis to get the details right. Finally, biasing circuits and pad are designed and added. After all this, a layout file will be sent to the manufacturer (Win Semiconductors in Taiwan). They will return, after a processing time of several months, diced amplifier samples. These will be mounted, similar to the transistor samples, on a copper carrier and then be tested for its full functionality.

# 1.5. Collaboration with Macquarie University

The work that is reported in this thesis was performed as part of a bachelor project for the Electrical Engineering study at the Delft University of Technology. In this bachelor project, a co-operation with Macquarie University, Sydney, Australia, was essential. During two internships, first the design and later the measurement of the power amplifier was performed. This took part at the part of Macquarie University that is known as the MAD Lab, the Macquarie Analog Devices Laboratory, that is an integral part of the Macquarie School of Engineering.

#### 1.6. Thesis outline

Following this introduction, the entire design and characterization process will be described. In chapter 2, the programme of requirements will be derived. This serves as a reference throughout the document. In chapter 3, the design methodology will be described. Included is the background needed to understand microwave power amplifier design. In chapter 4, the implementation of the design is described. Next to the design discussed, this also includes an experiment to share via-holes between adjacent transistors. The results might be useful for future work. The simulation results are reported in section 4.3. Chapter 5 describes the manufacturing phase. As this was performed by Win Semiconductors, this is only a short chapter. Chapter 6 describes the measurement setup. Specific for microwave measurements

1.6. Thesis outline 4

is the elaborate calibration procedure that we need to go through; also this calibration procedure is documented. Chapter 7 reports on the measurement results. In chapter 8 we compare measurements against simulations and discusses the results. Chapter 9 presents the conclusions, including suggestions for future work.

# Programme of Requirements

In this chapter, the Programme of Requirements is developed. Three distinct parts are distinguished: the Mandatory Requirements, the Objectives (consisting of Functional, Manufacturing and System Requirements) and the Key Performance Indicators. Throughout this report all design design decisions, simulations and measurements are referenced back to these requirements to ensure traceability and compliance.

#### 2.1. Introduction

The topic of this thesis is the design of an X-Band Power Amplifier. These power amplifiers are typically used in professional electronics. They are not commonly found in consumer electronics. Applications include sensor systems (in particular radar systems), communication infrastructure (in particular for links between base stations and to drive modulators for optical links) and aerospace systems (such as satellite links). Their prime function is to deliver microwave power at a defined frequency, and the topic of this thesis is to see whether very modern mm-wave technologies can be used at the lower X-Band frequency as well.

For the design of the amplifier, a Programme of Requirements (PoR) is established. The PoR consists of mandatory requirements and objectives. Finally, a set of Key Performance Indicators is outlined. The PoR will be used in the remainder of the thesis to assess the design and results. Throughout the entire report, we will refer back to the items listed in this chapter to assess compliance and to benchmark the achieved results against the initial performance requirements.

# 2.2. Mandatory Requirements

The following requirements arose:

- [2.2.1] frequency of operation must be at X-Band (10 GHz).

- [2.2.2] The output power of the amplifier must be above than 30 dBm.

- [2.2.3] The amplifier must be unconditionally stable.

- [2.2.4] The size of the amplifier is smaller than the maximum manufacturing reticle size.

These mandatory requirements reflect widely adopted industry standards for microwave power amplifier design. The choice of the X-band (10 GHz) frequency was made specifically by MAD Lab to align with wafer scheduled for fabrication, making it an ideal platform for both research objectives and for a first MMIC power-amplifier design.

# 2.3. Objectives

Under the objectives we distinguish 1) functional requirements, which are considered requirements that need a careful trade-off against each other, 2) manufacturing requirements, which are a result of the

technology in which the amplifier is manufactured and 3) system requirements, that originate from the environment in which the amplifier is tested or used.

#### 2.3.1. Functional Requirements

- [2.3.1.1] Frequency: The amplifier shall operate at 10 GHz with a bandwidth targeting 1 GHz.

- [2.3.1.2] Output power: The amplifier shall deliver a maximum power targeted at 36 dBm output power at 10 GHz.

- [2.3.1.3] Gain: The power gain shall be higher than 10 dB, targeting 15 dB.

- [2.3.1.4] Efficiency: The amplifier shall exhibit a maximum PAE, targeting 40 %.

- [2.3.1.5] Input reflection: The amplifier shall have an input reflection below -10 dBm.

- [2.3.1.6] Sensitivity: The amplifier shall be insensitive to slight variations in external influences, such as a load mismatch or minor supply fluctuations.

#### 2.3.2. Manufacturing Requirements

- [2.3.2.1] Supply voltage: the PA shall operate at 20 V.

- [2.3.2.2] Area: The area of the integrated circuit shall be as small as possible, but not exceed 6 mm<sup>2</sup>.

- [2.3.2.3] Height: The height of the integrated circuit shall be 1.75 mm to allow integration with other designs on the semiconductor reticle.

#### 2.3.3. System Requirements

- [2.3.3.1] The control interface must digitally control the bias and be able to disable and enable all bias voltages.

- [2.3.3.2] The control interface must include current limits as protection feature.

- [2.3.3.3] The in- and output impedance of the amplifier must be in line with industry standards (i.e. 50 Ohm).

- [2.3.3.4] No DC voltage may be present at the RF in- and output ports, so that connected equipment will not be damaged or disrupted.

# 2.4. Key Performance Indicators

A concise set of Key performance indicators (KPI) is derived from the Objectives above, that facilitate assessment of the results:

- [2.4.1] Minimum power over the designed bandwidth. The output power should be as high as possible.

- [2.4.2] Minimum Power Added Efficiency over the designed bandwidth. The Power Added Efficiency should be as high as possible.

- [2.4.3] Stability, should be absolute.

- [2.4.4] Size, should be as small as possible.

# Design Methodology

In this chapter an extensive design methodology is introduced that briefly describes all aspects of the design phase. Manufacturing and measurement methods are described in the succeeding chapters.

The design methodology described includes the selection of semiconductor technology, a description of some relevant manufacturing and material characteristics of the chosen HEMT transistor, followed by the linear and non-linear transistor behaviour. The design process begins with a description of the load-pull measurements, which forms a critical foundation for determining the optimal operating conditions. Following this, the design and layout of the chip is illustrated. Finally, the check before submission for manufacturing are described. This consists of various stability checks, but also includes the manufacturer's design rule check and connectivity check.

### 3.1. MMIC Semiconductor Technologies

Selecting the right semiconductor technology for a Monolithic Microwave Integrated Circuits (MMICs) power amplifier depends on the output power requirements, operating frequency and frequency range, efficiency, linearity needs, thermal constraints and cost.

An ideal RF power amplifier (PA) must simultaneously deliver high output power, operate efficiently across a large frequency range, have a wide bandwidth, maintain linearity and be robust under varying operating conditions. Each technology, GaN, GaAs and InP, have their advantages and disadvantages that make them suitable for different applications.

Table 3.1 shows the fundamental properties of GaN, GaAs and InP. A larger bandgap allowes the material to withstand higher voltages, high electric breakdown fields ( $E_c$ ), and operate at elevated temperatures. GaN has about two to three times the bandgap energy compared to GaAs and InP. The saturated electron velocity plays a key role in switching speed and high-frequency performance, higher velocities enable faster device operation. To achieve high currents at these frequencies a high saturated velocity is desirable. GaAs has a very high electron mobility and is often used for that reason for high-frequency performance. GaN has a relative low electron mobility and is not the ideal choice for high frequencies.

The thermal conductivity ( $\kappa$ ) of a semiconductor material is extremely important since it ensures efficient heat dissipation, improving reliability and power handling. Poor thermal conductivity leads to worse results at elevated temperatures, this can be seen with GaAs and InP. The relative permittivity indicates the capacitive loading of a transistor and affects the device terminal impedances [2].

| Property                                                                                            | GaN/ AlGaN | GaAs / AlGaAs | InP / InGaAs |

|-----------------------------------------------------------------------------------------------------|------------|---------------|--------------|

| Bandgap energy, $E_g$ (eV)                                                                          | 3.44       | 1.43          | 1.35         |

| Electric breakdown field, $E_c$ (MV/cm)                                                             | 3          | 0.4           | 0.5          |

| Saturated (peak) velocity electrons, $v_{\text{sat}}$ ( $v_{\text{peak}}$ ) (×10 <sup>7</sup> cm/s) | 2.5 (2.7)  | 1.0 (2.1)     | 1.0 (2.3)    |

| Electron mobility HEMT,<br>$\mu_n$<br>(cm <sup>2</sup> /V·s)                                        | 2000       | 10000         | 10000        |

| 2DEG density, $n_s$ (×10 <sup>13</sup> cm <sup>-2</sup> )                                           | 1.0        | < 0.2         | < 0.2        |

| Thermal conductivity, $\kappa$ (W/cm·K)                                                             | 1.3 - 2.1  | 0.5           | 0.7          |

| Relative permittivity, $\varepsilon_r$                                                              | 9.0        | 12.8          | 12.5         |

Table 3.1: Material properties of MMIC Semiconductor Materials at 300 K [2]

### 3.2. High Electron Mobility Transistors (HEMTs)

With the material system of choice, GaN in our case, transistors are formed through a series of illuminations of photo-resist through masks, and a combination of etching and material growth techniques. This is a very complex process that is critical and highly specialized.

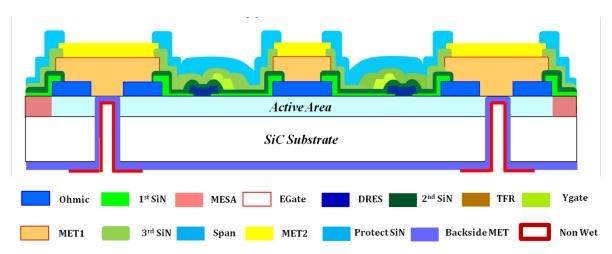

The transistor type that will be used is the microwave device that is currently the most popular for microwave power amplifier development: the High Electron Mobility Transistor (HEMT). An example of the cross-section of a GaN HEMT transistor is shown in Figure 3.1. A HEMT is a type of field-effect transistor; its operation is based on the possibility to deplete the region underneath the gate from charge carriers depending on a control voltage.

Figure 3.1: Cross-sectional view showing material layers of a GaN HEMT structure

There is a clear distinction between the GaN layers and the substrate. In the example, the substrate is semi-insulating (SI) Silicon Carbide (SiC). This is an excellent heat conductor, that largely defines the

good thermal properties.

On top of the substrate, a number of AlGaN and GaN layers are grown. These layers are epitaxially grown and the precise layer stack is a carefully guarded secret by the foundry. On top of the uniform layers, the contacts are present, both for the source and drain, as well as for the gate. The source and drain contacts are so-called ohmic contacts and consist of metal on top of highly doped GaN. They provide access to the active layer underneath with the lowest possible resistance.

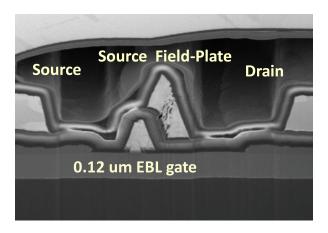

The gate contact is a so-called Shottky contact, that depletes the area underneath from electrons depending on the bias voltage between the gate and the source. The gate is the smallest feature of the transistor and the way it is formed is usually through an electron-beam process. The shape of the gate can have different forms. In Figure 3.1, it has a trapezoidal shape, often used at lower frequencies. At mm-wave frequencies, including the process that we will use, the base of the gate is so narrow that it will create a high resistance, and a T-gate (also called a mushroom gate) is created, where the wide hat lowers the resistance of the narrow base. The foot of the T-gate is seen as a tiny detail in Figure 3.2. Sometimes, also field-plates are added. These are extensions to the gate that lower the field strength to avoid breakdown, necessary due to the high voltages encountered. This entire gate structure, including the T-gate and the field plate is illustrated in the SEM picture in Figure 3.2.

Figure 3.2: Overview of EBL gate fabrication and GaN HEMT structure used in the RF power amplifier design

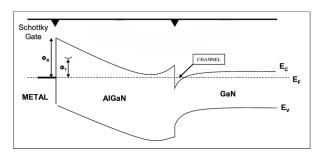

The active layers, that are a more complex stack than shown in Figure 3.1, are essentially needed to create free electrons (from the donor layer, the AlGaN) to form a very thin 2-dimensional sheet charge (called a two-dimensional electron gas, or 2-DEG), which forms the HEMT channel. This is possible because of the special band diagram of the HEMT heterostructure, see Figure 3.3. In this band diagram, the curve for  $E_c$  denotes the possible energy states for free electrons (that conduct), and  $E_v$  denotes the possible energy states for the valence electrons, that do not move. The sharp dip in the middle of the  $E_c$  curve denotes the channel, a very thin layer in which all the free electrons are captured. Note that the horizontal axis in Figure 3.3 corresponds to the vertical axis in Figure 3.1.

Figure 3.3: Energy band diagram of a HEMT structure [3]

For a microwave power amplifier, there are a few relations that are most important to assess its performance. In the first place, the transistor needs to be sufficiently fast. We measure that through the current-gain cutoff frequency (also called the transition frequency,  $f_T$ , the frequency where the current gain equals one) or the so-called maximum frequency ( $f_{max}$ , where the power gain equals one).

The current gain cutoff frequency ( $f_T$ ) is given by:

$$f_T = \frac{g_m}{2\pi (C_{GS} + C_{GD})} \tag{3.1}$$

Maximum frequency ( $f_{max}$ ) is given by [4]:

$$f_{max} = \frac{f_T}{\sqrt{4g_{DS}\left(R_{in} + \frac{R_S + R_G}{1 + g_m R_s}\right) + 2 \cdot \frac{C_{GD}}{G_{GS}}\left(1 + g_m R_S\right)^2}}$$

(3.2)

The low distance between the gate and the 2DEG will lead to a high  $g_m$ . A small footprint of the gate will lead to a low  $C_{GS}$  ( $C_{GD}$  is much smaller than  $C_{GS}$ ), and is hence the most important factor for determining the high-frequency capability of a HEMT. From the formula for  $f_{max}$ , we see that it follows  $f_T$ , where the term in the denominator will determine how much higher the  $f_{max}$  will be than the  $f_T$ .

The last equation that provides insight in the relation between material parameters and transistor performance is the maximum current:

$$I_{D.sat} = q \cdot n \cdot v_{sat} \cdot W \tag{3.3}$$

This relation states that the maximum current  $I_{D,sat}$  is related to the electron charge (q), the electron density (n), the saturated electron velocity ( $v_{sat}$ ) and the width of the transistor finger (W). Together with the high breakdown voltage of GaN (that follows from the high bandgap), these equations explains why GaN is such a good material system for microwave power amplifiers.

#### 3.3. Linear Transistor Behaviour

#### 3.3.1. Linear Transistor Modeling

Linear (small signal) transistor models play a foundational role in power amplifier design, as they allow circuit designers to predict device behaviour under small-signal excitation. These models are essential for extracting key performance parameters such as: gain, input/output matching, stability. This is essential and widely used in the early stages of RF circuit design.

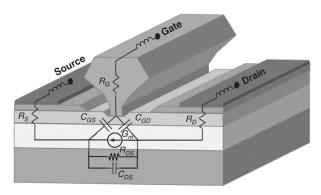

**Figure 3.4:** FET structure with equivalent circuit elements [5]

Figure 3.4 shows the structure of a Field Effect Transistor (FET) along with its equivalent circuit elements. This model separates the transistor into parasitic and intrinsic components. The parasitic elements ( $R_G$ ,  $R_S$ ,  $R_D$ ,  $L_G$ ,  $L_S$ ,  $L_D$ ) are primarily related to device metallisation and interconnects and are

independent of bias conditions. In contrast the intrinsic elements ( $C_{GS}$ ,  $C_{GD}$ ,  $C_{DS}$ ,  $R_{GD}$ ,  $R_{GS}$ ) depend on the transistor's bias voltages and represent its active behaviour.

To develop an accurate linear model, these elements must be extracted reliably, typically through S-parameters measurements performed at a single bias point. This is because small-signal models assume linear operations around a fixed operation point. This makes it unsuitable for large-signal or non-linear analysis.

#### 3.3.2. S-Parameters

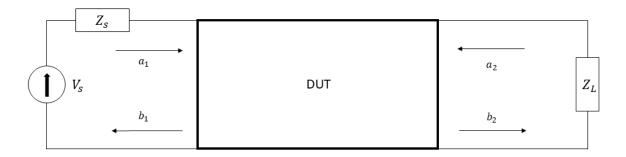

In microwave-frequency circuit analysis, it is more practical to describe electrical behaviour using waves than voltages and current as this is easier to measure. The foundation of this approach is shown in Figure 3.5 for a two-port network.

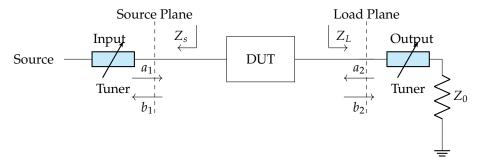

Figure 3.5: Two-port network

For a two-port network, the relation between incident waves  $a_1$ ,  $a_2$  and reflected waves  $b_1$ ,  $b_2$  is given in Equation 3.4.

$$\begin{pmatrix} b_1 \\ b_2 \end{pmatrix} = \begin{pmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{pmatrix} \begin{pmatrix} a_1 \\ a_2 \end{pmatrix}$$

(3.4)

Where:

- S<sub>11</sub> is the input reflection coefficient

- *S*<sub>21</sub> is the forward transmission (gain from port 1 to 2)

- $S_{12}$  is the reverse transmission

- $S_{22}$  is the output reflection coefficient

$$S_{11} = \Gamma = \frac{b_1}{a_1} \bigg|_{a_2 = 0} = \frac{Z_L/Z_0 - 1}{Z_L/Z_0 + 1} = \frac{Z}{Z + 2Z_0}$$

(3.5)

$$S_{21} = \left. \frac{b_2}{a_1} \right|_{a_2 = 0} = \frac{2Z_0}{2Z_0 + Z} \tag{3.6}$$

$$S_{12} = \left. \frac{b_1}{a_2} \right|_{a_1 = 0} = \frac{2Z_0}{2Z_0 + Z} \tag{3.7}$$

$$S_{22} = \frac{b_2}{a_2} \bigg|_{a_1=0} = \frac{Z}{Z + 2Z_0}$$

(3.8)

These parameters are complex and frequency-dependent and are typically measured using a Vector Network Analyser (VNA). IN RF design  $S_{21}$  is also known as the small-signal gain and  $S_{11}$ ,  $S_{22}$  help assess input and output matching conditions [6].

#### 3.3.3. Gain

At microwave frequencies the gain of a transistor is scarce and an accurate analysis is needed. Therefore, a distinction needs to be made between power gain, available gain and transducer gain. The differences between these definitions is primarily in the way the source and load are matched. In Equation 3.9 - 3.11 the different equations are shown. In Table 3.2 the difference between the equations is shown. The available power refers to the power that is provided by the source, while the delivered power represents the actual power that reaches and is absorbed by the transistor. For an RF power amplifiers, the transducer power gain is used as it also incorporates the effects of matching with the surrounding circuit [7].

The power gain can be expressed as the ratio of power dissipated in the load to the power delivered to the input of the two-port network:

$$G = \frac{P_L}{P_{in}} \tag{3.9}$$

The available power gain can be expressed as the ratio of power available from the two-port network to the power available from the source:

$$G_A = \frac{P_{avn}}{P_{avs}} \tag{3.10}$$

The transducer power gain can be expressed as the ratio of power delivered to the load of the power available from the source:

$$G_T = \frac{P_{\text{Power delivered to the load}}}{P_{\text{Power available from the source}}}$$

(3.11)

$$P_{out}$$

|          |                          | available power $P_{avs}$ | delivered power $P_L$ |

|----------|--------------------------|---------------------------|-----------------------|

| $P_{in}$ |                          | available power gain      | transducer power gain |

|          | delivered power $P_{in}$ | -                         | power gain            |

Table 3.2: Overview of gain definitions

### 3.4. Non-linear Transistor Behaviour

#### 3.4.1. Non-linear Transistor Modeling

While linear (small-signal) models are highly effective for showing the effects of the transistor in low-power conditions, they fail to accurately predict the behaviour under large-signal conditions. Non-linear transistor modeling becomes necessary when the device is driven into regions where gain compression, harmonic generation or other non-linear behaviour becomes visible.

Accurate modeling of the non-linear transistor behaviour for a 10 GHz power amplifier is essential. Gallium Nitride (GaN) high electron-mobility transistors (HEMTs) exhibit strong non-linearities due to their wide-bandgap material properties and large voltage and current handling capabilities. Non-linear models take over when the response of the transistor no longer behaves linearly as assumed in the small-signal model. When driven to saturation, these non-linear behaviours influence metrics such as PAE, output power and harmonic distortion [8].

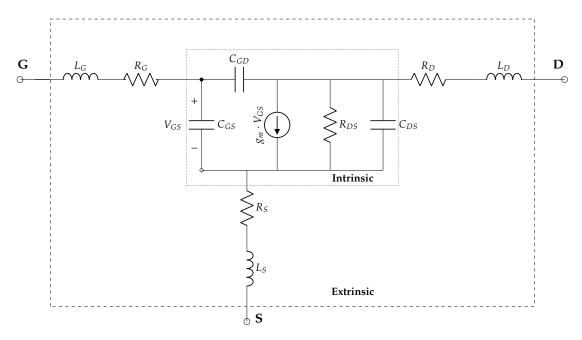

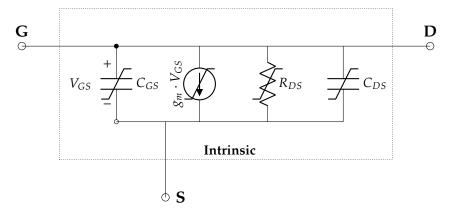

Figure 3.6 illustrates the linear transistor model, suitable for small-signal circuit analysis while Figure 3.7 shows the non-linear intrinsic model. The intrinsic model represents the active behaviour of the transistor, while the extrinsic components account for the passive connections of the transistor.

Figure 3.6: Linear Transistor Model

Linear models assume a fixed reponse at a defined DC bias point, which are used for impedance matching and stability analysis. In Figure 3.7 the intrinsic transistor elements that responsible for non-linear behaviours are shown, while the extrinsic elements, shown in Figure 3.6, remain linear. These non-linear behaviours of the intrinsic elements depend on the bias voltages and currents (at the bias point), thermal effects, frequency and material properties of GaN and are used to determine the compressed gain, output power and PAE.

Figure 3.7: Non-linear Intrinsic Circuit Model

In Table 3.3 the differences between the linear and non-linear model are shown.

|                  | Linear Modeling                        | Non-linear Modeling                   |

|------------------|----------------------------------------|---------------------------------------|

| Operation region | Small-signal conditions, low power     | Large-signal conditions, high power   |

| Characterization | Scattering parameters (S-parameters)   | large-signal metrics (Gain compres-   |

| Parameters       |                                        | sion, PAE, $P_{out}$ )                |

| Operating point  | Fixed at bias point                    | Varies with signal amplitude and bias |

|                  | <del>-</del>                           | voltage and currents                  |

| Behaviour focus  | Small-signal gain, input/ouput         | Gain compression, power saturation,   |

|                  | matching and stability                 | PAE and harmonic generation           |

| Harmonics        | Not modelled                           | Harmonic distortion included          |

| Common Applica-  | Low-power circuits, early-stage RF de- | Load-pull measurements and large      |

| tion             | sign                                   | signal analysis                       |

Table 3.3: Difference between non- and linear transistor model

#### 3.4.2. Large-Signal Metrics

When designing high-power amplifiers at 10 GHz, transistors rarely operate in the small-signal region. They are instead driven with RF power, pushing them into a non-linear region. Large-signal models are specifically developed to predict output power, efficiency and distortion.

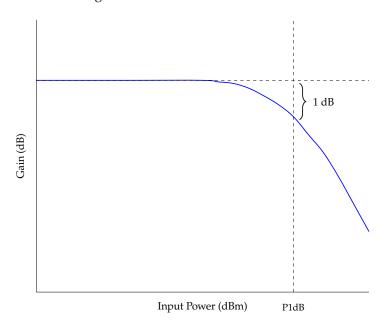

#### **Gain Compression**

Gain compression describes the phenomenon where as the input power to a transistor increases, the output power no longer scales linearly and begins to saturate. This occurs when the device moves into the non-linear operating region.

The 1-dB compression point (P1dB) is a industry standard used for quantifying the gain compression. It is defined as the input power level at which the small-signal gain of the device decreases by 1 dB compared to its ideal linear behaviour.

At the 1-dB compression point, the gain becomes:

$$G_{compressed} = G_{small-signal} - 1dB (3.12)$$

Figure 3.8 illustrates the concept of gain compression and the 1-dB compression point. The horizontal dashed line represents the ideal linear gain, while the solid curve shows the actual gain behavior as the device moves into its non-linear region.

Figure 3.8: 1dB compression gain

Physically the gain compression arises from several mechanisms within the transistor:

- Transconductance roll-off, where the rate of change of drain current with respect to gate voltage decreases at high drive levels.

- **Voltage-dependent capacitance** ( $C_{GS}$ , $C_{GD}$ ) that vary with signal amplitude and bias conditions

- Thermal effects, where self-heating reduces the carrier mobility and shifts the threshold voltage

- Charge trapping effects, leading to temporary carrier depletion

These non-linear effects collectively reduce the effective gain and limit the amplifiers output power [9].

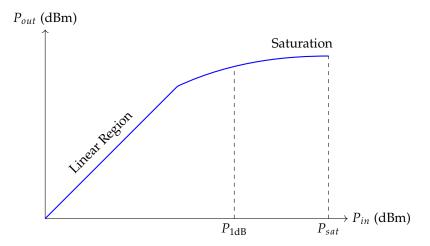

#### **Output Power Saturation**

As the input power to the amplifier increases, the output power initially grows linearly with the gain, as seen in Equation 3.13.

$$P_{out} = P_{in} + G_{linear} (3.13)$$

However as the device approaches its physical limits. The transistor gets up to its maximum drain current and gate voltage, the gain then decreases resulting in gain compression subsection 3.4.2. In GaN HEMTs, ouput power saturation is driven by several mechanism:

- Carrier velocity saturation: At high electric fields electron velocity reaches a maximum, limiting the drain current.

- Carrier density: At high input levels, the channel can run out of available carriers (electrons) restricting further current increase.

- Knee voltage constraint: The drain voltage cannot swing below the knee voltage  $V_{knee}$ , limiting the RF voltage swing.

- **Transconductance reduction:** The channel's charge modulation becomes nonlinear at high gate voltages.

- Thermal effects: Self-heating reduces carrier mobility and maximum current.

For a matched load, the optimum resistance can be expressed as:

$$R_{opt} = \frac{V_{dc}}{I_{max}/2} = \frac{V_{dc}}{I_{dc}} = \frac{V_{dc} - V_{knee}}{I_{max}/2}$$

(3.14)

where  $I_{max}$  is the peak drain current. Under this optimum loading, the maximum deliverable RF output power (saturation power) is:

$$P_{sat} = \frac{1}{2} \cdot (V_{dc} - V_{knee}) \cdot \frac{I_{max}}{2}$$

(3.15)

Beyond  $P_{sat}$ , increasing the input power further results mainly in increased distortion and does not significantly raise the output power [10].

**Figure 3.9:** Typical output power versus input power characteristic of a GaN power amplifier showing the linear region, 1-dB compression point, and saturation region

#### Power-Added Efficiency (PAE)

Power-added efficiency (PAE) is a key metric that measures how effectively a power amplifier converts DC power into RF output power:

$$PAE = \frac{|P_{out}| - |P_{in}|}{P_{dc}} \cdot 100\%$$

(3.16)

PAE does not simply increase and flatten at saturation. It exhibits a roll-over effect at the high input powers after reaching its maximum. This happens because the gain collapses, increased conduction losses, thermal degradation and breakdown limits seen in Table 3.4.

| Cause                       | Explanation                                                                                                                                          |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gain Collapse               | As the amplifier is overdriven, output power saturates while DC consumption continues to rise, reducing PAE as can be calculated with Equation 3.16. |

| Increased conduction losses | At larger powers the conduction losses increase, because more power has to be dissipated as heat instead of being converted to RF output power.      |

| Thermal degradation         | Self-heating reduces electron mobility and transconductance.                                                                                         |

| Breakdown limits            | Approaching device breakdown increases leakage currents and trapping                                                                                 |

Table 3.4: Causes of Power-added Efficiency degration in GaN PAs [11, 12, 13, 14, 15]

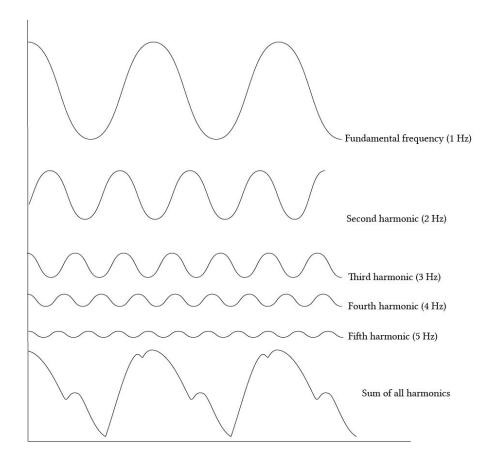

#### **Harmonic Generation**

RF power amplifiers are non-linear devices, meaning a sinusoidal input will produce output components at multiple frequencies (harmonics) in addition to the fundamental frequency.

Figure 3.10: Illustration of a distorted waveform decomposed into its fundamental and harmonic frequency components [16]

In a transistor PA, the RF output current is a distorted clipped version of the input drive due to the device's non-linear I-V characteristics. This output can be expressed as a Fourier series containing the fundamental and higher-order harmonic components, as shown in Equation 3.17 - 3.20 [10]. The amplitudes of these higher-order harmonics depends on the bias point and input drive level, which together determines the conduction angle (portion of the RF cycle during which current flows). A larger conduction angle (Class A) means the output current waveform is more sinusoidal and thus contains fewer harmonics, whereas a smaller conduction angle (class B, AB or C) produces a more clipped waveform with more harmonics [17].

In class AB, the transistor conducts more than half the full RF cycle. The current waveform is thus partially clipped and asymmetric, leading to both even- and odd-order harmonics. The drain current can be modeled as:

$$i_d(\theta) = \begin{cases} \frac{I_{\text{max}}}{1 - \cos(\alpha/2)} \Big[ \cos \theta - \cos(\alpha/2) \Big] & \text{for } \frac{-\alpha}{2} < \theta < \frac{\alpha}{2} \\ 0 & \text{otherwise} \end{cases}$$

(3.17)

The mean / DC current is:

$$I_{\rm dc} = \frac{I_{\rm max}}{2\pi} \cdot \frac{2\sin(\alpha/2) - \alpha\cos(\alpha/2)}{1 - \cos(\alpha/2)}.$$

(3.18)

The fundamental frequency components is:

$$I_1 = \frac{I_{\text{max}}}{2\pi} \cdot \frac{\alpha - \sin(\alpha)}{1 - \cos(\alpha/2)}.$$

(3.19)

3.5. Load-pull 18

And the n-th harmonic amplitude is:

$$I_n = \frac{1}{\pi} \int_{-\alpha/2}^{\alpha/2} \frac{I_{\text{max}}}{1 - \cos(\alpha/2)} \left[ \cos \theta - \cos(\alpha/2) \right] \cos(n\theta) \, \theta, \qquad n \ge 2.$$

(3.20)

GaN HEMT at X-band generate harmonics primarily through their intrinsic non-linearities (transconductance compression and non-linear conductance) and are secondarily influenced by parasitic non-linear elements (capacitances, resistances). The main implication is accurately controlling and predicting harmonic content that require models that include effect like  $g_m$  droop, knee voltage, self-heating and traps. GaN's harmonic behavior around 10 GHz is dominated by its channel physics and how those physics limit the RF waveforms. With load pull you can find the impedances of the fundamental signal and its harmonics (20 GHz, 30 GHz), after you can design to suppress the harmonics or leverage harmonics to enhance efficiency [10].

## 3.4.3. AWR Microwave Office<sup>TM</sup>

Cadence AWR Microwave Office<sup>TM</sup> is the simulation tool used in this report for the analysis of the small-and large-signal metrics and implement the (non)-linear models. Advanced Design System (ADS) is another widely used industry-standard tool for microwave circuit design, but the choice for AWR in this work reflects the preference of the company and its established workflow. In terms of capabilities both tools are largely equivalent.

### 3.5. Load-pull

Load-pull refers to the process of presenting a known impedance to a Device Under Test (DUT) in order to experimentally determine its optimal performance. In power amplifier design, the best loading conditions depend strongly on the non-linear behaviour and distortion characteristics of the transistor. The load-pull systems aid in identifying the optimum loading conditions experimentally, physically changing load reflection coefficient for extraction of design parameters, such as output power and PAE from transistor devices.

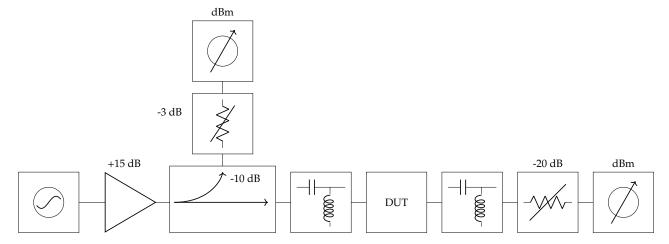

Figure 3.11: Schematic diagram of a load-pull measurement setup

A load-pull system consists of a tunable impedance tuner and a control mechanism that allows precise adjustment of the load reflection coefficient presented to the DUT. By varying the impedance, the system maps out the device's performance over a range of loading conditions. These measurements are used by designers as a target for the sign of the ouput matching network [18].

# 3.6. Impedance Matching Networks

Impedance matching is a critical aspect of RF and microwave circuit design for several reasons:

- Maximum power transfer: Proper matching between the source, transmission line and load ensures maximum power delivery while minimizing power losses.

- Improved signal-to-noise ratio: Impedance matching reduces reflections and as a result improve signal-to-noise ratio of the system, which is particularly important in sensitive applications such

3.7. Chip layout

as antennas and low-noise receivers.

• Reduced errors: Matching will reduce amplitude and phase errors in a power distribution network, leading to more accurate and stable system performance.

The process of designing a matching network involves several trade-offs. Choices must be made between the simplicity of the design, operational bandwidth, implementation and adjustability [7].

### 3.7. Chip layout

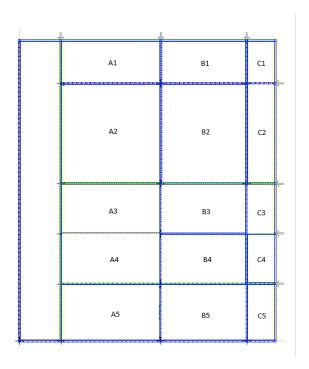

A foundry typically defines a maximum area that a single reticle can occupy. This reticle is shared among multiple designers, thereby constraining the area available for each individual device. During wafer fabrication, the wafer is separated into individual devices using a laser scribing process. For this particular fabrication run, the laser was limited to making only straight cuts spanning the entire reticle. Consequently, adjacent designs must have identical heights or widths, as illustrated in Figure 3.12.

Figure 3.12: Reticle Layout with Section Labels