# Route towards Power MOSFET large thin die mechanical robustness

Masters Thesis Report

Nikhil Gupta

# Route towards Power MOSFET large thin die mechanical robustness

# Masters Thesis Report

by

# Nikhil Gupta

Student number: 5362113

Date: 20th October, 2022 Thesis committee: Dr. René Poelma

Thesis committee: Dr. René Poelma Nexperia

Prof. Guoqi Zhang ECTM, TU Delft

Prof. Paddy French Bioelectronics, TU Delft

Prof. Willem van Driel ECTM, TU Delft

Institution: Delft University of Technology

### **ABSTRACT**

Today's cars are undergoing the greatest transformation the industry has seen. Power MOSFETs play a crucial role in making electronics more energy efficient by driving down switching losses and Rdson using a combination of next-generation trench technology and ultra-thin dies. Power MOSFET dies are becoming larger ( > 5 X 5 mm ) and thinner ( < 50  $\mu$ m ) to meet the high performance lifetime requirements of the automotive industry. The high aspect ratio and the new chip designs with trench technology offer challenges for assembly, packaging and testing.

The majority of the research performed in the past, aimed to reduce the risk of die crack by improving equipment and process strategies in back-end semiconductor processing. This thesis study aims at improving die strength from a front-end approach (device fabrication process) by making dies stronger to stress from die frontside. New chip designs are presented with new metal layer layouts for improved stress distribution. Materials like polyimide are investigated as new die top material for mechanical strengthening of die frontside. Key factors which influence die strength like trench-metal interaction, wafer stress and warpage are also analyzed in this thesis report.

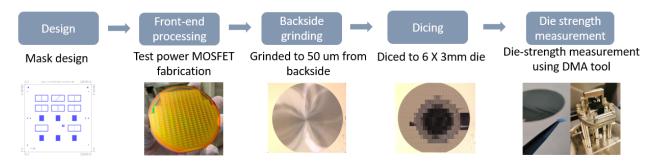

In this study, ultra-thin power MOSFET dies are realised on 100 mm diameter silicon wafers with dimensions of  $6 \times 3 \times 0.050$  mm. These dies are mechanical equivalent in design, robustness to commercial trench power MOSFETs. The processed wafers are grinded from the backside to realise 50  $\mu$ m thin wafers which are then sawned to obtain singulated dies. The strength of the dies are characterized by three-point bending tests and analyzed using probability plots for weibull distribution.

Different chip designs are compared with each other and robust designs are presented as recommendations for fabricating stronger thin power MOSFET dies to provide high performance and throughput in assembly and packaging processes.

Keywords: Power MOSFET, ultra-thin dies, back-end, front-end, trench, polyimide, three-point bending, weibull distribution.

## **ACKNOWLEDGEMENTS**

I would like to sincerely thank and appreciate the following people for their contribution in making this project possible. Dr. René Poelma for providing me the opportunity to work on this project in collaboration with Nexperia. I am grateful for your guidance, weekly discussions and sharp feedback which immensely helped me to shape this project in the right direction. Dr. Henk van Zeijl for his guidance through the fabrication part of this project and also for the great suggestions and discussions. I want to express my sincere thanks to Prof. Guoqi Zhang for giving me the chance to conduct my thesis research with Electronics Components Technology and Materials (ECTM) research group as well as for his excellent suggestions for improvement, constant encouragement, and pushing me to try new things.

Else Kooi Laboratory (EKL) played a big role in my project where I was allowed to use Class 100 clearnroom facilties for my sample's fabrication. I would like to thank the entire EKL team for their support. I am very grateful to Xinrui Ji for her support during my experimental phase. Her constant support and guidance allowed a smoother fabrication experience in EKL clearnroom. This project could not have been completed without support of Bob Knoppers from 'NXP Sample service center' where my wafer thinning and dicing process took place and also Patrick van Holst from department of Precision and Microsystems Engineering (PME) for giving me access to DMA tool for performing my stress measurements. My colleague Rami Younis from Nexperia constantly supported my project and helped me in learning tools required for my project.

At the end, I would like to thank my family and friends for being a constant pillar of support and motivation throughout my journey. I am thankful to my parents for providing me the opportunity to study in TU Delft for my master of science studies in microelectronics.

Nikhil Gupta Delft, October 2022

# Contents

| STRACT                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CKNOWLEDGEMENTS              | ii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| t of Figures                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| t of Tables                  | ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| t of Symbols & Acronyms      | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.2 Power MOSFET chip design | 10<br>12<br>15<br>16<br>18<br>18<br>19<br>20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.2 Fabrication stages       | 21<br>22<br>23<br>25<br>25<br>26<br>28<br>29<br>29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | t of Figures t of Tables t of Symbols & Acronyms PROJECT INTRODUCTION 1.1 Problem description 1.2 Research Objectives 1.3 Approach 1.4 Outline LITTERATURE OVERVIEW 2.1 Chapter introduction 2.2 Die strengthening dicing techniques 2.3 Post grinding wafer stress relief techniques: 2.4 Die pick-up and place optimization 2.5 Novel material for die top strengthening 2.6 Cantilever bending test for ultra-thin die strength measurement 2.7 Chapter Summary CHIP DESIGN AND DOE 3.1 Chapter introduction 3.2 Power MOSFET chip design 3.3.1 Different top metal design for test chip 3.3.2 Silicon trench designs 3.3.3 Mask design 3.3.1 Different top metal design for test chip 3.4.2 Study 2: Metal pattern investigation for robust gate 3.4.3 Study 3: Polyimide for die-top strengthening 3.4.4 Study 4: Impact of Trenches and their orientation on die strength 3.5 Chapter summary CLEANROOM FABRICATION OF POWER MOSFETS 4.1 Chapter Introduction 4.2.1 Deep silicon trench fabrication 4.2.2 Trench filling with poly-silicon 4.2.3 Die top metallization with aluminium 4.2.4 Passivation layers 4.2.5 Polyimide processing. 3.3.1 New process recipes for silicon trench etching. |

Contents iv

|   | <ul><li>4.4 Wafer stress and warpage analysis</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40<br>41<br>42                                                             |

| 6 | DIE STRENGTH CHARACTERIZATION 6.1 Chapter introduction 6.2 Die strength measurement setup 6.3 Testing methodology 6.4 Analytical equation for stress calculation 6.5 Die fracture strength analysis using Weibull distribution 6.5.1 Setting up a reference die 6.5.2 Die designs with negative response to die strength 6.5.3 Die designs with positive response to die strength 6.5.4 Polyimide analysis as new die top material 6.5.5 Metal layout and trench orientation interaction 6.6 Result validation using Finite Element 6.6.1 New stress equation validation using Finite element analysis 6.6.2 Polyimide pre-stress analysis 6.7 6-sigma methodology for robust assembly yield 6.8 Chapter Summary | 44<br>45<br>48<br>50<br>50<br>51<br>53<br>57<br>60<br>61<br>62<br>63<br>64 |

| 7 | SUMMARY AND CONCLUSIONS 7.1 Project Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

| A | Appendix A  A.1 Trench filling with PECVD TEOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |

# List of Figures

| 1.2<br>1.3 | cations in modern electric vehicles [24]                                                                                                                                                                                                                                                                                                                                | 1 2 2 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.4        | Different stages in thin die robustness investigation                                                                                                                                                                                                                                                                                                                   | 3     |

| 2.2        | The above graph shows the correlation between the grain size of the grinding wheel to the wafer backside roughness [20, 21]                                                                                                                                                                                                                                             | 6     |

| 2.3        | The above figure shows two stages in the die picking process, Stage 1 where collet pushes down to contact the die and applies vacuum; Stage 2 where the needle raises up to push the die and tape beneath move upwards and peels the tape from die. This is followed by collet pulling the die up under vacuum pressure [19]                                            | 6     |

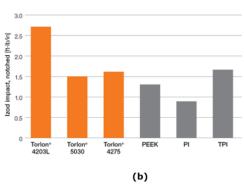

| 2.4        | Figure (a) shows histogram comparison between Torlon and metals where Torlon 7130 shows minimal thermal expansion; (b) shows histogram comparison between polymers for their toughness and Impact strength where Torlon is more than two times stronger than other polymers [34]                                                                                        | 7     |

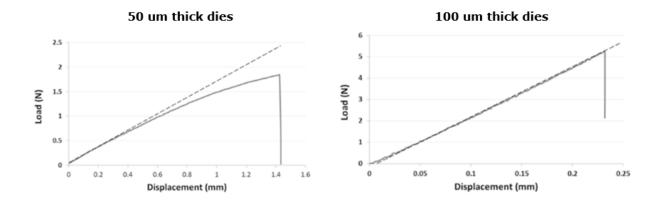

| 2.5        | Load tip force vs displacement curve for Si at 50 $\mu$ m um and 100 $\mu$ m thickness respectively as measured in three point bend test. The slope of the curve (stiffness) for 50 $\mu$ m is seen to follow                                                                                                                                                           |       |

| 2.6        | non-linear path compared to $100 \mu m$ thick silicon die [33]                                                                                                                                                                                                                                                                                                          | 8     |

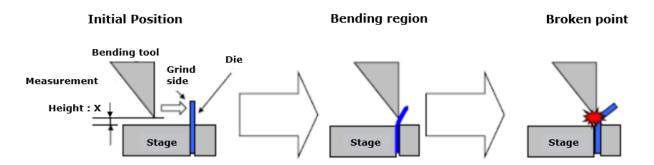

| 2.7        | plies shear stress to bend the die topside; Stage 3) die breaks around contact point [26] Traditional 3-point bend test setup by bruker where load-displacement control modes are used for die strength measurement [3]                                                                                                                                                 | 8     |

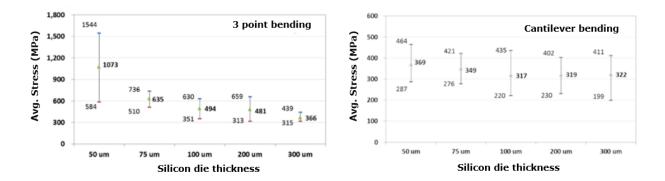

| 2.8        | Figure shows relation between average die stress vs silicon die thickness for two strength measurement techniques, 3-point bending (on left) and cantilever bending (on right). 50 $\mu$ m dies in 3-point bending test show high data variation which is reduced by cantilever bending test as it can support very short span length required for ultra thin dies [33] | 9     |

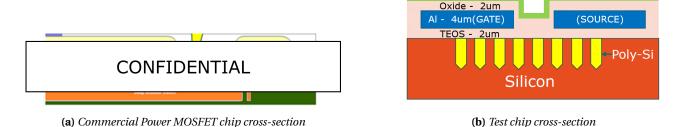

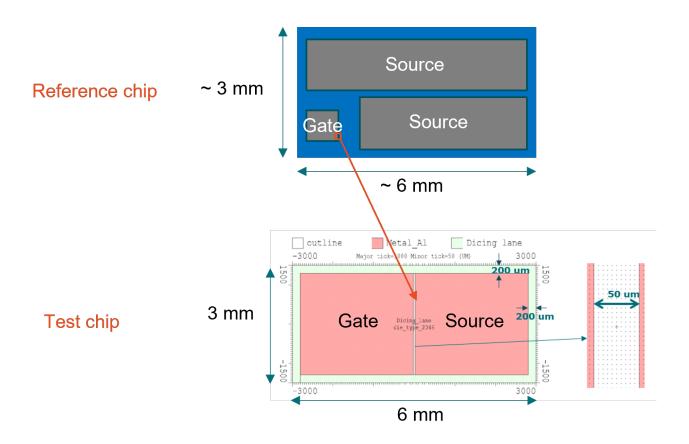

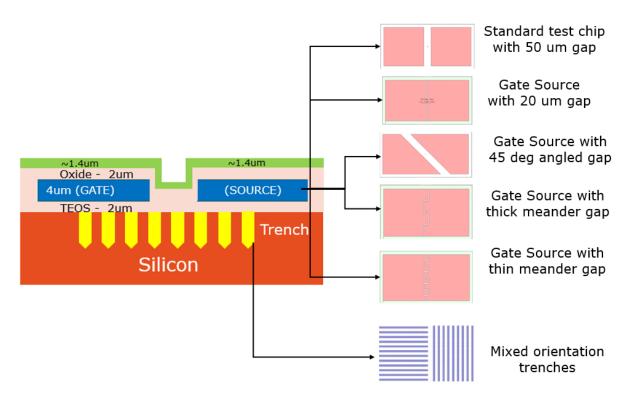

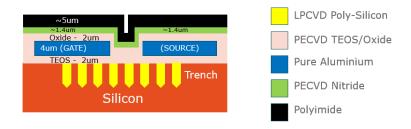

|            | Die cross-section comparison between commercial and dummy power MOSFET chip Outline of commercial large MOSFET die as compared to test chip die. Gate-Source gap is                                                                                                                                                                                                     | 10    |

|            | same for both outlines                                                                                                                                                                                                                                                                                                                                                  | 11    |

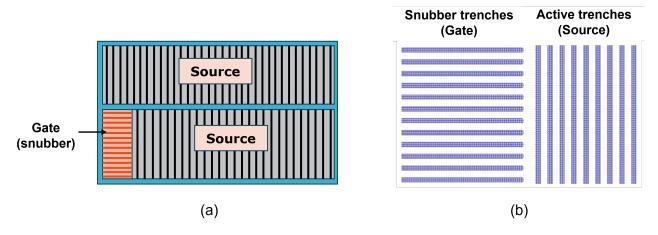

| 3.3        | a) Trench layout and orientation in commercial power MOSFET; b) Trenches in dummy test chip                                                                                                                                                                                                                                                                             | 11    |

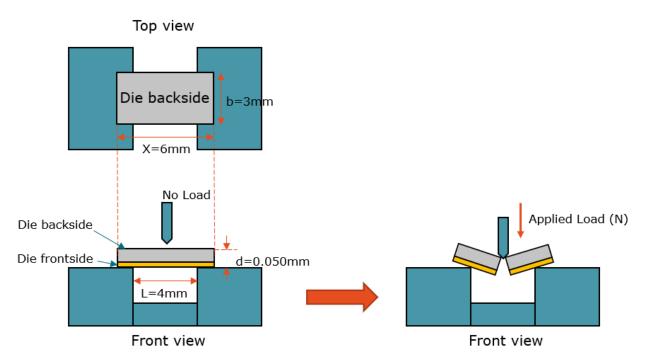

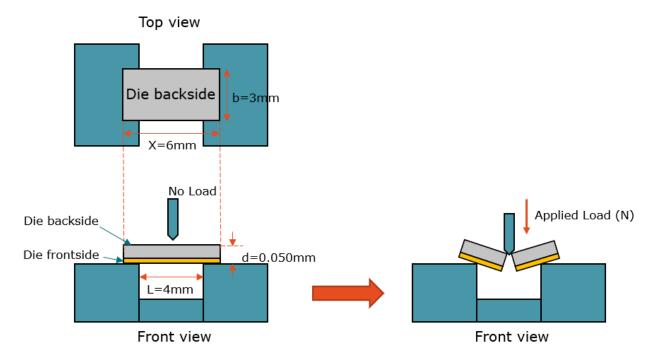

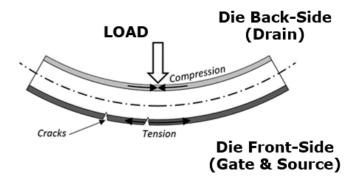

| 3.4        | The above schematic shows die specimen loading setup. Die is flipped exposing silicon backside to applied force and die cracks from frontside first under tensile stress                                                                                                                                                                                                | 12    |

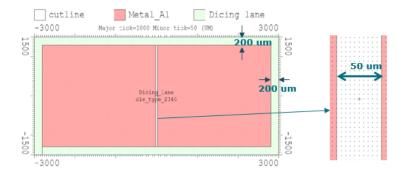

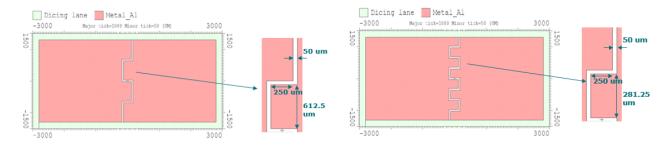

| 3.5        | Standard test chip where gate and source metal area are separated by a $50\mu m$ vertical line gap                                                                                                                                                                                                                                                                      | 13    |

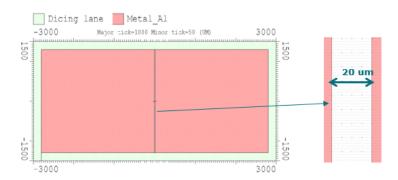

| 3.6        | Chip design with reduced gate and source metal area separation (20 $\mu$ m)                                                                                                                                                                                                                                                                                             | 13    |

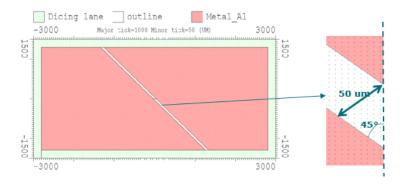

| 3.7        | Chip design where gate-source vertical separation is replaced with a $45^{\circ}$ angled metal layer $$ .                                                                                                                                                                                                                                                               | 14    |

| 3.8        | Chip design with different meander layouts for die metallization. The key difference between the two designs is that former has thicker metal between meander fingers compared to the                                                                                                                                                                                   |       |

| 3.9        | latter                                                                                                                                                                                                                                                                                                                                                                  | 14    |

| 3.10       | insights for meander design optimization                                                                                                                                                                                                                                                                                                                                | 14    |

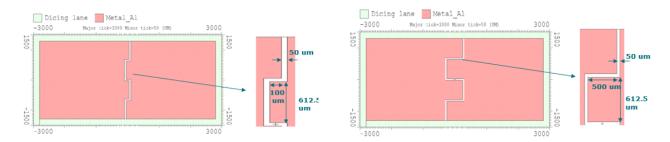

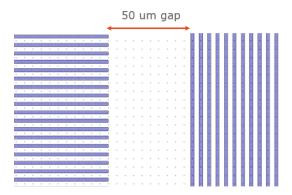

|            | tation pattern is also seen in commercial power MOSFET devices                                                                                                                                                                                                                                                                                                          | 15    |

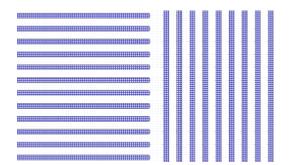

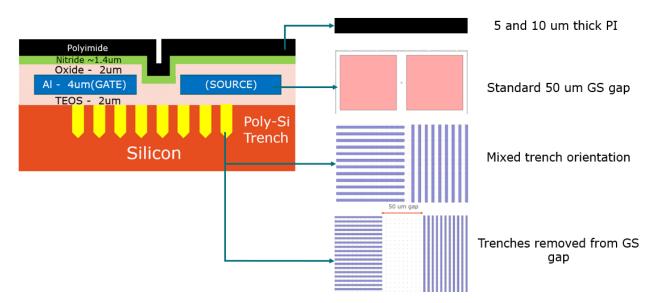

| 3.11       | Chip with mixed trench orientation but separated by a 50 $\mu$ m gap                                                                                                                                                                                                                                                                                                    | 16    |

List of Figures vi

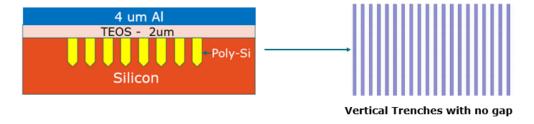

|      |                                                                                                                                                                                       | 16 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

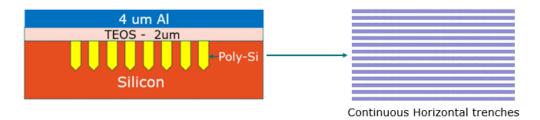

| 3.13 | Chip design with only horizontally oriented trenches                                                                                                                                  | 16 |

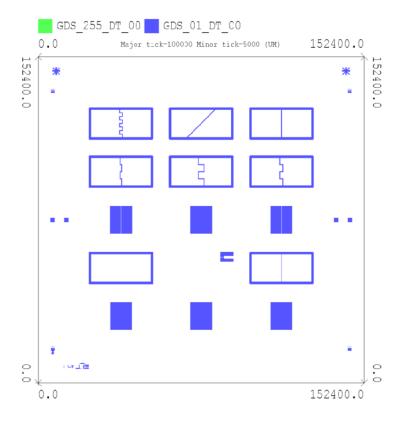

| 3.14 | The top cell which consists of all the various mask designs in single mask cell. The first two                                                                                        |    |

|      | rows represents different pattern for metal layer. Third and fifth row show masks with different                                                                                      |    |

|      | trench orientations                                                                                                                                                                   | 17 |

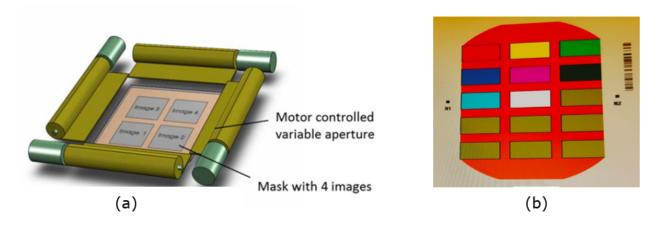

| 3.15 | (a) The mask blanking system of the PAS5500/80 waferstepper with 4 images; (b) job for mask                                                                                           |    |

|      |                                                                                                                                                                                       | 17 |

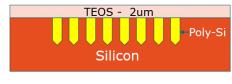

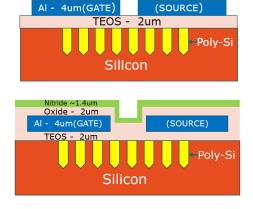

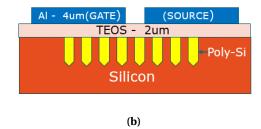

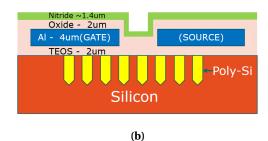

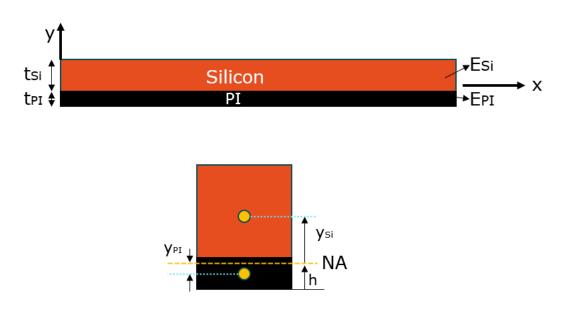

| 3.16 | The figure shows different die cross-sections with various semiconductor process layers. Die                                                                                          |    |

|      | cross-section are namely (a) Si + 4 $\mu$ m Al die; (b) Si + 6 $\mu$ m Al die; (c) Si + 4 $\mu$ m Al + passivation                                                                    |    |

|      | layers; (d) Si + 5 $\mu$ m PI                                                                                                                                                         | 18 |

| 3.17 | Test chip of 3 x 6 mm, 50 $\mu$ m thick with different top metal mask designs                                                                                                         | 19 |

|      | Die cross-section highlighting different trenches and polyimide thickness for investigation                                                                                           | 19 |

|      |                                                                                                                                                                                       | 20 |

|      | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                 | 20 |

| 0.20 | The cross section for investigating the stronger with only nonzontal trenence                                                                                                         |    |

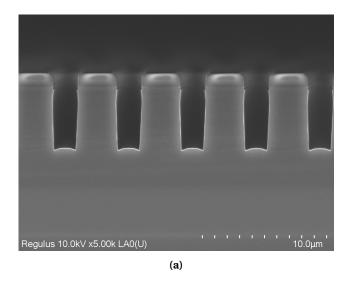

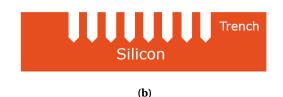

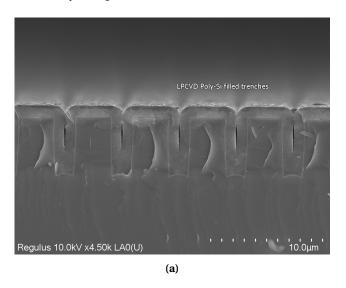

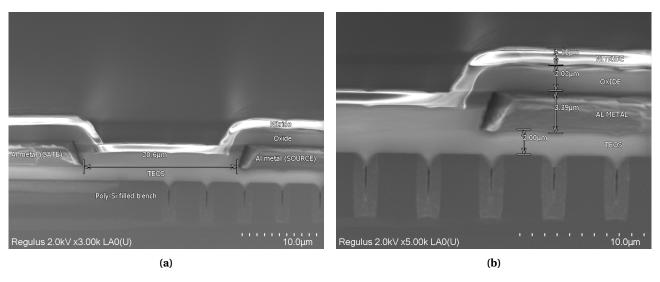

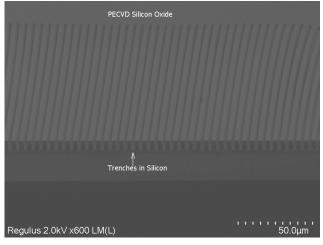

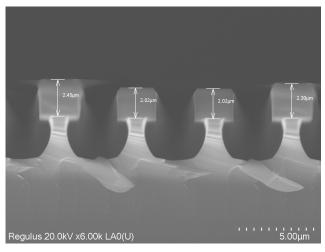

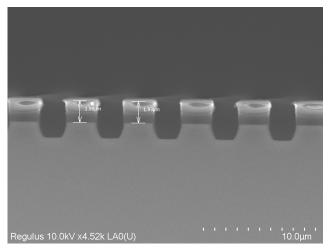

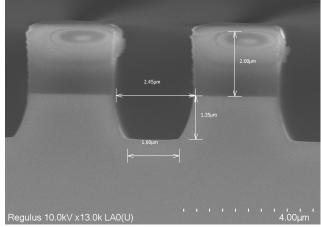

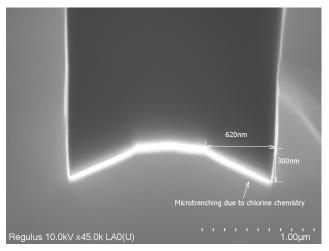

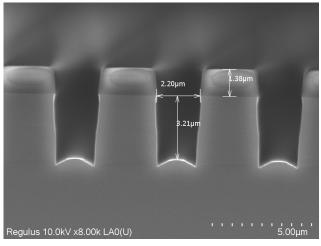

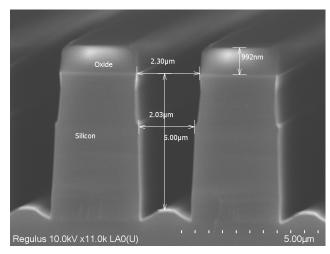

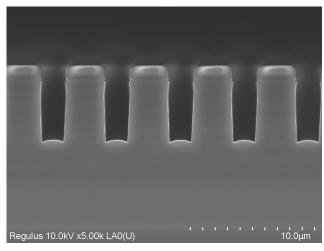

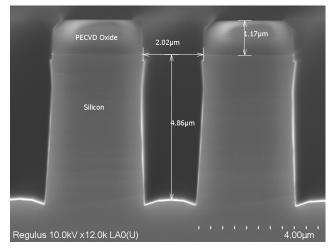

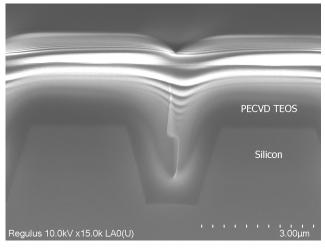

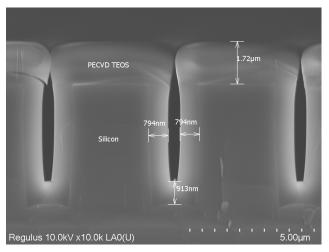

| 4.1  | (a) SEM image showing trenches in silicon with leftover oxide mask; (b) Die cross-section with                                                                                        |    |

|      |                                                                                                                                                                                       | 22 |

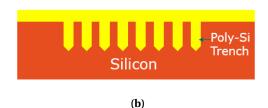

| 4.2  | (a) SEM image showing trenches filled with poly-silicon in low pressure deposition; (b) Die                                                                                           |    |

|      |                                                                                                                                                                                       | 23 |

| 4.3  | SEM image showing voids inside poly-silicon filled trenches. Residual poly-silicon is also ob-                                                                                        |    |

| 1.0  |                                                                                                                                                                                       | 24 |

| 4.4  | (a) LPCVD Poly-Si etched back using ICP-RIE etcher using 150 nm TEOS as stopping layer; (b)                                                                                           |    |

| 1.1  |                                                                                                                                                                                       | 24 |

| 4.5  | (a) Pure aluminium deposited and patterned in desired gate-source layout; (b) Die cross-                                                                                              |    |

| 1.0  |                                                                                                                                                                                       | 25 |

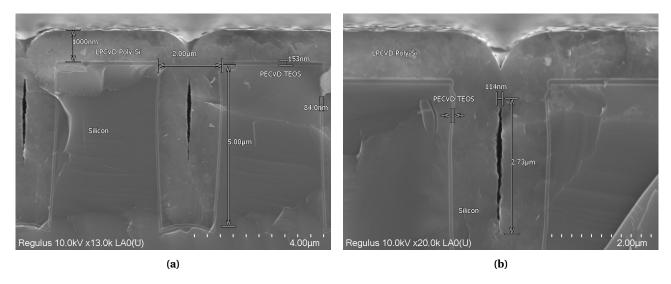

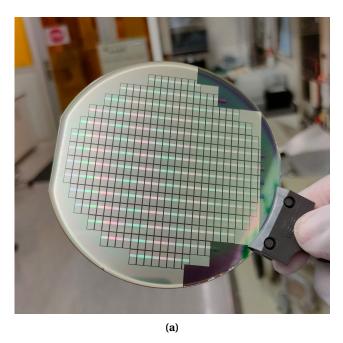

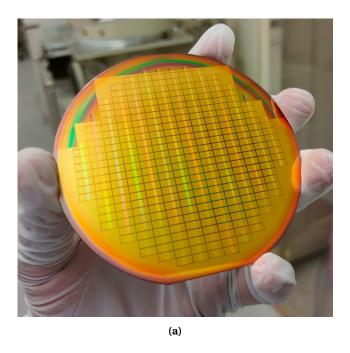

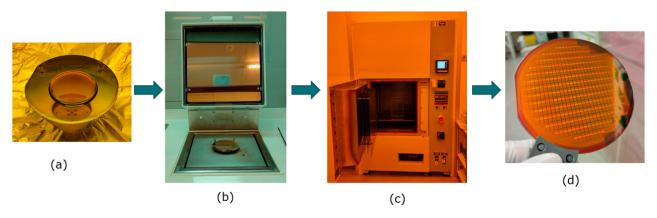

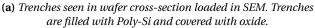

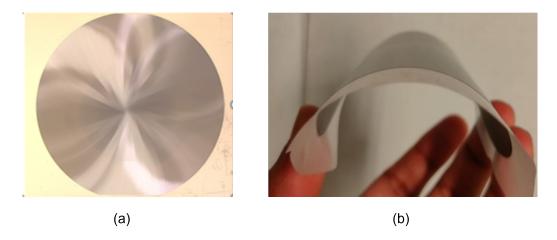

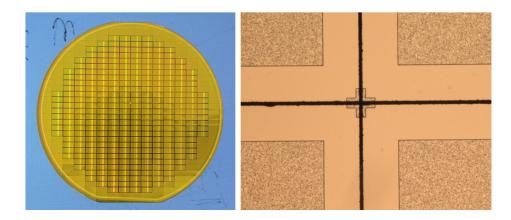

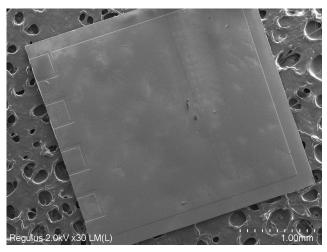

| 4.6  | (a) Processed wafer with dummy Power MOSFET dies similar to commercial trench power                                                                                                   | 20 |

| 4.0  | •                                                                                                                                                                                     | 26 |

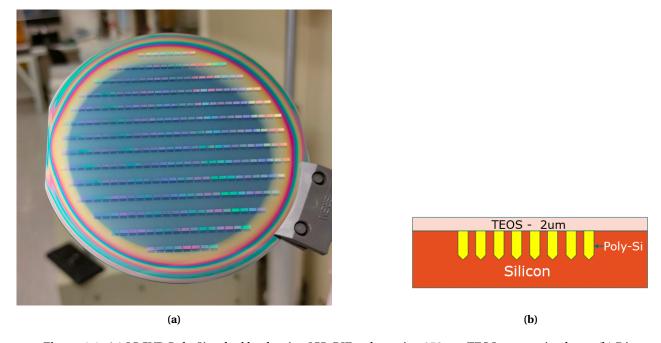

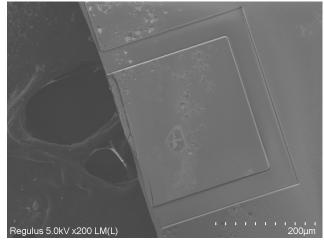

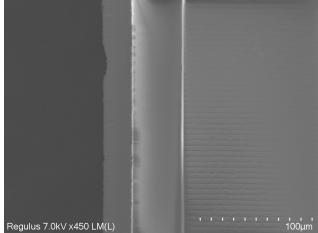

| 17   | (a) SEM image showing dummy Power MOSFET cross-section which is similar to commer-                                                                                                    | 20 |

| 4.7  | cial trench power MOSFET device cross-section; (b) A close-up SEM image showing different                                                                                             |    |

|      |                                                                                                                                                                                       | 26 |

| 4.0  |                                                                                                                                                                                       | 20 |

| 4.8  | Figure (a) PI is removed in a vertical line using acetone; (b) PI thickness measured using Dektak profilometer; (c) Graph showing difference between PI covered and uncovered region; | 27 |

| 4.0  |                                                                                                                                                                                       | 27 |

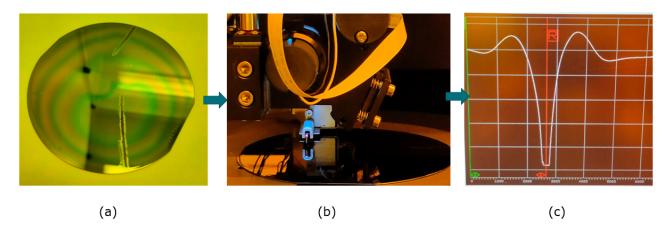

| 4.9  | Figure (a) shows polyimide on top of wafer for spin coating; (b) shows soft baking of polyimide                                                                                       | 20 |

| 4.10 |                                                                                                                                                                                       | 28 |

|      | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                 | 28 |

|      |                                                                                                                                                                                       | 28 |

| 4.12 | (a) shows <100> wafer with diamond tip tool for cleaving, (b) cleaved wafer with a thin wafer                                                                                         |    |

|      | strip, (c) shows thin wafer strip attached to the clamp, (d) shows loading of clamped wafer                                                                                           |    |

|      | •                                                                                                                                                                                     | 29 |

|      |                                                                                                                                                                                       | 30 |

|      |                                                                                                                                                                                       | 30 |

|      |                                                                                                                                                                                       | 31 |

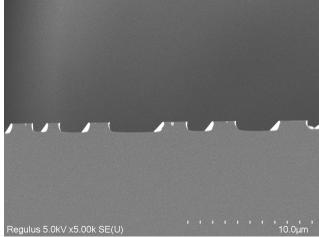

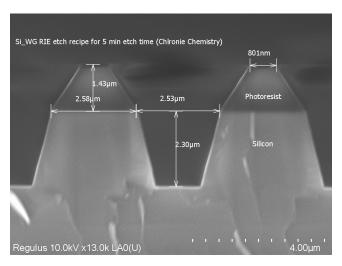

| 4.16 | The SEM image of tapered shallow trenches as obtained from recipe Si_WG (test run 3). The                                                                                             |    |

|      |                                                                                                                                                                                       | 32 |

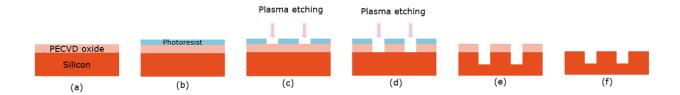

| 4.17 | The above figure shows different stages for making trenches using oxide based mask.(a) Silane                                                                                         |    |

|      | based oxide deposited using PECVD. (b) Photoresist coated on top of oxide. (c) Photoresist                                                                                            |    |

|      | layer patterned using lithography and then exposed oxide area etched using plasma etching.                                                                                            |    |

|      | (d) Silicon etched using patterned oxide mask. (e) Residual oxide mask to be remove using                                                                                             |    |

|      | BHF chemical solution (f) Final patterned silicon die                                                                                                                                 | 33 |

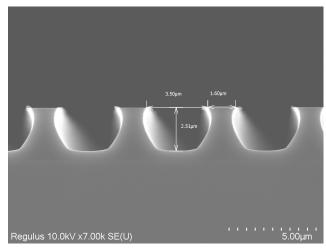

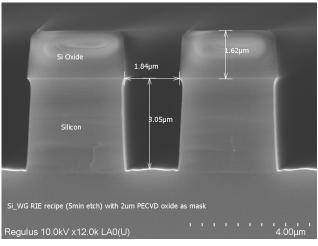

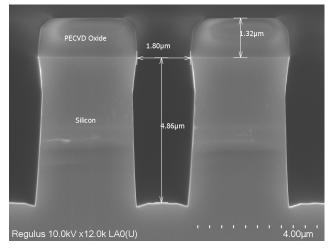

| 4.18 | The SEM image for trenches obtained by using Si_WG recipe with PECVD oxide mask for two                                                                                               |    |

|      | different etch times (a) 5 min etch; (b) 8 min etch                                                                                                                                   | 34 |

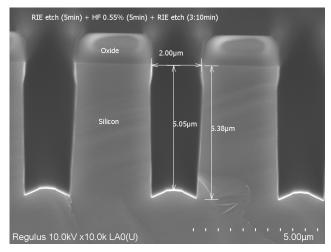

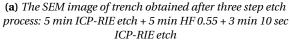

| 4.19 | The SEM image for trenches obtained by test run 5                                                                                                                                     | 35 |

| 4.20 | The SEM images show key process parameters influencing trench bottom (a) and trench side-                                                                                             |    |

|      | wall profile (b).                                                                                                                                                                     | 36 |

|      |                                                                                                                                                                                       |    |

List of Figures vii

| 4.21 | The SEM images showing trenches obtained by optimizing trench etch parameters to obtain desired trench aspect ratio and profile                                          | 36         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

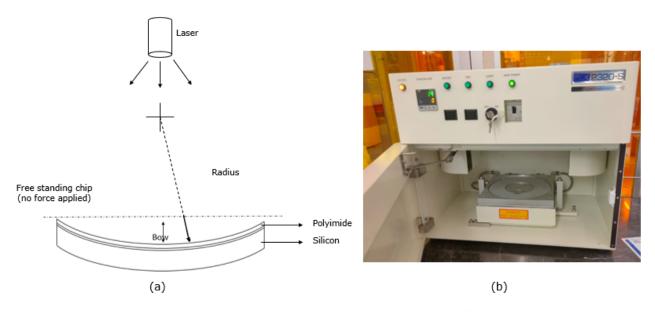

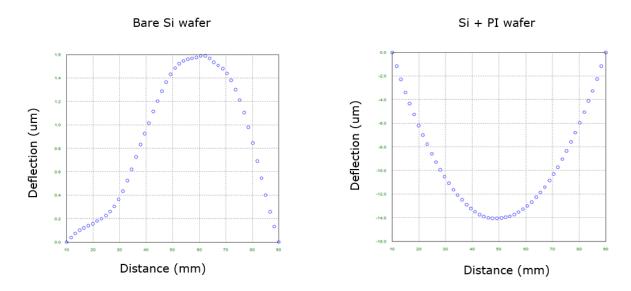

| 4.22 | (a) figure representing bow and radius of a warped silicon die with PI film; (b) Flexus tool used for thin film stress measurements in 100 mm wafers                     | 37         |

| 4.23 | Wafer bow measurements for bare silicon wafer (on left) as compared to wafer bow with addition of PI film on top. Cured PI film exhibits tensile stress.                 | 38         |

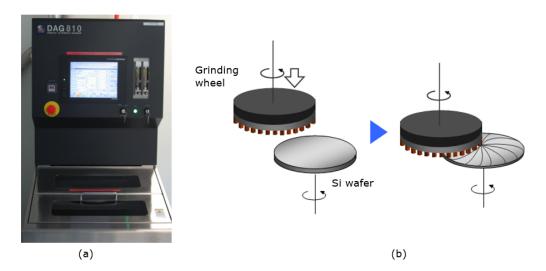

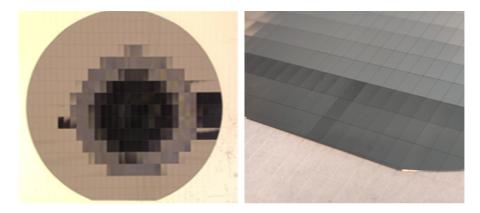

| 5.1  | Figure (a) shows the DAG810 automatic Surface grinder tool and figure (b) shows the Grinding                                                                             | 39         |

| 5.2  | mechanism [8]                                                                                                                                                            | 39<br>40   |

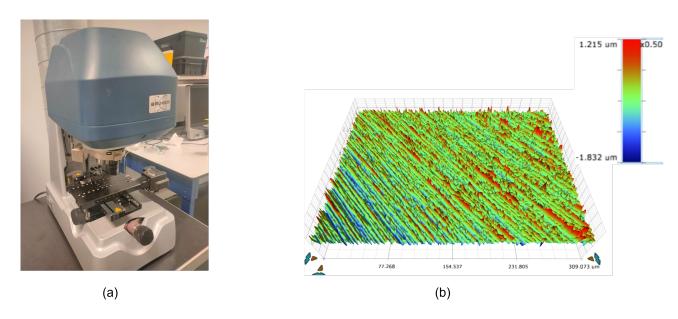

| 5.3  | (a) White light interferometer used for thin die backside roughness measurements; (b) 3-D plot for grinded silicon backside                                              | 40         |

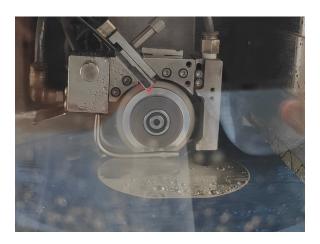

| 5.4  | Dicing blade dicing through silicon wafer to make 6X3 mm dies                                                                                                            | 41         |

| 5.5  | Individual dies seen post dicing process                                                                                                                                 | 41         |

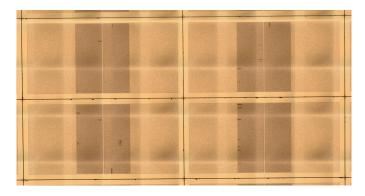

| 5.6  | Wafer diced into individual dies using cross marker                                                                                                                      | 42         |

| 5.7  | Wafer diced into individual dies without cross marker                                                                                                                    | 42         |

| 5.8  | Wafer mounted on top of low adhesive UV foil were singulated manually using tweezers                                                                                     | 43         |

| 6.1  | The above schematic shows die specimen loading setup. Die is flipped exposing silicon backside to applied force and die cracks from frontside first under tensile stress | 44         |

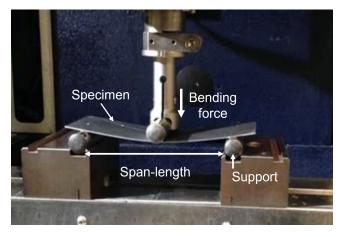

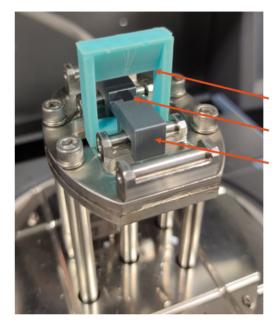

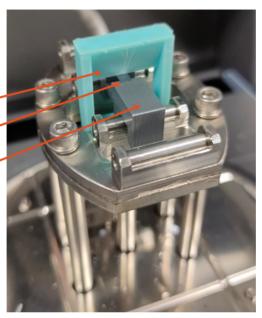

| 6.2  | The DMA test setup for three-point bend test for die strength characterization. The die rests                                                                            | 45         |

| 6.3  | on top of sample holder and a indenter (in green) applies load on the die                                                                                                | 45         |

| 0.5  | side experiences compressive stress and die frontside undergoes tensile stress which results                                                                             |            |

|      | in crack formation                                                                                                                                                       | 46         |

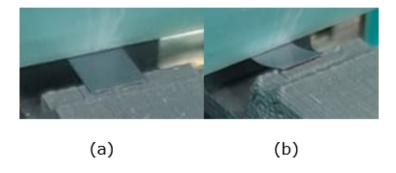

| 6.4  | (a) shows a custom made force indenter making contact with the backside of die (silicon) (b)                                                                             |            |

|      | thin die bending under applied load. ultra-thin silicon dies shows extraordinary flexibility $$                                                                          | 46         |

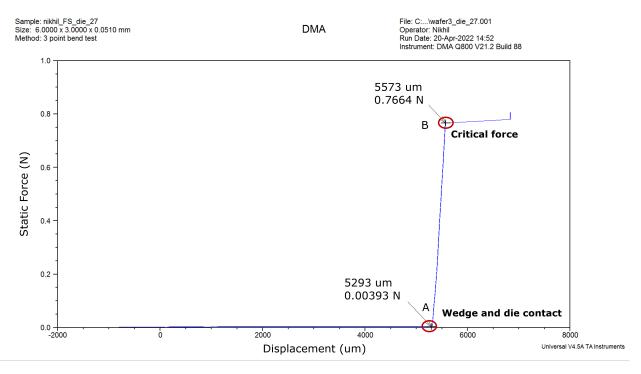

| 6.5  | Force- Displacement graph for a bare silicon die without any process layers. Point A marks the                                                                           |            |

|      | contact between the wedge and die where point B refers to the force and displacement where                                                                               | 47         |

| 6.6  | the die cracks                                                                                                                                                           | 47         |

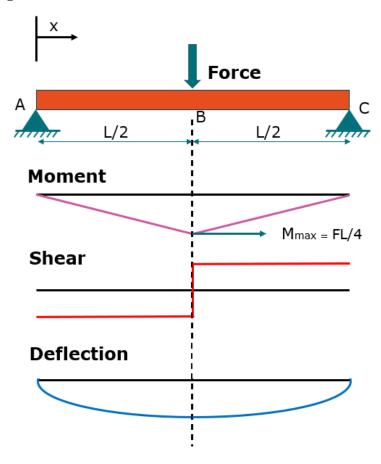

| 0.0  | of bending moment (M), shear (Q) and bending deflection (D). Schematic is a production                                                                                   |            |

|      | provided by [39]. Maximum bending moment M is observed at centre of the beam                                                                                             | 48         |

| 6.7  | Schematic of a composite beam of two materials with different young's modulus                                                                                            | 48         |

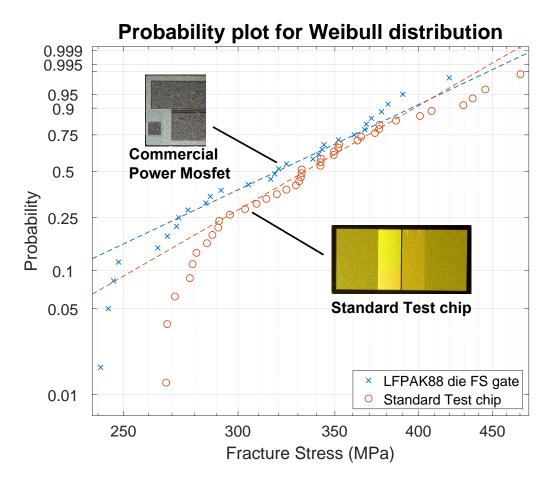

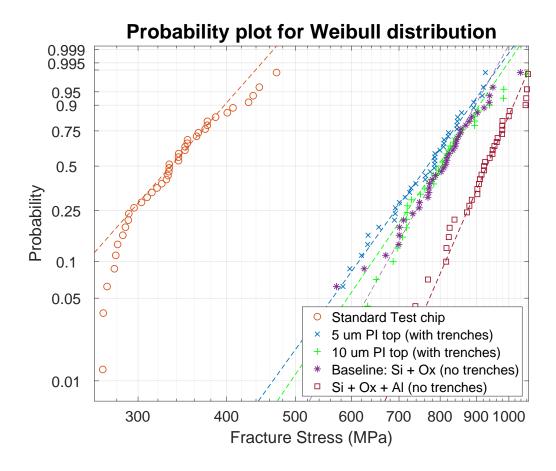

| 6.8  | Weibull distribution for fracture stress comparison of two chips namely commercial trench                                                                                |            |

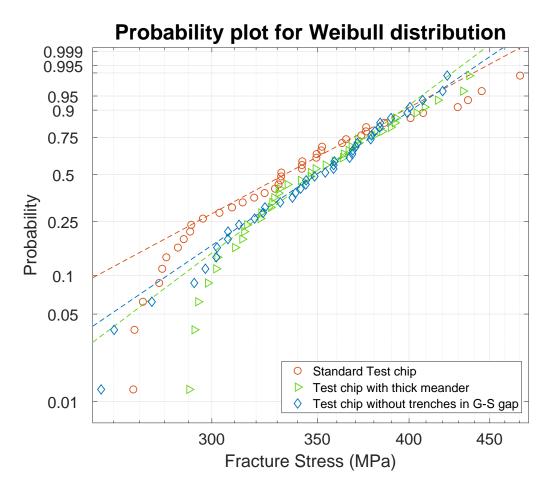

|      | power MOSFET chip and standard test chip                                                                                                                                 | 51         |

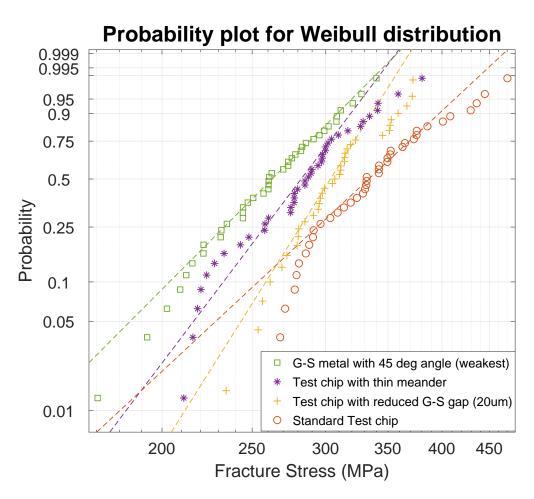

| 6.9  | Weibull probability plot for die designs which decreased frontside die strength as compared                                                                              | <b>5</b> 0 |

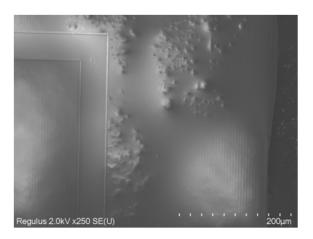

| 6 10 | to standard test chip. Dies with angled G-S separation showed lowest fracture strength SEM analysis for die crack for thin meander chip design                           | 52<br>53   |

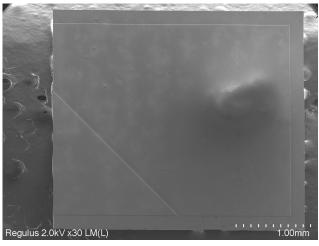

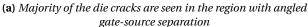

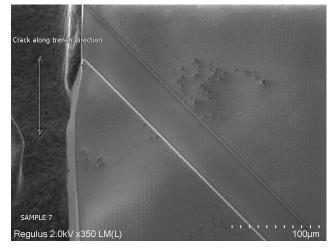

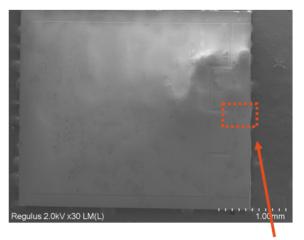

|      | SEM analysis for die crack for angled gate-source separated chip design                                                                                                  | 53         |

|      | Weibull probability plot showing die designs which increased die strength as compared to                                                                                 |            |

|      | standard test chip. Die design with thick meander and design where trenches are covered                                                                                  |            |

|      | with metal layer above show higher die fracture strength                                                                                                                 | 54         |

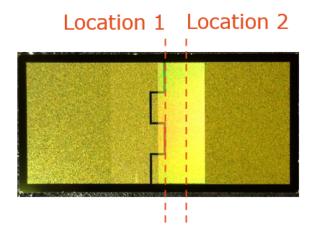

| 6.13 | Die crack seen observed at the meander path in metal absent region (left), closer inspection                                                                             |            |

|      | reveals crack initiation along vertical trenches (right)                                                                                                                 | 55         |

| 6.14 | The SEM image of die crack seen at the meander path in metal absent die region (left), closer                                                                            |            |

| 6 15 | inspection reveals crack initiation along vertical trenches (right)                                                                                                      | 55         |

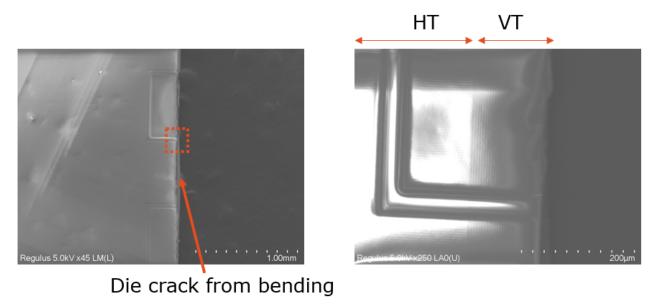

| 0.13 | The SEM shows die crack seen in thick meander die at location 2 (left) and closer inspection reveals crack initiation along vertical trenches under the metal (right)    | 56         |

| 6.16 | SEM analysis for die crack for thick meander chip design.                                                                                                                | 56         |

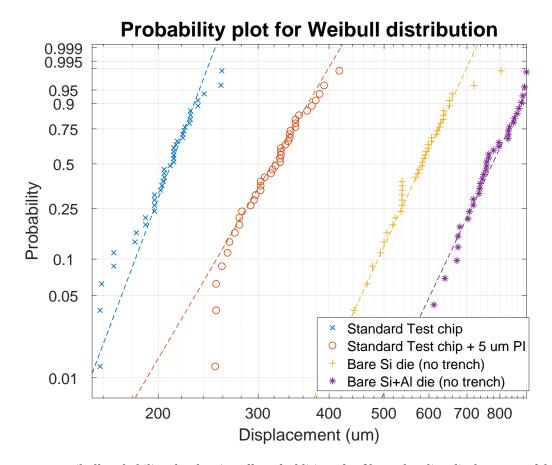

|      | Weibull probability plot implying effect of PI addition on die strength compared to die without                                                                          | 50         |

|      | PI                                                                                                                                                                       | 58         |

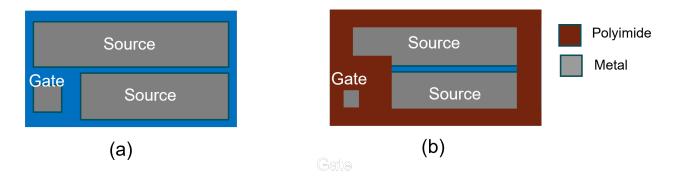

| 6.18 | (a) Standard commercial power MOSFET chip; (b) Proposed chip design with 5 $\mu$ m PI film on                                                                            |            |

|      | front-side                                                                                                                                                               | 58         |

List of Figures viii

| 6.19 | Weibull probability plot showing effect of addition of PI film on bending displacement of thin die compared to dies without PI                                                                                                                                                                                                                                                                                                     | 59       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

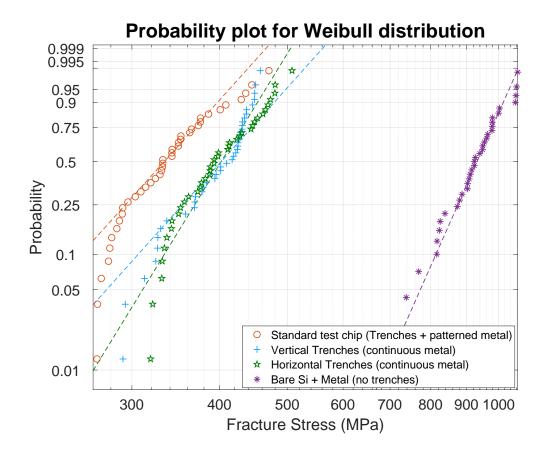

| 6.20 | Weibull probability plot for comparison of dies with and without trenches and continuous metal layer                                                                                                                                                                                                                                                                                                                               | 60       |

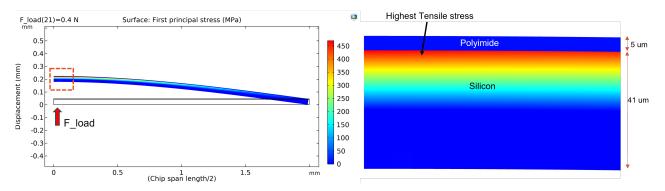

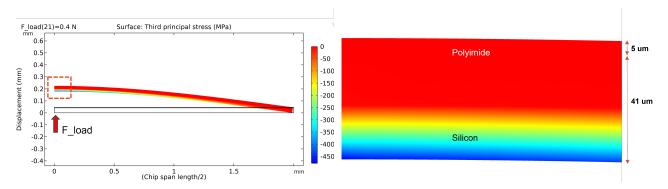

| 6.21 | FEA for tensile stress in thin silicon die with polyimide top. Maximum tensile stress (in red) is observed at silicon substrate. Soft materials like PI experience lower tensile stress (in shades                                                                                                                                                                                                                                 | co       |

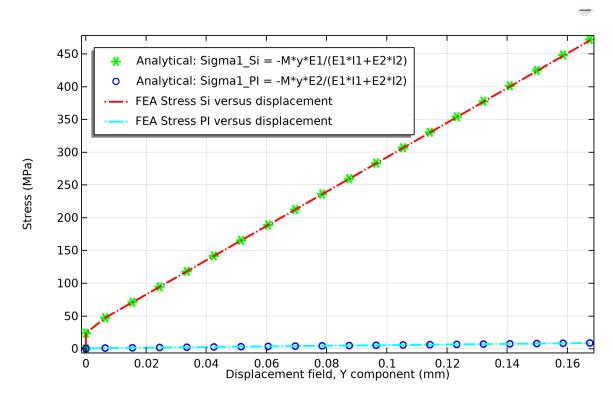

| 6.22 | of blue) because of their low stiffness                                                                                                                                                                                                                                                                                                                                                                                            | 62       |

| 6.23 | observed in PI film                                                                                                                                                                                                                                                                                                                                                                                                                | 62       |

| 6.24 | analytical equation satisfies the stress measured by the finite element model                                                                                                                                                                                                                                                                                                                                                      | 63<br>63 |

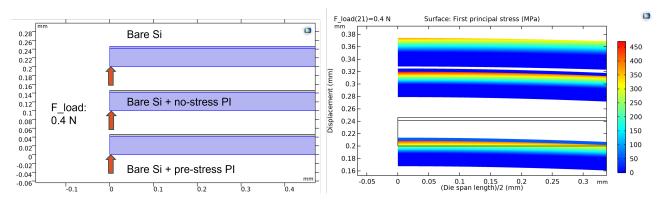

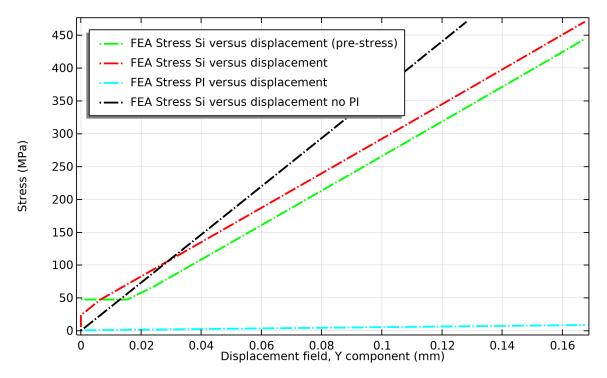

| 6 25 | Finite element                                                                                                                                                                                                                                                                                                                                                                                                                     | 64       |

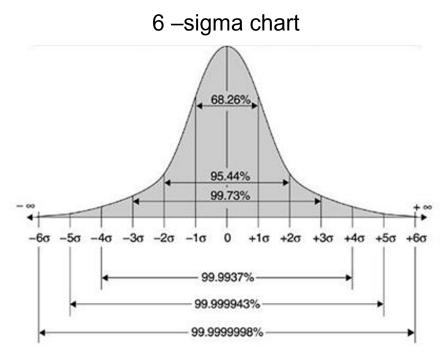

|      | 6-sigma chart for monitoring yield in assembly process [36]                                                                                                                                                                                                                                                                                                                                                                        | 65       |

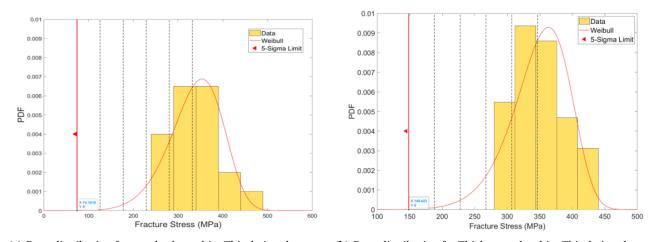

|      | Data distribution for the front-side die strength of standard test chip (M1) and thick meander chip (M2). 5-sigma value for robust high yield assembly process can be obtained from this                                                                                                                                                                                                                                           | 00       |

|      | distribution                                                                                                                                                                                                                                                                                                                                                                                                                       | 65       |

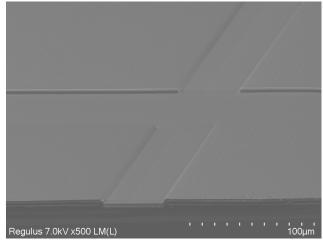

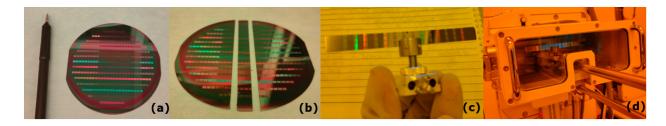

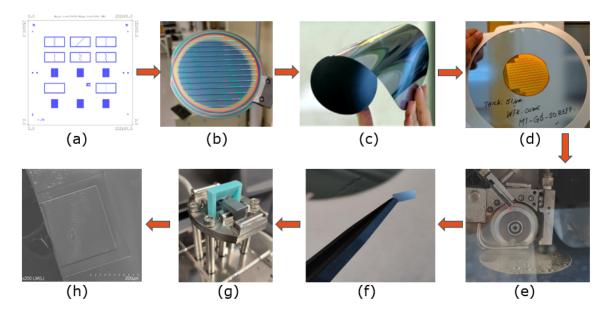

| 7.1  | Figure shows the flow for the various process steps in the project. (a) Mask cell for different metal and trench designs, (b) die fabrication on 100 mm silicon wafers, (c) Wafer thinning from backside to 50 $\mu$ m. (d) Low adhesive UV foil for mounting thin wafer, (e) wafer dicing for die singulation, (f) Die pick up with tweezers, (g) Die bending test for strength characterization, (h) Die failure analysis in SEM | 67       |

| 7.2  | (a) Standard test chip outline; (b) Chip cross-section                                                                                                                                                                                                                                                                                                                                                                             | 68       |

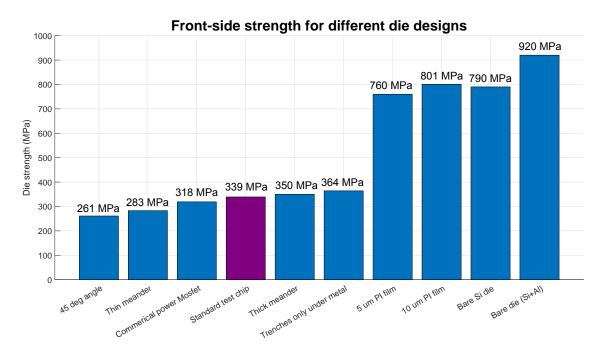

| 7.3  | Bar chart showing front-side die strength of different die designs                                                                                                                                                                                                                                                                                                                                                                 | 69       |

| A.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74       |

# List of Tables

| 4.1        | Trench parameters as seen in dummy power MOSFET devices                                                                                                                                | 22 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2        | Cured Film Properties of Durimide 7520                                                                                                                                                 | 27 |

| 4.3        |                                                                                                                                                                                        | 29 |

| 4.4        | Test run 2 for trench etch recipe development                                                                                                                                          | 31 |

| 4.5        | Test run 3 for trench etch recipe development                                                                                                                                          | 32 |

| 4.6        | Test run 4 for trench etch recipe development                                                                                                                                          | 33 |

| 4.7        | surements, negative sign (-) refers to compressive stress and positive sign (+) indicates tensile                                                                                      |    |

|            | stress in film.                                                                                                                                                                        | 37 |

| 5.1        | Roughness parameters for grinded die backside                                                                                                                                          | 40 |

| 6.1        | Data comparison for frontside strength between commercial and standard test chip                                                                                                       | 51 |

| 6.2        | Data comparison between standard test chip and designs which reduced die frontside strength.                                                                                           | 52 |

| 6.3<br>6.4 | Data comparison between standard test chip and designs which improved die frontside strength. Data comparison between standard test chip and dies with Polyimide and bare dies without | 54 |

|            | trenches                                                                                                                                                                               | 57 |

| 6.5        | Data comparison between standard test chip and other die designs for maximum die bending                                                                                               |    |

|            | deflection under applied fracture force                                                                                                                                                | 59 |

| 6.6        |                                                                                                                                                                                        | 60 |

| 6.7        | 5-sigma limit value comparison between standard test chip (M1) and chip with thick meander                                                                                             |    |

|            | (M2)                                                                                                                                                                                   | 65 |

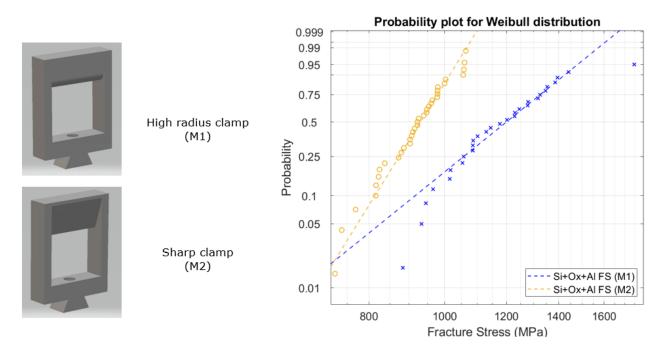

| A.1        | <b>1</b>                                                                                                                                                                               |    |

|            | wedges to study their influence on die strength. Sharp radius wedge (M2) is found to perform                                                                                           |    |

|            | better than high radius wedge (M1)                                                                                                                                                     | 73 |

# List of Symbols & Acronyms

### **Symbols**

CMP Chemical Vapor Polishing

DMA Dynamic Mechanical Analyzer

DOE Design Of Experiment

EKL Else Kooi Laboratory

HAR High Aspect Ratio

HF Hydrofluoric acid

HMDS Hexamethyldisilazane

HT Horizontal Trenches

ICP Inductively Coupled Plasma

LPCVD Low Pressure Chemical Vapor Deposition

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MT Mixed Trenches

PAI Polyamide-imide

PECVD Plasma Enhanced Chemical Vapor Deposition

PI Polyimide

RDSON Drain-Source On Resistance

RIE Reactive Ion Etching

TEOS Tetra Ethyl Ortho Silicate

UV Ultraviolet light

VT Vertical Trenches

# 1 PROJECT INTRODUCTION

Automotives are experiencing the most radical transition the industry has ever witnessed. Continued electrification is causing considerable modifications from the engine to the cloud. Innovative technologies and systems for the powertrain, chassis, safety, lighting, and body electronics contribute to the enhancement of overall vehicle efficiency and the reduction of fuel consumption,  $CO_2$  emissions, and costs. Power MOSFETs play a significant role in enhancing the energy efficiency of electronic devices by reducing switching losses and Drain-Source on resistance ( $R_{\rm DS(on)}$ ) through the use of cutting-edge trench technology and ultra-thin dies.

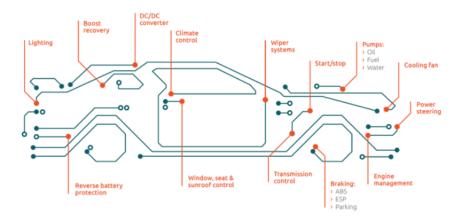

Power MOSFET devices can have two topographies, Trench MOSFET or Planar MOSFET. Trench MOSFET are used for low voltage application (  $< 200~\rm V$ ) as they offer higher channel density and lower on resistance ( $R_{DS(on)}$ ) [2, 30]. Planar MOSFET are used for high voltage applications where on resistance is dominated by epi-layer resistance and thus high channel density from trenches is not required [2]. The figure 1.1 below shows the wide range of applications where power MOSFET are used in automotives.

**Figure 1.1:** Power MOSFET are one of the key devices for power switching and other wide range of applications in modern electric vehicles [24]

In this project, focus is shifted to Si-based trench power MOSFETs where current is driven vertically from one surface to the other surface to achieve high driving capabilities. It is realised by packing millions of trenches on the die where each trench controls the current conduction around it with a combination of gate dielectric and gate electrodes [30].

### 1.1. Problem description

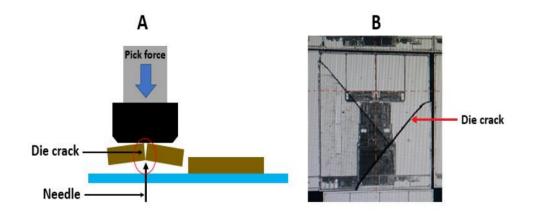

Power MOSFET dies are becoming larger ( > 5 x 5 mm ) and thinner ( < 50  $\mu m$  ) to meet the high performance and lifetime requirements of the automotive industry. The high aspect ratio and the new chip designs (unique trench technology) offer new challenges for assembly and packaging. This is because thin substrates and large area devices make dies susceptible to fracture from small cracks induced during dicing, thinning and other handling processes. In figure 1.2, one such instance of die cracking is shown during die pick-up process where the thin die is unable to handle needle and collet force applied by the pick-up tool and results in crack. This thesis presents an experimental study on how to increase mechanical robustness and reliability of large thin power MOSFET dies to reduce the risk of die crack for next generation packaging and assembly processes.

Power MOSFET device fabrication introduces structural stress from the different depositions, etching and other processes. This can result in wafer warpage due to the tensile or compressive stresses after fabrication.

Wafer thinning and sawing processes induce additional defects and stresses in these wafers. Post grinding and sawing, the ultrathin dies are picked up from the carrier. To meet the throughput requirement of the industry, an ultra fast pick up and place process is essential. The automation tools used for this segregation induce new forces and stress on the individual dies and hence increase the risk of crack initiation and device failure. The die after pick-up is attached to a lead frame and encapsulated. This packaging process establishes electrical connections and connects the die to the outside world. During the packaging phase, the die further undergoes various additional thermal and mechanical steps which exert stress on the silicon.

Figure 1.2: A) Thin die cracking during die pick-up process; B) Die crack as seen in silicon die [28].

It is imperative to ensure that the finished product is highly reliable during its lifetime. It is therefore important to prevent any factors which can potentially cause functionality failure of the installed power MOSFET device caused by die crack or other failures. For a continuous upscale in performance and efficiency of large-thin dies to drive next generation electric vehicles, wafer thinning is one of the key and most challenging strategy which demands for thin dies to be made more robust.

### Why make dies thinner?

- Large thin dies offer higher efficiency, longer lifetime and sustainability as they provide lower R<sub>DS(on)</sub>, reduced switching losses and increased current driving capability [16, 31, 29].

- Thin silicon wafers (50  $\mu$ m) improve heat dissipation of dies with high power densities [29].

- Thinner dies reduce die attach solder fatigue.

- Wafer thinning increases the mechanical stability of wafers, thus enabling bendable and flexible next generation devices [31].

| Parameter     | < 50 um<br>thick die | > 70um<br>thick die | Remarks           |

|---------------|----------------------|---------------------|-------------------|

| Performance   | 1                    | 1                   | On<br>resistance  |

| Reliability   | 1                    | 1                   | Solder<br>fatigue |

| Manufacturing | 1                    | 1                   | In assembly       |

| Robustness    | 1                    | 1                   | Die strength      |

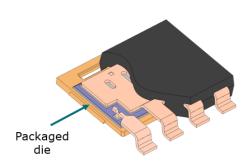

**Figure 1.3:** Thin dies packaged inside a copper-clip package for high performance and efficiency applications; Table comparing different parameters between thin and thick power MOSFET dies

To summarize, large-thin power MOSFET devices drive the rapid electrification of automotive industry by

delivering higher performance and efficiency compared to thicker MOSFET devices.

### 1.2. Research Objectives

The project aims to find new insights and build new understanding in trench power MOSFET device fabrication that influence thin die fracture strength. Research topics are discussed below:

- Investigate the effects of different stress buffer techniques to minimize pre-stress in dies front side (e.g. nitride and polyimide).

- Influence of the die-top metal-system layout.

- Influence of trench layout and orientation respective to die bending stress.

- Interaction between trenches and metal die top system.

The second objective is to develop a test chip to evaluate new designs and materials to speed up the research and development in semiconductor manufacturing.

### 1.3. Approach

Most of the current die strengthening strategies in the industry optimize or improve back-end processing of thin chips to ensure robust yield from wafer thinning and sawing to assembly and packaging. This project focuses on improving die strength from a front-end approach (device fabrication process) by making dies stronger to stress handling from die frontside.

- The first approach is to realize different test chip designs and platform to evaluate die strength.

- Investigate with new materials such as polyimide as die top materials for their potential application as stress buffer.

- Fabricate test power MOSFETs with high sensitivity. These devices will be close mechanical copy of actual trench MOSFETs.

- Wafer thinning and sawing of processed wafers to obtain ultrathin dies ( $<50~\mu$ ) to induce high sensitivity for strength tests. At present, commercially available device thickness is  $>75~\mu$ .

- Measurement of ultra-thin die strength is realized using three-point bending strategy. Obtained test

data analyzed using Weibull and 5-sigma limit analysis for characterizing bending strength of different die designs.

The mask design was made using L-edit software by Tanner tools. The dummy power MOSFETs are fabricated using CMOS fabrication facility in class 100 cleanroom of EKL at TU Delft . Wafer thinning and dicing was supported by NXP sample service center. Three-point bending for die strength characterization is done in faculty of PME, TU Delft using DMA tool. In some instances, the project required new process technologies and recipes to be developed to deliver comparable samples which are close to industry manufactured power MOSFET.

Figure 1.4: Different stages in thin die robustness investigation

We omit complexity such as the device electrical functionality, different trench profiles and aspect ratios for

1.4. Outline 4

gate and source areas. This was replaced by one common trench profile and aspect ratio for both regions. Silicon doping is also removed from the process and investigation is purely focused on the geometrical aspects of trench layout and die top system. The experimental results will then be used to propose design improvements for potential implementation in new chip designs and front-end manufacturing.

### 1.4. Outline

The outline of this thesis is as follows: In chapter 2, a bird's eye view of existing semiconductor process strategies, materials to strengthen thin dies are discussed. Chapter 3 highlights different design of mask layers used for lithography in fabrication process of power MOSFETs. A design of experiment is also formulated to support different designs for same process layers. In chapter 4, various fabrication processes undertaken for making test power MOSFETs using the EKL cleanroom facilities are discussed. The chapter briefly explains each of the process step and their challenges.

Following this, chapter 5 contains the back-end processing of the processed silicon test power MOSFETs. Strategies and challenges involved in wafer thinning and singulation are discussed. In chapter 6 the singulated dies are measured for their fracture strength using three-point bend test and data is analyzed using weibull analysis. Chapter 7 consists of project summary along with conclusions and recommendations.

# 2 LITERATURE OVERVIEW

### 2.1. Chapter introduction

This chapter highlights different strategies used in semiconductor industry today to improve mechanical robustness of thin dies. The majority of die-strengthening techniques are implemented in the semiconductor chip's back-end process stage. This includes strategies in grinding, dicing, die pick-up and place where traditional methods were found to inflict more damage to dies on top of their existing stress from front-end device fabrication. Novel materials for die top strengthening and an outlook on a new die strength measurement technique for ultra thin dies ( < 50  $\mu m$ ) are also discussed later in the chapter)

### 2.2. Die strengthening dicing techniques

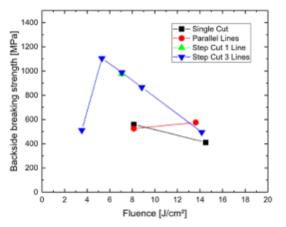

Dicing of thin silicon dies with traditional dicing technique like mechanical dicing results in increased chipping at the die edges which negatively influences the die mechanical stability. Dicing via ultrafast laser with ultra short pulses is found to enhance die strength under specific operating conditions like lowering pulse energy, scan speed and number of accumulated fluences (stream of particles) per scan in the process [9]. Also the backside breaking strength of dies are found higher using step cut dicing method as compared to parallel line cut and single line cut as seen in figure 2.1a.

(a) Figure shows mean backside breaking strength using different sawing techniques. Dies diced with step-cut are mechanically stronger dies compared to parallel and single cut dies [9]

(b) The above figure explains step cutting strategy which is a dual dicing process wherein first a half cut is performed, followed by a full cut. This is done to efficiently cut the wiring layer formed during the semiconductor fabrication process [7].

Dicing before thinning technique is another commonly used technique which promotes greater robustness than traditional dicing after grinding process [4, 22]. This technique minimizes edge crack and dicing marks which influence die strength substantially [15, 27, 22].

### 2.3. Post grinding wafer stress relief techniques:

Wafer thinning process is commonly used to reduce the total wafer thickness by removing silicon from backside using grinding technique [18]. Grinding the wafers have found to induce a lot of stress and warpage to thin silicon wafers. A stress relief technique used to remove this damage layer is backside wet chemical etching or Chemical Mechanical Polishing (CMP) [23].

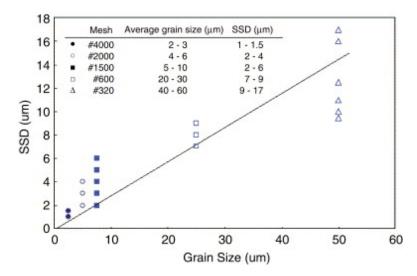

As the strength of the singluated dies is also found correlated to its backside roughness. Using a finer grain size grinding wheel for backside grinding can help minimize this backside roughness and reduce the risk of failure caused by it. Figure below shows the influence of grinding wheel type on the backside roughness

**Figure 2.2:** The above graph shows the correlation between the grain size of the grinding wheel to the wafer backside roughness [20, 21]

### 2.4. Die pick-up and place optimization

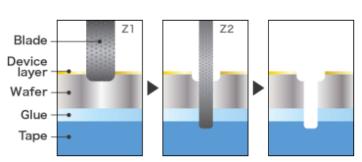

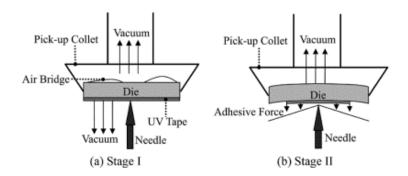

Dies need to be singulated for packaging, post grinding and dicing process. It requires die to be successfully picked up, without any damage from the carrier foil where the diced dies are attached. Die-cracks during pick-up of ultra-thin, high aspect ratio dies is one of the major challenges to robust yield in assembly process. In industry this process is facilitated using automated die pick-up and place tool. An unoptimized process can lead to increased risk of die breakage or pick-up failure, leading to unusable damaged dies. Some of the steps undertaken to optimize this process are discussed below

- Optimize collet (where the die sticks after de-attaching from wafer) shape and push-down force applied on the die during the pick up.

- Ejection needles can result in localised damage on die. Needle positions and size used for pushing the die from below the foil are optimized to minimize their negative impact on thin die pick-up

- Thin dies are found to have an increased adhesion with dicing foil which leads to an increased pull-force [5]. Very low adhesive UV foils are thus required for die pick-up process.

**Figure 2.3:** The above figure shows two stages in the die picking process, Stage 1 where collet pushes down to contact the die and applies vacuum; Stage 2 where the needle raises up to push the die and tape beneath move upwards and peels the tape from die. This is followed by collet pulling the die up under vacuum pressure [19]

Ejectorless die pick-up process eliminates the use of ejector pins to achieve robust pick-up of high aspect ratio thin die at the cost of reduced throughput [29]

### 2.5. Novel material for die top strengthening

Polymers were investigated to support the die top as buffer layer for mechanical robustness. Polymers like polyimide have unique properties suitable for this strengthening like

- High tensile strength over wide temperature range ( -270 °C to 300°C)

- Excellent resistance to stress cracking

- High glass transition temperature up to 400°C

- · Minimal thermal expansion

- Good processability compatible with current silicon based semiconductor fabrication.

Polyamide-imide (PAI) is a polymer which shows properties of both polyimide and polyamide as well. Torlon, a PAI from manufacturer Solvay promises to exhibit metal like performance at elevated temperatures as it can retain its toughness to resist cracking at higher temperatures. As per manufacturer, Torlon has the highest strength and stiffness than any commercial thermoplastic. This property of PAI polymer makes it an ideal candidate for its application as stress buffer layer for die top strengthening. In the figure 2.4, key properties like coefficient of thermal expansion (CTE) and material toughness is compared between Torlon (PAI) and other materials.

### Coefficient of Linear Thermal Expansion (ASTM D696)

# 18 15 15 16 3 0 Torlon\* Torlon\* Torlon\* Torlon\* 4203L Aluminum 2017, 7075 Copper Bronze Stainless Carbon steel (a)

### Toughness and Impact Strength (ASTM D256)

**Figure 2.4:** Figure (a) shows histogram comparison between Torlon and metals where Torlon 7130 shows minimal thermal expansion; (b) shows histogram comparison between polymers for their toughness and Impact strength where Torlon is more than two times stronger than other polymers [34]

### 2.6. Cantilever bending test for ultra-thin die strength measurement