### Technische Universiteit Delft Faculteit Elektrotechniek, Wiskunde en Informatica Delft Institute of Applied Mathematics

Het versnellen van CONTACT-programmatuur met behulp van de Graphics Processing Unit.

Engelse titel:

Speeding-up the CONTACT package by means of the Graphics Processing Unit.

Verslag ten behoeve van het Delft Institute for Applied Mathematics als onderdeel ter verkrijging

van de graad van

$\begin{array}{c} {\rm BACHELOR~OF~SCIENCE} \\ {\rm in} \\ {\rm TECHNISCHE~WISKUNDE} \end{array}$

door

MICHIEL DE REUS

Delft, Nederland Augustus 2010

Copyright © 2010 door Michiel de Reus. Alle rechten voorbehouden.

### BSc verslag TECHNISCHE WISKUNDE

"Het versnellen van CONTACT-programmatuur met behulp van de Graphics Processing Unit."

(Engelse titel: "Speeding-up the CONTACT package by means of the Graphics Processing Unit.")

MICHIEL DE REUS

Technische Universiteit Delft

**Begeleiders**

Prof.dr.ir. C. Vuik Dr.ir. E.A.H. Vollebregt

Overige commissieleden

Dr. J.G. Spandaw

Augustus, 2010 Delft

## **Preface**

As the final part of the bachelor programme Applied Mathematics at Delft University of Technology, a bachelor project must be completed. This thesis is the result of one semester of research in the field of GPU computing. Being a mathematics student, numerical analysis has my interest and I also have a lot of affinity with computer science. This is the reason why this particular project, 'Speedups of the CONTACT-software through the GPU', immediately took my interest. GPU computing makes it possible to do floating point calculations at very high speeds. The biggest problem is that the algorithms have to be suitable for the tasks a GPU can perform, which in practice means they have to be adapted quite a lot. The speedup is also highly dependent on the scale the algorithm can be parallelized. Because of the fact this field is relatively new, it took my special interest.

In addition this was one of few projects in cooperation with a company, which, I think, also contributes to the value of it. The company I worked with is VORtech BV. VORtech is situated in Delft, and is a combination of a software house and an engineering firm in applied mathematics. They combine a thorough knowledge of mathematical modeling, simulation techniques and computational algorithms with state-of-the-art software development methods. VORtech spun off from Delft University of Technology in 1996. Since then, it has seen a steady development, which still continues to this day. They service a broad range of customers, including both government departments and many commercial clients. VORtech supports the CONTACT computer programme that was developed by professor J.J. Kalker at Delft University of Technology. This software is considered to be an accurate model for contact mechanics and is used in various application fields. VORtech finances an active research programme to further extend and improve the software.

I want to specially thank professor Vuik and Edwin Vollebregt for guiding me through the project. Edwin is one of the founders of VORtech, and has a lot of knowledge of the CONTACT programme. Whenever I had questions about the algorithms involved, he helped me out. Professor Vuik helped me with the more general numerical issues, and the programming on the GPU in general. Furthermore the feedback they gave on my drafts helped me to improved the final result. A final word of thanks to all the people who posted on the CUDA GPU Computing forums of NVIDIA<sup>1</sup>. They helped me solving a lot of minor issues in a short amount of time.

<sup>&</sup>lt;sup>1</sup>CUDA GPU Computing Subforums: http://forums.nvidia.com/index.php?showforum=62

# Contents

| 1        | Pro  | oblem formulation             |    |  |  |  |  |  |  |

|----------|------|-------------------------------|----|--|--|--|--|--|--|

| <b>2</b> | The  | he frictional contact problem |    |  |  |  |  |  |  |

|          | 2.1  | One-dimensional grid          | 12 |  |  |  |  |  |  |

|          | 2.2  | Two-dimensional grid          | 13 |  |  |  |  |  |  |

|          | 2.3  | Normal contact problem        | 14 |  |  |  |  |  |  |

|          |      | 2.3.1 Conjugate Gradients     | 15 |  |  |  |  |  |  |

|          | 2.4  | Tangential contact problem    | 16 |  |  |  |  |  |  |

| 3        | CUI  | DA                            | 19 |  |  |  |  |  |  |

|          | 3.1  | Historical background         | 19 |  |  |  |  |  |  |

|          | 3.2  | The programming model         | 20 |  |  |  |  |  |  |

|          | 3.3  | Lay-out of the device         | 21 |  |  |  |  |  |  |

|          | 3.4  | Extension of the C language   | 23 |  |  |  |  |  |  |

|          | 3.5  | Compute capability            | 24 |  |  |  |  |  |  |

|          | 3.6  | Different memory types        | 24 |  |  |  |  |  |  |

|          |      | 3.6.1 Global memory           | 25 |  |  |  |  |  |  |

|          |      | 3.6.2 Shared memory           | 27 |  |  |  |  |  |  |

|          |      | 3.6.3 Registers               | 32 |  |  |  |  |  |  |

|          | 3.7  | Timing                        | 32 |  |  |  |  |  |  |

|          | 3.8  | Accuracy                      | 33 |  |  |  |  |  |  |

| 4        | Mat  | Matrix-vector products 35     |    |  |  |  |  |  |  |

|          | 4.1  | Direct implementation         | 35 |  |  |  |  |  |  |

|          | 4.2  | Using shared memory           | 39 |  |  |  |  |  |  |

|          | 4.3  | Results                       | 42 |  |  |  |  |  |  |

|          |      | 4.3.1 Direct implementation   | 42 |  |  |  |  |  |  |

|          |      | 4.3.2 Shared Memory           | 43 |  |  |  |  |  |  |

| 5        | Inne | er products                   | 49 |  |  |  |  |  |  |

|          | 5.1  | -                             |    |  |  |  |  |  |  |

|          | 5.2  | GPU Implementation            | 51 |  |  |  |  |  |  |

|          |      | 5.2.1 Sum reduction           | 53 |  |  |  |  |  |  |

|          | 5.3  | Results                       | 58 |  |  |  |  |  |  |

|          |      | 5.3.1 CPU implementation      | 58 |  |  |  |  |  |  |

|          |      | 5.3.2 GPU implementation      | 59 |  |  |  |  |  |  |

8 CONTENTS

| 6            | Con | clusio | ns & recommendations     | 63   | 3 |

|--------------|-----|--------|--------------------------|------|---|

|              | 6.1 | Matrix | x-vector multiplication  | . 63 | 3 |

|              | 6.2 | Inner  | products                 | . 63 | 3 |

| $\mathbf{A}$ | Sou | rce co | øde                      | 65   | 5 |

|              | A.1 | Matrix | x-vector multiplication  | . 65 | 5 |

|              |     | A.1.1  | CPU implementation       | . 65 | 5 |

|              |     | A.1.2  | GPU implementation       | . 67 | 7 |

|              |     | A.1.3  | Utility functions        | . 73 | 3 |

|              | A.2 | Inner  | product calculation      | . 74 | 1 |

|              |     | A.2.1  | CPU implementation       | . 74 | 1 |

|              |     | A.2.2  | Sum reduction algorithms | . 79 | ) |

|              |     | A.2.3  | GPU implementation       | . 82 | 2 |

|              |     | A.2.4  | Utility functions        | . 88 | 3 |

## Chapter 1

## Problem formulation

CONTACT is a computer programme designed to calculate deformations in three-dimensional frictional contact problems. The programme is based on algorithms designed by professor J.J. Kalker.<sup>1</sup>

When two surfaces roll over each other, both surfaces deform due to tractions in the normal and tangential directions. The three-dimensional frictional contact problem determines the contact area of the two surfaces, and divides this area into a slip and an adhesion area. This gives information on which are the wearing parts of the surfaces. For example this information is used to determine where abrasion takes place on a train wheel and rail.

Figure 1.1: Train wheel on the rail, from www.emeraldinsight.com.

To determine which points are in adhesion and which are in slip, an iterative process makes sure all deformations are in equilibrium, under the condition of certain non-linear frictional constraints.

$<sup>^1{\</sup>rm See~http://www.kalkersoftware.org/}$  for more information on the programme and papers describing the used algorithms.

During the iterative process, the Conjugate Gradients method and a certain Gauss-Seidel method are used. The first method consists of a full matrix-vector product during each iteration, the second method consists of a single inner product during each iterations. It are these operations that we will investigate in detail during this project.

The GPU is known for its parallel power, since it consists of a lot of seperate processors, each capable of performing floating point operations simultaneously. When calculating matrix-vector products and inner products, most calculations are independent of each other, and therefore might be suitable for the GPU. The goal of this Bachelor project is to investigate possible speedups by using the parallel arithmetic capabilities of the Graphics Processing Unit, instead of just the Central Processing Unit, when calculating these matrix-vector products and the inner products.

## Chapter 2

# The frictional contact problem

The general problem considered is the three-dimensional frictional contact problem with homogeneous, but not necessarily the same, materials. In this problem, two surfaces roll over each other. The contact area is assumed to be concentrated. This means that the contact area is much smaller than the typical size of the objects. The contact surfaces can then be taken flat. The forces exerted on both surfaces will result in deformation of both materials. The degree of deformation depends on the materials used and the total force exerted.

During the solution process both the normal and the tangential contact problem are solved. The procedure is an iterative one, which will alternate between solving the normal contact problem and solving the tangential contact problem, using the solution of the last problem solved as input for the next. This process is repeated until all the forces are in balance, or in practice, until some tolerance is met. During this process, the contact area is updated continuously, resulting, in the end, in the true contact area.

The main equation, governing the deformations is

$$u_i(\underline{x}) = \sum_j \int_C A_{ij}(\underline{x}, \underline{y}) p_j(\underline{y}) ds, \text{ for } i = x, y, n.$$

(2.1)

$A_{ij}(\underline{x},\underline{y})$  is the influence coefficient of the force at  $\underline{y}$  in the direction j, on the deformation at  $\underline{x}$  in the direction i.  $p_j(\underline{y})$  is the traction, or force per unit area, at  $\underline{y}$  in the direction j, and ds is the surface element.  $u_i(\underline{x})$  is the resulting deformation at  $\underline{x}$  in the direction i. In general the possible directions are x, y and n. The integral is taken over C, the contact area. Of course points outside the contact area will not contribute to the deformation. C can also be taken as the potential contact area, setting  $p_j(y) = 0$  outside the contact area.

One important property of the influence coefficients is that they are invariant under translation. This means that points with the same relative position to each other will have the same influence on each other. This makes it possible to reduce the number of independent influence coefficients dramatically, resulting in less memory usage. The details about the storage structure will be discussed later.

## 2.1 One-dimensional grid

The first step to solve the problem, is to discretize the contact area. If we look at the one-dimensional problem, the contact area is an interval  $[0, L] \subseteq \mathbb{R}$ . Equation 2.1 will change to

$$u(x) = \int_0^L A(x, y) p(y) dy.$$

(2.2)

This equation needs to be discretized in order to perform the calculations. The interval is divided into nx equal-sized intervals  $x_I$ ,  $1 \le I \le nx$ , of size  $\delta x = \frac{L}{nx}$ . The tractions are assumed to be constant in each interval, and the influence coefficient is determined by integrating over the inverval. The integral in Equation 2.2 changes to a sum over all the intervals. The resulting sum is

$$u(x_I) = \sum_{I=1}^{nx} A(x_I, x_J) p(x_J), \text{ for } 1 \le I \le nx.$$

(2.3)

This sum can be written as a matrix-vector product. If **u** and **p** are defined so that  $u_I = u(x_I)$  and  $p_I = p(x_I)$ , and the matrix A is given by  $A_{IJ} = \int_I A(x_I, y) \cdot dy$ , then Equation 2.3 can be written as

$$\mathbf{u} = A\mathbf{p}.\tag{2.4}$$

As stated earlier, influence coefficients are invariant under translations. This means, for the one dimensional case, that  $A(x_I, x_J) = A(x_K, x_L)$  if  $x_I - x_J = x_K - x_L$ . So an array  $B_K$  can be defined by

$$B_K = B_{J-I} = A(x_I, x_J), \text{ for } -n+1 \le K \le n-1.$$

(2.5)

The total number of independent influence coefficients will now be 2n-1. Remark that in general  $B_K \neq B_{-K}$ . The total number of independent influence coefficients is much smaller than without this symmetry, 2n-1 instead of  $n^2$ . For n=128 for example, the number of independent influence coefficients is 255 instead of 16384. In the two dimensional case the difference will be even bigger.

The original sum can now be replaced by

$$u_I = \sum_{J=1}^n A_{IJ} p_J = \sum_{I=1}^n B_{J-I} p_J, \text{ for } 1 \le I \le n.$$

(2.6)

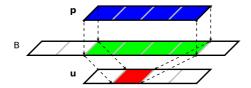

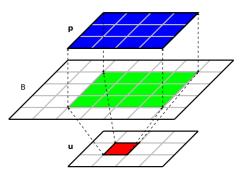

This will be used later, when implementing the calculations on the computer. Geometrically this sum can be visualized by stretching the B vector from left to right, and aligning the  $\mathbf{p}$  vector above it, with the rightmost element of  $\mathbf{p}$  shifted I-1 elements to the left and then taking the inner product of elements aligned above each other. See Figure 2.1 for an example. The blue elements of  $\mathbf{p}$  are multiplied with the green elements of A, aligned above each other, and after addition, this results in the red element of  $\mathbf{u}$ .

Figure 2.1: Example of an one dimensional inner product.

## 2.2 Two-dimensional grid

In the two-dimensional case a rectangular potential contact area is defined. This potential contact area is divided into  $nx \times ny$  rectangular elements of size  $\delta x \times \delta y$ . The elements will be labeled by  $\underline{x}_I$ , with  $I = (iy-1) \times nx + ix$ . ix and iy represent the x and y coordinates of a grid point. The tractions now have three components, two components in the plane of the grid and one component in the normal direction. For simplicity we will only consider the normal direction. The tangential tractions will be covered later. This does not affect the process, because during the solving of the normal contact problem, the tangential effects are assumed to be constant, and are covered by the term  $h_I^*$ , as we will see later. Again the tractions and influence coefficients are assumed to be constant in each particular element. This will change the integral over the potential contact area to a sum over the individual elements, so Equation 2.1 will change to

$$u(\underline{x}_I) = \sum_J A(\underline{x}_I, \underline{x}_J) p(\underline{x}_J). \tag{2.7}$$

$A(\underline{x}_I, \underline{x}_J)$  is the influence coefficient of the traction at element  $\underline{x}_J$  on element  $\underline{x}_I$ . If we again define  $A_{IJ} = \left( \int_J A(\underline{x}_I, \underline{x}') d\underline{x}' \right) \cdot \delta x \cdot \delta y, \ p_J = p(\underline{x}_J)$  and  $u_I = u(\underline{x}_I)$ , this sum can be written as

$$u_I = \sum_{J} A_{IJ} p_J.$$

(2.8)

As in the one dimensional case, the influence coefficients are invariant under translation. If the source and the target have the same relative position, the influence coefficients are equal. This means that  $A_{IJ} = A_{KL}$  if ix - jx = kx - lx and iy - jy = ky - ly. As in the one dimensional case, an array B can be introduced so that

$$B_K = A_{I,J} \Rightarrow B_{(kx,ky)} = A_{(ix,iy),(jx,jy)}, \tag{2.9}$$

with kx = jx - ix and ky = jy - iy. Remark that K is no longer a grid point, but a vector, representing the position of grid point J relative to I. Because  $ix, jx \in \{1, ..., nx\}$ , we have  $kx \in \{-(nx-1), ..., 0, ..., nx-1\}$ , which results in a total number of possible values for kx of 2nx-1. In the same way we have  $iy, jy \in \{1, ..., ny\}$ , so the total possible values of ky is 2ny-1. The dimensions of B are therefore  $(2nx-1) \times (2ny-1)$ . So the number of independent influence

coefficients is  $(2nx-1) \times (2ny-1)$  instead of  $(nx \cdot ny)^2$ . Equation 2.8 can now be written as a matrix-vector product,

$$\mathbf{u} = A\mathbf{p},\tag{2.10}$$

exactly as in the one-dimensional case.

There is also a geometric interpretation in terms of B and  $\mathbf{p}$ . If B and  $\mathbf{p}$  are represented as two dimensional arrays, the different inner products of the matrix-vector product can be calculated by aligning  $\mathbf{p}$  on top of B, and choosing the appropriate two-dimensional translation. So  $\mathbf{p}$  is shifted over B in two directions.  $u_I$  can be calculated by aligning  $\mathbf{p}$  so that  $p_I$  is on top of  $B_0$ . Values of B and  $\mathbf{p}$  on top of each other are now multiplied, and the total sum is the inner product needed in the matrix-vector product. See Figure 2.2 for an example. As in the one dimensional case, the blue elements of  $\mathbf{p}$  are multiplied with the green elements of B, aligned directly above each other, and after addition, this results in the red element of  $\mathbf{u}$ .

Figure 2.2: Example of a two dimensional inner product.

## 2.3 Normal contact problem

With the grid defined, the normal contact problem can now be solved.  $e(\underline{x})$  is defined as the distance between the two bodies, in deformed state, and  $h(\underline{x})$  is the distance in undeformed state. As stated earlier  $u(\underline{x})$  is the deformation in the normal direction, so

$$e(\underline{x}) = h(\underline{x}) + u(\underline{x}). \tag{2.11}$$

As stated at the beginning of this section, the normal and tangential contact problem are solved in an iterative way, alternating between the two. Because of this, during the solving process of the normal contact problem, tangential tractions are assumed to be constant. In practice this means that deformations due to tangential tractions can be absorbed in the term representing the distance in undeformed state. We will therefore write  $h^*(\underline{x})$  instead of  $h(\underline{x})$ . This results in

$$e(x) = h^*(x) + u(x). (2.12)$$

If  $e(\underline{x}) > 0$  the traction is zero since there is no contact, so  $p(\underline{x}) = 0$ . If  $e(\underline{x}) \le 0$ , there is a traction acting. The deformation as function of the traction is now given by Equation 2.1.

For the discretized problem, two sets of grid points are defined. Grid points for which  $e_I > 0$  are set 'inactive'. At these points, the bodies are not in contact, so there is no traction. Points for which  $e_I \leq 0$  are set 'active'. At these points there is contact and thus a traction. The set of active points is C, the contact area, and the set of inactive points is E, the exterior area. Note that these sets will change during the iterations. The problem we now want to solve, is to find the active grid points, and the tractions  $p_I$  at these grid points, so that the distances in deformed state are zero for active grid points. In this case the bodies will only be in contact at the surfaces, and they will not interpenetrate each other, which, of course, would be nonsense in reality. Equation 2.12 will change to

$$e_I = h_I^* + u_I = 0, (2.13)$$

for all active grid points  $I \in C$ .

The deformations  $u_I$  are given by Equation 2.8. If we substitute this in Equation 2.13, we get

$$e_I = h_I^* + \sum_J A_{IJ} p_J = 0$$

, for all  $I \in C$ . (2.14)

Remark that it does not matter whether the sum is taken over all grid points J, or  $J \in C$ , since  $p_J = 0$  if  $J \notin C$ . We can write this equation as

$$A\mathbf{p} = -\mathbf{h}^*. \tag{2.15}$$

We now have a large linear system in  $p_J$ , for all active grid points  $I \in C$ . This system is solved by the iterative Conjugate Gradients method is used instead. This method will iterate, until the relative norm of the update of the solution vector is within a certain tolerance. When this tolerance is met, the iteration is stopped and the sets of active and inactive grid points are updated. From the resulting  $p_I$ , new  $u_I$  and  $e_I$  can be calculated. All grid points  $I \in C$  with  $p_I < 0$  are moved to the exterior set E, and all grid points  $I \in E$  with  $e_I < 0$  are moved to the contact set C.

The normal contact problem is iterated until the contact area is constant, so when C and E do no longer change.

For the first iteration of the Conjugate Gradient method, a starting vector is needed. It is assumed that  $p_I^{(0)} = 0$  for all I in the potential contact area, so from Equation 2.14 we have

$$e_I^{(0)} = h_I^*. (2.16)$$

#### 2.3.1 Conjugate Gradients

The Conjugate Gradients method works only for positive semi-definite systems. In general, the system we get from the normal problem possesses this property, so the method will converge. The most important property of the Conjugate Gradients method, from our point of view, is that during each iteration a full matrix-vector product has te be calculated, which in general is very

time-consuming. There are several possible implementations of the iterative Conjugate Gradients method. We have for example Algorithm 2.1 from [3].

Algorithm 2.1 Iterative conjugate gradients algorithm.

```

\mathbf{u}_0 := 0

\mathbf{r}_0 := \mathbf{b}

\mathbf{for} \ k = 1, 2, ... \ \mathbf{do}

\mathbf{if} \ k = 1 \ \mathbf{then}

5: \mathbf{p}_1 = \mathbf{r}_0

\mathbf{else}

\beta_k := \frac{\mathbf{r}_{k-1}^T \mathbf{r}_{k-1}}{\mathbf{r}_{k-2}^T \mathbf{r}_{k-2}}

\mathbf{p}_k := \mathbf{r}_{k-1} + \beta_k \mathbf{p}_{k-1}

\mathbf{end} \ \mathbf{if}

10: \alpha_k := \frac{\mathbf{r}_{k-1}^T \mathbf{r}_{k-1}}{\mathbf{p}_k^T A \mathbf{p}_k}

\mathbf{u}_k := \mathbf{u}_{k-1} + \alpha_k \mathbf{p}_k

\mathbf{r}_k := \mathbf{r}_{k-1} - \alpha_k A \mathbf{p}_k

\mathbf{end} \ \mathbf{for}

```

As can be seen on lines 10 and 12, the matrix-vector product  $A\mathbf{p}_k$  has to be calculated. In Chapter 4 this matrix-vector product is discussed in detail.

## 2.4 Tangential contact problem

The tangential contact problem is defined through the friction law. The discretization is similar to the normal contact problem, resulting in the same grid as in Section 2.2. Since the constraints are non-linear, the Conjugate Gradients method cannot be applied. A specific version of the Gauss-Seidel method is used, to solve the non-linear problem.

During each iteration of the Gauss-Seidel like algorithm, the frictional constraints are taken care of, by shifting grid points from the slip area to the adhesion area and vice versa. During each iteration, four inner products need to be calculated. These inner products determine the total slip distance in the x and y direction in element I, due to the tractions in the x and y direction. There is also an additional term, consisting of the distance due to tractions in the normal direction and the rigid shift of the bodies.

The total deformation in both the x and y direction for grid point I is given by

$$\begin{cases}

s_{Ix} = W_{Ix}^* + \sum_J A_{IJ}^{xx} p_{Jx} + \sum_J A_{IJ}^{xy} p_{Jy} \\

s_{Iy} = W_{Iy}^* + \sum_J A_{IJ}^{yx} p_{Jx} + \sum_J A_{IJ}^{yy} p_{Jy}.

\end{cases}$$

(2.17)

We use the same indexing as in Section 2.2, so we have  $I = (iy - 1) \cdot nx + ix$  and  $J = (jy - 1) \cdot nx + jx$ .

The influence coefficients have the same translational invariance as in the normal contact problem, so again we can define matrices B, with the geometric

interpretation explained in Section 2.2. This will change Equation 2.17 to

$$\begin{cases} s_{Ix} = W_{Ix} + \sum_{J} B_{K}^{xx} p_{Jx} + \sum_{J} B_{K}^{xy} p_{Jy} \\ s_{Iy} = W_{Iy} + \sum_{J} B_{K}^{yx} p_{Jx} + \sum_{J} B_{K}^{yy} p_{Jy}, \end{cases}$$

(2.18)

with kx = jx - ix and ky = jy - iy. Remark that the inner products stated in Equation 2.18 are exactly the inners product from Figure 2.2. In Chapter 5 the inner products are discussed in detail.

## Chapter 3

## **CUDA**

In this chapter we will first review some historical background behind scientific computing on graphics cards, after which the way CUDA works will be described in more detail. The main goal is that the implementations in the next chapter can be understood.

## 3.1 Historical background

Nowadays almost all desktop computers come with a graphics accelerating card. These cards are specially designed to perform the calculations necessary to render three-dimensional images. Because most of these calculations can be performed independently of each other, these cards have a highly parallel character. The same calculations are performed on different sets of data. For this reason, a lot of space on the chip, normally used for control logic (fetching and decoding instructions etcetera), can be dedicated to performing calculations. This combined with a huge market demand for better and faster graphics cards, especially from the video game industry, resulted today in high performance cards, with calculation performance comparable with supercomputers. Figure 3.1 illustrates the exponential growth of the graphics card performance, compared to general processors. In the figure, NVIDIA graphics cards are compared to Intel processors.

Figure 3.1: Intel CPU's compared to NVIDA GPU's, from [1]

In the past, all the stages performed by the graphics card were hardwired. These were the so-called fixed-function graphics pipelines. The application created the input data, and the graphics card performed a set of fixed operations on these data, resulting ultimately in a three-dimensional picture on the screen. One example is the stage applying the textures to the objects, built up from a large set of triangles.

This was the way graphics cards operated from the early 1980s to the late 1990s. During this time, the different stages were optimized, and new graphical algorithms resulted in ever increasing performance. But by the graphics industry growing larger, the application developers became more and more sophisticated, and the demand for more features grew with them. These demands could not be realized using the built-in fixed functions, so the next step was a programmable processor.

In 2001 NVIDIA took the first step with their GeForce 3. The developers could access the instruction set of the floating-point vertex engine. At the same moment, DirectX and OpenGL came with new releases to use these new features, allowing developers to use their own algorithms. The most interesting stages to be programmable were the stages where the different render algorithms take place. These are the stages using the most computational power, in particular, the vertex shader and pixel shader.

Because these stages performed so well on independent floating-point operations, it quickly took the attention of scientists in the field of scientific computing. They saw possibilities to port certain algorithms, gaining a huge performance boost for a relative low price. The problem was that, because the graphics cards were meant for graphical purposes, the interface was not suitable for general problems. So scientific problems needed to be adapted to 'graphical problems', meaning for example, that data needed to be translated to the same format as how vertices are stored on the GPU. Also the memory interface did not allow to read from, or write to random locations. So it took a huge effort to program the graphics card for general purposes. Because of these difficulties, only a few scientists demonstrated some useful applications.

To make scientific computing on the graphics card more accessible, NVIDIA introduced CUDA in November 2006. CUDA is an acronym for Compute Unified Device Architecture, and gives developers the opportunity to program the GPU using an extended version of the C programming language. Since the hardware architecture has to support CUDA, only the more recent models of the NVIDIA GPU's are compatible with CUDA.

## 3.2 The programming model

In the CUDA programming model, a distinction is made between the host and the device. The host consists of the CPU, together with the internal memory<sup>1</sup>. The device consists of the GPU, with different kinds of memory residing on the graphics card. When writing a CUDA program, separate code is written to run on the host and the device. The host code initializes the device for performing

<sup>&</sup>lt;sup>1</sup>We will call the traditional internal memory the host memory.

the calculations. This means memory on the device is allocated and data needed for the calculations is transferred from the host memory to the device memory. After this is done, the host program calls a function intended to run on the device, a so-called *kernel*. It is the kernel that performs the calculations, using the data that is transferred earlier.

During the execution of a program, it is possible to invoke the same kernel more than one time, or to invoke different kernels. To every kernel call, a specific *grid* is attached. A grid is set of *blocks*, with a one- or two-dimensional structure, defined by the programmer. Every block consists of a set of *threads*, which are organized in a one-, two- or three-dimensional structure, again this structure is defined by the programmer. This hierarchy is important, because threads in different blocks are more limited to access the same memory locations than threads in the same block. Threads can identify themselves by built-in variables, containing the index of the block they are part of, and their own index, inside the block they are part of. This gives for example a mechanism to determine which memory index should be referenced. A more detailed explanation will follow later.

Another important consequence of the way threads are divided into blocks, is the way the threads are scheduled by the device. To better understand this, the lay-out of the device needs to be explained.

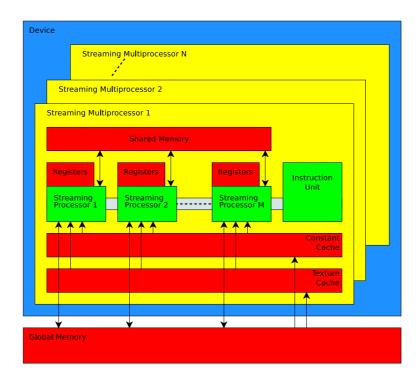

## 3.3 Lay-out of the device

A device consists of different parts. Figure 3.2 shows an overview. Every device is equipped with a number of *Streaming Multiprocessors*, and a certain amount of *global memory*. Multiprocessors are processing units operating independent of each other. The number of multiprocessors depends on the device model and can vary from 1 on the older notebook models to 120 on the high-end Tesla models. The total amount of global memory also varies, usually between 512 MiB for the older models and 2 GiB for the new high-end ones. A small portion of the global memory is accessible through the constant cache and the texture cache. These parts are usually called the *constant memory* and *texture memory*. These parts cannot be written to from the device. Because they are cached, memory read transactions from the same locations have a much lower latency than the normal global memory. The constant memory has a capacity of 16 KiB (per multiprocessor). The constant memory and texture memory will not be used during this project.

Every multiprocessor consists of 8 Streaming Processors, an Instruction Unit, 16 KiB of shared memory and a number of registers, each capable of storing 4 bytes of data. The total number of registers depends on the device and can vary between 8192 and 16384. Since the shared memory and registers are on-chip, they can be accessed very fast. However their size is very limited, because they are used by all the threads active on that multiprocessor. The differences between the different kinds of memories will be explained in detail later.

Since each multiprocessor has only one Instruction Unit, every processor in a multiprocessor executes the same instructions, and thus calculations, at the

Figure 3.2: Layout of a typical GPU, adapted from [1]

same moment. The data on which these instructions are executed can of course differ. This model is called SIMT (Single-instruction multiple-threads) by NVIDIA. It is very similar to the SIMD-model (single-instruction multiple-data).

Now the role of threads and blocks can be explained. During execution, up to 8 blocks are assigned to a particular multiprocessor. These are called the active blocks. The actual number of blocks can be lower, depending on the number of threads per block and the amount of memory used per block. For example older models have a maximum of 768 active threads, so if the number of threads per block is 128, there are only 6 active blocks per multiprocessor. Furthermore if each block uses 4 KiB of shared memory, there will be only 4 active blocks, due to the limited amount of shared memory. For the use of registers the same applies. The reason we want as much active threads as possible, is that because when one set of threads is waiting until some high latency operation is finished, the (hardware) scheduler can assign a different set of threads for execution. This way the total time spent waiting for these high latency operations will be minimized.

The occupancy is defined as the number of active threads, compared to the maximum number of active threads possible. So if we have blocks of 256 threads, we can achieve an occupancy of 1, if memory usage allows three active blocks per multiprocessor. If we only have two active blocks, because each block uses a lot resources, the occupancy will be  $\frac{2}{3}$ , since we only have 512 active threads. The threads are executed in groups, called warps. Although the number of pro-

cessors is only 8 per multiprocessor, a warp consists of 32 consecutive threads, from the same block.<sup>2</sup> This means that all 32 threads in a warp will execute the same instruction at a specific moment. One important consequence of warps executing the same instructions, is branching. When the code contains conditional statements, and the threads in a warp 'diverge', they will execute different statements. But as mentioned earlier this is not possible since there is only one Instruction Unit, so the execution will be performed sequentially. In general this will cost more execution time. When the threads converge again, execution will continue parallel. Remark that because warps consist of 32 threads from the same block, the number of threads per block should be a multiple of 32 for maximum performance.

A warp is divided in two *half-warps*. Each consisting of 16 consecutive threads. Remark that from a programmers point of view, the division of threads into warps is completely transparent. This means that for the correctness of the code, you do not have to be aware of the existence of warps. But huge performance gains can be realized when the code is designed with this division in mind.

### 3.4 Extension of the C language

As already mentioned, CUDA is an extension of the C programming language. This means that extra keywords and special syntax are added, which are then compiled by the NVIDIA compiler. Without getting into too much detail, some of these extension are discussed.

The most important part is the kernel. The kernel is the function that is executed on the device. When launching the kernel, the CUDA driver needs to know certain parameters. We will be using only three of them, the number of blocks in the grid, the number of threads per block and the amount of (dynamic) shared memory used by each block. A kernel launch has the form

```

Kernel<<<dimGrid, dimBlock, Sharedmem>>>(...);

```

Kernel is the name of the function. dimGrid and dimBlock are the dimensions of the grid and the blocks. The parameters are of type dim3, which is a structure of three unsigned integers, representing the structure of the grid and the blocks. Sharedmem is the amount of shared memory used, in bytes. The type is size\_t, which basically is an unsigned integer. The dots represent the additional arguments used by the kernel, like pointers to global memory locations, or the size of a particular array. When defining (or declaring) the kernel, the keyword \_\_global\_\_ has to be placed in front, and the type is void. So we get something of the form

```

__global__ void Kernel(...);

```

The keyword \_\_global\_\_ specifies that this function can be called from both the device and the host. It is executed on the device. Other possible keywords are

<sup>&</sup>lt;sup>2</sup>This has to do with the different pipeline stages during the executing of an instruction.

\_\_device\_\_ which means the function can be called from the device only, and is executed on the device, and the \_\_host\_\_ keyword, which means the function can be called from the host and is executed on the host. This is also the default keyword. Inside the kernel several built-in variables are accessible. These can be used by a thread to identify itself, as in calculating its unique index, and determining what the the dimensions of the grid and blocks are. The used built-in variables are threadIdx, blockIdx, blockDim and gridDim. For example the unique index of a thread in a grid can be calculated by blockIdx.x \*blockDim.x + threadIdx.x; given that blocks have a one-dimensional structure. Otherwise extra terms consisting of y and z members have to be added. One important other CUDA function that is used is \_\_syncthreads(). This function makes sure execution continues only when all threads in that particular block have reached that statement. This is important when data is shared between different threads. It ensures that memory updates are in sync. We will see the importance later on.

These are just the basic CUDA keywords used. Later on other functions will be introduced, for example when allocating memory on the device, and copying data. Also the use of shared memory will require special syntax.

### 3.5 Compute capability

To make it easy to get information on what the capabilities of a specific device are, NVIDIA assigned a 'compute capability' to every CUDA compatible device. This compute capability consists of a major revision number and a minor revision number. The major revision number defines the core architecture. The minor revision number corresponds to small improvements of the core architecture, and newly introduced features. At the moment of writing, all the cores are of major revision number 1. The minor revision numbers can vary from 0 to 3. For example only devices with compute capability 1.3 support double precision floating-point numbers. Devices with lower compute capability only support single precision floating-point numbers. Furthermore compute capability 1.2 and 1.3 have 16384 registers per multiprocessor while 1.0 and 1.1 only have 8192 registers per multiprocessor. There are also differences in the way memory accesses are 'coalesced'. We will see this later in more detail. We will not get into too much detail regarding the compute capabilities, and all the code written is compatible with the lowest compute capability 1.0.<sup>3</sup>

## 3.6 Different memory types

As mentioned earlier, there are different types of memory. In this section a detailed description of the global memory, shared memory and the registers will be given and the syntax needed to use these different memories will be

<sup>&</sup>lt;sup>3</sup>Although the code is compatible with any compute capability, there can be performance differences between different compute capabilities. For example because of different ways of memory coalescence.

explained. We will also look at the effect of the number of blocks assigned per multiprocessor due to the amount of memory used by each block and thread.

#### 3.6.1 Global memory

Of the different types of device memory, the global memory has the biggest capacity. As mentioned earlier it can range from 512 MiB to 2 GiB. For the purposes of this project this will be more than enough. The global memory is used to store the bulk of the data supplied by the host. Because this memory is not located on-chip, it has a relatively high latency. Meaning that transactions from and to the global memory will cost a lot of clock ticks and should be avoided as much as possible. Also, for maximum performance, when moving data between the host and the device, it is better to move big data chunks instead of moving multiple small data chunks.

Allocating memory, freeing memory and copying data from the host memory to the global memory on the device and vice versa is done by special CUDA API calls. These functions are invoked from the host code, so before or after a kernel is invoked. There are different kinds of functions. For moving data for example, there are synchronous and asynchronous functions available. We will be using the synchronous functions only.

All the CUDA API calls return an error code. In the case of no error, the value cudaSuccess will be returned. In case of an error, a code describing what went wrong is returned, for example cudaErrorMemoryAllocation is returned when allocating memory fails. For obvious reasons we will check these return values when a CUDA function is invoked.

Allocating memory is done by invoking the function

The location of the allocated memory is stored in \*devPtr. The second argument, size is amount of memory to be allocated, in bytes. Freeing memory is done by invoking

```

cudaError_t cudaFree( void * devPtr ).

```

where devPtr is the location of the memory chunk to be freed. Once memory is allocated, data can be copied to and from that location. This is done by the function

where dst is a pointer to the destination of the data. This can be located either in the host memory or the global memory. src is a pointer to the source of the data. This can also be either in the host or the global memory. count is the amount of data to be copied, in bytes. Finally, kind gives the direction in which

the memory has to be copied. The possible values are cudaMemcpyHostToHost, cudaMemcpyHostToDevice, cudaMemcpyDeviceToHost and

cudaMemcpyDeviceToDevice. These values speak for themselves. We will mainly use the second and third mode. Again different kinds of error codes can be returned in case of an error.

When the data is copied to the global memory, it can be accessed from within a kernel. When invoking that kernel, the location of the chunk of data (in the global memory) is passed as a pointer in the argument list of the kernel, and normal C statements can be used to access it. Remark that the global memory has one memory space, so every thread can access every location. Still the global memory should not be used to communicate between threads of different blocks. This is because the order of execution of the different blocks is not defined. Even for threads in the same block it is very important to keep an eye on synchronization issues. A thread writing to a specific memory location, can change the input of another thread, because the order of thread execution is not defined. All we know for certain is that threads in the same warp are executed simultaneously. If a programmer does not anticipate this, and does not use \_\_syncthreads() properly, this may lead to undefined results.

Special care is needed by the use of these pointers. The host memory and the global memory consist of different memory spaces, so a particular pointer points to particular locations both in the general and the global memory. When using a pointer, pointing to allocated memory in the global memory space, in the context of the host memory the results will be undefined, and an exception is probably raised. Vice versa it will lead to undefined results, since non-initialized data is used. For this reason we will be using prefixes in the names of the variables, making clear to which type of memory it points. We will use the h to point to host memory and the d to point to device memory. For example float\* hA will point to some location in the host memory, while float\* dA will point to a location in the device memory.

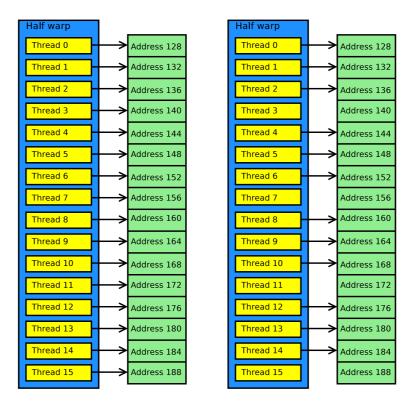

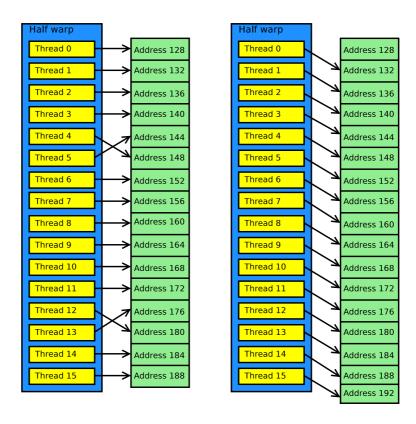

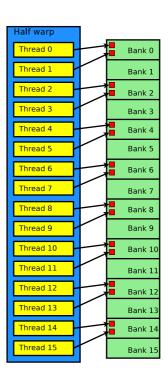

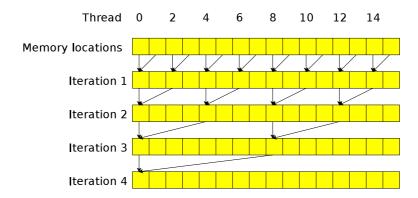

For maximum performance, it is important to use the correct alignments when moving data. For example, for device capability 1.0 and 1.1, when a half-warp, consisting of 16 threads, access consecutive 4-byte memory locations in a single 64-byte segment, aligned at a 64-byte boundary, this will result in a single memory transaction. This is called *memory coalescence*, and the memory transaction is called *coalesced*. In contrast to a non-coalesced memory transaction, for example when the alignment is incorrect. It is very important to ensure coalescing happens when possible, because it can have drastic influence on the total performance. When a memory transaction is non-coalesced, is it serialized in 16 seperate transactions. See Figure 3.3 for an example. Both access patterns are coalesced and will result in one memory transaction. In the access pattern on the right-hand side, the warp has diverged because of some conditional statement. This will lead to bandwidth loss, because some data that is read is not used, but the pattern is still coalesced.

In Figure 3.4 there are two examples of access patterns that will lead to non-coalesced memory transactions. The left access pattern is non-sequential, and will lead to 16 memory transactions on devices of compute capability 1.0 and 1.1. The right access pattern is misaligned, because the first thread does not

Figure 3.3: Examples of coalesced global memory transactions

access a location on a 64-byte boundary. This access pattern will also lead to 16 memory transactions. This illustrates that it is very important to make sure transactions are coalesced.

On devices with a higher compute capability, misaligned memory transactions will result in two memory transaction instead of 16, one for each segment data is requested from.

In the next chapter, the first CUDA implementation will show the use of the global memory. Also the effect of coalescing will be shown.

#### 3.6.2 Shared memory

The next type of memory is the shared memory. Shared memory is shared among threads of the same block. This makes it the easiest and fastest way of data exchange between threads. The current devices consist of 16 KiB shared memory per multiprocessor. This amount is shared between all the active blocks. As mentioned earlier, when blocks use a lot of shared memory, this might lead to a decrease of the number of active blocks per multiprocessor. In the case of a block exceeding the total amount of 16 KiB, the kernel will not launch at all.

The shared memory can be used in two ways, either static or dynamic. Static means that the amount of shared memory per block is known when the code is compiled and dynamic means it is only known when the kernel is invoked.

28 CHAPTER 3. CUDA

Figure 3.4: Examples of non-coalesced global memory transactions

So the total amount per block can be determined during runtime. These two different ways of using the shared memory need different syntax.

To make use of the shared memory, variables have to be declared as shared explicitly. This is done by the type qualifier \_\_shared\_\_. When using static shared memory, a variable can be declared within the kernel, with the \_\_shared\_\_ type qualifier. For example

#### \_\_shared\_\_ float values[16];

For each block a different instance of the array values will be allocated. Threads from the same block will access the same instance of values, and can read and write from and to it. As mentioned earlier, special care is needed to avoid sync issues.

When using dynamic shared memory, the total amount of used shared memory is given by the programmer as a parameter when the kernel is launched. This amount of memory is then allocated by the CUDA engine as a linear array. It is the responsibility of the programmer to make sure this linear array is divided in the correct structure. A special statement,

has to be placed in the global scope, and the kernel has to be invoked by a statement like

```

Kernel<<<dimGrid, dimBlock, Sharedmem>>>(...);

```

where Sharedmem is the desired amount of shared memory, in bytes. The CUDA engine makes sure that for each block this amount is allocated and it can be accessed by the threads through array.

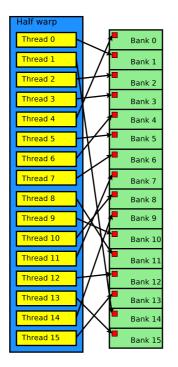

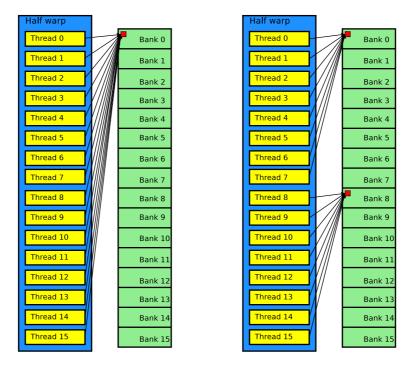

When using shared memory it is important to understand how this memory is organized for maximum performance. The total shared memory is divided into 16 memory modules, or banks. These banks can be accessed simultaneously. The memory is divided in such a way that successive 4-byte words fall in successive banks. During each cycle, each bank can deliver one 4-byte word. If multiple threads try to read different 4-byte words from the same bank, the requests are serialized, resulting in a lower performance. This is called a bank conflict. Since there are 16 banks and 32 threads in a warp, the first half-warp is served first, and then the second half-warp is served. This means that there cannot be bank conflicts between threads in a different half-warp. When accessing an array of shared memory, it is important to make sure the access pattern does not result in bank conflicts. See Figure 3.5 for an example. The left access pattern will not lead to any bank conflict, since every bank serves one word to one thread. The right access pattern will lead to a two-way bank conflict, since half of the banks have to serve two different words.

The shared memory also has a broadcast mechanism. This means that one of the words can be broadcast to all the threads in the half-warp. See Figure 3.6 for an example. The right access pattern will lead to a single memory transaction, since the word from Bank 0 will be broadcast. The left access pattern will lead to two memory transactions.

CHAPTER 3. CUDA

Figure 3.5: Examples of access patterns with and without shared memory bank conflicts: The left access pattern will not load to a bank conflict, the right access pattern will lead to a two-way bank conflict.

Figure 3.6: An example of how the shared memory broadcast mechanism works: The left access pattern will lead to one single memory transaction, while the right access pattern will lead to two sequential transactions.

When no bank conflicts occur, accessing shared memory is as fast as accessing registers.

### 3.6.3 Registers

Registers are the fastest memory (together with shared memory with no conflicts). When using registers, an instance of a variable is made for every thread. This means that when in a kernel n register variables are used, the total number of registers used per block will be  $n \times m$ , where m is the number of threads per block. It is important not to exceed the total number of registers of 8192 or 16384, otherwise the kernel will not launch. It is possible to make sure the compiler uses a maximum number of registers for the kernel. This is achieved by mapping some variables to the global memory (which in this context is called the 'local memory'). Although this might lead to more active threads, it costs a lot of extra time to access these variables.

Registers are used for variables of standard types which are declared inside the kernel. Small structures and arrays are also mapped to registers. To avoid register memory bank conflicts, the best results are achieved when the number of threads per block is a multiple of 64. These conflicts are resolved by the compiler, and the programmer has no influence on it.

## 3.7 Timing

To measure the performance of a certain implementation, time measurements have to be taken. Both the host and the device can be used to do the timing. When using CUDA for timing, we have to work with CUDA-events. Although this might be a bit more accurate, the differences are small. This is the reason that the timing mechanism of the host is used.

To get the most accurate results, the gettimeofday() function, from the <sys/time.h> header is used. This function returns the current time, in seconds and microseconds. Timing can be achieved by simply taking the difference of two different results of gettimeofday().

The resolution of the measurements is usually about 10 ms, but accurate information cannot be given without getting in too much detail. For example the resolution is both dependent on the hardware, and the software platform running on. For our purposes, a resolution of 10 ms is sufficient, and we will not get into more detail.

For accurate timing it is necessary to realize that some CUDA functions behave asynchronous. For example, when a kernel is invoked, the CPU continues executing the next statements, and will not wait for the kernel to finish. This can be solved by invoking the function cudaThreadSynchronize(). This function will not return until all previous CUDA calls are finished. So before taking any time measurement, cudaThreadSynchronize() should be called. In particular before the first measurement, since the CUDA engine might be performing certain startup routines in the background.

3.8. ACCURACY 33

## 3.8 Accuracy

Floating point accuracy is an important concept in scientific computing. Calculations have to be performed accurate enough, and rounding errors should not build up, resulting in significant differences. One important consequence of programming on the GPU is that floating point operations can produce slighly different results than on the CPU. This is a consequence of different methods of rounding off, for example because this might save space on the chip, making them cheaper. To make sure the results are accurate enough, each experiment run on the GPU is also run on the CPU, and the results are compared. This comparison is done by calcuting the relative norm of the difference vector of the two results. So we check if

$$rac{\|\mathbf{u}_{ ext{CPU}} - \mathbf{u}_{ ext{GPU}}\|}{\|\mathbf{u}_{ ext{CPU}}\|} < \epsilon,$$

for some small  $\epsilon \approx 10^{-5}$ . This also validates the algorithms on the GPU. We will not get in more detail on rounding off differences.

## Chapter 4

# Matrix-vector products

In Section 2.3 we see that the normal contact problem is solved using the iterative conjugate gradients method. During the execution of this method a large matrix-vector product has to be calculated during each iteration. This matrix has a special geometric structure, which results in the matrix B. See Figure 2.2 for the structure of this matrix.

In this chapter we will investigate a number of implementations of this matrix-vector product, using CUDA. Because a lot of calculations can be performed independent of each other, a huge speed-up might be possible when using the GPU. The first implementation is a direct port of the CPU version, using only global memory. Then we will use shared memory, to gain performance. All the implementations are written in the C programming language, with the CUDA extensions.

During the experiments, the performance is given by the number of floating point operations executed divided by the execution time. The number of floating point operations executed during a matrix-vector product is the number per inproduct, multiplied by the number of rows. The total number of floating point operations per inproduct is  $2 \cdot n$ , we have n multiplications, followed by n additions. The number of rows is also n, bringing the total number of floating point operations to  $2n^2$ .

## 4.1 Direct implementation

In this section we will derive an algorithm for calculating the matrix vector product  $\mathbf{u} = A\mathbf{p}$ , in terms of the matrix B. This algorithm will be implemented on both the CPU and GPU.

From Equation 2.9 we have

$$B_{(kx,ky)} = A_{(ix,iy),(jx,jy)},$$

with kx = jx - ix and ky = jy - iy. As stated earlier, we have  $kx \in \{-(nx - 1), ..., 0, ..., nx - 1\}$  and  $ky \in \{-(ny - 1), ..., 0, ..., ny - 1\}$ . We can now rewrite Equation 2.8 in terms of B, resulting in

$$u_I = \sum_J A_{IJ} p_J \quad \Rightarrow \quad u_{(ix,iy)} \quad = \quad \sum_{jy} \sum_{jx} A_{(ix,iy),(jx,jy)} p_{(jx,jy)}$$

$$= \quad \sum_{jy} \sum_{jx} B_{(kx,ky)} p_{(jx,jy)},$$

(4.1)

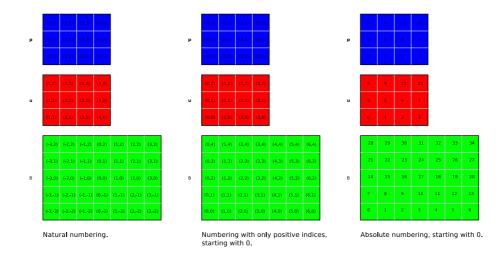

Figure 4.1: The different ways of numbering, for a grid of size  $4 \times 3$ .

with kx = (jx - ix) and ky = (jy - iy).

When implementing in C, we want positive indices, starting with 0. For ix, iy, jx we simply subtract 1 from the values. We then have ix' = ix - 1, iy' = iy - 1, jx' = jx - 1 and jy' = jy - 1, with  $ix, jx \in [0, nx - 1]$  and  $iy, jy \in [0, ny - 1]$ . For kx and ky, we add an offset nx - 1 to kx and an offset ny - 1 to ky, resulting in

$$kx' = kx + (nx - 1)$$

, with  $kx' \in \{0, ..., nx - 2\}$  and  $ky' = ky + (ny - 1)$ , with  $ky' \in \{0, ..., ny - 2\}$ .

From now on, we will always use this zero-based indexing, unless states otherwise.

Because we use linear (one-dimensional) arrays in C, we have to transform the double indices to a single index. In the arrays, the horizontal lines of  $\mathbf{u}$ ,  $\mathbf{p}$  and B will occupy consecutive memory locations. This results in an absolute index  $kk = ky' \cdot bx + kx'$  for B, and  $ii = iy \cdot nx + ix$  for  $\mathbf{u}$  and  $\mathbf{p}$ . See Figure 4.1 for an example of the different ways of labeling the grid points. Algorithm 4.1 gives the resulting algorithm for calculating  $\mathbf{u} = A\mathbf{p}$ .

This algorithm can be implemented in C directly. For the source code, see Appendix A.

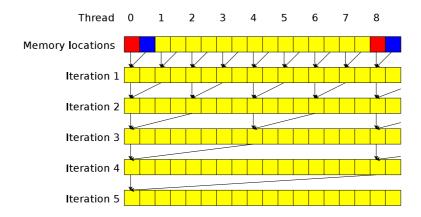

We can now port this algorithm to the GPU. In doing so, we have to choose how we divide the total work over the different blocks and threads. One possible method to proceed, is to divide  $\mathbf{u}$  into rectangular tiles, and let each block calculate the values of  $\mathbf{u}$  in one specific tile. Each thread in a block can then calculate a specific element of  $\mathbf{u}$ . We denote the size of a tile by tx and ty. The total number of tiles is denoted by Tx and Ty. See Figure 4.2 for an illustration of this division. Here the grid has size  $8\times 4$ , and is divided into  $4\times 2$  tiles each of size  $2\times 2$ . So we have nx=8, ny=4, Tx=4, Ty=2 and tx=ty=2. Of course the dimensions of a tile must be chosen in such a way, that the whole grid can be tiled.

When using a division like this, each tile of **u** is calculated by a different block,

#### **Algorithm 4.1** Algorithm to calculate $\mathbf{u} = A\mathbf{p}$ in terms of B.

```

for iy = 0 to ny - 1 do

for ix = 0 to nx - 1 do

ii = iy \cdot nx + ix

u_{ii} = 0

5:

for jy = 0 to ny - 1 do

ky = jy - iy + ny - 1

for jx = 0 to nx - 1 do

kx = jx - ix + nx - 1

jj = jy \cdot nx + jx

kk = ky \cdot bx + kx

10:

u_{ii} = u_{ii} + B_{kk} \cdot p_{jj}

end for

end for

end for

15: end for

```

Figure 4.2: Example of a division in tiles of the grid.

and in each tile, each component of  $\mathbf{u}$  is calculated by a different thread. Since the threads are executed in parallel, we do not need the two outer-most loops of Algorithm 4.1. Each thread calculates its unique ix, iy and ii values and proceeds with the inner-loops. This way each iteration of the outer-most loop of Algorithm 4.1 corresponds to a different block, and each iteration of the first nested loop corresponds to a different thread in a particular block.

Algorithm 4.2 gives the steps that need be to performed by each thread when using a tiling like this.

**Algorithm 4.2** Algorithm when using tiles to divide **u**. This algorithm is executed by each thread in the grid.

```

iy = \texttt{blockIdx.y} \cdot \texttt{blockDim.y} + \texttt{threadIdx.y}

ix = \texttt{blockIdx.x} \cdot \texttt{blockDim.x} + \texttt{threadIdx.x}

ii = iy \cdot nx + ix

u_{ii} = 0

5: for jy = 0 to ny - 1 do

ky = jy - iy + ny - 1

for jx = 0 to nx - 1 do

kx = jx - ix + nx - 1

jj = jy \cdot nx + jx

10: kk = ky \cdot bx + kx

u_{ii} = u_{ii} + B_{kk} \cdot p_{jj}

end for

end for

```

When stating an algorithm like this for the GPU, it is executed by each thread of all blocks. We assume that all threads in a block simultaneously execute a particular line of code. This way memory synchronization problems cannot occur. It is important to be aware of the fact that when implementing an algorithm in CUDA the lines of code are not executed simultaneously, but in warps, and we have to use the \_\_syncthreads() instruction for synchronization. This is particularly important when using shared memory.

This algorithm is implemented on both the CPU and the GPU, where on the CPU the tiling has no effect and we just iterate over ii and jj.

On the CPU we expect more or less equal speeds, regardless the size of the grid. There might be deviations when using small grids, due to memory latencies. For smaller grids, which allow the whole matrix A to be stored in the host memory, the matrix vector product is calculated using both A and B. This shows the effect of the extra addressing when using B.

On the GPU the size of the tiles is important. This is because of memory coalescing and thread divergence. If the number of grid points in a block is not a multiple of 32, we expect less performance because of warps that are not filled completely. On the other hand, we expect the number of memory transactions to be much higher than the number of arithmetic instructions, and for memory transactions only half-warps are important. So we expect the difference between tiles with tx = 32 and tx = 16 to be less then the difference between tiles with tx = 16 and tx = 8. If we chose tx to be a multiple of 32 none of these problems

arise.

As mentioned earlier, when threads in a half-warp access consecutive locations in the global memory, this will result in a single memory transaction. When using the tiling described earlier, for memory coalescing, threads in the same half-warp, with consecutive threadIdx.x indices have to access consecutive memory locations. Also the first thread should access a memory location on a 64-byte boundary. Assuming that in Algorithm 4.2 the arrays  $B,\ p$  and u are aligned on such a boundary, we can see that the write operations to u are always coalesced if blockDim.x is a multiple of 16, but the read operations from B and p are not, in general.

In Section 4.3 the results of these implementations will be discussed.

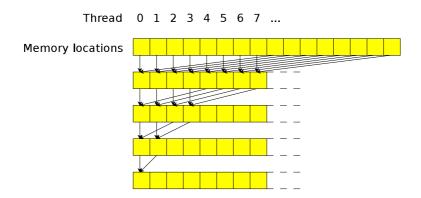

## 4.2 Using shared memory

In the previous section only the global memory was used. This resulted in a lot of non-coalesced memory transactions. We will now investigate the use of shared memory to gain higher performance. The total amount of shared memory per multiprocessor is 16 KiB, or 4096 4-byte floating point numbers. We must make sure not to exceed this amount per block, or else the kernel will fail to launch.

When using shared memory, a lot of addressing has to be performed. This means the threads need to perform a lot of integer arithmetic, not contributing to the overall floating-point performance. As we will see in Section 4.3, the size of the tiles in the y direction does not have much influence on the performance. For these reasons, we will use tiles with only one grid point in the y direction. The number of grid points in the x direction should be a multiple of 32 to make sure it can be divided in a particular number of warps. We might want to maximize the size in the x direction, for maximum use of the shared memory.

We define Tx as the number of tiles in the x direction, and tx as the size of the tiles in the x direction. Again we choose kx = jx - ix + nx - 1 and ky = jy - iy + ny - 1. Furthermore we have  $jx = jTx \cdot tx + jtx$  and  $ix = iTx \cdot tx + itx$ . We can now rewrite Equation 4.1 to

$$u_{(ix,iy)} = \sum_{jy=0}^{ny-1} \sum_{jx=0}^{nx-1} B_{(kx,ky)} p_{(jx,jy)} = \sum_{jy=0}^{ny-1} \sum_{jTx=0}^{Tx-1} \left( \sum_{jtx=0}^{tx-1} B_{(kx,ky)} p_{(jx,jy)} \right). \tag{4.2}$$

Each block calculates one tile of  $\mathbf{u}$  and each thread calculates one element of  $\mathbf{u}$ . This means we can use a register variable for this value of  $\mathbf{u}$ . For  $\mathbf{p}$  and B we will use shared memory. Because shared memory is scarce we cannot load the complete arrays at once, and we have to load tiles of B and  $\mathbf{p}$  during the kernel execution. We denote the regions of shared memory by B' and p'. We will focus on the inner-most loop of Equation 4.2.

For particular tiles of **u** and **p**, that is, for particular values of iTx and jTx, we have

$$jx \in [jTx \cdot tx, (jTx+1) \cdot tx - 1],$$

$ix \in [iTx \cdot tx, (iTx+1) \cdot tx - 1].$

For kx we then have

$$kx \in [(jTx - iTx - 1) \cdot tx + nx, (jTx - iTx + 1) \cdot tx + nx - 2].$$

As expected, when calculating the contribution of a specific tile of  $\mathbf{p}$  to a tile of  $\mathbf{u}$  we need tx values of p and 2tx-1 values of B. We can now define new indices

$$\begin{cases} ix' = (iTx+1) \cdot tx - ix - 1 \\ jx' = jx - jTx \cdot tx \\ kx' = kx - (jTx - iTx - 1) \cdot tx - nx, \end{cases}$$

so that we have

$$ix' \in [0, tx - 1]$$

$jx' \in [0, tx - 1]$

$kx' \in [0, 2tx - 2].$

Furthermore, since kx = jx - ix + nx - 1 we have kx' = ix' + jx' and  $jx' = jx - jTx \cdot tx = jTx \cdot tx + jtx - jTx \cdot tx = jtx$ . If we now define

$$\begin{cases} u' = u_{(ix,iy)} \\ p'_{jx'} = p_{(jx,jy)} \\ B'_{kx'} = B_{(kx,ky)}, \end{cases}$$

Equation 4.2 can be rewritten as

$$u' = \sum_{jy=0}^{ny-1} \sum_{jTx=0}^{Tx-1} \left( \sum_{jx'=0}^{tx-1} B'_{kx'} p'_{jx'} \right). \tag{4.3}$$

Algorithm 4.3 states how we can calculate the matrix-vector product using the shared memory. Remark that we perform one assignment for p', but two for B'. This is because we need to load one tile of  $\mathbf{p}$  but two tiles of B.

When implementing this in CUDA, we will use a block to attain a particular value of iTx, and the threads of that block to attain the values of itx. Each thread will then loop over jy, jTx and jx'. The tiles of p and B are read from the global memory on the beginning of the loop over jTx, just before the values are needed. When reading from global memory, each thread will read one value. Of course after the read instructions, a synchronization is needed to make sure all threads read and stored their values. A synchronization is also needed before reading the new tiles from the global memory, to make sure all the previously read values are used.

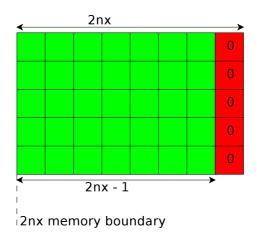

When tx is a multiple of 16, the read operation of p will coalesce, but special care is needed when reading B. We will read 2tx values for each value of jTx, but because the size of B in the x-direction is 2nx-1, for values of  $iy \neq 0$ , these read operations will in general be non-coalesced, since they do not start at a 64-byte boundary. Furthermore, when the very last tile of B is read, this will result in reading non-allocated memory location. This is of course always a bad idea. The common solution for these two problems, is to add a dummy value at the end of each row of B. thereby changing its dimensions to  $2nx \times (2ny-1)$

#### Algorithm 4.3 Algorithm when using shared memory.

```

iy = blockIdx.y

iTx = blockIdx.x

ix'=\mathtt{threadIdx.x}

u' = 0

5: for jy = 0 to ny - 1 do

ky = jy - iy + ny - 1.

for jTx = 0 to Tx - 1 do

kx = (jTx - iTx - 1)tx + nx + \texttt{threadIdx.x}

kx' = \texttt{threadIdx.x}

B'_{kx'} = B_{(kx,ky)}

10:

B_{kx'+tx}^{n} = B_{(kx+tx,ky)} jx = jTx \cdot tx + \texttt{threadIdx.x}

jx' = \texttt{threadIdx.x}

\begin{aligned} p'_{jx'} &= p_{(jx,jy)} \\ ix' &= \texttt{threadIdx.x} \end{aligned}

15:

for jx' = 0 to tx - 1 do

kx' = jx' + ix'

u' = u' + B'_{kx'} \cdot p'_{jx'}

end for

end for

20:

end for

ix = (iTx + 1)tx - 1 - \texttt{threadIdx.x}

ix' = \mathtt{threadIdx.x}

u_{(ix,iy)} = u'

```

Figure 4.3: A dummy entry is padded to each row of B.

instead of  $(2nx-1) \times (2ny-1)$ . Of course when accessing a specific row of B, we should now stride by 2nx values instead of 2nx-1 values. Figure 4.3 shows what changes when nx=4 and ny=3. The red entries are read, but never used for calculations. The dotted line shows where the 2nx boundaries are. We see that each tile will start on a tx boundary, so read transactions will coalesce if tx is chosen properly. Again the source code can be found in Appendix A.

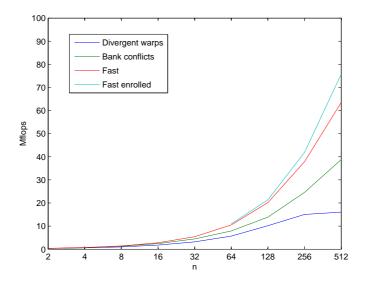

#### 4.3 Results

For the results each implementation is run on the specified system. For each point in the dataset, the corresponding implementation is run 5 times, and the average runtime is used. The GPU on which all the implementations are tested is a NVIDIA Quadro FX 570M, consisting of 256 MiB global memory, and 4 multiprocessors. The clock rate is 0.95 GHz. The device has compute capability 1.1. The system is running Ubuntu 9.04, and CUDA 3.0 is used.

The CPU's on which the direct implemenation is tested, are the Intel Core 2 Duo T7300 2.00 GHz, running Ubuntu 9.04, and the Intel Pentium 4 3.40 GHz, running Ubuntu 10.04.

#### 4.3.1 Direct implementation

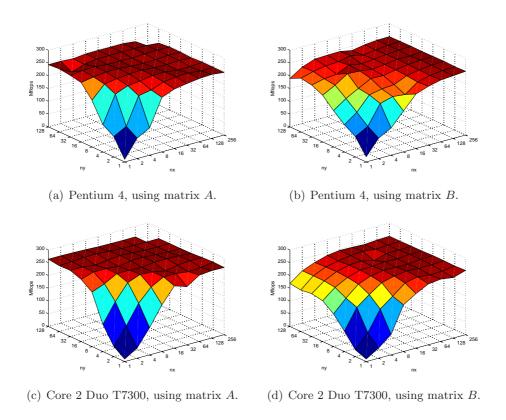

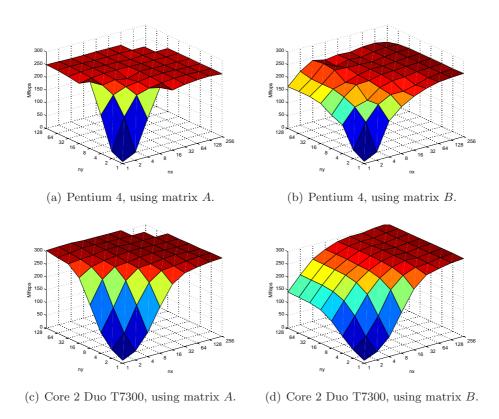

The direct implementation is run on both the CPU and the GPU. Figure 4.4 shows the overall computation speed, expressed in Mflops for different grid sizes. We see that in both cases the performances is higher when using matrix A. This is because less integer arithmetic is needed for addressing. Both figures show that with growing grid sizes, the performance quickly converges to a maximum, as we expected. The maximum performance achieved is 252 Mflops.

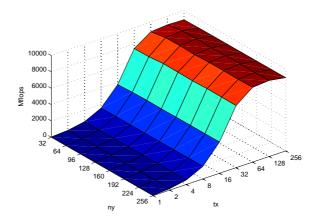

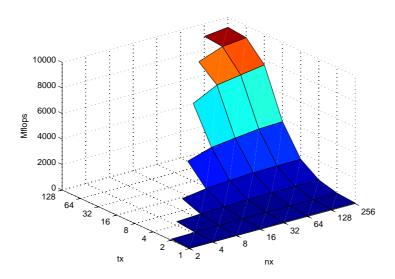

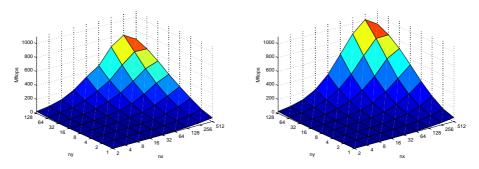

When we use the GPU for the direct implementation, we can vary both the grid size and the tile size. Figure 4.5 shows the results for a grid of  $256 \times 256$ ,

<sup>&</sup>lt;sup>1</sup>See Section 3.5 for more information.

4.3. RESULTS 43

Figure 4.4: Performance of the direct implementation on the Pentium 4 and the Intel Core 2 Duo T7300.

for different tile sizes. Since a tile can consist of a maximum of 512 grid points, only values of tx and ty are valid with  $tx \cdot ty \leq 512$ . We see that when  $tx \leq 8$  the performance is very low. This is because of the non-coalesced memory transactions. When  $tx \geq 16$  the differences are small, but we see that the smaller tx and ty the higher the performance. This might be explained because when tiles are small, there are more blocks, and the hardware scheduler can assign more block per multiprocessor. This leads to better results, because during the time one active block is waiting for some memory transaction to be completed, the multiprocessor can perform work for another active block. The maximum performance achieved is 555 Mflops. This is about twice the speed when using the direct implementation on the CPU.

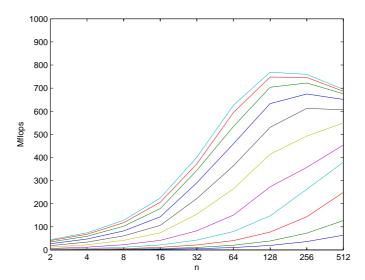

#### 4.3.2 Shared Memory

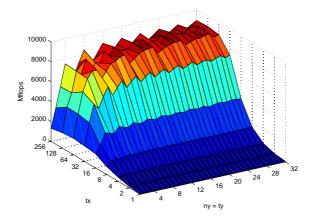

In Figure 4.6 we see that using the shared memory implementation, the performance is much higher. The grid size in the x direction is 256 grid points, divided into tiles of size tx. The grid size in the y direction, ny, is varying from 1 to 32. We use tile size ty = 1 in the y direction. We see two distinct effects. For small values of ny the performance is low, but grows very quickly as ny grows, to a maximum. Furthermore, for small values of tx, the performance is very low, but grows quickly when tx gets bigger, and converges to a maximum

Figure 4.5: Results for grid size  $256 \times 256$  and different tile sizes.

for  $tx \geq 64$ .

That the performance is low when ny is small, can be explained by the fact the when tx is small, the total number of tiles, and thus blocks, is small, and as we saw earlier, this limits the performance. Furthermore, when ty is odd, we see the performance drops a bit, which is probably caused because the total number of multiprocessors is even, so the last block has to run on a multiprocessor with the other multiprocessors idle. Here we assumed the multiprocessors are finished at the same time with the other blocks, which in general might not be true, but deviations are likely to be small compared to the time it takes to complete one block.

The rise in performance when tx gets bigger, can be explained by two reasons. First of all, For tx < 32 we have blocks consisting of less threads then 32, thus less then one warp. This decreases the performance tremendously. Furthermore, by looking at Algorithm 4.3 we see that the bigger tx, the more shared memory is used, and the less memory bandwidth is an issue. We see that for  $tx \ge 64$  the performance is more or less stagnant.

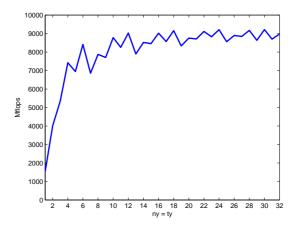

Figure 4.7 shows that for nx=256, ny has no significant influence on the performance if it is taken a multiple of 32. In the figure different grid sizes are shown, with ny multiples of 32. The tiles have size 1 in the y direction. The maximum performance achieved is 9305 Mflops, for tx=128. This is a factor 17 higher then in the direct implementation on the GPU. We also see that for  $tx \le 32$  performance significantly increases for growing tiles. This is the effect of warps being more and more filled, until we have full warps for tx=32.

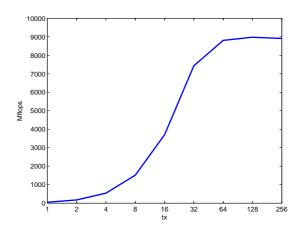

Finally, Figure 4.8 shows that the value of nx does not have a significant influence on the performance. This, together with the observation that ty does not have much influence either, makes us expect that the implementation of the algorithm performs well when the grid size is scaled up in either direction.

4.3. RESULTS 45

(a) Performance for ny varying from 1 to 32.

(b) Performance for different grid sizes in y direction, for  $t_x = 128$

Figure 4.6: Results for shared memory implementation, using grid size  $256 \times ny$  with ty = 1 and tx varying.

The tile size does have a significant influence, and tiles should be scaled up as much as posible.

We have seen that when only using the global memory, the tile sizes are not very important, as long as they are larger then the size of a warp. This is a consecuence of memory coalescence. When using shared memory the tile size is of great influence on the total performance. In general the tile size should be relatively large, so that the use of shared memory is maximized. This results in a performance gains of a factor 17 compared to the global memory implementation, and a gain of a factor 37 compared to the CPU implementation.

(a) Performance for different tile sizes  $tx\times 1$  for growing grid in y direction.

(b) Performance for different tile sizes  $tx \times 1$  when ny = 32.

Figure 4.7: Influence of different tile sizes  $tx \times 1$  and grid sizes in the y direction, with ny varying from 32 to 256 and nx = 256.

4.3. RESULTS 47

Figure 4.8: Influence of growing grid size in the x direction, for different tile sizes  $tx \times 1$ . ny = 128.

# Chapter 5

# Inner products

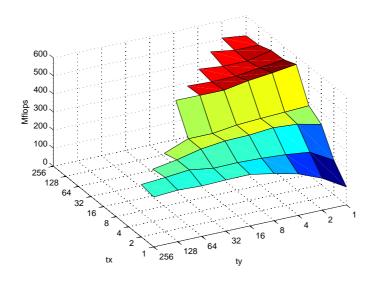

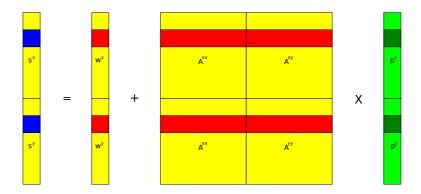

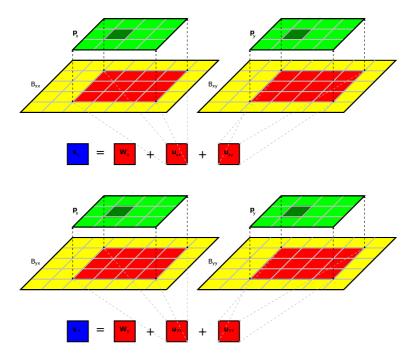

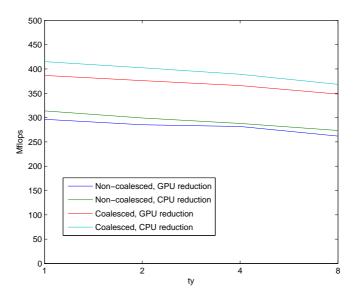

As stated in Section 2.4, during each iteration of the tangential algorithm, four inner products have to be calculated. In general there are four matrices of influence coefficients,  $A^{xx}$ ,  $A^{xy}$ ,  $A^{yx}$  and  $A^{yy}$ . During each iteration of the tangential algorithm, one value of  $s_x$  and one value of  $s_y$  are updated. With these new values of  $s_x$  and  $s_y$ , a system of equations is solved, resulting in new values of the corresponding elements of  $p_x$  and  $p_y$ . See Figure 5.1 for an illustration of the inner products calculated.

During a specific iteration, the inner products of the red rows of the A matrices with the  $\mathbf{p}$  vectors are calculated, and the red values of the  $\mathbf{W}^*$  vectors are added. This results in the two new blue elements of the  $\mathbf{s}$  vectors. Then the second part of the algorithm calculates the new dark greens elements of the  $\mathbf{p}$  vectors. All four A matrices have the translational invariance explained in Chapter 2, so we have four associated B matrices. Figure 5.2 visualizes the calculations using the B matrices. For simplicity the grids of the  $\mathbf{W}^*$  vectors and  $\mathbf{s}$  vectors are omitted.

Since after each iteration new values of  $\mathbf{p}$  are calculated, the inner products of different iterations cannot be calculated parallel, but have to be calculated in a consecutive order. On the GPU this means a significant drawback of performance, since we can only perform four inner products simultaneously. In

Figure 5.1: Inner products in terms of matrices A.

Figure 5.2: Inner products in terms of matrices B.

the next sections of this chapter we will consider implementations on the CPU and the GPU, and the results will be stated.

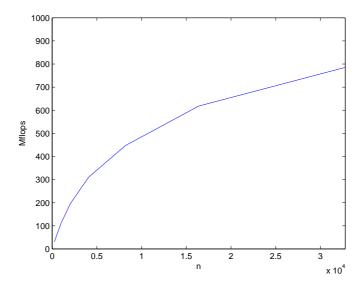

To determine the performance of a specific implementation, we need the total number of floating point operations executed.<sup>1</sup> Per inner product we have to perform  $n = nx \cdot ny$  multiplications, and the same number of additions, so the total number of floating points operations per inner product is 2n. Per iteration we calculate 4 inner products, and finally we add two inner products, and the corresponding element of  $\mathbf{W}^*$  together for each direction x and y, so the total number of floating point operations, per iteration is given by 8n + 6. During the experiments, we measure the time it takes to perform the inner products for each element, so the total number of iterations will be n, bringing the total number of floating point operations to  $8n^2 + 6n$ .

During the program execution, this whole process will be repeated a given number of times, to make sure background processes do not influence the outcome significantly. The actual number of times an experiment is run will be stated at the results.

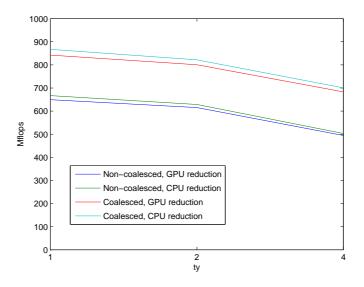

## 5.1 CPU Implementation