Vlad-Mihai Sima

# Compiler Assisted Runtime Adaptation

# **Compiler Assisted Runtime Adaptation**

### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. Ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op maandag 30 januari 2012 om 12:30 uur

door

Vlad-Mihai SIMA

Master of Science University Politehnica of Bucharest geboren te Boekarest, Roemenië Dit proefschrift is goedgekeurd door de promotor: Prof.dr.ir. H.J. Sips Copromotor: Dr. K.L.M. Bertels

Samenstelling promotiecommissie:

| Rector Magnificus,            | voorzitter                                |

|-------------------------------|-------------------------------------------|

| Prof.dr.ir. H.J. Sips,        | Technische Universiteit Delft, promotor   |

| Dr. K.L.M. Bertels,           | Technische Universiteit Delft, copromotor |

| Prof. dr. R. Tripiccione      | UNIFE, Italië                             |

| Prof. dr. ir. K. De Bosschere | Universiteit Gent, België                 |

| Prof. dr. F.M.T. Brazier      | Technische Universiteit Delft             |

| Dr. A.D. Pimentel             | University of Amsterdam                   |

| Dr. ir. L. Jóźwiak            | Technische Universiteit Eindhoven         |

| Prof. dr. C. Witteveen,       | Technische Universiteit Delft, reservelid |

|                               |                                           |

### CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Vlad-Mihai Sima

Compiler Assisted Runtime Adaptation Delft: TU Delft, Faculty of Elektrotechniek, Wiskunde en Informatica - III Ph.D. Thesis Technische Universiteit Delft.

Met samenvatting in het Nederlands.

ISBN 978-90-72298-25-6

Subject headings: compiler optimizations, runtime optimizations, reconfigurable computing.

### Copyright © 2012 Vlad-Mihai Sima

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed in The Netherlands

To my family and to the friends I have all over the world

### Compiler Assisted Runtime Adaptation

Vlad-Mihai Sima Abstract

N this dissertation, we address the problem of runtime adaptation of the application to its execution environment. A typical example is changing the processing element on which a computation is executed, considering the available processing elements in the system. This is done based on the information and instrumentation provided by the compiler and taking into account the status of the environment. The work focuses on heterogeneous multicore embedded architectures. We address three aspects of application optimizations: hardware software mapping, memory allocation and parallel execution. For each aspect, an algorithm is developed and, using a suitable application, it is tested on the hardware platform. The programming paradigm on which this work is based is the Molen programming paradigm, extended and adapted for our specific platform and operating environment.

The hardware software mapping algorithm objective is to choose at runtime, on which processing element it is more efficient to execute a function. For the memory allocation we propose an algorithm, that using compile-time gathered information and the current execution environment, decides on the best allocation for memory, at runtime. For dealing with parallel applications we developed an algorithm that selects the best trade-off between area and speedup and decides on the number of concurrent units that execute.

The experiments were performed on an embedded multicore heterogeneous platform, namely the hArtes Hardware Platform (hHP). This platform contains an ARM processor as General Purpose Processor (GPP), an Atmel Magic Diopsis Digital Signal Processor (DSP) and a Xilinx Virtex4 Field Programmable Gate Array (FPGA). The applications used to validate the algorithms are real life applications from the multimedia field: a video encoder/decoder and a wavefield synthesis application. The mapping algorithms obtains improvements between 5% and 43%. We showed this is an adaptable algorithm, that will adapt the execution in case the execution overhead increases. The memory allocation algorithm obtained a speedup of 18% on the selected application. For this algorithm we show that the solution is within 14% of the optimal solution, computed using Integer Linear Programming (ILP). The scenario based selection of parallel computations, is between 21% to 92% better than existing solutions.

### Acknowledgments

I would like to thank here all the people that encouraged me and supported me to pursue the difficult endeavor of obtaining a PhD. I would start with my university adviser Prof. Dr. Irina Athanasiu, which convinced me during my master thesis that I can and should continue my studies. Even if she can not be present among us today, she lives through her students, that gained with her not only technical knowledge, but also important life lessons. Next, I would like to thank Prof. Dr Stamatis Vassiliadis, whom, although I met only a couple of times, I feel had a great impact, even if indirect, on my path in life. From the first meeting I had in Delft with him and Dr. Koen Bertels, I felt inspired to come and help to solve some of the intriguing questions in our field. Fate decided that I will not work with him, but I am sure that his influence manifests itself through all the people that knew him.

Would like to give a special thanks to Dr. Koen Bertels, who supported me during this challenging period in my life. His dedication to work and ability to overcome all the obstacles were an example that I will always try to follow. I am grateful to everybody that helped me improve the quality of the thesis by providing comments and suggestion. This include the committee members: Prof. Dr. H. J. Sips, Assoc. Prof Andy Pimentel, Assoc. Prof. L. Jóźwiak. Then, my colleagues that helped in the various stages of the writing: Anca Molnos, Carlo Galuzzi and Ozana Silvia Dragomir. Also, a special thanks to the people that helped with the Dutch language: Roel Meeuws and Roel Seedorf.

For all the answers they provided me during the years, I would like to thank Dimitris Theodoropoulos and Lu Yi. For all the discussion related to various problems, I will thank Razvan Nane, Yana Yankova and Elena Moscu Panainte. Also, would like to thank for the support to Lidwina Tromp, Erik de Vries and Eef Hartman.

The work in this thesis was also made possible by the hArtes EU project, so a thank is due to all the great partners and to their efforts toward building a successful project. My life in Delft would have been very hard and boring without the many good friends I made here. Would mention, in totally random order: Ana, Catalin, Aki, Bea, Li, Dejan, Noe and many others I would not list here.

The final thanks go to my parents who always supported me and encouraged me to start this adventure.

Vlad-Mihai Sima

Delft, The Netherlands, January 2012

# Table of contents

| Ab  | stract  |         |                                                     | i |

|-----|---------|---------|-----------------------------------------------------|---|

| Acl | knowl   | edgmen  | nts                                                 | i |

| Tab | ole of  | Content | ts                                                  | V |

| Lis | t of Ta | ables . | iz                                                  | K |

| Lis | t of Fi | gures   |                                                     | i |

| Lis | t of Li | stings  |                                                     | 7 |

| Lis | t of A  | cronym  | s and Symbols                                       | i |

| 1   | Intro   |         |                                                     | l |

|     | 1.1     | Proble  | em Overview                                         | 3 |

|     |         | 1.1.1   | Dissertation Scope                                  | 1 |

|     |         | 1.1.2   | Contribution of the thesis                          | 7 |

|     | 1.2     | Disser  | tation Organization                                 | 3 |

| 2   | Back    | ground  | and Related Research                                | l |

|     | 2.1     | Resear  | rch context                                         | l |

|     |         | 2.1.1   | Computing Platforms                                 | l |

|     |         | 2.1.2   | Toolchains                                          | 3 |

|     |         | 2.1.3   | The Applications                                    | 5 |

|     | 2.2     | Relate  | d Research                                          | 5 |

|     |         | 2.2.1   | Memory Related Problems and Solutions 17            | 7 |

|     |         | 2.2.2   | Partitioning Related Problems and Solutions 21      | l |

|     |         | 2.2.3   | Parallelism and Scheduling Related Problems and So- |   |

|     |         |         | lutions                                             | 1 |

|     | 2.3     | Summ    | ary                                                 | 5 |

| 3 | Rese | earch Co | ntext                                               | 27 |

|---|------|----------|-----------------------------------------------------|----|

|   | 3.1  | Method   | dology overview                                     | 28 |

|   | 3.2  | hArtes   | Hardware Platform (hHP)                             | 28 |

|   |      | 3.2.1    | General Platform Description                        | 29 |

|   |      | 3.2.2    | Hardware Platform Issues                            | 32 |

|   | 3.3  | The Mo   | olen Abstraction Layer                              | 34 |

|   |      | 3.3.1    | The Molen Programming Paradigm                      | 35 |

|   |      | 3.3.2    | hArtes Implementation of The Molen Programming      |    |

|   |      |          | Paradigm                                            | 41 |

|   |      | 3.3.3    | The Molen Paradigm and OpenMP                       | 43 |

|   |      | 3.3.4    | The Molen Paradigm and OpenCL                       | 45 |

|   | 3.4  | hArtes   | Toolchain                                           | 48 |

|   |      | 3.4.1    | Using GPP Compiler to Generate Molen Primitives     | 49 |

|   |      | 3.4.2    | Development and Toolchain Debugging                 | 52 |

|   |      | 3.4.3    | Toolchain Retargetability                           | 55 |

|   | 3.5  |          | Applications                                        | 57 |

|   |      | 3.5.1    | Video application - The H.264 codec                 | 57 |

|   |      | 3.5.2    | Immersive audio - Beamforming and Wavefield Syn-    |    |

|   |      |          | thesis                                              | 67 |

|   |      | 3.5.3    | In Car Audio - Enhanced Listening Experience        | 71 |

|   | 3.6  |          | ed Problems                                         | 75 |

|   | 3.7  |          | putions                                             | 76 |

|   | 3.8  | Summa    | ary                                                 | 77 |

| 4 | Runt | ime Hard | dware/Software mapping                              | 79 |

|   | 4.1  |          | iction                                              | 79 |

|   | 4.2  | Backgr   | ound and Related Research                           | 80 |

|   | 4.3  | •        | m Definition                                        | 81 |

|   | 4.4  |          | ional Hardware Execution for Molen                  | 83 |

|   |      | 4.4.1    | Selecting The Functions And The Relevant Input Data | 84 |

|   |      | 4.4.2    | Runtime Profile Data Module                         | 86 |

|   |      | 4.4.3    | Decision Module                                     | 88 |

|   | 4.5  | Results  | 3                                                   | 89 |

|   | 4.6  | Conclu   | sions                                               | 93 |

| 5 | Runi | ime Men  | nory Allocation                                     | 95 |

|   | 5.1  |          | ound and Related Research                           | 96 |

|   | 5.2  |          | m Definition                                        | 96 |

|     | 5.3     | Memory al    | location in | nfrastru  | ictui      | e.  | •  |       | <br> |   |       |   | <br>97  |

|-----|---------|--------------|-------------|-----------|------------|-----|----|-------|------|---|-------|---|---------|

|     |         | 5.3.1 All    | ocation T   | racking   | g Mo       | odu | le |       | <br> |   |       |   | <br>100 |

|     |         | 5.3.2 Ex     | ecution M   | odule     |            |     |    |       | <br> |   |       |   | <br>102 |

|     |         | 5.3.3 Ma     | pping Alg   | gorithm   | ns.        |     |    |       | <br> |   |       |   | <br>102 |

|     | 5.4     | Empirical '  | Validation  |           |            |     |    |       | <br> |   |       |   | <br>108 |

|     |         | 5.4.1 H.2    | 264 video   | Encode    | er.        |     |    |       | <br> |   |       |   | <br>109 |

|     |         | 5.4.2 Syr    | nthetic Ap  | plication | ons        |     |    |       | <br> |   |       |   | <br>110 |

|     | 5.5     | Summary      |             |           |            |     | •  | <br>• | <br> | • | <br>• | • | <br>112 |

| 6   | Scena   | ario Based F | Runtime M   | apping    |            |     |    |       | <br> |   |       |   | <br>113 |

|     | 6.1     | Backgroun    | d and Rela  | ated Re   | esear      | rch |    |       | <br> |   |       |   | <br>113 |

|     | 6.2     | Static algor | rithm       |           |            |     |    |       | <br> |   |       |   | <br>114 |

|     |         | 6.2.1 Pro    | blem Def    | inition   |            |     |    |       | <br> |   |       |   | <br>114 |

|     |         | 6.2.2 All    | ocation A   | lgorith   | <b>m</b> . |     |    |       | <br> |   |       |   | <br>116 |

|     | 6.3     | Results      |             |           |            |     |    |       | <br> |   |       |   | <br>118 |

|     | 6.4     | Runtime A    | lgorithm    |           |            |     |    |       | <br> |   |       |   | <br>122 |

|     | 6.5     | Conclusion   | ıs          |           |            |     | •  |       | <br> |   |       | • | <br>123 |

| 7   | Conc    | usions       |             |           |            |     |    |       | <br> |   |       |   | <br>125 |

|     | 7.1     | Outlook .    |             |           |            |     |    |       | <br> |   |       |   | <br>125 |

|     | 7.2     | Dissertatio  | n Contribu  | utions    |            |     |    |       | <br> |   |       |   | <br>126 |

|     | 7.3     | Future dire  | ctions .    |           |            |     | •  |       | <br> |   |       | • | <br>127 |

| Bib | oliogra | phy          |             |           |            |     | •  |       | <br> |   |       |   | <br>131 |

| Lis | t of Pu | blications   |             |           |            |     | •  |       | <br> |   |       |   | <br>141 |

| Sai | menva   | tting        |             |           |            |     |    |       | <br> |   |       | • | <br>143 |

| Cu  | rriculu | m Vitae      |             |           |            |     |    |       | <br> |   |       |   | <br>145 |

# List of Tables

| 3.1  | Transfer speed of a memory block of 32 kB size between SPM and SDRAM for hArtes Hardware Platform.                                                                    | 34 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | The Molen concepts and their corresponding OpenCL concepts.                                                                                                           | 46 |

| 3.3  | Molen primitives and their corresponding OpenCL functions                                                                                                             | 47 |

| 3.4  | Compilation times using FPGA flow at different frequency constraints.                                                                                                 | 56 |

| 3.5  | x264 application metrics.                                                                                                                                             | 58 |

| 3.6  | Comparison of profile information between Intel x86 and ARM for x264 application.                                                                                     | 62 |

| 3.7  | Number of calls for each combination of parameters and per-<br>cent from the total number of invocations for <i>sad</i> , when run-<br>ning on a set of sample videos | 63 |

| 3.8  | Number of calls for each combination of parameters and per-<br>cent from the total number of invocations for <i>satd</i> , when run-<br>ning a set of sample videos.  | 64 |

| 3.9  | The synthesis statistics for the <i>satd</i> kernel on the Virtex4-ML410 board.                                                                                       | 65 |

| 3.10 | Processing times and speedups for kernel <i>satd</i> in various scenarios.                                                                                            | 65 |

| 3.11 | Processing times and speedups in various scenarios for <i>satd</i> unrolled                                                                                           | 66 |

| 3.12 | The synthesis statistics for the <i>sad</i> kernel on the Virtex4-ML410 board                                                                                         | 66 |

| 3.13 | The WFS application metrics.                                                                                                                                          | 68 |

| 3.14 | 4 Percent of floating point operations, from the total number of operations used, for the WFS application.                                                                                                                                |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.15 | The synthesis statistics for the <i>fFD</i> kernel on the Virtex4-ML410 board                                                                                                                                                             | 70  |

| 3.16 | Execution of units tests for <i>fFD</i> kernel on Virtex4-ML410                                                                                                                                                                           | 71  |

| 3.17 | In car Audio Enhanced Listening application metrics                                                                                                                                                                                       | 72  |

| 3.18 | Execution of units tests for the <i>FracShift</i> kernel on Virtex4-ML410.                                                                                                                                                                | 73  |

| 3.19 | Execution of units tests for the <i>FracShift</i> kernel with the unroll optimization on Virtex4-ML410.                                                                                                                                   | 75  |

| 4.1  | Parameter values for <i>satd</i> call                                                                                                                                                                                                     | 86  |

| 4.2  | Parameters and execution time on Virtex ML510 board for <i>satd</i> call                                                                                                                                                                  | 89  |

| 4.3  | Kernel execution times in different scenarios. Reference is executing all calls in software.                                                                                                                                              | 91  |

| 5.1  | AMMA algorithm example.                                                                                                                                                                                                                   | 104 |

| 5.2  | AMMAe algorithm example                                                                                                                                                                                                                   | 106 |

| 5.3  | Execution time overhead of constructing memory allocation table for stack and dynamically allocated variables                                                                                                                             | 109 |

| 5.4  | Average mapping module execution times tested on the hard-<br>ware platform (outside of the context of an application)                                                                                                                    | 109 |

| 6.1  | Implementation scenarios for beamforming application. The various scenarios are obtained by increasing the level of paral-<br>lelism used in the hardware for each task in each thread. The area is considered for platform Virtex II Pro | 115 |

# List of Figures

| 1.1 | The hArtes project toolchain and platform                                                                                                                                                                                                                                                                            | 5  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | The Molen machine organization.                                                                                                                                                                                                                                                                                      | 13 |

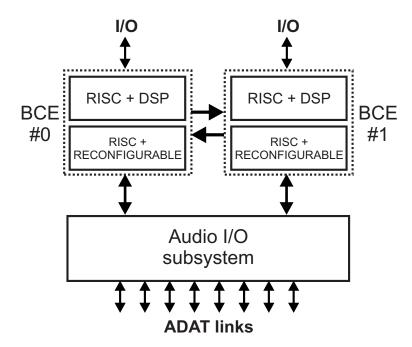

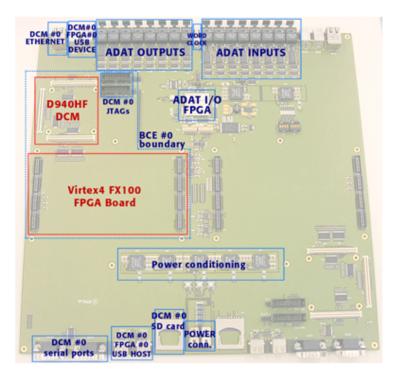

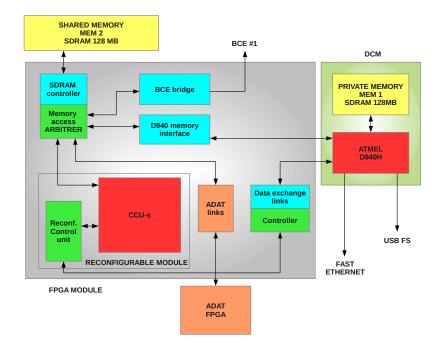

| 3.1 | Top level architectural structure of the hArtes Hardware Plat-<br>form. The system has two independent heterogeneous and<br>configurable processors, which communicate among each<br>other and with an audio I/O subsystems supporting several<br>Alesis Digital Audio Tape (ADAT) channels                          | 30 |

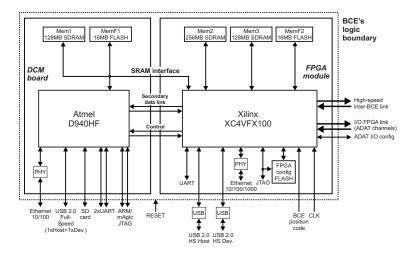

| 3.2 | Detailed block digram of the Basic Configurable Element (BCE) of the hArtes Hardware Platform. The BCE is the basic building block of the platform, supporting several processing architectures. One or more BCEs work in parallel to support a hArtes application.                                                  | 31 |

| 3.3 | Picture of the hArtes Hardware Platform. The two BCEs use<br>two daughters boards each, one for the D940HF processor and<br>one for the FPGA based infrastructure. The ADAT interfaces<br>and several standard I/O connectors are clearly visible at the<br>top and at the bottom of the picture, respectively. [83] | 32 |

| 3.4 | Overlay of components over a picture of the hArtes Hardware Platform.                                                                                                                                                                                                                                                | 33 |

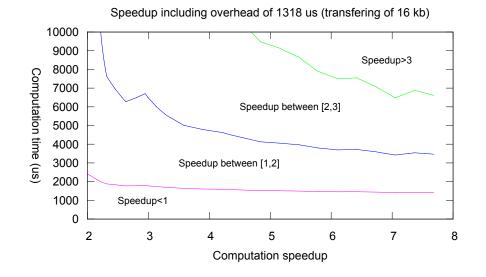

| 3.5 | Possible speedups including memory transfer of 16kb func-<br>tion of speedup and execution time, for the hArtes hardware                                                                                                                                                                                             | 25 |

| 26  | platform.                                                                                                                                                                                                                                                                                                            | 35 |

| 3.6 | Internal organization of firmware used for Xilinx Virtex4 FPGA.                                                                                                                                                                                                                                                      | 42 |

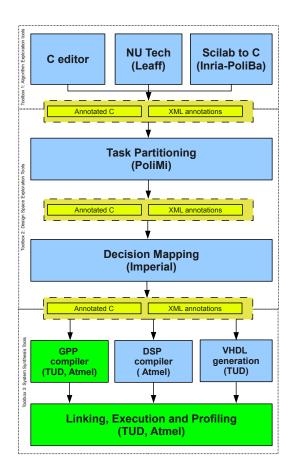

| 3.7 | The hArtes toolchain overall architecture.                                                                                                                                                                                                                                                                           | 50 |

| 3.8  | The initial profile results on Intel x86 architecture for the x264application.59                                                                                                       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.9  | The initial profile results on Intel x86 architecture, without inlineing, for the x264 application                                                                                     |

| 3.10 | Profile on Intel x86 processor                                                                                                                                                         |

| 3.11 | Profile on the ARM processor for the x264 application 61                                                                                                                               |

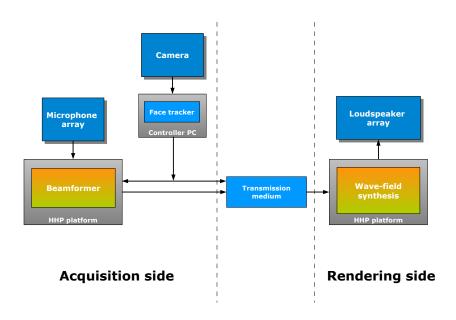

| 3.12 | Immersive Audio Architecture                                                                                                                                                           |

| 3.13 | Profile information on the Intel x86 architecture for the WFS application                                                                                                              |

| 3.14 | Profile information on ARM processor for WFS application 70                                                                                                                            |

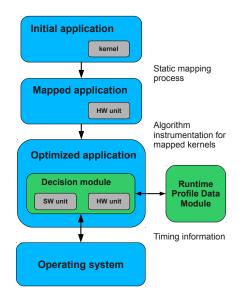

| 4.1  | The overall structure of the AMAP algorithm                                                                                                                                            |

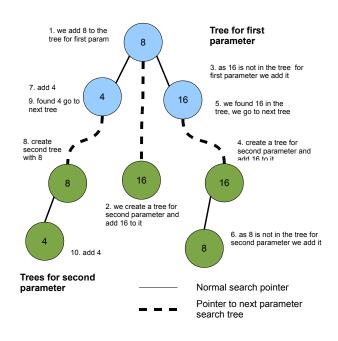

| 4.2  | Search tree for 2 parameter <i>functionC</i>                                                                                                                                           |

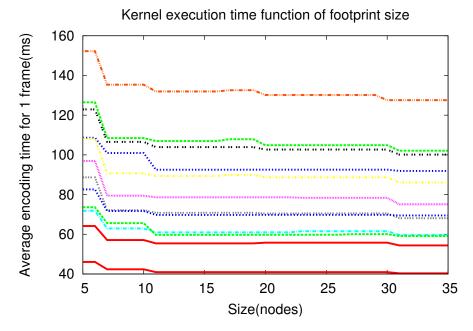

| 4.3  | Algorithm performance for different cache sizes (each line represents a different video)                                                                                               |

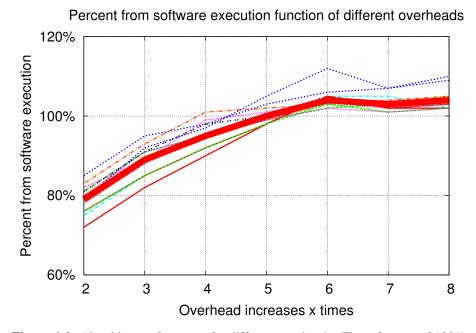

| 4.4  | Algorithm performance for different overheads. The reference<br>of 100% represents software execution. Each line represents<br>a different video, the thick line represents average 93 |

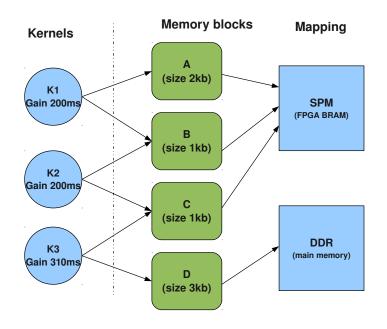

| 5.1  | Motivational example for AMMA algorithm                                                                                                                                                |

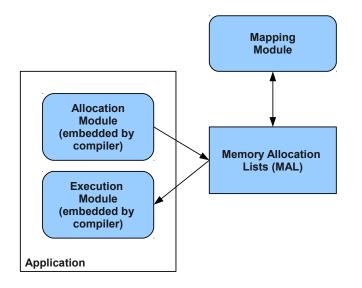

| 5.2  | AMMA infrastructure organization                                                                                                                                                       |

| 5.3  | Code added to functions for stack instrumentation (architec-<br>ture dependent)                                                                                                        |

| 5.4  | Application execution trace before and after AMMA algorithm. 104                                                                                                                       |

| 5.5  | Application execution trace before and after AMMAe algorithm. 107                                                                                                                      |

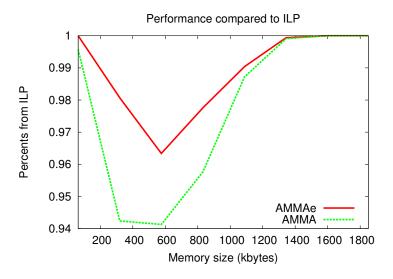

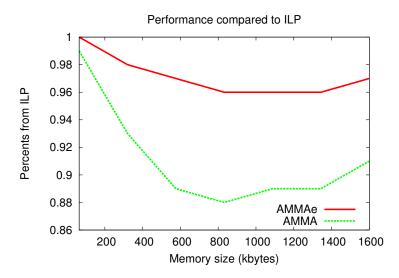

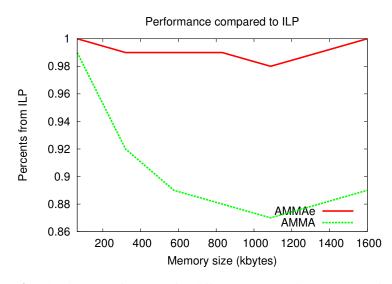

| 5.6  | Algorithms performance for different memory sizes, number of kernels between 5 and 10                                                                                                  |

| 5.7  | Algorithms performance for different memory sizes, number of kernels between 10 and 30                                                                                                 |

| 5.8  | Algorithms performance for different memory sizes, number of kernels between 20 and 60                                                                                                 |

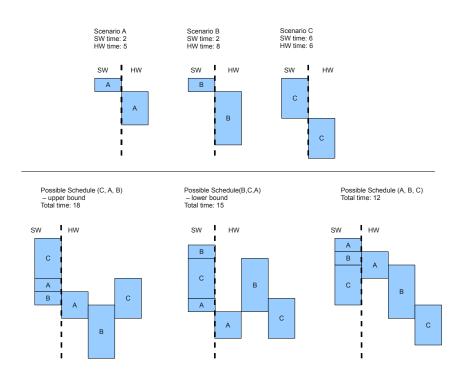

| 6.1 | Example of scenarios (software only scenarios ommited for<br>brevity) and schedules. As this is not fixed at compile-time,<br>each schedule can arise during normal program execution. We<br>give here the upper and lower bound, and also one more of the<br>possible schedules                          | 117 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

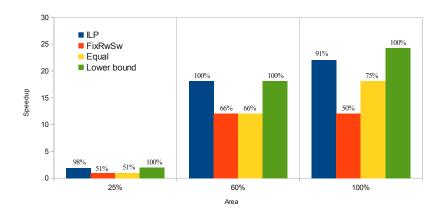

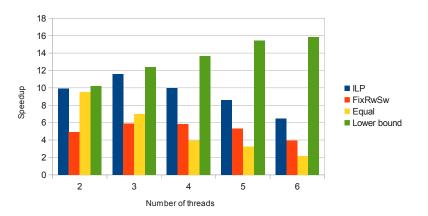

| 6.2 | Beamforming application speedup compared to software ex-<br>ecution. The percentage represents the percentage obtained<br>from the lower bound case (the closest is the percentage to<br>100%,the better).The application contains two threads and<br>each thread contain 8 and respectively 6 scenarios. | 120 |

| 6.3 | Execution time for synthetic applications for different number of threads.                                                                                                                                                                                                                                | 121 |

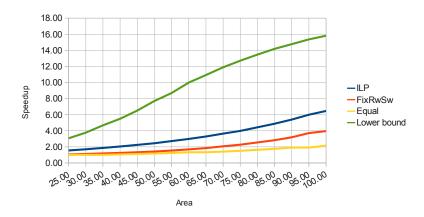

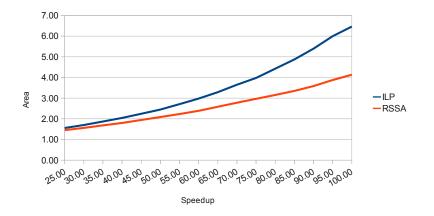

| 6.4 | Synthetic application execution time versus area                                                                                                                                                                                                                                                          | 121 |

| 6.5 | Synthetic applications speedup for different areas used of the FPGA                                                                                                                                                                                                                                       | 124 |

# List of Listings

| 3.1 | Molen pragma on function definition, mapping function <i>func</i> to processing element Virtex4 with implementation identifier 1.                 | 40       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.2 | Molen pragma on function call, mapping that specific call to function <i>func</i> to processing element Virtex4 with implementation identifier 2. | 40       |

| 3.3 | A Molen pragma in the context of OpenMP sections.                                                                                                 | 40<br>43 |

|     |                                                                                                                                                   |          |

| 3.4 | Molen primitives generated for the OpenMP sections example.                                                                                       | 44       |

| 3.5 | Dummy signals used to check the version of CCUs                                                                                                   | 53       |

| 3.6 | Initial definition for x264_pixel_satd functions                                                                                                  | 60       |

| 3.7 | Rewritten function <i>pixel_sad_wxh</i>                                                                                                           | 60       |

| 3.8 | The <i>FracShift</i> kernel                                                                                                                       | 72       |

| 3.9 | Optimized code for <i>FracShift</i> kernel                                                                                                        | 73       |

| 4.1 | Motivational example from x264 application.                                                                                                       | 82       |

| 4.2 | Rejected function example                                                                                                                         | 85       |

| 4.3 | Parameter usage example                                                                                                                           | 85       |

| 4.4 | Example function                                                                                                                                  | 87       |

| 4.5 | Node identification in the tree                                                                                                                   | 87       |

| 4.6 | The AMAP decision module                                                                                                                          | 88       |

| 5.1 | AMMA algorithm.                                                                                                                                   | 103      |

| 5.2 | AMMAe algorithm.                                                                                                                                  | 106      |

| 6.1 | Runtime scenario selection algorithm.                                                                                                             | 122      |

## List of Acronyms and Symbols

| ADAT | Alesis Digital A | udio Tape |

|------|------------------|-----------|

|------|------------------|-----------|

- **AMAP** Adaptive Mapping Algorithm

- **AMMA** Adaptive Memory Mapping Algorithm

- AMMAe Adaptive Memory Mapping Algorithm Extended

- **ARM** Advanced RISC Machine

- **BCE** Basic Configurable Element

- **CCU** Custom Computing Unit

- **CPU** Central Processing Unit

- **DCM** Digital Clock Module

- **DFG** Data Flow Graph

- **DMA** Direct Memory Access

- **DSP** Digital Signal Processor

- **DWARV** Delft Workbench Automated Reconfigurable VHDL Generator

- **ELF** Executable and Linkable Format

- **FPGA** Field Programmable Gate Array

- **FPU** Floating Point Unit

- **gcc** GNU Compiler Collection

- **GPP** General Purpose Processor

- **GPU** Graphics Processing Unit

- **hHP** hArtes Hardware Platform

- **ILP** Integer Linear Programming

- JTAG Joint Test Action Group

- **KPN** Kahn Process Networks

- **LLVM** Low Level Virtual Machine

- MAL Molen Abstraction Layer

- **MEMAL** memory allocation lists

- **RISC** Reduced Instruction Set Computing

- **RSSA** Runtime Scenario Selection Algorithm

- **RTL** Register Transfer Level

- **SDRAM** Synchronous Dynamic Random Access Memory

- **SD** Secure Digital

- **SIMD** Single Instruction Multiple Data

- **SPM** Scratch Pad Memory

- **UART** Universal Asynchronous Receiver/Transmitter

- **USB** Universal Serial Bus

- **VHDL** VHSIC Hardware Description Language

- VHSIC Very-High-Speed Integrated Circuits

- VLIW Very Long Instruction Word

- **WFS** Wave-Field Synthesis

- **XREG** Exchange Registers

# Introduction

MBEDDED systems are a constant presence in our daily life. These systems support and fulfill essential roles in our modern society. From ✓ transport infrastructure, to providing communication facilities, allowing doctors to make better diagnostics, entertain people, almost any aspect of our life is related to them. Embedded electronic devices proved to be an invaluable asset in many aspects of life. Starting from the first microprocessor, the Intel 4004 developed in 1971, the spread of such devices has been exponential. The exponential use is mirrored by an exponential growth in the number of transistors present on a chip. This number doubled almost every 2 years as predicted by the Moore's law - an empirical law postulated in 1965 by the Intel co-founder, Gordon E. Moore. To take full advantage of the large number of transistors and, thus, the available resources, applications constantly evolve and have higher computational demands. Every year, new applications are developed, which require more and more computation power, as, for example, newer video and audio protocols, executing on smaller devices, that consume less power. To show a representative example, nowadays, the volatile memory available in a mobile phone is in the range of hundreds of megabytes, where, 20 years ago, the memory available for a standard desktop system was in the range of megabytes.

The increase in frequency played an important role in the overall performance improvement. The increasing number of transistors was exploited to increase the memory capacities and to move the memory closer to the processing units. Nevertheless this trend is changing: due to the physical limitations it becomes much harder to further increase the frequency. Other paths to improve performance have to be explored by the engineers developing the embedded systems of the future. In modern devices, the main direction of development is heterogeneous multicore computing where, one or multiple specialized cores are used in order to outperform by orders of magnitude the performance of a single core General Purpose Processor (GPP). One of the disadvantages of heterogeneity is that each core has to be designed with an application field in mind. Tasks with a high level of parallelism can take advantage of the multicore and increase by orders of magnitude the throughput of the system. Of course, some platforms might choose to implement only heterogeneous computing, with dedicated cores for each type of task, while others might choose to implement only homogeneous multicores. *It is the author's belief that by combining the two approaches, the best results can be obtained*.

Performance is not the only aspect which needs to be taken into consideration when dealing with embedded systems. Some systems have high deployment costs and may require additional infrastructure work that can not be performed often. Examples are rail signaling systems and surveillance systems in buildings or metro among others. As a result, upgrade capabilities of these systems need to be taken into account at design time as well. Traditionally this was a task accomplished by software upgrades, relying on the possibilities of the GPP, which is many different tasks with a good level of performance. If software upgrades are not possible, a newer system needs to replace the old one. Over the last years, Field Programmable Gate Array (FPGA)s [75] have become very popular and can be used to address this problem. By using this technology, hardware components can be upgraded in place, extending in this way, the life span of existing products. Additionally, this improves reliability, as bugs in the hardware design can be corrected even after the deployment of the system.

The development of software for such systems would be very hard without the availability of tools and operating systems. The role of tools is to help the developer to focus on the relevant aspects of the problem, while the tools take care of all the specific details related to the platform in use. During the development of a product, many aspects play an important role. For example, the translation of the high-level description of the problem to an implementation, the verification of the implementation, the profiling of the application. For each of these tasks, tools have been developed to ease the work of the developers. At runtime, it is the responsibility of an operating system to manage the various resources and, possibly, the multiple applications running concurrently. This further increases the level of flexibility during the design of applications, and it facilitates even more the work of the developers.

In this thesis, we propose improvements to the interaction between the compile-time tools used by developers, the operating environment and the hardware platforms. The purpose of these improvements is to take full ad-

vantage of all the possible optimizations, that might be hidden if the analysis is performed only at compile-time, only for one hardware platform or only by the operating system.

### **1.1 Problem Overview**

Existing computing platforms come in families. This is mainly due to the considerable efforts involved during the development of a platform, and different needs for different computing areas. These families share a general architecture and processing elements, but are customized for different scenarios. For example, some of these platforms are low-cost models with less functionality, or they are hardened platforms, which can work in a wider temperature range. Having a family of platforms has both advantages and disadvantages. An example of such an advantage is that the expertise for developing for a family of platforms can be reused. A disadvantage is that the process of choosing a variation and then the mapping of an application becomes more complex. Some examples of variations that can make the mapping problem more complex are: the presence or absence of a specific processing core, the different operating frequencies of the various components, the different sizes for memory and/or caches, and the different input/output ports available.

The developers, usually divide the applications in several parts and assign each of them to a processing core, while managing the communication needed between the different elements. This process is usually based on an analysis performed on a specific platform variant and with a particular data set. The tools provide guidance for each aspect of the process and allow the designer to perform critical choices. Usually, the adaptability to platform variants is not the primary concern. This happens because at the moment of development time, the different variants might not even be available on the market. All of this can result either in an increased development time or in an inefficient use of resources. Additionally, in dynamic systems, the interaction between applications is a deciding factor in the overall system performance. This can be managed manually, by the developer or the system administrator. Special policies can be implemented in the operating system to cope with each type of situation. Anyhow, with a manual approach, such efforts are targeted to instances of the problem and do not give a comprehensive solution. A more comprehensive solution would be to provide tools producing applications which adapt to the platform and the execution environment. By using compile-time information, these tools can improve the efficiency and they can reduce the time spent in the development process.

In this dissertation we will address specific sub-problems of the embedded systems development. These are specific because of the architecture choice (heterogeneous) and optimization methods used (runtime). A high level overview of these problems is:

- Mapping what is the most efficient resource to map a computation on, taking into account the current state of the execution environment?

- Communication how can we reduce communication between the various processing elements?

- Parallelism how can we exploit the parallelism provided by heterogeneous platforms?

Each of these problems will be outlined in more details in Chapter 3. Besides these problems, the field of embedded computing faces several other problems among which we would mention scheduling, energy consumption optimization, data representation optimization, choosing the model of computations, etc. Although these problems are important for the field, we focused on that set of problems that were the most stringent for our platform and applications.

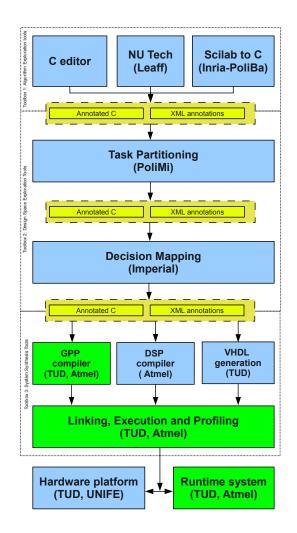

It should be noted that the work in this thesis was done in the context of hArtes project [16], a project focused primarily on performance and toolchain development rather than, for example, power efficiency. The hArtes project was an Integrated Project funded by the European Union, whose purpose was to lay the foundation for a holistic approach used when developing complex embedded systems. A high-level sketch of the content of hArtes project is given in Figure 1.1. The work in this thesis influenced mostly the modules/tools represented in green.

### **1.1.1 Dissertation Scope**

An application can be optimized in many ways. In this dissertation, we only focus on optimizations involving compile-time analysis coupled with runtime decisions. We consider that a platform can change in time and thus runtime optimizations decisions are beneficial. The platform changes could include hardware upgrades or additional software installation. As we focus on embedded devices, the runtime decision algorithms that we develop have to run in a constrained environment and, therefore, need to be computationally fast. Summarizing, we focus on algorithms with the following chrachteristics:

Figure 1.1: The hArtes project toolchain and platform

- The algorithms need a significant analysis of the application at compiletime, which can only be performed by a compiler. Examples are, the identification of parameters, that influence the control structure of the function, or parameters only used to access data.

- Optimization decisions can not be taken at compile-time. This can happen due to multiple reasons. We outline the main two reasons in the following. First, the execution time of a function cannot be completely

determined at compile-time, where, for example, loop bounds or conditional flags are not known. Second, the execution environment can change at runtime, in a way that is not easily controllable. Examples of this are multiple applications running concurrently, hardware changes in the platforms, or changes in operational parameters (battery level).

• The algorithms are affected by the heterogeneity of the platform. Examples of this include different types of processing elements or non uniform memory hierarchies.

One set of applications which benefit from the optimization algorithms with the above characteristics are complex media applications that run on embedded systems, for example in-car audio and video systems.

Additionally, for experimental purpose, the validation of the proposed algorithms assumes the following:

- The platform used follows the Molen machine organization (outlined in Chapter 2).

- The tools used to compile the applications for such a platform adhere to the Molen programming paradigm.

- Access to the source code of the compilers and operating system of the platform is available.

- The applications can be executed on the target platform and profiled using real data.

- The designer can manually control the tools to a certain extent assuming a semi-automatic procedure.

We furthermore exclude from the scope of the thesis a number of topics, not because they are not important but would make the complexity of the problem unmanageble. More specifically we do not look at: hardware/software co-design, partitioning, run-time reconfiguration area management, scheduling, power optimizations, etc. Some of these issues were studied in the hArtes project but were never included in the final toolchain. This thesis focuses primarily on some of the operational and implementable results of the hArtes project.

### **1.1.2** Contribution of the thesis

The main contributions of the work proposed in this dissertation are the following:

- The definition and development of a mapping algorithm able to identify on which processing element a particular computation can be computed in the shortest amount of time. Compared to existing mapping algorithms, the mapping decision is delayed until runtime, when, by using data gathered at compile-time, a decision that will minimize the execution time can be made. We will show later in this dissertation that this organization allows an algorithm to take advantage of some optimization possibilities lost in case the analysis is performed only at compiletime, even if the analysis is done by an expert developer. In terms of experimental results, the application of the mapping algorithms results in improvements between 5% and 43% for the whole application, when compared to a static decision algorithm which can only decide for a specific computation to either run it in hardware or software. The wide variation is due to the fact that the application execution time is strongly linked to the input data, for example, in our case, videos containing a variable level of motion. Additionally, we outline the behavior of the algorithms in case the characteristics of the platform change at runtime. The characteristic that we analyze is the overhead involved in invoking a processing element. This situation might arise if, for example, other applications use the same communication resources between the GPP and the FPGA. Our finding is that the obtained performance gradually degrades and it is close to the maximum performance achievable given the circumstances.

- The development of a memory allocation algorithm targeted to heterogeneous platforms. This algorithm uses the application execution history and the characteristics of the computations, to decide, at runtime, the best memory allocation in the current memory hierarchy. The use of the memory allocation algorithm results in an overall speedup of 18% of the H.264 video encoding application. We present two variations of the same algorithm. The first can be executed very fast, while the second provides better application performance. By using synthetic applications, we have shown that both algorithms are within 14% and respectively 5% of the optimal solution, computed using an ILP approach for the same problem. The application speedup obtained for the synthetic

application was between 2x and 6x.

- The development of a scenario based selection algorithm for parallel applications. This algorithm decides which combinations of parallelism is better, in case multiple applications or threads are competing for the same resources (i.e. FPGA area). For the selection of the scenario used in a system with multiple threads applications, we first give an ILP formulation of the problem. Then, with the ILP as a reference we give a runtime algorithm which is within 7% of the ILP solution and is better than existing solution by 21% to 92% in terms of application performance.

- The description of the integrated toolchain that uses these algorithms to improve performance on a heterogeneous platform, based on the Virtex4 FPGA. The problems that appeared during the development of such a framework are discussed and the chosen solutions are presented in detail.

### **1.2** Dissertation Organization

The work proposed in this dissertation is organized in chapters. Chapter 2 analysis the existing related work. The three main domains for our work, namely computing platforms, toolchains and execution environments, as well as the Molen programming paradigm and machine organization are described in detail. The chapter continues with the analysis of the mapping and the memory allocation algorithms. Finally, we present the work related to the parallel execution of applications on heterogeneous reconfigurable architectures.

In Chapter 3, we present the work done in the context of the hArtes project. The work includes supporting the development of a custom heterogeneous board and developing a toolchain that supports such a board. First, we present the hardware platform and then continue with the essential ideas behind the toolchain. We will also present a thorough analysis of the applications used as motivational examples for the algorithms presented in this thesis. These are real-world applications, and the evaluation process is the same process that was used during the development of the hArtes toolchain. All the information is collected at runtime, by using realistic input data. Finally, the chapter provides a list of problems that will be addressed in the following chapters.

In Chapter 4, we present a mapping algorithm, which decides if a computation should be performed on the GPP of the platform, or on any other of the processing elements. The computations used as a motivational examples are dynamic by nature and their execution time varies a lot depending on the parameters with which the computation is called. These are not the typical applications that were implemented in the embedded systems in the past, but with these devices becoming more and more used, more high level applications have to be targeted using automated tools to embedded platforms. Building flexibility into applications lowers the development cost associated with re-targeting to a new platform. Based on the execution time obtained for various input data, a runtime module decides if a function should be executed either on one co-processing element or on the GPP. To do this, it uses a 'software' cache in which the execution time for each processing element is stored. Then, based on this information, it makes the decision on where to run the computation. The benefit of such an approach is that it can adapt to various conditions changes, like, for example, frequency lowering of a processing element in case of low power, or even a complete shutdown of some of the processing elements.

A runtime memory allocation algorithm that relies on instrumented code is presented in Chapter 5. When allocating a memory block, for a complex memory hierarchy there can be several memories where the block can be allocated. The decision of which memory to place the block to obtain the best performance is not an obvious task. The memory block will be used during the application execution by one or more computations. At their turn, each of those computations can use multiple blocks. For each computation, multiple implementations for different processing elements can be available. However, in order to run on some processing elements, all the used memory blocks have to be in the scratch pad memory of the element before the computation can start. The result is that transfers between memories have to be performed during the execution, which will affect the total execution time. By tracking at runtime the memory used in each computation, we can determine an efficient way of allocating it to the various scratch pad memories. By using a simple persistence mechanism, we can improve subsequent application executions by performing future allocation, based on the saved profiling data.

We continue in Chapter 6, by presenting the issues that emerge when trying to map an application with multiple threads to a heterogeneous reconfigurable platform. An important difference from a platform with multiple identical cores is that, for a reconfigurable platform, the number of cores and memory organizations can be different and vary over time.

Conclusions are presented in Chapter 7, where we summarize the main contributions of this thesis and we discuss the relation between the presented algorithms. Finally, we propose a list of open questions and future research directions.

# 2

# Background and Related Research

N this chapter, we define the research context of the work presented in the following chapters. More specifically, we discuss the relations between the problem analyzed and the relevant concepts involved, such as platforms, toolchains and operating systems. We present the machine organization and the programming paradigm on which the following chapters are based on. Finally, we present the related research in the field.

### 2.1 Research context

The problems presented in the following chapters are part of a complex research context, which in the following is discussed from three points of view: the hardware platforms, seen at the level of processing elements and memories, the applications that have to run on those platforms and, finally the toolchain which has to transform the application into binary code suitable for a platform. We address each of these aspects separately.

### 2.1.1 Computing Platforms

Computing platforms have evolved in time from basic platforms with Central Processing Unit (CPU) and one type of memory to complex systems with multiple heterogeneous components inter-connected by various elements such as buses and networks-on-chip. These heterogeneous components fulfill many roles, and, usually provide an interface between the various peripherals while increasing performance. A classical example of components used to increase performance are the Graphics Processing Unit (GPU)s [26], which represent a highly customized type of Single Instruction Multiple Data (SIMD) processors. These processors are specialized for different types of computations which they perform much faster than to classical CPU. Another hardware component used for processing is the Field Programmable Gate Array (FPGA) [75]. One of its biggest advantages over hardwired circuits is its capability to change the hardwired connections even after it has been shipped to customers. This means improvements and bug fixes are possible both for the hardware and the software part of the system. Over the years, memory systems evolved as more transistors could be integrated easily on the same die. Caches became larger and multilevel cache hierarchies appeared [70] [33]. Nevertheless, the increase in number of transistors had also made communication inside the chips a serious bottleneck [89]. One solution to this problem is the development of networks-on-chip capable of providing support for fast data transfers [76]. Another solution, used also in this thesis, is to optimize the memory allocation and thus reduce the need of transfers.

### The Molen Machine Organization

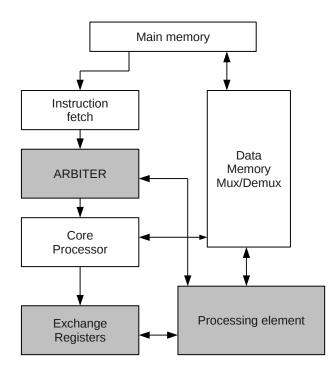

Well-known problems for heterogeneous computing platforms are the integration of different components and the programmability of the system. In our research, we are following the Molen machine organization to address these issues [82]. This organization is generic and not restricted to any particular architecture. Its main purpose is to allow a virtually unlimited number of extensions of a base General Purpose Processor (GPP) to be implemented with the least amount of effort compared to redesign manually the system to include each new extension. The Molen machine organization is presented in Figure 2.1.

This architecture is build on the processor - coprocessor model. A core processor, which is a GPP, executes the programs and, for certain computations, it invokes other processing elements. In Figure 2.1, we see a generic processing element that could be, for example, a FPGA or a Digital Signal Processor (DSP). The "Arbiter" block represents the component responsible for the identification of the special Molen primitives, and it is responsible for redirecting them to the processing elements. An Exchange Registers (XREG) block is tightly connected between all the processing elements and the GPP for fast data exchange. The tightly integration of the XREG block enables a fast communication path between the GPP and the different processing elements, avoiding the high latencies imposed by the memory accesses.

Figure 2.1: The Molen machine organization.

# 2.1.2 Toolchains

The notion of a tool to help developers to use computing system appeared as early as 1954 [7]. Compilers were the first tools that appeared. The compiler's task is to translate the code from a high-level description to a low level description, specific to a machine or platform in use. Later, as the development process become more complex, monolithic tools were divided in sub-tools addressing specific tasks. They evolved, for example, into frameworks for lifelong program analysis and transformation as, for example the Low Level Virtual Machine (LLVM) [52], compilers that target multiple architectures as the **GCC!** (**GCC!**) [34], assemblers, and linkers among others. The connection of all these tools together, resulted in the creation of a toolchain. Nowadays more and more tools are added to toolchains, in order to improve the development process. With increasingly complex architectures and applications, the toolchains are seen today as one of the key enabler of a specific platform and even architectural paradigm [47].

The traditional compilation toolchains consider the architecture to be fixed, without significant changes during the lifetime of the product. With the current platforms, this is not always the case. The best examples are the reconfigurable architectures in which most of the components of the platform can change in different ways. The development of separate toolchain for each possible combinations is not a viable approach. On the other hand, the development of a toolchain for a specific platform means that optimization opportunities are limited. By loosing optimization opportunities, the platform can not be fully utilized, which, in turn, means that resources are lost, and the economic viability of the whole system is less than possible. A solution to these problems is to extend the current toolchains in such a way that adaptability to different platforms can be taken into consideration. This, usually, involves modifications at multiple levels. For example, by inserting new annotations at the programming languages level, or by providing a linker able to link the different processing elements.

One partial solution to the problem of developing tools for different architectures and paradigms are the reconfigurable compilers frameworks. These are compilers frameworks that allow developers to build compilers for a new architecture in a short amount of times. In this category we mention the open source compiler **GCC!** [34] which targets a large sets of architectures, the CHESS compiler which focuses on fixed point DSP processors [80], RECORD compiler [55] and CoSy compiler development system [24].

#### **The Molen Programming Paradigm**

The Molen programming paradigm was developed in order to efficiently exploit the Molen machine organization. This programming paradigm relies on five primitives that link the processor of a system with the heterogeneous cores [82]. Although special consideration was given to FPGAs in its initial design, the paradigm can be successfully employed for other types of processing elements as well as as shown later in Chapter 3. The programming paradigm relies on the sequential consistency model for memory access.

A set of predefined instructions added to the instruction stream of the GPP manages the computations executed on the different processing elements. These five primitive instructions are SET, MOVET, MOVEF, EXECUTE and BREAK. The original proposal included two SET instructions, namely a partial SET and a complete SET. Anyhow we consider them as one entity as their

role is similar. In the following, we summarize in short the role of each instruction:

- SET it configures/loads the computation on the processing element. This is an information the runtime system can use to prepare in advance for the actual execution;

- MOVET/MOVEF it transfers the parameters/result to/from the XREG.

- EXECUTE it starts the execution.

- BREAK it checks if the execution has finished.

A detailed discussion on these primitives in the context of research is presented next, in Chapter 3.

# 2.1.3 The Applications

Another aspect that has to be taken into account during the analysis of the problem is represented by the applications, which are the input of toolchains. Despite a lot of research in the field of programming languages and modeling languages many applications for embedded systems are still written in plain C [83]. This is because the programmers need a lot of control on the inner workings of the system, to obtain performance and to adapt to new platforms, without relying on complex and, possibly, unreliable middle-ware. The companies are reluctant to rewrite the code in a new language that works for some niche platforms as the adaptation of the legacy code to new architectures can be problematic.

The C language was developed between 1969 and 1973 as a programming language for system software [74]. Due to the fact that at the moment of its conception the architectures were rather different from today architectures, two concepts are totally missing from C, which are needed when porting an application to modern embedded systems. These concepts are mapping (of memory and processing) and parallelism. This can be seen as an advantage as programs remain generic, but also as a disadvantage as programs must be adapted to meet performance. Additionally, even if not present in the language, several solutions exist to augment existing C applications with this kind of information.

To summarize in one phrase our problem we can say: how can we implement complex C applications on heterogeneous platforms, which may evolve in time, without loosing flexibility or performance? As porting an application to a new platform involves many problems, in the following we limit our analysis to a limited subset: partitioning, memory allocation, and scheduling. Our solutions are specific to each objective discussed, although the main idea is the same for all: to integrate parts of the optimization algorithms in the application and to delay the decision-making process, when possible, until runtime. Then, when the exact architecture is known, the best decision can be taken giving the best performance for the application.

# 2.2 Related Research

Recently, frameworks [25] [3] were proposed to make applications more adaptable to the platforms. The framework presented in [25] proposes a system that follows the cycle "sense, reason, react". The system is organized as a decision engine coupled with software and hardware components. When using an FPGA, the framework can hide the details of the implementation from the developer. Examples of such implementation detail is the partial reconfiguration capability. Nevertheless, the exact decision engine has to be implemented on a per application basis. One such example is presented in [29], where a pulse detection system uses the reconfigurability of the FPGA to adapt to changes in the environment. The framework presented in [3] adapts the thread model to heterogeneous embedded systems by defining a Hardware Thread Interface. This type of interface enables platform independent user level semantics that promote thread migration across the system.

Independent of the frameworks mentioned, there is a large volume of research related to the problem this dissertation addresses. Classifying this work will help in providing a clear image of the related research. As our work is focused on runtime optimization, we consider a classification based on the moment at which the optimization is done, coupled with a classification based on the area in which the optimization is applied.

From a time point of view, optimizations can be divided in off-line (compiletime) optimization and on-line optimization. Then, according to the problems defined in the previous section, we have related work dealing with the memory optimization in embedded systems and we can divide this optimization into memory related problems (cache and scratch pad memory), partitioning problems and parallelism and scheduling problems.

#### 2.2.1 Memory Related Problems and Solutions

An ideal processing element would have an infinite amount of memory with instant access. However in reality, as the access time of the memory decreases, its cost increases and size decreases. The typical scenario is that in a system, the fastest memories are the smallest [39]. Various mechanisms are used to map parts of the application data to the memories present in the system. In the following we will explain the techniques used and their application to the case of reconfigurable heterogeneous hardware.

#### **Cache Memories**

Cache memories are a mechanism used to hide the long access time needed to access external memories [39]. This is achieved by relying on the spatial and temporal locality of the data accessed by a program. One of the biggest advantages of the caches is that they improve the execution time in a transparent way. The programmer does not need to make any modification in the source code of the application to take advantage of a cache. This advantage comes at the cost of a larger area occupied on the chip.

When used together with an FPGA, caches can enable speedups of up to 7.8x (geometric mean) and up to 4.1x reduction in power when compared to a general purpose processor [71]. This is achieved by performing a static alias analysis on the code, with the help of the 'restrict' keyword. The obtained results are good as the authors target HPC applications that do not contain complex aliasing. As the analysis is performed at compile-time and relies on static analysis, it is not able to deal with the complex situation encountered in our test applications. In our case, depending on the input data, different memory blocks are used during the program execution.

When compared to scratch pad memories, caches can be less efficient in terms of power and performance. This is shown in [9], where, by using an instruction simulator and power estimator, it is shown that Scratch Pad Memory (SPM) are on average 40% more energy efficient than caches. This is a an implication of the fact that a cache contains more transistors compared to an SPM of the same size, needed to implement the various extra logic, for example, tag arrays.

# **Virtual Memories**

Virtual memory is a technique invented to manage multiple levels of memories, especially when a program can not fit completely in the first level of memory. It organizes the memory in pages and provides address translation between the virtual addresses used by the processor and the real address where the data can be found. Other advantages of virtual memory are protection of processes and sharing of memory and program relocation [39]. For Virtex and Altera platforms, in [86], Vuletic et al. present a unified virtual memory manager. This manager allows both hardware and software processing elements to use the benefits of virtual memory when accessing memory.

#### **Scratch Pad Memory**

SPMs have the same function as caches, although they are managed by the application developer/toolchain directly. If they are used efficiently, they perform better than caches in speed, energy efficiency, and in the area occupied [2] [9].

For the specific case of loop nests, where dependencies can be analyzed at compile-time, [48] provides an algorithm to design a custom SPM hierarchy. In case the memory hierarchy is already given, an algorithm that transforms the loop to better fit the hierarchy is presented. Both algorithms rely on the availability of information about dependencies in the loops, and can not be used for generic C code.

For specific cases, static solutions exist which provide significant performance improvements (more than 6x) by using a careful allocation of memory resources on the FPGA [13].

A low level partitioning algorithm between several SPM memories of the system is presented in [92]. The application model is a Data Flow Graph (DFG), where each node represents a coarse grained task. A special edge is inserted in the graph to model a loop carried dependency. Each node accesses a set of variables. By using two algorithms, HAFF (High Access Frequency First) or GVP (Global View Prediction), the algorithm maps each variable to one of the SPMs in the system, and then schedules the tasks in the DFG on each processing element. Additionally, they utilize a loop pipeline scheduling algorithm (RSVP) to reduce dependencies for scheduling. However, in the paper they do not consider heterogeneous architectures, and external memories are not included in the presented partitioning and scheduling schemes.

A big part of the previous work on SPMs, usually considers just one processing

element, like [6], which gives an Integer Linear Programming (ILP) formulation of the problem of mapping program variables to the SPMs. The first class of variables considered is the class of global variables. Two variants of the algorithms are presented for the stack variables. The stack variables differ from the global variables because they have a limited lifetime. The first variant of the algorithm considers the stack of one procedure as one 'aggregated' variable. The second approach allows each variable to be allocated to a different memory. The authors compare the execution time using a SPM capable of holding all the application variables to the execution time using an SPM 20% smaller than the previous one. The execution time for the small SPM is only 1.5x bigger compared to the use of a bigger SPM, which shows the effectiveness of presented techniques.

[40] presents a static method to determine the memory bank where a variable should be placed, based on the number of accesses and conflicts with the other variables. The proposed algorithm supports a complex memory hierarchy, which can be composed by a combinations of caches and application managed SRAMs. For caches, a 90% hit rate is assumed by the partitioning algorithm. In a similar way to the previous approach [6], the information used as input to the partition algorithm is provided by a detailed profiling, which gives the number of accesses for each variable. For the studied application the authors test that by changing the input data, the results are not affected more than 5%. Nevertheless, this does not hold for any application, as we will show in Chapter 3.

In [79], an algorithm is presented that determines the program points where local (stack) variables have to be transferred to/from main memory to the SPM. Program points candidates are the start of each procedure and the start of every loop in the program. Timestamps are given to each node, based on the order of their execution. Next, by using an iterative algorithm, the set of variables that are brought to the SPM and the set of variables that are written back to the DDR are determined for each program point, based on a cost model. This algorithm does not take into account dynamically allocated memory, and it does all the computations at compile-time. If the system configuration changes, the algorithm has to be applied again and the application recompiled.

In contrast to previous work, [14] instruments just the dynamic memory management primitives, such as *malloc* and *free*, along with all accesses to memory. Then, the developers collect data by providing the application with relevant inputs. An algorithm identifies block transfers and determines for each block transfer if it is better to perform it using DMA or using normal memory transfer. The disadvantage of this approach is that it targets only dynamic variables and it relies on static information.

A method at the boundary between static and dynamic allocation is presented in [62]. The authors perform a load time optimization that places the stack data in one of the memories using information computed at compile-time. The method starts with a profiling phase where, for each variable, a frequency per byte is measured using multiple input sets. The second phase consists of compiling and linking, which do not embed the actual variable addresses in the code, as these will be determined at runtime. The last phase is represented by the embedded loader, which determines the size of the SPM and, then, decides where each variable should be placed.

A dynamic SPM stack manager that reduces power consumption is presented in [49]. This manager operates at the granularity of function stack frames. The main advantages are that it does not need profile information, and it can adapt to different SPM sizes. Based on the stack frame sizes and on the SPM size, it can determine for which function calls the SPM stack manager calls needs to be inserted. These calls manage the swap-in/swap-out of stack frames to/from the SPM memory. Another dynamic SPM manager is presented in [23]. This work targets multi-application environments, but assumes there is only one processing element.

By providing both the heap and the stack management, [22] describes an iterative algorithm that determines the allocation of stack, global and heap variables and introduces transfer code when necessary. The method uses only compiletime heuristics to determine which is the best place to allocate blocks and where to transfer them from fast SPM to slower DDR.