#### Delft University of Technology

Faculty of Electrical Engineering, Mathematics, and Computer Science Department of Quantum & Computer Engineering

# Enabling High Performance Posit Arithmetic Applications Using Hardware Acceleration

Thesis by: Laurens van Dam

Advisors:

Prof. dr. H. P. Hofstee Dr. ir. Z. Al-Ars

Committee:

Prof. dr. H. P. Hofstee (Chair)

Dr. ir. Z. Al-Ars Dr. ir. M. Möller

# Enabling High Performance Posit Arithmetic Applications Using Hardware Acceleration

#### THESIS

submitted in partial fulfillment of the requirements for the degrees of

MASTER OF SCIENCE

in

COMPUTER ENGINEERING

Вr

**EMBEDDED SYSTEMS**

by

Laurens van Dam born in Spijkenisse, The Netherlands

to be defended publicly on September 17, 2018 at 15:00.

Student number: 4203321

Submission date: September 10, 2018

Responsible professors: prof. dr. H. P. Hofstee IBM Research, TU Delft

dr. ir. Z. Al-Ars TU Delft

Thesis committee: prof. dr. H. P. Hofstee IBM Research, TU Delft, jury chairman

dr. ir. Z. Al-Ars

dr. ir. M. Möller

TU Delft, jury member

TU Delft, jury member

CE-MS-2018-07

ISBN 978-94-6186-957-9

Quantum & Computer Engineering

Faculty of Electrical Engineering, Mathematics, and Computer Science

Delft University of Technology

Mekelweg 4

2628 CD Delft

The Netherlands

### **Abstract**

The demand for higher precision arithmetic is increasing due to the rapid development of new computing paradigms. The novel posit number representation system, as introduced by John L. Gustafson, claims to be able to provide more accurate answers to mathematical problems with equal or less number of bits compared to the well-established IEEE 754 floating point standard.

In this work, the performance of the posit number format in terms of decimal accuracy is analyzed and compared to alternative number representations.

A framework for performing high-precision posit arithmetic in reconfigurable logic is presented. The supported arithmetic operations can be performed without rounding off intermediate results, minimizing the loss of decimal accuracy. The proposed posit arithmetic units achieve approximately 250 MPOPS for addition, 160 MPOPS for multiplication and 180 MPOPS for accumulation operations.

A hardware accelerator for performing Level 1 BLAS operations on (sparse) posit column vectors is presented. For the calculation of the vector dot product for an input vector length of  $10^6$  elements, a speedup of approximately  $15000\times$  compared to software is achieved. The decimal accuracy is improved by one decimal of accuracy on average compared to posit emulation in software, and two additional decimals of accuracy are achieved compared to calculation using the IEEE 754 floating point format.

A study of the application of posit arithmetic in the field of bioinformatics is performed. The effect on decimal accuracy of the pair-HMM forward algorithm by replacing traditional floating point arithmetic with posit arithmetic is analyzed. It is shown that the maximum achievable decimal accuracy using posit arithmetic is higher compared to the IEEE floating point format for the same number of required bits.

The design of a hardware accelerator for the pair-HMM forward algorithm using posit arithmetic is proposed for two different interfaces: a streaming-based accelerator and an accelerator interfacing with Apache Arrow columnar data, both connected by the CAPI (SNAP) platform. Overall, the posit number format beats the IEEE floating point number format in terms of decimal accuracy, ranging from an improvement of 0.5 to 1 additional decimal of accuracy for the performed test cases. A throughput of 1.6 and 1 giga cell updates per second is measured for both accelerator implementations, respectively.

## **Preface**

Before you lies the final product of my work of the last nine months, titled "Enabling High Performance Posit Arithmetic Applications Using Hardware Acceleration".

I could not have accomplished this work without the strong support from people I care about. First, my parents, who have always supported me with love and understanding. Secondly, my friends, who were there to support me during my endeavors (and to distract me once in a while).

My special thanks goes to Jinho Lee for the help with testing and debugging my hardware designs.

Thank you Matthias Möller for agreeing to be part of the graduation committee and providing me with useful research directions.

Lastly, I would like to thank my thesis supervisors, Peter Hofstee and Zaid Al-Ars, each of whom has provided patient guidance throughout this research process.

Thank you all for your unwavering support.

Laurens van Dam Delft, The Netherlands September 10, 2018

## **Contents**

| Li | st of 1 | Figures |                                       | 11 |

|----|---------|---------|---------------------------------------|----|

| Li | st of   | Tables  |                                       | 13 |

| 1  | Intr    | oductio | on                                    | 17 |

|    | 1.1     | Motiv   | ation                                 | 17 |

|    | 1.2     | Thesis  | S Aim & Contributions                 | 18 |

|    | 1.3     | Thesis  | Outline                               | 20 |

| 2  | Bacl    | kgroun  | d                                     | 21 |

|    | 2.1     | The U   | num Arithmetic Framework              | 21 |

|    |         | 2.1.1   | Type I Unum                           | 21 |

|    |         | 2.1.2   | Type II Unum & SORNs                  | 22 |

|    |         | 2.1.3   | Type III Unum (Posit)                 | 25 |

|    | 2.2     | Featur  | re Comparison of IEEE Float and Posit | 28 |

|    |         | 2.2.1   | Not-A-Number (NaN)                    | 28 |

|    |         | 2.2.2   | Negative Zero and $\pm \infty$        | 29 |

|    |         | 2.2.3   | Critique                              | 29 |

|    | 2.3     | Posit A | Arithmetic Hardware Implementations   | 30 |

|    | 2.4     | Alterr  | native High-Precision Number Formats  | 31 |

|    |         | 2.4.1   | Decimal Floating Point                | 31 |

|    |         | 2.4.2   | Boost Multiprecision                  | 32 |

|    | 2.5     | Comp    | iler Optimization                     | 32 |

|    |         | 2.5.1   | Optimization Level                    | 32 |

|    |         | 2.5.2   | Subnormal Numbers                     | 33 |

|    |         | 2.5.3   | Multiply-Accumulate                   | 34 |

|    | 2.6     | Meası   | are of Decimal Accuracy               | 34 |

|    | 2.7     | Apach   | ne Arrow                              | 35 |

| 3  | App     | licatio | ns in Bioinformatics                  | 37 |

|    | 3.1     | Pair H  | (Iidden Markov Model (Pair-HMM)       | 37 |

|    |         | 3.1.1   | Pair-HMM Forward Algorithm            | 39 |

|    |         | 3.1.2   | Pair-HMM Hardware Acceleration        | 41 |

8 CONTENTS

|   | 3.2   | GATK                                              |

|---|-------|---------------------------------------------------|

|   | 3.3   | Pair-HMM in Float and Posit Representation        |

|   |       | 3.3.1 Quantitative Analysis                       |

|   |       | 3.3.2 Phred Scale                                 |

|   |       | 3.3.3 Pair-HMM Forward Algorithm                  |

| 4 | Fran  | nework for Hardware Posit Arithmetic 5            |

|   | 4.1   | Framework Design                                  |

|   |       | 4.1.1 Posit Extraction                            |

|   |       | 4.1.2 Posit Normalization                         |

|   |       | 4.1.3 Posit Adder                                 |

|   |       | 4.1.4 Posit Multiplier                            |

|   |       | 4.1.5 Posit Accumulator                           |

|   | 4.2   | Hardware Implementation                           |

|   | 4.3   | Evaluation of Framework Accuracy & Performance    |

|   |       | 4.3.1 Decimal Accuracy                            |

|   |       | 4.3.2 Performance                                 |

|   | 4.4   | Summary                                           |

|   |       |                                                   |

| 5 |       | t Vector Arithmetic Accelerator                   |

|   | 5.1   | Accelerator Design                                |

|   | 5.2   | Hardware Implementation                           |

|   | 5.3   | Evaluation of Performance & Accuracy              |

|   |       | 5.3.1 Vector Operations                           |

|   |       | 5.3.2 Gram-Schmidt Process                        |

|   | 5.4   | Summary                                           |

| 6 | Pair- | -HMM Posit Accelerator 7                          |

|   | 6.1   | Overall Design                                    |

|   |       | 6.1.1 Processing Element (PE)                     |

|   |       | 6.1.2 Accumulator                                 |

|   | 6.2   | Streaming Implementation (CAPI)                   |

|   |       | 6.2.1 Accelerator Design                          |

|   |       | 6.2.2 Hardware Implementation                     |

|   |       | 6.2.3 Evaluation of Performance & Accuracy        |

|   | 6.3   | Higher-Accuracy In-Memory Hardware Implementation |

|   |       | 6.3.1 Accelerator Design                          |

|   |       | 6.3.2 Hardware Implementation                     |

|   |       | 6.3.3 Evaluation of Performance & Accuracy        |

|   | 6.4   | Summary                                           |

| 7 | Con   | clusions 9                                        |

| ٨ | Dair  | -HMM Pseudocode 10                                |

| CONTENTS | 9 |

|----------|---|

|          |   |

| В   | Posit Field Widths for Arithmetic Framework 1 |               |     |  |  |

|-----|-----------------------------------------------|---------------|-----|--|--|

|     | B.1                                           | Regular Value | 103 |  |  |

|     | B.2                                           | Sum           | 104 |  |  |

|     | B.3                                           | Product       | 104 |  |  |

|     | B.4                                           | Accumulation  | 104 |  |  |

| Bil | bliog                                         | raphy         | 107 |  |  |

## **List of Figures**

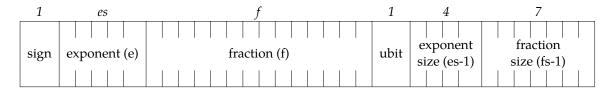

| 2.1 | Schematic overview of the bit fields of a unum type I. The field widths are indicated above each field                                                                                                                                                                                                                                   | 22 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

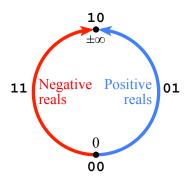

| 2.2 | Visual representation of the projective real number line of type II unums in the case of a 2-bit unum type II [3]                                                                                                                                                                                                                        | 23 |

| 2.3 | Two-input SORN addition table. Red and blue represent the negative and positive values, while a circle represents an open interval and a rectangle an exact value [3]                                                                                                                                                                    | 24 |

| 2.4 | The mapping to projective reals of a 4-bit type II unum, showing the symmetries along the horizontal (negation) and vertical (reciprocal) axes [3]                                                                                                                                                                                       | 24 |

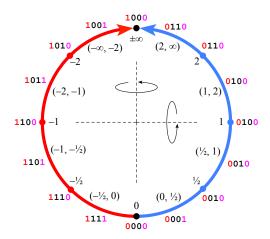

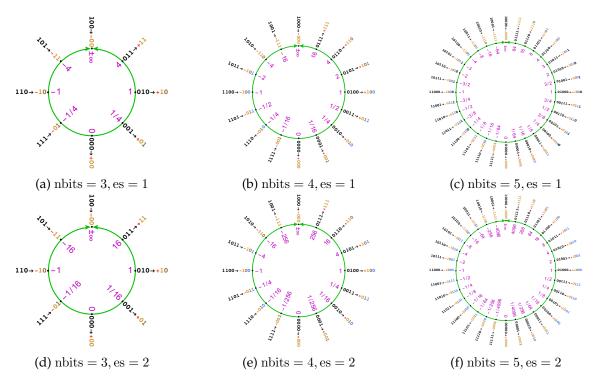

| 2.5 | Representable values for combinations of $\mathrm{nbits}=3,4,5$ and $\mathrm{es}=1,2$ [7]                                                                                                                                                                                                                                                | 27 |

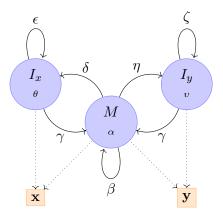

| 3.1 | A pair-HMM with 3 states. Symbols can be inserted into sequences $x$ or $y$ . $\delta$ and $\eta$ are the probabilities of emitting symbol $x$ and $y$ respectively, while $\alpha$ denotes the probability of emitting two aligned symbols into sequences $x$ and $y$ . The remaining symbols denote the state transition probabilities | 38 |

| 3.2 | Anti-diagonal recurrence. The anti-diagonal dashed lines indicate computations that can be calculated in parallel. Dotted lines indicate a data dependency.                                                                                                                                                                              | 41 |

| 3.3 | Mapping of 2 processing elements (highlighted as white and gray) to base comparison tasks for a read and haplotype sequence length of 4 base pairs. As the number of PEs is smaller than the input sequence length, two passes are required.                                                                                             | 42 |

| 3.4 | Mapping to three processing elements (PEs) of two batches (highlighted white and gray) of a read and haplotype sequence of 3 base pairs each. One clock                                                                                                                                                                                  |    |

|     | cycle is represented by each row.                                                                                                                                                                                                                                                                                                        | 42 |

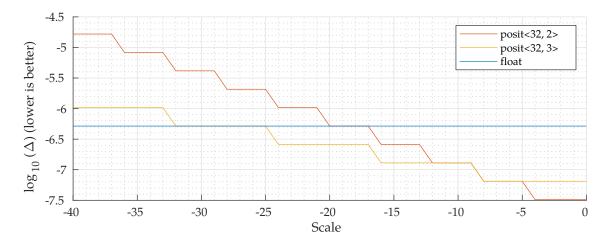

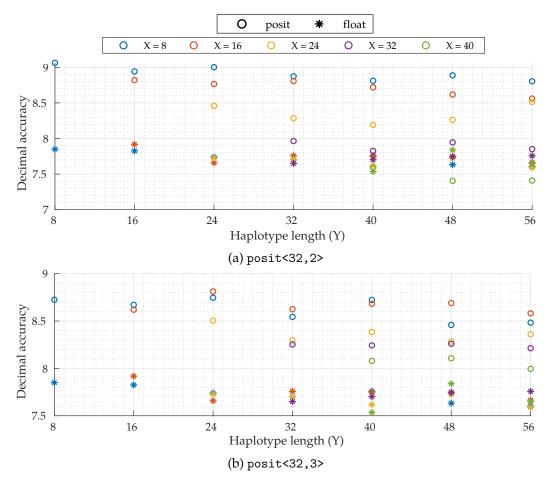

| 3.5 | Relative change in magnitude for posit<32,2>, posit<32,3> and float                                                                                                                                                                                                                                                                      | 46 |

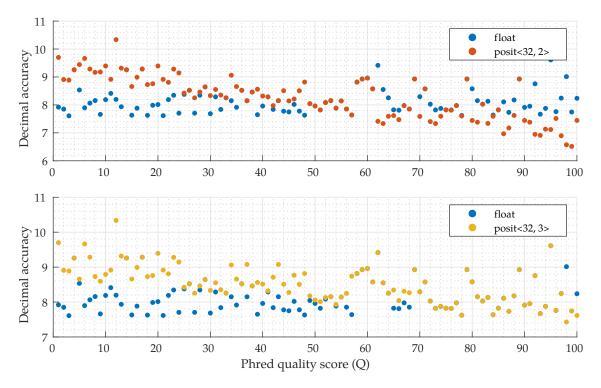

| 3.6 | Decimal Accuracy for the conversion to error probabilities of Phred-scaled quality scores ranging from 1 to 100 for float, posit<32,2> and posit<32,3>.                                                                                                                                                                                  | 48 |

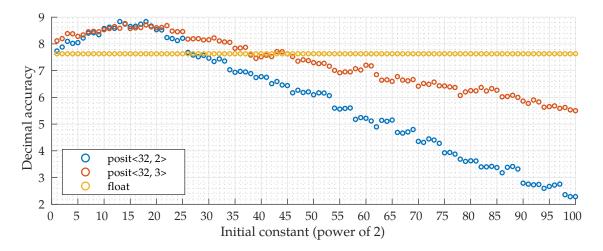

| 3.7 | Comparison of decimal accuracy for the evaluation of the pair-HMM forward algorithm for different values of the initial scaling constant                                                                                                                                                                                                 | 50 |

| 3.8 | Decimal accuracy of pair-HMM forward algorithm calculations for posit<32,2> and posit<32,3> compared to the decimal accuracy of calculations with the float type. X and Y denote the read and haplotype input sequence lengths                                                                                                           |    |

|     | respectively                                                                                                                                                                                                                                                                                                                             | 51 |

12 List of Figures

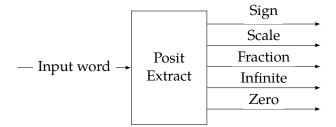

| 4.1 | Schematic overview of the in- and output products for the proposed posit extraction unit                                                                                                                                                                                                                   | 54         |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.2 | Schematic overview of the in- and output products for the proposed posit nor-                                                                                                                                                                                                                              |            |

|     | malization unit                                                                                                                                                                                                                                                                                            | 55         |

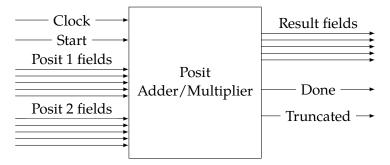

| 4.3 | Schematic overview of the in- and output products for the proposed posit adder and multiplier                                                                                                                                                                                                              | 56         |

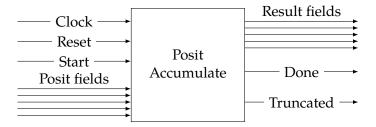

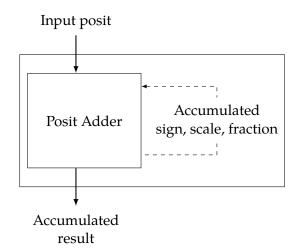

| 4.4 | Schematic overview of the in- and output products for the proposed posit accumulator.                                                                                                                                                                                                                      | 57         |

| 4.5 | Schematic overview of the posit wide accumulator, consisting of a posit adder module with the accumulated looped back as an input operand                                                                                                                                                                  | 58         |

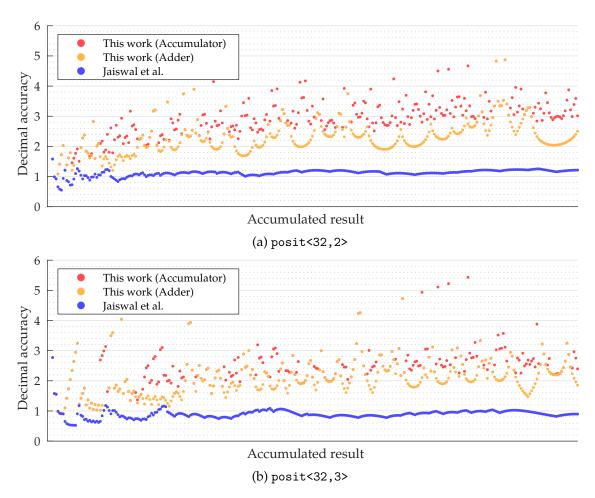

| 4.6 | Decimal accuracy of an accumulation of 300 incrementing fractional numbers for a 32-bit posit number format with 2 and 3 exponent bits, respectively                                                                                                                                                       | 60         |

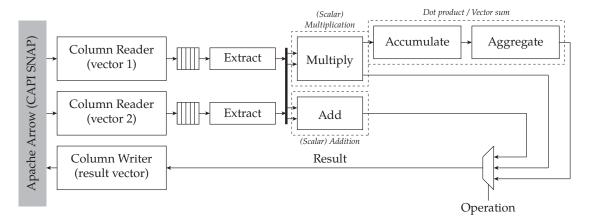

| 5.1 | Schematic overview of the data flow for the posit vector arithmetic accelerator, starting from the input vector representations in Apache Arrow. Each component is annotated with the operations this component is used for.                                                                               | 66         |

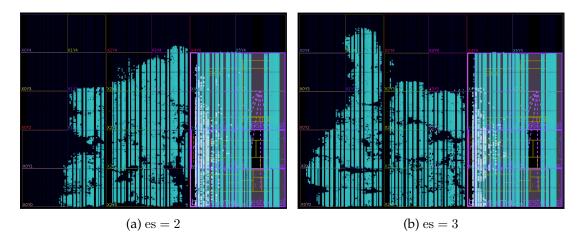

| 5.2 | Post-route layouts of the posit vector arithmetic accelerator interfacing with Apache Arrow in-memory data using the CAPI SNAP platform. FPGA device: Xilinx UltraScale XCKU060                                                                                                                            | 68         |

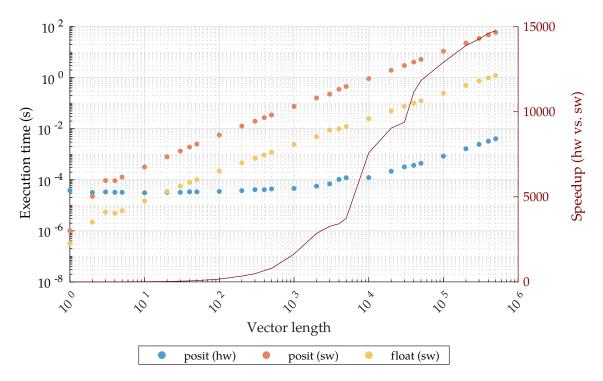

| 5.3 | Execution time for a posit dot product calculation using the proposed hardware accelerator compared to dot product calculation in software (single-thread) for different input vector lengths. The curve illustrates the speedup of the hardware posit implementation compared to software posit emulation | 70         |

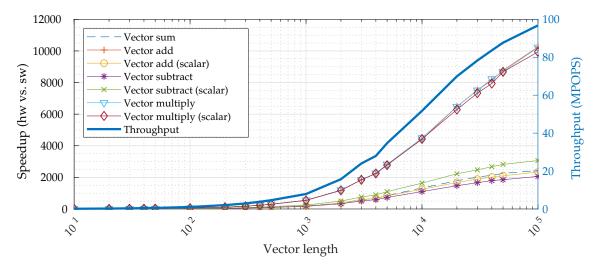

| 5.4 | Speedup of the posit vector arithmetic accelerator for different vector operations and vector input lengths, compared to the execution time for posit emulation in software. The hardware throughput (in MPOPS) is depicted on the right axis                                                              | 70         |

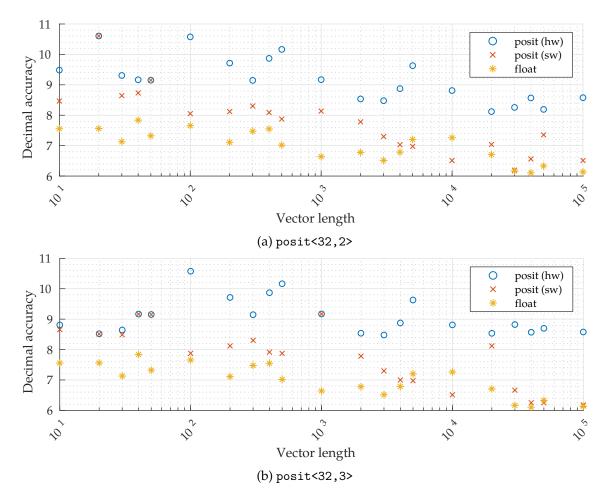

| 5.5 | Decimal accuracy of calculation results of the posit dot product operation performed by the proposed posit vector arithmetic accelerator and compared to software calculation results through software emulation, for different input                                                                      | <b>5</b> 1 |

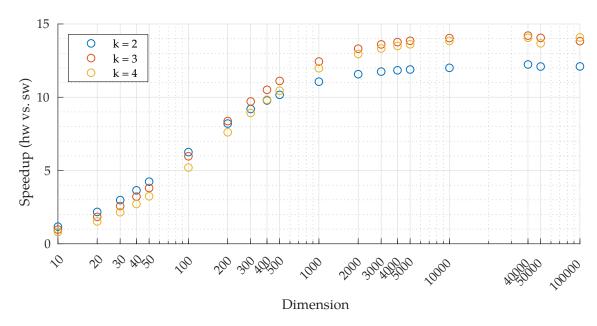

| 5.6 | vector lengths                                                                                                                                                                                                                                                                                             | 71<br>73   |

|     | in sortware for different framework of vectors and vector difficiency.                                                                                                                                                                                                                                     | , 0        |

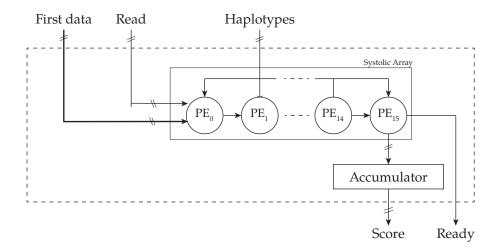

| 6.1 | Overall overview of the pair-HMM accelerator core design                                                                                                                                                                                                                                                   | 78         |

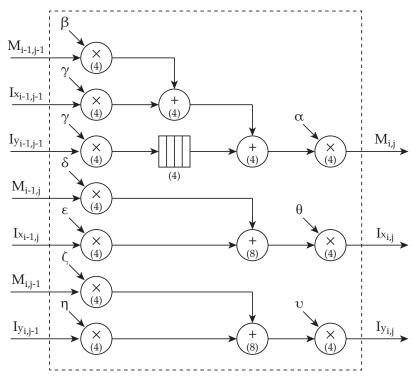

| 6.2 | Schematic overview of a Processing Element. The latency (in clock cycles) of each unit is indicated between parentheses.                                                                                                                                                                                   | 79         |

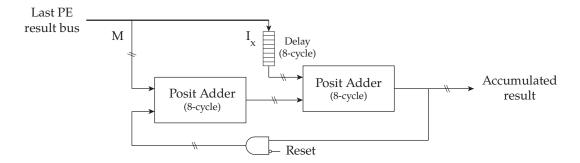

| 6.3 | Schematic overview of the pair-HMM accumulation stage using two regular posit adder units                                                                                                                                                                                                                  | 80         |

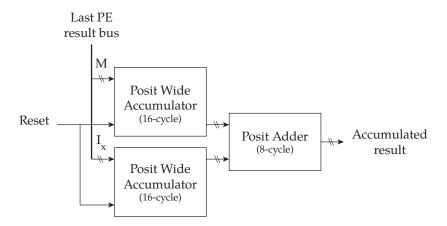

| 6.4 | Schematic overview of the pair-HMM accumulation stage using posit wide accumulator units.                                                                                                                                                                                                                  | 81         |

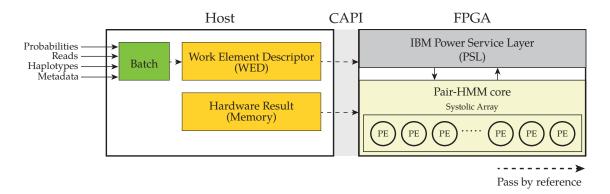

| 6.5  | Communication between host (CPU) and FPGA through Coherent Accelerator Processor Interface (CAPI). The pair-HMM accelerator core is implemented in        |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | a Computing Unit that communicates with the Power Service Layer (PSL)                                                                                     | 82  |

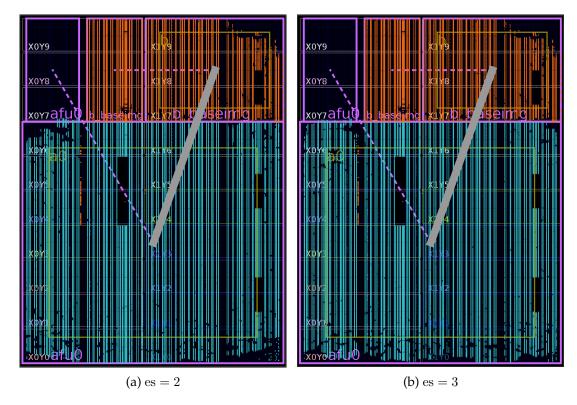

| 6.6  | Post-route layouts of the pair-HMM posit accelerator with streaming interface using the CAPI platform. FPGA device: Xilinx Virtex-7 XC7VX690T-2           | 83  |

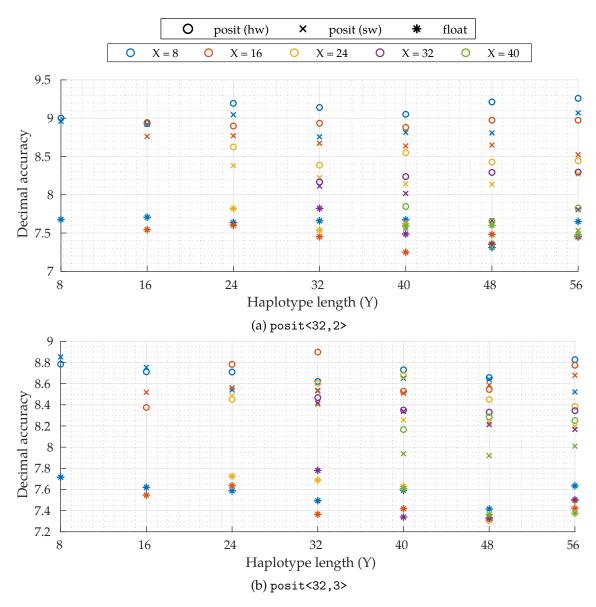

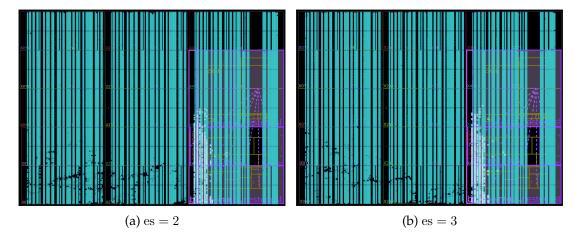

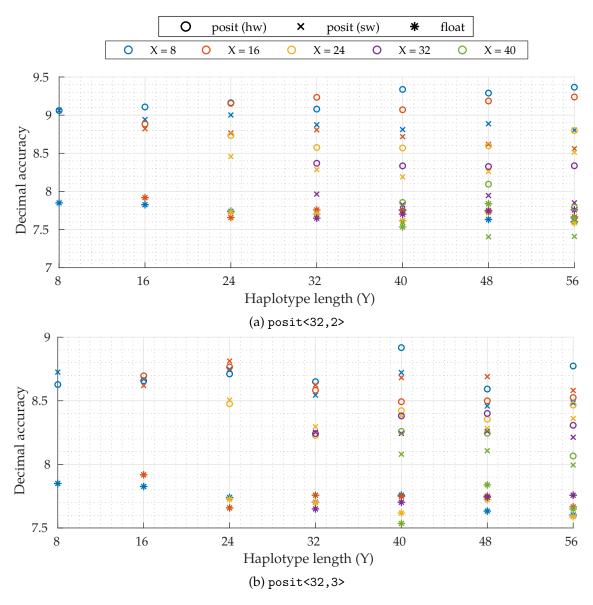

| 6.7  | Decimal accuracy of the proposed pair-HMM hardware accelerator results, compared to traditional float computation for posit<32,2> and posit<32,3>.        |     |

|      | X and Y denote the read and haplotype input sequence lengths respectively                                                                                 | 86  |

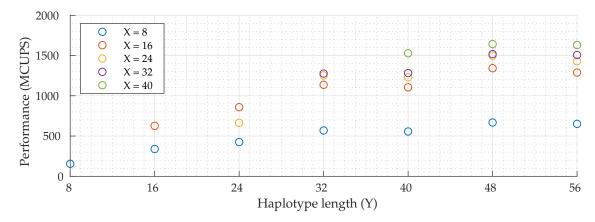

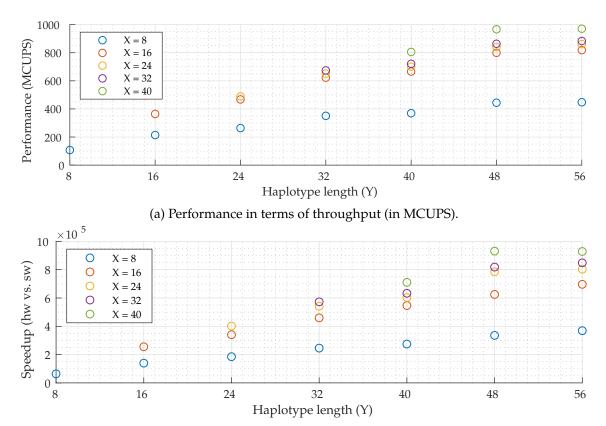

| 6.8  | Performance in terms of throughput (in MCUPS) of the proposed pair-HMM                                                                                    |     |

|      | accelerator design. X and Y denote the read and haplotype input sequence                                                                                  |     |

|      | lengths respectively                                                                                                                                      | 87  |

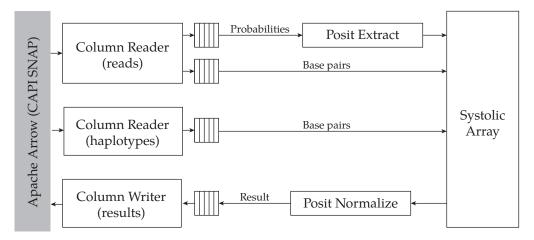

| 6.9  | Schematic overview of the high-level components inside the pair-HMM accel-                                                                                | 0.0 |

|      | erator core design, interfacing with Apache Arrow.                                                                                                        | 90  |

| 6.10 | Schematic overview of the high-level connection between multiple pair-HMM accelerator core instantiations and the host, interfacing with a read/write bus |     |

|      | arbiter connected to the CAPI SNAP AXI bus                                                                                                                | 90  |

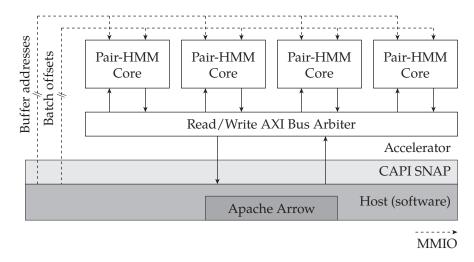

| 6.11 | Post-route layouts of the pair-HMM posit accelerator interfacing with Apache Arrow in-memory data using the CAPI SNAP platform. FPGA device: Xilinx       |     |

|      | UltraScale XCKU060                                                                                                                                        | 91  |

| 6.12 | Decimal accuracy of the proposed pair-HMM hardware accelerator results, compared to traditional float computation for posit<32,2> and posit<32,3>.        |     |

|      | X and Y denote the read and haplotype input sequence lengths respectively                                                                                 | 93  |

| 6.13 | Performance in terms of throughput (in MCUPS) and speedup compared to software calculation for the proposed pair-HMM accelerator design. X and Y          |     |

|      | denote the read and haplotype input sequence lengths respectively                                                                                         | 94  |

|      |                                                                                                                                                           |     |

|      |                                                                                                                                                           |     |

## **List of Tables**

| 2.1 | Effect of the GNU Compiler Collection (GCC) fast Optimization Level on          |    |  |

|-----|---------------------------------------------------------------------------------|----|--|

|     | floating point calculation semantics for the GCC compiler [15]                  | 33 |  |

| 2.2 | Example table (a) represented in a traditional memory buffer (b) and an Apache  |    |  |

|     | Arrow columnar memory buffer (c)                                                | 35 |  |

| 3.1 | Example sequence observations $x$ and $y$ and their underlying sequence of hid- |    |  |

|     | den states $z$ for the pair-HMM model illustrated in Fig. 3.1                   | 38 |  |

| 3.2 | Example Phred-scaled quality scores and their associated error probability      | 48 |  |

14 List of Tables

| 4.1 | Area utilization for the implementation of the posit adder, accumulator and multiplier designs discussed in Section 4.1                                                                                                                    | 59 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | Computation performance in MPOPS of the units presented in the posit arithmetic framework, as well as for posit operations computed by means of posit emulation through an external library for the platform described in Section 4.3.2.   | 62 |

| 5.1 | FPGA resource utilization and power consumption estimation of the posit dot product accelerator implementation, both for the accelerator core only and for the total implementation including the Power Service Layer                      | 69 |

| 6.1 | FPGA resource utilization and power consumption estimation of the streaming-<br>based pair-HMM posit accelerator implementation, both for the accelerator<br>core only and for the total implementation including the Power Service Layer. | 84 |

| 6.2 | Schematic overview of the Arrow schema for the Arrow pair-HMM Accelerator implementation, consisting of the columns used to feed the pair-HMM                                                                                              | 89 |

| 6.3 | accelerator                                                                                                                                                                                                                                | 89 |

| 0.5 | posit accelerator implementation for Apache Arrow, both for the accelerator                                                                                                                                                                |    |

|     | core only and for the total implementation including the Power Service Layer.                                                                                                                                                              | 92 |

## **List of Acronyms**

**BID** Binary Integer Decimal

**BLAS** Basic Linear Algebra Subprograms

**CAPI** Coherent Accelerator Processor Interface

**CUPS** Cell Updates Per Second

**DPD** Densely Packed Decimal

FMA Fused Multiply-Add

**FPGA** Field-Programmable Gate Array

**FPU** Floating-Point Unit

FTZ Flush-To-Zero

**GATK** Genome Analysis Tool Kit

GCC GNU Compiler Collection

**GPU** Graphics Processing Unit

**HMM** Hidden Markov Model

**INDEL** Insertion/Deletion

**LSB** Least Significant Bit

**LUT** Lookup Table

MAC Multiply-Accumulate

MMIO Memory Mapped Input/Output

NaN Not-A-Number

**PE** Processing Element

PHMM Pair Hidden Markov Model

POPS Posit Operations Per Second

**PSL** Power Service Layer

**SA** Systolic Array

SIMD Single Instruction, Multiple Data

**SNP** Single Nucleotide Polymorphism

**SORN** Sets Of Real Numbers

**ULP** Unit of Least Precision

**WED** Work Element Descriptor

## Chapter 1

## Introduction

#### 1.1 Motivation

The demand for higher precision arithmetic units is increasing due to the rapid development of new computing paradigms. The IEEE Standard for Floating-Point Arithmetic (IEEE 754) is the floating point implementation standard that the vast majority of contemporary computing systems have adopted. Although the first version of the standard was published in 1985, its main characteristics have to date not been changed, mainly for compatibility reasons. Because we now have more computing power at our disposal, the ability to process larger amounts of data becomes possible. In addition to this, we impose large precision requirements, either while accumulating big portions of data or when there is the desire to have a high-precision calculation result while imposing strict boundaries on bandwidth and the available processing power. This is often the case when limited computing resources are available, for example in low-power applications such as in embedded systems.

Over the course of the past few decades, the IEEE floating point representation has become the de facto standard in modern computing systems. Although it has proven to be a popular standard for representing floating point numbers, multiple shortcomings have been identified that have not been treated as major issue in the past, mainly because the standard was simply "good enough" for the conditions and requirements imposed at that time. A selection of the shortcomings of the IEEE floating point standard are listed below [1].

Different computers using the same IEEE floating point format are not required to

produce the same result. If a computation result does not fully fit into the chosen

number representation, the number will be rounded to the nearest representable

value. Hidden guard digits were introduced to improve the accuracy of those rounded

off answers. However, hardware designers are not obliged to implement these hidden guard digits. Therefore, inconsistent results can occur across different computing platforms.

- Non-conformance of the law of Associativity and Distributivity: due to the fact that

rounding is performed on individual operands of a specific calculation, the basic

mathematical laws of associativity, commutativity and distributivity do not hold.

This means that, for instance, the sum of two numbers in floating point representation does not necessarily match the exact sum of those two numbers if they were to

be represented as exact numbers.

- A portion of the available number of bit patterns is "wasted" on exceptions. An example of an exception is the Not-A-Number (NaN) value, which is used to represent an undefined or unrepresentable number. This is often the result of having illegal arguments as an input to a mathematical function. For instance, dividing by zero leads to a NaN. The IEEE 754 floating point standard defines different types of NaN representations. This is discussed in detail in Section 2.2.1.

The aforementioned discussion regarding the shortcomings of the widely adopted IEEE 754 standard was what led to the idea of developing an alternative number representation system that would serve as a worthy successor. The recently introduced *posit* number representation system was introduced by John L. Gustafson and claims to be able to provide more accurate answers to mathematical problems with an equal or smaller number of bits for some applications [2]. The posit data type is discussed in Section 2.1.3. Furthermore, the discussion on the shortcomings of the floating point standard and how the posit data type fixes these shortcomings is described. A key feature of this format is the *quire*, a scratchpad that can be used to perform fused operations, such as a multiply-accumulate operation, without rounding intermediate values and therefore reducing loss of precision in the final result.

The differences in semantics of the posit number format compared to the traditional IEEE 754 floating point number format lead to the question whether the posit number format might be a suitable replacement for applications that rely on precision. Furthermore, applications with smaller accuracy requirements could also benefit from a more accurate number representation system as a smaller number of bits could be used compared to floating point numbers, while preserving results with tolerable precision.

#### 1.2 Thesis Aim & Contributions

The main goal of this thesis is to explore a selection of potential applications for the novel posit number representation system. The potential advantages of the posit representation are exploited through the design of multiple hardware accelerator designs. These accelerators are built upon the most recent Coherent Accelerator Processor Interface (CAPI) in order to establish a high-speed connection between a host and accelerator. Furthermore, the accelerators presented in this work will be able to interface with data represented in the Apache Arrow columnar in-memory format.

#### **Research Questions**

The main research questions for this thesis are formulated as follows.

- 1. Study the suitability of the posit number representation for replacing traditional IEEE 754 floating point numbers in terms of accuracy and performance.

- 2. Does the posit number format deliver better, more accurate results compared to the IEEE 754 floating point standard for the following applications:

- a) Pair Hidden Markov Model (pair-HMM) for pairwise alignment of DNA sequence reads

- b) Level 1 BLAS Vector Operations (addition/subtraction, multiplication and dot product)

- 3. Can the computational performance of the posit implementation of the applications as mentioned in (2) be improved through acceleration using reconfigurable logic?

#### Research Methodology

The procedure to address the above mentioned research questions is described as follows. First, a theoretical analysis is performed on the definition of the posit number representation format. As the IEEE 754 floating point format is seen as the most popular alternative to the posit number format, a detailed analysis is made regarding the characteristics of both number formats. After analyzing the theoretical characteristics of both formats, a more practical exploration is performed in the context of the pair-HMM pairwise alignment algorithm. The algorithm is evaluated for both number formats and compared in terms of decimal accuracy of the calculation results. For the implementation of posit arithmetic in reconfigurable logic, a framework is designed that enables posit arithmetic in hardware with a focus on the preservation of decimal accuracy. Using this framework, an implementation of an accelerator for the pair-HMM algorithm using posit arithmetic is designed, as well as an accelerator for performing Level 1 Basic Linear Algebra Subprograms (BLAS) operations on column vectors consisting of posit numbers. Both hardware implementations are evaluated based on performance and the achieved decimal accuracy. Finally, a conclusion is made based on the obtained results.

#### **Contributions**

The contributions described in this thesis can be summarized as follows.

- A feasibility study to explore potential improvement in accuracy of computation results when replacing traditional floating point numbers with numbers represented in the posit number format.

- Design, implementation and evaluation of a novel framework for performing posit arithmetic operations in hardware while minimizing loss in decimal accuracy caused

by intermediate calculations.

https://github.com/lvandam/posit\_arith\_hdl

Design, implementation and evaluation of a vector arithmetic accelerator for posit vectors interfacing with the Apache Arrow columnar in-memory format through the CAPI SNAP platform.

https://github.com/lvandam/posit\_blas\_hdl

- Design, implementation and evaluation of a hardware accelerator for the pair-HMM forward algorithm using posit arithmetic for two different interfaces:

- A streaming-based implementation interfacing through the CAPI platform.

https://github.com/lvandam/pairhmm\_posit\_hdl\_stream

- Interfacing with data structures represented in the Apache Arrow columnar in-memory format through the CAPI SNAP framework. https://github.com/lvandam/pairhmm\_posit\_hdl\_arrow

#### 1.3 Thesis Outline

This thesis is structured as follows. Chapter 2 discusses background information related to the proposed unum arithmetic framework. Next, a comprehensive analysis of the posit number format compared to the IEEE 754 floating point standard is performed. The chapter is concluded with an overview of existing methods for controlling the desired numerical precision in software applications during the compilation time of a program. The feasibility of applying posit arithmetic in the field of bioinformatics is discussed in Chapter 3. In particular, the Pair Hidden Markov Model and its computational implementations are discussed. A detailed theoretical and empirical analysis is performed in order to determine the potential improvement in terms of calculation precision. Chapter 4 discusses the design, implementation and evaluation of a novel framework for performing posit arithmetic in reconfigurable logic. The framework consists of posit arithmetic units that can be used for performing calculations that are optimized with respect to decimal accuracy. The design and implementation of a hardware accelerator for performing posit vector arithmetic operations are discussed in Chapter 5. Subsequently, the design, implementation and evaluation of an accelerator for the pair-HMM forward algorithm using posit arithmetic in discussed in Chapter 6. An overall conclusion on the analysis, design and implementation efforts presented in this thesis, including recommendations based on the performed analyses, is given in Chapter 7. Additionally, a recap on the research questions initially proposed in the introduction of this thesis is given.

## **Chapter 2**

## Background

In this chapter we discuss background information related to the analyses performed and the implementations presented in this work. First, a description of the unum arithmetic framework, consisting of the proposals of unum type I, II and III (posit), is discussed. Next, a comparison between features of the IEEE 754 floating point standard and the novel posit number format is performed. Building upon the background theory on the posit number format, the recent efforts in hardware implementations of posit arithmetic are then discussed. We will also explore alternative number representation systems. In the concluding sections of this chapter we will cover background information on compiler optimizations for controlling desired floating point calculation accuracy, the Apache Arrow columnar in-memory format and a definition of the measure of decimal accuracy.

#### 2.1 The Unum Arithmetic Framework

The shortcomings of the IEEE 754 floating point number standard as discussed in Section 1.1 have led to an alternative number format that could resolve those issues. The universal number, abbreviated as *unum* [1], is introduced by John L. Gustafson and is seen as one of the most promising alternatives to the IEEE standard that has been the standard for decades. The unum number format has evolved over the past few years, dividing the unum into three different iterations or types: type I, II and III.

#### 2.1.1 Type I Unum

The main feature of a unum value compared to a regular IEEE 754 number is its ability to represent either an exact number or an open interval of 1 Unit of Least Precision (ULP) wide. The reason for wishing to incorporate this feature in the unum number scheme is that a computation is often not able to provide a numerically exact answer due to limitations in the number representation it uses. Therefore, when a number is unrepresentable in a certain degree of precision, it is rounded off to the nearest representable number. A unum is able to indicate that the value is accurate within a range of 1 ULP through the so-called *ubit*, which is a 1-bit field within the unum number representation. In this way,

Figure 2.1: Schematic overview of the bit fields of a unum type I. The field widths are indicated above each field.

ubit = 0 indicates that the unum corresponds to an exact number while ubit = 1 indicates that the unum corresponds to an interval between exact unums.

The unum format borrows most of the components of the IEEE 754 floating point scheme, such as the *exponent* and *fraction* (or mantissa) fields. The distinctive feature of the type I unum, however, is the fact that the widths of those fields are variable. One could choose to either represent a large number by assigning more bits to the exponent field, or one could opt for more decimal precision by having more fraction bits. The *exponent size* and *fraction size* fields are added to the unum scheme in order to annotate the widths of the exponent and fraction fields, biased upward by 1 as there is always at least one exponent and fraction bit.

In order to cover all the bit field widths of the exponent field as defined in the IEEE 754 standard, having 4 bits to indicate the exponent size (es - 1) is sufficient [1]. Similarly, having 7 bits to indicate the fraction size (fs - 1) is sufficient to cover the different IEEE floats. The complete format of unum type I is schematically depicted in Fig. 2.1.

#### 2.1.2 Type II Unum & SORNs

#### Motivation & Shortcomings of Unum Type I

The proposal of the type I unum proved to be a promising new number representation system, but was not free of any drawbacks. Implementing type I unum arithmetic in hardware is particularly challenging [3]. For example, the fact that unums can have a variable number of total bits and exponent bits leads to the requirement having variable storage sizes available. As implementing dynamic storage in hardware is challenging, one would need to unpack unums to a fixed storage size using a specific scheme [1]. Furthermore, the *ubit* field in a unum always has to be determined before the remaining fields of a unum can be unpacked. This introduces more complexity to a hardware implementation. For example, the ubit introduces more comparisons that have to be performed compared to a hardware implementation for floats. Another drawback of type I unums is that certain values can be represented in different ways, i.e. with different combinations of the number of total bits and exponent bits. Therefore, a number could be represented by using fewer exponent bits compared to another possible representation for the same number that would fill up a bigger portion of the fraction field. The second version of unum, type II, was proposed to resolve some of the shortcomings described above.

Figure 2.2: Visual representation of the projective real number line of type II unums in the case of a 2-bit unum type II [3].

#### Description

One of the distinctive features of the type II unum is its different mapping of unum values onto the projective real line. This mapping consists of a line with negative and positive reals, where the two ends meet at a single point, representing either plus or minus infinity. A visualization of how unums are mapped to the real line is depicted in Fig. 2.2. As can be seen, the point where a 2's complement number changes from positive to negative is the same point as where the positive reals wrap into the negative reals. This point also represents the value  $\pm\infty$ .

Another component the type II specification introduces is the Sets Of Real Numbers (SORN). The SORN is a bit string that represents whether or not a region or subset is present (1) or absent (0) in a given range. A SORN is therefore able to define a specific interval using subsets of the projective real numbers. The subsets of the projective reals depicted in Fig. 2.2 are  $\pm\infty$ ,  $(-\infty,0)$ , 0 and  $(0,\infty)$ . If one were to use a SORN to encode a unum with an interval of  $(-\infty,0]$ , the SORN would be 0110 (thereby indicating that the subsets  $(\infty,0)$  and 0 are part of the interval).

As noted by the author, the SORN can be used for operations that would normally result in indeterminate forms with single numbers. Expressions that would usually result in an indeterminate form such as zero divided by zero or infinity minus infinity are valid expressions when using SORNs because they produce valid SORNs. A SORN, for example, is able to represent the range of all numbers (by including all subsets). Analogously, for a division by zero, one can take the limit to 0 and end up with either or minus infinity. A SORN is then able to represent the value  $\pm\infty$ .

In order to perform arithmetic operations on SORNs it is necessary to perform table lookups to determine the outcome of any SORN operation on two or more operands. An example of such an operation (addition) is depicted in Fig. 2.3. Since these lookups need to be frequently performed, it is imperative to make this fast and efficient. When implementing unums in hardware these Lookup Tables (LUTs) could, for instance, be implemented in ROMs.

An interesting property that arises from the way in which the projective reals are mapped (as described above) is that there are geometrical analogies about the horizon-

| +     |         | 0 • 0 0 |         | 000  |

|-------|---------|---------|---------|------|

|       | 1 • 1 • |         |         |      |

| O • O |         | 0 • 0 0 | 0 • 0 0 | □●■● |

| □○■○  |         | 0 • 0 0 |         | 000  |

|       |         | □ ● ■ ● |         |      |

Figure 2.3: Two-input SORN addition table. Red and blue represent the negative and positive values, while a circle represents an open interval and a rectangle an exact value [3].

Figure 2.4: The mapping to projective reals of a 4-bit type II unum, showing the symmetries along the horizontal (negation) and vertical (reciprocal) axes [3].

tal and vertical axes of the unum representation. Take for instance the four-bit unums depicted in Fig. 2.4. When flipping about the horizontal axis, the values are negated. Analogously, flipping about the vertical axis results in the reciprocal value. Like type I unums, the *ubit* field classifies a unum as representing an open interval (ubit = 1) between adjacent exact points (ubit = 0).

#### Critique

One can imagine that the proposal of a new, alternative number representation system that directly competes with a settled number format (the IEEE 754 floating point standard) sprouts discussions between proponents of both number formats. Prof. W. Kahan, one of the lead architects on the initial version of the IEEE 754 floating point standard [4], has publicly expressed his critique on the proposed unum type II number format that includes the concept or SORNs. His critique led to a major discussion between proponents of both the IEEE 754 and unum number representation systems. We will now review a summary of Kahan's opinions and arguments as described in a document published in 2015 [5] and presented at ARITH 23 in 2016 [6].

The following arguments are directed towards unum type I and II (SORNs), for which some have been addressed in the type III (*posit*) number format as discussed in the next section.

- The *algebraic integrity* is violated with SORNs, as different expressions or the same rational function could produce different SORN results.

- Unum computation involves a too high cost:

- The latency compared to floats is increased because of the additional unpacking pipeline stages for variable-width unums.

- Fetching unums costs at least one extra indirect address reference compared to floats due to the variable fraction and exponent sizes.

- The area cost for SORN arithmetic can be significantly large: depending on the number of available collections of SORNs, chip area might increase significantly. Arbitrary SORN collections would require  $\mathcal{O}(2^{3N})$  area for SORNs each represented by  $2^N$  bits wide words. Schemes with pairs of N-bit pointers would need  $\mathcal{O}(N \times 2^{2N})$ , but this is slower. This might be good for low-precision interval arithmetic. However, low-precision interval arithmetic might not be used at all.

- The debugging of SORNs and unum arithmetic might be difficult:

- Lengthy computations with SORNs would produce too wide intervals which are difficult to diagnose and/or resolve.

- The IEEE 754 flags are absent in SORNs and unums: wide SORNS or unums caused by underflow or overflow would be difficult to diagnose and/or resolve as there are no pointers to the location of the first occurrence of an exception. Furthermore, no Not-A-Number (NaN) value exists for unums, which might make it difficult to discover invalid operations.

#### 2.1.3 Type III Unum (Posit)

#### Motivation

Although type II unums were praised for their mathematical properties, one of the biggest drawbacks is the reliance on lookup tables in hardware implementations. For an n-bit type II unum there is a worst-case LUT size of  $2^{2n}$  per 2-argument function scenario [2]. As discussed in Section 1.1, one of the most desired features of a number format is to have support for fused operations. However, type II unums prove to be unsuitable for use in fused operations due to the fact that any unum can have a variable number of (exponent) bits. This makes it difficult to store unums with different configurations in one accumulator. A successor to type II unums was therefore proposed. Type III unums, also known as *posits*, would take the general ideas and advantages of the type I and II unums to a point where hardware implementations supporting posit arithmetic would be very similar to the existing logic used for IEEE 754 floating point arithmetic [2].

#### Description

Compared to types I and II unums, the scheme of posits changed drastically. The posit format consists of the *sign*, *regime*, *exponent* and *fraction* fields.

**Sign** The sign bit is 0 for positive numbers and 1 for negative numbers, in which case the 2's complement form for the remaining part of the posit has to be taken before extracting the remaining fields.

**Regime** The regime field is used for calculating a scale factor k. This scale factor is determined by the number of repetitions of the leading bit in the regime field. If the regime field consists of leading 1's, this number determines the value k after subtracting 1. For a number of leading 0's, the number is negated. For example, if a 4-bit regime field is set to 1110, then k=2. Analogously, regime=0001 would indicate k=-3. Therefore, a bit that is opposite to the other leading bits terminates the regime field and marks the first position of the next field (exponent).

**Exponent** Similar to the type I and II unums, the exponent field has a variable width and determines the scaling factor  $2^{es}$  of the value represented by a posit. Recall that type I unums have a dedicated field to indicate the width of the exponent field. Posits do not require this field, as the number of exponent bits (es) is known in advance. Furthermore, the first bit of the exponent field is located directly after the regime field (which is dynamically terminated by a bit opposite to its leading bits, as mentioned above).

**Fraction** The remaining bits that have not been occupied by the sign, regime and exponent occupy the fraction field. The format for the fraction bits is the same as for IEEE floating point numbers (also sometimes termed *significand* or *mantissa*). The value of the fraction field is normalized, i.e. the represented decimal value starts with 0.xxx.

The decimal value of a posit is then calculated as

$$(-1)^{sign} \times useed^k \times 2^e \times (1+f) \tag{2.1}$$

where:

useed the scaling factor determined by the number of exponent bits (es), equal to  $2^{2^{\mathrm{es}}}$

k the value of the *regime* field

e the value of the *exponent* field

f the value of the fraction field

Fig. 2.5 shows the representable values for a selection of posit configurations. The bit strings around the outside of the rings can be treated as 2's complement integers. As can be seen, the point where the integers transition from positive to negative values is the same point as where the represented numbers transition from positive to negative as well. In much the same way as the characteristics of unum type II (Section 2.1.2), flipping a posit number around the vertical axis yields its negative value. For 0,  $\pm\infty$  and powers of two flipping across the horizontal axis yields the reciprocal.

Figure 2.5: Representable values for combinations of nbits = 3, 4, 5 and es = 1, 2 [7].

#### **Fused Operations**

When performing any calculation on one or multiple operands, rounding is performed in order to fit the final result back into a specific format. Intermediate rounding of results can therefore be a source of accuracy loss. This is especially the case when calculation results are being used as input operands for next calculations. Multiple approaches exist in order to defer the rounding of results until the very last calculation, such as the Fused Multiply-Add (FMA) operation (refer to Section 2.5.3). The proposal of the posit number representation system describes the concept of the quire, which can be seen as a fixed-size scratchpad register that can be used for different operations. The size of this scratchpad register is wide enough to obviate the need of having to round intermediate answers. The calculation of the required quire width for a specific calculation is discussed in Appendix B. Although the concept of scratchpad registers that can be used for fused operations is not novel, the concept of the quire yields a slightly different approach. While existing scratchpad registers are not controllable on the user-level, a quire unit would be accessible by the user. Hence, the user could instantiate a quire and provide a reference to this quire in any calculation he would like to perform without rounding of calculation results.

#### **Valids**

The specification for the posit number system also describes the notion of the *valid* mode, representing a number range that can be used for interval arithmetic. In its simplest form, a valid consists of two posits indicating the start and end of a bound. Valids are therefore useful for computations that require bounds on their results. Any loss of accuracy is tracked, since the inaccuracy bound will increase whenever any uncertainty is added to the overall computation. Another advantage of applying valids would be to verify the correct numerical behavior of a program, thereby keeping track of how much inaccuracy a program introduces in its intermediate computations [7]. The resulting bound could therefore serve as an indication to perform calculations with higher precision in order to decrease the error bounds for precision-critical applications.

#### 2.2 Feature Comparison of IEEE Float and Posit

As the proposal for the posit number format advertises itself as an alternative for the IEEE 754 floating point standard, direct comparisons are often made between both number formats. In this section we will discuss the major differences between both formats on an architectural level. Furthermore, we take a look at past discussions between opponents and advocates of the novel number format.

#### 2.2.1 Not-A-Number (NaN)

The IEEE 754 standard has defined that an exceptional number (such as NaN or  $\pm \infty$ ) should be represented by having all exponent bits set to one [4]. The remaining sequence of bits (fraction bits) then determines the exception cases: if the bit sequence is set to zero, the complete bit pattern represents  $\pm \infty$ , depending on the sign bit. A non-zero sequence represents NaN (as discussed in Chapter 1). The first bit of this bit string indicates the type of NaN, which can be either quiet NaN (propagating through arithmetic operations without an exception being raised) or signaling NaN (signaling an invalid operation exception). The remaining fraction bits are to be used as a payload, which could for example be used to indicate where in the program the NaN has occurred. However, this is often not used in practice as there is no user-friendly software-defined interface for programmers to control the payload (mantissa) field of a NaN floating point value. As the payload field of a NaN value can yield any value, there are different implementations for several programming languages that each have their own way of making use of the "unused" payload field of NaN values. This method is otherwise known as NaN boxing and is heavily used in JavaScript engines, among others [8]. The idea of "hacking" numbers via the principles of NaN boxing draws negative feedback. John L. Gustafson for example notes that this "breaks just about every rule there is about creating maintainable standards" [1].

In the case of a 32-bit single-precision IEEE 754 floating point number, there are 23 fraction bits available. Since the value zero is used to represent  $\pm \infty$ , this means that there are  $2^{23}-2=8\,388\,606$  different bit patterns to represent NaN. This is approximately 0.2%

of the total number of representations possible for a 32-bit single-precision number. One would argue that it is a waste of bit patterns to dedicate this amount to solely represent an invalid number.

As discussed in Section 2.1.3, the posit number format employs a different view on the use of NaN values. Instead of encoding different types of NaN values (such as quiet or signaling NaN), the posit arithmetic framework has no bit representations for NaN values at all [7]. The rationale behind this is that cases where a program returns a NaN value during or after calculation should not occur. Therefore, an interrupt should be asserted whenever a situation arises where an invalid value is the result of a computational routine. This interrupt can be handled by the program to, for instance, run a backup routine that acts as a "workaround" to still be able to generate a valid outcome.

There are multiple advantages of not having to represent NaN values in a number representation system. For example, the arithmetic hardware becomes less complex as less checks have to be performed to identify a bit string as either a number or a special value. Furthermore, the number of bit patterns that would have been used to represent NaN (or any other special value) can be used to represent a bigger range of numbers. As discussed, the 32-bit single precision IEEE 754 format has approximately 0.2% of all bit patterns reserved for NaN values. For posits, this portion can actually be used to represent more numbers.

#### 2.2.2 Negative Zero and $\pm \infty$

As discussed in the analysis in Section 2.1.3, positive values change to negative values at the same point as for 2's complement integers. This is contrary to the IEEE 754 floating point standard which also contains a value to represent the value negative zero. This value is not representable in posits. Analogously, posits have a single representation for the value  $\pm\infty$  (similar to the wraparound at  $\pm\infty$  shown in Fig. 2.2) whereas IEEE floats have separate values for  $\infty$  and  $-\infty$ .

#### 2.2.3 Critique

As discussed in Section 2.1.2, William Kahan, principal architect of the IEEE 754 floating point standard, has expressed a considerable amount of critique on the unum number format. The posit (type III unum) format addresses multiple points of criticism from Kahan, including the removal of interval arithmetic using the concept of SORNs (refer to Section 2.1.2). Furthermore, as opposed to the unum type II proposal, unum bit lengths are not variable any more and instead calculations are performed for a pre-selected fixed posit configuration. Kahan's suggested alternative solution to accomplishing more reliable arithmetic compared to the current state-of-the-art is by investing in software support for IEEE 754 diagnostics such as the NaN flags that point to sites where the first arithmetic exception has occurred. As discussed earlier in this chapter, the signaling NaN values intended for diagnostics purposes are often either not supported or used for other purposes.

#### 2.3 Posit Arithmetic Hardware Implementations

Since the initial introduction of the posit number format in mid-2017, the amount of research and development related to this novel number representation has been increasing rapidly. Starting from the introduction of the type I unum, a range of different hardware implementations for arithmetic units have been proposed, including hardware arithmetic implementations for the type III unum (posit). Recent developments in the design of posit arithmetic units have resulted in a range of different approaches to implementing posit arithmetic operations such as additions and multiplications in hardware.

The design of the posit matrix-multiply unit presented by Chen et al. [9] proves to be a high-performance implementation of posit arithmetic, achieving approximately 10 GFlops on an IBM POWER8 platform featuring the CAPI 1.0 interface. The Coherent Accelerator Processor Interface (CAPI) 1.0 interface is used to feed input data from the host to the accelerator. In this work, a quire register (refer to Section 2.1.3) is implemented that enables vector dot products to be performed without intermediate rounding. For the Xilinx Virtex-7 VX690 FPGA, the reported effective performance is 16 GPOPS (Giga Posit Operations Per Second) when streaming in posit elements and performing a multiply-accumulate operation. This implementation is limited to 32-bit posit numbers with es = 2.

As discussed in Section 2.1.3, one of the key features of the posit number format is the ability to adjust the total number of bits used to represent a number, along with the amount of bits used to represent the number exponent (similar to the IEEE floating point format). The ability to deal with posit numbers of variable-width fields becomes challenging when designing a hardware implementation of posit arithmetic due to the fixed, static nature of hardware. Although earlier work has focused on designing posit arithmetic units for reconfigurable logic with a configurable number of (exponent) bits using a synthesis parameter, being able to provide accurate computation results for all input combinations still proves to be challenging. For instance, the arithmetic hardware generator with configurable number of posit bits as proposed by [10] is not synthesizeable for any posit configuration with zero exponent bits. Furthermore, the posit arithmetic units presented in this work do not apply a rounding scheme. Instead, fraction values are simply truncated when normalizing to an N-bit posit word. Moreover, the presented posit arithmetic unit implementations are not pipelined, placing an entire calculation in a single combinational path, and as such are not directly useable in high-speed designs. For the proposed posit multiplier with the posit<32,2> configuration, a latency of approximately 16 ns is reported for the Xilinx Virtex-6 Field-Programmable Gate Array (FPGA), resulting in a operating frequency of 62.5 MHz.

#### 2.4 Alternative High-Precision Number Formats

With the IEEE 754 floating point standard being the most popular number representation system, alternative number formats that can be used in software are often based on this standard. The reason for this is the fact that integrated Floating-Point Units (FPUs), which are designed specifically for performing operations on floating point numbers, exist since the era of the x87 subset of the x86 architecture, providing an instruction set related to performing floating point operations in hardware [11].

Number formats that are not based on the IEEE 754 floating point format often rely on software emulation due to the lack of dedicated hardware support. Software emulation of number representation formats often appears to be significantly slower than hardware floating point operations, as we will see for the emulation of a posit dot product calculation discussed in Section 5.3.

In this section, we discuss a selection of alternative number formats, based on the IEEE 754 standard, that are designed to perform calculations with more decimals of accuracy.

#### 2.4.1 Decimal Floating Point

The decimal floating-point format is part of the 2008 version of the IEEE 754 specification [12]. The format differs from other floating point representations in the sense that the decimal format is able to emulate decimal rounding. Hence, floating point numbers are rounded exactly on decimals, which is often wanted in financial applications. Furthermore, the number fields are not normalized. This makes it possible for multiple representations to exist for the same number.

The significand of a decimal floating point number can be represented by two different methods, being Binary Integer Decimal (BID) or Densely Packed Decimal (DPD). However, both representations result in the same range of representable values. For BID, the significand is represented by a positive integer in binary representation. In the DPD representation, the significand is stored as decimal digits. Hence, in order to represent a single decimal digit, 4 bits are required per digit. The Densely Packed Decimal (DPD) [13] encoding is used in order to encode the digits after the most significant digit in order to save bandwidth.

Although the decimal floating point number format proves to be useful for applications critical for exact decimal calculations, there are a number of disadvantages for using this concept.

**Hardware Support** Several checks have to be performed before performing calculations. For example, it is determined which significand representation is used. Furthermore, not all possible combinations inside a decimal number are supported. For example, the BID significand representation does not support significand values larger than  $10^{34}-1$ . Any values above this limit are treated as zero. These checks need to be performed in hardware and thus can be a source for performance issues or an increase in area usage.

**Rounding Errors** Extreme rounding errors may occur. As significands do not have to be normalized, a large error can occur when adding values with different exponents. This is caused by the fact that the smallest number is shifted in order to match both exponents. After addition, the result is rounded up to a fixed number of digits. As the bits truncated in the final result are weighted by a factor of  $10^e$ , the decimal error can increase significantly. An example 7-digit calculation is depicted below, illustrating the possibility of having large rounding errors.

$$1.460147$$

$\times 10^{6}$  +  $2.194512 \times 10^{2}$

=  $1.460147$   $\times 10^{6}$  +  $0.0002194512 \times 10^{6}$  (shift)

=  $1.4603664512$   $\times 10^{6}$  (round)

#### 2.4.2 Boost Multiprecision

The Boost C++ libraries [14], a widely used set of C++ extensions, provides the Multiprecision library that is designed to provide arithmetic types with a high number of decimals of accuracy. The cpp\_dec\_float type, for instance, claims to provide at least 100 decimals of precision. Internally, cpp\_dec\_float numbers are represented in radix-10, similar to the decimal floating point format discussed before. Similar to IEEE 754 floating point numbers, both infinity and NaN values are supported. As reported in the Boost documentation, multiple guard digits are implemented in order to reduce error when values are being truncated.

#### 2.5 Compiler Optimization

Although the semantics of the employed number representation system are of great importance to calculation accuracy, it is often possible to adjust the desired level of precision of computation results through available options that can be set at the compiler level. In this section we will explore a selection of compiler options that can be used to control the desired level of floating point calculation precision.

#### 2.5.1 Optimization Level

It is often possible to choose the desired floating point semantics at compile-time of a program by setting corresponding compiler flags. This way, the user is able to control the level of granularity of floating point calculations to a certain degree. For the majority of the compilers available, the amount of optimization that is performed is controlled through the *optimization level* flag. For an optimization level of 0 (-O0), optimization transformations on a program are minimized. Each increasing level of optimization might improve

| Optimization              | Description                                                                           |  |  |

|---------------------------|---------------------------------------------------------------------------------------|--|--|

| no-math-errno             | Single-instruction math operations do not set the <i>errno</i> (Error Number) field   |  |  |

| unsafe-math-optimizations | Arithmetic input operands and results are assumed valid without validation            |  |  |

| finite-math-only          | No checks are performed for NaN or $\pm \infty$ numbers, allowing finite numbers only |  |  |

| no-rounding-math          | Assume default rounding behavior when performing optimizations                        |  |  |

| no-signaling-nans         | Reduced number of NaN values that would generate user-visible traps                   |  |  |

| excess-precision=fast     | Compute with wider precision whenever this would result in a faster program           |  |  |

Table 2.1: Effect of the GCC fast Optimization Level on floating point calculation semantics for the GCC compiler [15].

program performance, while potentially giving in on accuracy of floating point calculations. For the GNU Compiler Collection (GCC), the optimization levels 0-3 do not affect floating point arithmetic behavior. However, the fast optimization level does enable several optimizations regarding floating point semantics. The optimizations that are in effect for this mode are depicted in Table 2.1.

#### 2.5.2 Subnormal Numbers

Arithmetic underflow can occur when a calculation result becomes smaller than the actual representable value in a certain number representation. Depending on the distribution of the representable numbers by a number representation system, the *underflow gap* between the smallest positive representable number and the smallest negative representable number is several orders of magnitude larger than the interval of one ULP in the regular, non-overflow case. Multiple approaches to dealing with underflowing values exist. Historically, underflow values were treated as zero. This feature, also known as Flush-To-Zero (FTZ), is still a configurable option in common compilers through a FTZ flag. In particular, asserting the FTZ flag flushes underflowing floating point computation results to zero [16]. The main advantage of setting the FTZ flag is the potential performance improvement. As more values are treated as zero, fewer computations have to be performed. However, this does induce a potential loss of precision, as information is being discarded. Therefore, the flush-to-zero option gives the user control over a trade-off between program performance and the desired level of accuracy.

An alternative to the traditional flush-to-zero behavior, the concept of *subnormal numbers*, was introduced in the IEEE 754 floating point specification and fills in the underflow gap described above [17]. Subnormal numbers are values smaller than the smallest "normal" representable value in a number representation system. For the IEEE 754 floating point standard, a subnormal value is indicated by setting the exponent field to the smallest representable value. Although the mantissa of a normal floating point value is represented by a hidden 1 bit, subnormal numbers are represented by a hidden 0 bit and therefore allow for smaller numbers to be represented. The introduction of subnormal numbers enables *gradual underflow*: instead of underflowing to zero, the nearest subnormal value is used [18]. Although the process of gradual underflow induces a loss of precision, the severity of the precision loss is minimized since a flush-to-zero is avoided.

#### 2.5.3 Multiply-Accumulate

Multiply-Accumulate (MAC) is an instruction designed to compute the product of two input numbers and add the result to an *accumulated* value. Hence, the MAC operation performs the following calculation:

$$z \leftarrow z + x \times y \tag{2.2}$$

The MAC instruction rounds the result of the product  $(x \times y)$  to a specific number of significant digits, followed by an addition to the accumulated value z, after which rounding to a specific number of significant digits is performed again. This procedure is alternatively called *double rounding*. It is trivial to see the disadvantage of having the double rounding scheme in place for the MAC operation. For every MAC operation, two roundings are performed, which can in turn cause a significant error.

As opposed to the double rounding scheme for the MAC operation, the FMA operation performs rounding only once: the complete multiply-accumulation  $x \times y + z$  is calculated and then rounded to a specific number of significant digits. The FMA operation was initially introduced as part of the RISC instruction set of the IBM POWER1 processor [19]. Subsequently, the FMA instruction has found its way into nearly all contemporary processors. The FMA operation has been part of the IEEE 754 floating-point standard since 2008 [12].

#### 2.6 Measure of Decimal Accuracy

In order to express the error between a value and an exact reference value, a wide range of measures exist. For example, the absolute error, calculated as the absolute difference between a value and its reference, is a popular error metric. Building upon this definition, the relative error gets rid of the order of magnitude of both numbers by dividing the absolute error by the exact value. This measure, however, is particularly unsuitable for quantifying the number of digits that are correct between a computed and exact value, as only a ratio is given. Furthermore, the relative error is not informative for cases when the computed value has a different sign compared to the reference value as the absolute value is taken.

The previously described drawbacks of the commonly used measures for error lead to the proposal of the measure of *decimal accuracy* [7]. Suppose we have the true value X and the calculated value  $\tilde{X}$ , which for example can be the result of a calculation in float or posit mode. We can define the *decimal error* as the ratio between an exact and computed value:

$$\operatorname{decimal error} = \left| \log_{10} \left( \frac{\tilde{X}}{X} \right) \right| \tag{2.3}$$

2.7. APACHE ARROW

35

| ٠. | / \ |   |    | 1      | 1  |

|----|-----|---|----|--------|----|

| 1  | (a) | ١ | Га | n      | 16 |

| А  | u   | , | ıч | $\sim$ | т, |

|       | Field 1 | Field 2 | Field 3 |

|-------|---------|---------|---------|

| Row 1 | 1       | 2       | 3       |

| Row 2 | 4       | 5       | 6       |

| Row 3 | 7       | 8       | 9       |

(b) Regular Buffer

| r |

|---|

|   |

|       | 1 |

|-------|---|

| Row 1 | 2 |

|       | 3 |

|       | 4 |

| Row 2 | 5 |

|       | 6 |

|       | 7 |

| Row 3 | 8 |

|       | 9 |

|       |   |

|         | 1 |

|---------|---|

| Field 1 | 4 |

|         | 7 |

|         | 2 |

| Field 2 | 5 |

|         | 8 |

|         | 3 |

| Field 3 | 6 |

|         | 9 |

|         |   |

Table 2.2: Example table (a) represented in a traditional memory buffer (b) and an Apache Arrow columnar memory buffer (c).

The *decimal accuracy* is then defined as a measure of the number of decimals of accuracy and is equal to the log base 10 of the inverse of the decimal error [7]:

decimal accuracy =