Delft University of Technology

## European Test Symposium Teams an Anniversary Snapshot

Jenihhin, M.; Raik, J.; Jutman, A.; Mir, S.; Taouil, M.; Fieback, M.; Bishnoi, R.; Hamdioui, S.; Ma, K.; More Authors

**DOI**

[10.1109/ETS63895.2025.11049652](https://doi.org/10.1109/ETS63895.2025.11049652)

**Publication date**

2025

**Document Version**

Final published version

**Published in**

Proceedings - 2025 IEEE European Test Symposium, ETS 2025

**Citation (APA)**

Jenihhin, M., Raik, J., Jutman, A., Mir, S., Taouil, M., Fieback, M., Bishnoi, R., Hamdioui, S., Ma, K., & More Authors (2025). European Test Symposium Teams: an Anniversary Snapshot. In *Proceedings - 2025 IEEE European Test Symposium, ETS 2025* (Proceedings of the European Test Workshop). IEEE. <https://doi.org/10.1109/ETS63895.2025.11049652>

**Important note**

To cite this publication, please use the final published version (if applicable).

Please check the document version above.

**Copyright**

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**

Please contact us and provide details if you believe this document breaches copyrights.

We will remove access to the work immediately and investigate your claim.

**Green Open Access added to [TU Delft Institutional Repository](#)

as part of the Taverne amendment.**

More information about this copyright law amendment

can be found at <https://www.openaccess.nl>.

Otherwise as indicated in the copyright section:

the publisher is the copyright holder of this work and the

author uses the Dutch legislation to make this work public.

# European Test Symposium Teams: an Anniversary Snapshot

M. Jenihhin<sup>2</sup>, J. Raik<sup>2</sup>, A. Jutman<sup>2</sup>, N. Cherezova<sup>2</sup>, R. Ubar<sup>2</sup>, L. Miclea<sup>3</sup>, S. Enyedi<sup>3</sup>, I. Stefan<sup>3</sup>, O. Stan<sup>3</sup>, C. Corches<sup>3</sup>, Z. Peng<sup>4</sup>, P. Eles<sup>4</sup>, R. Drechsler<sup>5A</sup>, S. Eggersglüß<sup>5B</sup>, G. Fey<sup>5C</sup>, A. Glowatz<sup>5B</sup>, D. Tille<sup>5B</sup>, G. Gielen<sup>6A</sup>, A. Coyette<sup>6A,B</sup>, W. Dobbelaere<sup>6B</sup>, R. Vanhooren<sup>6B</sup>, P.-Y. Chuang<sup>7</sup>, E. J. Marinissen<sup>7</sup>, G. Di Natale<sup>8</sup>, M. Barragan<sup>8</sup>, P. Maistri<sup>8</sup>, S. Mir<sup>8</sup>, E.-I. Vatajelu<sup>8</sup>, P. Bernardi<sup>9</sup>, S. Di Carlo<sup>9</sup>, P. Prinetto<sup>9</sup>, M. Sonza Reorda<sup>9</sup>, M. Violante<sup>9</sup>, H.-G. Stratigopoulos<sup>10</sup>, M. K. Michael<sup>11</sup>, S. Neophytou<sup>11</sup>, S. Hadjitheophanous<sup>11</sup>, K. Christou<sup>11</sup>, M. Skitsas<sup>11</sup>, A. Bosio<sup>12A</sup>, B. Deveautour<sup>12B</sup>, P. Girard<sup>12C</sup>, M. Traiola<sup>13A</sup>, A. Virazel<sup>12C</sup>, F. Fernandes dos Santos<sup>13A</sup>, A. Kritikakou<sup>13A,B</sup>, G. Casagranda<sup>14</sup>, M. Vallero<sup>14</sup>, F. Vella<sup>14</sup>, P. Rech<sup>14</sup>, L. M. Bolzani Poehls<sup>15A</sup>, M. Krstic<sup>15A,B</sup>, M. Andjelkovic<sup>15A</sup>, F. Vargas<sup>15A</sup>, G. Tshagharyan<sup>16</sup>, G. Harutyunyan<sup>16</sup>, V. Vardanian<sup>16</sup>, S. Shoukourian<sup>16</sup>, Y. Zorian<sup>16</sup>, J. Dworak<sup>17A</sup>, K. Nepal<sup>17B</sup>, T. Manikas<sup>17A</sup>, M. Taouil<sup>18</sup>, M. Fieback<sup>18</sup>, A. Gebregiorgis<sup>18</sup>, R. Bishnoi<sup>18</sup>, S. Hamdioui<sup>18</sup>, A. Chatterjee<sup>19A</sup>, A. Saha<sup>19A</sup>, S. Komarraju<sup>19B</sup>, K. Ma<sup>19C</sup>, C. Amarnath<sup>19D</sup>, M. Tahoori<sup>20</sup>, M. Mayahinia<sup>20</sup>, M. Rajabalipanah<sup>21</sup>, K. Basharkhah<sup>21</sup>, N. Nosrati<sup>21</sup>, Z. Jahanpeima<sup>21</sup>, Z. Navabi<sup>21</sup>, H.-J. Wunderlich<sup>22A</sup>, S. Hellebrand<sup>22B</sup>

<sup>2</sup>Department of Computer Systems, Tallinn University of Technology, Tallinn, Estonia,

<sup>3</sup>Technical University of Cluj-Napoca, Romania, <sup>4</sup>Embedded Systems Lab. (ESLAB), Linköping Univ., Sweden,

<sup>5A</sup>Group of Computer Architecture, University of Bremen, Bremen, Germany, <sup>5B</sup>Siemens EDA, Tessent, Hamburg, Germany, <sup>5C</sup>Institute of Embedded Systems, Hamburg University of Technology, Hamburg, Germany,

<sup>6A</sup>ESAT-MICAS, KU Leuven, Belgium, <sup>6B</sup>onsemi Belgium, Mechelen, Belgium,

<sup>7</sup>Advanced Reliability, Robustness, and Test (AR<sup>2</sup>T), imec, Leuven, Belgium,

<sup>8</sup>Univ. Grenoble Alpes, CNRS, Grenoble INP, TIMA, France, <sup>9</sup>Politecnico di Torino, Italy,

<sup>10</sup>Sorbonne Université, CNRS, LIP6, Paris, France, <sup>11</sup>Department of Electrical and Computer Engineering, University of Cyprus, Nicosia, Cyprus, <sup>12A</sup>Centrale Lyon, INSA Lyon, CNRS, Université Claude Bernard Lyon 1, CPE Lyon, INL, UMR5270, France, <sup>12B</sup>Nantes Université, CNRS, IETR UMR 6164, F-44000 Nantes, France,

<sup>12C</sup>LIRMM, University of Montpellier/CNRS, Montpellier 34000 France, <sup>13A</sup>Univ Rennes, Inria, CNRS, IRISA, Rennes, France, <sup>13B</sup>Institut universitaire de France (IUF), France, <sup>14</sup>University of Trento, Italy,

<sup>15A</sup>IHP – Leibniz Institute for High Performance Microelectronic, Frankfurt Oder, Germany,

<sup>15B</sup>University of Potsdam, Germany, <sup>16</sup>Synopsys Armenia, Embedded Test & Repair Group, Yerevan, Armenia,

<sup>17A</sup>Southern Methodist University, Dallas, Texas, USA, <sup>17B</sup>University of St. Thomas, St. Paul, Minnesota, USA, <sup>18</sup>Delft University of Technology, The Netherlands,

<sup>19A</sup>Department of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, USA,

<sup>19B</sup>Intel Corporation, <sup>19C</sup>Rebellions AI, South Korea, <sup>19D</sup>Google Inc, Sunnyvale, CA, USA,

<sup>20</sup>Faculty of Computer Science, Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany,

<sup>21</sup>School of Electrical and Computer Engineering, College of Engineering, University of Tehran, Tehran, Iran,

<sup>22A</sup>University of Stuttgart, Germany, <sup>22B</sup>Paderborn University, Germany

**Abstract**—The IEEE European Test Symposium (ETS) has been facilitating progress in electronic systems testing since its launch in 1996. On the occasion of its 30th anniversary, this collaborative paper gathers sections by 21 ETS teams to outline their influential ideas and milestones. Each team’s section highlights historical perspective, current research, frameworks and projects as well as forward-looking research agendas in the area of electronic-based circuits and systems testing, reliability, safety, security and validation. This anniversary summary documents how research of various ETS teams, exemplifying the test community, has been evolving and transitioning from concepts to practical standards and Electronic Design Automation (EDA) tools and flows. This legacy is a strong base to drive the next generation of advances in electronic systems testing.

## 1. INTRODUCTION

Electronic systems testing has undergone an impressive evolution over the past three decades, keeping pace with the exponential growth in semiconductor complexity. Since the establishment of the IEEE European Test Symposium (started as the IEEE European Test Workshop) in the mid-1990s, the ETS community’s research has been leading and reflecting major shifts in how we design for testability, generate and apply test patterns, and ensure the reliability and security of integrated circuits. This journey spans from foundational design-for-test (DFT) breakthroughs that made large designs testable, to sophisticated techniques today that safeguard cutting-edge

hardware AI accelerators and even upcoming quantum devices. Along this path, ETS served as a global forum uniting diverse research teams from Europe and all continents to collaborate on advancing the state of the art. In this joint paper, we review the milestones and the key research themes of the community based on representative contributions of several ETS teams who submitted their sections in response to an open call. A summary of the ETS history from 1996 to 2019 is also outlined in [1].

**The rise of standardized test and DFT.** In the 1990s, ETS witnessed a transformative period marked by the standardization of DFT techniques. The adoption of *IEEE 1149.1 Boundary-Scan ("JTAG")* revolutionized test access by providing a universal interface for testing and debugging integrated circuits. This was followed by advances in *full-scan design*, where all flip-flops were made scannable, enabling *automated test pattern generation (ATPG)* tools to achieve high fault coverage. Boundary scan became the foundation of test infrastructure and paved the way for later standards (e.g., *IEEE 1500* for core wrappers and *IEEE 1687 "LJTAG"* for on-chip instruments) that extended the scan paradigm. *IDDQ (I<sub>DD</sub> Quiescent)* testing became a critical method for beyond stuck-at-fault defect screening, leveraging quiescent supply current measurements to identify faulty ICs, while *at-speed testing* emerged as a solution to detect timing-related defects in high-frequency circuits.

**Built-in self-test and hybrid testing techniques.** With the growth of complexity, *built-in self-test (BIST) techniques* have gained prominence. *Memory BIST* became essential for embedded SRAM and ROM testing, significantly reducing test time and using on-chip pattern generators and signature analyzers. For logic testing, *hybrid BIST* combined pseudorandom patterns with deterministic ATPG vectors hard-to-detect faults, optimizing fault coverage while minimizing test time. *Software-based self-test (SBST)* emerged as a versatile solution for processors, allowing in-field testing using self-generated software routines. Initially proposed for periodic in-field testing of mission-critical systems, SBST soon became interesting for manufacturing test of processors where traditional DFT was limited, at the same time enabling at-speed testing with zero extra hardware.

**The Core-Based SoC testing paradigm.** The transition to system-on-chip (SoC) designs in the late 1990s brought new challenges, and ETS played a pivotal role in developing *core-based testing*. Here, rather than treating the chip as a single entity, each embedded core could be isolated with a test wrapper and accessed via a shared *test access mechanism (TAM)* bus. The *IEEE 1500 standard* formalized core wrappers and test access mechanisms, allowing modular testing of complex SoCs. Optimizing test access and scheduling for multi-core systems became a key research focus, with ETS teams supporting innovations in TAM design and *test scheduling algorithms*.

**Compressing test data and controlling power.** In the 2000s, test data volume became a critical challenge, leading to the development of *test compression techniques*. Methods like *scan compression* reduced requirements for data storage and transfer, while *low-power testing techniques* minimized

the risk of excessive switching activity during testing. ETS teams pioneered numerous solutions for *X-filling* (assigning “don’t-care” bits in test patterns to reduce toggling), *power-aware test scheduling*, and *segmented scan*, making high-quality testing feasible even for power-sensitive designs. The community led several of these developments and influenced standards (e.g., the *IEEE P1838 standard* for 3D test access specifically considering power-aware features).

**Advanced fault models and formal methods.** ETS research has also driven advances in fault modeling and test generation. From *decision diagram assisted techniques*, such as Structurally Synthesized Binary Decision Diagrams (SSBDDs) in the late 1980s, to the practical application of *SAT-based ATPG*, these methods have expanded the scope of testable faults, especially in complex designs. Formal methods have enabled efficient test pattern generation and fault diagnosis, ensuring that even hard-to-detect faults can be addressed.

**Analog, mixed-signal, and non-digital testing.** While digital test techniques dominated, ETS teams also expanded their focus to support *analog and mixed-signal testing*, an inherently challenging area. The *IEEE 1149.4 standard* for analog boundary scan and *oscillation-based BIST* for analog circuits self-test demonstrated that analog testing could be simplified to a digital-like measurement.

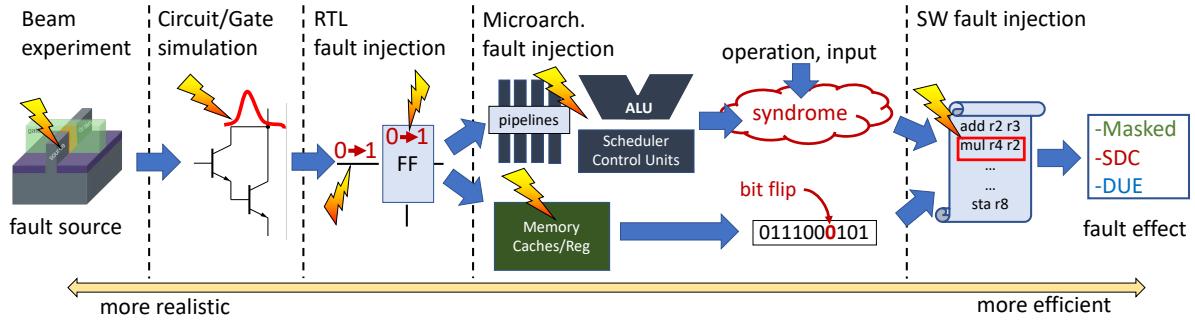

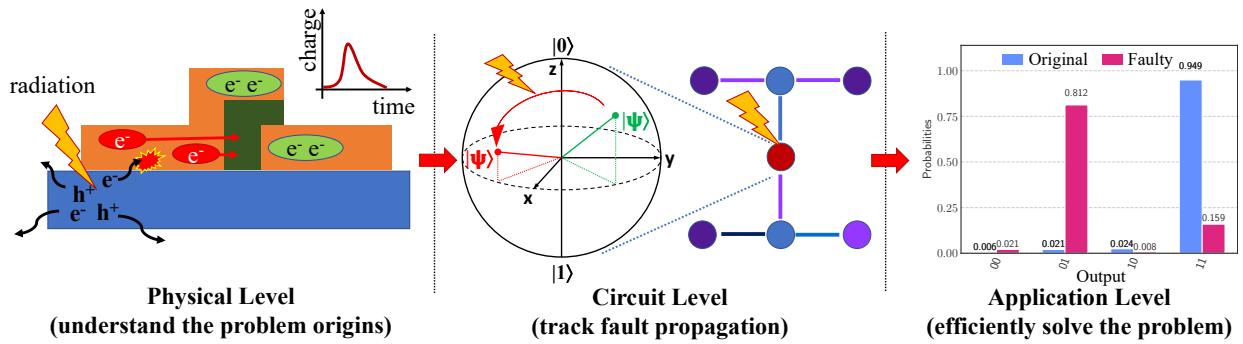

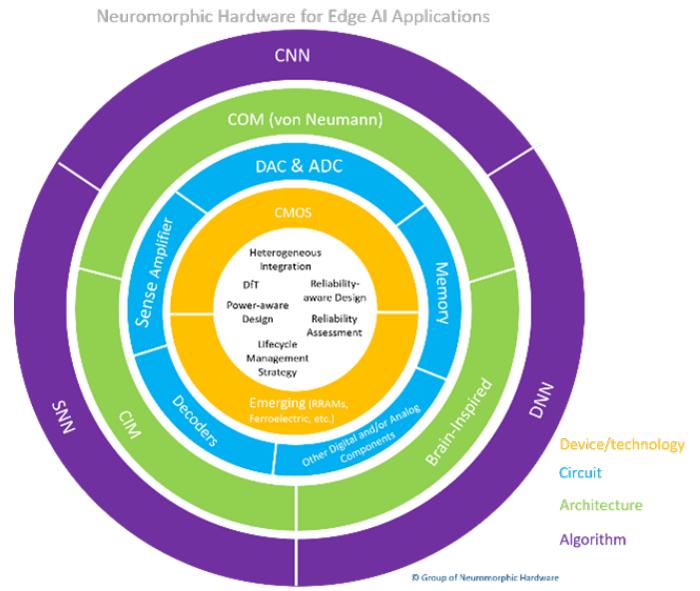

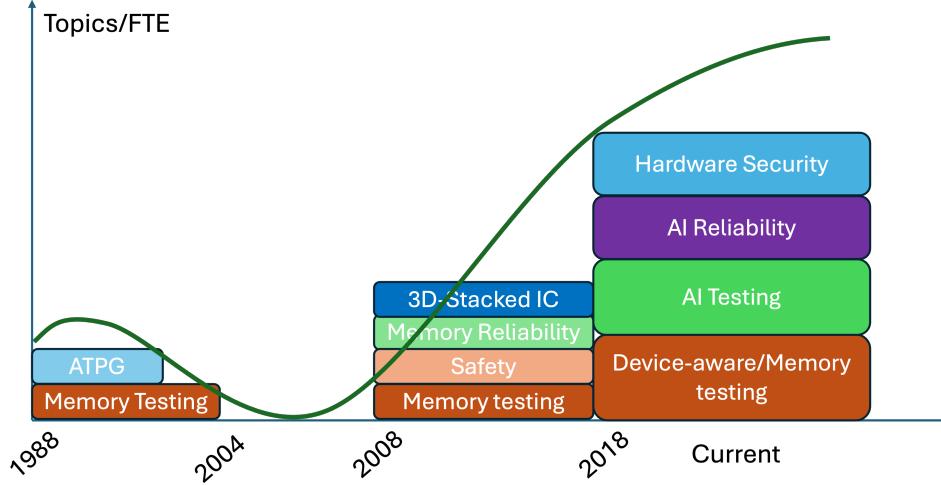

**Reliability and resilience in the Era of AI and beyond.** In recent years, the focus of electronics testing has broadened from manufacturing defect detection to ensuring *reliability* and *resilience* of systems in the field. As feature sizes shrink, the community has strengthened addressing soft errors, aging effects, and weak-defect tolerance in designs. A significant trend has been *cross-layer reliability approaches*, where vulnerabilities are analyzed and mitigated across different abstraction levels (from devices up to software) and system layers. The concept of *self-healing* and *self-health aware hardware* is gaining traction, advocating electronic systems that can monitor their own “health” and adapt or reconfigure themselves to tolerate faults. This vision extends the traditional scope of testing into *runtime monitoring* and maintenance, aligning with emerging standards in *silicon lifecycle management*. The advent of AI hardware has posed new reliability challenges and has become a focal point for recent contributions of the ETS teams. These include methods for *fault resilience assessment* and *selective hardening* of DNN models considering the heterogeneous vulnerability of the neural network’s components. Looking even further ahead, the ETS community is addressing *emerging technologies* like quantum computing, where quantum devices are inherently fragile, suffering from decoherence and noise, along with the threats in focus for conventional technologies, e.g. soft errors.

Over the past 30 years, the ETS teams’ collective innovations have shaped the practice of electronic testing. Many of the highlighted breakthroughs transitioned from academic papers to industry standards and EDA tools, emphasizing collaboration between researchers across sectors. The ETS teamwork is evident in numerous synergistic multi-partner projects and cross-border research initiatives. This legacy is a strong base for the next generation of advances in electronic systems testing.

## 2. TALTECH: FROM DECISION DIAGRAMS TO EDGE AI RELIABILITY<sup>1,2</sup>

*Maksim Jenihhin, Jaan Raik, Artur Jutman, Natalia Cherezova, Raimund Ubar.*

*Tallinn University of Technology, Estonia*

This section outlines the evolution of test research at Tallinn University of Technology (TalTech), spanning from pioneering work on structural decision diagrams to cutting-edge reliability solutions for Edge AI chips. We detail our historical contributions, current advancements, and future directions, emphasizing our longstanding ties with the IEEE European Test Symposium.

### 2.A. Historical perspective of related research

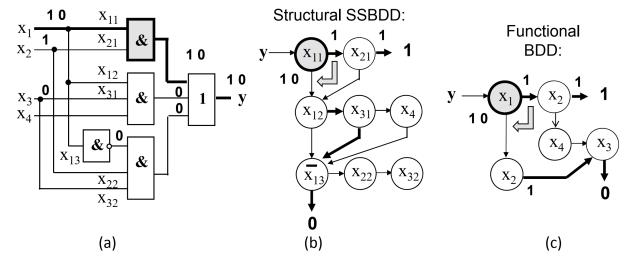

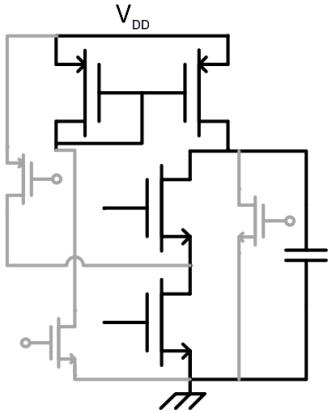

The origins of our test research at TalTech date back to the 1970s, a transformative era in digital testing when foundational methodologies were being established to address the growing complexity of electronic systems. During this period, decision diagrams emerged as a powerful tool for representing and manipulating Boolean functions, largely due to the seminal work of Sheldon Akers introducing Binary Decision Diagrams (BDDs)<sup>3</sup> as a compact and canonical representation of logic functions. In the 1970s, Raimund Ubar introduced Alternative Graphs (AGs)<sup>4</sup>, later refined as Structurally Synthesized Binary Decision Diagrams (SSBDDs), to model both the logic functions and gate-level structures of digital circuits (Fig. 2.1) [2]. Unlike traditional BDDs, which focus solely on functional representation, SSBDDs establish a one-to-one mapping between graph nodes and circuit signal paths, enabling efficient fault simulation and test generation. This structural awareness facilitates detailed fault simulation, test generation, and analysis of fault propagation phenomena, such as fault masking and detectability. For example, SSBDDs can represent multiple stuck-at faults as "fault packages," allowing parallel simulation<sup>5</sup> of fault effects across a circuit. This capability drastically improves efficiency compared to sequential fault injection methods, which struggle with the combinatorial explosion of multiple fault scenarios [2].

To address the growing complexity of digital systems, we extended this framework to High-Level Decision Diagrams (HLDDs). HLDDs generalize SSBDDs for higher abstraction levels, such as register transfer level (RTL) and instruction set architecture (ISA), facilitating cross-level diagnostic modelling. This uniform formalism enabled the development of

<sup>1</sup>The authors thank their current academic colleagues in the TalTech team: Prof. Gert Jervant, Prof. Masoud Daneshthalab, Prof. Samuel Pagliarini, Prof. Peeter Ellerjee, Dr. Tara Ghasempouri, Dr. Levent Aksoy, Dr. Anton Tsertov, Dr. Sergei Devadze, Dr. Mahdi Taheri, Dr. Mohammad H. Ahmadilivani as well all our great postdocs, PhD and MSc students and engaged researchers.

<sup>2</sup>We acknowledge the support by the Estonian Research Council grant PRG1467 CRASHLESS, CoE "Foundations of the Universe" (TK202), and EU Grants TAICHP (#101160182) and TIRAMISU (#101169378).

<sup>3</sup>S. B. Akers, "Binary Decision Diagrams," IEEE Trans. Comput., vol. C-27, no. 6, pp. 509–516, 1978.

<sup>4</sup>R. Ubar (1976) Test generation for digital circuits with alternative graphs. Proc Tallinn Technical Univ 409:75–81 (in Russian)

<sup>5</sup>R. Ubar, S. Devadze, J. Raik and A. Jutman, "Ultra Fast Parallel Fault Analysis on Structurally Synthesized BDDs," ETS, 2007, pp. 131-136.

implementation-independent test generation algorithms, achieving high stuck-at-fault coverage for RISC-type processors<sup>6</sup> and even modelling and verification of temporal assertions<sup>7</sup>. Our comprehensive theory of structural DDs, detailed in [2], integrates these advancements, providing a robust foundation for test-related methods across abstraction levels. Our early adoption of SSBDDs in automated test pattern generators (ATPGs) in the 1980s, deployed within the Soviet defence and computer industries, and the global licensing of the Turbo-Tester software underscore the historical impact.

Fig. 2.1. Representation of a gate-level circuit by SSBDD and BDD

Among other notable research directions of the TalTech team are board-level test solutions employing JTAG and IJTAG [3] technologies that facilitated the creation in 2005 of a spin-off company Testonica Lab<sup>8</sup> led by Artur Jutman. The team has studied Built-In Self-Test<sup>9</sup>, testing of NoCs<sup>10</sup> and nanoelectronics ageing (NBTI) and mitigation [4]. It has contributed to establishing of the open-source RTL analysis EDA tool zamiaCAD<sup>11</sup>, automated RTL debug<sup>12</sup> and cross-level design dependability analysis.

Beyond technical innovation, our historical perspective reflects a collaborative spirit. The team's engagement with the international test community, particularly through the ETS, began in the 1990s and has grown steadily by hosting the symposium in 2005, 2020 and 2025, VLSI-SoC in 2016, editions of DDECS in 2012 and 2023 and numerous other events by the test community. The team led several successful European multi-partner projects RIA DIAMOND (2009-2012, J. Raik), RIA BASTION (2014-2017, Jutman), RIA IMMORTAL (2015-2018, J. Raik), Twinning TUTORIAL (2016-2018, J. Raik), MSCA DN RESCUE (2017-2021, M. Jenihhin), Twinning SAFEST (2021-2023, S. Pagliarini).

<sup>6</sup>A.S. Oyeniran, R. Ubar, M. Jenihhin, C.C. Gürsoy and J. Raik, "High-Level Combined Deterministic and Pseudo-exhaustive Test Generation for RISC Processors," ETS, 2019, pp. 1-6.

<sup>7</sup>M. Jenihhin, J. Raik, A. Chepurov and R. Ubar, "Temporally Extended High-Level Decision Diagrams for PSL Assertions Simulation," ETS, 2008.

<sup>8</sup>Testonica Lab OÜ <https://testonica.com/>

<sup>9</sup>G. Jervan, P. Eles, Z. Peng, R. Ubar, M. Jenihhin, "Test time minimization for hybrid BIST of core-based systems," ATS, 2003, pp. 318-323

<sup>10</sup>J. Raik, R. Ubar and V. Govind, "Test Configurations for Diagnosing Faulty Links in NoC Switches," ETS, 2007, pp. 29-34.

<sup>11</sup>A. Tsepurov, G. Bartsch, R. Dorsch, M. Jenihhin, J. Raik and V. Tihhomirov, "A scalable model based RTL framework zamiaCAD for static analysis," VLSI-SoC, 2012, pp. 171-176.

<sup>12</sup>M. Jenihhin et al., "Automated Design Error Localization in RTL Designs," in IEEE Design & Test, vol. 31, no. 1, pp. 83-92, Feb. 2014.

## 2.B. State of play and assets in related research

In the present day, our research has shifted to address one of the most pressing challenges in modern computing: ensuring cost-efficient reliability for Edge AI chips, with a particular emphasis on Deep Neural Network (DNN) hardware accelerators. The shift to Edge AI, driven by real-time inference demands in resource-constrained environments, has heightened the need for reliable hardware in safety- and mission-critical applications. Our current efforts focus on developing innovative tools and techniques<sup>1</sup> to tackle these challenges.

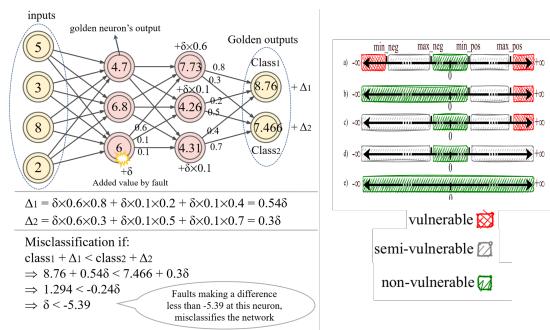

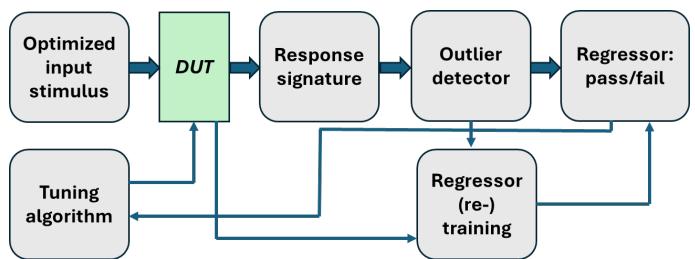

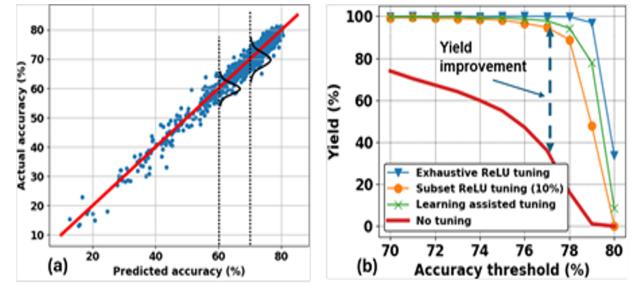

A recent survey<sup>2</sup> categorizes the state-of-the-art DNN reliability assessment methods into fault injection, analytical and hybrid methods. DeepVigor [5] is a semi-analytical method that assesses DNN fault resiliency by providing vulnerability value ranges for neurons and vulnerability factors for layers and models (Fig. 2.2). This approach leverages analytical pruning of the fault space, reducing the need for exhaustive simulation while pinpointing areas requiring selective hardening with minimal overhead. The tool is at the core of open-source frameworks for DNN reliability assessment and enhancement<sup>3,4</sup>.

Fig. 2.2. DeepVigor's semi-analytical DNN reliability assessment through neuron vulnerability value ranges [5]

Recently, we have been exploring approximate computing (AxC) and quantization as a strategy for balancing reliability and efficiency in DNN accelerators<sup>5,6</sup>. Our current work includes in-field error correction techniques, such as the adaptive fault-tolerant approximate multiplier architecture (AdAM) [6], which achieves "negative-overhead" reliability by repurposing unutilized resources in approximate multipliers. These advancements align with industry needs for systolic-array- and data-flow-based accelerators on ASICs and FPGAs in resource-constrained environments.

Industry-scale solutions for today's (FPGA-)SoCs demand a comprehensive cross-layer analysis in the systems fault-

<sup>1</sup>M. Jenihhin et al., "Keynote: Cost-Efficient Reliability for Edge-AI Chips," LATS, 2024.

<sup>2</sup>M. H. AhmadiLivan, M. Taheri, J. Raik, M. Daneshlalab, and M. Jenihhin, "A systematic literature review on hardware reliability assessment methods for deep neural networks," ACM Comput. Surv., 2024.

<sup>3</sup><https://github.com/mhahmadiLivan/DeepVigor>

<sup>4</sup><https://github.com/mhahmadiLivan/SentinelNN>

<sup>5</sup>N. Cherezova et al., "Heterogeneous Approximation of DNN HW Accelerators based on Channels Vulnerability," VLSI-SoC, 2024, pp. 1-4.

<sup>6</sup>S. Nazari, M. Taheri, et al., "FORTUNE: A Negative Memory Overhead Hardware-Agnostic Fault Tolerance Technique in DNNs", ATS, 2024.

tolerance vendor- and user-spaces<sup>7</sup>. Here, the process for fault detection, localization and recovery may be sophisticated and application-dependant, implying on-chip monitors' data analysis and SoC health management protocols<sup>8</sup>, e.g. supported by IJTAG-based infrastructure.

## 2.C. Perspectives and outlook

Looking ahead to the era dominated by AI-centric and highly integrated chips, we foresee growing demand for cost-efficient reliability solutions as Edge-AI applications expand into safety-critical domains. We are exploring advanced techniques, including in-field error correction and cross-layer reliability management, to ensure dependable DNN accelerators.

One key trend is the increasing complexity and heterogeneity of computing architectures: next-generation chips will combine general-purpose processors with AI accelerators, distributed across cloud and edge, and fabricated in advanced technologies that can be more susceptible to faults. TalTech's team is building strong assets for collaboration through participation in European research initiatives, providing a bridge between academia and industry. Notably, the group recently started coordinating EU projects MSCA DN TIRAMISU (2024-2028, M. Jenihhin) and Twinning TAICHP (2024-2027, M. Jenihhin), which focus on energy-efficient and reliable Edge AI hardware. Through these projects, TalTech researchers are partnering with universities and industry players across Europe to develop cross-layer reliability and energy-efficiency solutions from circuit-level up to model- and system-levels for safety-critical applications.

We are eager to address future challenges in digital test and reliability of Edge AI, reinforcing our commitment to the ETS ecosystem. Here, an important direction is improving the autonomy and resiliency of electronic systems. The concept of self-healing or self-aware hardware is emerging, where chips can monitor their own health and adapt to failures. This calls for extending the silicon lifecycle management solutions through SoC-level system health management that TalTech develops in collaboration with the Testonica team.

The interplay between the EU Chips Act and the EU AI Act creates a powerful synergy and amplifies the potential of open-source HW/EDA frameworks by strengthening Europe's semiconductor infrastructure. TalTech is advancing such frameworks through collaboration with the RISC-V community. It also contributes to establishing a new national chips competence centre supported by Chips JU KIIP (2025, J. Raik).

Our vision for the future is deeply collaborative. The ETS community is already very successful, yet it can even further strengthen ties by sharing tools, datasets and expertise, and co-leading joint research projects on tomorrow's computing systems resilience, and contributing to open-source initiatives.

<sup>7</sup>N. Cherezova, K. Shabin, M. Jenihhin, and A. Jutman, "Understanding fault-tolerance vulnerabilities in advanced SoC FPGAs for critical applications," Microelectronics Reliability, vol. 146, 2023.

<sup>8</sup>K. Shabin, M. Jenihhin, A. Jutman, S. Devadze and A. Tserkov, "On-Chip Sensors Data Collection and Analysis for SoC Health Management," DFT, 2023, pp. 1-6

### 3. A LEGACY OF DEPENDABILITY IN CLUJ-NAPOCA, ROMANIA<sup>1</sup>

*Liviu Miclea, Szilárd Enyedi, Iulia Stefan, Ovidiu Stan, Cosmina Corcheș.*

*Technical University of Cluj-Napoca, Romania*

Electronic systems testing has been fundamental to the technological and industrial progress in Cluj-Napoca, with institutions like IPA Cluj (Design Institute for Automation, Cluj-Napoca branch) [7] playing pivotal roles. We trace the evolution of testing in Cluj from 1976 to present-day advancements continued by the DeSy (Dependable Systems) Group at the Technical University of Cluj-Napoca's Automation Department. The conferences co-organized by these teams are also important, starting with THETA in 1982 which evolved into present-day AQTR, and including ETS 2015, TSS 2015, DDECS 2019.

#### 3.A. Historical perspective

Cluj-Napoca has played a pivotal role in the advancement of Romanian computer science, particularly in the fields of automation and testing. The city's contributions date back to 1958 when it organized the first national symposia on cybernetics. This foundation was further strengthened in 1975 with the establishment of the Cluj Territorial Computing Center (CTCC), which turned, back then, the city into a national informatics hub.

A major milestone in Cluj's technological development was the founding of the Design Institute for Automation (IPA) Cluj in 1976. Initially conceived as a regional branch of IPA Bucharest, its establishment was influenced by a government strategy that aimed to develop automation and medical instrumentation industries in Cluj. Prof. Dr. Eng. Marius Hăngănut played a key role in defining its niche focus on automated testing technologies, an area where IPA Cluj quickly excelled.

Under Prof. Hăngănut's leadership, IPA Cluj became a center of innovation, closely collaborating with the Technical University of Cluj-Napoca (TUCN). Prof. Hăngănut later became the head of TUCN's Automation Department. Many of IPA's early specialists, such as Alfred Letia, Clement Festilă, and Olimpiu Negru, were affiliated with TUCN. The institute was instrumental in developing Romania's first programmable logic controllers (AP 101, AP 117) and the ECAROM-800 process computers. During the 1980s, IPA Cluj expanded its expertise, collaborating with major industrial players such as Automatica, Electromagnetica, and IEIA Cluj. Their efforts led to pioneering developments in distributed control systems (SDC-2050) and hydroelectric turbine regulation systems (REH-76M). One of its landmark achievements was the THETAROM family of automated test systems (1976-1993), which were successfully exported to countries like Germany, Poland, and China, enhancing Romania's reputation in automated testing technology.

In 1982, IPA Cluj, led by Prof. Hăngănut, launched the THETA Symposium (Technologies and Equipment for Automated Testing), which became an annual event until 1989. The first edition, held on November 5-6, 1982, featured 135

scientific papers and 227 participants from 28 institutions. The symposium played a crucial role in familiarizing Romania's technical community with global trends in quality assurance, reliability, and maintainability in electronics and automation.

Despite the economic and industrial challenges following the transition to a market economy in the 1990s, IPA Cluj demonstrated resilience by shifting its focus toward SCADA systems, system integration projects, and software-based automation. This transition laid the groundwork for an academic shift, with key IPA figures, including Prof. Dr. Eng. Liviu Miclea, moving into academia. Prof. Miclea, an IPA Cluj researcher from 1984 to 1995, later became a professor at TUCN, significantly influencing automation and dependable systems research.

In 1996, the THETA symposium was rebranded under the IEEE-AQTR (Automation, Quality and Testing, Robotics conference [8]) umbrella, resuming under the leadership of Ioan Stoian (Director of IPA Cluj) and Liviu Miclea (TUCN faculty). Since 2004, the conference has been co-sponsored by the IEEE Computer Society through TTTC, represented by Mr. Yervant Zorian, President of TTTC USA. The conference proceedings since 2006 have all been indexed in IEEE Xplore and Web of Science, accumulating over 1600 papers with authors from over 18 countries, the conference upholding an average acceptance rate of 63%.

#### 3.B. Team

The Dependable Systems (DeSy) group is led by Prof. Dr. Eng. Liviu Miclea. Other members are Prof. Dr. Eng. Honoriu Vălean, Prof. Dr. Eng. Silviu Folea, Prof. Dr. Eng. Ovidiu Stan, Assoc. Prof. Dr. Eng. Szilárd Enyedi, Assoc. Prof. Dr. Eng. Dan Goța, Lecturer Dr. Eng. Iulia Stefan, Lecturer Dr. Eng. Cosmina Corcheș, Lecturer Dr. Eng. Adela Pop, Lecturer Dr. Eng. Alexandra Fanca, Lecturer Dr. Eng. Claudiu Domuța, and Assist. Eng. Marius Misaros.

The PhD student members of the DeSy team include Eng. Henrietta-Helena Futo, Eng. Diana-Elena Niti, Eng. Alexandru Stanciu, Eng. Pavel-Alexandru Bejan, Eng. Alexandru Ciobotaru, Eng. Tudor Covrig, Eng. Lucian Farmathy-Pop, Eng. Alexandra-Elena Dobre, Eng. Vlăduț Dobra, Eng. Andreea Muscan, Eng. Razvan Dologa, Eng. Bogdan Drăghici, Eng. George Flutur, and Eng. Alexandru Jibotean.

The academic transition from IPA Cluj was solidified with the leadership of Prof. Dr. Eng. Liviu Miclea, who played a crucial role in maintaining the legacy of IPA Cluj within TUCN. After joining TUCN as a lecturer in 1995, Prof. Miclea ascended to a full professorship by 2004, serving as Head of the Automation Department (2003-2011), Dean of the Faculty of Automation and Computer Science (2012-2024), currently vice-president of TUCN's Senate.

At TUCN, the Dependable Systems Research Group (DeSy, <https://desy.utcluj.ro>) continues the tradition of automation research and testing while integrating modern challenges such as cybersecurity, artificial intelligence, IoT, and cyber-physical systems (CPS) [9]. The DeSy group focuses on system reliability, security, and resilience, addressing critical sectors such as energy, transportation, and healthcare. Their notable projects include research on cybersecurity, autonomous vehicles, and

<sup>1</sup>Special thanks to DeSy team member Assoc. Prof. Dr. Dan Ioan Goța.

intelligent systems. The group offers consulting, training, and system design services for industries and academia, ensuring the continued relevance and application of their research. Many of the current members finalized their PhD stages under Prof. Miclea's or Prof. Vălean's supervision, several completing training courses abroad.

The IEEE-AQTR biennial conference series is steered by its general chair Prof. Dr. Eng. Liviu Miclea—the DeSy team leader—with the DeSy team members heavily involved in organizing it. With a strong network of international collaborators and industry partnerships, the team remains at the forefront of dependable and secure system development.

### 3.C. Recent publications

The Dependable Systems (DeSy) group has made significant contributions to the field through numerous high-impact publications in recent years.

In 2025, the team continues the research with two new articles on the reliability of assistive robots<sup>1</sup>, and the reliability of neural networks on resource-constrained hardware<sup>2</sup>.

In 2024, DeSy analyzed the feasibility of training neural networks on data sourced directly from medical imaging equipment, rather than on images generated by them<sup>3</sup>. The team assessed the reliability of the Pepper Robot in handling office documents<sup>4</sup>. We also explored security in IoT with Kubernetes and Raspberry Pi clusters<sup>5</sup>. The team also analyzed the dependability of a real-time monitoring testing setup<sup>6</sup>.

In 2023, a team member co-authored a study on hybrid Retina Net classifiers for thermal imaging<sup>7</sup>. The team also examined advancements in autonomous service robots<sup>8</sup>. Meanwhile, other members of the team investigated environmental monitoring and air quality prediction for occupational health<sup>9</sup>.

<sup>1</sup>M. Misaros, L. Miclea, D. Goța, A. Stan, O. Stan, and S. Enyedi, "Reliability Calculation for Pepper Robots. Case Study: Assistive Robot With Human," in Lecture Notes in Electrical Engineering, Springer Basel AG, 2025.

<sup>2</sup>S. Enyedi, C.-A. Deac, L. Miclea, O.-P. Stan, D.-I. Gota, and M. Misaros, "A Reliability and Performance Study of Neural Networks on Resource-Constrained Platforms," in Lecture Notes in Electrical Engineering, Springer Basel AG, 2025.

<sup>3</sup>S. Enyedi, "On the Feasibility of Deep Learning Classification from Raw Signal Data in Radiology, Ultrasonography and Electrophysiology," AQTR, 2024, pp. 1–6.

<sup>4</sup>M. Misaros, O. P. Stan, S. Enyedi, A. Stan, I. Donca, and L. C. Miclea, "A Method for Assessing the Reliability of the Pepper Robot in Handling Office Documents: A Case Study," Biomimetics, vol. 9, no. 9, 2024.

<sup>5</sup>I.-C. Donca, O. P. Stan, M. Misaros, A. Stan, and L. Miclea, "Comprehensive Security for IoT Devices with Kubernetes and Raspberry Pi Cluster," Electronics, vol. 13, no. 9, 2024.

<sup>6</sup>D.-E. Nită, T. Kubik, S. Enyedi, and L. C. Miclea, "Increasing the Dependability of a Real-Time System," AQTR, 2024, pp. 1–6.

<sup>7</sup>V. Teju, K. V. Sowmya, S. R. Kandula, A. Stan, and O. P. Stan, "A Hybrid Retina Net Classifier for Thermal Imaging," Applied Sciences, vol. 13, no. 14, 2023.

<sup>8</sup>M. Misaros, O.-P. Stan, I.-C. Donca, and L.-C. Miclea, "Autonomous Robots for Services—State of the Art, Challenges, and Research Areas," Sensors, vol. 23, no. 10, 2023.

<sup>9</sup>A. Pop (Puscasiu), A. Fanca, D. Gota, and H. Valean, "Monitoring and Prediction of Indoor Air Quality for Enhanced Occupational Health," IASC, vol. 35, no. 1, pp. 925–940, 2022.

During 2022, the team members improved continuous integration and deployment for software projects<sup>10</sup>. In another key study, the team examined RFID object identification systems in IoT environments<sup>11</sup>.

An influential work [10] explored early advances in low-power IoT solutions for smart home automation, laying the groundwork for subsequent innovations in the field.

Another paper, tackling reconfiguration security for hardware agents in testing [11], is noteworthy for its applicability, cited by several patents in IEEE Xplore.

The DeSy team's papers have over 1600 citations in international indexes.

### 3.D. Recent projects

The DeSy group has been actively involved in multiple research and development projects, both nationally and internationally, addressing critical areas such as cybersecurity, artificial intelligence, IoT, and cyber-physical systems.

Several team members give lectures within Google's *Cybersecurity Seminars* project<sup>12</sup>, aiming to improve cybersecurity education and awareness. The team also collaborates with École Centrale de Lyon, in a project focusing on developing robust AI systems<sup>13</sup>.

DeSy was also involved in the Inno-EU+ project<sup>14</sup>, a Higher Education Initiative aimed at supporting innovation and entrepreneurship. Another key project focused on integrating cognitive capabilities into robotics for autonomous applications<sup>15</sup>.

DeSy played a vital role in a national PN2-Partnerships project that developed reliable, collaborative SCADA solutions for water resource management<sup>16</sup>. Before that, the team worked with Siemens on a project exploring the use of drones for railway infrastructure maintenance<sup>17</sup>.

DeSy contributed to a European FP7 project that developed highly personalized and ecologically sustainable product-service solutions<sup>18</sup>. Another international collaboration project with Italy's Politecnico di Torino focused on cloud-driven self-healing mechanisms<sup>19</sup>.

The DeSy team members have also received two prestigious ITC/TTTC "Gerald W. Gordon" awards, and international awards for best papers and patents.

<sup>10</sup>I.-C. Donca, O. P. Stan, M. Misaros, D. Gota, and L. Miclea, "Method for Continuous Integration and Deployment Using a Pipeline Generator for Agile Software Projects," Sensors, vol. 22, no. 12, 2022.

<sup>11</sup>C. Corches, M. Daraban, and L. Miclea, "Availability of an RFID Object-Identification System in IoT Environments," Sensors, vol. 21, no. 18, 2021.

<sup>12</sup>Google and TUCN, "Cybersecurity Seminars," 2024-2026.

<sup>13</sup>ECL and TUCN, "FortifyAI: Enhancing Efficiency, Reliability, and Security through Integrated HW-SW Co-Design for AI Algorithms," 2024-2025.

<sup>14</sup>European University of Technology Alliance, "The Innovative European University of Technology," 2021-2023.

<sup>15</sup>UPB et al., "Robots and Society: Cognitive Systems for Personal Robots and Autonomous Vehicles (ROBIN)," 2018-2020.

<sup>16</sup>IPA et al., "SCADA Federation, Collaborative Instrument for Water Management – Someș River Pilot Application (F2S)," 2014-2017.

<sup>17</sup>Siemens and TUCN, "Use of Commercial Drones for Autonomous Maintenance Services in Railways," 2013-2016.

<sup>18</sup>TUCN et al., "Collaborative Environment for Design of Ambient Intelligence Enhanced Product-Services (ProSEco)," 2013-2017.

<sup>19</sup>Politecnico di Torino and TUCN, "Designing Cloud-based Self-healing Cyber-Physical Systems (CyCloSe)," 2013-2014.

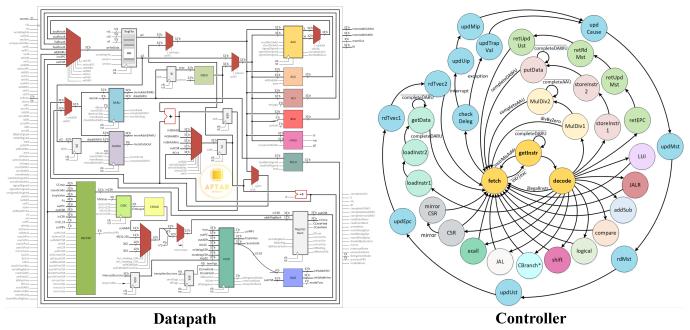

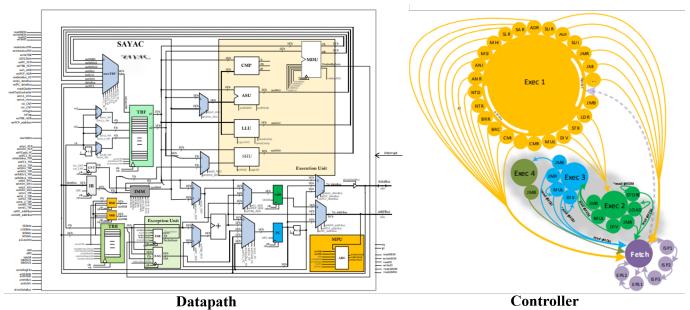

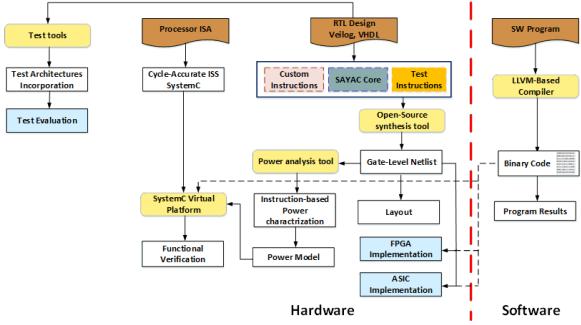

#### 4. ESLAB/LINKÖPING U: SOC TESTING AND DFT

*Zebo Peng and Petru Eles.*

*ESLAB, Linköping University, Sweden*

This section presents briefly the research activities in the areas of SoC testing and DFT at the Embedded Systems Lab (ESLAB) of Linköping University in the last 30 years. It highlights several contributions that were published in the Proceedings of the European Test Symposium and the IEEE Transactions on Very Large-Scale Integration (VLSI) Systems.

##### 4.A. Historical Perspective

The ESLAB research group traces its origins to the 1980s, with a focus on developing the CAMAD high-level synthesis (HLS) system. CAMAD was designed to transform behavioral specifications, written in VHDL, into hardware implementation structures at the register-transfer level. Our approach to HLS introduced a formal representation based on an Extended Timed Petri Nets (ETPN) model, which provides distinct yet interconnected descriptions of control and data paths. ETPN serves as an intermediate design representation, enabling an iterative transformation process that refines high-level specifications into optimized hardware implementations.

The fundamental principle of our methodology is that once a behavioral specification is mapped into an ETPN model, it can be viewed as a primitive implementation, and correctness-preserving transformations can be systematically applied to refine and improve the design. The selection of transformations is guided by an optimization strategy, which concurrently addresses key synthesis tasks, including operation scheduling, data path allocation, and control allocation. Our integrated approach enhances the likelihood of achieving a globally optimal solution. This foundational research has significantly contributed to the evolution of HLS techniques, establishing ESLAB as a pioneer in the field.

Building on the ETPN model and the transformational approach to HLS, we began developing DFT techniques in the 1990s. Our initial focus was on creating a testability analysis technique to assess the intermediate results of the HLS transformation process. This algorithm evaluates key testability metrics, including test generation costs, fault coverage, and test application time. Based on the testability analysis results, targeted testability-improvement techniques are applied to the most test-resistant areas of the design.

We developed three primary testability enhancement techniques: 1) controllability/observability-balance allocation to ensure a more uniform distribution of controllability and observability across the design; 2) partial scan insertion to selectively insert scan registers to improve test coverage while minimizing overhead; and 3) conditional scan installation to introduce conditional scan paths to enhance observability in specific design regions. Unlike traditional post-synthesis testability enhancement methods, our approach integrates testability-improvement transformations directly into the HLS process. By simultaneously considering testability factors alongside operation scheduling, data path allocation, and control allocation, we achieve globally optimized, highly testable designs.

We developed a comprehensive framework for SoC testing, incorporating a suite of algorithms to address test scheduling, test access mechanism (TAM) design, test set selection, test parallelization, and test resource placement. Our approach aims to minimize test application time and reduce TAM cost, while adhering to constraints on power consumption and resource availability. A key component of our methodology is an efficient heuristic-based approach for designing a core-level test interface (wrapper) and a TAM architecture, along with its optimized test schedule [12]. This approach ensures compliance with IEEE P1500 standards while achieving a balance between performance and efficiency.

We developed a hybrid Built-In Self-Test (BIST) solution for SoC testing, integrating pseudorandom test sequences with stored deterministic test patterns in a cost-effective manner. It achieves the optimal balance between these two test techniques, minimizing both test time and memory requirements while maintaining high fault coverage. To achieve this balance, we propose two algorithms that determine the optimal stopping point for pseudorandom test generation and to switch to stored deterministic patterns. Additionally, to accelerate the optimization process, we introduce a fast estimation method that efficiently evaluates the expected cost of different test configurations with minimal computational overhead. Furthermore, we implement an advanced algorithm that identifies the optimal ratio of pseudorandom sequences and deterministic test patterns, ensuring minimum energy consumption while meeting memory constraints, all without compromising test quality [13].

We developed a power-constrained test scheduling method for SoC testing in an abort-on-first-fail environment, where testing is terminated as soon as a fault is detected. Our approach leverages defect probabilities of individual cores to strategically guide test scheduling, ensuring that the expected total test time is minimized while adhering to peak power constraints. We proposed a heuristic algorithm that identifies a near-optimal scheduling order, balancing test efficiency and power constraints. Our method was also extended to support both test-per-clock and test-per-scan approaches, making it adaptable to a wide range of SoC architectures and enhancing flexibility in practical test applications.

Over the years, we have also developed a range of innovative techniques for testing hardware/software systems, addressing both hardware and software components in a unified manner. One of our key contributions is a hierarchical test generation technique for embedded systems, which ensures a seamless approach to testing integrated hardware-software architectures. Additionally, we developed a framework for optimizing assertion placement in time-constrained hardware/software modules, aimed at detecting transient and intermittent faults. This framework systematically identifies candidate assertion locations, associates optimal assertions with each location, and selects the most effective assertion set based on performance impact and assertion tightness [14].

##### 4.B. Thermal-aware Test Techniques

In recent years, our research has focused on addressing thermal-related challenges in SoC testing, where high tempera-

tures pose significant challenges for SoC testing and system performance and reliability. To address these challenges, a thermal-aware test scheduling technique is essential to minimize test application time while ensuring that core temperatures remain within safe operating limits.

We have developed a set of thermal-aware optimization techniques that effectively reduce test time while preventing core overheating. Our approach leverages test set partitioning, dividing test sets into shorter sequences interspersed with cooling periods to dissipate heat and maintain temperature stability. Additionally, we interleave test sequences from different test sets, strategically utilizing cooling periods and test bus bandwidth for data transportation—an approach that significantly reduces overall test time. In this context, the test scheduling problem is formulated as a combinatorial optimization problem, which we solve using constraint logic programming (CLP) to achieve an optimal test execution strategy.

Beyond temperature management during testing, research has also shown that different defects manifest at varying temperature levels, necessitating multi-temperature testing for improved defect detection. To address the extended test time challenge associated with multi-temperature testing, we developed a test scheduling technique that generates the shortest possible test schedules, ensuring that cores under test remain within a defined temperature interval while maintaining high defect detection efficiency. Our work contributes to enhanced SoC reliability by balancing test efficiency, thermal constraints, and defect detection accuracy, making multi-temperature-aware testing a viable solution for SoCs.

In advanced SoC designs, large temperature gradients also pose a significant challenge, exacerbating defects such as early-life failures and delay faults. Traditionally, thermal-aware test schedule techniques usually aimed only to minimize test application time while avoiding overheating. However, these techniques may overlook defects that manifest only under specific temperature conditions or gradients. For example, certain defects, such as clock-skew related faults, may require specific temperature gradients between neighboring blocks to be detected. Consequently, efficient detection of these defects requires precise thermal control during the testing process, to ensure that temperature gradients of appropriate magnitudes are applied to the circuit under test. This challenge is even more pronounced in 3D-stacked integrated circuits (3D-SICs) compared to traditional 2D ICs, due to their inherently larger temperature gradients [15].

To address this issue, we have developed efficient methods for enforcing specified temperature gradients on 3D-SICs during both burn-in and delay-fault testing. Our approach applies high-power stimuli to specific cores through the test access mechanism, eliminating the need for external heating mechanisms. By strategically injecting high-power test stimuli, we generate controlled thermal stress conditions, allowing for targeted defect detection. To further optimize this process, we jointly schedule the execution of the test, the application of high-power stimuli, and the cooling intervals, using temperature simulations to rapidly enforce the desired temperature gradi-

ents [15]. The test schedule generation is guided by thermal functions derived from a set of thermal equations, ensuring precise temperature control throughout the testing process. Experimental results validate the effectiveness of our approach, demonstrating its ability to efficiently enforce specified temperature gradients, thereby enhancing the reliability and accuracy of burn-in and delay-fault testing for both 2D and 3D SoCs.

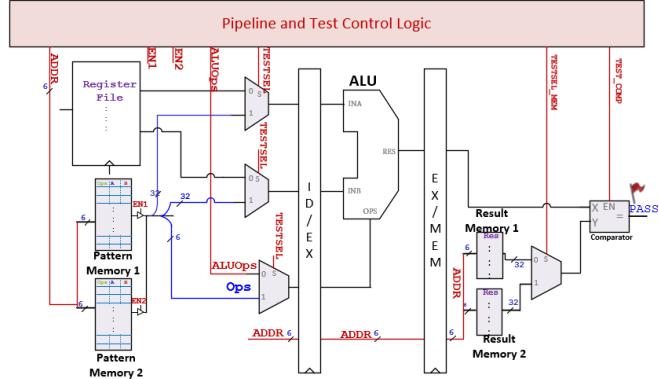

We have also developed a thermal-aware software-based self-testing (SBST) method leveraging bounded model checking (BMC) to ensure that test temperatures remain within specified limits while accurately detecting worst-case delay faults under high-temperature conditions. It employs sequential constraints to guide automatic test pattern generation (ATPG), ensuring that the generated delay test patterns operate in functional mode. Additionally, it utilizes multi-level processor information to reduce model complexity, prevent BMC time-out aborts, and enable automated test program generation [16]. Experimental results demonstrate that our method achieves high delay fault coverage, effectively mitigates yield loss from over-testing, and enhances reliability in temperature-sensitive scenarios.

#### 4.C. Perspectives and Future Directions

Our ongoing research will focus on thermal-aware test and design techniques for SoC and cyber-physical systems (CPS). Many traditional techniques were developed with the assumption that chips within the same batch experience similar temperature profiles during testing and operation. In reality, however, deep-submicron technologies introduce significant process variations, resulting in temperature discrepancies even among chips produced in the same fabrication process. These variations, driven by differences in thermal resistance, capacitance, and power dissipation, require adaptive test and operation strategies that account for these inconsistencies. Addressing these complexities is essential to develop robust and reliable SoC/CPS testing and design methodologies.

Traditional SoC designs that disregard process variation risk inefficiency and unreliable operation. To mitigate these issues, our aim is to develop a framework for analyzing temperature-induced performance characteristics and failure mechanisms that incorporates process variation uncertainties. Since offline temperature simulations often deviate from actual on-chip conditions, an online scheduling approach, where real-time temperature monitoring via on-chip sensors informs test execution, can enhance adaptability. However, such an approach introduces run-time overhead and delays from temperature readouts. A hybrid strategy that takes advantage of both offline and online scheduling is necessary to balance efficiency and accuracy.

Future research directions include also: 1) Integrated design methodologies that holistically address thermal, reliability, security, and performance constraints, streamlining the SoC and CPS design process. 2) On-the-fly CPS optimization, leveraging machine learning and real-time sensor data to dynamically manage fluctuating workloads that cannot be fully anticipated at design time. 3) Efficient testing methodologies capable of handling the growing complexity of CPS architectures, ensuring long-term robustness and reliability throughout the system's lifecycle.

## 5. WHEN SAT-BASED ATPG BECAME PRACTICAL<sup>1</sup>

R. Drechsler<sup>UniB</sup>, S. Eggersglüß<sup>Siemens</sup>, G. Fey<sup>TUHH</sup>, A. Glowatz<sup>Siemens</sup>,

D. Tille<sup>Siemens</sup>.

<sup>UniB</sup>University of Bremen, Germany

<sup>Siemens</sup>Siemens EDA, Germany

<sup>TUHH</sup>Hamburg University of Technology, Germany

While test generation based on Boolean Satisfiability had been proposed early on, taking it to practice took another 15 years. The advent of powerful solvers for Boolean Satisfiability together with deep insights on circuit modeling and features of test pattern generation were the enablers.

### 5.A. Motivation

While Moore's law was still on full track with exponentially increasing numbers of gates per chip, achieving sufficient fault coverage by pre-computed tests became more and more difficult. Classical structural algorithms for *Automatic Test Pattern Generation* (ATPG) were very successful but increasing logic depth and complexity of circuit structures started causing test pattern generation to fail. Here, failing means that the goal of more than 99.9 percent fault coverage was not achieved anymore. To reach such a coverage it is necessary to find test patterns for the modeled faults or to prove that a certain fault is untestable due to logic redundancies. Even relaxing parameters of structural test generation algorithms like FAN conjoined with accepting longer run times for test generation did not fully classify all faults but lead to many unclassified faults, resulting in a low fault coverage.

At about the same time, modern solvers for *Boolean Satisfiability* (SAT) had been developed and shown to be very effective in solving verification problems that had not been solved before. This gave rise to revisit the idea of using SAT for ATPG and lead to the industrial scale application of SAT-based ATPG in the longer run.

### 5.B. Historical Perspective

ATPG uses fault models where the stuck-at fault model was sufficient to create tests that detect all relevant physical defects for a long time. The extension to delay faults then continued to suffice until around 2010. Delay faults can be reduced to stuck-at faults for test generation, so in principle the same algorithms were suitable. The main difference is that two time frames and – by this – a more difficult search problem must be considered.

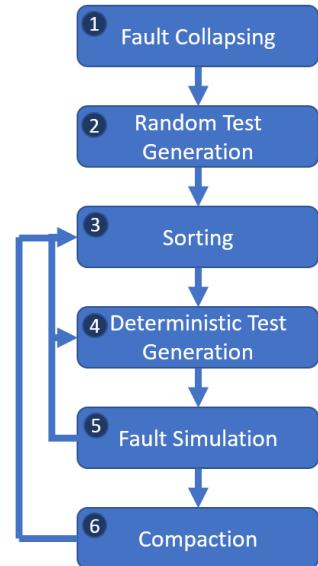

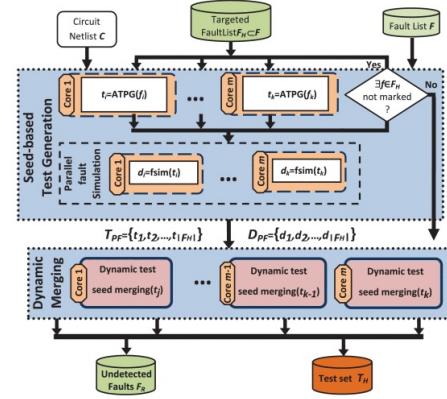

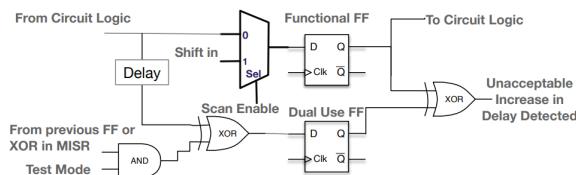

Deterministic test generation is the underlying most complex – NP-complete – problem that decides whether a fault for a specific modeled fault exists or whether the fault is untestable. However, this effort is only required for the faults that are most difficult to test or that are difficult to prove untestable while many faults are easily tested, i.e., many of the possible input assignments would show a difference from the correct behavior in presence of the fault. Thus, larger ATPG frameworks as illustrated in a simplified manner in Figure 5.1 combine deterministic test generation with fault collapsing,

Fig. 5.1. ATPG Framework

random simulation, sorting heuristics and fault compaction to create small test suites with high fault coverage.

Structural algorithms for ATPG like the D-algorithm, PODEM or FAN have been directly running on the circuit structure. The D-algorithm uses the basic insight that a Boolean difference between the faulty and the correct circuit must exist along a structural path between the site of a modeled fault to an observable (pseudo) primary output. PODEM starts at (pseudo) primary inputs to search for assignments that lead to a test for a given modeled fault. FAN starts from the fault location to justify an assignment that creates a difference between faulty and correct circuit that then is propagated towards outputs. Backtracking was needed whenever an assignment was found to not create a test. Basic learning techniques helped to transfer information between backtracking steps, but kept mainly local information and were difficult to implement.

Conceptually, all deterministic test generation algorithms exploit that the Boolean difference between the function of a faulty circuit and the correct circuit must be non-zero. This has been exploited by computing the Boolean difference directly, but the related symbolic algorithms did not scale well for large circuits and complex circuit structures. On the other hand SAT-based ATPG has early been used for comparing two circuits with respect to their functional equivalence using a so-called miter structure. Embedding structural knowledge related to the D-algorithm propagation rules into that model significantly improved the performance, but was – for a long time – not competitive versus the structural algorithms.

This was until SAT solvers became much more powerful tools. Benefiting from the underlying homogeneous data structure related to the conjunctive normal form, non-chronological backtracking, conflict resolution, and the resulting ability to exclude large non-solution spaces efficiently, brought a gigantic advance in their efficiency.

<sup>1</sup>We would like to thank Friedrich Hapke and Jürgen Schlöffel for their contribution and many helpful discussions.

TABLE 5.1

INTEGRATING SAT-BASED ATPG AND FAN [17]

| Circuit | #targ.           | SAT |       | FAN(de) |        | FAN+SAT |        |

|---------|------------------|-----|-------|---------|--------|---------|--------|

|         |                  | ab. | time  | ab.     | time   | ab.     | time   |

| p99k    | $1.6 \cdot 10^5$ | 0   | 6:50m | 1398    | 6:02m  | 0       | 7:25m  |

| p177k   | $1.7 \cdot 10^5$ | 0   | 1:19h | 270     | 16:06m | 0       | 19:03m |

| p462k   | $6.7 \cdot 10^5$ | 6   | 2:16h | 1383    | 1:34h  | 0       | 1:51h  |

| p565k   | $1 \cdot 10^6$   | 0   | 2:23h | 1391    | 2:21h  | 0       | 2:47h  |

| p1330k  | $1.5 \cdot 10^6$ | 1   | 5:05h | 889     | 4:15h  | 0       | 5:00h  |

### 5.C. Collaborative Work and Advancement

A team was formed in 2005 consisting of academic and industrial researchers from the University of Bremen, Germany, as well as from Philips/NXP Semiconductors, Hamburg, Germany. This fruitful collaboration resulted in advancements in the field of ATPG as well as in SAT solving techniques. A short technical overview of the main achievements with respect to the ETS community is given in the following.

With the increase in SAT performance, SAT-based ATPG was able to outperform classical structural algorithms on hard problem instances, i.e., faults for which structural algorithms failed to find a test pattern or could not classify the fault as untestable [18]. While this effectively handles the deterministic test generation problem on a single fault, exploiting this efficiency within a full ATPG framework requires significant effort [17]. The integration with existing engines is an engineering aspect. Non-Boolean behavior of circuitry must efficiently be encoded. Environment constraints resulting from the integration into larger structures must be enforced to generate valid tests that can be applied in practice. If these practical aspects are treated, SAT-based ATPG can speed up the overall process significantly while increasing the fault coverage at the same time. The work in [17] showed that a significant fault coverage increase was achieved on industrial circuits. Table 5.1 shows for selected circuits with a given number of ATPG targets (#targ.) how SAT reduces the number of unclassified faults (ab.) and the combination FAN+SAT yields also acceptable run times.

However, the increase in design sizes, complexity and more complex fault models require also a continuous improvement of modeling and solving techniques to maintain the practicability of SAT-based ATPG. A selection of these improvements is discussed in the following.

An advantage of turning test generation into a satisfaction problem is that constraint modeling allows – in principle – to easily embed other types of faults. While the traditional modeling consisted of only stuck-at faults, the SAT-based ATPG formulation was extended to transition faults, path delay faults as well as small delay defects. However, the computational complexity is still NP-complete, thus only increasing the size of the problem instance may still lead to performance bottlenecks. Smart encoding achieves the required scalability and the guarantees on test quality needed for the practical application [19].

The traditional approach of first generating the complete SAT instance and then solving it has its disadvantages. Firstly,

conflicts within untestable faults often occur locally bounded to the fault site. While proving them unsatisfiable is trivial, the complete instance has to be generated at first. Secondly, unlike circuit-based approaches, it is not sufficient to propagate the fault effect to an observation point and justify the required propagation paths. Instead, the complete SAT instance has to be solved. Incremental techniques, where a partial instance is generated initially and extended if necessary, have shown significant improvements [20].

Usually, a SAT instance is a one-to-one mapping of the circuit structure to a Boolean formula. The redundancy, often contained in the circuit logic, is therefore encoded in the SAT instance as well. This leads to increased solving runtimes. Optimizing the Boolean logic, e.g. with the application of BDDs, can significantly reduce the SAT instance size and consequently the required runtime of SAT-based ATPG [21].

Applying other reasoning techniques like interpolation or induction, adding structural information into the SAT solving process can further improve the speed. Replacing of the SAT solver by a Pseudo Boolean SAT or Optimization solver facilitates more powerful modeling, e.g., to find longest paths.

### 5.D. Outlook

Today, SAT-based ATPG is a standard engine due to its effectiveness and versatility in including new fault models. Until today numerous further techniques have been developed to address test compaction, newer fault models, integrating technology information and working towards system-level test.

## 6. ONSEMI AND KU LEUVEN: ADVANCES IN AUTOMATED DEFECT-ORIENTED TESTING OF ANALOG AND MIXED-SIGNAL INTEGRATED CIRCUIT<sup>1,2</sup>

*A. Coyette, R. Vanhooren, W. Dobbelaere - onsemi Belgium;

G. Gielen - KU Leuven, Belgium*

During their research collaboration over the past decade, onsemi and KU Leuven have strongly invested in the development of defect models and techniques for the automated generation of defect-oriented test methods and design-for-test techniques for analog and mixed-signal (AMS) integrated circuits (ICs), with the goal to maximize defect coverage and minimize test escapes. This paper gives an overview and perspective of the main achievements.

### 6.A. Historical perspective of the research

Throughout their decade of collaborative research, onsemi and KU Leuven have realized significant achievements with high impact. These have highly increased the detection of hard and latent defects and reduced the test escapes in AMS IC testing: 1) several analog defect models have been published; 2) novel design-for-test (DFT) structures have been presented and frameworks have been developed for their automatic insertion in AMS circuits to enhance controllability and observability; and 3) techniques have been developed for the (automated) generation of test signals and signature/test data analysis. Several of these achievements will now be highlighted below.

1) *Defect Models*: A fundamental and critical element of a defect-oriented testing approach obviously resides in the defect models being used. While the large body of literature uses over and over again – and with success – the same typical fault models such as the 5-fault or 6-fault models for transistors, the onsemi-KU Leuven collaboration also analyzed the weaknesses of these existing models in adequately representing physical failures, and invested in the development and validation of better analog defect models: the open gate model and the pre-activation of gate oxide breakdown.

In [22], KU Leuven-onsemi have presented a new open-gate DC fault model instead of the commonly used high-resistance model. The model is validated on experimental results on fabricated test circuits in 0.35- $\mu\text{m}$  BCD technology. The paper also presents a new testing approach to detect open defects in analog circuits, based on forcing the transistors outside their designed operation region.

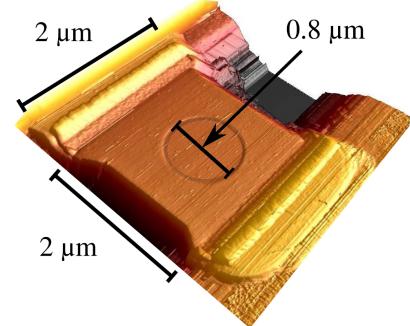

Once all hard defects adequately detected through testing, the main problem for test escapes that cause IC failures in the field comes from latent defects like pinholes. In [23], KU Leuven-onsemi have presented a compact model for such pinhole defects that can be used to develop test methods for latent defect detection. The model has experimentally been validated on a 0.35- $\mu\text{m}$  DMOS technology and establishes the practical range of model values that should be used in simulations. The experiments consist of characterizing transistors containing

<sup>1</sup>The authors acknowledge the Flemish authorities for funding this work through multiple projects: Safe-IC 1, Safe-IC 2, NoRMA and AnalogTRIC.

<sup>2</sup>Other co-authors of this work are Baris Esen, Nektar Xama and Jhon Gomez.

latent defects that have been introduced artificially by etching pinholes in their gate (see an example in Figure 6.1). The measurement results show that the drain current in transistors with defects increases with the area and depth of the defect, and that this behavior can be modeled accurately using an effective  $\text{tox}$  value during test simulations.

As clear indication of the impact of this work, these contributions on AMS defect models have been anchored into IEEE standards like P2427 on Analog Defect Modeling.

Fig. 6.1. Atomic force microscopy picture of a transistor on which a pinhole was introduced for the modeling of latent defects in [23].

2) *Automated insertion of DfT structures* : The focus in this part of the collaboration has been to develop DfT structures and optimization algorithms to insert these structures into the Circuit under Test (CUT) such as to increase the defect coverage at the lowest possible cost. The targeted DfT solutions were lightweight in order to minimize the silicon area overhead and to facilitate generic deployment, i.e. they should be general enough, such that they can be inserted in all or most types of circuits. For instance, one simple DfT example explored was to add test diodes to the circuit, allowing a fully simultaneous detection of potential defects<sup>3</sup>.

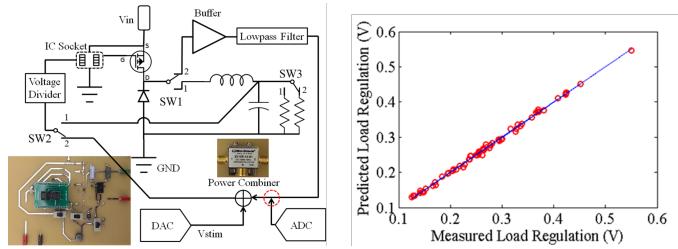

To enhance the controllability of a given AMS circuit during testing, the topology modification technique has been developed, so that pull-up or pull-down test transistors are inserted into the initial circuit to make a connection between targeted nodes and the ground or power supply<sup>4</sup>. During testing, the gates of these inserted transistors and hence the connections are activated, hereby modifying the topology of the circuit to better expose targeted defects. Later this topology modification method was developed further to address the specific case of screening out latent defects [24], a contribution that received the ETS 2017 Best Paper award and illustrated in Figure 6.2.

To enhance the observability of a given circuit, a technique has been introduced [25] to determine circuit locations to which locally small detection blocks are to be connected. The presence of a targeted defect triggers such “detector block”, which then leaves a detectable trace in the power consumption. Hence,

<sup>3</sup>B. Esen, et al. "A very low cost and highly parallel DfT method for analog and mixed-signal circuits," proceedings IEEE European Test Symposium (ETS), 2017.

<sup>4</sup>A. Coyette, et al. "Automated testing of mixed-signal integrated circuits by topology modification," proceedings IEEE VLSI Test Symposium (VTS), 2015.

Fig. 6.2. Example of topology modification (in gray) applied in [24].

defect coverage is increased without extra test pins and with limited extra area.

Later on, controllability-enhancing and observability-enhancing DfT structures were co-generated and their combination was co-optimized to maximize the overall defect coverage at minimum extra test cost<sup>1</sup>. This was then extended to a full Built-In Self-Test (BIST) approach for analog IP blocks, where the blocks are co-designed with low-cost DfT structures for on-chip test signal generation and response analysis.

This work had a large impact on industry. Siemens has presented in 2024 at the International Test Conference follow-up developments and results capitalizing on the usage of the topology modification and local-detection techniques. For example, ADC circuits can now be tested within microseconds with high defect coverage and defect simulations within the same day. Further investigations are also occurring at onsemi to effectively deploy these techniques in the field.

3) *Automated generation and analysis of test signals:* The third part of the onsemi-KU Leuven collaboration focused on methods for the automated generation of improved test signals and test response analysis to increase the coverage of hard and latent defects.

For automated analog test signal generation, the ADAGE tool has been developed<sup>2</sup>. It determines optimal test stimuli to maximize the defect coverage, while simultaneously adding the necessary DfT circuitry. It uses circuit partitioning and interval arithmetic to deal with large circuit complexity<sup>3</sup>. Experiments show a large increase in coverage at minimum test cost.

Several methods have been developed for improved test response analysis. The optimized selection of proper defect-specific masks on test outputs has been shown to improve the

<sup>1</sup>A. Coyette, et al. "Automatic generation of test infrastructures for analog integrated circuits by controllability and observability co-optimization," *Integration, the VLSI Journal*, 2016.

<sup>2</sup>A. Coyette, et al. "ADAGE: automatic DfT-assisted generation of test stimuli for mixed-signal integrated circuits," *IEEE Design & Test*, Vol. 35, no. 3, June 2018.

<sup>3</sup>A. Coyette, et al. "Automatic test signal generation for mixed-signal integrated circuits using circuit partitioning and interval analysis," *proceedings IEEE International Test Conference (ITC)*, 2016.

defect coverage<sup>4</sup>. Also the use of Dynamic Part Average Testing (DPAT) instead of standard PAT at the final testing stage of ICs has been shown to improve the analog fault coverage<sup>5</sup>. The combination of this DPAT with information from visual inspection allows to effectively screen out outliers at a small increase in yield loss [26], a contribution that received the ETS 2020 Best Paper award. The use of multivariate statistical methods has also been shown to be effective for building predictor models for outlier behavior<sup>6</sup>. And even the use of relatively simple metrics such as the Difference in Distance to Mean value (DDTM) has been demonstrated to better identify latent defects at zero extra cost<sup>7</sup>.

### 6.B. Current state of play

Recent work is focusing on improving the defect coverage even further, also for latent defects, to bring the level of AMS test escapes closer to the target of zero part-per-billion (PPB) needed to avoid field returns. The use of machine learning techniques has been shown to extract even more information out of test data to this purpose. An approach using pre-trained SVM classifiers showed excellent results for latent defect detection at limited yield loss and without extra tests in the test program<sup>8</sup>. Secondly, embedding test generation and signature analysis in analog IP blocks with embedded BIST not only allows continuous monitoring of circuit functioning, but also shortens the total test time development<sup>9</sup>.

### 6.C. Connection to ETS and outlook

Many of the publications resulting from the joint onsemi-KU Leuven research collaboration have been published at the European Test Symposium (ETS), and two papers even received the Best Paper Award (in 2017 and 2020). It is clear that techniques for automating and improving the effectiveness of AMS IC testing and the related DfT methods are extremely important in industry, especially for safety-critical applications like automotive. In addition, industry is being confronted with many additional constraints. Time to market pressure is always high, not only for design but also for test development. Also the tasks of the engineers keep rising, with additional constraints such as functional safety, cybersecurity assessment and formal requirement management. These constraints need effective solutions in the near future.

<sup>4</sup>A. Coyette, et al. "Optimization of analog fault coverage by exploiting defect-specific masking," *proceedings IEEE European Test Symposium (ETS)*, 2014.

<sup>5</sup>W. Dobbelaere, et al. "Analog fault coverage improvement using final-test dynamic part average testing," *proc. International Test Conference (ITC)*, 2016.

<sup>6</sup>N. Xama, et al. "Avoiding mixed-signal field by outlier detection of hard-to-detect defects based on multivariate statistics," *proceedings IEEE European Test Symposium (ETS)*, 2020.

<sup>7</sup>J. Gomez, et al. "DDtM: increasing latent defect detection in analog/mixed-signal ICs using the difference in distance to mean value," *IEEE Tr. on Computer-Aided Design*, Vol. 41, no. 11, Nov. 2022.

<sup>8</sup>N. Xama, et al. "Boosting latent defect coverage in automotive mixed-signal ICs using SVM classifiers," *IEEE Tr. on Computer-Aided Design*, Vol. 42, no. 10, Oct. 2023.

<sup>9</sup>J. Gomez, et al. "High-cover analog IP block test generation methodology using low-cost signal generation and output response analysis," *proceedings IEEE European Test Symposium (ETS)*, 2023.

## 7. IMEC IN TEST

*Po-Yao Chuang and Erik Jan Marinissen.

imec – Leuven, Belgium*

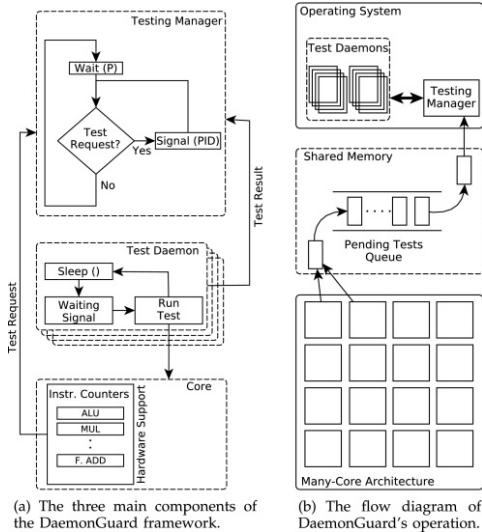

### 7.A. Team Composition

For the first 24 years of imec's existence, "test" was not considered a research topic. Imec's fabs — at the time only two, one for  $\phi 200$ mm wafers and one for  $\phi 300$ mm wafers — produced numerous wafers filled with parametric test structures such as Meander-Forks and Van der Pauws. These structures help(ed) characterize various technology options as part of imec's world-leading wafer processing technology research. However, testing was seen as routine operational work, not worth patenting or publishing.

This all changed in October 2008 with the arrival at imec of Erik Jan Marinissen. Several customers from imec's 3D-Integration research program had begun inquiring about how and when to test 3D-stacked multi-dies. In response, imec hired Marinissen, who had previously worked for almost 20 years at Philips Research on various test and design-for-test (DfT) topics, the most important one being modular testing of embedded-core-based SoC testing.

For fifteen years, imec's test research team was a one-man operation, occasionally supported by individual colleagues, suppliers, customers, and students. Among those colleagues were Phillippe Absil, Eric Beyne, Kristof Croes, Jeroen De Coster, Jaber Derakhshandeh, Bart De Wachter, Ingrid De Wolf, Luc Dupas, Mario Konijnenburg, Dimitri Linten, Rafal Magdziak, Stephan O'Loughlin, Herman Oprins, Armita Pod-pod, Siddharth Rao, Gouri Sankar Kar, Michele Stucchi, Joris Van Campenhout, and Geert Van der Plas. Among the suppliers were companies like Cadence Design Systems, Mentor Graphics (now Siemens EDA), Synopsys, Cascade Microtech (now FormFactor), Feinmetall, MPI Corporation, Technoprobe, and Tokyo Electron, while among the customers were ARM, GLOBALFOUNDRIES, Qualcomm, and TSMC.

Students from around the world traveled to Leuven, usually for internships lasting six to nine months: Jouke Verbree (TU Delft), Chun-Chuan Chi (NTHU Hsinchu), Sergej Deutsch (Braunschweig), Po-Yuan Chen (NTHU Hsinchu), Christos Papameletis (TU Delft), Tobias Burgherr (FHNW), Konstantin Shibin (TalTech), Ferenc Fodor (Cluj-Napoca), Ming Shao (KU Leuven), Yu Li (KU Leuven), Harm van Schaaijk (TU Eindhoven), Yu-Rong Jian (NTHU Hsinchu), Pai-Yu Tan (NTHU Hsinchu), Santosh Malagi (TU Delft), Leonidas Katselas (Thessaloniki), Michael Mainemer (TU Delft), Min-Chun Hu (NTHU Hsinchu), Stef Hermans (TU Eindhoven), Ricardo Pardo Parado (TU Eindhoven), Francesco Lorenzelli (Bologna), Marco Claessens (TU Eindhoven), Lizhou Wu (TU Delft), Zhan Gao (TU Eindhoven), Po-Yao Chuang (NTHU Hsinchu), Francesco Lorenzelli (KU Leuven), Sicong Yuan (TU Delft), Tsung-Hsuan (Annie) Wang (NTHU Hsinchu), and Fang-Ying (Kelly) Chen (NTHU Hsinchu).

In 2022, imec, under influence of Marinissen's Parkinson's Disease, opened a vacancy for a second employee in the Test and DfT team. There was a lot of response on this vacancy