#### An Efficient Rectifier Hybridizing Synchronized Electric Charge Extraction and Bias-Flipping for Triboelectric Energy Harvesting

Peng, Wenyu; Van Driel, Willem; Zhang, Guogi; Du, Sijun

DOI

10.1109/ISCAS58744.2024.10558007

Publication date

**Document Version**Final published version

Published in

ISCAS 2024 - IEEE International Symposium on Circuits and Systems

Citation (APA)

Peng, W., Van Driel, W., Zhang, G., & Du, S. (2024). An Efficient Rectifier Hybridizing Synchronized Electric Charge Extraction and Bias-Flipping for Triboelectric Energy Harvesting. In *ISCAS 2024 - IEEE International Symposium on Circuits and Systems* (Proceedings - IEEE International Symposium on Circuits and Systems). IEEE. https://doi.org/10.1109/ISCAS58744.2024.10558007

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## An Efficient Rectifier Hybridizing Synchronized Electric Charge Extraction and Bias-Flipping for Triboelectric Energy Harvesting

Wenyu Peng, Willem van Driel, Guoqi Zhang, Sijun Du

Department of Microelectronics, Delft University of Technology, Delft, the Netherlands

sijun.du@tudelft.nl

Abstract—A triboelectric nanogenerator (TENG) is a kinetic energy transducer with small and time-varying internal capacitance, which increases the difficulties of extracting harvested energy. In this paper, an efficient rectifier, hybridizing synchronized electric charge extraction (SECE) and bias-flipping techniques, is proposed. The two techniques alternatively operate at opposite voltage polarities of the TENG. By taking advantage of the varying capacitance, the proposed synchronized extraction and flipping (SEF) rectifier shows significantly improved energy extraction performance. The design is implemented in a 180-nm high-voltage BCD technology, and the results show a 7.4X energy extraction enhancement, 65-V voltage tolerance, and 35-nA quiescent current.

Index Terms—Energy harvesting (EH), synchronized switch harvesting on inductor (SSHI), synchronous electrical charge extraction (SECE), triboelectric nanogenerator (TENG)

#### I. INTRODUCTION

Internet-of-Things (IoT) and biomedical devices are used to make people's lives smarter and easier. Most of them are powered by batteries, which will run out of energy eventually. Energy harvesting technology is considered an alternative power supply with more durability and a smaller form factor. The triboelectric nanogenerator (TENG) is one of the kinetic energy transducers proposed recently. It transforms kinetic energy into electrical energy via the displacement current generated by contact electrification [1]. Different from conventional kinetic energy transducers, such as electromagnetic generators and piezoelectric transducers (PT), TENG is advantageous in harvesting energy from low-amplitude and irregular vibrations, i.e., it is not limited by a fixed resonant frequency [2]. Hence, its applications in ambient and biological energy harvesting are largely widened [3]–[5].

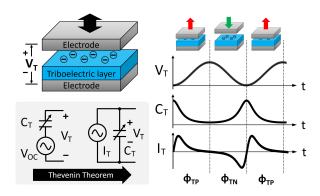

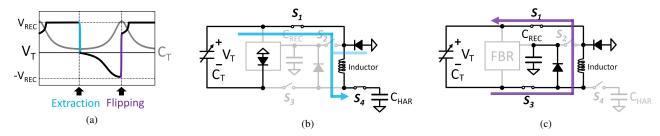

Fig.1 presents a typical TENG and its electrical characteristics. The top and bottom electrodes produce an inherent capacitance,  $C_T$ , that is small and time-varying due to the displacement. Varying from tens to hundreds of pico-farads,  $C_T$  introduces high open-circuit voltage and asymmetric output impedance, decreasing energy extraction efficiency when using passive rectifiers. With the increasing research interest in triboelectric energy harvesting (TEH), several solutions were proposed previously. A dual-output full-bridge rectifier (FBR) with maximum power point tracking (MPPT) was proposed to improve the energy extraction performance of passive rectifiers [6], [7]. Active rectifiers were employed, such as synchronized

Fig. 1: The structure, equivalent circuit and characteristics of a typical TENG.

switch harvesting on inductor (SSHI) [8], [9], multi-chipstacked bias-flip (MCS-BF) [10], and multi-shot synchronous electric charge extraction (SECE) [11] rectifiers, to increase the energy harvesting efficiency. The bias-flip technique aligns the phases of the output voltage,  $V_T$ , and current,  $I_T$ , to decrease the energy loss when charging  $C_T$ . However, during the negative- $I_T$  semi-period of TENG,  $C_T$  increases, which leads to electrostatic energy degradation of the flipped charge on  $C_T$   $(E = \frac{1}{2}Q^2/C)$ . This phenomenon only applies to varying- $C_T$  TENGs, the majority of widely used TENGs. Hence, constant- $C_T$  TENGs, such as wind-driven TENGs, are exempted from this energy loss. On the other hand, the SECE rectifier has lower energy extraction efficiency due to the charge-sharing loss. Therefore, efficient energy extraction circuits for varying- $C_T$  TENGs are needed to minimize the electrostatic energy loss.

This work proposes a synchronized extraction and flipping (SEF) rectifier, hybridizing SECE and bias-flip techniques, to optimize energy extraction performance from TENGs. The theoretical research and topology of the proposed energy harvester will be first presented in Section II. Then, implementation details are presented in Section III, followed by the layout design and simulation results discussed in Section IV. Finally, the conclusion is drawn in Section V.

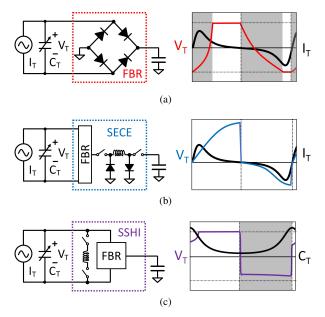

Fig. 2: The circuit and operation waveform of an (a) full-bridge, (b) SECE, and (c) SSHI rectifiers.

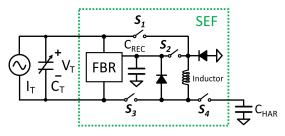

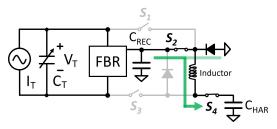

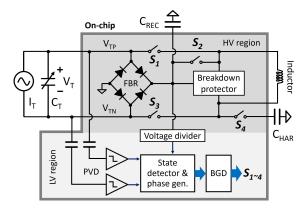

Fig. 3: The proposed synchronized extraction and flipping (SEF) technique for triboelectric energy harvesting.

### II. PROPOSED SYNCHRONIZED EXTRACTION AND FLIPPING TECHNIQUE

#### A. Triboelectric energy harvesting optimization

Similar to piezoelectric energy harvesting, the internal capacitor of TENG,  $C_T$ , introduces a phase difference between the output voltage and current when harvesting energy via FBR, as presented in Fig.2(a), which causes energy loss. SECE and SSHI rectifiers were proposed to tackle this issue. An SECE rectifier accumulates the charge on  $C_T$  and extracts it when  $V_T$  reaches the peak. However, the current BCD technology can hardly tolerate the high open-circuit voltage from TENGs. On the other hand, an SSHI rectifier flips  $V_T$ when  $I_T$  changes polarity and extracts energy to a storage capacitor through a full-bridge rectifier (FBR). Nevertheless, the flipped charge will lose energy during the negative period due to the increasing- $C_T$  as shown in Fig.2(c). Therefore, in this paper, we propose a new synchronized extraction and flipping (SEF) rectifier, employing the SECE and SSHI techniques in different half periods to optimize the energy extraction performance from TENGs.

Fig. 4: The operation and current path when  $V_{REC}$  exceeds breakdown voltage.

#### B. Operational principle

Fig.3 presents the diagram of the proposed SEF rectifier. The FBR block and a rectification capacitor,  $C_{REC}$ , are used to store the extracted energy temporarily and to maintain the rectification voltage  $V_{REC}$  at a high level. Due to the high open-circuit voltage of the TENG, the maximum output power point is usually at hundreds of volts; thus,  $V_{REC}$  should be maintained at the breakdown voltage of the device to maximize the extracted power. The energy is converted to the harvesting capacitor  $C_{HAR}$  when  $V_{REC}$  exceeds breakdown voltage via a shared inductor, with the current path presented in Fig.4.

The operation waveform of the proposed SEF rectifier is shown in Fig.5. When  $I_T$  switches from positive to negative, when  $C_T$  is at its minimum value, an extracting phase occurs to completely extract the energy stored in  $C_T$  to  $C_{HAR}$  with the phases presented in Fig.5(b). At this moment, an SECE operation is more advantageous than a bias-flip operation because  $C_T$  will increase in the following semi-period, which degrades the energy of charge on it. Thus, emptying the charged in  $C_T$  reduces the subsequent electrostatic energy loss. Besides, it eliminates the polarity difference between  $V_T$  and  $I_T$  to reduce the energy loss in charging  $C_T$ . After a semiperiod,  $I_T$  switches from negative to positive, and  $C_T$  is at its maximum value. Since  $C_T$  will decrease in the next semiperiod, the charge on  $C_T$  can help harvest electrostatic energy. Hence, a bias-flip operation is more preferred here, compared to an SECE operation. Thus, bias-flipping is employed to synchronize the polarities of  $V_T$  and  $I_T$  and retain the charge in  $C_T$ . The operation phases of the bias-flipping are presented in Fig.5(c). Therefore, the proposed SEF is the most optimized electrostatic energy extraction method compared to single SECE or SSHI.

#### III. IMPLEMENTATION

#### A. System architecture

The architecture of the proposed SEF rectifier is presented in Fig. 7. The high-voltage (HV) 180-nm BCD technology is utilized to achieve a maximum device break-down voltage of 65V. The switches operating in HV region are implemented with laterally-diffused MOS (LDMOS) transistors with a breakdown voltage of 65V, while the control circuit works at 1.8V to lower the power consumption of the whole system. The TENG state detector monitors  $V_T$  and thus is designed with HV isolation and low-voltage (LV) MOSFETs. Based on

Fig. 5: (a) The operation waveform of SEF, and the current path when (b) synchronized extracting and (c) bias-flipping.

Fig. 6: The top-level block diagram of the proposed system.

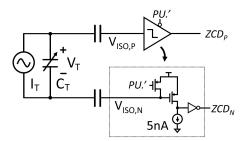

Fig. 7: The proposed peak voltage detector with HV capacitive isolation and fast low-power falling-edge trigger.

the current state, the phase generator block will control the HV switches via bootstrap gate drivers (BGDs). The details of the state detector and BGDs will be elucidated in the following.

#### B. TENG state detector and phase controller

The voltage drop at the outputs of TENG when  $I_T$  crosses zero is monitored by a peak voltage detector (PVD). It consists of two parts: an HV capacitive isolation and a fast low-power falling-edge trigger. To protect LV MOSFET,  $V_{ISO}$  is pulled up when there is a sharp  $V_T$  variation. When utilized to sense the TENG state, the  $V_T$  variation can be converted to the trigger without degradation due to the high input impedance. This trigger is designed to operate at 1nA quiescent current, achieving fast responses to voltage drop.

In addition to TENG state detection, the PVD is also utilized to determine the flipping phase length in the biasflip operation. During the flipping phase,  $V_T$  oscillates. The

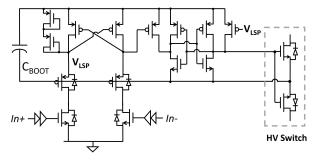

Fig. 8: The circuit diagram of the bootstrap gate driver (BGD) block and the HV switch (HVS).

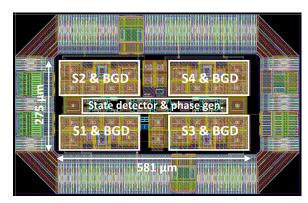

Fig. 9: The layout of the proposed rectifier.

oscillation should be stopped after exactly a half pseudo-period when  $V_T$  reaches the maximum. To achieve this, fast responses to the voltage change are required. Thanks to the quick response of the PVD, nanosecond-scale control is achieved, which guarantees efficient bias-flipping.

#### C. High-voltage switch and bootstrap gate-driver (BGD)

Fig. 8 presents the circuit diagram of the BGD and the HV switches driven. The HV switch comprises two n-type LDMOS with source terminals connected to reject leakage current through the body diode. Due to poor mobility, LDMOS switches should be well-sized to hold the current. With a 1-mH inductor and thanks to the small  $C_T$ , the current flowing through the inductor is at the mA level; hence, the onresistance of switches does not result in severe energy loss. The BGD drives this switch by controlling the gate-source voltage. To drive the switch,  $V_{BOOT}$  is charged to 5V first.

TABLE I: Comparison of the state-of-the-arts.

|                                                 | JSSC 2021 [7]   | TCAS-I 2021 [8] | JSSC 2022 [10]                     | This work* |

|-------------------------------------------------|-----------------|-----------------|------------------------------------|------------|

| Process                                         | 180-nm BCD      |                 |                                    |            |

| TENG capacitance                                | Varying         | Varying         | Fixed                              | Varying    |

| Extraction Technique                            | Dual-output FBR | P-SSHI          | MCS-BF                             | SEF        |

| Inductor                                        | 10mH            | 2×1mH           | 10mH                               | 1mH        |

| Quiescent current                               | 121nA           | 53nA            | N/A                                | 35nA       |

| Power extracted by rectifier $(P_{\text{EXT}})$ | 3.9-10.5 μW     | 1.53mW          | 1.2mW (2-chips) / 823 µW (3-chips) | 133 µW     |

| FoM $(P_{\text{EXT}}/P_{\text{FBR,ideal}})$     | N/A             | 1.62×           | 3.14× (2-chips) / 2.14× (3-chips)  | 7.4×       |

<sup>\*</sup> Simulation results

Fig. 10: The waveform of key signals in the rectifier.

After providing a pulse to In+, the gate terminal of the switch is connected to  $V_{BOOT}$  so that when the source voltage lifts, the gate voltage follows to avoid the breakdown of the LDMOS. The switch is turned off by giving a pulse to the other input node In- so that the  $V_{gs}$  is set to zero. This structure is advantageous in low static power consumption and can achieve free level shifting between 0V and 65V.

#### IV. POST LAYOUT AND SIMULATION RESULTS

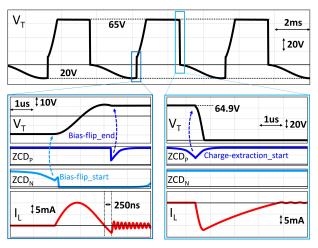

The layout of the proposed SEF rectifier is shown in Fig.9, with key blocks highlighted. The chip occupies an active area of  $0.16\,\mathrm{mm}^2$  ( $0.46\,\mathrm{mm}^2$  with pad-ring). The TENG model used in the simulations has an open-circuit voltage of 200V and capacitance varying between 45pF and 550pF. A segment of the transient waveform of  $V_T$  is presented in Fig. 10 when the operation frequency of the TENG is set as 200Hz. The system can operate at a maximum voltage of 65V. The biasflip starts when PVD detects voltage drop at the negative side of  $V_T$  ( $V_{TN}$ ). The flipping stops when a voltage drop is detected at the positive side of  $V_T$  ( $V_{TP}$ ), which indicates that  $V_T$  reaches the peak. Due to the parasitic capacitance of the circuit, the voltage drop is delayed from the zerocrossing point of  $I_L$  by around 250 ns, which leads to a slight degradation in the flipping efficiency. Thanks to the FBR, the voltage at either side of the inductor is limited to 65V to avoid on-chip device breakdown. Then, at the next zero- $I_T$  moment, synchronized charge extraction starts after detecting a voltage

Fig. 11: The extracted power versus rectified voltage.

drop at  $V_{TP}$ . The extraction stops when  $V_{TP}$  drops below 0 V, which eliminates the need for precise control due to the current path through the diode.

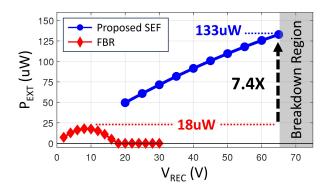

The output power in a range of rectification voltage  $V_{REC}$  is presented in Fig. 11. The output power reaches a peak of  $133\,\mu\mathrm{W}$  when  $V_{REC}$  is equal to  $65\,\mathrm{V}$ , which is 7.4 times higher compared to an ideal FBR. Thus, the proposed SEF rectifier effectively improves the energy extraction efficiency from TENGs. Besides, the quiescent current of the proposed rectifier is only  $35\,\mathrm{nA}$ , which strengthens the advantage of this system in low-power application scenarios.

Table. I compares the proposed rectifier with state-of-theart triboelectric energy harvesting interfaces from different perspectives. This is the first time to hybridize the SECE and bias-flip techniques in triboelectric energy harvesting, achieving energy extraction enhancement of 7.4 times the output power of an ideal FBR and low-power sensing with a 35nA quiescent current.

#### V. CONCLUSION

This paper presents an efficient rectifier hybridizing the synchronized electric charge extraction (SECE) and bias-flipping techniques. Taking advantage of the varying internal capacitance of a TENG, the proposed rectifier minimizes the electrostatic energy loss and improves the energy extraction efficiency. Thanks to the HV process, the rectifier can tolerate 65V at the maximum to extract more energy and sense the TENG state with only 35 nA quiescent current. The energy extraction performance is enhanced by 7.4 times compared to a passive FBR interface.

#### REFERENCES

- L. Zhou, D. Liu, J. Wang, and Z. L. Wang, "Triboelectric nanogenerators: fundamental physics and potential applications," *Friction*, vol. 8, no. 3, pp. 481–506, 2020.

- [2] W. Peng and S. Du, "The advances in conversion techniques in triboelectric energy harvesting: A review," *IEEE Transactions on Circuits* and Systems I: Regular Papers, vol. 70, pp. 3049–3062, 2023.

- [3] J. S. Y. Tan, J. H. Park, J. Li, Y. Dong, K. H. Chan, G. W. Ho, and J. Yoo, "A fully energy-autonomous temperature-to-time converter powered by a triboelectric energy harvester for biomedical applications," *IEEE Journal* of Solid-State Circuits, vol. 56, no. 10, pp. 2913–2923, 2021.

- [4] S. Zhang, M. Bick, X. Xiao, G. Chen, A. Nashalian, and J. Chen, "Leveraging triboelectric nanogenerators for bioengineering," *Matter*, vol. 4, no. 3, pp. 845–887, 2021.

- [5] Y. Song, J. Min, Y. Yu, H. Wang, Y. Yang, H. Zhang, and W. Gao, "Wireless battery-free wearable sweat sensor powered by human motion," *Sci Adv*, vol. 6, no. 40, p. eaay9842, 2020. [Online]. Available: https://www.ncbi.nlm.nih.gov/pubmed/32998888

- [6] I. Park, J. Maeng, M. Shim, J. Jeong, and C. Kim, "A high-voltage dual-input buck converter achieving 52.9

- [7] J. Maeng, I. Park, M. Shim, J. Jeong, and C. Kim, "A high-voltage dual-input buck converter with bidirectional inductor current for triboelectric energy-harvesting applications," *IEEE Journal of Solid-State Circuits*, vol. 56, no. 2, pp. 541–553, 2021.

- [8] I. Kara, M. Becermis, M. A. A. Kamar, M. Aktan, H. Dogan, and S. Mutlu, "A 70-to-2 v triboelectric energy harvesting system utilizing parallel-sshi rectifier and dc-dc converters," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 68, no. 1, pp. 210–223, 2021

- [9] S. H. Lee, Y. W. Jeong, S. J. Park, and S. U. Shin, "A rectifier-reusing bias-flip energy harvesting interface circuit with adaptively reconfigurable sc converter for wind-driven triboelectric nanogenerator," *IEEE Transactions on Industrial Electronics*, vol. 70, no. 8, pp. 8022–8031, 2023.

- [10] J. Lee, S. H. Lee, G. G. Kang, J. H. Kim, G. H. Cho, and H. S. Kim, "A triboelectric energy-harvesting interface with scalable multi-chipstacked bias-flip and daisy-chained synchronous signaling techniques," *IEEE Journal of Solid-State Circuits*, pp. 1–15, 2022.

- [11] M. Pathak, S. Xie, C. Huang, and R. Kumar, "High-voltage triboelectric energy harvesting using multi-shot energy extraction in 70-v bcd process," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 69, no. 5, pp. 2513–2517, 2022.