**TEMPERATURE SENSOR BASED ON 4H SILICON

CARBIDE WITH MEASUREMENT RANGE UP TO

400°C**

# **TEMPERATURE SENSOR BASED ON 4H SILICON CARBIDE WITH MEASUREMENT RANGE UP TO 400°C**

## **Proefschrift**

ter verkrijging van de graad van master

aan de Technische Universiteit Delft,

door

**Chengshang YUAN**

Faculteit Elektrotechniek, Wiskunde en Informatica

Technische Universiteit Delft, Delft, Nederland,

geboren te Nanyang, China.

Dit proefschrift is goedgekeurd door de

Supervisor: prof. dr. Guoqi Zhang      Technische Universiteit Delft

Daily supervisor: dr. ir. Brahim el Mansouri      Technische Universiteit Delft

## Samenstelling promotiecommissie:

Prof. dr. Paddy French      Technische Universiteit Delft

Prof. dr. Willem van Driel      Technische Universiteit Delft

**Keywords:** 4H Silicon Carbide, Bipolar Junction Transistor, Temperature Sensor, 400 °C

Copyright © 2022 by Chengshang Yuan.

An electronic version of this dissertation is available at

<http://repository.tudelft.nl/>.

*Efforts and courage are not enough

without purpose and direction.*

John Fitzgerald Kennedy

# ACKNOWLEDGEMENTS

I would like to extend my gratitude to Brahim: his patience, instructions and expertise guided me through this bumpy yet meaningful thesis journey. I would like to say thanks to my thesis supervisor Professor Zhang: his criticism keeps me moving forward during in the valleys of my research; his introducing me to relevant industry and scientists is highly appreciated. My gratitude also goes to Professor van Driel: thanks for the supportive words to calm me down during the stressful moments; thanks for the light-heart and frank discussion.

Thank Jiarui for his insightful, detailed feedback to my writing and his instructions in the measurement. Thanks to Henk for his check on the mask design, his suggestions on presentation. Thanks to Dong for helping the source meter scripts, to Bram for the helpful latex tips, and to the EKL staff Bruno, Paolo, Koos, Silvana, Vincent, Mario for their assistance in my clean room fabrication.

The heartfelt gratefulness goes to my friends as well: Dave, Gabriel, Edwin, Qiyi, Christina, Junjie, Ana, Flora, Sohrab, Tom, Mustafeez, Esad, Samantha, Samhitha and Eecke. The fun we had together refreshed me in the difficult days of this research.

Lastly and most importantly, the sincere gratitude goes to my parents. Thanks for their consistent financial and spiritual support during my master in Delft. Their unconditional love is the firmest source of endorsement to achieve my personal ambitions; their care and understanding lifted me up through the darkest hours of the pandemic.

Michaël Chengshang Yuan,

30th October, 2022.

# SUMMARY

Wide band gap semiconductor has attracted significant industrial interest over the past decade with its superior properties: such as high critical electrical field, high thermal conductivity and wide band gap. Meanwhile many industries operating in harsh environments have long had demands for sensing solutions that function at high temperature. Current commercially available silicon-based temperature sensing IC has measure range limited to 155°C . This research work aims to develop a temperature sensor based on 4H silicon carbide with pronounced higher measurement range but comparable linearity. Furthermore, this work introduces silicon carbide based bipolar junction transistor (BJT) technology in the Else Kooi Lab (EKL).

Ratio-metric measurement technique from CMOS technology is adapted to eliminate PN diode and BJT's non-linearity as a temperature sensor; and devices are implemented experimentally on epitaxial 4H-silicon carbide wafers in the EKL.

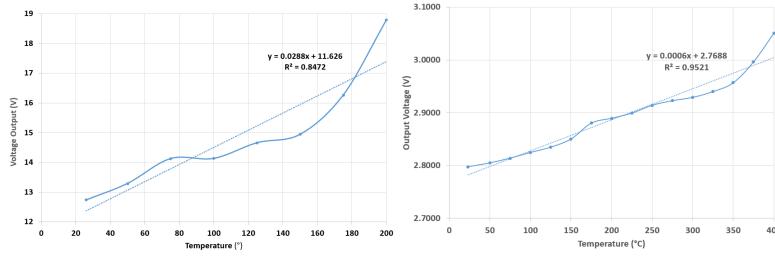

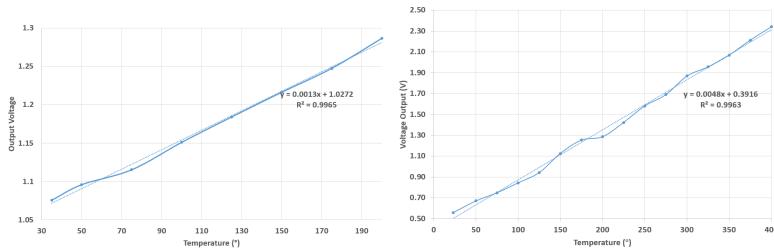

The characterization data shows that diode version sensor operates to 400 °C with a  $R^2$  value of 0.9963, the sensitivity under 1 mA constant current source is 4.8 mV/°C . The BJT version operates to 200 °C with a  $R^2$  of 0.9965. In the future the sensor's integration with pressure, gas, and other types of sensing solutions can provide a comprehensive sensing package. Such a package can be used to predict life time of critical components in harsh environment installations; and hence reduce the maintenance cost. Examples of application scenarios include oil&gas exploration, industrial furnaces, geothermal extraction, and so on.

# SAMENVATTING

WIDE band gap halfgeleider heeft het afgelopen decennium veel industriële belangstelling getrokken met zijn superieure eigenschappen: zoals een hoog kritisch elektrisch veld, hoge thermische geleidbaarheid en brede bandgap. Ondertussen hebben veel industrieën die in ruwe omgevingen opereren, al lang behoeft aan sensoroplossingen die bij hoge temperaturen werken. De huidig, commercieel verkrijgbare temperatuursensor IC, welk op silicium gebaseerd is, heeft een meetbereik dat beperkt is tot 155 °C . Dit onderzoekswerk heeft tot doel een temperatuursensor te ontwikkelen op basis van 4H siliciumcarbide met een uitgesproken hoger meetbereik maar vergelijkbare lineariteit. Bovendien introduceert dit werk de op siliciumcarbide gebaseerd bipolaire junctietransistor (BJT) technologie in Else Kooi Laboratorium.

De ratiometrische meettechniek van CMOS-technologie is aangepast om de niet-lineariteit van PN-diodes en BJT als temperatuursensor te elimineren; en apparaten worden experimenteel geïmplementeerd op epitaxiale 4H-siliciumcarbide substraten in het EKL-laboratorium.

De karakteriseringsggevens laten zien dat de diodeversie van het sensor tot 400 °C werkt met een  $R_2$ -waarde van 0,9963. Hier is de gevoelighed onder 1 mA constante stroombron, 4,8 mV/°C . De BJT-versie werkt tot 200 met een  $R_2$  van 0.9965. In de toekomst kan de integratie van de sensor met druk-, gas- en andere soorten detectieoplossingen een uitgebreid detectiepakket opleveren. Een dergelijk pakket kan worden gebruikt om de levensduur van kritieke componenten in installaties in ruwe omgevingen te voorschrijven; en dus de onderhoudskosten verlagen. Voorbeelden van toepassingsscenario's zijn onder meer olie- en gasexploratie, industriële ovens, geothermische winning, enzovoort.

# CONTENTS

|                                                                   |            |

|-------------------------------------------------------------------|------------|

| <b>Acknowledgements</b>                                           | <b>vii</b> |

| <b>Summary</b>                                                    | <b>ix</b>  |

| <b>Samenvatting</b>                                               | <b>xi</b>  |

| <b>List of Figures</b>                                            | <b>xv</b>  |

| <b>1 Introduction</b>                                             | <b>1</b>   |

| 1.1 Motivation and Problem Formulation . . . . .                  | 2          |

| 1.2 Thesis Outline . . . . .                                      | 3          |

| <b>2 Background Theory</b>                                        | <b>5</b>   |

| 2.1 Introduction to Silicon Carbide . . . . .                     | 6          |

| 2.1.1 Crystal Structure . . . . .                                 | 6          |

| 2.1.2 Material Properties . . . . .                               | 7          |

| 2.2 PN Diode as a Temperature Sensor . . . . .                    | 7          |

| 2.2.1 Qualitative Operation Mechanism . . . . .                   | 8          |

| 2.2.2 Ideal Diode Characteristics . . . . .                       | 8          |

| 2.2.3 Non-idealities of PN Junction . . . . .                     | 10         |

| 2.3 Bipolar Junction Transistor as a Temperature Sensor . . . . . | 10         |

| 2.3.1 BJT's Operating Mechanism . . . . .                         | 11         |

| 2.3.2 BJT's Non-linearity . . . . .                               | 14         |

| 2.3.3 BJT's Temperature Dependence . . . . .                      | 17         |

| 2.4 Ratiometric Temperature Measurement . . . . .                 | 19         |

| 2.4.1 Proportional to Absolute Temperature . . . . .              | 20         |

| 2.4.2 Circuit Level Design . . . . .                              | 21         |

| <b>3 Device Design and Simulation</b>                             | <b>23</b>  |

| 3.1 Simulation Setup . . . . .                                    | 24         |

| 3.2 Physic Models . . . . .                                       | 24         |

| 3.2.1 Band Gap Narrowing(BGN) . . . . .                           | 24         |

| 3.2.2 Incomplete Ionization . . . . .                             | 25         |

| 3.2.3 Recombination Models . . . . .                              | 26         |

| 3.2.4 Surface Effects . . . . .                                   | 29         |

| 3.3 Simulation Result . . . . .                                   | 30         |

| 3.3.1 Gummel Characteristics . . . . .                            | 30         |

---

|                                            |           |

|--------------------------------------------|-----------|

| <b>4 Device Fabrication</b>                | <b>39</b> |

| 4.1 Fabrication Concepts . . . . .         | 40        |

| 4.1.1 Chemical Vapor Deposition . . . . .  | 40        |

| 4.1.2 Lithography . . . . .                | 40        |

| 4.1.3 Reactive Ion Etching (RIE) . . . . . | 40        |

| 4.1.4 Schottky Barrier . . . . .           | 41        |

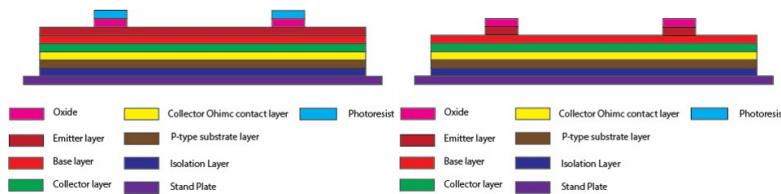

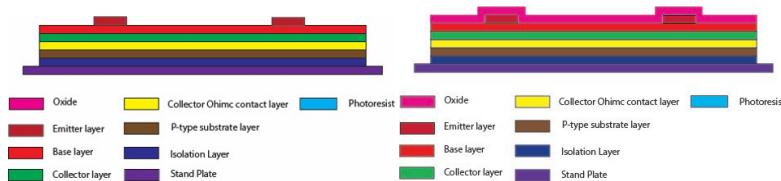

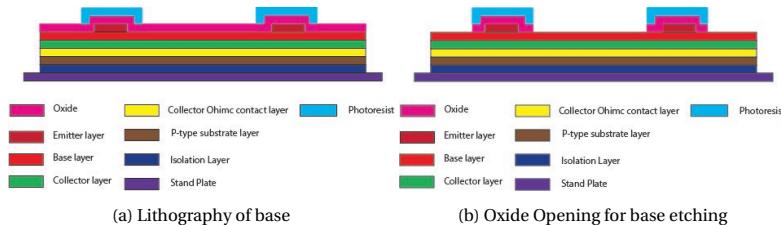

| 4.2 Critical Steps . . . . .               | 43        |

| 4.3 Fabrication flow . . . . .             | 44        |

| 4.4 Product Overview . . . . .             | 45        |

| <b>5 Device Characterization</b>           | <b>47</b> |

| 5.1 Measurement Setup . . . . .            | 48        |

| 5.2 Measurement Result . . . . .           | 49        |

| <b>6 Conclusion and Future Work</b>        | <b>53</b> |

| 6.1 Conclusion . . . . .                   | 54        |

| 6.2 Future Work . . . . .                  | 54        |

| <b>A Appendix A</b>                        | <b>63</b> |

| <b>B Appendix B</b>                        | <b>71</b> |

# LIST OF FIGURES

|      |                                                                                                                                                                                                 |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Bonded silicon carbon cluster, source[16] . . . . .                                                                                                                                             | 6  |

| 2.2  | Hexagonal packing positions of silicon carbon pair,source[16] . . . . .                                                                                                                         | 6  |

| 2.3  | SiC-C pair's stacking sequences along the c-axis in 3C-, 4H-, and 6H-SiC, source[16] . . . . .                                                                                                  | 7  |

| 2.4  | Difference between Fermi-Dirac function and Maxwell-Boltzmann approximation, source[17] . . . . .                                                                                               | 9  |

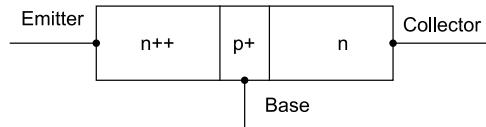

| 2.5  | Simple sketch of a npn BJT . . . . .                                                                                                                                                            | 11 |

| 2.6  | Ideal Doping of a npn BJT . . . . .                                                                                                                                                             | 11 |

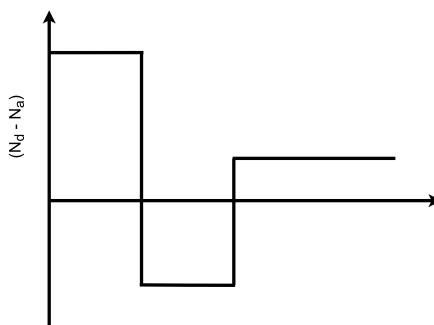

| 2.7  | The gradient of current components, source[17] . . . . .                                                                                                                                        | 12 |

| 2.8  | Theoretical collector current versus base collector voltage plot . . . . .                                                                                                                      | 13 |

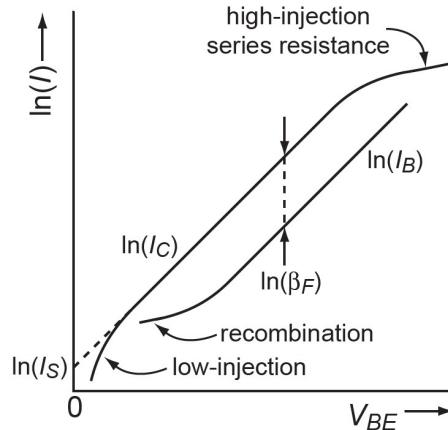

| 2.9  | High and low injection, source[18] . . . . .                                                                                                                                                    | 15 |

| 2.10 | Diode connection of a BJT . . . . .                                                                                                                                                             | 15 |

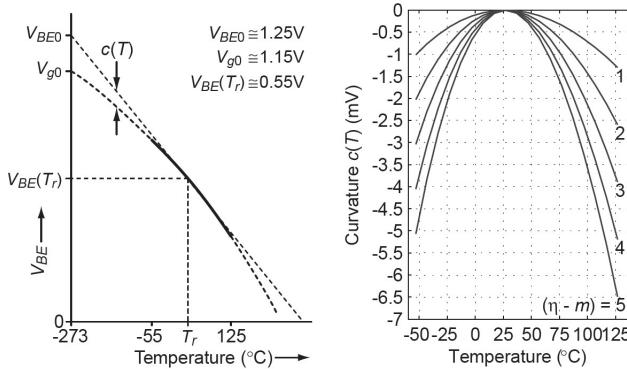

| 2.11 | On the left is the temperature dependency of base emitter voltage (the curvature is exaggerated), on the right is the curvature at different ( $\eta$ - m), $T_r = 300$ K, source[22] . . . . . | 19 |

| 2.12 | the PTAT configuration of two diodes . . . . .                                                                                                                                                  | 20 |

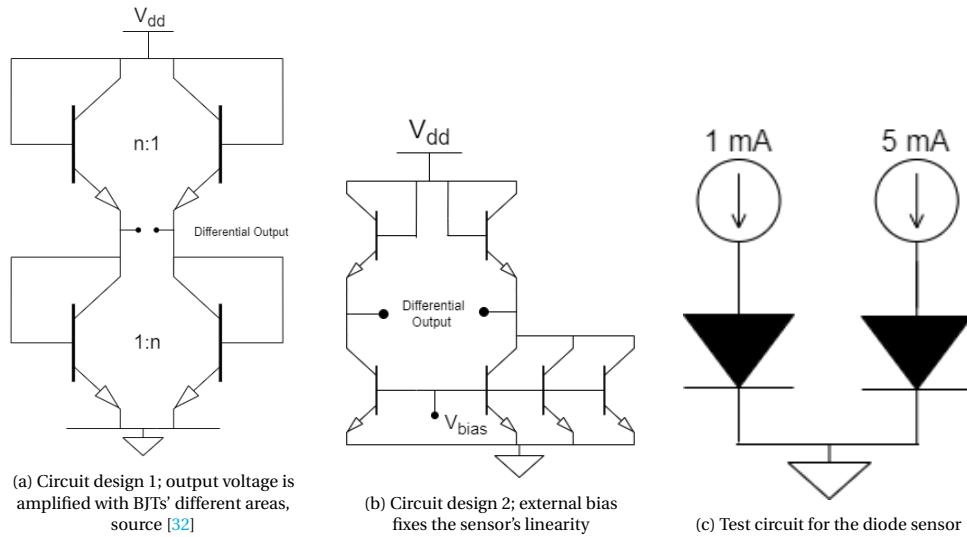

| 2.13 | Three schematics of the temperature sensor . . . . .                                                                                                                                            | 21 |

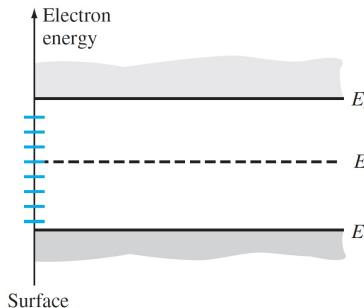

| 3.1  | Distribution of surface state energies in the band gap, source[17] . . . . .                                                                                                                    | 29 |

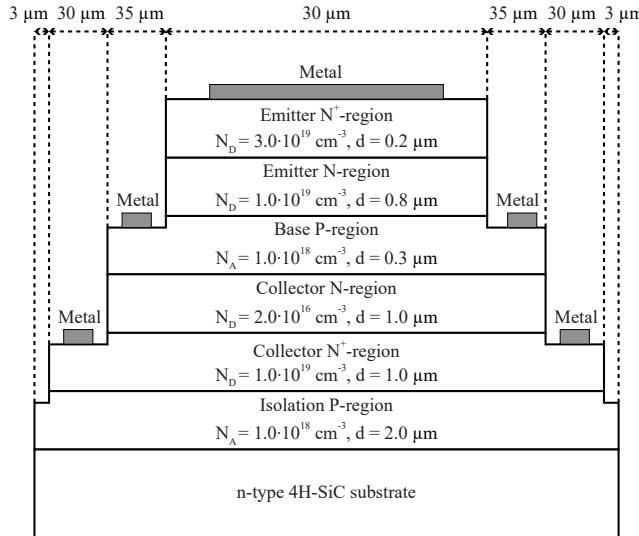

| 3.2  | A diagram of the device . . . . .                                                                                                                                                               | 31 |

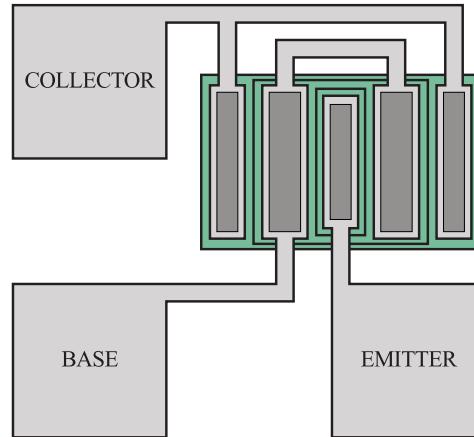

| 3.3  | Illustration of the Mask . . . . .                                                                                                                                                              | 32 |

| 3.4  | Gummel Characteristics of generation zero 300K . . . . .                                                                                                                                        | 32 |

| 3.5  | Base doping's impact on Gummel Characteristics . . . . .                                                                                                                                        | 33 |

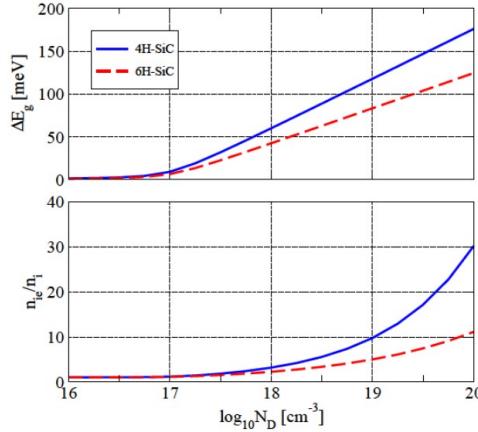

| 3.6  | band gap narrowing in $\alpha$ -SiC as a function of doping, the graph on the bottom shows its effect on the intrinsic carrier concentration, source[44] . . . . .                              | 33 |

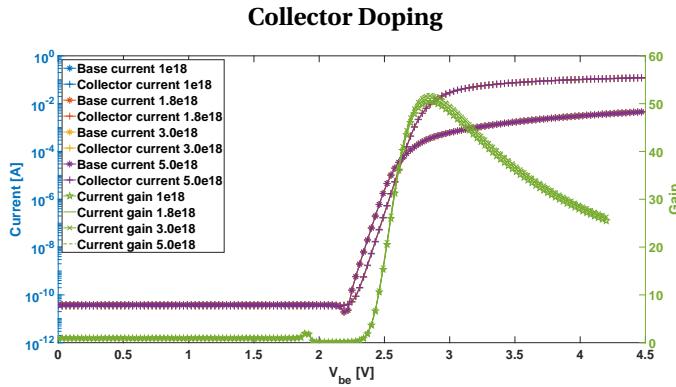

| 3.7  | Impact of collector doping: the base current decreases slightly . . . . .                                                                                                                       | 34 |

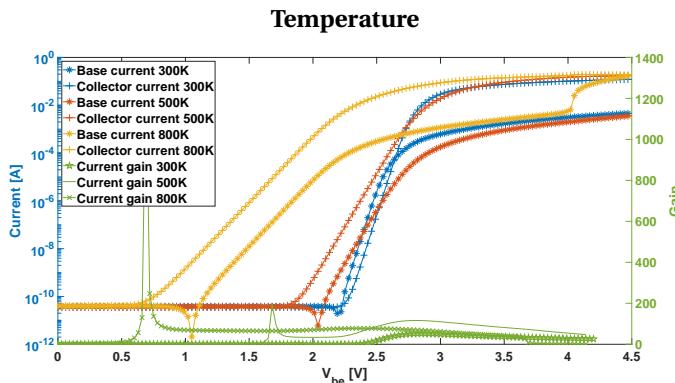

| 3.8  | Temperature's impact on the device performance . . . . .                                                                                                                                        | 35 |

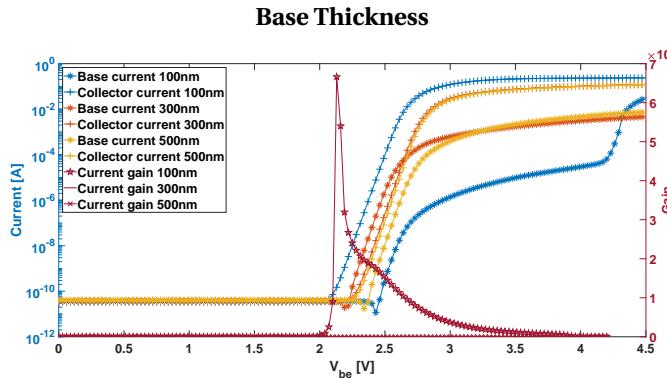

| 3.9  | Device performance at different base thicknesses . . . . .                                                                                                                                      | 36 |

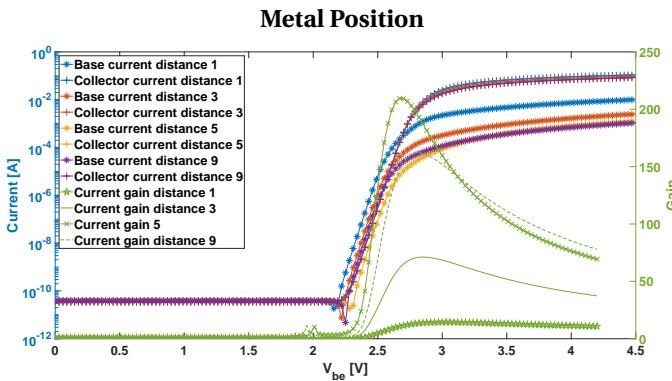

| 3.10 | Impact of metal position . . . . .                                                                                                                                                              | 36 |

| 3.11 | Parameter"distance from the edge" . . . . .                                                                                                                                                     | 37 |

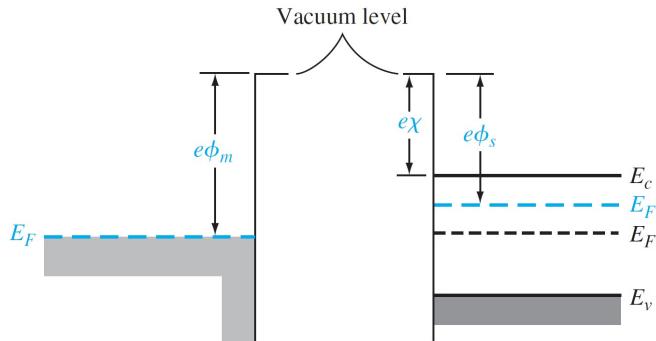

| 4.1  | Energy band diagram of n-type semiconductor and metal; the work function of semiconductor is smaller than that of metal . . . . .                                                               | 42 |

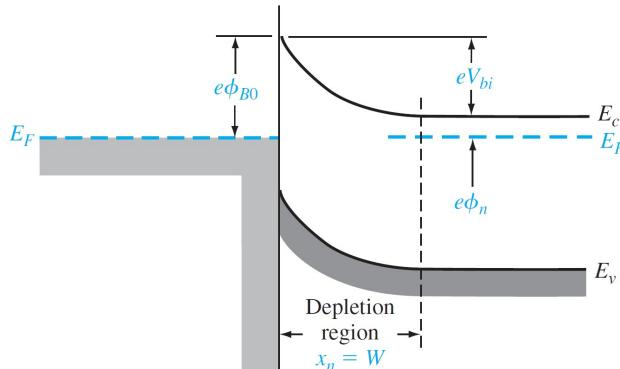

| 4.2  | Energy band diagram of the junction at thermal equilibrium,source[17] . . . . .                                                                                                                 | 42 |

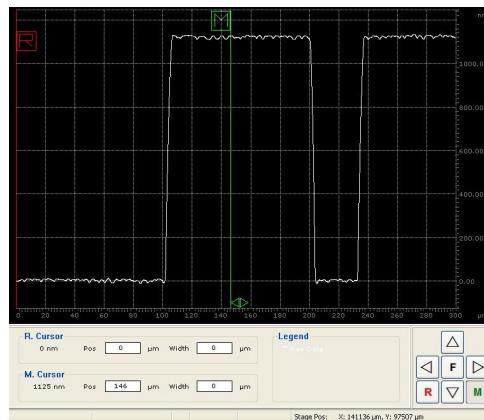

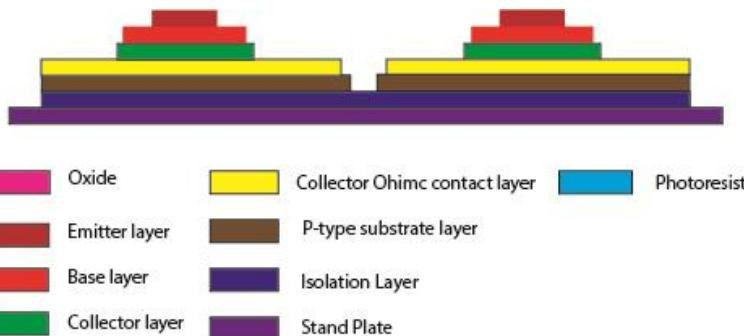

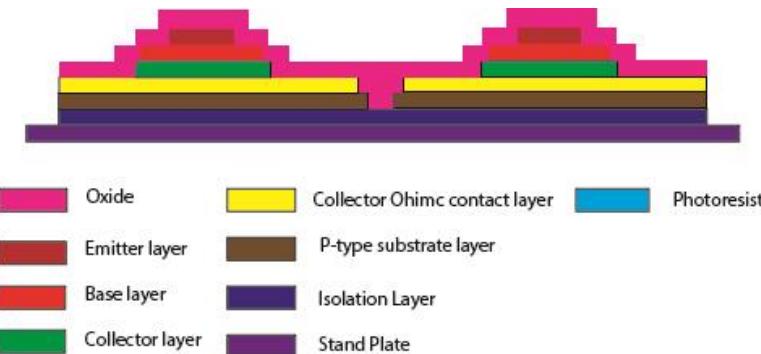

| 4.3  | Surface profile after emitter etching . . . . .                                                                                                                                                 | 43 |

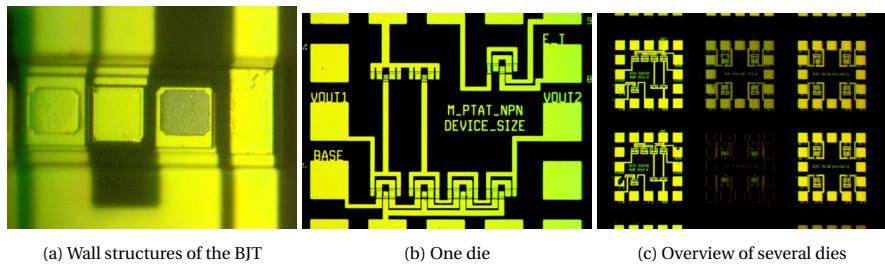

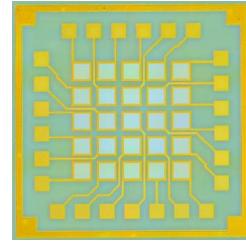

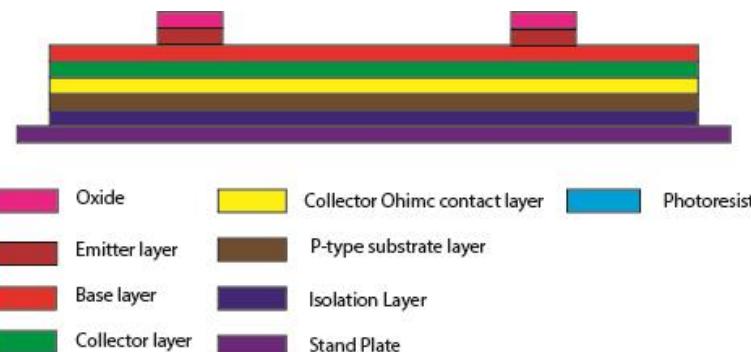

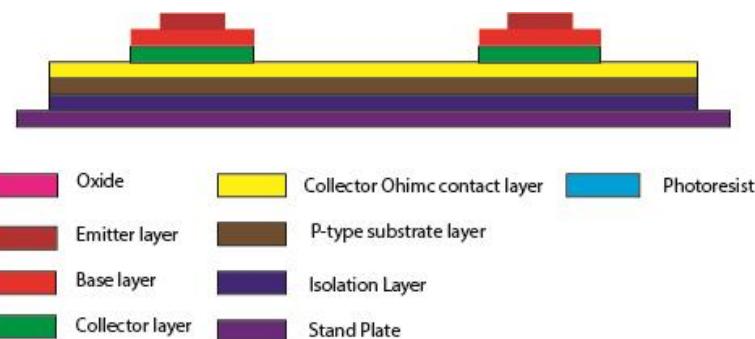

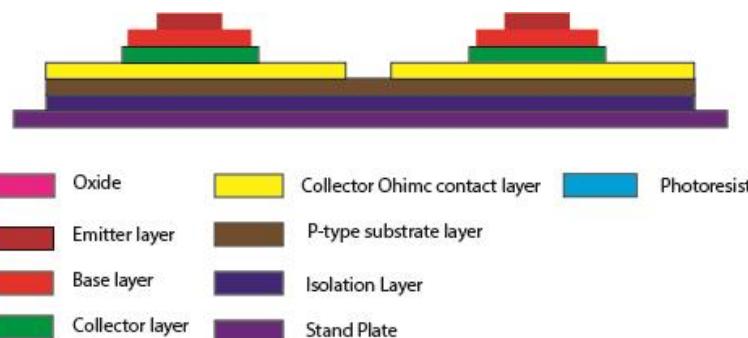

| 4.8  | Device outlook after collector ohmic cycle . . . . .                                                                                                                                            | 45 |

| 4.9  | Microscope images of the wafer . . . . .                                                                                                                                                        | 46 |

| 4.10 | Current product overview . . . . .                                                                                                                                                              | 46 |

|     |                                                              |    |

|-----|--------------------------------------------------------------|----|

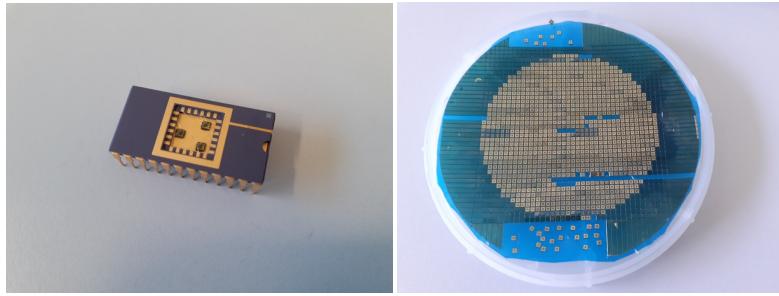

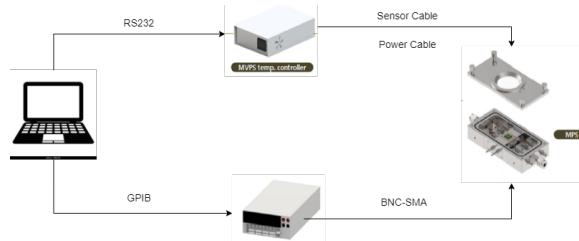

| 5.1 | Diagram for diode temperature sensor's measurement . . . . . | 48 |

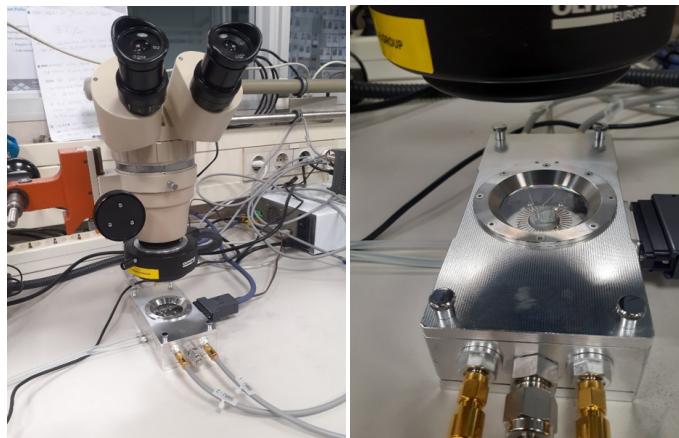

| 5.2 | Measurement set up . . . . .                                 | 48 |

| 5.3 | Equipment used in device characterization . . . . .          | 49 |

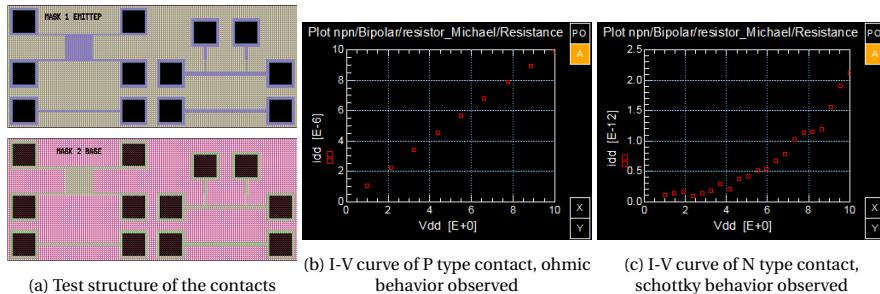

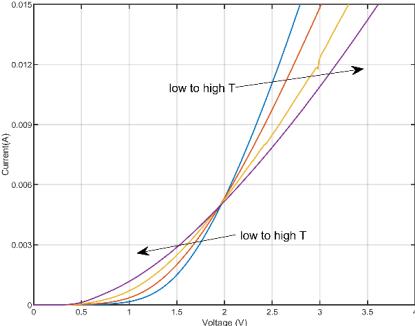

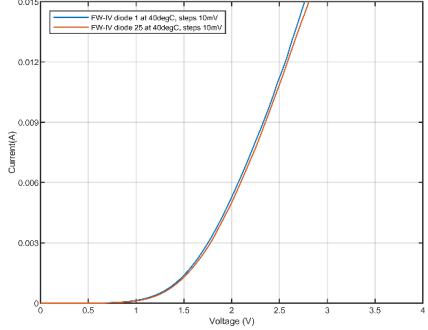

| 5.4 | Ohmic test of the contacts . . . . .                         | 49 |

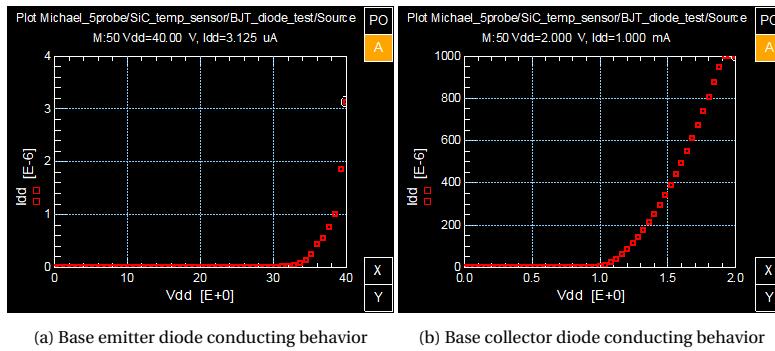

| 5.5 | Conduction of the two diodes inside the BJT . . . . .        | 50 |

| 5.6 | One arm devices' Performance . . . . .                       | 50 |

| 5.7 | Temperature sensors' performance . . . . .                   | 51 |

# 1

## INTRODUCTION

Wide band gap (WBG) semiconductors are semiconductor materials that have higher energy band gaps than conventional semiconductor materials. For example, silicon carbide(SiC) as a WBG material has an band gap energy of 3.25 eV; gallium nitride(GaN) has a band gap energy of 3.4 eV. On the other hand, silicon as a conventional semiconductor material has a band gap of 1.1 eV; germanium has a band gap of 0.7 eV [1]. Generally, the electronic properties of WBG materials fall in between those of semiconductors and insulators. WBG semiconductor allows devices to function at higher temperature, higher frequencies, and higher voltages than conventional semiconductor materials. They are the critical components in military radars, lasers, and short-wavelength LEDs. They are also one of the leading candidates for next-generation semiconductor devices of general use.

Among the large group of WBG semiconductor materials, SiC is a candidate that has attracted extensive industrial interest with its outstanding electrical and physical properties[2]–[4]. The low intrinsic concentration and high band gap energy enable SiC devices to function at much higher temperature than silicon ones. Moreover, the high thermal conductivity, high break-down electrical field, and high saturation electron velocity makes them suitable for operating under extreme conditions. Over the past decade, there has been intensive research efforts into its application in harsh environments electronics and sensors[5].

The reasoning for SiC's superior material properties lies in silicon-carbide bond's high strength[6]. There exist a huge number of different crystal structure built from the same silicon-carbon grouping; they are known as polytypes when organized into diverse stacking sequences. Although over 100 polytypes exist, R&D efforts have been focused on only three polytypes: 6H, 4H and 3C. Critical properties of those SiC polytypes and other semiconductor materials are presented in table 1.1. Growth technology of 6H-SiC was advancing faster in the beginning because it was used as the substrate in producing GaN blue LEDs. However, 4H-SiC demonstrated superior material properties and are preferred for other electronics devices; for example, its on-axis mobility is ten times as high as that of the 6H-SiC. Moreover, the high band gap of 3.25 eV significantly re-

duces the number of electron-hole pairs resulting from the thermal activation through the band gap; and that enable the devices made from it operational at higher than 400°C [7]. 3C-SiC is more suitable to fabricate MEMS sensor because it can grow on the silicon wafer; this property considerably reduces the manufacturing costs[8].

Table 1.1: Material Properties,source [9]

| Property                                    | Si   | Diamond   | 3C-SiC    | 4H-SiC    | 6H-SiC    |

|---------------------------------------------|------|-----------|-----------|-----------|-----------|

| Energy Bandgap [eV]                         | 1.12 | 5.5       | 2.3       | 3.0       | 3.2       |

| Critical Field [MV/cm]                      | 0.6  | 5         | 1.8       | 2.5       | 2.5       |

| Thermal Conductivity [W/cmK]                | 1.5  | 20        | 3-5       | 3-5       | 3-5       |

| Saturated Electron Velocity [ $10^{-7}$ /s] | 1.0  | 2.8       | 2.5       | 2.0       | 2.0       |

| Electron Mobility [cm <sup>2</sup> /Vs]     | 1200 | Very high | 750       | 400       | 800       |

| Hole Mobility [cm <sup>2</sup> /Vs]         | 420  | Very High | 40        | 90        | 115       |

| Young's Modulus [GPa]                       | 190  | 1035      | 450       | 450       | 450       |

| Chemical Stability                          | Fair | Fair      | Excellent | Excellent | Excellent |

| Yield Strength [GPa]                        | 7    | 53        | 21        | 21        | 21        |

## 1.1. MOTIVATION AND PROBLEM FORMULATION

Conventional silicon-based IC gives a limited temperature range: when the temperature becomes high, the crystal lattice expands and the atomic bonds become weakened. The energy required for an electron to jump into the conduction band hence decreases. If the density of the carrier increases tremendously, the current increases sharply. Then semiconductor material reaches the characteristics similar to conductor. Therefore, the silicon-based IC typically has a limited temperature range up to 155°C [10]. In the research work of Zhang Nuo, the diode technology based the 4H-SiC has the measurement range up to 600°C [7]. However, this technology is still in the research phase. Current commercially mature temperature sensing technologies can be mainly divided into four categories: Resistance temperature detector(RTD), thermal-electrical thermometer(Thermal Couple), silicon temperature IC, and the thermistor. Table 1.2 gives an overview of the those technologies regard to their price, response time, measurement range, measurement precision, linearity and size. One can observe that existing sensing

Table 1.2: Overview of the commercially available temperature sensing technologies, source [11]–[14]

| Type           | Price | Response    | Range      | Precision | Linearity | Size                    |

|----------------|-------|-------------|------------|-----------|-----------|-------------------------|

| RTD            | +++   | 1–7Sec      | -200–500°  | 0.1–1°    | ++        | 3.175–6.350 mm          |

| Thermal couple | ++    | <1Sec       | -180–2320° | 0.5–5°    | ++        | 2–3m                    |

| Silicon IC     | ++++  | <1Sec       | 25–155°    | <0.1°     | +++       | several cm <sup>2</sup> |

| Thermistor     | +     | 0.05–2.5Sec | -100–300°  | 0.1–1.5°  | +         | 2–3m                    |

technologies all have their shortcomings. RTD sensor's response time is long while the thermal couple doesn't give enough precision. Silicon-based IC is precise enough but the measurement range is limited. Thermistor has the disadvantage of negative temperature coefficient. If a sensor has the same precision level as the silicon-based IC, but

meanwhile with measurement range higher than the typical device, it will be a big improvement on the current sensing technology. Temperature sensing based on SiC has the potential to achieve such a goal; the thesis project designs and tests that idea.

Specifically, the three objectives of the thesis are:

- Develop a 4H-SiC Bipolar Junction Transistor (BJT) device level model based on epitaxial structure.

- Introduce a SiC epitaxial based BJT technology to Else Kooi laboratory (EKL).

- Develop a temperature sensor based on the BJT, it should have a significantly higher measurement range than conventional silicon technology and a comparable linearity.

## 1.2. THESIS OUTLINE

Content of the thesis are divided into six chapters; in addition to introduction, the rest five chapters are organized as follows:

- Chapter two gives the background theory of SiC materials properties, operating mechanism of temperature sensor based on pn diode ; operating mechanism of temperature sensor based on bipolar junction transistor, and devices' circuit design.

- Chapter three documents establishment of the 4H-SiC BJT model. Different parameters' impact on the device are examined, those parameters include devices' vertical, horizontal geometries, contacts positions, and doping concentrations.

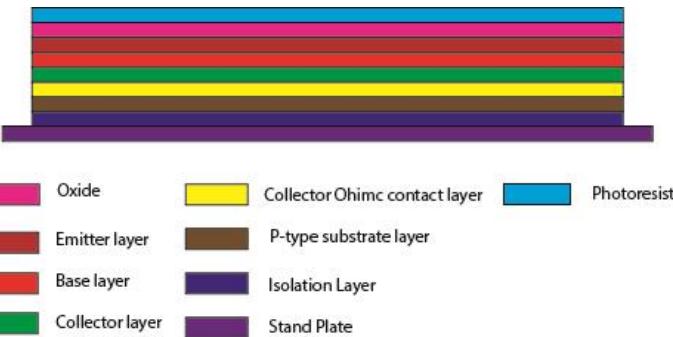

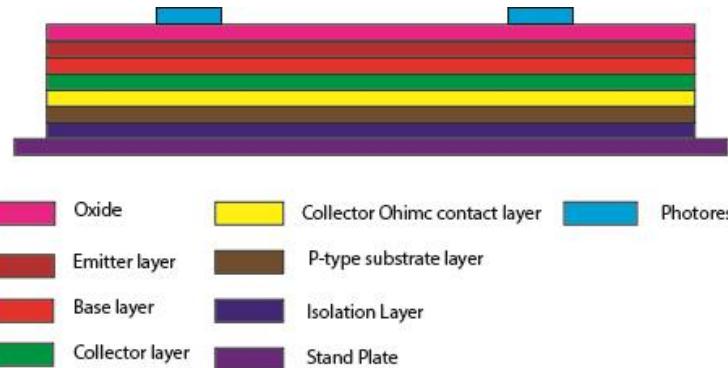

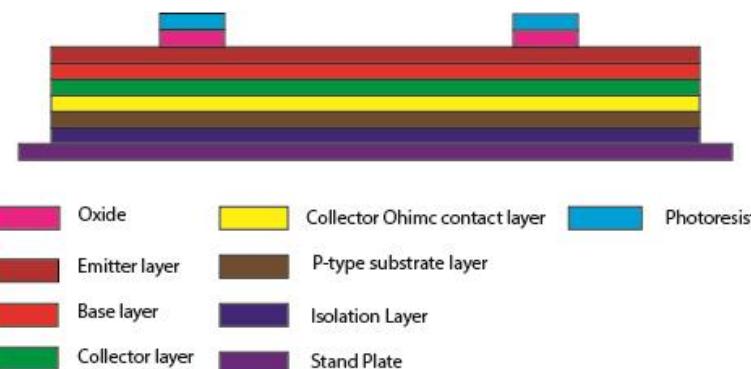

- Clean room fabrication of the devices is presented in Chapter four. Relevant concepts and tools used for fabrication are first introduced for the reader's reference. Critical fabrication steps that impact the device's performance are then discussed. The reader can find the complete flowchart in appendix B.

- Chapter five reports the device characterization. Temperature sensors based on diodes and bipolar junction transistors are both tested. And Bipolar junction transistor's I-V characters are presented. This chapter also analyzes the non-linearity of the temperature performance.

- Chapter six concludes this master thesis work and gives future research directions.

# 2

## BACKGROUND THEORY

*This chapter provides the background theory of temperature sensor based on PN diode and BJT. First SiC's crystal structure and material properties are briefly covered in section 2.1; after that section 2.2 discusses the PN diode's operating mechanism, and its non-idealities as a temperature sensor. Section 2.3 investigates bipolar junction transistor's operating mechanism and its temperature dependence. This section provides the theory support for performance analysis in chapter five.*

## 2.1. INTRODUCTION TO SILICON CARBIDE

### 2.1.1. CRYSTAL STRUCTURE

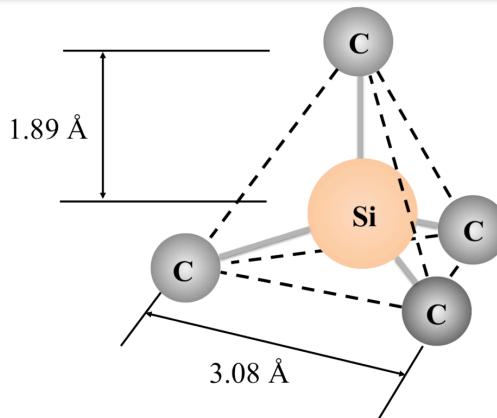

SiC is a compound semiconductor, both silicon and carbon are group IV materials. In its crystal lattice each silicon atom is tetrahedrally connected to four carbon atoms. The distance between the silicon atom and carbon one is approximately 1.89 Å; and the distance between Si-Si and C-C atoms is 3.08 Å [15]. Figure 2.1 shows the tetrahedrally bonded silicon carbon cluster.

Figure 2.1: Bonded silicon carbon cluster, source[16]

There exist different SiC that have the same chemical composition but have different crystal structures. These are defined as polytypes. Over 100 different polytypes of SiC have been discovered, and the ones that have attracted most industrial research efforts are 3C-SiC, 4H-SiC and 6H-SiC.

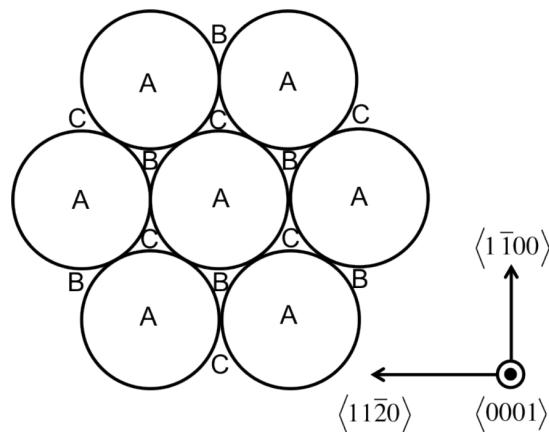

Figure 2.2: Hexagonal packing positions of silicon carbon pair,source[16]

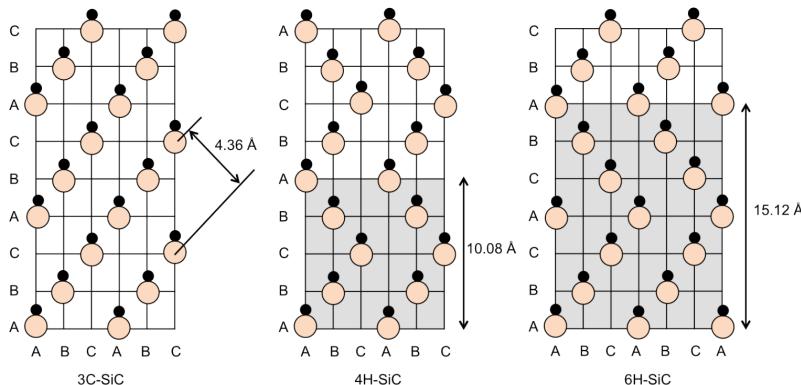

The difference between those SiC polytypes falls in their silicon-carbon layer stacking sequence. Silicon-carbon pairs form a hexagonal pattern when they are stacked in a plane. Figure 2.2 depicts such a pattern; note that one silicon-carbon pair is represented as a sphere. The position of the first layer is indicated as A-site position; the next layer on top of the first layer can either land on the B-site position or one the C-site position. 4H-SiC's stacking sequence is ABCB; throughout the crystal lattice those four layers are repeated. Likewise, 6H-SiC's stacking sequence is ABCACB. Crystal Structures of 4H-SiC and 6H-SiC are both hexagonal. 3C-SiC is the only polytype that has a cubic crystal structure; its stacking sequence is ABC. Figure 2.3 shows the schematic structures of those three SiC polytypes.

Figure 2.3: SiC-C pair's stacking sequences along the c-axis in 3C-, 4H-, and 6H-SiC, source[16]

### 2.1.2. MATERIAL PROPERTIES

SiC's superior electrical and physical properties make it suitable for harsh environment sensing applications. Low intrinsic carrier concentrations and wide band gap energy allows devices to operate at much higher temperature. In addition, high thermal conductivity, high saturation electron velocity, and high breakdown field permits SiC devices to function at harsh environments. It is noteworthy that SiC's mobility and critical field are anisotropic; they are dependent on the current flow and applied electric field. Table 1.1 is the overview of the common three polytypes' material properties; silicon and diamond's properties are added as a comparison. 4H-SiC is used in this research work as it has the highest band gap for temperature sensor.

## 2.2. PN DIODE AS A TEMPERATURE SENSOR

This section investigates PN diode's performance as a temperature sensor. Subsection 2.2.1 qualitatively discusses PN diode's operating mechanism. Subsection 2.2.2 develops PN diode ideal current voltage characteristics starting from electron concentration at a certain applied voltage. Subsection 2.2.3 gives a more accurate model of the I-V characteristics and clarifies its non-linearity as a temperature sensor.

### 2.2.1. QUALITATIVE OPERATION MECHANISM

When a piece of n-type and a piece of p-type semiconductor material are put together, electrons from the n-type material will diffuse into the p-type one and holes from the p-type material will diffuse into the n-type one, leaving positively charged acceptors in the n region and negatively charged donors in the p region. Charged acceptors and donors form an electrical field; such a field yields the drift current. In thermal equilibrium the drift current and diffusion current are of the same magnitude but are in opposite directions[17], hence the net current flow is zero.

Upon application of an external electrical field, such a diffusion-drift balance is disrupted. A forward bias favours the diffusion current, generating a net current from the p side to the n side and reducing the base-emitter depletion region length.

### 2.2.2. IDEAL DIODE CHARACTERISTICS

Subsection 2.2.1 gives a qualitative demonstration of PN diodes' operation. This subsection develops the quantitative relationship between the current and applied external voltage. The electron concentration on the p-side depletion region is given by[17]:

$$n_{p-side} = n_{p0} \cdot \exp\left(\frac{eV}{kT}\right) \quad (2.1)$$

Similarly, the hole concentration on the edge of the n-side depletion region is

$$p_{n-side} = p_{n0} \cdot \exp\left(\frac{eV}{kT}\right) \quad (2.2)$$

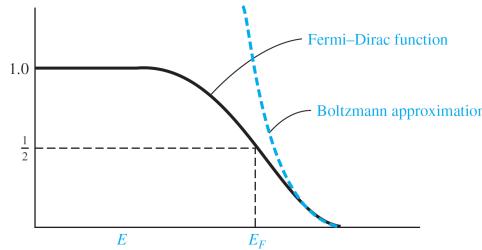

Equation 2.1 and equation 2.2 result from the Maxwell-Boltzmann approximation of the Fermi-Dirac probability function. The Fermi-Dirac probability function gives the probability of a quantum state at Energy level E occupied by an electron. It results from maxing the independent ways of arranging  $N$  electrons in a system with  $n$  energy levels. The probability function itself is

$$f_F(E) = \frac{1}{1 + \exp\left(\frac{E-E_F}{kT}\right)} \quad (2.3)$$

Assuming the difference between the quantum state energy E and Fermi energy is significantly higher than  $kT$  the 1 in the denominator of equation 2.3 could be eliminated, and the probability function reduces to its Maxwell-Boltzmann approximation:

$$f_F(E) = \frac{-(E_F - E)}{kT} \quad (2.4)$$

Figure 2.4 illustrates the range over which the approximation has reasonable accuracy.

Figure 2.4: Difference between Fermi-Dirac function and Maxwell-Boltzmann approximation, source[17]

When an external electrical field  $V$  is applied to the diode, the Fermi energy position will change with  $V$ ; therefore, we have the exponential dependency of minority carrier concentration on the applied voltage in equation 2.1 and equation 2.2. Away from the depletion region in the p-type material, the minority carrier concentration remains the thermal equilibrium values; hence there is a gradient at the depletion region and the area away from depletion. The gradient gives rise to diffusion current; the same mechanism happens in the n region. Total diffusion current can therefore be described by

$$I_D = \frac{qAD_n(n_{p-side} - n_{p0})}{L_n} + \frac{qAD_p(p_{n-side} - p_{n0})}{L_p} \quad (2.5)$$

$A$  is the junction cross-section area,  $D_n$  and  $D_p$  are the diffusion coefficients of electrons and holes;  $L_n$  and  $L_p$  are their diffusion lengths. When equation 2.1 and equation 2.2 are substituted into equation 2.5, we have the classical diode characteristics:

$$I_D = I_S \left( \exp\left(\frac{qV}{kT}\right) - 1 \right) \quad (2.6)$$

In which saturation current  $I_S$  is

$$I_S = \frac{qAD_n n_{p0}}{L_n} + \frac{qAD_p p_{n0}}{L_p} \quad (2.7)$$

Assuming complete ionization, the electron and hole equilibrium concentration can be represented by intrinsic carrier concentration  $n_i$ , acceptor concentration  $N_a$ , and donor concentration  $N_d$  respectively.

$$n_{p0} = \frac{n_i^2}{N_a} \quad p_{n0} = \frac{n_i^2}{N_d} \quad (2.8)$$

Substituting 2.8 into 2.7, the saturation current is simplified by

$$I_S = qAn_i^2 \left( \frac{D_n}{L_n N_a} + \frac{D_p}{L_p N_d} \right) \quad (2.9)$$

When the forward voltage  $V$  is significantly larger than the thermal voltage  $\frac{kT}{q}$ , the -1 in equation 2.6 can be ignored. The voltage drop across the diode  $V$  given an applied current  $I_D$  is then

$$V_{forward} = \frac{kT}{q} \ln\left(\frac{I_D}{I_S}\right) \quad (2.10)$$

Theoretically diode's forward voltage is proportional to absolute temperature.

### 2.2.3. NON-IDEALITIES OF PN JUNCTION

In subsection 2.2.2, it is assumed that diffusion current is the only component of the conduction current. However, in the depletion region there is another recombination current component. Such an component is described by:

$$I_{rec} = I_{r0} \cdot \exp\left(\frac{qV}{2kT}\right) \quad (2.11)$$

$I_{rec}$  is the recombination current. The term  $I_{r0}$  is related to the intrinsic carrier concentration, minority carrier lifetime  $\tau_0$ , depletion region length  $W$ , and cross-section area  $A$

$$I_{r0} = \frac{eWn_iA}{2\tau_0} \quad (2.12)$$

The derivation of recombination current involves with Shockley-Read-Hall recombination and an assumption that the recombination rate is uniform across the depletion region. The total conduction current is the sum of equation 2.11 and equation 2.6. Since there is a 2 in the exponential term in equation 2.12, the total conduction current is given by:

$$I_D = I_S \left( \exp\left(\frac{qV_{forward}}{nkT}\right) - 1 \right) \quad (2.13)$$

$n$  is the non-ideal factor in the range of 1 to 2. Under low forward bias,  $n$  approaches 2; under high bias, the diffusion dominates the recombination and  $n$  reaches 1. Equation 2.13 is a more accurate model compared to equation 2.48; in other words, the exponential behavior between current and voltage is distorted due to the recombination. If equation 2.13 is rewritten with voltage on the left:

$$V_{forward} = \frac{nKT}{q} \ln\left(\frac{I_D + I_S}{I_S}\right) \quad (2.14)$$

The voltage is proportional to absolute temperature; but there is a non-ideal factor  $n$ . In bipolar junction transistor (BJT), such an recombination current is compensated by base current. In section 2.3, reader will see that  $I_S$  is also related to temperature. The diode voltage in regard to temperature is not completely linear.

## 2.3. BIPOLAR JUNCTION TRANSISTOR AS A TEMPERATURE SENSOR

Section 2.2 demonstrates the qualitative model of PN diode, the quantitative relationship between current and voltage, as well as its non-idealities from the ideal current voltage characteristics. At the end of that section, it is mentioned that BJT's base current compensates for the recombination current. Therefore, bipolar transistor's temperature characteristics is closer to the ideal exponential relation in equation 2.10. This section conducts a closer review on the device, and its performance as a temperature sensor. In subsection 2.3.1 the operating mechanism is presented, then non-linearity that impacts sensing performance is discussed in subsection 2.3.2; in the end voltage and currents' characteristics regard to temperature are investigated in subsection 2.3.3.

### 2.3.1. BJT's OPERATING MECHANISM

A bipolar junction transistor consists of three regions: emitter, base, and collector. Depending on the whether the device is NPN or PNP, these three regions are doped with different dopants. Doping concentration in the emitter is highest among these three,

Figure 2.5: Simple sketch of an NPN BJT

the base lower and collector the lowest. Typically base region has a smaller width compared with the other two. Figure 2.5 gives a simple sketch of a NPN transistor, the reason for relative doping concentrations and narrow base width will become clear as the theory develops. BJTs are normally biased in the *forward active* mode when working as a current

Figure 2.6: Ideal Doping of an NPN BJT

amplifier: the base-emitter junction is forward biased while the base-collector junction is in reverse. During operation the forward voltage in the base-emitter pushes majority carrier electrons in the emitter into the base region, creating an excessive concentration of minority carrier; meanwhile, on the edge of the reversely-biased base-collector junction, the minority carrier electron concentration should be zero.

Figure 2.7: The gradient of current components, source[17]

As shown in Figure 2.7, the huge gradient of electrons makes them diffuse across the base region; then the electrical field in the space charge region of base-collector junction sweeps them into the collector. Since ideally as many electrons as possible should arrive at the emitter, the base width should be smaller than the diffusion length of the minority carrier; otherwise, the recombination with holes will dominate in the base region, resulting in an increased base current and decreased collector current.

Under the assumption that the minority carrier decreases linearly in the base region, the collector diffusion current is written as

$$i_C = eD_n A_{BE} \frac{dn(x)}{dx} = eD_n A_{BE} \left[ \frac{n_B(0) - 0}{0 - x_B} \right] = \frac{-eD_n A_{BE} \cdot n_{B0} \cdot \exp(-\frac{v_{BE}}{V_t})}{x_B} \quad (2.15)$$

$D_n$  is the electron diffusion coefficient,  $A_{BE}$  is the cross-section area,  $n_{B0}$  is the thermal equilibrium concentration of electrons at the base edge and  $V_t$  is the thermal voltage. As far as multitude is concerned, equation 2.15 can be simplified as

$$i_C = I_S \cdot \exp(-\frac{v_{BE}}{V_t}) \quad (2.16)$$

Equation 2.16 illustrates the basic operation mode of a BJT transistor: a voltage-controlled current source in which  $i_C$  is controlled by  $v_{BE}$ .

Since the base-emitter junction is forward biased, the majority holes in the base region will be injected into the emitter region, this constitutes part of the emitter current. Similar to collector current, such a component is exponentially related to  $v_{BE}$ :

$$i_{E1} = I_{S1} \cdot \exp(-\frac{v_{BE}}{V_t}) \quad (2.17)$$

The second component,  $i_{E2}$  results from the electrons injected from emitter to base; hence it is  $i_C$  in essence. The Emitter current is the sum of these two components:

$$i_E = i_{E1} + i_{E2} = I_{SE} \cdot \exp(-\frac{v_{BE}}{V_t}) \quad (2.18)$$

As shown in equation 2.16 and equation 2.18, both  $i_C$  and  $i_E$  are functions of  $v_{BE}$ , their ratio is hence a constant.

$$\alpha = \frac{i_C}{i_E} \quad (2.19)$$

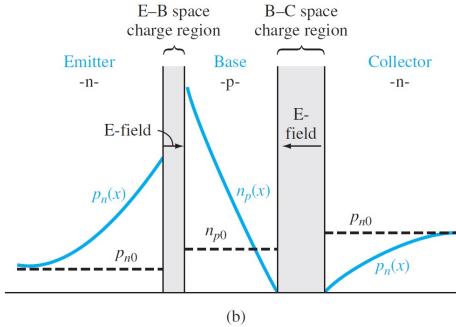

The constant is defined as the *common base amplification factor*. Since  $i_{E1}$  constitutes the base current, a higher  $i_{E1}$  also means a higher base current, it is optimal to keep  $\alpha$  as close to one as possible. Ideally, the collector current is determined only by  $v_{BE}$  and independent of  $v_{CE}$ ; the BJT works as a constant current source, as shown in Figure 2.8

Figure 2.8: Theoretical collector current versus base collector voltage plot

In addition to  $i_{E1}$ , there is another component of base current. In the above discussion, we assumed the linear distribution of minority carrier concentration in the base, implying no recombination. However, the presence of majority carrier holes and minority carrier electrons makes recombination inevitable. Taking that into consideration, the consumed majority holes in recombination should be supplied by an influx of positive charges  $i_{Bb}$ ; such an influx contributes to base current. To ensure the recombination current is as small as possible, the base width is normally designed narrow, smaller than the diffusion length of the minority carrier; this explains the relatively narrow width of base in figure 2.5.

The recombination rate of holes in the base depends on the minority carrier concentration and therefore base-emitter voltage  $v_{BE}$ . The total base current will be the sum of  $i_{E1}$  and  $i_{Bb}$ .

$$i_B = i_{Ba} + i_{Bb} = i_{E1} + i_{Bb} \quad (2.20)$$

As both components are exponentially related to  $v_{BE}$ , the base current is also proportional to  $\exp(\frac{v_{BE}}{V_t})$ . Now the ratio of  $i_C$  and  $i_B$  will also be a constant:

$$\beta = \frac{i_C}{i_B} \quad (2.21)$$

$\beta$  is defined as the *common emitter amplification factor*, it measures the amplification ability of a BJT and is usually in the order of tens to hundred in a SiC BJT device.

### 2.3.2. BJT's NON-LINEARITY

#### DEVIATIONS IN CURRENT-VOLTAGE RELATIONSHIP

2

When the base-collector junction is reversely biased, carrier-generation occurs in the depletion region; this forms the first contributor of deviations in the  $I_C - V_{BE}$  characteristics (The  $I_C - V_{BE}$  plot is named the Gummel Plot). Another factor is the diffusion of minority carriers into the collector. When the base-collector voltage is zero, these two factors could be ignored.

But under such a condition, the minority carrier concentration at the base side of base-emitter junction is no longer zero, but equal to equilibrium carrier concentration. In the case of a PNP transistor, we take the symbol  $p_{B0}$ ; The hole concentration at the emitter side of the base region is represented as  $p_{n,emi}$ . Although equation 2.15 applies to NPN transistors, similar collector characteristics hold for PNP devices:

$$i_C = eD_p A_{BE} \left[ \frac{p_{n,emi} - p_{B0}}{0 - x_B} \right] = \frac{-eD_p A_{BE}}{x_B} \cdot p_{B0} \cdot \left( \exp\left(\frac{V_{BE}}{V_t}\right) - 1 \right) \quad (2.22)$$

To make it straightforward

$$I_C = I_S \left( \exp\left(\frac{qV_{BE}}{kT}\right) - 1 \right) \quad (2.23)$$

Equation 2.23 renders  $\Delta V_{BE}$  in the optimal PTAT performance in equation 2.48 as

$$\Delta V_{BE} = \frac{kT}{q} \cdot \ln\left(\frac{pI_{C1} + I_S}{I_{C1} + I_S}\right) \quad (2.24)$$

Only if  $I_{C1}$  and  $pI_{C1}$  are significantly higher than  $I_s$  is the PTAT voltage reasonably accurate. Such a requirement is particularly important at higher operating temperature as the saturation current increases significantly with temperature. (The detailed reason will be clear in the later sections)

When building the device  $I_C$  cannot be set at a random high value. As the base-emitter voltage increases, the low-level injection assumption no longer holds. In other words, the minority carrier concentration in the base due to  $V_{BE}$  reaches the same multitude as the majority carrier concentration. Figure 2.9 illustrates the effect of high-injection. Meanwhile, at the lower bias, the recombination current dominate.

Figure 2.9: High and low injection, source[18]

To conclude, in the range where  $I_C$  is way larger than  $I_S$  but not so big as to get into the high-injection region, the current can be accurately used in PTAT application.

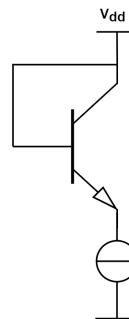

#### NON-LDEALITIES IN DIODE CONNECTION

In the CMOS technology driving the advances of integrated circuits industries over the past decades, bipolar junction transistors are usually the parasitic devices. As a result, the collectors of BJT are on the substrate and are not accessible. Such a configuration is called a diode connection, Figure 2.10 shows the diode connection of a NPN device.

Figure 2.10: Diode connection of a BJT

By connecting base and collector, the base-collector voltage becomes zero and the resulting collector current is smaller than the applied emitter current:

$$I_C = I_E - I_B = \alpha_F \cdot I_E = \frac{\beta_F}{1 + \beta_F} \cdot I_E \quad (2.25)$$

In this equation,  $\alpha_F$  is the common base gain factor, and  $\beta_F$  is the ratio between  $I_C$  and

$I_B$ .  $\alpha_F$  denotes how much emitter current arrives at the collector region, ideally it should be unitary.

To make sure the generated voltage is proportional to temperature, as in equation 2.48, we need to make sure that  $\alpha_F$  is current independent. In other words, the applied emitter currents ratio should yield exactly the collector currents.

$\alpha_F$  is determined by the base currents. It can be divided into three factors and these three factors concern the corresponding base current mechanisms.

$$\alpha_F = \gamma \cdot \alpha_T \cdot \delta \quad (2.26)$$

$\gamma$  is the emitter injection efficiency. It describes the fact that there is a small diffusion electron current into the emitter from the base in a PNP transistor. The associated base current in this case is:

$$I_{B1} = \frac{qA n_{iE}^2 \overline{D_n}}{L_n N_a} \cdot \exp\left(\frac{qV_{BE}}{kT}\right) \quad (2.27)$$

In this equation the  $\overline{D_n}$  is the average diffusion constant of the minority carrier in the emitter;  $L_n$  is the diffusion length of it.  $N_a$  is the emitter acceptor doping concentration and  $n_{iE}$  is the intrinsic carrier concentration in this region. To increase the emitter injection efficiency: there are two approaches. Either by increasing  $N_a$  to decrease the  $I_B$ , as shown in equation 2.27. Or decreasing the base-emitter width  $x_B$ , as illustrated in 2.15 so that the collector current becomes larger while the base current remains the same.

The base transport factor is defined as the ratio of minority carrier flux to the collector and the minority carrier flux entering the base from the emitter. Under the assumption that B-E junction are forward biased efficiently so that  $\exp\left(\frac{qV_{BE}}{kT}\right)$  is larger than 1, and the assumption that base width  $x_B$  is way smaller than the minority carrier diffusion length  $L_B$ , the base transport factor can be approximated as:

$$\alpha_T = \frac{1}{\cosh\left(\frac{x_B}{L_B}\right)} = \frac{1}{1 + \frac{1}{2}(x_B/L_B)^2} = 1 - \frac{1}{2}(x_B/L_B)^2 \quad (2.28)$$

The third factor of the  $\delta$  concerns the recombination in the base-emitter junction region, emitter-base channel, and the surface recombination. Processing defects yield surface traps and other traps and result in a current component

$$I_{B3} \propto \exp\left(\frac{qV_{BE}}{n_E kT}\right) \quad (2.29)$$

$n_E$  is the low-current forward emission coefficient. It ranges from 2 to 4 depending on the density of the current. The only factor that does not have the same relationship with  $V_{BE}$  as the collector current is  $\delta$ . At high currents, the base current from recombination indicated by  $\delta$  is negligible, making a high  $\beta$  and also the same emitter and collector current ratios. But at the low current scenario, the impact of  $\delta$  becomes dominant and hence the emitter and collector ratios become twisted.

To wind up, if the BJT has a range where  $\beta_T$  is constant regardless of the applied current, then this current range provides optimal PTAT performance. In the substrate PNP BJT in the CMOS industry, it provides such a range. In our test of the SiC counterpart, such a range should be measured to verify the device's capacity for PTAT temperature measuring application.

### 2.3.3. BJT'S TEMPERATURE DEPENDENCE

In section 2.2, equation 2.7 gives the expression of the saturation current in a diode at an ideal situation. A BJT is in essence two diode connected together. However, their  $I_C - V_{BE}$  characteristics are different. Consider an NPN transistor operating in forward active region. The injection of electrons into the base induces a minority carrier concentration  $n_{p,em}$  at the emitter side. It is larger than the equilibrium minority carrier in the base, but still way smaller than the majority carrier concentration (the low-injection assumption). The carrier concentration is proportional to the exponential  $V_{BE}$ , its expression is given by:

$$n_{p,em} = n_{p0} \cdot \exp\left(\frac{qV_{BE}}{kT}\right) \quad (2.30)$$

Such an exponential term results from The Boltzmann approximation to the Fermi-Dirac distribution function. The equilibrium minority carrier concentration is given by:

$$n_{p0} = \frac{n_i^2}{N_a} \quad (2.31)$$

$n_i$  is the intrinsic carrier concentration, and  $N_a$  is the acceptor concentration in the base.

As we have discussed in subsection 2.3.1, if the base width is small compared with minority carrier diffusion length  $L_n$  and the base-collector junction is reversely biased. Then the minority carrier concentration at the collector side of the base region is zero. The diffusion of electrons could be simplified as a linear process, the diffusion current is:

$$I_C = \frac{qA\overline{D_n}n_{p,em}}{W_B} \quad (2.32)$$

$A$  is the emitter area,  $\overline{D_n}$  is the average diffusion constant.  $W_B$  is the width of the base region.

Combining equation 2.30, equation 2.31 and equation 2.32, we have the classical  $I_C - V_{BE}$  characteristics.

$$I_C = I_S \cdot \exp\left(\frac{qV_{BE}}{kT}\right) \quad (2.33)$$

The saturation current is given by:

$$I_S = \frac{qAn_i^2\overline{D_n}}{W_B N_a} \quad (2.34)$$

In the denominator  $W_B N_a$  is the so-called Gummel characteristics  $G_B$ , it tells the number of impurities per unit area. When the doping is not uniform, it is the integral of doping concentration over the base width. The average electron diffusion constant appears from the Einstein relation:

$$\frac{\overline{D_n}}{\overline{\mu_n}} = \frac{kT}{q} \quad (2.35)$$

And the saturation current can thus be expressed as

$$I_S = \frac{kTA n_i^2 \overline{\mu_n}}{G_B} \quad (2.36)$$

Now we have derived  $I_S$ , let us investigate how the individual terms are related to temperature. The equation could be then rewritten as:

$$I_S(T) = \frac{kTA n_i^2(T) \bar{\mu}_n(T)}{G_B(T)} \quad (2.37)$$

The intrinsic carrier concentration's dependency on temperature is given by

$$n_i^2(T) \propto T^3 \exp\left(\frac{-qV_g(T)}{kT}\right) \quad (2.38)$$

$V_g(T)$  is the band-gap voltage of the material. We can assume that  $V_g(T)$  is a linear function at this moment

$$V_g(T) = V_{g0} - \alpha T \quad (2.39)$$

$V_{g0}$  is the extrapolated band gap voltage at 0 K[19]. The effective electron mobility  $\mu_n$  is proportional to  $T^{-n}$ , and  $n$  is a constant. Because of the bandwidth modulation effect, the Gummel number is in reality dependent on temperature. But for the sake of discussion, at this moment we assume that the Gummel number is constant at different temperatures. When putting together the temperature dependencies of all those terms, the saturation current can be written as

$$I_S(T) = CT^\eta \exp\left(\frac{-qV_{g0}}{kT}\right) \quad (2.40)$$

$\eta = 4 - n$  and  $C$  is a constant. When putting equation 2.40 into equation 2.33, we have the  $I_C$  characteristics dependent on temperature

$$I_C(T) = CT^\eta \cdot \exp\left(\frac{q(V_{BE}(T) - V_{g0})}{kT}\right) \quad (2.41)$$

It could be rewritten as

$$V_{BE}(T) = V_{g0}\left(1 - \frac{T}{T_r}\right) + \frac{T}{T_r}V_{BE}(T_r) - \eta \frac{kT}{q} \ln\left(\frac{T}{T_r}\right) + \frac{kT}{q} \ln\left(\frac{I_C(T)}{I_C(T_r)}\right) \quad (2.42)$$

In the equation,  $V_{BE}(T_r)$  is the base-emitter voltage at the reference temperature  $T_r$

In the Spice simulation to verify this model, it is found that there is a great discrepancy between the measurement result and the model prediction. The difference is usually in the order of several microvolts. Tsividis proposed that this difference originated from the inaccurate assumption we made in equation 2.39. He gave another model of  $V_g(T)$ , which reduces the inaccuracy by an order of magnitude[20]. In Meijer's work, it is demonstrated that the inaccuracy is further reduced to less than 0.1 ,microvolt if  $\eta$  and  $V_{g0}$  in equation 2.42 are derived from the measured  $V_{BE}(T)$  data[21]. Those derived values of  $\eta$  and  $V_{g0}$  are often found in conflict with the physics discussed above. The  $\eta$  is found at 4.3, but since  $\eta = 4 - n$  it is not allowed to be bigger than 4. Such a discrepancy resulted from the inaccurate physical models such as the temperature dependency of  $V_g$  in equation 2.39.

Meijer also proposes another interesting aspect of presenting his model. He presents equation 2.42 as a linear approximation with a nonlinear curvature residue:

$$V_{BE}(T) = \underbrace{V_{BE0} - \lambda T}_{\text{tangent at } T=T_r} + c(T) \quad (2.43)$$

$T_r$  is a reference temperature, it could be any random temperature at which the  $V_{be}$  is measured.  $c(T)$  is the non-linearity; from the Fourier transform of equation 2.42, it is derived as:

$$c(T) = \frac{k}{q} \eta \left( T - T_r - T \ln \left( \frac{T}{T_r} \right) \right) + \frac{k}{q} \left( T \ln \left( \frac{I_C(T)}{I_C(T_r)} \right) - (T - T_r) \frac{T_r}{I_C(T_r)} \left[ \frac{\partial I_C}{\partial T} \right]_{T=T_r} \right) \quad (2.44)$$

$\lambda$  is the slope of the tangent line from temperature  $T_r$ .

$$\lambda = \frac{V_{BE0} - V_{BE}(T_r)}{T_r} \quad (2.45)$$

$V_{BE0}$  is the extrapolation of the tangent line to zero temperature. To calculate it, refer to equation 2.44 and equation 2.42 we have:

$$\begin{aligned} V_{BE0} &= V_{g0} - c(0) \\ &= V_{g0} + \frac{k T_r}{q} \left( \eta - \frac{T_r}{I_C(T_r)} \left[ \frac{\partial I_C}{\partial T} \right]_{T=T_r} \right) \end{aligned} \quad (2.46)$$

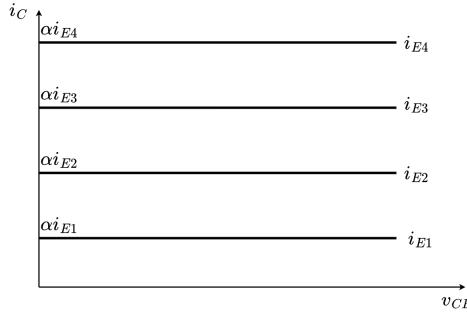

Figure 2.11: On the left is the temperature dependency of base emitter voltage (the curvature is exaggerated), on the right is the curvature at different  $(\eta - m)$ ,  $T_r = 300$  K, source[22]

Figure 2.11 shows the  $V_{BE}$  and the curvature based on the model. In the data gathered from CMOS processing by Wang the curvature from temperature  $-50^{\circ}$  to  $125^{\circ}$  mounts to 4 micro volt[23], which is in line with the model's prediction.

## 2.4. RATIO METRIC TEMPERATURE MEASUREMENT

As discussed in section 2.2 and section 2.3, the performance of both devices as a temperature sensor is not perfect regarding their linearity. This section presents the ratiometric

measurement techniques to tackle this issue. Subsection 2.4.1 gives the theoretical concept for reducing non-linearity. Subsection 2.4.2 presents the circuit implementation in our research work.

## 2

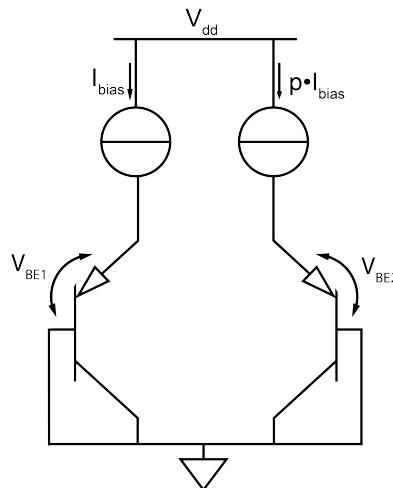

### 2.4.1. PROPORTIONAL TO ABSOLUTE TEMPERATURE

All device characteristics in integrated circuits depend on temperature, the mechanisms of temperature sensors hence are largely based on the temperature dependency of devices; such as resistors[24], [25], diodes[26], MOS transistors[27], and bipolar junction transistors (BJT)[28], [29]. Most devices' characteristic on temperature, however, are non-linear and have offset. One solution is to use a reference signal and compare the measured signal to the reference[30]. In other words, the difference in base-emitter voltage  $\Delta V_{BE}$  between two transistors is PTAT should these two transistors be biased at different current densities. Figure 2.12 gives an example of the proportional to absolute temperature set up with a Bipolar Junction Transistor.

Figure 2.12: the PTAT configuration of two diodes

In the simplest model, the voltage across a diode is related to the thermal voltage  $\frac{kT}{q}$  and the current through the diode, as shown in equation 2.47

$$V_D = \frac{kT}{q} \ln\left(\frac{I_D}{I_S}\right) \quad (2.47)$$

As discussed in subsection 2.3.2, equation 2.40 illustrates that saturation current is exponentially dependent on temperature at different biasing conditions. Therefore, a single diode or BJT's output voltage in regard to temperature is non-linear. The ratiometric measurement method applies two current  $I_D = I_1$ , and  $I_D = p \cdot I_1$  to a diode consecutively. The difference in the voltage drops is given by[31]

$$\Delta V = \frac{kT}{q} \ln\left(\frac{I_1}{I_S}\right) - \frac{kT}{q} \ln\left(\frac{p \cdot I_1}{I_S}\right) = -\frac{kT}{q} \ln(p) \quad (2.48)$$

Figure 2.13: Three schematics of the temperature sensor

Theoretically, the saturation current is cancelled and the output temperature is PTAT with high linearity. Another option is to inject currents of different amplitudes into devices of same fabrication batch. In this manner the process variation is minimized. Furthermore, this measurement technique gives designer the possibility to increase the temperature sensor's output voltage amplitude with area design.

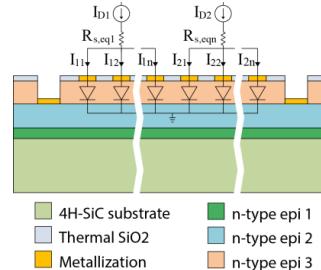

### 2.4.2. CIRCUIT LEVEL DESIGN

This section presents the two schematics of temperature sensor. In schematic one, the area ratio of the top two transistors is different from the that of the bottom two transistors. On the left arm, output voltage is  $\frac{1}{n+1}$  of  $V_{dd}$ ; on the right arm output voltage is  $\frac{n}{n+1}$  of  $V_{dd}$ . The differential output voltage is then  $\frac{n-1}{n+1}$  of  $V_{dd}$ . The output voltage is in the same amplitude of  $V_{dd}$  when  $n$  is large enough, therefore there is no need for additional amplifier to process the signal. In schematic two, the external bias sets the current of those two arms at exactly a ratio of 3:1; hence the linearity is expected to be better than schematic one. Schematics three tests the diode temperature sensor with external current source. Its disadvantage is the external precise current meter needed.

# 3

## DEVICE DESIGN AND SIMULATION

*This chapter documents the establishment of the device level model of the SiC BJT. Section 3.1 introduces the simulation setup; section 3.2 presents a selection of the physics models involved for reader's reference. In section 3.3 the simulation result and its analysis is given.*

### 3.1. SIMULATION SETUP

In the semiconductor device development flow, the Technology Computer Aided Design (TCAD) aims to give an accurate prediction of devices' thermal, electrical, and physical characteristics. The whole process consists of process simulation and device simulation. Process simulation sketches the dopant profile, device geometry, and stress profiles of the device; it serves as a prerequisite for device simulation, which concerns the electrical characteristics.

3

In this design, Synopsys Sentaurus is chosen as the TCAD tool. In addition to the process and device simulation, the software suit also has visualization instruments to support inspection. Originally from the Standard University Processing Modelling program, it was created by combining features of existing process simulation tools in 2004. Industrial partners include Samsung Electronics, Infineon Technologies, PowerJazz, Onsemi, and so on.

### 3.2. PHYSIC MODELS

Appropriate physics models in TCAD Sentaurus give accurate simulation results with the fabricated device. Here the physics models concerning a Bipolar Junction transistor's performance are presented, those physical models give directions in device designs and insights.

#### 3.2.1. BAND GAP NARROWING(BGN)

When a high concentration of doping is injected into the material, the orbitals of impurities start to overlap. As a result, the discrete energy levels of impurities start to form an energy band. Additionally, random distribution of impurities also results in potential fluctuations and hence a broadened impurity band. Ionization energy level of impurity is therefore reduced. When the impurity band overlaps with the valence or conduction band, the band-gap energy is narrowed[33], [34]. In the research work carried out by Schubert, it is pointed out that such a phenomenon is particularly pronounced when doping exceeds  $10^{17} \text{ cm}^{-3}$ [35]. In our design doping of emitter and collector ohmic layers both exceed  $10^{18} \text{ cm}^{-3}$ ; hence BGN is important in understanding the device's characteristics in the data analysis of the next chapter.

By default Synopsys models the density of states with the following equations:

$$g_c(E) = \frac{dN_c(E)}{dE} = \frac{1}{2\pi^2} \left( \frac{2m^*}{\hbar^2} \right)^{3/2} (E_g - E_c)^{1/2} \quad (3.1)$$

$$g_v(E) = \frac{1}{2\pi^2} \left( \frac{2m_h^*}{\hbar^2} \right)^{3/2} (E_v - E_g)^{1/2} \quad (3.2)$$

the band gap energy should vary as a function of the doping level. In our simulation we adopt the classical Slotboom model[19]:

### SLOTBOOM MODEL

The change in the band gap energy is

$$\Delta E_g = E_{ref} \left( \ln \left( \frac{N_I}{N_{ref}} \right) + \sqrt{[\ln(\frac{N_I}{N_{ref}})]^2 + \frac{1}{2}} \right) \quad (3.3)$$

In equation 3.3  $N_I = N_a + N_d$ , and the other parameters are material properties. The fraction of band gap narrowing taken up by the conduction is also considered material-specific, in silicon, it is 0.5.

However, in Donna's research, it is suggested that the slotboom model is not accurate enough to predict the diode's forward characteristics[36]. The authors proposed that the model provided by Schubert gives better accuracy[37]:

### SCHUBERT MODEL

$$\Delta E_g = \frac{-q^2 \beta}{4\pi\epsilon_0\epsilon_r} \quad (3.4)$$

In this model  $\beta$  is the Tomas-Fermi Screening length. In the data analysis part of the next chapter, the accuracies of those two models will be verified.

#### 3.2.2. INCOMPLETE IONIZATION

Incomplete ionization refers to the situation when the temperature within a semiconductor is so low that the donor or acceptor impurity atoms are not fully activated. The carrier concentration will hence not be the same as the dopant concentration. For nitrogen donors or aluminum acceptors in silicon carbide, the impurity energy levels are deeper than the thermal energy  $k \cdot T$ . Incomplete ionization should thus be taken into account in these cases.

Fermi-Dirac distribution describes the concentration of the ionized impurity atoms:

$$N_D = \frac{N_{D,0}}{1 + g_D \exp\left(\frac{E_{F,n} - E_D}{kT}\right)} \quad (3.5)$$

$$N_A = \frac{N_{A,0}}{1 + g_A \exp\left(\frac{E_A - E_{F,p}}{kT}\right)} \quad (3.6)$$

In Equation 3.5 and Equation 3.6  $N_{D,0}$  and  $N_{A,0}$  are the substitution donor and acceptor concentrations.  $g_D$  and  $g_A$  are the degeneracy factors for impurity levels.  $E_D$  and  $E_A$  are the activation energies. In another model proposed by Matsuura [38], the general distribution function for the incomplete ionization is given as

$$N_D = \frac{N_{D,0}}{1 + G_D(T) \exp\left(\frac{E_{F,n} - E_C}{kT}\right)} \quad (3.7)$$

$$N_A = \frac{N_{A,0}}{1 + G_A(T) \exp\left(-\frac{E_{F,p} - E_V}{kT}\right)} \quad (3.8)$$

The  $G_D(T)$  and  $G_A(T)$  are the ionization factors proposed in [39] and [40]. In the lower part of our measurement range incomplete ionization might contribute to some deviant behaviors of the temperature sensor.

### 3.2.3. RECOMBINATION MODELS

The rate at which the electrons and holes recombine plays an important role in devices' characteristics. This is especially important for Silicon carbide BJTs as abundant surface traps are present at the interface of silicon carbide and oxide [16], [41], [42].

In thermal equilibrium situation, and under the assumption of low-injection, the recombination rate is inversely proportional to the mean carrier lifetime. In a piece of infinitely large p-type material the thermal-equilibrium recombination rate is given as[17]:

$$3 \quad R'_n = -\frac{d\delta_n(t)}{dt} = \alpha_r p_0 \delta_n(t) = \frac{\delta_n(t)}{\tau_{n0}} \quad (3.9)$$

$\tau_{n0}$  is the minority carrier lifetime and under this circumstance, it is simply related to  $\alpha_r$  and minority carrier concentration.

During device fabrication there are always defects on the lattice and the ideal periodic potential function is no longer valid. If the concentration of the defects within the material is not great, they will create discrete energy states within the forbidden-energy band gap. Otherwise, those states need to be accounted for explaining some unexpected results.

In the following sections, the impact those states have on the device's behavior will be investigated.

#### SCHOCKLEY-REAL-HALL MODEL (SRH) OF RECOMBINATION

An allowed energy state within the forbidden band gap is called a trap and it acts as a recombination center. The electrons and holes will get captured by the center with equal probability. In the Shockley-Real-Hall model, the energy of the trap is assumed to be  $E_t$ . There are four basic processes[17]:

- Process 1: the capture of an electron from an conduction band by an initially empty trap.

- Process 2: the emission of an electron that is from an occupied trap back to the conduction band.

- Process 3: the capture of a hole from the valence band by a trap containing an electron ( we could also consider it in another way, there is an electron emission from the trap into the valence band.

- Process 4 is the other way of process 3: the emission of a hole from a neutral trap into the valence band. (Or there is an electron from the valence band being captured by the trap)

In process 1, the rate of combination is proportional to the density of electrons in the conduction band and the density of empty trap states. The capture rates are given by:

$$R_{cn} = C_n N_t [1 - f_F(E_t)] n \quad (3.10)$$

In equation 3.10,  $R_{cn}$  is the capture rate ( $\#/cm^3 - s$ ) and  $C_n$  is the constant proportional to the electron-capture cross section;  $N_t$  is the total concentration of trapping centers

and  $n$  is the electron concentration in the conduction band.  $f_F(E_t)$  is the fermi function at the trap energy level. More specifically,

$$f_F(E_t) = \frac{1}{1 + \exp\left(\frac{E_t - E_F}{kT}\right)} \quad (3.11)$$

It gives the probability that an electron is present inside the trap.  $[1 - f_F(E_t)]$  is then the probability that a trap is empty.

For process 2, the rate at which the electrons emit from the traps is proportional to the density of filled traps.

$$R_{en} = E_n N_t f_F(E_t) \quad (3.12)$$

In the equation

$R_{en}$  = emission rates ( $\#/cm^3 - s$ )

$E_n$  = constant

$f_F(E_t)$  = the probability that the trap is occupied.

Under thermal equilibrium, the emission of electrons from the traps should be the same as the capture of electrons from the conduction band. Therefore we have:

$$E_n N_t f_F(E_t) = C_n N_t [1 - f_{F0}(E_t)] n_0 \quad (3.13)$$

$f_{F0}$  denotes the thermal-equilibrium Fermi function. In this case, the  $n_0$  is the electron concentration in the conduction band at thermal equilibrium. With Boltzmann approximation, we could write  $E_n$  in terms of  $C_n$  as

$$E_n = C_n n' \quad (3.14)$$

$n'$  is equivalent to the concentration of electrons that would have existed if the quasi-Fermi energy level  $E_F$  coincided with trap energy level  $E_t$ .

$$n' = N_c \exp\left[\frac{-(E_c - E_t)}{kT}\right] \quad (3.15)$$

it is equivalent to the electron concentration if the Fermi energy level is at  $E_t$ .

Now we have discussed the situation of thermal equilibrium. Let's investigate the non-equilibrium scenarios. In this case, the excessive electrons exist; so the net rate of electrons captured from the conduction band is given by:

$$R_n = [C_n N_t (1 - f_F(E_t)) n] - [E_n N_t f_F(E_t)] \quad (3.16)$$

It is noteworthy that in non-equilibrium scenarios,  $n$  refers to the total electron concentration, including the thermal-equilibrium one and the excessive concentration. Also, the Fermi energy level in the Fermi probability function should be replaced by the quasi-Fermi energy. Given the relation of  $E_n$  and  $n'$  in equation 3.14, the net combination rate is given as:

$$R_n = C_n N_t [n (1 - f_F(E_t)) - n' f_F(E_t)] \quad (3.17)$$

And in the case of process 3 and process 4, the net rate holes captured from the valence band are given by

$$R_p = C_p N_t [p f_F(E_t) - p' (1 - f_F(E_t))] \quad (3.18)$$

Where  $C_p$  is a constant proportional to the hole-capture cross-section, and  $p'$  is the hole concentration in valence band in non-equilibrium, including the excess hole concentration:

$$p' = N_v \exp \left[ \frac{-(E_t - E_v)}{kT} \right] \quad (3.19)$$

If the trap density is not too large, the excess hole and electron concentration should equal; so do the combination rate of electrons and capture rate of holes. Put equation 3.16 and equation 3.18 in equal and solve the Fermi function, we have

3

$$f_F(E_t) = \frac{C_n n + C_p p'}{C_n (n + n') + C_p (p + p')} \quad (3.20)$$

In equation 3.15 and equation 3.19, it is figured out that  $n' p' = n_i^2$ . Substituting equation 3.20 into equation 3.17 or equation 3.18, the recombination rate of electrons and holes due to the traps at energy level  $E_t$  is:

$$R_n = R_p = \frac{C_n C_p N_t (np - n_i^2)}{C_n (n + n') + C_p (p + p')} \equiv R \quad (3.21)$$

In the case of thermal equilibrium, we have  $np = n_i^2$ . Then equation 3.21 is zero. It represents the recombination rate of excess electrons and holes. Now that  $R$  in equation is the recombination rate of both electrons or holes:

$$R = \frac{\delta n}{\tau} \quad (3.22)$$

Similar to equation 3.9,  $\delta n$  is the excess carrier concentration, and  $\tau$  is the excess carrier lifetime.

### SIMPLIFICATION OF SRH MODEL

The previous section gives the deduction of the Shockley-Real-Hall model; in the end, equation 3.21 gives the accurate recombination rate of electrons and holes at a certain energy level.

Nevertheless, equation 3.21 could be simplified under certain conditions. In the example of an n-type extrinsic material those two assumptions are:

- Low injection, which means the concentration of excess minority carriers is significantly lower than that of the minority carrier concentration.  $n_0 \gg p_0$ ,  $n_0 \gg \delta p$

- The trap energy level is near mid-band gap so that  $n'$  and  $p'$  will not differ from intrinsic carrier concentration greatly.  $n_0 \gg n'$ ,  $n_0 \gg p'$

With the above-mentioned assumptions, equation 3.21 is reduced to

$$R = C_p N_t \delta p \quad (3.23)$$

Again,  $C_p$  is the constant related to the hole capture cross-section. To associate recombination rate with mean life carrier lifetime. Comparing equation 3.23 with equation 3.22:

$$R = \frac{\delta n}{\tau} = C_p N_t \delta p \equiv \frac{\delta p}{\tau_{p0}} \quad (3.24)$$

The minority hole lifetime is then

$$\tau_{p0} = \frac{1}{C_p N_t} \quad (3.25)$$

If the trap concentration increase, the probability of excess holes recombining will increase; therefore, the minority carrier lifetime decrease.

Similarly, in the case of p-type material, under the assumption of high injection and heavy doping  $p_0 \gg n_0$ ,  $p_0 \gg \delta n$ ,  $p_0 \gg n'$ ,  $p_0 \gg p'$ , the minority carrier electron lifetime is given by:

$$\tau_{n0} = \frac{1}{C_n N_t} \quad (3.26)$$

Comparing equation 3.26 and equation 3.25, it is noteworthy that in the n-type material the minority carrier lifetime is related to the hole capture cross section while the minority carrier lifetime in the p-type material is related to the electron capture cross-section.

### 3.2.4. SURFACE EFFECTS

So far the development of theory depends on the assumption that semiconductor material is infinitely large. However, in real life, all the devices are fabricated on wafers and any semiconductor material should be diced. The sharp transition from solid material to a surface, for example, air, induced electrical states called surface states. The presence of those states impacts the base current density of a BJT. In this section, we address the origin of these states and investigate their recombination rate based on the SRH model discussed in subsection 3.2.3

In the SRH physics model, simple defects in the semiconductor will generate discrete energy states within the forbidden band gap. At the termination of the semiconductor, the periodic potential of the crystal lattice is disrupted. Such disruption leads to a distribution of energy states in the band gap. Figure 3.1 gives a schematic overview of the energy states.

Figure 3.1: Distribution of surface state energies in the band gap, source[17]

Equation 3.26 and equation 3.25 show that excess minority carrier lifetime is inversely proportional to the density of trap states. Traps density at the surface is larger than that at the bulk. Therefore the excess minority carrier lifetime on the surface is

smaller than that in the bulk. In the case of an extrinsic n-type semiconductor, the recombination rate of the excess carrier in the bulk, according to equation 3.24 is given by:

$$R = \frac{\delta p}{\tau_{p0}} \equiv \frac{\delta p_B}{\tau_{p0}} \quad (3.27)$$

In which  $\delta p_B$  is the bulk concentration of excess minority holes. A similar expression for the recombination rate at the surface is given by

3

$$R_s = \frac{\delta p_s}{\tau_{p0s}} \quad (3.28)$$

in which  $\delta p_s$  is the surface excess minority carrier hole concentration and  $\tau_{p0s}$  is the excess minority carrier lifetime at the surface.

If we assume that the generation rate of excessive carrier is the same throughout the semiconductor, then the recombination rate at the surface and bulk are also equal. This is because the generation rate and recombination rate are equal in equilibrium at a homogeneous semiconductor. If  $\tau_{p0s} < \tau_{p0}$ , then the excessive minority carrier concentration at the surface is smaller than the excessive minority carrier concentration at the bulk. In other words,  $\delta p_s < \delta p_B$ . There is a gradient of excessive carrier concentration from the bulk to the surface:

$$- D_p \left[ \hat{n} \cdot \frac{d(\delta p)}{dx} \right]_{\text{surf}} = s \delta p|_{\text{surf}} \quad (3.29)$$

$\hat{n}$  is a vector perpendicular to the surface. dimensional analysis reveals that the unit of  $s$  is  $\text{cm/s}$  Hence  $s$  is claimed as surface recombination velocity. When there is no difference between the surface and bulk excess carrier concentrations, then the gradient and zero and so is the surface recombination velocity. It is an indication of the surface characteristics compared with the bulk region.

In this section physics models concerning the device's performance are covered; in the next section. Geometries in the design are also presented and discussed to investigate the potential impact on devices' characteristics.

### 3.3. SIMULATION RESULT

During the simulation, different parameters of the device are changed to verify impact on the device's Gummel characteristics. Those parameters are base doping, collector doping, temperature, base thickness and metallization. The writer uses those simulation as a verification to deepen his understanding of semiconductor device physics theory. Also, the simulation results provide insights into device's design.

#### 3.3.1. GUMMEL CHARACTERISTICS

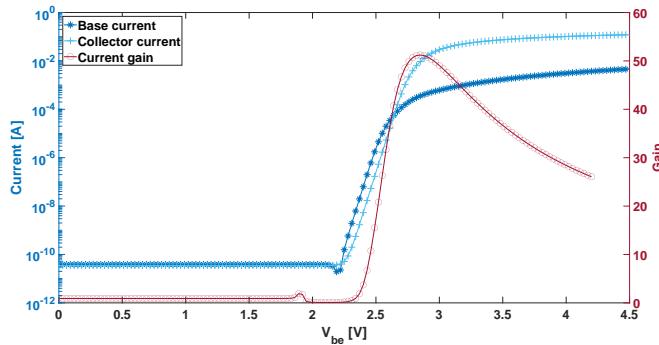

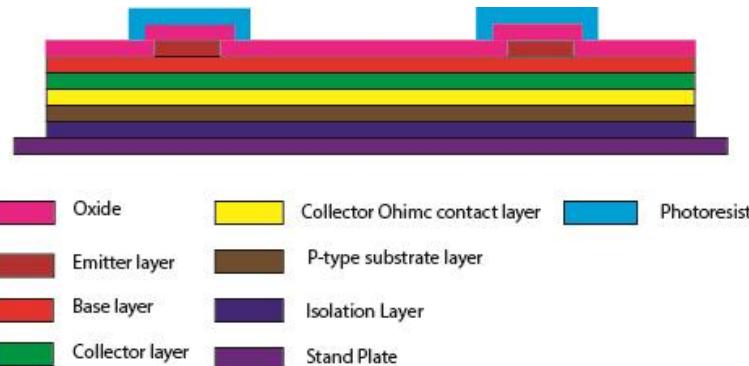

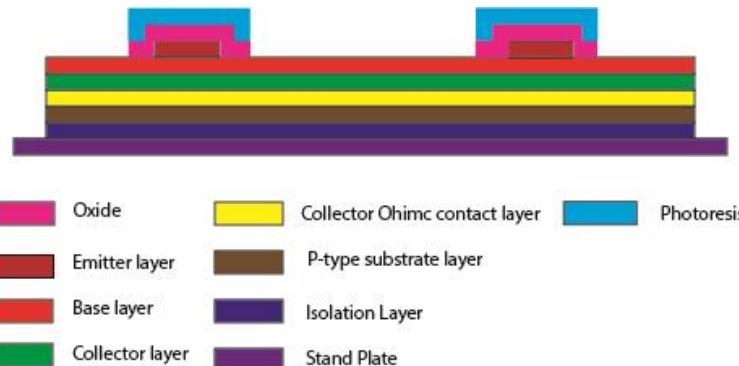

The Gummel plot depicts devices' base and collector currents versus the base emitter voltage. When different design parameters are tweaked, some unexpected phenomena happens. In this section, those phenomena are discussed with the knowledge presented in section 3.2 Figure 3.4 gives the zero device's Gummel characteristics at 300 Kelvin; further simulations reveal the conducting mechanism of the junction transistor.

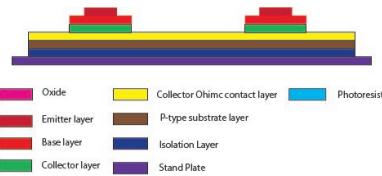

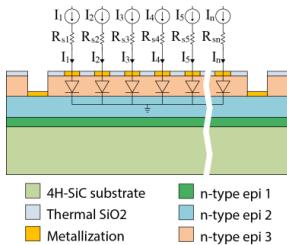

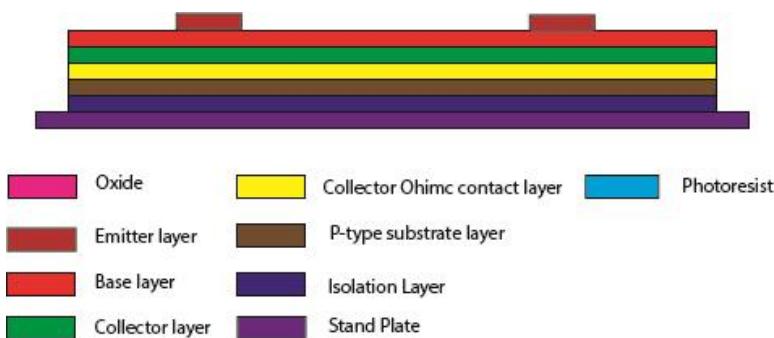

Figure 3.2: A diagram of the device

## IMPACT OF BASE DOPING

As observed from figure 3.5 the base current first reduces significantly when doping increases; at extremely high doping the base current rises again. As for the collector current, it displays the same changing pattern with base doping.

As discussed in section 2.3 the collector current results from the diffusion of minority carrier concentration across the base region; if doping in the base region increases, the minority carrier concentration should decrease following the low injection assumption.

There are two components of base current: one is due to the injection of minority carrier holes in the base region under the forward bias of the base-emitter junction. Another one results from the recombination of minority electrons and holes in the base region. The recombination current is a function of both the minority carrier concentration and the carrier lifetime.

$$i_{B1} = \frac{q A_E D_p n_i^2}{N_D L_P} e^{\nu_{BE}/V_T} \quad (3.30)$$

The injection of holes in the emitter remains the same; but the recombination current reduces significantly. It is explained in the width of the forward biased region. The width of the forward biased region is given in equation 3.41. The width decreases with doping and hence the recombination current in the region decreases.

Meanwhile, there is this argument about the electrons from the emitter will be pushed into the base, the minority carrier increases and the recombination should increase.

However, this happens at different time. What we compared, however, is what happened at the same time instance while the doping changed. Hence it is a paradoxical

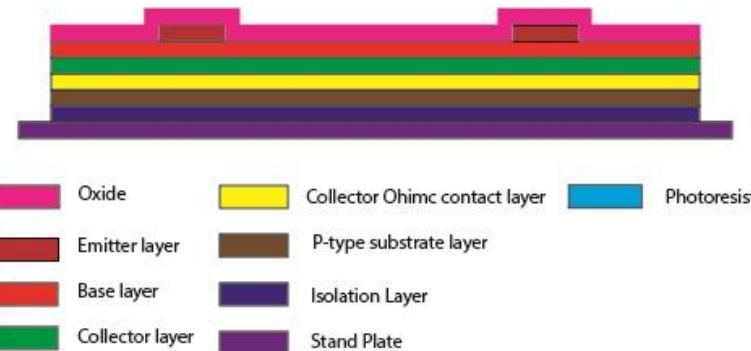

Figure 3.3: Illustration of the Mask

### Gummel Characteristics of Zero Device

Figure 3.4: Gummel Characteristics of generation zero 300K

question. Phenomenon explained.